Power transistor manufacture method

A technology for power transistors and fabrication methods, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as latch-up effect, unfavorable mass production, parasitic bipolar transistor turn-on, etc., to improve the ability to resist latch-up , The effect of large current driving capability and small on-resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

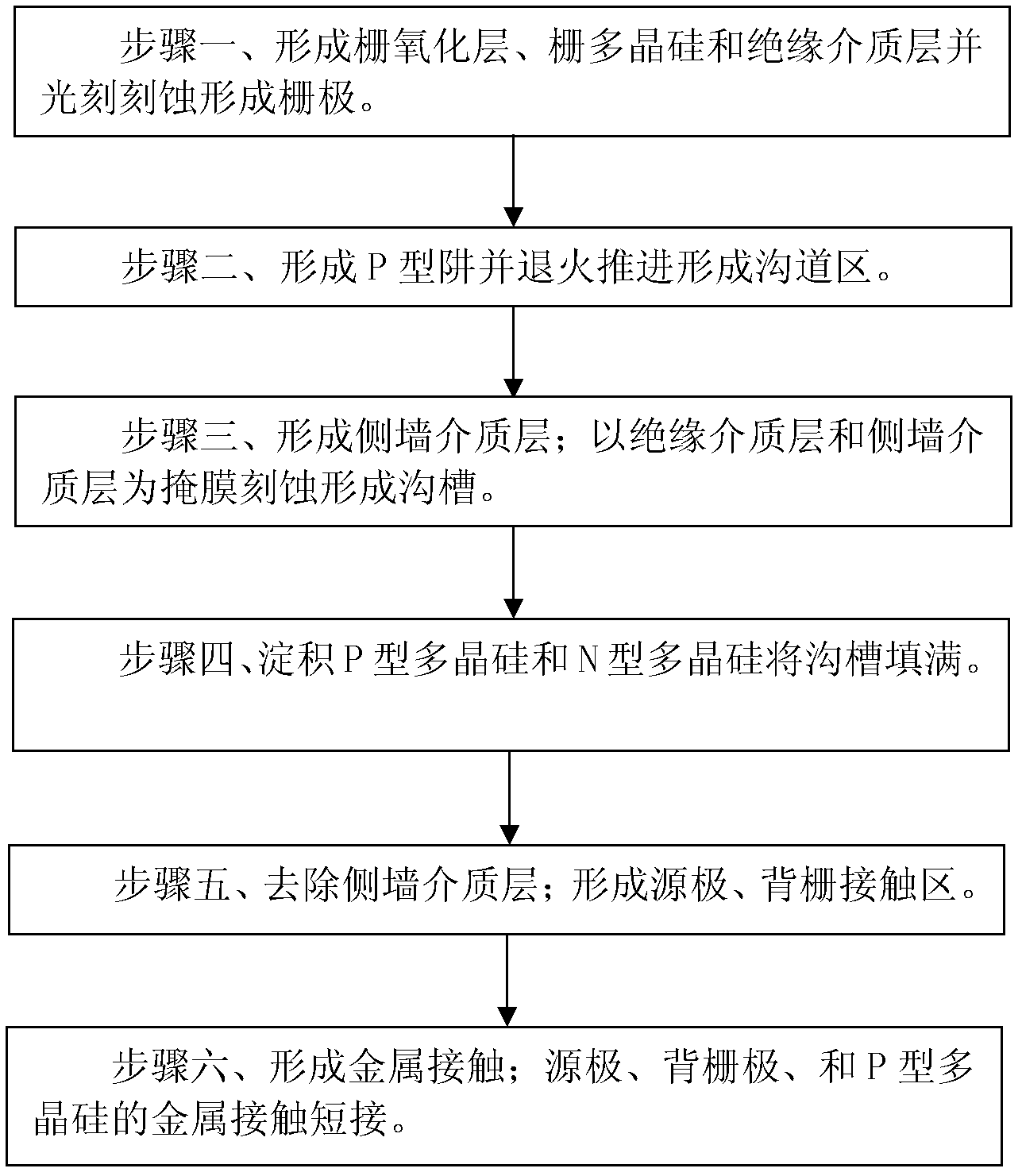

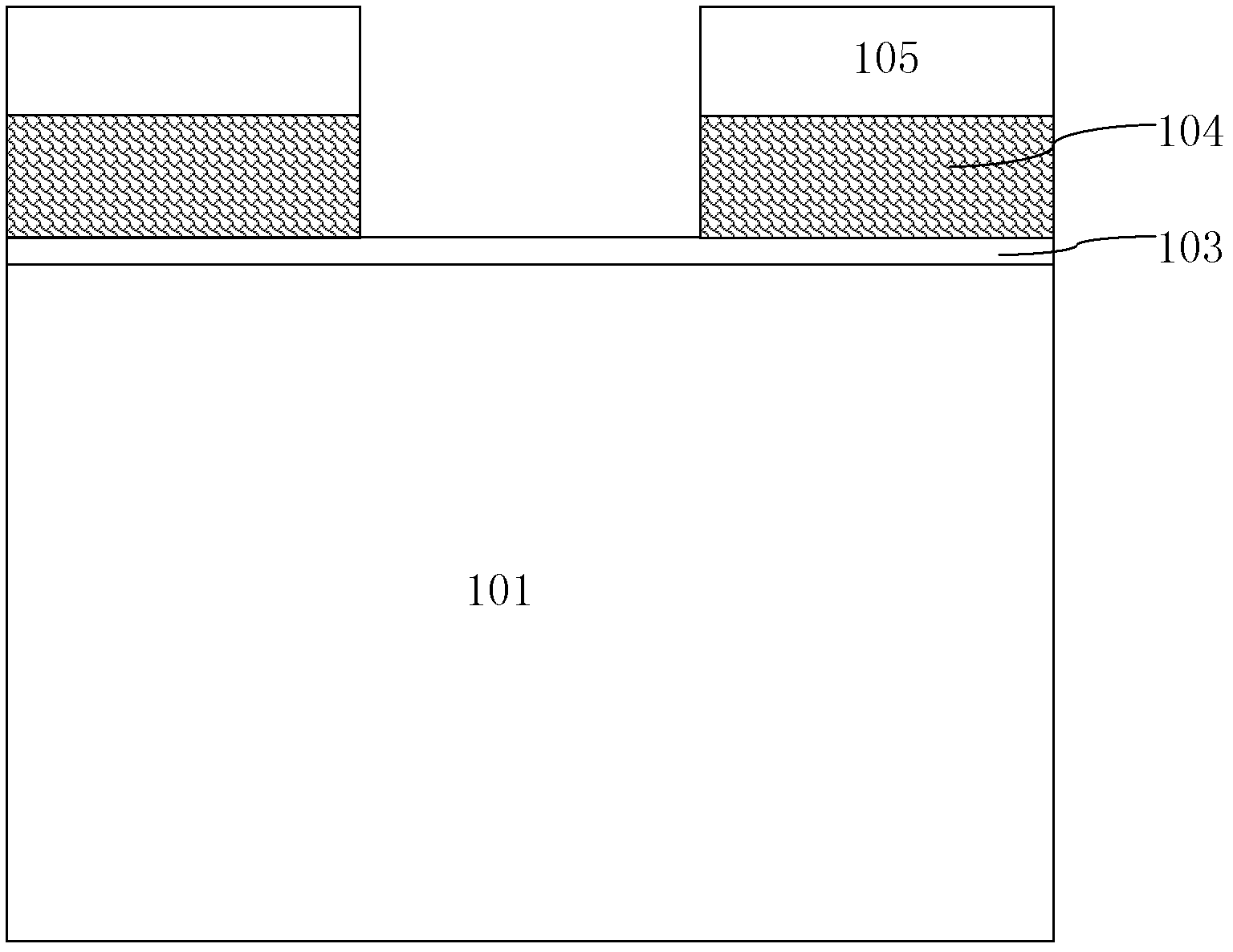

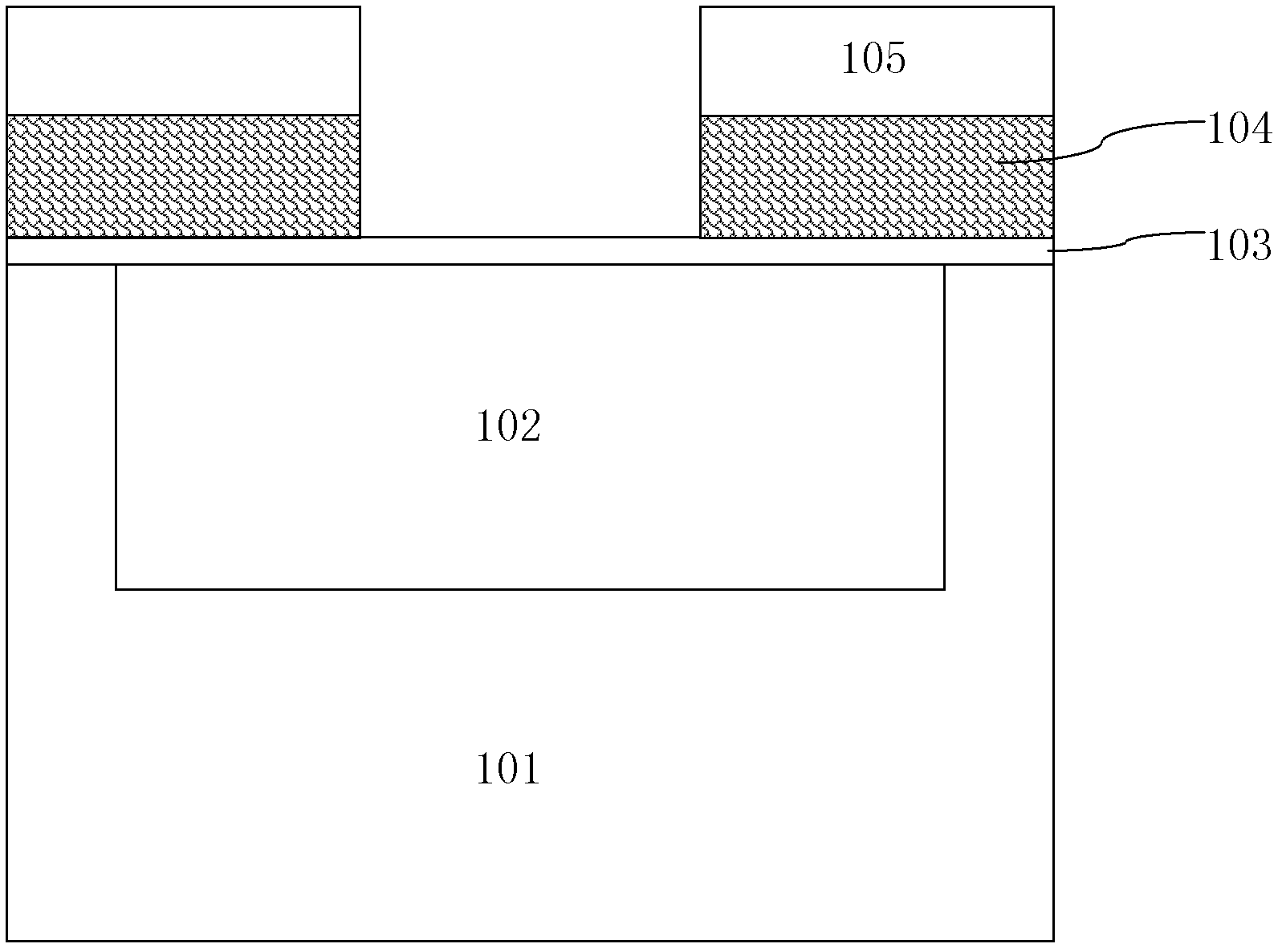

[0023] Such as figure 1 Shown is the flow chart of the method of the embodiment of the present invention; Figure 2 to Figure 7 Shown is a schematic diagram of the device structure in each step of the method of the embodiment of the present invention. The manufacturing method of the power transistor according to the embodiment of the present invention includes the following steps:

[0024] Step 1, such as figure 2 As shown, a gate oxide layer 103, a gate polysilicon 104 and an insulating dielectric layer 105 are sequentially formed on the surface of the N-type pressure receiving region 101 from bottom to top; the insulating dielectric layer 105 and the gate polysilicon 104 are etched performing etching to form the gate.

[0025] The isolated power transistor can be a silicon-based device or a compound semiconductor device. When the isolated power transistor is a silicon-based device, the N-type pressure receiving region 101 is a silicon epitaxial layer, or Czochralski sin...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More