IGBT having super junction structure and preparation method thereof

A gate trench and collector technology, applied in the field of IGBT, can solve problems such as large saturation voltage drop, and achieve the effects of reducing saturation voltage drop, increasing breakdown voltage, and shortening processing time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

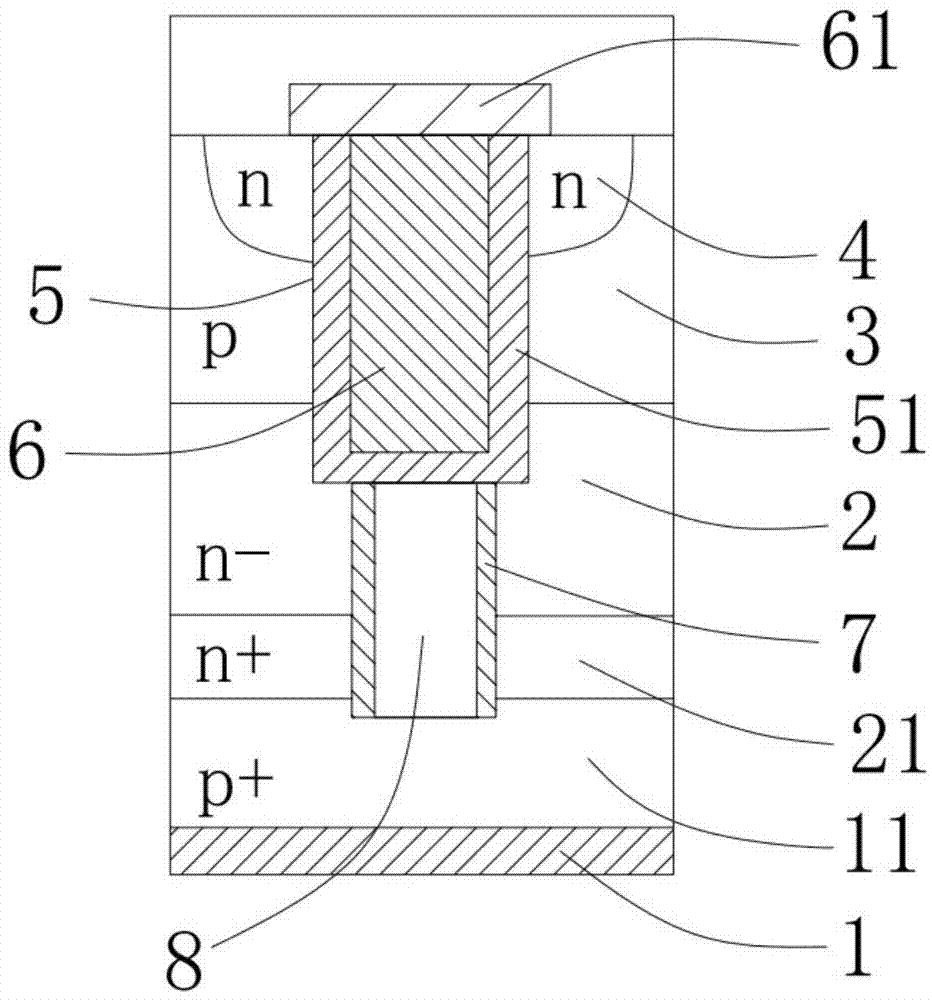

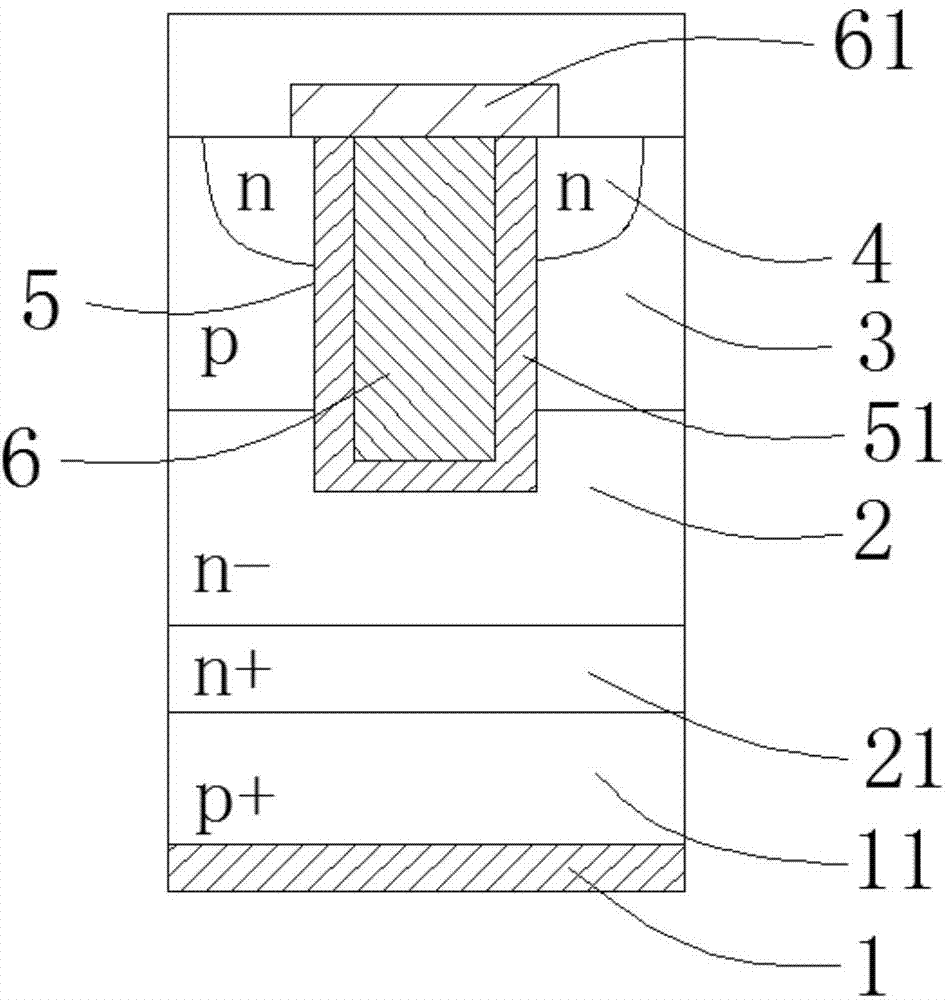

[0030] Such as figure 1 As shown, an IGBT with a super junction structure, the IGBT with a super junction structure includes a collector 1, a drift region 2, a P-type base region 3 and an N-type emitter region 4, and the P-type base A gate trench 5 is provided in the region 3 and the N-type emitter region 4, a gate electrode 6 is provided in the gate trench 5, and a P-type electrode 6 is provided between the bottom of the gate trench 5 and the collector elect...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More