Patents

Literature

59 results about "Trench igbt" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Semiconductor device

ActiveUS20090020852A1Guaranteed uptimeIncrease marginTransistorTrench igbtElectrical resistance and conductance

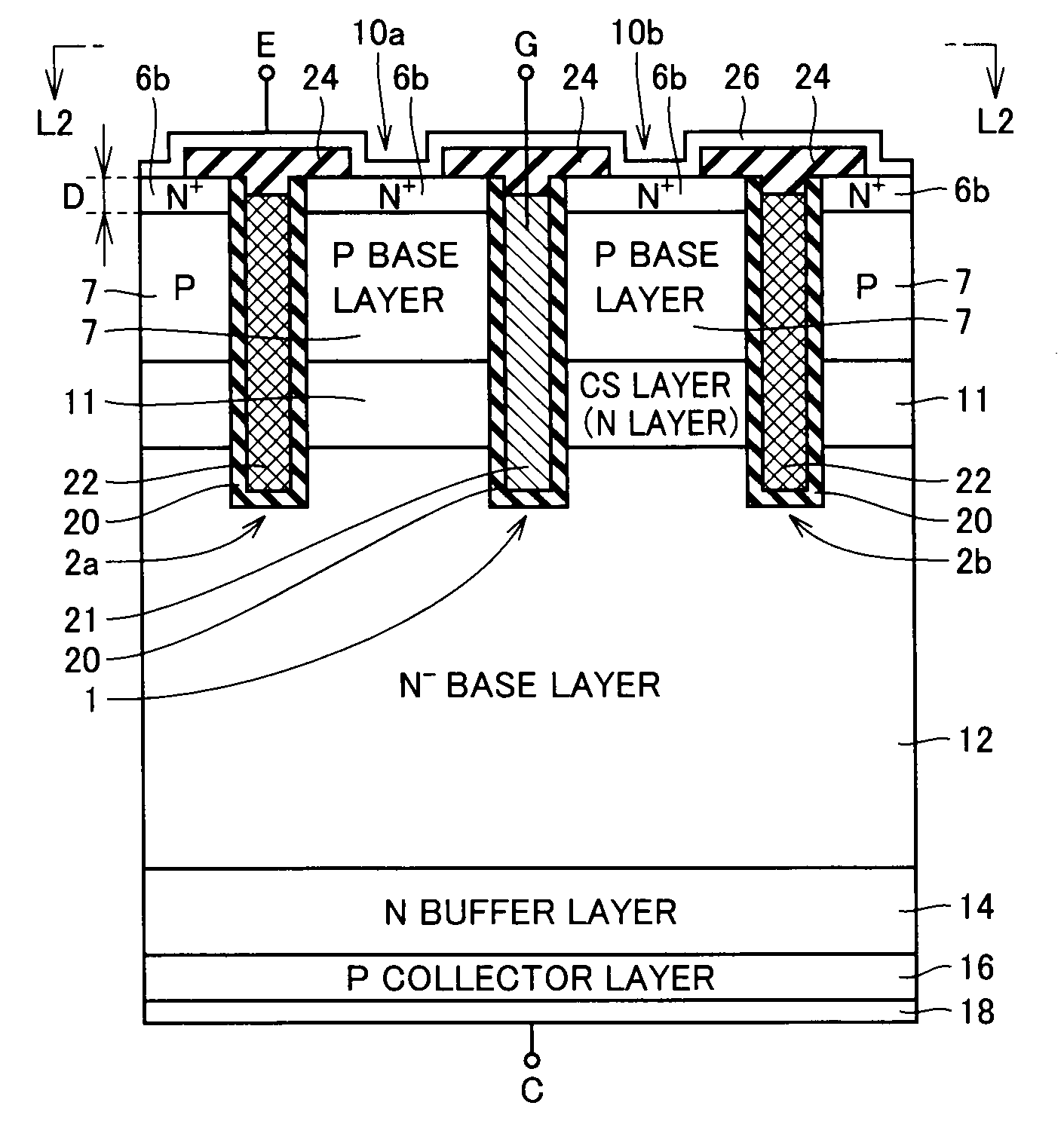

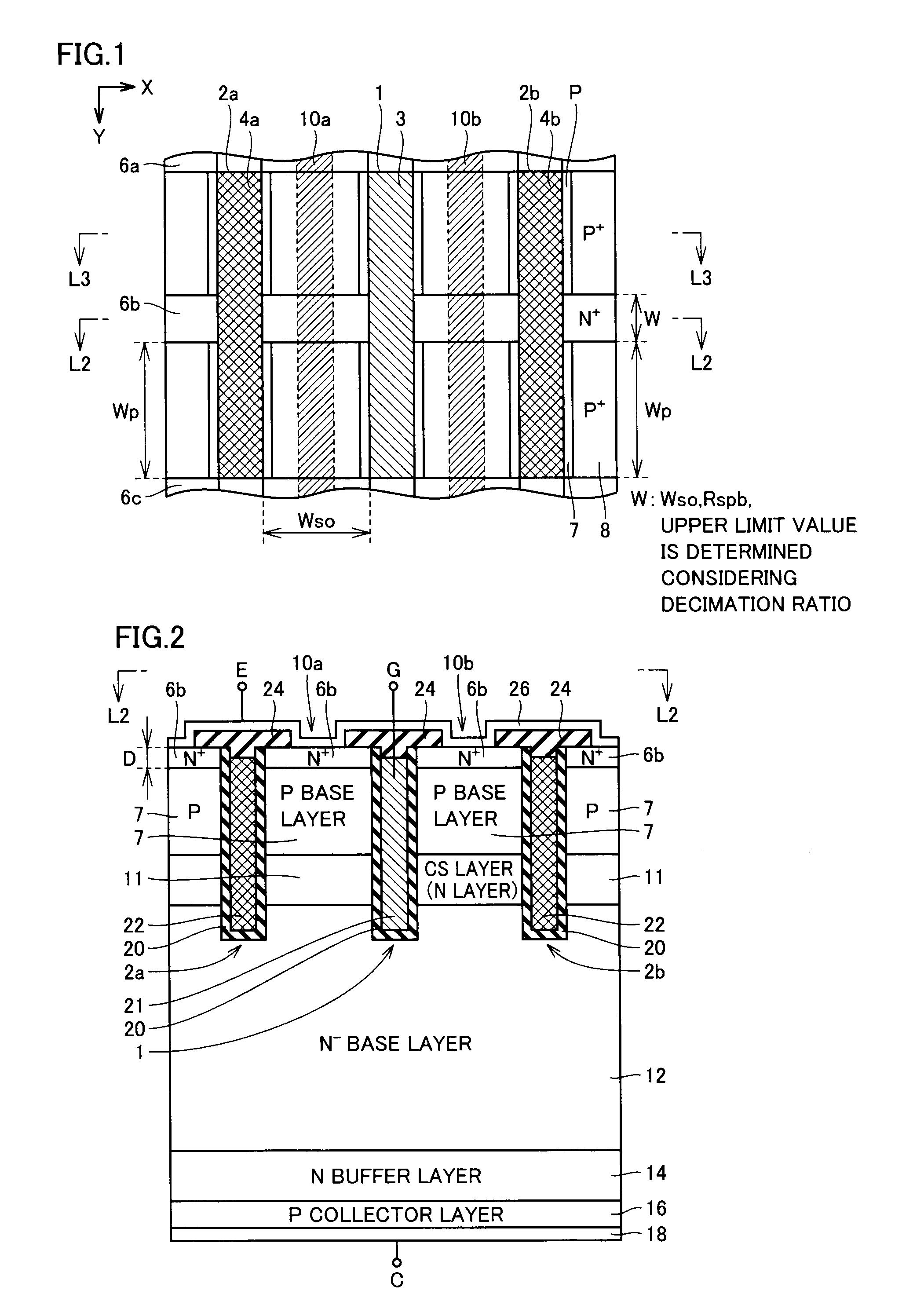

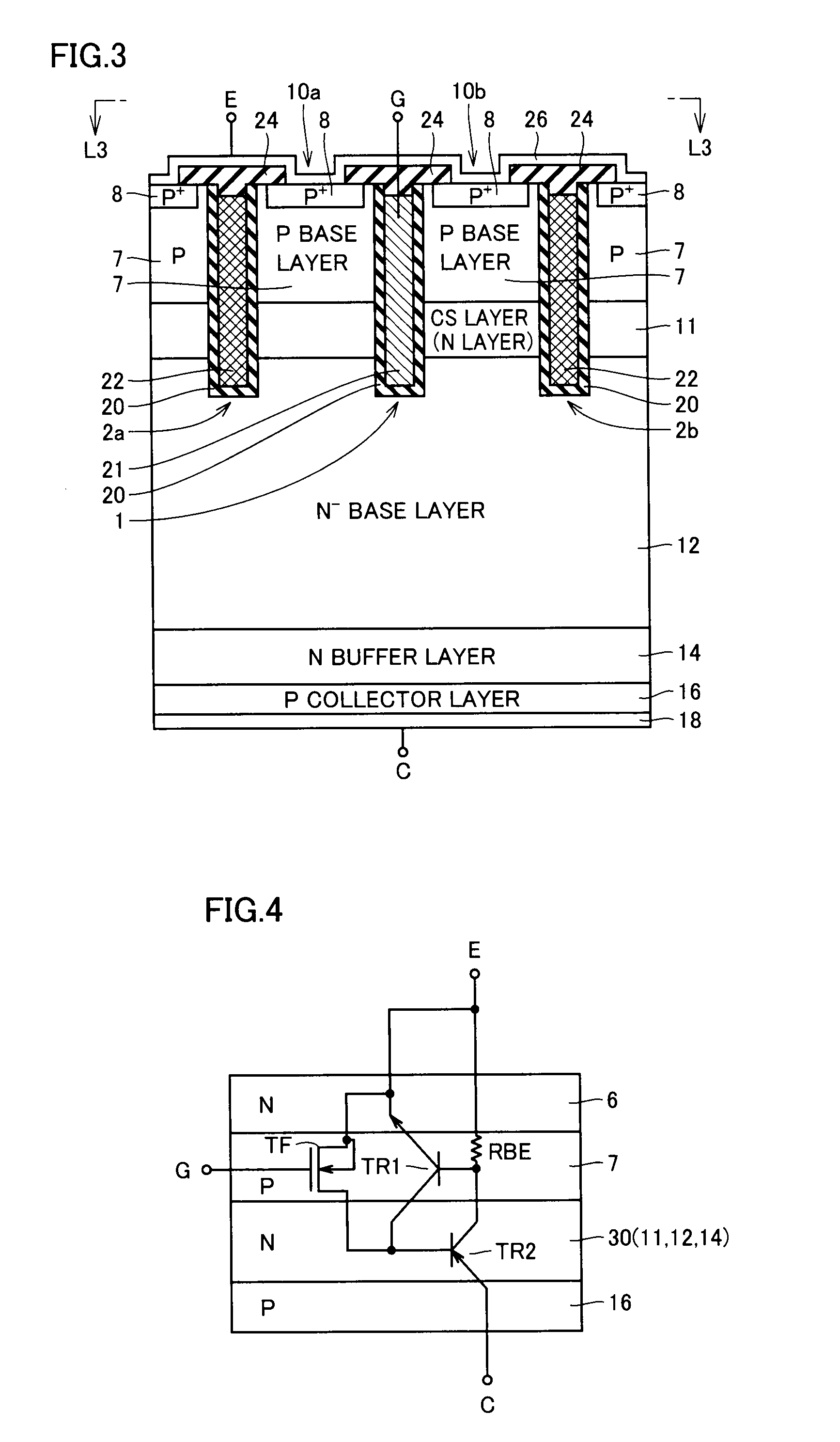

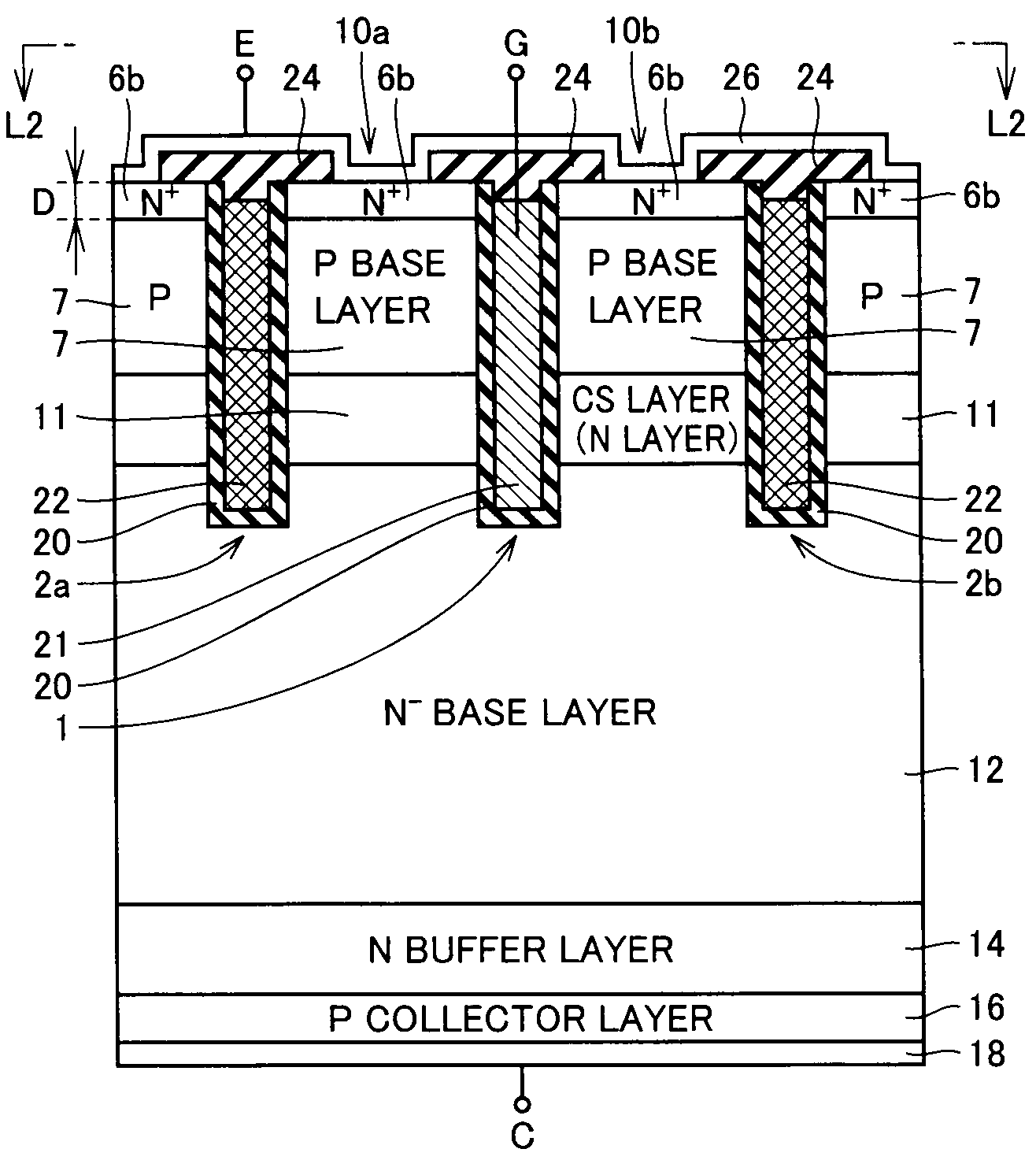

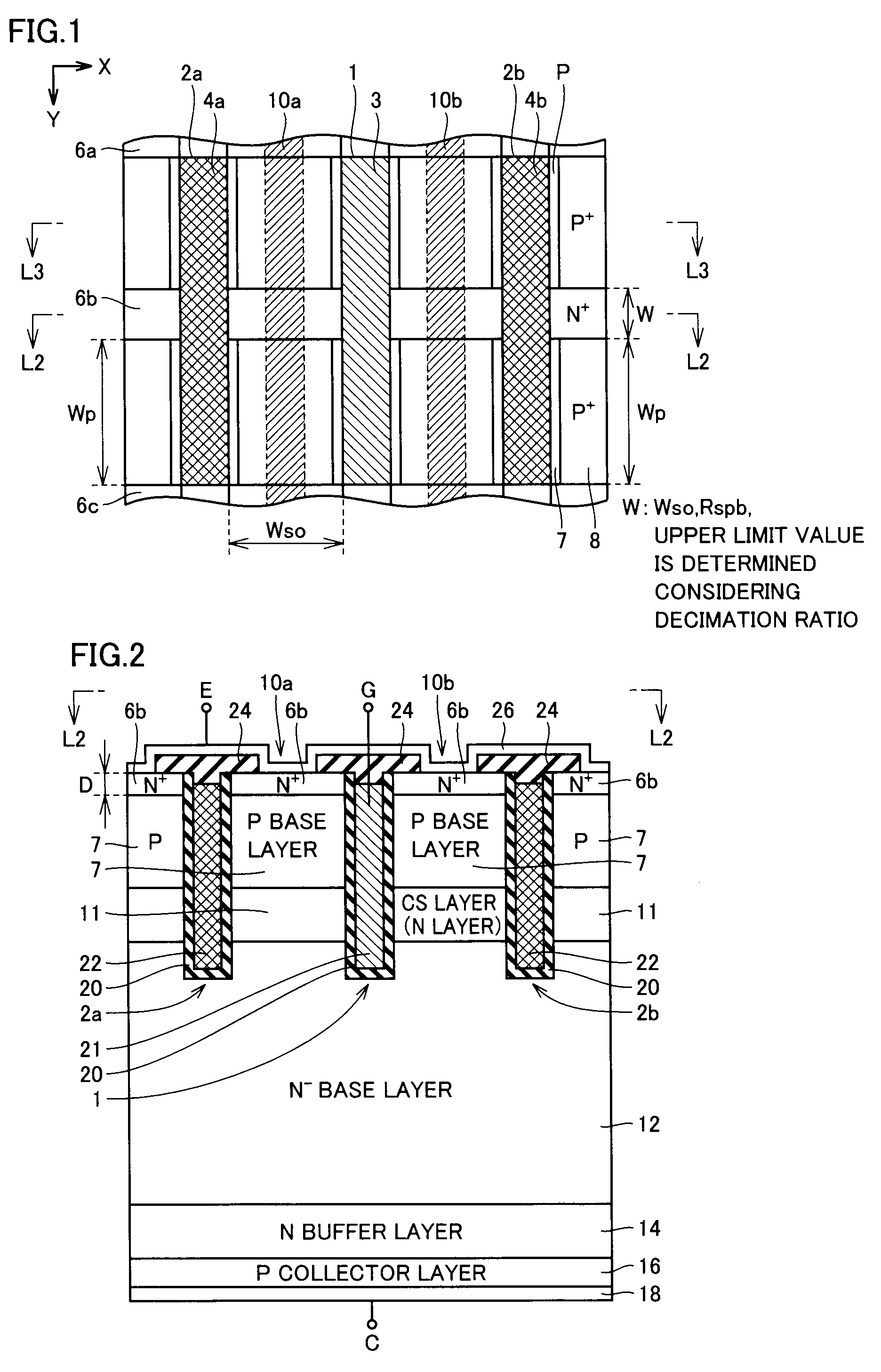

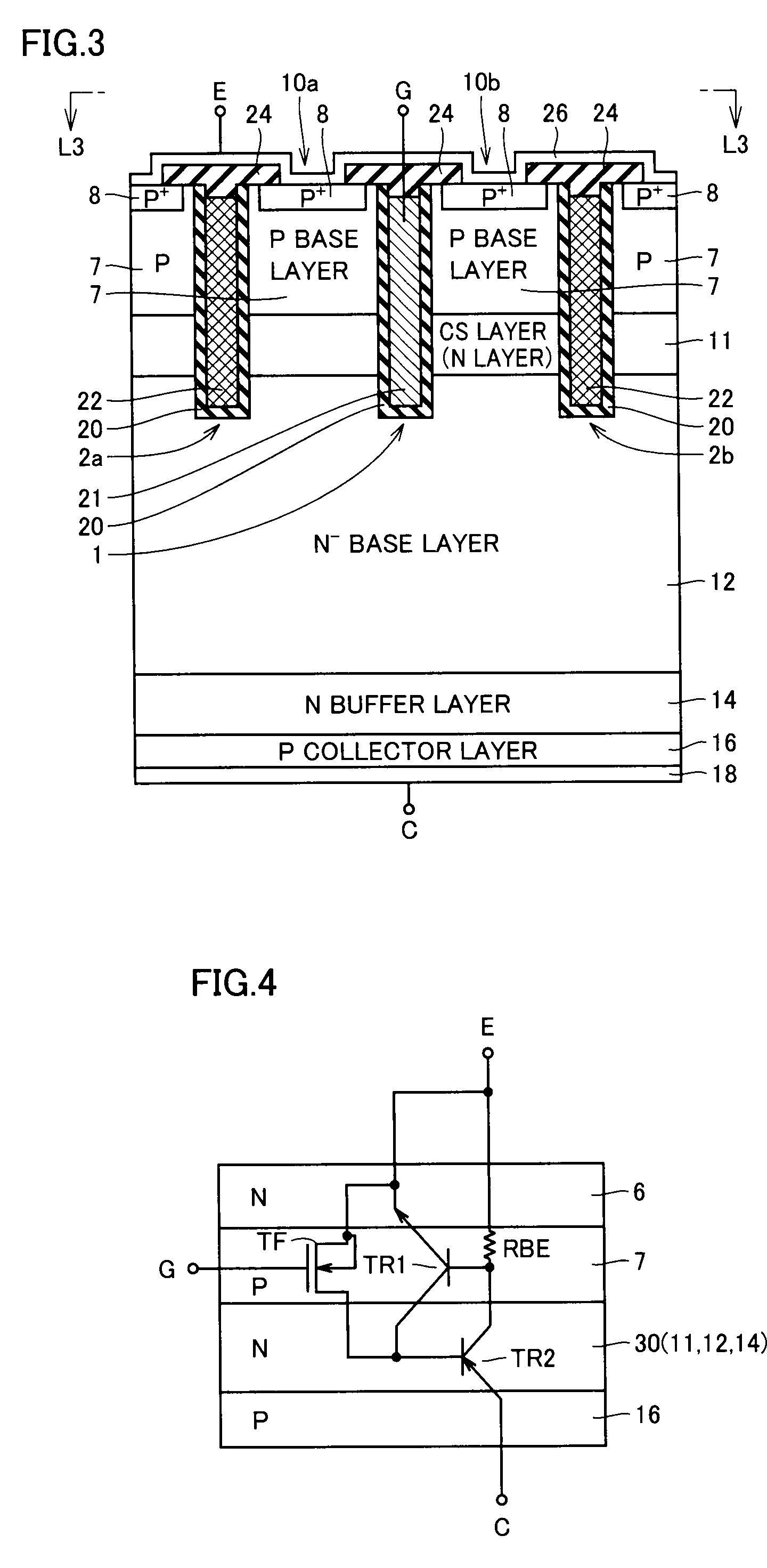

An emitter layer is provided in stripes in a direction orthogonal to an effective gate trench region connected to a gate electrode and a dummy trench region isolated from the gate electrode. A width of the emitter layer is determined to satisfy a predetermined relational expression so as not to cause latch-up in an underlying P base layer. In the predetermined relational expression, an upper limit value of the width W of the emitter layer is (3500 / Rspb)·Wso·exp(decimation ratio), where Rspb is a sheet resistance of the P base layer immediately below the emitter layer, Wso is an interval between the trenches, and the decimation ratio is a ratio of the number of the effective gate trench region to the total number of the trench regions. Variations in saturation current in a trench IGBT can be suppressed, and a tolerance of an Reverse Bias Safe Operation Area can be improved.

Owner:MITSUBISHI ELECTRIC CORP

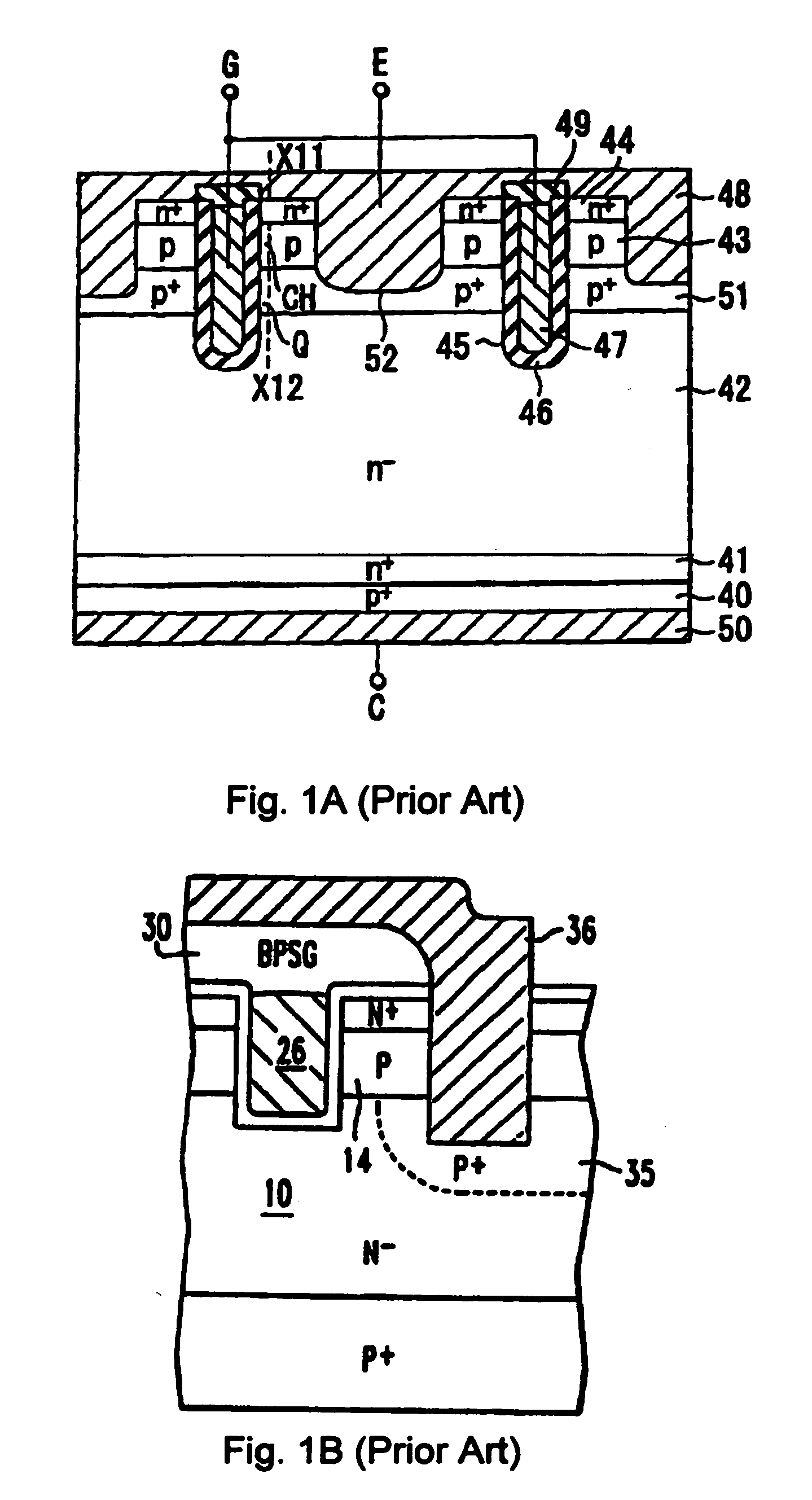

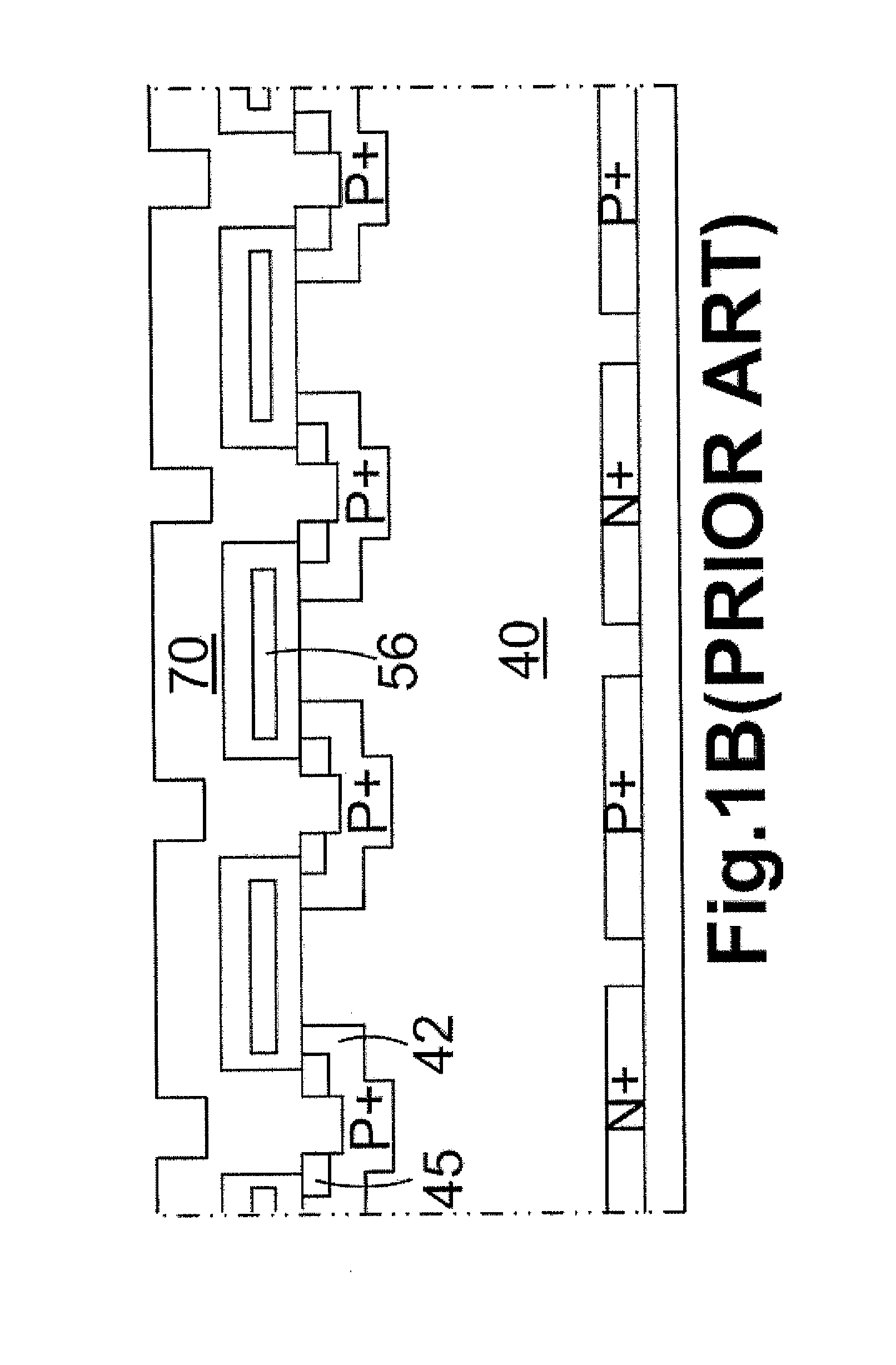

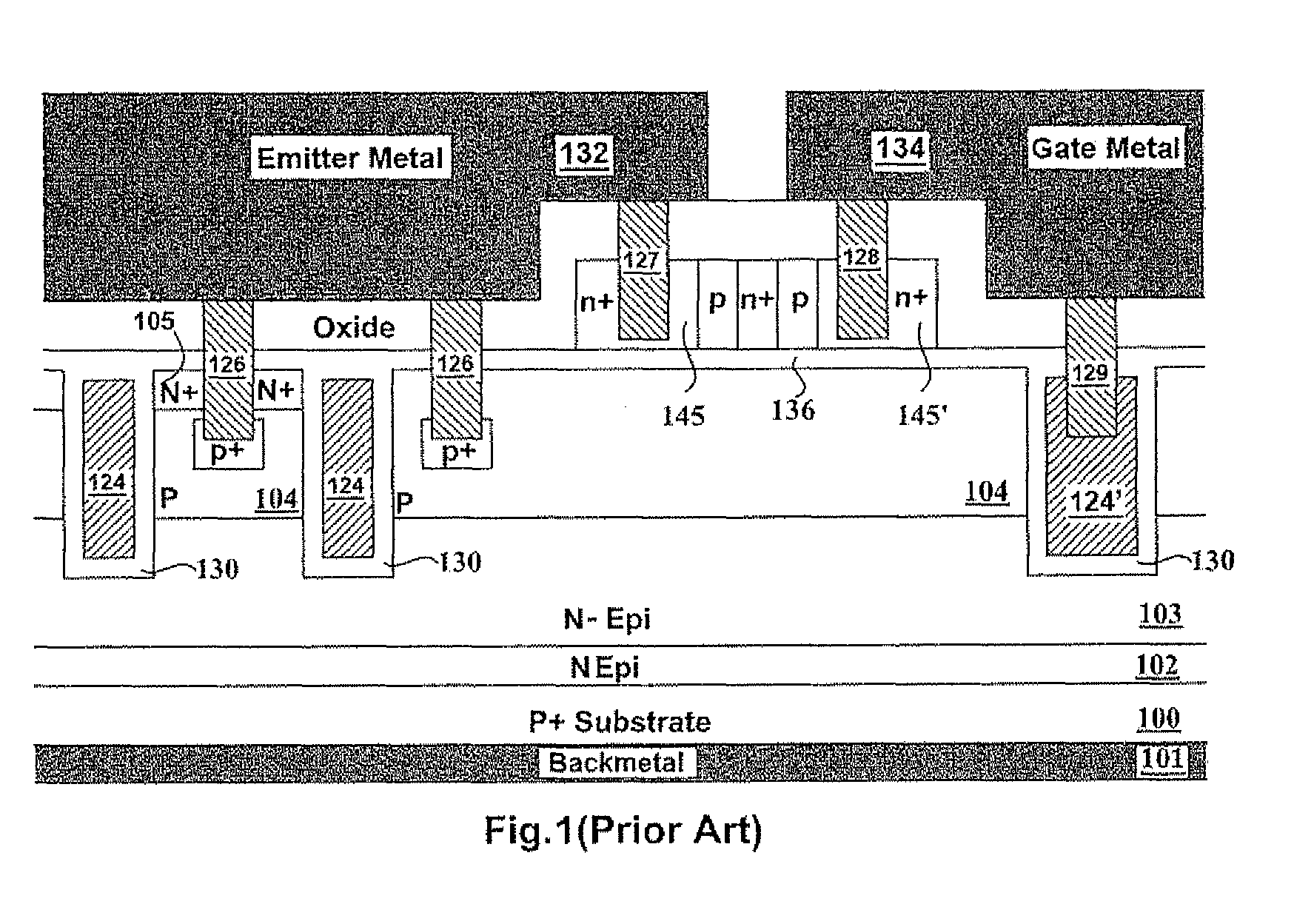

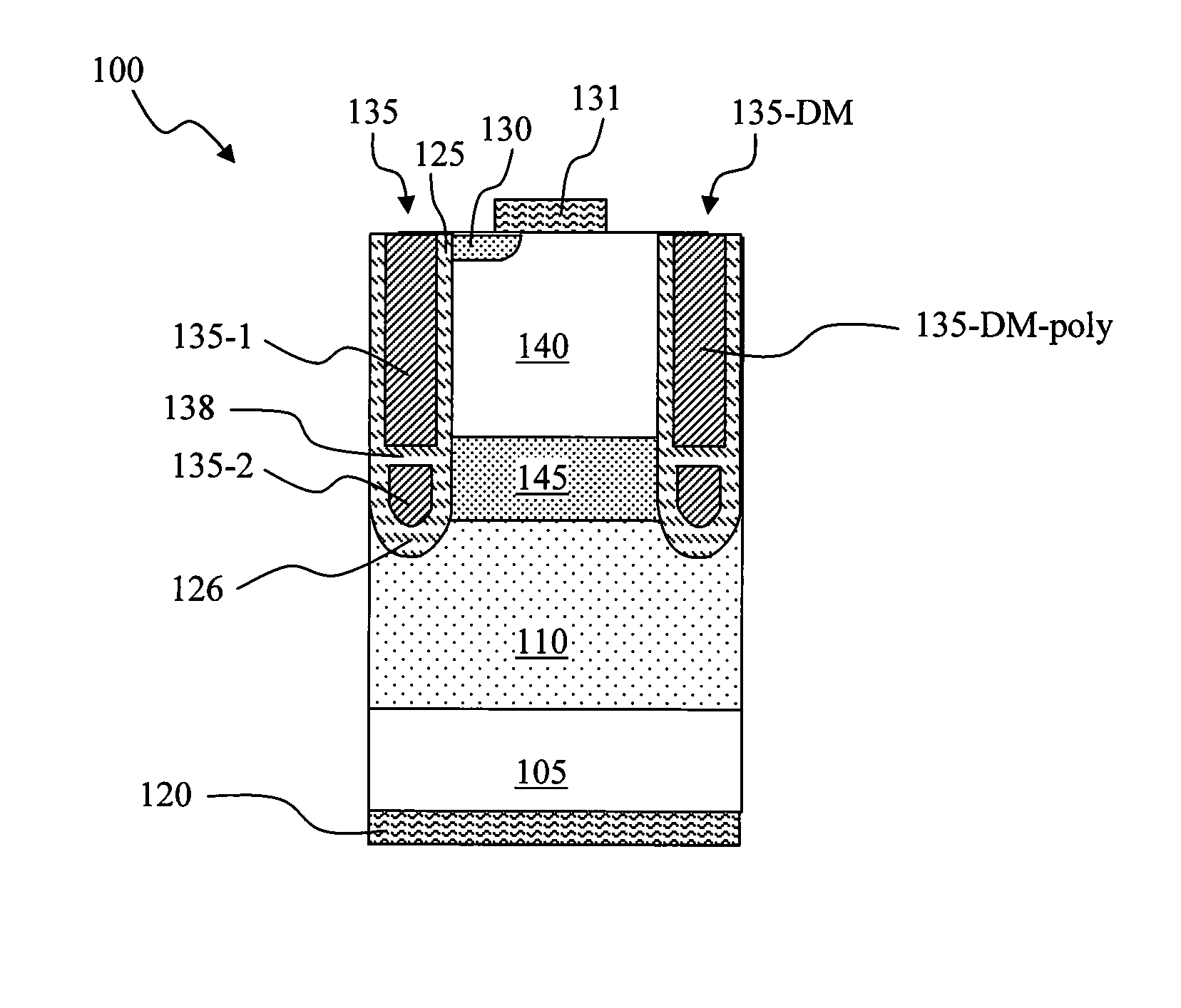

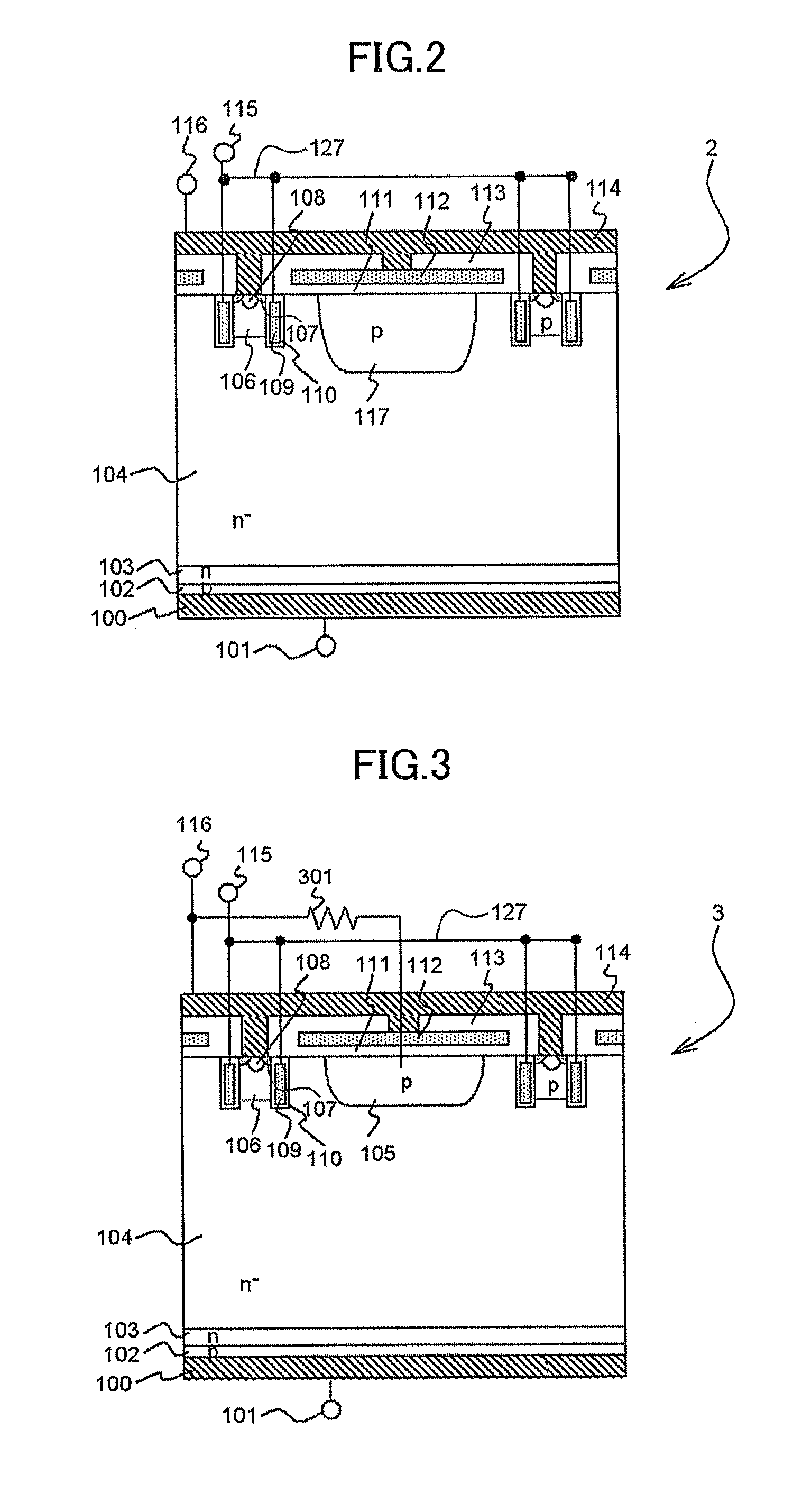

Trench insulated gate bipolar transistor (GBT) with improved emitter-base contacts and metal schemes

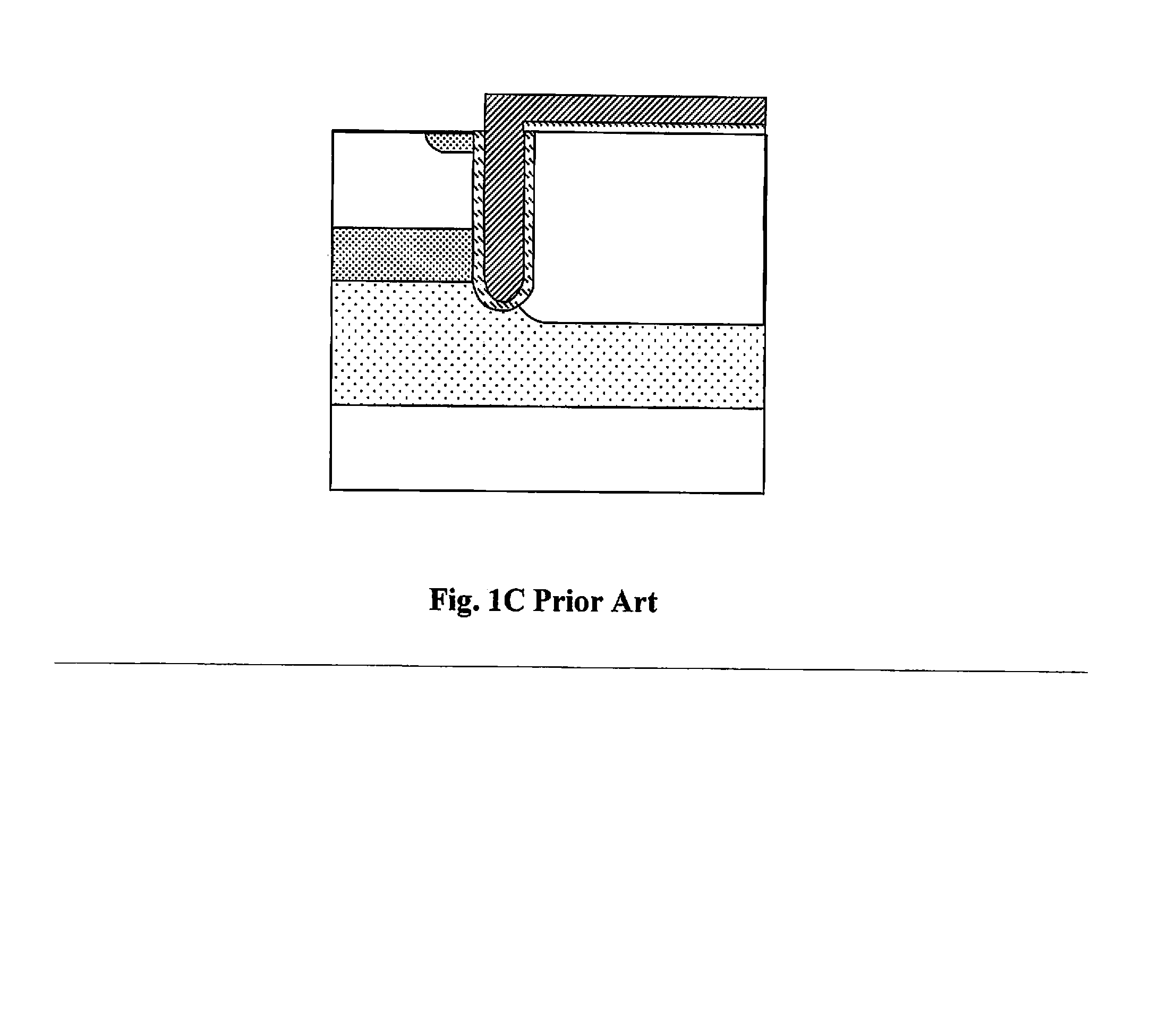

InactiveUS20100193835A1Reduce base contact resistanceEnhance latch-up immunity capabilitySemiconductor/solid-state device manufacturingSemiconductor devicesTrench igbtDopant

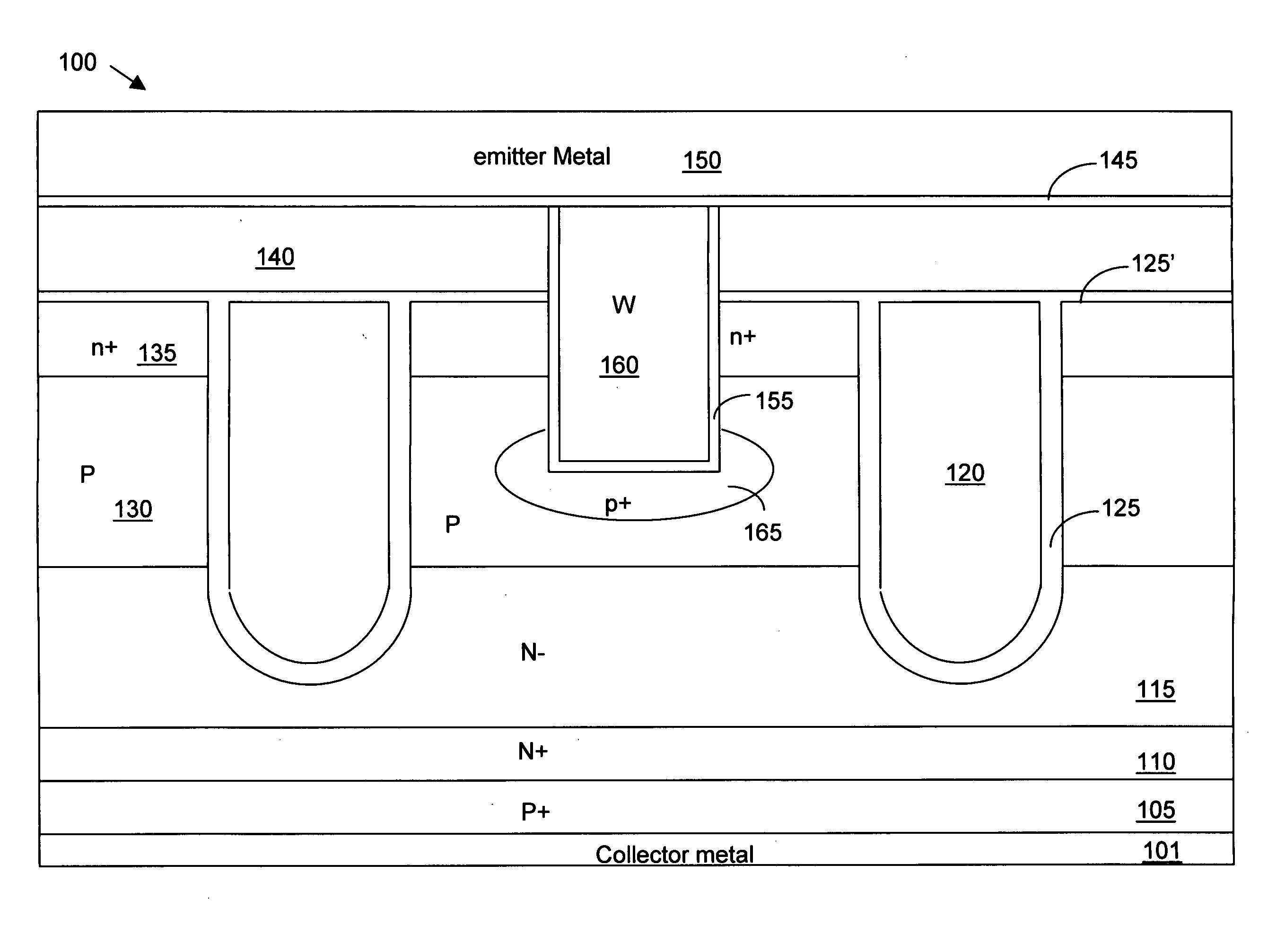

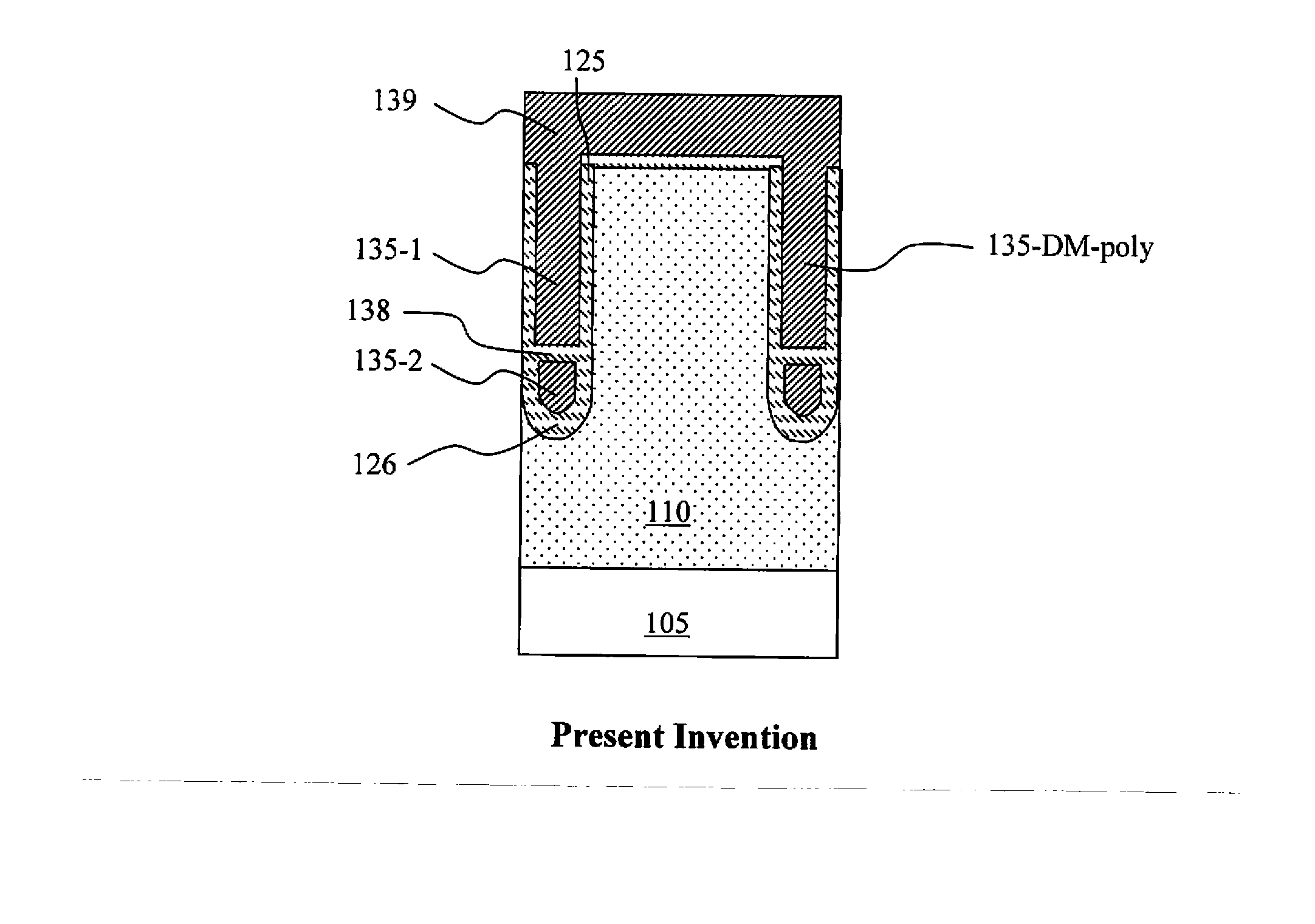

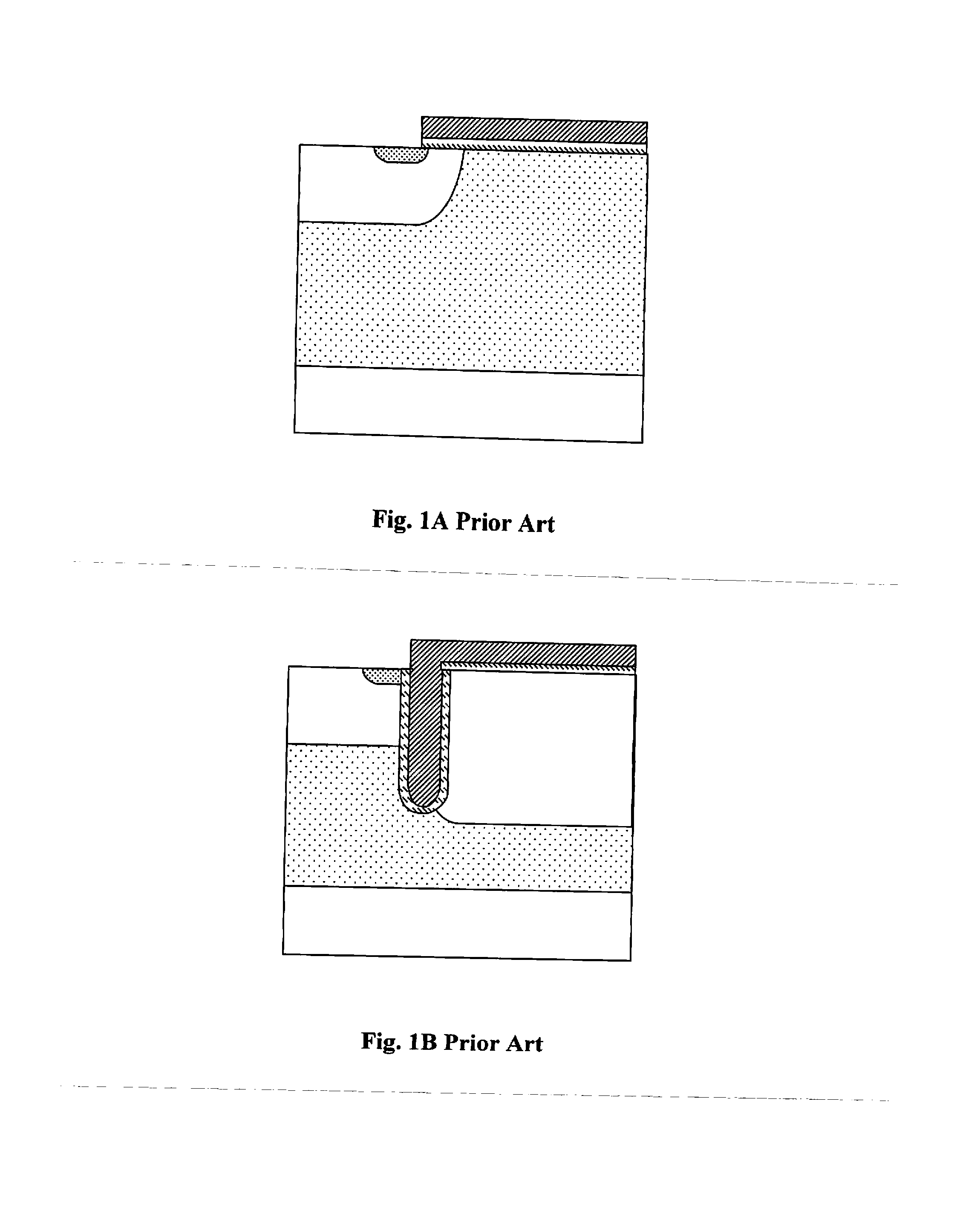

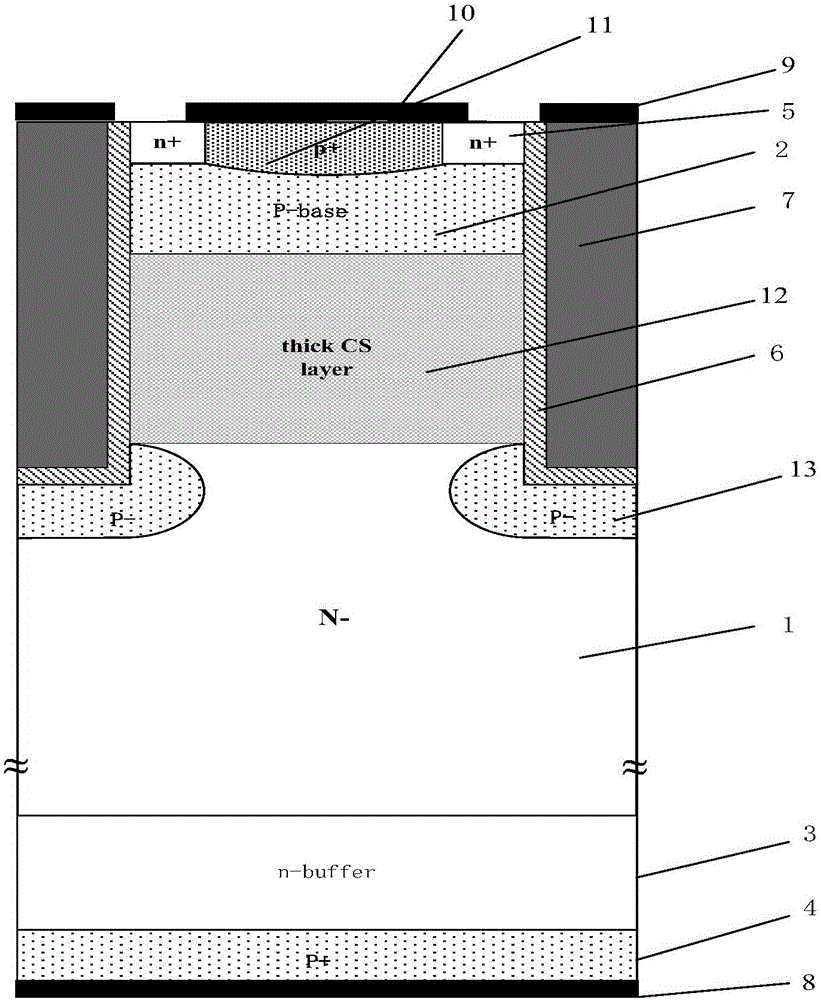

A trench insulation gate bipolar transistor (IGBT) power device includes a plurality of trench gates surrounded by emitter regions of a first conductivity type near a top surface of a semiconductor substrate encompassed in base regions of a second conductivity type and a collector layer disposed at a bottom surface of the semiconductor substrate. The trench IGBT power device further includes an insulation layer covering over the top surface over the trench gate and the emitter regions having emitter-base contact trenches opened therethrough between the trench gates and extending to the base regions and an emitter-base contact dopant region disposed in the base region of the second conductivity type surrounding a lower region of the contact trenches. The emitter-base contact dopant region is disposed at a distance away from a channel near the trench gates for reducing an emitter-base resistance without increasing a gate-emitter threshold voltage.

Owner:FORCE MOS TECH CO LTD

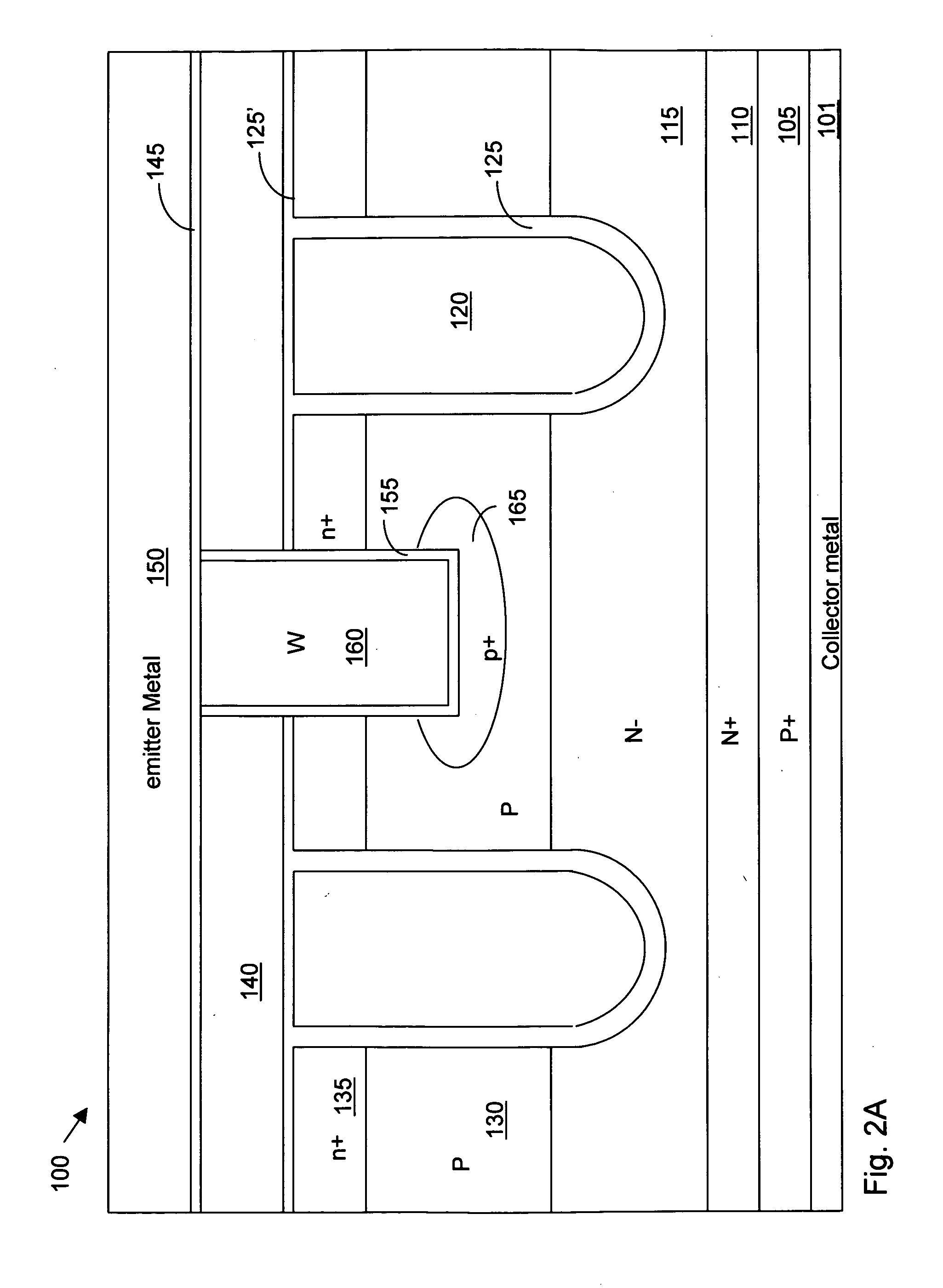

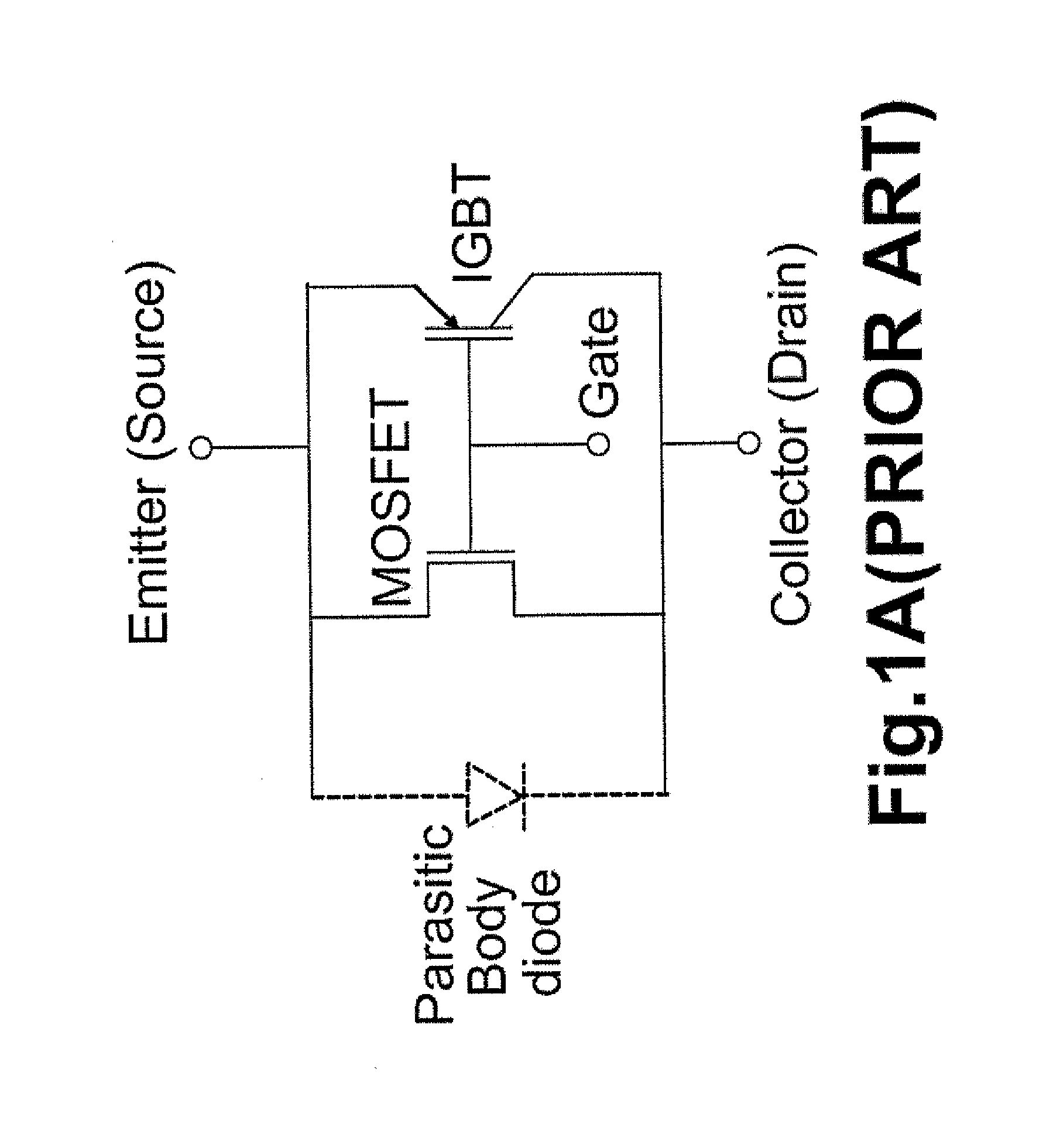

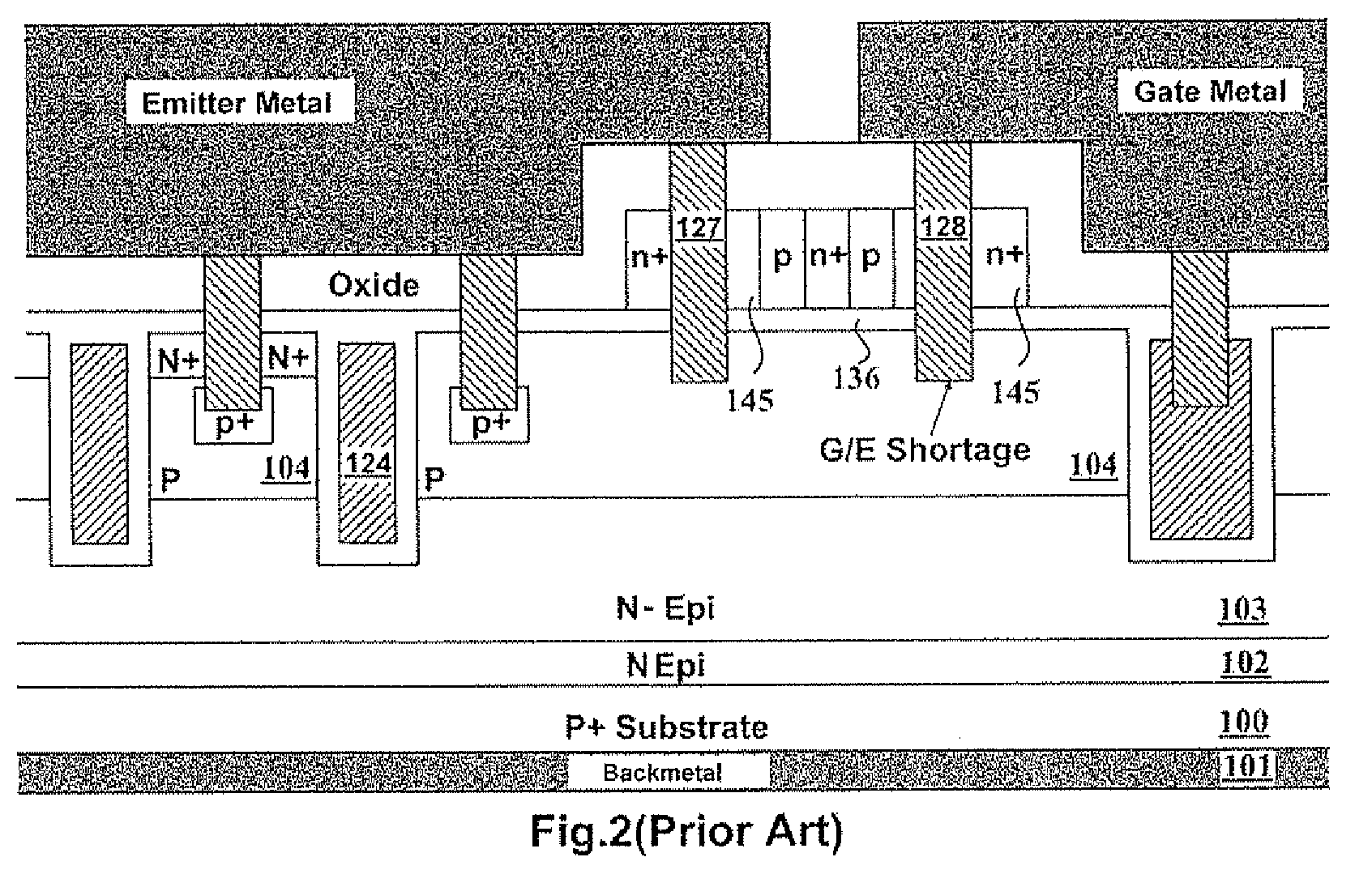

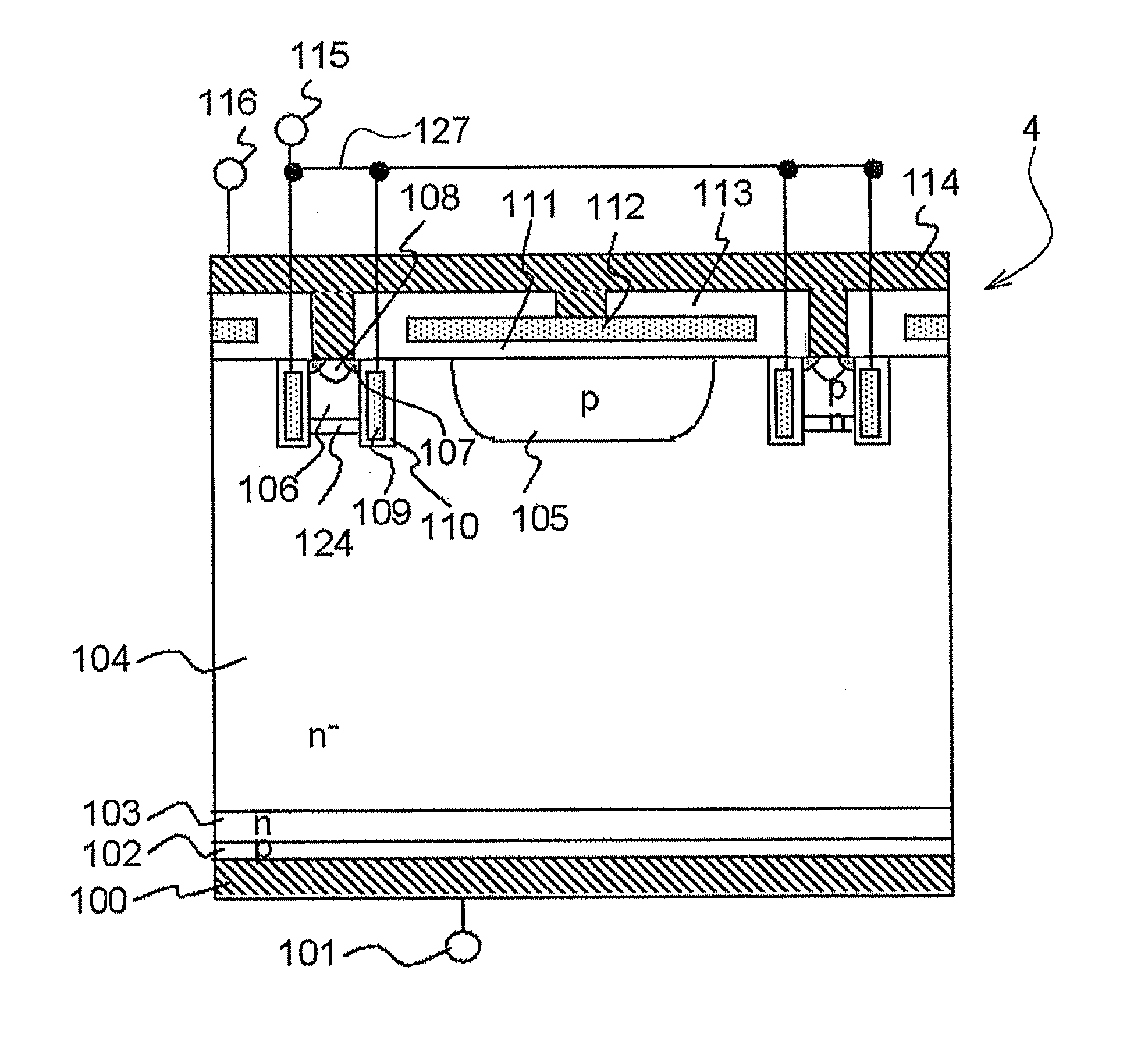

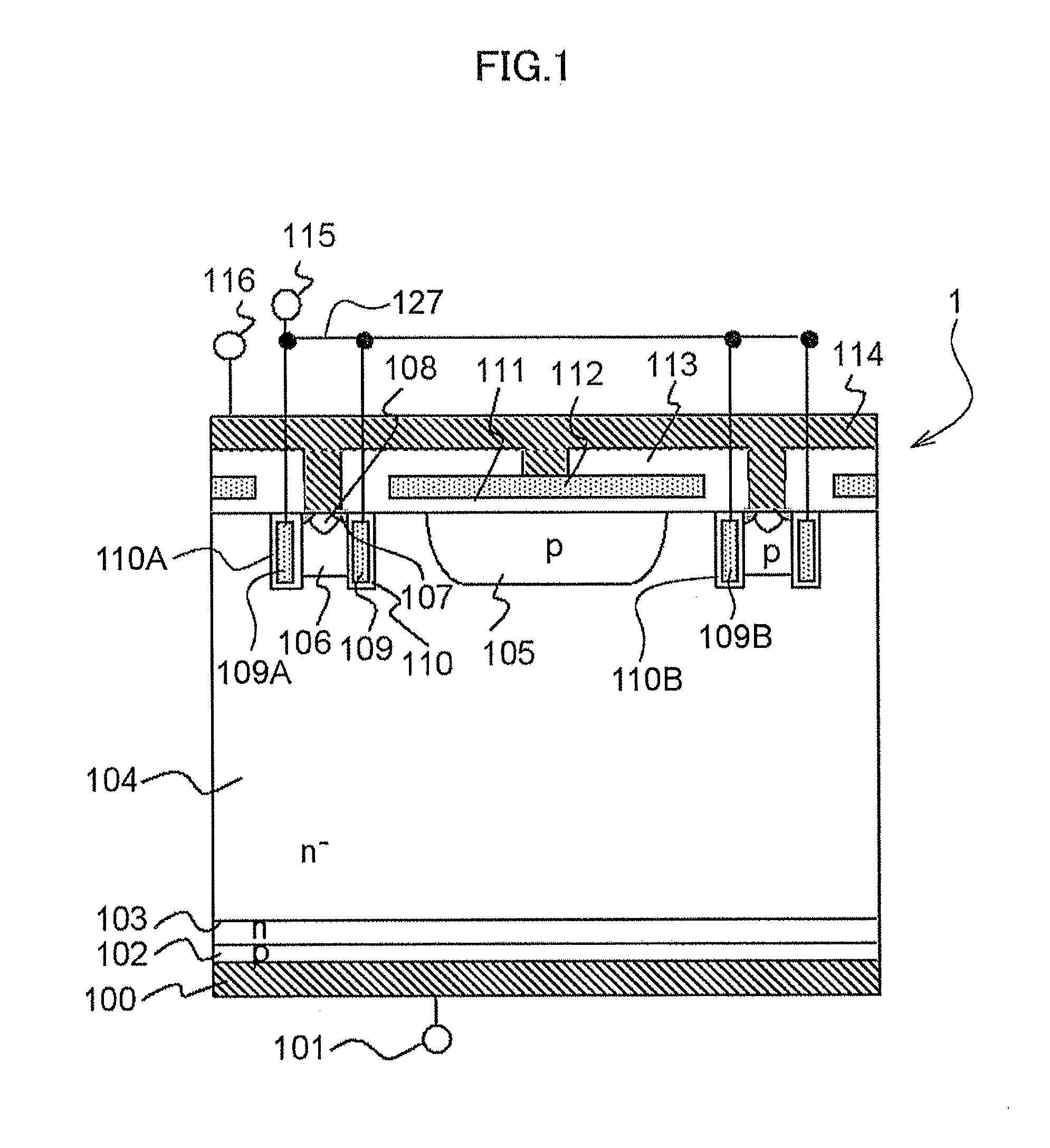

IGBT with integrated mosfet and fast switching diode

InactiveUS20120217541A1Reduce switching lossesThyristorSemiconductor/solid-state device detailsPower semiconductor deviceTrench igbt

A power semiconductor device comprising a trench IGBT, a trench MOSFET and a fast switching diode for reduction of turn-on loss is disclosed. The inventive semiconductor power device employs a fast switching diode instead of body diode in the prior art. Furthermore, the inventive semiconductor power device further comprises an additional ESD protection diode between emitter metal and gate metal.

Owner:FORCE MOS TECH CO LTD

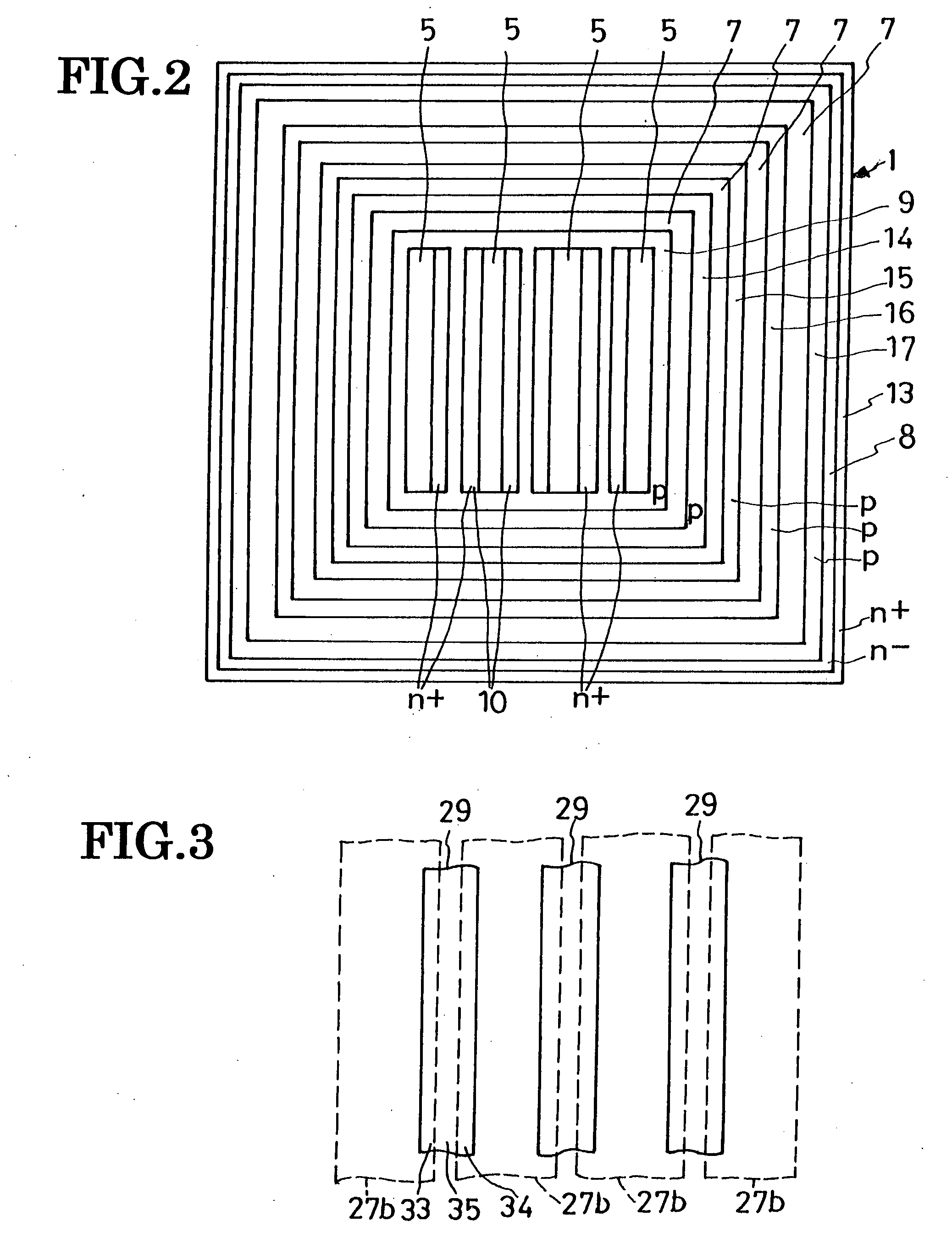

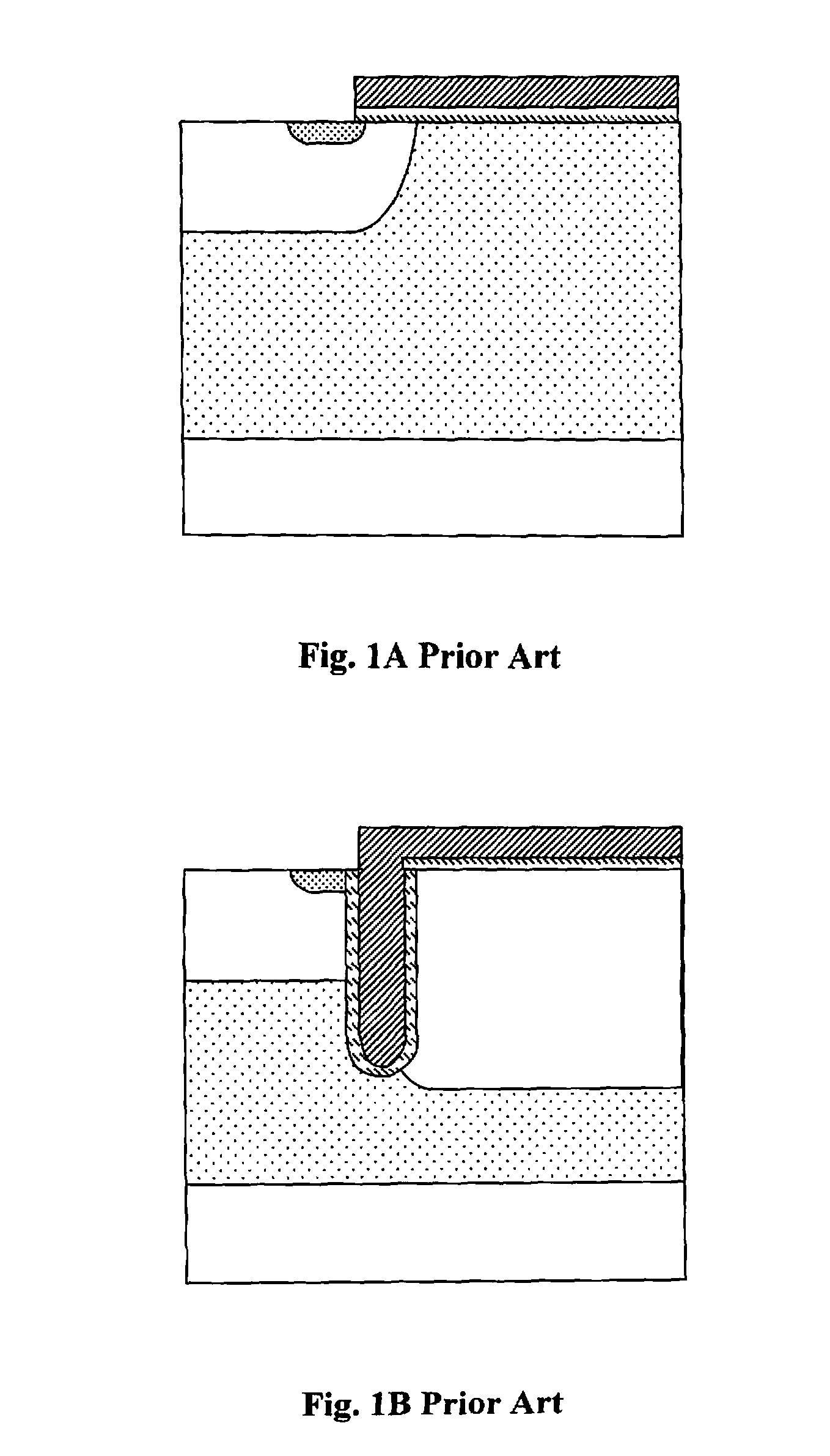

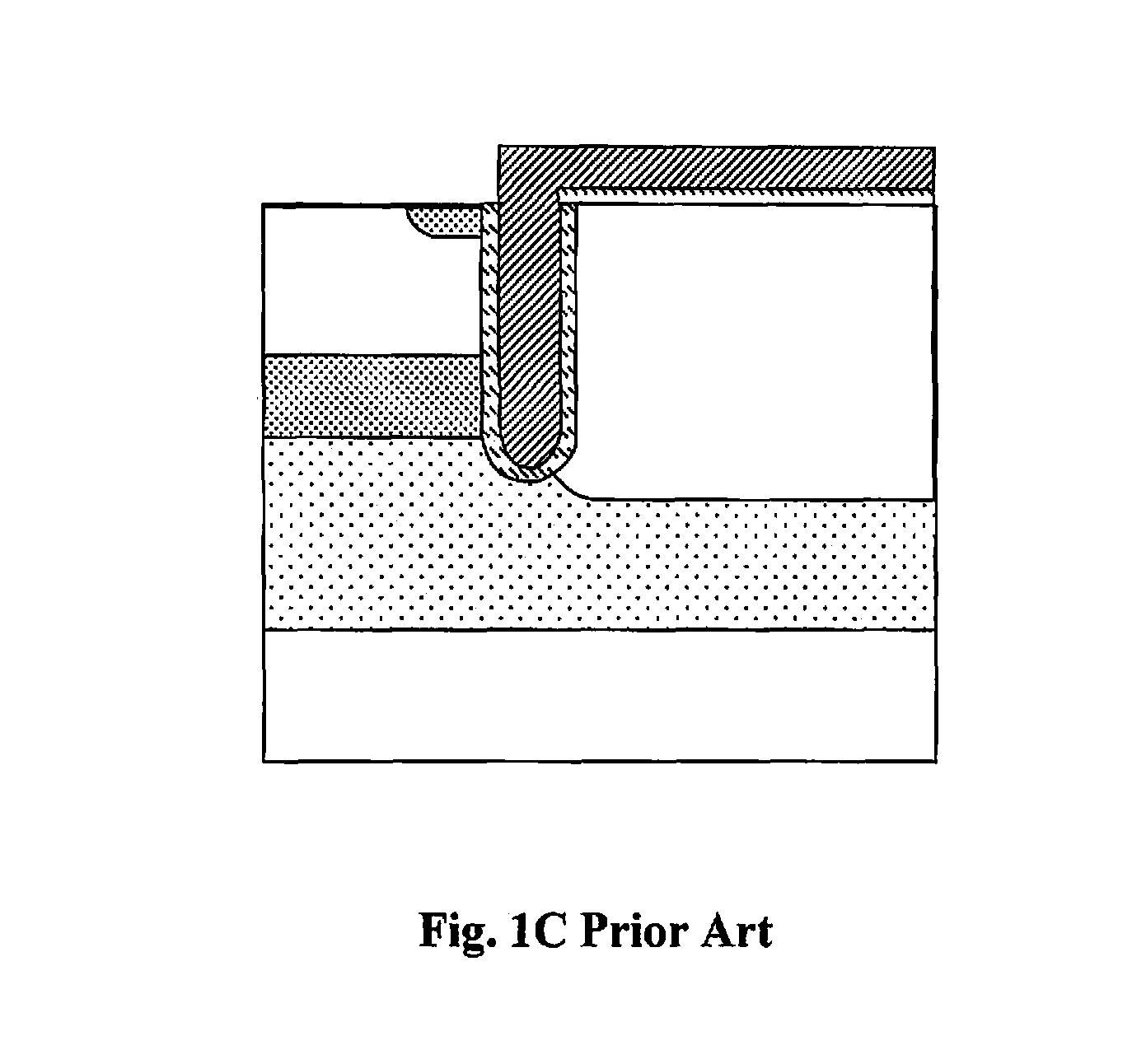

Trench semiconductor device of improved voltage strength, and method of fabrication

InactiveUS20070052014A1Improve pressure resistanceSimple processTransistorSemiconductor/solid-state device manufacturingCapacitanceTrench igbt

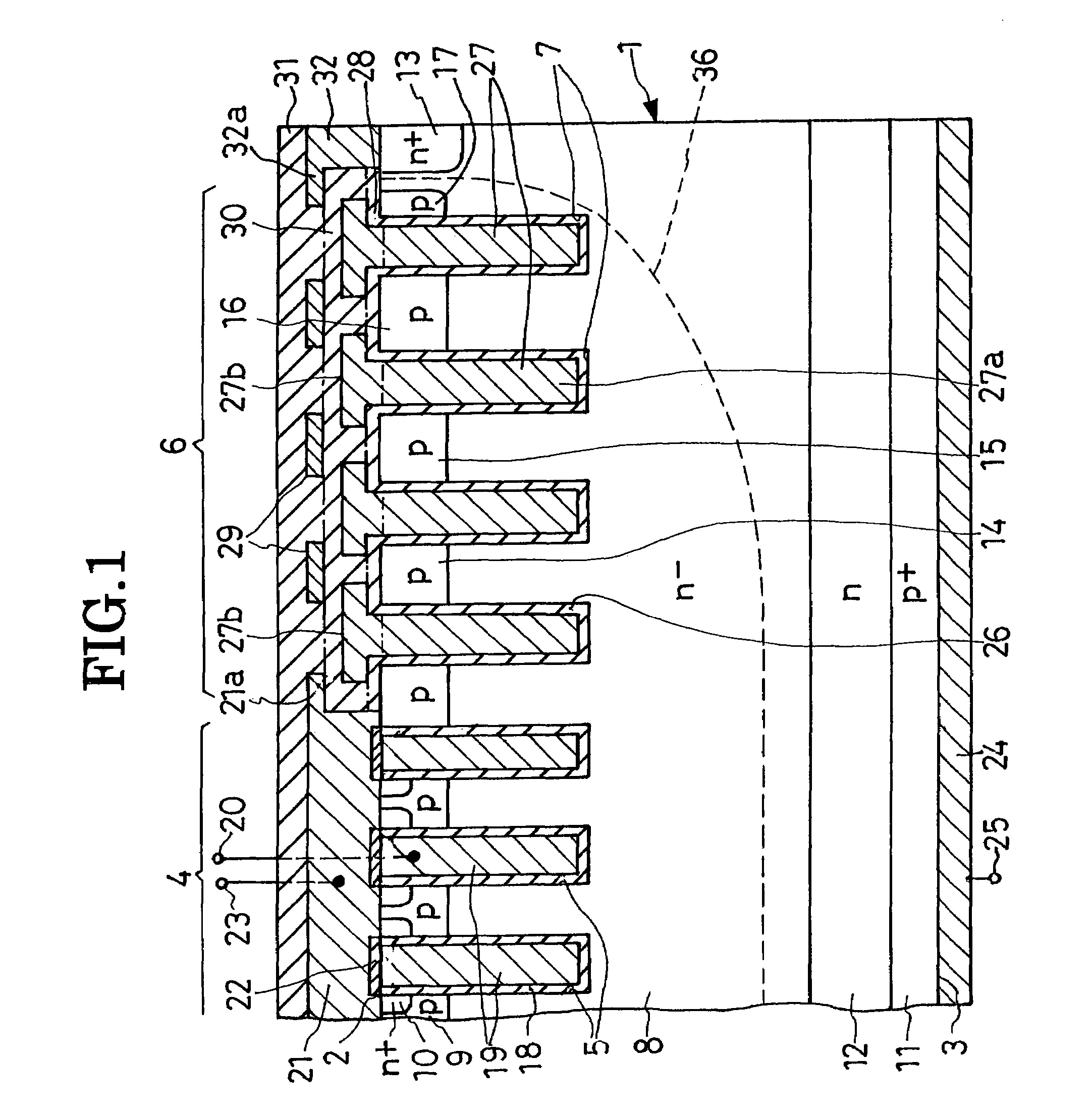

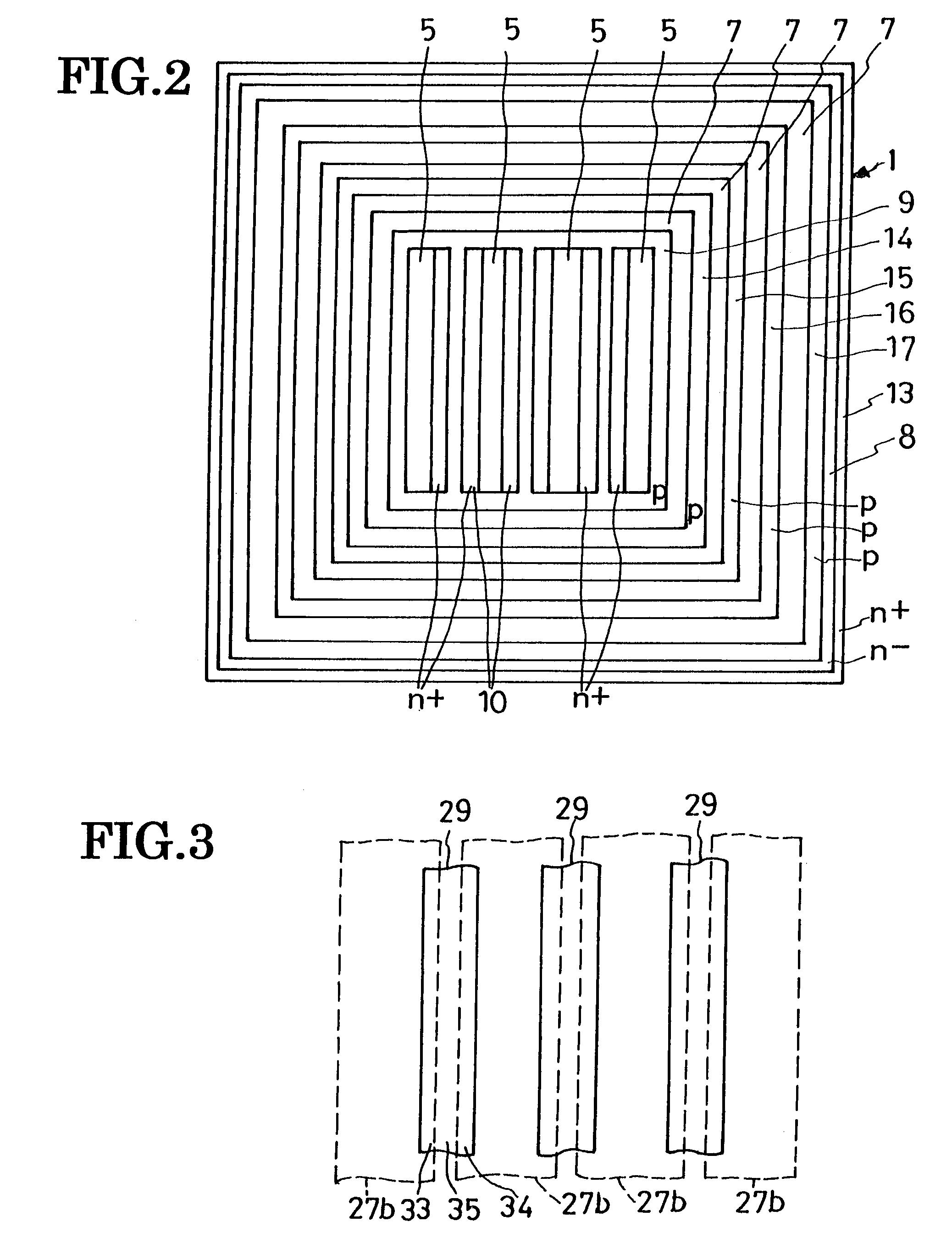

A trench IGBT is disclosed which includes a semiconductor substrate having formed therein a set of cell trenches formed centrally and a set of annular guard trenches concentrically surrounding the cell trenches. The cell trenches receive cell trench conductors via cell trench insulators for providing IGBT cells. The guard trenches receive guard trench conductors via guard trench insulators for enabling the IGBT to withstand higher voltages through mitigation of field concentrations. Capacitive coupling conductors overlie the guard trench conductors via a dielectric layer, each for capacitively coupling together two neighboring ones of the guard trench conductors. The capacitive coupling conductors are easily adjustably variable in shape, size and placement relative to the guard trench conductors for causing the individual guard trench conductors to possess potentials for an optimal contour of the depletion layer.

Owner:SANKEN ELECTRIC CO LTD

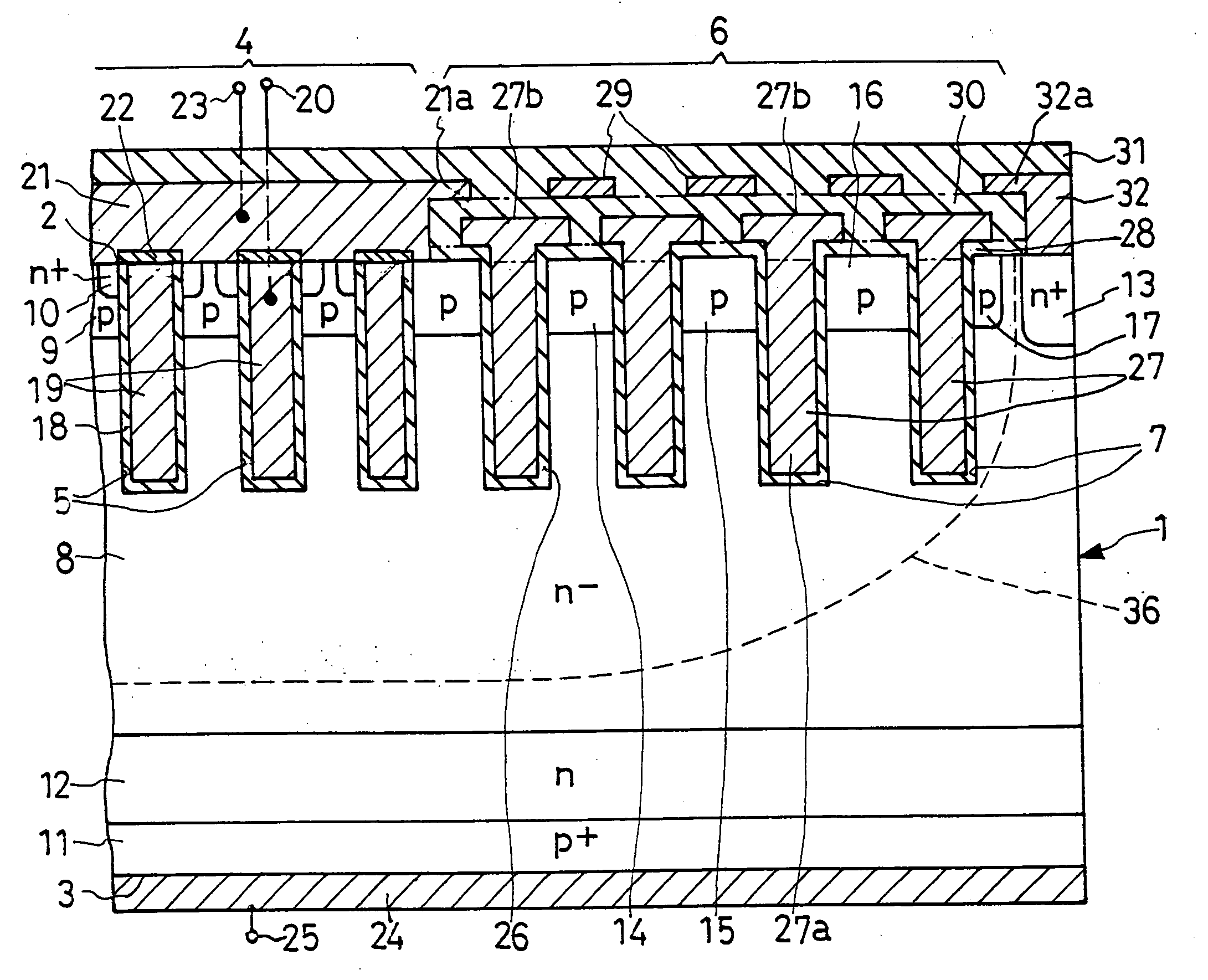

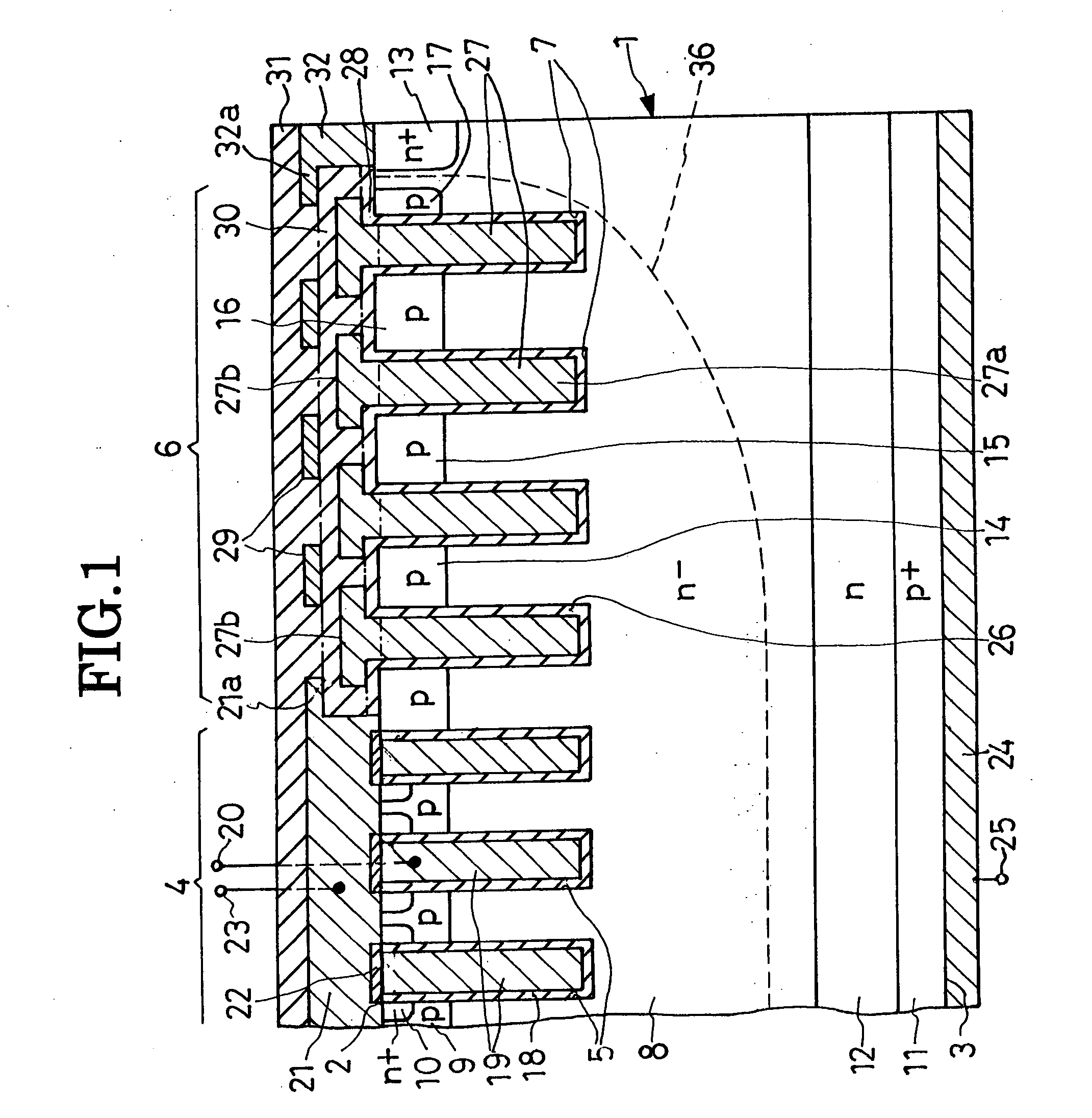

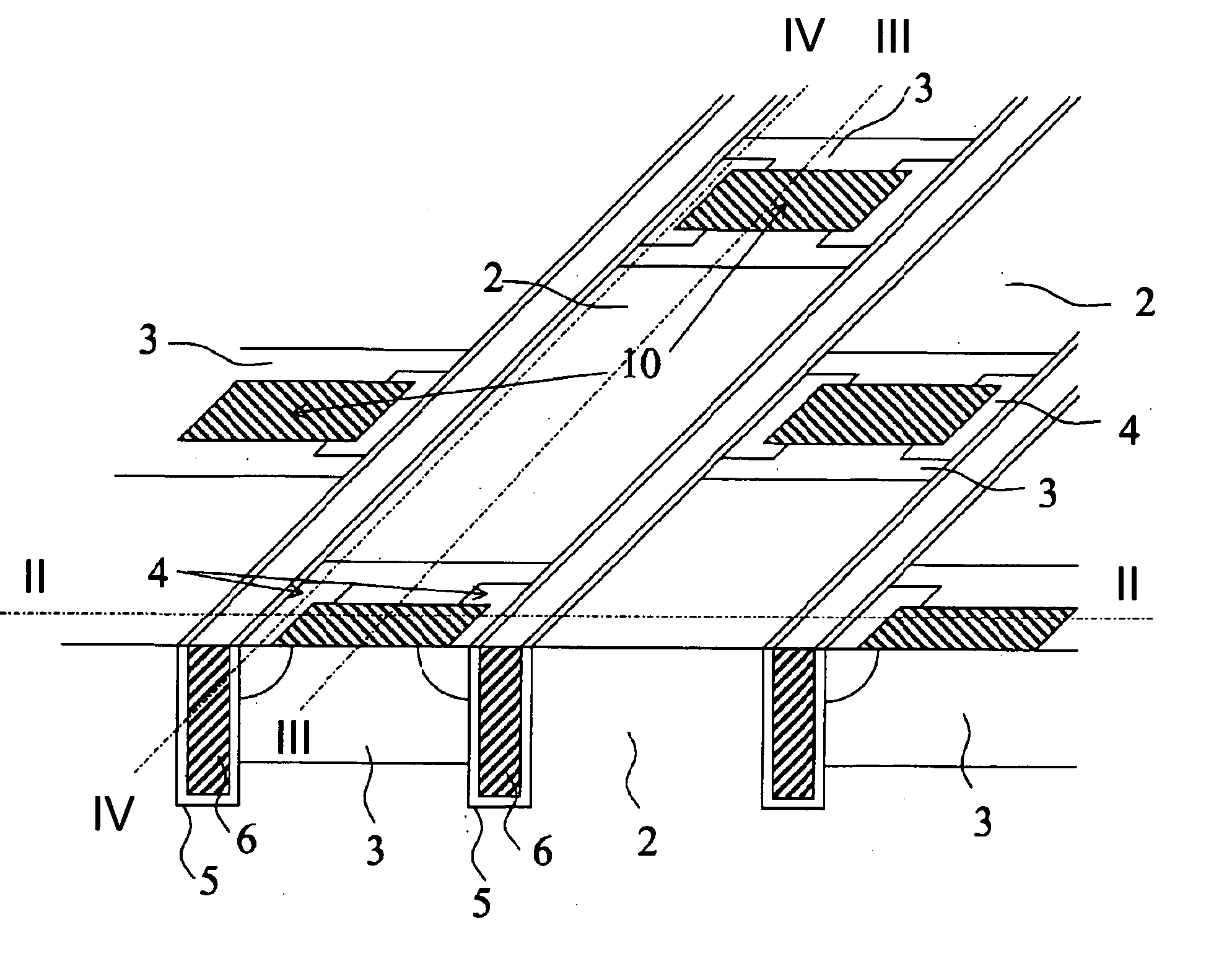

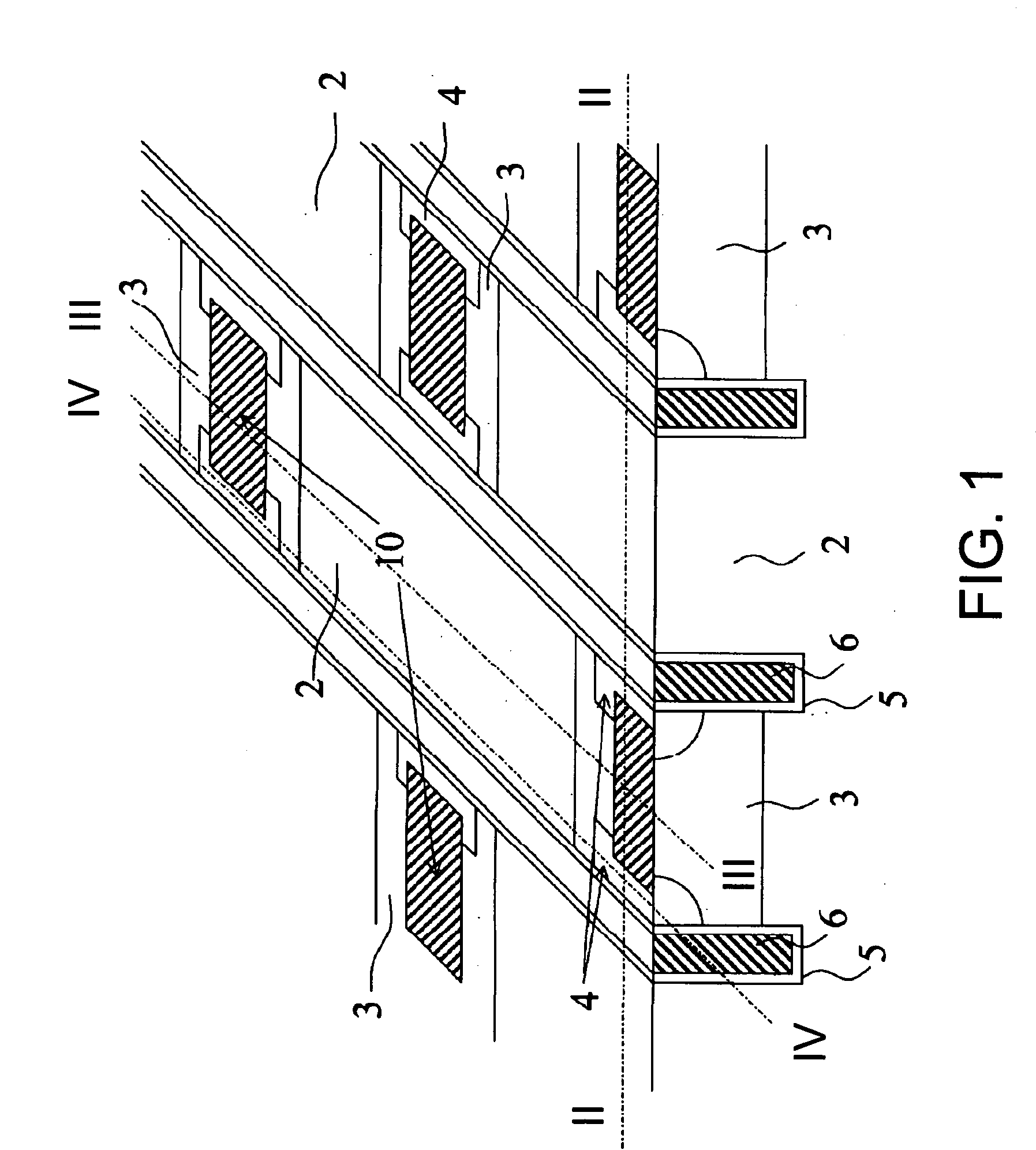

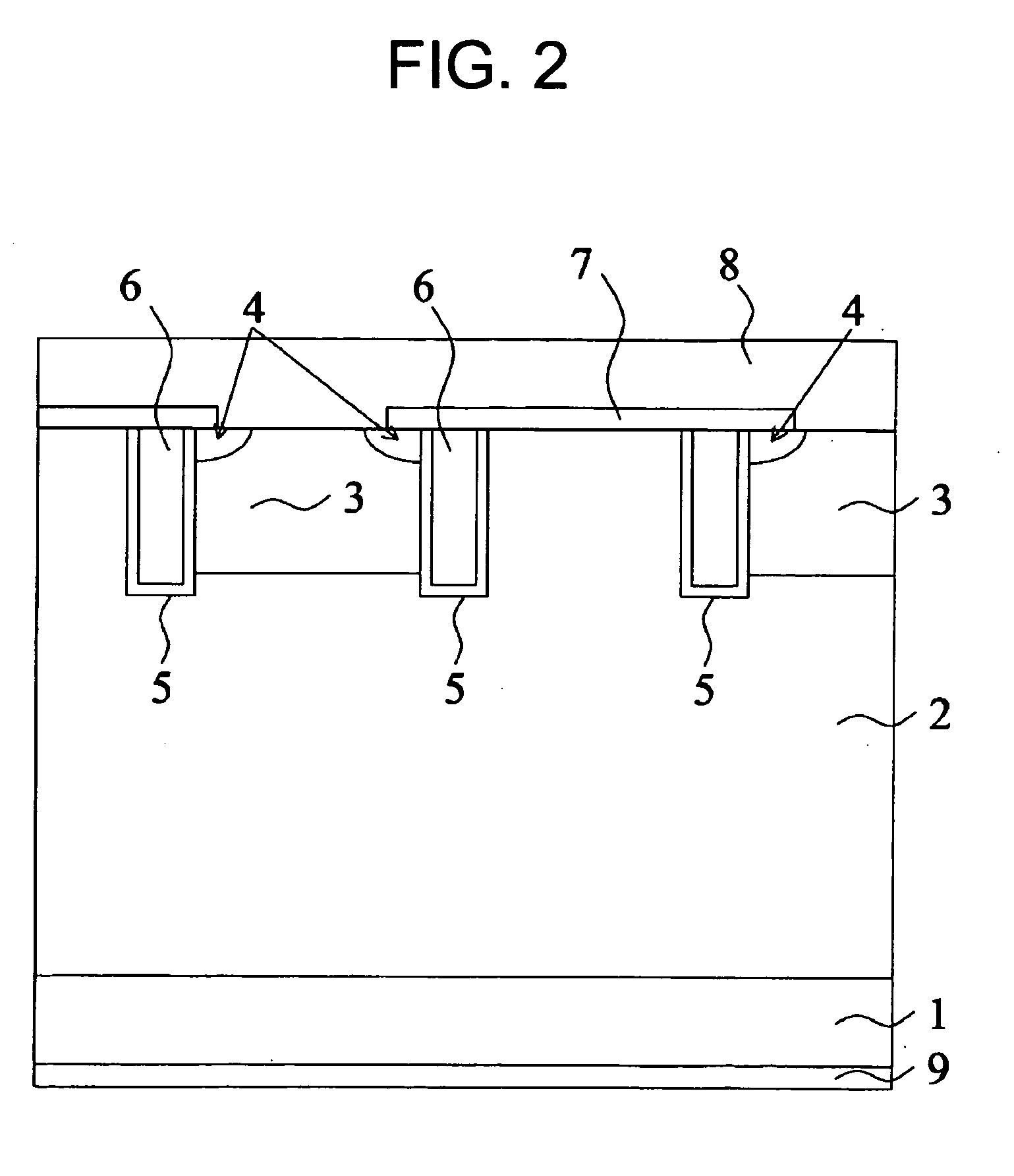

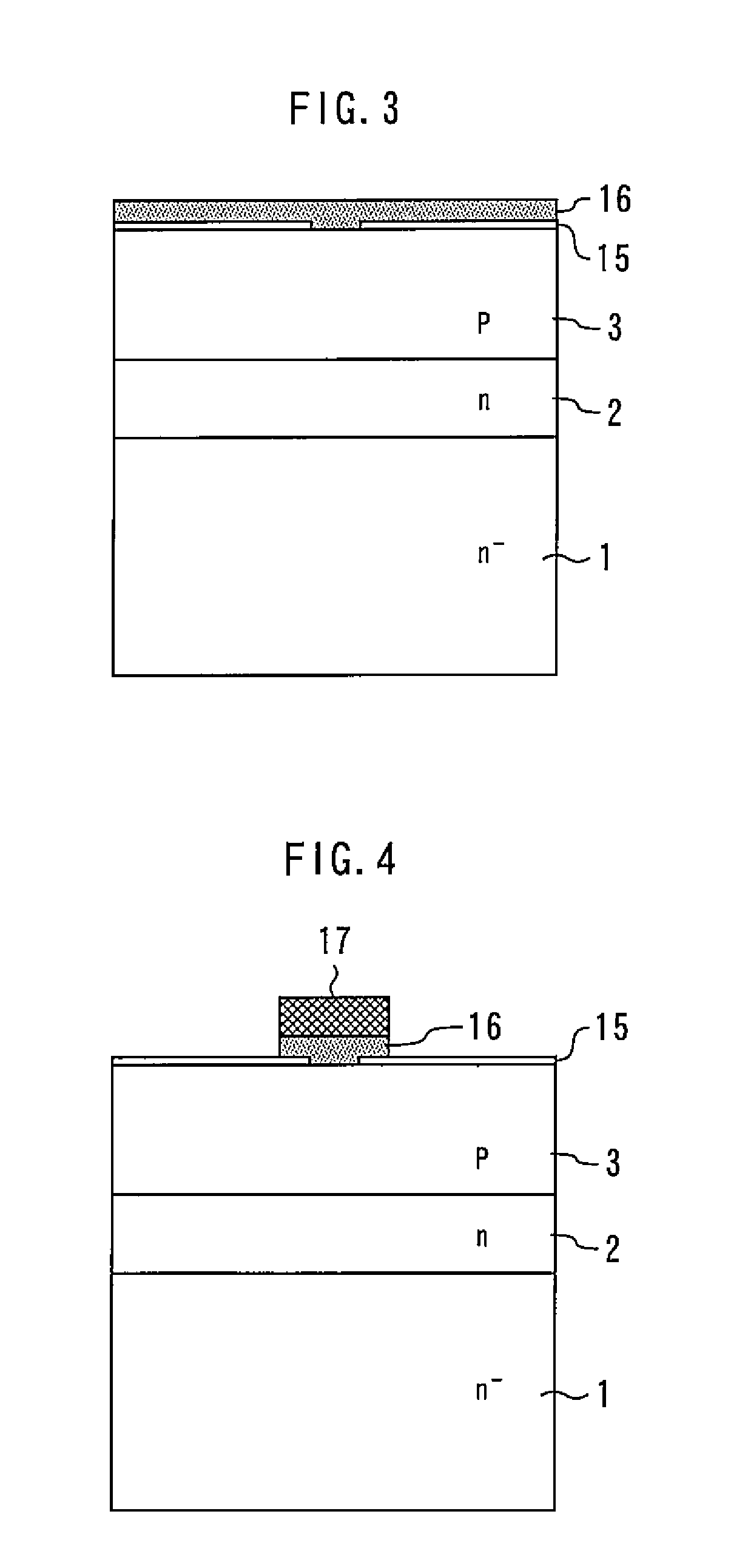

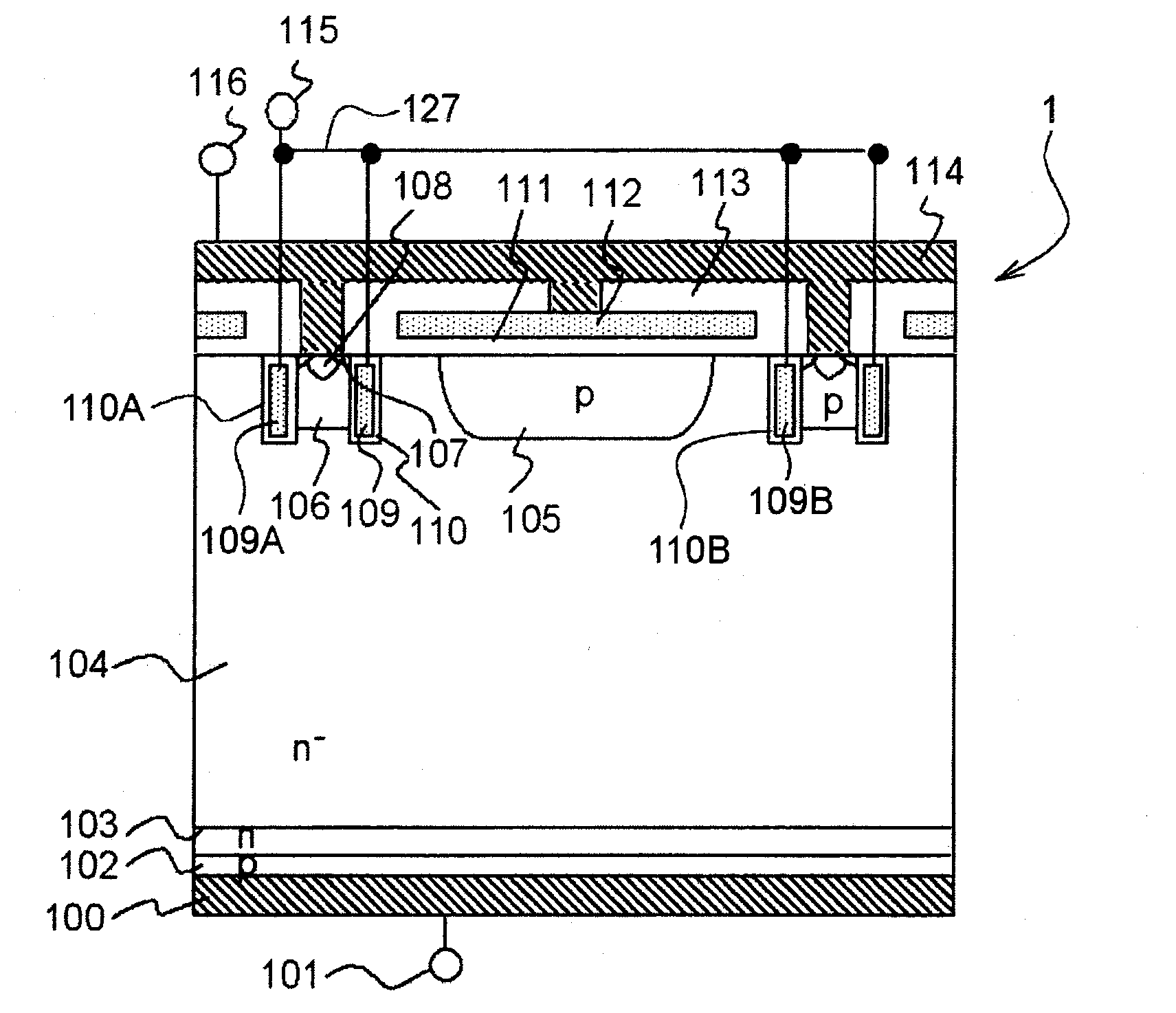

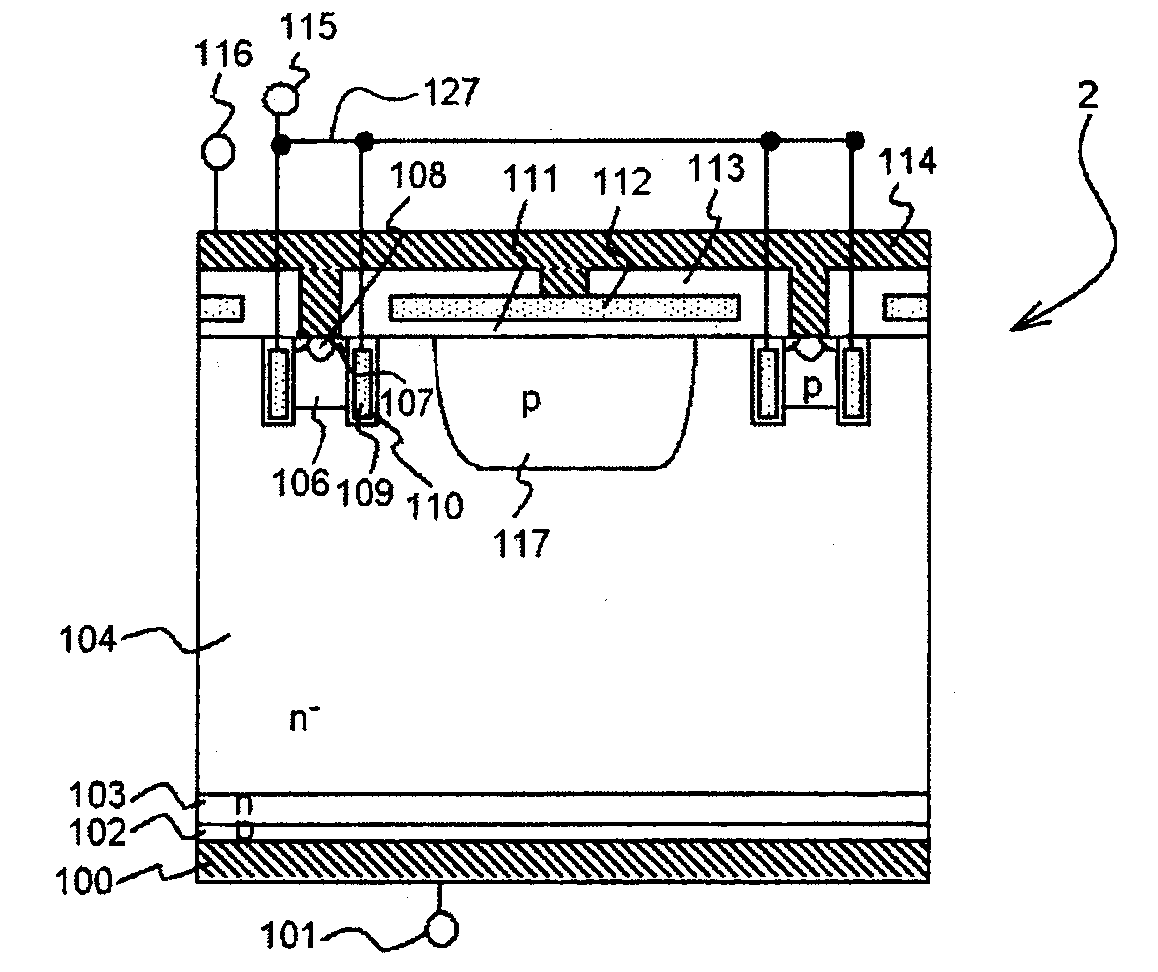

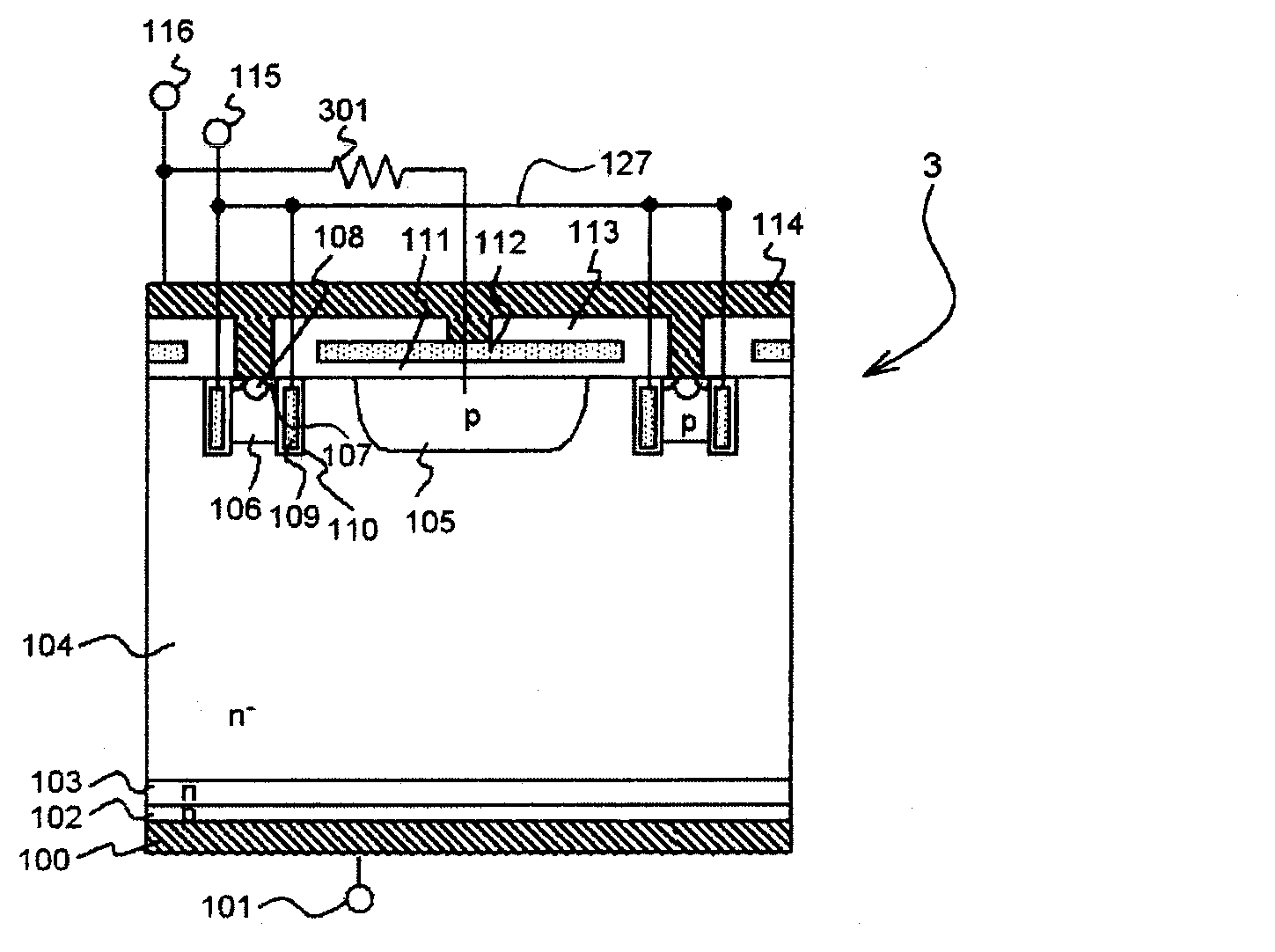

Insulated gate semiconductor device

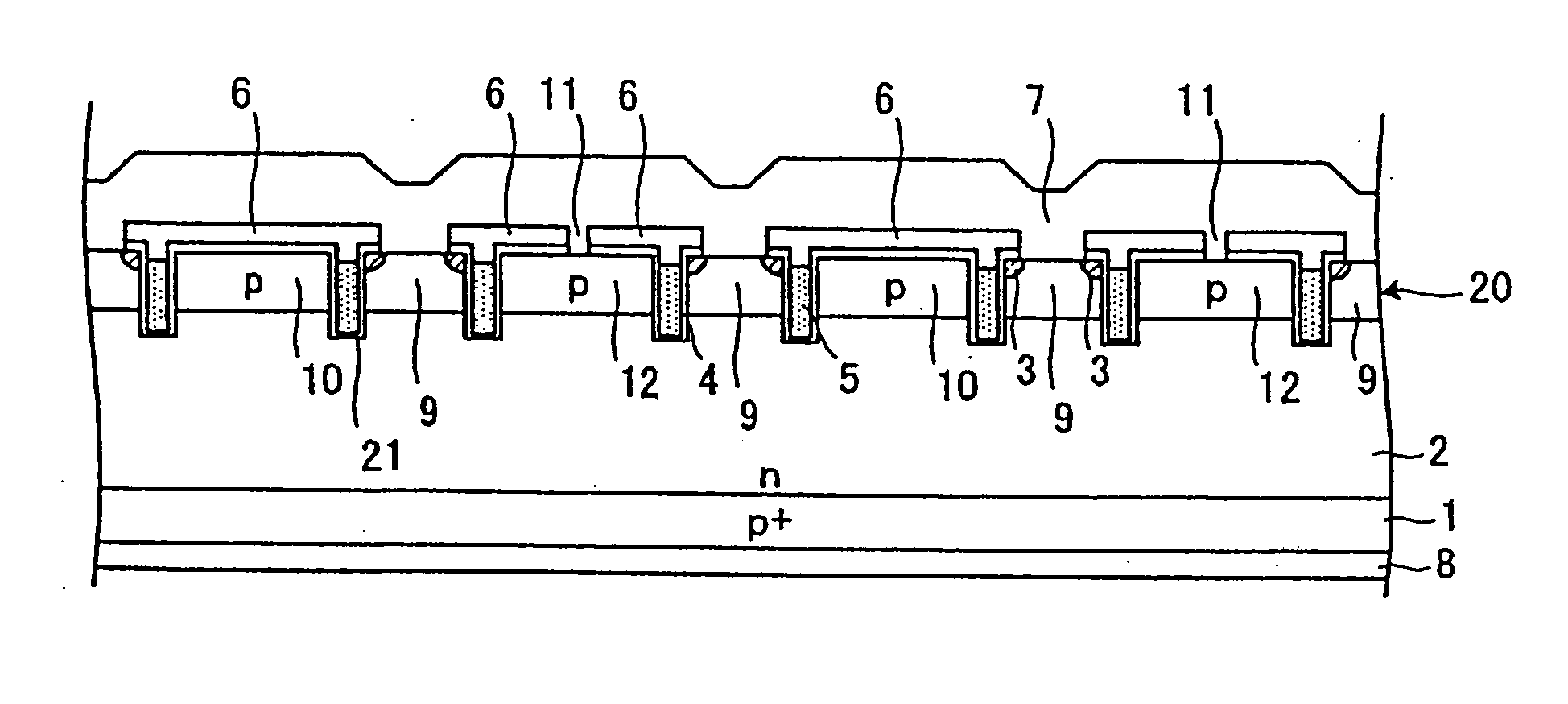

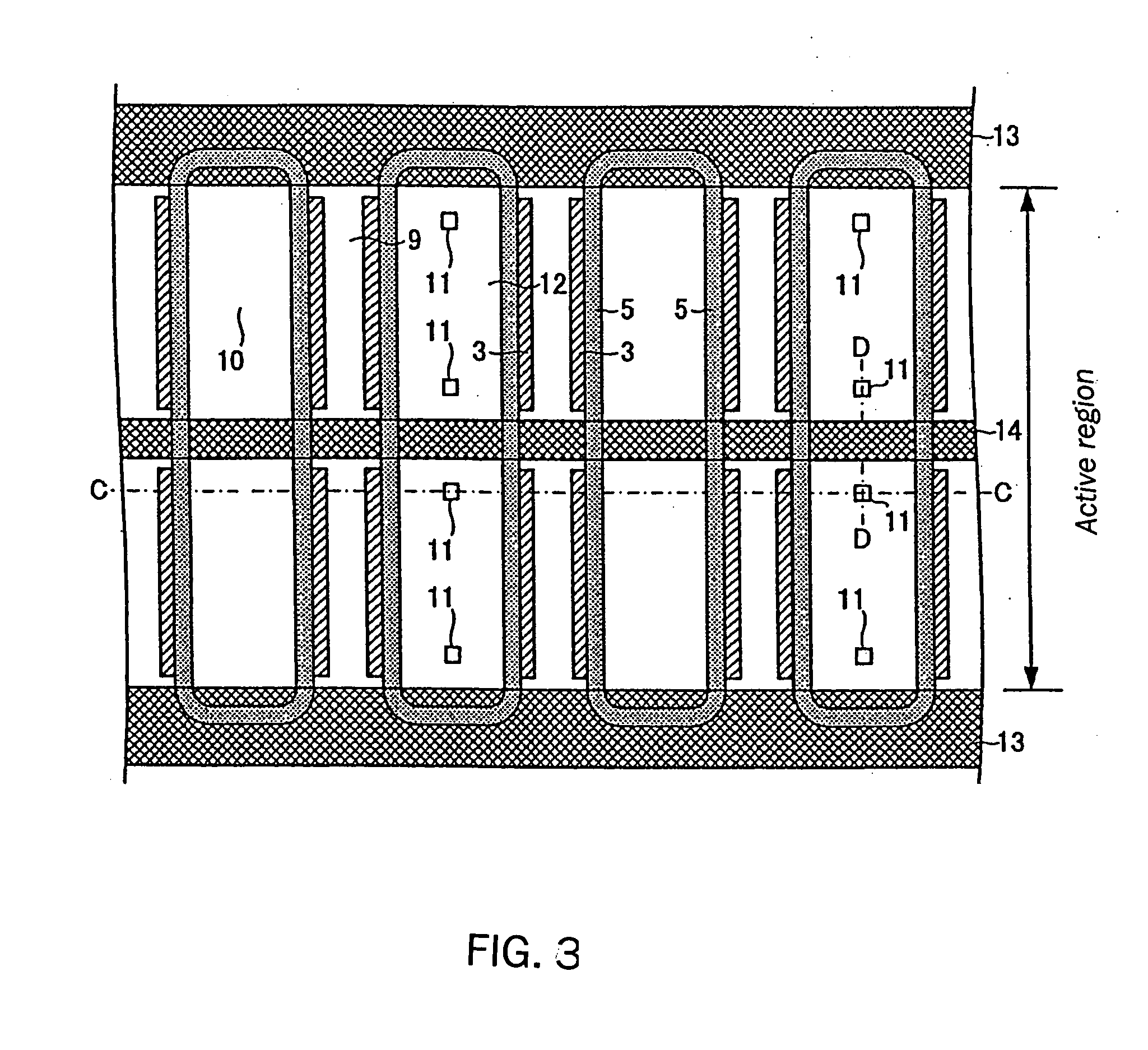

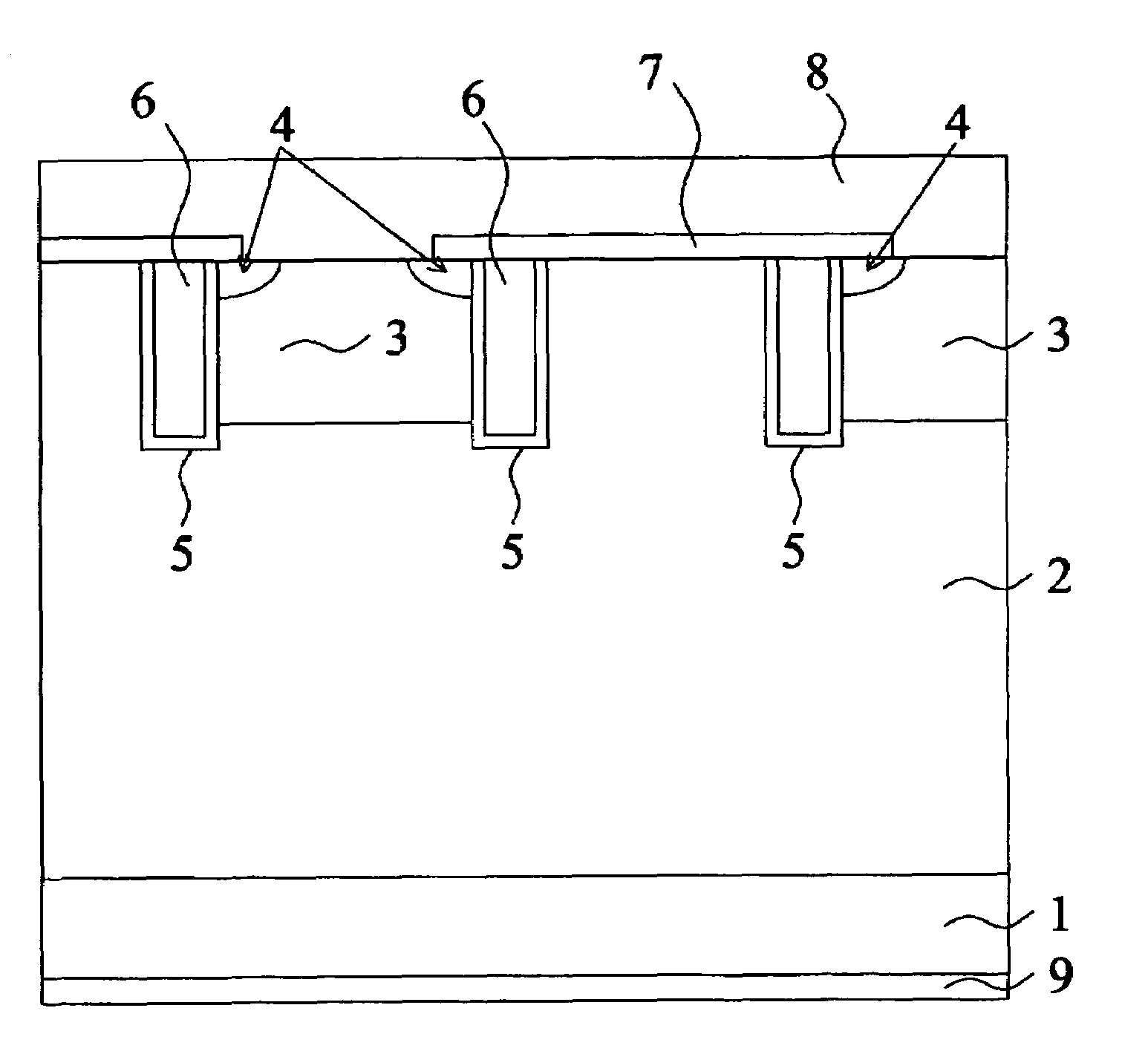

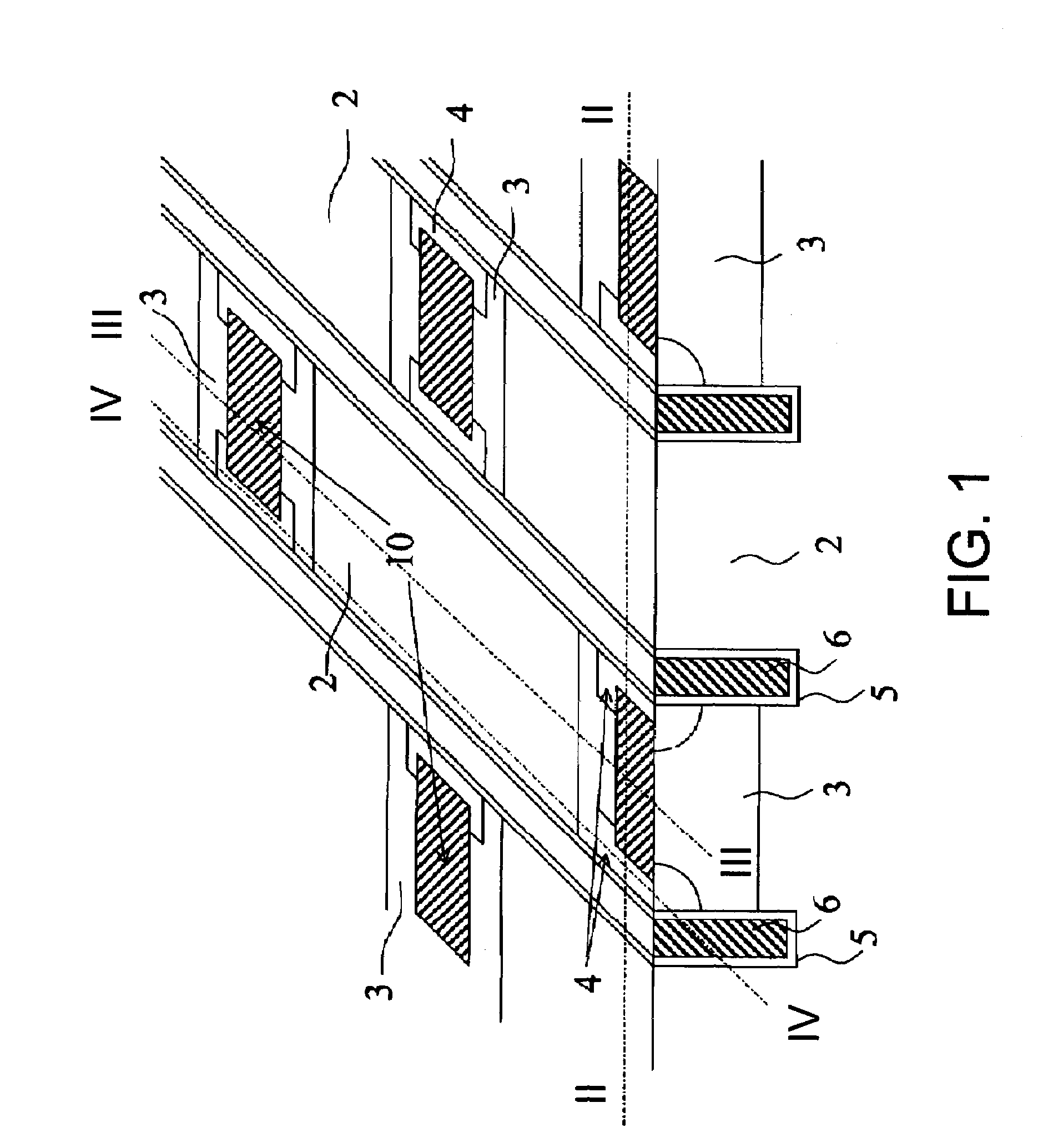

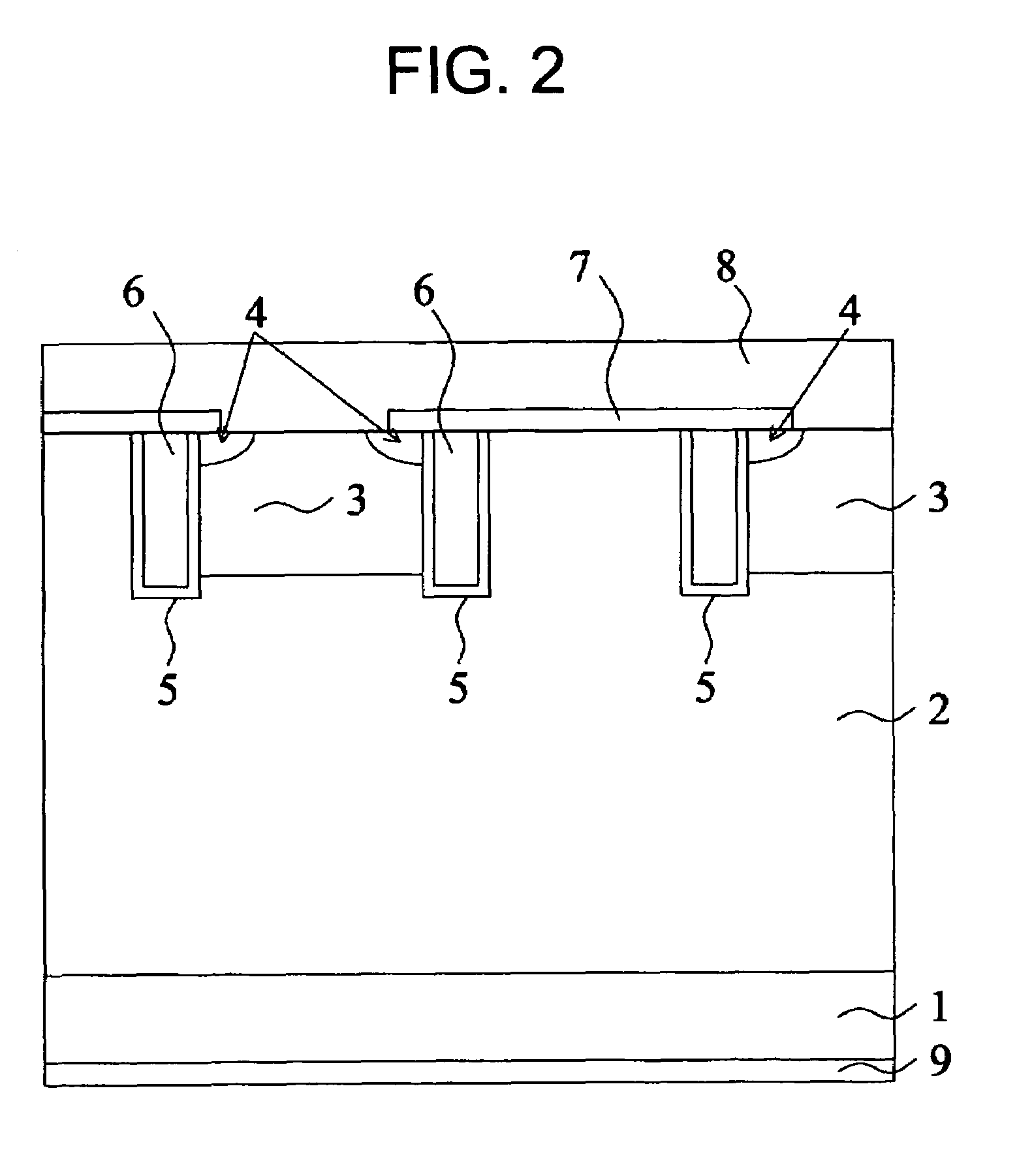

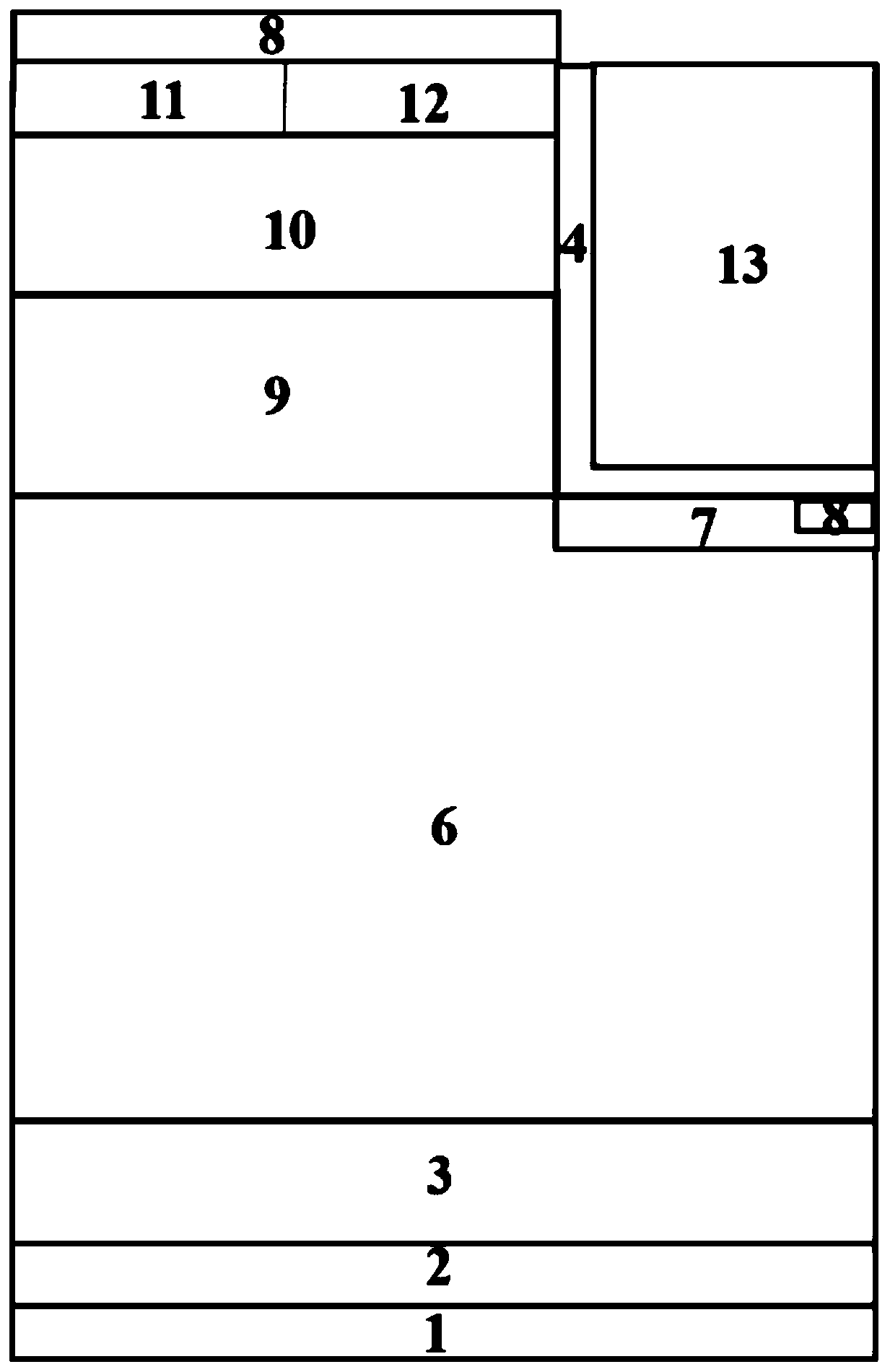

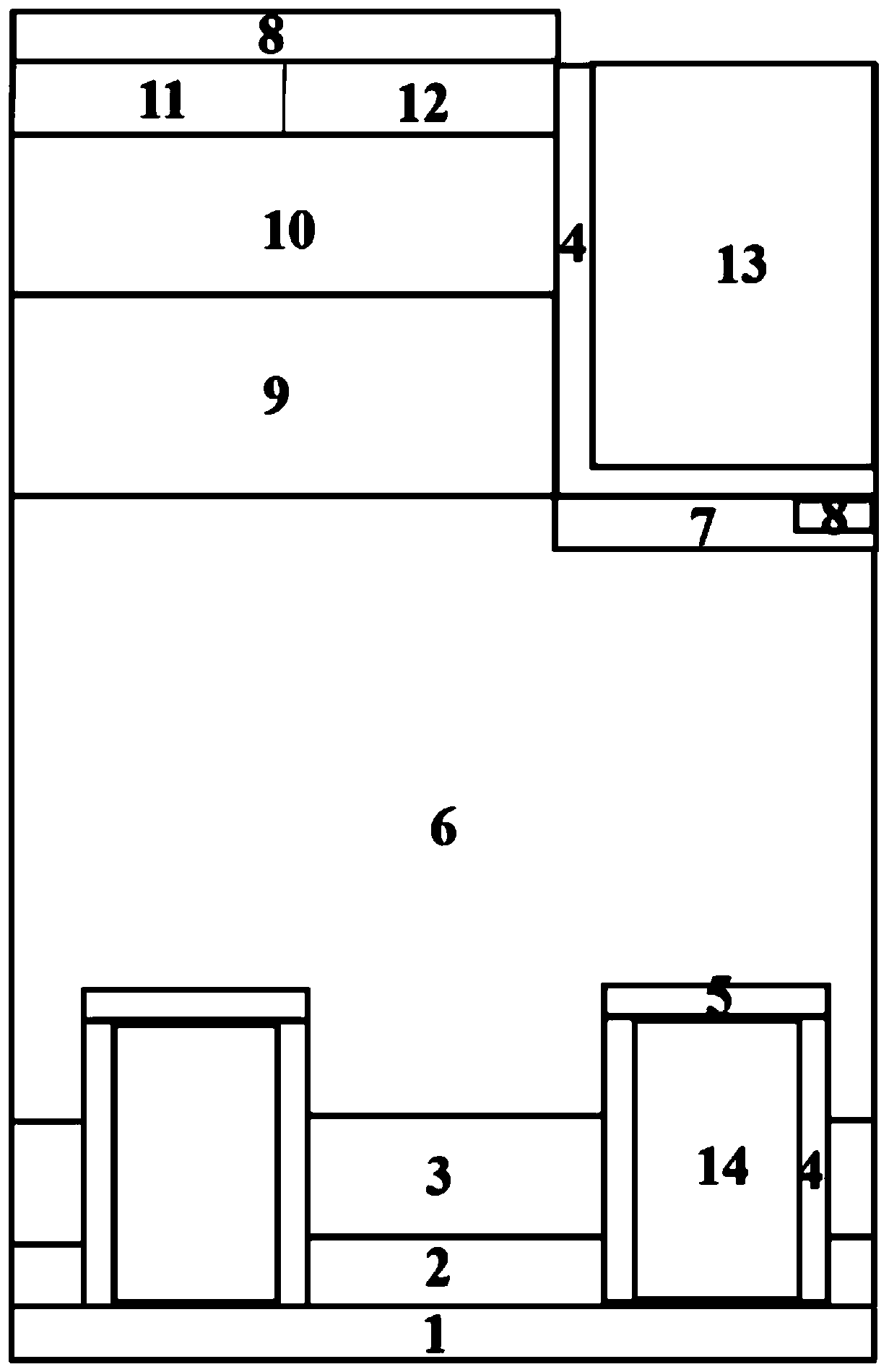

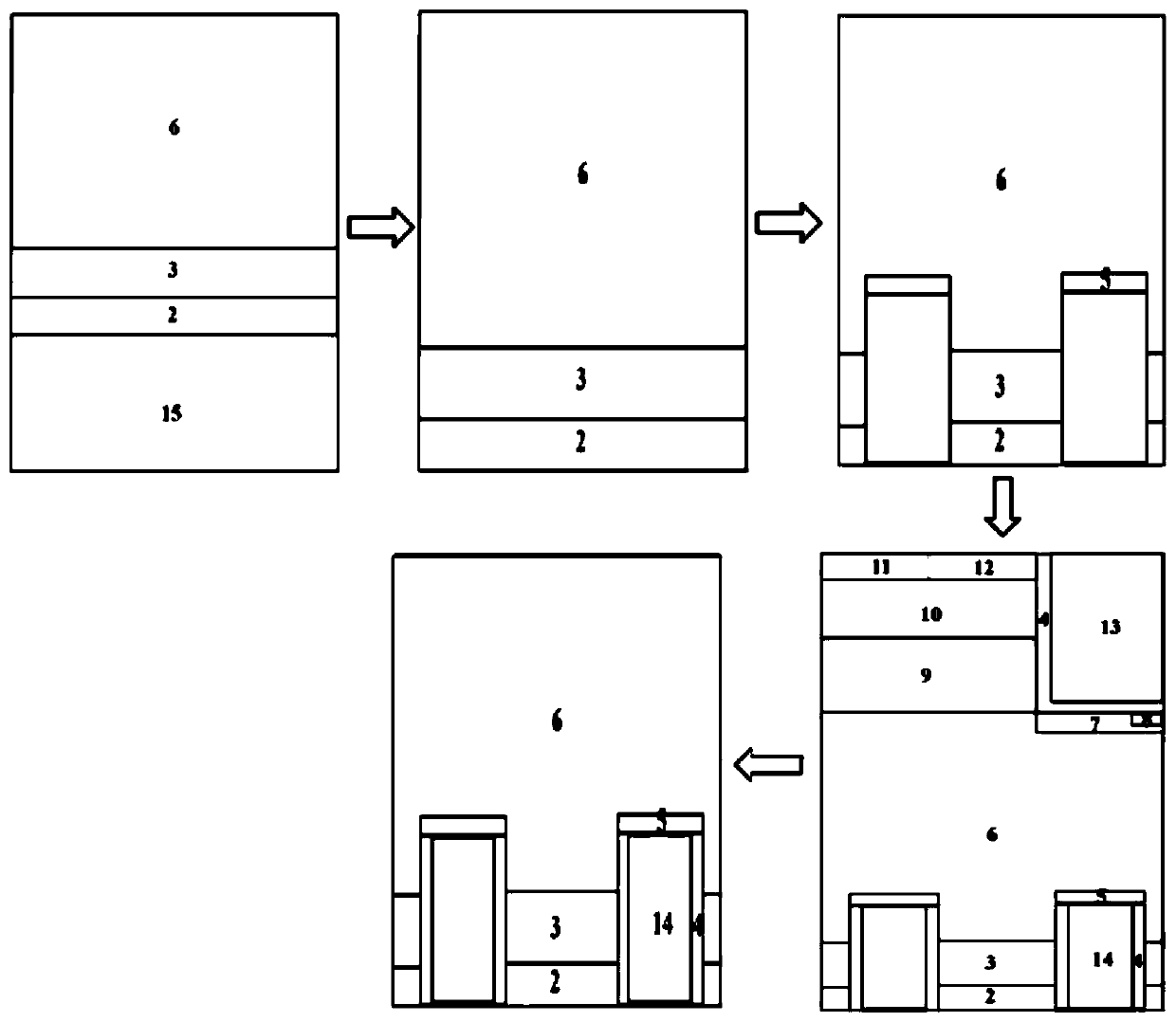

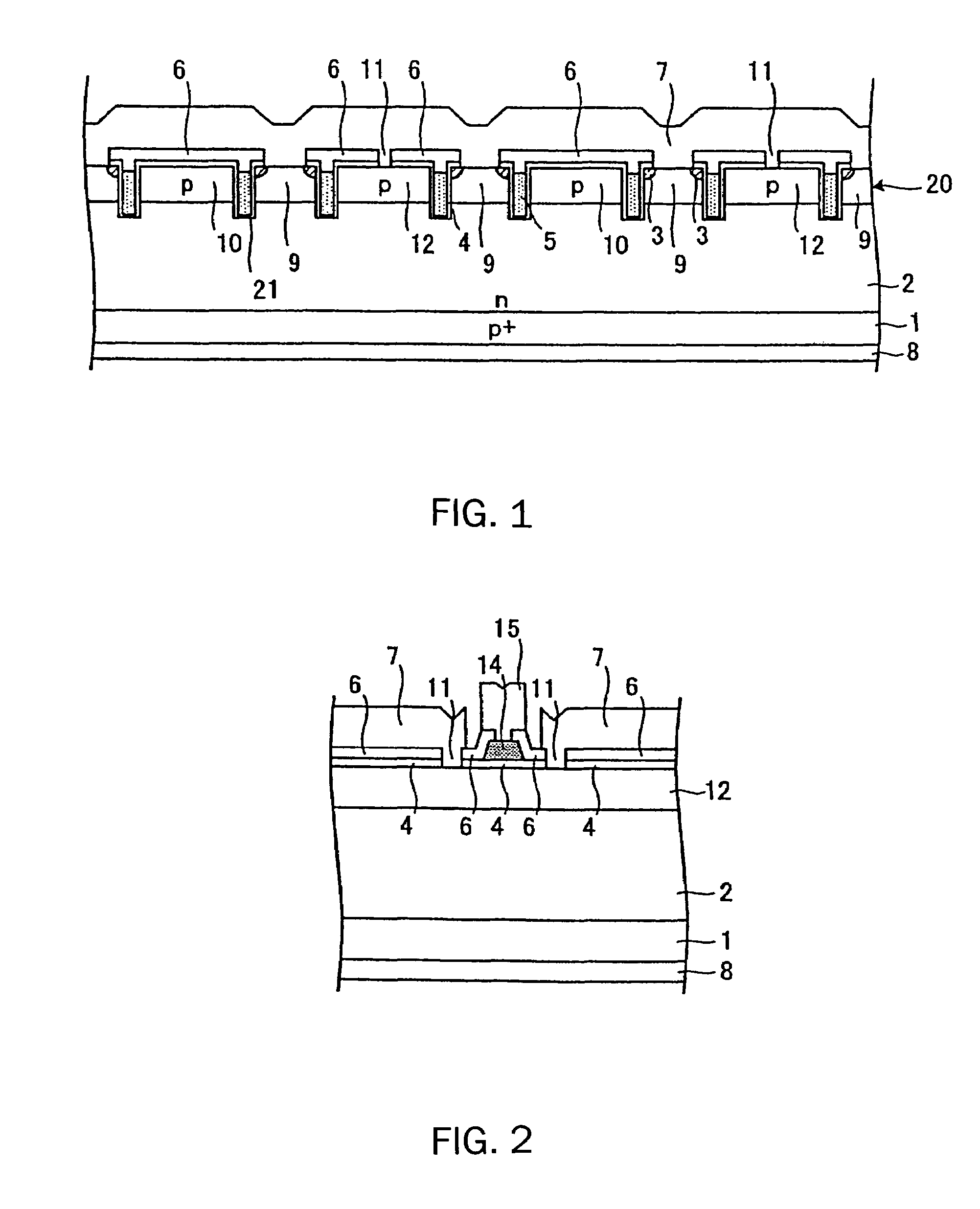

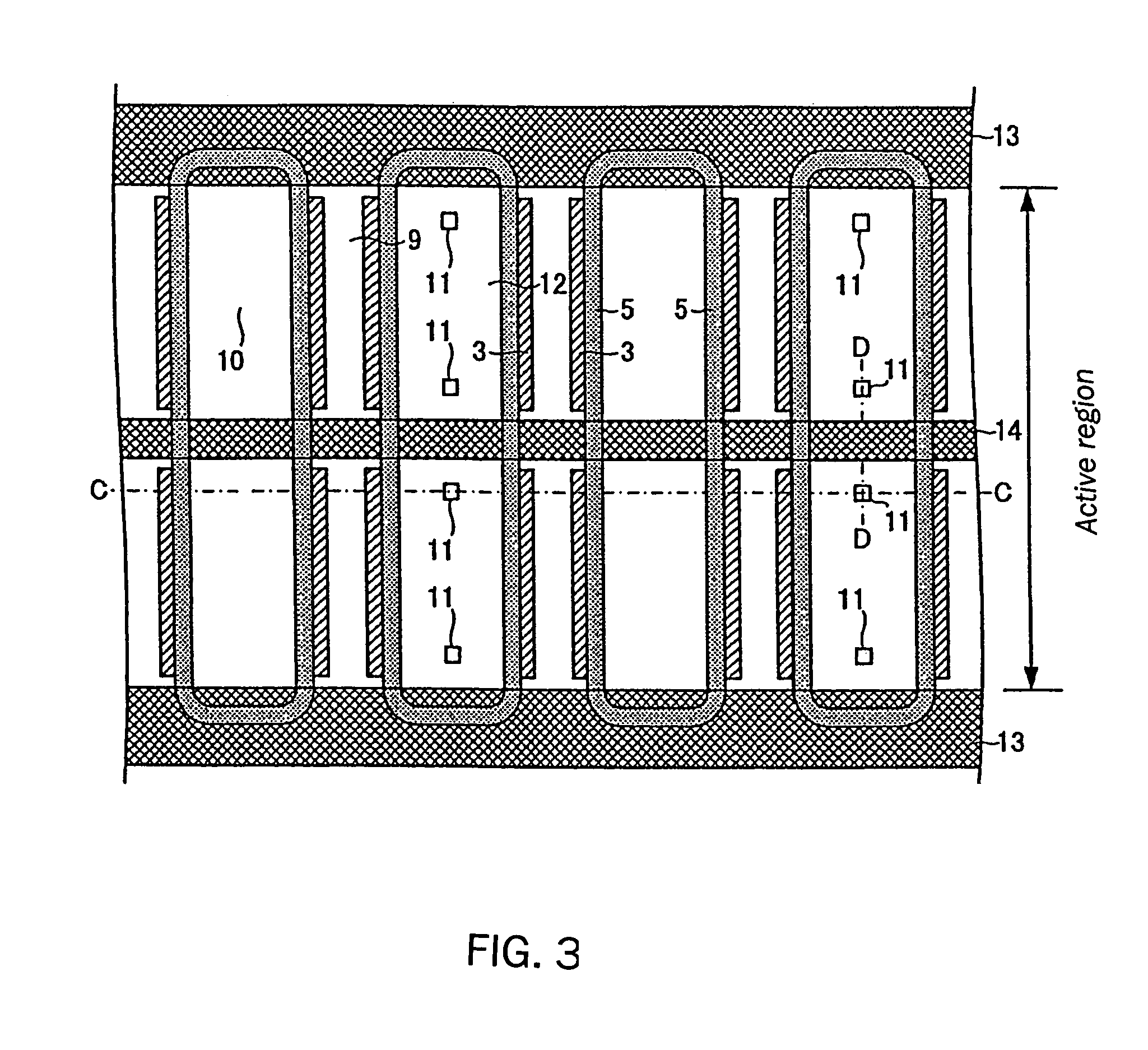

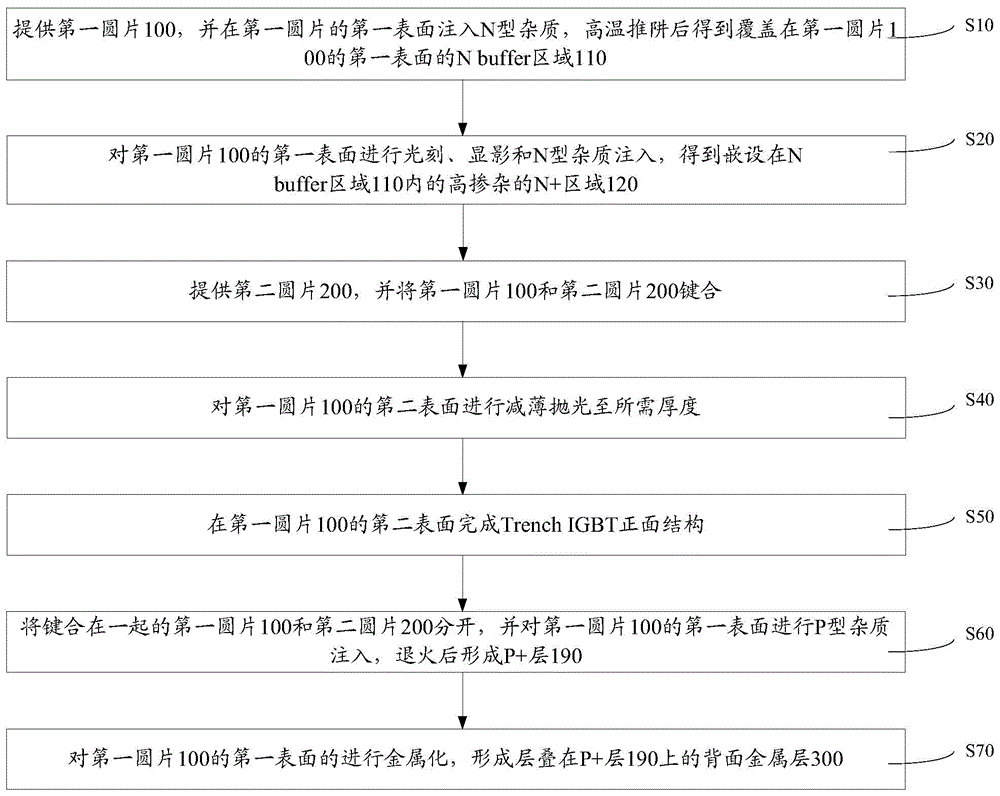

A trench IGBT is disclosed which meets the specifications for turn-on losses and radiation noise. It includes a p-type base layer divided into different p-type base regions by trenches. N-type source regions are formed in only some of the p-type base regions. There is a gate runner in the active region of the trench IGBT. Contact holes formed in the vicinities of the terminal ends of the trenches and on both sides of the gate runner electrically connect some of the p-type base regions that do not include source regions to an emitter electrode. The number N1 of p-type base regions that are connected electrically to the emitter electrode and the number N2 of p-type base regions that are insulated from the emitter electrode are related with each other by the expression 25≦{N1 / (N1+N2)}×100≦75.

Owner:FUJI ELECTRIC CO LTD

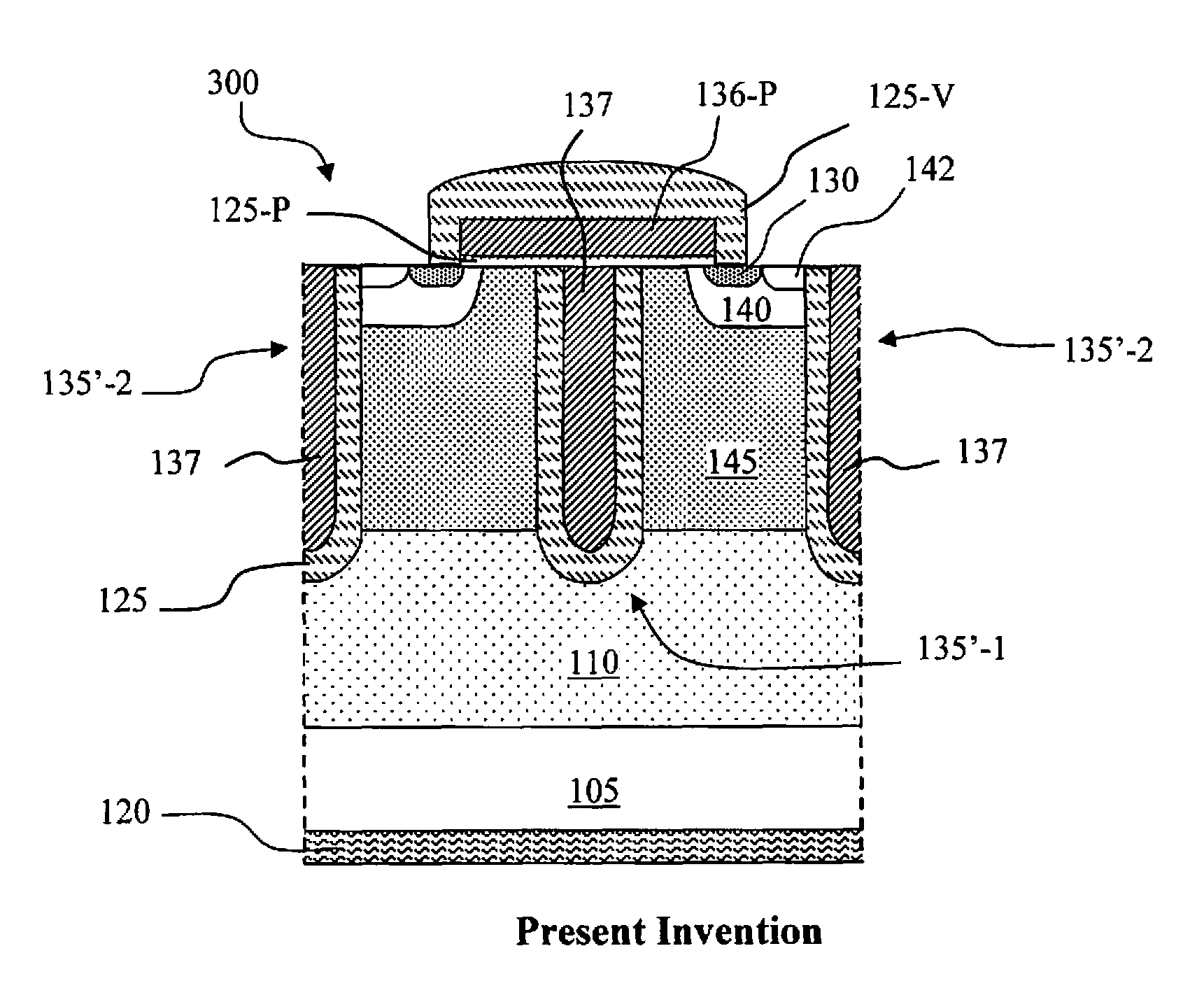

Dual-gate trench IGBT with buried floating p-type shield

ActiveUS20140264433A1Increased durabilityEasy injectionTransistorSemiconductor/solid-state device manufacturingTrench igbtDopant

A method of manufacturing an insulated gate bipolar transistor (IGBT) device comprising 1) preparing a semiconductor substrate with an epitaxial layer of a first conductivity type supported on the semiconductor substrate of a second conductivity type; 2) applying a gate trench mask to open a first trench and second trench followed by forming a gate insulation layer to pad the trench and filling the trench with a polysilicon layer to form the first trench gate and the second trench gate; 3) implanting dopants of the first conductivity type to form an upper heavily doped region in the epitaxial layer; and 4) forming a planar gate on top of the first trench gate and apply implanting masks to implant body dopants and source dopants to form a body region and a source region near a top surface of the semiconductor substrate.

Owner:ALPHA & OMEGA SEMICON INC

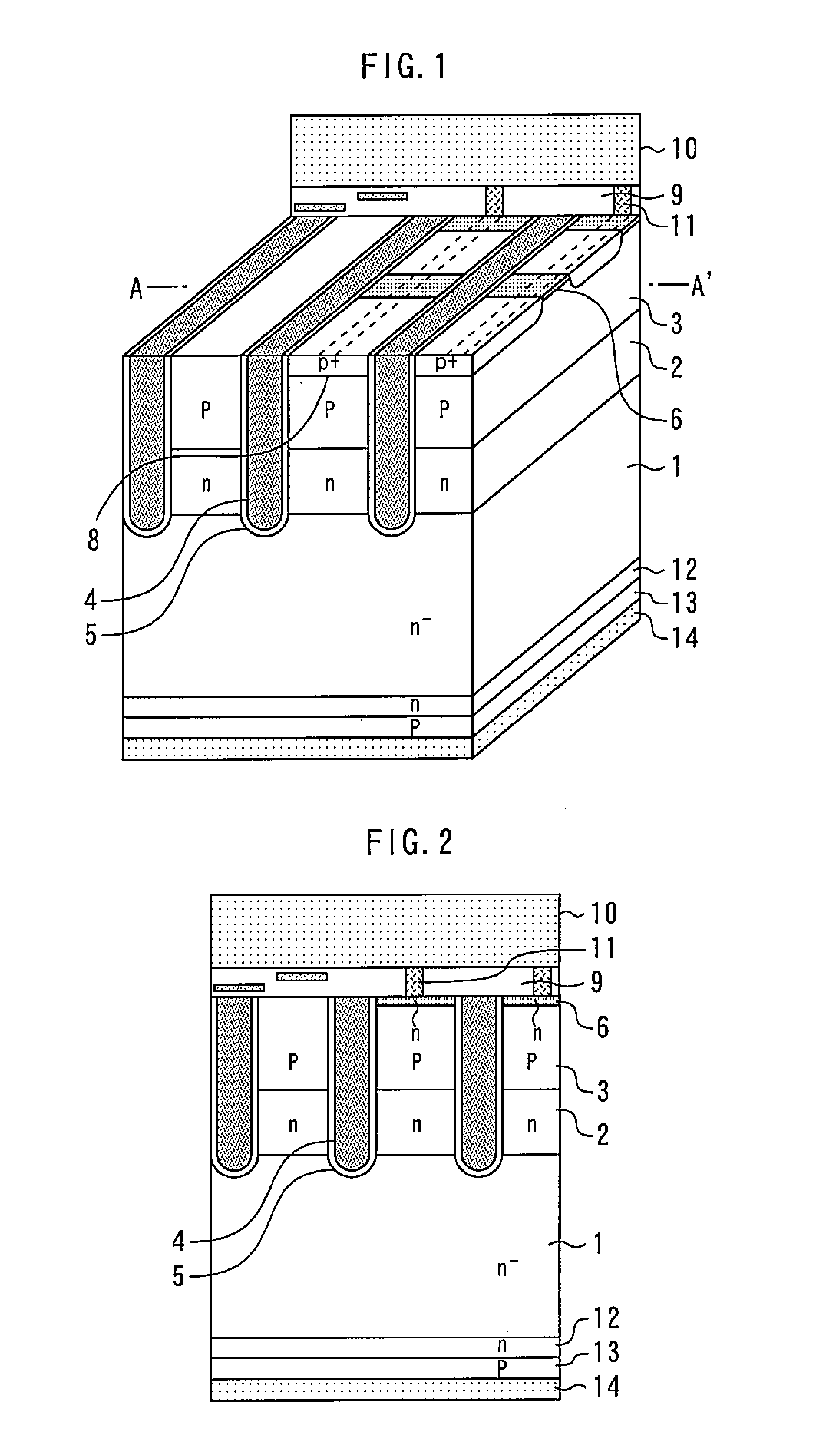

Insulated gate semiconductor device and method of manufacturing the same

ActiveUS20060163649A1Improve breakdown voltageReduce switching lossesSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceTrench igbt

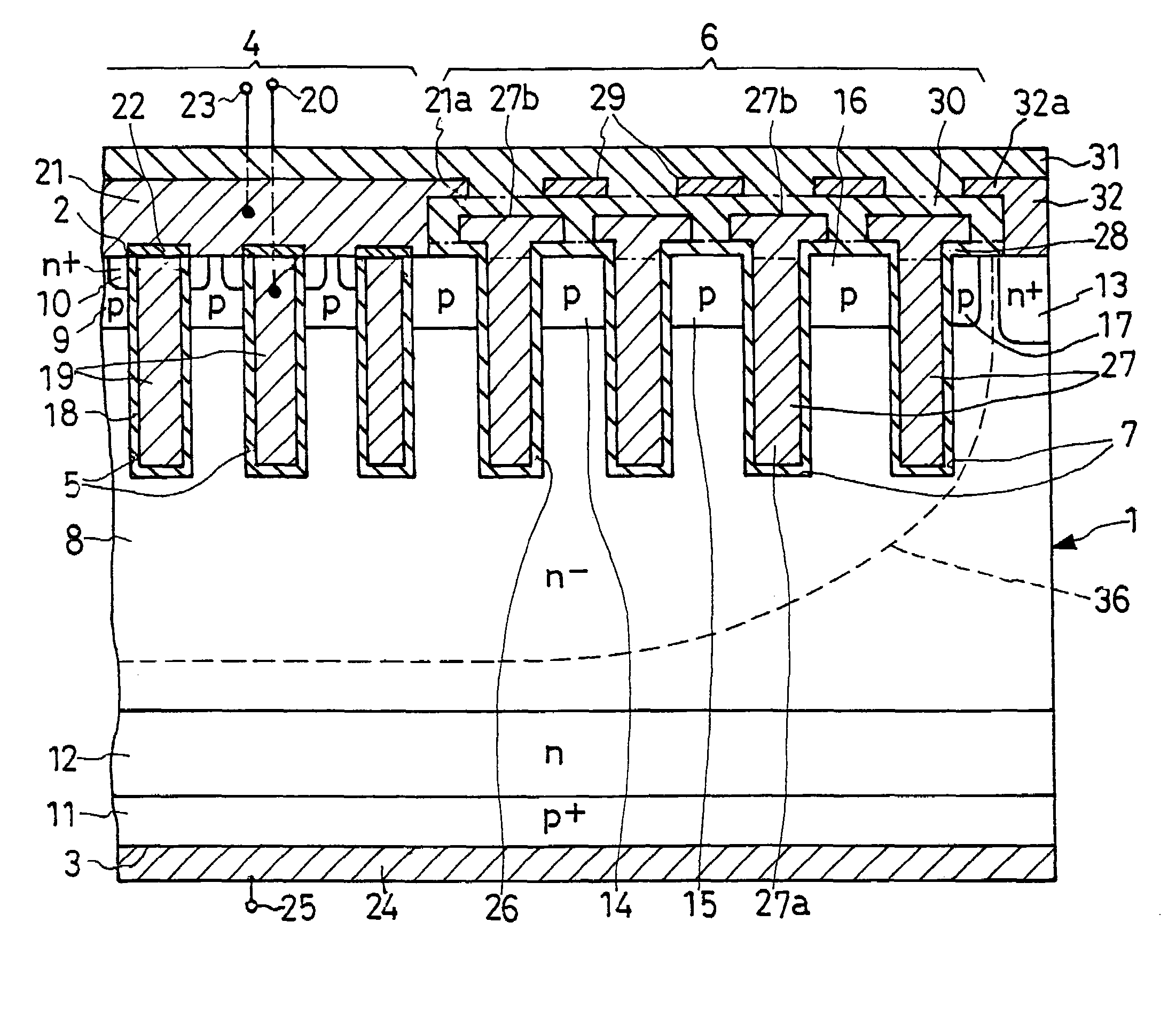

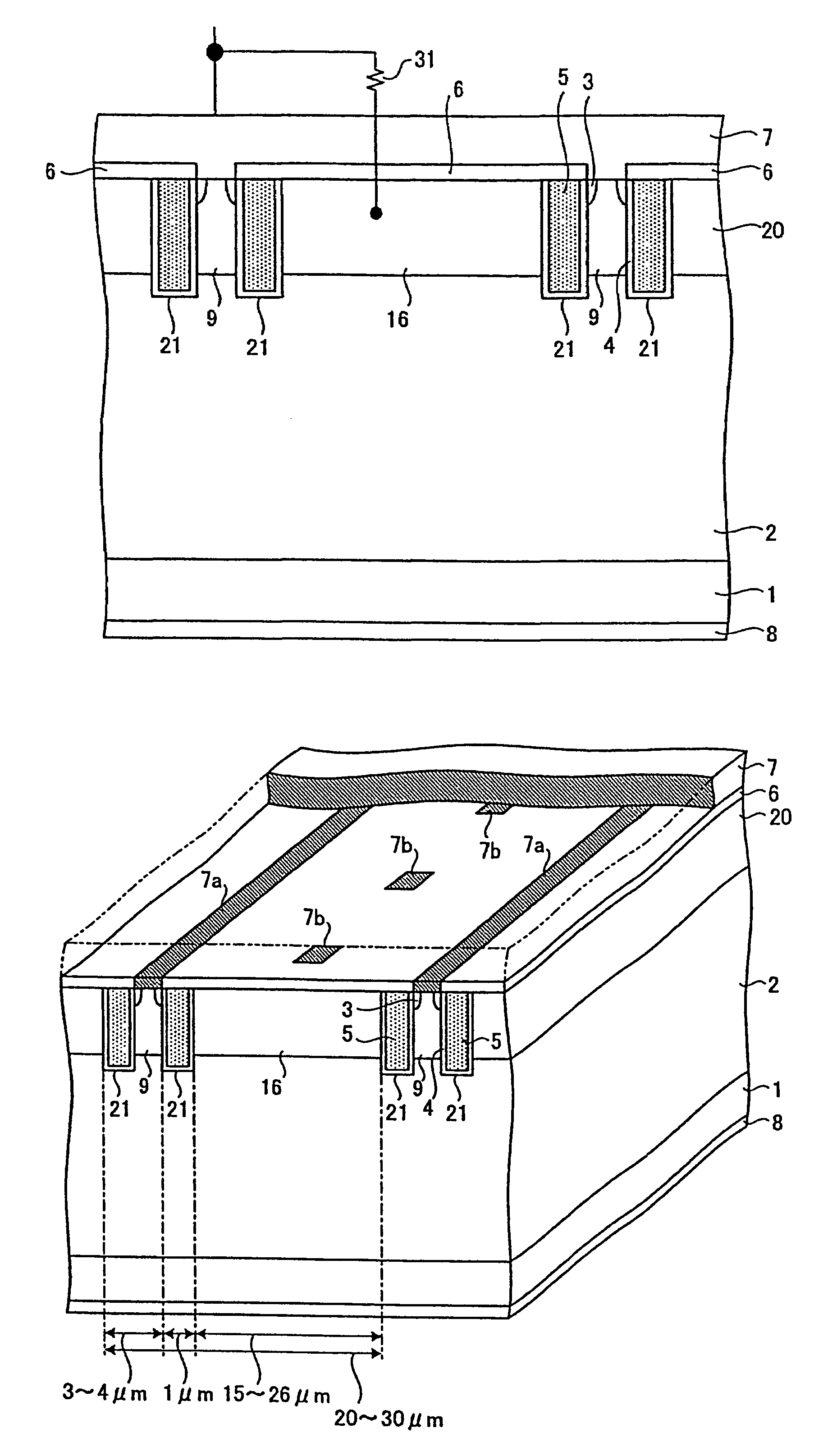

A trench MOSFET includes mesa regions between the trenches. The mesa regions are connected to an emitter electrode to fix the mesa region potential so that the mesa regions do not form a floating structure. P-type base regions are distributed in the mesa regions, and the distributed p-type base regions (e.g., the limited regions in the mesa regions) are provided with an emitter structure. The trench MOSFET can lower the switching losses, reducing the total losses while suppressing the ON-state voltage drop of the trench IGBT as low as the ON-state voltage drop of the IEGT, and improving the turn-on characteristics thereof. The trench MOSFET also can reduce the capacitance between the gates and the emitter thereof, since the regions where the gate electrode faces the emitter structure are reduced. The trench MOSFET can have trench gate structures set at a narrow interval to relax the electric field localization to the bottom portions of the trenches and obtain a high breakdown voltage. The trench MOSFET narrows the mesa region width between the trenches such that the portions of the n-type layer in the mesa regions extending between the trenches are depleted easily by applying a voltage of around several volts.

Owner:FUJI ELECTRIC CO LTD

Trench-type insulated gate bipolar transistor (Trench IGBT) with enhanced internal conductivity modulation

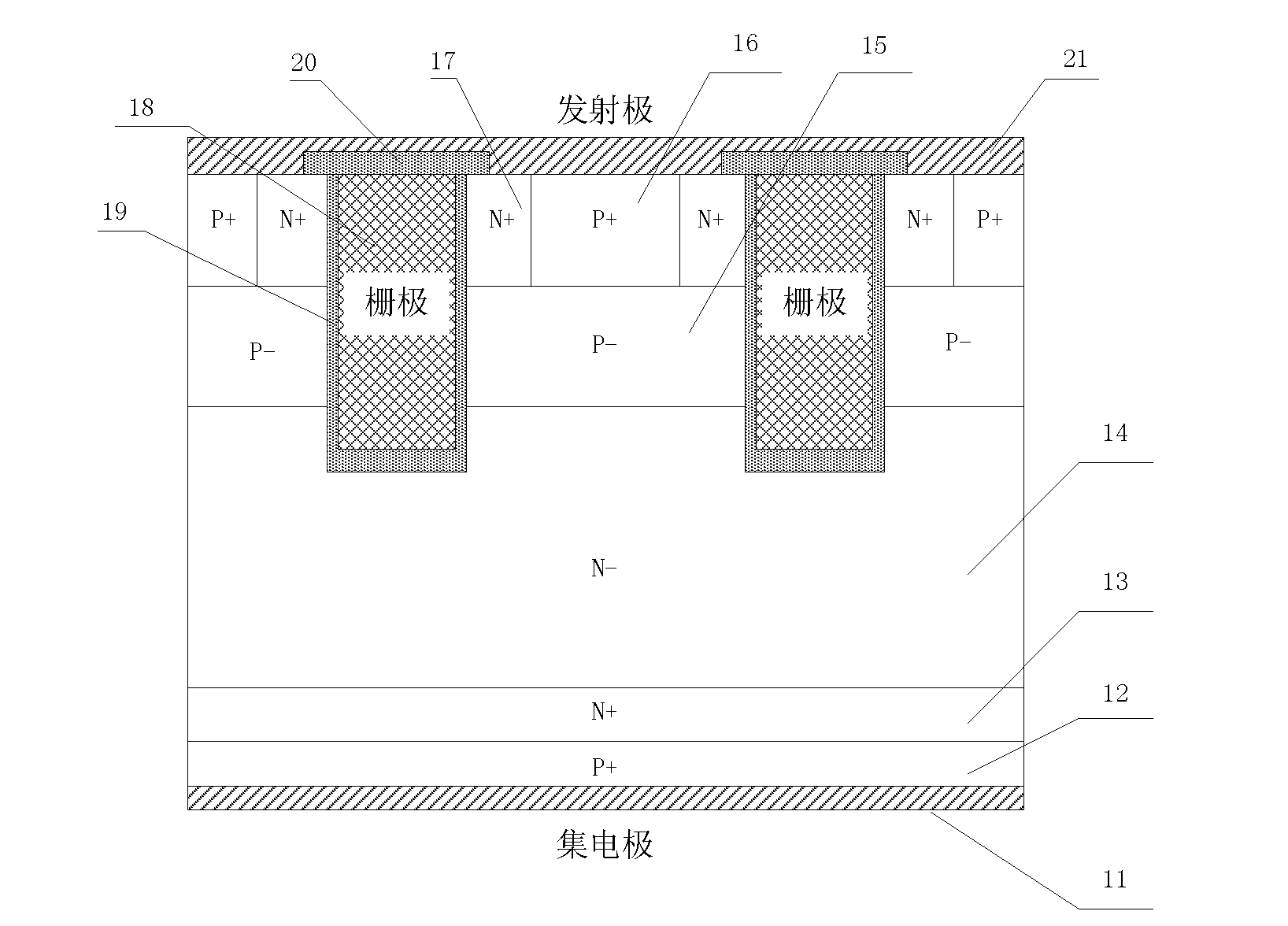

InactiveCN102201439AReduce forward voltage dropImprove concentration distributionSemiconductor devicesTrench igbtParasitic bipolar transistor

The invention relates to a Trench IGBT with enhanced internal conductivity, belonging to the technical field of power semiconductor device. According to the invention, on the basis of the structure of the conventional Trench IGBT device, a dielectric layer is introduced between a P<-> base region and an N<-> drift region of the device so as to effectively prevent the P<-> base region from extracting minority carrier holes at the edge of the N<-> drift region during forward conduction, thereby greatly increasing electrons and hole density of the whole N<-> drift region, optimizing the density distribution of carriers in the drift region, enhancing the conductivity modulation in the device, lowering the forward conduction voltage drop of the device, and better compromising the forward conduction voltage drop and the turn-off loss. Meanwhile, the chip surface utilization rate is not reduced and the chip area is saved. The Trench IGBT is suitable for the field of semiconductor power devices and power integrated circuits from small power to large power.

Owner:INST OF ELECTRONICS & INFORMATION ENG IN

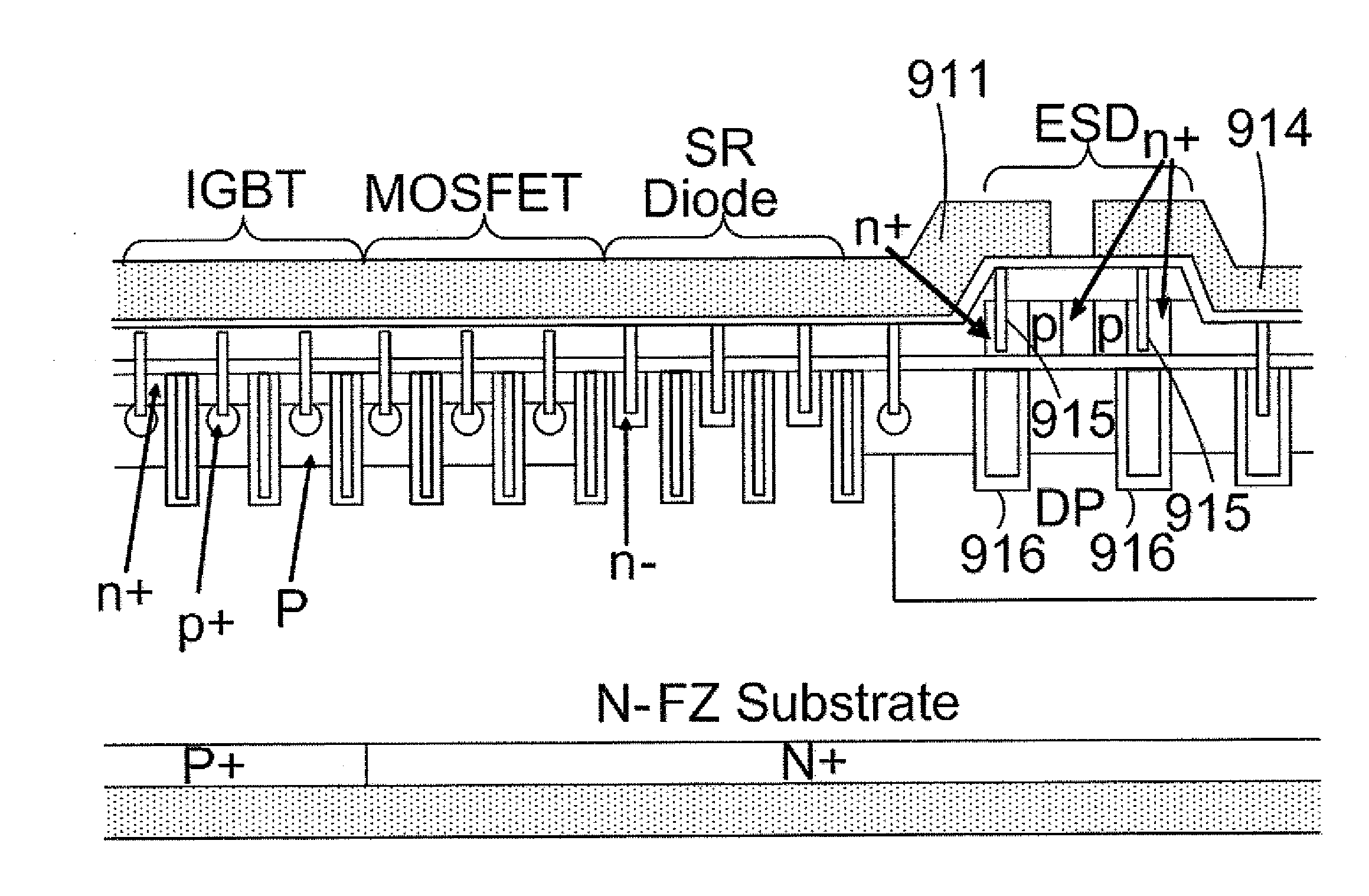

Trench IGBT with trench gates underneath contact areas of protection diodes

A trench PT IGBT (or NPT IGBT) having clamp diodes for ESD protection and prevention of shortage among gate, emitter and collector. The clamp diodes comprise multiple back-to-back Zener Diode composed of doped regions in a polysilicon layer doped with dopant ions of a first conductivity type next to a second conductivity type disposed on an insulation layer above said semiconductor power device. Trench gates are formed underneath the contact areas of the clamp diodes as the buffer layer for prevention of shortage.

Owner:FORCE MOS TECH CO LTD

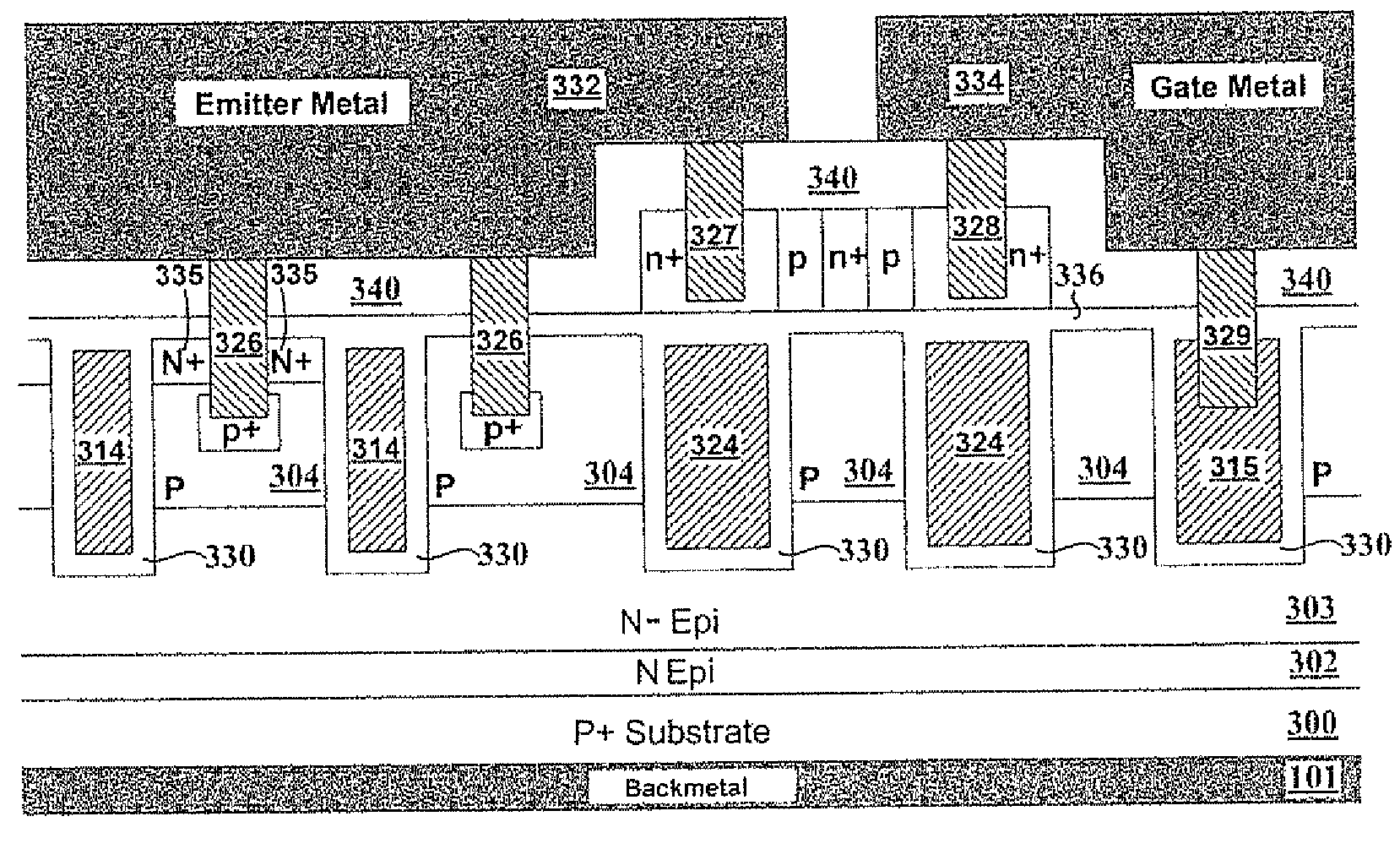

New dual-gate trench IGBT with buried floating p-type shield

ActiveUS20160336394A1Increased durabilityEasy injectionTransistorSemiconductor/solid-state device manufacturingDopantTrench igbt

A method of manufacturing an insulated gate bipolar transistor (IGBT) device comprising 1) preparing a semiconductor substrate with an epitaxial layer of a first conductivity type supported on the semiconductor substrate of a second conductivity type; 2) applying a gate trench mask to open a first trench and second trench followed by forming a gate insulation layer to pad the trench and filling the trench with a polysilicon layer to form the first trench gate and the second trench gate; 3) implanting dopants of the first conductivity type to form an upper heavily doped region in the epitaxial layer; and 4) forming a planar gate on top of the first trench gate and apply implanting masks to implant body dopants and source dopants to form a body region and a source region near a top surface of the semiconductor substrate.

Owner:ALPHA & OMEGA SEMICON INC

Semiconductor device

ActiveUS7615846B2Guaranteed uptimeIncrease marginTransistorTrench igbtElectrical resistance and conductance

An emitter layer is provided in stripes in a direction orthogonal to an effective gate trench region connected to a gate electrode and a dummy trench region isolated from the gate electrode. A width of the emitter layer is determined to satisfy a predetermined relational expression so as not to cause latch-up in an underlying P base layer. In the predetermined relational expression, an upper limit value of the width W of the emitter layer is (3500 / Rspb)·Wso·exp(decimation ratio), where Rspb is a sheet resistance of the P base layer immediately below the emitter layer, Wso is an interval between the trenches, and the decimation ratio is a ratio of the number of the effective gate trench region to the total number of the trench regions. Variations in saturation current in a trench IGBT can be suppressed, and a tolerance of an Reverse Bias Safe Operation Area can be improved.

Owner:MITSUBISHI ELECTRIC CORP

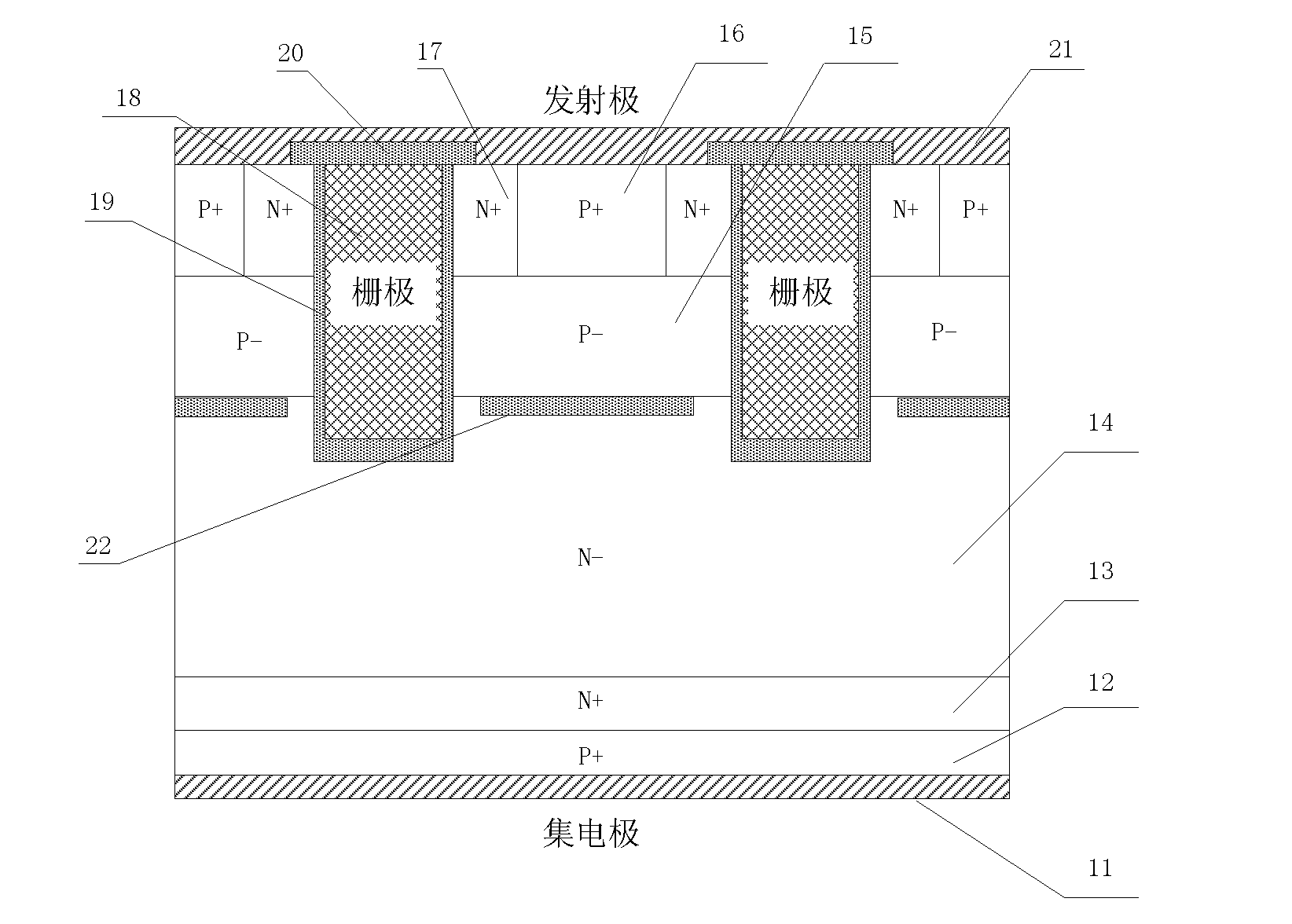

Trench insulated gate bipolar transistor and preparation method therefor

InactiveCN105789269AFacilitated DiffusionAvoid concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesTrench igbtPower flow

The invention discloses a trench insulated gate bipolar transistor and a preparation method therefor. The trench insulated gate bipolar transistor (IGBT) comprises an N- type base region, a P type base region, an N+ buffer layer, a back P+ emitter region, an N+ collector region, a gate oxide layer, a polycrystal gate, a collector electrode, an emitting electrode, a gate electrode, a P+ type base region, a carrier storage layer, and a P- type floating layer, wherein the N- type base region, the N+ buffer layer, the back P+ emitter region and the collector electrode are arranged from the upper to lower in sequence; a groove body is formed around the upper part of the N- type base region; and the P- type floating layer is arranged in the groove body. According to the trench insulated gate bipolar transistor and the preparation method therefor provided by the invention, the carrier storage layer is introduced to the conventional trench IGBT structure, so that the electron diffusion can be improved, current centralization can be avoided, and electric conductance modulation can be reinforced; and meanwhile, the P- type floating layer is additionally arranged at the lower end of the trench gate, so that a voltage-division effect is achieved, and the withstand voltage of the device is improved.

Owner:SHANGHAI Y POWERSEMI ELECTRONICS TECH CO LTD

Deep N diffusion for trench IGBT

InactiveCN1921146ALower forward voltageReduce forward voltage dropTransistorTrench igbtHigh concentration

The present invention relates to a deep N diffusion for trench IGBT. An increased conductivity deep diffusion of the same conductivity type as that of the drift region is provided between adjacent trenches of a trench type IGBT and below the trenches to reduce the on resistance components of the drift region resistance and spreading resistance to current flow when the device is turned on. The deep diffusion has a higher concentration than that of the drift region, and has a width of from 4 to 10 microns. The wafer or die has a total width (or thickness) of about 70 to about 300 microns.

Owner:INTERNATIONAL RECTIFIER COEP

Variable threshold trench IGBT with offset emitter contacts

ActiveUS20090146177A1Reduce field crowdingReduce channel densityTransistorSolid-state devicesTrench igbtEngineering

A trench type IGBT as disclosed herein includes a plurality of channel regions having one threshold voltage for the normal operation of the device and a plurality of channel regions having a threshold voltage higher than the threshold voltage for the normal operation of the device.

Owner:INFINEON TECH AMERICAS CORP

Insulated gate semiconductor device and method of manufacturing the same

ActiveUS7633122B2Improve breakdown voltageReduce switching lossesSemiconductor/solid-state device manufacturingSemiconductor devicesTrench igbtCapacitance

A trench MOSFET includes mesa regions between the trenches. The mesa regions are connected to an emitter electrode to fix the mesa region potential so that the mesa regions do not form a floating structure. P-type base regions are distributed in the mesa regions, and the distributed p-type base regions (e.g., the limited regions in the mesa regions) are provided with an emitter structure. The trench MOSFET can lower the switching losses, reducing the total losses while suppressing the ON-state voltage drop of the trench IGBT as low as the ON-state voltage drop of the IEGT, and improving the turn-on characteristics thereof. The trench MOSFET also can reduce the capacitance between the gates and the emitter thereof, since the regions where the gate electrode faces the emitter structure are reduced. The trench MOSFET can have trench gate structures set at a narrow interval to relax the electric field localization to the bottom portions of the trenches and obtain a high breakdown voltage. The trench MOSFET narrows the mesa region width between the trenches such that the portions of the n-type layer in the mesa regions extending between the trenches are depleted easily by applying a voltage of around several volts.

Owner:FUJI ELECTRIC CO LTD

Trench semiconductor device of improved voltage strength, and method of fabrication

InactiveUS7521755B2Improve pressure resistanceSimple processTransistorSemiconductor/solid-state device manufacturingTrench igbtCapacitance

A trench IGBT is disclosed which includes a semiconductor substrate having formed therein a set of cell trenches formed centrally and a set of annular guard trenches concentrically surrounding the cell trenches. The cell trenches receive cell trench conductors via cell trench insulators for providing IGBT cells. The guard trenches receive guard trench conductors via guard trench insulators for enabling the IGBT to withstand higher voltages through mitigation of field concentrations. Capacitive coupling conductors overlie the guard trench conductors via a dielectric layer, each for capacitively coupling together two neighboring ones of the guard trench conductors. The capacitive coupling conductors are easily adjustably variable in shape, size and placement relative to the guard trench conductors for causing the individual guard trench conductors to possess potentials for an optimal contour of the depletion layer.

Owner:SANKEN ELECTRIC CO LTD

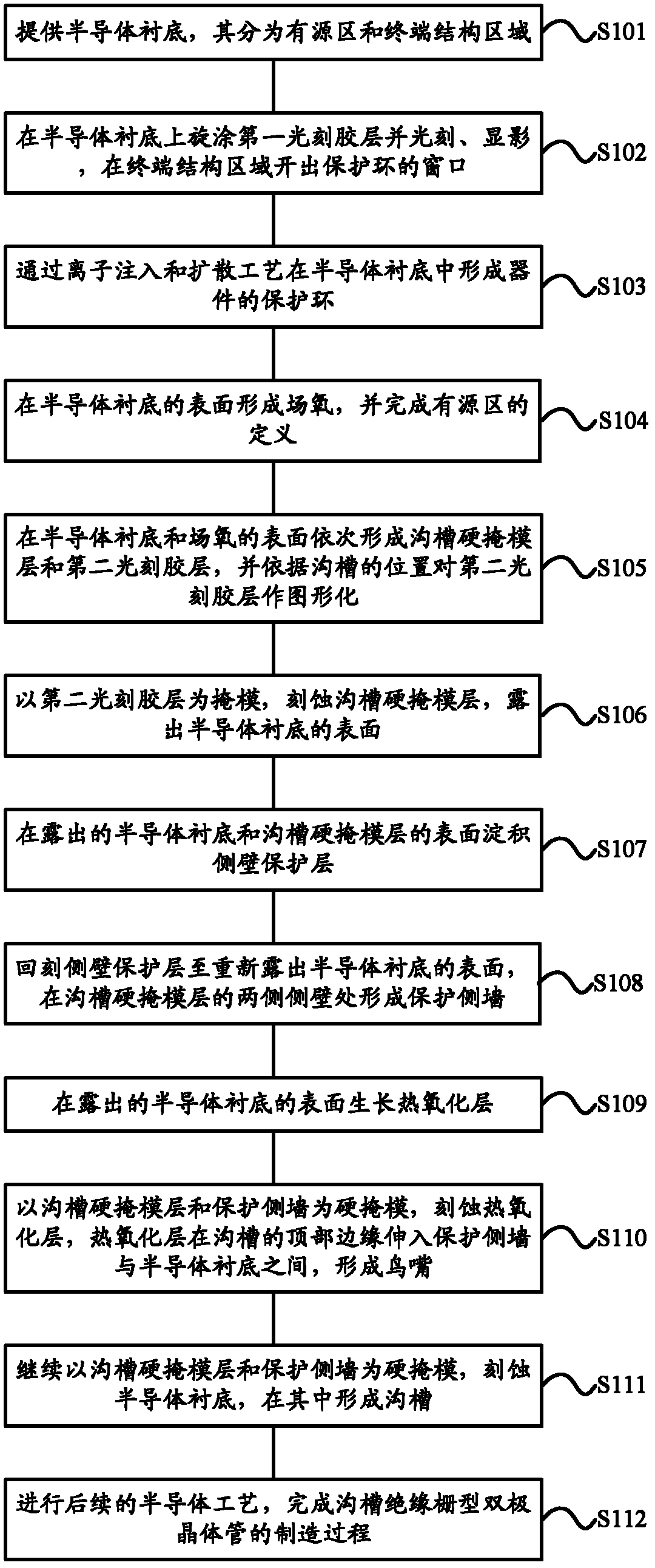

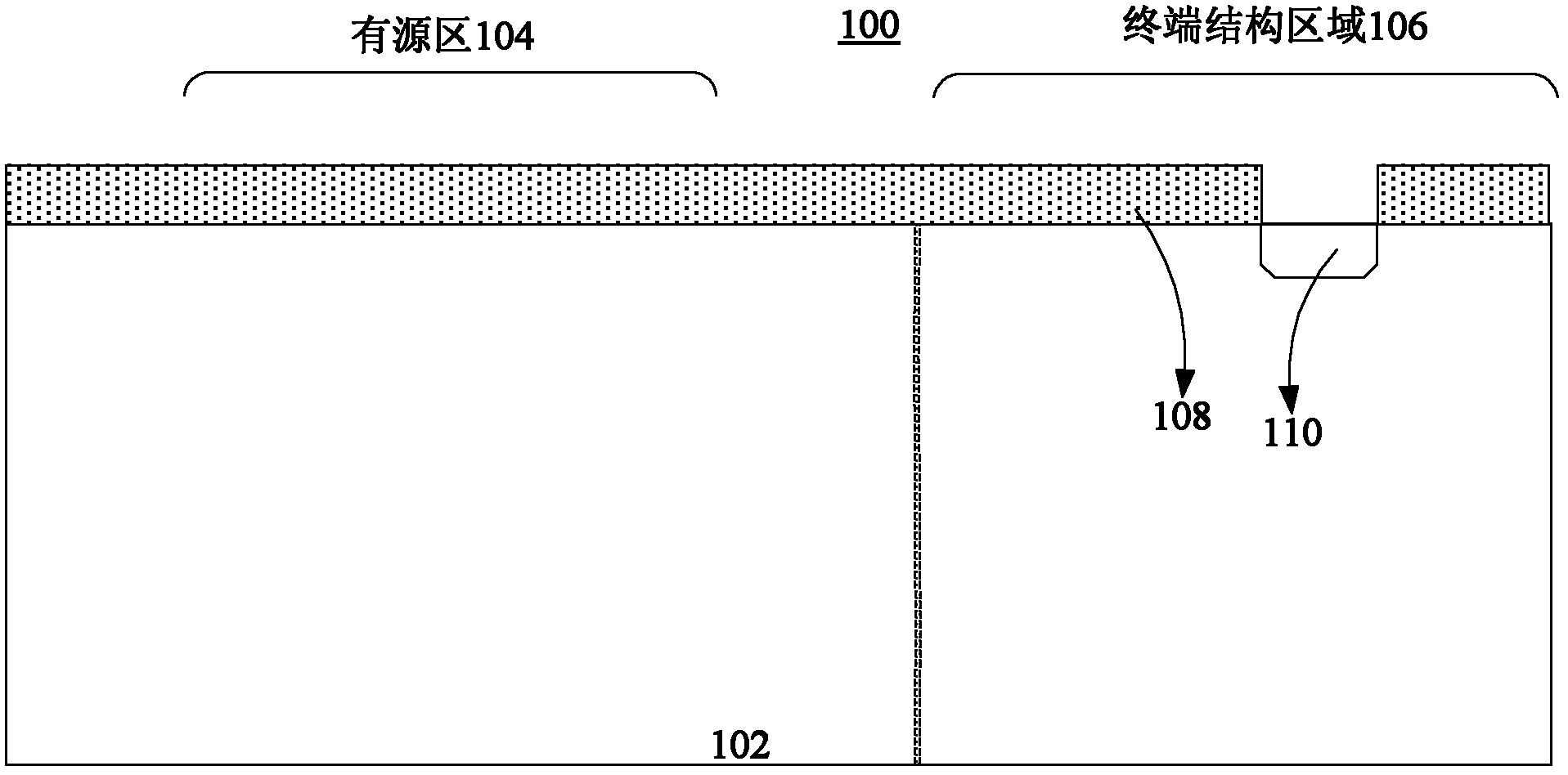

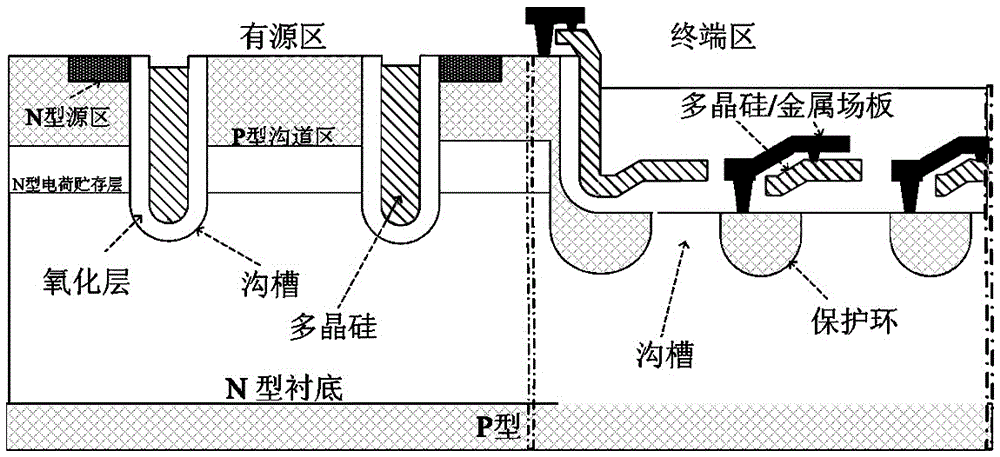

Manufacturing method of trench IGBT

ActiveCN102496573AAvoid leakage failureAvoid reliabilitySemiconductor/solid-state device manufacturingTrench igbtEngineering

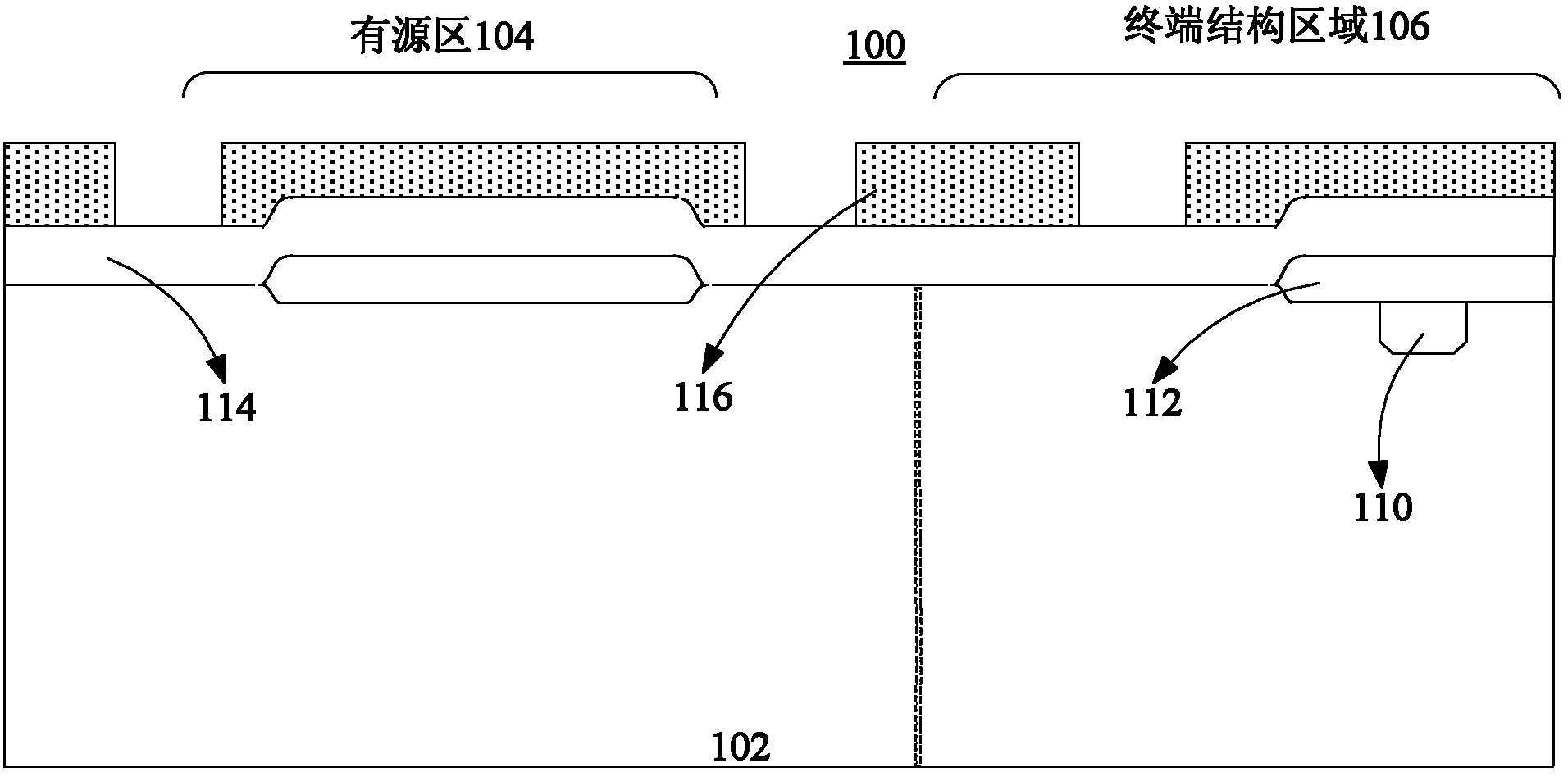

The invention provides a manufacturing method of a trench IGBT. The method comprises the following steps: providing a substrate and dividing into an active region and a terminal structure region; opening a window of a protection ring in the terminal structure region; through an ion implantation and diffusion technology, forming the device protection ring in the substrate; forming field oxide on a surface of the substrate and completing an active region definition; forming a groove hard mask layer and a photoresist layer on the surfaces of the substrate and the field oxide, and imaging the photoresist layer; etching the groove hard mask layer and exposing the substrate; depositing a sidewall protection layer on the surface of the substrate and performing etchback, forming protection side walls on sidewalls of two sides of the groove hard mask layer and growing a thermal oxide layer on the surface of the substrate; taking the groove hard mask layer and the protection side walls as the hard mask so as to successively etch the thermal oxide layer and the substrate and forming a groove in the substrate, wherein the thermal oxide layer which is on a top of the groove extends between the protection side walls and the substrate so as to form a beak. According to the invention, generation of a closed angle of the groove top can be avoided. Grid leakage failure and a reliability problem caused by the closed angle can be prevented.

Owner:ADVANCED SEMICON MFG CO LTD

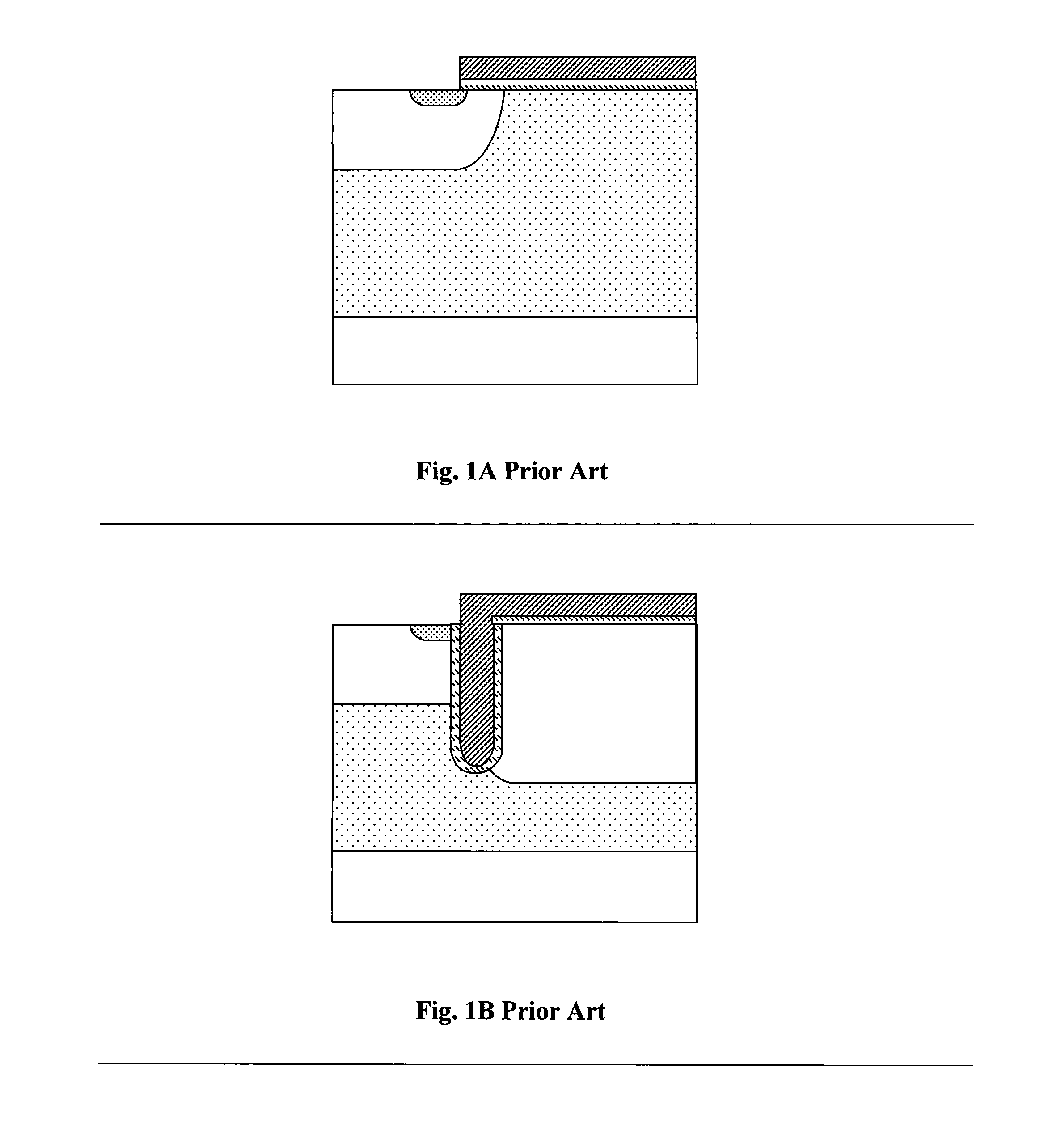

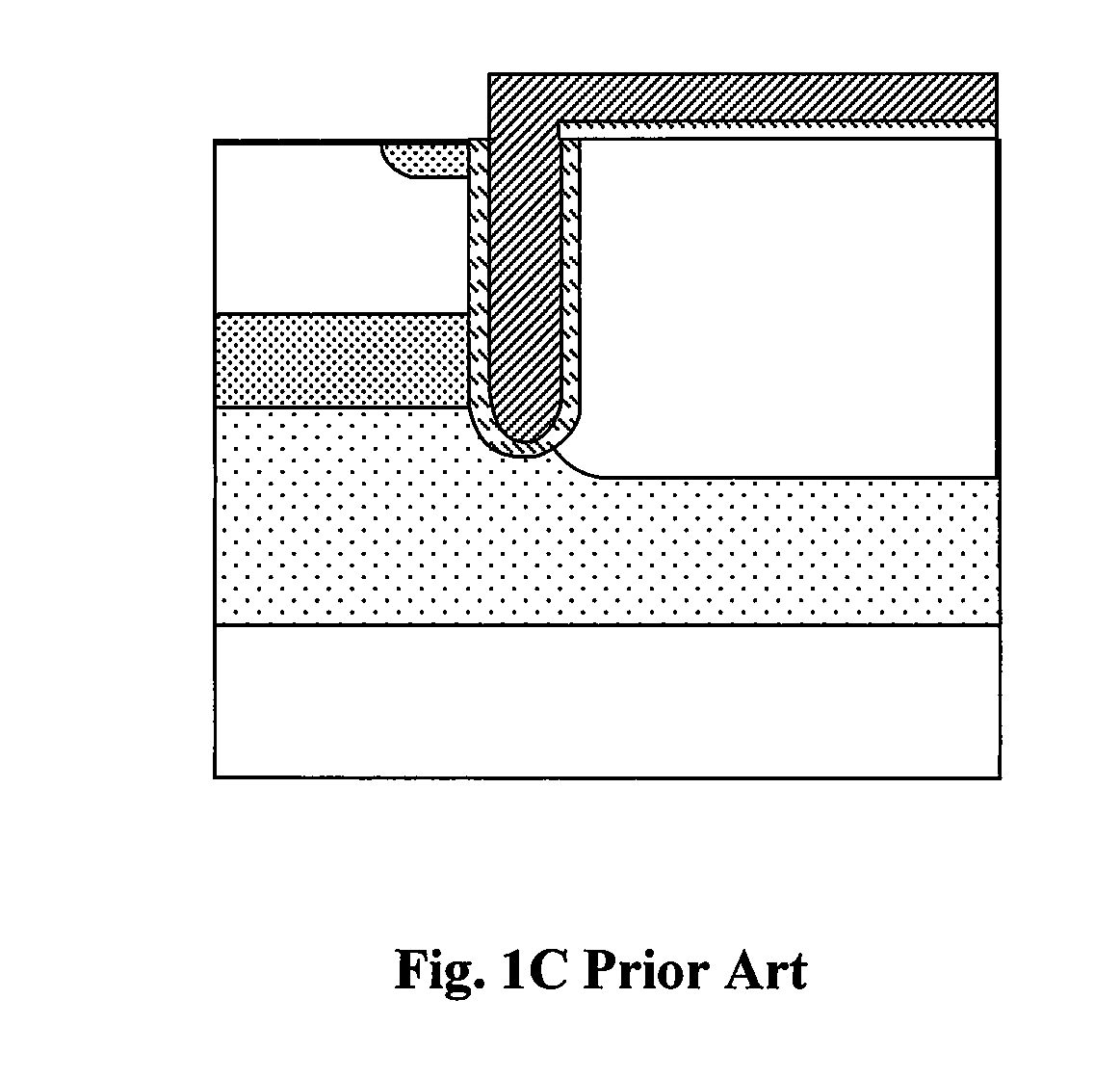

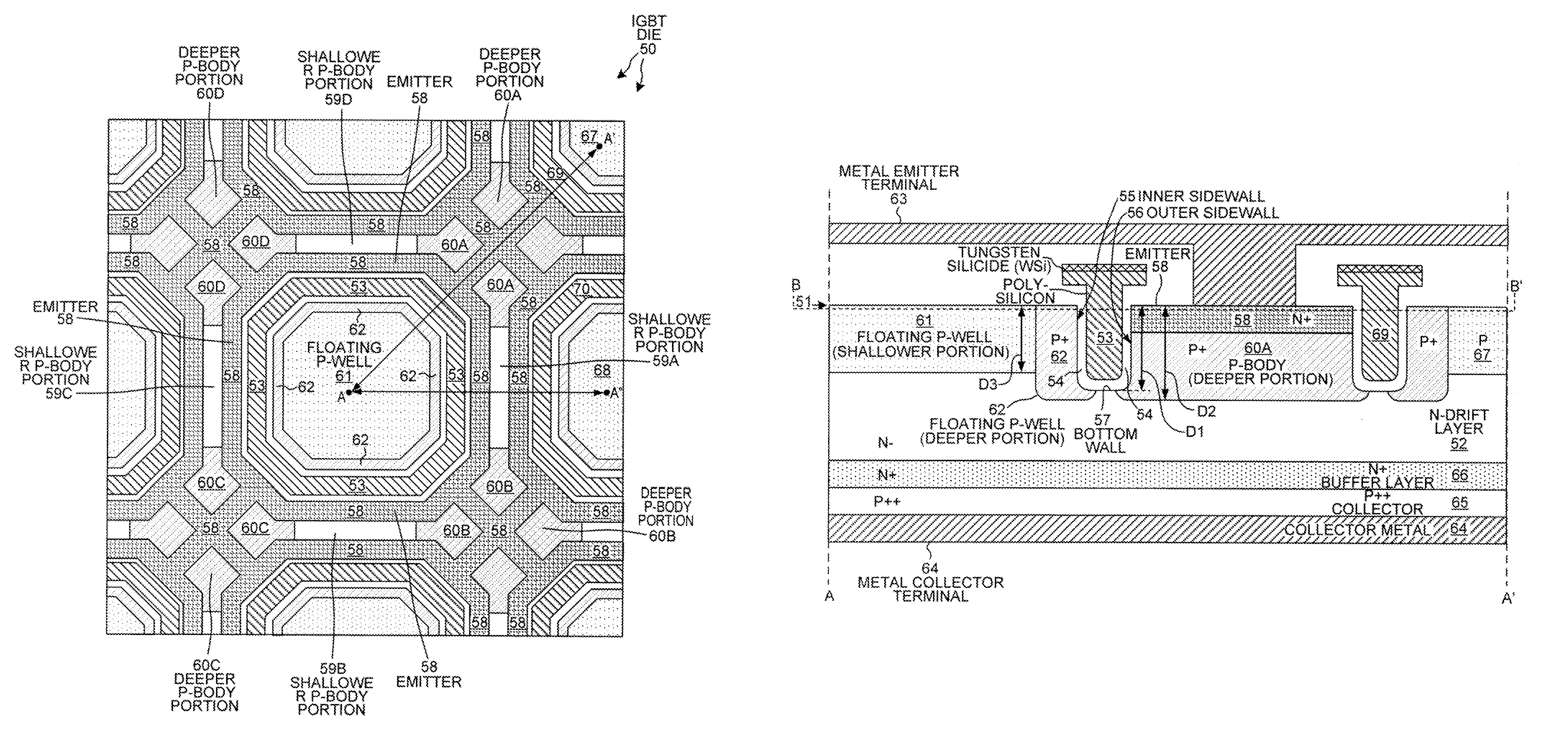

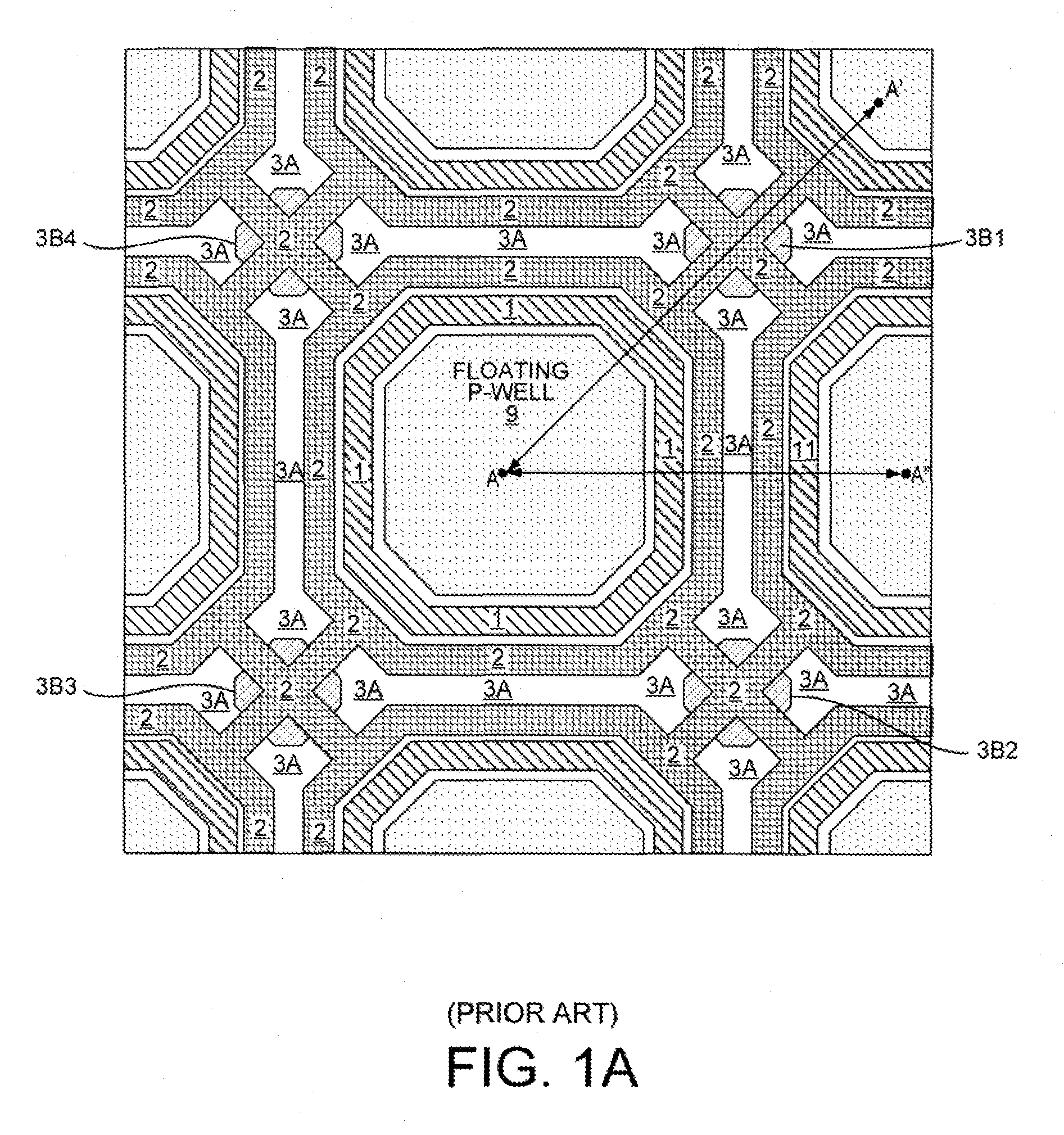

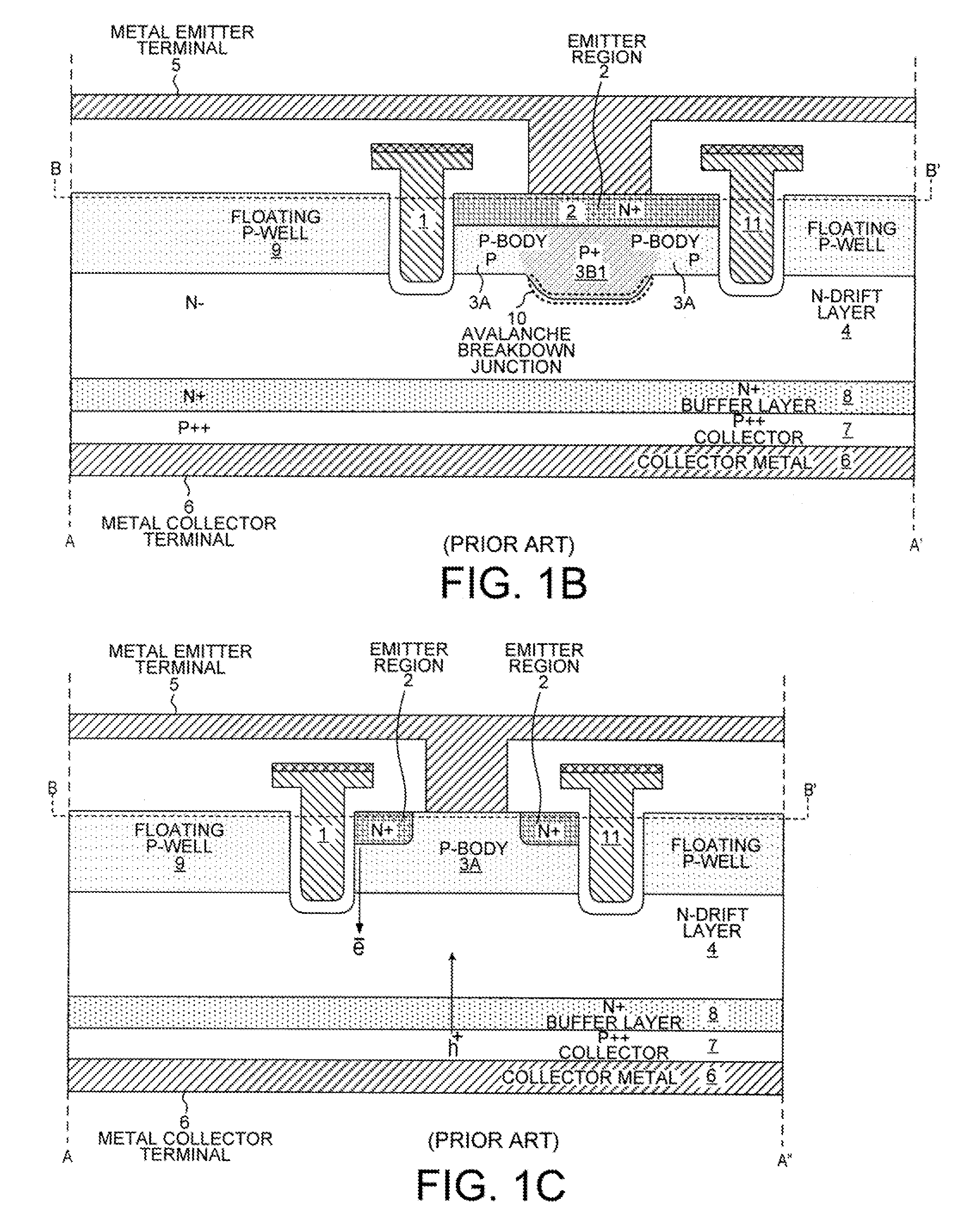

Trench IGBT with tub-shaped floating P-well and hole drains to P-body regions

A trench IGBT has a gate electrode disposed in a trench. A tub-shaped floating P-well is disposed on one side of the trench. The tub-shaped floating P-well has a central shallower portion and a peripheral deeper portion. An inner sidewall of the trench is semiconductor material of the peripheral deeper portion of the floating P-well. On the other side of the trench is a P type body region involving a plurality of deeper portions and a plurality of shallower portions. Each deeper portion extends to the trench such that some parts of the outer sidewall of the trench are semiconductor material of these deeper P-body portions. Other parts of the outer sidewall of the trench are semiconductor material of the shallower P-body portions. A shallow N+ emitter region is disposed at the top of the outer sidewall. The IGBT has fast turn off and enhanced on state conductivity modulation.

Owner:LITTELFUSE INC

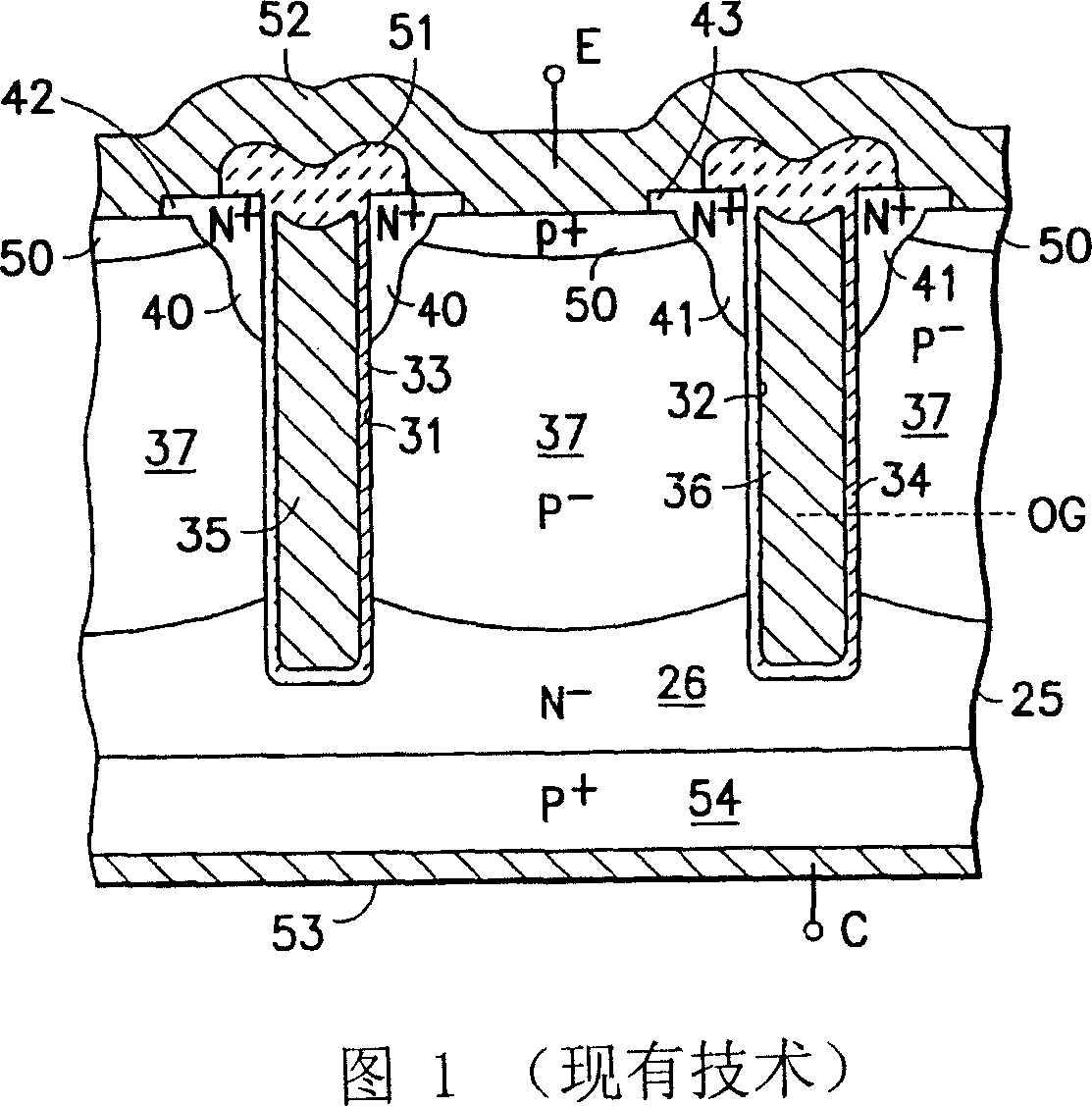

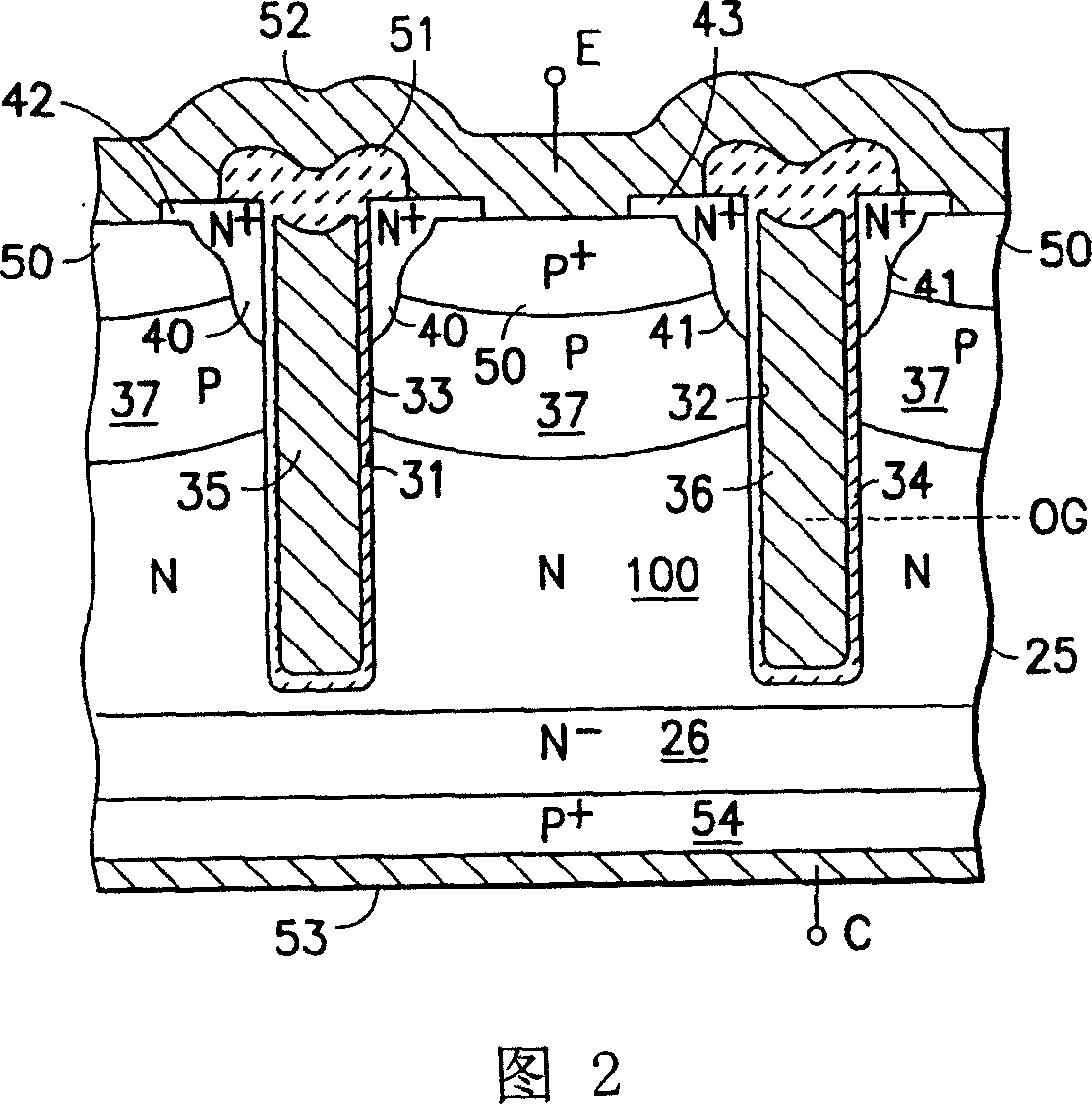

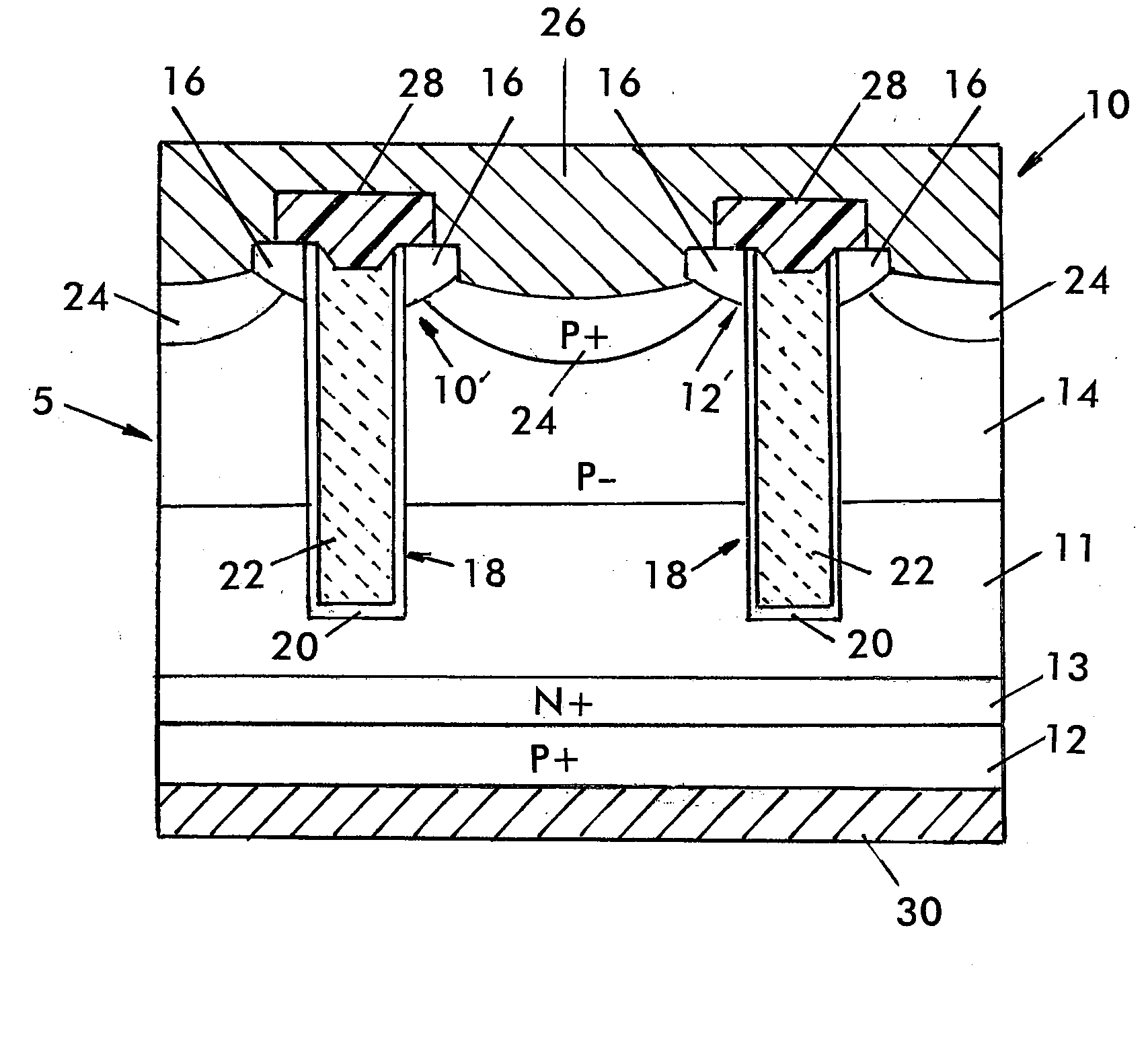

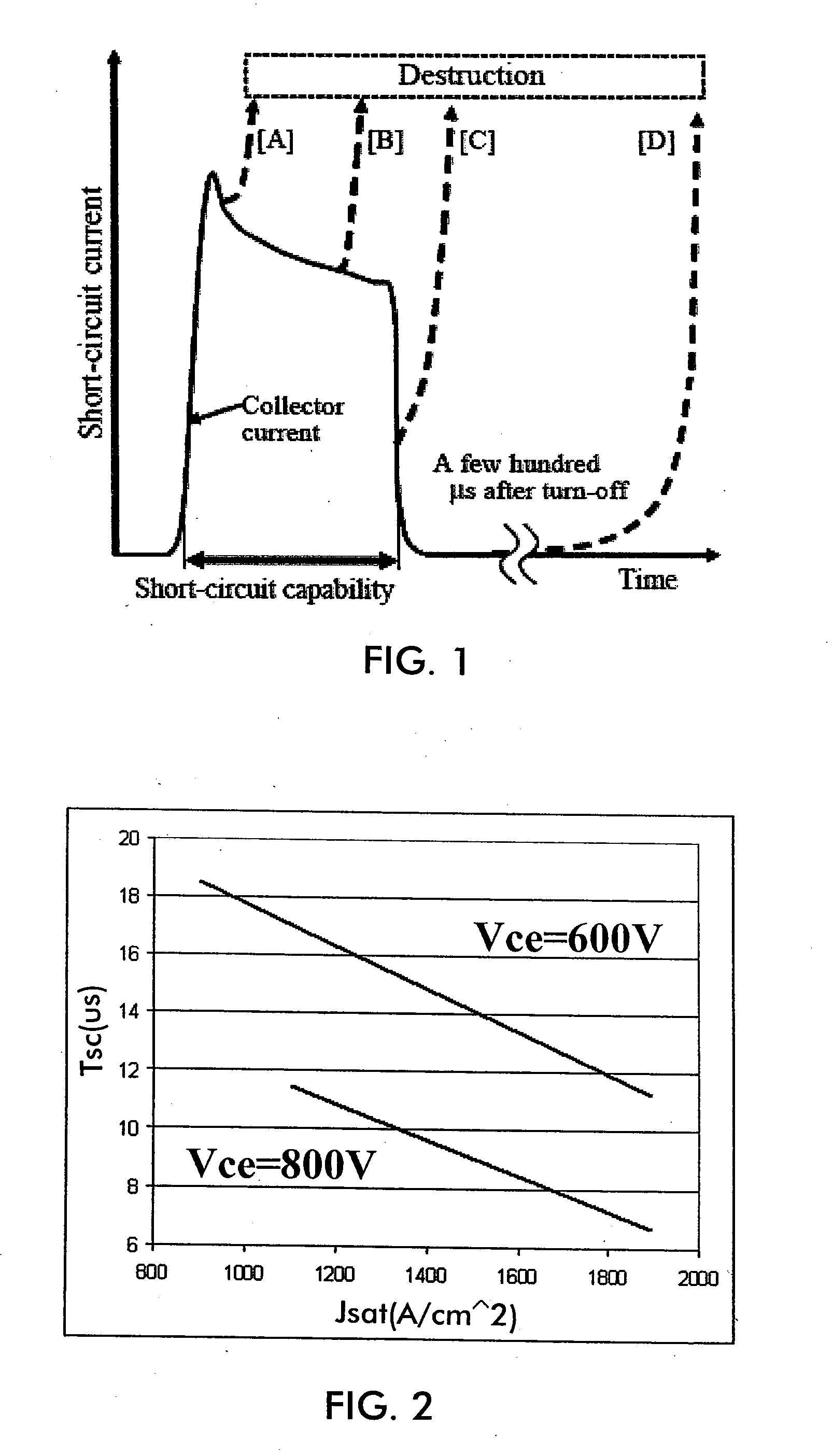

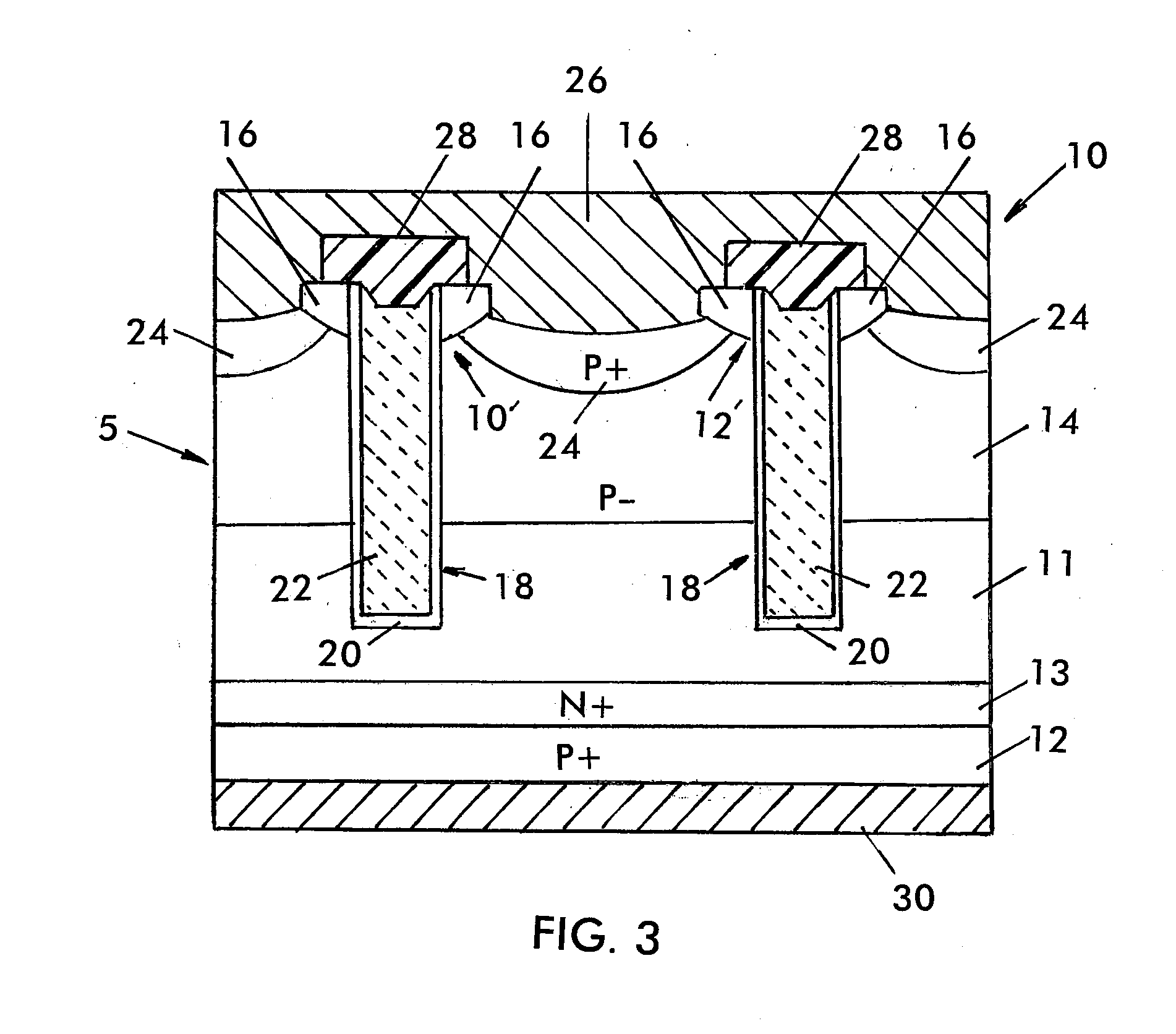

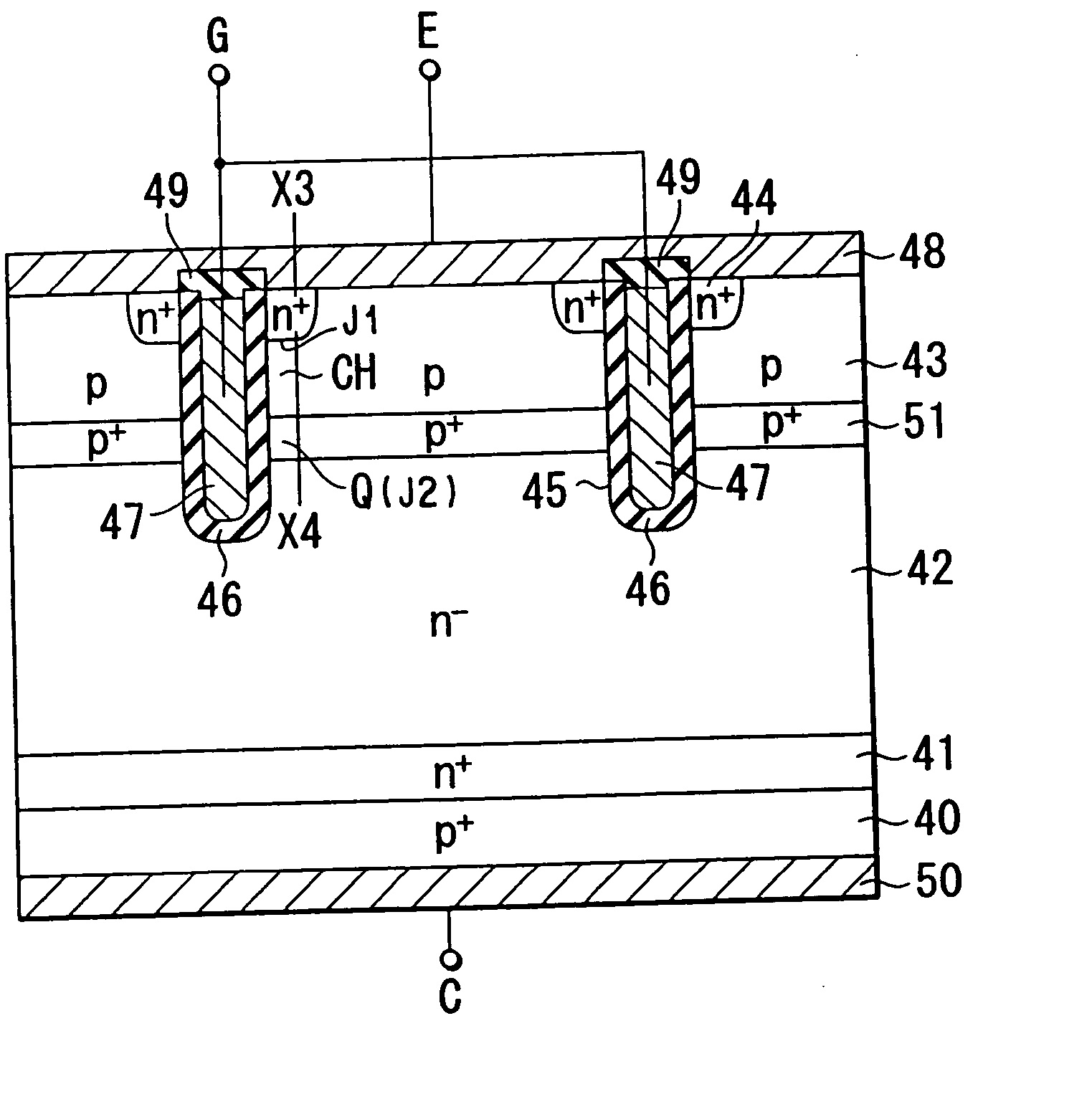

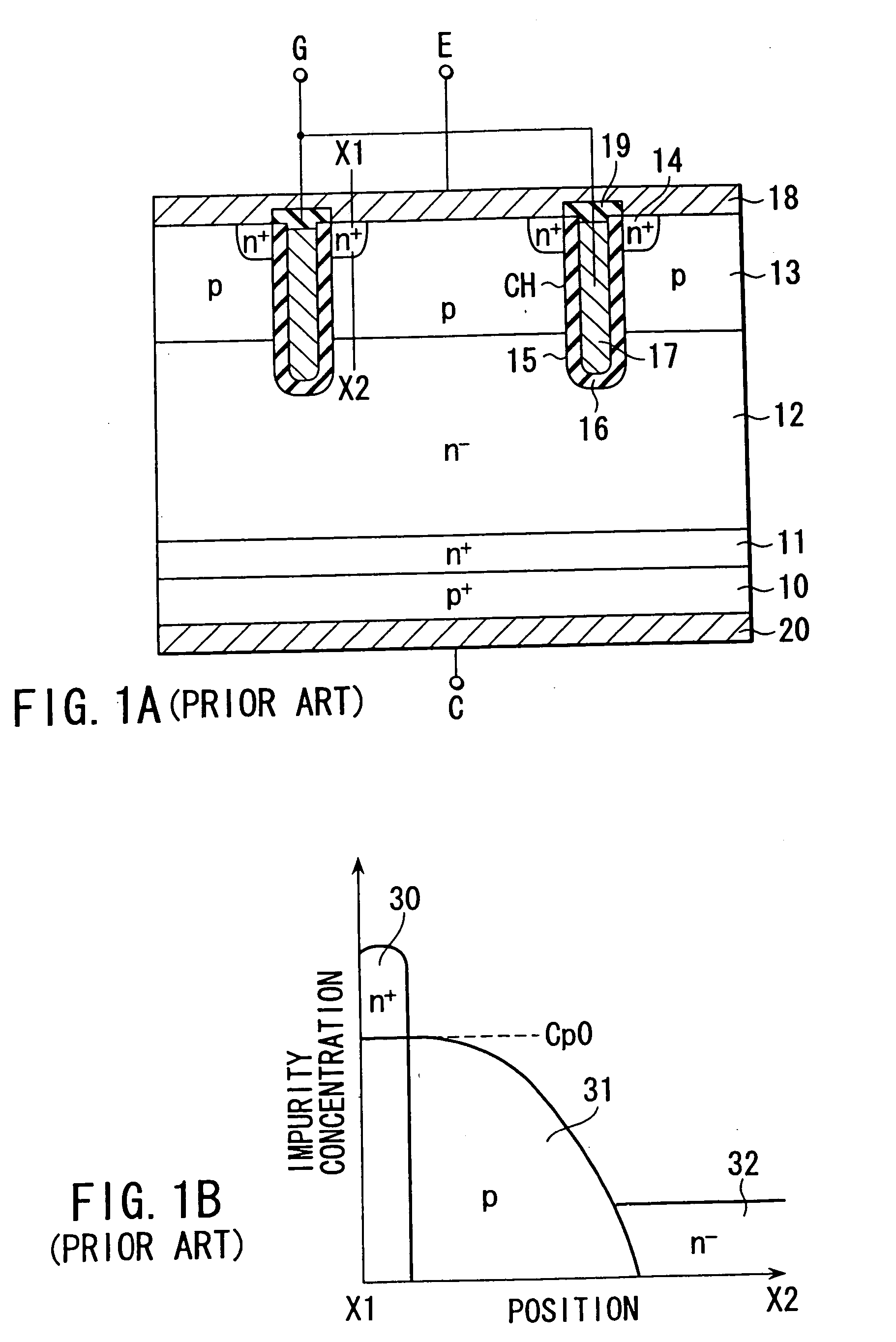

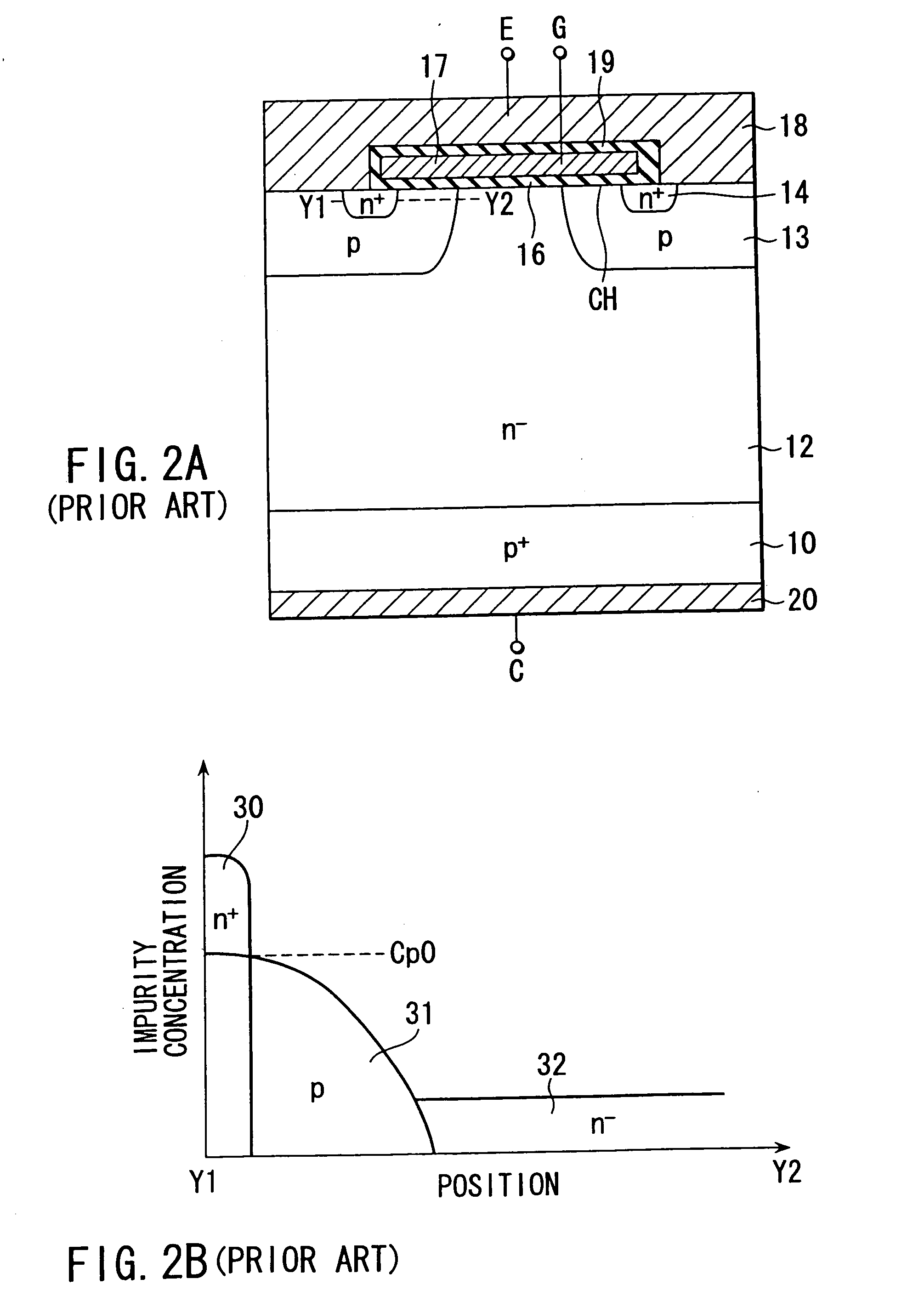

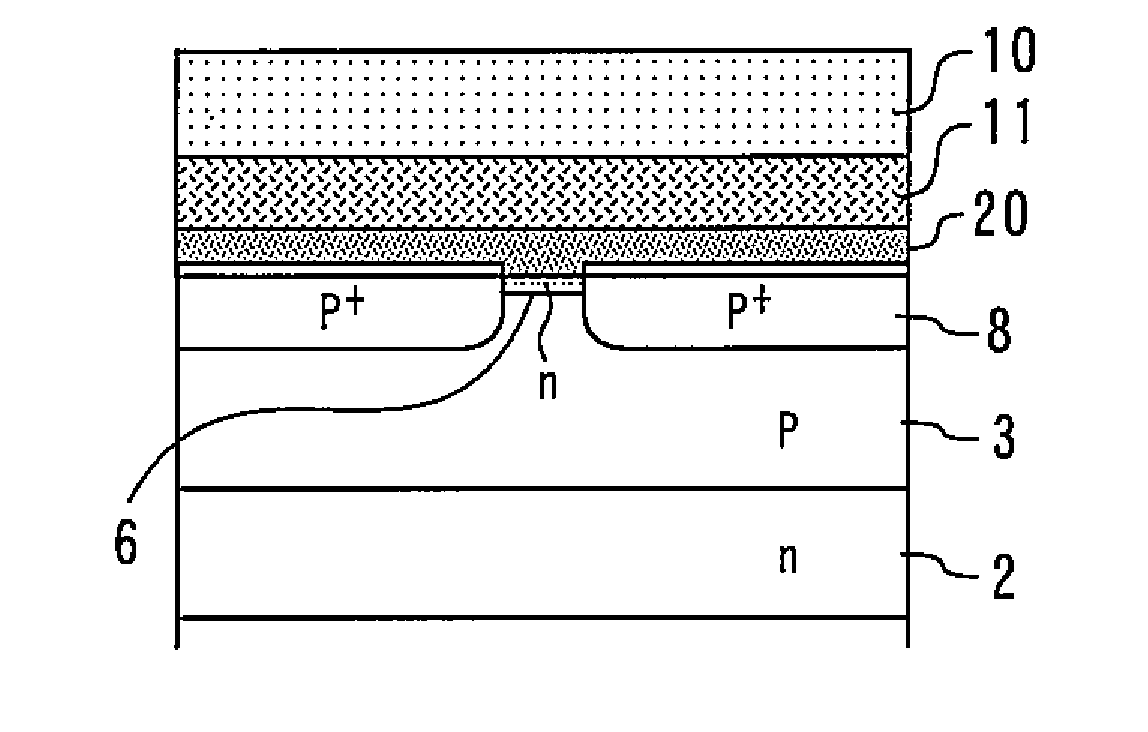

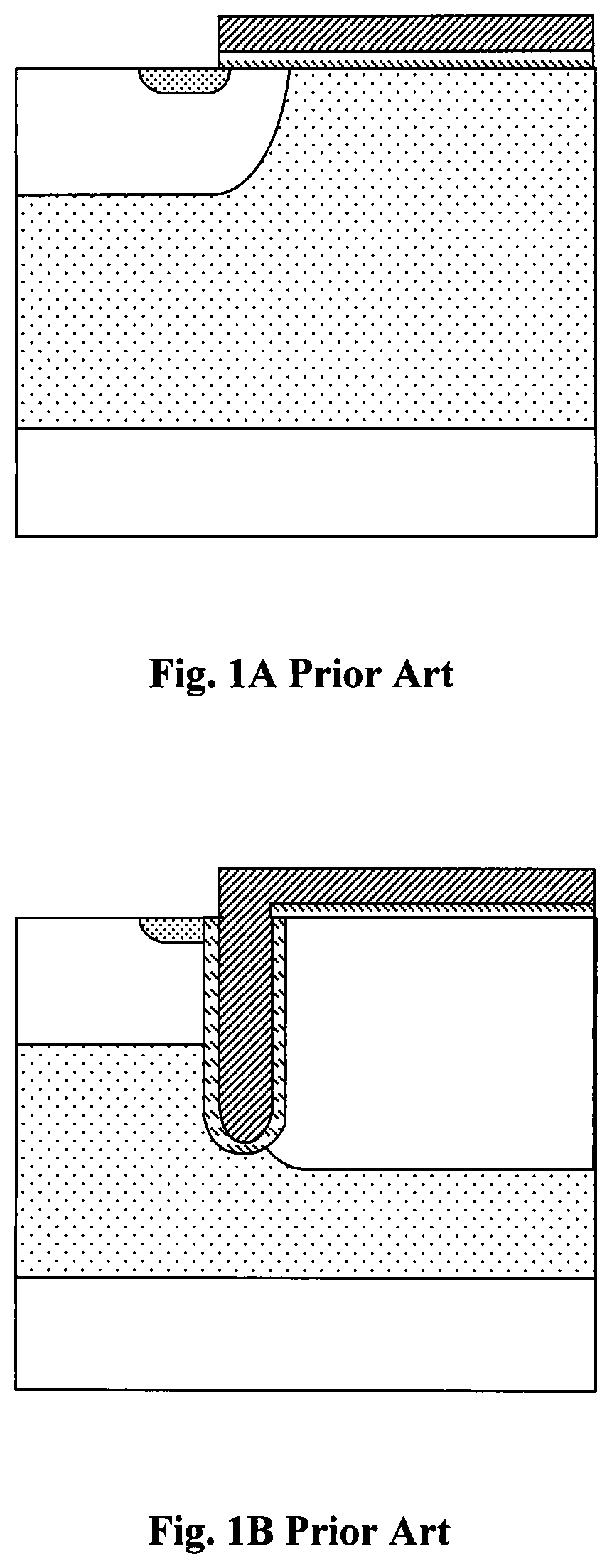

Power semiconductor element capable of improving short circuit withstand capability while maintaining low on-voltage and method of fabricating the same

InactiveUS20050062064A1Improve abilitiesLower turn-on voltageTransistorSolid-state devicesTrench igbtEngineering

In a p-type base layer of a trench IGBT comprising a p-type collector layer, an n-type base layer formed on the p-type collector layer, the p-type base layer formed on the n-type base layer, and an n-type emitter layer formed on the surface of the p-type base layer, the point of the highest impurity concentration is located closer to the n-type base layer than the junction with the emitter layer. In other words, the pinch-off of the channel is generated in the position closer to the n-type base layer than to the junction between the p-type base layer and the n-type emitter layer.

Owner:KK TOSHIBA

Manufacturing method for terminal structure of trench IGBT device

InactiveCN105679667AReduce performance instabilitySemiconductor/solid-state device manufacturingSemiconductor devicesTrench igbtPhysical chemistry

A manufacturing method for a terminal structure of a trench IGBT device is disclosed. The manufacturing method comprises the steps of growing an N type epitaxial part on an N type epitaxial silicon substrate or a regional fuse piece to form a charge storage region with certain doping concentration and thickness; continuing to grow a P type epitaxial part to form a channel region with an MOS-structured top layer; photoetching a terminal region trench pattern, dry etching the silicon substrate and growing a field oxide layer; photoetching an active region and etching the field oxide layer; photoetching a terminal region protection ring, and injecting P type impurities and enabling the impurities to be diffused to form an active protection ring; photoetching an active region gate trench, etching the trench and growing a gate oxide layer; depositing an in-situ-doped polysilicon material to fill the trench; then photoetching the gate pattern and a terminal protection field board, and etching the polysilicon; photoetching an N type source region and injecting N type impurities, then depositing the oxide layer or silicon nitride and other insulating materials, and performing annealing and compacting, photoetching contact holes, and etching the insulating layer to expose P well regions and N type source region silicon surfaces of all the pre-formed cells.

Owner:SHANGHAI DAOZHI TECH CO LTD

Dual-gate trench IGBT with buried floating P-type shield

A method of manufacturing an insulated gate bipolar transistor (IGBT) device comprising 1) preparing a semiconductor substrate with an epitaxial layer of a first conductivity type supported on the semiconductor substrate of a second conductivity type; 2) applying a gate trench mask to open a first trench and second trench followed by forming a gate insulation layer to pad the trench and filling the trench with a polysilicon layer to form the first trench gate and the second trench gate; 3) implanting dopants of the first conductivity type to form an upper heavily doped region in the epitaxial layer; and 4) forming a planar gate on top of the first trench gate and apply implanting masks to implant body dopants and source dopants to form a body region and a source region near a top surface of the semiconductor substrate.

Owner:ALPHA & OMEGA SEMICON INC

Semiconductor Device and Electric Power Conversion Device Using Same

InactiveUS20120273897A1High fracture toleranceLow voltage displacementTransistorSolid-state devicesTrench igbtElectrical conductor

The trench IGBT is provided with a plurality of trench gates disposed in a manner so as to form wide and narrow of gaps; has a MOS structure that has a channel of a first conductivity type and that is between the trench gate pair that is disposed with a narrow gap therebetween; and is provided with a floating semiconductor layer of the first conductivity type and that is separated from the trench gates by interposing a portion of a third semiconductor layer of a second conductivity type between the trench gate pair that is disposed with a wide gap therebetween. Also, this floating semiconductor layer is disposed parallel to and at a position corresponding to an emitter electrode and a first semiconductor layer having the same electric potential, with a insulating film therebetween.

Owner:HITACHI LTD

Vertical trench IGBT and method for manufacturing the same

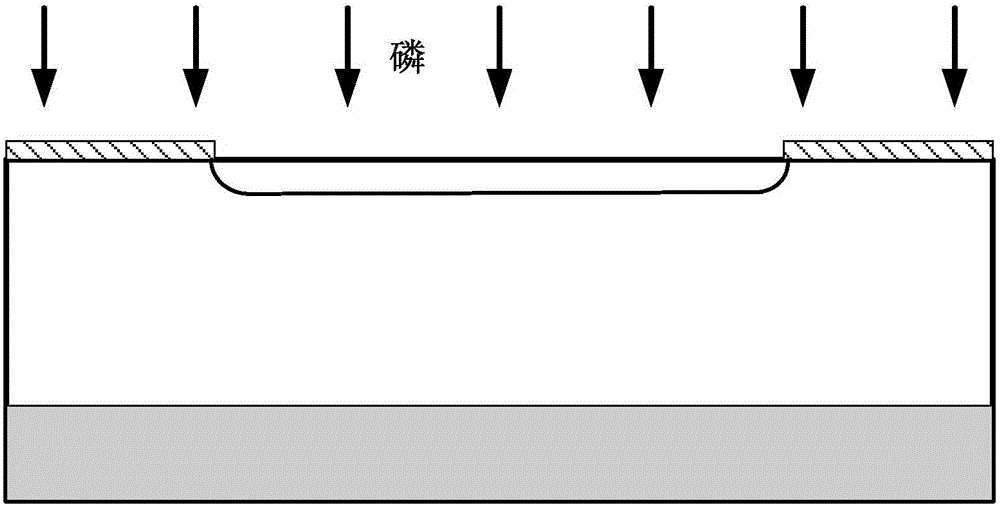

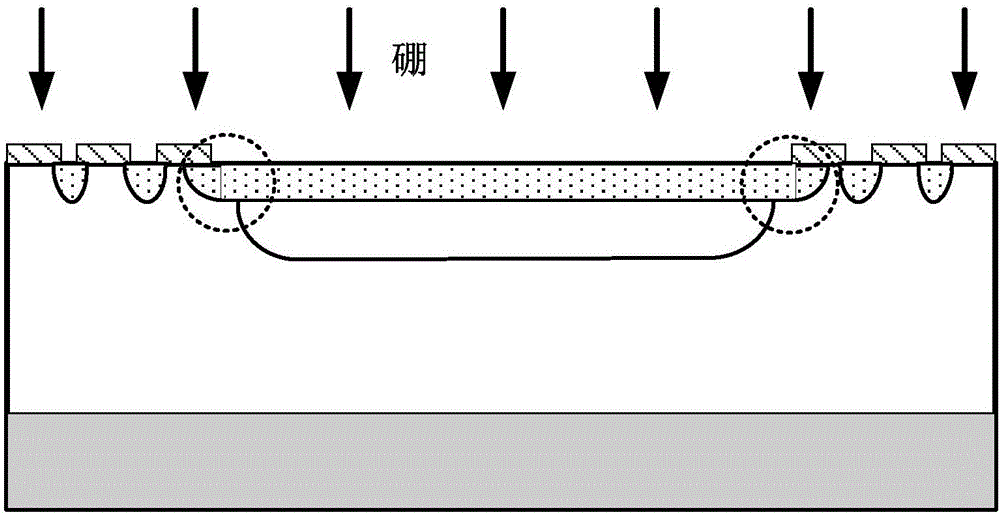

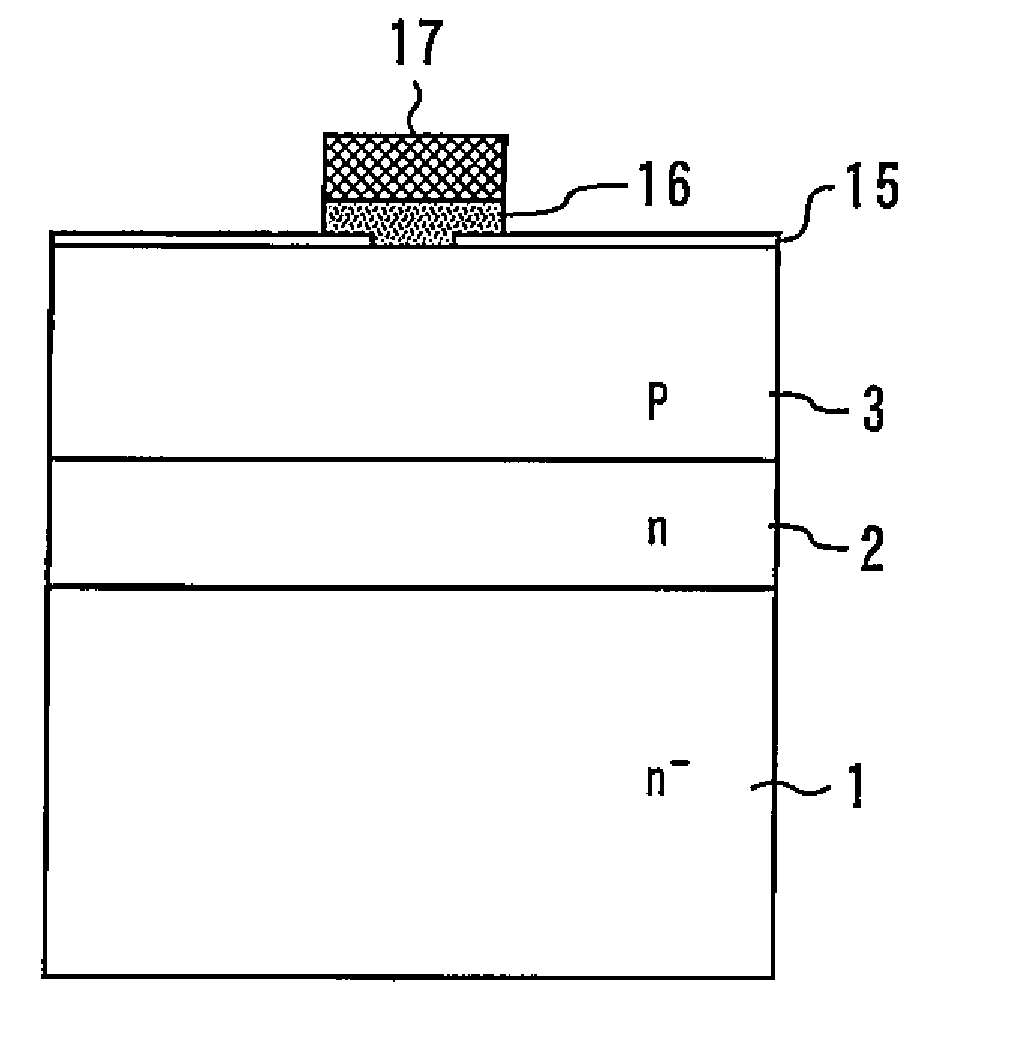

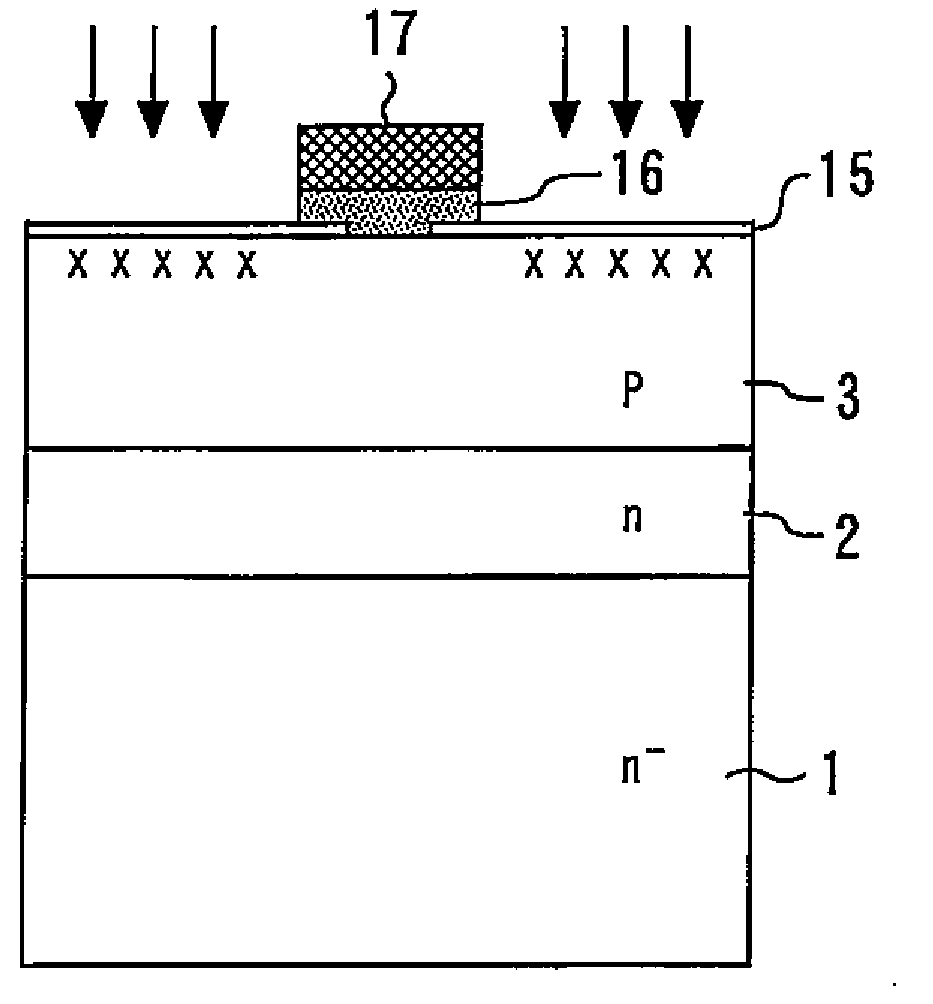

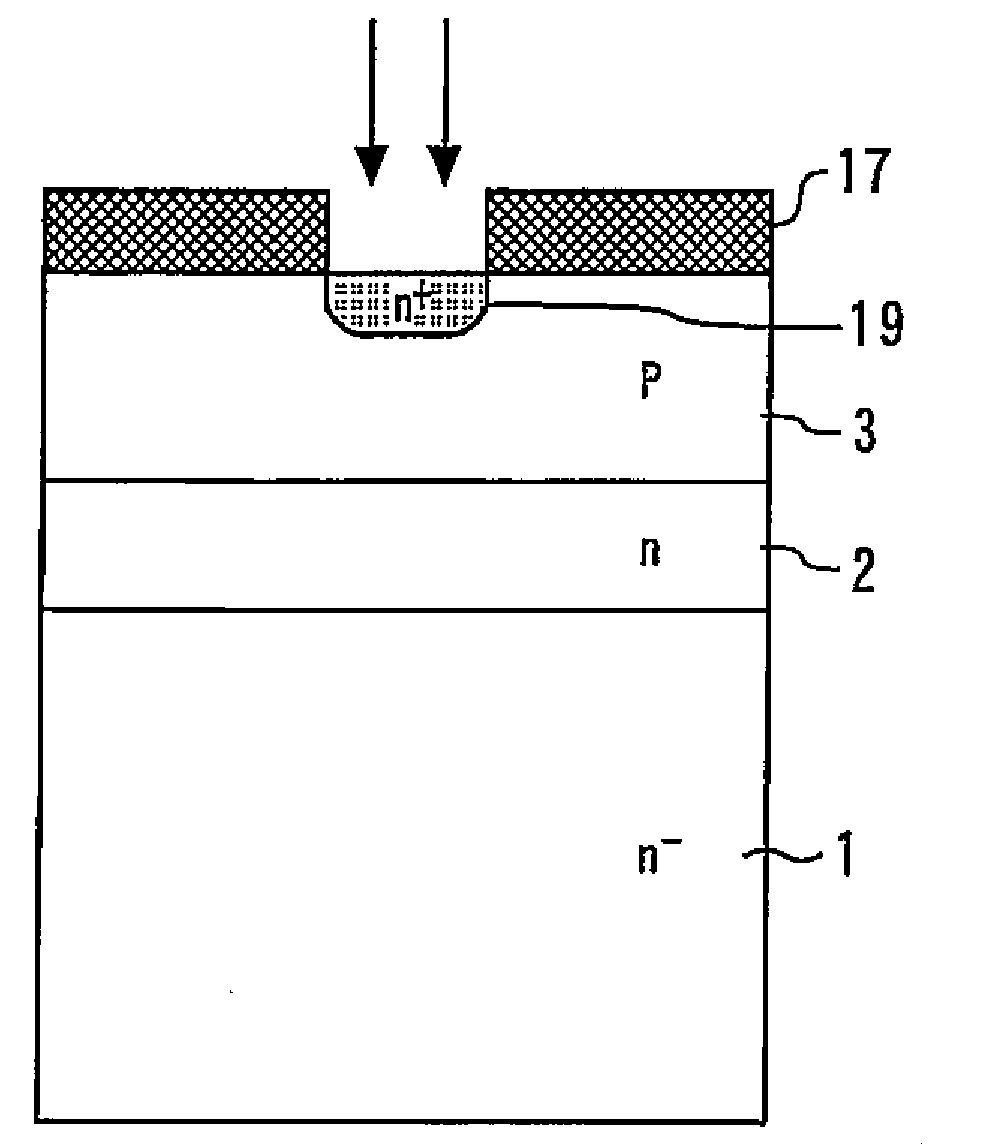

ActiveUS20130234200A1Improve RBSOA capacityIncrease capacitySemiconductor/solid-state device manufacturingSemiconductor devicesTrench igbtEngineering

A method for manufacturing a vertical trench IGBT includes: forming a body layer of a second conductivity type on a semiconductor substrate of a first conductivity type; forming a trench passing through the body layer; forming a trench gate in the trench via a gate insulating film; forming a polysilicon film containing an impurity of a first conductivity type on the body layer; diffusing the impurity from the polysilicon film into the body layer to form an emitter layer of a first conductivity type on the body layer; and forming a collector layer of a second conductivity type on a lower surface of the semiconductor substrate.

Owner:MITSUBISHI ELECTRIC CORP

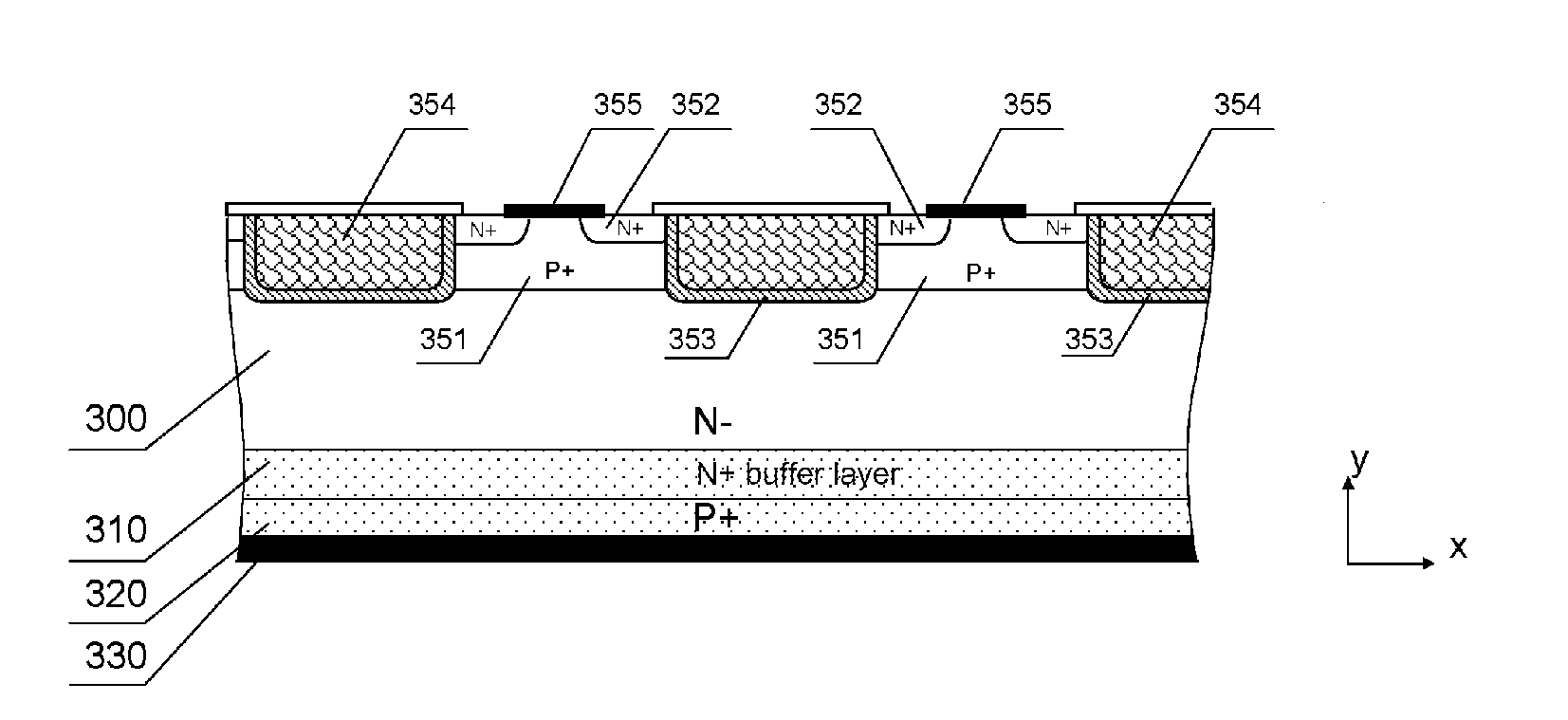

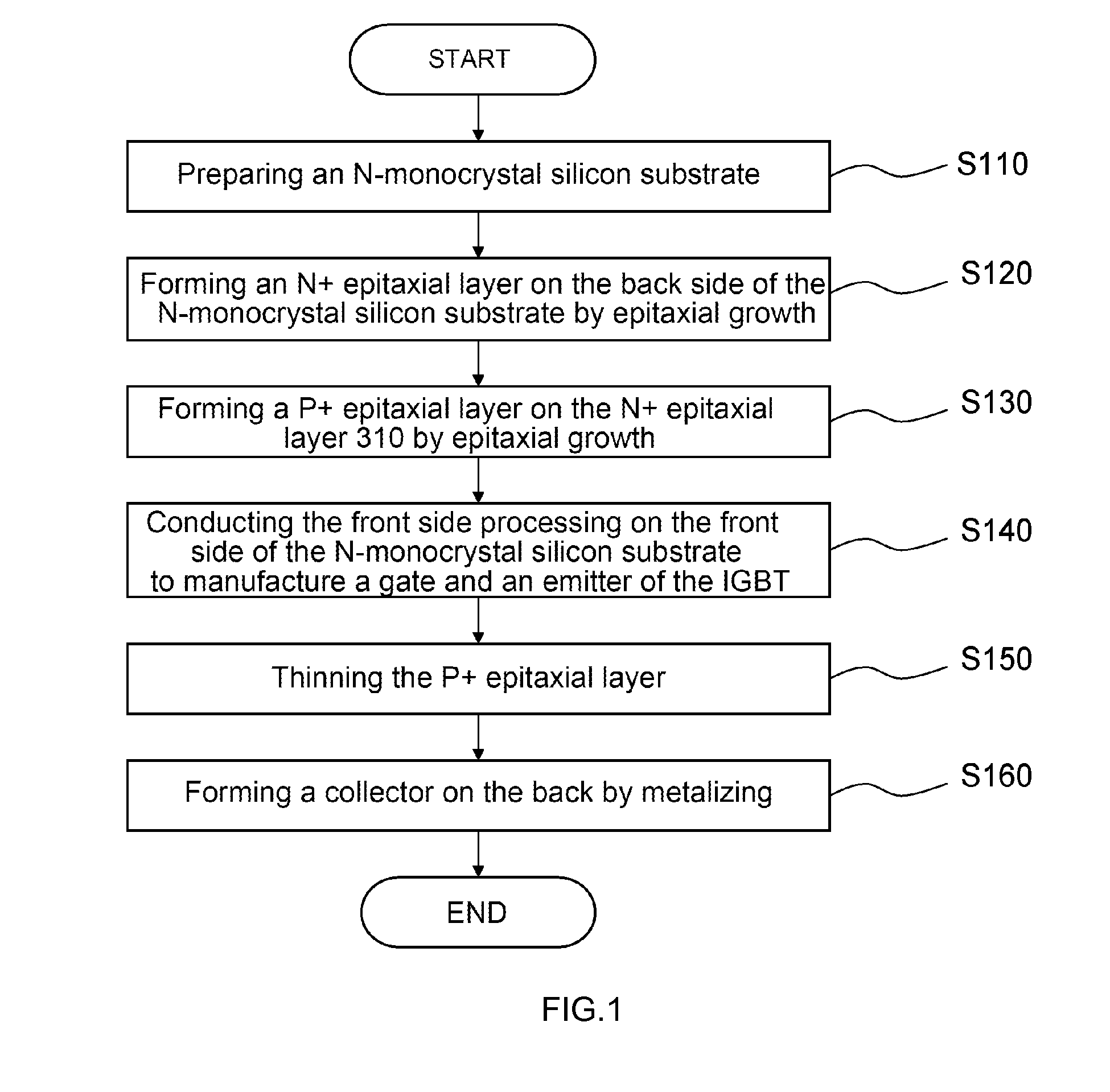

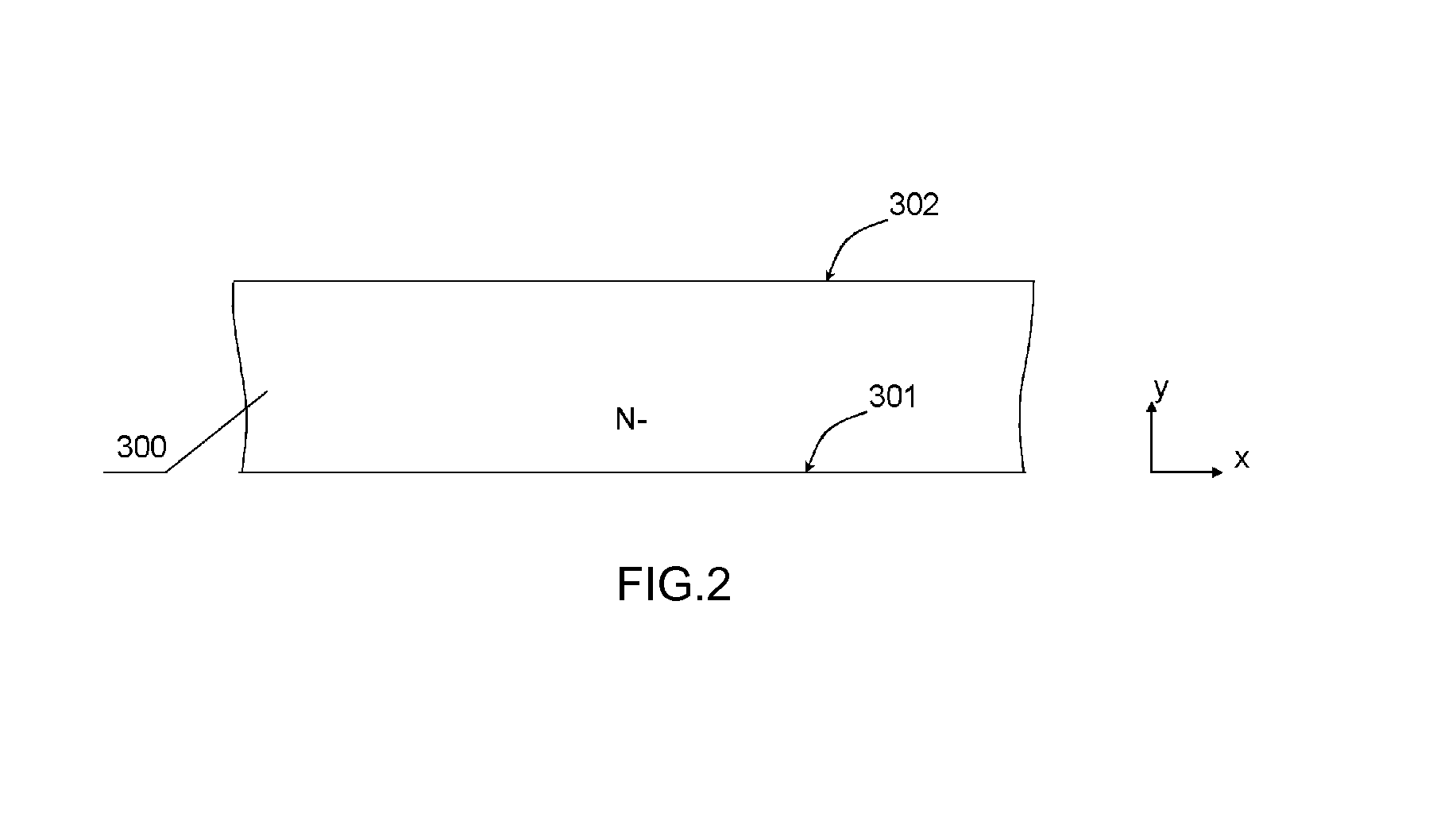

Trench insulated-gate bipolar transistor and manufacture method thereof

ActiveUS20140346562A1Low costQuality improvementTransistorSemiconductor/solid-state device manufacturingTrench igbtParasitic bipolar transistor

A Trench Insulated Gate Bipolar Transistor (IGBT) and a manufacture method thereof are provided by the present invention, which belongs to the field of IGBT technical field. The manufacture method includes following steps: (1) preparing a semiconductor substrate; (2) forming an epitaxial layer grow on a first side of the semiconductor substrate by epitaxial growth; (3) preparing and forming a gate and an emitter of the Trench Insulated Gate Bipolar Transistor on a second side of the semiconductor substrate; (4) thinning the epitaxial layer to form a collector region; (5) metalizing the collector region to form a collector. The cost of the manufacture method is low and the performance of the Trench IGBT formed by the manufacture method is good.

Owner:WUXI CHINA RESOURCES HUAJING MICROELECTRONICS

Silicon carbide trench IGBT structure and manufacturing method thereof

ActiveCN111146274AImprove extraction speedShorten off timeEfficient power electronics conversionSemiconductor/solid-state device manufacturingTrench igbtEngineering

The invention discloses a silicon carbide trench IGBT structure, and the structure comprises an N-drift region, an N-type buffer layer, a P-type well region, a P+ ohmic contact region, an N+ emitter region, a P+ trench collector region, a trench collector, a P+ collector region, an N+ substrate layer, a trench gate and a gate oxide dielectric layer. Compared with a traditional structure, the structure is additionally provided with the trench collector on the collector, and is also additionally provided with the P+ trench collector above the trench collector; due to a fact that no N+ buffer layer is arranged above the P+ trench collector region of the new device, the hole injection efficiency during forward conduction is enhanced, and the turn-on voltage of the new device is reduced; when the new device is turned off, the trench collector provides a low-resistance channel, so the extraction of electrons is accelerated, and the turn-off loss is further reduced.

Owner:厦门吉顺芯微电子有限公司

Insulated gate semiconductor device

ActiveUS7151297B2Reduce capacitanceIncreasing the voltage drop speed and the current increase speedSemiconductor devicesTrench igbtSemiconductor

Owner:FUJI ELECTRIC CO LTD

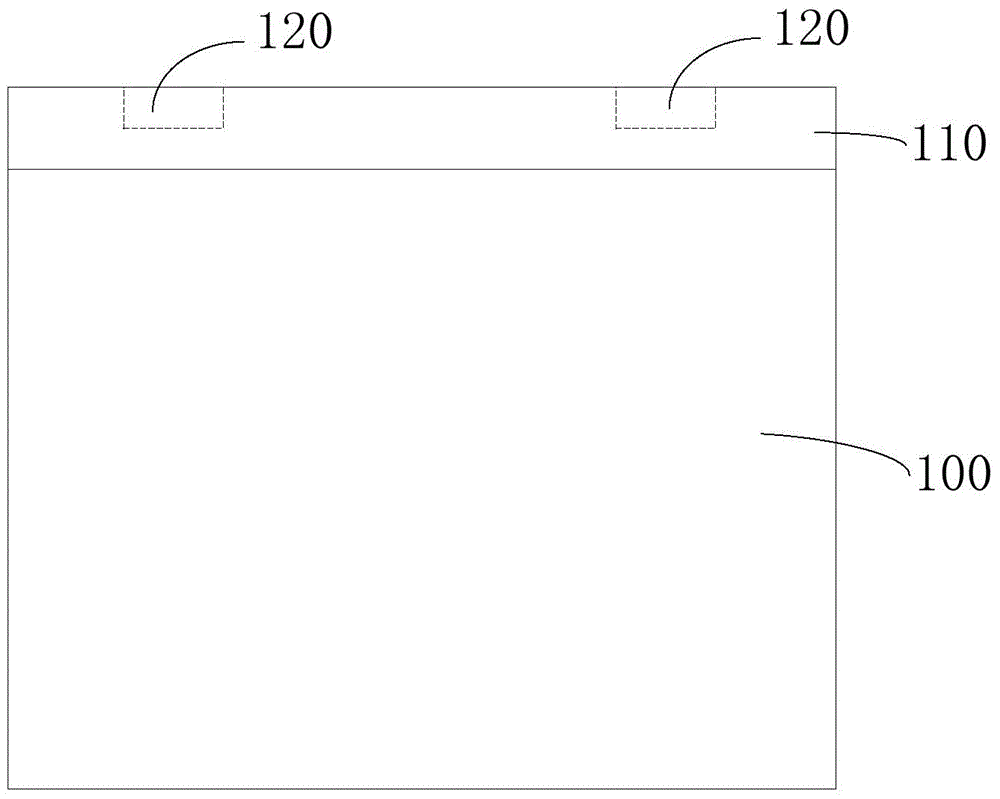

Preparation method of Trench IGBT with reverse conducting structure

ActiveCN104576533ALow costSimple processSemiconductor/solid-state device manufacturingSemiconductor devicesTrench igbtEngineering

The invention discloses a preparation method of a Trench IGBT with a reverse conducting structure. The preparation method comprises the following steps: providing a first wafer, and forming an N buffer area and a highly doped N+ area in sequence on the first surface of the first wafer; providing a second wafer, and bonding the first wafer and the second wafer, wherein the first surface of the first wafer is in direct contact with the second wafer; carrying out thinning polishing on the second surface of the first wafer to required thickness; completing a Trench IGBT front-side structure on the second surface of the first wafer; separating the first wafer and the second wafer, which are bonded together, and forming a P+ layer and a back metal layer in sequence on the first surface of the first wafer. According to the preparation method of the Trench IGBT with the reverse conducting structure, through the bonding of the first wafer and the second wafer, firstly thinning is carried out, and then the Trench IGBT front-side structure is completed, so that photoetching or developing equipment for an ultrathin piece is not needed, and the process is simple.

Owner:CSMC TECH FAB2 CO LTD

Semiconductor device and electric power conversion device using same

InactiveCN102714217AImprove resistance to damagePrevent overcurrentTransistorSolid-state devicesLow noiseTrench igbt

The invention provides a semiconductor device and an electric power conversion device using same. Specifically, disclosed is an IGBT that suppresses overcurrent flowing during a short-circuit, while being low-loss and low-noise (low electric potential displacement, low current oscillation), and wherein an element has high fracture tolerance. The IGBT is a trench IGBT; is provided with a plurality of trench gates disposed in a manner so as to form two types (wide and narrow) of gaps; has a MOS structure that has a channel of a first conductivity type and that is between the aforementioned trench gate pair that is disposed with a narrow gap therebetween; and is provided with a floating semiconductor layer of the first conductivity type and that is separated from the aforementioned trench gates by interposing a portion of a third semiconductor layer of a second conductivity type between the aforementioned trench gate pair that is disposed with a wide gap therebetween. Also, this floating semiconductor layer is disposed parallel to and at a position corresponding to an emitter electrode and a first semiconductor layer having the same electric potential, with a insulating film therebetween. By means of the above structure, the electric field concentration in the corner sections of the aforementioned trench gates is eased, voltage resistance is increased, and low noise and low loss are achieved.

Owner:HITACHI LTD

Vertical trench IGBT and method for manufacturing the same

ActiveCN103311121AImprove toleranceSemiconductor/solid-state device manufacturingSemiconductor devicesTrench igbtEngineering

A method for manufacturing a vertical trench IGBT includes: forming a body layer of a second conductivity type on a semiconductor substrate of a first conductivity type; forming a trench passing through the body layer; forming a trench gate in the trench via a gate insulating film; forming a polysilicon film containing an impurity of a first conductivity type on the body layer; diffusing the impurity from the polysilicon film into the body layer to form an emitter layer of a first conductivity type on the body layer; and forming a collector layer of a second conductivity type on a lower surface of the semiconductor substrate.

Owner:MITSUBISHI ELECTRIC CORP

New dual-gate trench IGBT with buried floating p-type shield

ActiveUS20210020567A1Increased durabilityEasy injectionSemiconductor/solid-state device detailsSolid-state devicesTrench igbtDopant

A method of manufacturing an insulated gate bipolar transistor (IGBT) device comprising 1) preparing a semiconductor substrate with an epitaxial layer of a first conductivity type supported on the semiconductor substrate of a second conductivity type; 2) applying a gate trench mask to open a first trench and second trench followed by forming a gate insulation layer to pad the trench and filling the trench with a polysilicon layer to form the first trench gate and the second trench gate; 3) implanting dopants of the first conductivity type to form an upper heavily doped region in the epitaxial layer; and 4) forming a planar gate on top of the first trench gate and apply implanting masks to implant body dopants and source dopants to form a body region and a source region near a top surface of the semiconductor substrate.

Owner:ALPHA & OMEGA SEMICON INC