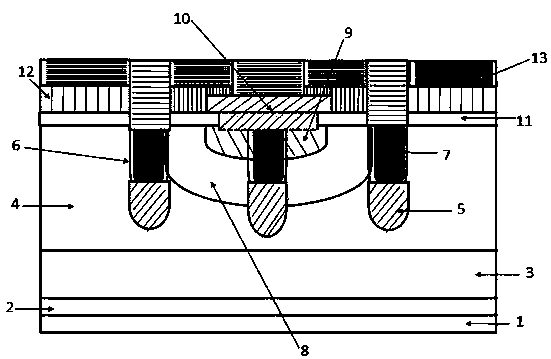

Electrostatic shielding effect transistor and design method thereof

A technology of electrostatic shielding and design method, applied in the direction of electric solid devices, circuits, electrical components, etc., can solve the impact resistance and high frequency radiation resistance to be improved, the secondary breakdown voltage resistance is poor, and the thermal stability is not good. and other problems, to achieve the effect of large power capacity and safe working area, high secondary breakdown voltage and good thermal stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

[0033] In the description of the present invention, it should be understood that the orientation or positional relationship indicated by the terms "upper", "lower", "front", "rear", "inner", "outer" etc. Orientation or positional relationship is only for the convenience of describing the present invention and simplifying the description, and does not indicate or imply that the referred device or element must have a specific orientation, be constructed and operated in a specific orientation, and thus should not be construed as a limitation of the present invention.

[0034] In the description of the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More