Patents

Literature

46results about How to "Reduce dynamic loss" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

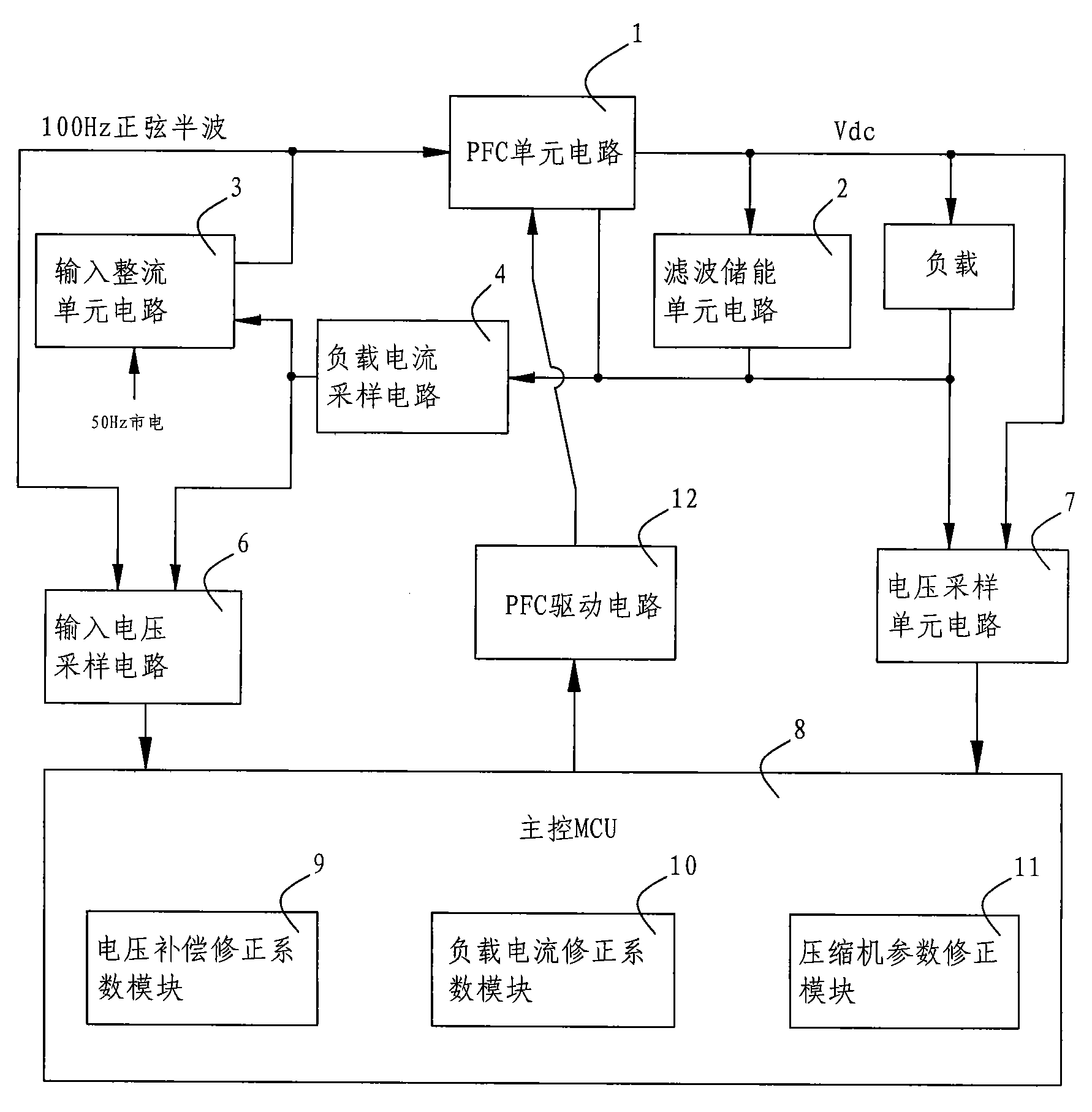

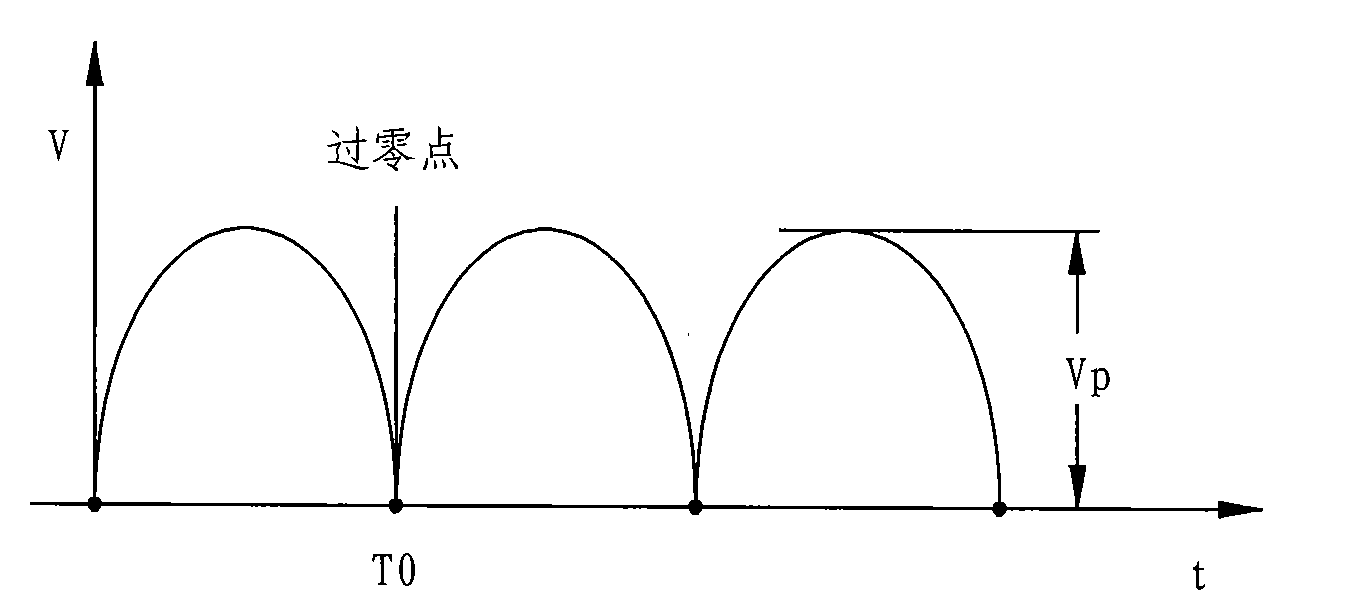

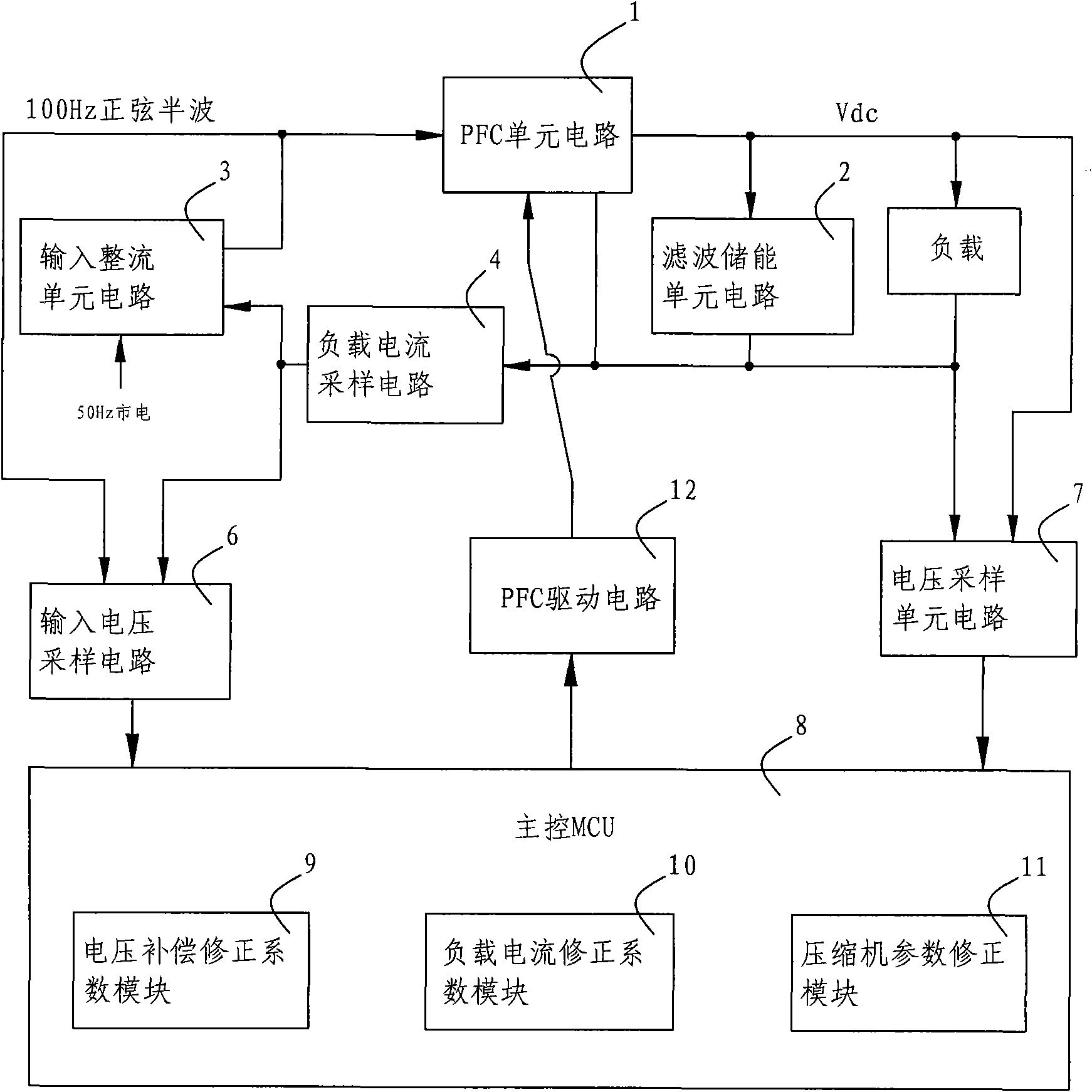

Control device with compensatory active PFC (power factor correction) and control method thereof

InactiveCN101777828AGuaranteed power factorReduce dynamic lossEfficient power electronics conversionPower conversion systemsSampling circuitsEngineering

The invention relates to a control device with a compensatory active PFC (power factor correction) and a control method thereof. The control device with the compensatory active PFC comprises an input rectifying unit circuit, a PFC unit circuit and a filtering energy storage unit circuit which are sequentially connected, wherein an input voltage sampling circuit is connected with the output of the input rectifying unit circuit in parallel; a load current sampling circuit is connected between the PFC unit circuit and the input rectifying unit circuit in series; a voltage sampling unit circuit of PFC output voltage is connected with the filtering energy storage unit circuit in parallel; a PFC driving circuit is connected with the PFC unit circuit; a main control unit (MCU) is respectively connected with the input voltage sampling circuit, the PFC driving circuit and the voltage sampling unit circuit; and the MCU comprises any one or a combination of more than two of a voltage compensation correction factor module, a load current correction factor module and a compressor parameter correction module. The invention has the characteristics of flexible operation and reduction of interference, loss and cost.

Owner:MIDEA GRP CO LTD

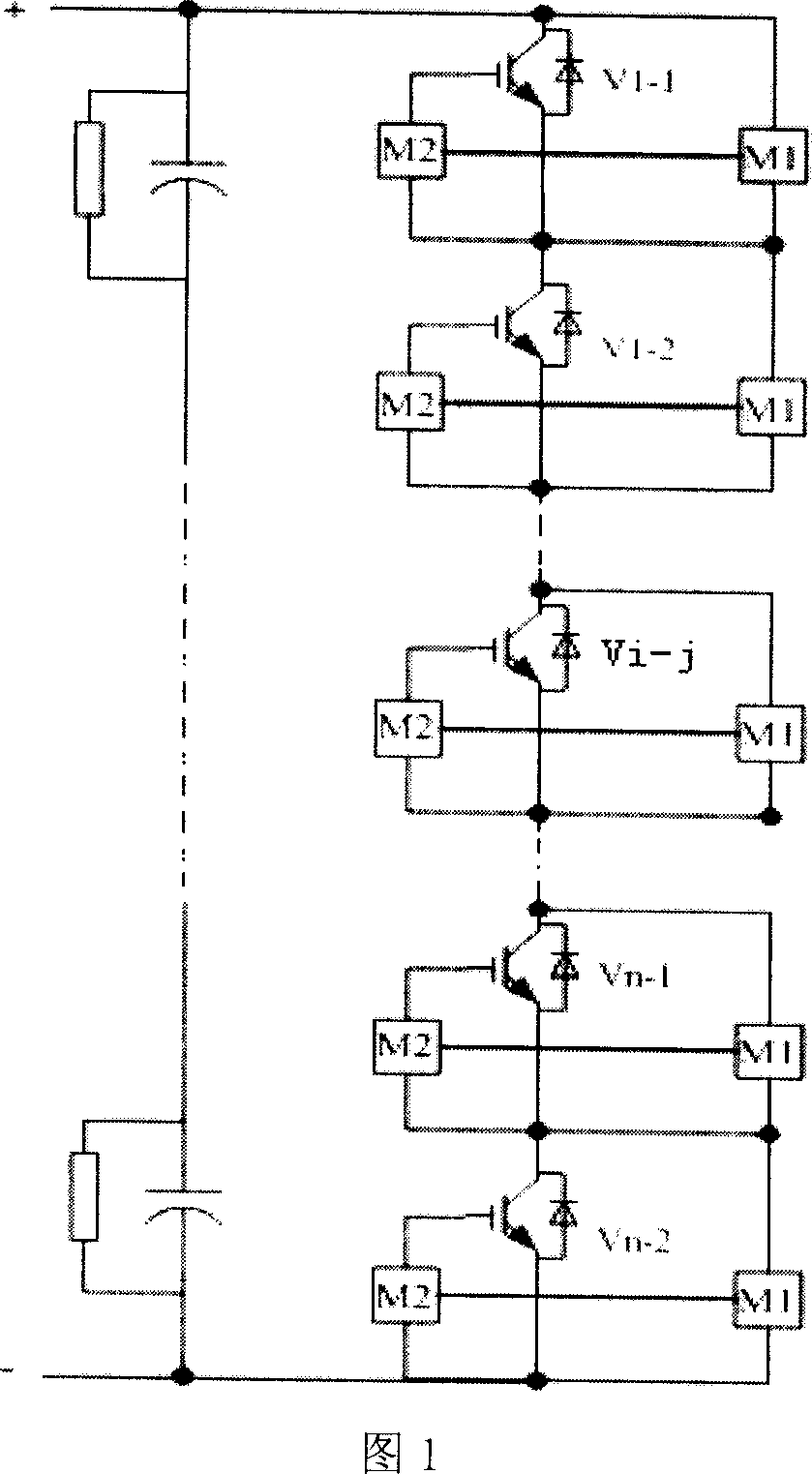

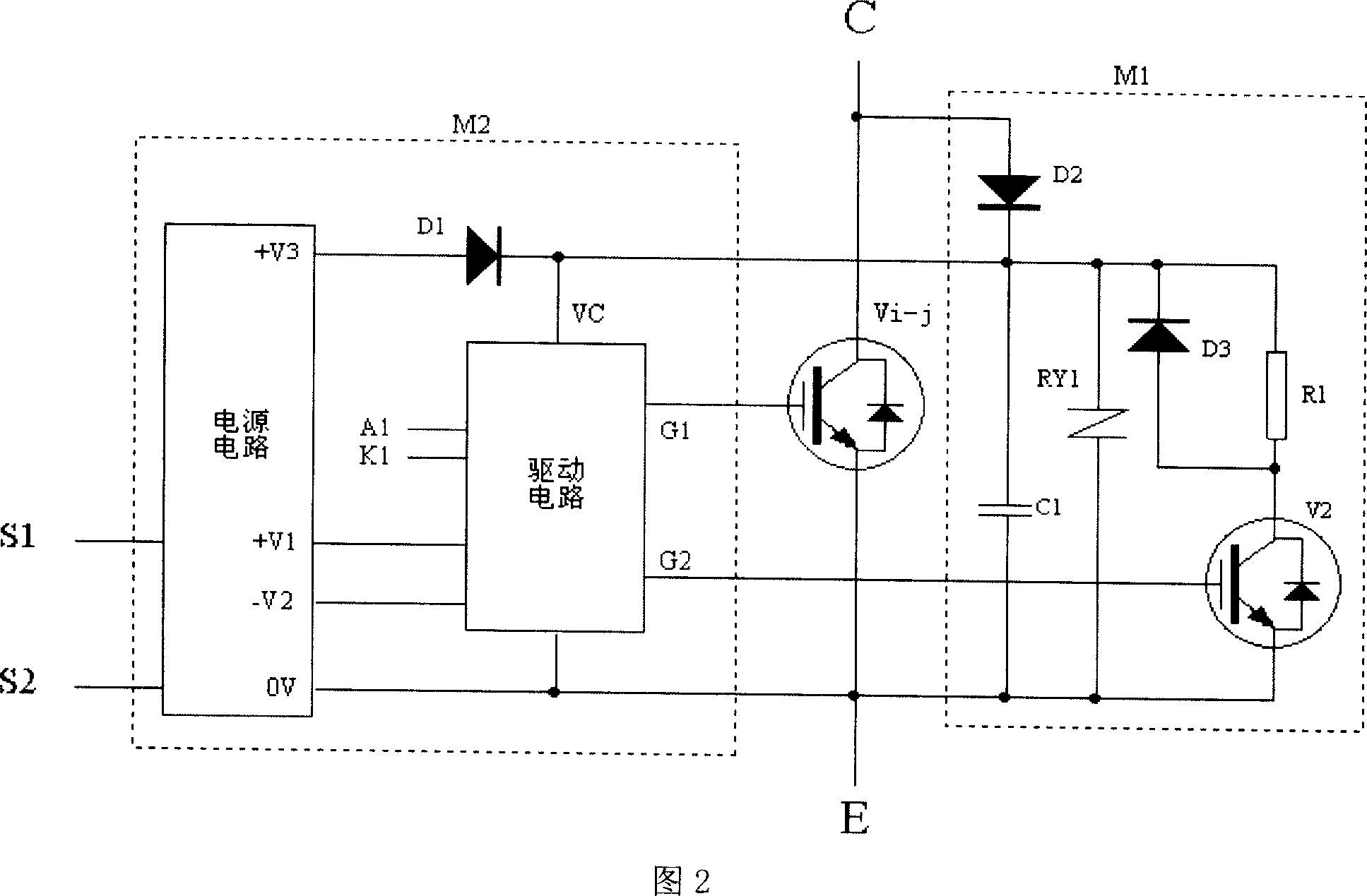

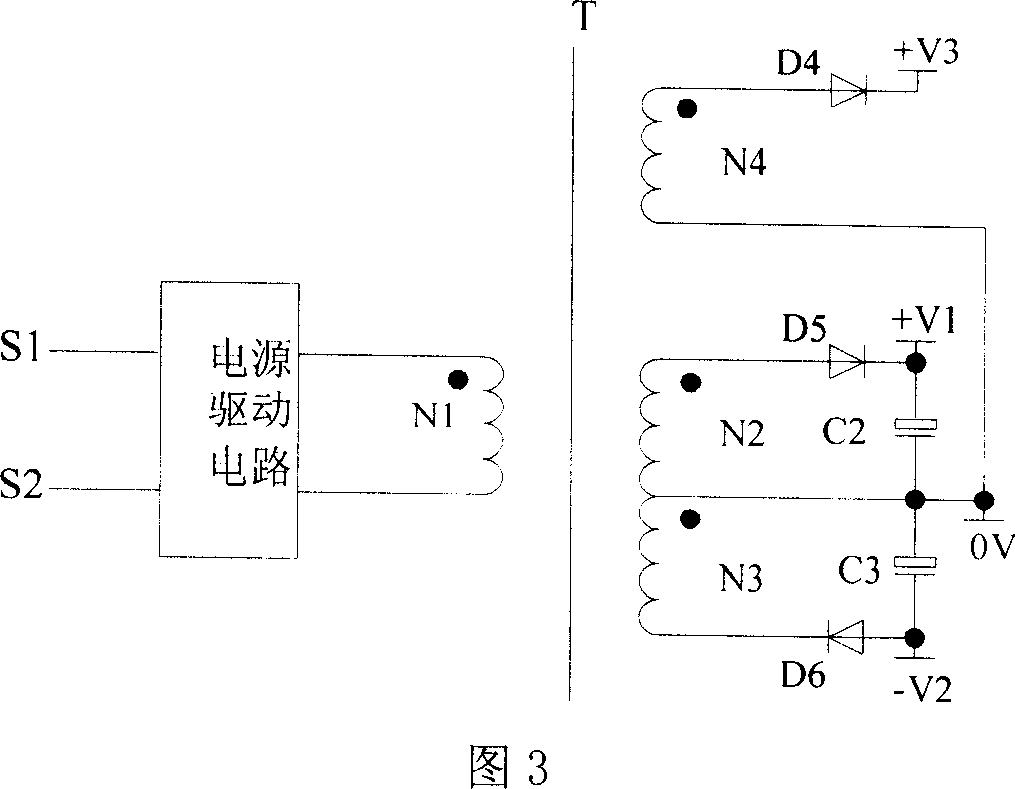

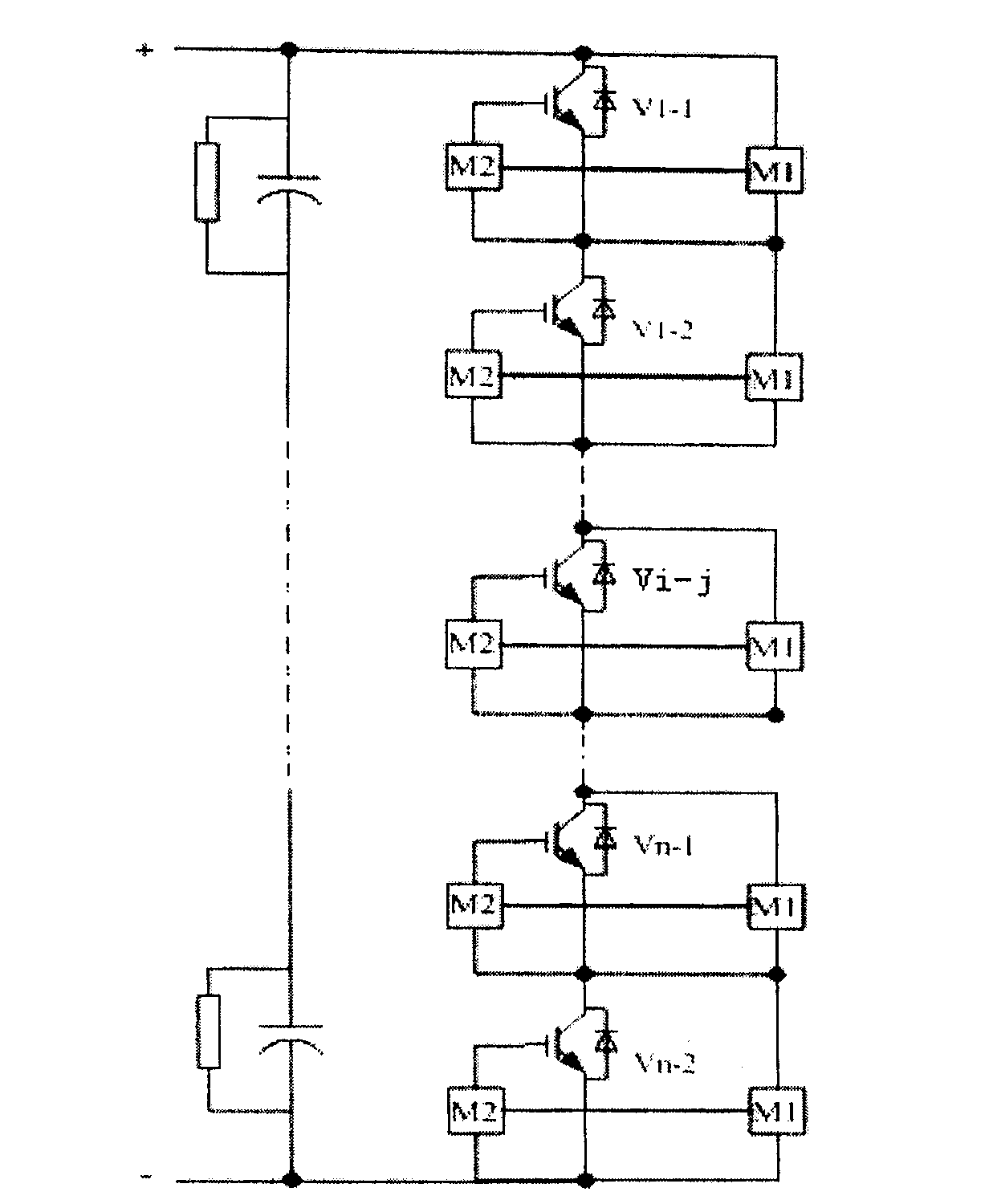

Cascade active voltage-stabilizing controller of power switch

InactiveCN101030701AWide range of choicesStrong pressure equalization control abilityEmergency protective circuit arrangementsControl signalControl theory

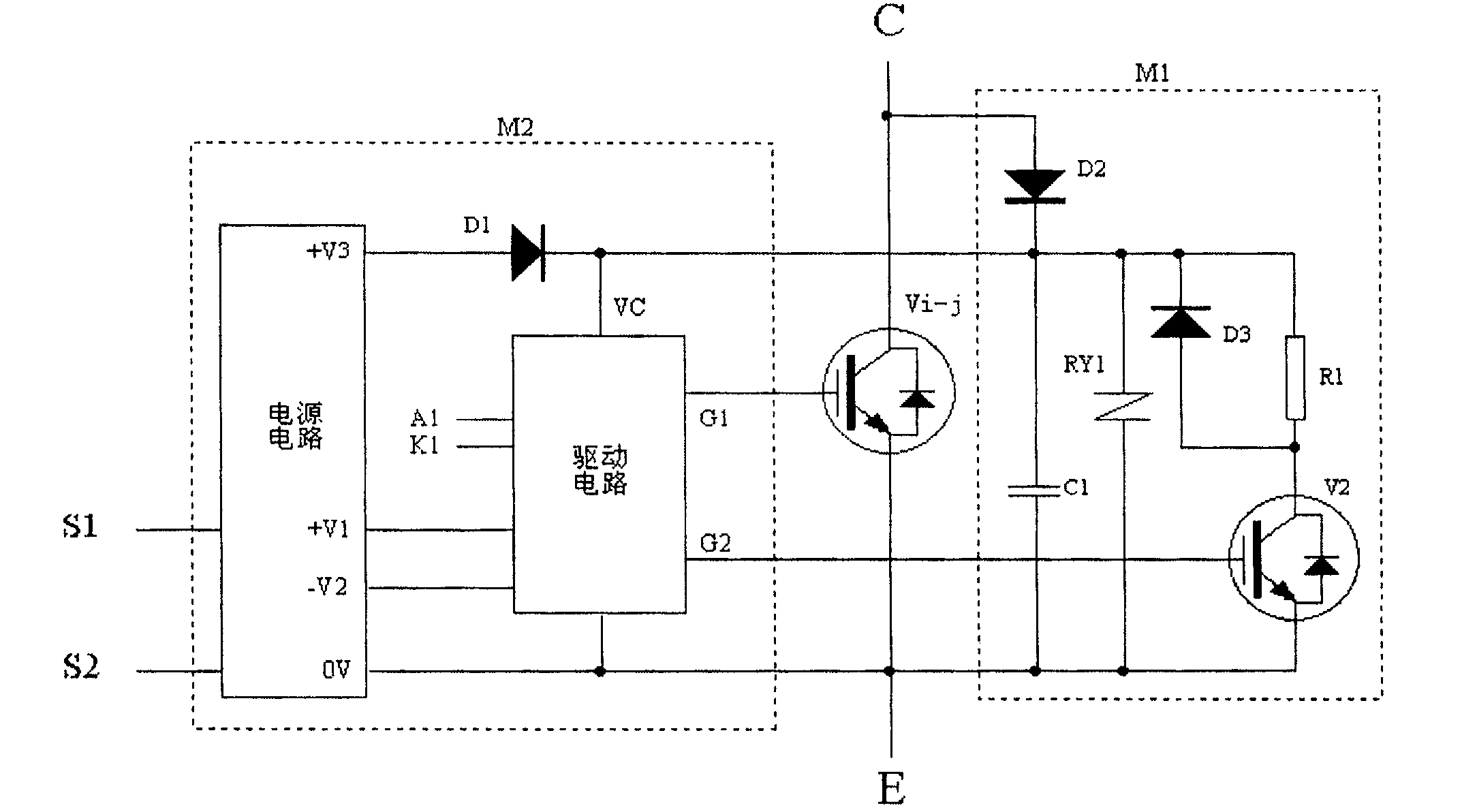

The invention is concerned with the active series connection equal-press controlling equipment for the power switch, the characteristic is: sets the active equal-press absorb module for the series power module, the active equal-press absorb module crosses and parallel connects with the C and E end of each main power tube Vi-j; sets the driving controlling module, the outputting controlling signal of the driving controlling module accesses each power module and the active equal-press absorb module. The invention is lower power consumption, simple circuit.

Owner:HEFEI UNIV OF TECH

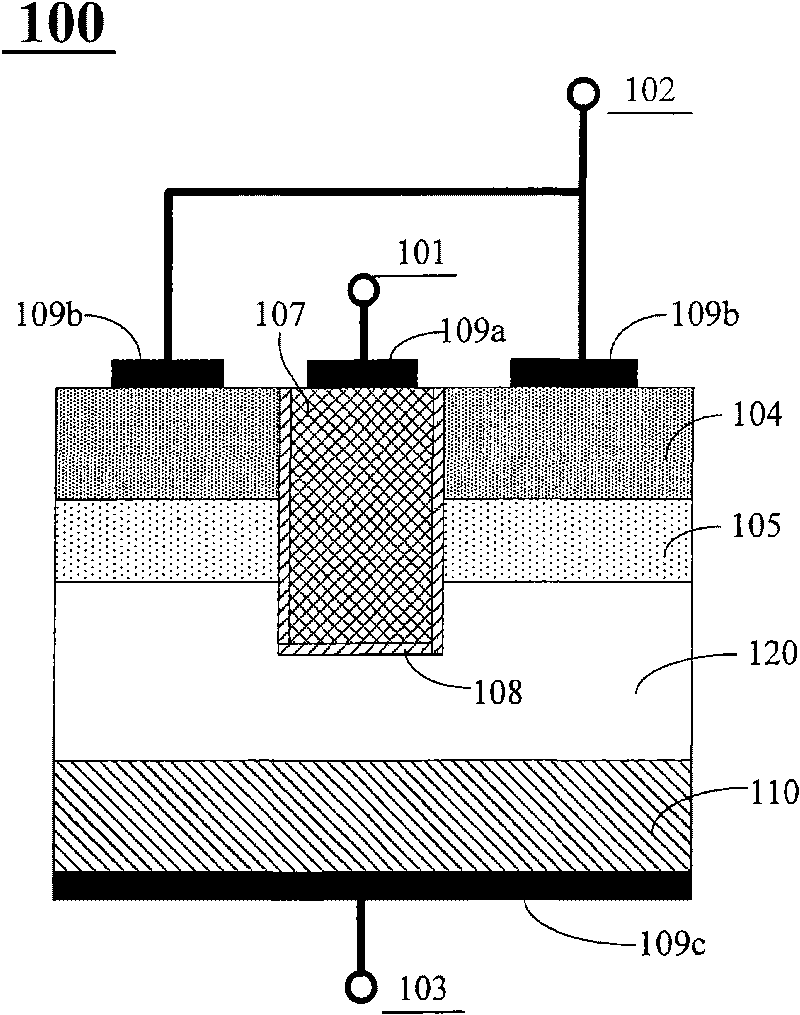

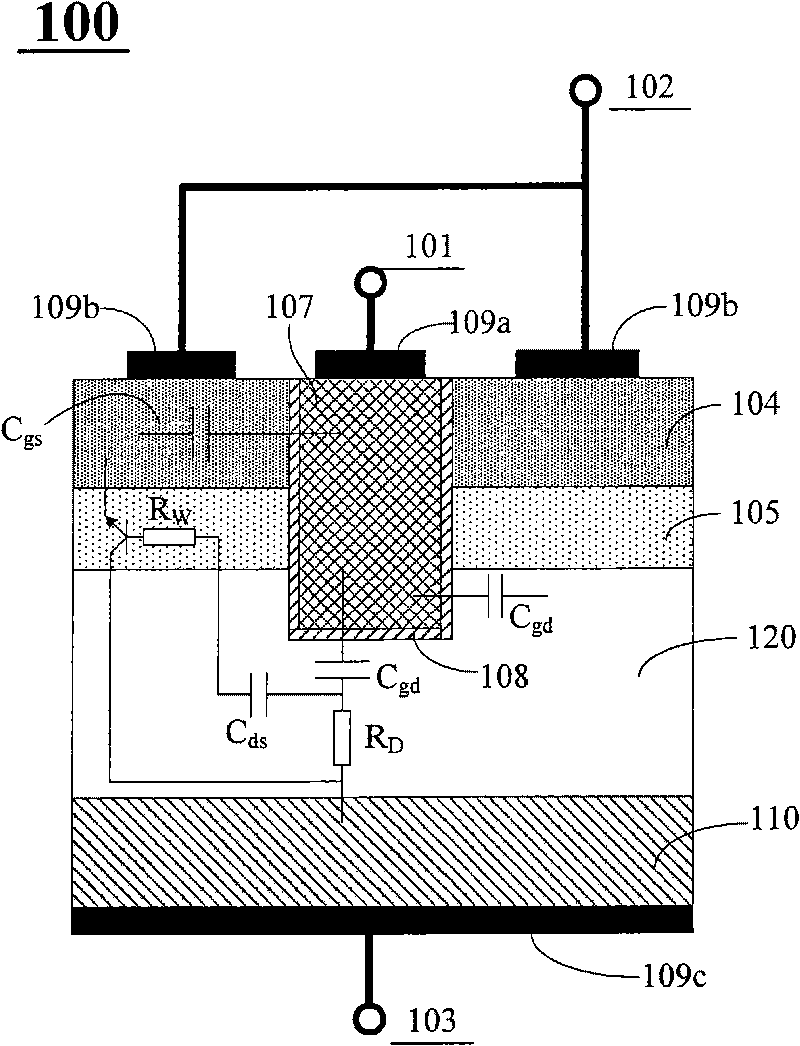

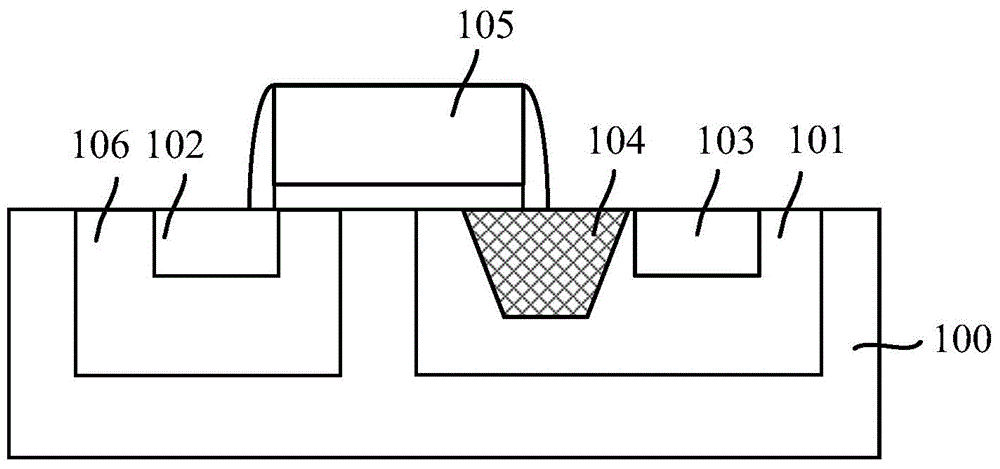

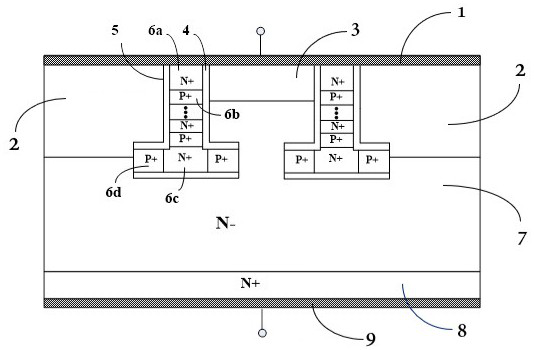

Grooved field-effect tube and preparation method thereof

InactiveCN101764155AIncrease the doping concentrationIncrease distanceSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceInsulation layer

The invention relates to a grooved field-effect tube and a preparation method thereof, belonging to the field of semiconductor devices; an insulation layer with thicker thickness is led in between a gate oxide at bottom part of the groove and a polysilicon gate of the groove, so as to increase the relative distance among the polysilicon gate, an extension layer and a substrate layer used as a drain region, that is, the distance between two electrode plates of a gate-drain capacitance is increased, therefore, the gate-drain capacitance of the grooved field-effect tube is reduced, the charging and discharging time of the field-effect tube to the gate-drain capacitance is greatly shortened in the switching process, the switching speed of the grooved field-effect tube is improved, dynamic loss is reduced and the performance of the devices are greatly improved on the premise of not changing the polysilicon gate area and not increasing the conduction resistance.

Owner:GRACE SEMICON MFG CORP

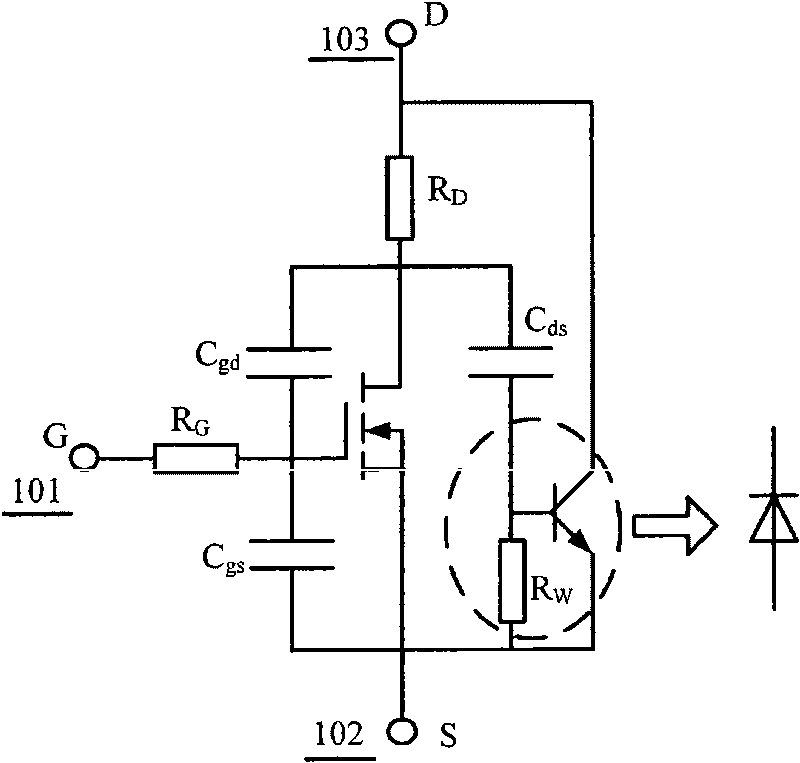

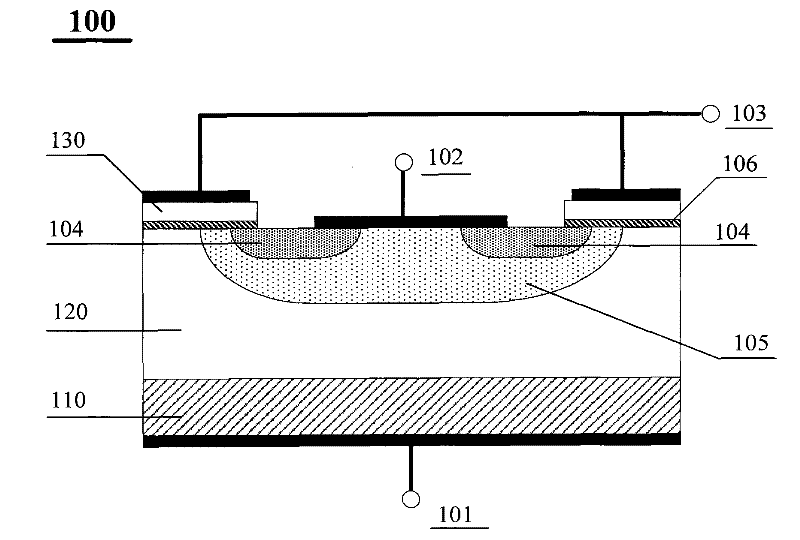

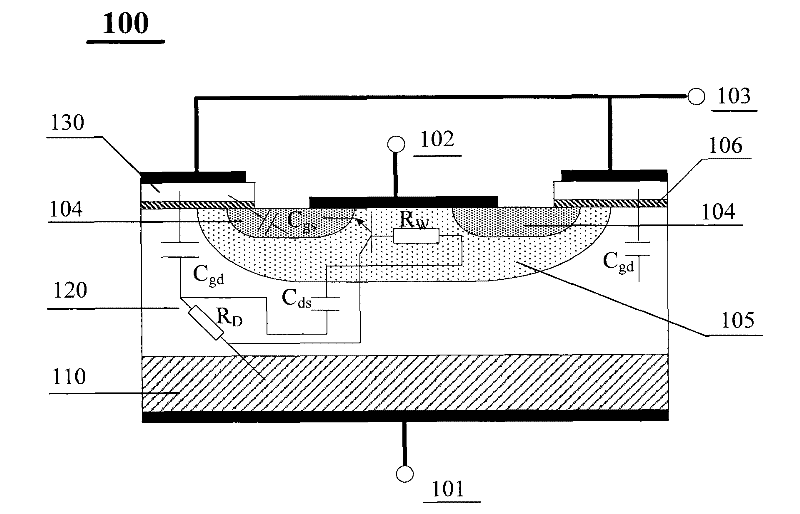

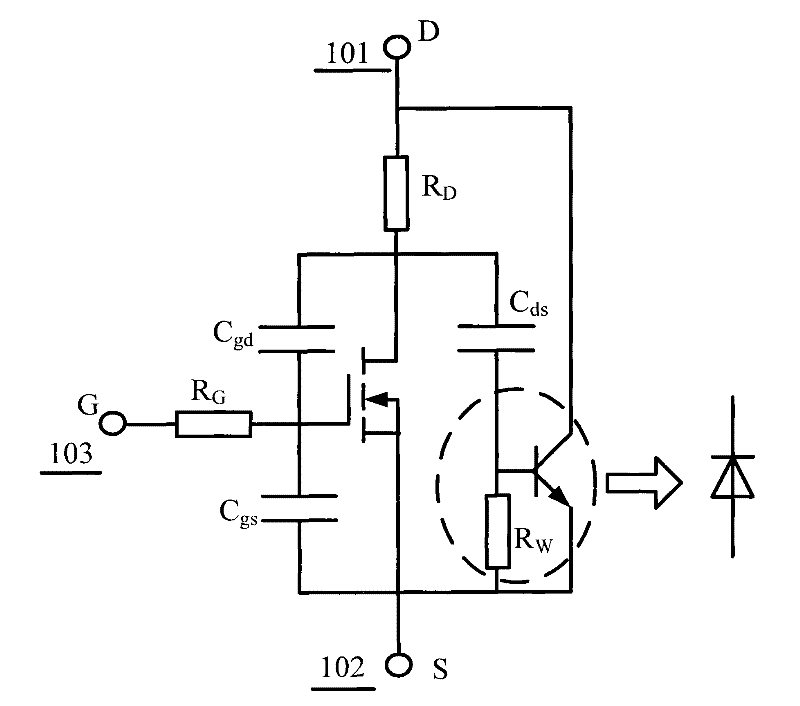

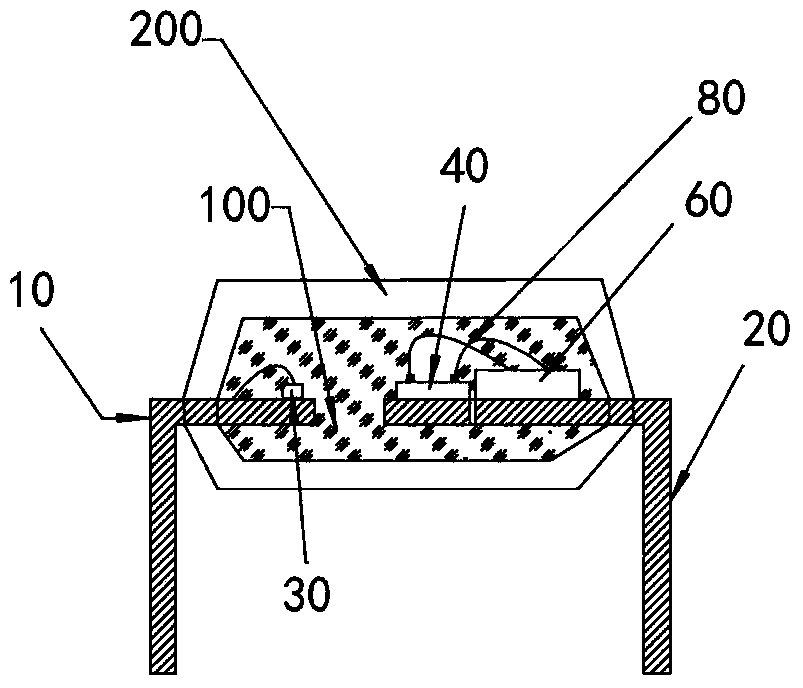

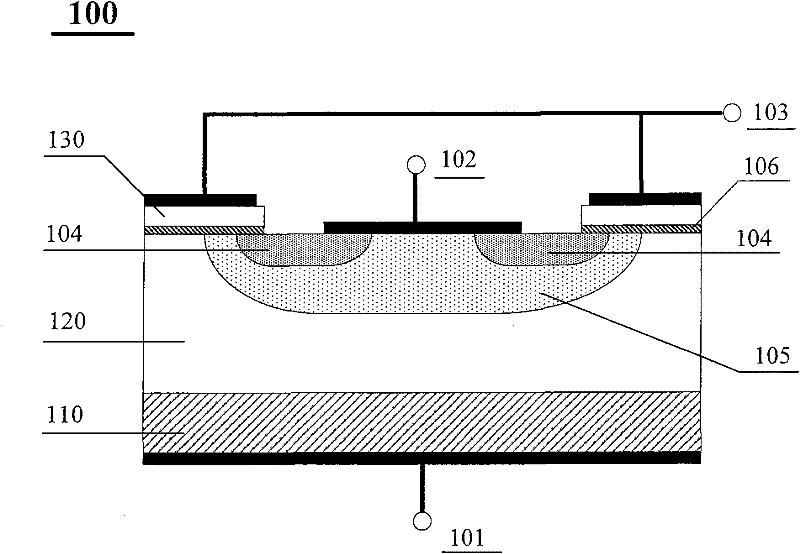

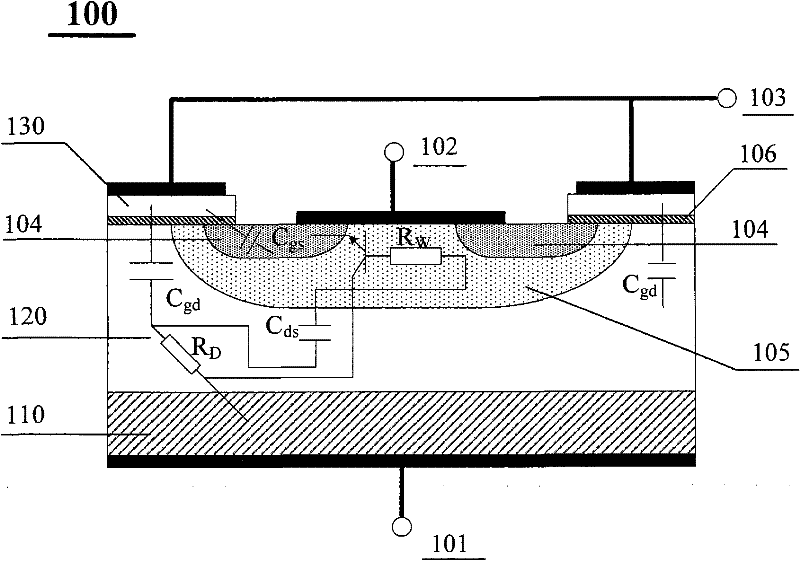

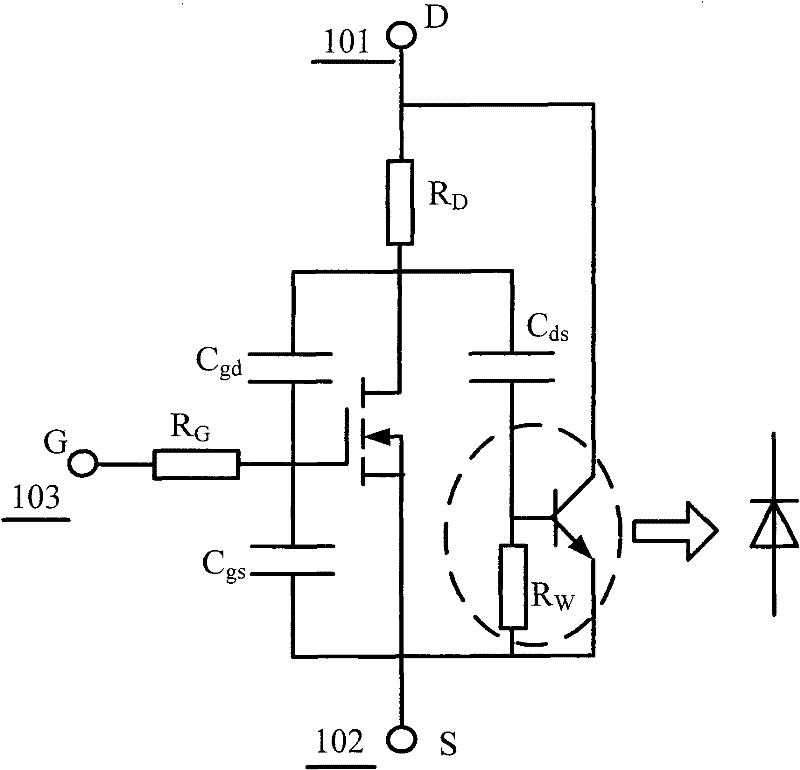

VDMOS (Vertical Double-diffused Metal Oxide Semiconductor) transistor

InactiveCN102456738AIncrease distanceShort charge and discharge timeSemiconductor devicesCapacitancePolysilicon gate

The invention relates to a VDMOS (Vertical Double-diffused Metal Oxide Semiconductor) transistor, belonging to the field of semiconductor devices. The VDMOS transistor comprises a semiconductor substrate, an epitaxial layer, a source doping region, a channel region, a gate oxide layer and a polysilicon gate, and an insulation dielectric layer with a thickness larger than that of the gate oxide layer is deposited at the side of the channel region between the polysilicon gate and the gate oxide layer in a horizontal direction through PECVD (Plasma Enhanced Chemical Vapor Deposition) process. By introducing the insulation dielectric layer, the relative distance between the polysilicon gate and the epitaxial layer is increased, namely the distance between the two polar plates of the gate-drain capacitance of the device is increased, thus under the condition that the area of the polysilicon gate is not changed and the on-resistance of the device is not increased, the gate-drain capacitance of the device is effectively reduced; the charging and discharging time for the gate-drain capacitance during the switching of the MOS (Metal Oxide Semiconductor) transistor is greatly reduced, the switching speed of the MOS transistor is increased, the dynamic loss is reduced, and therefore the performance of the device is greatly improved.

Owner:GRACE SEMICON MFG CORP

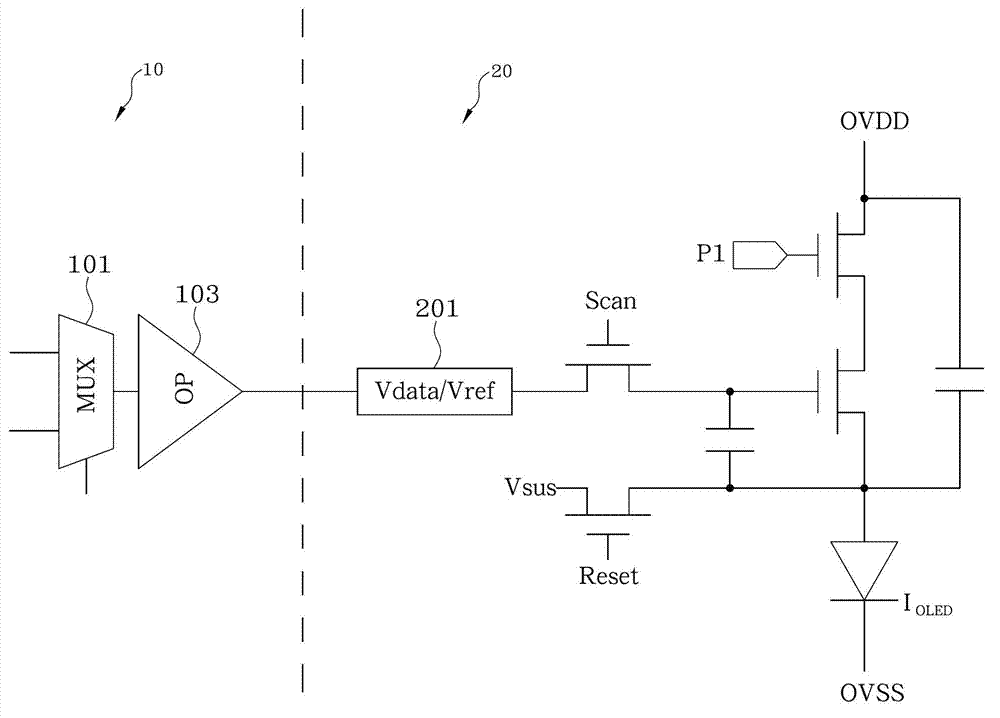

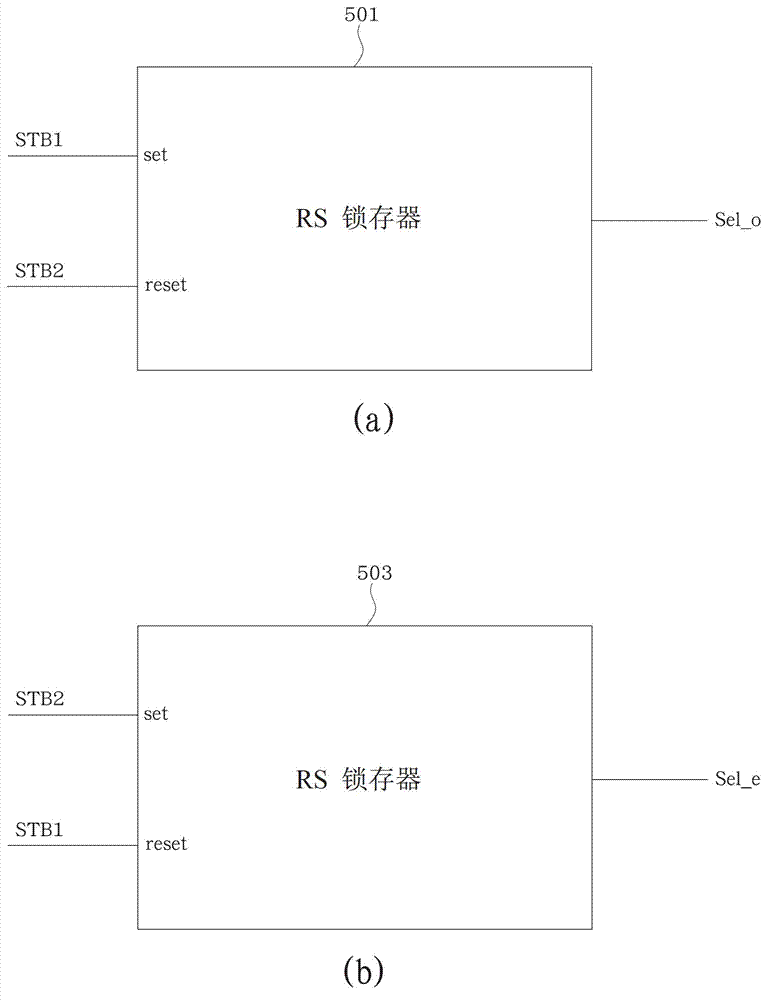

Drive circuit for OLED (Organic Light Emitting Diode) panel

InactiveCN102779481AReduce dynamic lossLower working temperatureStatic indicating devicesMultiplexerWorking temperature

The invention provides a drive circuit for an OLED (Organic Light Emitting Diode) panel. The drive circuit comprises a line buffer and an output buffer. The input end of the line buffer is used for receiving a data voltage signal; the output buffer is electrically connected to the line buffer, a first multiplexer of the output buffer outputs one of the data voltage signal and the reference voltage signal through a first enable signal, and a second multiplexer of the output buffer outputs the other one of the data voltage signal and the reference voltage signal through a second enable signal. The first multiplexer outputs the data voltage signal and the reference voltage signal in a staggered manner, and the second multiplexer outputs the reference voltage signal and the data voltage signal in a staggered manner. With the adoption of the drive circuit provided by the invention, the first multiplexer and the second multiplexer of the output buffer output the data voltage signal and the reference voltage signal in a staggered manner, so that two channels can be used for the charge sharing operation when the first multiplexer and the second multiplexer are switched, since each channel only takes charge of half voltage variation when sharing charges, dynamic loss of the circuit can be reduced effectively, and the work temperature of the circuit can be reduced.

Owner:AU OPTRONICS CORP

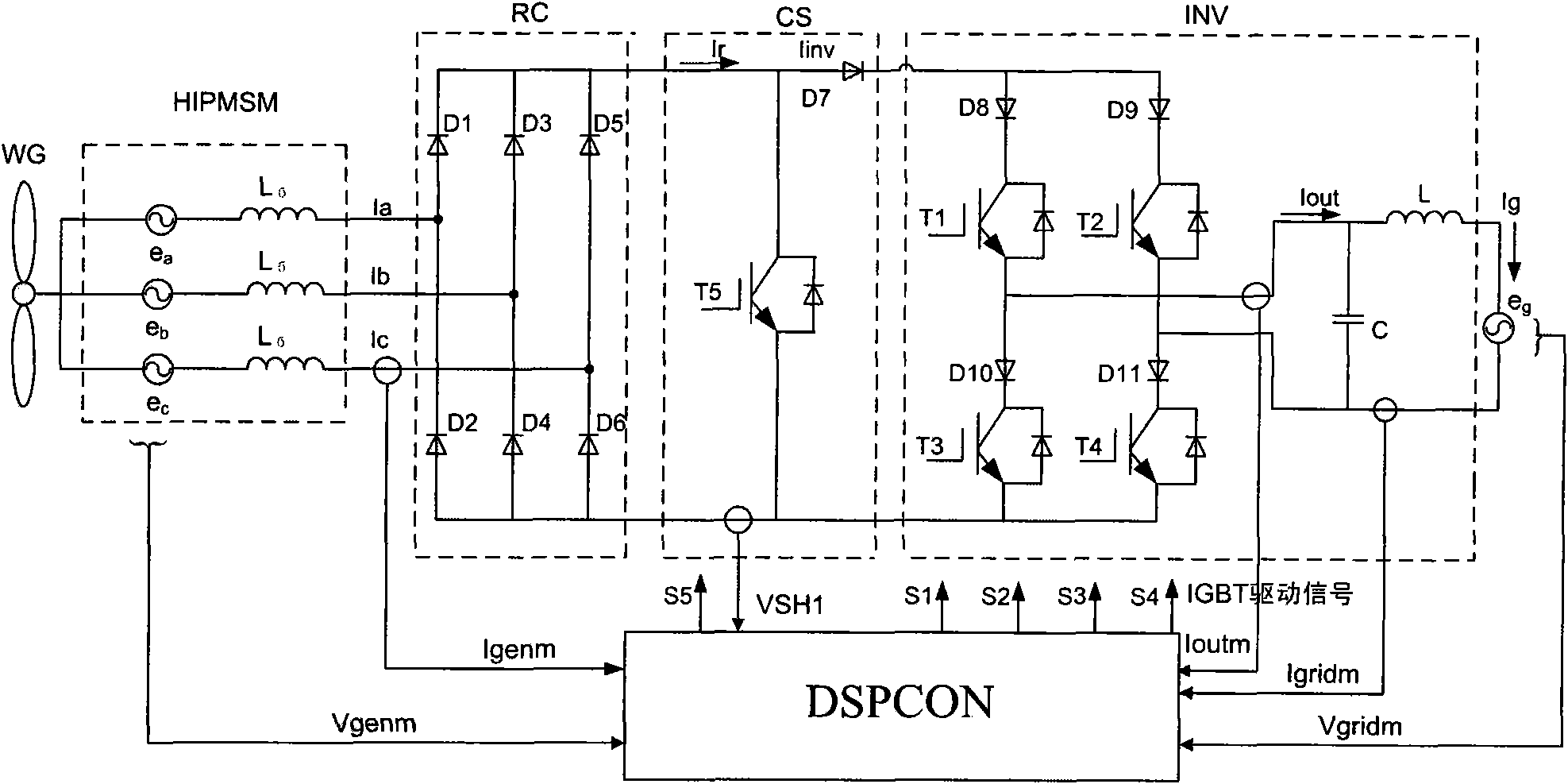

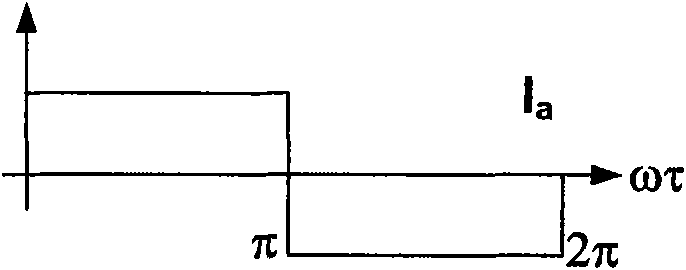

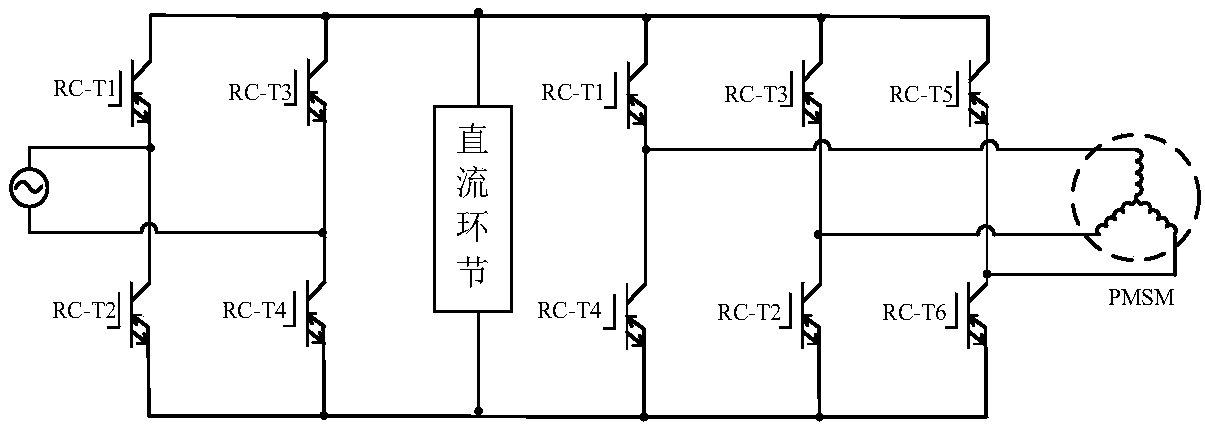

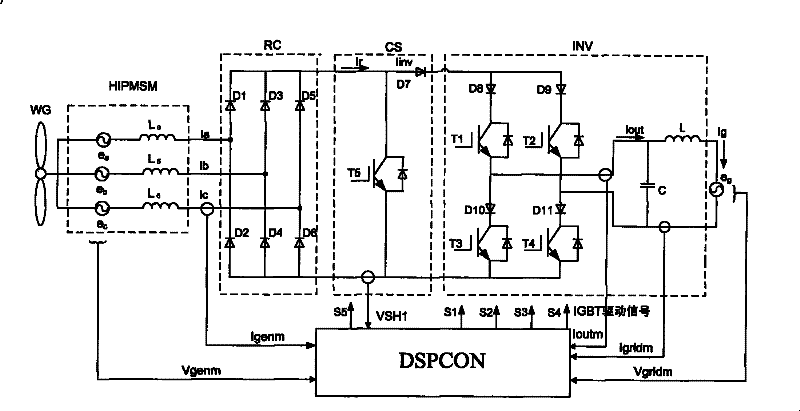

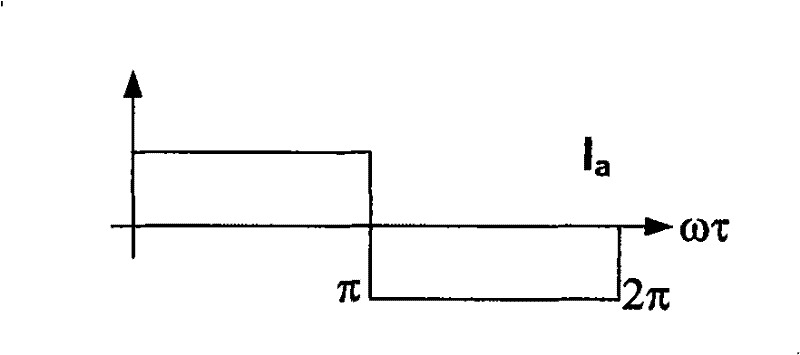

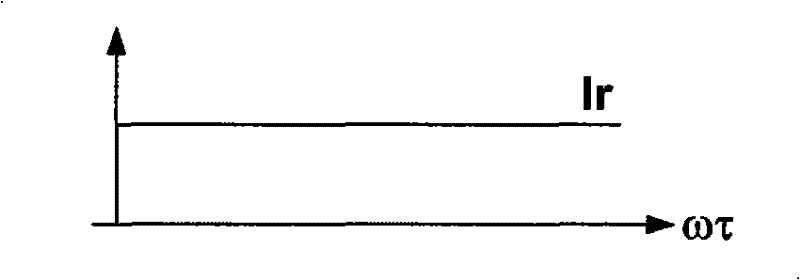

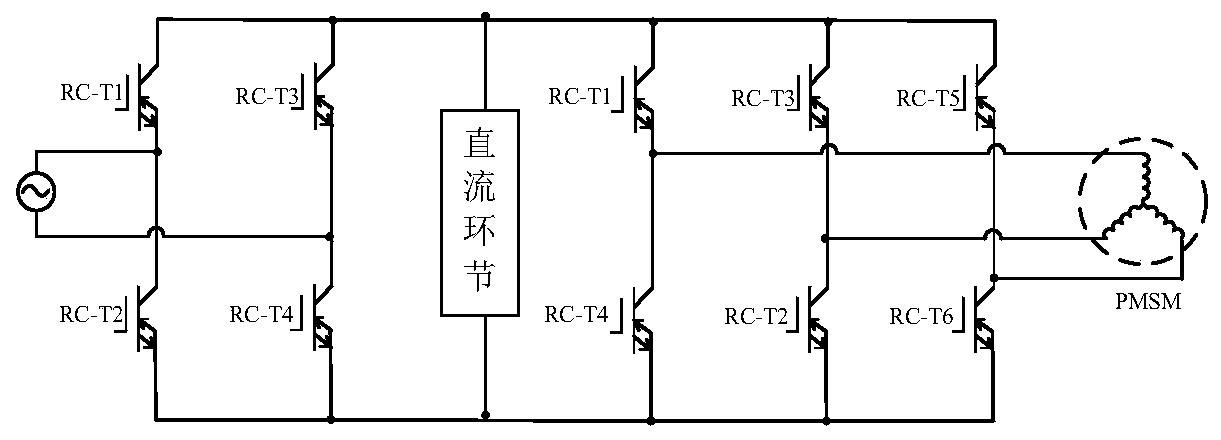

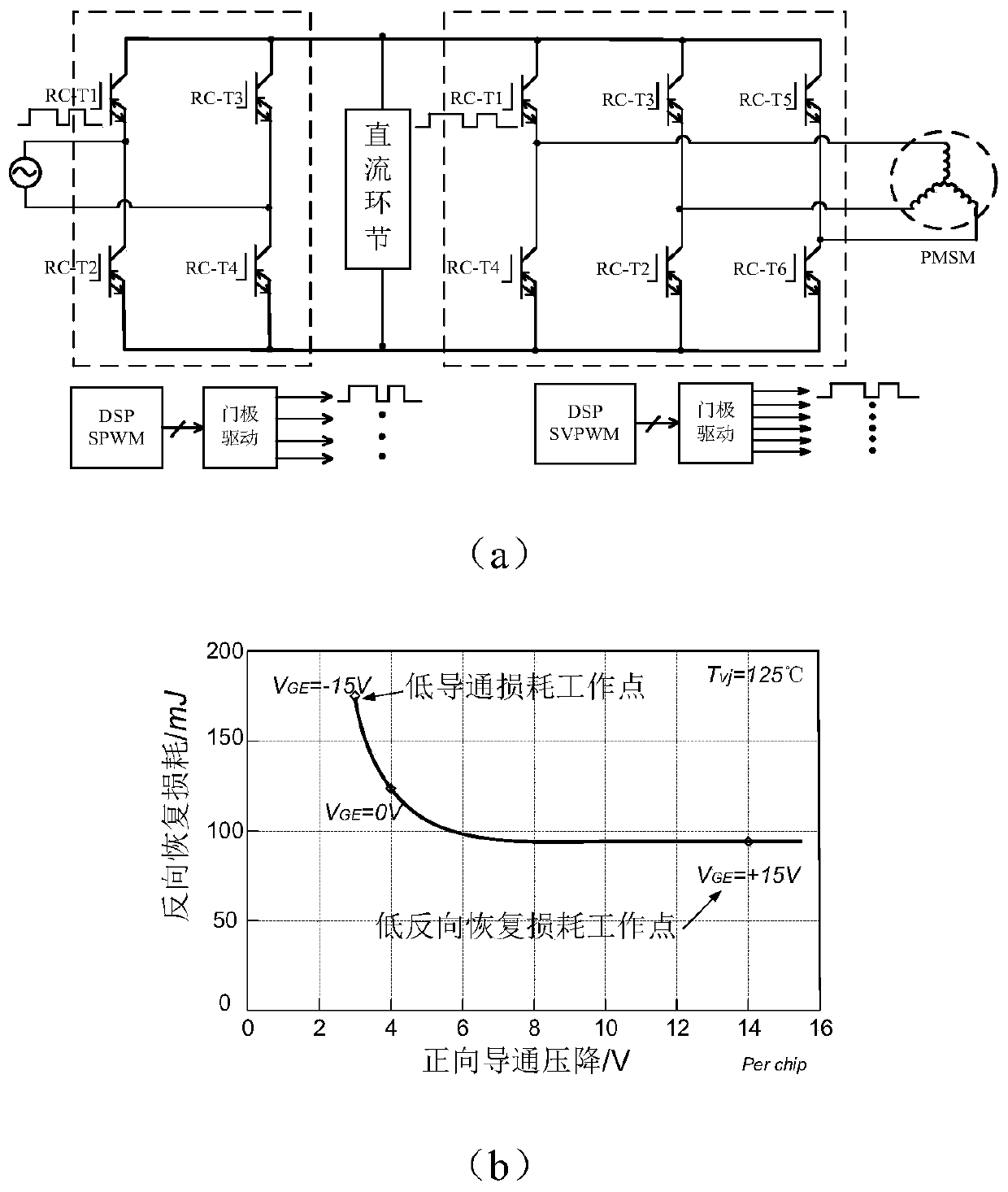

Directly-driven wind power generation system and mode for modulating SPWM inversion control signal in system

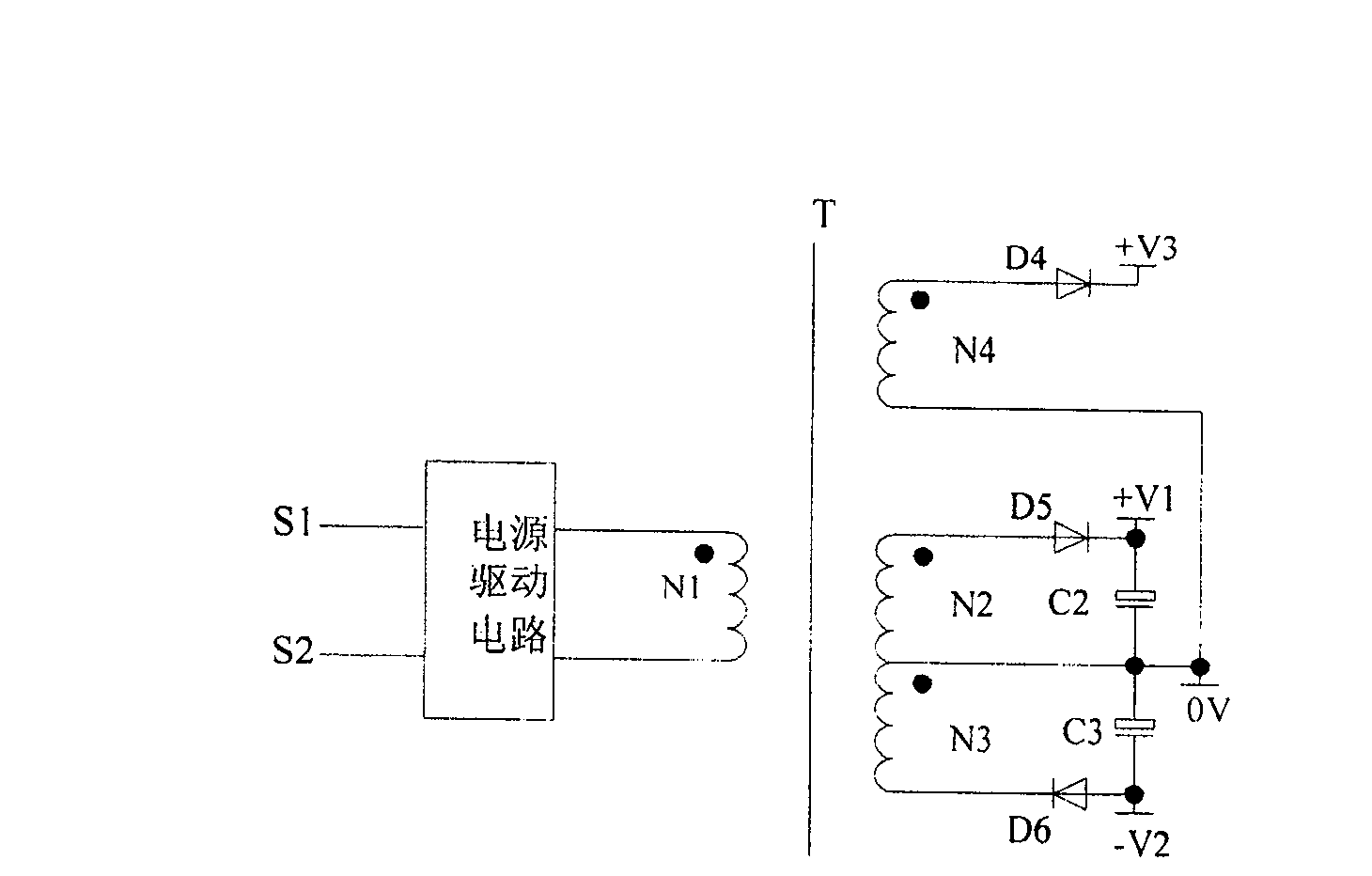

InactiveCN101599649ASimple designEasy to controlAc-dc conversionSingle network parallel feeding arrangementsFull bridgeDc current

The invention relates to a directly-driven wind power generation system and a mode for modulating an SPWM inversion control signal in the system. The directly-driven wind power generation system is characterized in that a high-inductance permanent magnet synchronous generator is arranged and coaxially connected with a wind turbine; an alternating current signal output end of the high-inductance permanent magnet generator is connected in series with a triphase uncontrollable rectifier; direct current output by the triphase uncontrollable rectifier is used as an input signal of a subsequent current type inverter; an output signal of the current type inverter is filtered by a wave filter and fed to an alternating current network as sinusoidal current; the current type inverter consists of a fully-controlled power electronic switch and a current source type full-bridge inverting circuit; and the fully-controlled power electronic switch uses a sinusoidal pulse-width modulating signal SPWM as a control signal. Under the condition of a low wind speed, the directly-driven wind power generation system can also generate power without needing a direct current capacitor of the convertor, simplifies a controlling system, improves the generating efficiency of the whole machine and reduces the cost.

Owner:HEFEI UNIV OF TECH

Electrostatic shielding effect transistor and design method thereof

ActiveCN104009087AImprove high frequency characteristicsReduce dynamic lossSemiconductor/solid-state device detailsSolid-state devicesEngineeringConductive materials

The invention discloses an electrostatic shielding effect transistor. The electrostatic shielding effect transistor comprise a collector, groove-type grids, a base region, an oxidization layer, a polycrystalline silicon layer and emitters. The collector comprises a leading-out end, an N+ substrate, an N+ conductive material layer and an N- conductive material layer. The groove-type grids are arranged on the N- conductive material layer, B ions of certain concentration are injected into the bottom of a groove to serve as P+ regions, and the base region injected with the B ions is arranged between the grids. The oxidization layer is arranged on the grids and the base region, the emitters are formed on the base region and the oxidization layer, the polycrystalline silicon layer is deposited on the oxidization layer and the polycrystalline silicon layer forms an emitting region below the emitters after high-temperature diffusion. The electrostatic shielding effect transistor is provided with the emitters and the base region which are super shallow in junction and small in size, and therefore, the emitter current crowding effect and the base region flow extruding effect of the device can be greatly improved. Due to the super small junction depth of the structure and the base region of the device, the hole extraction speed is increased and the high frequency property of the device is improved.

Owner:SHENZHEN SHENGYUAN SEMICON

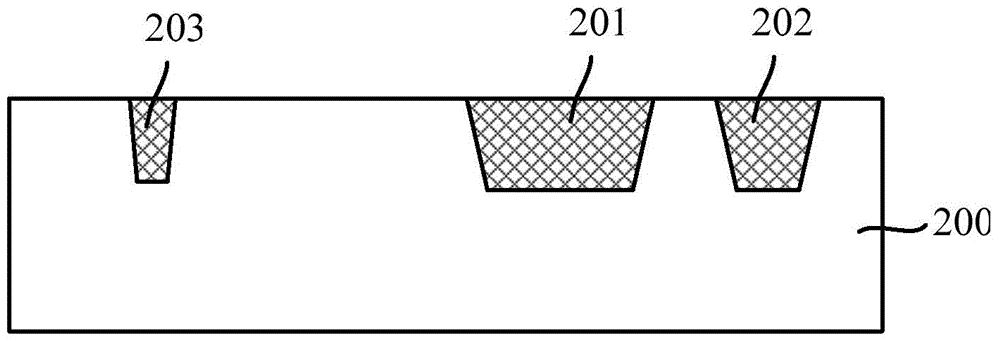

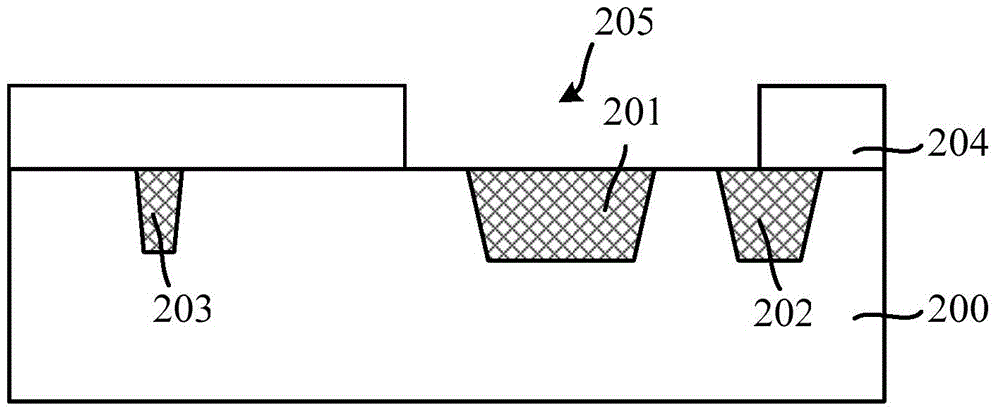

Lateral double-diffusion field effect transistor and forming method therefor

ActiveCN105448979AReduce dynamic lossIncreased breakdown resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesBody regionIon

The invention discloses a lateral double-diffusion field effect transistor and a forming method therefor. The lateral double-diffusion field effect transistor comprises a semiconductor substrate which is provided with foreign ions of a first conductive type in a doped manner; a first shallow trench isolation structure located in the semiconductor substrate; a drift region located in the semiconductor substrate, wherein the drift region surrounds the first shallow trench isolation structure and is provided with foreign ions of a second conductive type in a doped manner, and the second conductive type is different from the first conductive type; an inverted-type doping region located in the drift region, wherein the depth of the inverted-type doping region is less than the depth of the drift region, and the inverted-type doping region is provided with the foreign ions of the first conductive type in a doped manner; a body region which is located in the semiconductor substrate at one side of the drift region, and is provided with the foreign ions of the first conductive type in a doped manner; and a grid structure formed on the semiconductor substrate, wherein one end of the grid structure extends above the body region, and the other end of the grid structure stretches above the first shallow trench isolation structure. The grid-drain stray capacitance of the lateral double-diffusion field effect transistor is reduced.

Owner:SEMICON MFG INT (SHANGHAI) CORP

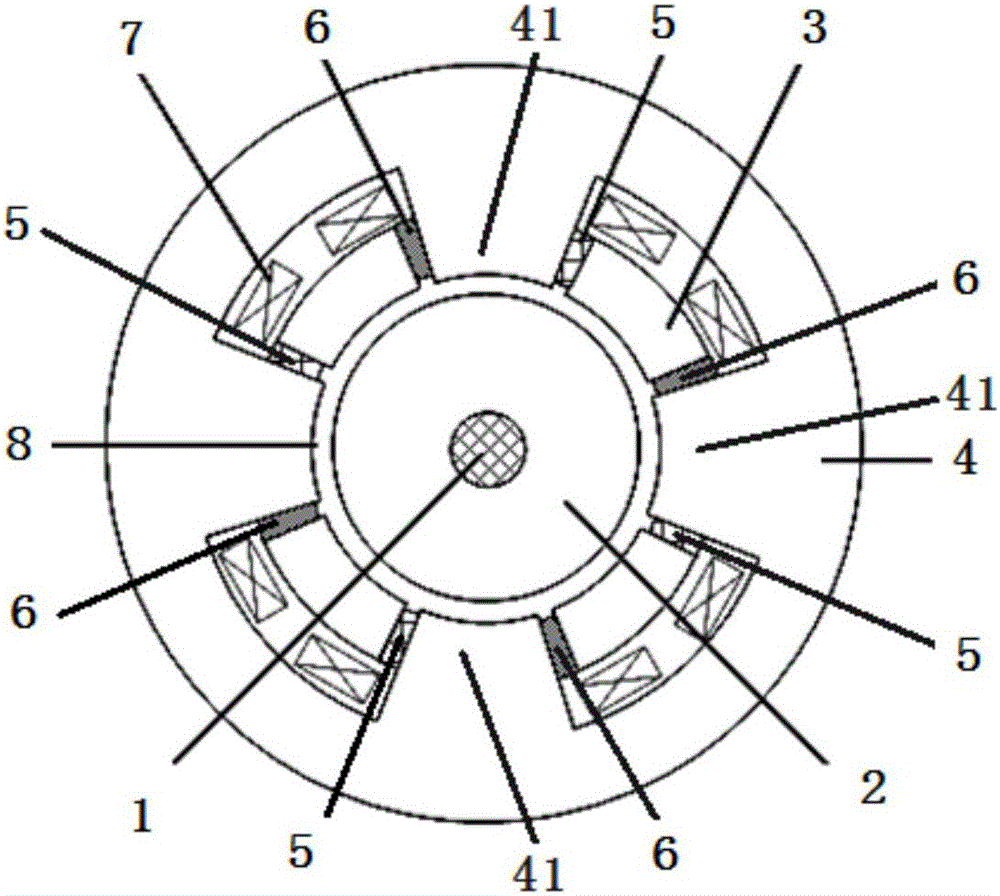

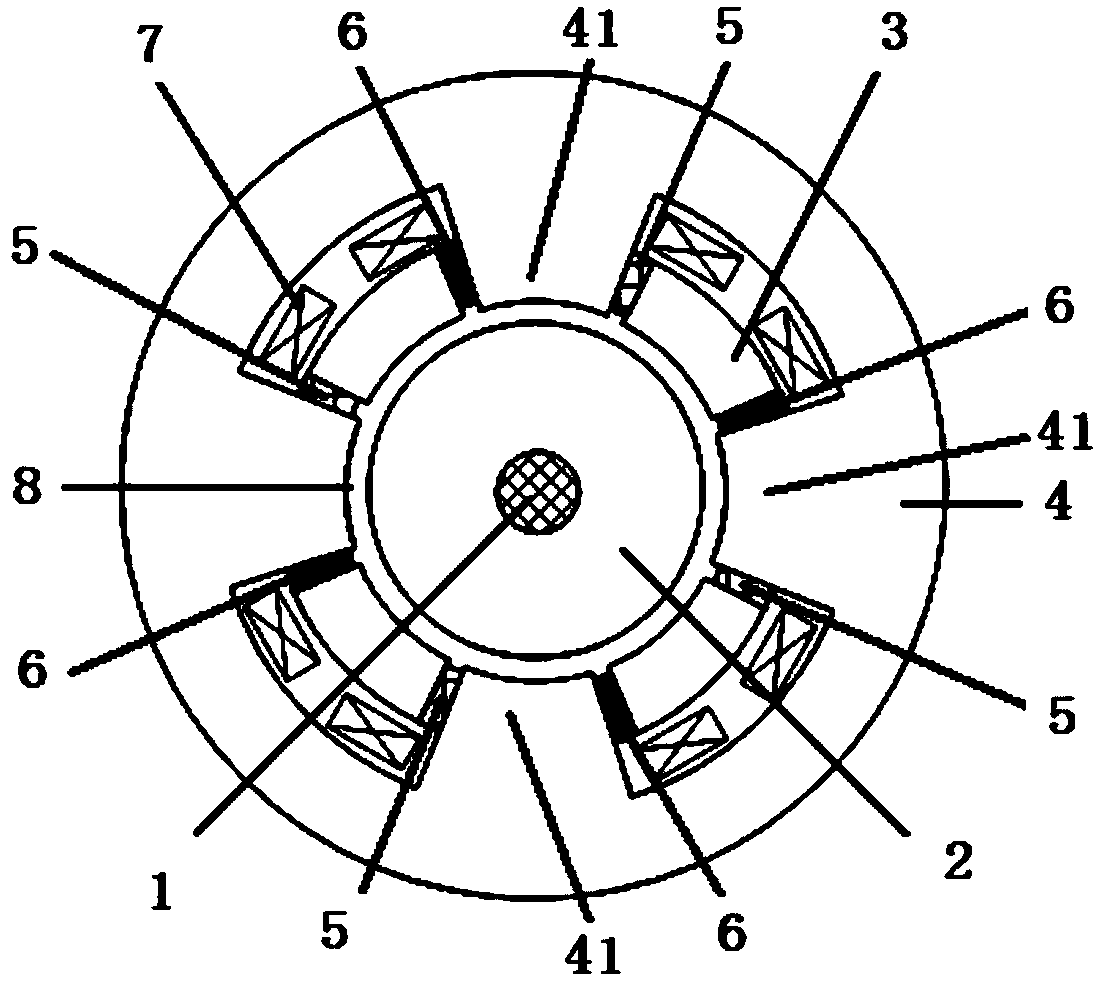

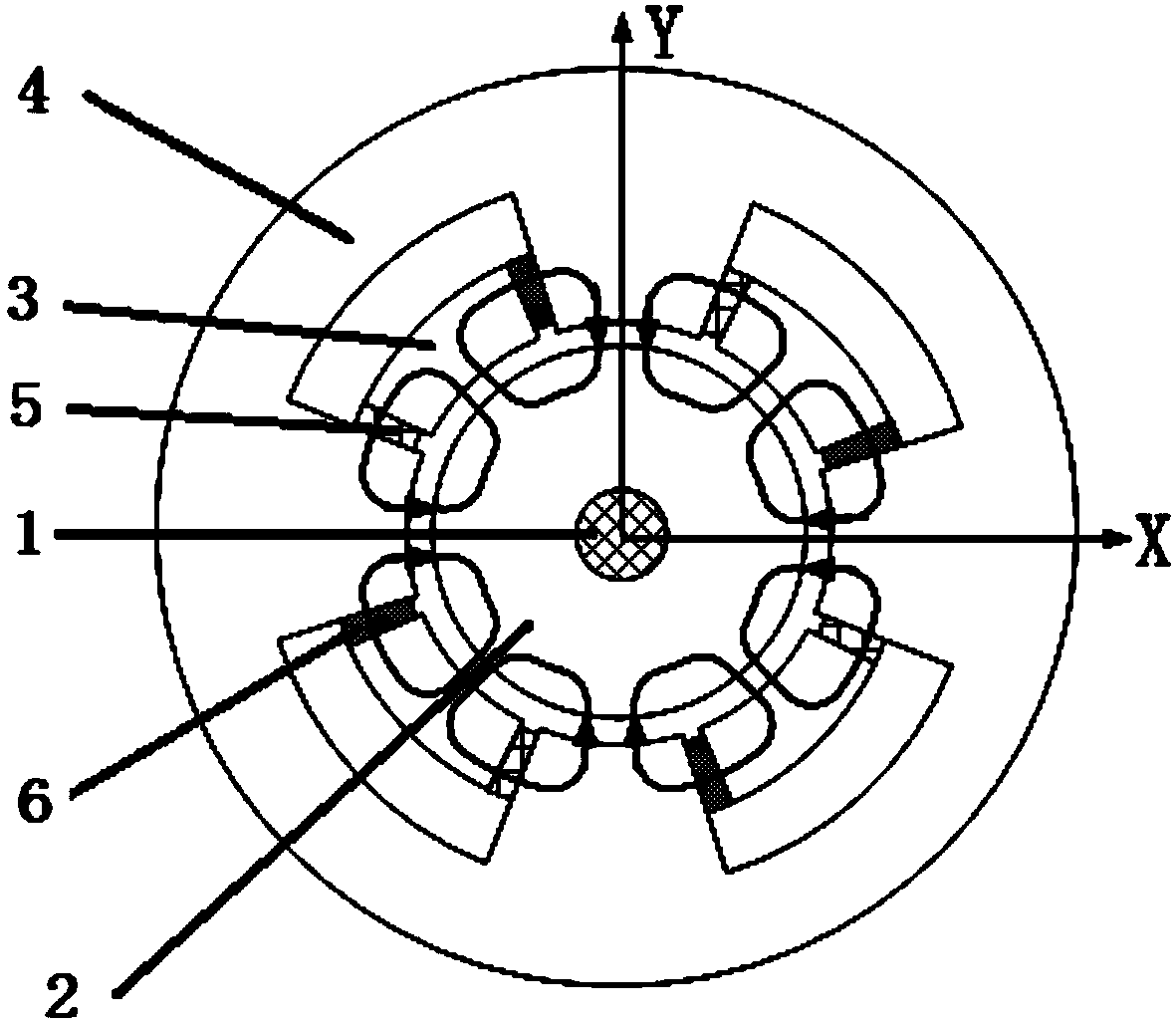

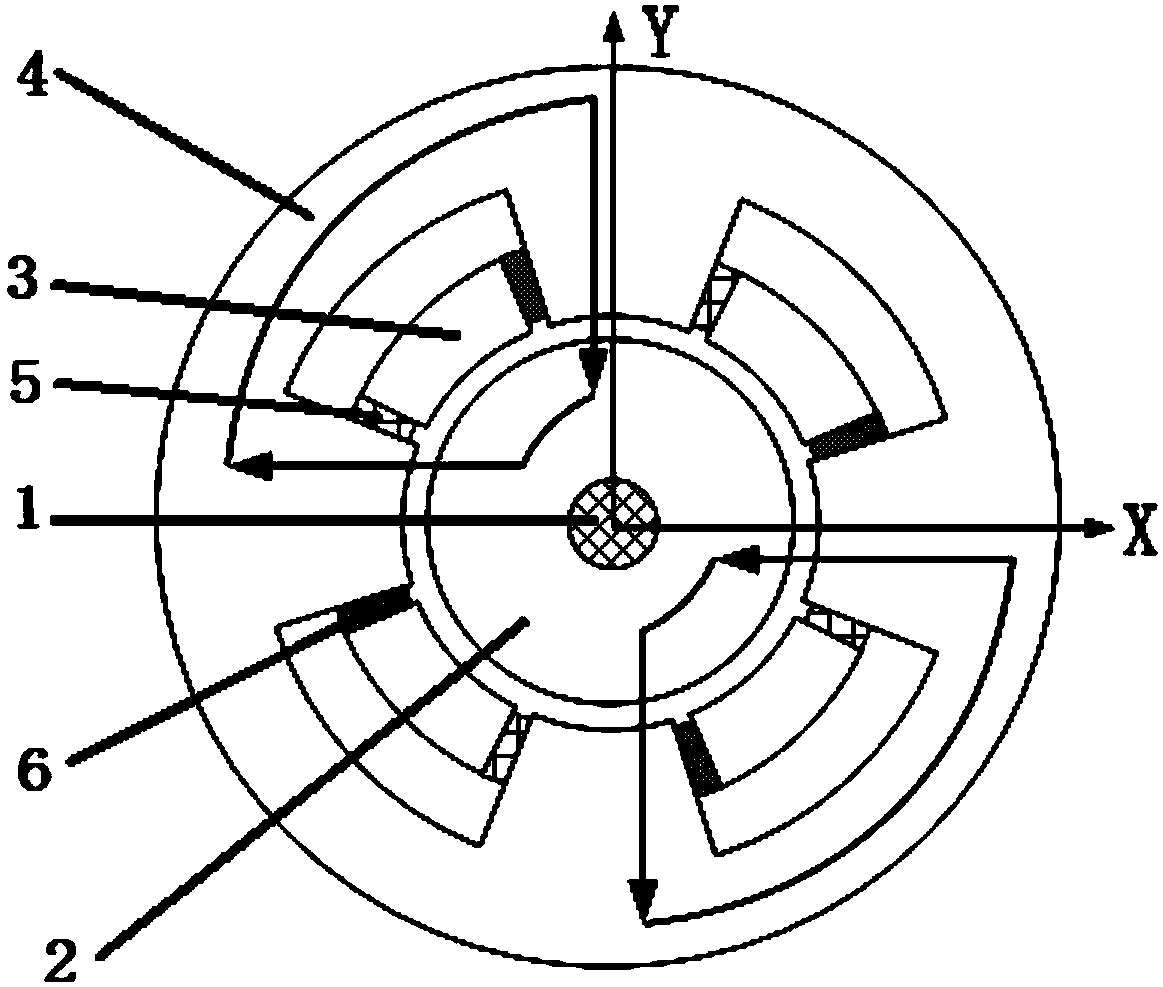

Heterospolar type permanent magnet bias mixed radial magnetic bearing

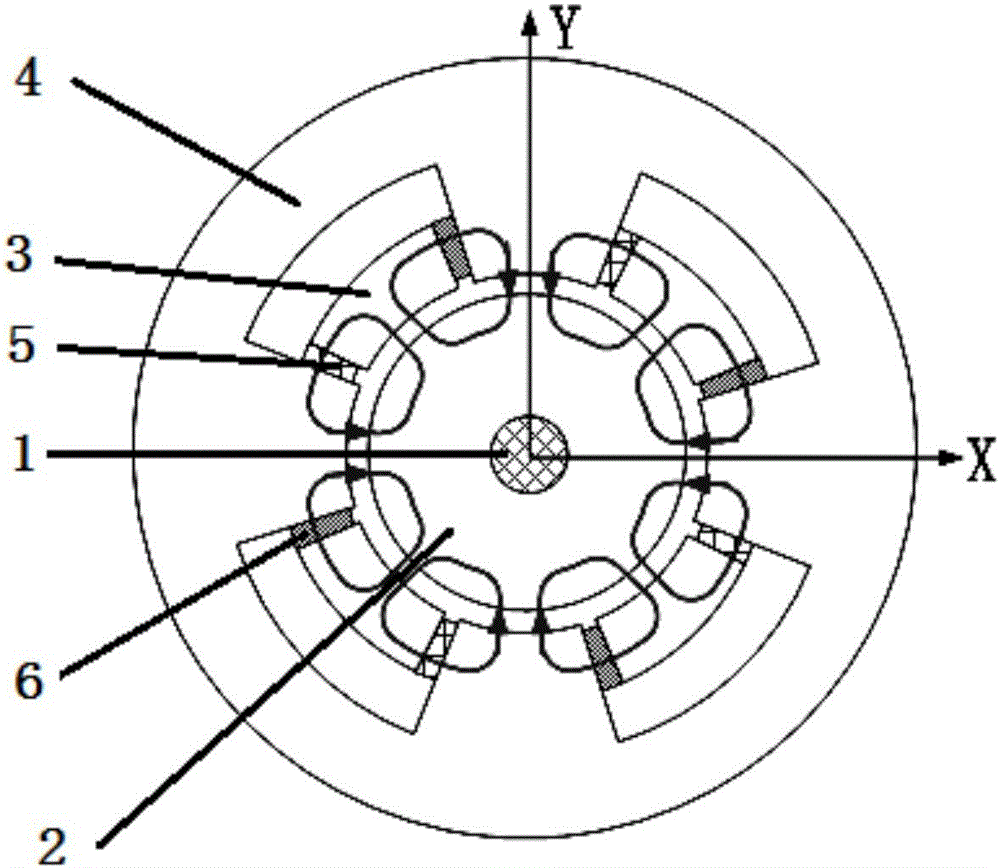

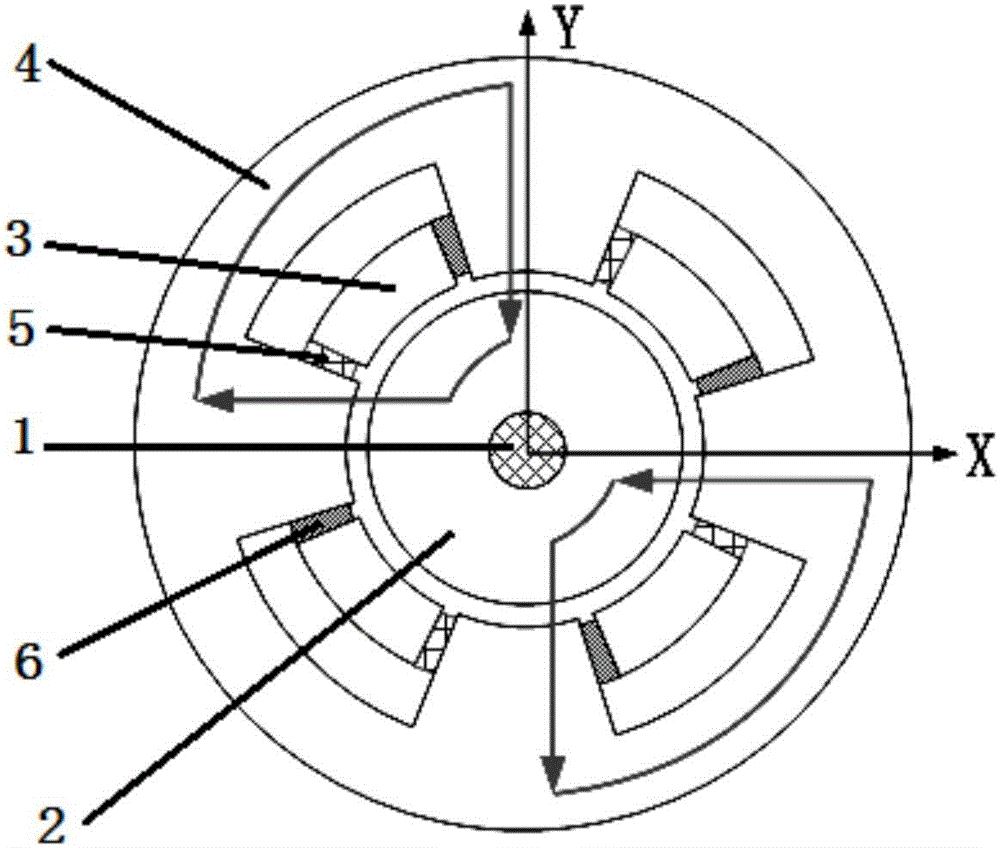

ActiveCN106337876AWill not cause irreversible demagnetizationElectric excitation magnetomotive force is smallBearingsMagnetic bearingMagnetic poles

The invention discloses a heterospolar type permanent magnet bias mixed radial magnetic bearing. The heterospolar type permanent magnet bias mixed radial magnetic bearing comprises a stator assembly and a rotor assembly. The rotor assembly comprises a rotary shaft and a rotor iron core arranged outside the rotary shaft. The stator assembly comprises auxiliary magnetic poles, a stator iron core, permanent magnets and excitation coils. Stator magnetic poles with the number of the multiple of four are distributed on the inner surface of the stator iron core evenly at intervals in the circumferential direction. One auxiliary magnetic pole is arranged between every two adjacent stator magnetic poles. One permanent magnet is embedded between each stator magnetic pole and the adjacent auxiliary magnetic pole. The magnetizing directions of every two adjacent permanent magnets are opposite. One set of excitation coils are arranged in a groove between every two adjacent stator magnetic poles. Work air gaps are arranged between the surfaces, toward the axes, of the stator magnetic poles and the auxiliary magnetic poles, and the outer surface of the rotor iron core. An electrical excitation magnetic path of the magnetic bearing does not pass the permanent magnets, additional air gaps do not exist, the auxiliary magnetic poles effectively solve the problem that the stator yoke thickness is large, the stator outer diameter can be reduced, and the space utilization ratio is increased.

Owner:NAVAL UNIV OF ENG PLA

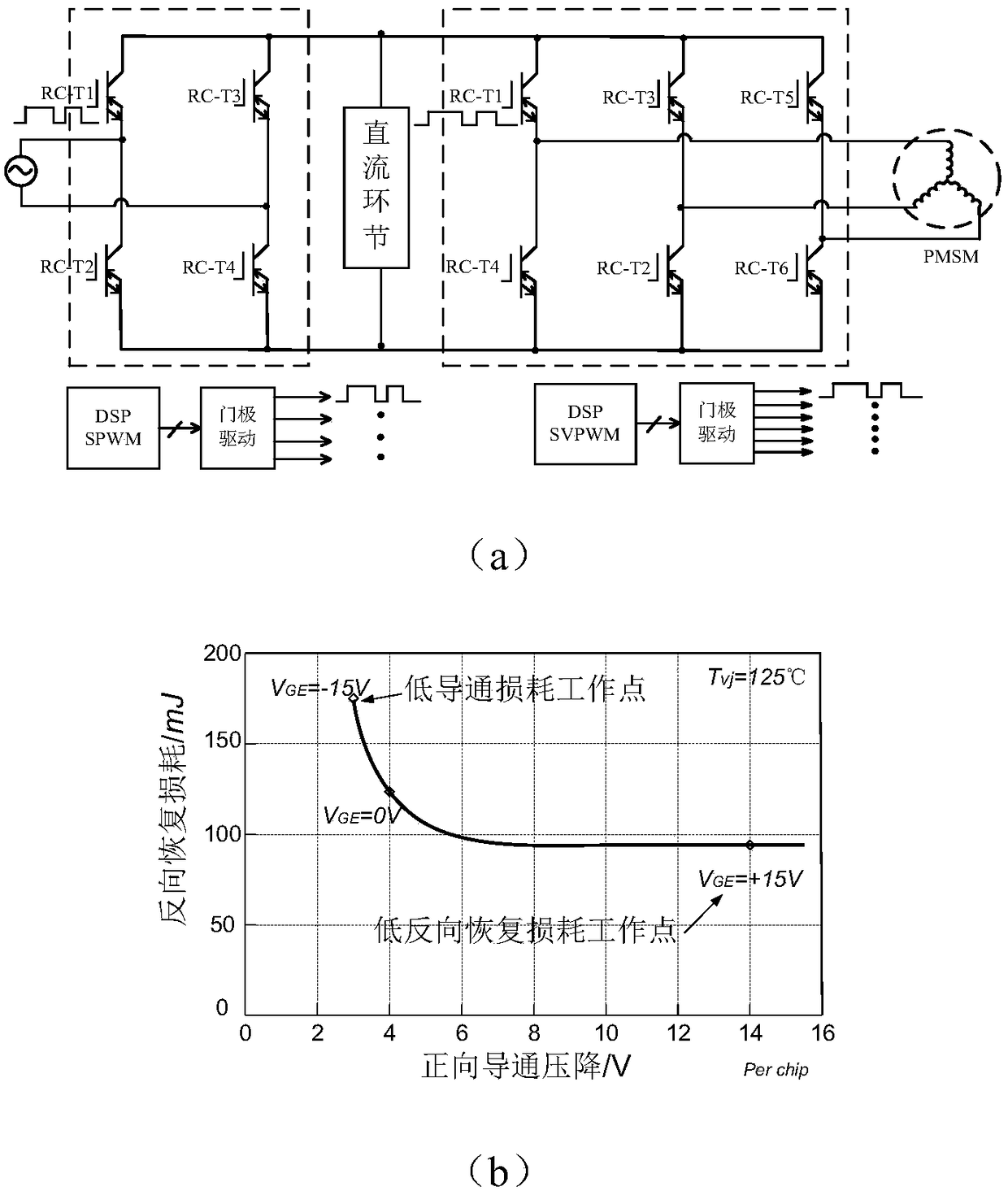

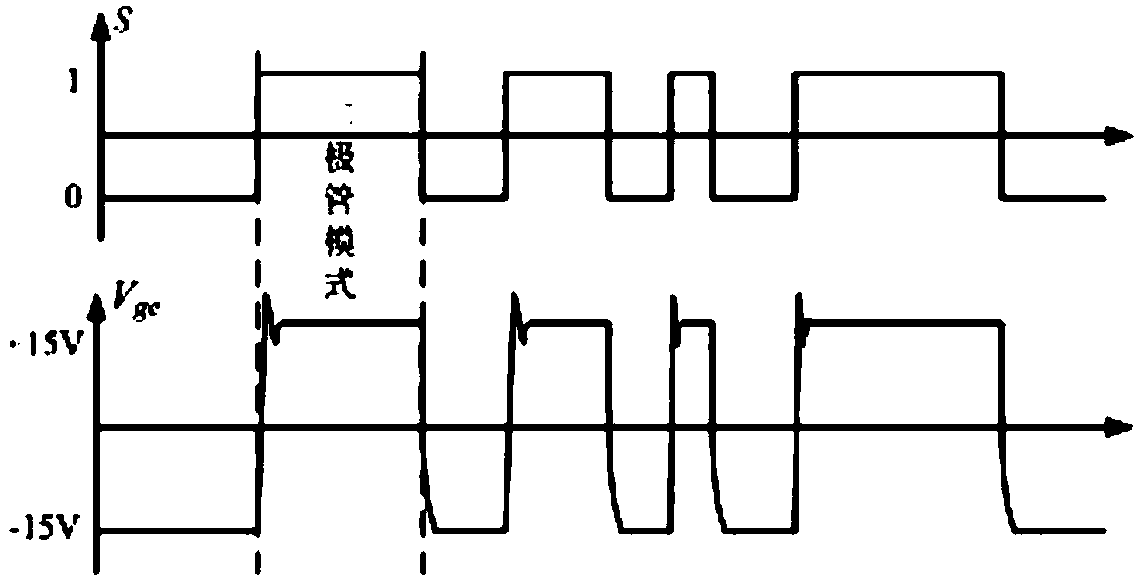

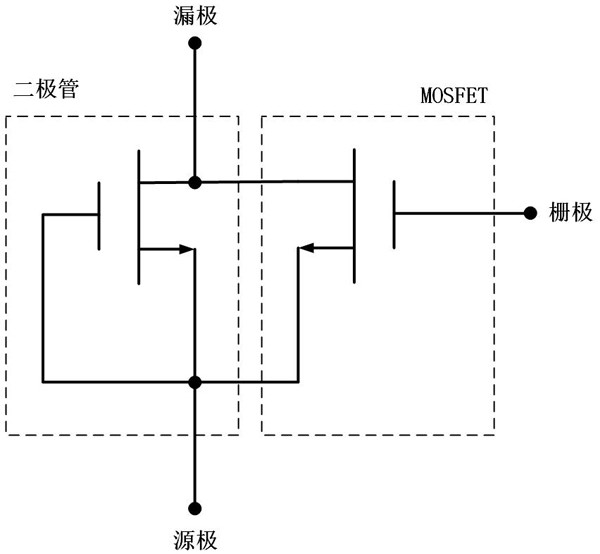

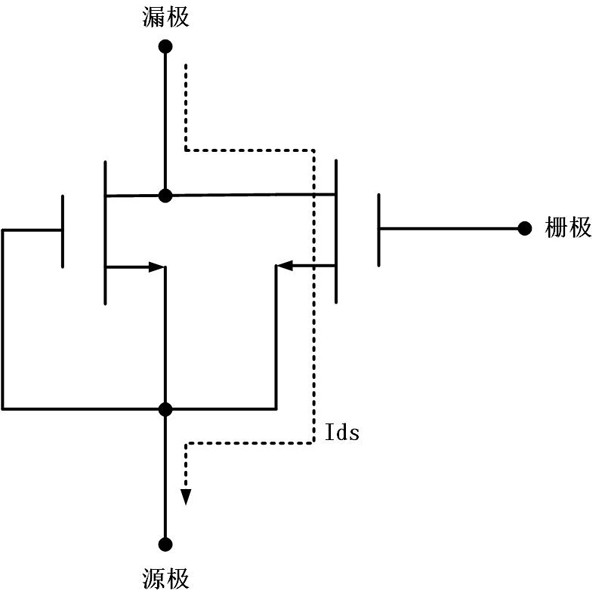

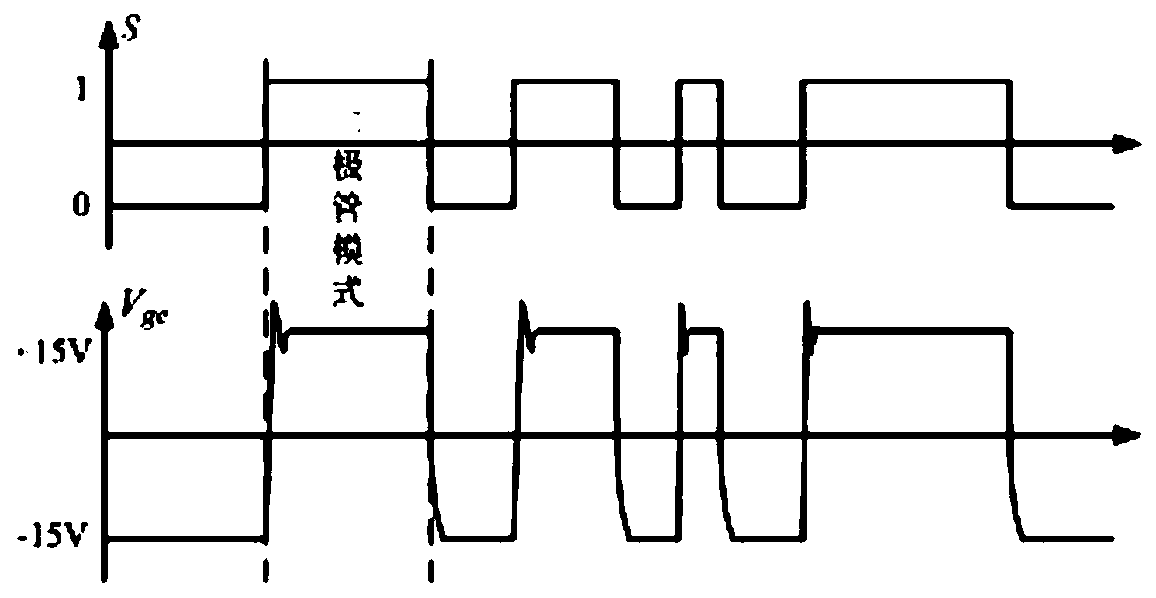

Current threshold judgment-based pre-withdrawing saturation driving method of reverse conduction IGBT gate pole

ActiveCN108390547AImprove thermal performanceReduce system maintenance workloadEfficient power electronics conversionElectronic switchingElectric energyCurrent threshold

The invention relates to a current threshold judgment-based pre-withdrawing saturation driving method of a reverse conduction IGBT gate pole. An external power MOSFET is arranged in the reverse conduction IGBT gate pole and has an effect of flexibly converting a driving level. By the driving circuit, the running mode of the reverse conduction IGBT can be monitored in real time, an average currentpassing through the circuit is obtained by a current measurement method, thus, whether a voltage of the gate pole is needed to be changed is judged, the dynamic and static characteristics of an integrated diode in the reverse conduction IGBT are optimized, the dynamic and static loss of a three-phase inversion system is reduced, and the system efficiency is improved; through calculation, the system capacity can be improved by about 30% on the premise that the volume is maintained unchanged when the pre-withdrawing saturation gate pole driving circuit is applied to a three-phase inverter, the loss release is reduced by 10-15%, and the electric energy can be saved by 10-12% by an IMW-level three-phase inverter.

Owner:BEIJING JIAOTONG UNIV

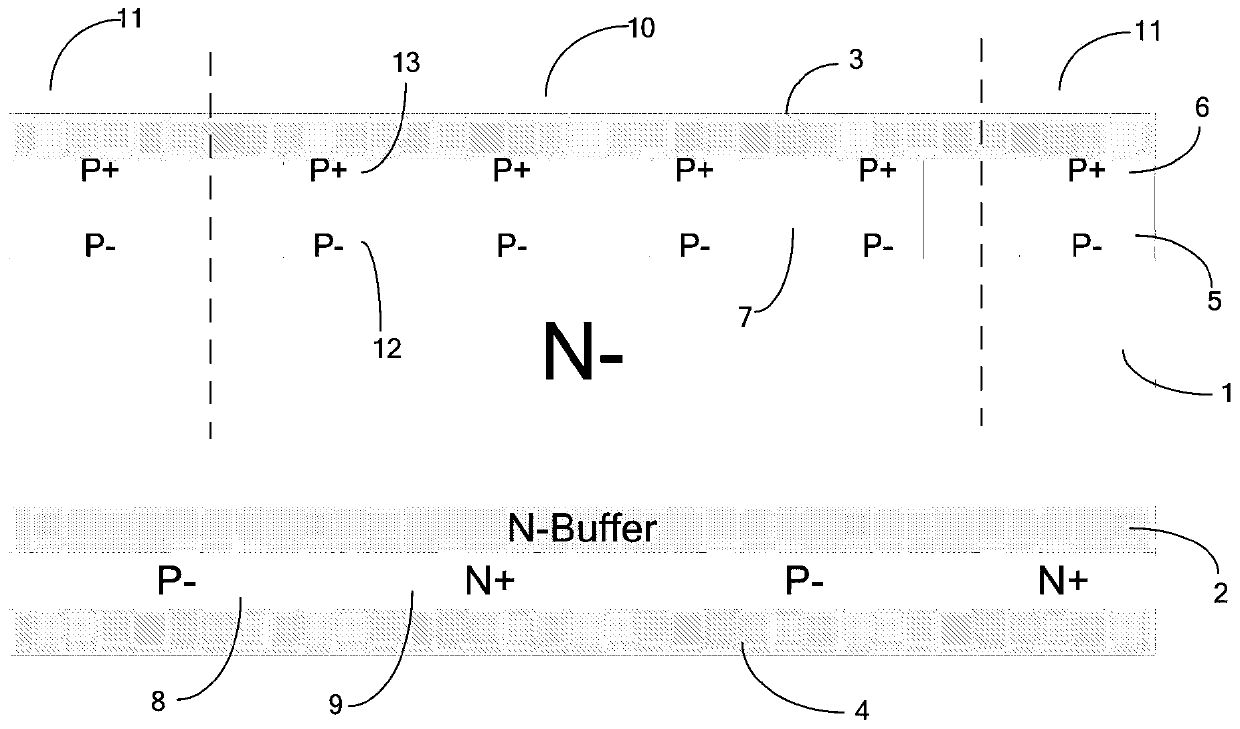

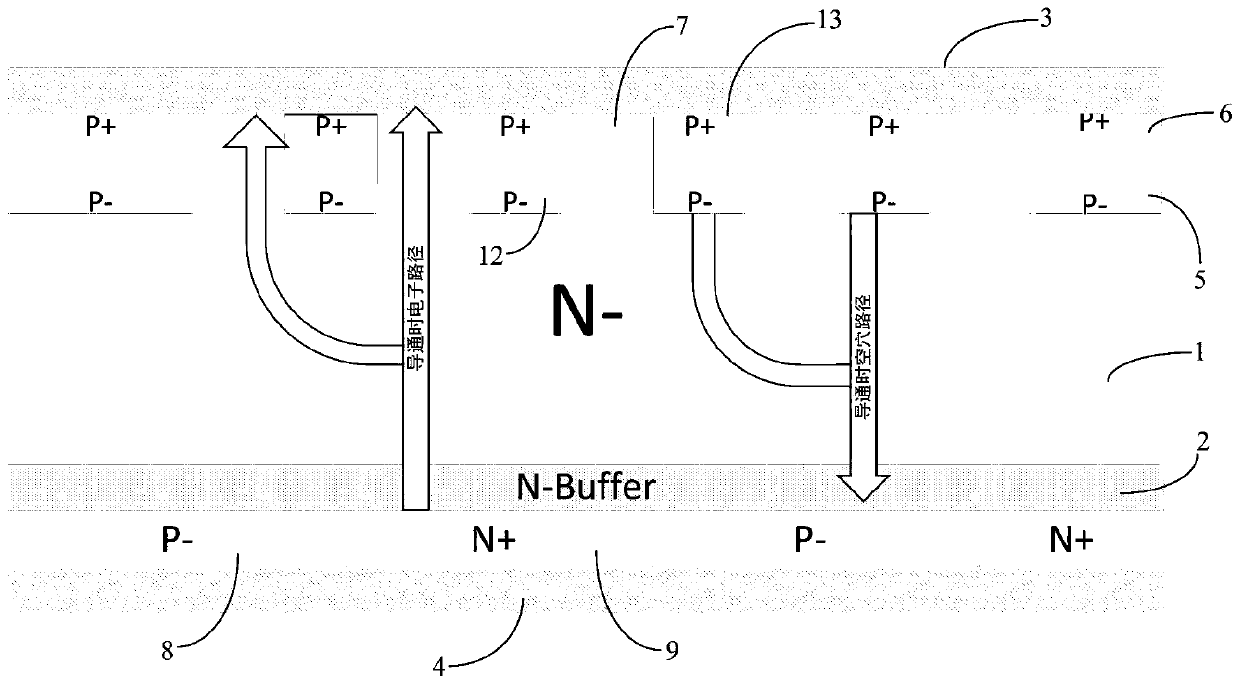

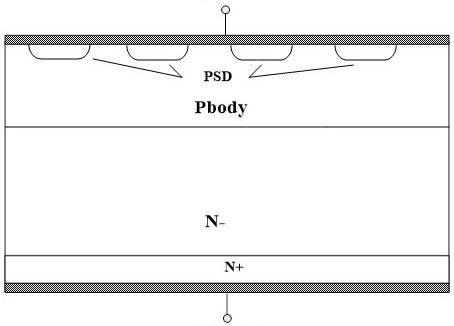

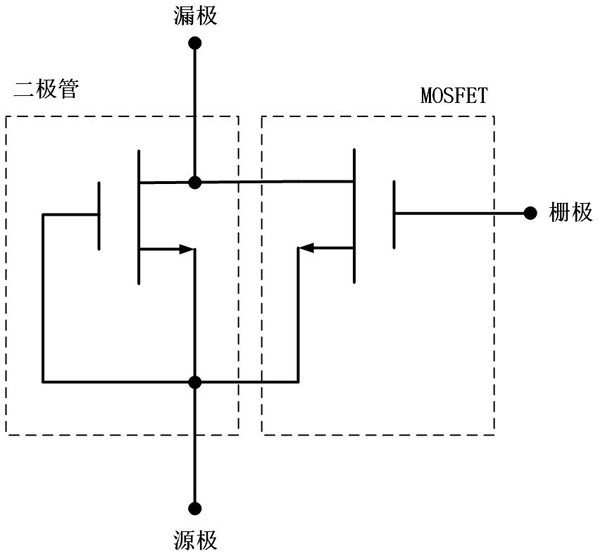

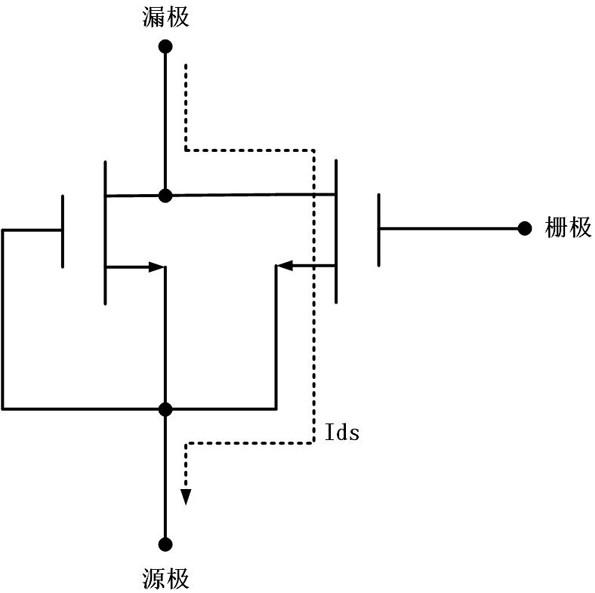

Double-sided Schottky controlled fast recovery diode device and preparation method

ActiveCN110416319ALarge speed changeHigh speedFinal product manufactureSemiconductor/solid-state device manufacturingReverse recoveryOhmic contact

The invention relates to a double-sided Schottky controlled fast recovery diode device and a preparation method. The fast recovery diode device comprises a semiconductor substrate, the semiconductor substrate comprises an N-type substrate and an N-type buffer layer, and an active region is arranged in the central area of the N-type substrate. On the cross section of the diode device, the active region comprises a number of alternately distributed active P-columns and active N-columns. Anode metal is arranged on the N-type substrate. The active P-columns are in ohmic contact with the anode metal on the N-type substrate, and the active N-columns are in Schottky contact with the anode metal on the N-type substrate. A number of alternately distributed cathode P- regions and cathode N+ regionsare arranged on the N-type buffer layer, the cathode N+ regions are in ohmic contact with cathode metal, and the cathode P- regions are in Schottky contact with the cathode metal. Fast reverse recovery can be realized, the dynamic loss can be reduced, the excellent softness can be improved, and the device has high reliability.

Owner:JIANGSU CAS IGBT TECHNOLOGY CO LTD

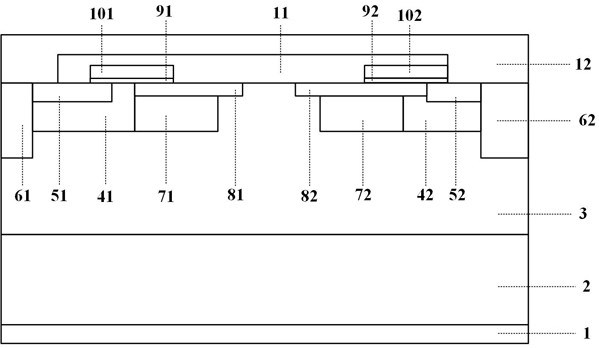

Semiconductor device with conduction voltage drop self-clamping and preparation method thereof

ActiveCN114883417ALimit inrush currentReduce dynamic lossSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialZener diode

The invention belongs to the technical field of power semiconductor devices, and particularly relates to a semiconductor device with conduction voltage drop self-clamping and a preparation method thereof. Compared with a traditional fast recovery diode structure, the Zener diode structure capable of achieving self-clamping voltage drop is integrated, the first N-type polycrystalline silicon and the first P-type polycrystalline silicon are longitudinally and alternately arranged on the upper portion in the groove, the second N-type polycrystalline silicon and the second P-type polycrystalline silicon are transversely and alternately arranged on the lower portion in the groove, the device is integrated with the Zener diode in reverse parallel connection, and therefore the device can achieve self-clamping voltage drop. When large surge current is generated, the Zener breakdown characteristic can be used for clamping conduction voltage drop, so that the device is prevented from being damaged; by arranging the inverted T-shaped groove between the body region and the P-type heavily doped region, the P-type heavily doped region with relatively shallow junction depth can be shielded in a dynamic reverse recovery process, so that the P-type heavily doped region is effectively protected, and a reverse bias safe working area (RBSOA) of the device is increased.

Owner:VANGUARD SEMICON CORP

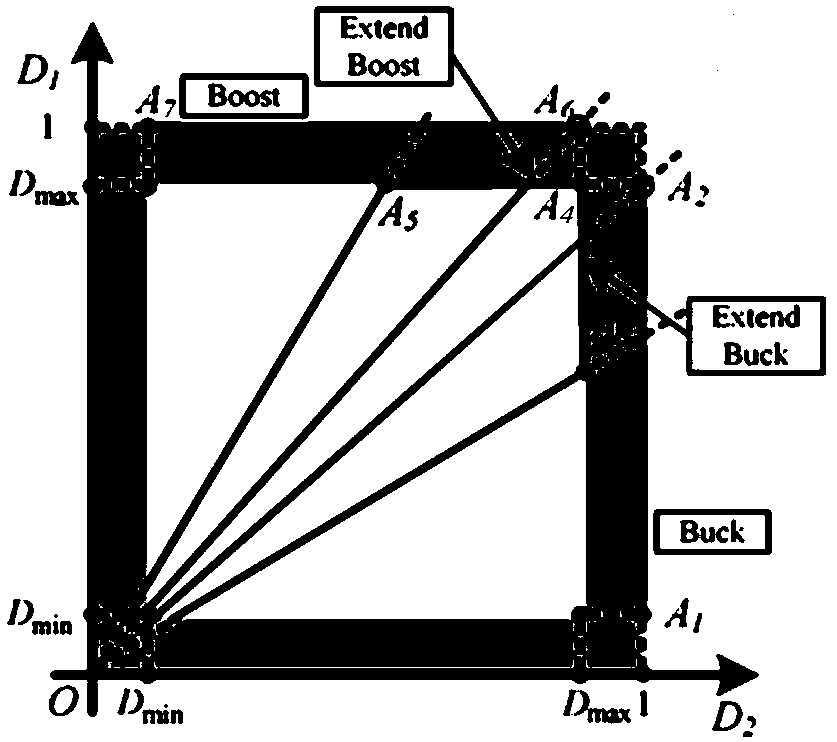

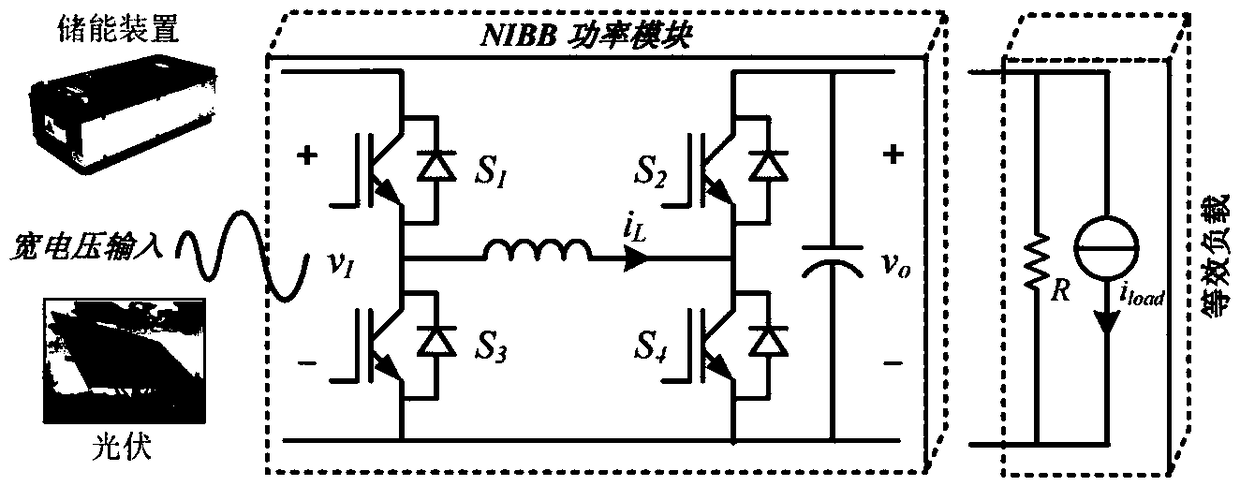

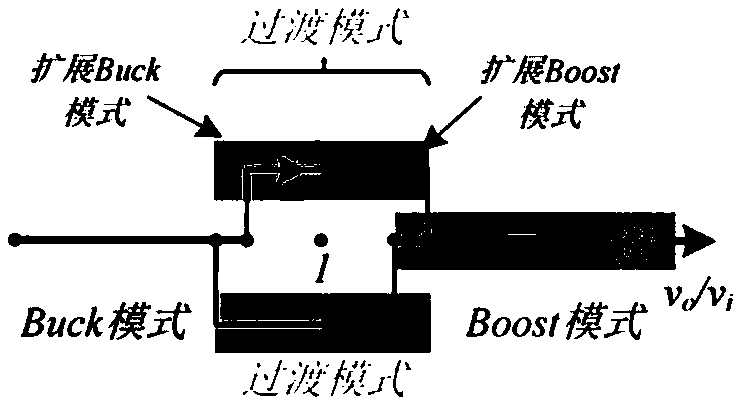

Unified mode control method for non-inverting Buck-Boost converter

InactiveCN108649796ALow costShorten the timeDc-dc conversionElectric variable regulationTransient stateDc dc converter

The invention provides a unified mode control method for a non-inverting Buck-Boost converter (NIBB). By establishing an average model and a unified mode control model of the NIBB, under the control of the unified mode, the input control amount is the equivalent duty ratio d, and the duty ratio is finally calculated by the Buck mode, the extended Buck mode, the extended Boost mode and the Boost mode. The working mode of the controller provided by the invention is completely determined by the equivalent duty ratio, and no additional input voltage sensor is needed compared with the discrete modecontrol, thereby reducing the system cost. The invention realizes flexible switching of each working mode of the converter under transient state, reduces the output settling time and recovery time ofthe controller, reduces the output voltage deviation, and improves the system dynamic performance, thereby reducing the number of active switches per cycle, reducing overall switching dynamic loss, and improving conversion effectiveness of a DC-DC converter compared with synchronous control.

Owner:SHANGHAI JIAO TONG UNIV

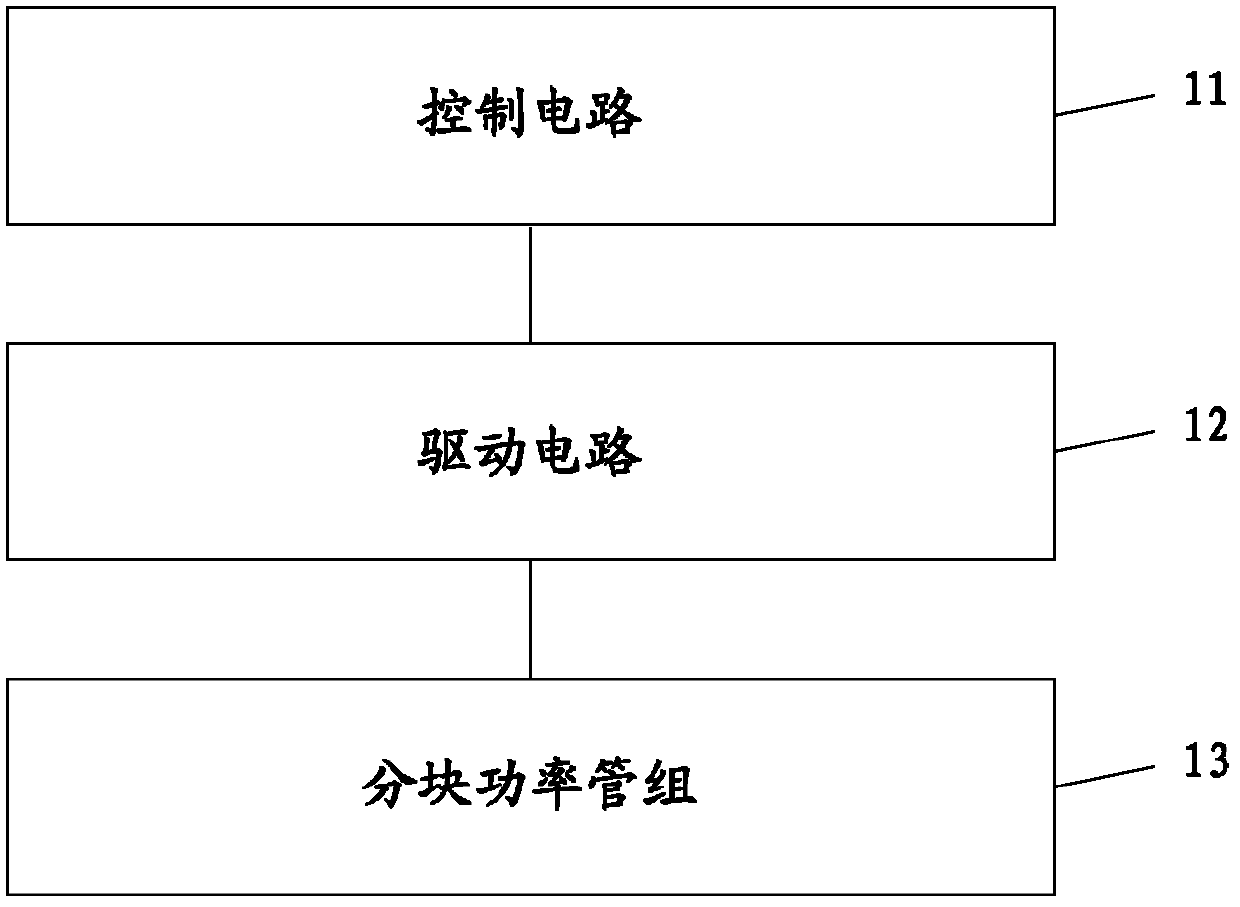

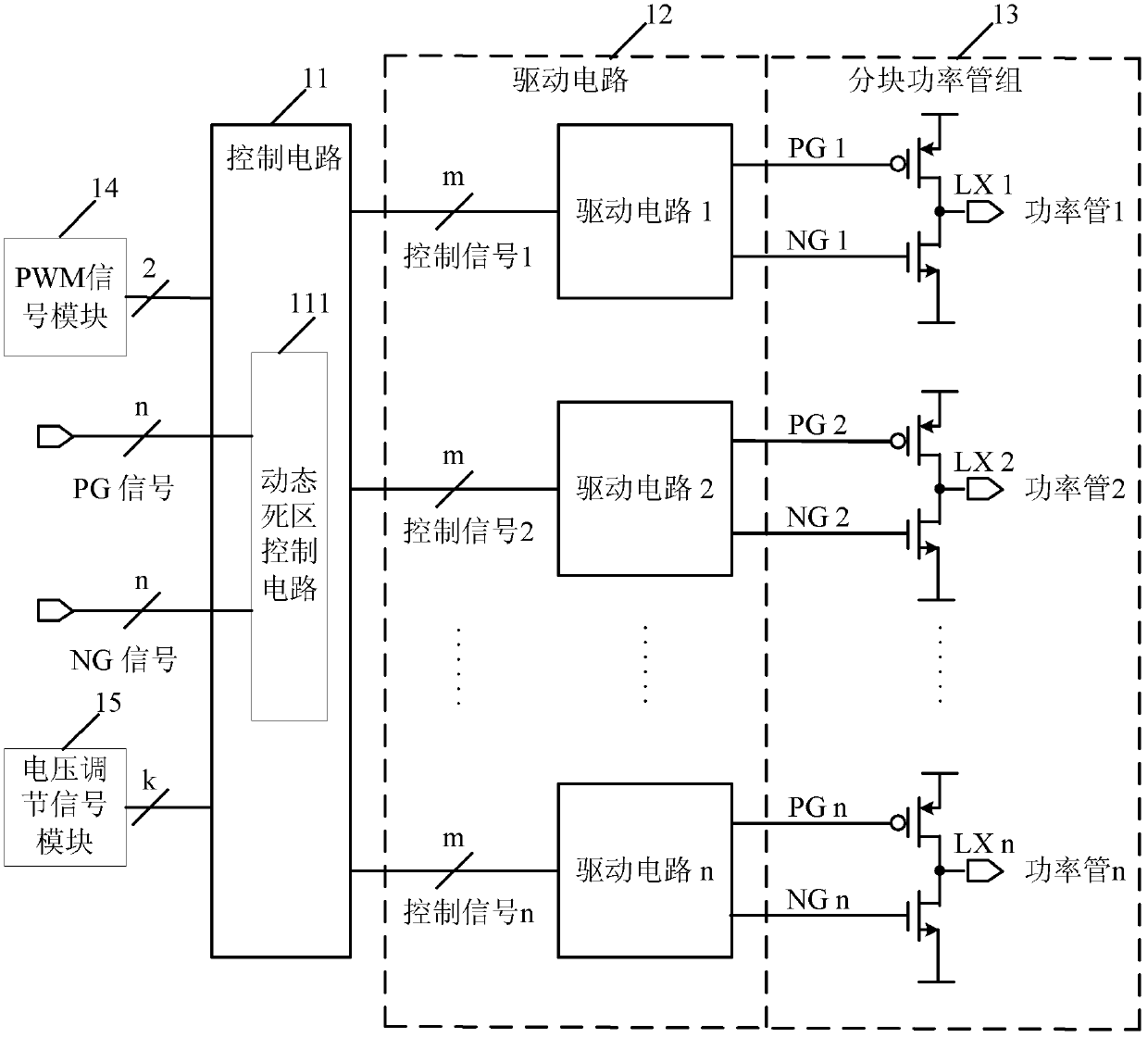

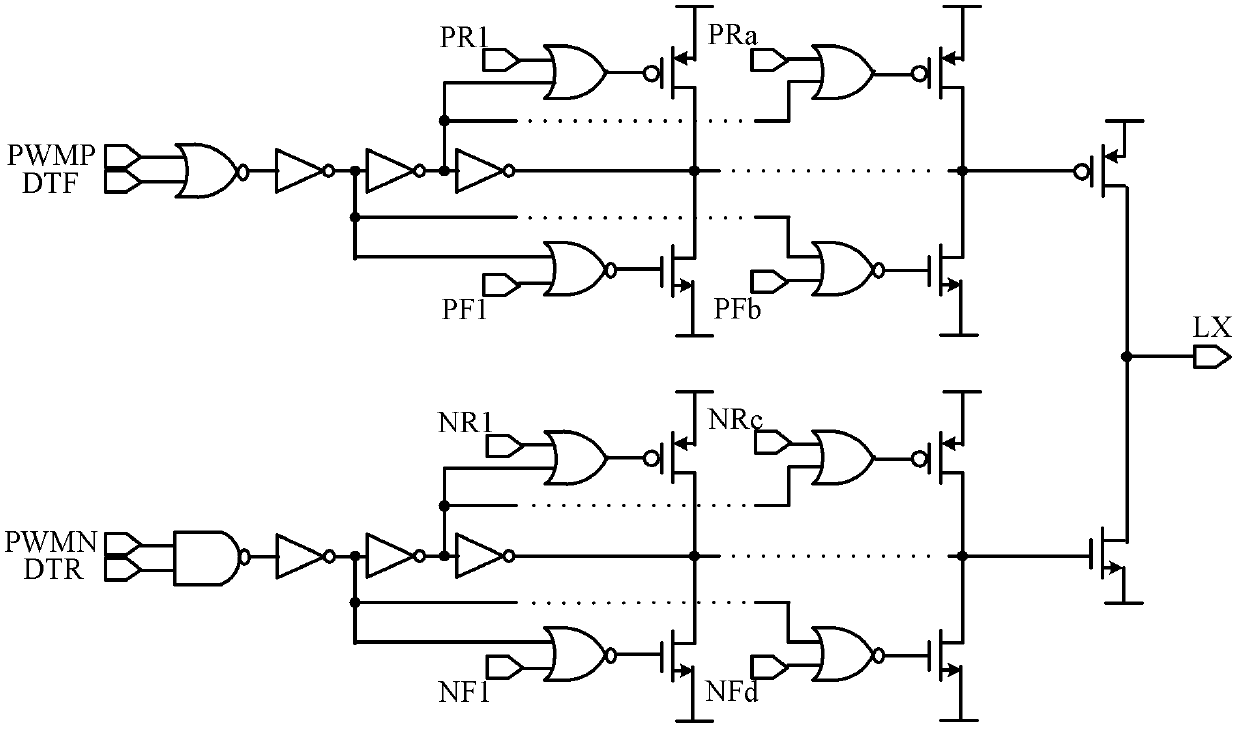

Block power tube circuit and mtehod for realizing same

ActiveCN102439832AImprove efficiencyReduce lossProgrammable logic circuit arrangementsDc-dc conversionControl signalVoltage regulation

The embodiment of the invention discloses a block power tube circuit and a method for realizing the same. The block power tube circuit comprises a control circuit used for adjusting the square wave duty ratio of a PWM signal according to a voltage adjustment signal to generate a PWMP signal, a PWMN signal and a control signal m; a drive circuit of which a PWMP signal end and a PWMN signal end receive the PWMP signal and PWMN signal sent by the control circuit to generate a drive signal PG and a drive signal NG to control the power tube to control the opening and closing states of a PMOS power tube and an NMOS power tube; a block power tube group comprising at least one power tube pair, wherein, each power tube pair comprises a PMOS power tube and an NMOS power tube, the input ends of the PMOS power tube and the NMOS power tube receive the PG signal and NG signal sent by the drive circuit respectively. The invention is suitable for being used in a switch power supply.

Owner:HUAWEI TECH CO LTD

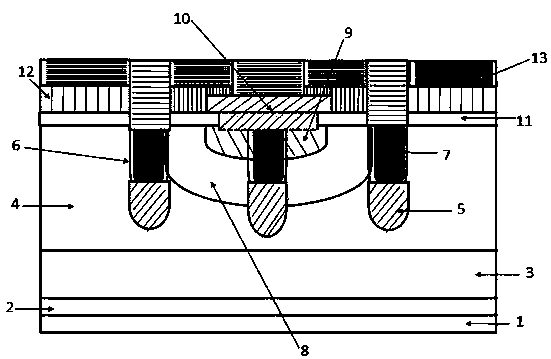

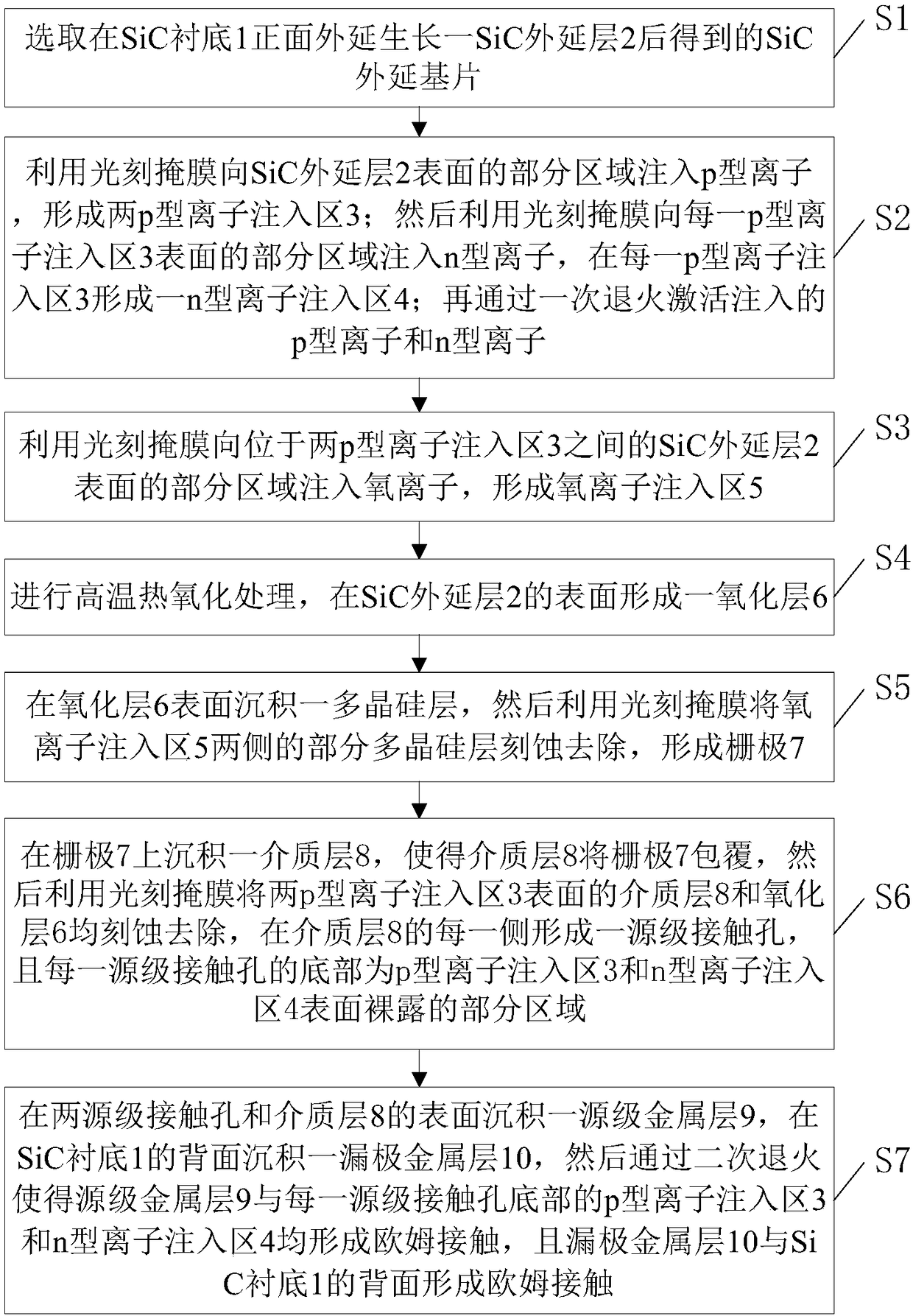

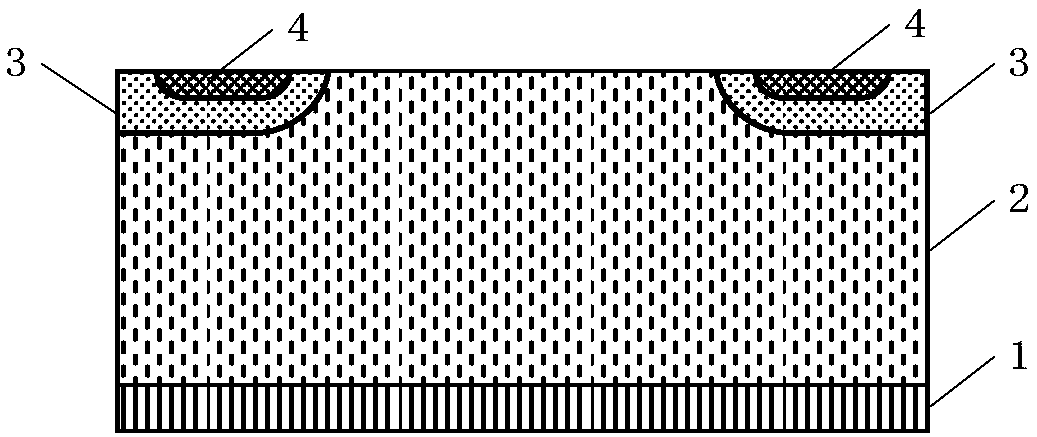

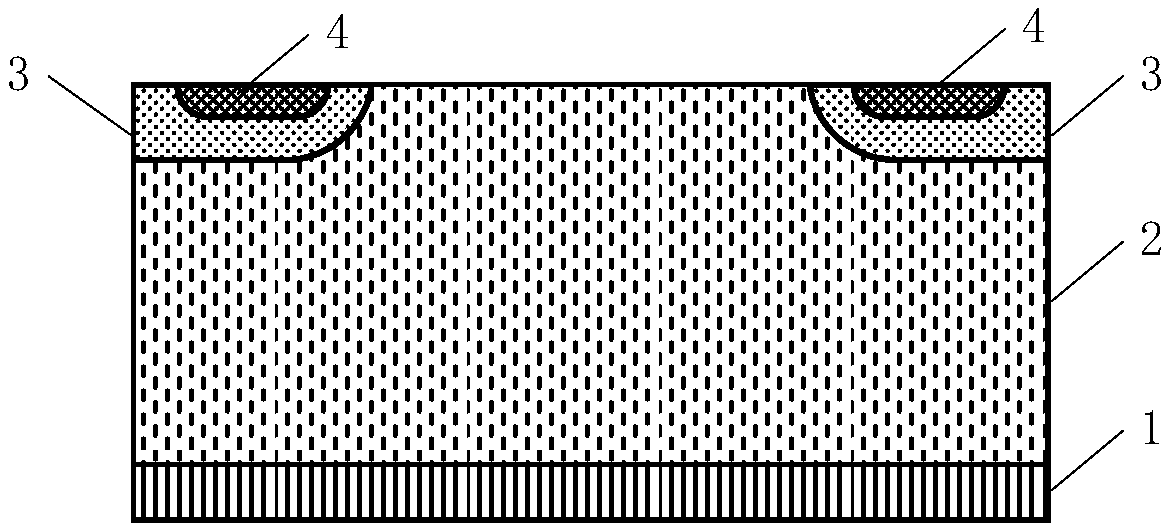

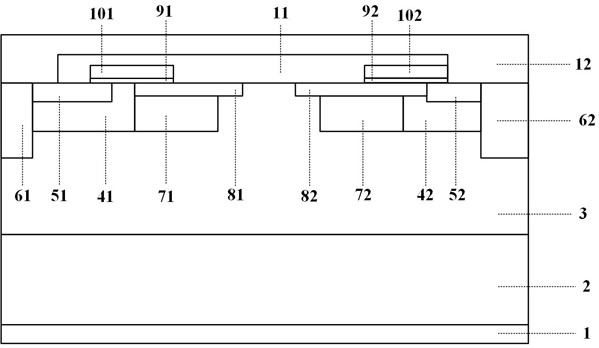

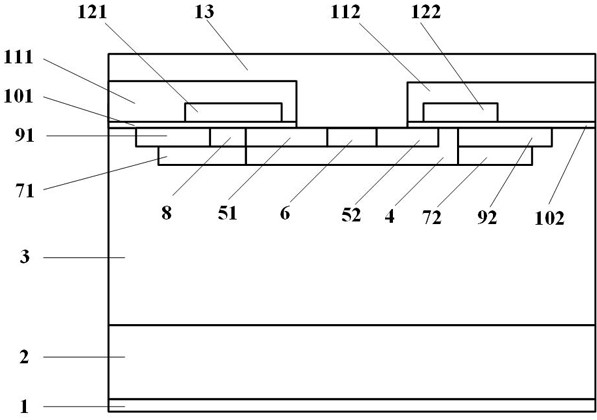

SiC-based DI-MOSFET preparation method and SiC-based DI-MOSFET

InactiveCN108257872AIncreasing the thicknessReduce gate-to-drain capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETCapacitance

The invention discloses a SiC-based DI-MOSFET preparation method and the SiC-based DI-MOSFET. The SiC-based DI-MOSFET comprises a SiC epitaxial substrate, two p-type ion implantation regions (3) and two n-type ion implantation regions (4) formed on the surface of a SiC epitaxial layer (2), an oxide layer (6), a grid (7) covering the surface of the oxide layer (6), a dielectric layer (8) wrapping the grid (7), a source metal layer (9) covering surfaces of two source contact holes and the dielectric layer (8), and a drain metal layer (10) covering the back surface of a SiC substrate (1), whereineach n-type ion implantation region (4) is arranged in each p-type ion implantation region (3), thickness of the oxide layer (6) between the two p-type ion implantation regions (3) is greater than thickness of the oxide layer (6) at other regions, two sides of the dielectric layer (8) are respectively provided with one source contact hole, and the drain metal layer (10) and the SiC substrate (1)are in ohmic contact. The SiC-based DI-MOSFET is advantaged in that gate leakage capacitance of devices can be reduced.

Owner:BEIJING PINJIE ELECTRONICS TECH CO LTD

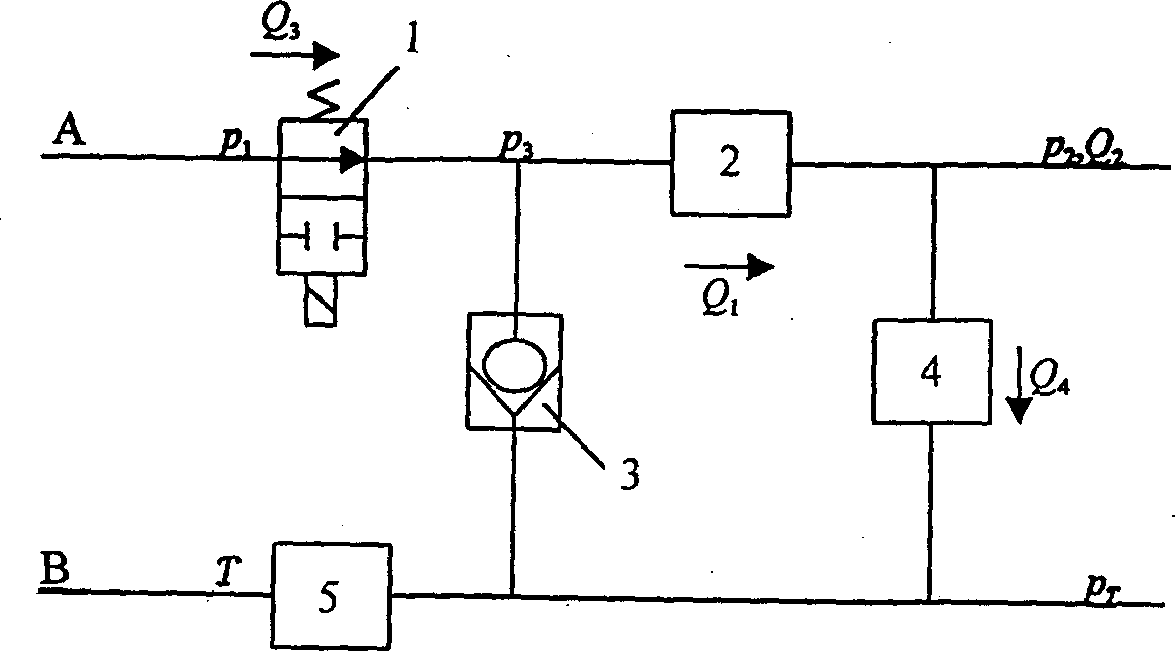

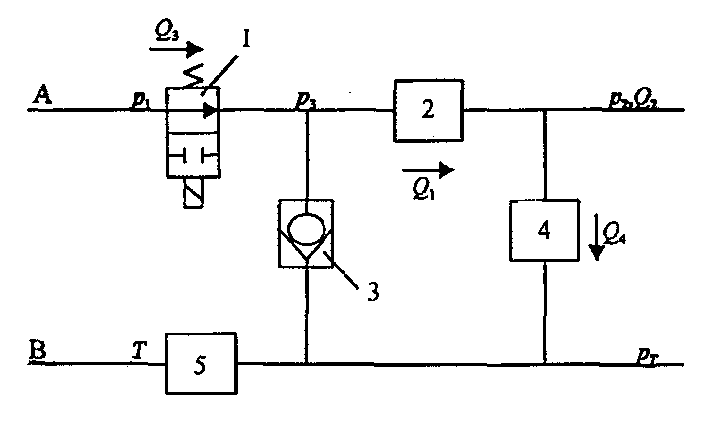

Pressure-reducing and flow rate-increasing swtich liquid pressure source with oil returning back pressure

InactiveCN1375640ASmall pressure fluctuationsReduce dynamic lossFluid-pressure convertersPressure decreaseEngineering

The present invention discloses a pressure-decreasing flow-increasing type switch hydraulic source with oil-returning backpressure, which is characterized by that the high-speed switch valve and liquid inductance element are series-connected on the hydraulic main line oil supply pipeline, the backpressure valve is connected on the hydraulic main line oil-returning pipeline, the non-return valve and liquid volume element are respectively cross-connected between the hydraulic main line oil supply pipeline and oil-returning pipeline, the output end of the non-return valve is connected with output end of high-speed switch valve and input end of liquid inductance element, and the input end of liquid volume element is connected with output end of liquid inductance element, and the output end ofnon-return valve and output end of liquid volume element are connected with input end of backpressure valve.

Owner:ZHEJIANG UNIV

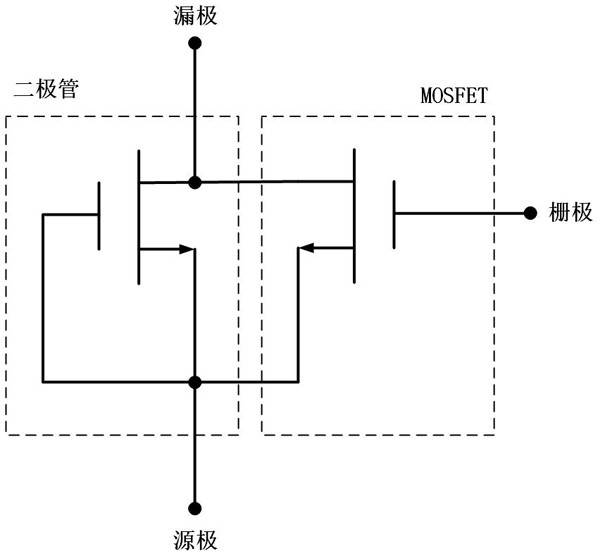

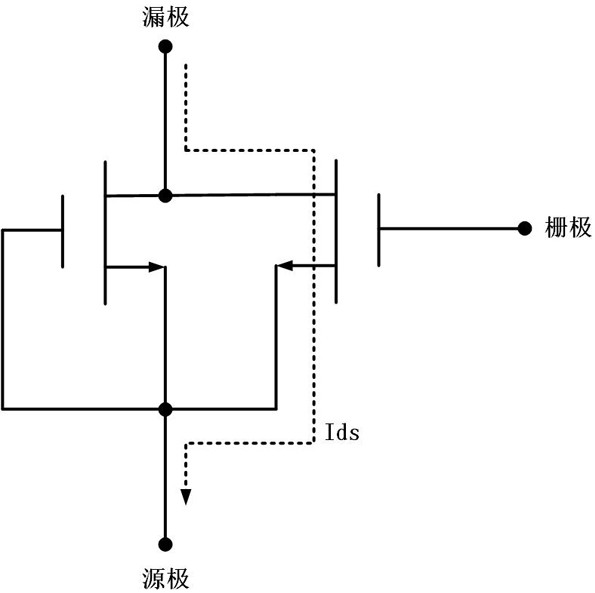

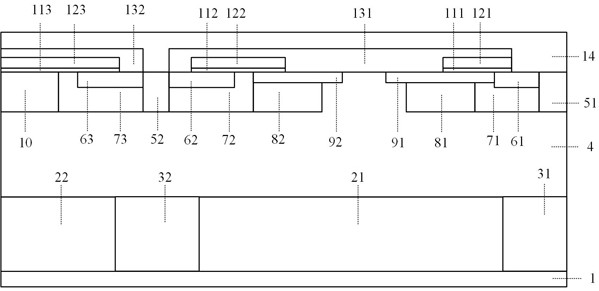

Silicon carbide separation gate MOSFET cell of integrated gate-controlled diode and preparation method thereof

ActiveCN114551586AReduced Miller CapacitanceReduce switching lossesEfficient power electronics conversionSemiconductor/solid-state device manufacturingMOSFETEngineering

The invention relates to a silicon carbide separation gate MOSFET (Metal-Oxide-Semiconductor Field Effect Transistor) cell integrated with a gate-controlled diode and a preparation method thereof, belonging to the technical field of power semiconductor devices. The MOSFET adopts a separation gate design to reduce the switching loss of the device; in order to solve the problem that the reliability of gate oxide is reduced due to a separation gate structure, a P-type buried layer is added to reduce the electric field intensity of a gate oxide layer at the edge of polycrystalline silicon; an N-type diversion layer is added, and current is introduced into a drift region of the device from a channel; in order to reduce the conduction voltage drop of a parasitic body diode of the silicon carbide MOSFET so as to reduce the reverse recovery current of the body diode, a grid control diode based on an accumulation type channel MOS structure is introduced to the other side of a cell of the MOSFET. According to the invention, the accumulation type channel is adopted to fully reduce the conduction loss of the diode, and the source electrode metal is in contact with the polycrystalline silicon of the grid control diode on the side wall by etching and filling the metal, so that the cell size is reduced.

Owner:NOVUS SEMICON CO LTD

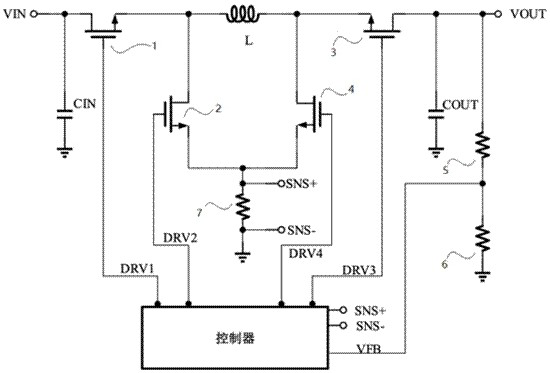

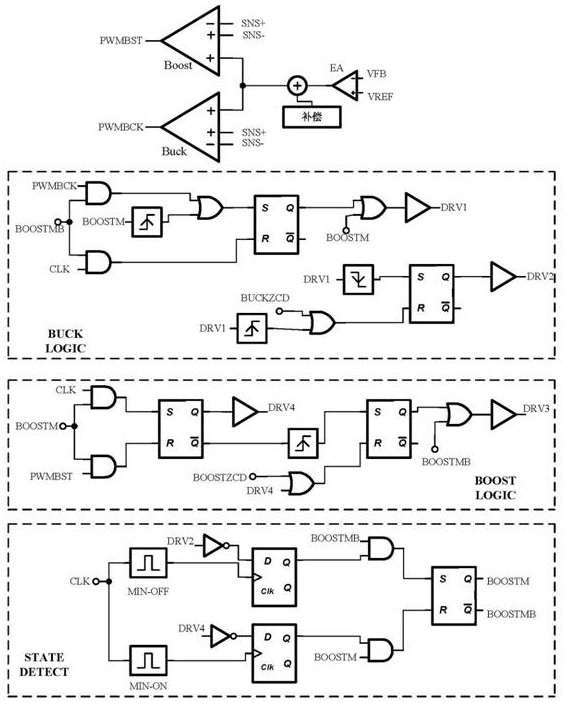

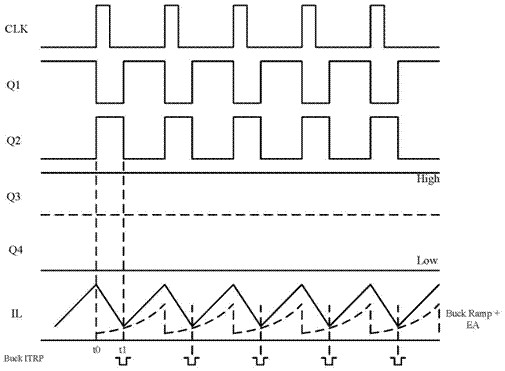

Buck-boost controller based on current mode

ActiveCN112072916AReduce dynamic lossAdjust MIN-ONEfficient power electronics conversionDc-dc conversionBoost controllerHemt circuits

A buck-boost controller based on a current mode comprises a controller, a voltage feedback loop and a current sampling circuit, a drain electrode of a first switch tube is connected with a VIN input signal, a grid electrode of the first switch tube is connected with a DRV1 signal of the controller, and a source electrode of the first switch tube is connected with a drain electrode of a second switch tube; a drain electrode of a third switch tube is connected with a VOUT output signal, a grid electrode of the third switch tube is connected with a DRV3 signal of the controller, and a source electrode of the third switch tube is connected with a drain electrode of a fourth switch tube; the source electrode of the second switch tube and the source electrode of the fourth switch tube are connected with a current sampling resistor, and the grid electrode of the second switch tube is connected with a DRV2 signal of the controller; and the grid electrode of the fourth switching tube is connected with a DRV4 signal of the controller. According to the invention, smooth seamless switching from voltage boosting to buck-boost to voltage boosting is realized.

Owner:SHENZHEN INJOINIC TECH

Cascade active voltage-stabilizing controller of power switch

InactiveCN100530881CWide range of choicesStrong pressure equalization control abilityEmergency protective circuit arrangementsControl signalEqualization

The active series voltage equalization control device of the power switch is characterized in that for each power module working in series, an active voltage equalization absorption module is provided, and the active voltage equalization absorption module is connected in parallel across C, Terminal E: a drive control module is set, and the output control signals of the drive control module are respectively connected to each power module and the active voltage equalization absorption module. The invention adopts active control, and has the advantages of low power consumption, reliable voltage equalization, strong discrete adaptability of power switches, simple circuit and the like.

Owner:HEFEI UNIV OF TECH

Novel optical MOS relay

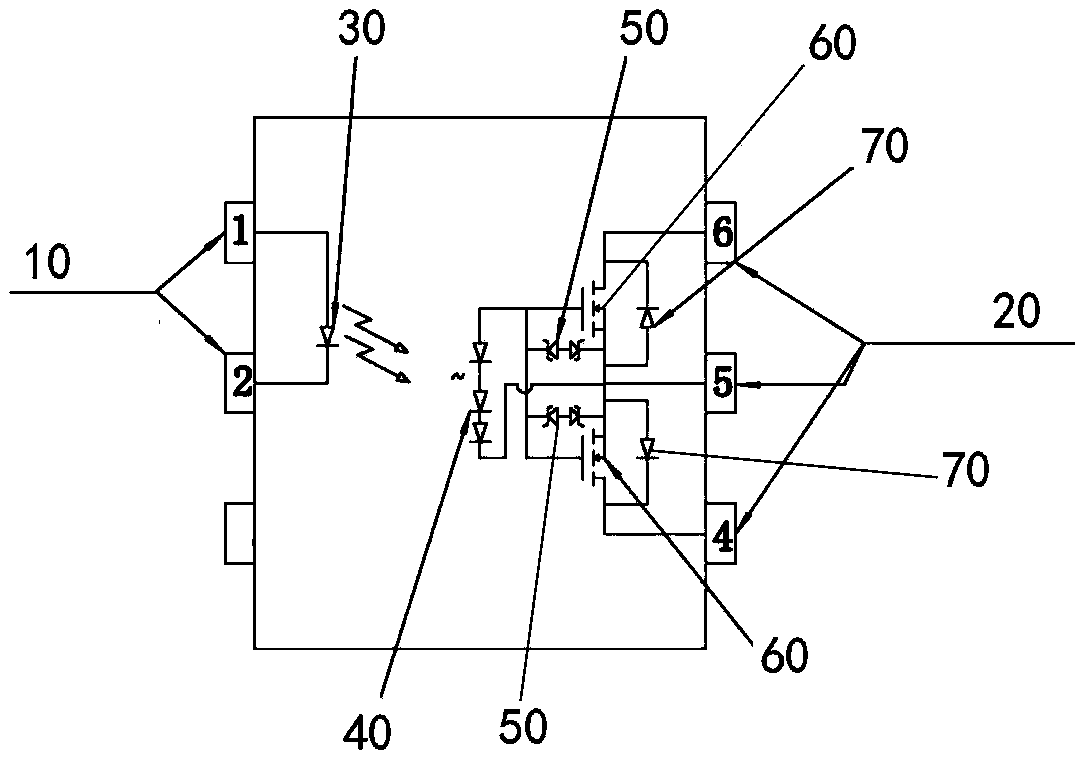

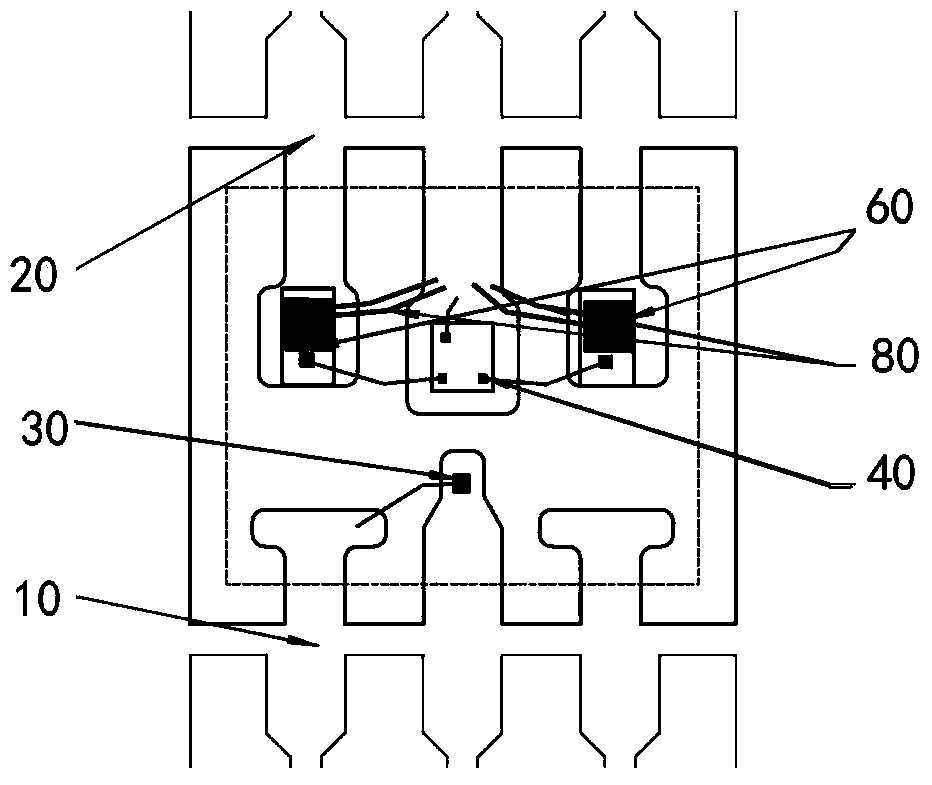

InactiveCN104184445AAvoid defectsImprove antistatic performanceElectronic switchingMOSFETReverse recovery

The invention provides a novel optical MOS relay. The novel optical MOS relay is characterized in that an input end is composed of an infrared LED, a pin 1 of the input end is connected with the positive pole of the infrared LED, and a pin 2 of the input end is connected with the negative pole of the infrared LED; an output end is composed of a PDA and an MOSFET integrated with an ESD and a reverse recovery diode, the positive pole of the PDA is connected with the G pole of the MOSFET, and the negative pole of the PDA is connected with the S pole of the MOSFET; the D pole of the MOSFET is connected with a pin 4 and a pin 6 of the output end, and the S pole of the MOSFET is connected with a pin 5 of the output end; the infrared LED, the PDA, the MOSFET, the ESD and the reverse recovery diode are all located in the same plane; the input end and the output end are formed by encapsulating an inner encapsulating material and an outer-layer black encapsulating material which are made of transparent or semitransparent resin. According to the optical MOS relay, the antistatic capacity is improved, withstand voltage of media between the input end and the output end is improved, on-state and switching losses are greatly reduced, and the switching speed is also increased.

Owner:XIAMEN SILICON TOP OPTO ELECTRONICS CO LTD

Method for preparing vertical double-diffusion MOS transistor

ActiveCN101719472BIncrease the doping concentrationThickness is easy to controlSemiconductor/solid-state device manufacturingCapacitanceDouble diffusion

The invention relates to a method for preparing a vertical double-diffusion MOS transistor, which comprises the following steps: firstly, simultaneously growing thick insulating layers at a position beside a channel region on the surface of an epitaxial layer in the horizontal direction and on a buffering isolation oxide layer of a device layer at the position; and secondly, finishing the preparations of a source electrode, a drain electrode and a grid electrode of the vertical double-diffusion MOS transistor by adopting a conventional process method. The introduction of the thick insulating layers increases the relative distance between a polysilicon gate and the epitaxial layer, namely increases the distance two pole plates of a grate-drain capacitor, so under the condition of not changing the polysilicon grate area and not increasing the on-resistance of a device, the method effectively reduces the grate-drain capacitance of the device, greatly shortens the time for charging and discharging the grate-drain capacitor in the switching process of the MOS transistor, improves the switching speed of the MOS transistor, reduces the dynamic loss of the MOS transistor, and greatly improves the performance of the device.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

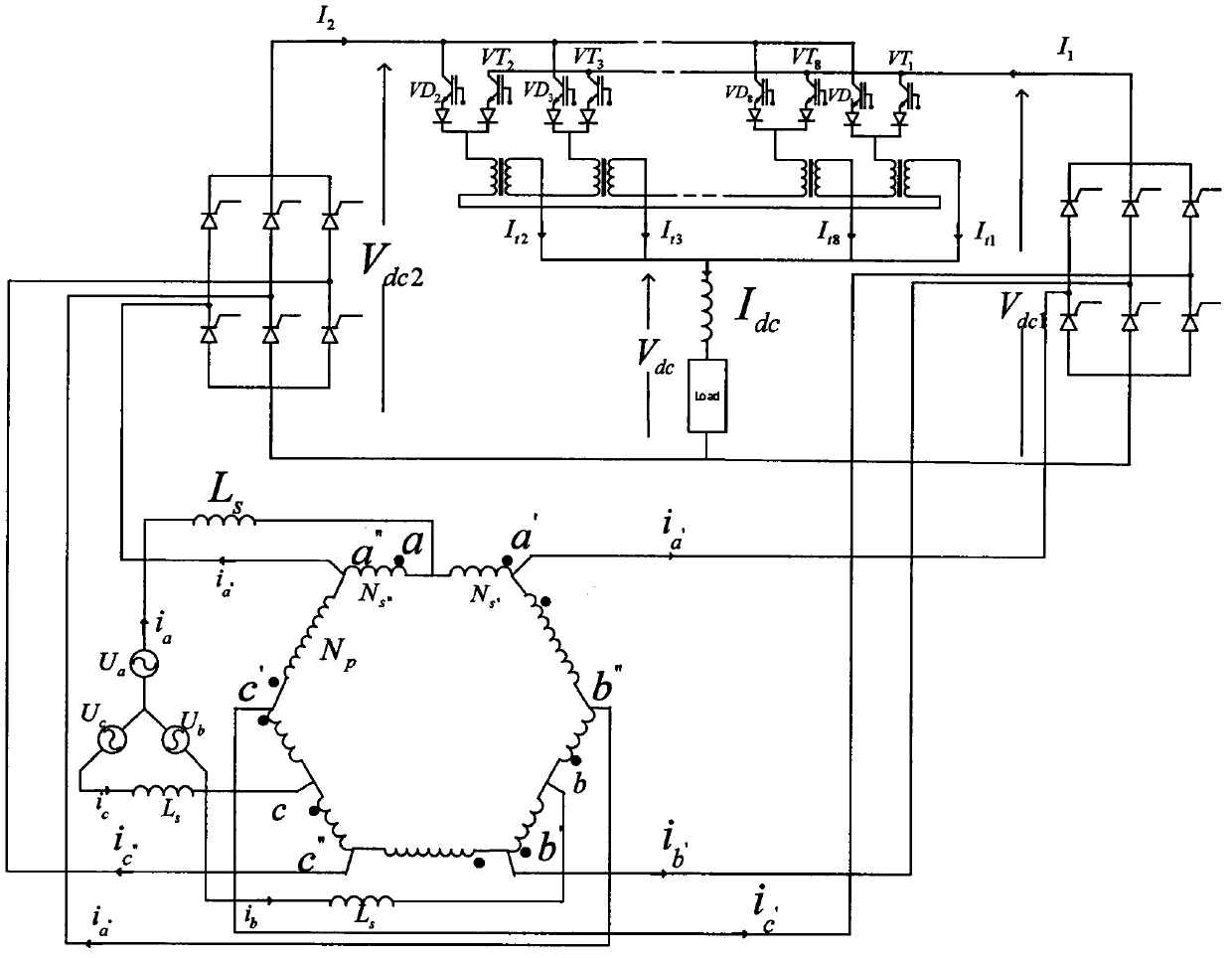

Directly-driven wind power generation system and mode for modulating SPWM inversion control signal in system

InactiveCN101599649BSimple designEasy to controlAc-dc conversionSingle network parallel feeding arrangementsControl signalFull bridge

The invention relates to a directly-driven wind power generation system and a mode for modulating an SPWM inversion control signal in the system. The directly-driven wind power generation system is characterized in that a high-inductance permanent magnet synchronous generator is arranged and coaxially connected with a wind turbine; an alternating current signal output end of the high-inductance permanent magnet generator is connected in series with a triphase uncontrollable rectifier; direct current output by the triphase uncontrollable rectifier is used as an input signal of a subsequent current type inverter; an output signal of the current type inverter is filtered by a wave filter and fed to an alternating current network as sinusoidal current; the current type inverter consists of a fully-controlled power electronic switch and a current source type full-bridge inverting circuit; and the fully-controlled power electronic switch uses a sinusoidal pulse-width modulating signal SPWM as a control signal. Under the condition of a low wind speed, the directly-driven wind power generation system can also generate power without needing a direct current capacitor of the convertor, simplifies a controlling system, improves the generating efficiency of the whole machine and reduces the cost.

Owner:HEFEI UNIV OF TECH

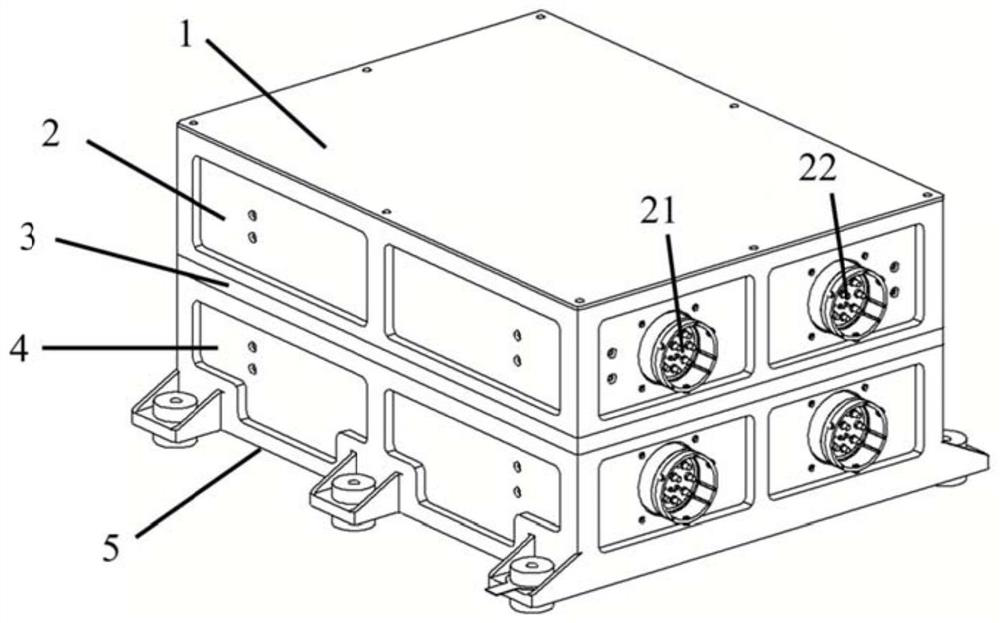

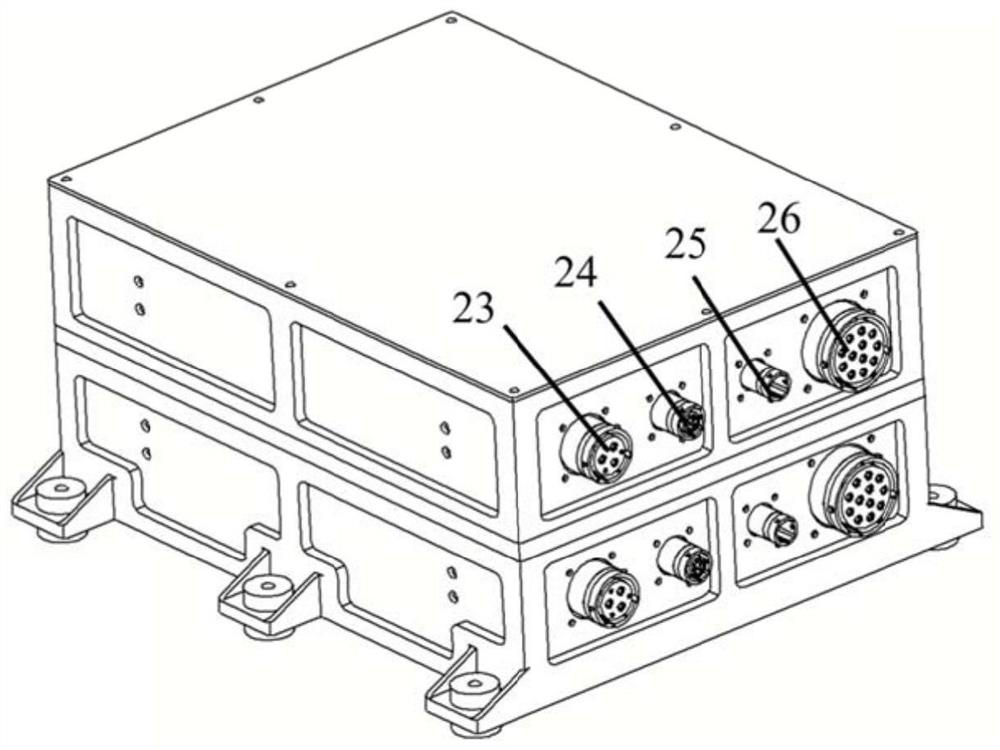

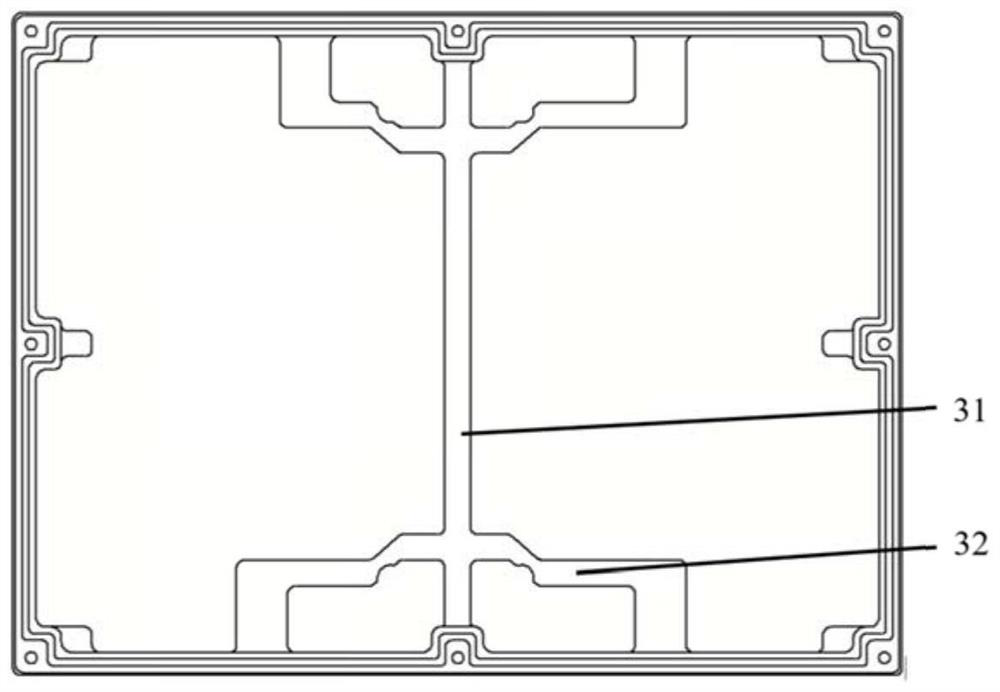

Dual-redundancy 270V high-voltage high-power load monitoring device

ActiveCN112822899ASolve the cooling problemEasy to installCircuit arrangements on support structuresModifications by conduction heat transferOff timeMonitor unit

The invention provides a dual-redundancy 270V high-voltage high-power load monitoring device, which comprises an upper-layer shell, a first load monitoring unit, a partition plate, a second load monitoring unit and a lower-layer shell, and is characterized in that the first load monitoring unit and the second load monitoring unit are of dual-redundancy design; a supporting structure extending to the middle of the shell and used for fixing a printed board of the first load monitoring unit are processed on a side plate, close to the partition plate, of the upper-layer shell; the partition plate is in direct contact with the power device on the printed board to implement heat conduction; a supporting structure extending towards the middle of the shell is processed on a side plate, close to a bottom plate, of the bottom of the lower-layer shell and used for fixing a printed board of the second load monitoring unit, and the bottom plate of the lower-layer shell is in direct contact with a power device on the printed board to implement heat conduction; and the first load monitoring unit and the second load monitoring unit control the power distribution switch by adopting a driving circuit with controllable on-off time. The load monitoring device is used for high-voltage and high-power distribution, and solves the problems of insufficient driving technology and poor heat dissipation capability.

Owner:CHINA AEROSPACE TIMES ELECTRONICS CORP

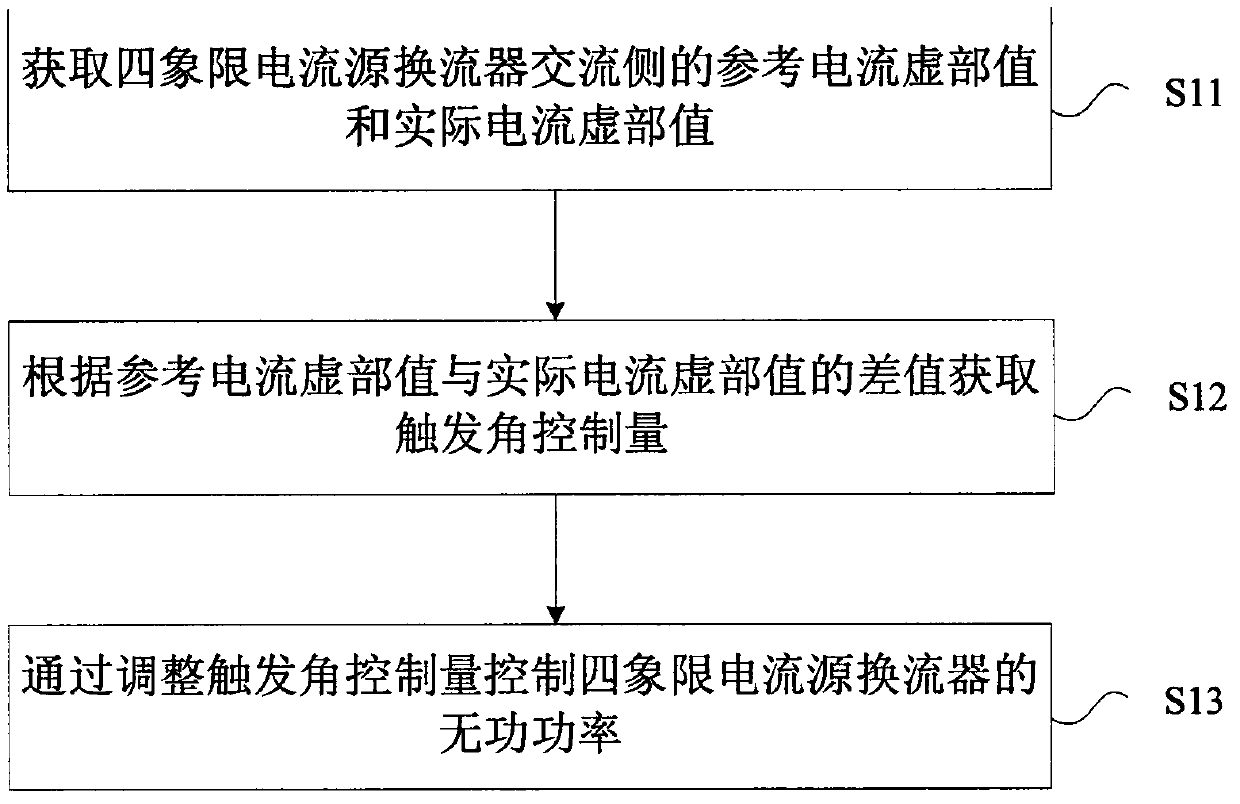

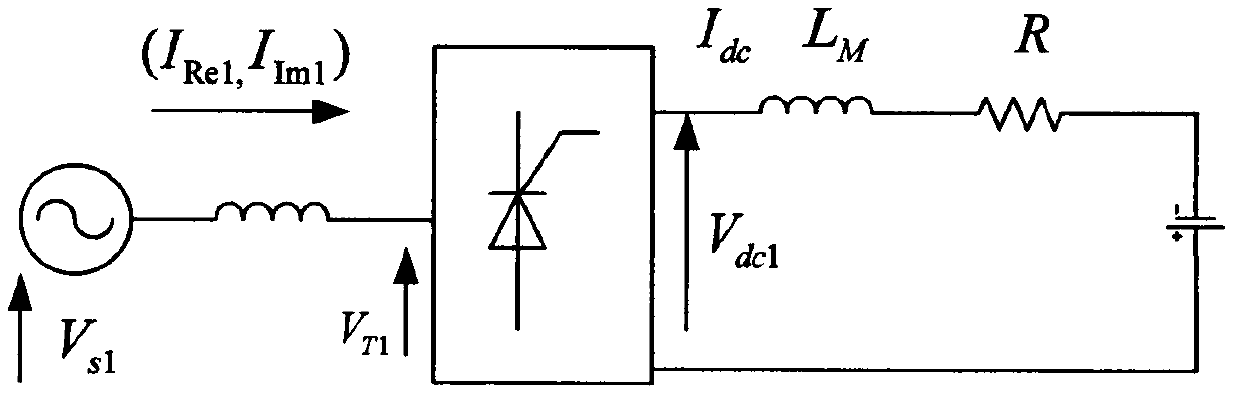

Reactive power control method and device for a four-quadrant current source converter

ActiveCN106058881BReduce dynamic lossSolve the stressReactive power adjustment/elimination/compensationReactive power compensationFour quadrantsReference current

Owner:GLOBAL ENERGY INTERCONNECTION RES INST CO LTD +2

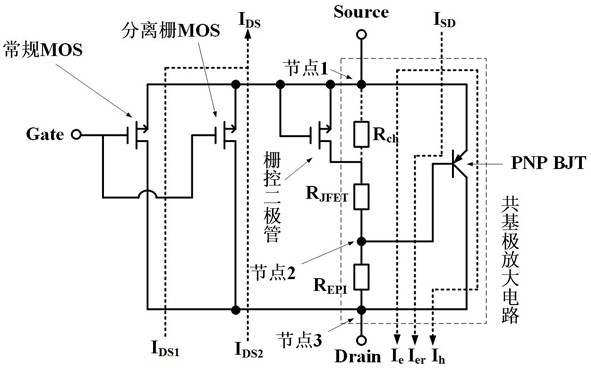

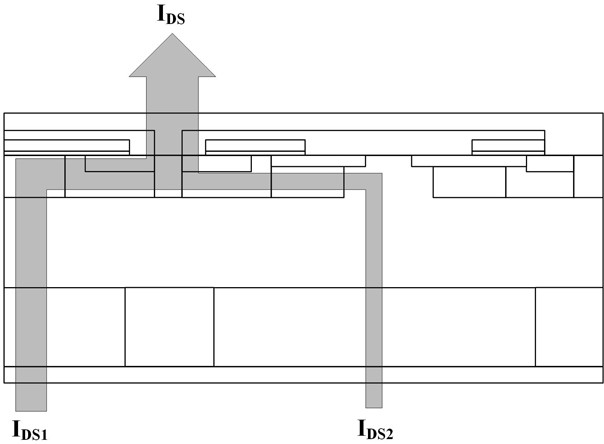

Silicon carbide mosfet with integrated gated diode for high surge current capability

ActiveCN114551601BReduced Miller CapacitanceReduce switching lossesEfficient power electronics conversionSemiconductor devicesCarbide siliconPower semiconductor device

The invention relates to a silicon carbide MOSFET with high anti-surge current capability and integrated gate-controlled diode, which belongs to the technical field of power semiconductor devices. As the withstand voltage of silicon carbide power devices becomes higher and higher, the drift region becomes thicker and thicker, which makes more and more minority carriers recombine in the drift region during the bipolar conduction process of the PIN to form a recombination current. It will all be borne by the channel of the gated diode, which will greatly reduce the reliability of the gate oxide layer of the gated diode. In order to alleviate this problem, a parallel PNP BJT is integrated for the gated diode, and the reverse-biased PN junction is used to reduce the effective base region thickness and reduce the recombination of minority carriers in the base region, that is, reduce the generation of recombination current and alleviate the wave The current density of the channel region in the surge state improves the overall surge current resistance capability of the device.

Owner:NOVUS SEMICON CO LTD

Silicon carbide split gate mosfet with integrated high-speed freewheeling diode and preparation method

ActiveCN114122123BReduced Miller CapacitanceReduce switching lossesTransistorSolid-state devicesMOSFETElectrical field strength

The invention relates to a silicon carbide split-gate MOSFET integrated with a high-speed freewheeling diode and a preparation method thereof, belonging to the technical field of power semiconductor devices. The MOSFET of the present invention adopts the design of the split gate to reduce the switching loss of the device. In order to prevent the gate oxygen reliability problem caused by the split gate structure, a P-type buried layer is added to reduce the electric field intensity of the polysilicon edge gate oxide layer. Furthermore, an N-type conduction layer is added to introduce current from the channel to the drift region of the device. In addition, in order to reduce the turn-on voltage drop of the silicon carbide MOSFET parasitic body diode and introduce a unipolar conduction mode, a high-speed freewheeling diode based on a MOS structure is introduced on the other side of the MOSFET cell. Compared with the traditional method, the present invention The high-speed freewheeling diode uses the surface tailing of the P-type buried layer to form a channel region, that is, the conduction voltage drop of the high-speed freewheeling diode is reduced as much as possible without adding additional versions.

Owner:NOVUS SEMICON CO LTD

A Reverse Conduction IGBT Gate Pre-Desaturation Driving Method Based on Current Threshold Judgment

ActiveCN108390547BAvoid Oscillating PhenomenaEasy to operateEfficient power electronics conversionElectronic switchingSystem capacityAverage current

The invention relates to a reverse conduction type IGBT gate pre-desaturation driving method based on current threshold judgment, using an external power MOSFET in the reverse conduction type IGBT gate to achieve flexible conversion of the drive level, and the drive circuit can be monitored in real time The operation mode of the reverse conduction IGBT, and the average current flowing through the circuit is obtained through the current measurement method, so as to judge whether it is necessary to change the gate voltage to optimize the dynamic and static characteristics of the internal integrated diode of the reverse conduction IGBT, thereby reducing the three-phase The dynamic and static loss of the inverter system can improve the system efficiency. After calculation, applying this pre-desaturated gate drive circuit to the three-phase inverter can increase the system capacity by about 30% while keeping the volume unchanged. Reducing 10%-15% loss release, 1MW class three-phase inverter can save 10%-12% of electric energy.

Owner:BEIJING JIAOTONG UNIV

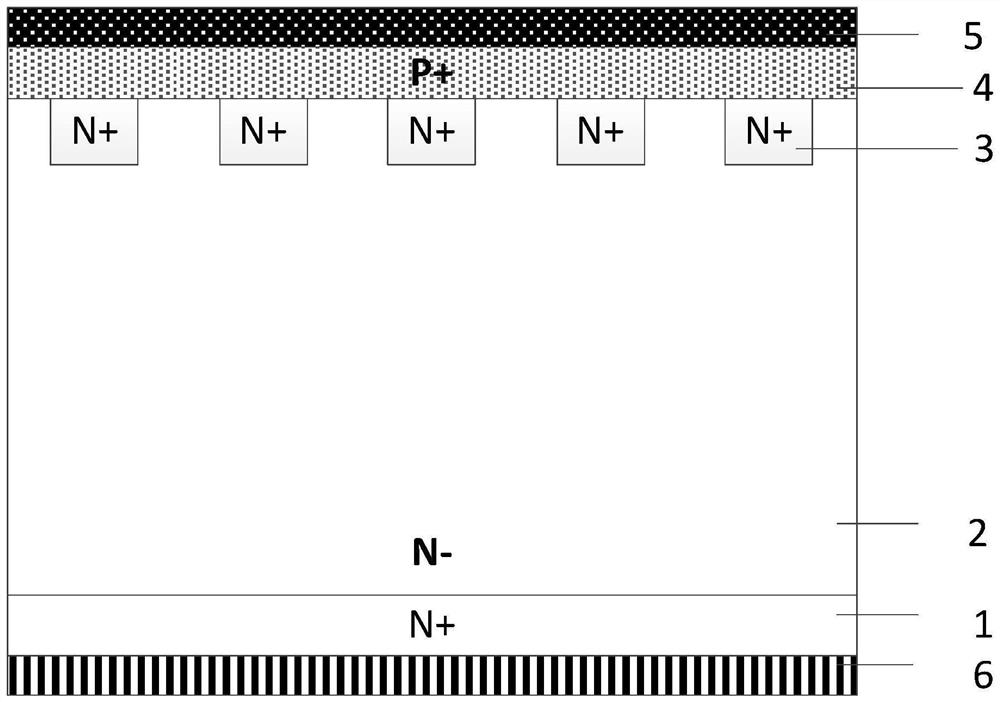

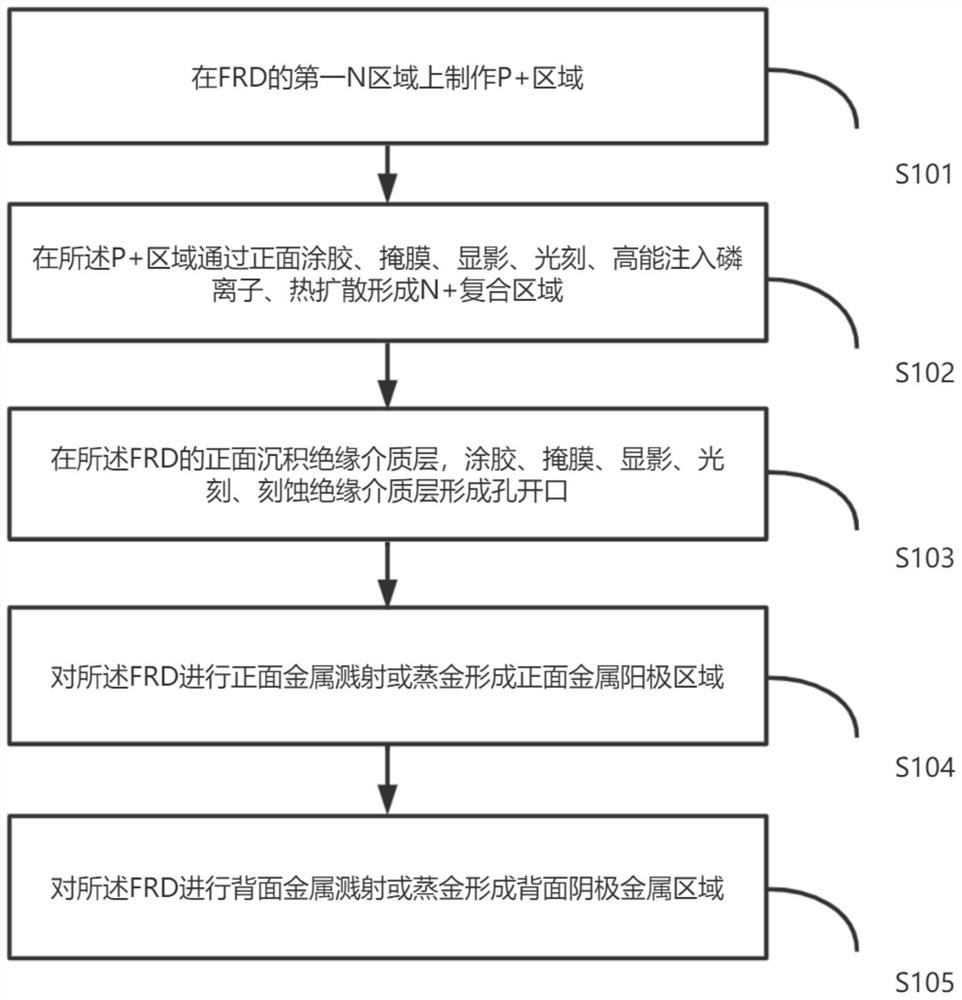

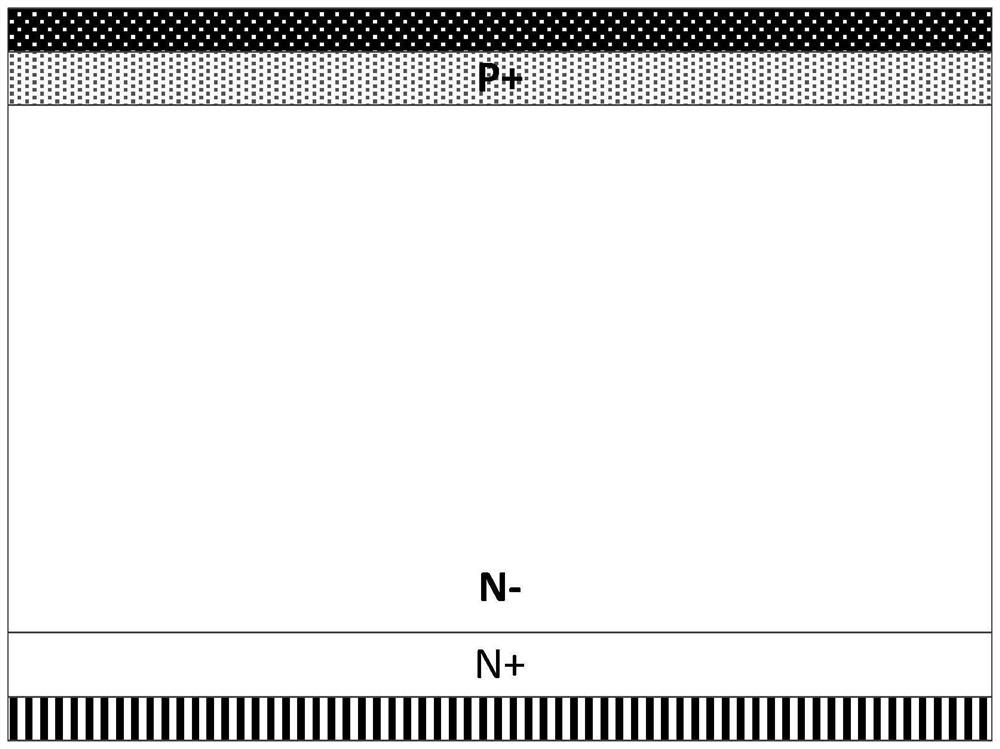

FRD device structure manufacturing method

PendingCN114823921AReduce dynamic lossReduced injection efficiencySemiconductor/solid-state device manufacturingSemiconductor devicesMaterials sciencePhysics

The invention provides an FRD device structure. The FRD device structure comprises a first N region, a P + region, an N + composite region, a front anode metal region and a back cathode metal region, the first N region comprises a first N + region and a first N-region; the first N-region is located above the first N + region; the P + region is located on the first N-region; the N + composite region is located in the first N-region; the front anode metal region is located on the P + region; and the back cathode metal region is located below the first N + region. On the premise of not reducing the concentration of the front P-type region, the N + composite region is introduced to reduce the front hole injection efficiency, so that the dynamic loss of the device is reduced.

Owner:上海埃积半导体有限公司

Silicon carbide split gate mosfet cell with integrated gated diode and preparation method

ActiveCN114551586BReduced Miller CapacitanceReduce switching lossesEfficient power electronics conversionSemiconductor/solid-state device manufacturingEngineeringMaterials science

The invention relates to a silicon carbide split gate MOSFET cell with integrated gate control diode and a preparation method thereof, belonging to the technical field of power semiconductor devices. The MOSFET of the present invention adopts the design of split gate to reduce the switching loss of the device; In order to reduce the reliability of the gate oxide caused by the structure, a P-type buried layer is added to reduce the electric field strength of the polysilicon edge gate oxide layer; an N-type conduction layer is added to introduce the current from the channel to the drift region of the device; In order to reduce the turn-on voltage drop of the parasitic body diode of the SiC MOSFET to reduce the reverse recovery current of the body diode, a gated diode based on the accumulation channel MOS structure is introduced on the other side of the MOSFET cell. The invention adopts the accumulation type channel to fully reduce the conduction loss of the diode, and makes the source metal contact the polysilicon of the gated diode on the sidewall by etching and filling the metal, thereby reducing the cell size.

Owner:NOVUS SEMICON CO LTD

Heteropolar Permanent Magnet Bias Hybrid Radial Magnetic Bearings

ActiveCN106337876BWill not cause irreversible demagnetizationElectric excitation magnetomotive force is smallBearingsMagnetic bearingMagnetic poles

Owner:NAVAL UNIV OF ENG PLA