Silicon carbide split gate mosfet with integrated high-speed freewheeling diode and preparation method

A freewheeling diode and silicon carbide technology, which is applied in the manufacture of diodes, transistors, semiconductor/solid-state devices, etc., can solve the problems of high conduction voltage drop of SiC body diodes, inability to use freewheeling diodes, and high density of JFET regions. The effect of improving long-term reliability, reducing utilization efficiency, and improving robustness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

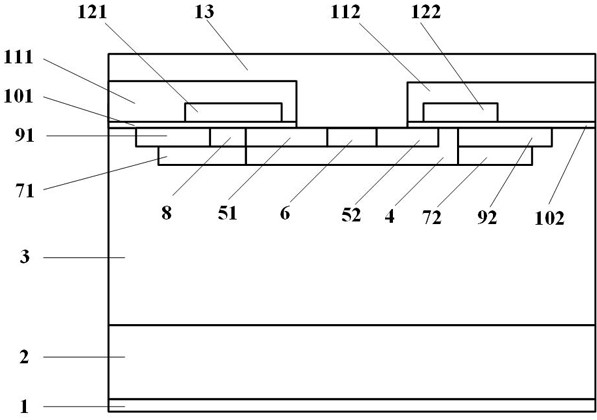

[0048] Such as figure 1 As shown, this embodiment provides a silicon carbide split-gate MOSFET integrating high-speed freewheeling diodes, including a rear ohmic contact alloy 1, an N-type doped silicon carbide substrate 2, an N-type doped silicon carbide epitaxial layer 3, and a P-type silicon carbide epitaxial layer 3. Doped well region 4, first N-type doped source region 51, second N-type doped source region 52, P-type doped source region 6, first P-type doped buried layer 71, second P-type doped source region Buried layer 72, P-type doped diode channel region 8, first N-type doped guide layer 91, second N-type doped guide layer 92, first gate oxide layer 101, second gate oxide layer 102, A first interlayer dielectric 111, a second interlayer dielectric 112, a first polysilicon 121, a second polysilicon 122, and a source metal 13;

[0049] The N-type doped silicon carbide substrate 2 is located above the back ohmic contact alloy 1; the N-type doped silicon carbide epitaxia...

Embodiment 2

[0060] This embodiment provides a method for preparing a silicon carbide split-gate MOSFET integrated with a high-speed freewheeling diode, which includes the following steps:

[0061] Step 1: Epitaxially forming an N-type doped silicon carbide epitaxial layer 3 on an N-type silicon carbide substrate 2; Figure 5 structure;

[0062] Step 2: Form the first barrier layer 21 by chemical vapor deposition on the surface of the N-type doped silicon carbide epitaxial layer 3, and photolithographically form the first barrier layer 21 to form the first ion implantation window 1-1, using high-temperature Al with a temperature greater than 773K Ion implantation forms a P-type doped well region 4; Figure 6 structure;

[0063] Step 3: Form the second barrier layer 22 on the surface of the first barrier layer 21 and the P-type doped well region 4 by chemical vapor deposition, and leave the sidewall of the second barrier layer 22 by etching to form the second ion implantation window 1- 2...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More