Semiconductor device with reduced miller capacitance and fabrication method thereof

A device and power semiconductor technology, applied in the field of metal-oxide-semiconductor field-effect transistor devices and their fabrication, can solve problems such as slow switching speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

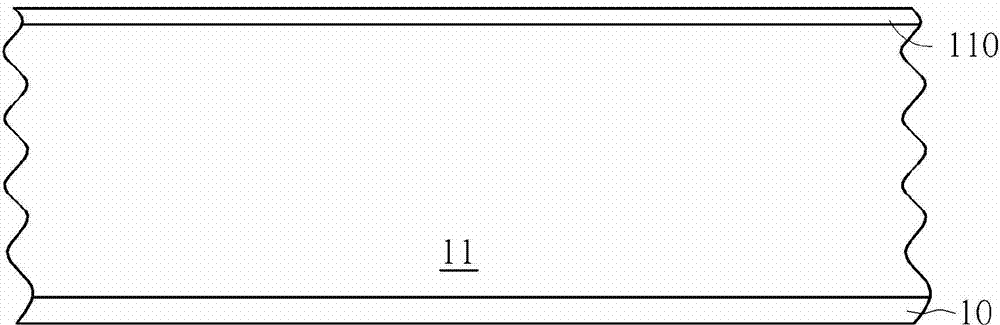

[0022] see Figure 1 to Figure 8 , which is a schematic diagram of a method for manufacturing a trench-type power transistor device according to an embodiment of the present invention. First, if figure 1 As shown, a semiconductor substrate 10 is provided, such as an N-type heavily doped silicon substrate, which can be used as a drain of a transistor device. Next, an epitaxial layer 11 , such as an N-type epitaxial silicon layer, is formed on the semiconductor substrate 10 by an epitaxial process. Next, a cushion layer 110 , for example, a silicon oxide cushion layer, may be formed on the surface of the epitaxial layer 11 .

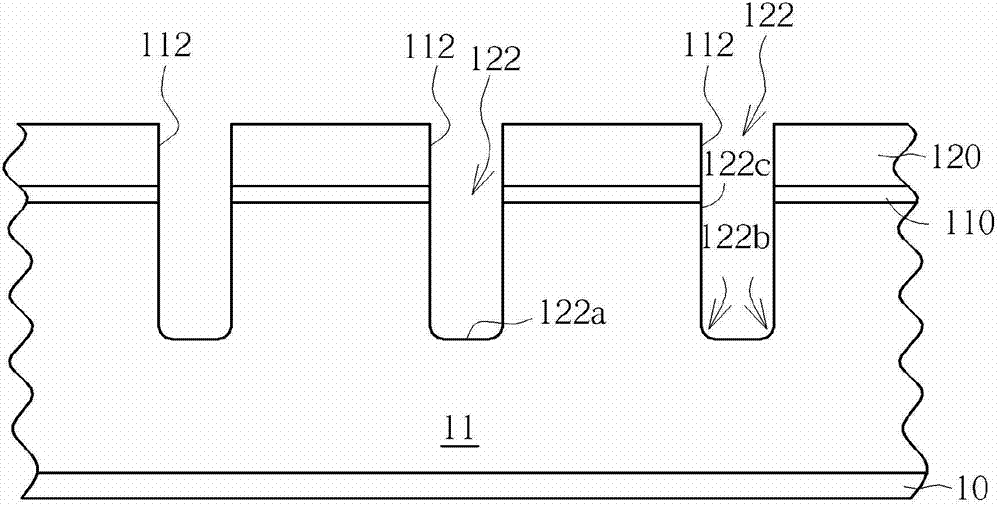

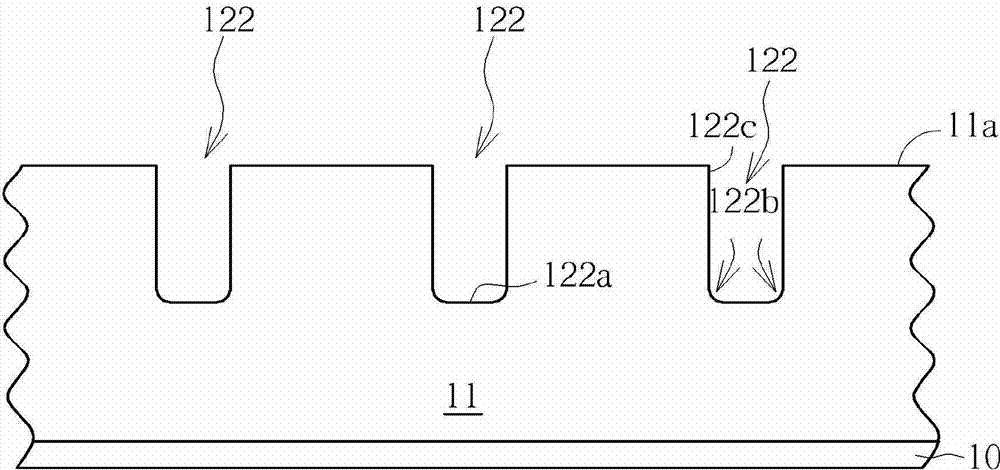

[0023] Such as figure 2 As shown, a hard mask layer 120 such as a silicon nitride layer is deposited on the epitaxial layer 11, and then an opening 112 is formed in the hard mask layer 120 by using photoresist and photolithography. Then the photoresist is removed, and then, the epitaxial layer 11 is etched to a predetermined depth through the opening ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More