VDMOS (Vertical Double-diffused Metal Oxide Semiconductor) transistor

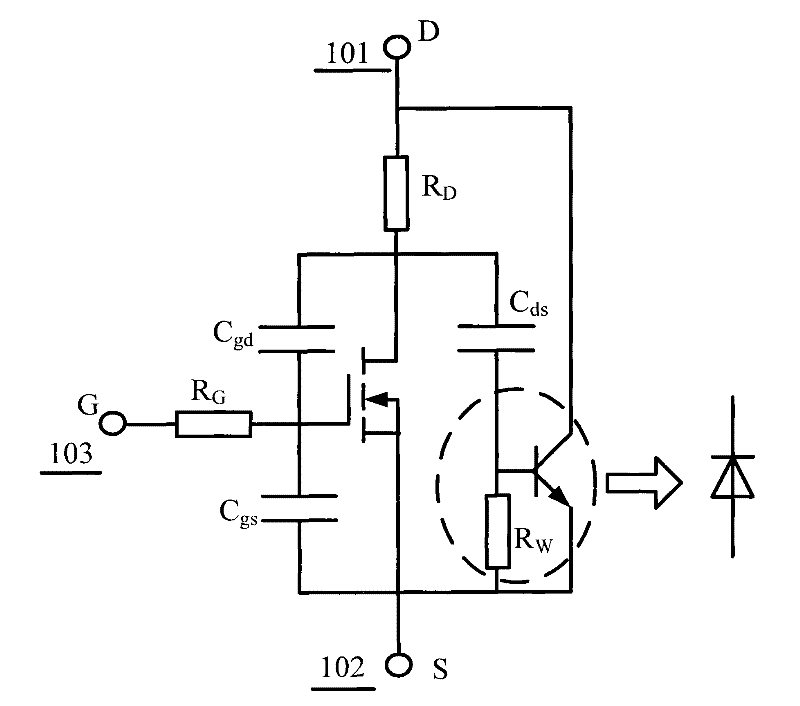

A transistor and semiconductor technology, applied in the direction of semiconductor devices, electrical components, circuits, etc., can solve the problems of mutual integration of MOS transistors, increase switching loss, device current, voltage performance degradation, etc., to shorten the charge and discharge time, reduce Gate-drain capacitance, effect of increasing switching speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings.

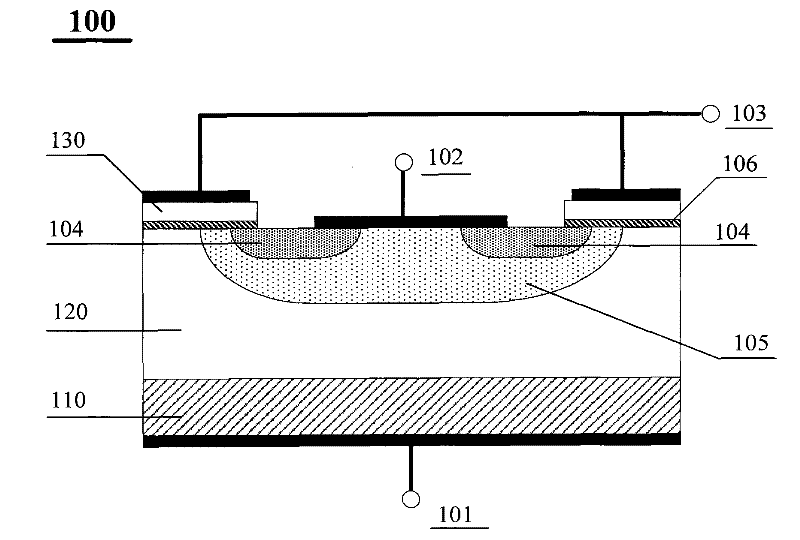

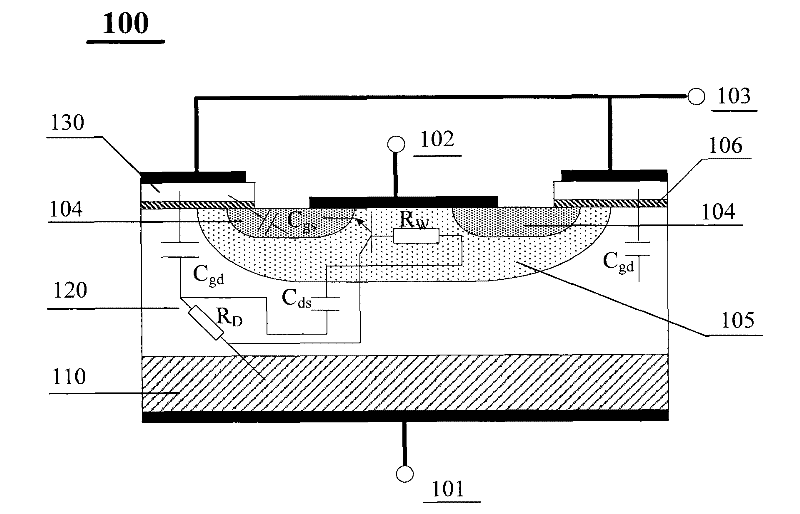

[0023] figure 2 It is a schematic diagram of the first embodiment of the VDMOS transistor provided by the present invention.

[0024] Such as figure 2 As shown, VDMOS transistor 200 includes:

[0025] a semiconductor substrate 210 of the first conductivity type;

[0026] An epitaxial layer 220 of the first conductivity type covering the surface of the semiconductor substrate 210;

[0027] A source doped region 201 of the first conductivity type and a channel region 202 of the second conductivity type located in the epitaxial layer 220;

[0028] A gate oxide layer 203 covering the surface of the epitaxial layer 220 and other parts except the source doped region 201;

[0029] An insulating dielectric layer 205 located on the upper surface of the gate oxide la...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More