SiC-based DI-MOSFET preparation method and SiC-based DI-MOSFET

A technology of substrate and ion implantation area, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as limiting device switching speed, large gate-to-drain capacitance, increasing device switching loss, etc., to reduce dynamic loss, The effect of reducing gate-drain capacitance and increasing operating frequency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

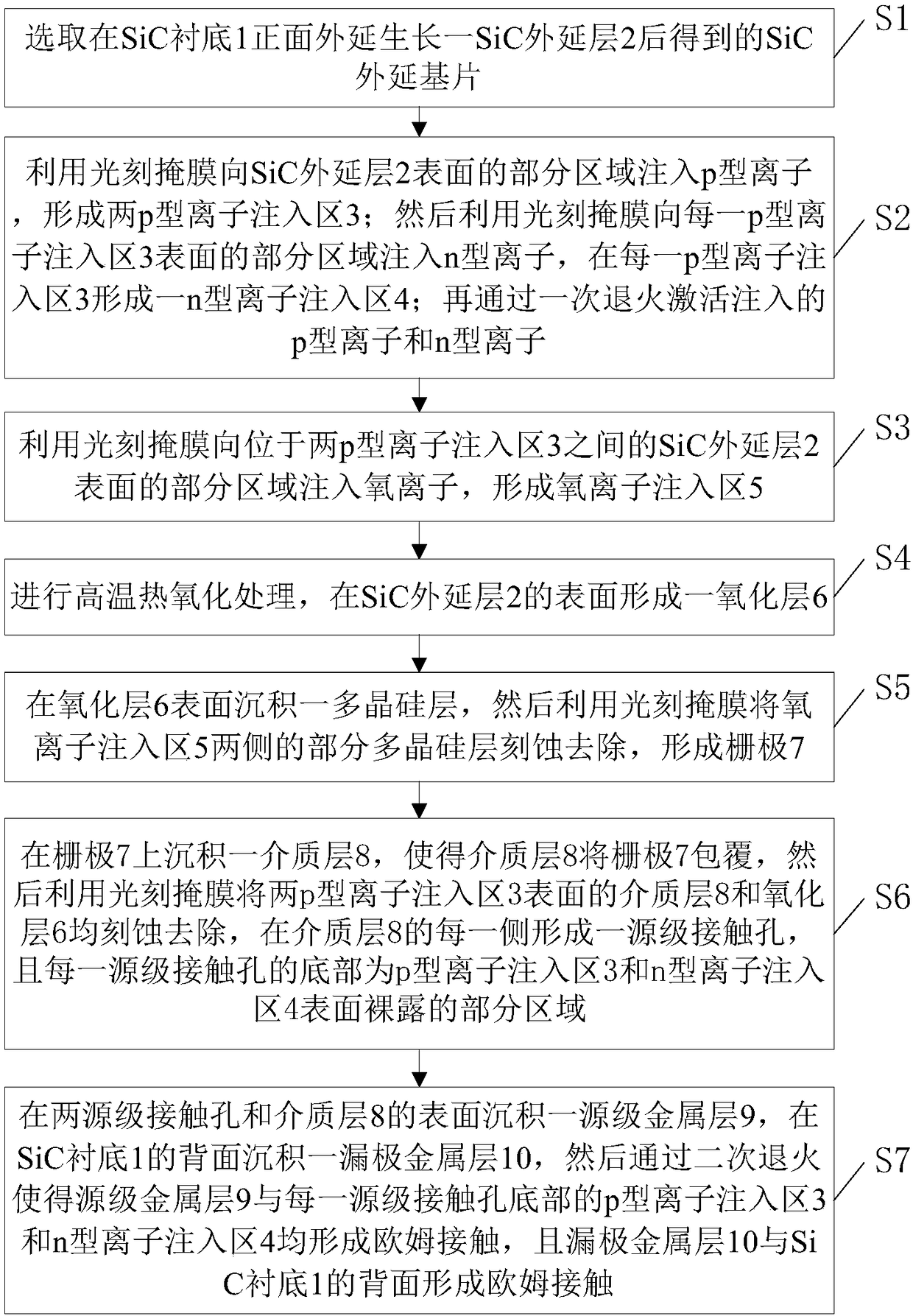

[0037] This embodiment provides a method for preparing a SiC-based DI-MOSFET, such as figure 1 Shown, this preparation method comprises the steps:

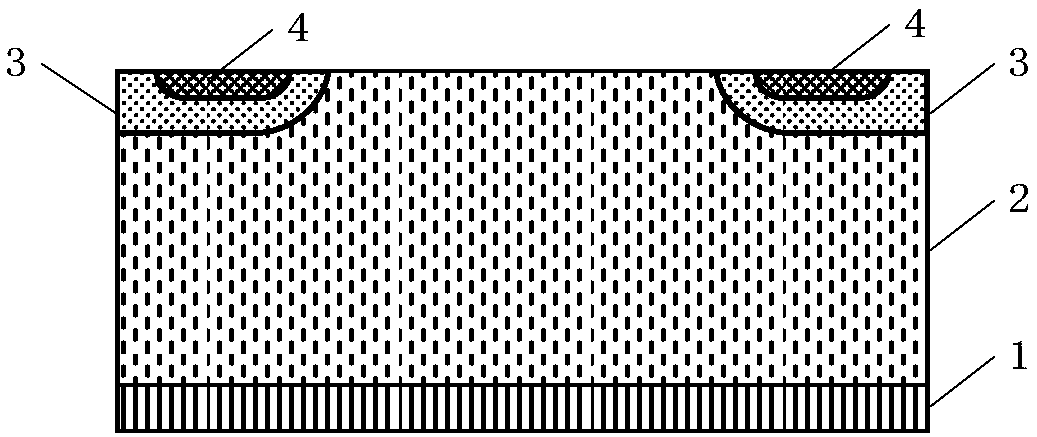

[0038] S1: Select the SiC epitaxial substrate obtained after epitaxially growing a SiC epitaxial layer 2 on the front side of the SiC substrate 1, such as figure 2 shown;

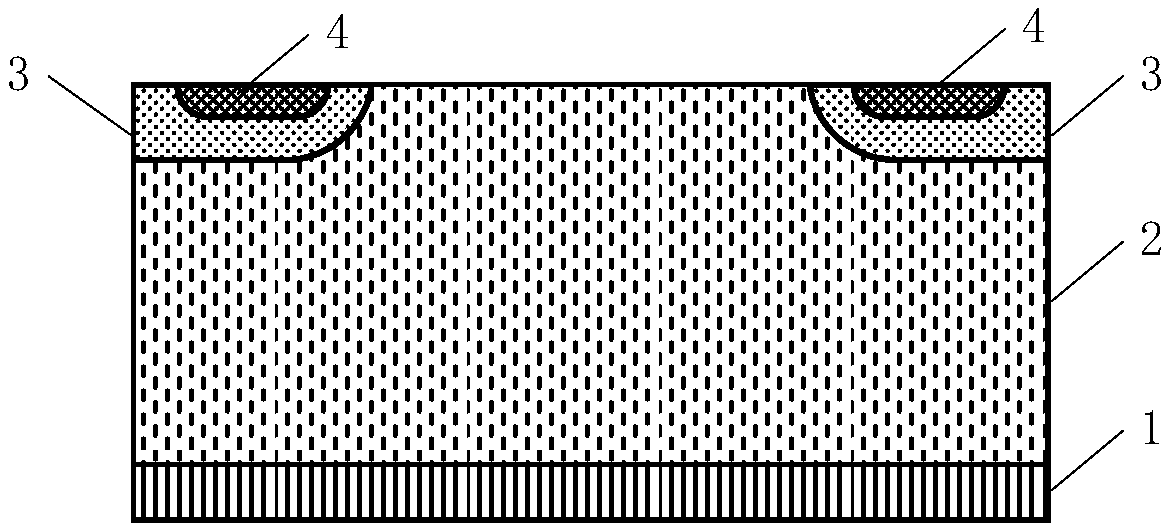

[0039] S2: Implanting p-type ions into a part of the surface of the SiC epitaxial layer 2 using a photolithography mask to form two p-type ion implantation regions 3; and then implanting into a part of the surface of each p-type ion implantation region 3 using a photolithography mask N-type ions form an n-type ion implantation region 4 in each p-type ion implantation region 3; the implanted p-type ions and n-type ions are activated by an annealing, such as image 3 shown;

[0040] S3: using a photolithographic mask to implant oxygen ions into a part of the surface of the SiC epitaxial layer 2 located between the two p-type ion implantation regions 3 to form...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More