Silicon carbide separation gate MOSFET cell of integrated gate-controlled diode and preparation method thereof

A technology of gate-controlled diodes and silicon carbide, which is applied in the manufacture of diodes, electrical components, semiconductors/solid-state devices, etc., can solve the problems of high conduction voltage drop of SiC body diodes, increased dynamic losses of devices, and high density of JFET regions, etc., to achieve Effects of improving long-term reliability, reducing Miller capacitance, and reducing conduction voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0045] The principles and features of the present invention will be described below with reference to the accompanying drawings. The examples are only used to explain the present invention, but not to limit the scope of the present invention.

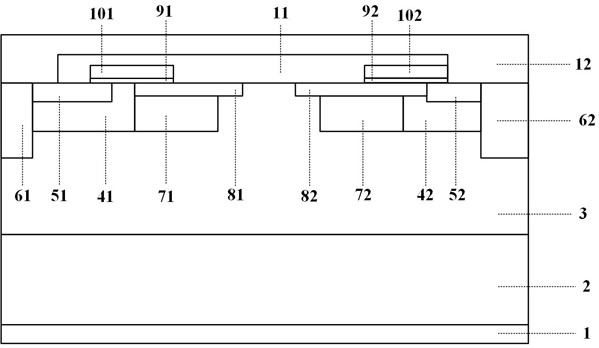

[0046] This embodiment provides a silicon carbide split gate MOSFET cell with integrated gated diode, such as figure 1 As shown, it includes a backside ohmic contact alloy 1, an N-type doped silicon carbide substrate 2, an N-type doped silicon carbide epitaxial layer 3, a first P-type doped well region 41, a second P-type doped well region 42, The first N-type doped source region 51, the second N-type doped source region 52, the first P-type doped source region 61, the second P-type doped source region 62, the first P-type doped buried layer 71, The second P-type doped buried layer 72, the first N-type doped guide layer 81, the second N-type doped guide layer 82, the first gate oxide layer 91, the second gate oxide layer 92, the first p...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More