Separated gate CSTBT with self-biased PMOS and manufacturing method thereof

A separation gate and self-biasing technology is applied in the field of separation gate CSTBT and its production, which can solve the problems of CSTBT device breakdown voltage drop, device saturation current density increase, and short-circuit safe working area deterioration, etc., so as to improve device reliability. , reduce saturation current, improve the effect of clamping effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

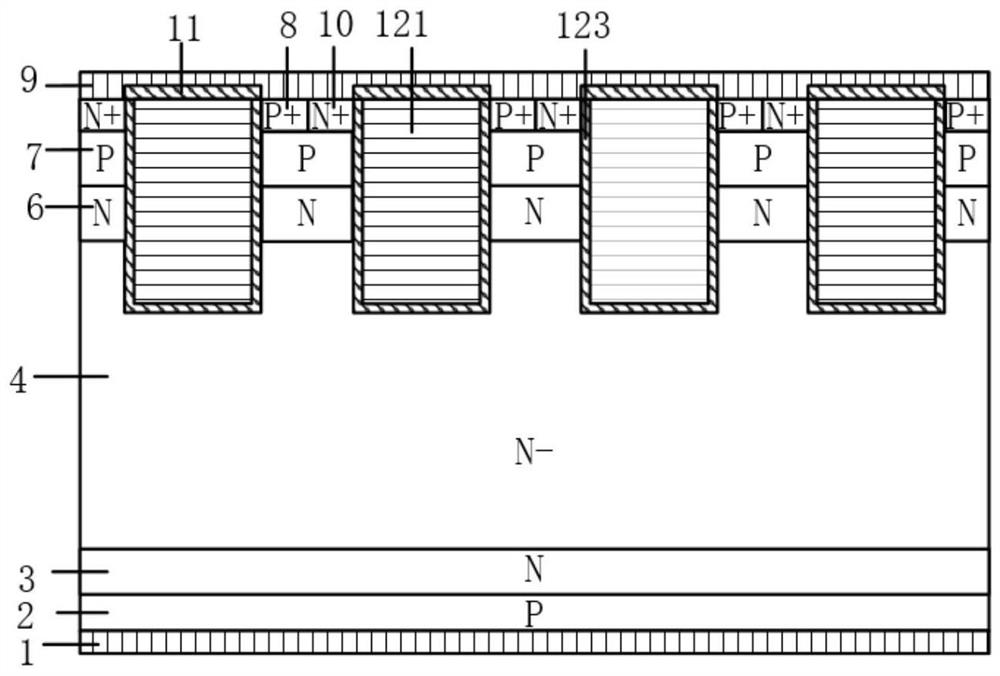

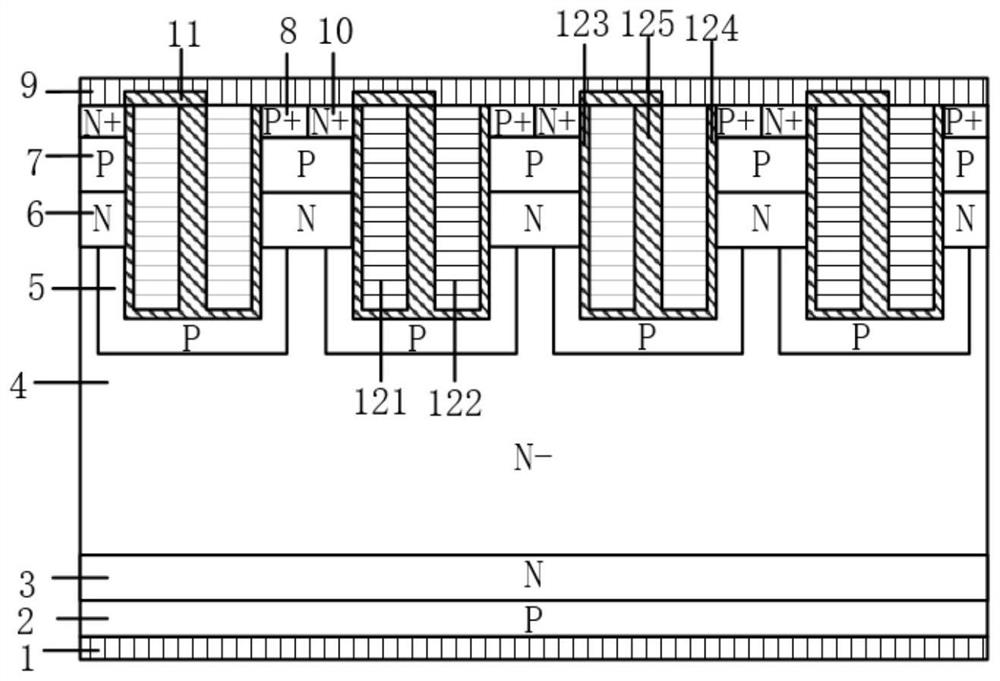

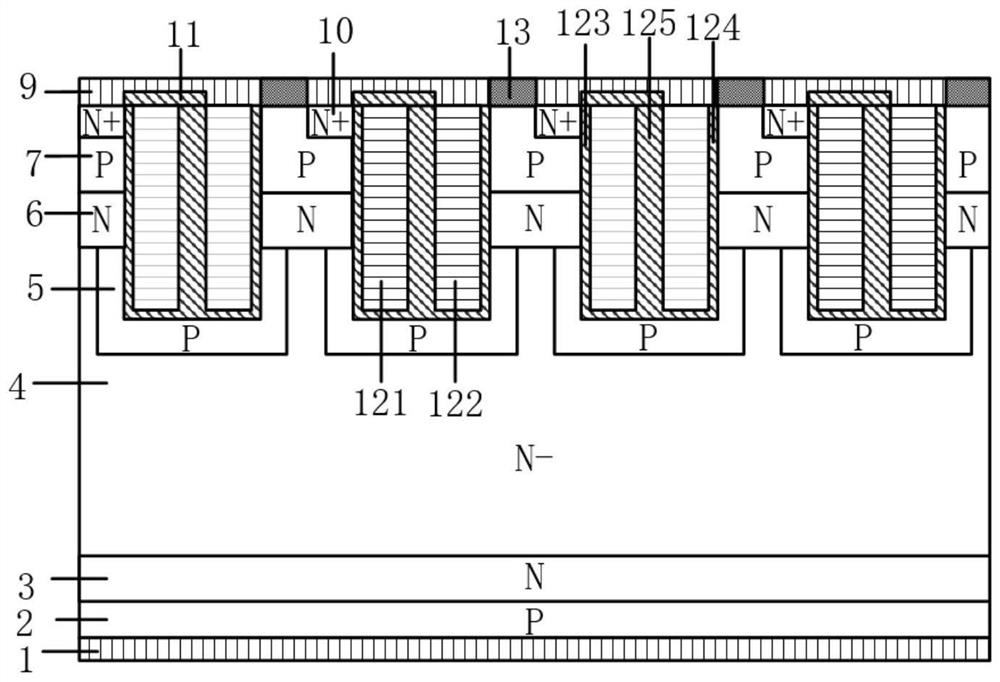

[0057] The principles and features of the present invention are described below in conjunction with the accompanying drawings. The specific embodiments of the present invention are illustrated by taking an IGBT with a voltage level of 1200V as an example. The examples are only used to explain the present invention, not to limit the scope of the present invention.

[0058] Such as figure 2 As shown, a self-biased PMOS split-gate CSTBT provided in Embodiment 1 of the present invention has a cell structure including back collector metal 1, P-type collector region 2, and N-type field stacked sequentially from bottom to top. Blocking layer 3 and N-drift region 4; the upper layer of the N-drift region 4 has N-type charge storage layers 6 and trench structures alternately arranged, and the depth of the lower surface of the trench structure is greater than that of the N-type charge storage layer 6 the junction depth of the lower surface;

[0059] The upper surface of the N-type char...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More