An insulated gate bipolar transistor and a preparation method thereof

A bipolar transistor and insulated gate technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as band bending, low forward conduction voltage drop, increase, etc., and achieve a change in the forbidden band width , excellent device characteristics, and the effect of improving the carrier concentration distribution

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

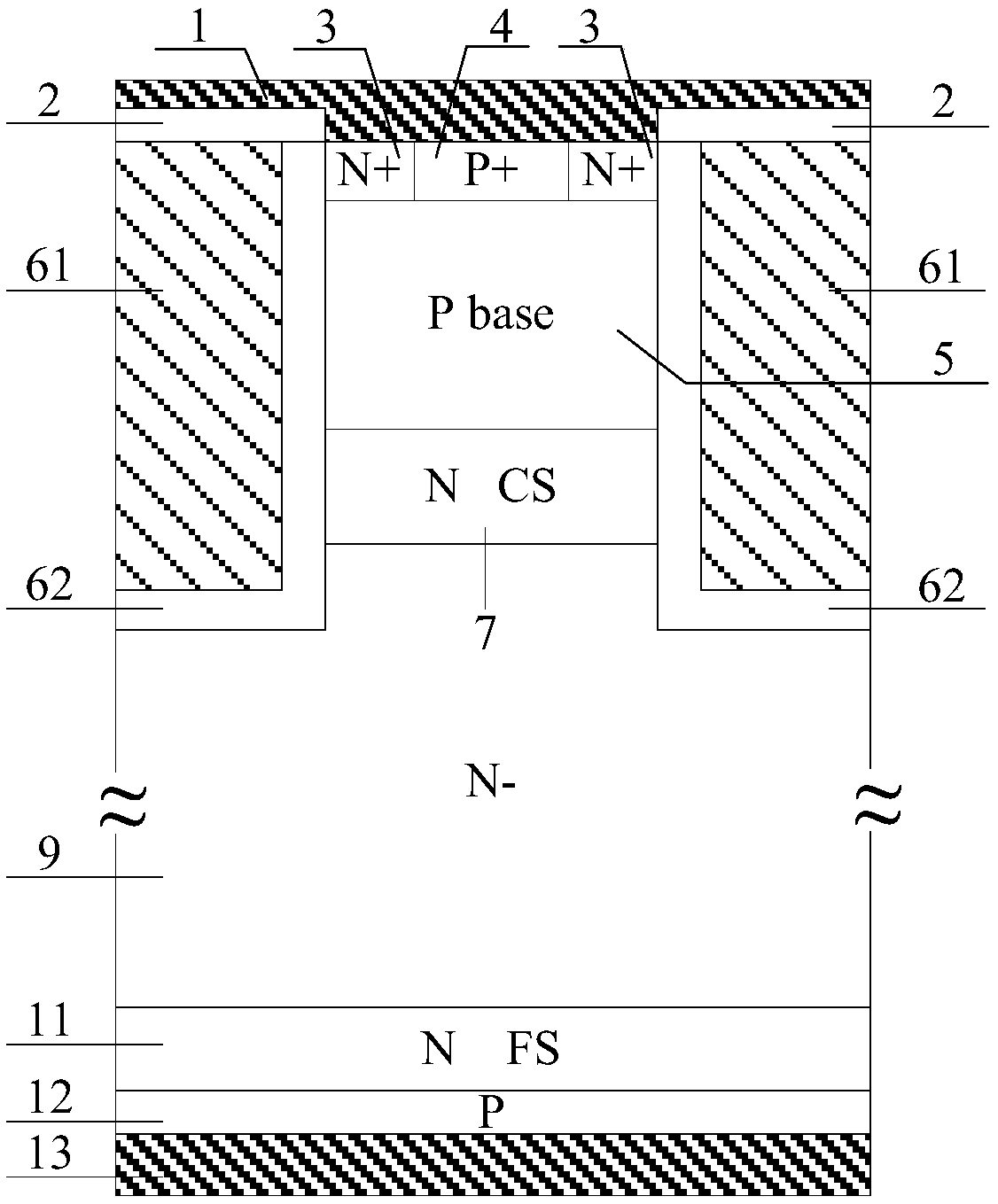

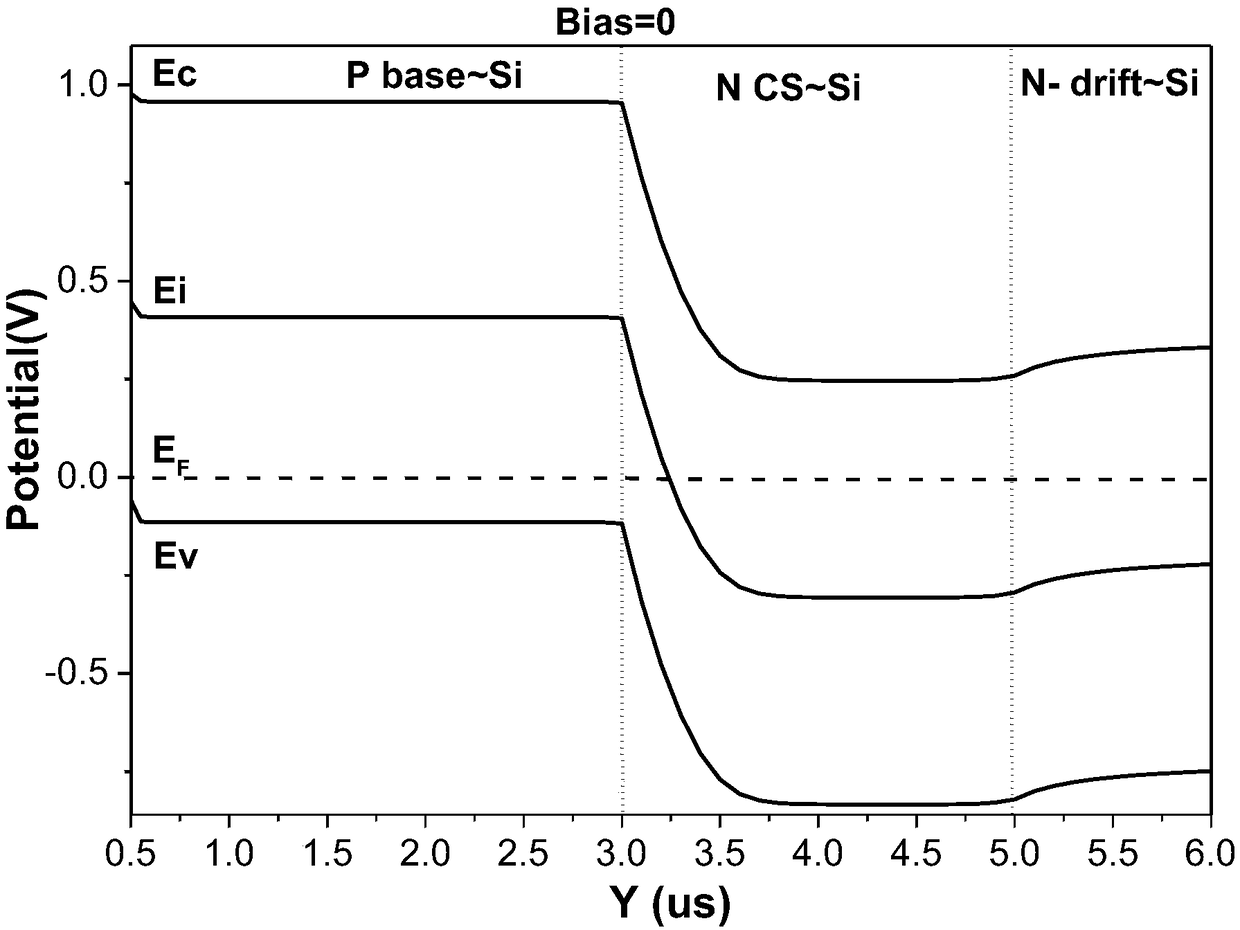

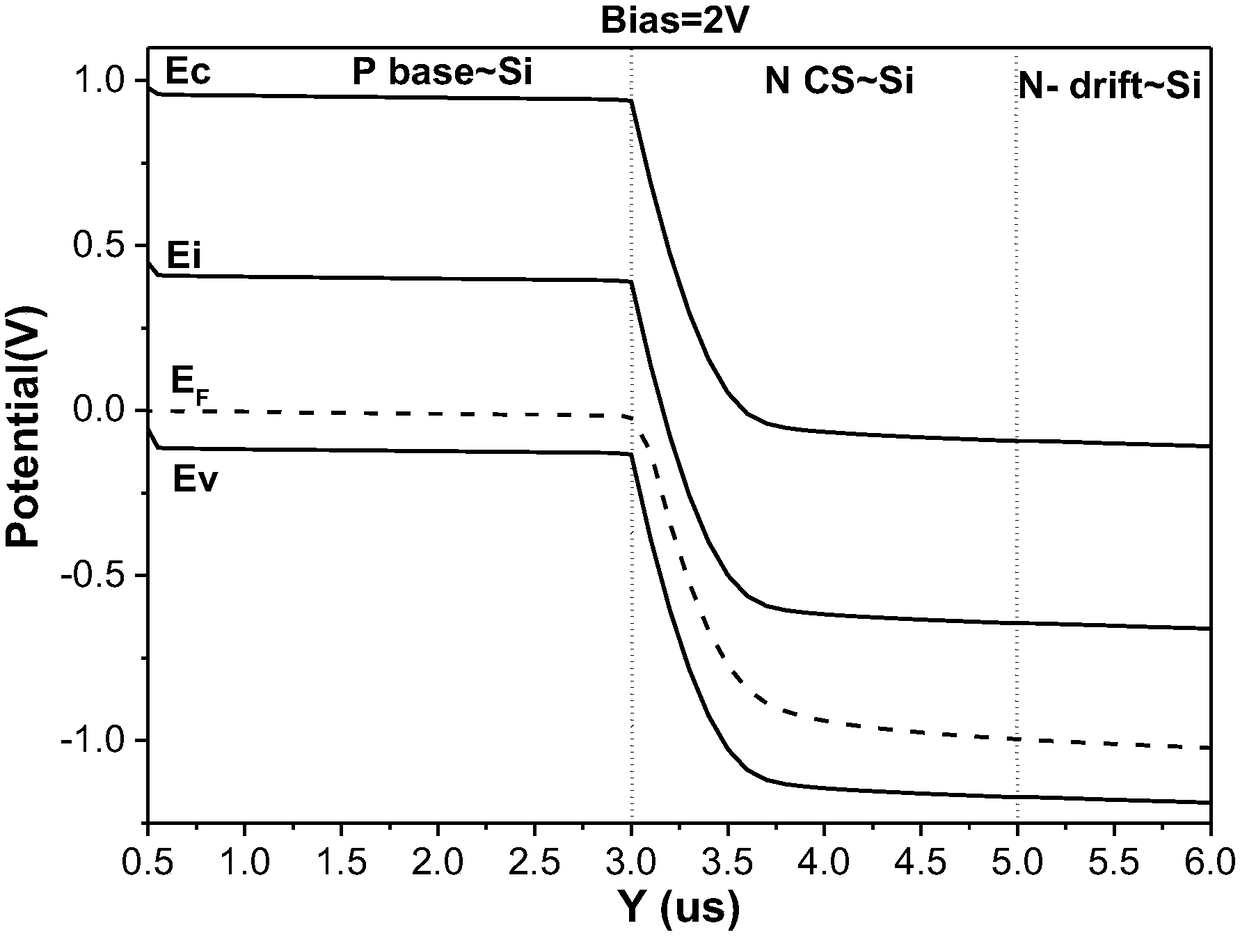

[0075] This embodiment provides a strained Si~Si 1-x Ge x Insulated gate bipolar transistors with heterojunction base regions, Figure 4 Its semi-cellular structure is shown, and its cellular structure includes: collector metal 13, P-type collector region 12, N-type drift region 9, P-type base region 5, P+ emitter region 4, N+ emitter region 3, gate structure and the emitter metal 1; the collector metal 13 is arranged on the back of the P-type collector region 12; the N-type drift region 9 is arranged on the front of the P-type collector region 12; the P-type base region 5 is arranged on the side of the N-type drift region 9 Top layer; P+ emitter region 4 and the N+ emitter region 3 that is in contact with both sides of P+ emitter region 4 are arranged side by side on the top layer of P-type base region 5; the gate structure includes gate electrode 61 and gate dielectric layer 62, and gate electrode 61 passes gate The dielectric layer 62 is in contact with the N+ emitter reg...

Embodiment 2

[0081] This embodiment provides a strained Si~Si 1-x Ge x Insulated gate bipolar transistors with heterojunction base regions, Figure 11 Its semi-cellular structure is shown. In this embodiment, except in P-type Si 1-x Ge x A P-type Si layer 53 is added on the lower surface of the layer 52 to form a double potential barrier. The junction depths of the P-type Si base region 51 and the P-type Si layer 53 are both 1 μm, and the rest of the structure is the same as that of Embodiment 1.

[0082] In this embodiment, the P-type Si 1-x Ge x A P-type Si layer 53 is added to the lower surface of the base region 52, thereby introducing a heterojunction hole barrier, further improving the conductance modulation effect of the device, thereby reducing the forward conduction voltage drop and conduction loss of the device, and improving The trade-off relationship between the turn-off loss and the forward conduction voltage drop is shown.

[0083] Figure 12 with 13 Respectively Si~...

Embodiment 3

[0087] This embodiment provides a strained Si~Si 1-x Ge x Insulated gate bipolar transistors with heterojunction base regions, Figure 16 Its semi-cellular structure is shown. In this embodiment, except that an N-type charge storage layer 7 with a junction depth of 2 μm is introduced under the P-type base region 5 , other structures are the same as those in Embodiment 2.

[0088] In this embodiment, the hole barrier is introduced on the side of the N-drift region 9 close to the emitter by introducing the N-type charge storage layer 7, thereby further improving the conductance modulation effect of the device and reducing the forward conduction voltage drop and conduction of the device. Loss, while improving the trade-off relationship between turn-off loss and forward voltage drop.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More