Patents

Literature

50results about How to "Guaranteed breakdown voltage" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

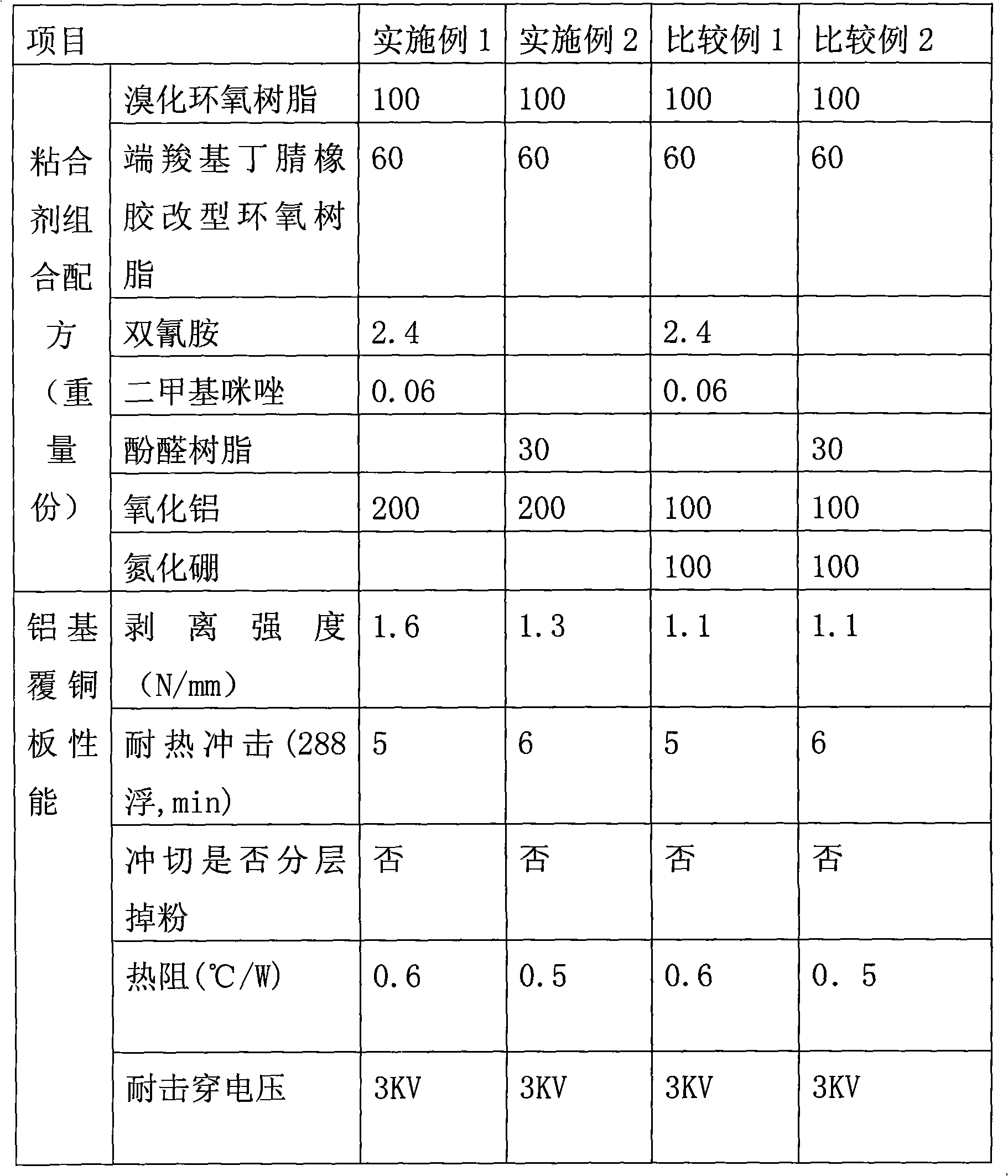

Epoxy resin composition, glue film made of same and preparation method

The invention discloses an epoxy resin composition, a continuous glue film made of the same and a preparation method. The epoxy resin composition comprises solid ingredients and organic solvents, wherein the solid ingredients comprise epoxy resin (A), thermoplastic resin or / and synthetic nitrile rubber (B), solidified agents (C), curing accelerators (D) and inorganic heat-conducting fillers (E). In addition, the invention also relates to the continuous glue film made of the epoxy resin composition and the preparation method. Because the continuous glue film is made by automated equipment, thecontinuous glue film has good consistency on thickness and performance, so that the breakdown voltage of a metal based copper-clad laminate and the stability of thermal resistance are ensured. The product made by the invention has good heat-conducting performance and electric insulation performance.

Owner:广东全宝科技股份有限公司

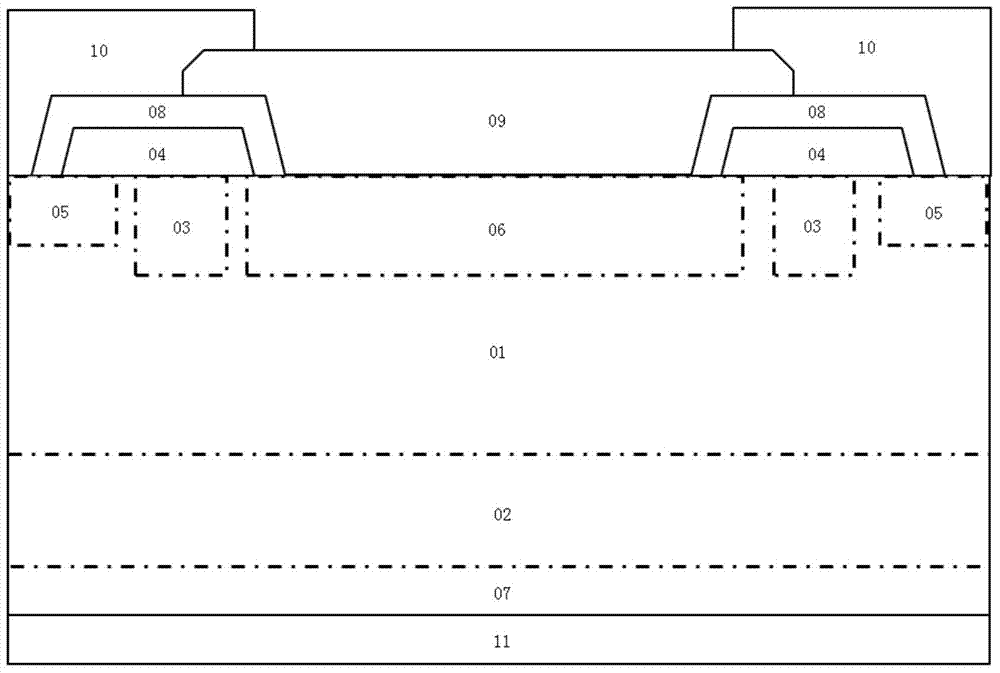

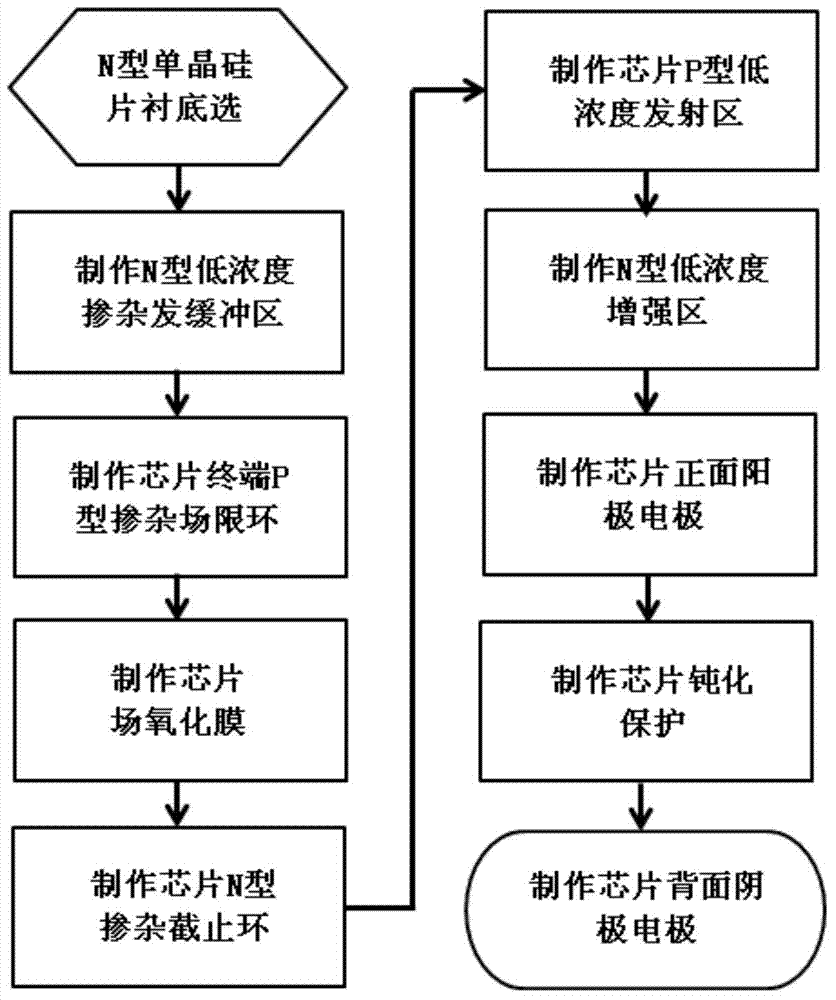

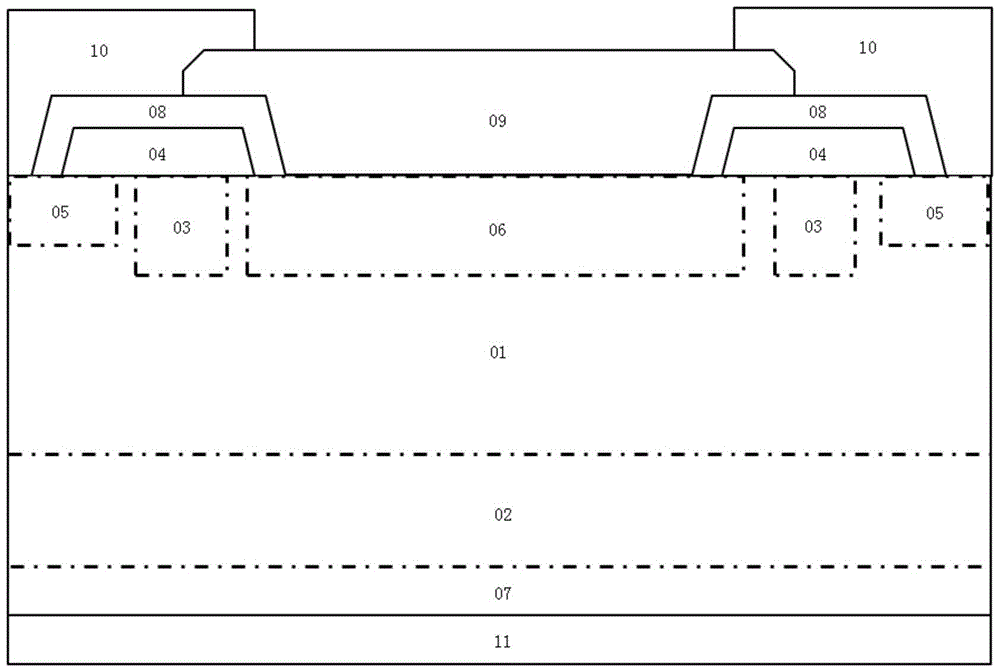

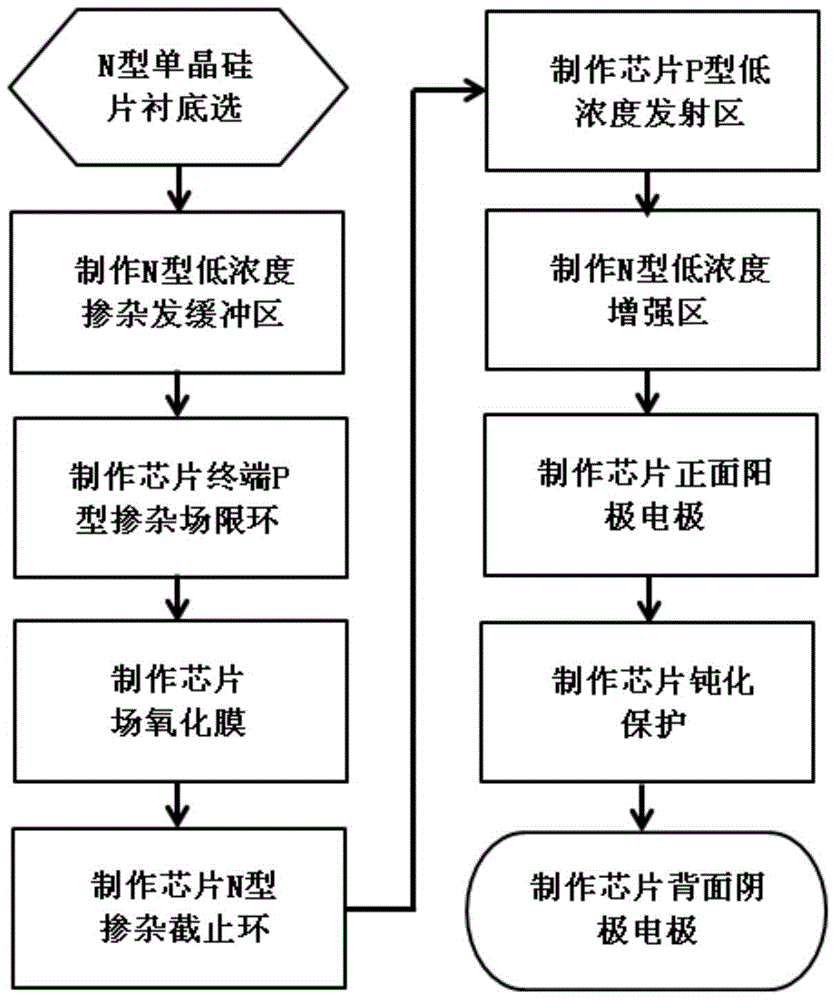

Fast recovery diode chip of low-concentration doped emitter region and manufacturing method thereof

ActiveCN103579367AExcellent electrical characteristic parametersThe concentration of holes at the junction decreasesSemiconductor/solid-state device manufacturingSemiconductor devicesVoltage dropP type doping

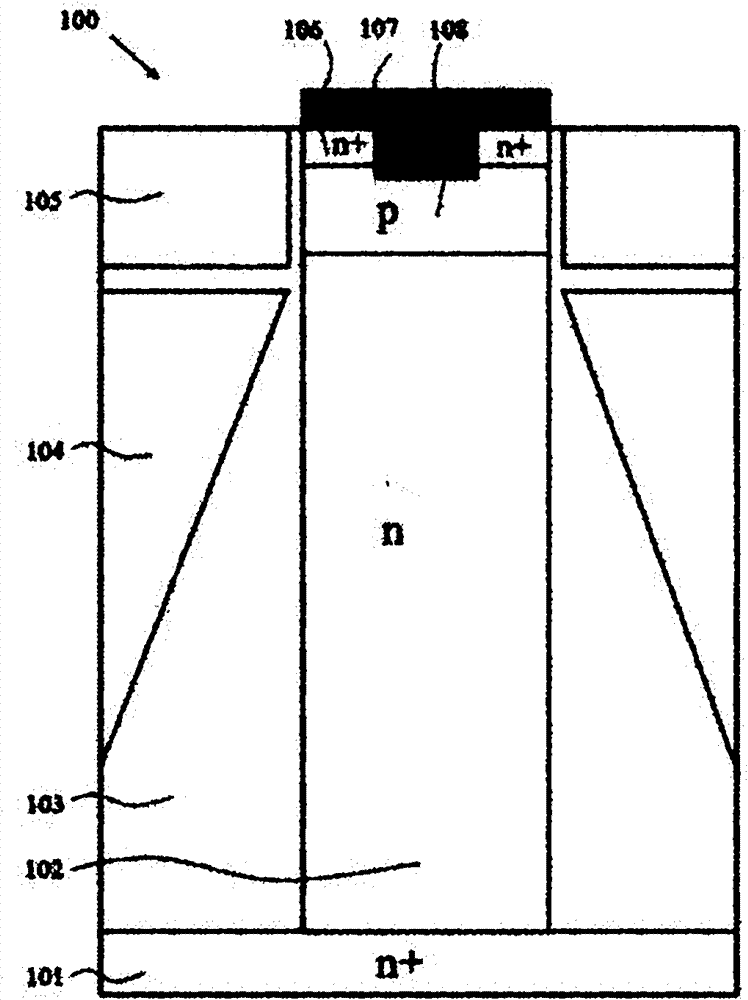

The invention relates to a power device and a manufacturing method of the power device, in particular to a fast recovery diode chip of a low-concentration doped emitter region and a manufacturing method of the fast recovery diode chip of the low-concentration doped emitter region. The fast recovery diode chip of the low-concentration doped emitter region comprises a metal cathode, a metal anode, a P-type doped layer, an N-type doped layer, an N-type substrate arranged between the P-type doped layer and the N-type doped layer, field oxide layers and passivation protective layer structures, wherein the metal anode is a low-concentration P-type doped region, the metal cathode is a low-concentration N-type buffer doped region and a low-concentration N-type reinforced doped region, the special manufacturing mode of injection doped of the reverse side is formed through an obverse side protection technology, and a device structure is formed through the special manufacturing mode of injection doped of the reverse side. According to the fast recovery diode chip of the low-concentration doped emitter region and the manufacturing method of the fast recovery diode chip of the low-concentration doped emitter region, due to the fact that the doped concentration of an anode emitter region and the doped concentration of a cathode emitter region are reduced, the self-key electric potential difference of a PN-junction is reduced, the total number of injection holes of the P-type doped region is reduced, performance of a fast recovery diode is integrally optimized, it is ensured that the fast recovery diode has low forward communication voltage drop, and the dynamic performance of a device is improved.

Owner:STATE GRID CORP OF CHINA +2

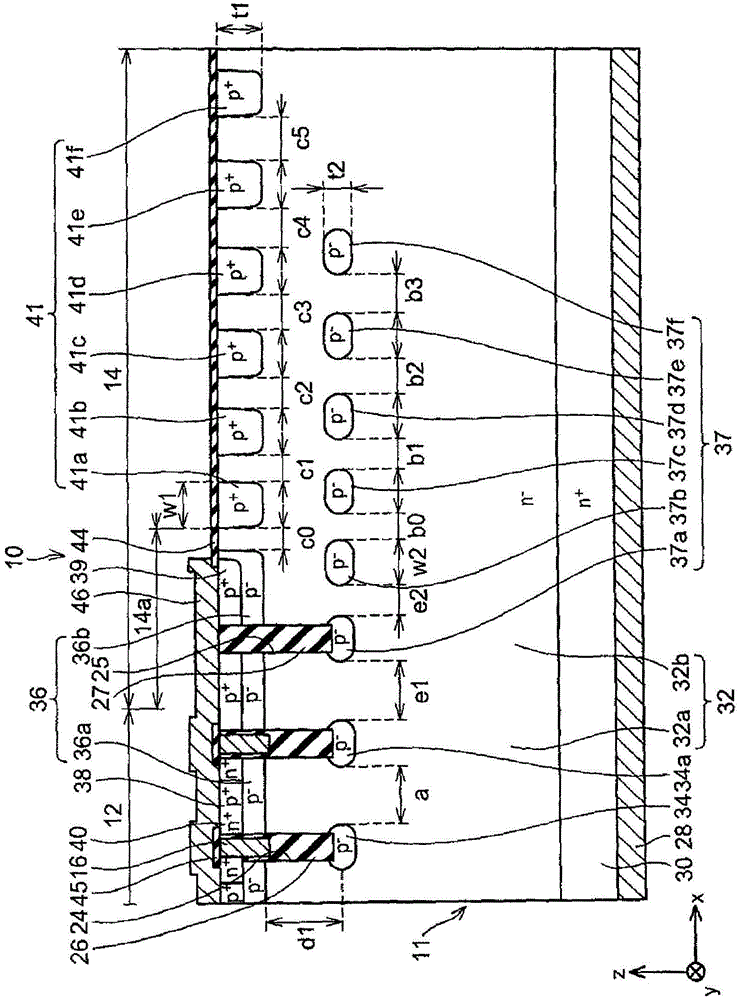

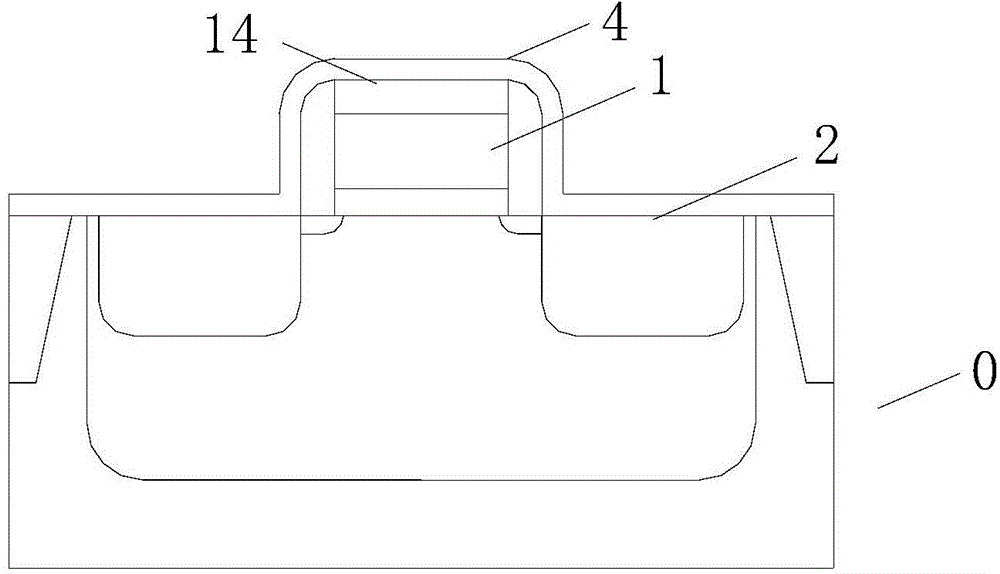

Semiconductor device

InactiveCN104465719AAvoid concentrationReduce electric field strengthSemiconductor devicesPower semiconductor deviceBody region

Owner:TOYOTA JIDOSHA KK

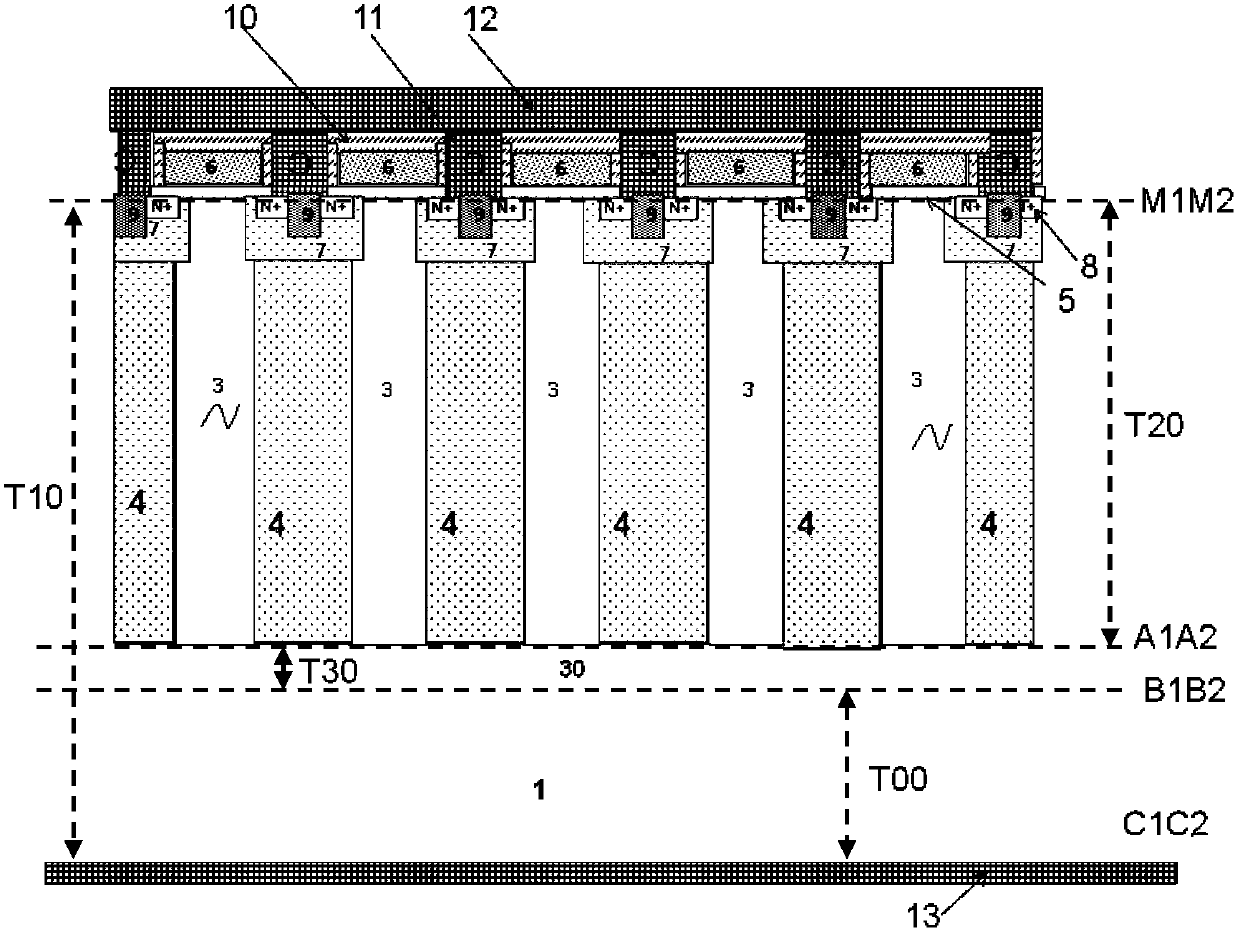

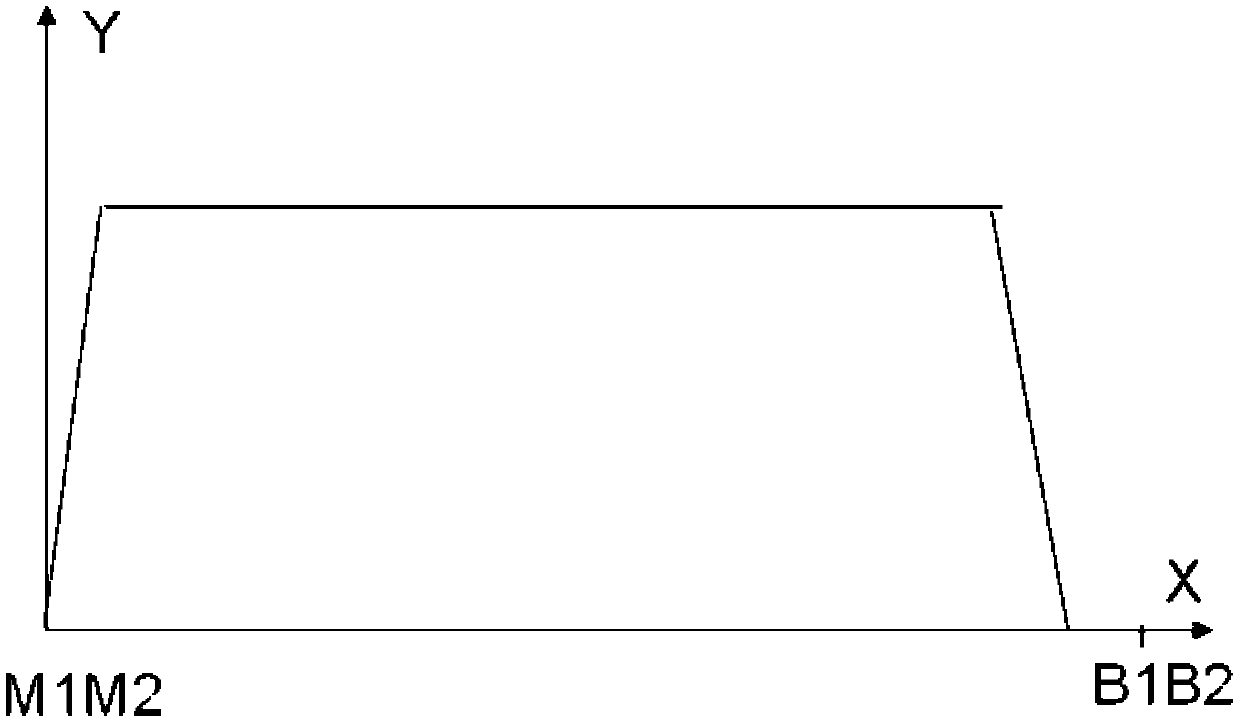

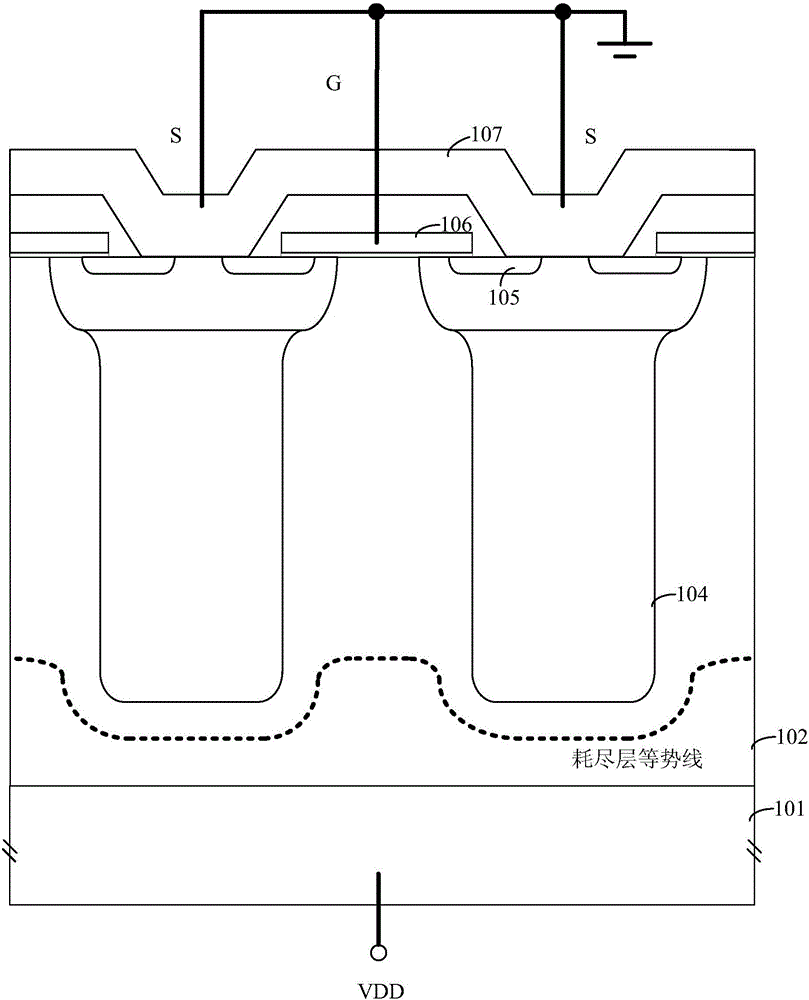

Super junction device and manufacturing method thereof

ActiveCN107768443AReduce the effects of electromagnetic interferenceRaise the minimumSemiconductor/solid-state device manufacturingSemiconductor devicesElectric fieldCapacitance

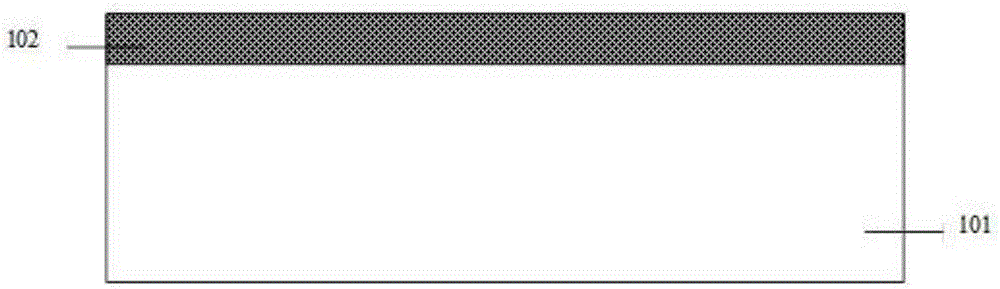

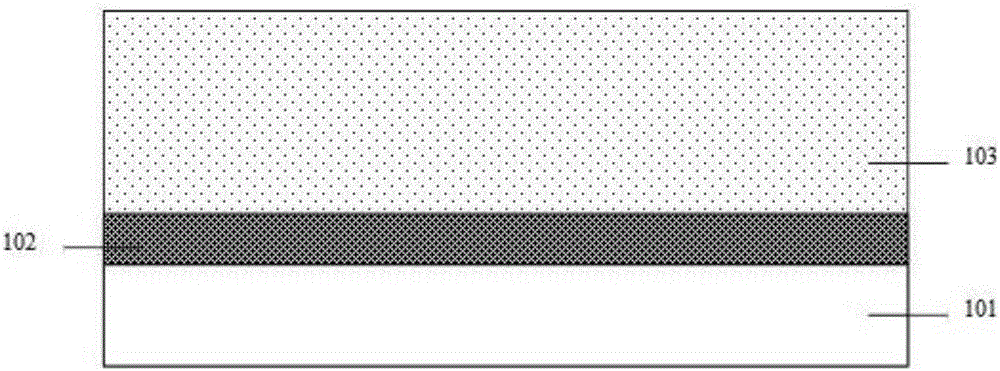

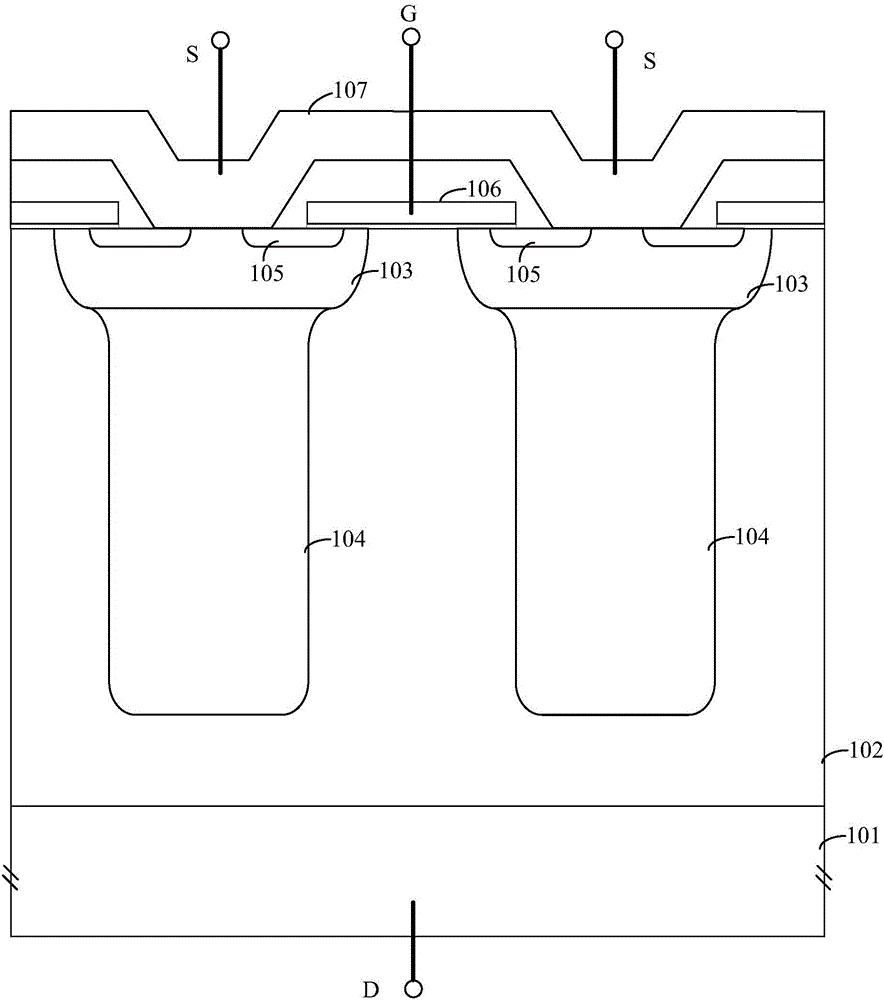

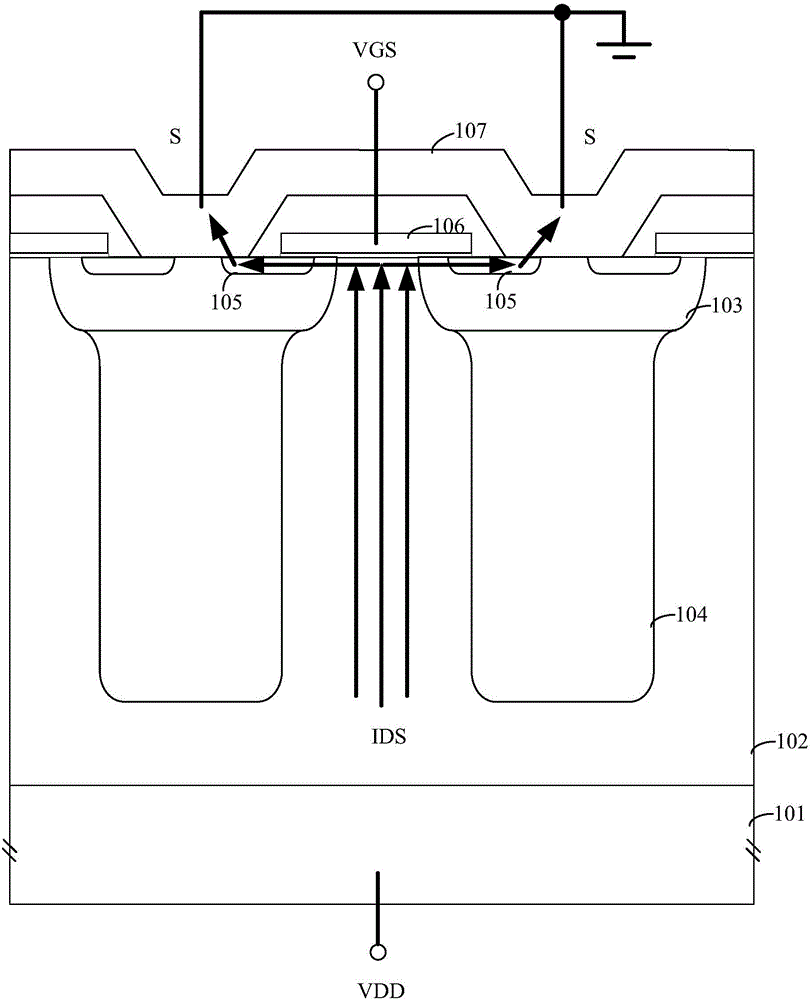

The present invention discloses a super junction device. P-type columns of at least one super junction unit are internally provided with N-type electric field barrier layers, and the N-type electric field barrier layers are configured to segment the P-type columns into first and second P-type columns which are respectively located at the top portions and the bottom portions of the electric field barrier layers; the N-type electric field barrier layers are configured to realize segmentation exhaustion of super junction structures at a top portion and a bottom portion; when a source-drain voltage of a super junction device is smaller than or equal to a first voltage value, the super junction structure at the top portion is only exhausted; and when the source-drain voltage of the super junction device is larger than the first voltage value, the super junction structures at the top portion and the bottom portion are exhausted. The present invention further discloses a manufacturing methodof a super junction device. According to the invention, a gate-drain capacitance and the minimum value of the gate-drain capacitance can be improved to effectively reduce the electromagnetic interference performance of the device in an application circuit and effectively reduce current and voltage overshoot caused by the device in the application circuit, reversely recovered soft factors of the device can be increased, and a breakdown voltage of the device can be maintained.

Owner:SHENZHEN SANRISE TECH CO LTD

A planar insulated gate bipolar transistor and a preparation method thereof

ActiveCN109166917AImprove breakdown voltageImprove reliabilityTransistorSemiconductor/solid-state device manufacturingHeterojunctionParasitic bipolar transistor

The invention relates to a planar insulated gate bipolar transistor and a preparation method thereof, belonging to the technical field of power semiconductors. A semiconductor layer or Schottky contact metal having a relatively small band gap is introduced into the upper surface of the base region of the device adjacent to the outer side of the emitter region, By using heterojunction or Schottky contact as minority carrier barrier to enhance the conductivity modulation effect, the conduction voltage drop is reduced and the tradeoff between forward voltage drop and turn-off loss is optimized. As the heterojunction or Schottky contact introduced by the invention can replace the CS layer functionally, the electric field strength of the PN junction formed in the base region and the drift region is reduced to improve the breakdown voltage of the device; And the electric field intensity of the gate oxide layer is below the safe value (3MV / cm), so the reliability of the gate oxide layer is ensured. In addition, the fabrication process of the device is simple and controllable, and the device has strong compatibility with the existing process.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

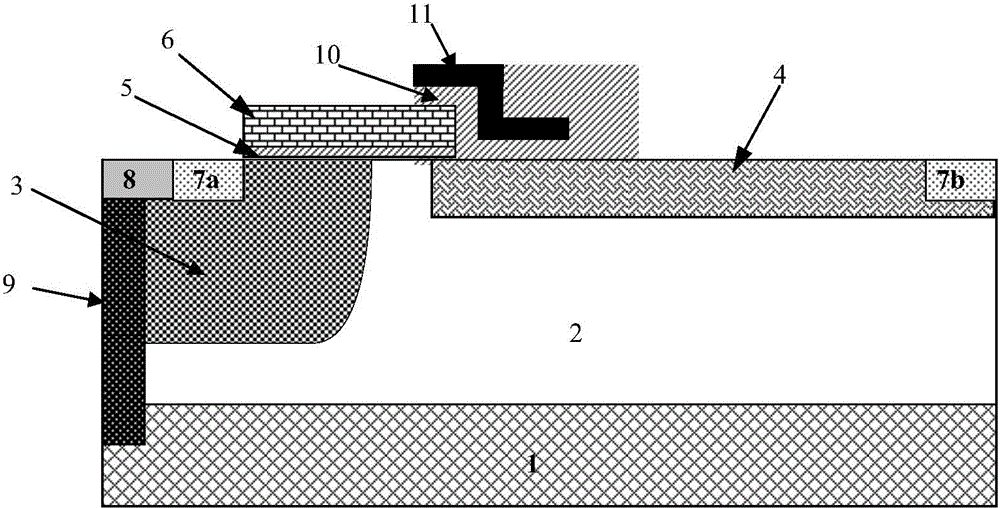

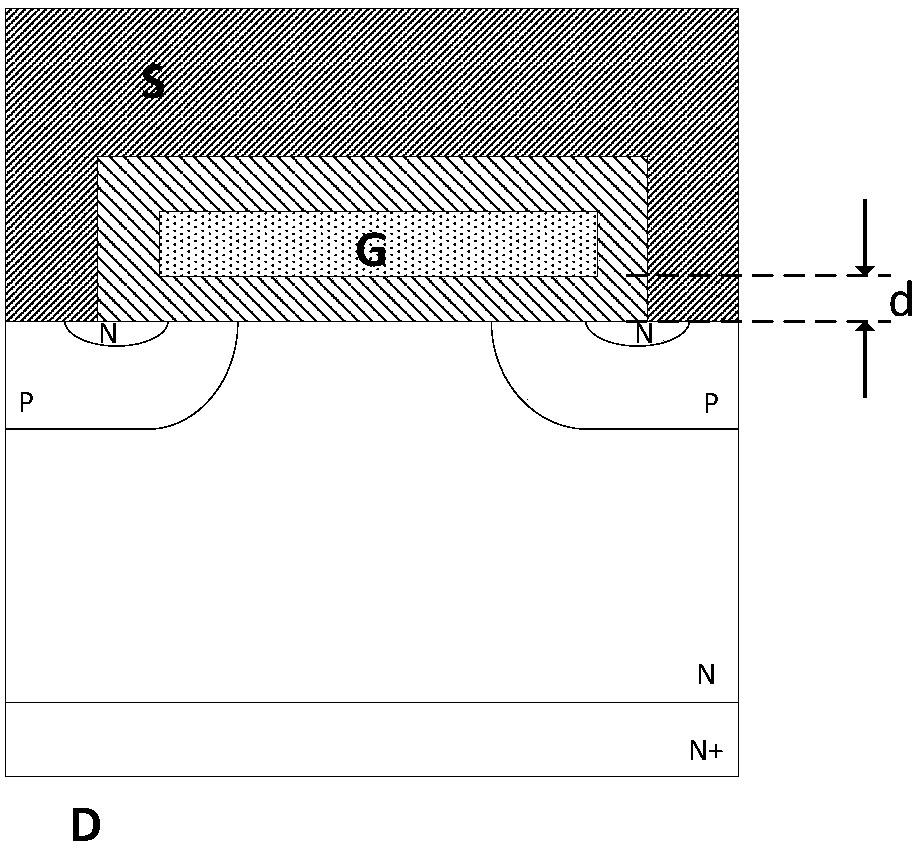

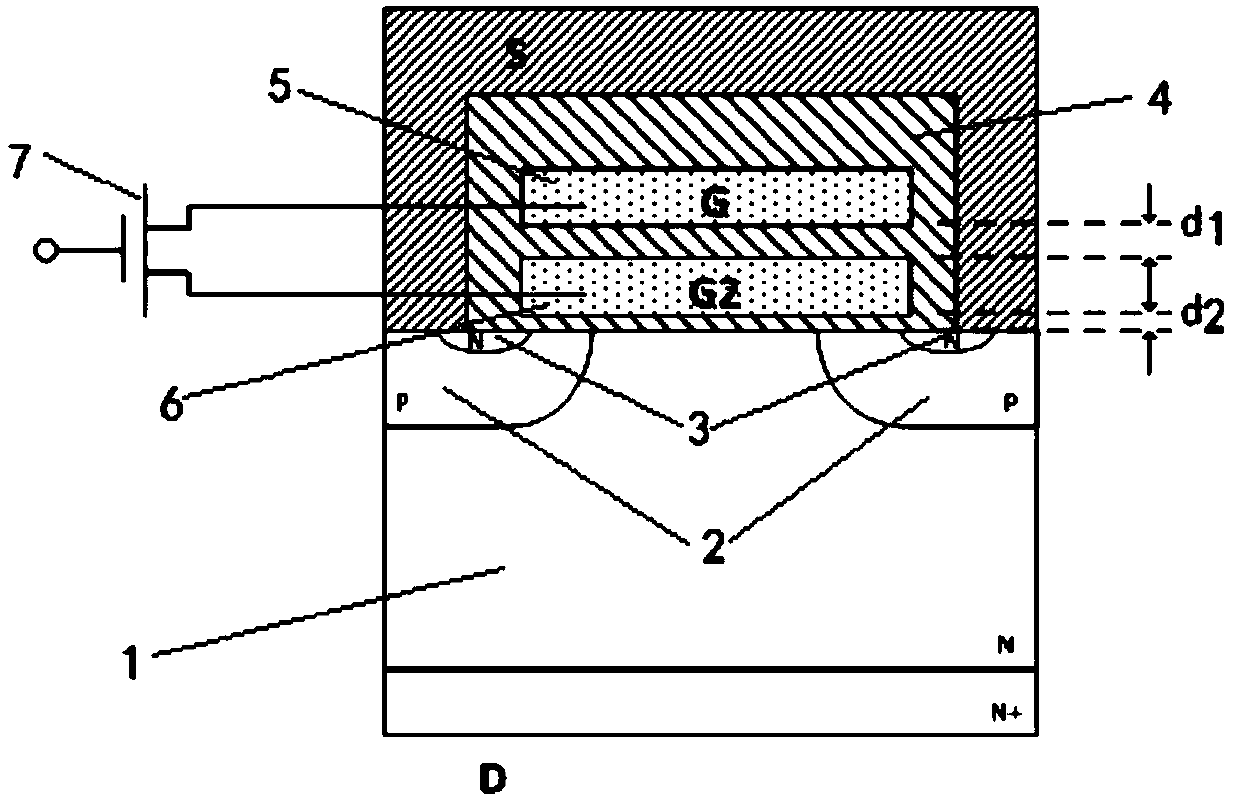

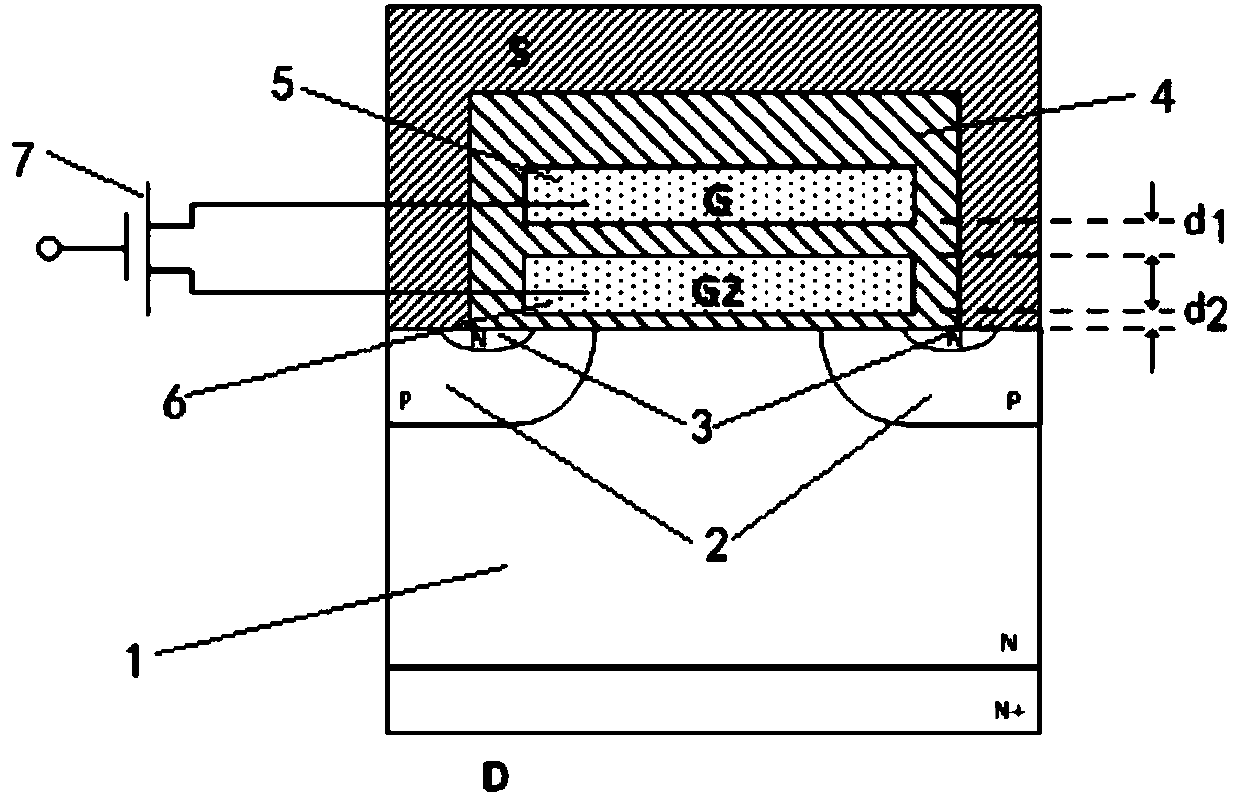

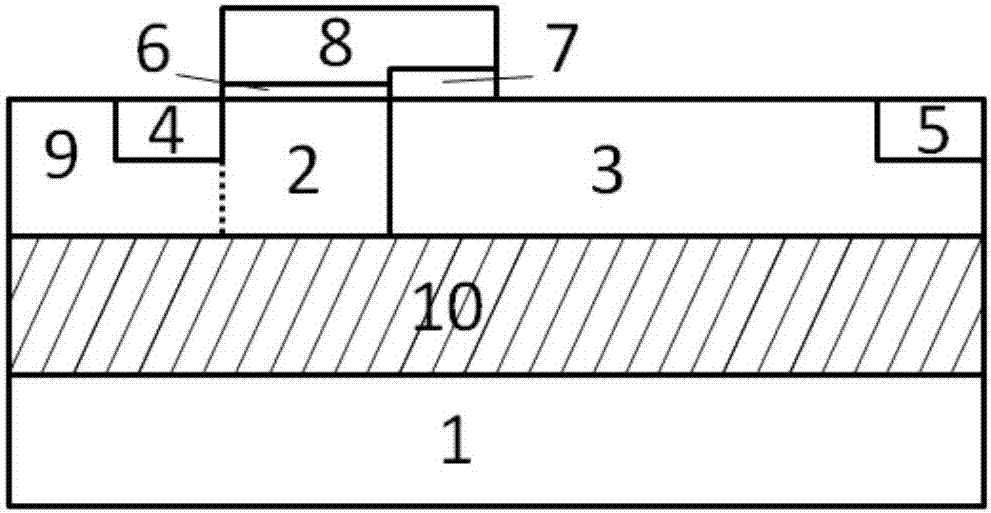

Radio-frequency LDMOS (Laterally Diffused Metal Oxide Semiconductor) device and manufacturing method thereof

ActiveCN104538441AIncrease drive currentLower on-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceRadio frequency

The invention discloses a radio-frequency LDMOS (Laterally Diffused Metal Oxide Semiconductor) device. A drift region is in a nonuniform structure formed by a first ion injection region and a second ion injection region; the first ion injection region is self-aligned to a polysilicon gate; the second ion injection region is defined by photoetching and is at a distance from the polysilicon gate; a crossover region of the first ion injection region and the second ion injection region has higher doping concentration which can improve driving current of the device and reduce switch-on resistance of the device; the lower doping concentration of the first ion injection region can reduce the intensity of an electric field on the edge of the polysilicon gate, improve breakdown voltage of the device, reduce injection capacity of a hot carrier on the edge of the polysilicon gate and improve robustness of the device; and the lower doping concentration and great depth of the second ion injection region can reduce output capacitance of the device. The invention further discloses a manufacturing method of the radio-frequency LDMOS device.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

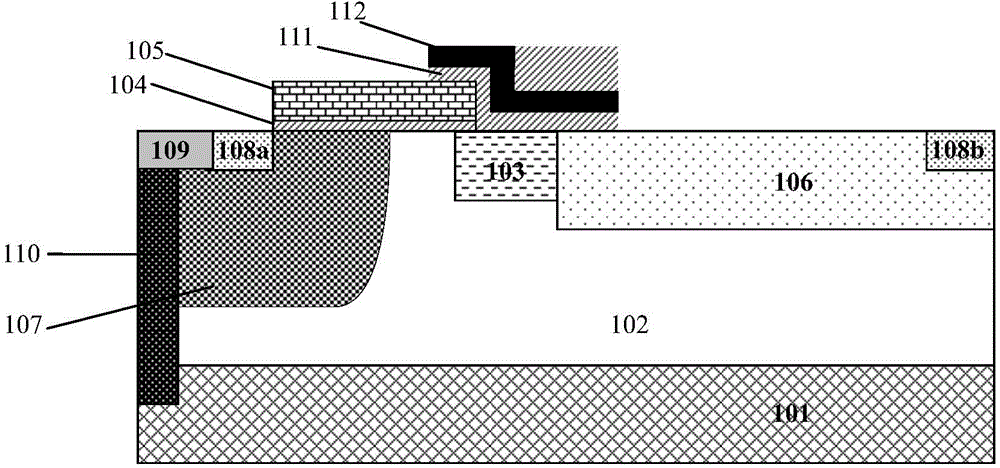

N-type LDMOS device and technical method thereof

InactiveCN105140289AImprove featuresLower on-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesLDMOSEngineering

The invention discloses an N-type LDMOS device and a technical method thereof. According to the device, a low resistance substrate is provided with an N-type buried layer thereon. The N-type buried layer is provided with an N-type epitaxy thereon. The N-type epitaxy is provided with a P-well and a drift region therein. The drift region is also provided with an N-well and an STI structure therein. The P-well is also provided with a source region of the LDMOS device therein. The N-well of the drift region is provided with a drain region of the LDMOS device therein. The P-well is also provided with a heavily doped P-type region therein so as to draw forth the P-well. The surface of the N-type epitaxy is provided with a gate oxide layer and a polycrystalline silicon gate of the LDMOS device, and the two sides of the polycrystalline silicon gate are side walls. The bottom portion of the STI structure in the drift region is provided with heavily doped polycrystalline silicon. The P-type doped polycrystalline silicon layer is added to the bottom portion of the STI structure in the drift region, a P-type auxiliary exhaustion region is formed above the drift region, and a surface electric field intensity is lowered, which enable the LDMOS device to have a lower on-resistance and at the same time a higher breakdown voltage. The invention also discloses a technical method of the N-type LDMOS device.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

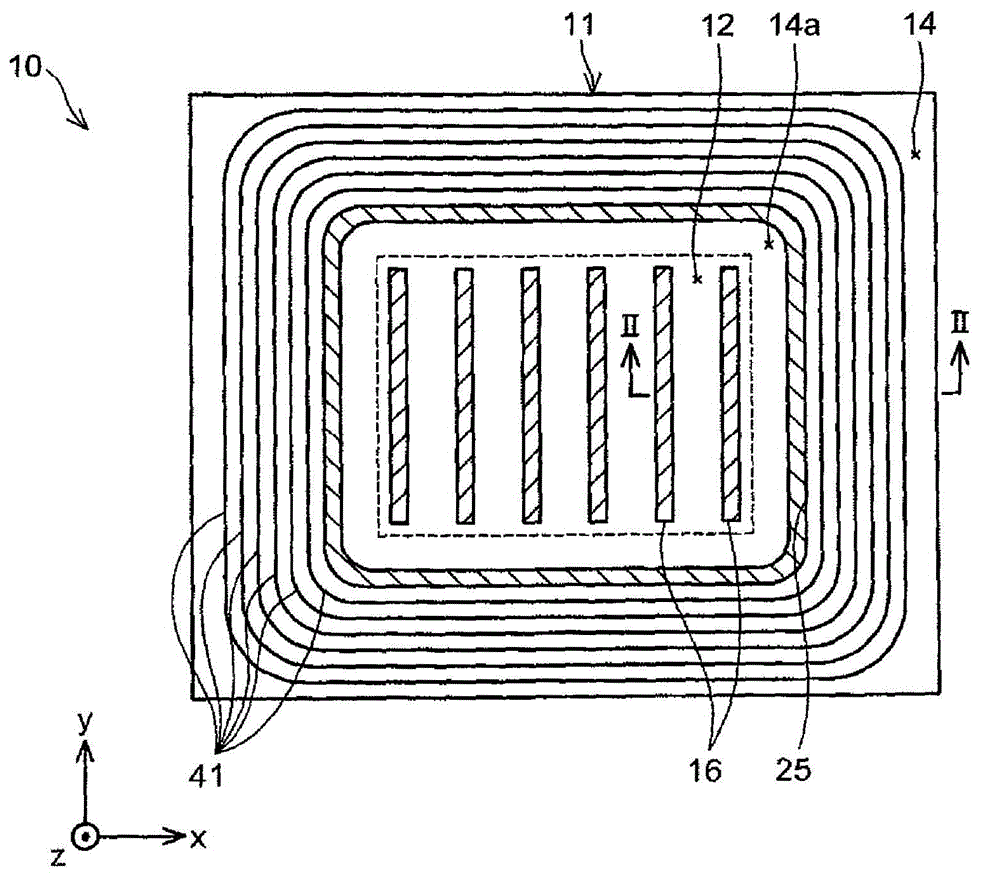

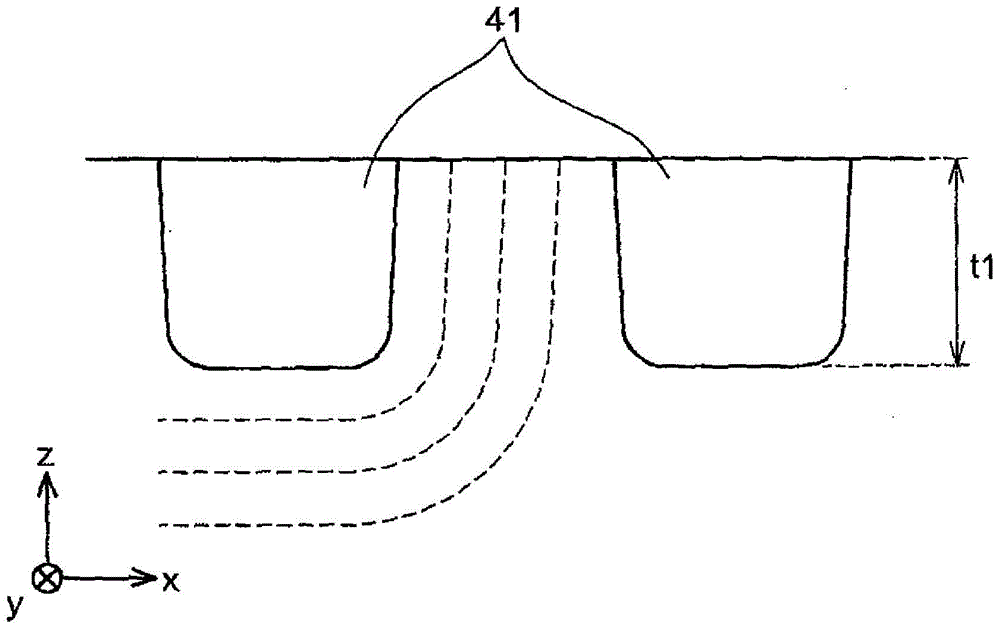

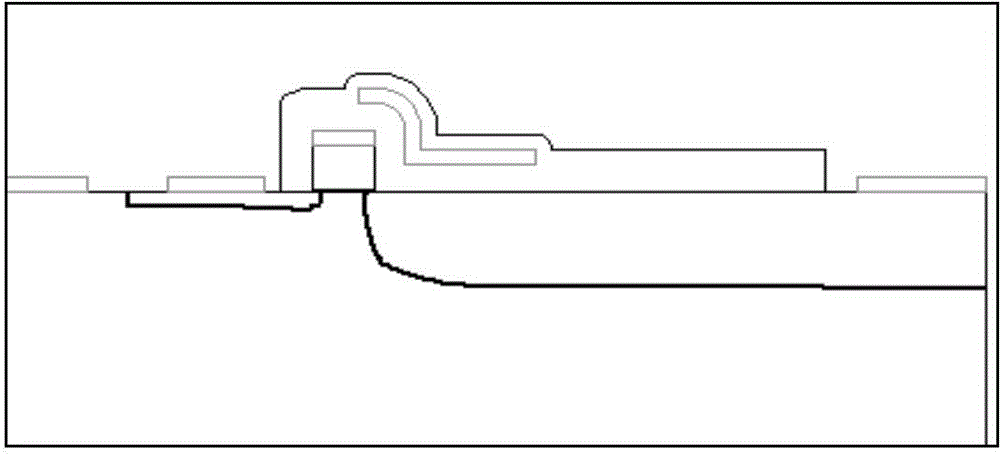

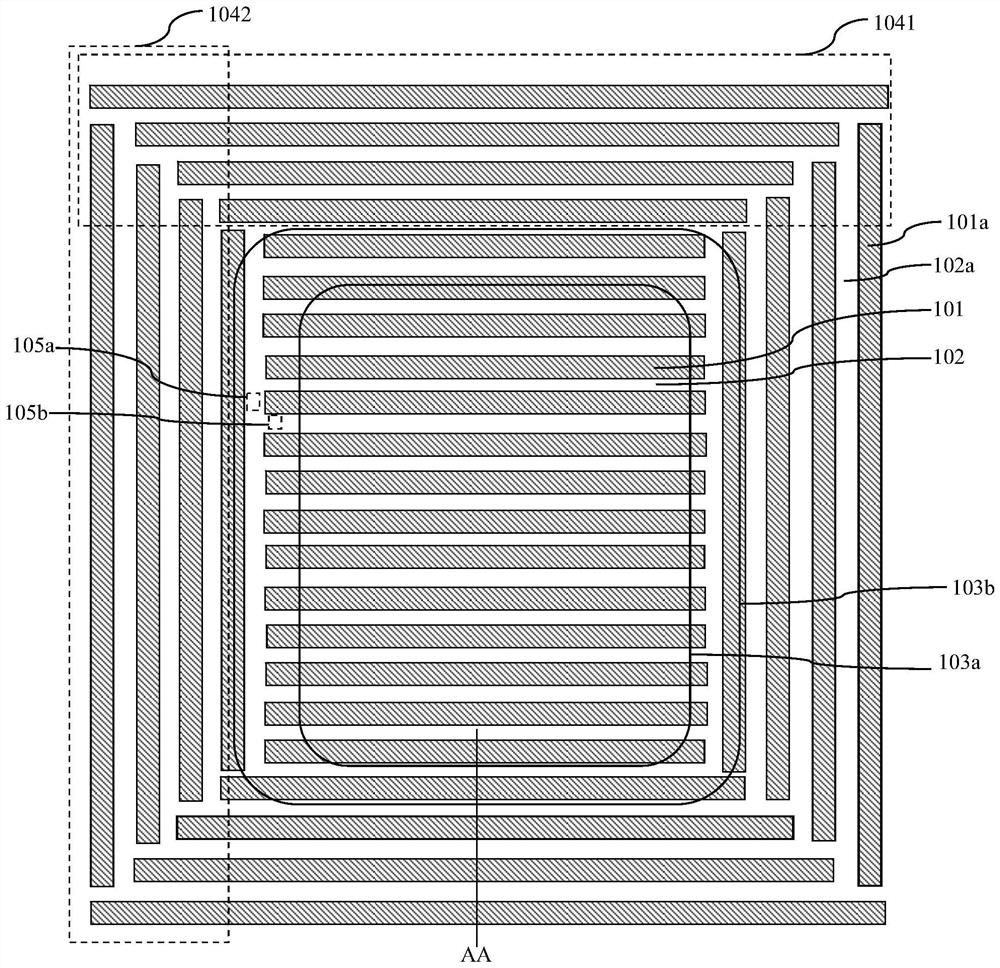

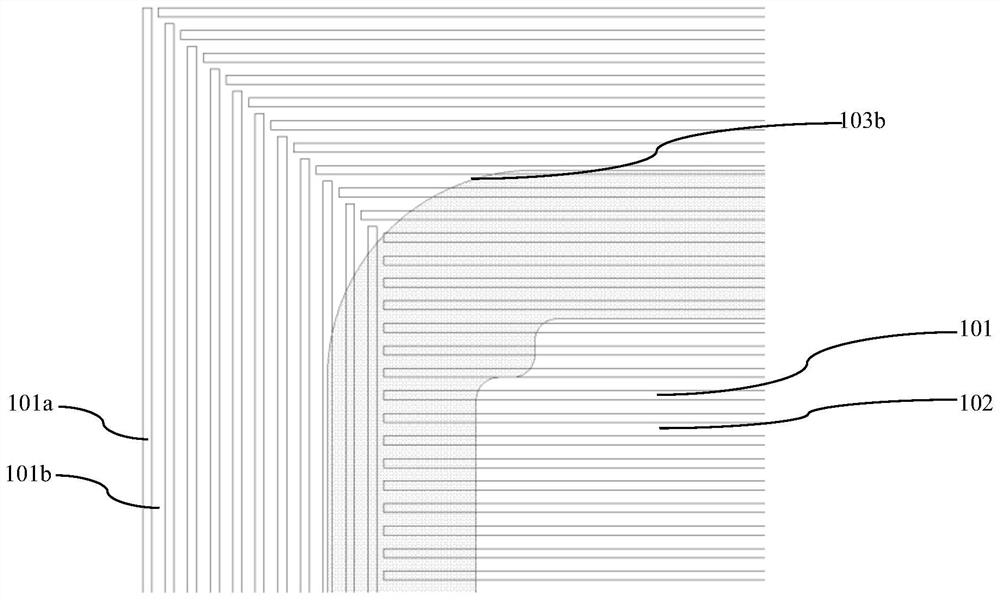

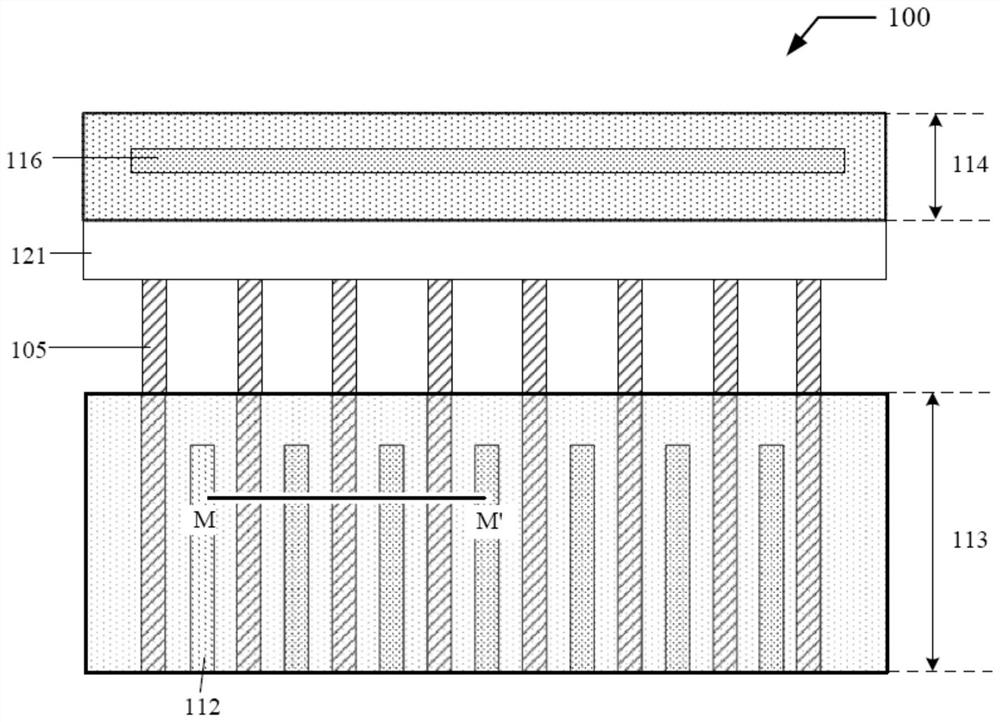

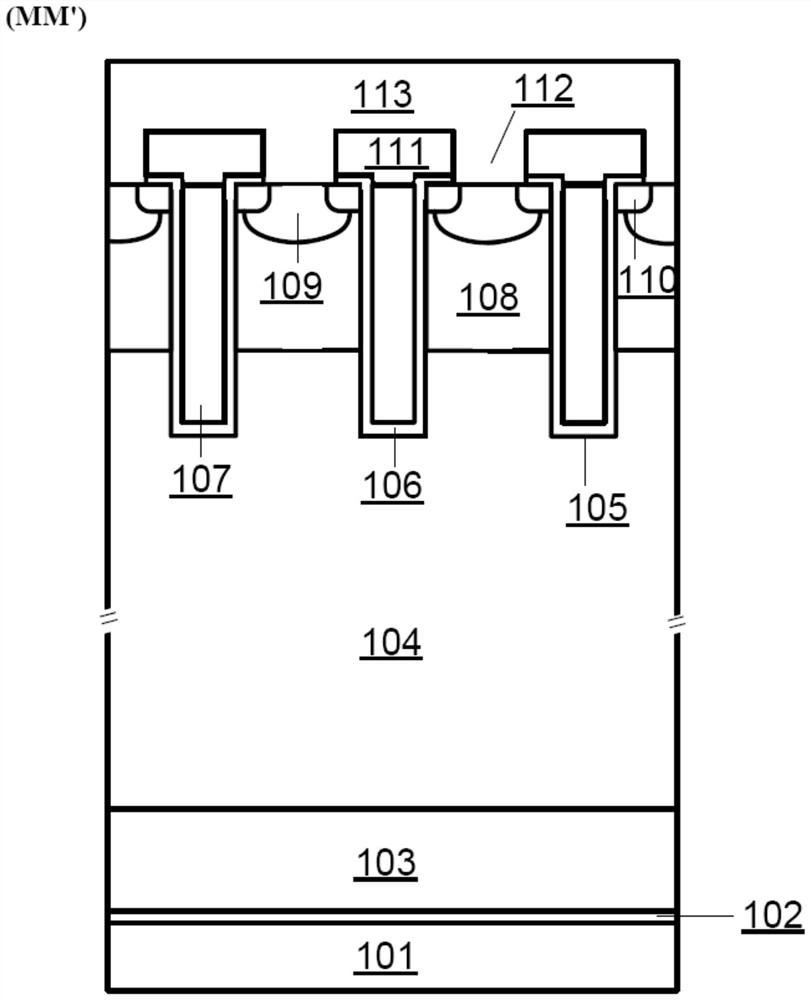

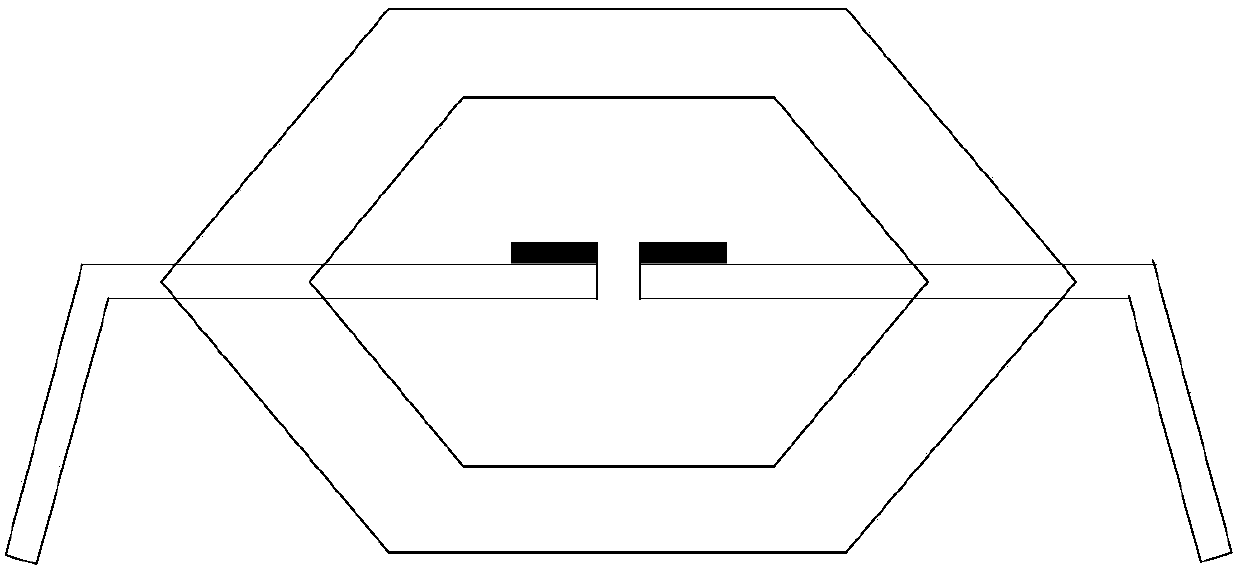

Semiconductor device with super junction structure, manufacturing method thereof, and photomask

ActiveCN104992963AGuaranteed to workGuaranteed breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesP type dopingSemiconductor

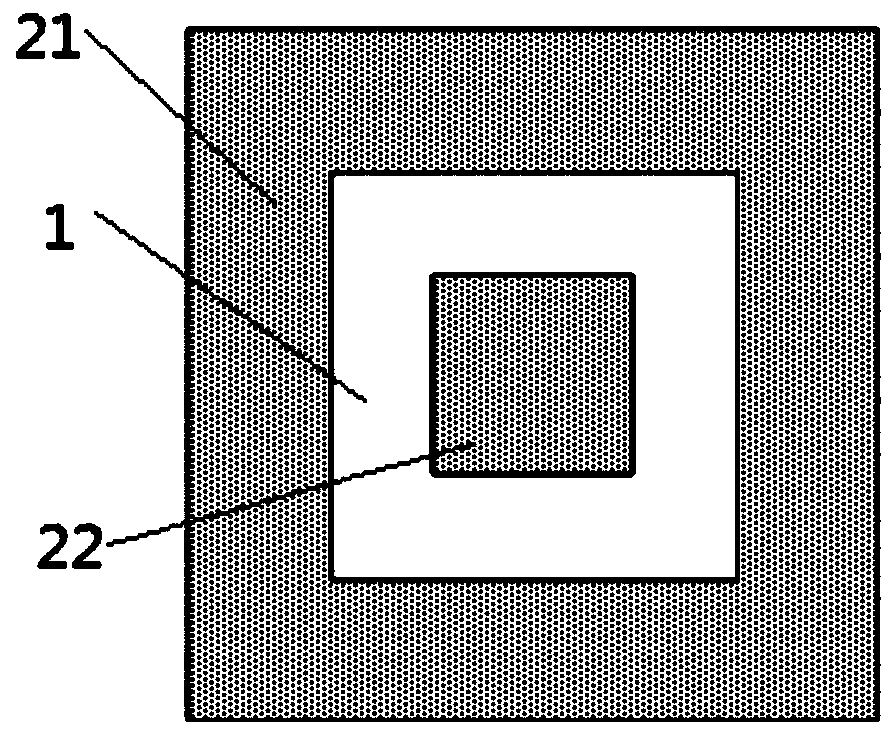

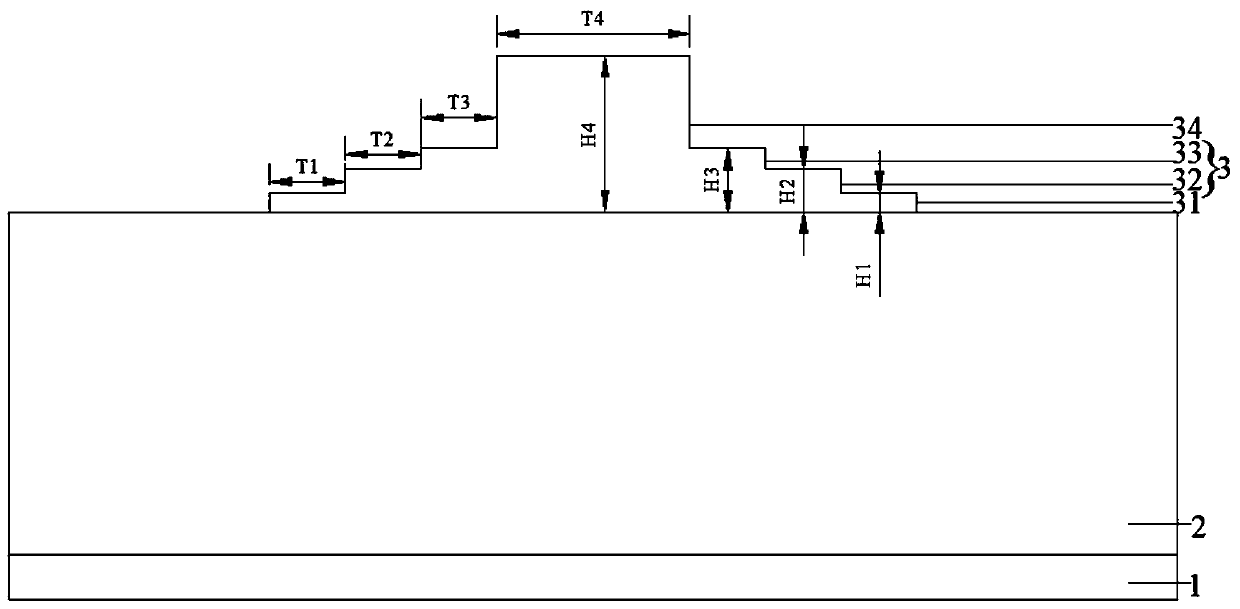

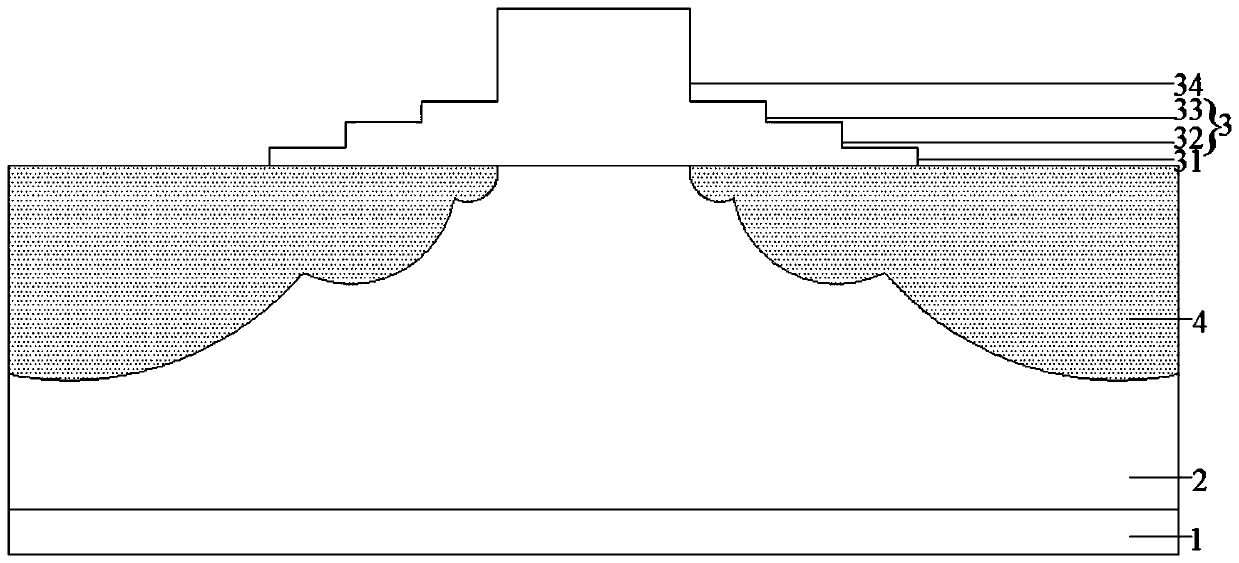

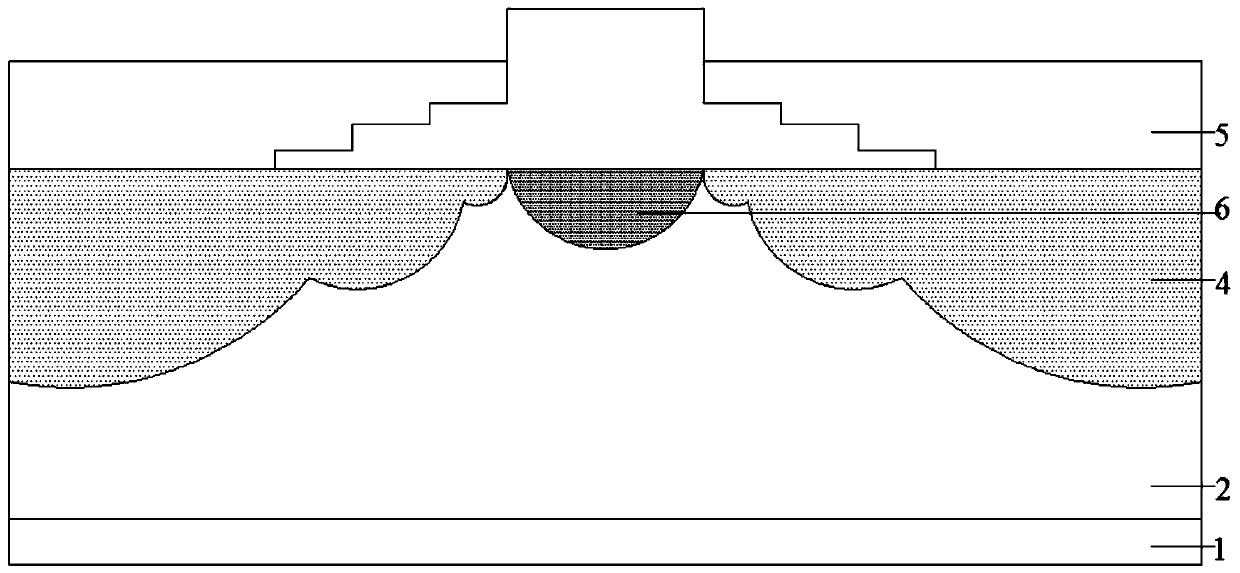

The invention provides a semiconductor device with a super junction structure, a manufacturing method thereof, and a photomask. The layout plane of the semiconductor device comprises an active region and a potential dividing ring region located at the periphery of the active region. The semiconductor device is characterized in that the active region is internally provided with multiple first P-type doping regions extending along the first direction; the multiple first P-type doping regions are arranged at equal distances in the second direction; the potential dividing ring region is internally provided with multiple second P-type doping regions extending along the first direction; the multiple second P-type doping regions are arranged at equal distances in the second direction; the breakdown voltage of each first P-type doping region is smaller than that of each second P-type doping region; and the second direction is perpendicular to the first direction. Contradiction between conduction resistance and a device area can be overcome, the breakdown point of the device is constantly in the active region, and the device can be ensured to work normally.

Owner:HANGZHOU SILAN MICROELECTRONICS

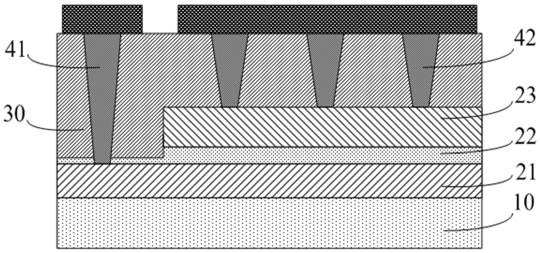

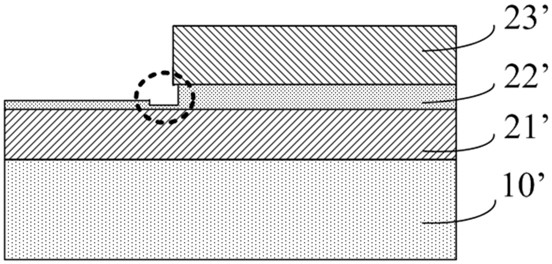

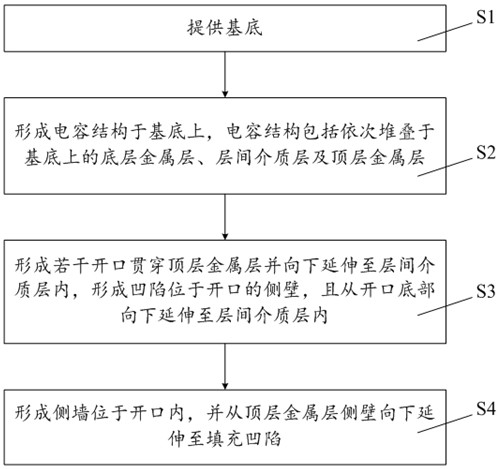

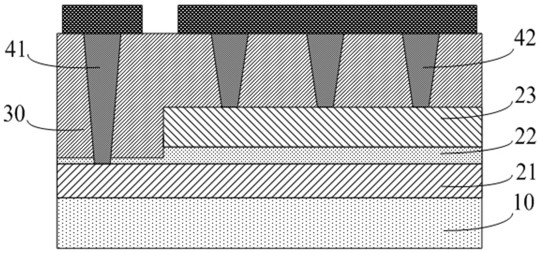

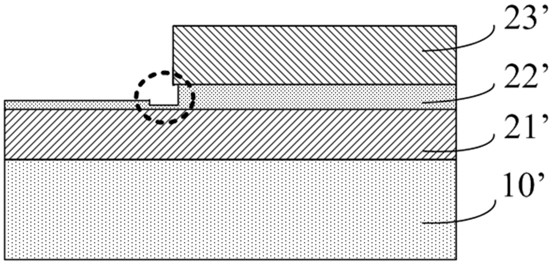

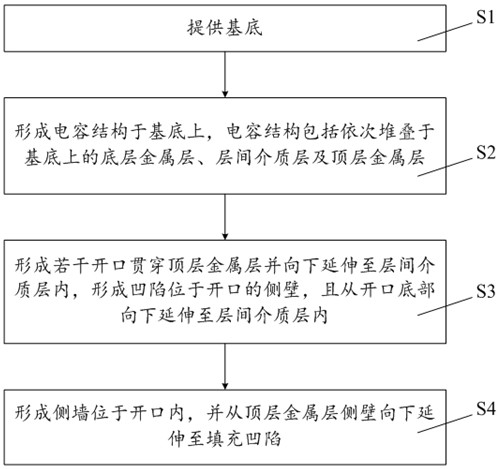

Metal capacitor structure and preparation method thereof

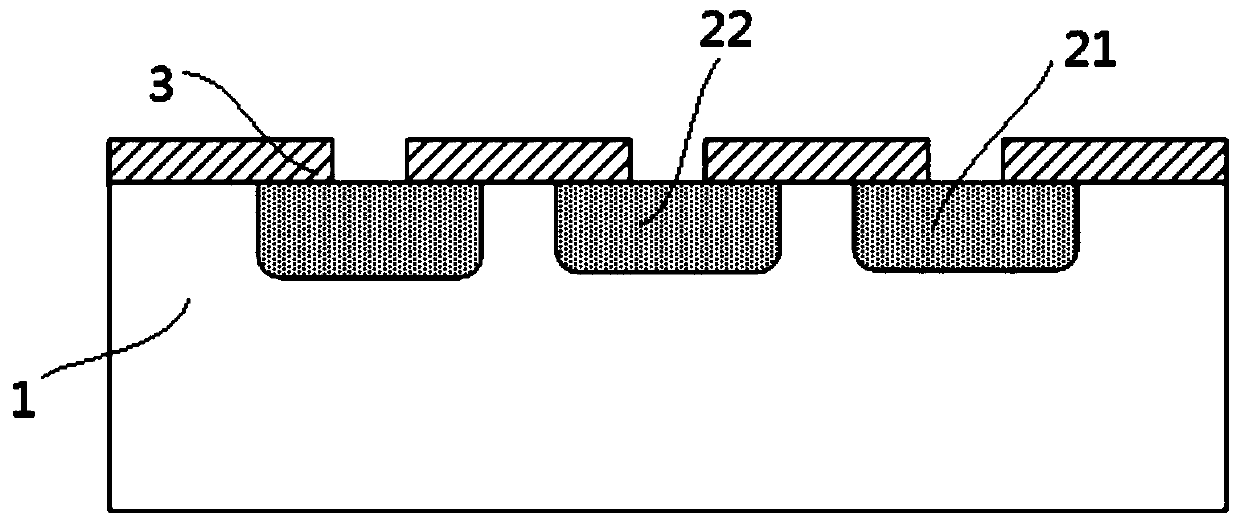

ActiveCN113517400ALower breakdown voltageGuaranteed breakdown voltageSolid-state devicesCapacitorsCapacitanceStructural engineering

The invention provides a metal capacitor structure and a preparation method thereof. The structure is characterized by comprising a substrate, a capacitor structure, a plurality of openings, a recess, and a side wall; the capacitor structure comprises a bottom metal layer, an interlayer dielectric layer and a top metal layer which are sequentially stacked on the substrate; the plurality of openings penetrate through the top metal layer and extend downwards into the interlayer dielectric layer; the recess is positioned on the side wall of the opening and extends downwards into the interlayer dielectric layer from the bottom of the opening; and the side wall is located in the opening and extends downwards from the side wall of the top metal layer to fill the recess; The breakdown voltage of the metal capacitor structure is improved.

Owner:GUANGZHOU CANSEMI TECH INC

High-Early-voltage lateral transistor structure and preparation method thereof

PendingCN110828559ASuppress width changesHigh early voltageTransistorSemiconductor/solid-state device manufacturingImpurity dopingPhysical chemistry

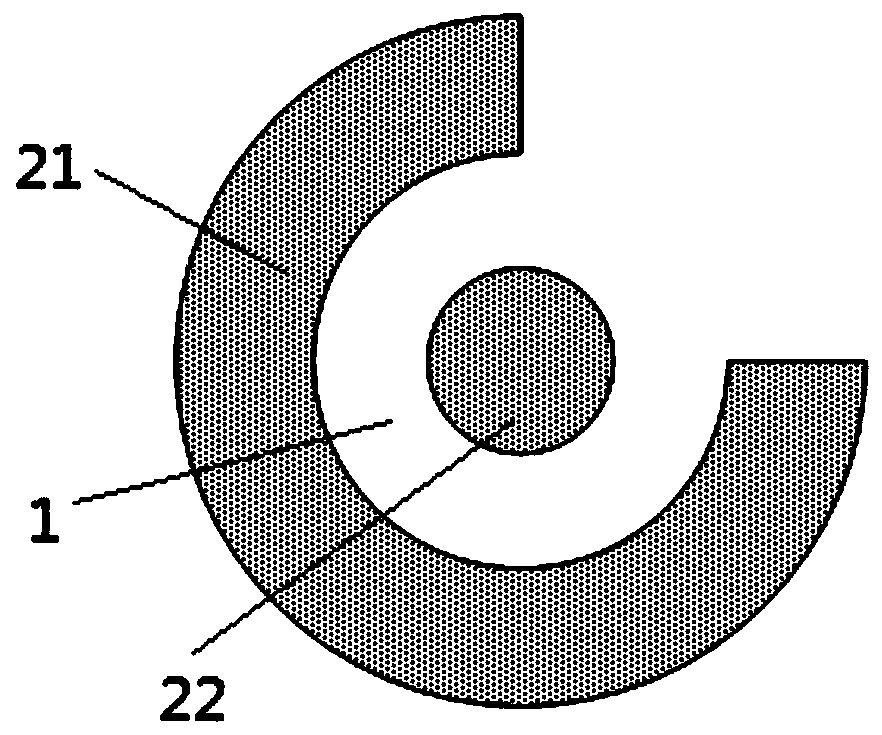

The invention discloses a high-Early-voltage lateral transistor structure and a preparation method thereof. The lateral PNP transistor is formed by performing selective P-type impurity doping on an N-type epitaxial layer, that is, an emitter region of the PNP transistor is formed by a P-type doped region, a collector region of the PNP transistor is formed by a complete or partial annular P-type doped region outside the emitter region, and an N-type doped epitaxial layer is arranged between the two P-type doped regions to form a base region of the PNP transistor, so that a lateral P-N-P structure is formed, and the lateral PNP transistor is formed. Different from the traditional PNP transistor, the P-type collector region of the lateral PNP transistor with the novel structure is independently doped, the impurity concentration of the P-type collector region is lower than that of the N-type base region, when the CE voltage of the PNP transistor is increased, a CB junction space charge region is mainly expanded to the P-type collector region because the concentration of the P-type collector region of the lateral PNP transistor is lower than that of the N-type collector region, and thewidth change of the base region caused by the increase of the CE voltage is inhibited, so that a relatively high Early voltage is obtained.

Owner:XIAN MICROELECTRONICS TECH INST

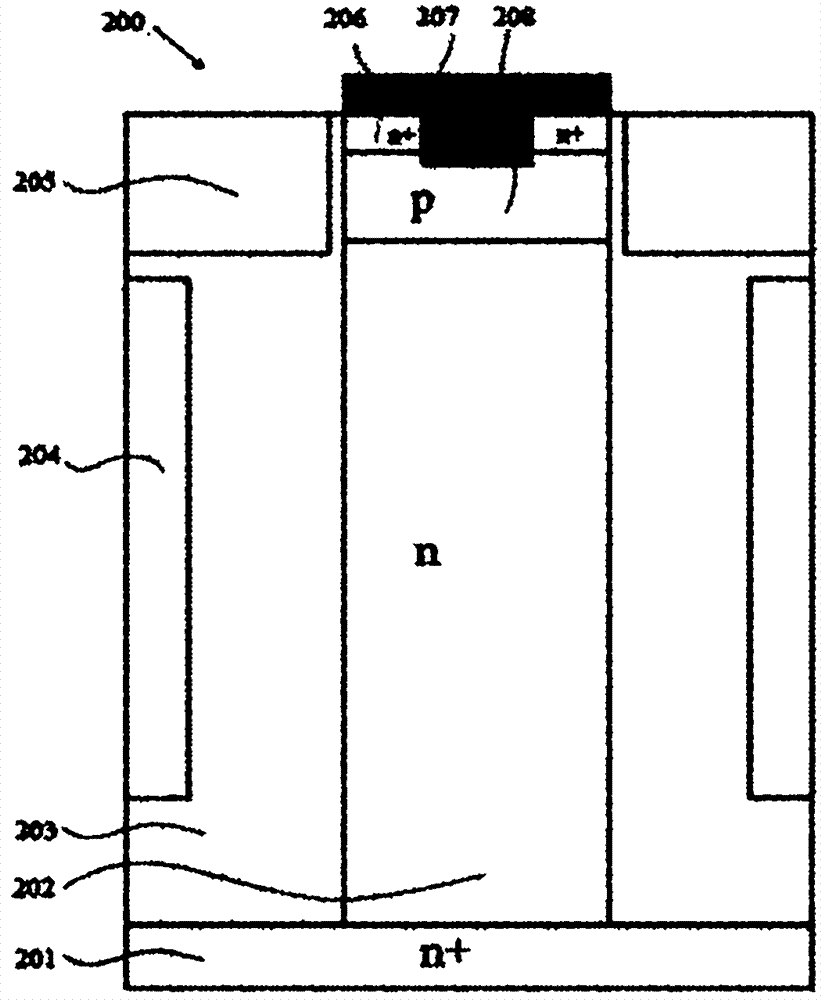

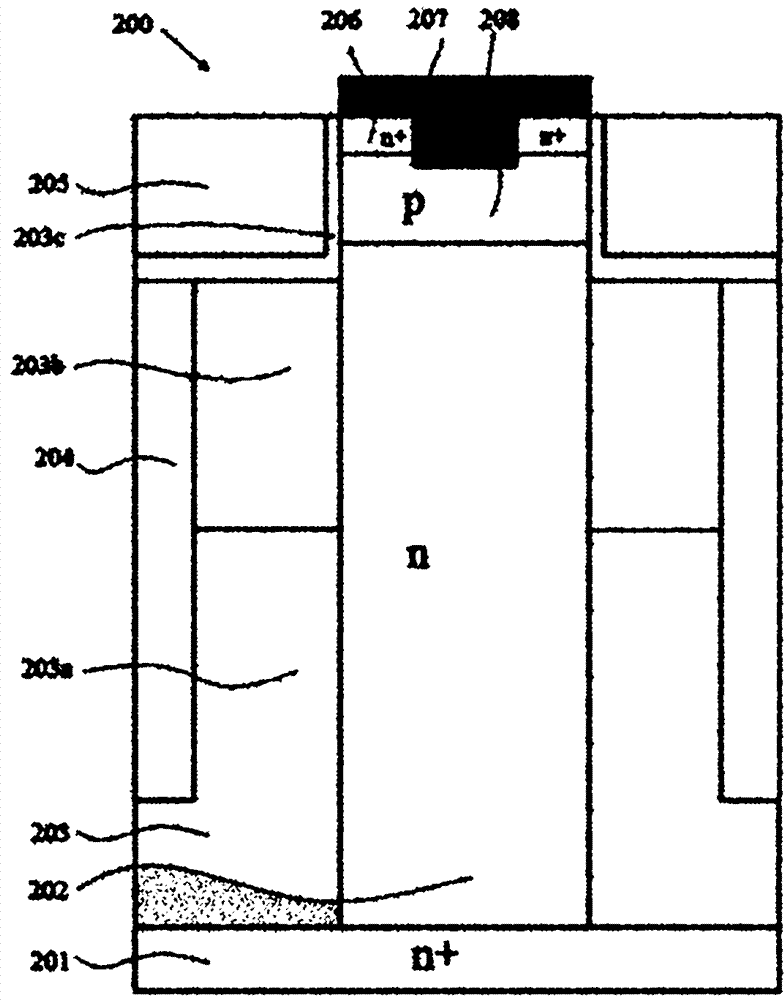

Grid enhanced-power semiconductor field effect transistor

InactiveCN102148256BLarge structure sizeSmall sizeSemiconductor devicesMOSFETElectrical resistance and conductance

The invention provides a grid enhanced-power semiconductor field effect transistor which comprises a drain region (201), a drift region (202), a dielectric layer (203), a split grid (204), a grid electrode (205), an n+ layer (206), a source electrode (207) and a channel region (208), wherein K values of the dielectric layer (203) are distributed according to a certain law, namely, the K values become smaller from the source electrode to the drain electrode. In the grid enhanced-power semiconductor field effect transistor, the dielectric layer, the K values of which are distributed according to a certain law, is used for replacing an original side oxide structure, therefore, the drain-source on resistance is reduced on the condition that the withstand voltage of a device is not sacrificed. The transistor is compatible with the conventional MOSFET (metal-oxide-semiconductor field effect transistor) process, has very strong feasibility and can meet the application requirements of a power electronic system more easily.

Owner:HARBIN ENG UNIV

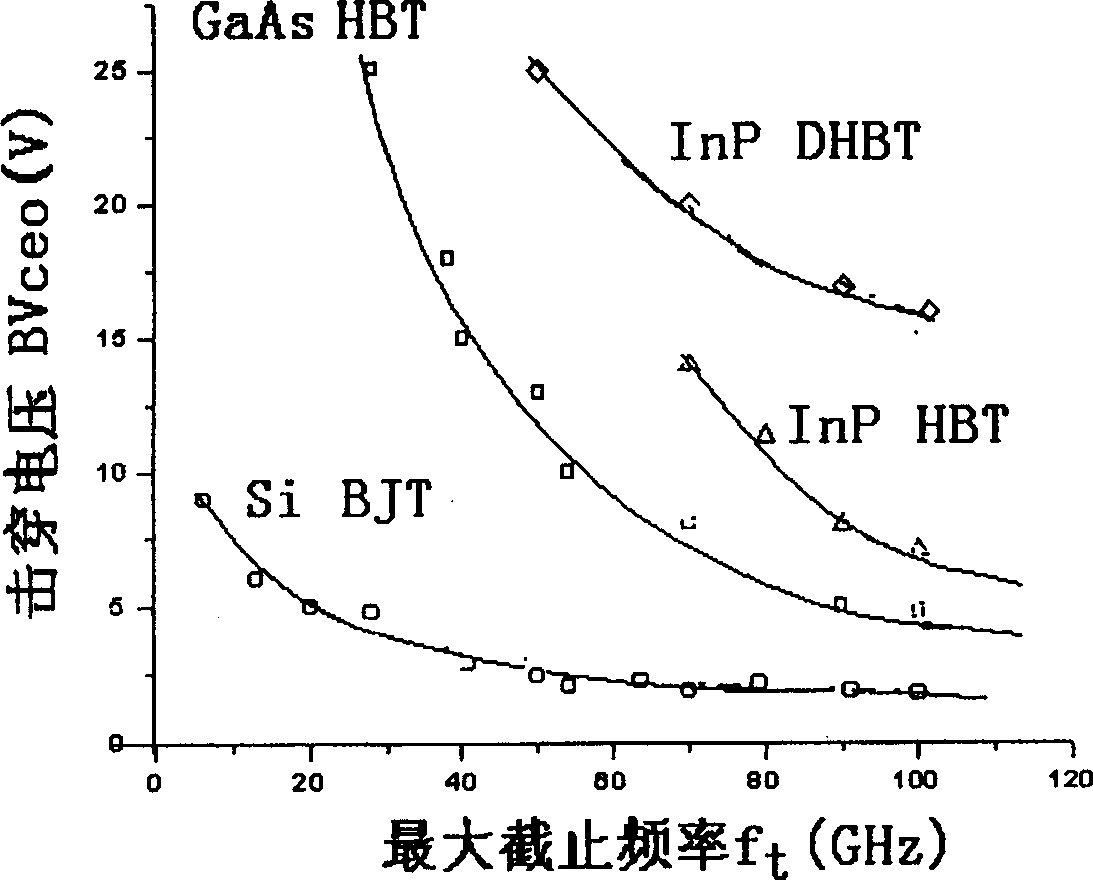

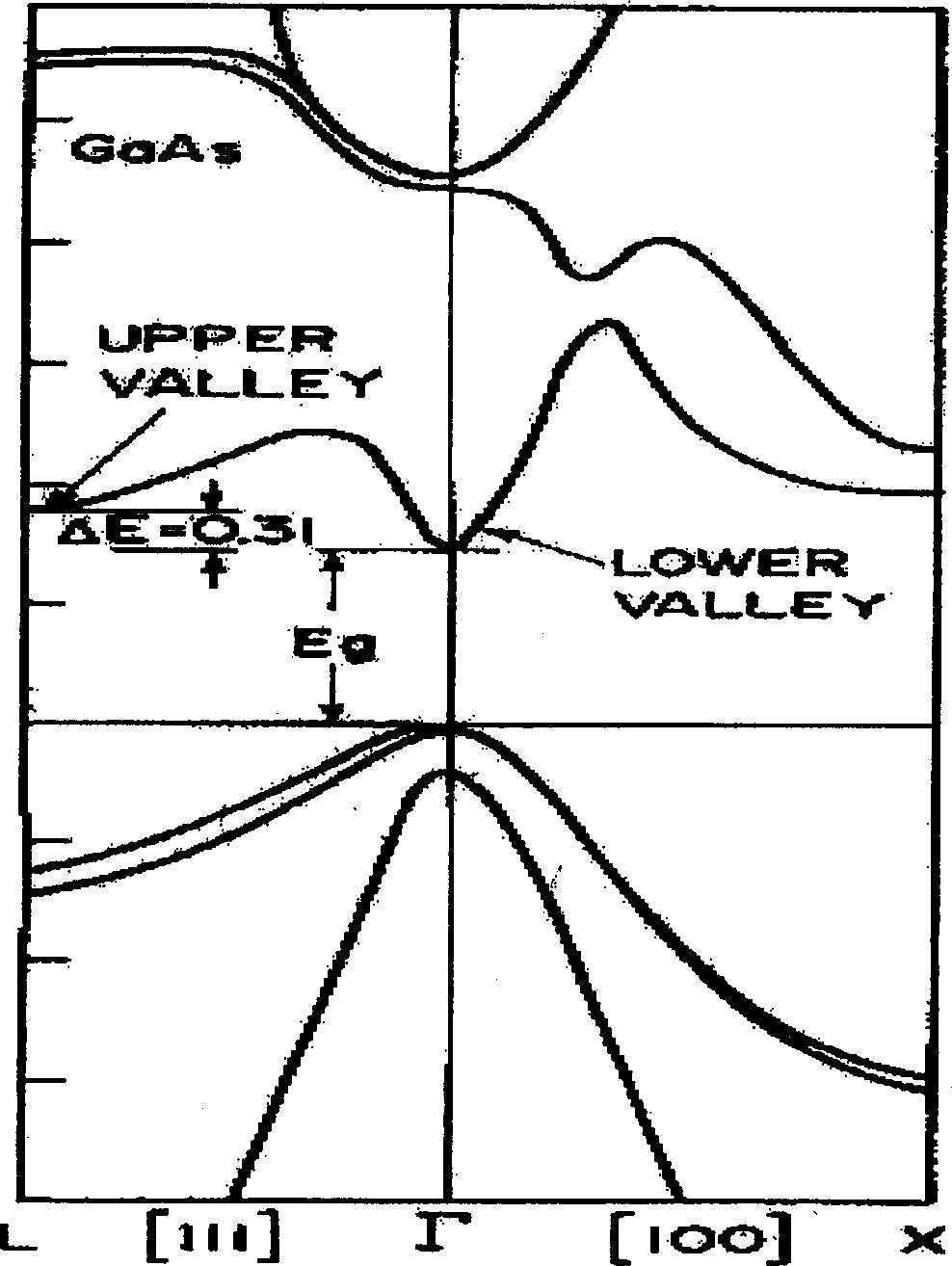

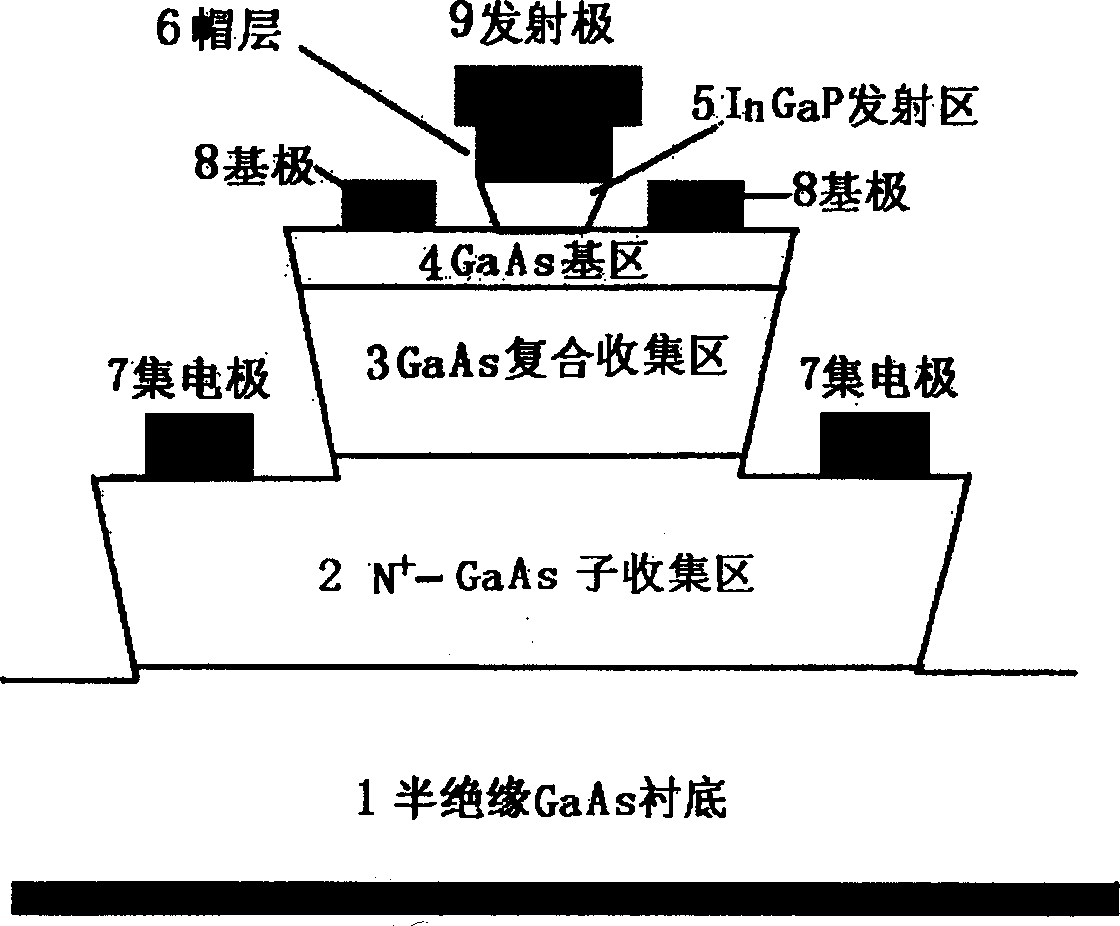

GaAs based composite collecting region trajectory transmitting heterojunction bipolar transistor

InactiveCN1464564ACharacteristic Frequency GuaranteeRaise the eigenfrequencySemiconductor devicesGallium arsenideSemi insulating

The invention discloses a GaAs based composite collecting region trajectory transmitting heterojunction bipolar transistor comprising, a semi-insulating GaAs substrate, a N#+[+] adulterated GaAs collecting sub-region grown on the semi-insulating GaAs substrate, a composite collecting region grown on the N#+[+] adulterated GaAs collecting sub-region, a heavy type P GaAs base grown on the composite collecting region. On the base region a type N InGaP emitting region is formed the top of which is a cap layer used for making Ohm contact, an emitting electrode is formed on the cap layer, and a base electrode is formed on the type N InGaP emitting region on the base region.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

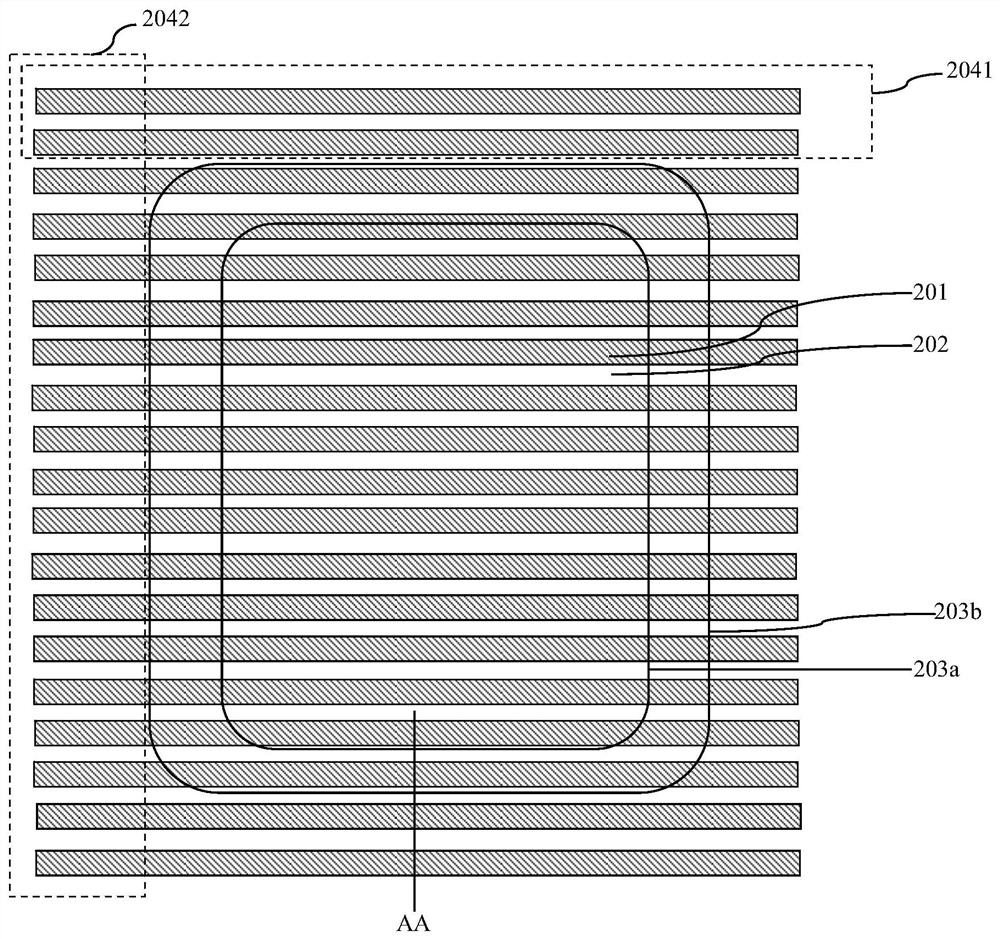

Super junction device

ActiveCN113782584AImprove breakdown voltageGood process compatibilityFinal product manufactureSolid-state devicesChinese charactersEngineering

The invention discloses a super junction device. A charge flow region comprises a first super junction structure formed by alternately arranging first P-type columns and first N-type columns. In the width direction of the first P-type columns, the first P-type columns and the first N-type columns continue to be alternately arranged and enter the first terminal area. In the length direction of the first P-type columns, the first P-type columns and the first N-type columns of the charge flow region directly extend into a partial region, namely a straight strip-shaped region, of the second terminal region, and a region shaped like a Chinese character 'hui' is arranged on the outer side of the straight strip-shaped region. And the width of the straight strip-shaped region is set according to the widening width of the depletion region in the second terminal region when the super junction device is withstand voltage. And a second super junction structure formed by alternately arranging second P-type columns and second N-type columns is arranged in the rectangular-ambulatory-plane region. According to the invention, the advantages of the full-straight-strip-shaped super junction structure and the homocentric-square-shaped super junction structure can be compatible and the defects of the two super junction structures can be overcome, so that the breakdown voltage of the device can be improved and the problem of unstable test of the device can be solved.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Fast recovery diode chip with low-concentration doped emitter region and its manufacturing method

ActiveCN103579367BExcellent electrical characteristic parametersIncreased hole concentration at the junctionSemiconductor/solid-state device manufacturingSemiconductor devicesVoltage dropP type doping

The invention relates to a power device and a manufacturing method of the power device, in particular to a fast recovery diode chip of a low-concentration doped emitter region and a manufacturing method of the fast recovery diode chip of the low-concentration doped emitter region. The fast recovery diode chip of the low-concentration doped emitter region comprises a metal cathode, a metal anode, a P-type doped layer, an N-type doped layer, an N-type substrate arranged between the P-type doped layer and the N-type doped layer, field oxide layers and passivation protective layer structures, wherein the metal anode is a low-concentration P-type doped region, the metal cathode is a low-concentration N-type buffer doped region and a low-concentration N-type reinforced doped region, the special manufacturing mode of injection doped of the reverse side is formed through an obverse side protection technology, and a device structure is formed through the special manufacturing mode of injection doped of the reverse side. According to the fast recovery diode chip of the low-concentration doped emitter region and the manufacturing method of the fast recovery diode chip of the low-concentration doped emitter region, due to the fact that the doped concentration of an anode emitter region and the doped concentration of a cathode emitter region are reduced, the self-key electric potential difference of a PN-junction is reduced, the total number of injection holes of the P-type doped region is reduced, performance of a fast recovery diode is integrally optimized, it is ensured that the fast recovery diode has low forward communication voltage drop, and the dynamic performance of a device is improved.

Owner:STATE GRID CORP OF CHINA +2

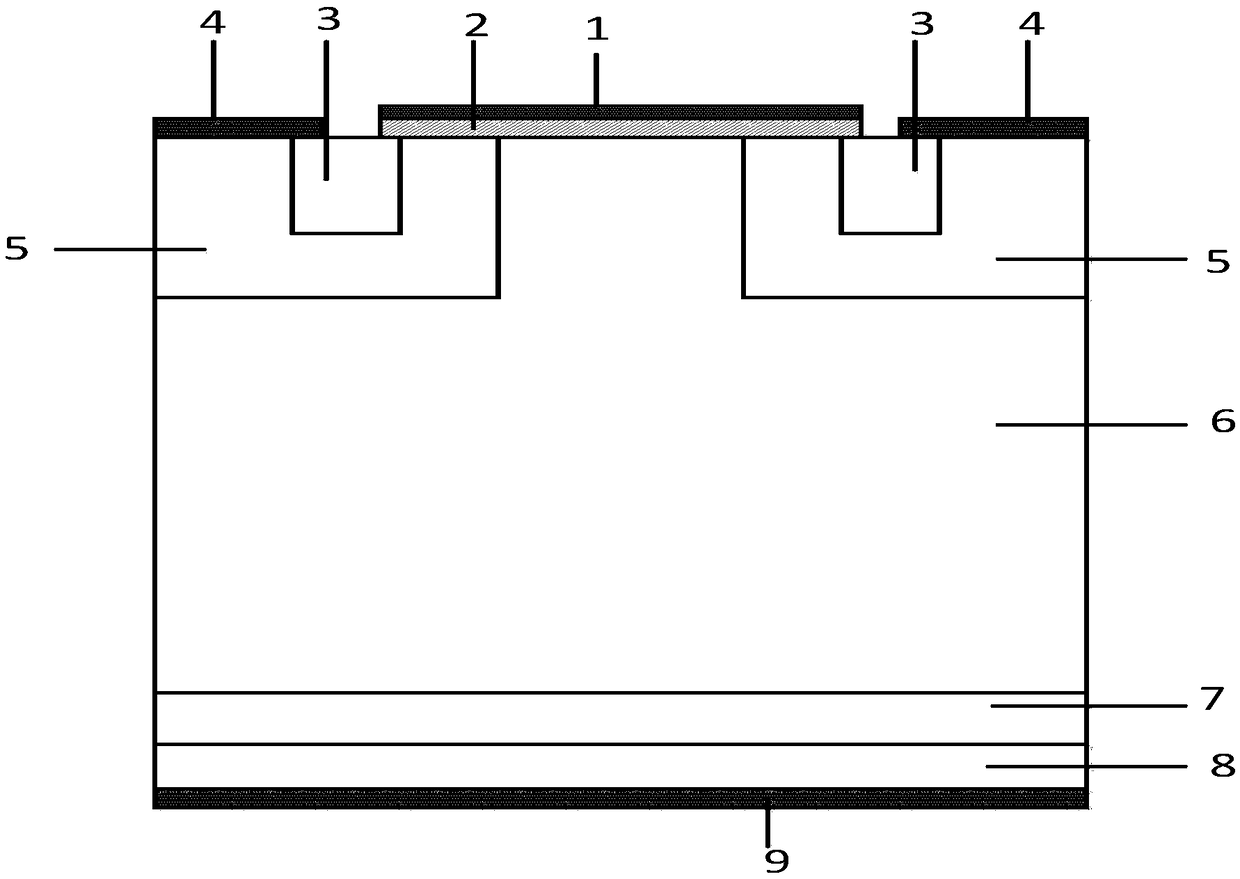

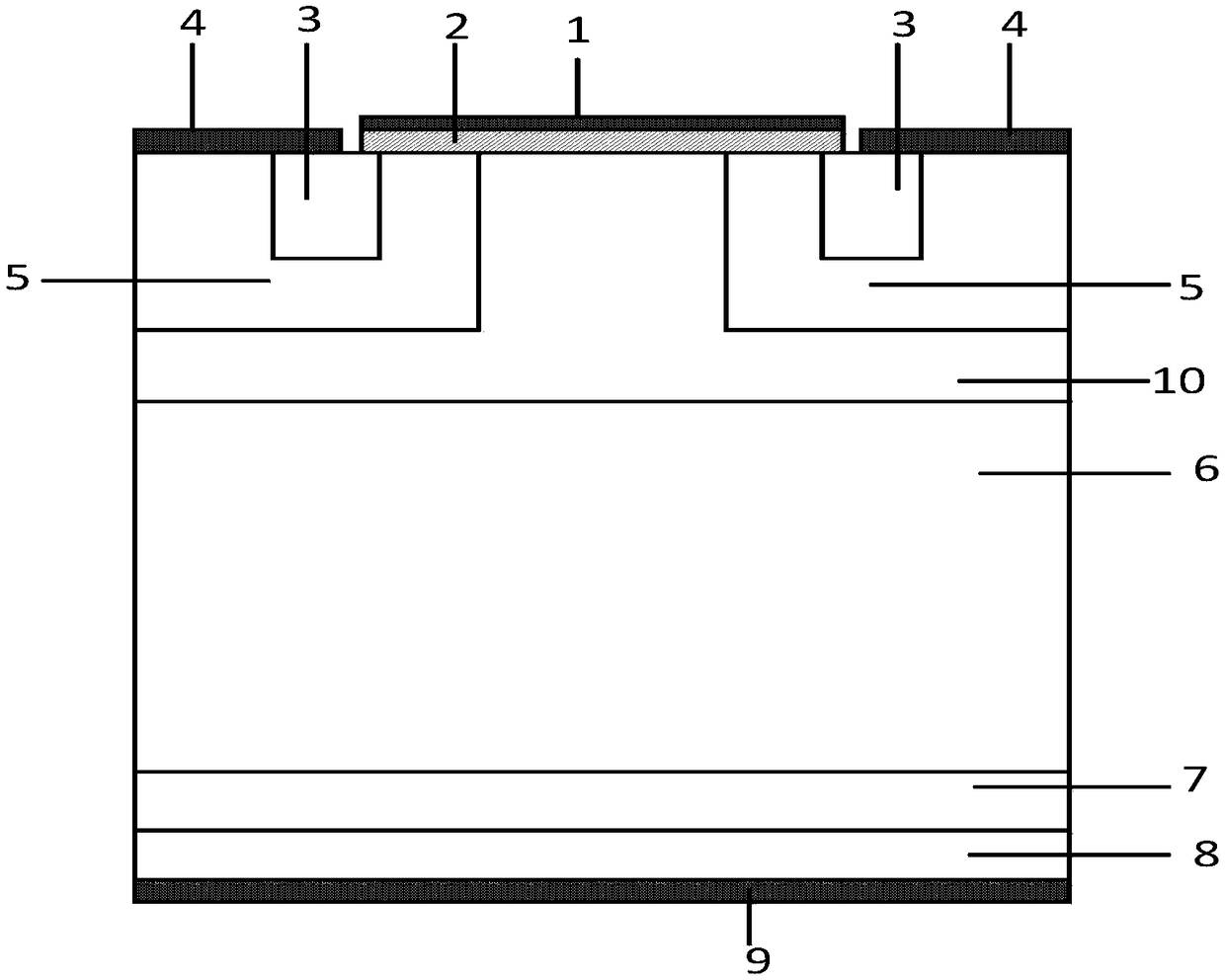

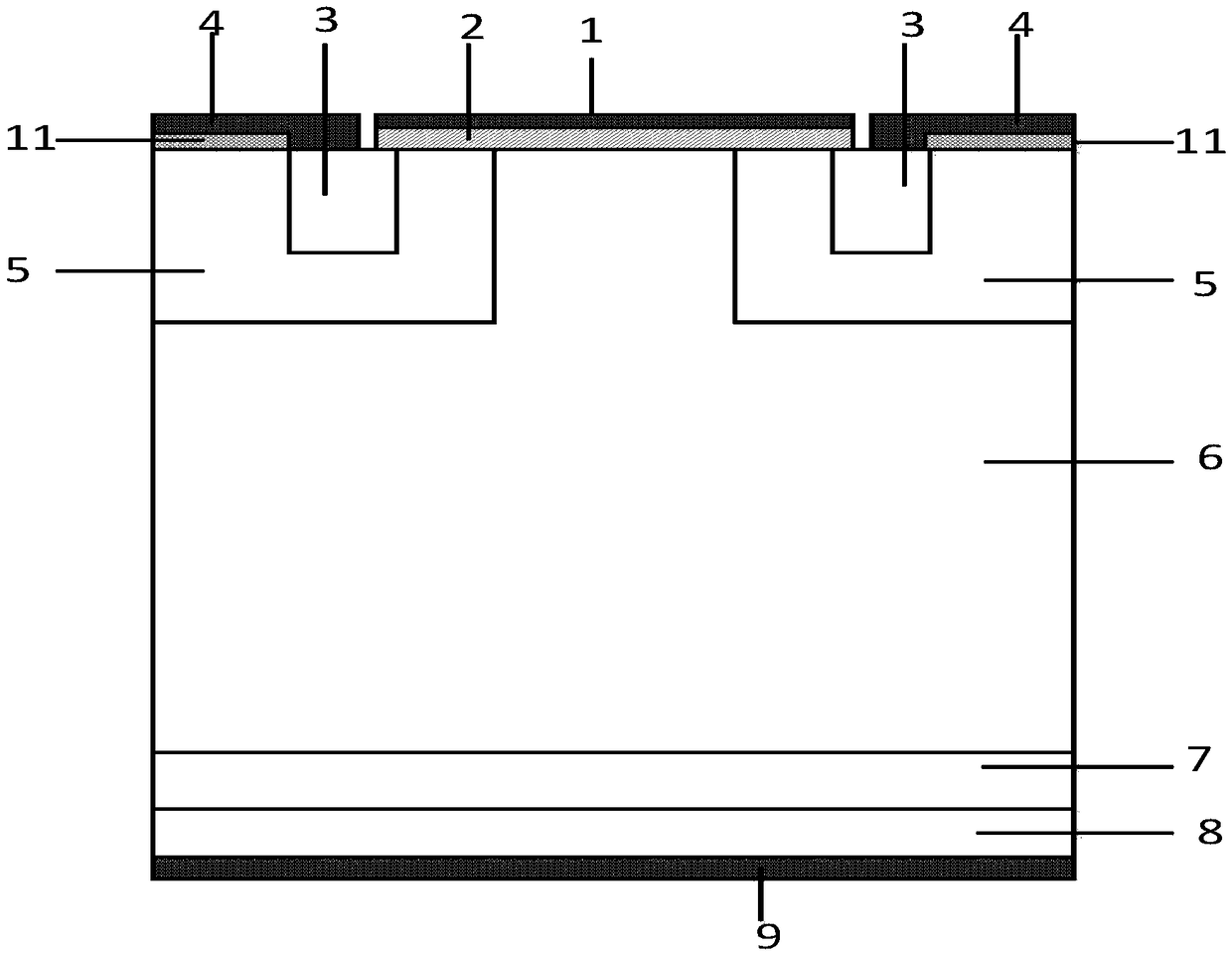

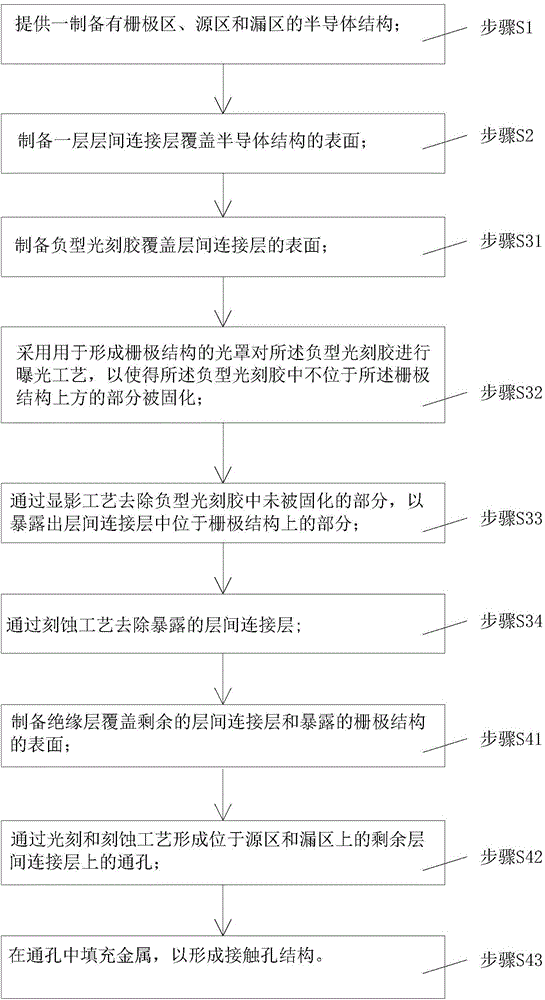

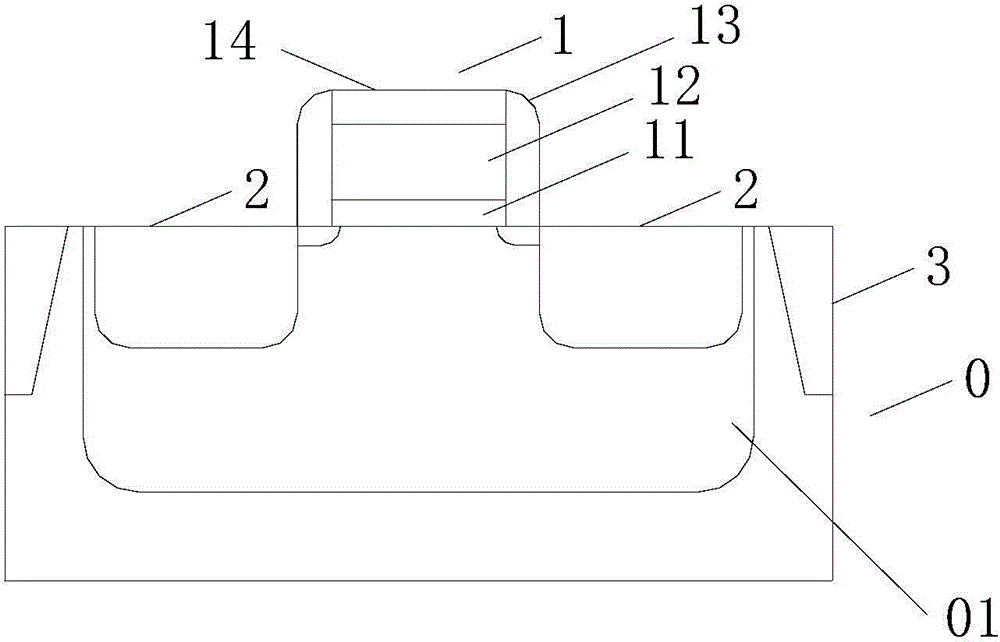

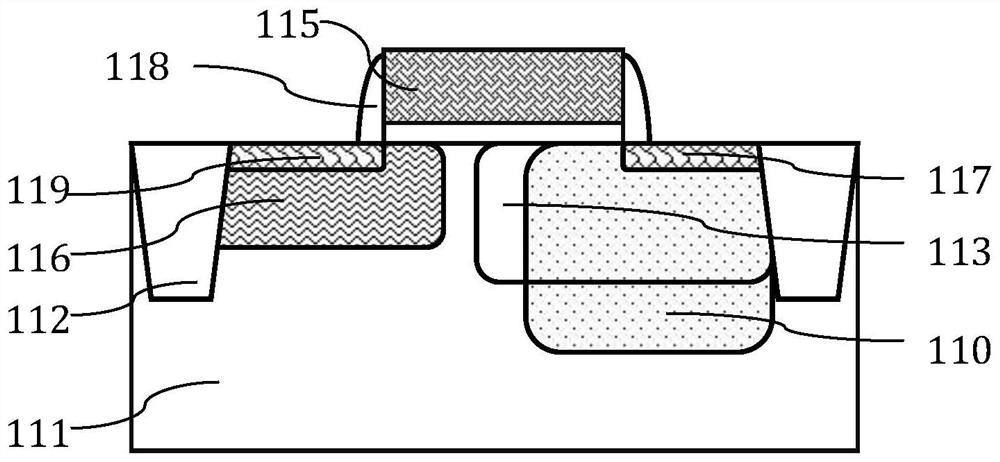

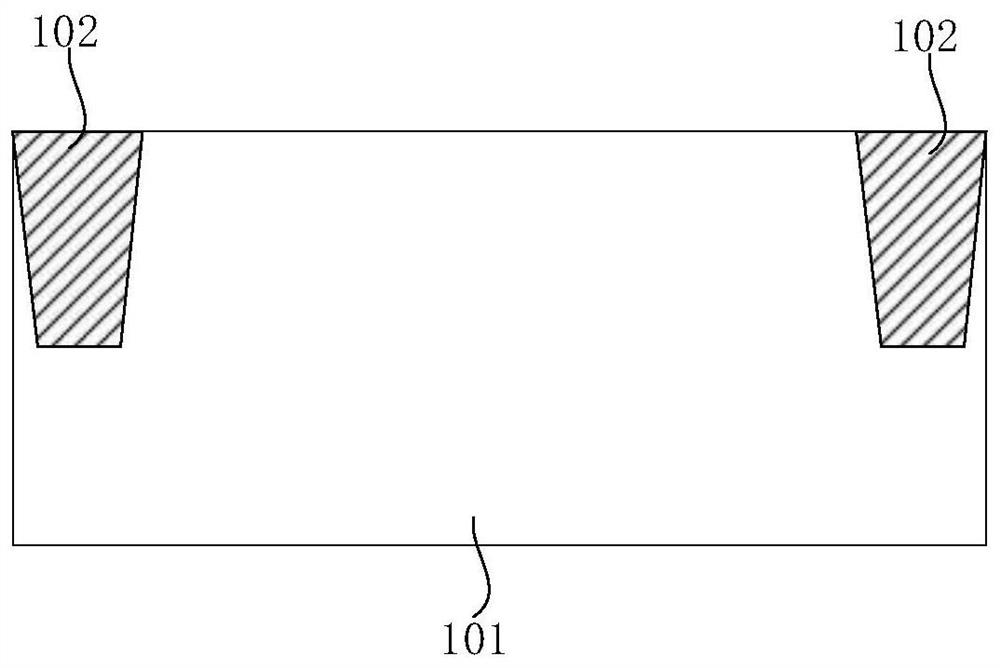

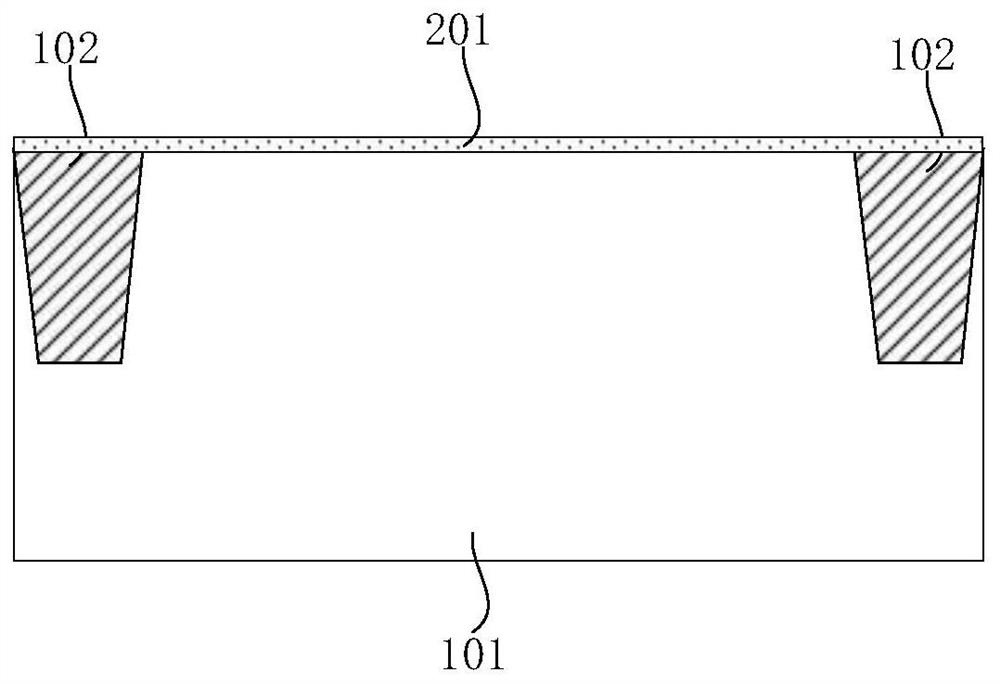

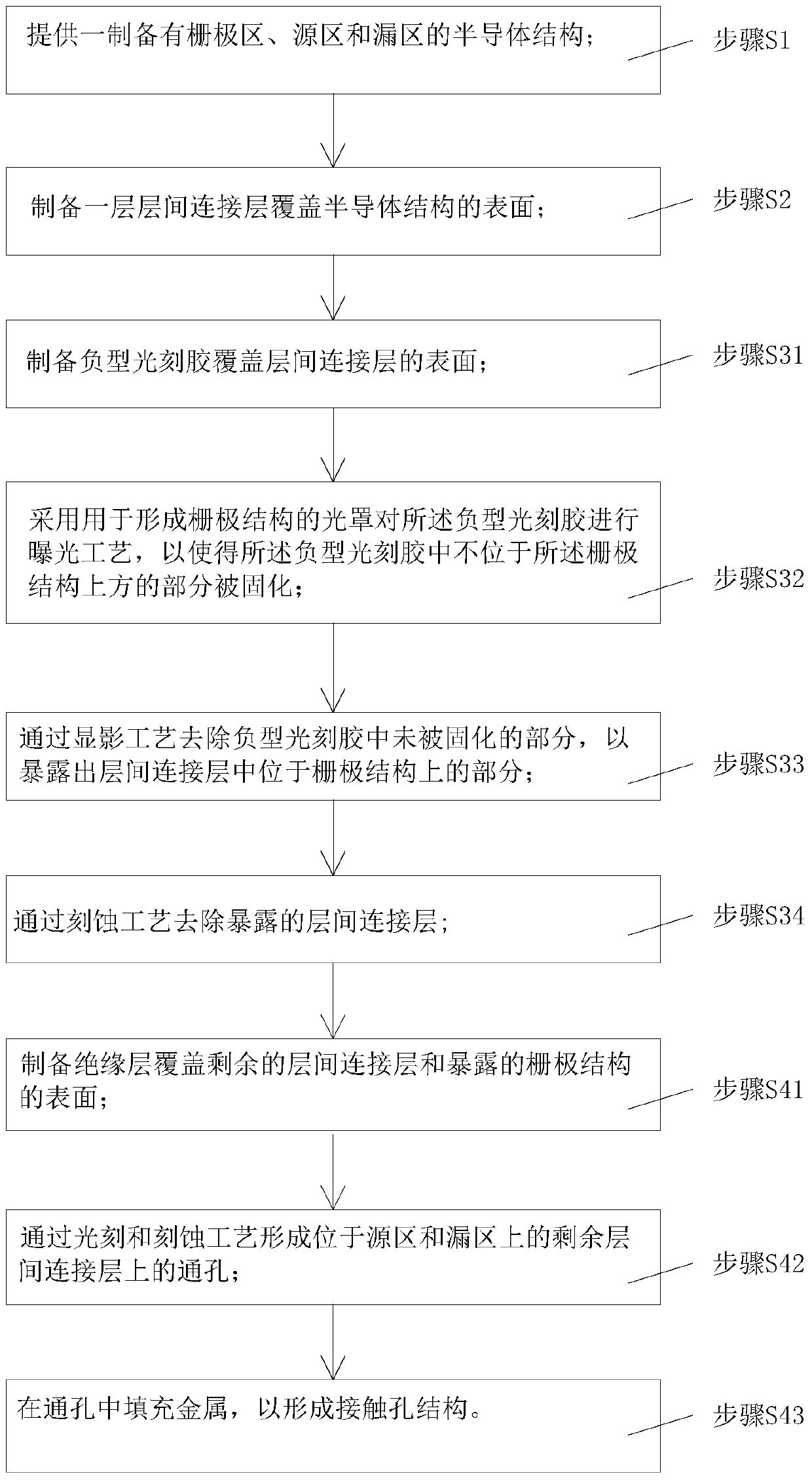

Semiconductor and fabrication method thereof

ActiveCN105789112AGuaranteed breakdown voltageReduce areaSemiconductor/solid-state device detailsSolid-state devicesInter layerParasitic capacitance

The invention provides a semiconductor device and a fabrication method thereof. By arranging a poly-silicon inter-layer connection layer on the surfaces of a source region and a drain region of the device, the source region and the drain region of the device can extend to the surface of a substrate by the inter-layer connection layer, are connected with contact holes by the inter-layer connection layer and are connected other inter-connection layers at the upper part, so that the areas of source-drain regions are not needed to be excessive large due to catering to the contact holes, and the probability is provided for further reducing the areas of the source region and the drain region. Further, the poly-silicon inter-layer connection layer in the semiconductor device only covers the surface of an active region and are not arranged on the side wall of a grid or other regions, thus, parasitic capacitance between the source-drain regions and the grid cannot be generated, and meanwhile, the device is enabled to have required breakdown voltage.

Owner:SEMICON MFG INT (SHANGHAI) CORP

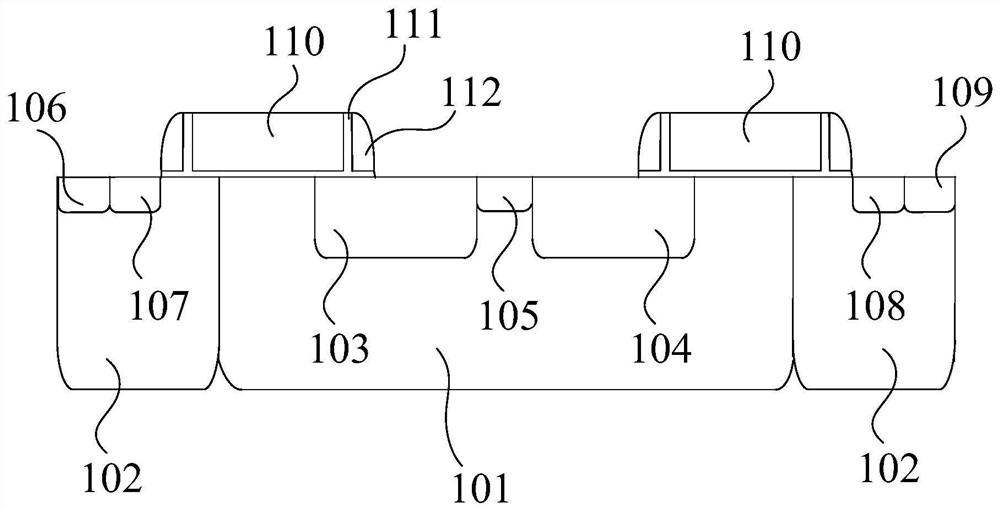

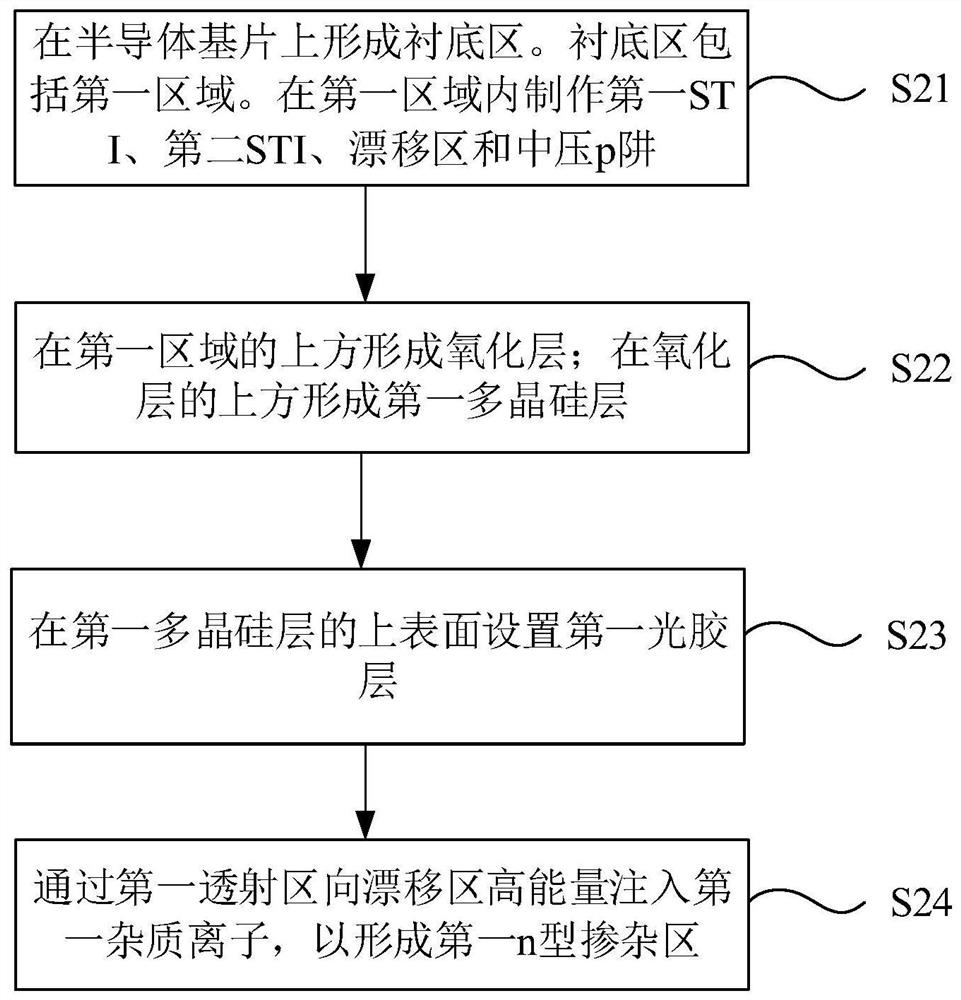

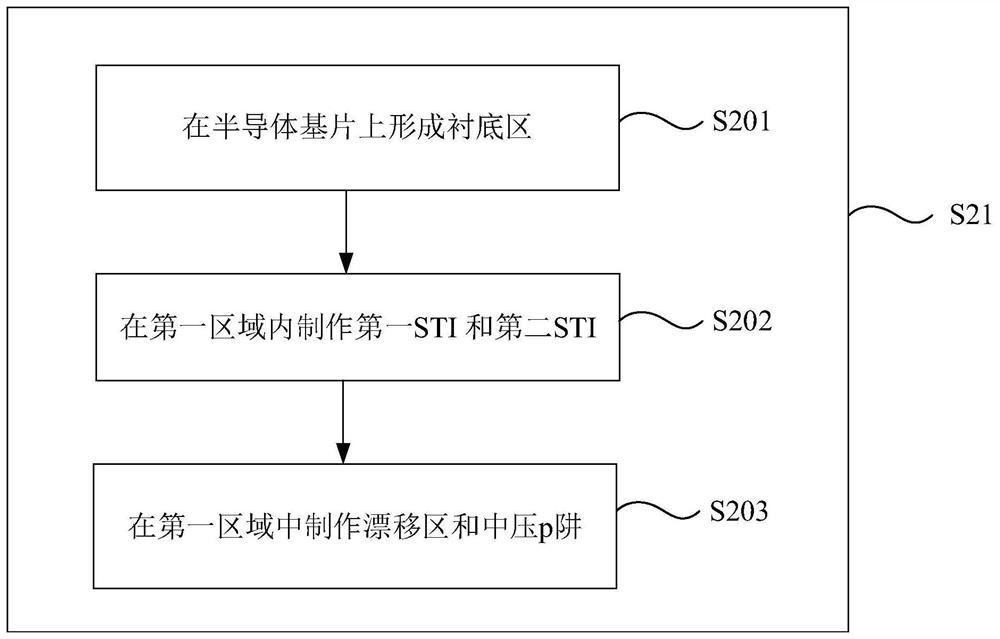

LDMOS and manufacturing method thereof

PendingCN111834221ALower on-resistanceGuaranteed breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesLDMOSHigh energy

The invention discloses an LDMOS and a manufacturing method thereof. The manufacturing method comprises the following steps: forming a substrate region on a semiconductor substrate, wherein the substrate region comprises a first region; manufacturing a first STI, a second STI, a drift region and a medium-voltage p well in the first region; forming an oxide layer above the first region; forming a first polycrystalline silicon layer above the oxide layer; arranging a first optical cement layer on the upper surface of the first polycrystalline silicon layer, wherein the first optical cement layercomprises a first transmission region and a first blocking region, and the first blocking region is used for blocking foreign ions from passing through; and injecting first impurity ions into the drift region at high energy through the first transmission region to form a first n-type doped region. According to the invention, impurity ions are injected into the drift region of the LDMOS at high energy, so that the on resistance of the drift region is reduced, and the breakdown voltage can be maintained.

Owner:GTA SEMICON CO LTD

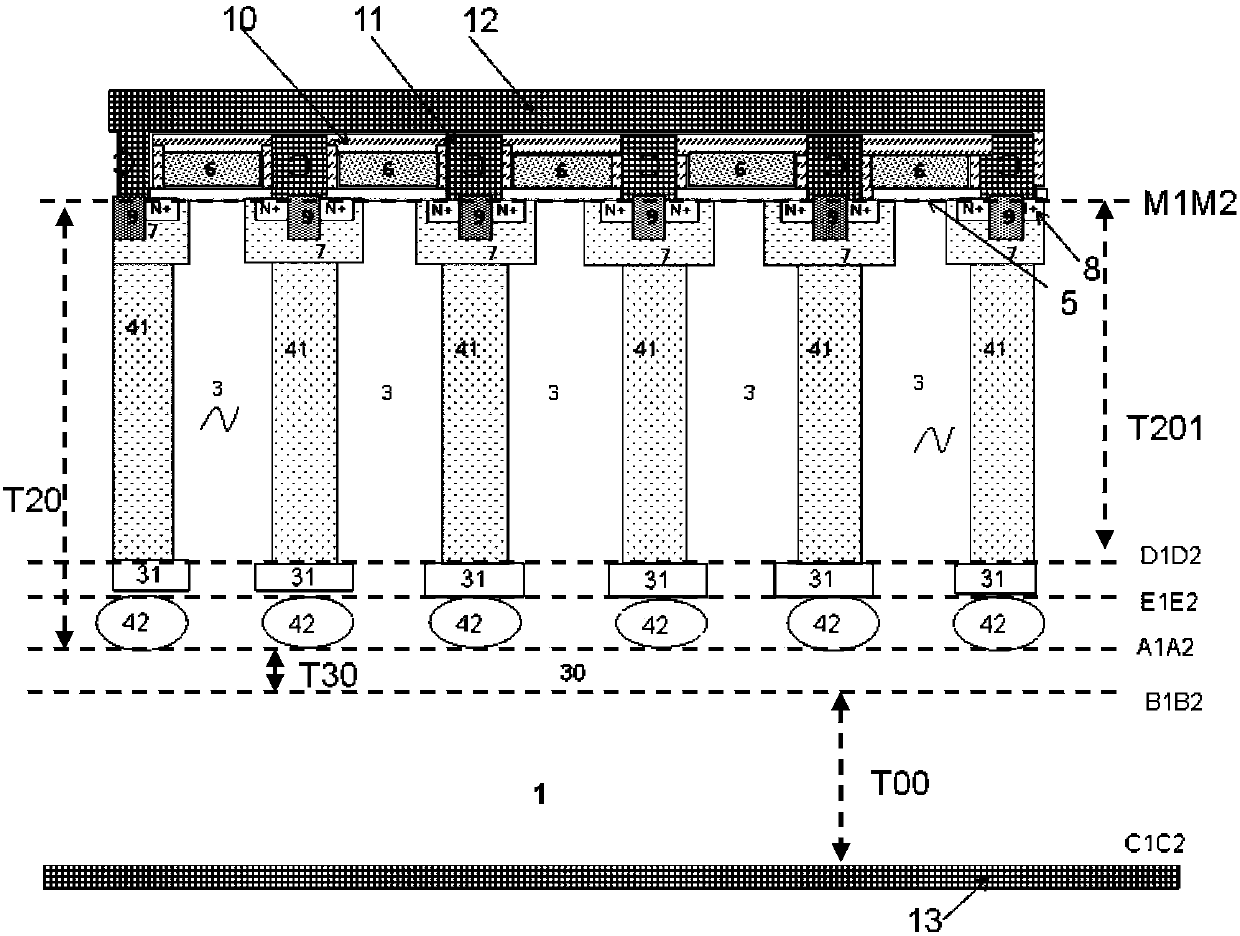

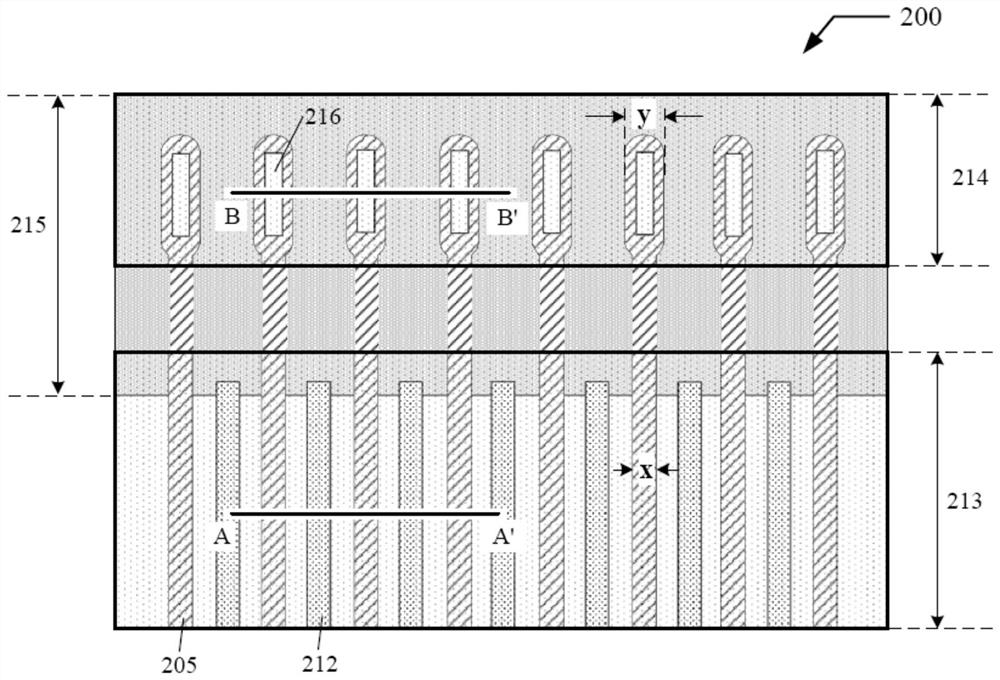

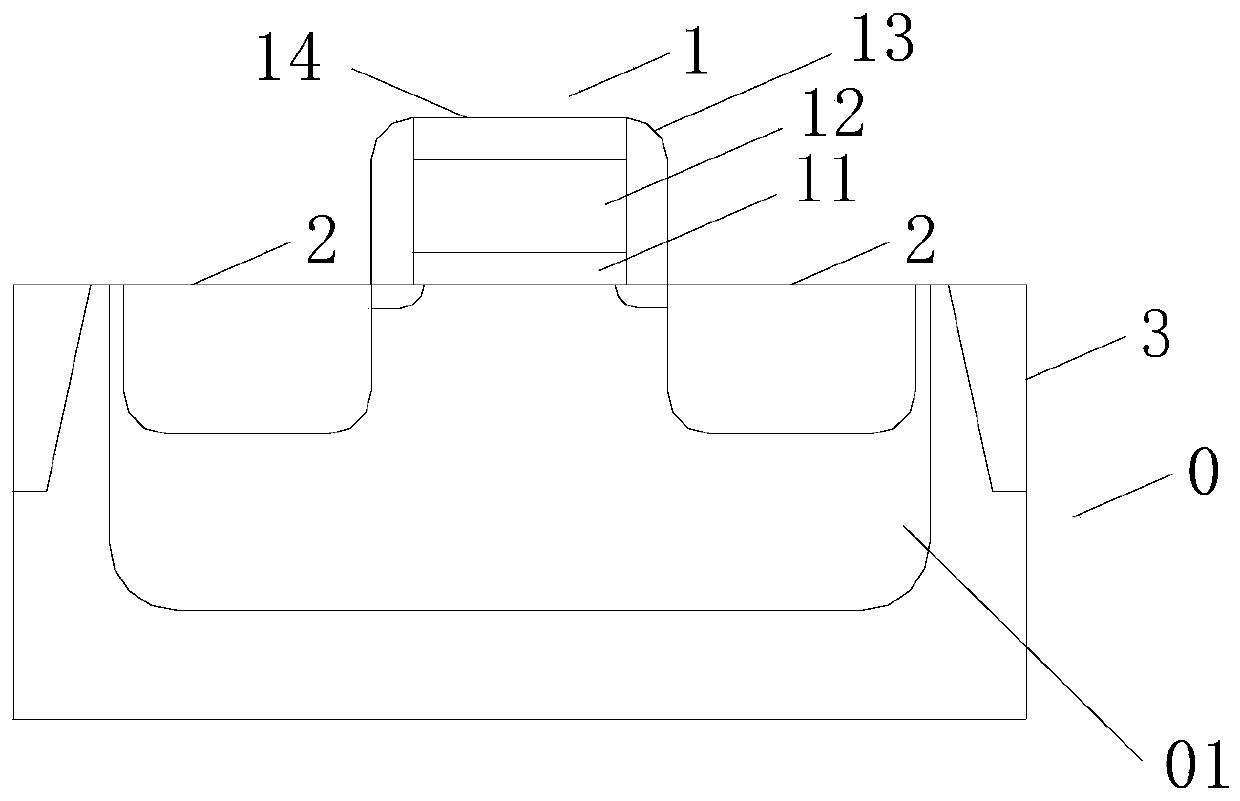

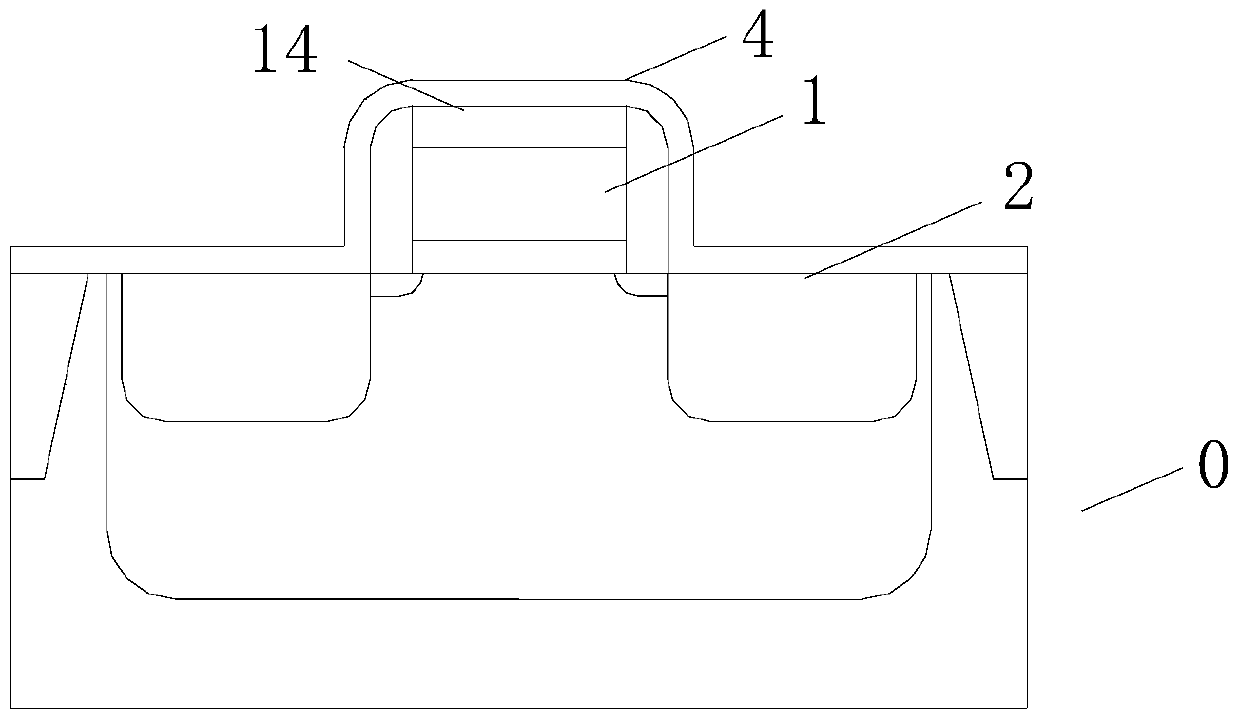

Trench type power semiconductor device and manufacturing method thereof

ActiveCN111725306AReduce manufacturing costReduce photolithography stepsSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceParasitic capacitance

The invention discloses a trench type power semiconductor device and a manufacturing method thereof, and relates to a power semiconductor device. In order to solve the problems that the manufacturingcost of a device is increased and the parasitic gate capacitance is increased due to the presence of a gate bus, the invention provides the following technical scheme: a gate contact hole is formed inan interlayer dielectric layer above the initial section of a trench, the gate conductive material in the trench is connected with the gate electrode metal layer above the gate conductive material through the gate contact hole, the width of the gate contact hole is smaller than that of the initial section of the trench, and the width of the initial section of the trench is larger than that of theextension section of the trench. The beneficial effects of the invention are that: according to the trench type power semiconductor device, stable and reliable grid connection can be realized on thebasis of not causing negative influence on the performance of the device; and by omitting a gate bus board, the photoetching process steps of the device are reduced, and the manufacturing cost of thedevice is reduced; and meanwhile, the gate parasitic capacitance introduced by the gate bus board is reduced, and the switching speed of the device is improved.

Owner:安建科技(深圳)有限公司

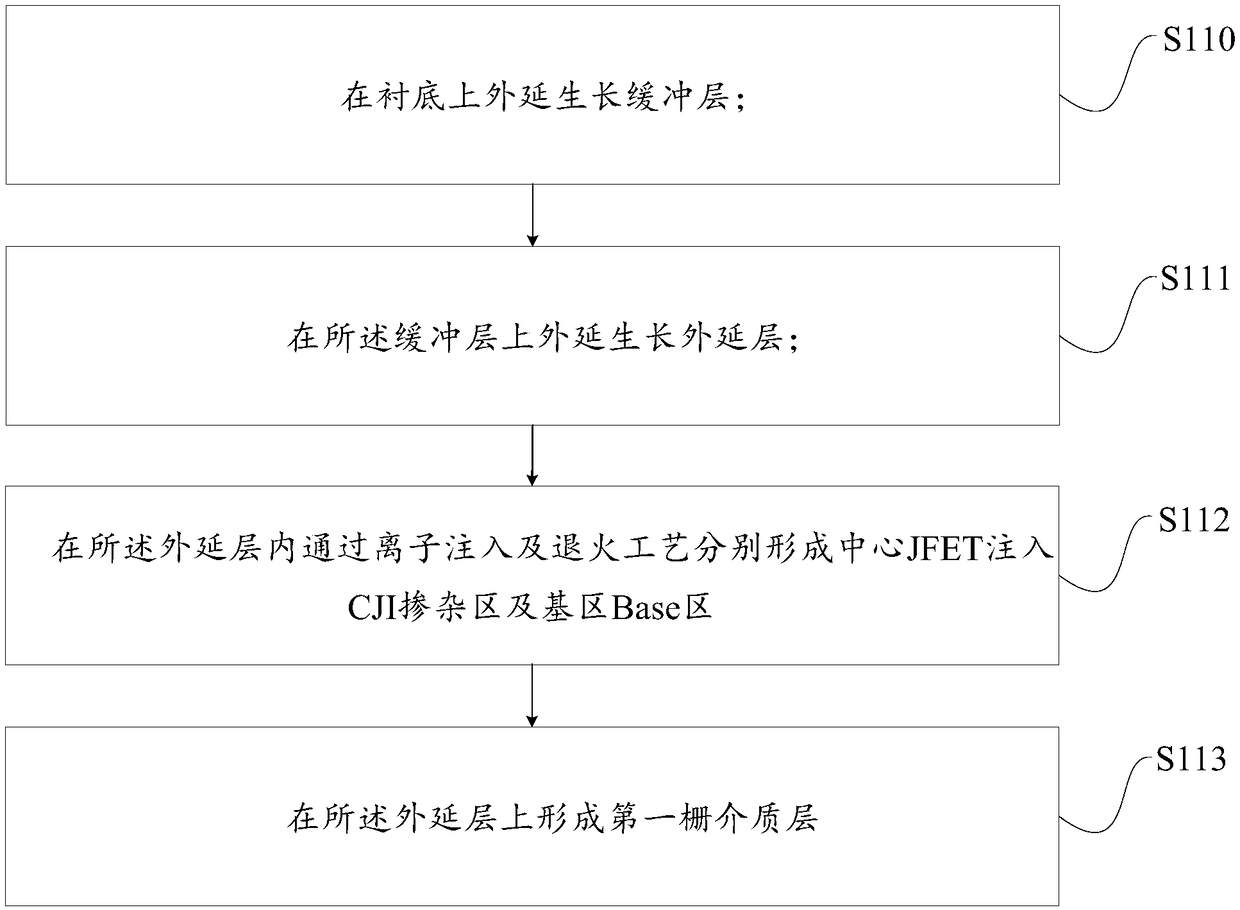

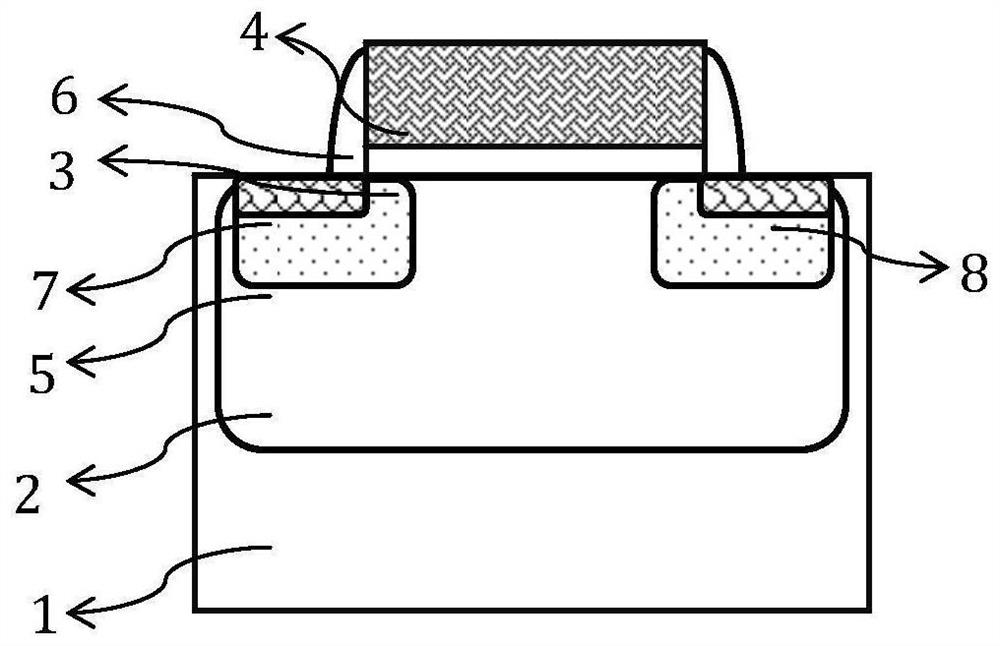

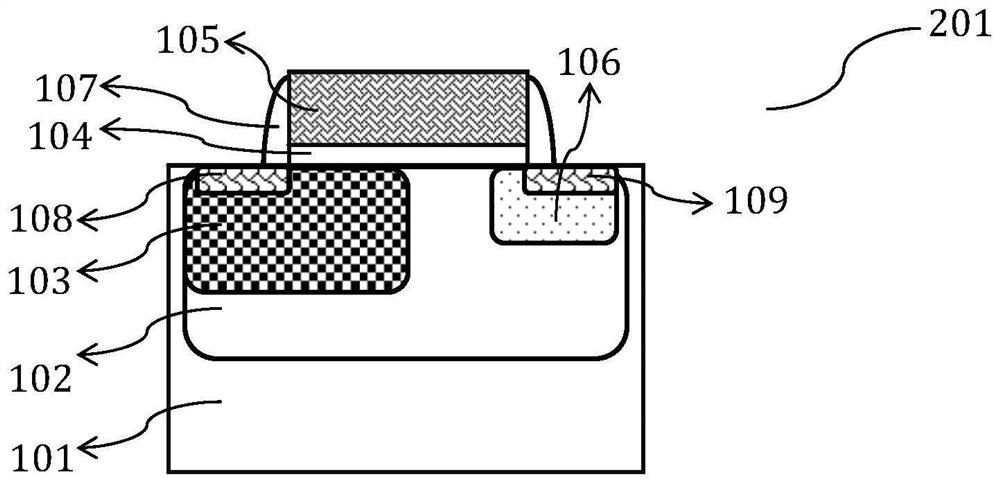

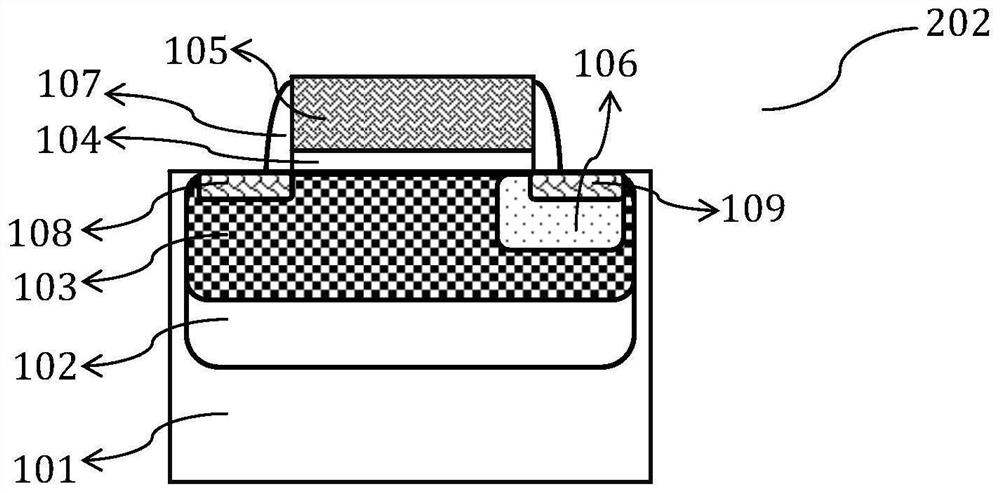

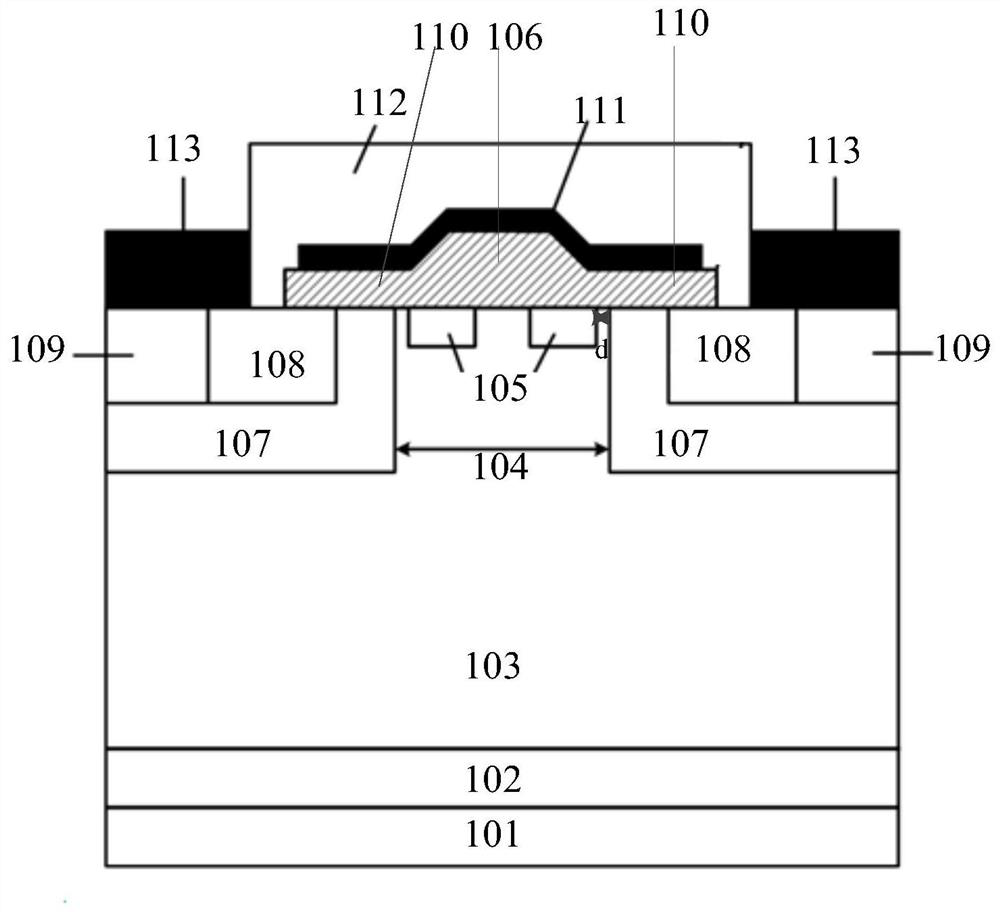

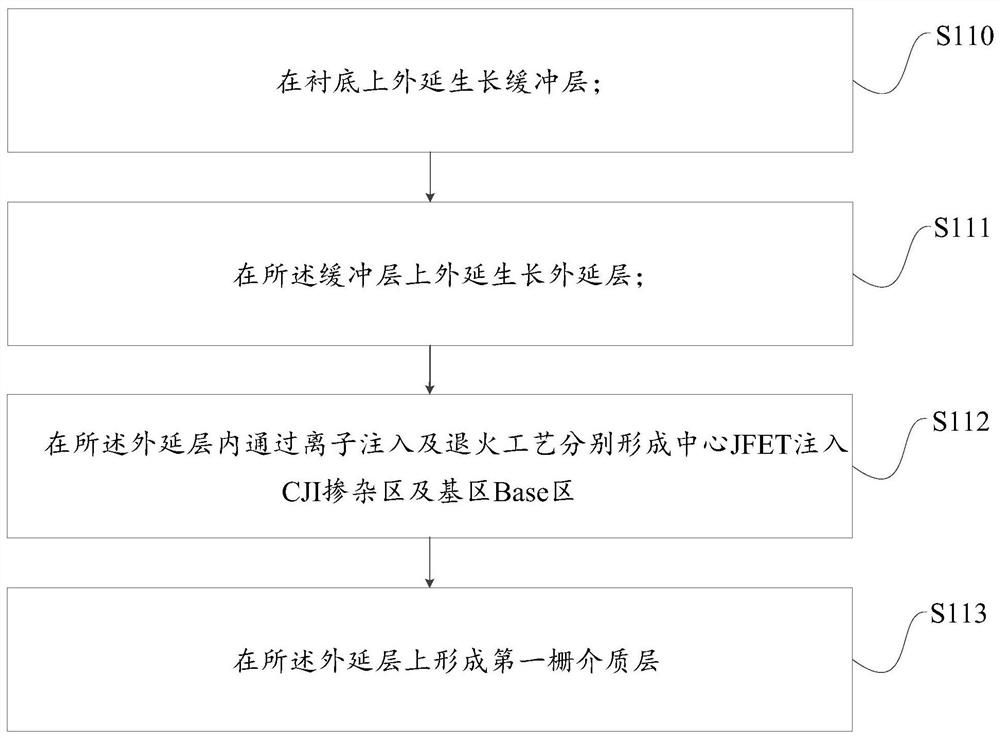

An insulated gate bipolar transistor and a manufacturing method thereof

ActiveCN109244126AImprove reliabilityImprove stabilitySemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricEngineering

The invention provides an insulated gate bipolar transistor and a manufacturing method thereof. The insulated gate bipolar transistor comprises a substrate; a buffer layer formed on the substrate; anepitaxial layer formed on the buffer layer; a junction type field effect structure JFET region formed in that epitaxial layer, and the width of the JFET region is 2.5 to 12 [mu]m; a CJI doped region formed in the JFET region, and the doped region is located at a thickness inflection point of the gate dielectric layer; A first gate dielectric layer formed on the epitaxial layer, the thickness of the first gate dielectric layer being 0.5 [mu]m to 1.2 [mu]m.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

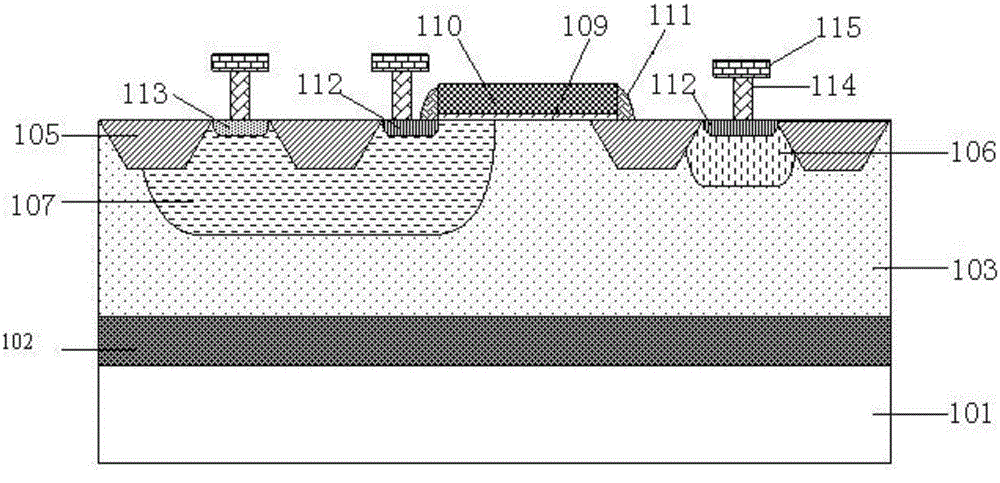

CMOS device in BCD process and manufacturing method thereof

ActiveCN111785774ASuppression of short channel effectsSmall sizeTransistorSemiconductor/solid-state device manufacturingCMOSLDMOS

The invention discloses a CMOS device in a BCD process. The CMOS device comprises a first MOS transistor with a channel conduction type of a first conduction type, and an LDMOS device comprises a first LDMOS with a channel conduction type of a second conduction type; a second conduction type doped first doped region is formed in a second conduction type first well region on the source region sideof the first MOS transistor, and the first doped region also forms a drift region of the first LDMOS. A first lightly doped drain region doped with the first conductivity type is formed in the first well region on the drain region side of the first MOS transistor. The first source region and the first drain region are formed on the surfaces of the first doped region and the first lightly doped drain region on the two sides of the first gate structure respectively. The invention further discloses a manufacturing method of the CMOS device in the BCD process. According to the invention, the high-voltage CMOS device can be realized, the short-channel effect of the device can be delayed, and the breakdown voltage of the device can be ensured without adding an additional process, so the size ofthe device can be further reduced, the conduction current is improved, and the conduction resistance is reduced.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

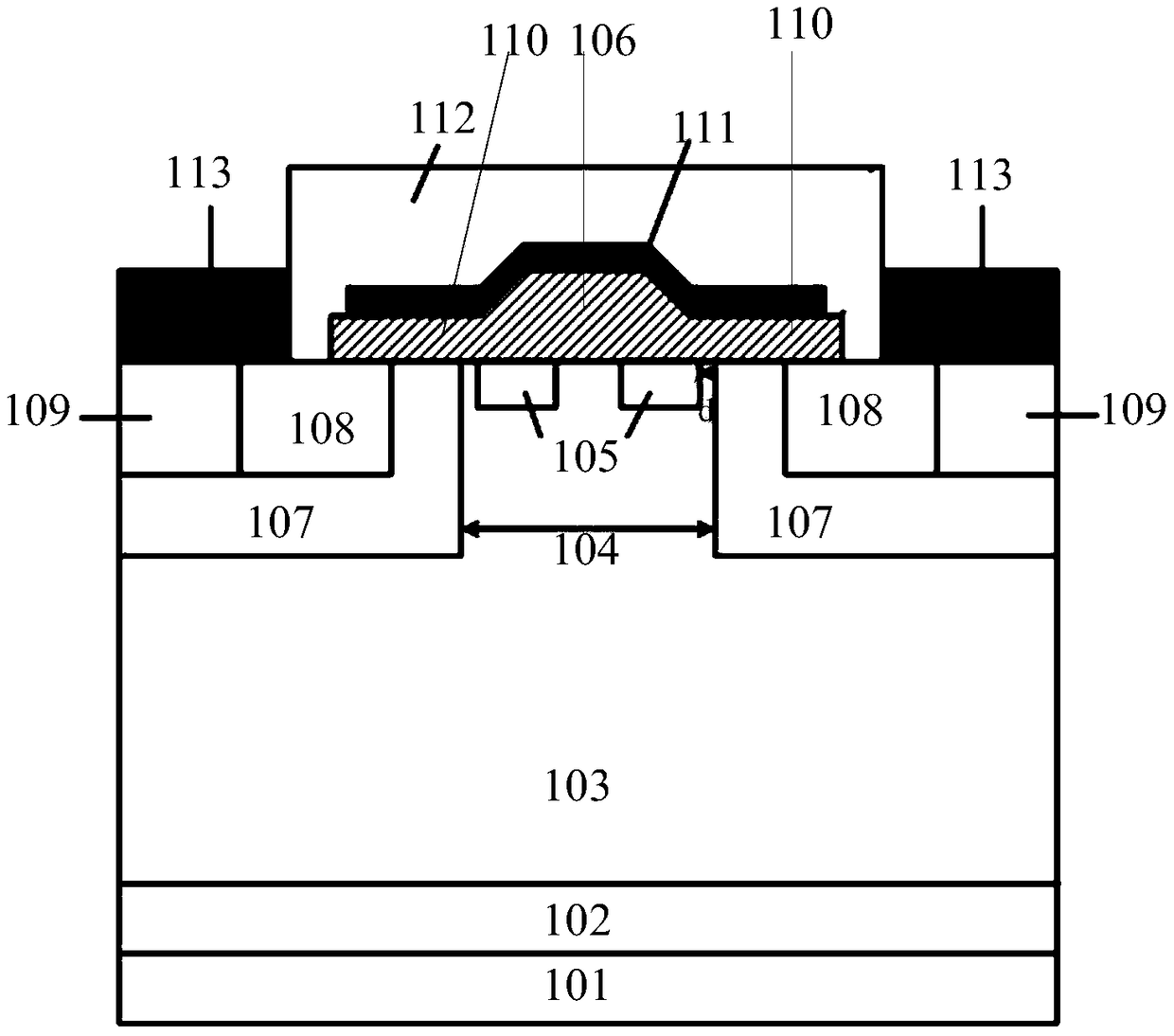

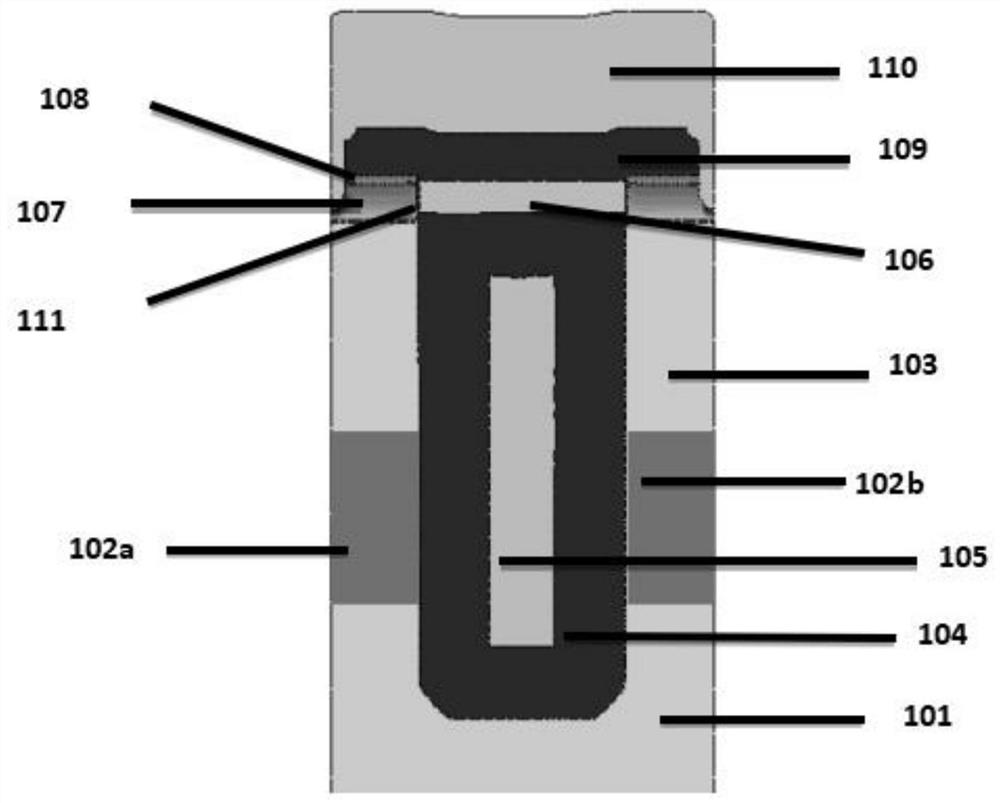

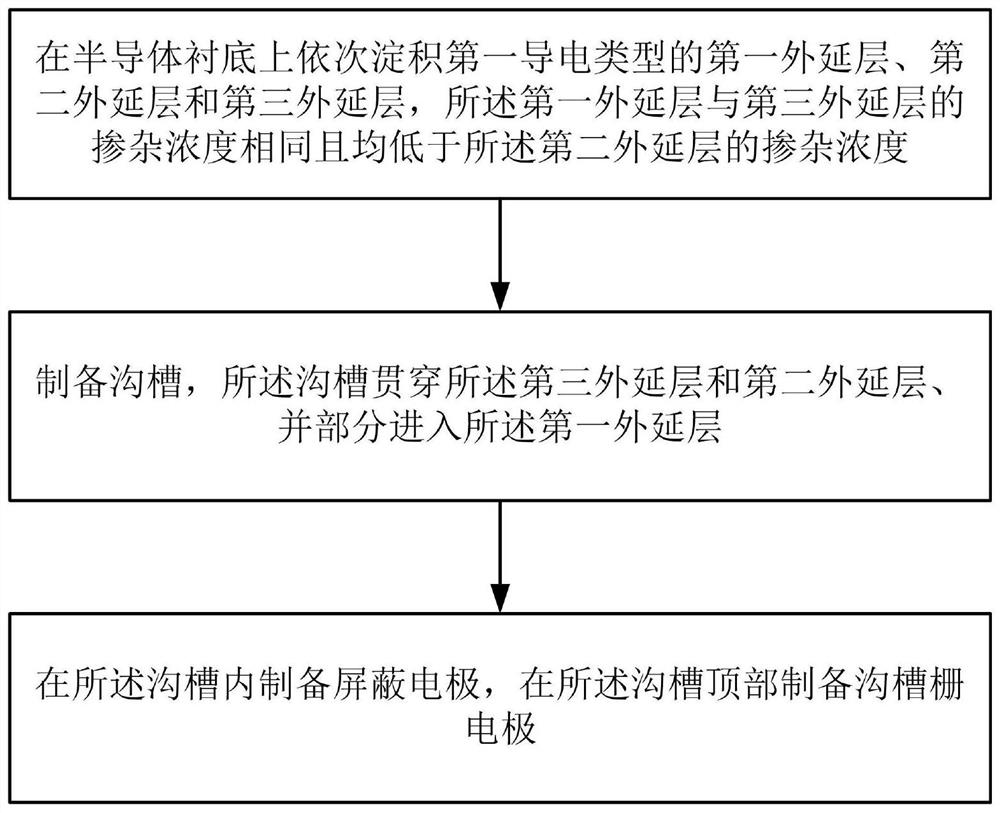

Split gate power MOSFET device with highly doped layer and preparation method thereof

ActiveCN111916502AAdjust the electric field distributionShorten design timeTransistorSemiconductor/solid-state device detailsDevice materialEngineering

The invention relates to a split gate power MOSFET device with a highly doped layer and a preparation method thereof, belongs to the field of semiconductor devices, and solves the problem that the on-state resistance of the device cannot be further reduced while the breakdown voltage is improved in the prior art. An MOSFET device conduction region comprises a plurality of primitive cells arrangedperiodically, and each primitive cell comprises a trench, a shielding electrode and a trench gate electrode. The trench is arranged in an epitaxial layer of the semiconductor substrate, the shieldingelectrode is arranged in the trench, and the trench gate electrode is arranged at the top of the trench. The shielding electrode and the trench gate electrode are both made of second conductive type materials, the epitaxial layer is made of a first conductive type material and comprises a first epitaxial layer, a second epitaxial layer and a third epitaxial layer which are sequentially stacked onthe semiconductor substrate and have the same doping type, and the doping concentration of the first epitaxial layer and the doping concentration of the third epitaxial layer are the same and are lower than the doping concentration of the second epitaxial layer. According to the MOSFET device, the on-resistance of the device is further reduced while the breakdown voltage is improved, and the FOM value of the device is improved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

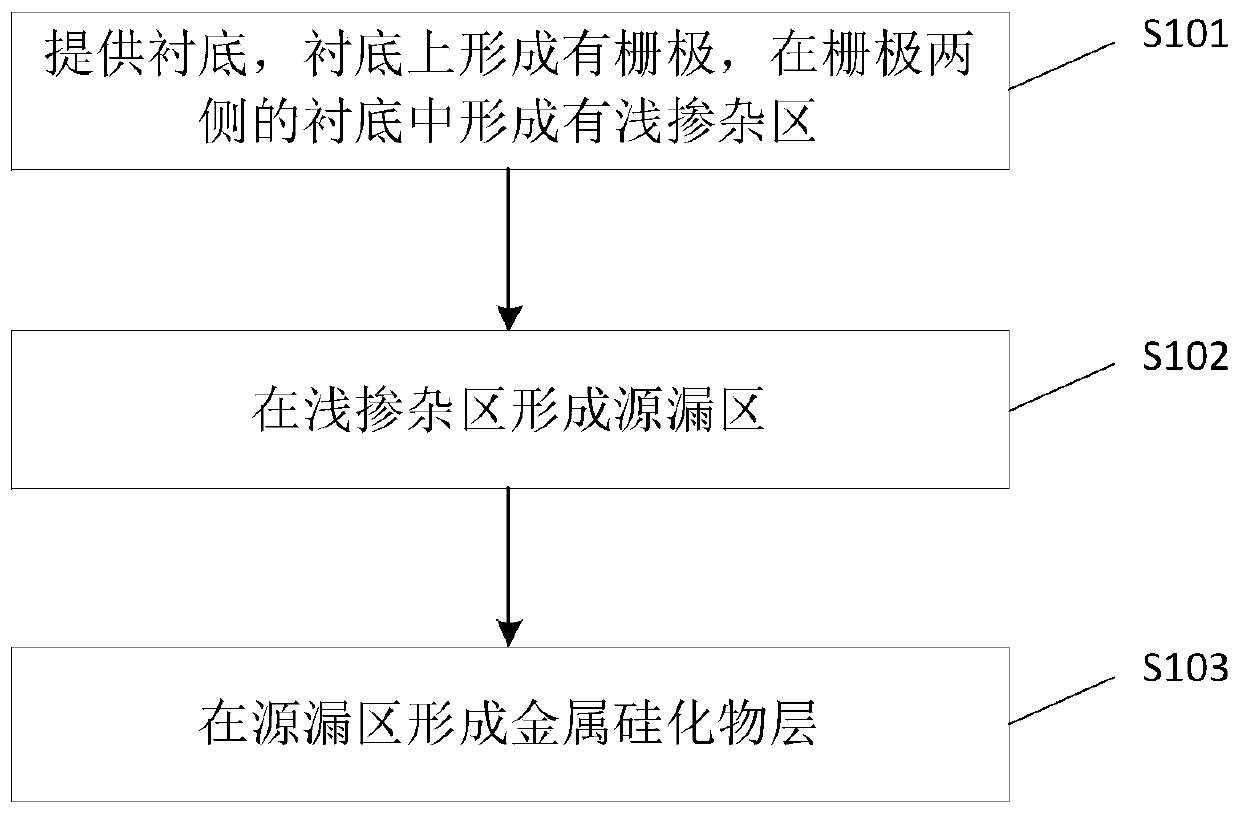

DDD UHV MOS device structure and manufacturing method thereof

InactiveCN110148564AReduce power consumptionImprove performanceSemiconductor/solid-state device manufacturingSemiconductor devicesMetal silicidePower consumption

The invention provides a DDD UHV MOS device structure and a manufacturing method thereof. A grid electrode can be formed on a substrate, shallow doping regions are formed in the substrate on two sidesof the grid electrode, source and drain regions can be formed in the shallow doping regions, and metal silicide layers can be formed in the source and drain regions, so that when the source and drainregions are connected with a contact plug in a peripheral circuit, the metal silicide layers can be in good contact with the source and drain regions while the high breakdown voltage of UHV is ensured, and the contact resistance between the contact plug and the source and drain is reduced, thereby reducing the overall power consumption of the device and improving the performance of the device.

Owner:YANGTZE MEMORY TECH CO LTD

Novel super-barrier power device and manufacturing method thereof

PendingCN111192916ASimple processImprove machining accuracySemiconductor/solid-state device manufacturingSemiconductor devicesPhysicsEngineering

Owner:FOUNDER MICROELECTRONICS INT

LDMOS device and manufacturing method thereof

PendingCN111883595AReducing polysilicon sizeImprove competitivenessSemiconductor/solid-state device manufacturingSemiconductor devicesPhysicsBody region

The invention relates to the technical field of semiconductor manufacturing, in particular to an LDMOS device and a manufacturing method thereof. The method comprises the following steps: providing asemiconductor substrate, and forming a shallow trench isolation structure around the semiconductor substrate of the device, wherein the shallow trench isolation structure extends downwards from the front face of the semiconductor substrate; forming a drift region in the semiconductor substrate surrounded by the shallow trench isolation structure; forming a body region in the drift region of the source end region of the device; forming a gate structure bridged between the body region and the drain terminal region; forming a high-voltage LDD region in the drift region of the drain terminal region of the device; forming side walls at the side edges of the gate structures of the connector region and the high-voltage LDD region respectively; respectively forming a source region and a drain region in the body region and the high-voltage LDD region, wherein the source region and the drain region form overlapping regions with the corresponding side walls, wherein the device is manufactured bythe method.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

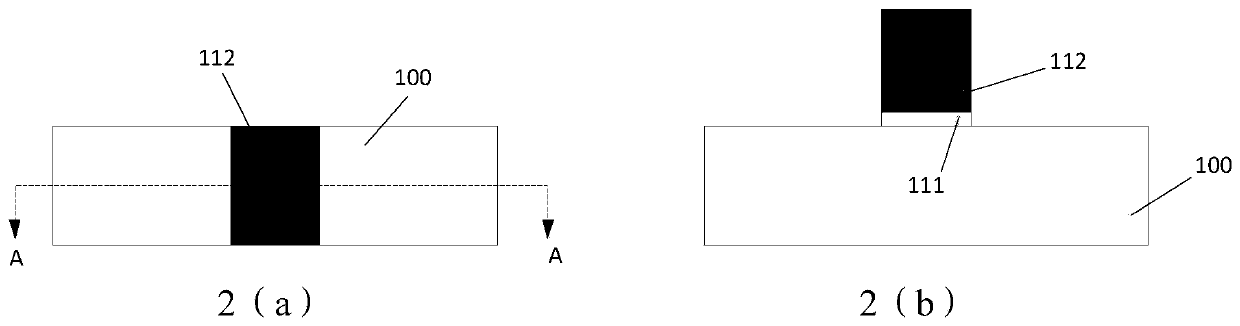

Semiconductor device and manufacturing method thereof

ActiveCN105789112BGuaranteed breakdown voltageReduce areaSemiconductor/solid-state device detailsSolid-state devicesInter layerParasitic capacitance

The invention provides a semiconductor device and a fabrication method thereof. By arranging a poly-silicon inter-layer connection layer on the surfaces of a source region and a drain region of the device, the source region and the drain region of the device can extend to the surface of a substrate by the inter-layer connection layer, are connected with contact holes by the inter-layer connection layer and are connected other inter-connection layers at the upper part, so that the areas of source-drain regions are not needed to be excessive large due to catering to the contact holes, and the probability is provided for further reducing the areas of the source region and the drain region. Further, the poly-silicon inter-layer connection layer in the semiconductor device only covers the surface of an active region and are not arranged on the side wall of a grid or other regions, thus, parasitic capacitance between the source-drain regions and the grid cannot be generated, and meanwhile, the device is enabled to have required breakdown voltage.

Owner:SEMICON MFG INT (SHANGHAI) CORP

IGBT structure with trench emitter buried layer

InactiveCN112510082APlay an auxiliary role in depletionIncrease the doping concentrationSemiconductor devicesPhysical chemistryEngineering

The invention discloses an IGBT structure with a trench emitter buried layer, and the structure enables an emitter to be made into a shallow trench structure on the basis of a conventional CSIGBT structure, adds two p-type doped regions MP and BP at the bottom of an emitter trench and the bottom of a gate trench, and on the basis of improves the concentration Ncs of a carrier storage layer, the gain of the amplified injection enhancement effect is retained and dynamic avalanche breakdown induced by Ncs increase is suppressed. The balance between the turn-off loss and the on-state voltage dropis optimized, and the interference of EMI noise is effectively suppressed.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Metal capacitor structure and preparation method thereof

ActiveCN113517400BLower breakdown voltageGuaranteed breakdown voltageSolid-state devicesCapacitorsCapacitanceDielectric layer

The invention provides a metal capacitor structure and a preparation method thereof, which is characterized in that it comprises: a substrate; a capacitor structure, including a bottom metal layer, an interlayer dielectric layer and a top metal layer sequentially stacked on the substrate; several openings, penetrating through the top metal layer and extending downward into the interlayer dielectric layer; the depression is located on the sidewall of the opening and extends downward from the bottom of the opening into the interlayer dielectric layer; the sidewall, Located in the opening and extending downward from the sidewall of the top metal layer to fill the recess; the invention improves the breakdown voltage of the metal capacitor structure.

Owner:GUANGZHOU CANSEMI TECH INC

A Vertical Double Diffused Metal Oxide Semiconductor Field Effect Transistor

ActiveCN106129113BGuaranteed breakdown voltagePlay a shielding roleSemiconductor devicesGate oxideField-effect transistor

Owner:北京中科微投资管理有限责任公司

A kind of insulated gate bipolar transistor and its manufacturing method

ActiveCN109244126BImprove reliabilityImprove stabilitySemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricEngineering

The invention provides an insulated gate bipolar transistor and a manufacturing method thereof. The insulated gate bipolar transistor comprises: a substrate; a buffer layer formed on the substrate; an epitaxial layer formed on the buffer layer; The junction field effect structure JFET region is formed in the epitaxial layer, and the width of the JFET region is 2.5-12 μm; the CJI doped region is formed in the JFET region, and the doped region is located at the thickness of the gate dielectric layer Inflection point: the first gate dielectric layer is formed on the epitaxial layer, and the thickness of the first gate dielectric layer is 0.5 μm˜1.2 μm.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

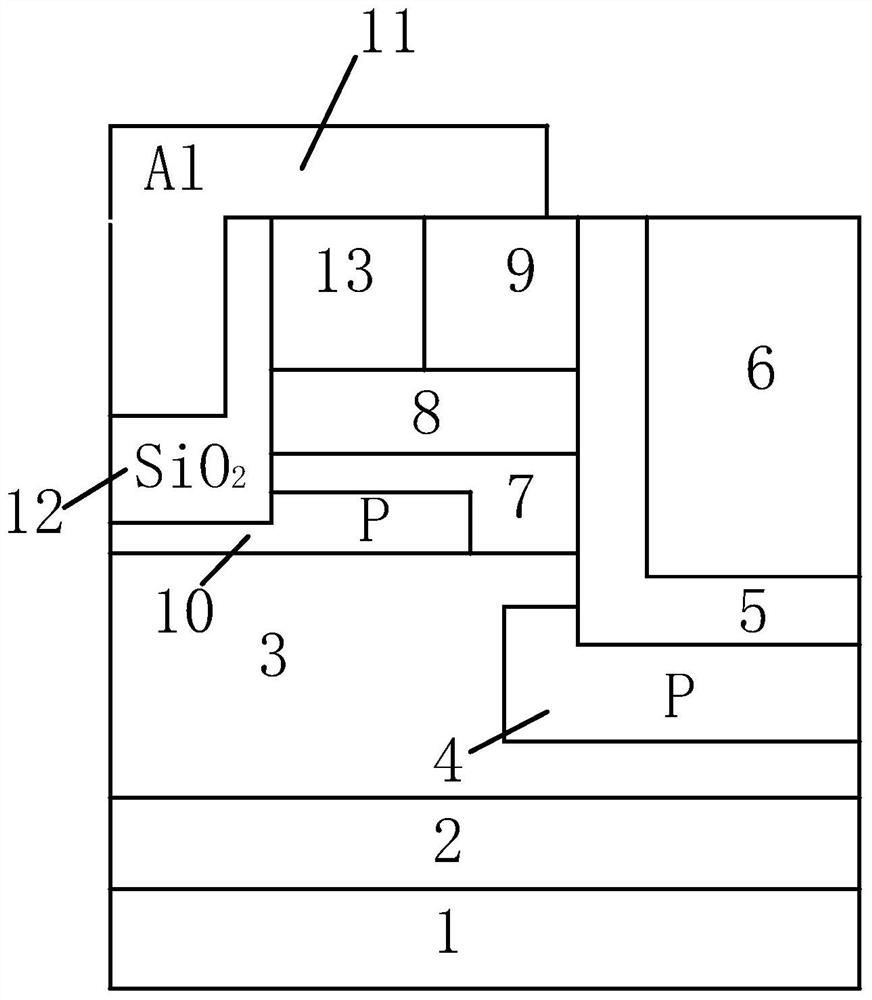

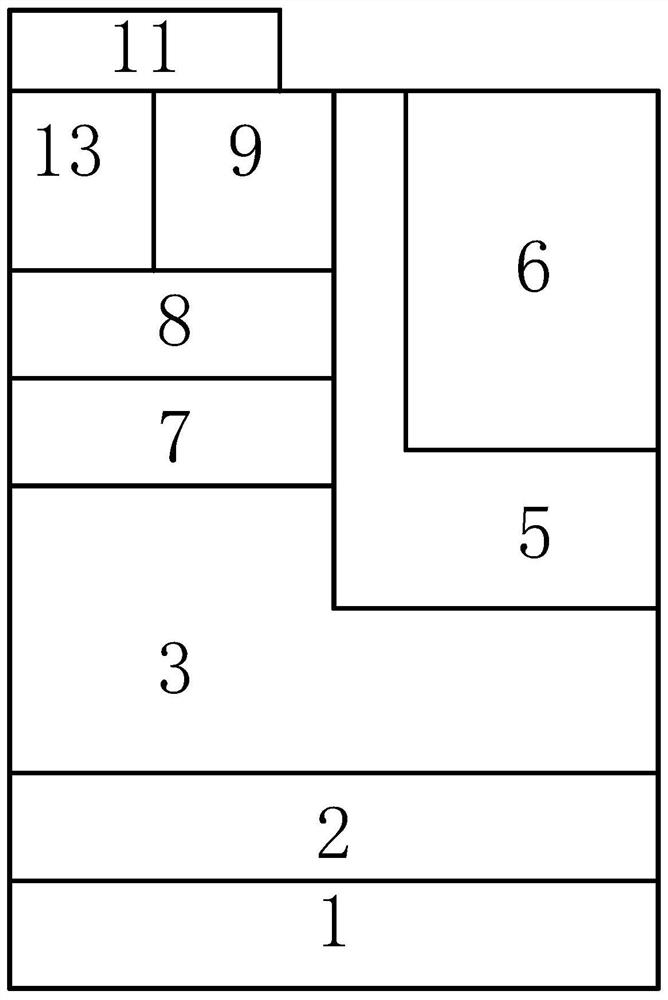

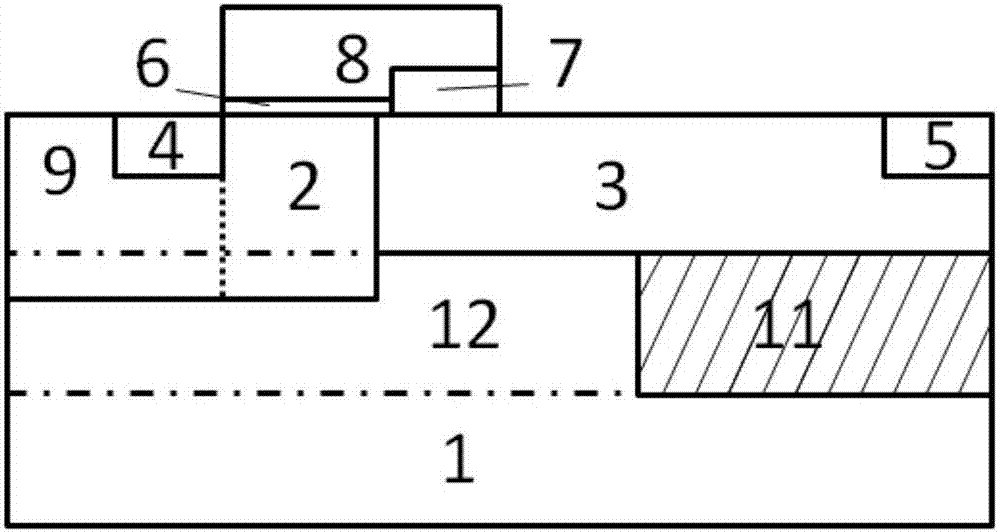

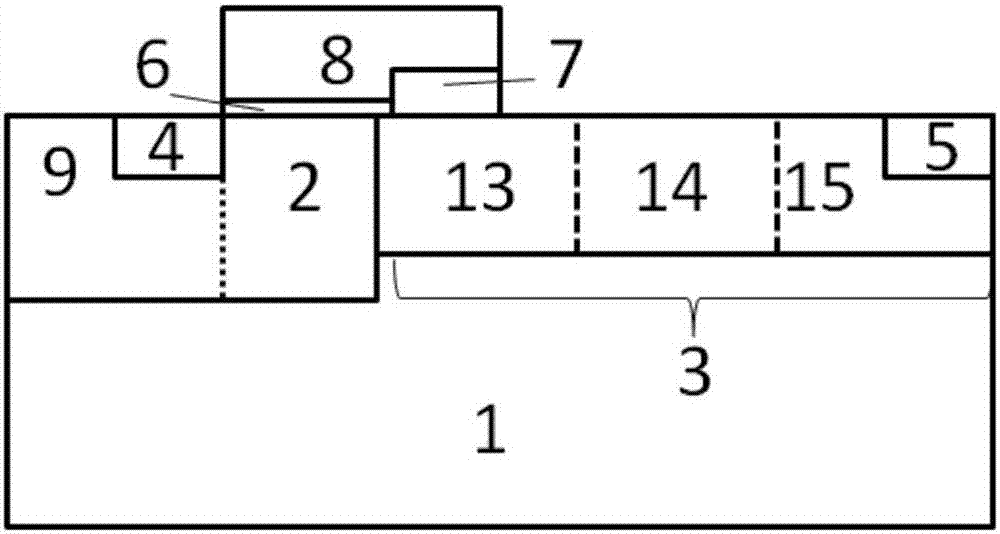

Local soi LDMOS device for frequency boosting overcoming short channel effect

ActiveCN104157692BIncrease working frequencyGood short channel characteristicsSemiconductor devicesOxygenGate oxide

The invention discloses a local ultra-thin SOI LDMOS device which overcomes the short channel effect and increases the frequency, and belongs to the field of semiconductor devices. Including semiconductor substrate 1, channel region 2, drift region 3, source region 4, drain region 5, gate oxide 6, field oxygen 7, gate 8, channel substrate heavily doped region 9, BOX layer 18, sidewall 19. The source extension region 20, wherein the drift region 3 is a lateral variable doping structure, characterized in that a through groove is opened along the width direction of the drift region at one end of the BOX layer close to the drift region, and the BOX layer 18 is located at the side of the channel Directly below, or directly below the channel and part of the source region, or directly below the channel and the source region, to ensure the breakdown voltage while improving the frequency characteristics and drive capability of the device. The invention effectively suppresses the short-channel effect, and improves the frequency characteristic and driving ability while ensuring the breakdown voltage.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

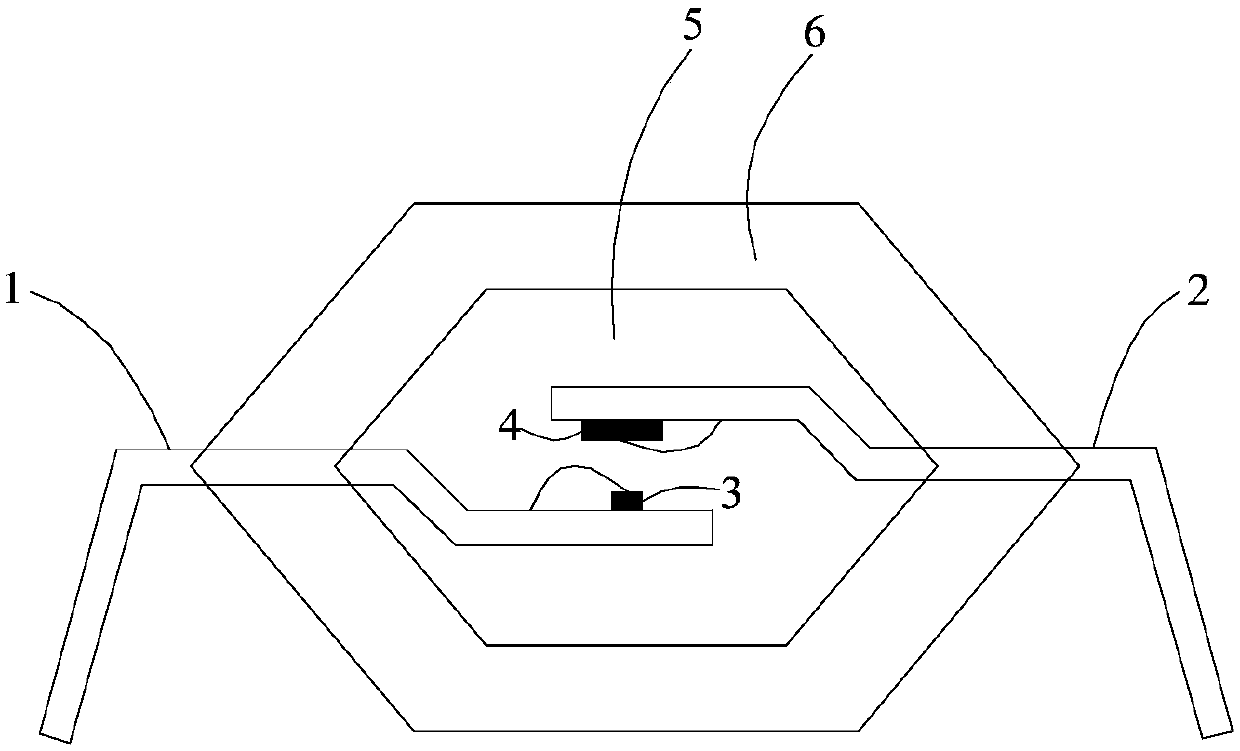

Anti-vibrating optocoupler relay

InactiveCN107911106AImprove reliabilityDistribute in timeElectronic switchingPhysical separationComputer science

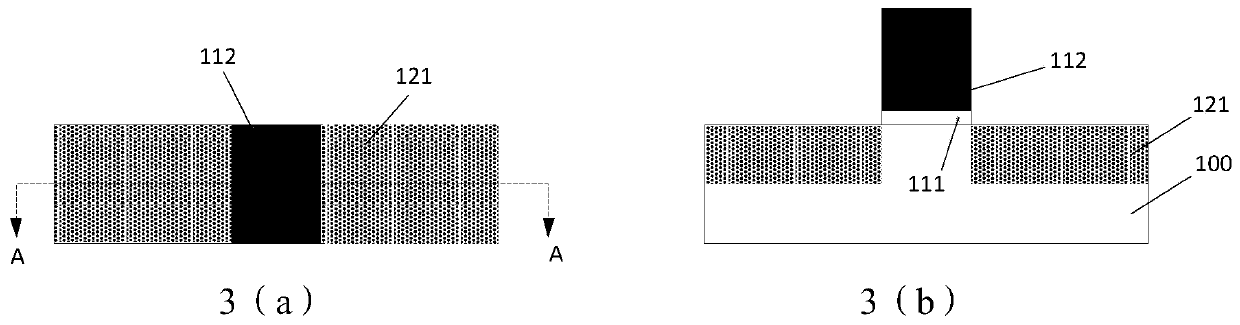

The invention discloses an anti-vibrating optocoupler relay, and relates to the technical field of the encapsulation. The optocoupler relay comprises a first frame and a second frame in physical separation; the first frame and the second frame are arranged in parallel in a horizontal direction of the section, and the first frame and the second frame are partially overlapped on a vertical directionof the section; a signal sending send is arranged on at overlapping location on the first frame, and a signal receiving end is arranged at the overlapping location on the second frame; the signal sending end and the signal receiving end are in face to face, and the signal sending end and the signal receiving end are in physical isolation,; the signal sending end and the signal receiving end are sealed in internal resin, and external resin are encapsulated at the external of the internal resin. The problem that the optocoupler relay is sensitive to vibration, low in reliability, small in isolation voltage, bad in radiating effect and has follow current due to the unibody design is solved, and the effects of buffering the impact of external force, improving the reliability, increasing the isolation voltage, avoiding the flow current influence and guaranteeing the radiation are achieved.

Owner:WUXI HAOBANG HIGH TECH CO LTD