Patents

Literature

800results about How to "Shorten design time" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Noncontact Electric Power Transmission System

ActiveUS20100219696A1Improve transmission efficiencyShorten design timeElectromagnetic wave systemTransformersElectric power transmissionTransmitter coil

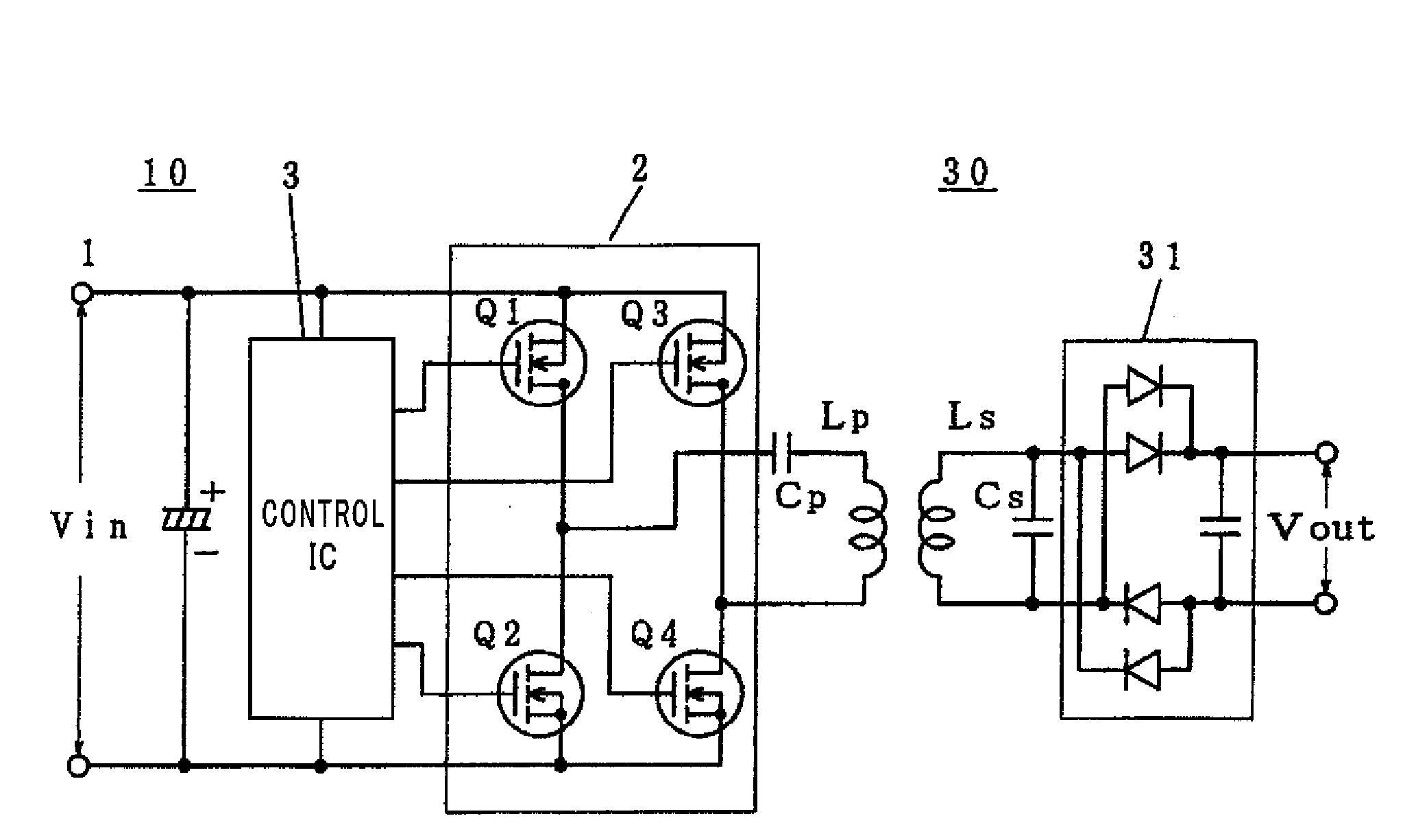

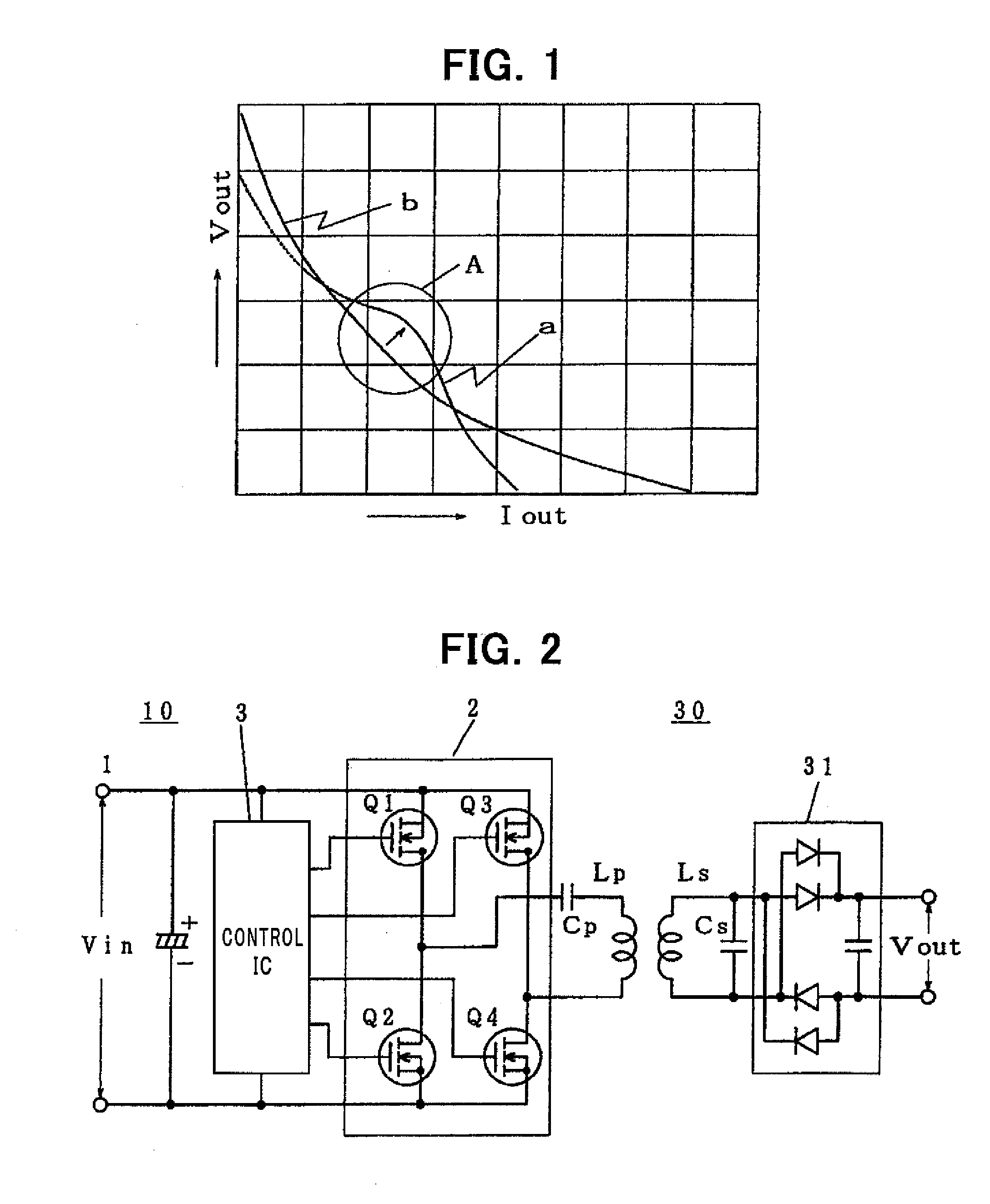

Disclosed is a noncontact electric power transmission system having a power transmitter circuit section 10 and a power receiver circuit section 30 which are adapted to be coupled to transmit electric power from a transmitter coil Lp provided in the power transmitter circuit section 10 to a receiver coil Ls provided in the power receiver circuit section 30, in a noncontact manner by means of electromagnetic induction. The noncontact electric power transmission system comprises: a separately-excited or self-excited switching circuit 2 provided in the power transmitter circuit section 10; a control IC 3 operable to drive the switching circuit 2; an LC series resonant circuit including a capacitor Cp connected in series to the transmitter coil Lp or an LC parallel resonant circuit including a capacitor Cp connected in parallel to the transmitter coil Lp; and an LC parallel resonant circuit including a capacitor Cs connected in parallel to the receiver coil Ls, wherein an oscillating frequency (Fosc) of the control IC 3, a resonant frequency (Fpr) of the LC series resonant circuit or the LC parallel resonant circuit in the power transmitter circuit section 10, and a resonant frequency (Fsr) of the LC parallel resonant circuit in the power receiver circuit section 30, have the following relationship: Fpr<Fosc<Fsr.

Owner:MURATA MFG CO LTD

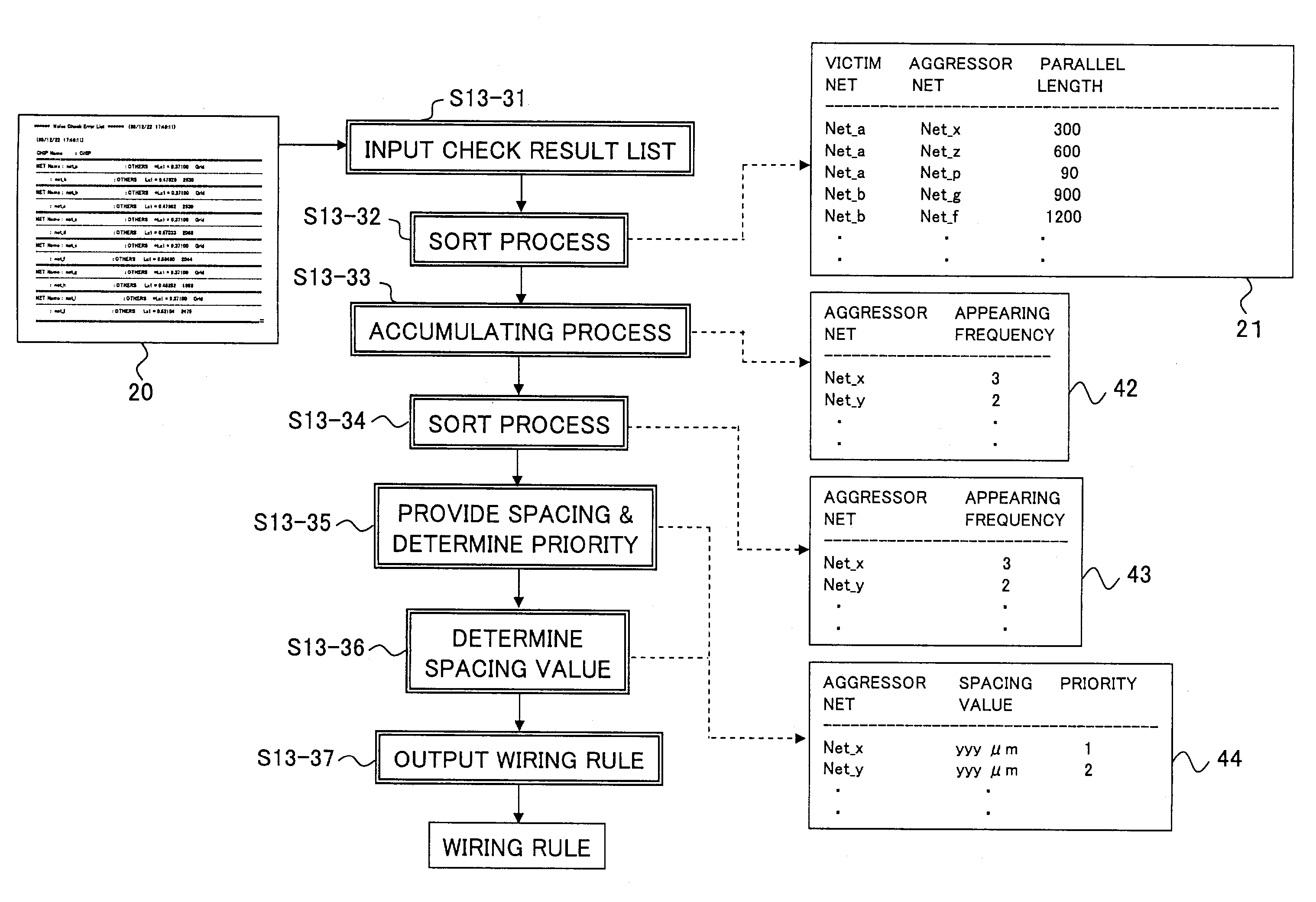

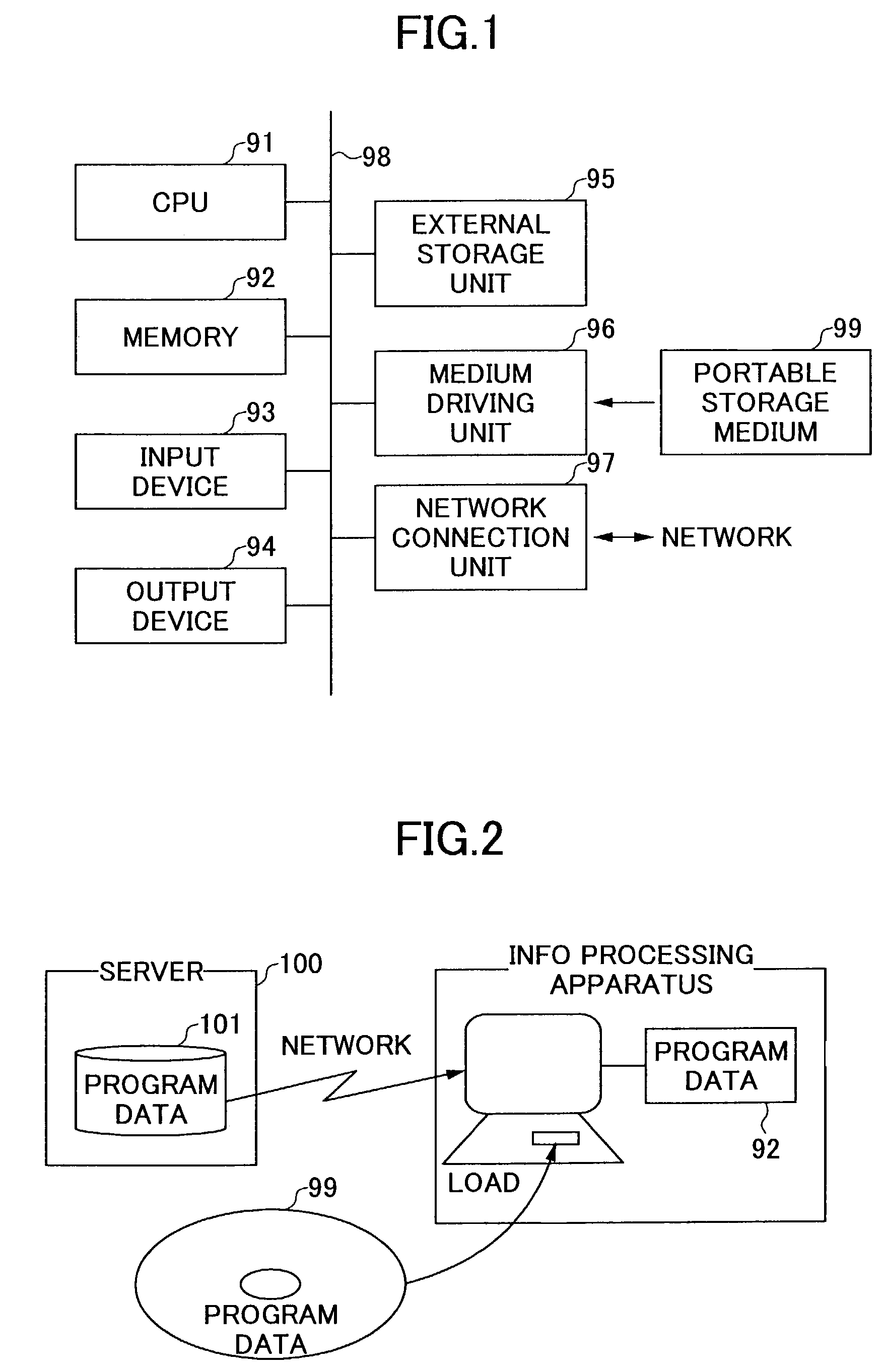

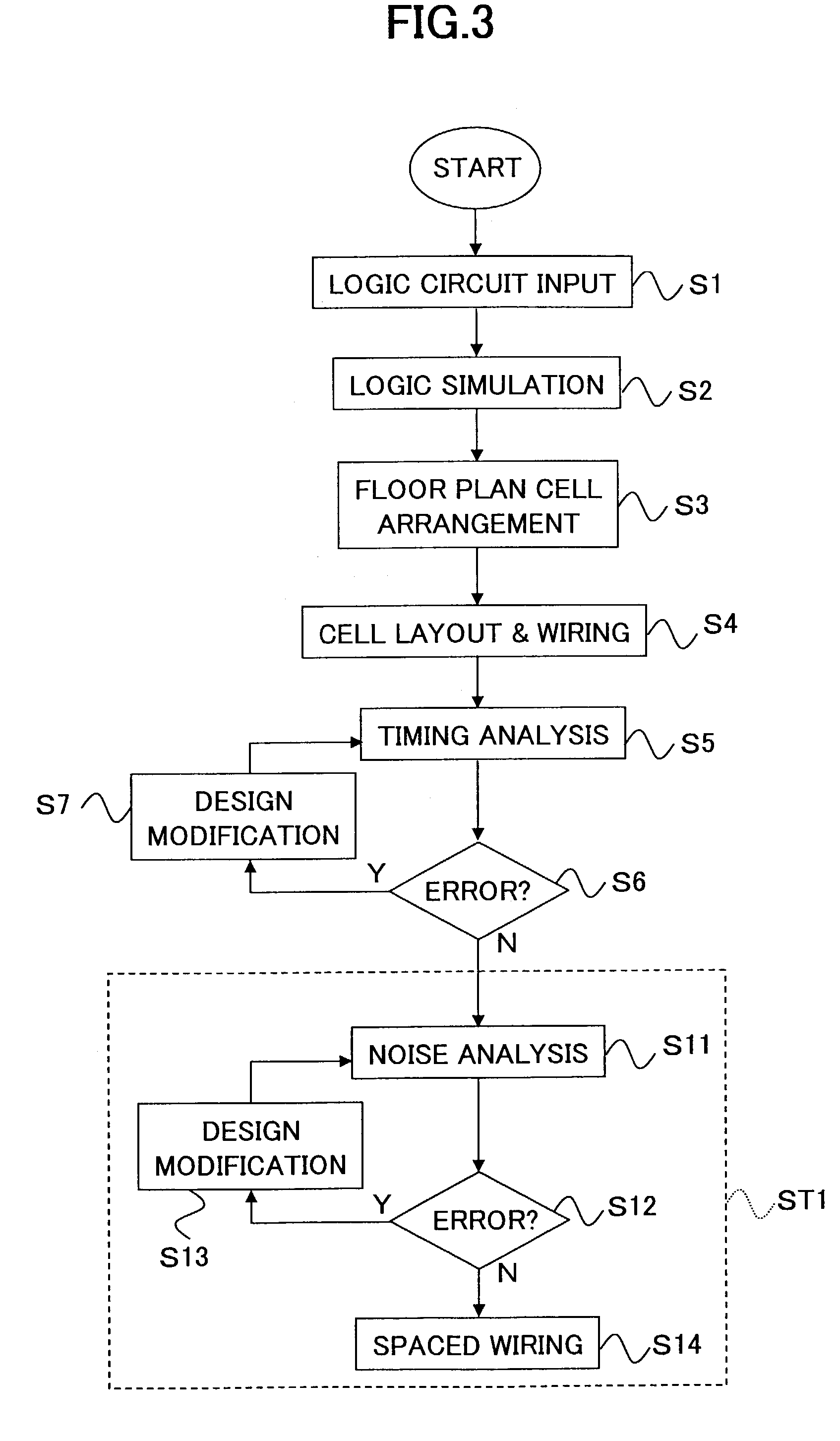

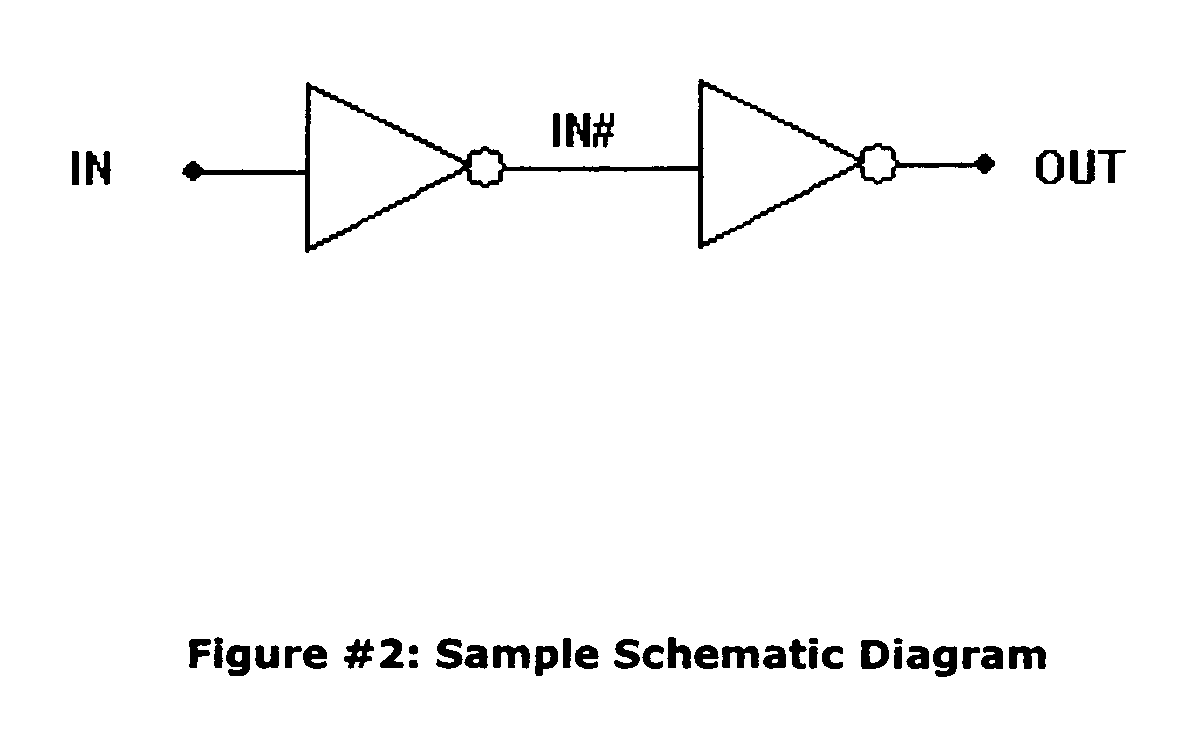

Electronic circuit design method, simulation apparatus and computer-readable storage medium

InactiveUS7086018B2Eliminate the problemReduce loadSemiconductor/solid-state device manufacturingComputer aided designEngineeringElectronic circuit design

An electronic circuit designing method analyzes noise with respect to a wiring pair, and automatically corrects the wiring pair by determining a spacing between wirings of the wiring pair so as to prevent generation of a noise error, if the noise error is detected based on the analysis of the noise.

Owner:FUJITSU LTD

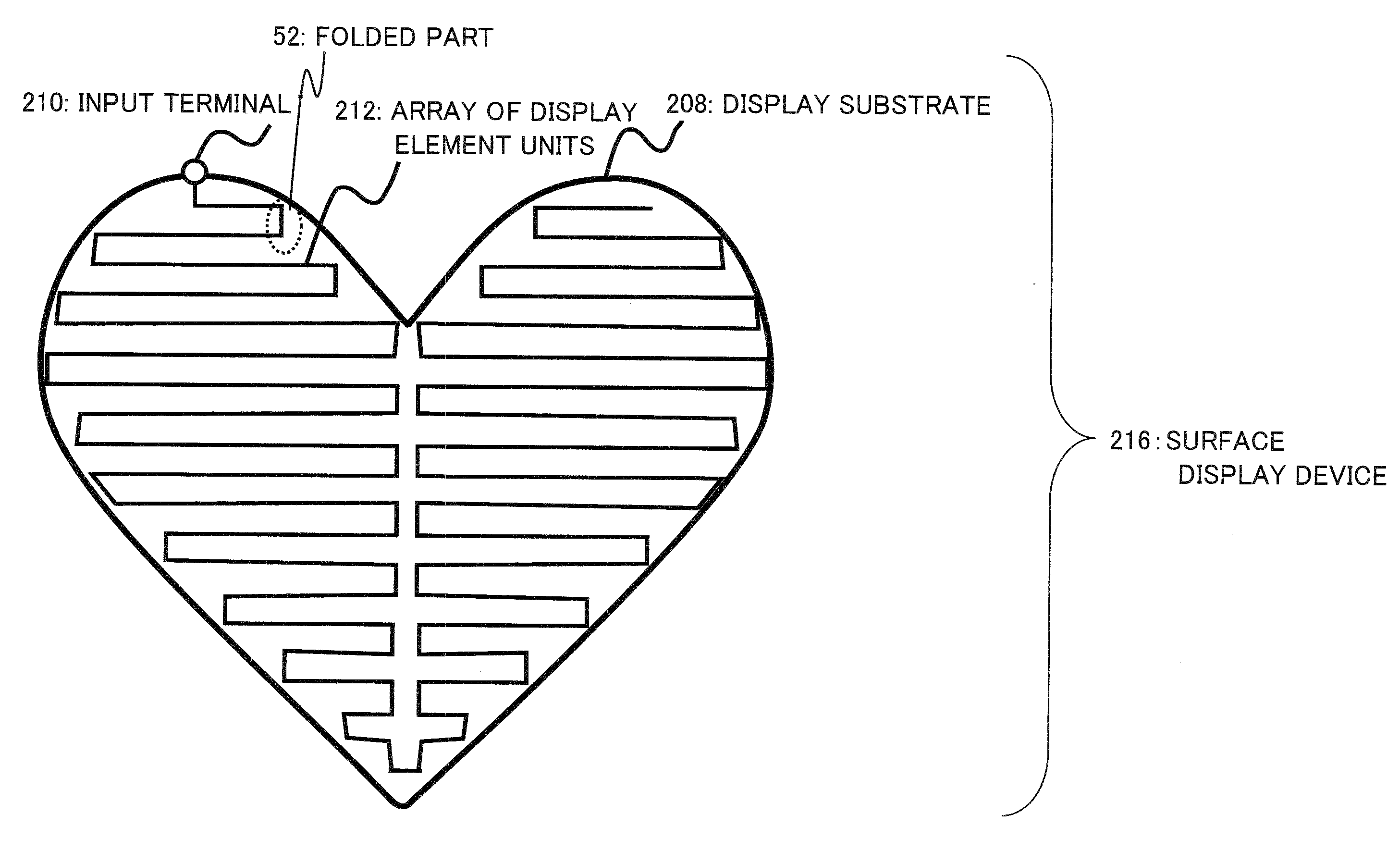

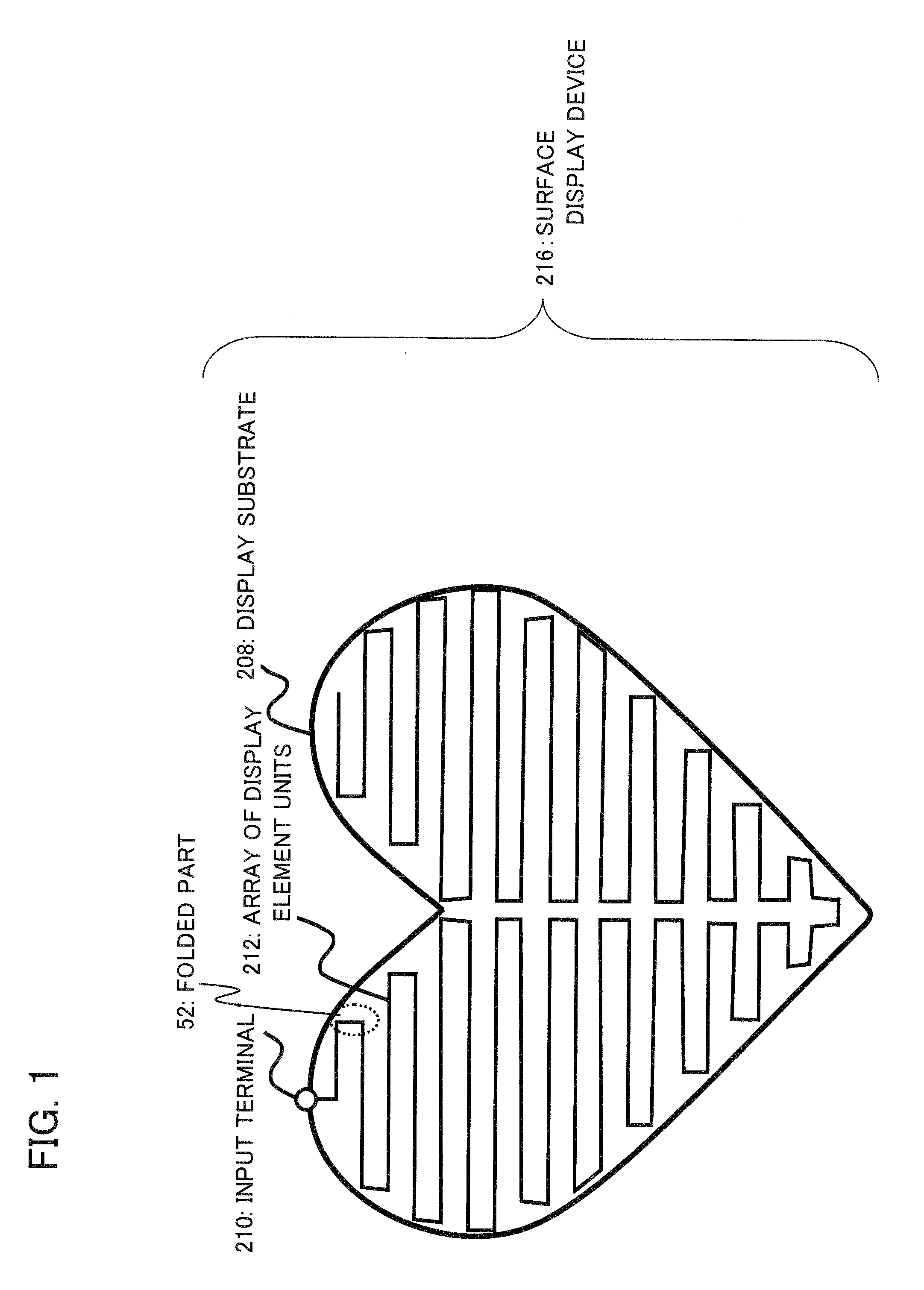

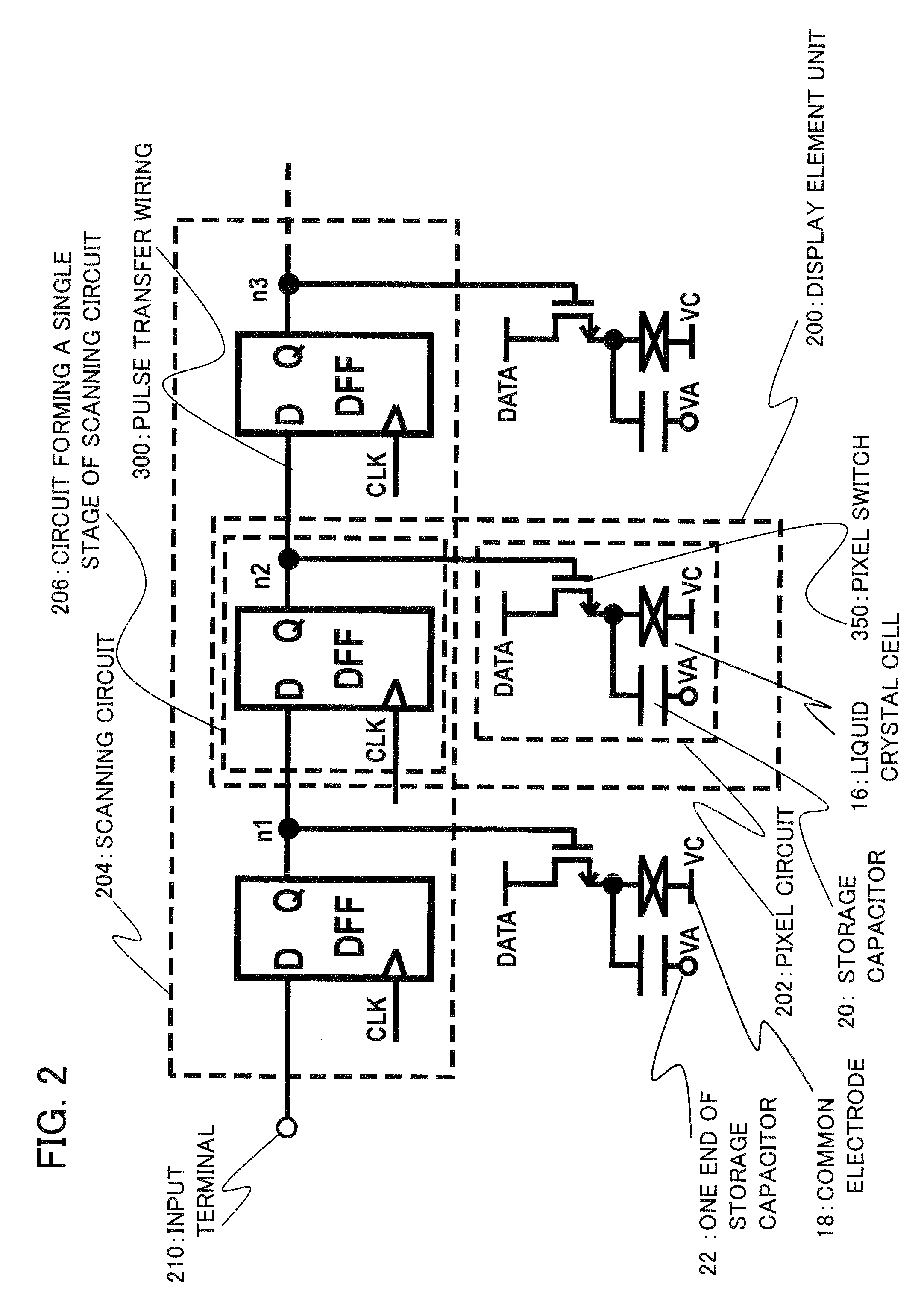

Display device

ActiveUS20080088568A1Reduce the number of connectionsReduce in quantityStatic indicating devicesNon-linear opticsSurface displaySingle stage

Disclosed is a display device for use of a surface display of an arbitrary shape, including a plural number of display element units, each made up of a circuit that forms a single stage of a scanning circuit and a pixel circuit connected to an output of the scanning circuit, are arranged in a unicursal fashion on a display substrate.

Owner:BEIHAI HKC OPTOELECTRONICS TECH CO LTD

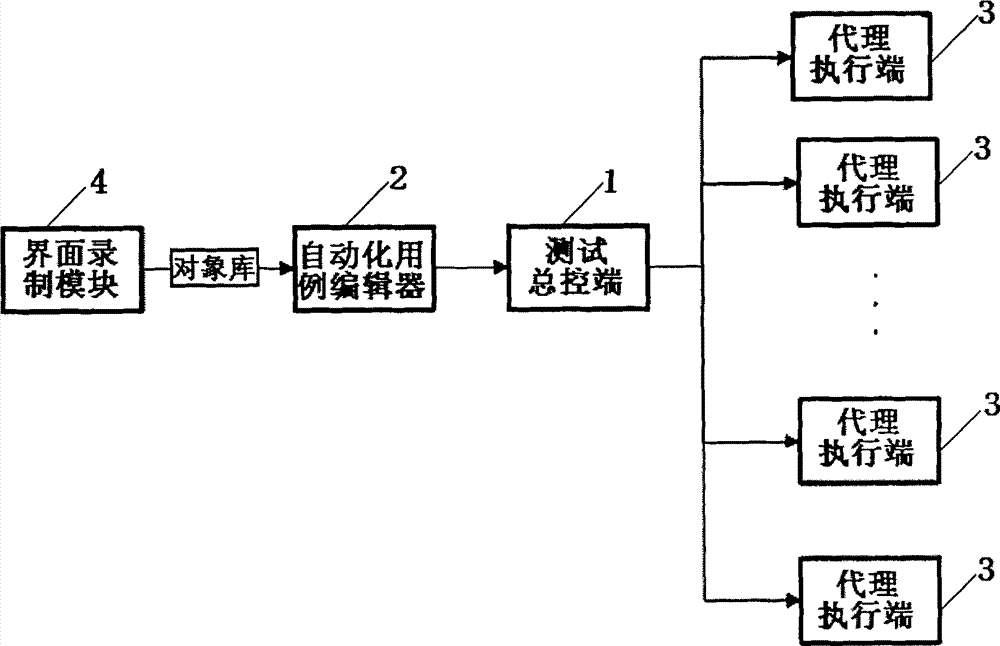

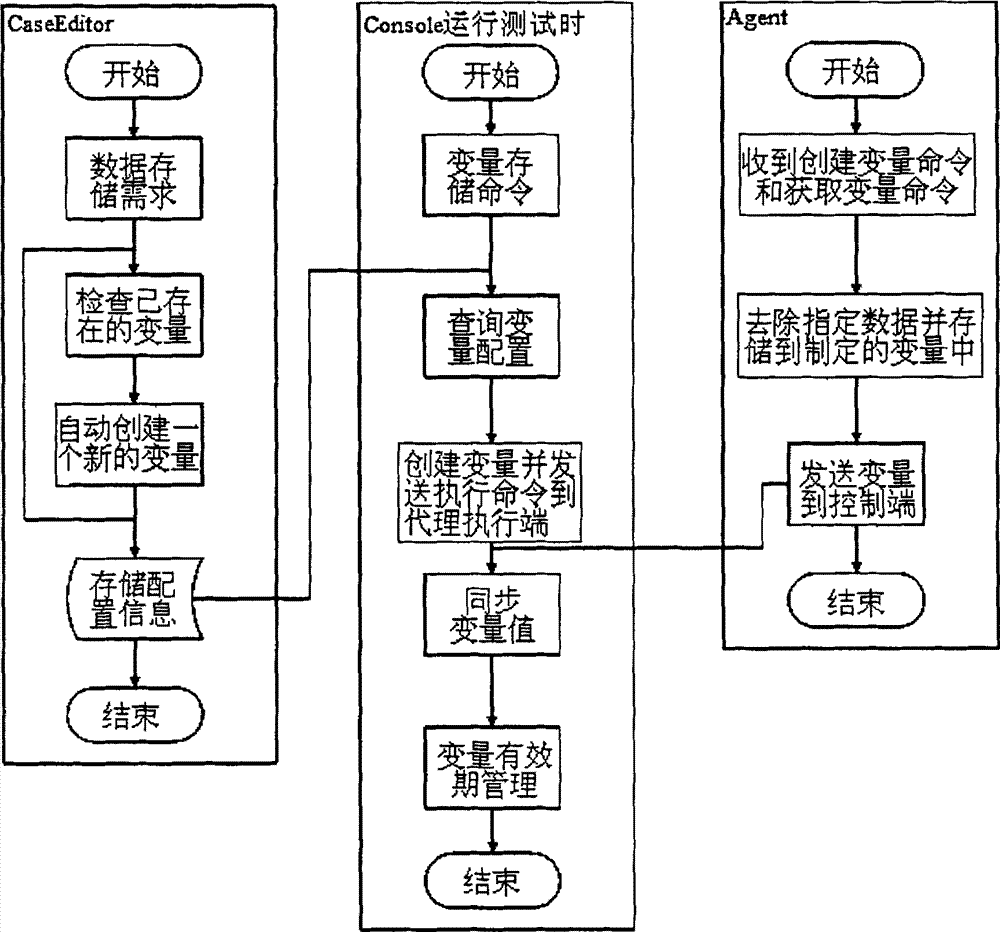

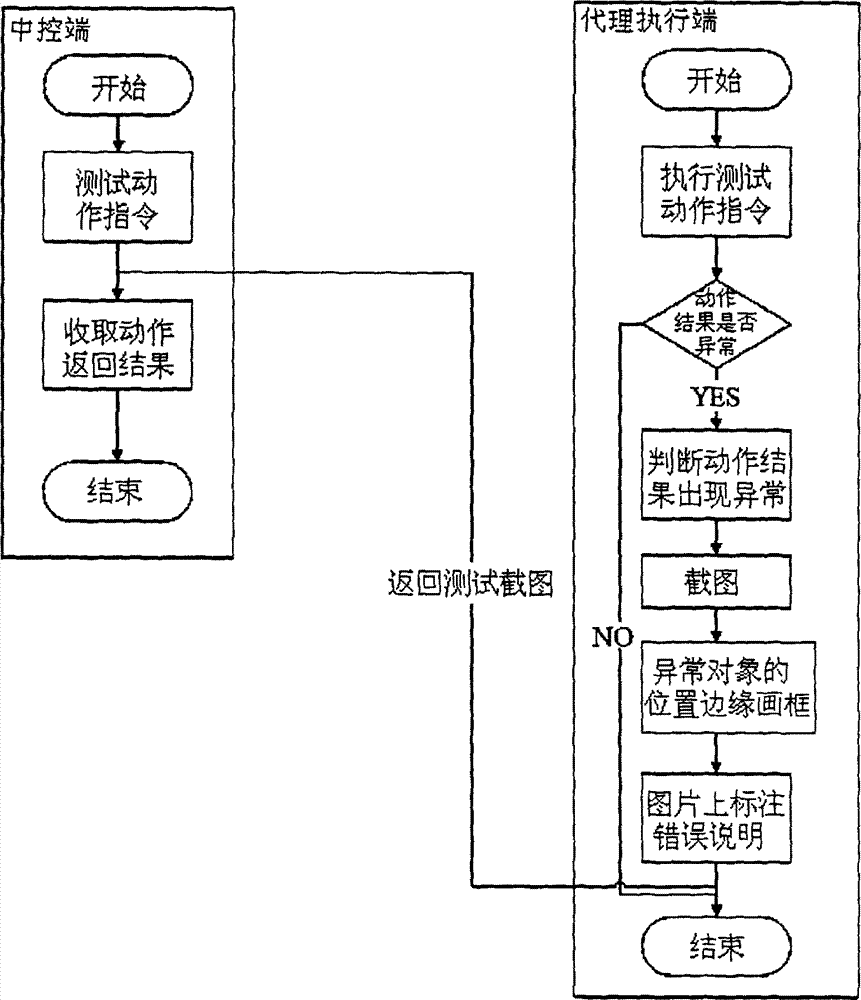

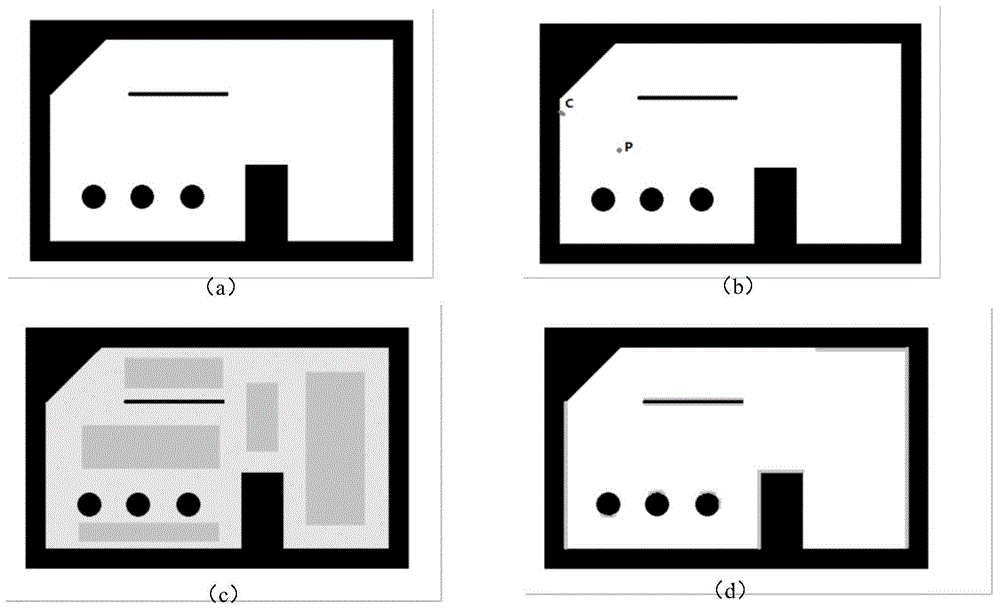

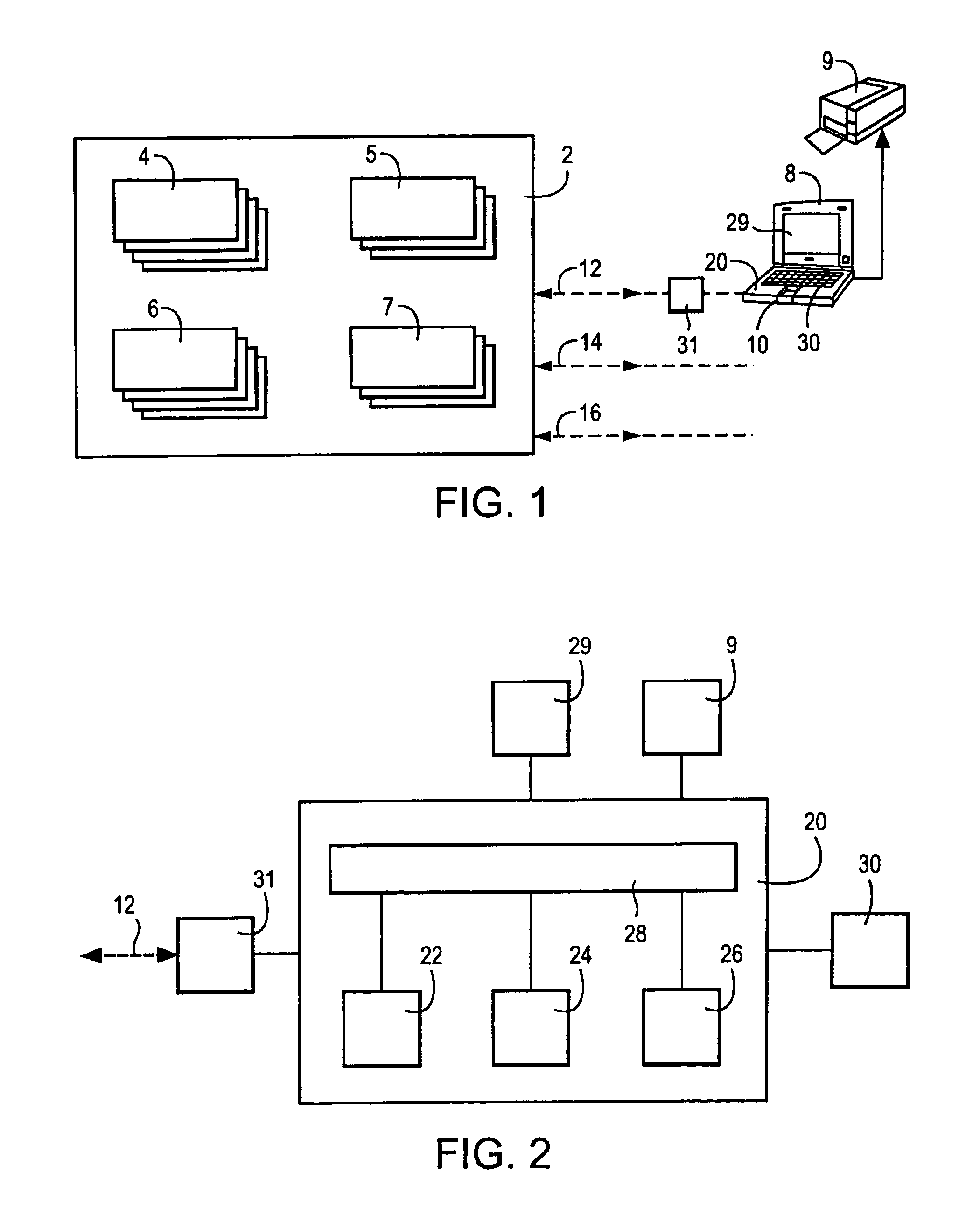

Interactive automated testing system and method thereof

ActiveCN103092756ABuild fastReduce the difficulty of buildingSoftware testing/debuggingSoftware engineeringAutomatic testing

The invention discloses an interactive automated testing system and a method of the interactive automated testing system. The interactive automated testing system comprises a test master control end which is respectively connected with an automatic use-case editor and a plurality of agent actuating ends. The automatic use-case editor is connected with an interface record module through a recorded control library file. The automatic use-case editor and the test master control end are provided with a similar natural language manager. The interactive automated testing system and the method of the interactive automated testing system firstly solves the problem how to achieve generation and usage of temporary storage data variable, and how the interactive automated testing system achieves unified management of life cycles of the data variable when a traditional mode that a programming script drives an automated testing is abandoned so as to achieve high-speed generation of an automated testing use-case, and secondly solves the problems that how to automatically and accurately marking positions of occurrences of issues on a picture after the automated testing carries out an automatic screenshot, and how to accurately and detailedly scripting the problems, and meanwhile a issue script is printed on the picture and is used as issue remark of the picture.

Owner:彭勇

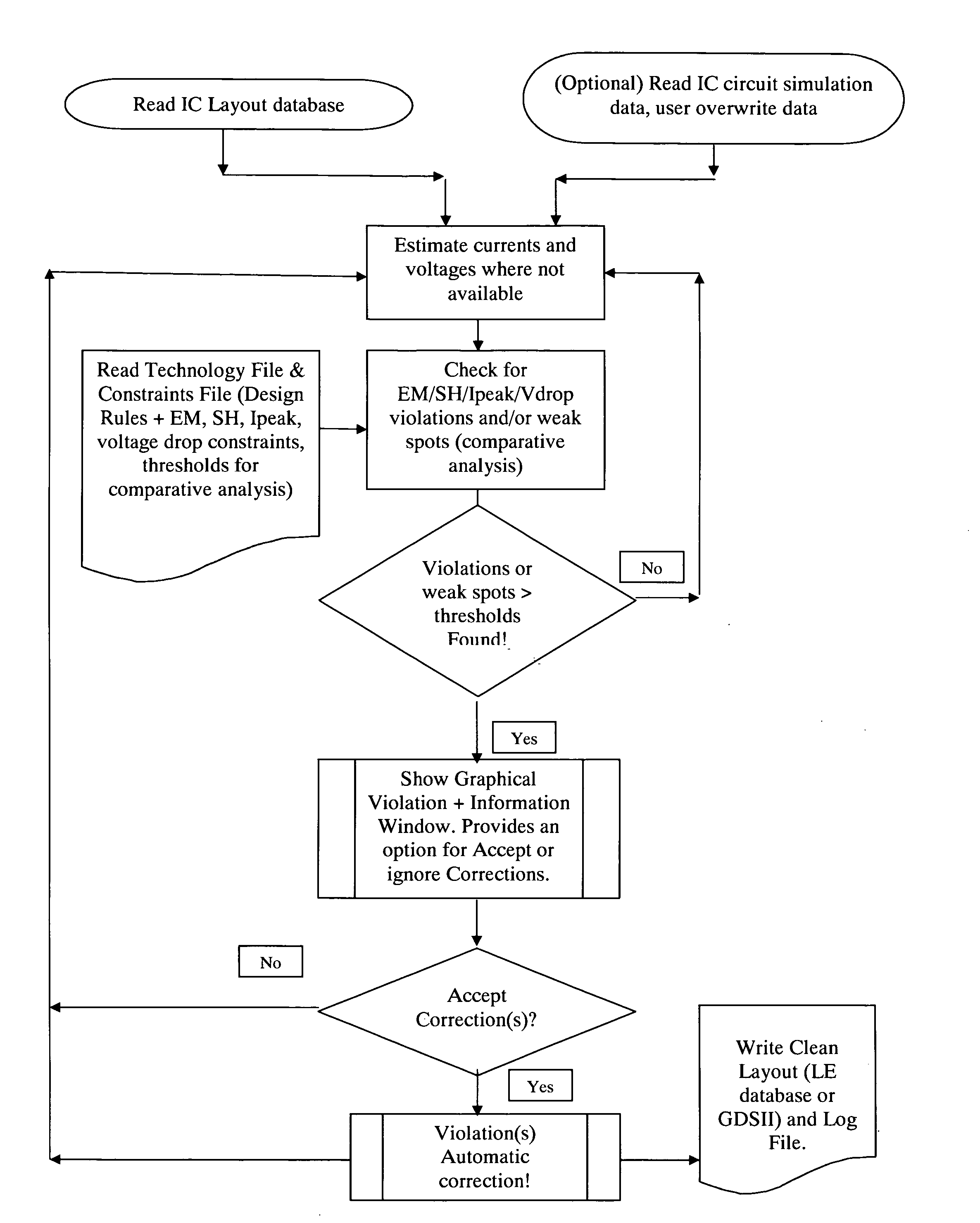

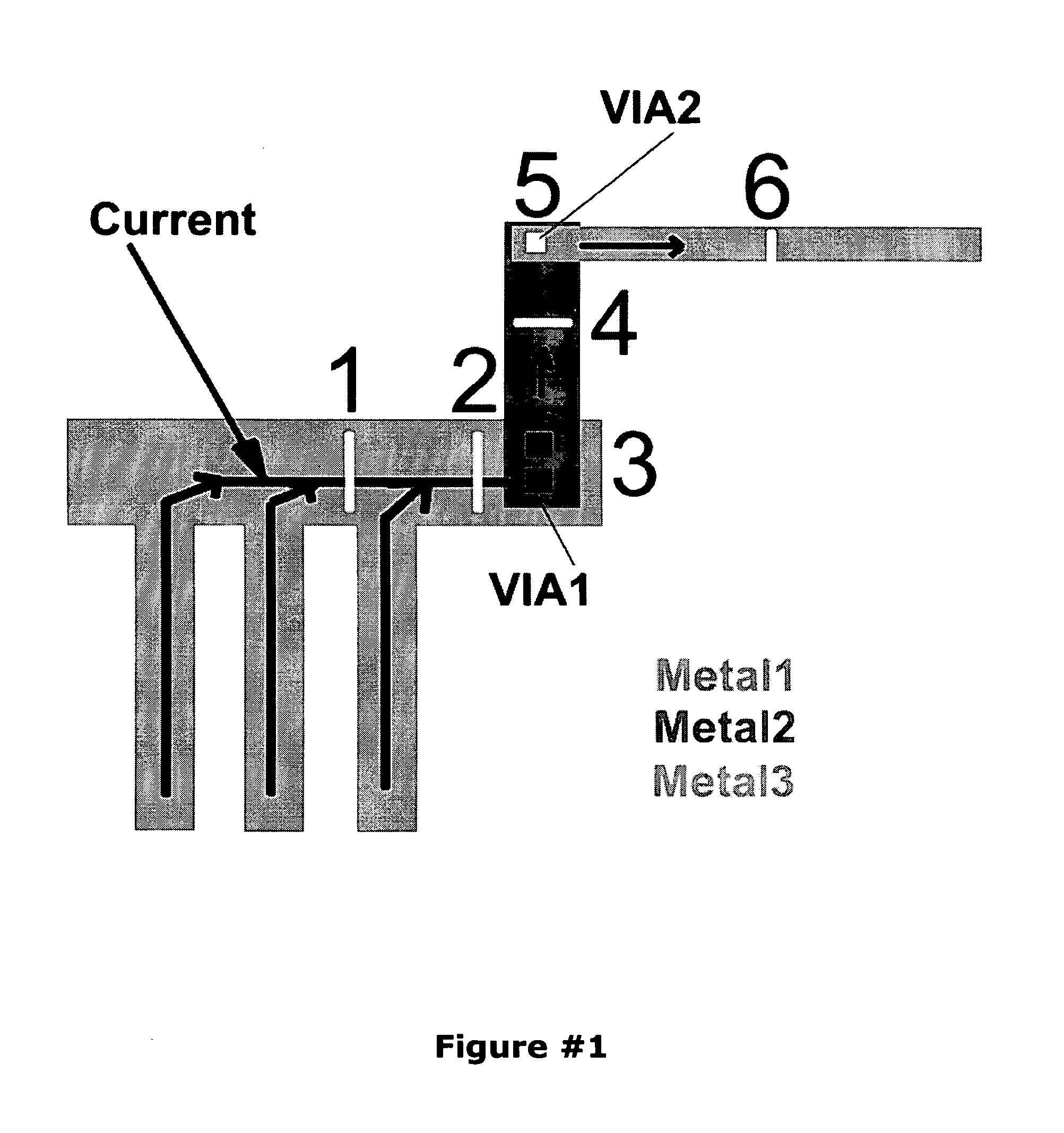

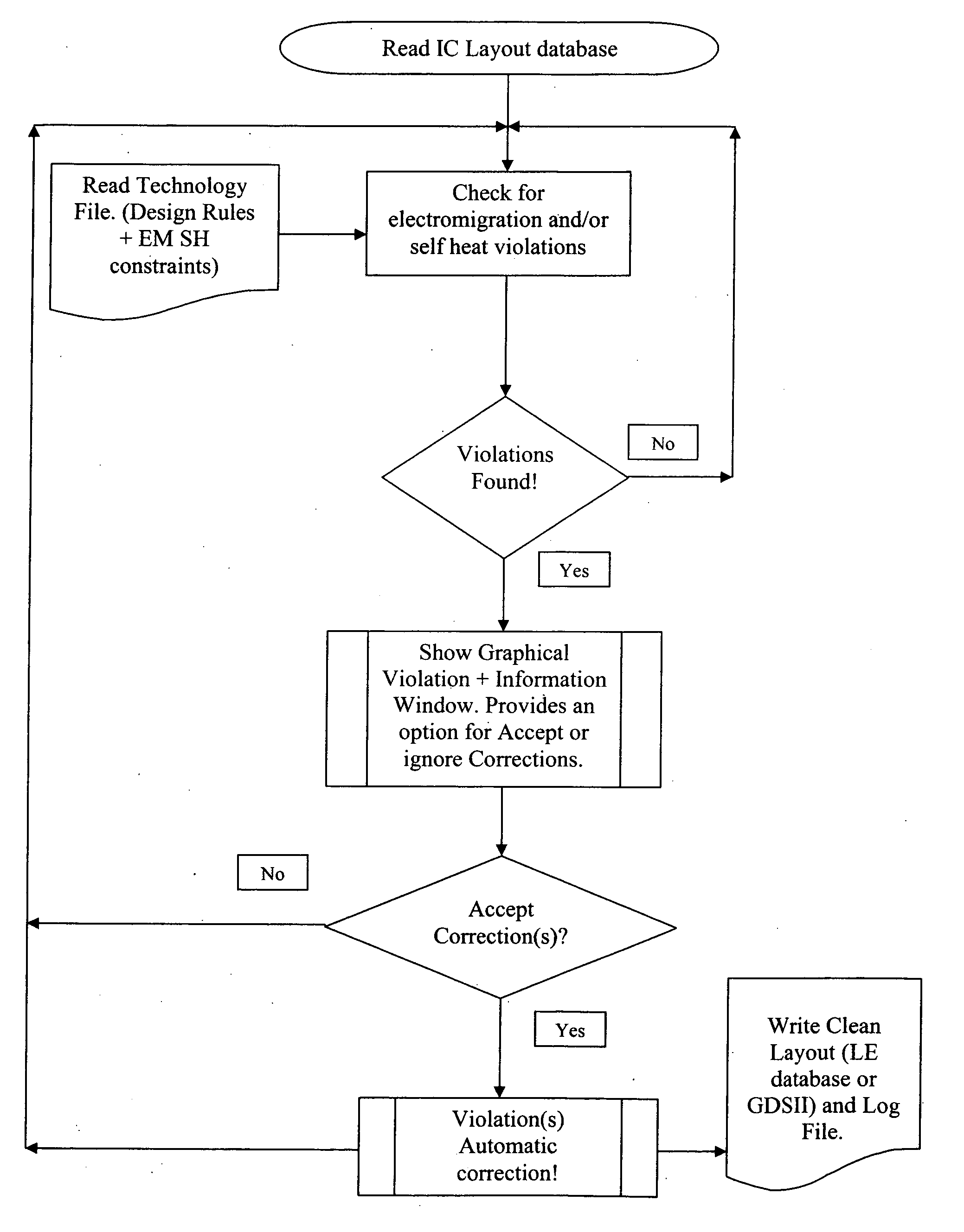

System and method for finding electromigration, self heat and voltage drop violations of an integrated circuit when its design and electrical characterization are incomplete

InactiveUS20090031264A1Eliminating and of reduced eliminatedShorten design timeComputer aided designSoftware simulation/interpretation/emulationElectricityVoltage drop

A system and method for finding electromigration (EM), self heat (SH) and voltage drop / droop violations of an integrated circuit, when its design and electrical characterization are not complete, are disclosed. The method includes analyzing polygons for average, root-mean-square (RMS) and Ipeak current densities and voltages of a mask layout block and obtaining one or more electromigration, self heat and / or voltage drop / droop rules associated with the polygon from a technology and an external constraints file. The system reads the available design simulation data to calculate the average, RMS and Ipeak current densities and voltages, and estimates the current densities and voltages when no data available. The method also includes topological analysis of the mask layout and analysis of the electrical circuit elements of the design. The method finds the polygons where the current densities are higher than electromigration and self heat rules as taken from technology or external constraints file. The method also finds the polygons where the current densities are higher than in other polygons, by the defined threshold. The method also finds the nodes where the voltage drop / droop is larger than the rule. The method also finds the polygons where the voltage drop / droop is larger than in other polygons by the defined threshold. The method and system work on GDSII, GDSIII format files and on industry standards layout editors' database.

Owner:MICROLOGIC DESIGN AUTOMATION

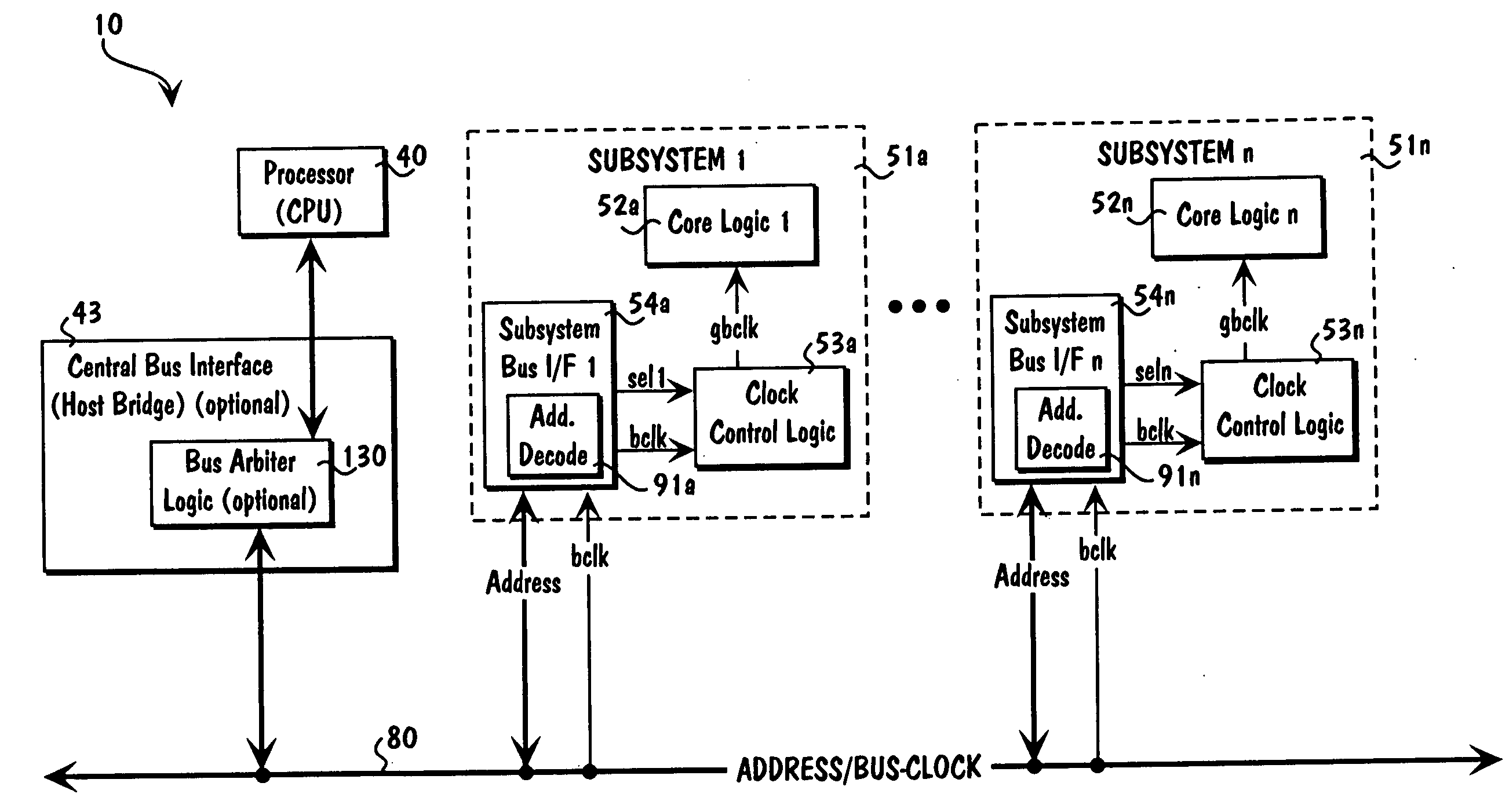

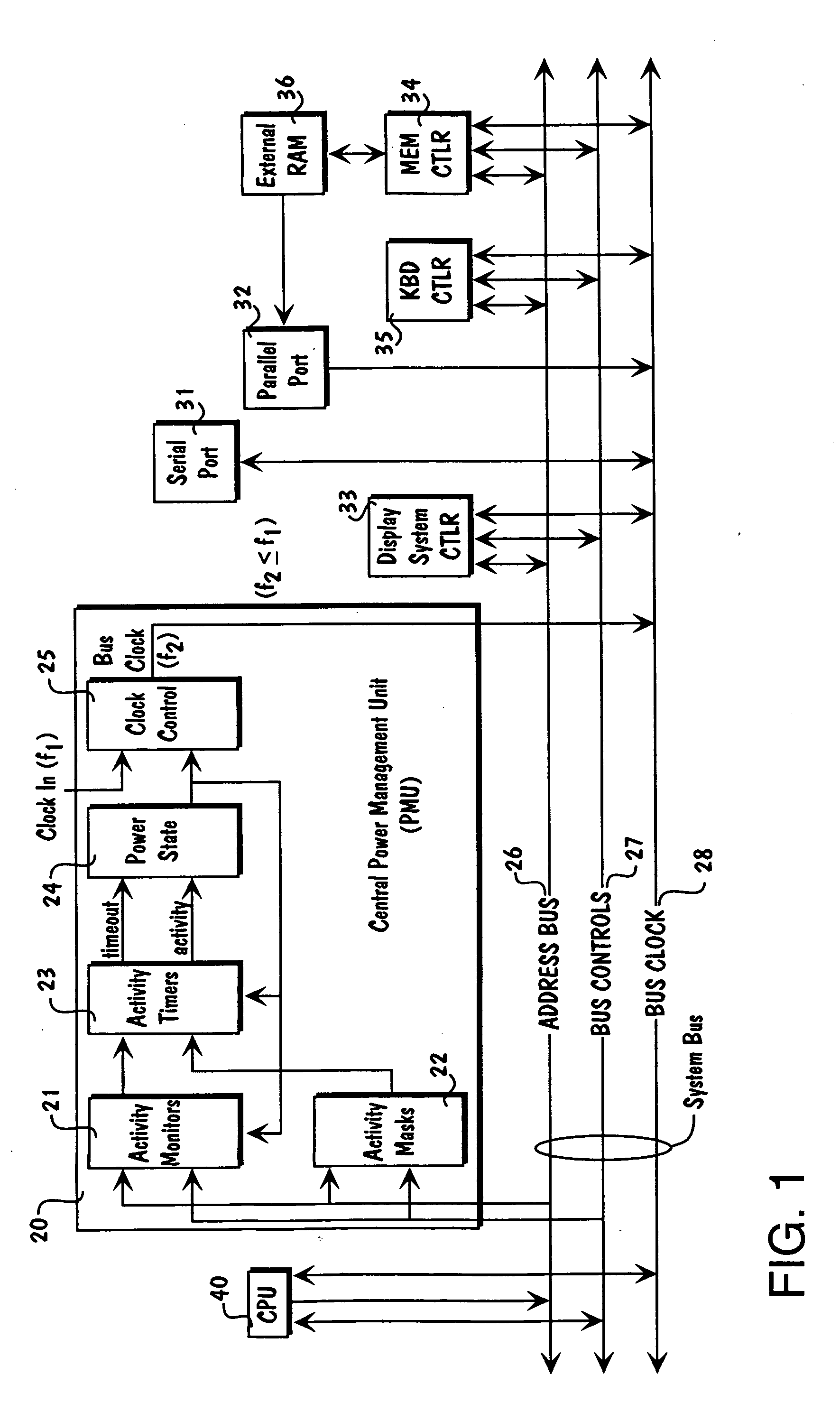

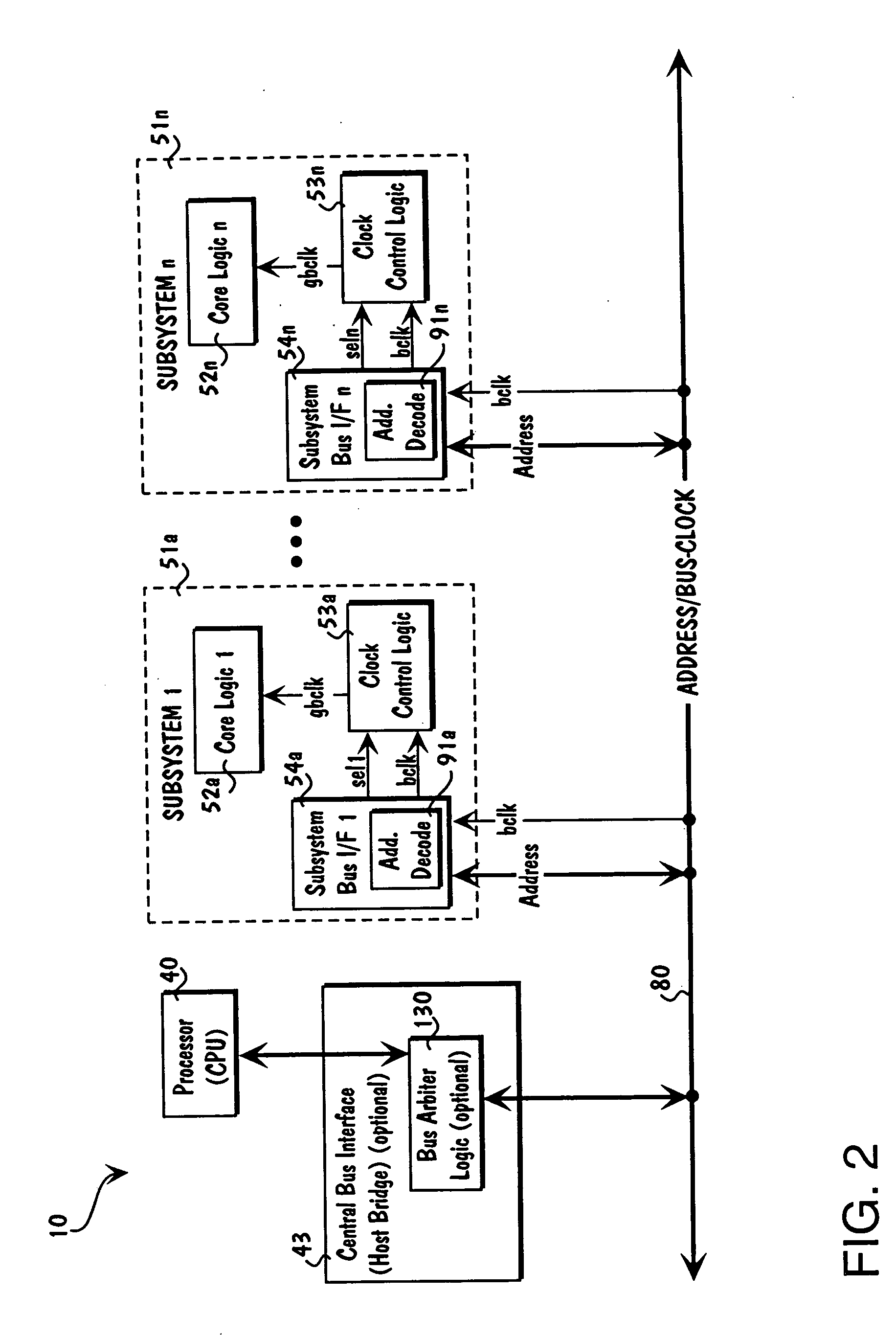

Method for modular design of a computer system-on-a-chip

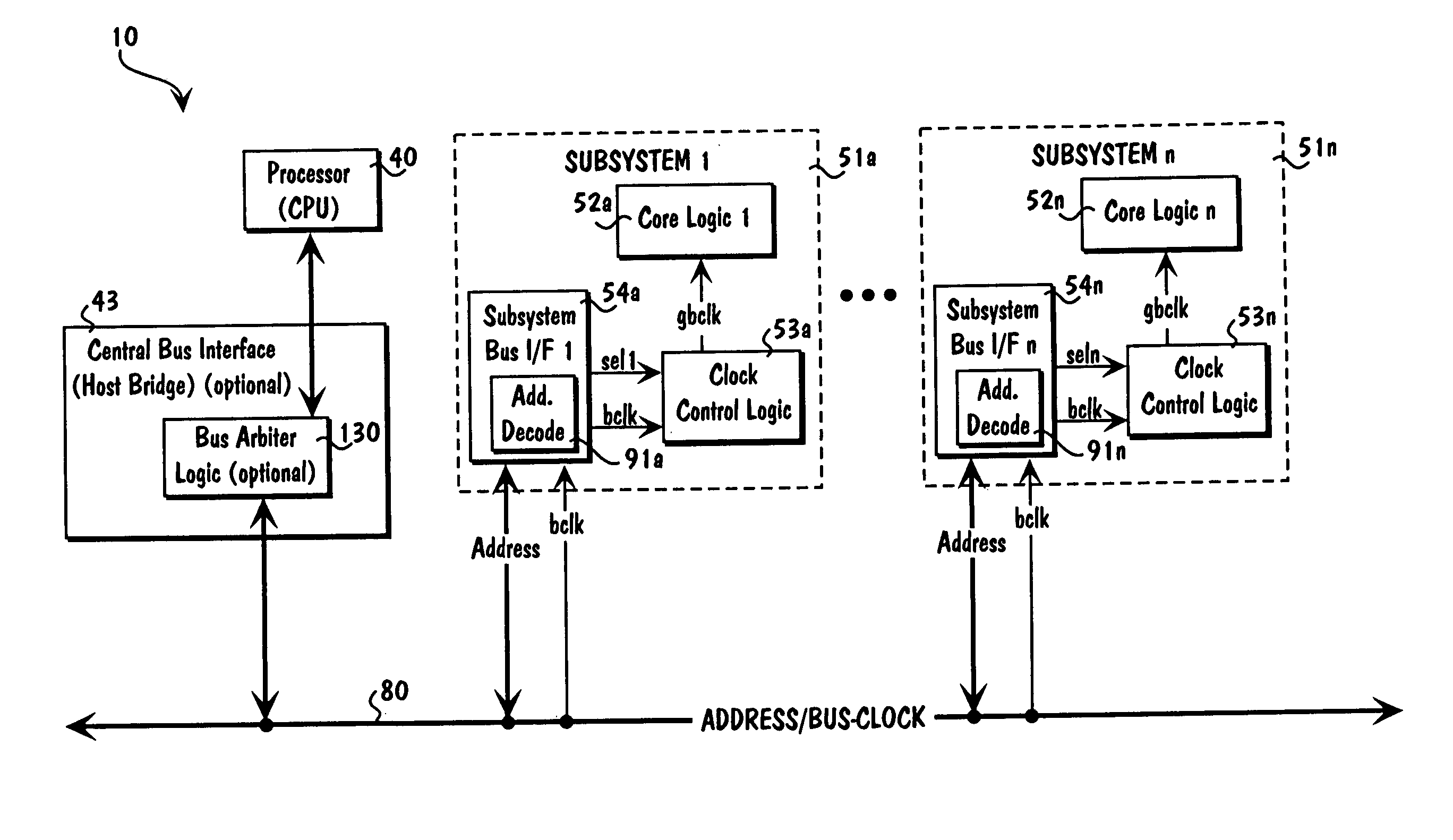

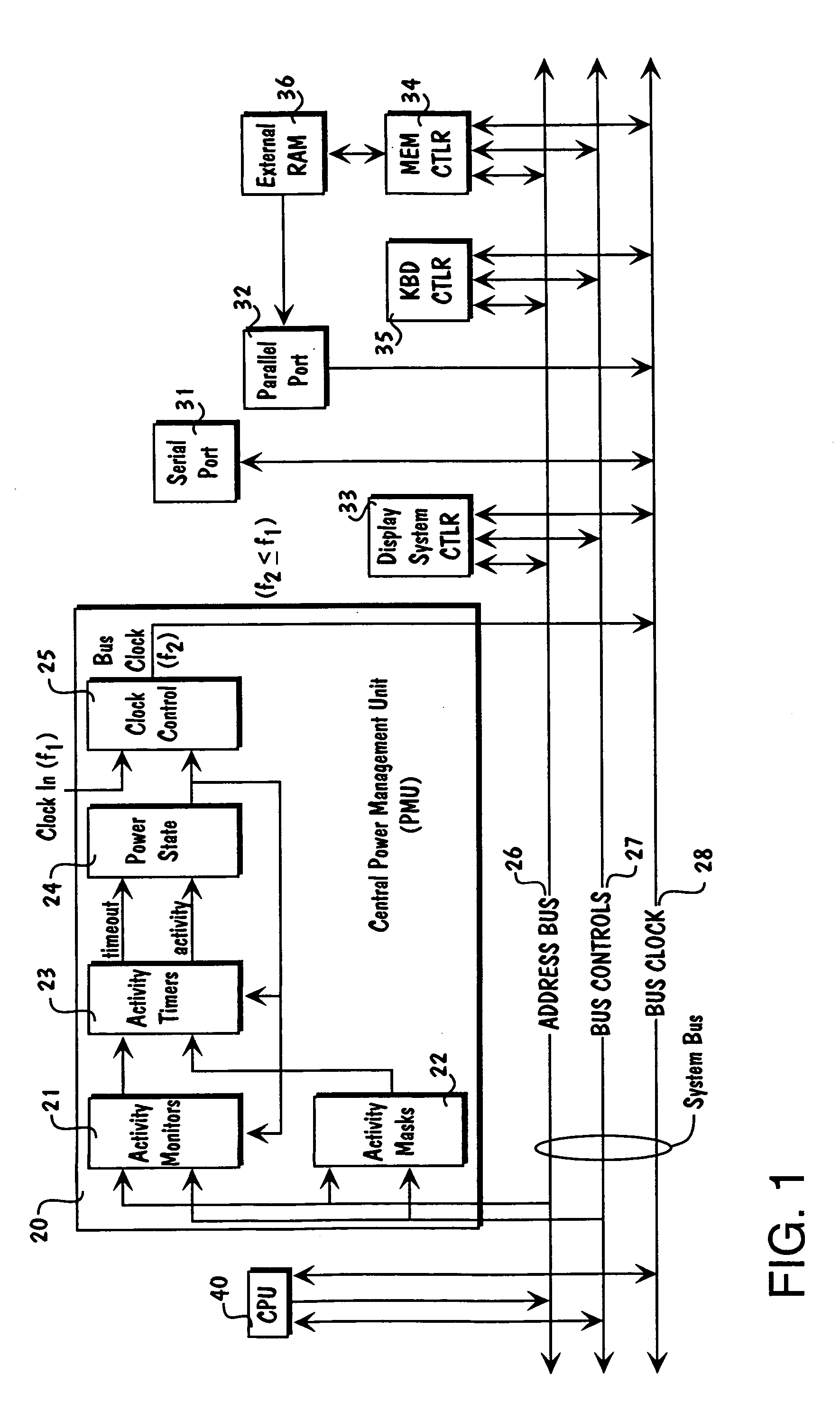

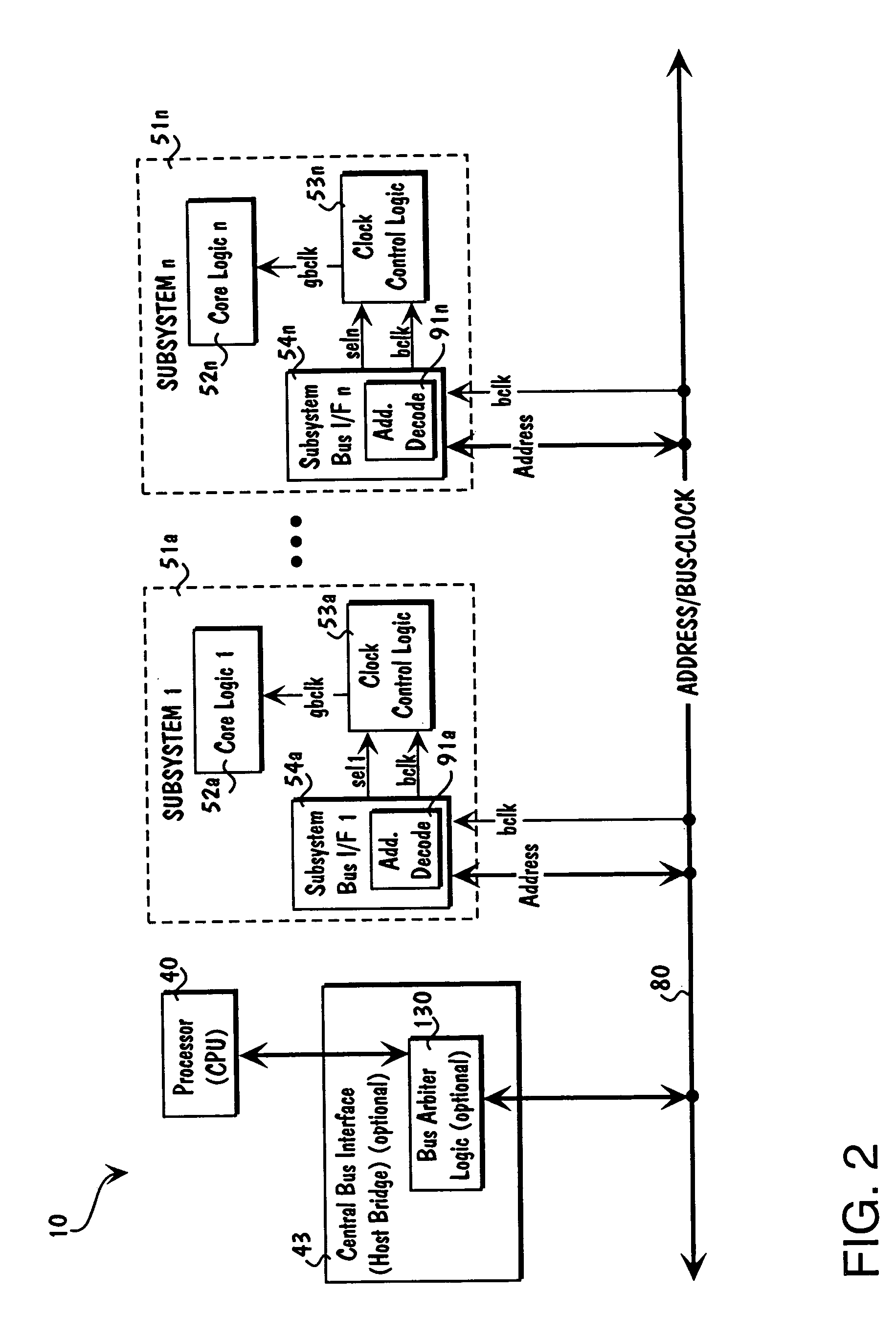

InactiveUS20050055592A1Reduce power consumptionMinimize power consumptionEnergy efficient ICTVolume/mass flow measurementComputer hardwareComputer architecture

In a computer system having a device and a communications link for communicating with the device. A method for dynamically managing power consumption by the computer system comprises associating a particular device identifier with the device. Communications are monitored over the communications link to determine whether the communications include the particular device identifier. A clock input is withheld from the device when the communications do not include the particular device identifier. Clock input is provided to the device only when the communications include the particular device identifier. The clock input causes the device to transition from a non-operational power conservative state to an operational state wherein the device consumes more power than in the non-operational state. A performance requirement is established for a task to be executed. Clock frequency is dynamically controlled according to the performance requirement established for the task being executed.

Owner:ST CLAIR INTPROP CONSULTANTS

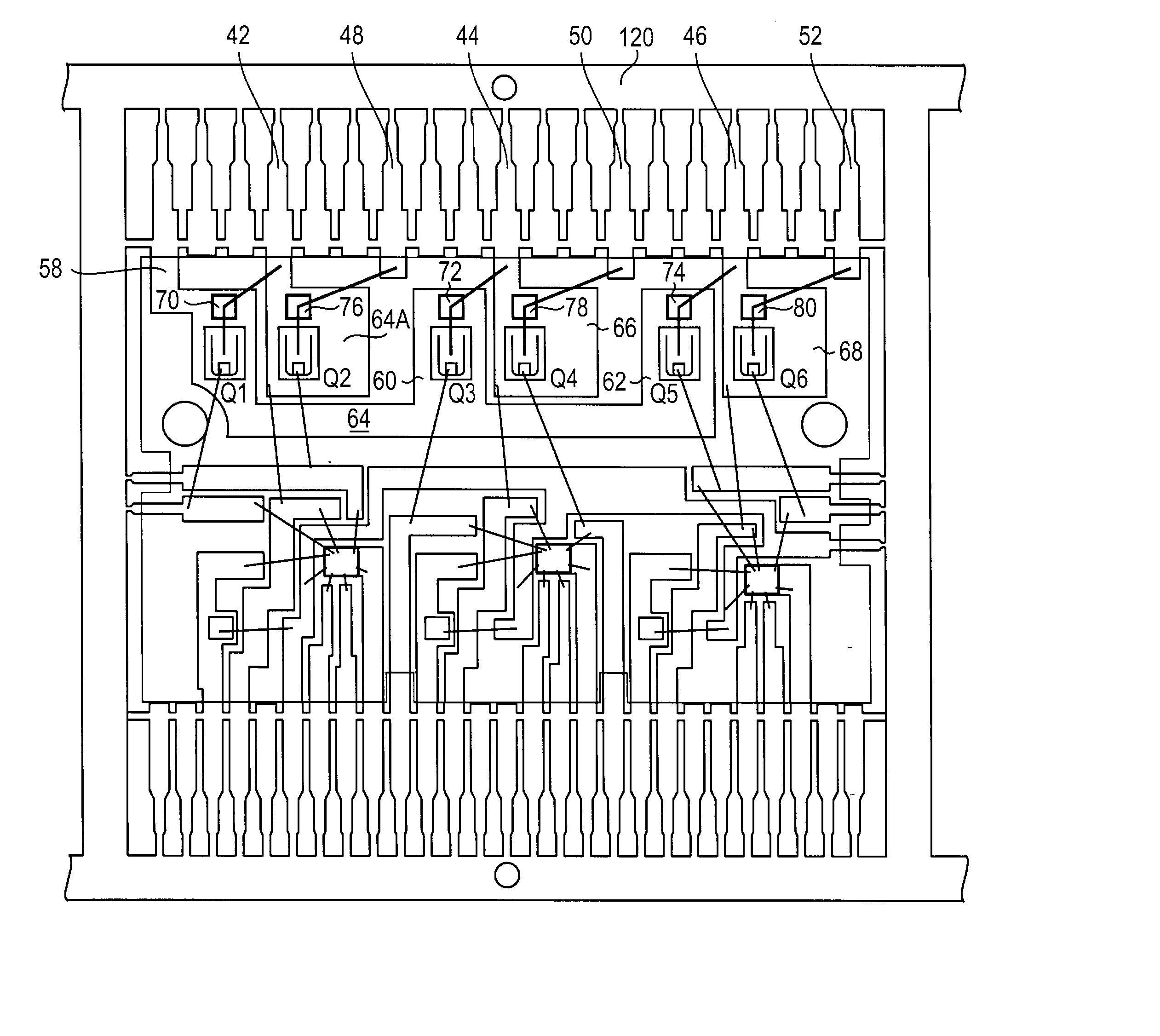

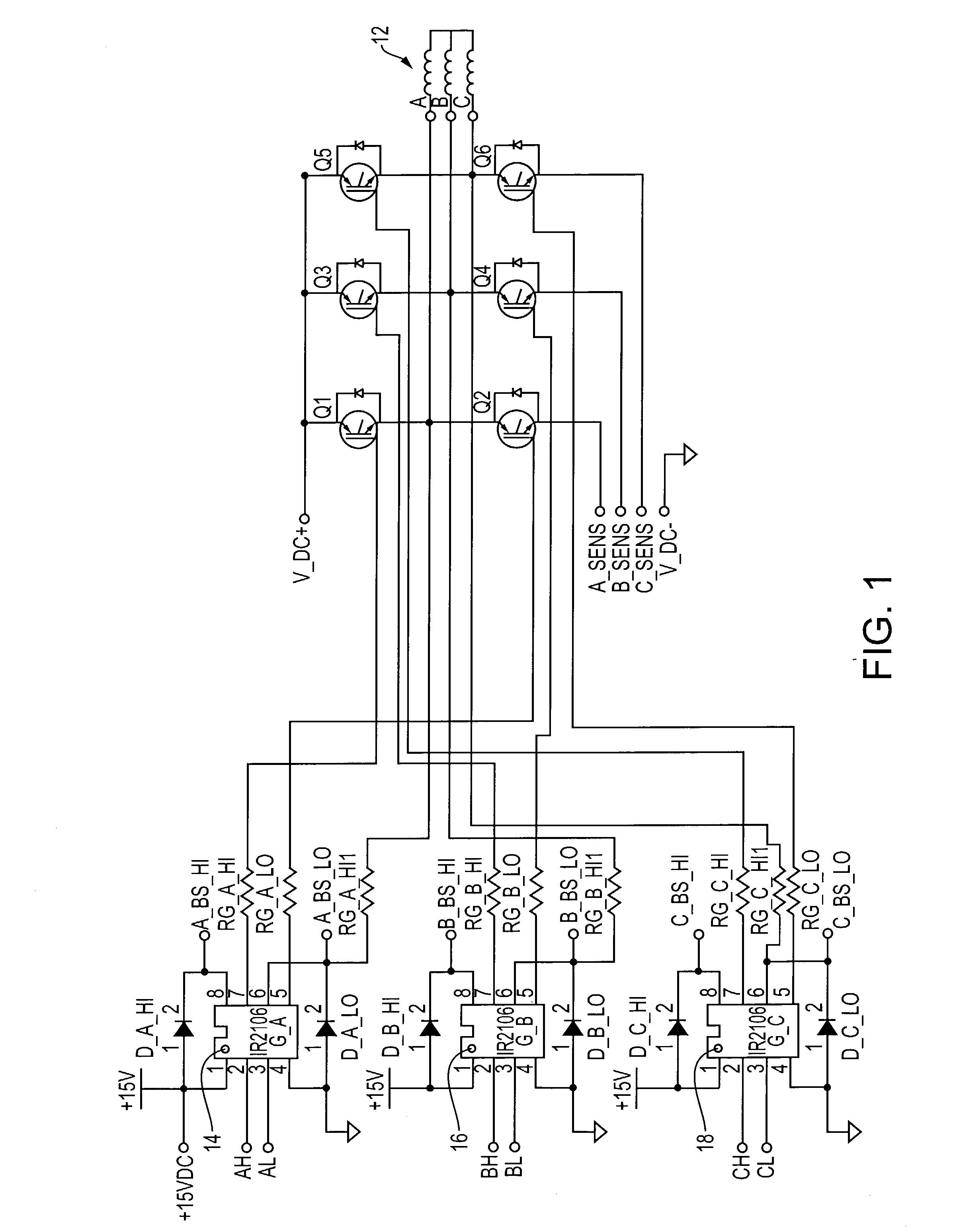

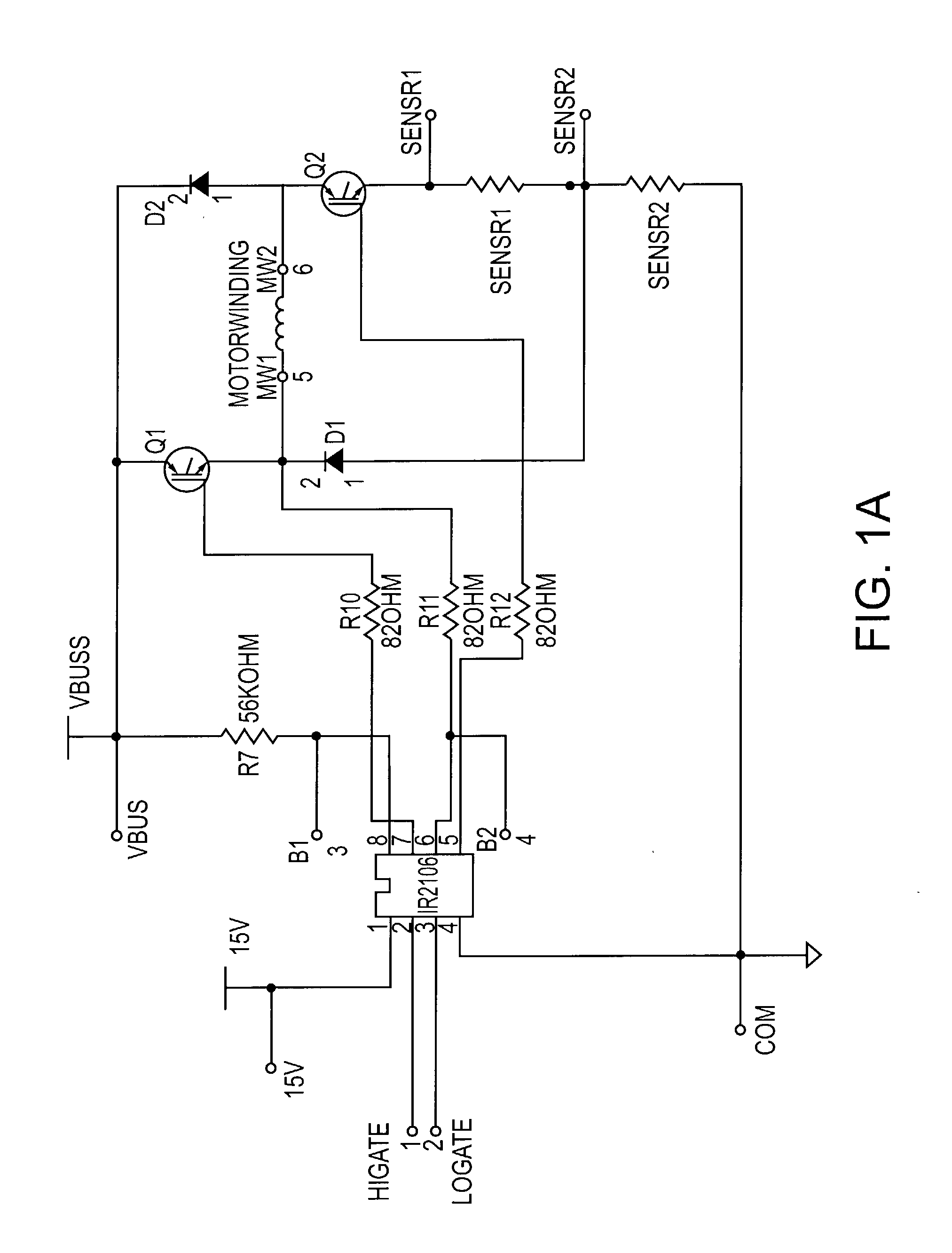

Intelligent motor drive module with injection molded package

InactiveUS20030107120A1High degree of integrationShorten design timeEfficient power electronics conversionSemiconductor/solid-state device detailsPower semiconductor deviceEngineering

A power module having a lead frame with a plurality of power switching devices and a plurality of driving devices mounted thereon. The driving devices control the power switching devices to provide power to a plurality of output leads via first wire bonds. The first wire bonds are substantially parallel to each other between the power switching devices and the output leads. Each power switching device preferably includes a power semiconductor device and a diode, the diodes and power switching devices being interconnected by second wire bonds which are also substantially parallel to each other. The power switching devices preferably comprise bare semiconductor die mounted on the lead frame, the lead frame and power switching devices being enclosed in a molded package. The molded package are preferably formed by transfer-molding or injection-molding.

Owner:INTERNATIONAL RECTIFIER COEP

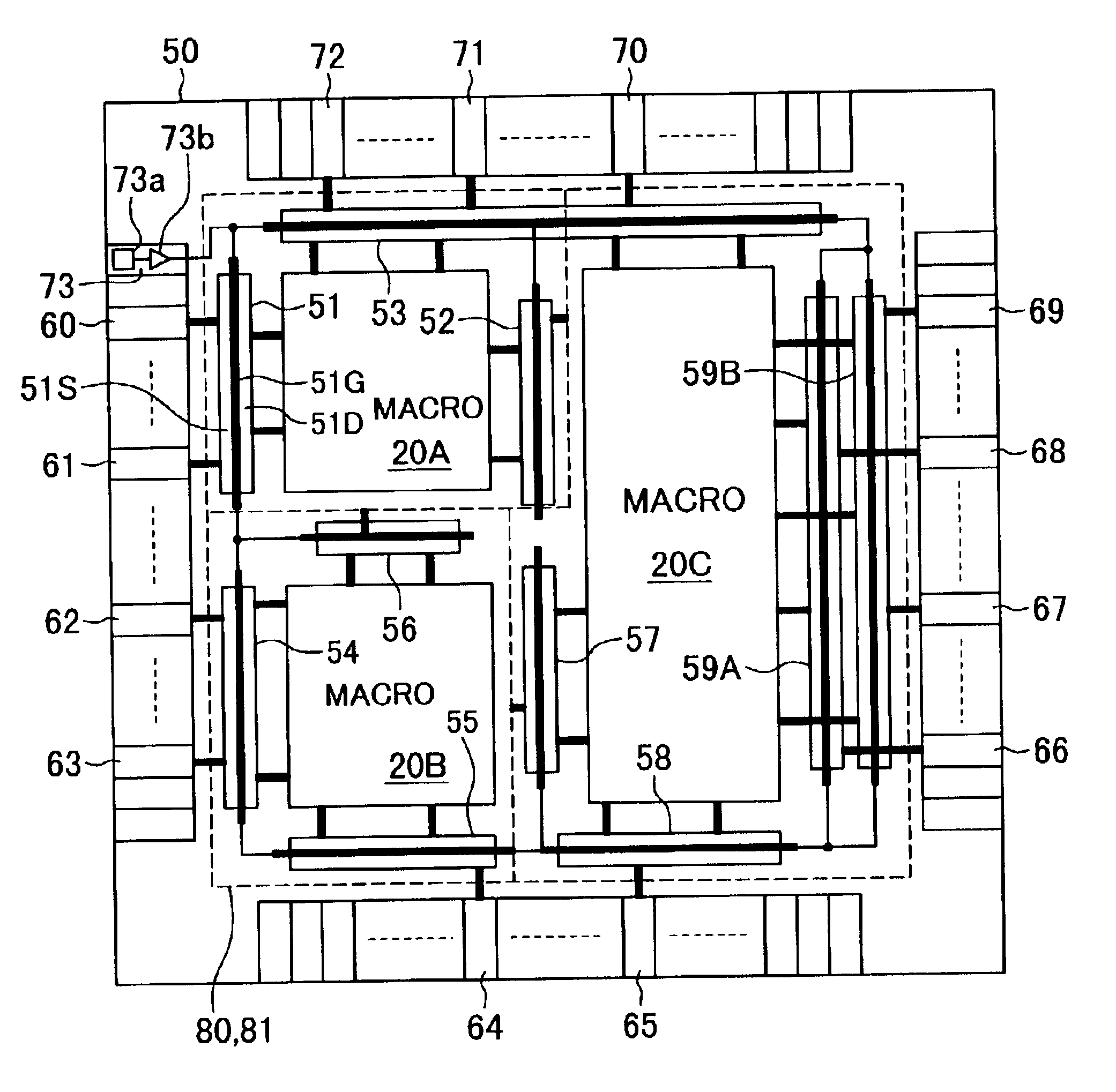

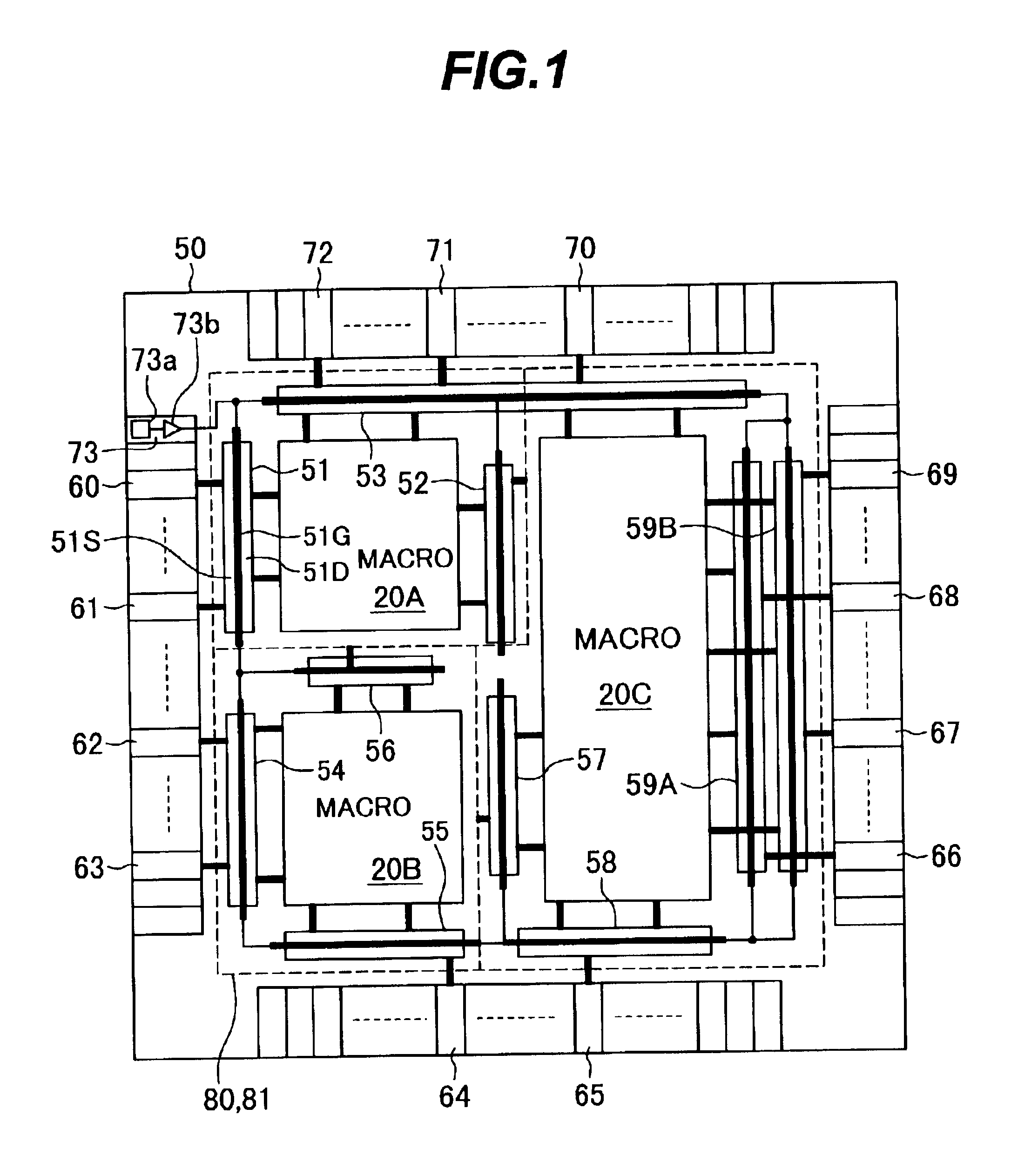

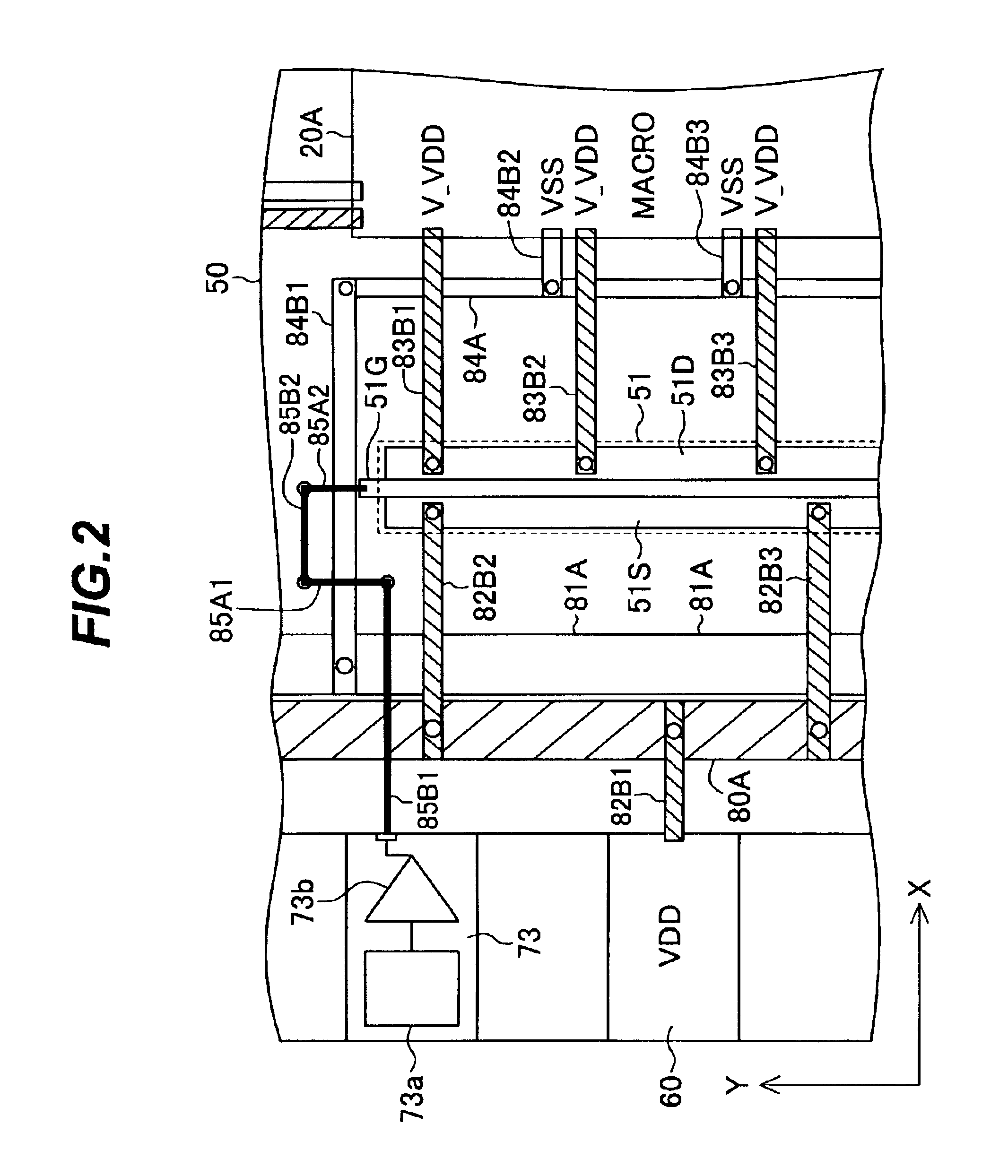

Multi-threshold MIS integrated circuit device and circuit design method thereof

InactiveUS6900478B2Shorten design timeIncrease the areaTransistorSemiconductor/solid-state device detailsEngineeringDrain current

On a chip 50A, disposed are macro cell 20A not including a virtual power supply line and a leak-current-shielding MOS transistor of a high threshold voltage, and a leak-current-shielding MOS transistor cell 51 of the high threshold voltage. The transistor cell 51 has a gate line 51G which is coincident with the longitudinal direction of the cell, is disposed along a side of a rectangular cell frame of the macro cell 20A, and has a drain region 51D connected to VDD pads 60 and 61 for external connection, the gate line 51G connected to an I / O cell 73 and a source region 51S connected to a VDD terminal of the macro cell 20A. This VDD terminal functions as a terminal of a virtual power supply line V_VDD.

Owner:SOCIONEXT INC

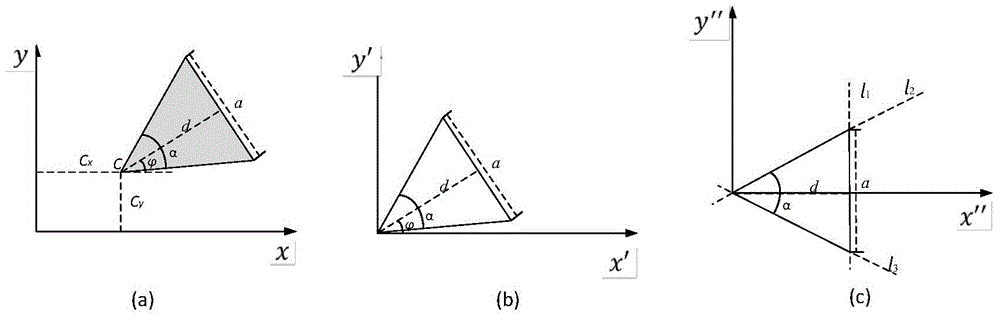

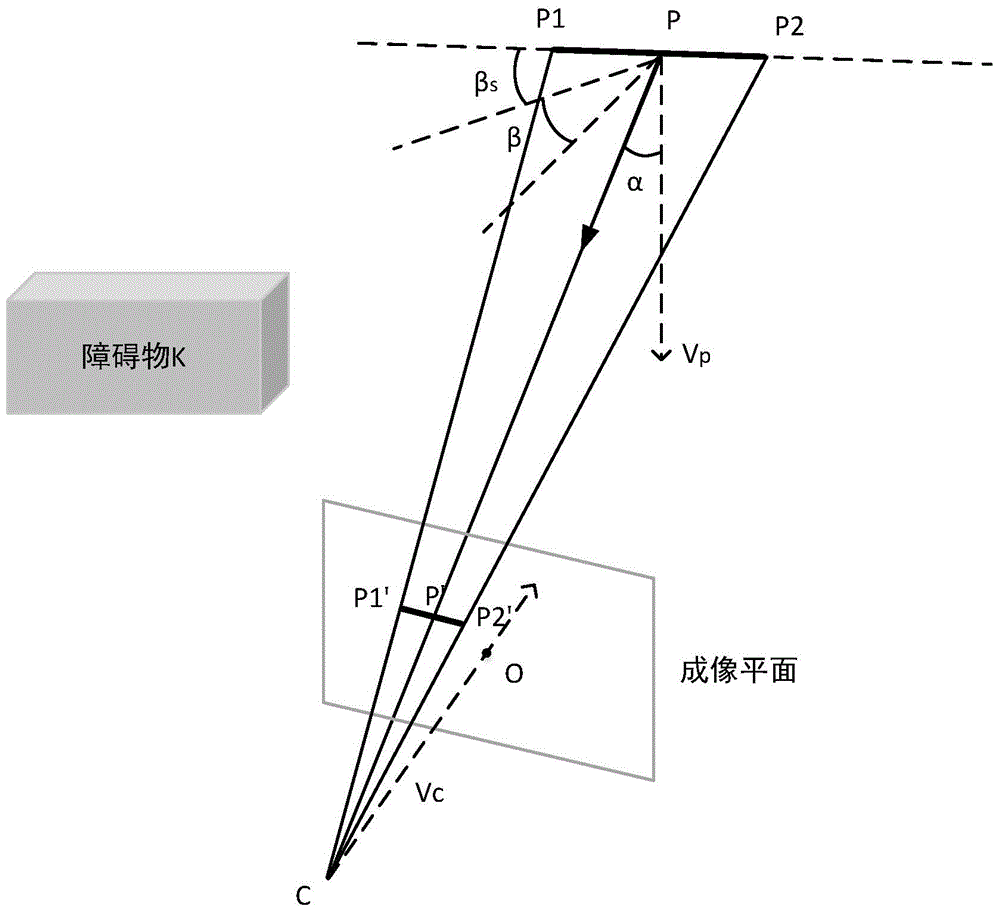

Camera layout optimization method for large-scale scene monitoring

InactiveCN104469322ASimplify design stepsShorten design timeTelevision system detailsColor television detailsVideo monitoringMathematical model

The invention discloses a camera layout optimization method for large-scale scene monitoring, and relates to the technical field of video monitoring. The method includes the following steps of conducting modeling of a monitoring scene, conducting modeling of monitoring requirements, and obtaining the optimal camera layout scheme through the optimization algorithm. According to the scheme, mathematical models can be established for the layout optimization problem of a whole camera, the layout optimization problem of multiple cameras is converted into the linear programming problem, and the optimal camera layout scheme meeting the monitoring requirement can be automatically achieved under the condition that multiple constraint conditions exist. The design steps can be simplified while the design effect is ensured, the design time is saved, and the scientific basis is provided for the camera layout optimization for the large-scale scene monitoring.

Owner:CHONGQING UNIV

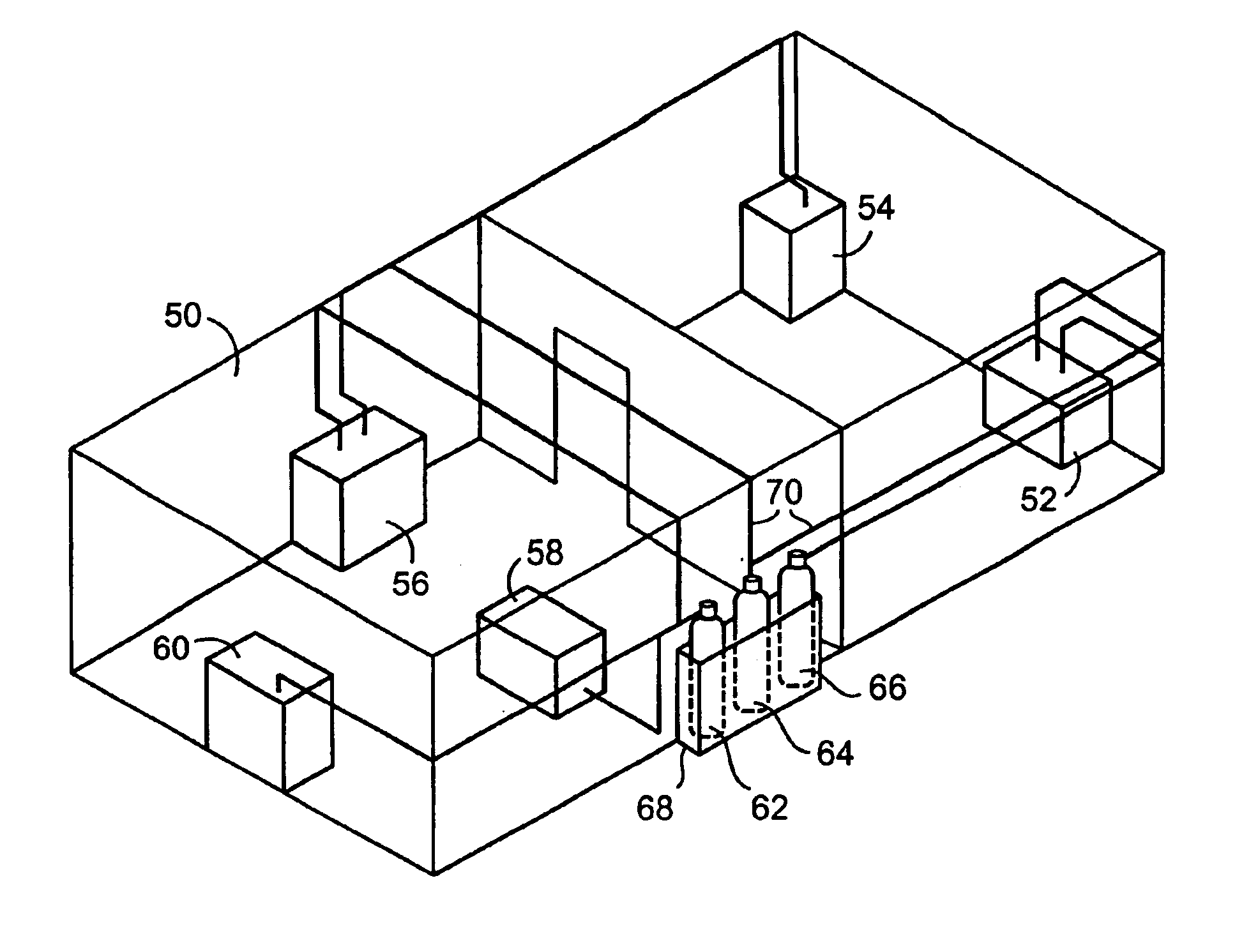

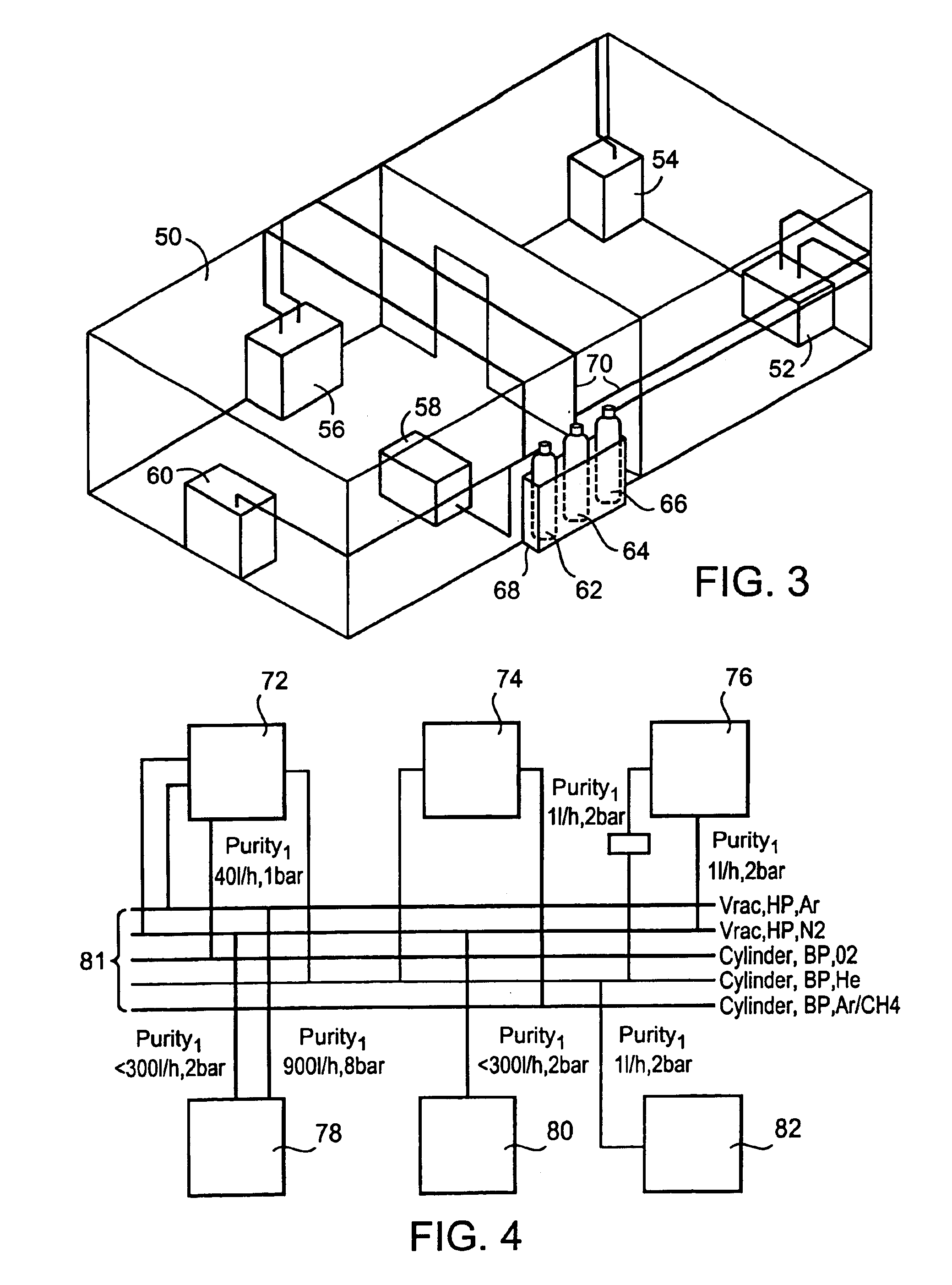

Process and apparatus for producing a diagram of an installation comprising apparatuses supplied with gas

InactiveUS6865522B1Rapid productionShorten design timeData processing applicationsComputer controlProcess engineeringProduct gas

The invention relates to a process for producing a diagram of an installation using apparatuses, each apparatus being supplied with gas, comprising:the consultation of one or more databases (5) comprising, for each apparatus, data on the flow rate, the nature, the purity of the gas supplying the apparatus, and the supply pressure of that gas for that apparatus,the selection, for each apparatus, of a value, or of a limit value, of duration or of frequency of use,the calculation, for each apparatus, of the consumption, or of the limit consumption, according to the utilisation value and to the flow rate data,the calculation, for each gas and for each gas purity, of the total of the consumptions of all of the apparatuses,the indication of technical constraints,the consultation of a database (5) for proposing, for each gas and each gas purity, a packaging, as a function of the consumption and of the technical constraints relating to the storage of the gas and / or to their delivery.

Owner:LAIR LIQUIDE SA POUR LETUDE & LEXPLOITATION DES PROCEDES GEORGES CLAUDE

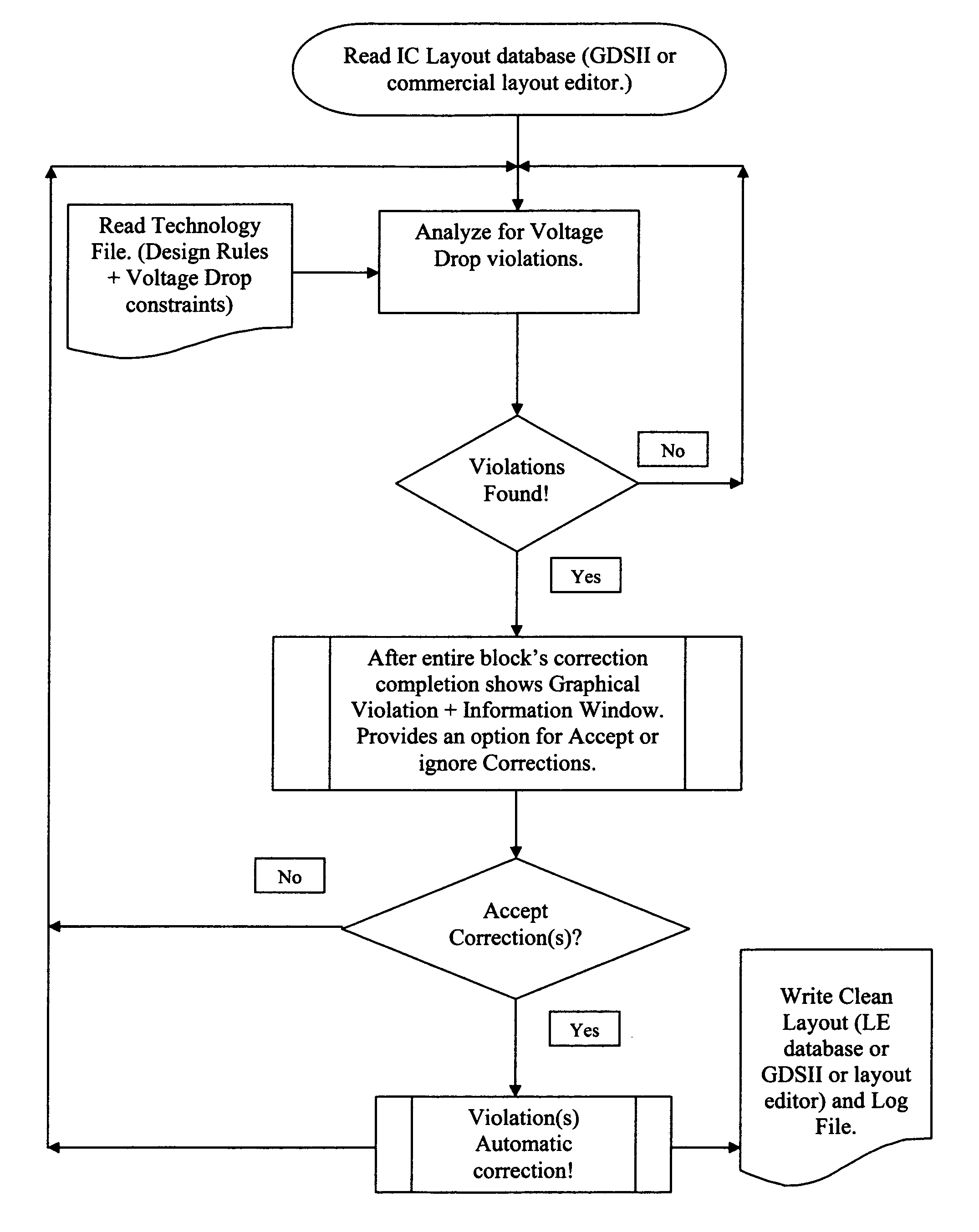

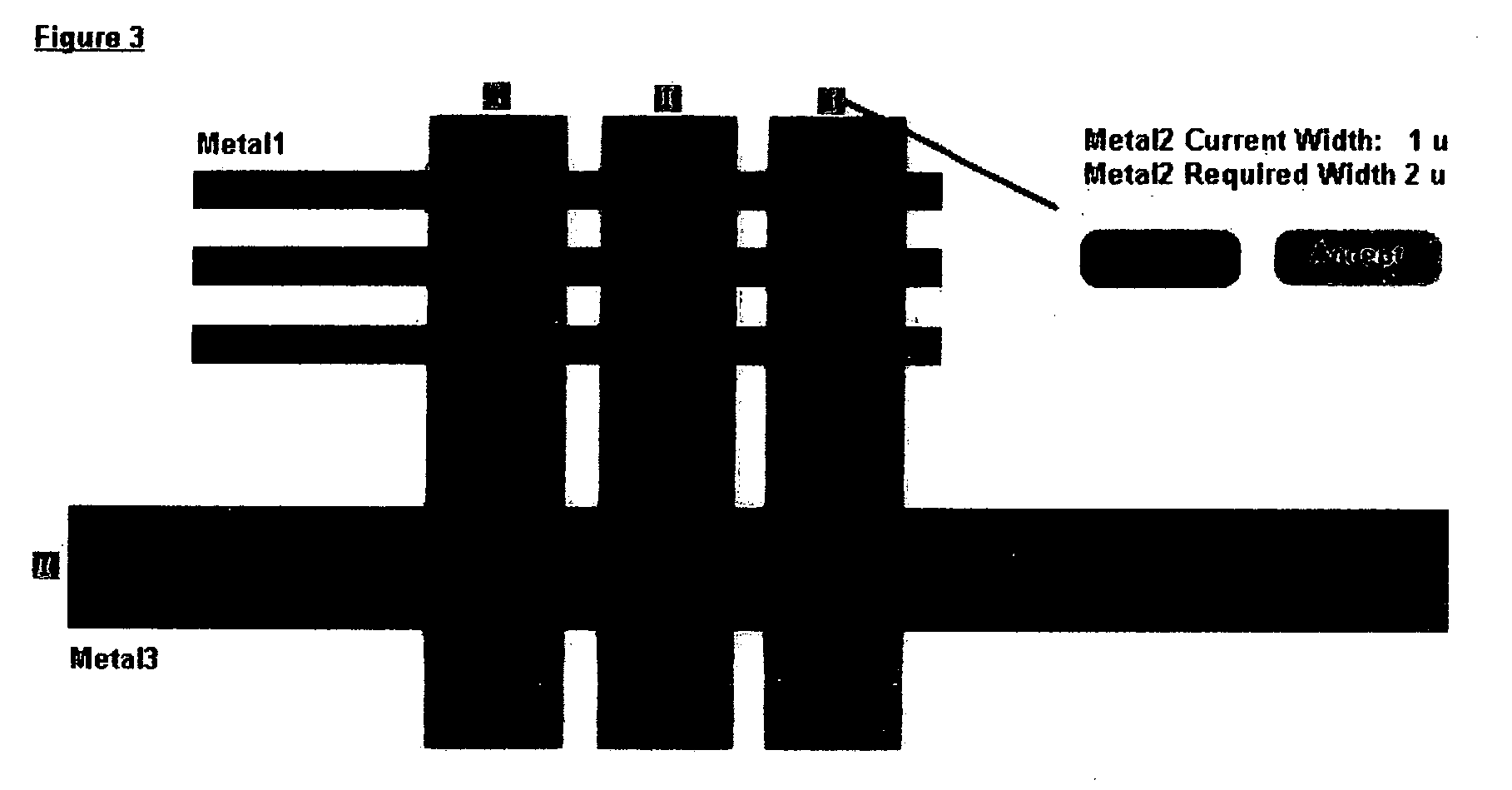

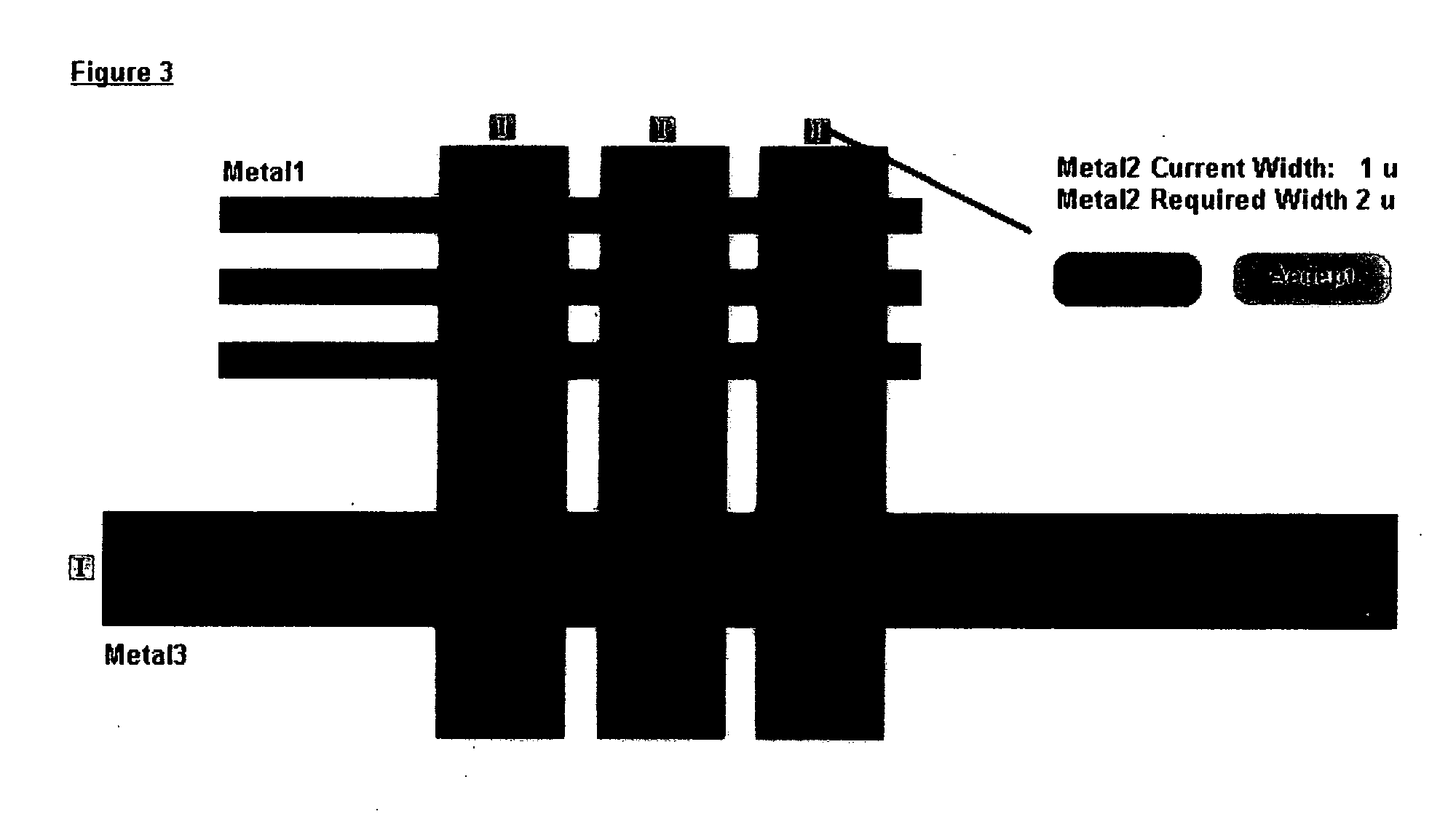

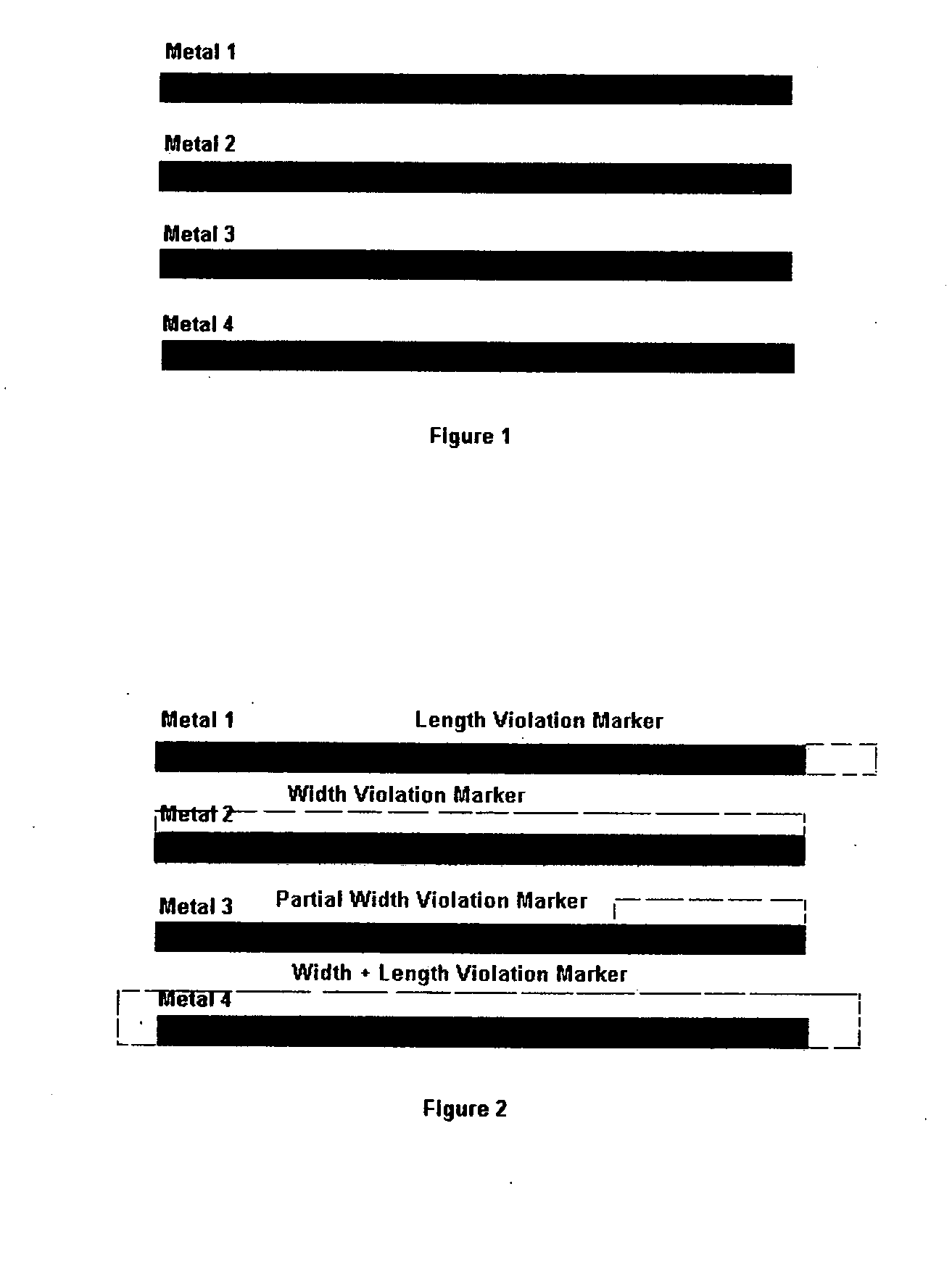

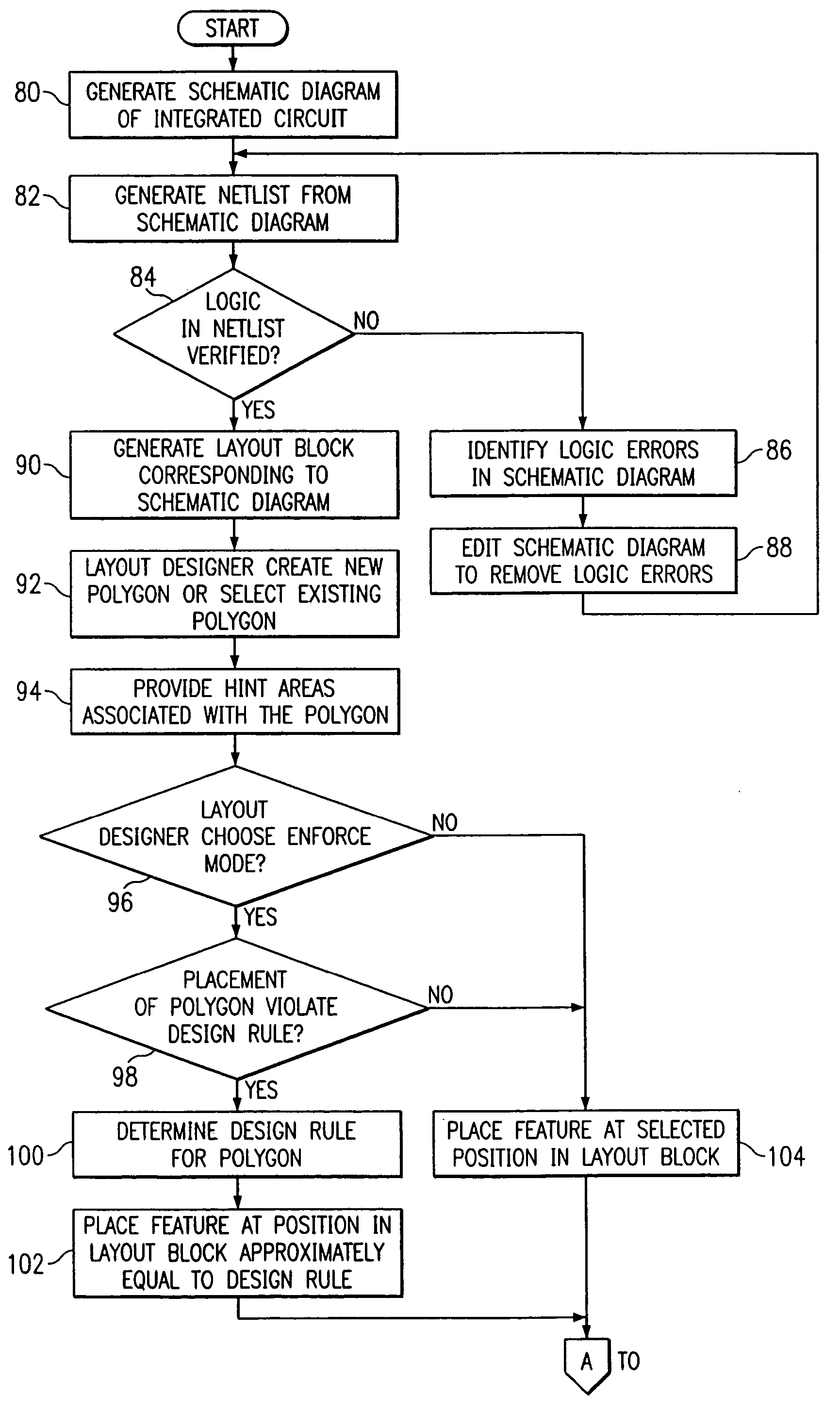

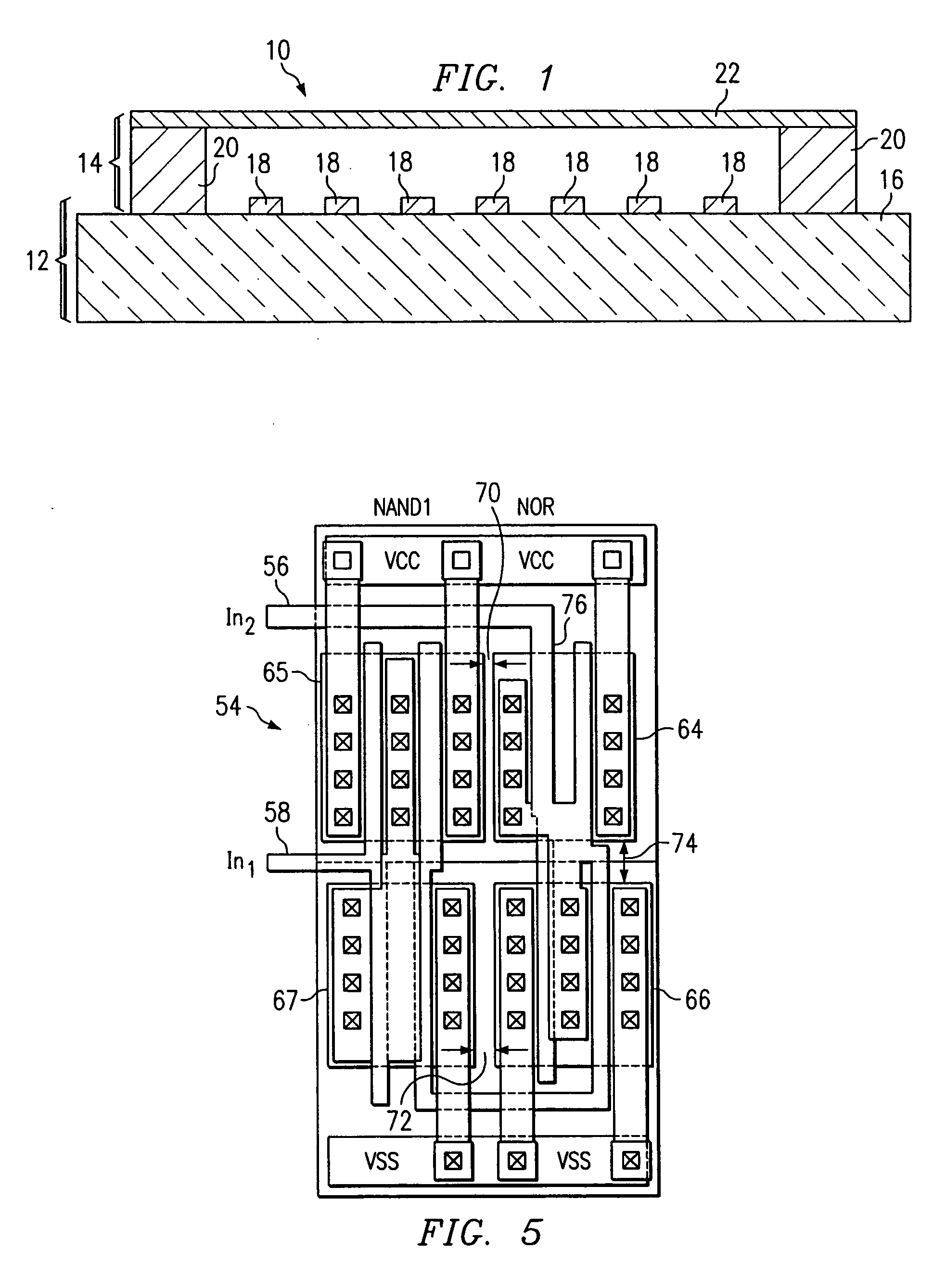

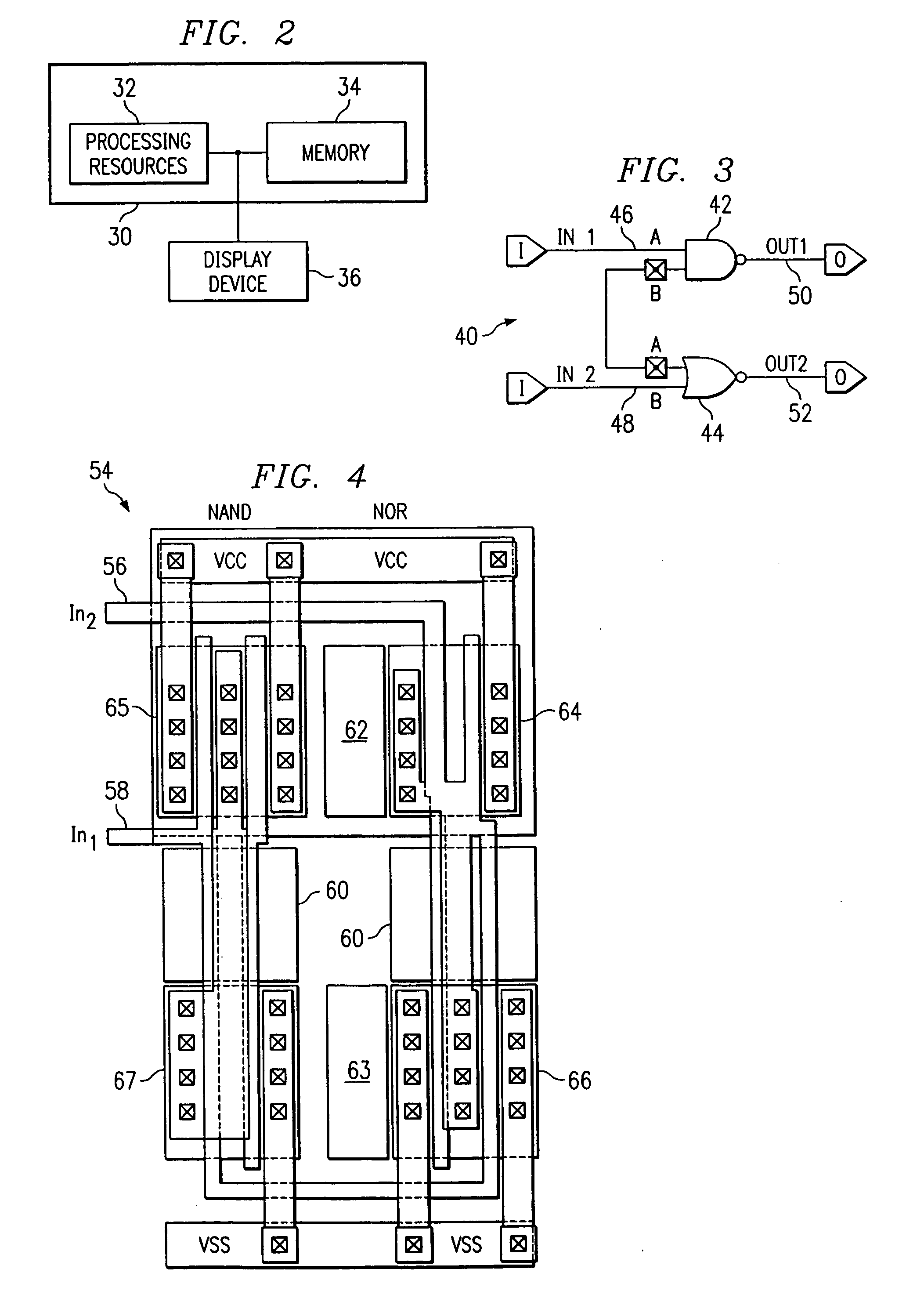

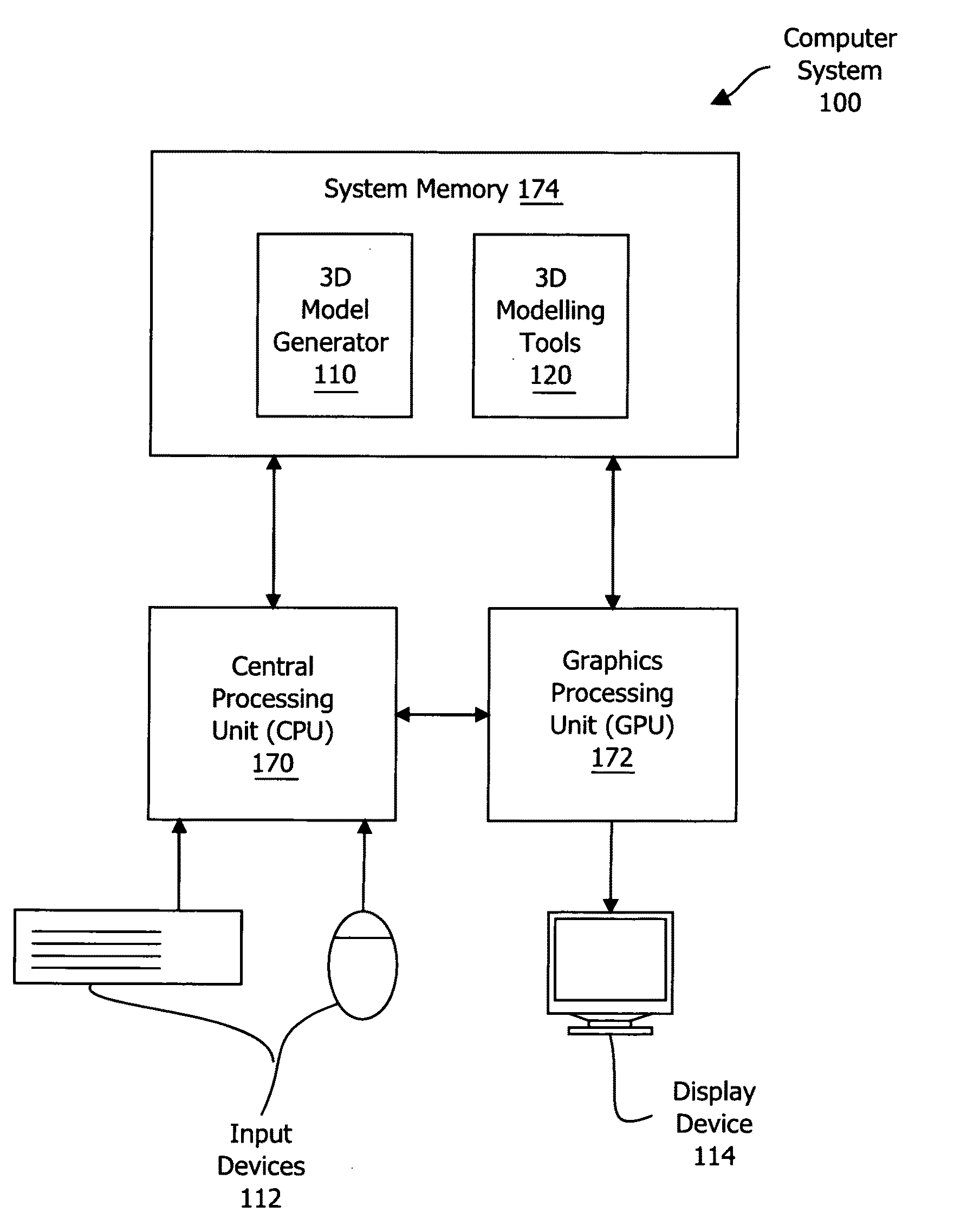

System and method for automatic elimination of voltage drop, also known as IR drop, violations of a mask layout block, maintaining the process design rules correctness

InactiveUS20080127020A1Eliminate pressure dropShorten design timeComputer programmed simultaneously with data introductionCAD circuit designEngineeringPosition dependent

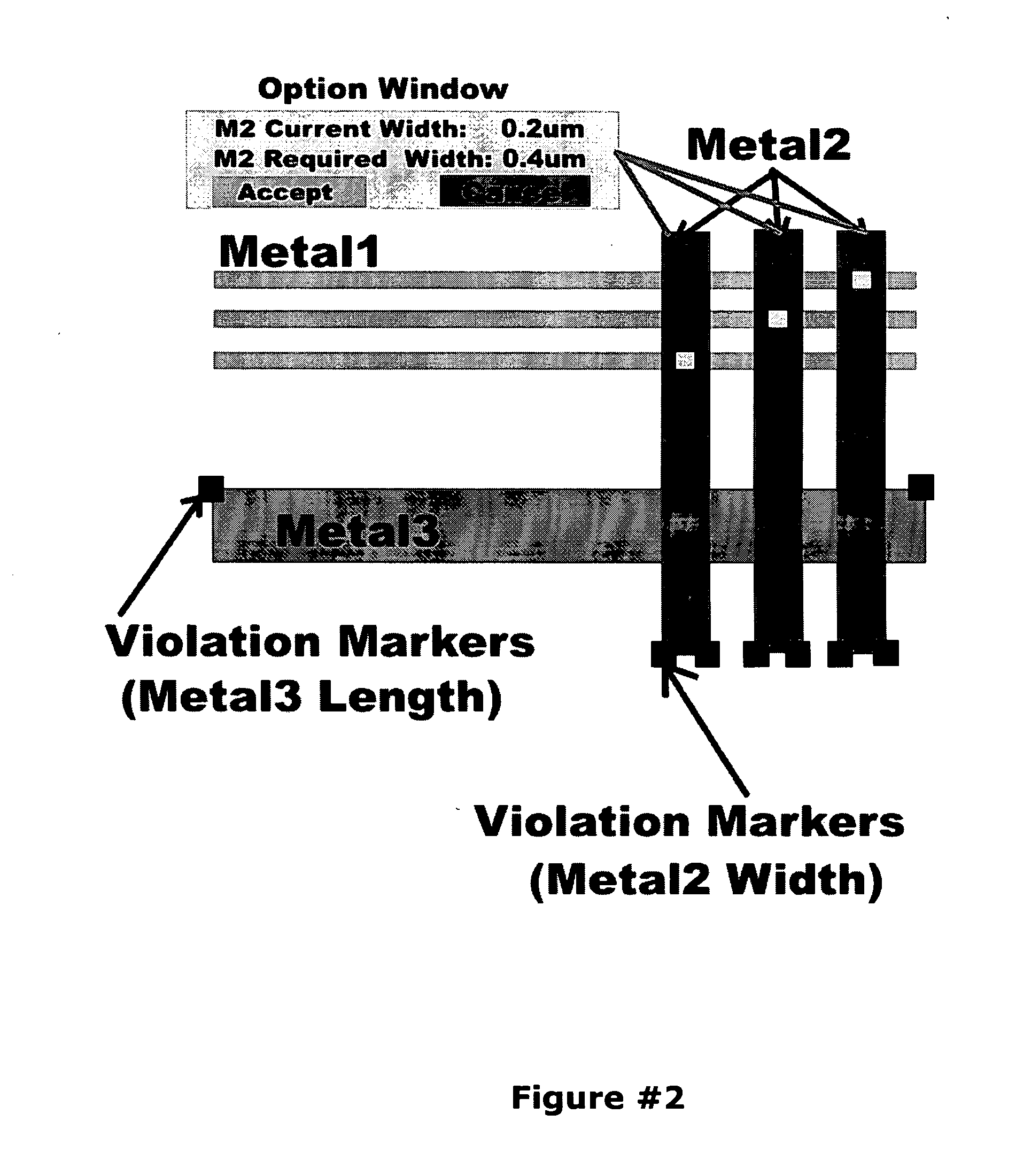

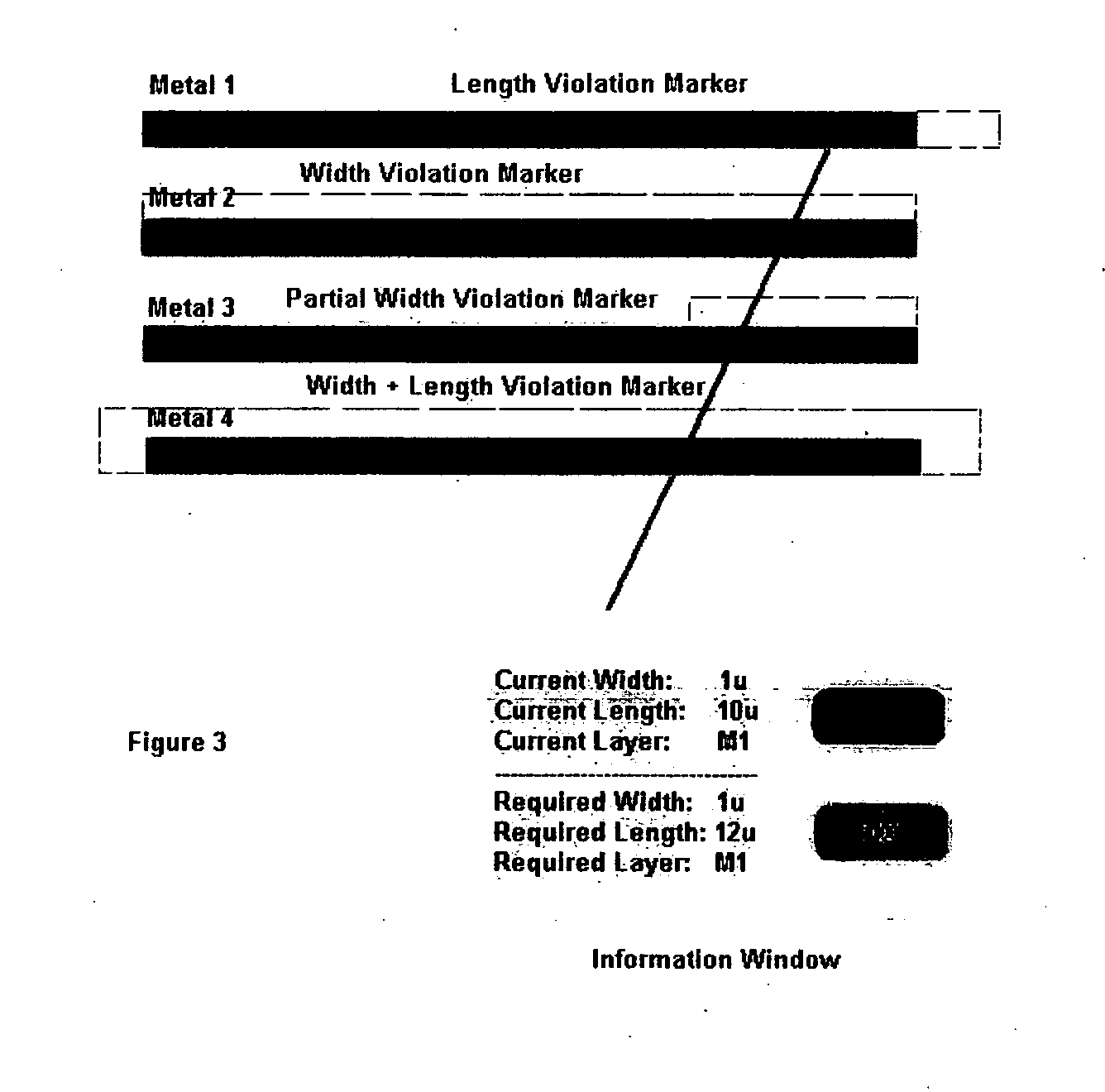

A system and method for automatic correction of voltage drop, also known as IR Drop violations of a mask layout block, maintaining the process design rules (DRC Clean) and layout connectivity (LVS Clean) correctness, are disclosed. The method includes analyzing polygons or signals for voltage drop violations, in a mask layout block and obtaining one or more voltage drop restriction information associated with polygons or signals from a technology and an external constraints file. The system automatically corrects all voltage drop violations if found, changing polygons space, width and length, maintaining the process design rules (DRC Clean) and layout connectivity (LVS Clean) correctness. The method also includes analysis and automatic correction of contacts and VIA's according to amount and location in order to comply with voltage drop requirements as taken from technology or external constraints file. The method provides a violation marker associated with position of polygons or signals that graphically represents a width, space, length violation. The method and system works on GDSII format files and on industry standards layout editor's database.

Owner:MICROLOGIC DESIGN AUTOMATION

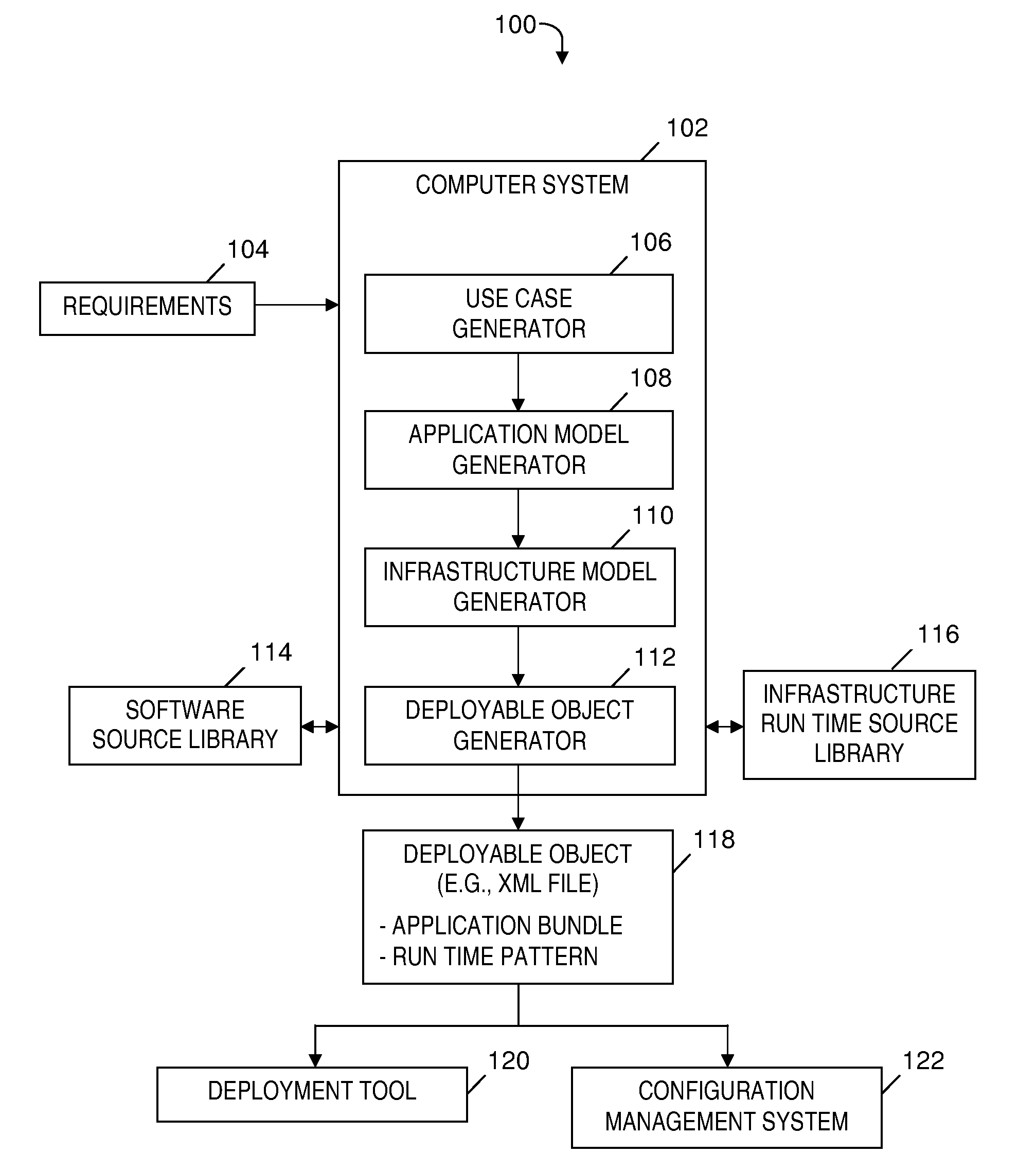

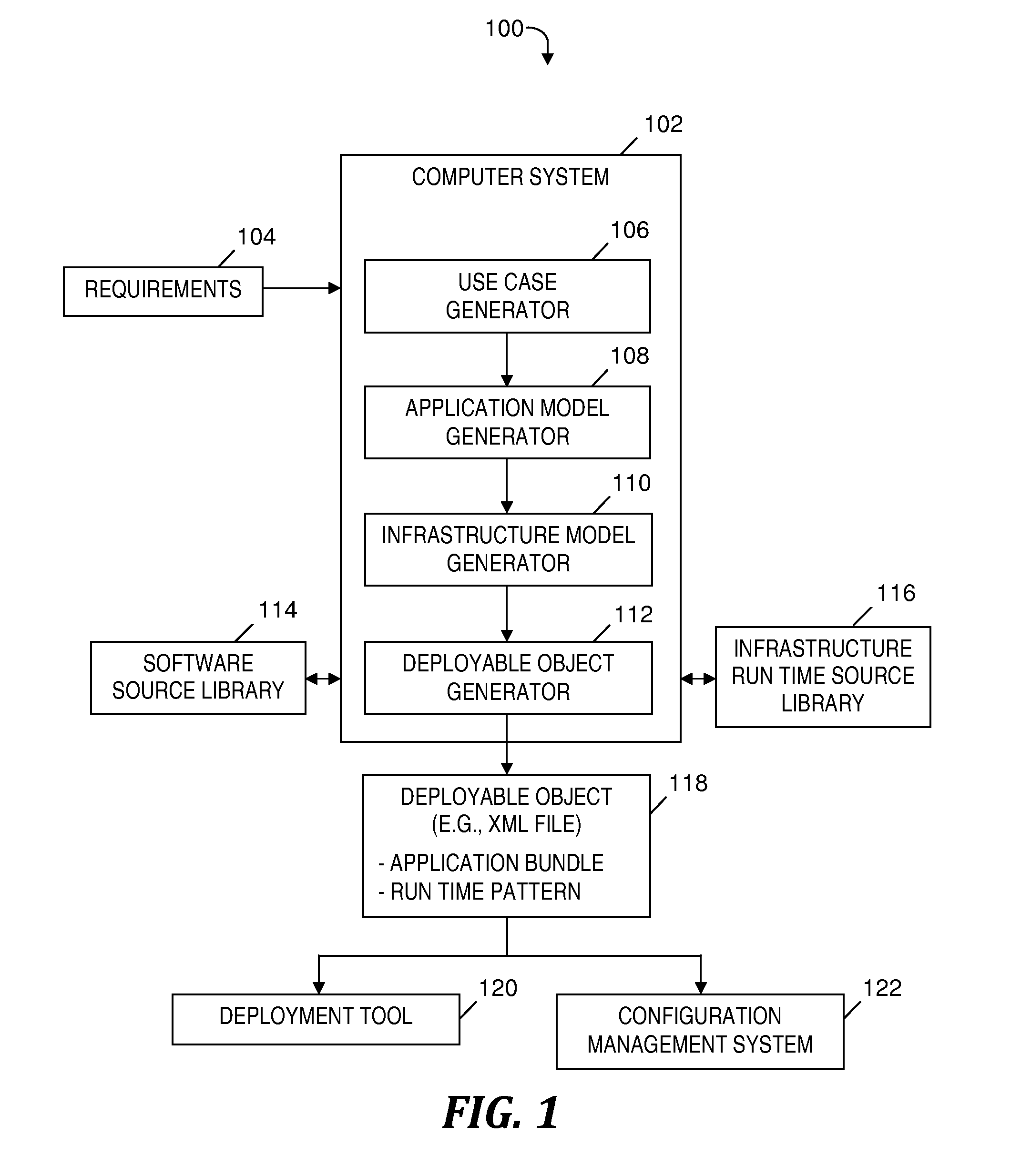

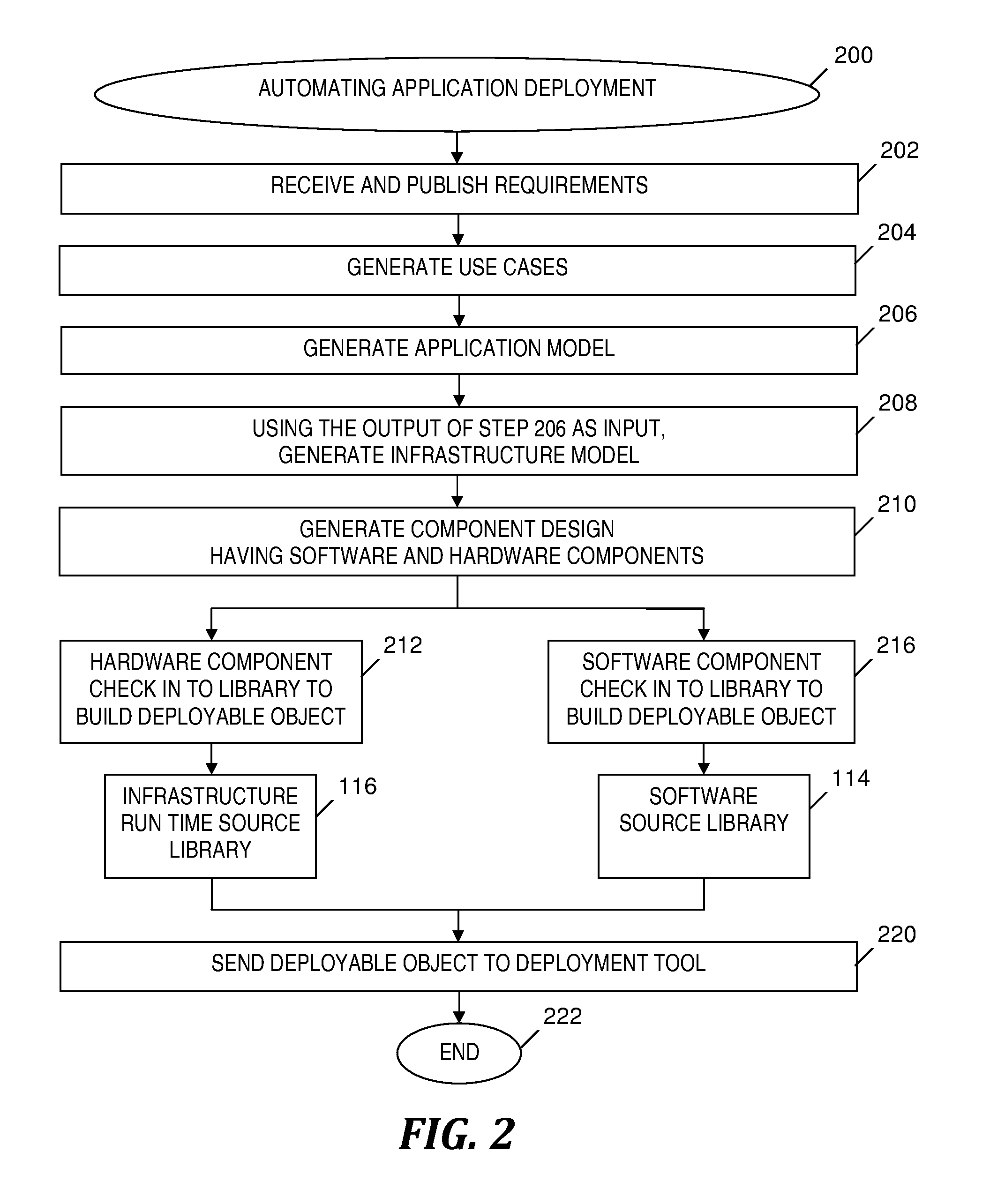

End to end automation of application deployment

InactiveUS20120079450A1Reduce timeReduce design timeDigital data information retrievalProgram loading/initiatingInformation technologyNon functional

Automatic deployment of an information technology (TT) system instance having hardware and software components. An application model of the software components is generated based on use cases and is associated with functional and non-functional requirements. An infrastructure model of the hardware components is generated based on the application model. The same software component modeling language represents both the application and infrastructure models. A markup language computer file is generated to include a design of the IT system instance and instructions for accessing library-stored assets that specify the hardware and software components. The computer file is exported to a deployment tool for automatic deployment of the IT system instance based on carrying out the instructions. In one embodiment, the impact of a proposed change is identified and managed in real time prior to a deployment of the proposed change.

Owner:IBM CORP

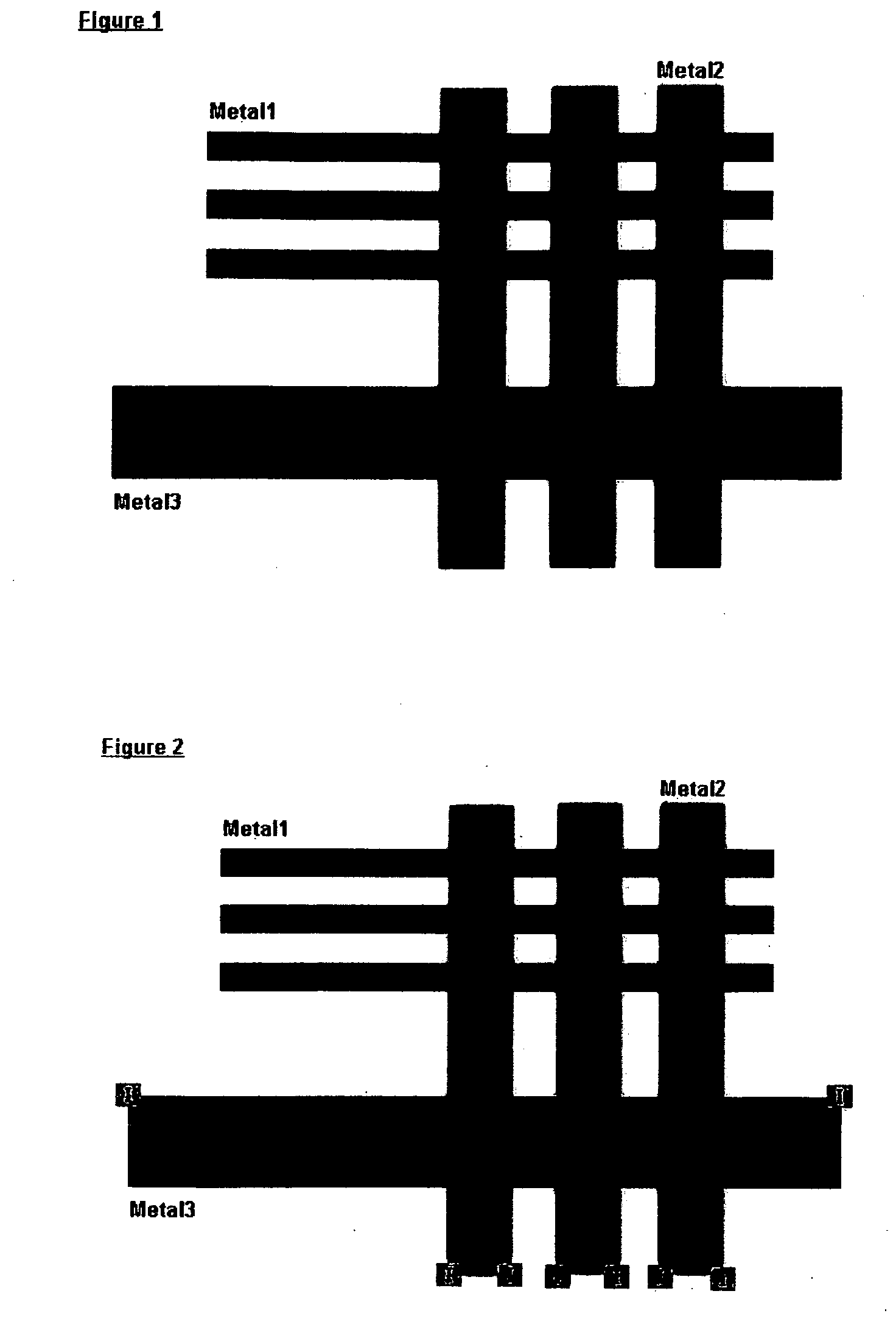

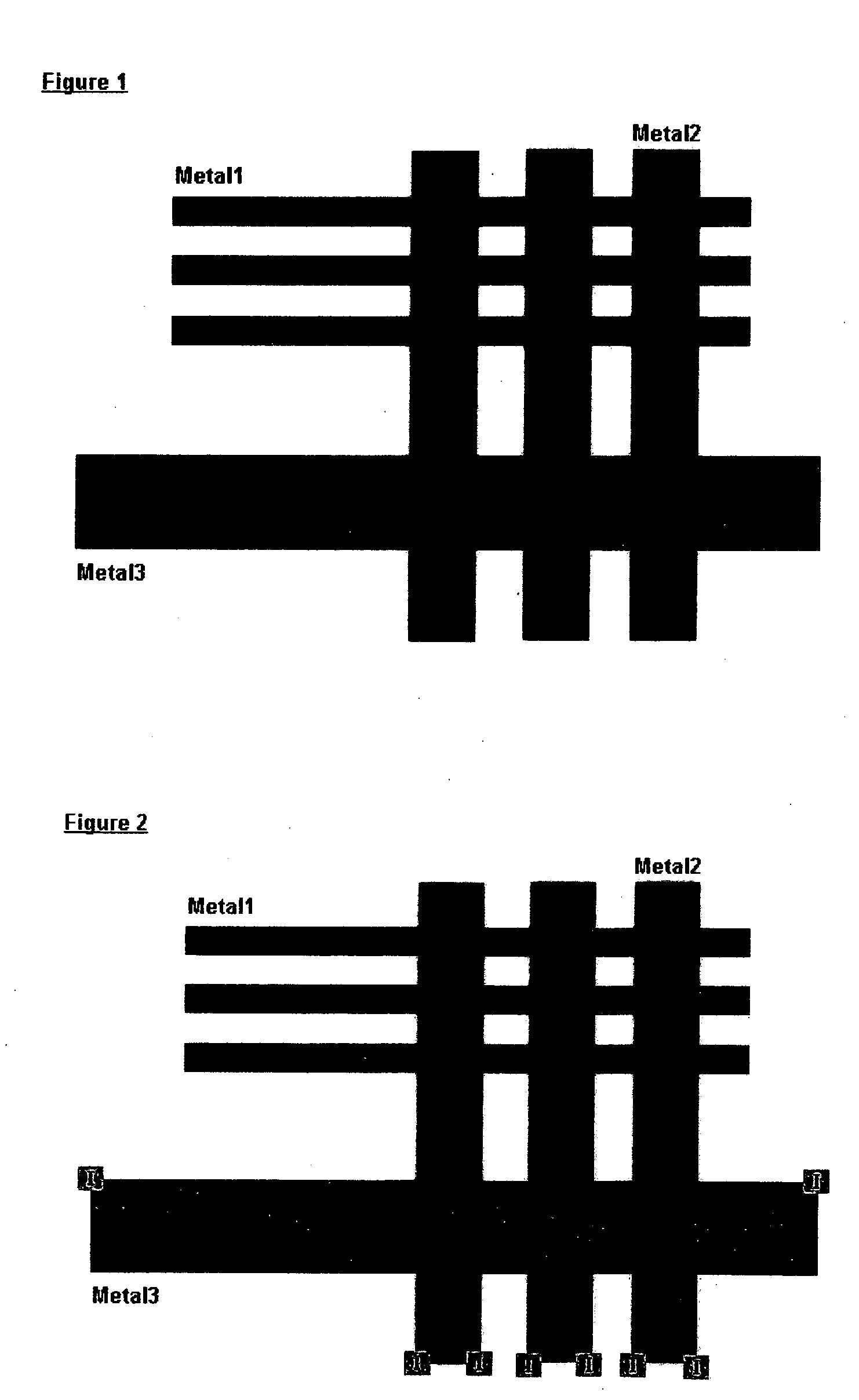

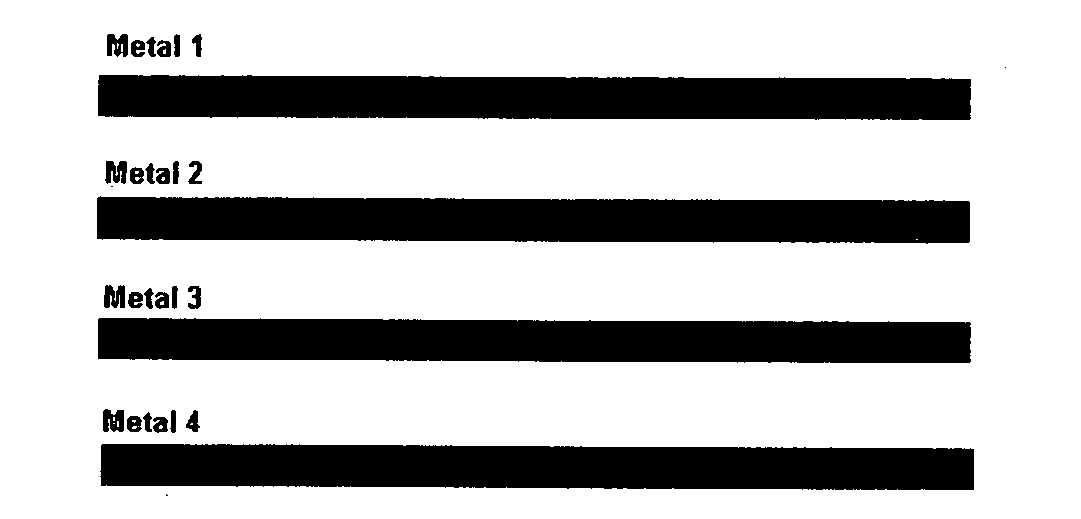

System and method for automatic elimination of electromigration and self heat violations of a mask layout block, maintaining the process design rules correctness

InactiveUS20080086708A1Shorten design timeComputer aided designSpecial data processing applicationsGraphicsPosition dependent

A system and method for automatic correction of electromigration (EM) and self heat (SH) violations of a mask layout block, maintaining the process design rules correctness are disclosed. The method includes analyzing polygons for space, width and length, in a mask layout block and obtaining one or more electromigration and / or self heat rules associated with the polygon from a technology and an external constraints file. The system automatically corrects all EM and / or SH violations if found, maintaining the process design rules correctness. The method also includes analysis and automatic correction of contacts and VIA's according to amount and location in order to comply with electromigration and self heat rules as taken from technology or external constraints file. The method provides a violation marker associated with the selected position for the polygon that graphically represents a width, space, length violation. The method and system works on GDSII format files and on industry standards layout editor's database.

Owner:MICROLOGIC DESIGN AUTOMATION

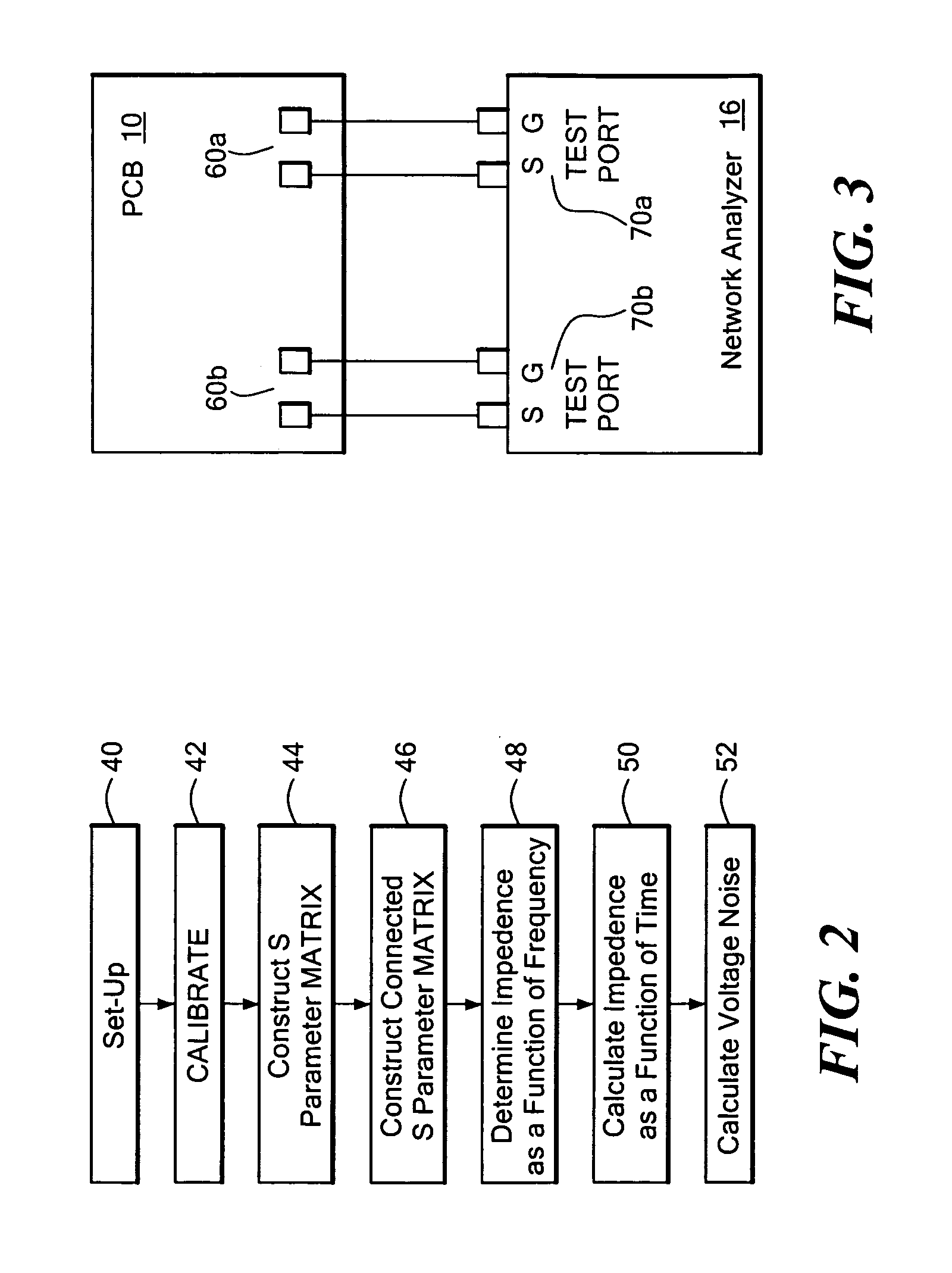

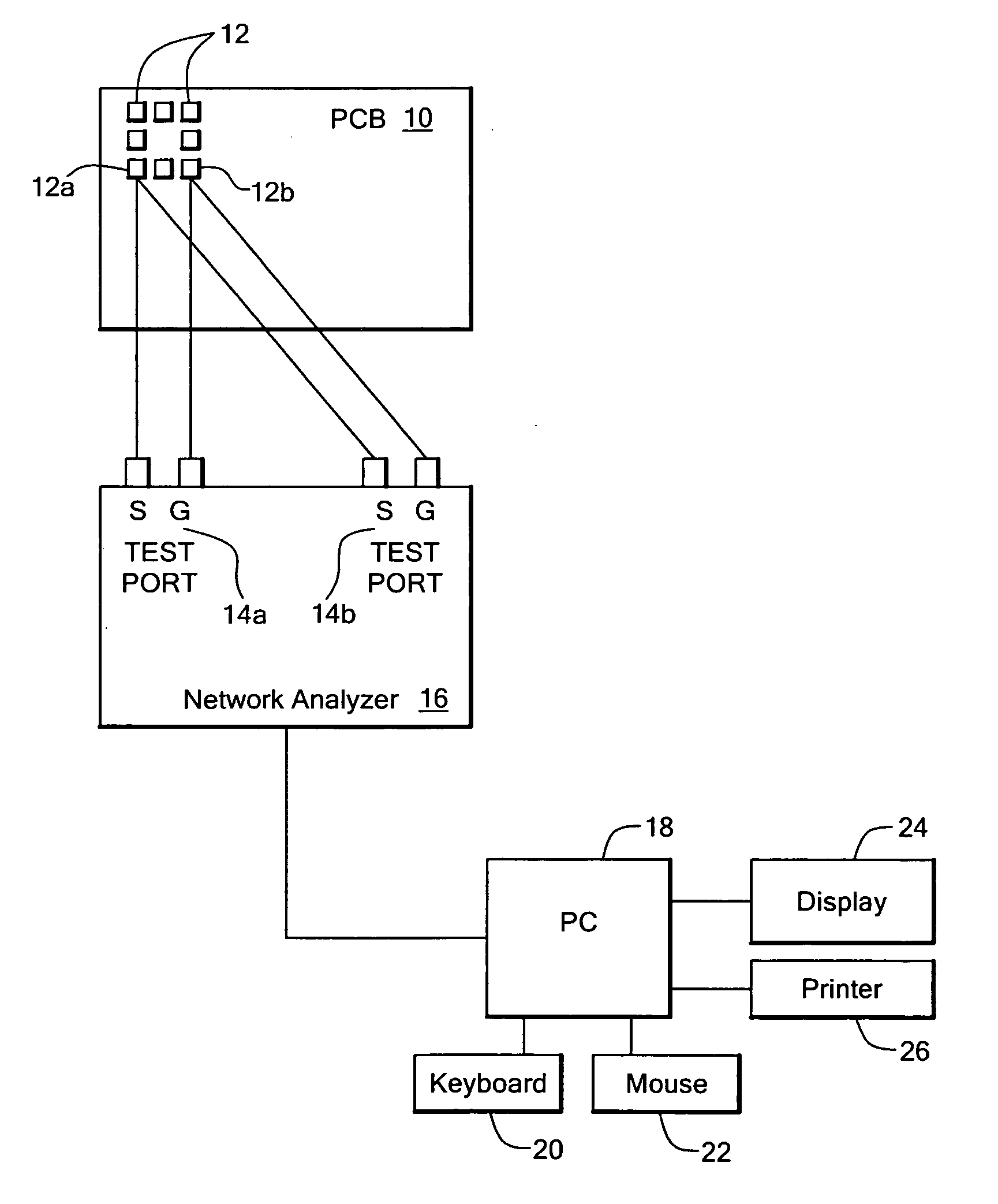

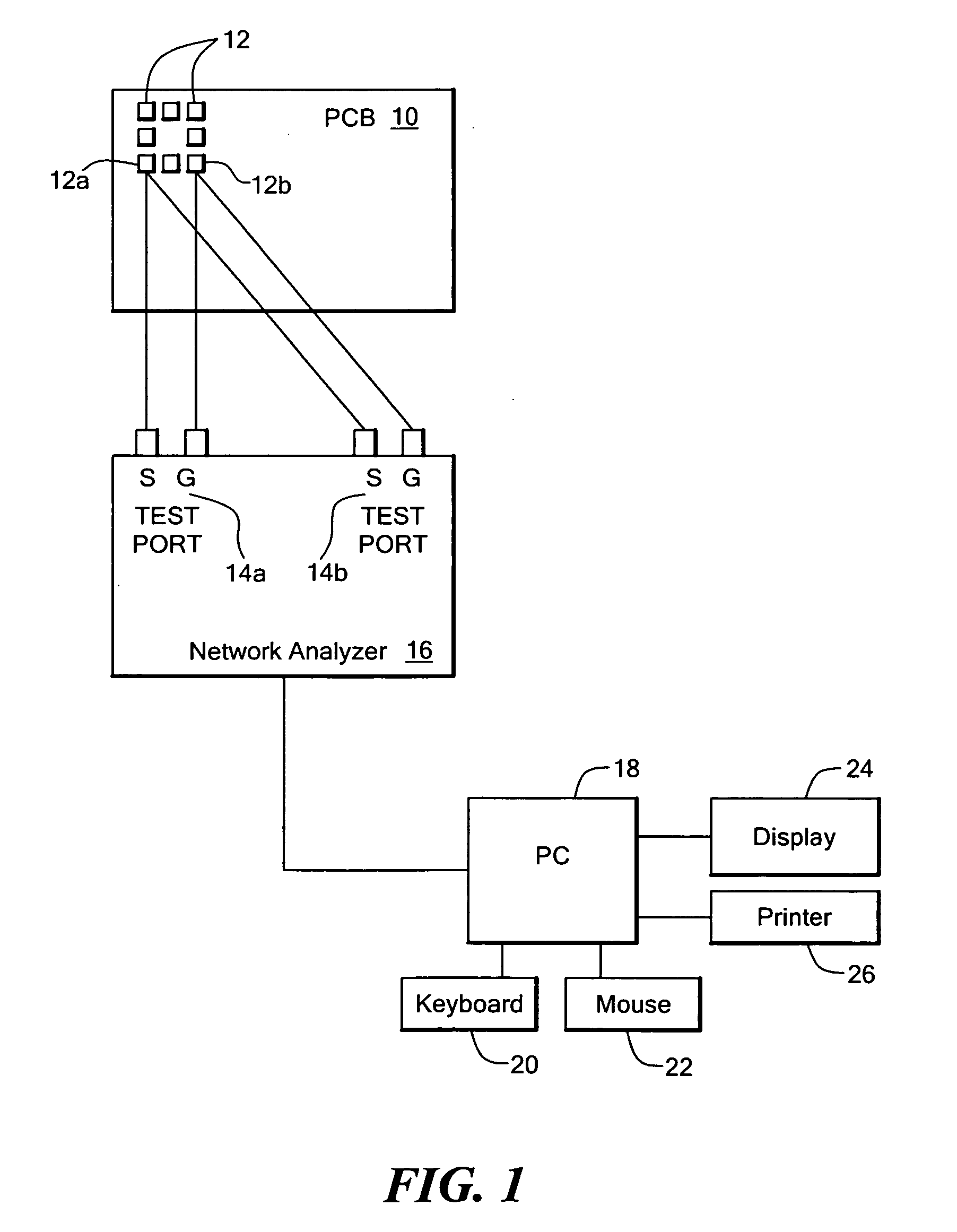

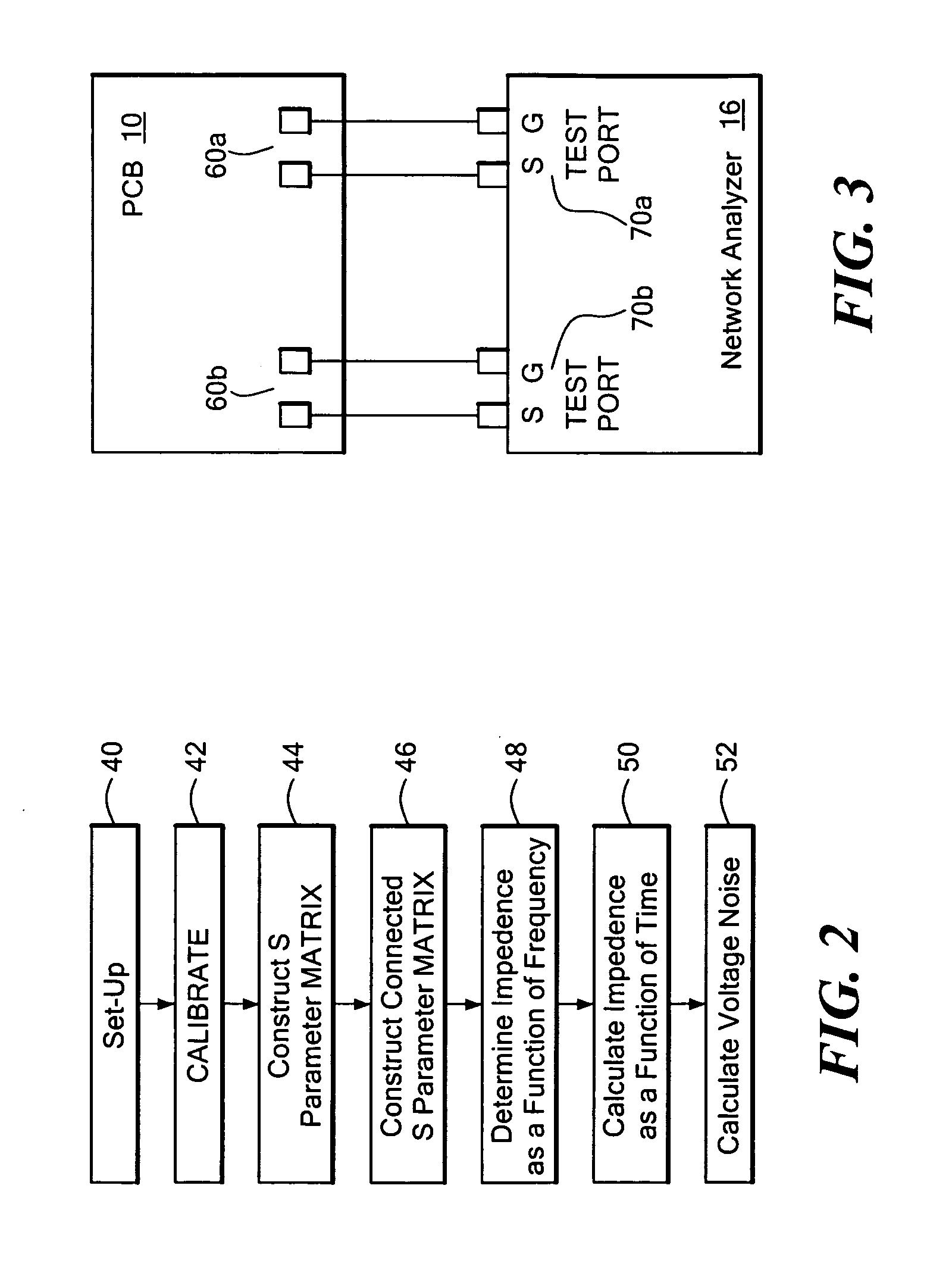

Method and system of characterizing a device under test

A system and method of characterizing a device under test wherein a signal is injected into the device under test, the response to the injected signal is measured to determine the impedance of the device under test in the frequency domain, the impedance is converted to the time domain, and the voltage noise of the device under test is calculated based on the impedance of the device under test in the time domain.

Owner:COLE J BRADFORD

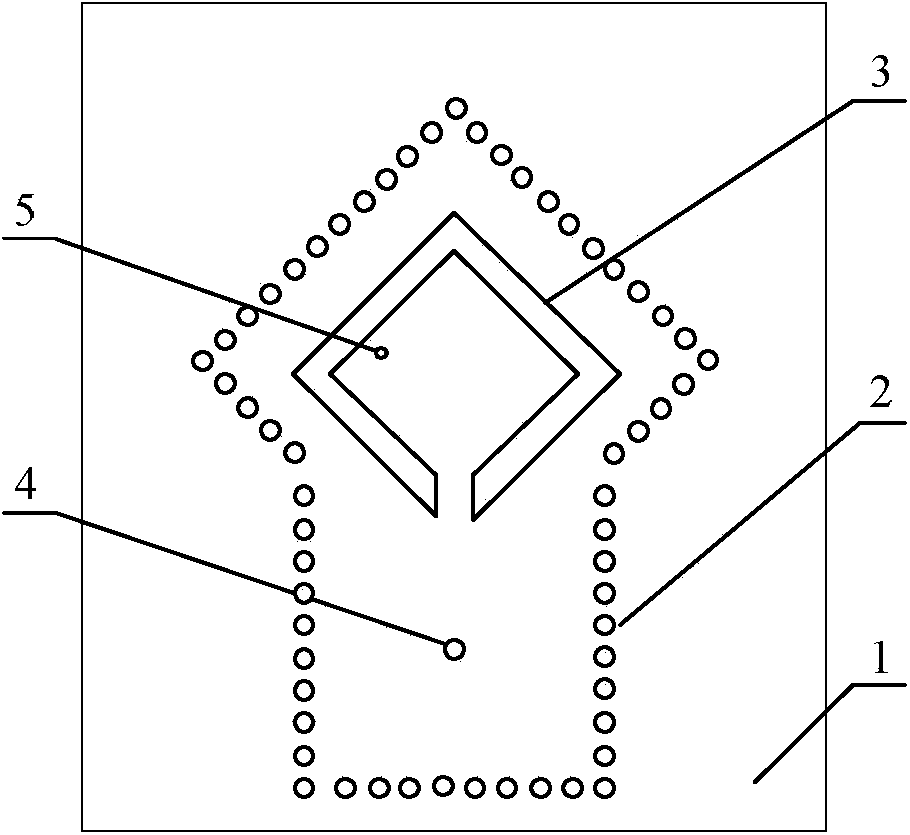

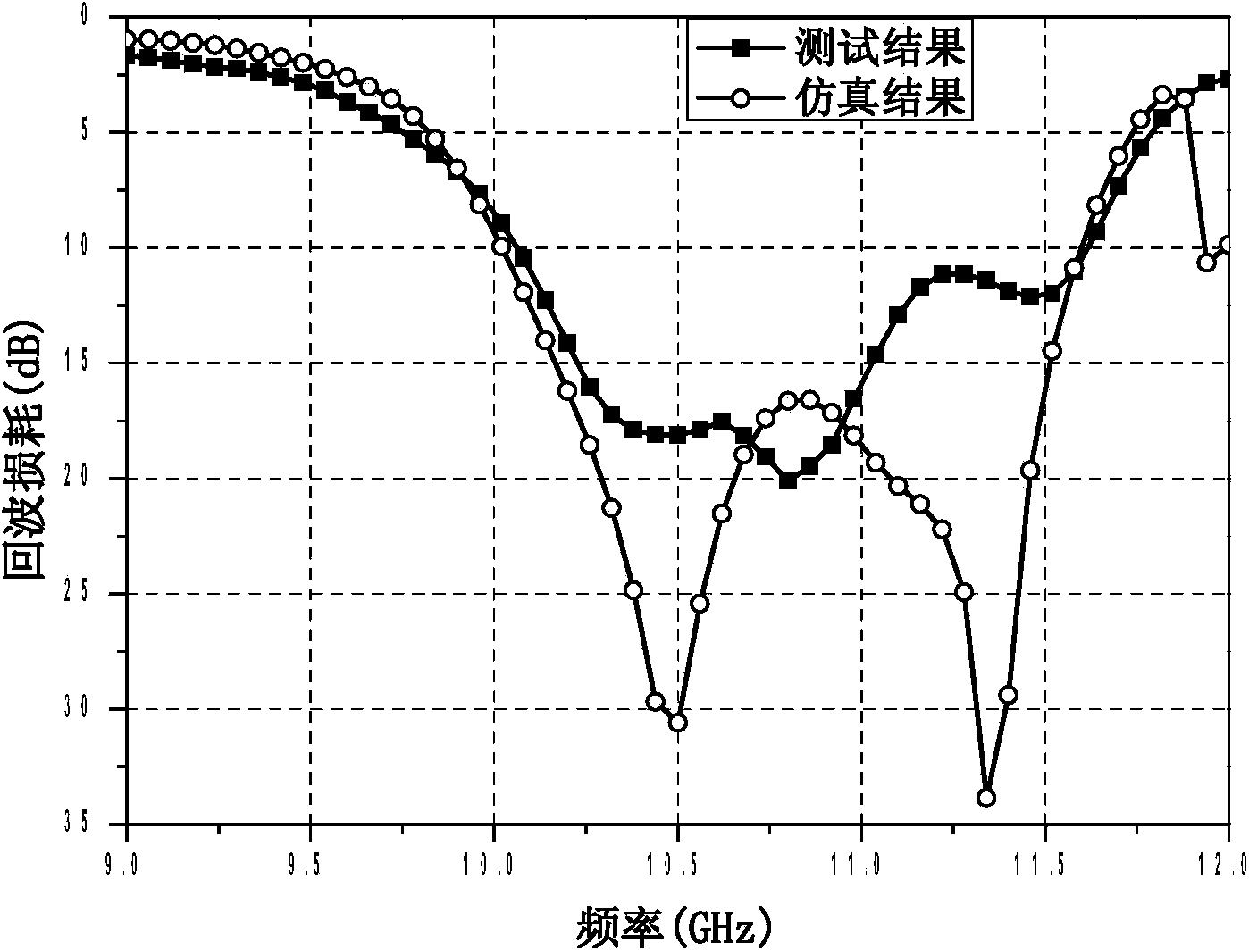

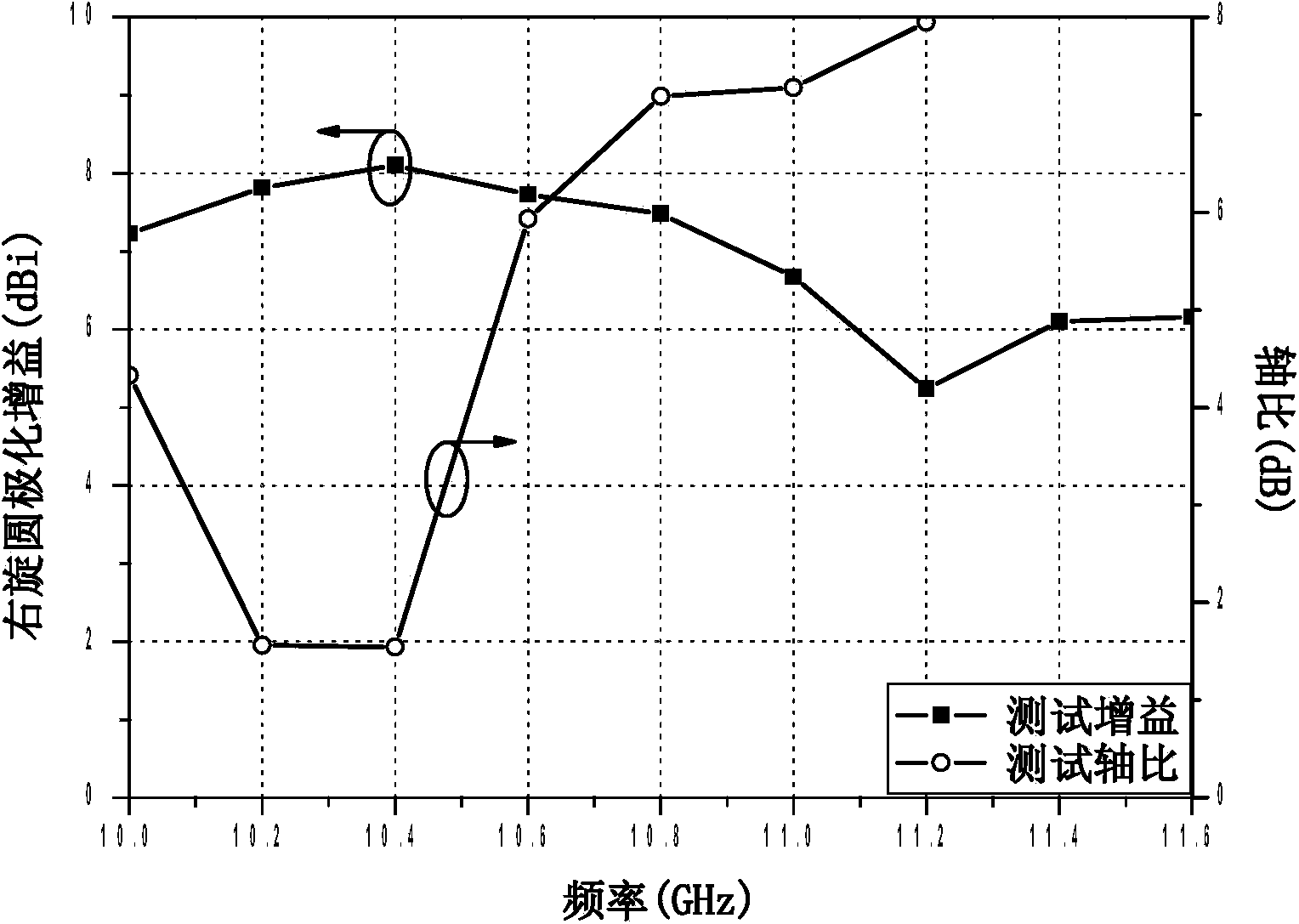

Broadband substrate integrated waveguide circularly polarized antenna array and manufacturing method thereof

InactiveCN103531918ASimple structureSimple working principleAntenna arraysRadiating elements structural formsCircularly polarized antennaBroadband

The invention discloses a substrate integrated waveguide technology-based high-gain circularly polarized antenna array and a manufacturing method of the antenna array. The broadband substrate integrated waveguide circularly polarized antenna array comprises an upper-layer radiation substrate and a lower-layer feed substrate, wherein the radiation substrate comprises a first antenna unit, a second antenna unit, a third antenna unit and a fourth antenna unit, and the first antenna unit, the second antenna unit, the third antenna unit and the fourth antenna unit are symmetrically arranged by taking the center of a circle as an axis; a radial substrate integrated waveguide power distributor which is divided into four parts is distributed on the feed substrate and is used for feeding the four antenna units. The high-gain circularly polarized antenna array disclosed by the invention has the advantages that the gain is high, the broadband is wide, the radiation characteristic is good, the design is simple, the machining is easy and the cost is low; compared with the current substrate integrated waveguide circularly polarized antenna, the antenna provided by the invention has the advantages that the gain is remarkably improved and the circularly polarized bandwidth is remarkably increased.

Owner:XIDIAN UNIV

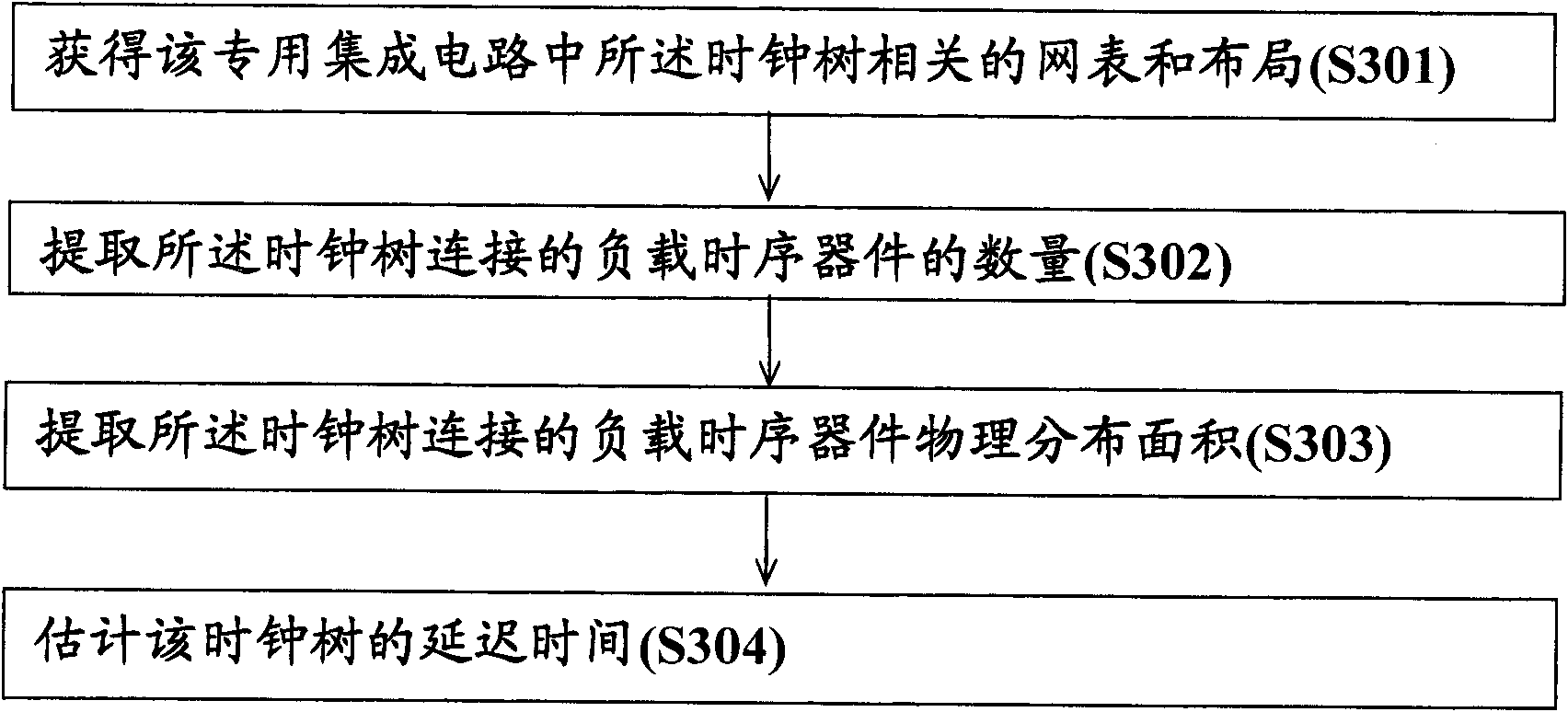

Estimation method and system of clock tree delay time in specified integrated circuit

ActiveCN102169515AShorten design timeImprove design efficiencyComputer aided designSpecial data processing applicationsLoad timeEstimation methods

The invention discloses an estimation method and system of clock tree delay time in a specified integrated circuit, wherein the method comprises the following steps of: obtaining a netlist and a layout relative to the clock tree in the specified integrated circuit; extracting the number of load time sequence apparatuses connected with the clock tree according to the netlist relative to the clock tree; extracting a physical distribution region area of the load time sequence apparatuses connected with the clock tree according to the layout relative to the clock tree; estimating the delay time of the clock tree according to the relation among the number of the load time sequence apparatuses, the physical distribution region area of the load time sequence apparatuses and the clock tree delay time in the historical data of the same process with the specified integrated circuit. An audit flow is reduced to days from weeks by using the improved specified integrated circuit design method, a designer can rapidly find and solve the problem; and therefore, the design time is reduced, and the design efficiency is improved.

Owner:GLOBALFOUNDRIES INC

System and method for automatic elimination of electromigration and self heat violations during construction of a mask layout block, maintaining the process design rules (DRC Clean) and layout connectivity (LVS Clean) correctness

InactiveUS20080086709A1Prevent electromigrationEliminate electromigrationComputer aided designSpecial data processing applicationsGraphicsPosition dependent

A system and method for automatic elimination of electromigration (EM) and self heat (SH) violations during construction of a mask layout block, maintaining the process design rules (DRC Clean) and layout connectivity (LVS Clean) correctness, are disclosed. The method includes analyzing a selected polygon for space, width and length, in a mask layout block and obtaining one or more electromigration and / or self heat rules associated with the polygon from a technology and an external constraints file. The method also includes analyzing contacts and VIA's for amount and location in order to comply with electromigration and self heat rules. The method provides a violation marker associated with the selected position for the polygon that graphically represents a width, space, length and other polygon's physical characteristics within the mask layout block where the selected polygon complies with the electromigration and / or self heat violation. The method and system also provides an option to automatically correct the electromigration (EM) and self heat violation of the mask layout block, maintaining the process design rules (DRC Clean) and layout connectivity (LVS Clean) correctness.

Owner:MICROLOGIC DESIGN AUTOMATION

Automated approach to constraint generation in IC design

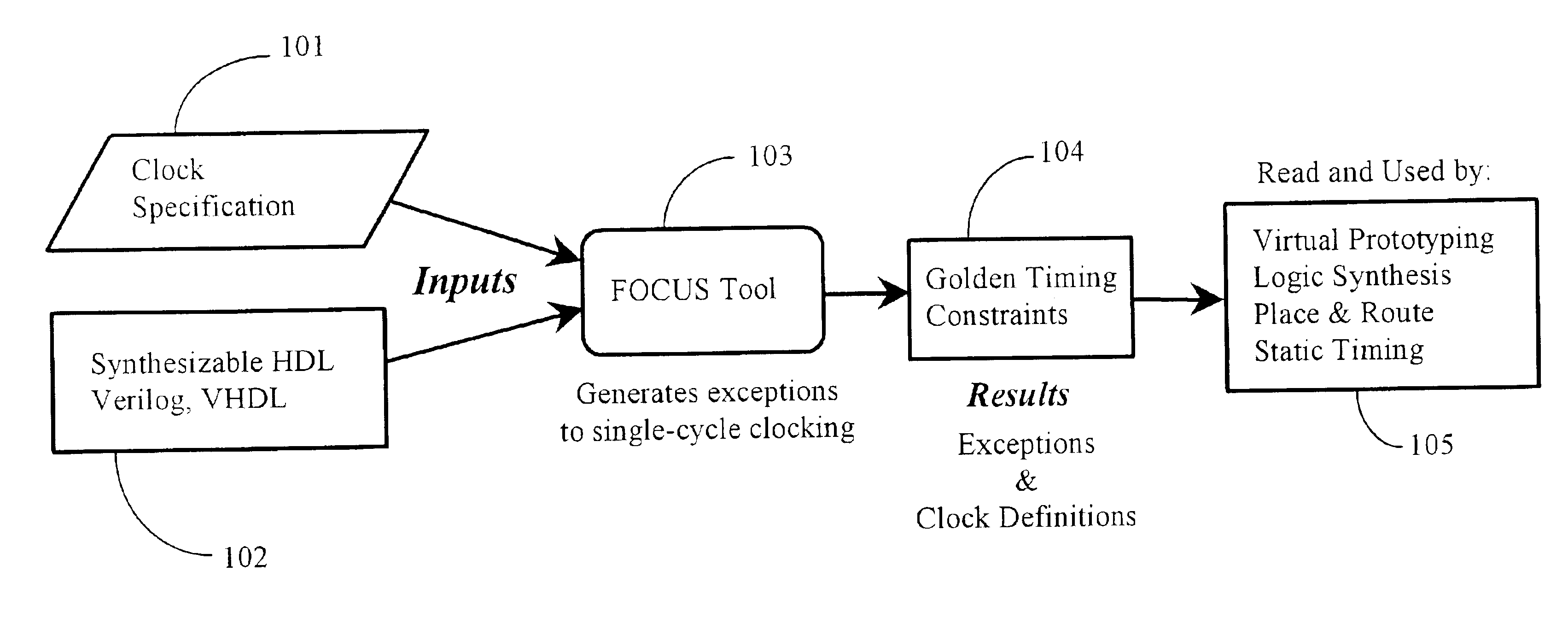

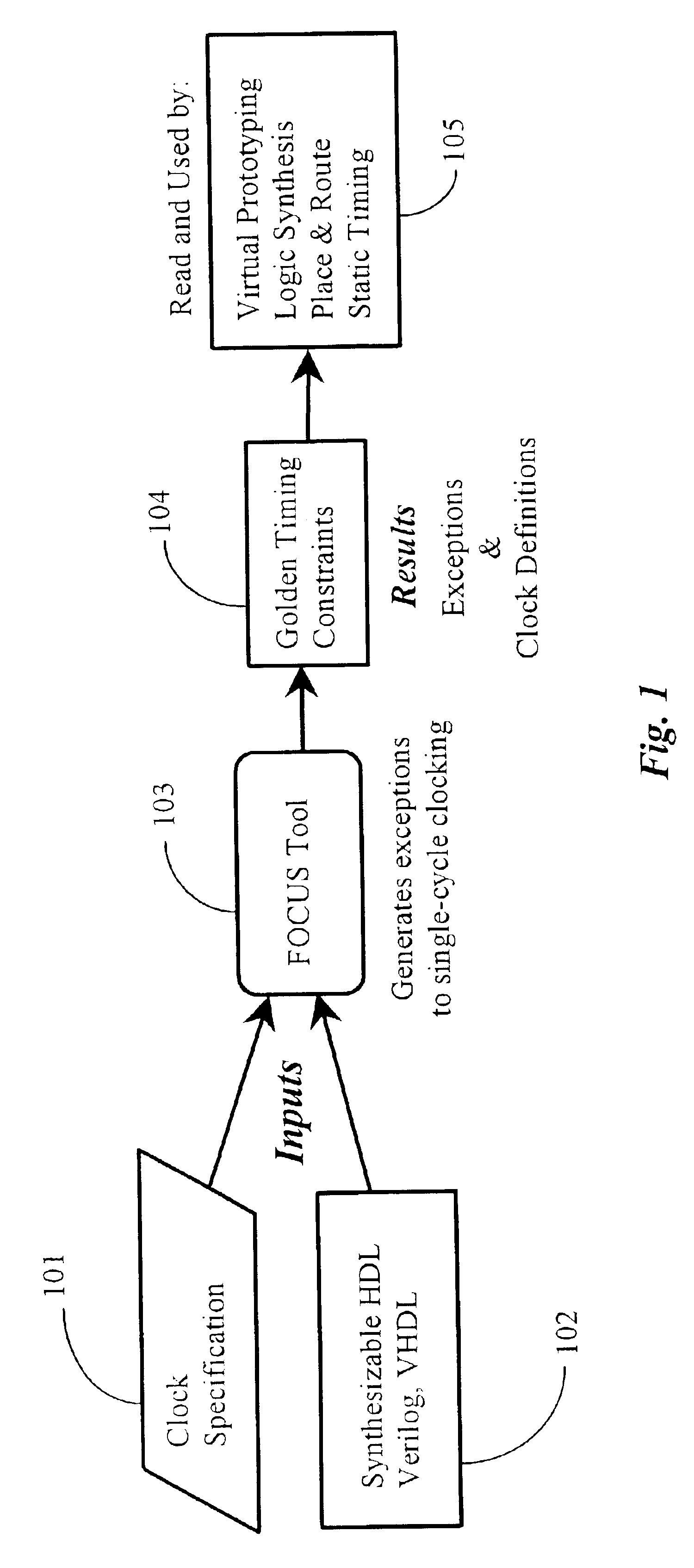

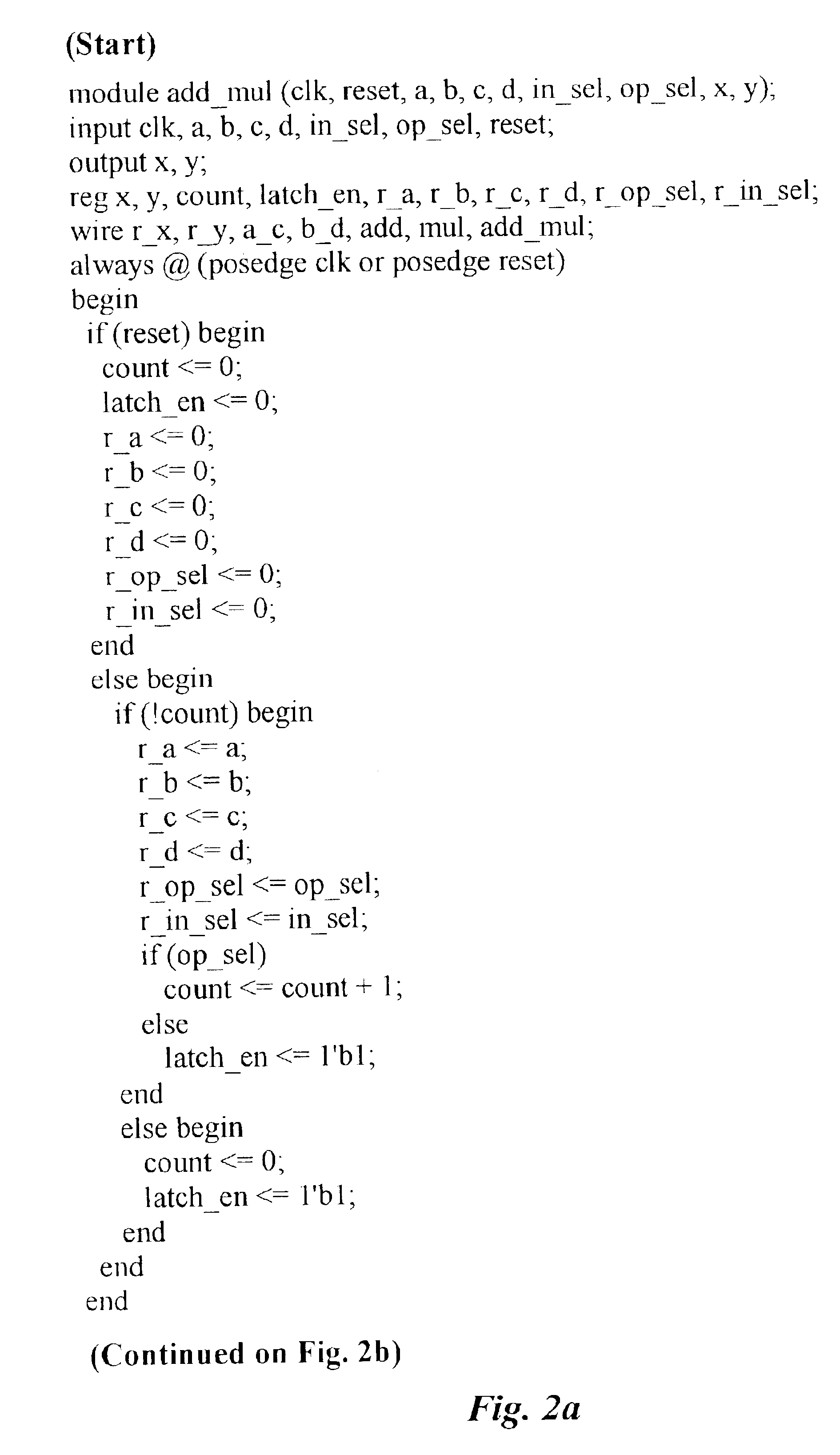

InactiveUS6877139B2Reduce riskRealisticConstraint-based CADCAD circuit designComputer architectureAutomated method

A software-based system for generating timing constraints for a proposed IC design has a first input as a synthesizable description of the proposed IC, a second input as a clock specification for the proposed IC, and a processing unit accepting the first and second inputs, and determining therefrom as an output, a set of timing constraints to guide implementation of the proposed IC design.

Owner:FISHTAIL DESIGN AUTOMATION

Photomask and integrated circuit manufactured by automatically eliminating design rule violations during construction of a mask layout block

InactiveUS20050022151A1Avoid creatingAvoid positioningSemiconductor/solid-state device detailsSolid-state devicesEngineeringPhotomask

A photomask and integrated circuit manufactured by eliminating design rule violations during construction of a mask layout block are disclosed. A photomask includes a substrate and a patterned layer including at least one feature formed on at least a portion of the substrate. The feature is defined in a mask pattern file generated by analyzing a selected position for a polygon during construction of a mask layout block and determining if the selected position creates a design rule violation in the mask layout block based on a design rule from a technology file. The mask pattern file is further generated by automatically preventing the polygon from being placed in the mask layout block at the selected position if the design rule violation exists.

Owner:TOPPAN PHOTOMASKS INC

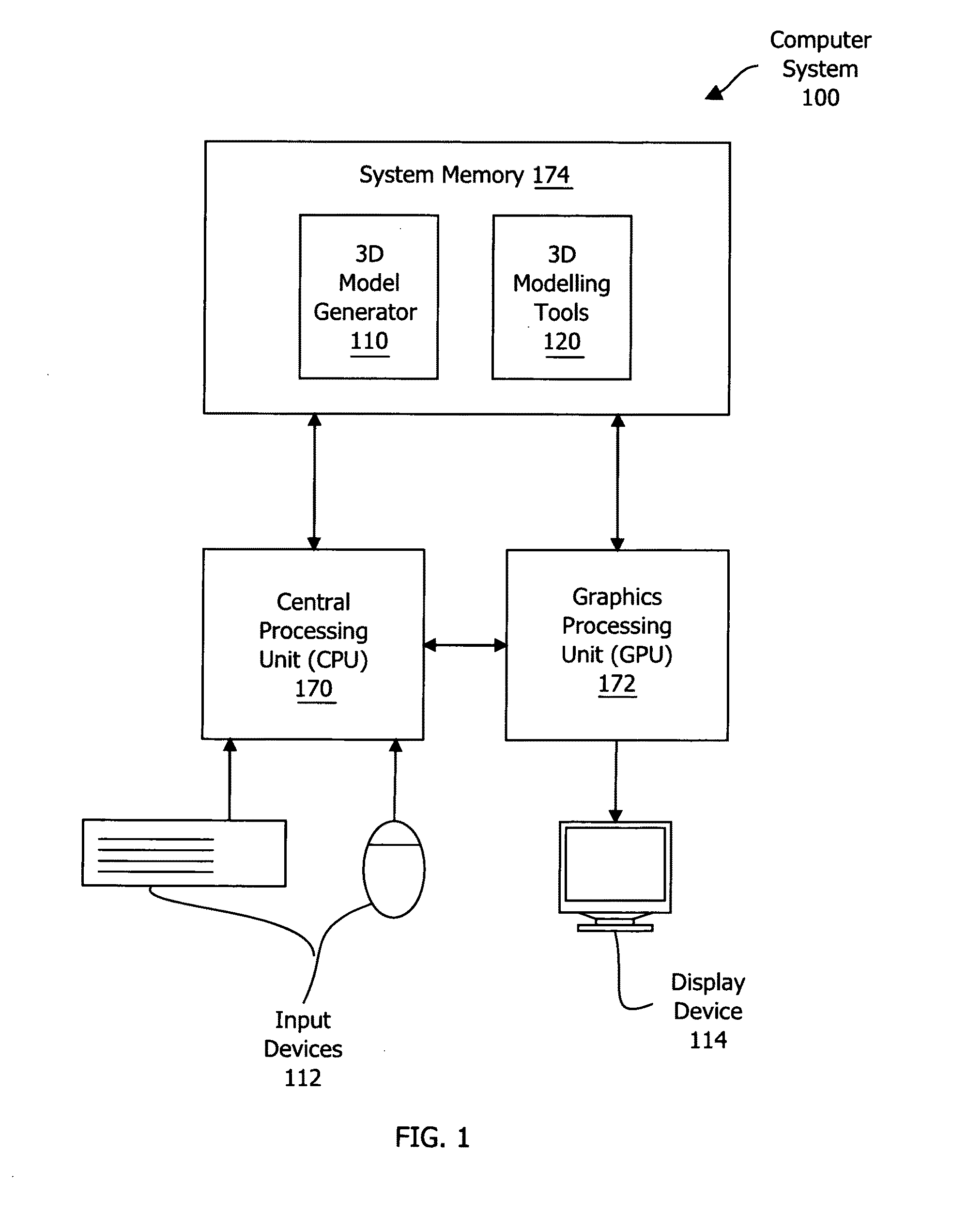

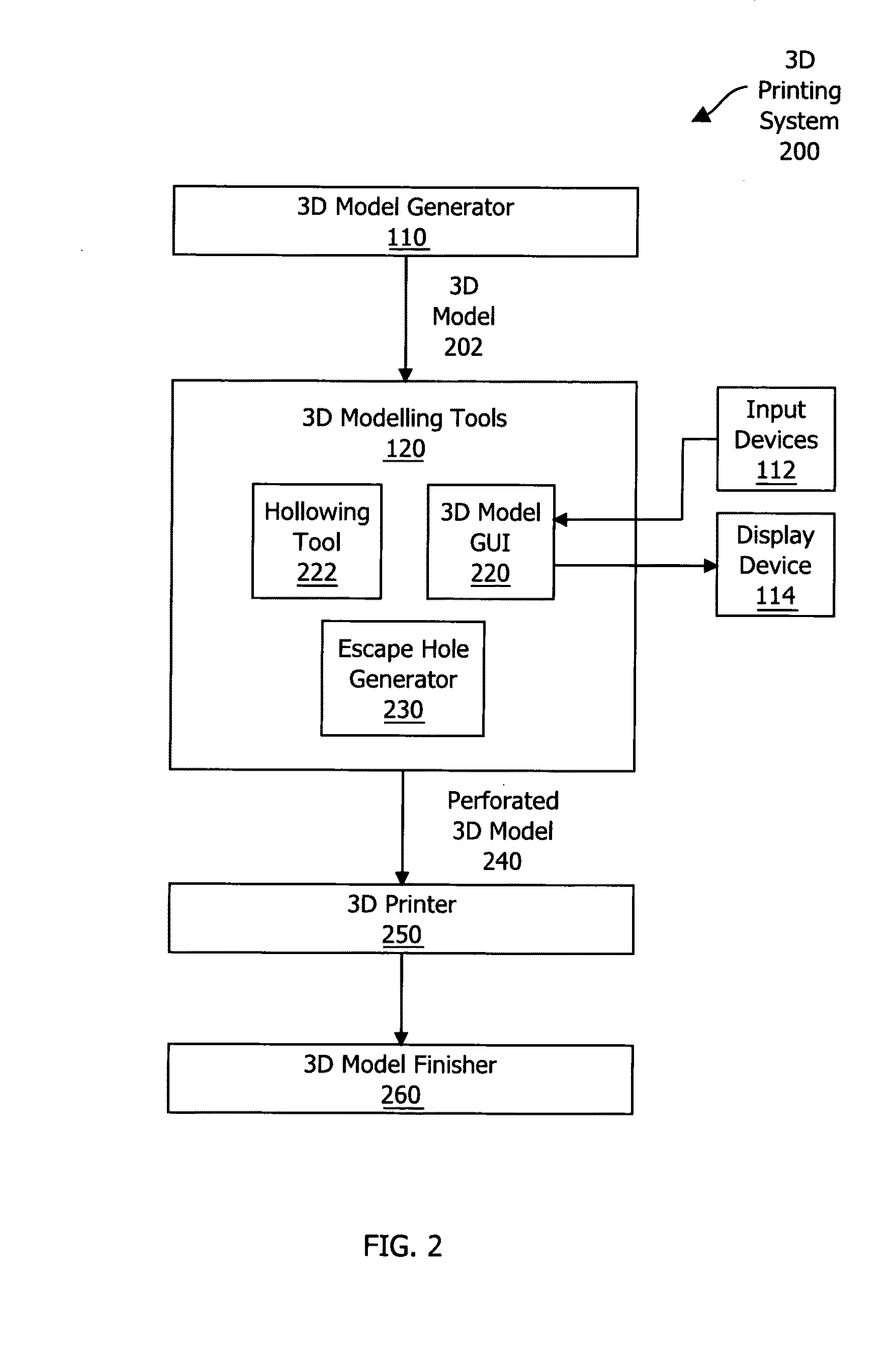

Techniques for Automatically Placing Escape Holes during Three-Dimensional Printing

ActiveUS20160136883A1Improve automationShorten design timeAdditive manufacturing apparatusAuxillary shaping apparatusHeuristicEngineering

In one embodiment of the present invention, an escape hole generator creates escapes holes designed to facilitate removal of support and / or unprinted material generated inside enclosed hollows of three-dimensional (3D) digital models during 3D printing. In operation, the escape hole generator identifies a hollow included in the three-dimensional model and then selects optimized locations for escape holes. Notably, the escape hole generator selects the locations to optimize placement heuristics, such as favoring locations closer to the bottom of the 3D model, while satisfying escape hole constraints (e.g., hole size and spacing requirements). The escape hole generator then perforates the hollow at the selected locations with geometries that provide channels from the outer surface of the hollow to the outer surface of the hollow. Advantageously, automating escape hole generation enables efficient creation of hollowed 3D models that reduce 3D printing time and material usage compared to solid 3D model counterparts.

Owner:AUTODESK INC

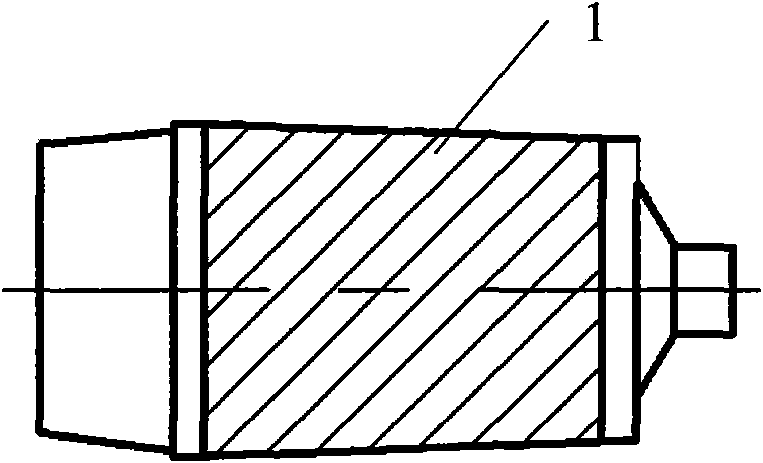

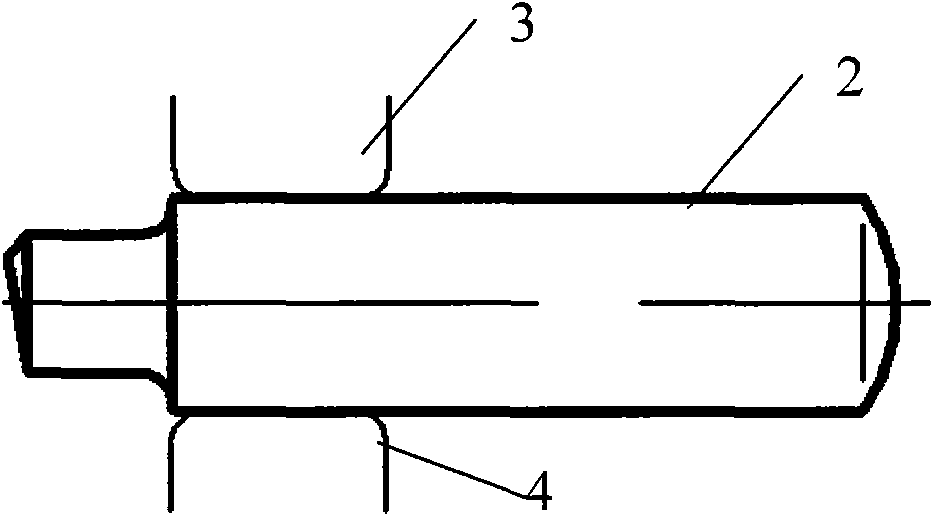

Process and device for forming straight-edge conical cylinder forged piece of nuclear power evaporator

ActiveCN101564750ASmall machining allowanceControl taperMetal-working apparatusNuclear powerEngineering

The invention belongs to the field of forging, and particularly relates to a process and a device for forming a straight-edge conical cylinder forged piece of a nuclear power evaporator, which are applicable to the nuclear power and the process design and manufacturing process for the straight-edge conical cylinder forged piece of a hydrogenation reactor. The forming process comprises the following steps: (1) primary forming of a blank; (2) forming of a conical cylinder structure and a thin-wall conical cylinder structure with equal wall thickness; and (3) forming of the straight-edge conical cylinder forged piece of the nuclear power evaporator. The forming device is provided with a trestle, a saddle and a correcting twist block, wherein the saddle is placed on the trestle; the saddle is matched with an upper flat anvil outside the forged piece blank; and the correcting twist block is matched with the saddle. The operation of the process is simple and convenient, the structure of the device is simple, and the problem that the straight-edge conical cylinder forged piece is difficult to form and the like is solved. The straight-edge conical cylinder forged piece forged by the process has even processing allowance, and the size of each part can meet the requirement of components.

Owner:CHINA ERZHONG GRP DEYANG HEAVY IND +1

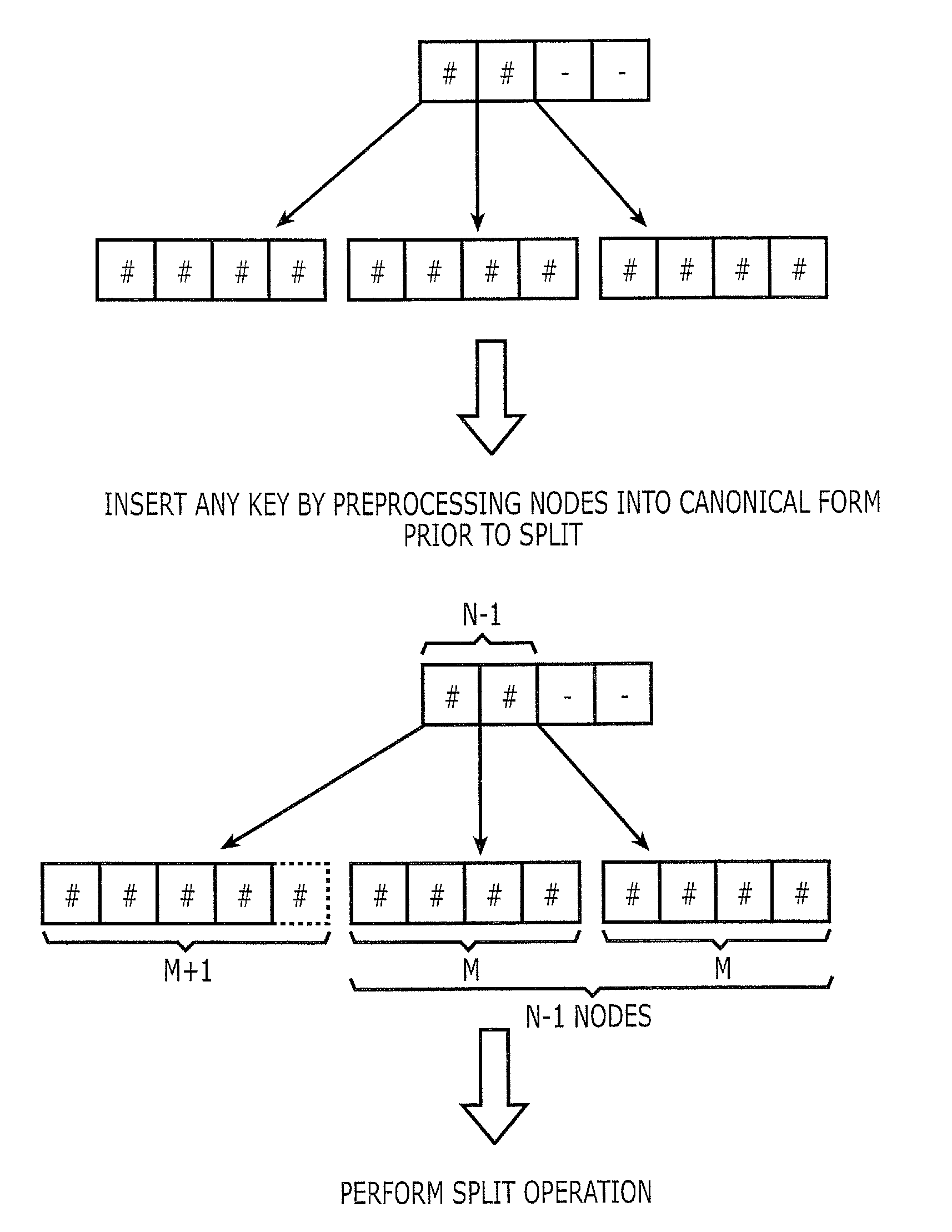

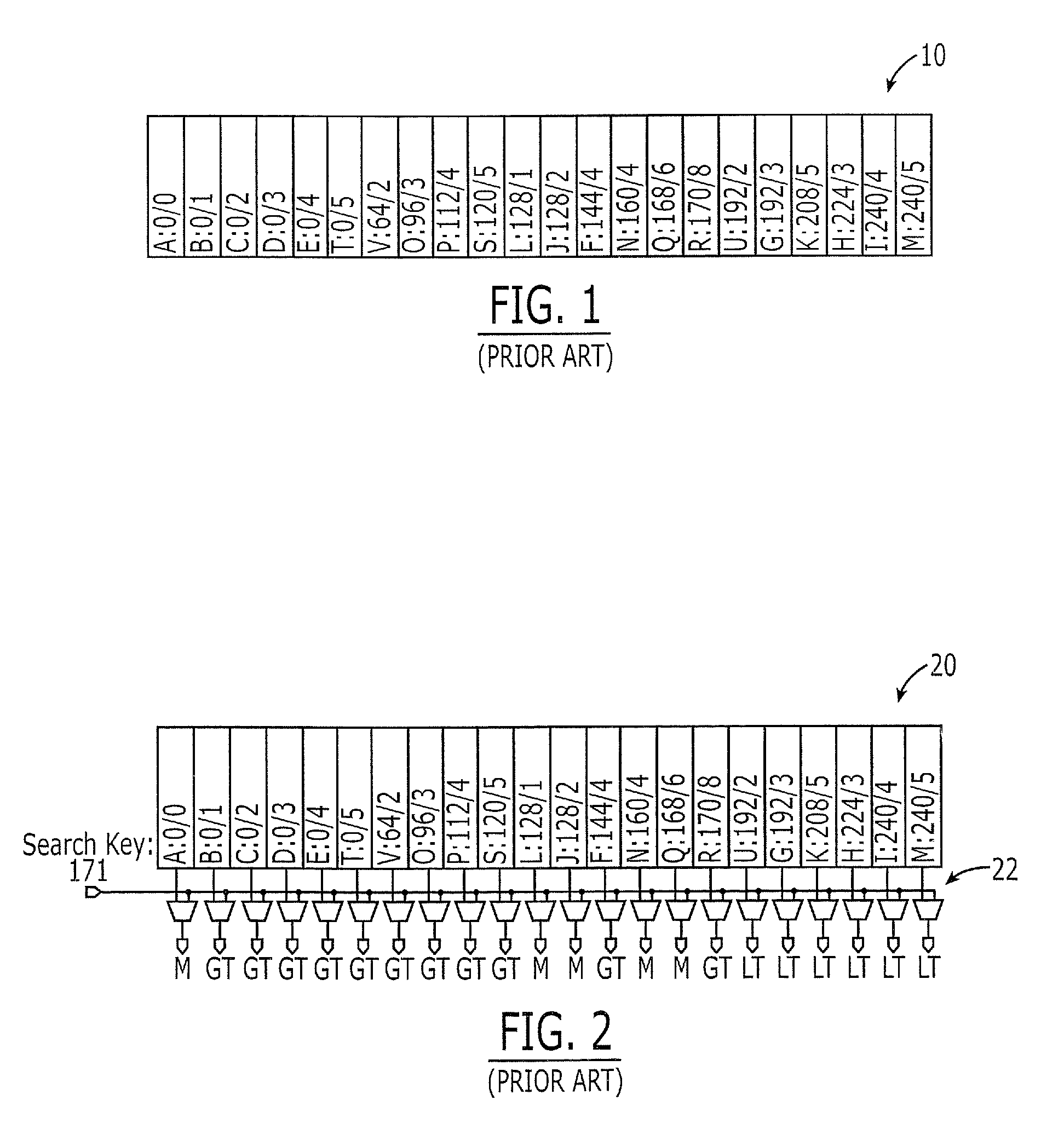

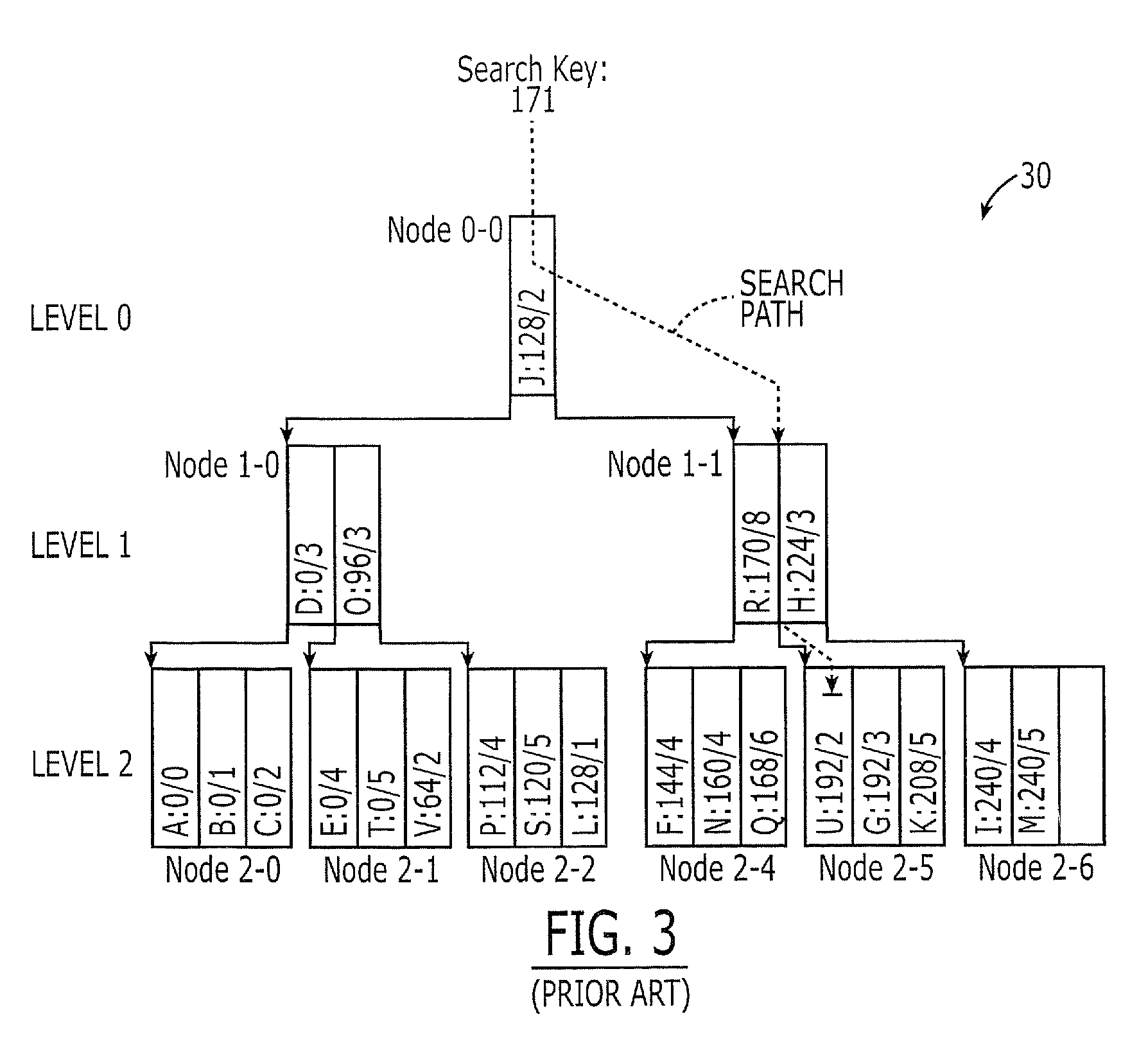

Integrated search engine devices and methods of updating same using node splitting and merging operations

InactiveUS7697518B1Shorten design timeReduce verification effortDigital data information retrievalData switching by path configurationTheoretical computer scienceTree (data structure)

Methods of updating b-tree data structures (e.g., b*tree data structure) using search key insertion and deletion operations proceed from respective known states (e.g., respective canonical forms). These insertion operations include inserting a first search key into the b-tree by reconfiguring (e.g., pre-processing) a plurality of sibling nodes of the b-tree into a predetermined overloaded form having a shape that is independent of a value of the first search key to be inserted therein. An operation is then performed to split the sibling nodes by redistributing the first and other search keys among an expanded plurality of the sibling nodes. These insertion operations use a process that trades off possibly performing additional memory accesses (e.g., to shift search keys (and / or handles or pointers) to the predetermined overloaded form) for the certainty that the same key movements are ultimately performed during operations to split sibling nodes.

Owner:AVAGO TECH INT SALES PTE LTD +1

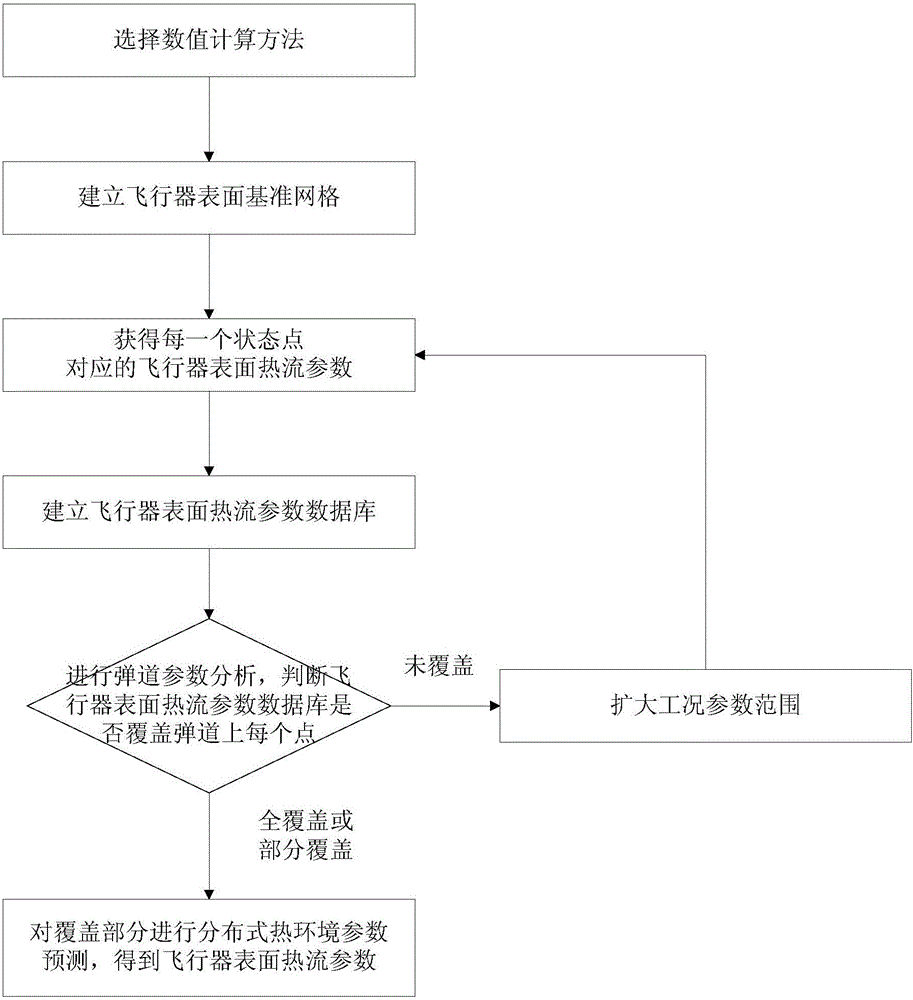

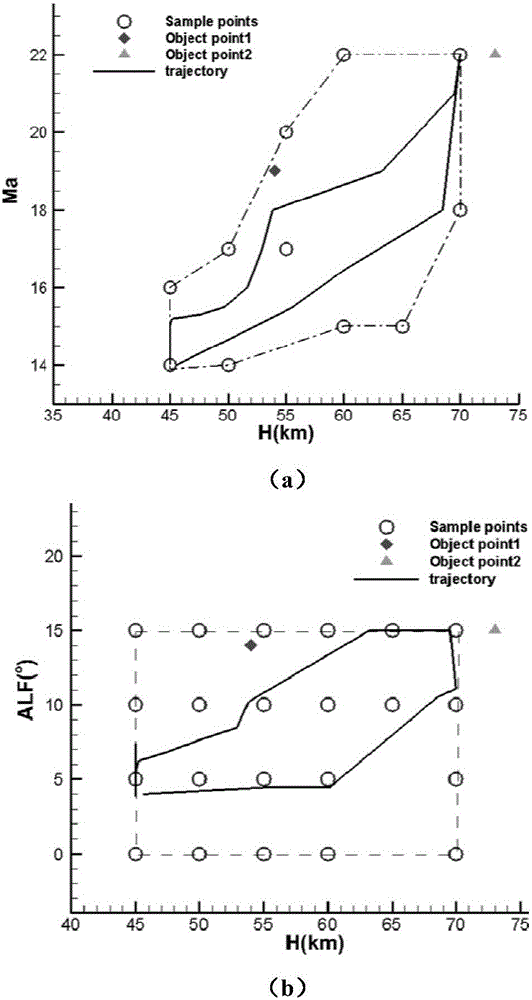

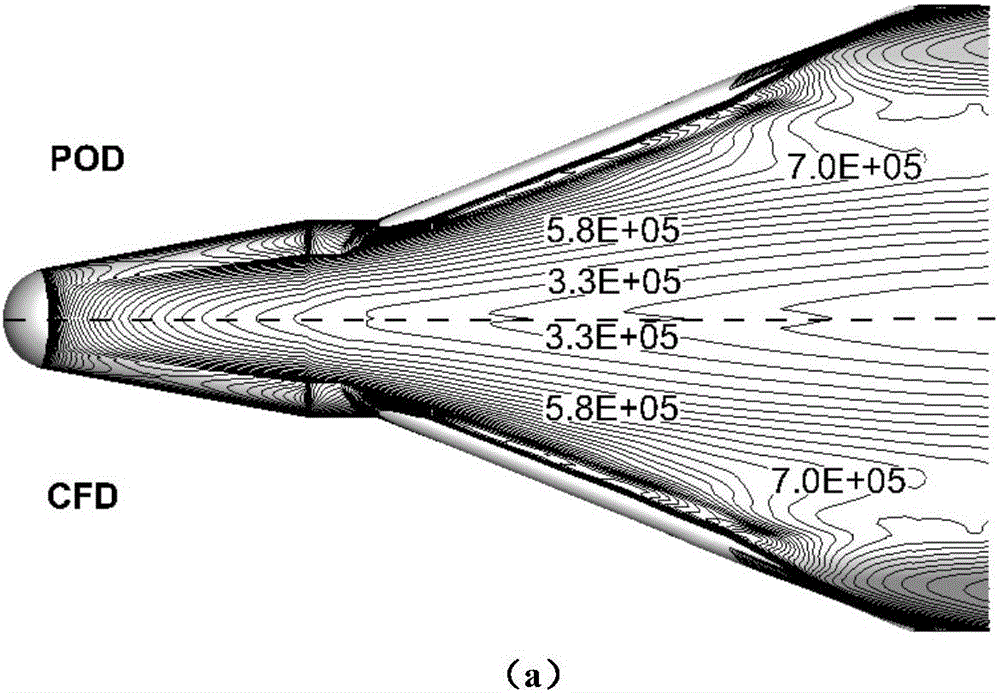

Database based complex-contour aircraft distributed heat environment parameter prediction method

ActiveCN106202804AAccurate predictionImprove design accuracyGeometric CADSustainable transportationEnvironmental designOrthogonal basis

The invention discloses a database based complex-contour aircraft distributed heat environment parameter prediction method and belongs to the field of aircraft heat environment design. The method comprises the steps that an aircraft surface heat flow database is established, order reducing processing is conducted on the database by utilizing a POD method to obtain orthogonal basis vectors of the database, and aircraft surface heat environment parameters can be predicted along a ballistic trajectory by combining with a corresponding basic coefficient interpolation method. The method can really reflect the space distribution characteristics and interference characteristics of the aerodynamic heat environment for all points on the surface of a complex-contour aircraft. Value result comparison shows that the method can remarkably improve the computational efficiency, and prediction precision is not lost. A surface distributed heat flow is provided for calculation of a heat proof temperature field through the points along the ballistic trajectory, more exquisite temperature distribution can be obtained, and accordingly the design level of a whole heat preventing and insulation system is improved.

Owner:BEIJING LINJIN SPACE AIRCRAFT SYST ENG INST +1

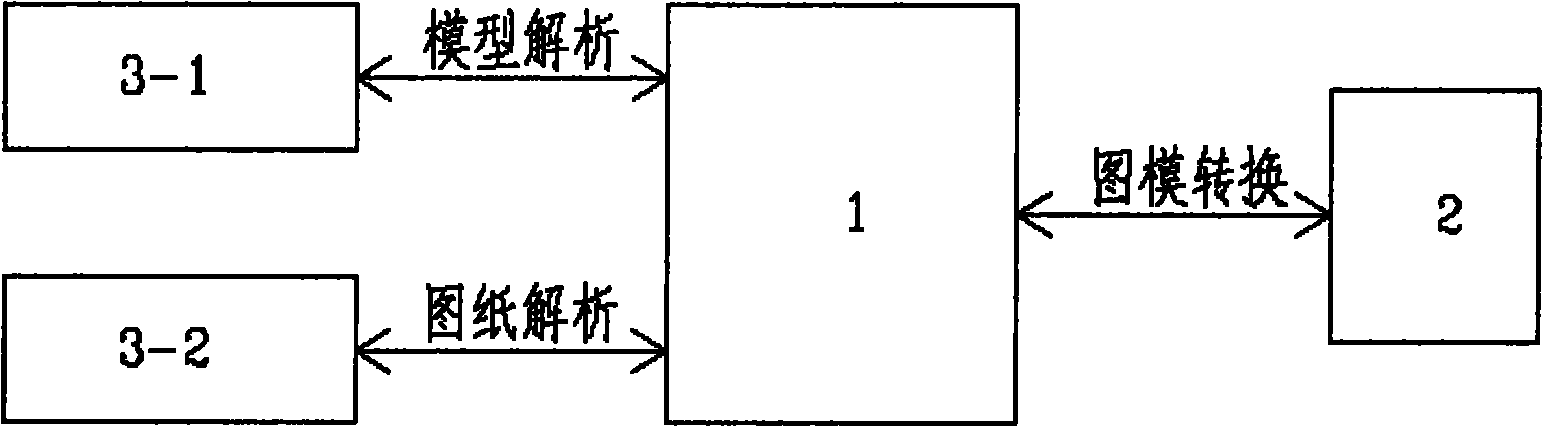

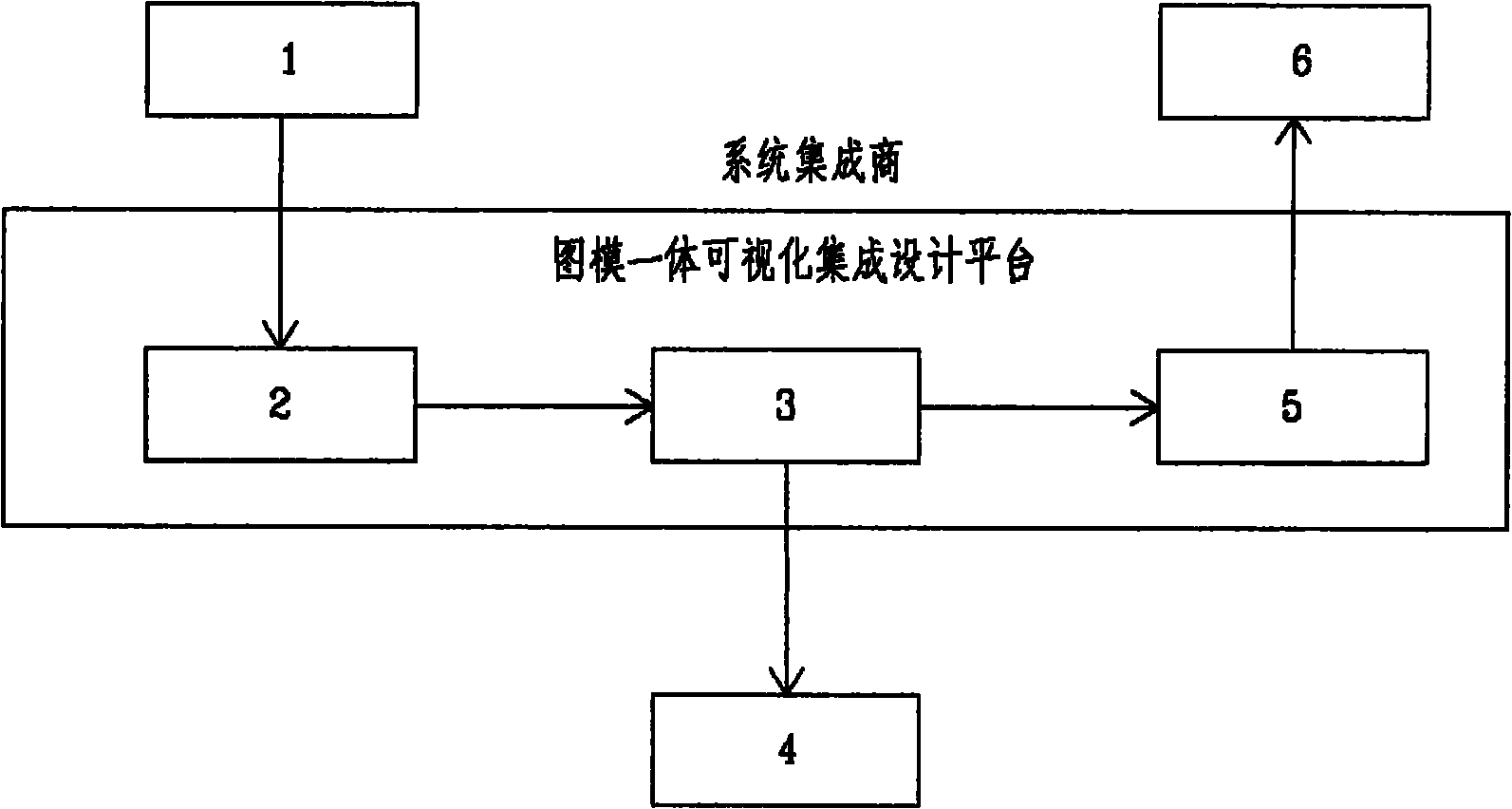

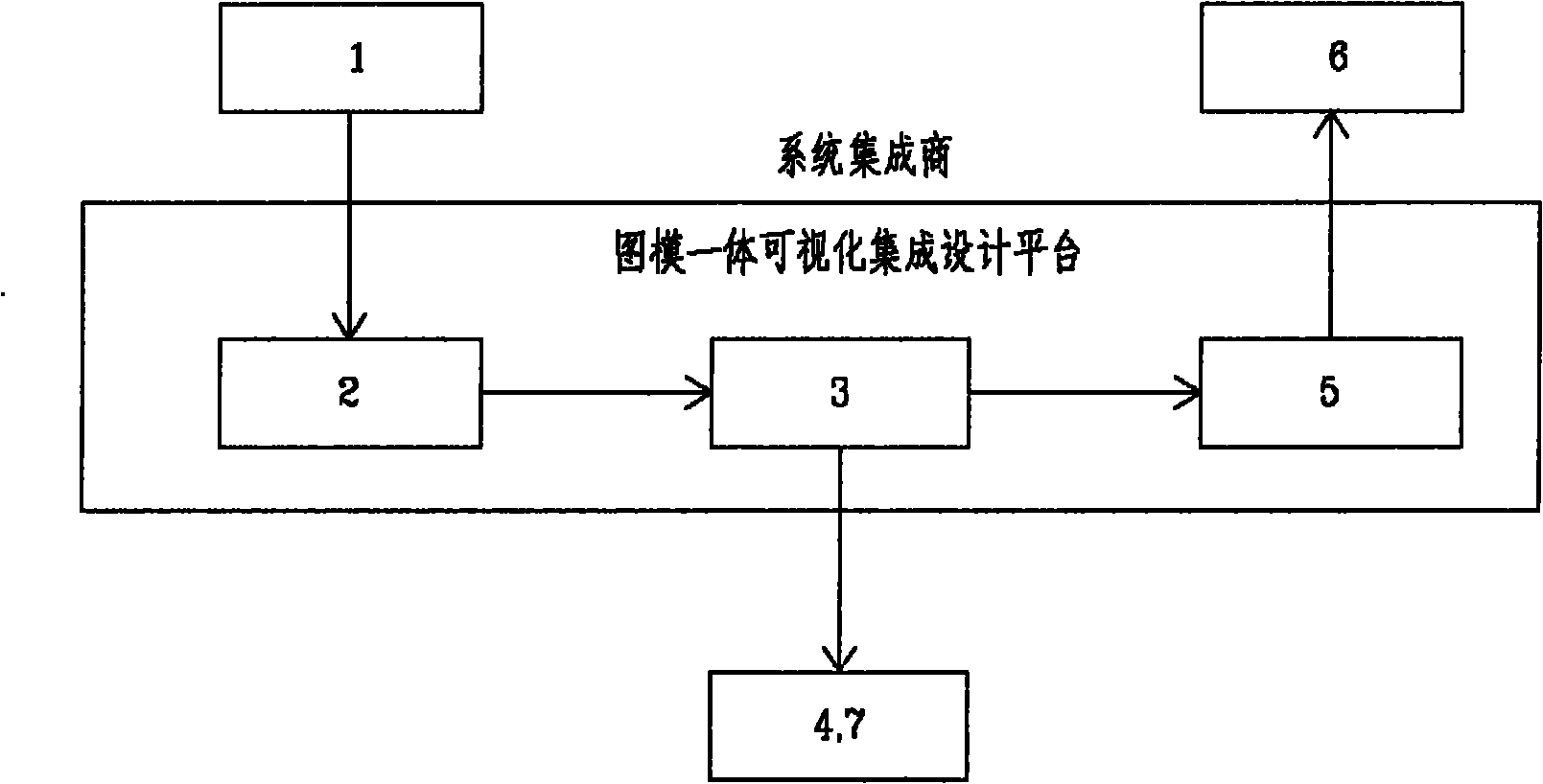

Drawing and model integrated visual integration design method

InactiveCN102184280AReduce repeated information exchangeShorten design timeSpecial data processing applicationsComputer Aided DesignGraphics

The invention discloses a drawing and model integrated visual integration design method. A design institute and a system manufacturer take the responsibility of a system integrator together to finish the work of a designing a drawing for a transform substation and modeling all-station information. In the method, secondary development is performed on an Auto computer-aided design (CAD) by adopting an ActiveX Automation technology by taking the AutoCAD as an information interaction platform so as to establish a native XML database (NXD)-based model text storage database. By adopting the drawing and model integrated integration design, both a design drawing and a model file provided by the design institute can be identified; the bonding of information is finished by the design method so that a CAD file which is finally provided for a user can not only display connection information in the model in a visual mode, but also export the model file for a required unit, a manufacturer or a system to use, and realize the bidirectional switching of the drawing and the model.

Owner:GUANGXI ELECTRIC POWER IND INVESTIGATION DESIGN & RES INST

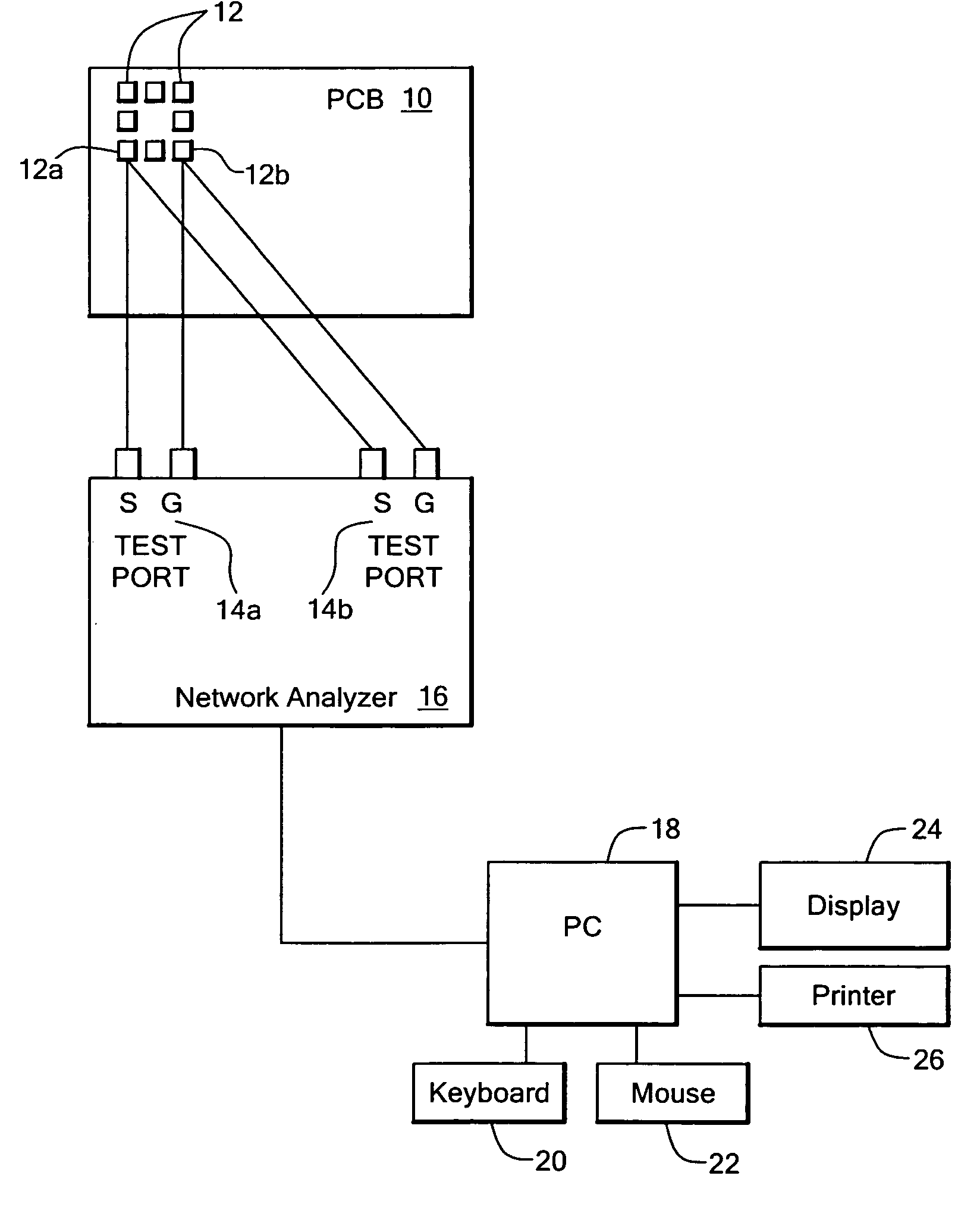

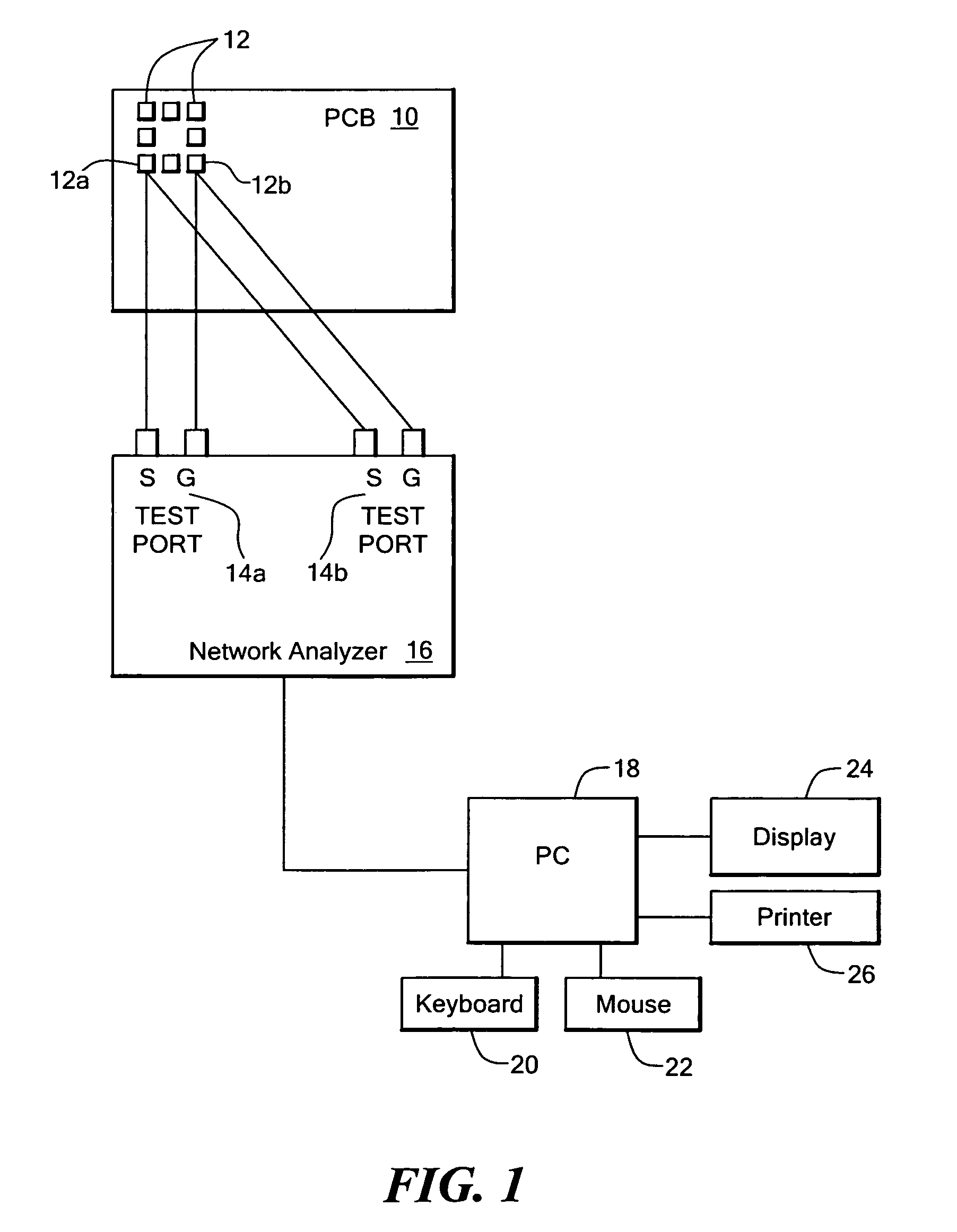

Method and system of characterizing a device under test

InactiveUS20050194981A1Correctly voltage noiseAccurate noiseResistance/reactance/impedenceTime domainEngineering

A system and method of characterizing a device under test wherein a signal is injected into the device under test, the response to the injected signal is measured to determine the impedance of the device under test in the frequency domain, the impedance is converted to the time domain, and the voltage noise of the device under test is calculated based on the impedance of the device under test in the time domain.

Owner:COLE J BRADFORD

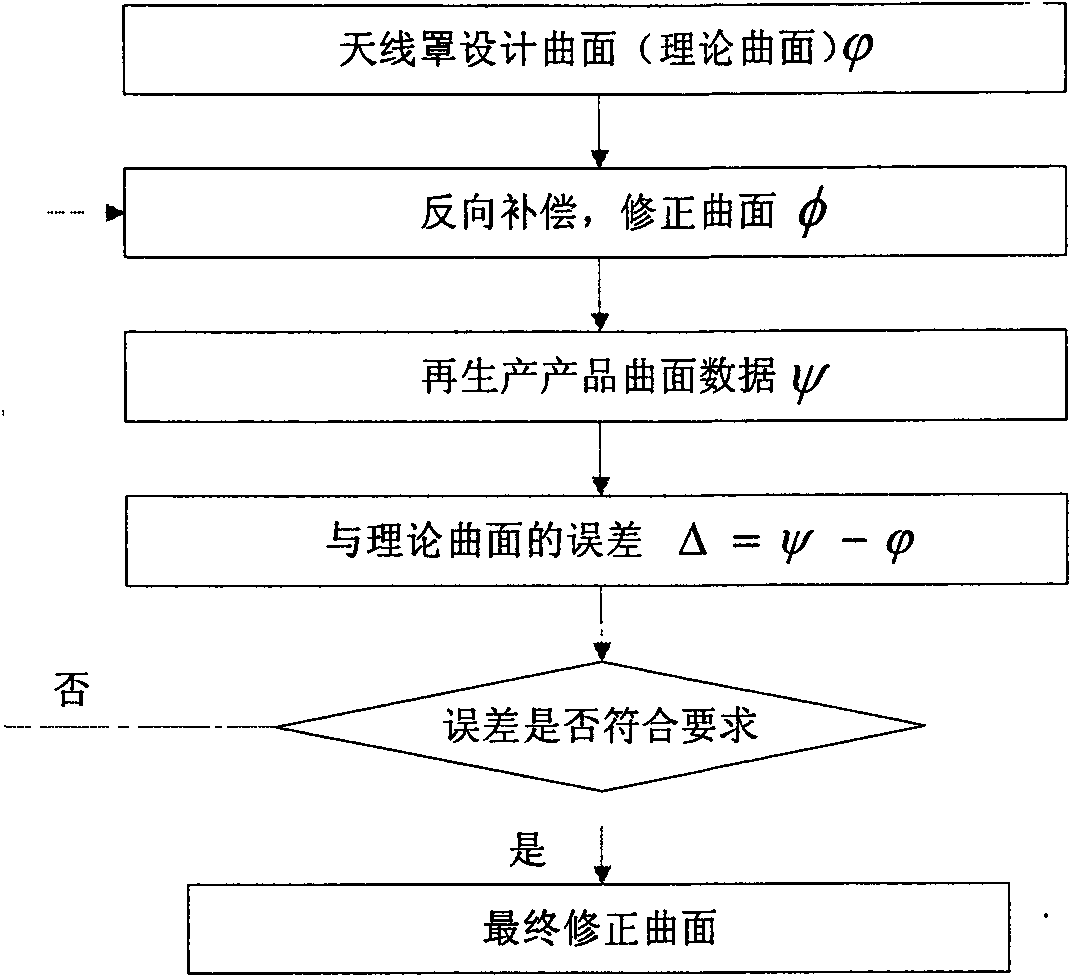

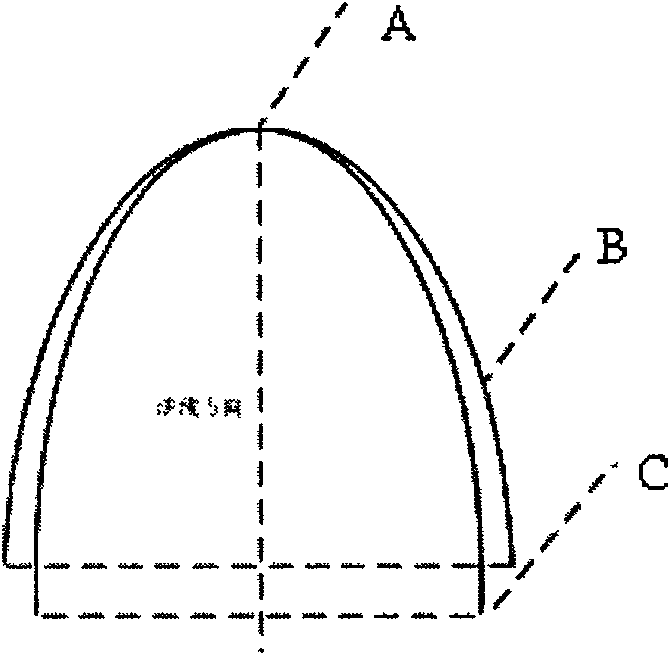

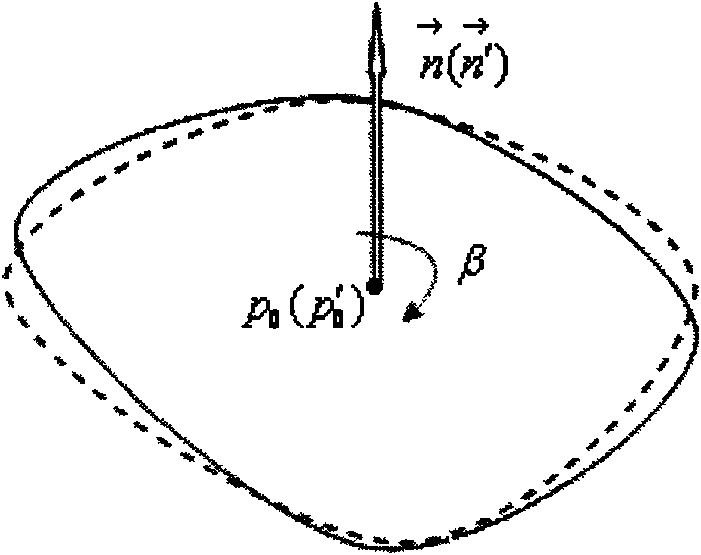

Method for correcting moulding surface of forming mould for antenna cover

InactiveCN102082319AFast preparationHigh precisionAntenna adaptation in movable bodiesFoundry mouldsNumerical controlPoint cloud

The invention relates to a method for correcting a moulding surface of a forming mould for an antenna cover, which is technically characterized in that a numerical control measuring machine is utilized for measuring the shape curved surface of a real object of the antenna cover, thus the measured point cloud data of the antenna cover is further obtained. By matching the measured point cloud data of the antenna cover with the designed curved surface of the antenna cover, the deviation between the measured point cloud data of the antenna cover and the designed curved surface of the antenna cover is calculated, the deviation value is taken as a deformation amount, the moulding surface of the mould is correspondingly corrected when the forming mould is designed for the antenna cover, and the high-precision antenna cover is further rapidly manufactured. The moulding surface of the forming mould for the antenna is corrected through deformation laws and deformation calculation of all points,and the forming precision of the antenna cover is improved. Compared with the conventional mould testing and mould repair method, the method provided by the invention has the advantages that the frequency of mould testing and mould repair and the design time of the mould are reduced, the utilization rate of materials is improved, and the manufacturing cost of the antenna cover is significantly reduced.

Owner:NORTHWESTERN POLYTECHNICAL UNIV +1

Method for modular design of a computer system-on-a-chip

InactiveUS7207014B2Reduce power consumptionEasy to control timeEnergy efficient ICTPower supply for data processingTelecommunications linkClock rate

In a computer system having a device and a communications link for communicating with the device. A method for dynamically managing power consumption by the computer system comprises associating a particular device identifier with the device. Communications are monitored over the communications link to determine whether the communications include the particular device identifier. A clock input is withheld from the device when the communications do not include the particular device identifier. Clock input is provided to the device only when the communications include the particular device identifier. The clock input causes the device to transition from a non-operational power conservative state to an operational state wherein the device consumes more power than in the non-operational state. A performance requirement is established for a task to be executed. Clock frequency is dynamically controlled according to the performance requirement established for the task being executed.

Owner:ST CLAIR INTPROP CONSULTANTS

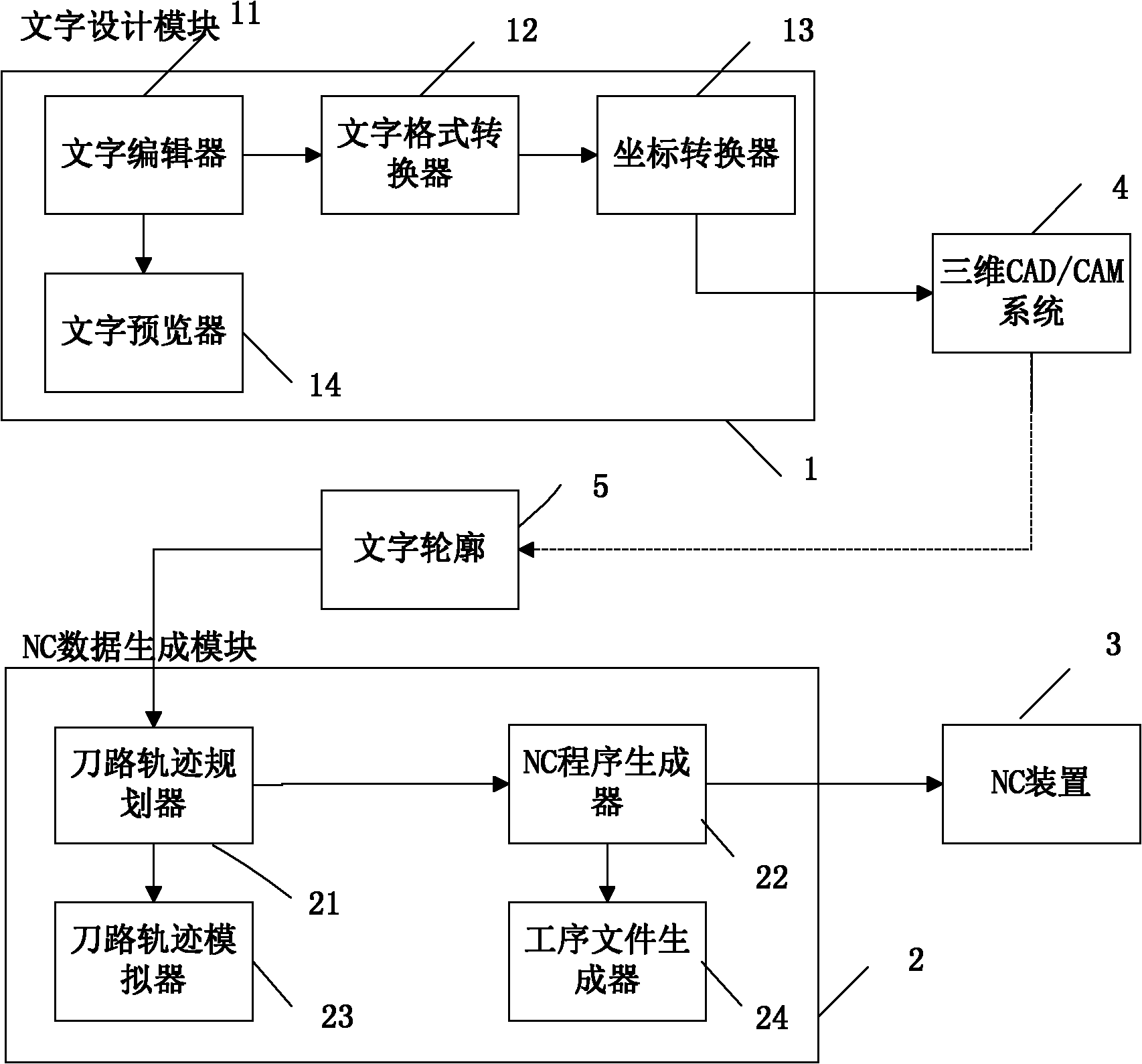

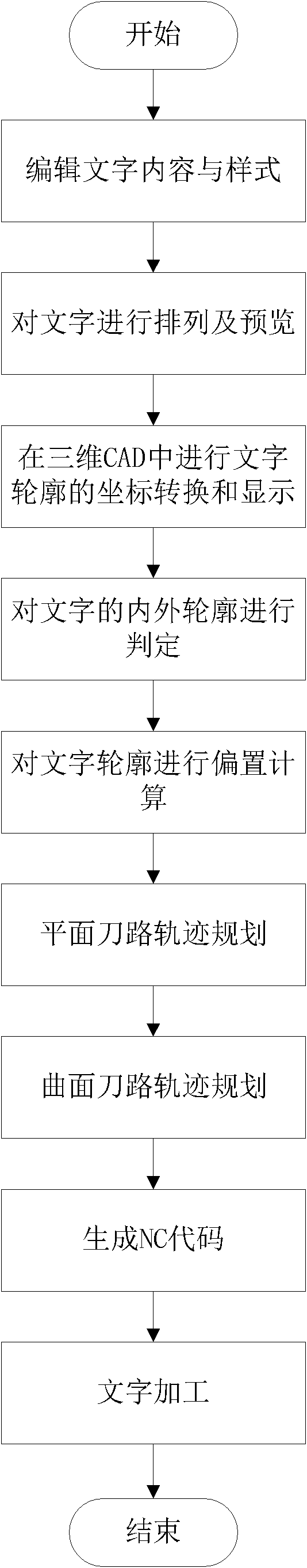

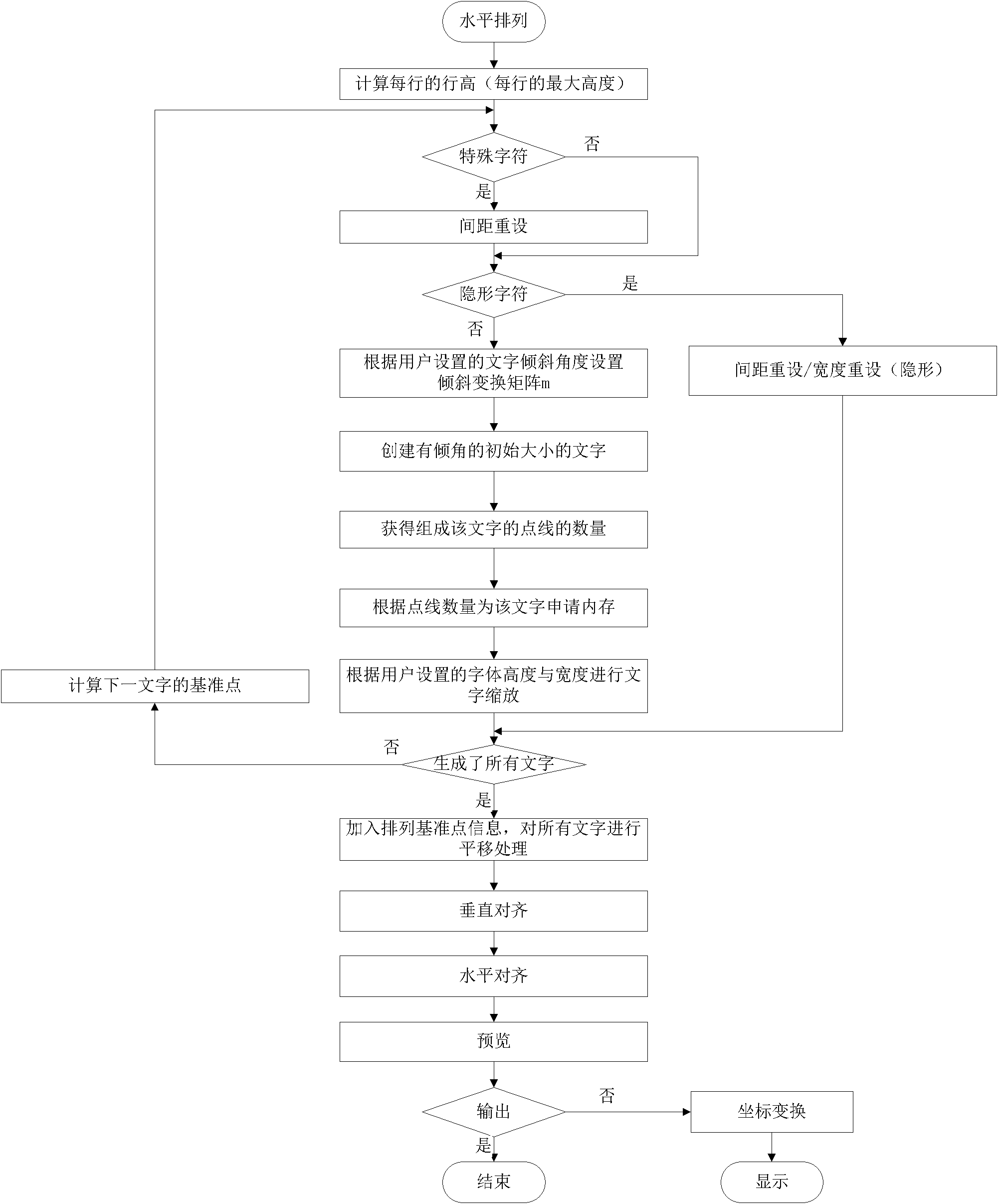

System and method for designing and processing characters for tire mold in three-dimensional CAD/CAM environment

The invention relates to a system and a method for designing and processing characters for a tire mold in a three-dimensional CAD / CAM environment. The system mainly comprises a character design module, an NC data generation module and an NC device, wherein the character design module is connected with the NC data generation module through a three-dimensional CAD / CAM system; and the NC data generation module is connected with the NC device; the character design module is used for designing and editing characters in the three-dimensional CAD / CAM environment and extracting character outlines for display; the NC data generation module is used for generating a cutting track according to the character outlines and further generating an NC program according to the condition of a machine tool; the NC device is used for controlling processing actions of the machine tool to process the characters according to the NC program; and the three-dimensional CAD / CAM system is an operating platform of a character designing and processing system for the tire mold, and connects the character design module with the NC data generation module through CAD / CAM-identified line elements.

Owner:山东山大华天软件有限公司

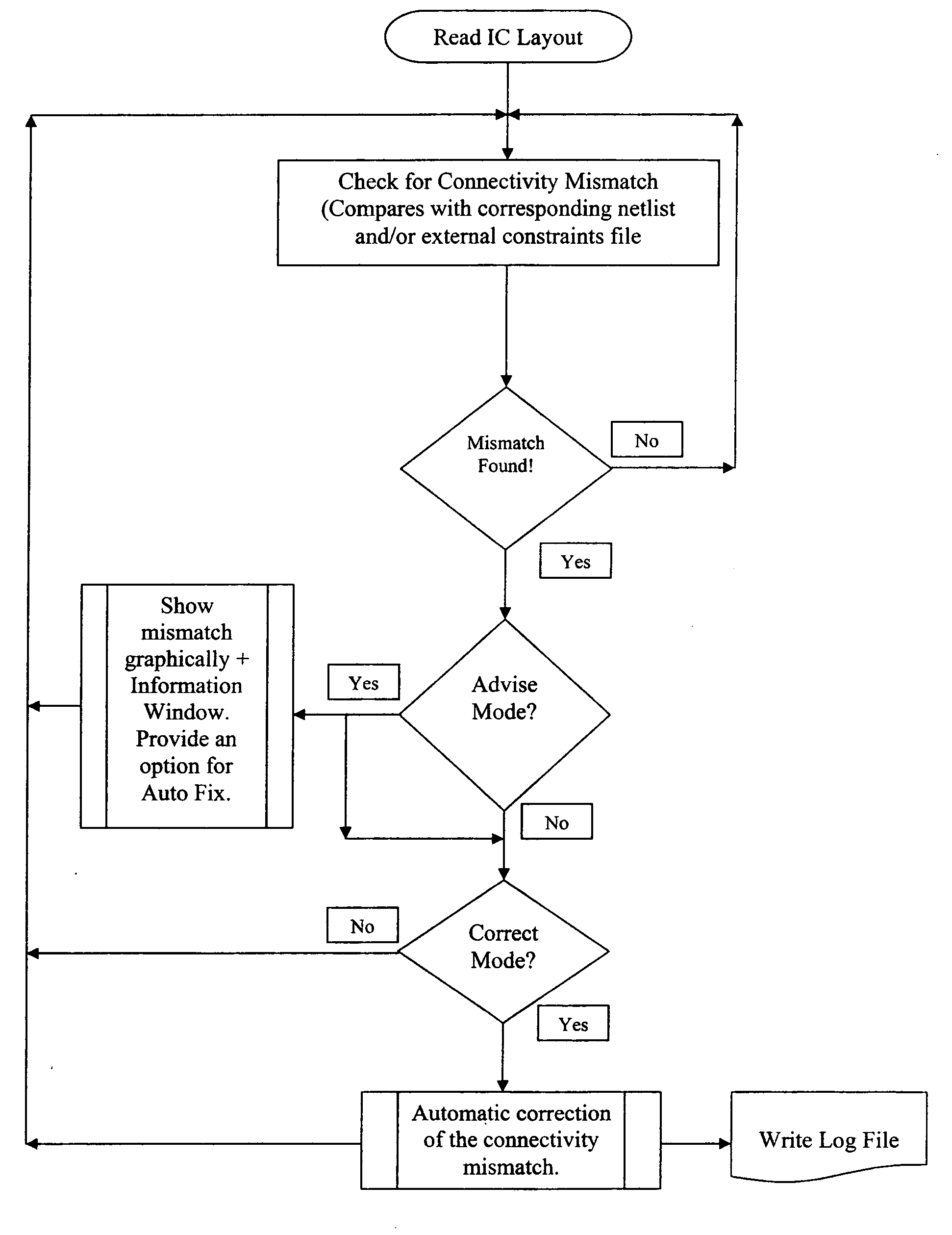

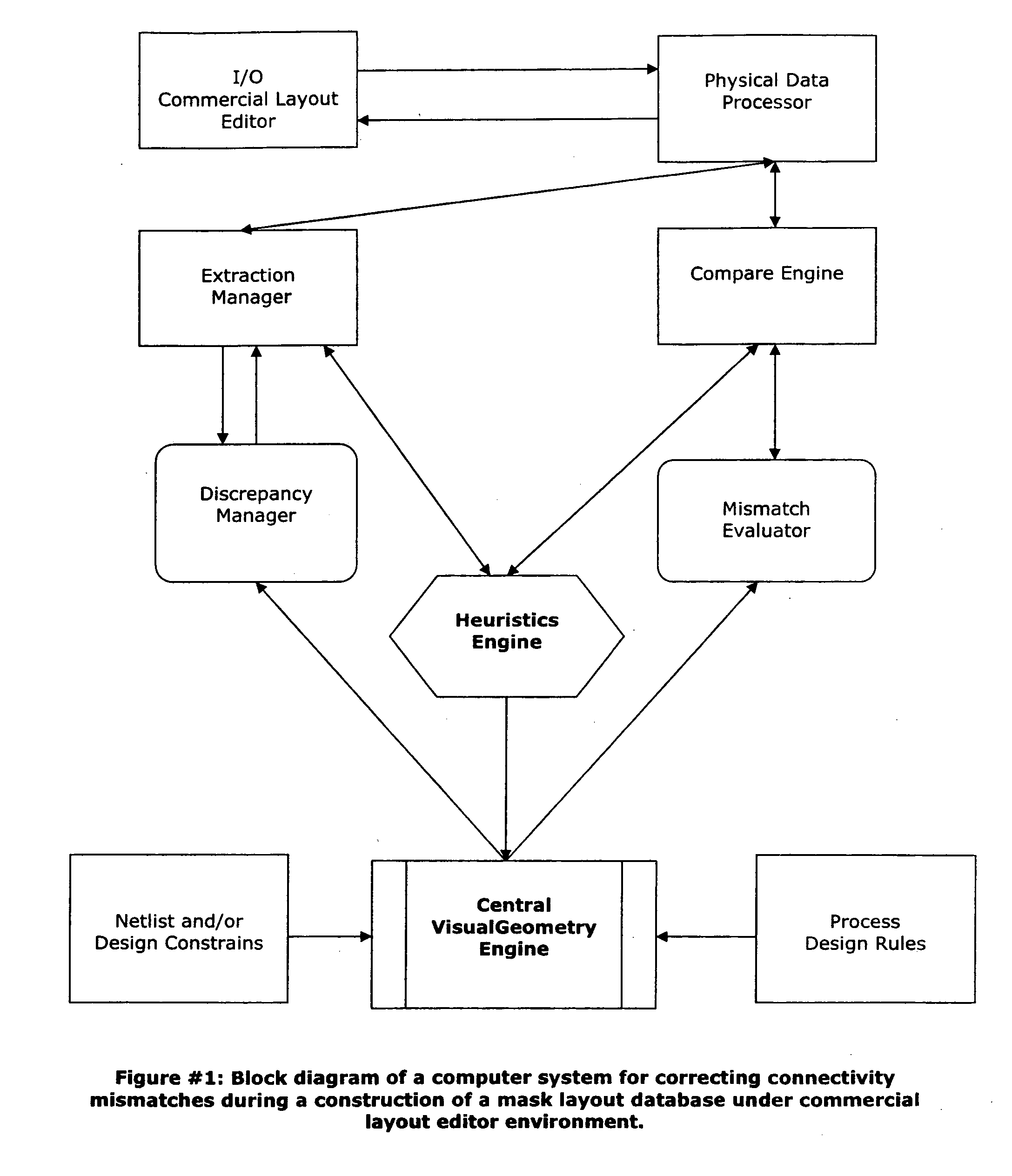

System and method for automatic elimination of connectivity mismatches during construction of a mask layout block, maintaining process design rule correctness

InactiveUS20080115102A1Eliminate the problemCorrecting connectivityCAD circuit designSpecial data processing applicationsGraphicsParallel computing

A system and method for automatic elimination of connectivity mismatches during construction of a mask layout block, maintaining the process design rules (DRC Clean) and layout connectivity (LVS Clean) correctness are disclosed. The method includes analyzing a selected polygon or net for connectivity, in a mask layout block and comparing it to a netlist that is associated with the polygon or net. The method includes comparing a physical connection in a mask layout database within a commercial layout editor to a corresponding connection in a schematic netlist and / or external constraints file. A connectivity mismatch is identified if the physical connection in the commercial layout editor database does not match the same connection in the netlist and / or external constraints file. When a mismatch is identified the connectivity error is graphically presented in the mask layout database within commercial layout editor. The method and system also provides an option to automatically correct the connectivity mismatch during the construction of the mask layout block within commercial layout editor using the editor's commands and functions.

Owner:MICROLOGIC DESIGN AUTOMATION

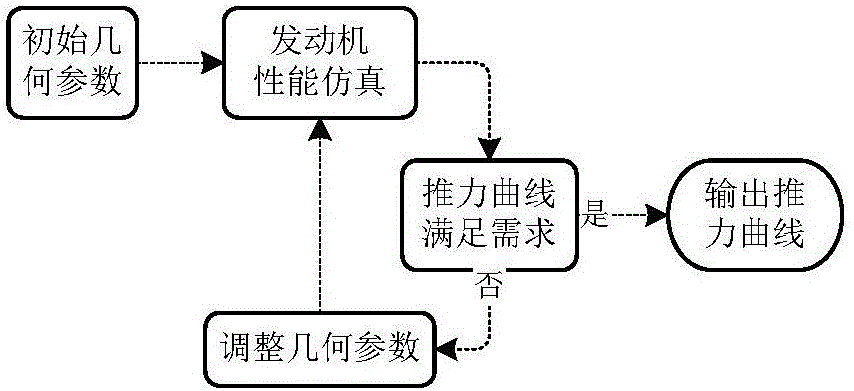

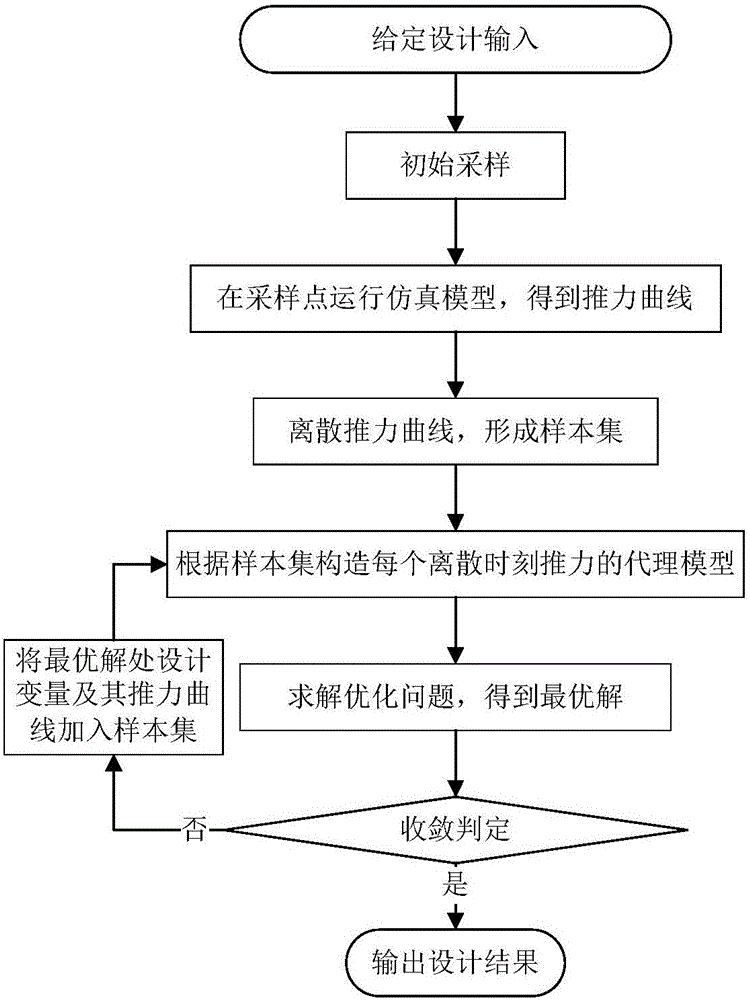

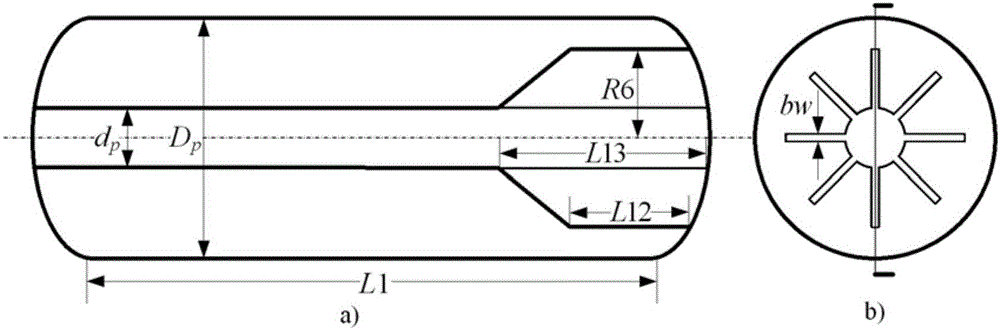

Charging design method of solid rocket engine

ActiveCN105956281AEffectively describe the law of changeReduce precisionDesign optimisation/simulationSpecial data processing applicationsRocketLeast squares

The invention provides a charging design method of a solid rocket engine. An agent model is used as a basis to directly carry out approximation on a thrust curve, and the thrust curve, instead of the agent model of a least square deviation between the thrust curve and a design index, is constructed to effectively describe a change rule of the thrust along with time so as to obviously reduce the simulation frequency of a high-precision burning surface and a trajectory. The agent model can better describe the change rule of the thrust curve, effectively guides subsequent search in a subsequent design, and can obviously improve the charging design efficiency of the solid rocket engine.

Owner:NAT UNIV OF DEFENSE TECH