LDMOS and manufacturing method thereof

A manufacturing method and area technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of large on-resistance in the drift region and affecting the performance of LDMOS

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

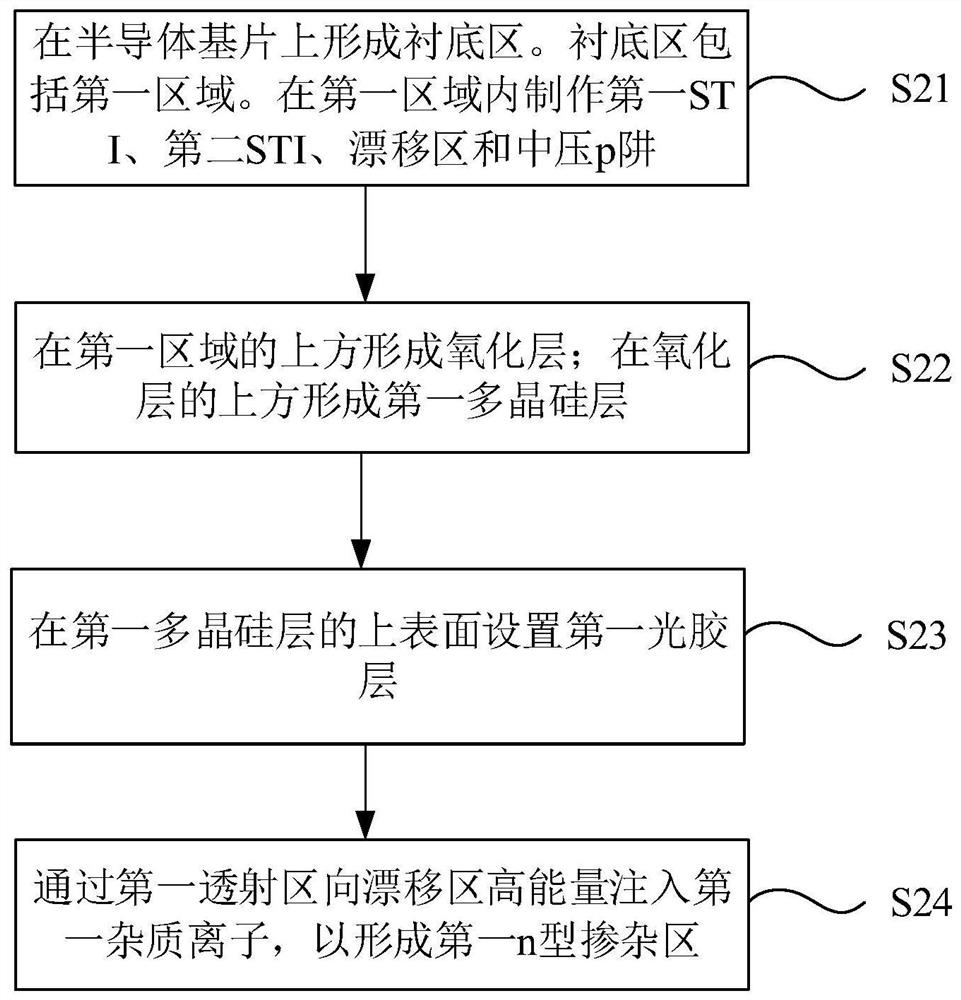

[0050] This embodiment provides a manufacturing method of LDMOS, referring to Figure 2 to Figure 9 , the production method includes the following steps:

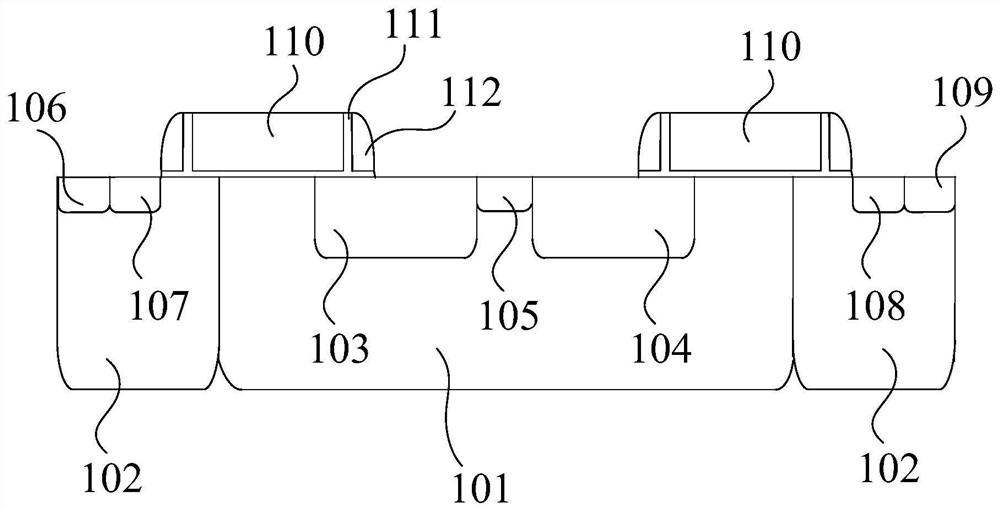

[0051] Step S21 , forming a substrate region on the semiconductor substrate. The substrate region comprises a first region 11 . The first STI 103, the second STI 104, the drift region 101 and the medium voltage p-well 102 are fabricated in the first region.

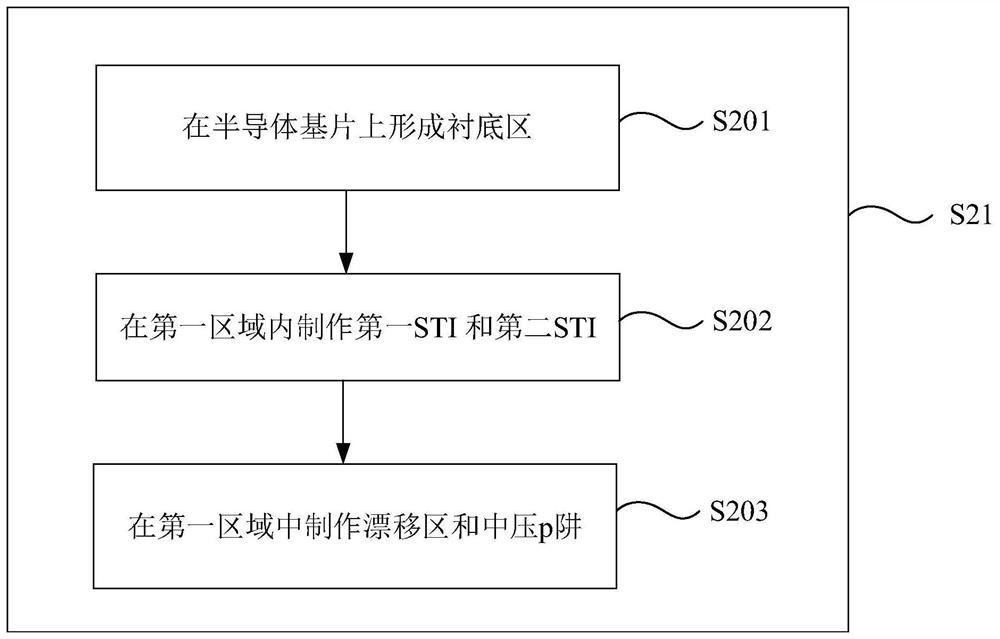

[0052] As a preferred implementation manner, step S1 includes:

[0053] Step S201, forming a substrate region on a semiconductor substrate.

[0054] Step S202 , making the first STI 103 and the second STI 104 in the first area 11 . Make a state reference after forming the first STI 103 and the second STI 104 Figure 4 .

[0055] Step S203 , fabricating a drift region 101 and a medium voltage p-well 102 in the first region 11 . The depth of the drift region 101 is greater than the depths of the first STI 103 and the second STI 104 . State reference after fabrica...

Embodiment 2

[0064] On the basis of the manufacturing method of the LDMOS in the first embodiment, this embodiment provides a manufacturing method of the LDMOS, the LDMOS further includes a high-resistance device, and the high-resistance device is formed by using the second region of the substrate region.

[0065] The flow process of making LDMOS by adopting the manufacturing method of LDMOS of the present embodiment is as follows:

[0066] In step S21, first, a substrate region is formed on a semiconductor substrate. refer to Figure 10 , the substrate region includes a first region 11 and a second region 12 . The first STI 103 and the second STI 104 are fabricated in the first region 11 , while the third STI 121 is fabricated in the second region 12 .

[0067] Then, refer to Figure 11 , and simultaneously implant the same impurity ions into the first region 11 and the second region 12 to form the drift region 101 in the first region 11 and form the first doped region 122 in the secon...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More