N-type LDMOS device and technical method thereof

A process method, N-type technology, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of low on-resistance, reduce device breakdown voltage, etc., and achieve low on-resistance, on-current The effect of increasing and decreasing the surface electric field strength

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

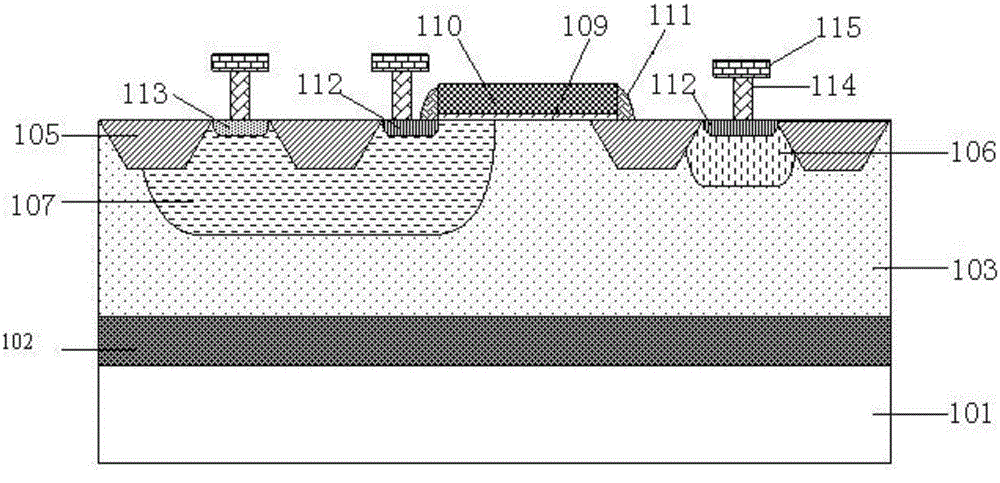

[0032] The N-type LDMOS device described in the present invention is as Figure 10 As shown, there is an N-type buried layer 102 on a low-resistance substrate 101 with a resistivity of 0.007-0.013 Ω·cm. On the buried layer 102 is an N-type epitaxy 103, and there are P wells abutting against each other in the N-type epitaxy 103. 107 and drift zone 108;

[0033] The drift region 108 also has an N well 106 and an STI isolation structure 105;

[0034] The source region 112 of the LDMOS device is provided in the P well 107, and the drain region 112 of the LDMOS device is provided in the N well 106 of the drift region 108 (both heavily doped N-type regions, using the same reference numeral);

[0035] The P well 107 also has a heavily doped P-type region 113, leading out the P well 107; the P well 107 is used as a channel region of the LDMOS device;

[0036] The N-type epitaxy 103 has a gate oxide layer 109 and a polysilicon gate 110 on the surface of the LDMOS device, and the two ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More