CMOS device in BCD process and manufacturing method thereof

A manufacturing method and technology for MOS transistors, which are applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., and can solve problems such as shortening the effective length of the device channel.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example B

[0078] The CMOS device in the BCD process of the first embodiment of the present invention:

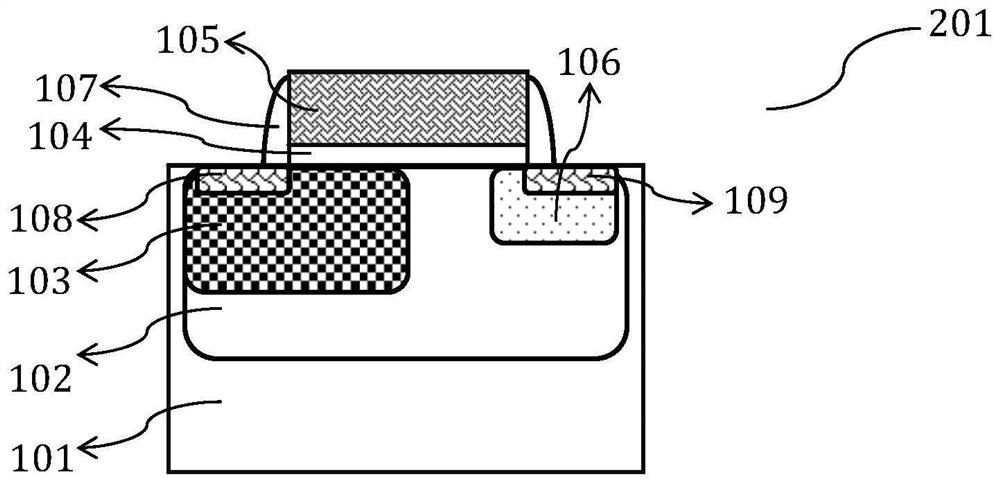

[0079] Such as figure 2 Shown is a schematic structural diagram of the first MOS transistor 201 of the CMOS device in the BCD process of the first embodiment of the present invention; the CMOS device and the LDMOS device in the BCD process of the first embodiment of the present invention are simultaneously integrated on the same semiconductor substrate 101 .

[0080] The CMOS device includes a first MOS transistor 201 whose channel conductivity type is the first conductivity type, and the LDMOS device includes a first LDMOS whose channel conductivity type is the second conductivity type. figure 2 In , the formation region of the first LDMOS is not shown.

[0081] The drift region of the first LDMOS is composed of the first doped region 103 doped with the second conductivity type. Since the formation region of the first LDMOS is not shown, the first doped region 103 constituting th...

no. 2 example B

[0097] The CMOS device in the BCD process of the second embodiment of the present invention:

Embodiment B

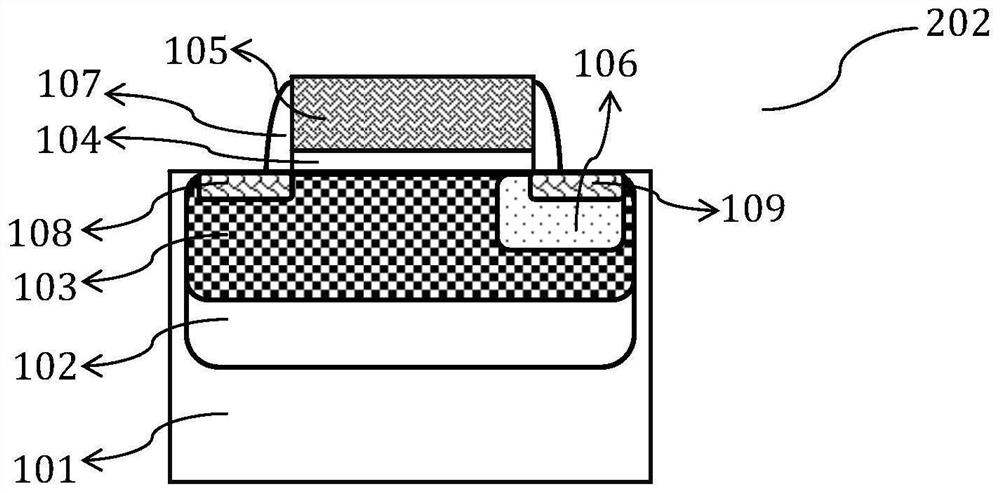

[0098] Such as image 3 As shown, it is a schematic structural diagram of the first MOS transistor 202 of the CMOS device in the BCD process of the second embodiment of the present invention; the difference between the CMOS device in the BCD process of the second embodiment of the present invention and the CMOS device in the BCD process of the second embodiment of the present invention where:

[0099] In the first MOS transistor 202, the first doped region 103 also extends to the first well region 102 outside the second side of the first gate structure and the first lightly doped Both the drain region 106 and the first drain region 109 are covered.

[0100] In the second MOS transistor, the second doped region also extends into the second well region outside the second side of the second gate structure and connects the second lightly doped drain region and Both the second drain regions are capped.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More