Trench type power semiconductor device and manufacturing method thereof

A power semiconductor, trench-type technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as high process risk, increase the difficulty and cost of device manufacturing, short circuit between gate and emitter, and achieve Reduce manufacturing costs, speed up switching, and avoid the effects of parasitic gate capacitance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

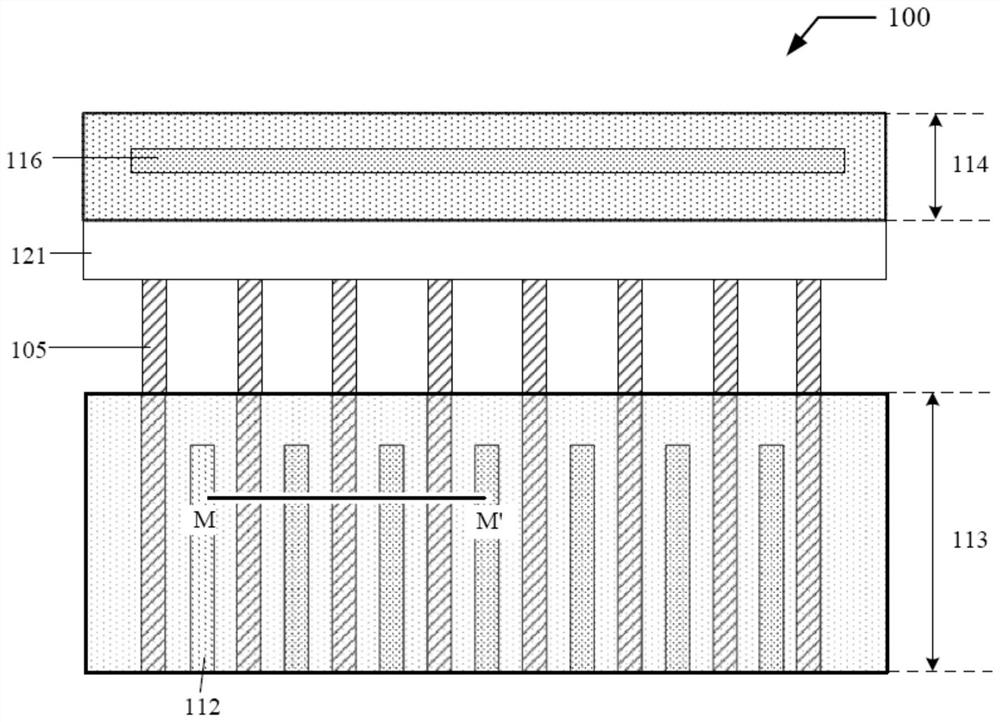

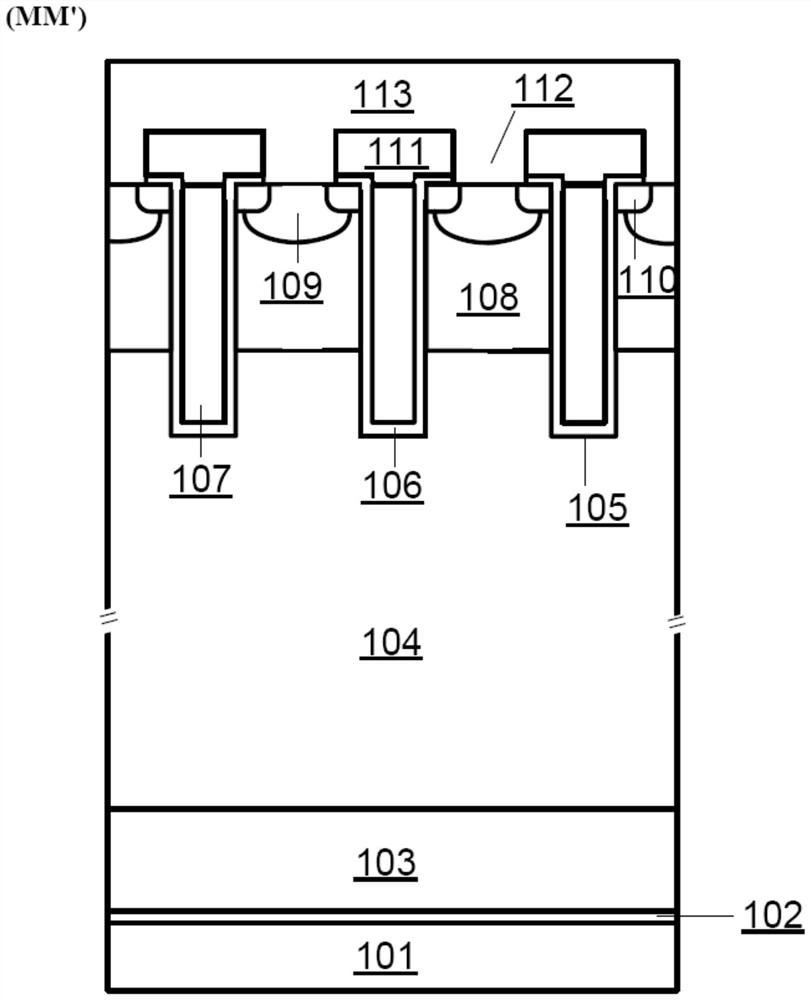

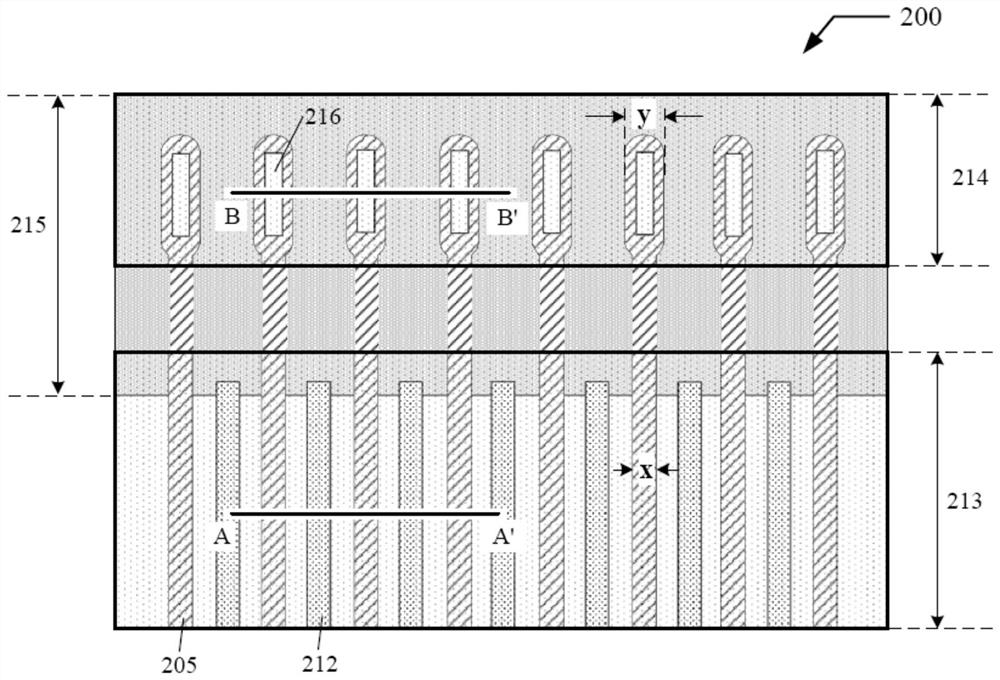

[0057] image 3 It is a schematic partial top view of the IGBT device 200 based on the first embodiment of the present invention, Figure 4 and Figure 5 corresponding to image 3 A schematic diagram of the cross-sectional structure of the A-A' and B-B' tangent lines of the middle device 200. Such as Figure 4 , 5 As shown, the device 200 has a collector metal layer (201) at the bottom of the device, a semiconductor region above the collector metal layer (201), and the semiconductor region includes p + type collector doped region (202), n type electric field stop layer (203) and n - type drift region (204); an interlayer dielectric layer (211) is provided on the semiconductor region, and the interlayer dielectric layer is generally made of materials such as silicon oxide or silicon nitride; in the interlayer dielectric layer ( 211) are respectively provided with an emitter electrode metal layer (213) and a gate electrode metal layer (214) composed of metal layers, such a...

Embodiment 2

[0063] Figure 24 is a schematic partial top view of an IGBT device 300 according to a second embodiment of the present invention, Figure 25 and Figure 26 corresponding to Figure 24 The schematic diagram of the cross-sectional structure of the C-C' and D-D' tangent lines of the middle device 300. Compared with the device 200 described above, the device 300 also has the following characteristics: there are several dummy trenches (218) arranged in parallel with the trenches (205), and the start of the dummy trenches (218) Both the initial section and the extension section are located under the emitter electrode metal layer (213), and the width of the initial section of the dummy trench (218) is greater than the width of its extension section. The dummy trench (218) is filled with a dummy gate conductive material (227), and a dummy gate contact hole (217) is provided above the initial section of the dummy trench (218), and the dummy gate conductive material (227) is connec...

Embodiment 3

[0065] Figure 27 is a schematic partial top view of an IGBT device 400 according to a third embodiment of the present invention, Figure 28 and Figure 29 corresponding to Figure 27 Schematic diagram of the cross-sectional structure of the E-E' and F-F' tangent lines of the middle device 400. Compared with the device 300 described above, the device 400 also has the following characteristics: there is more than one dummy trench (218) between adjacent trenches (205), and the dummy trenches (218) between adjacent dummy trenches (218) No emitter contact hole (212) is provided on the surface of the semiconductor region. A p-type body region (208) may be provided between the extensions of adjacent dummy trenches (218), such as Figure 28 shown. Since there is no emitter contact hole (212) between adjacent dummy trenches (218), the semiconductor region in this region can be in an electrically floating state, so more carriers can be stored when the IGBT is in the on-state, Red...

PUM

| Property | Measurement | Unit |

|---|---|---|

| width | aaaaa | aaaaa |

| width | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More