Patents

Literature

37results about How to "Reduce photolithography steps" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

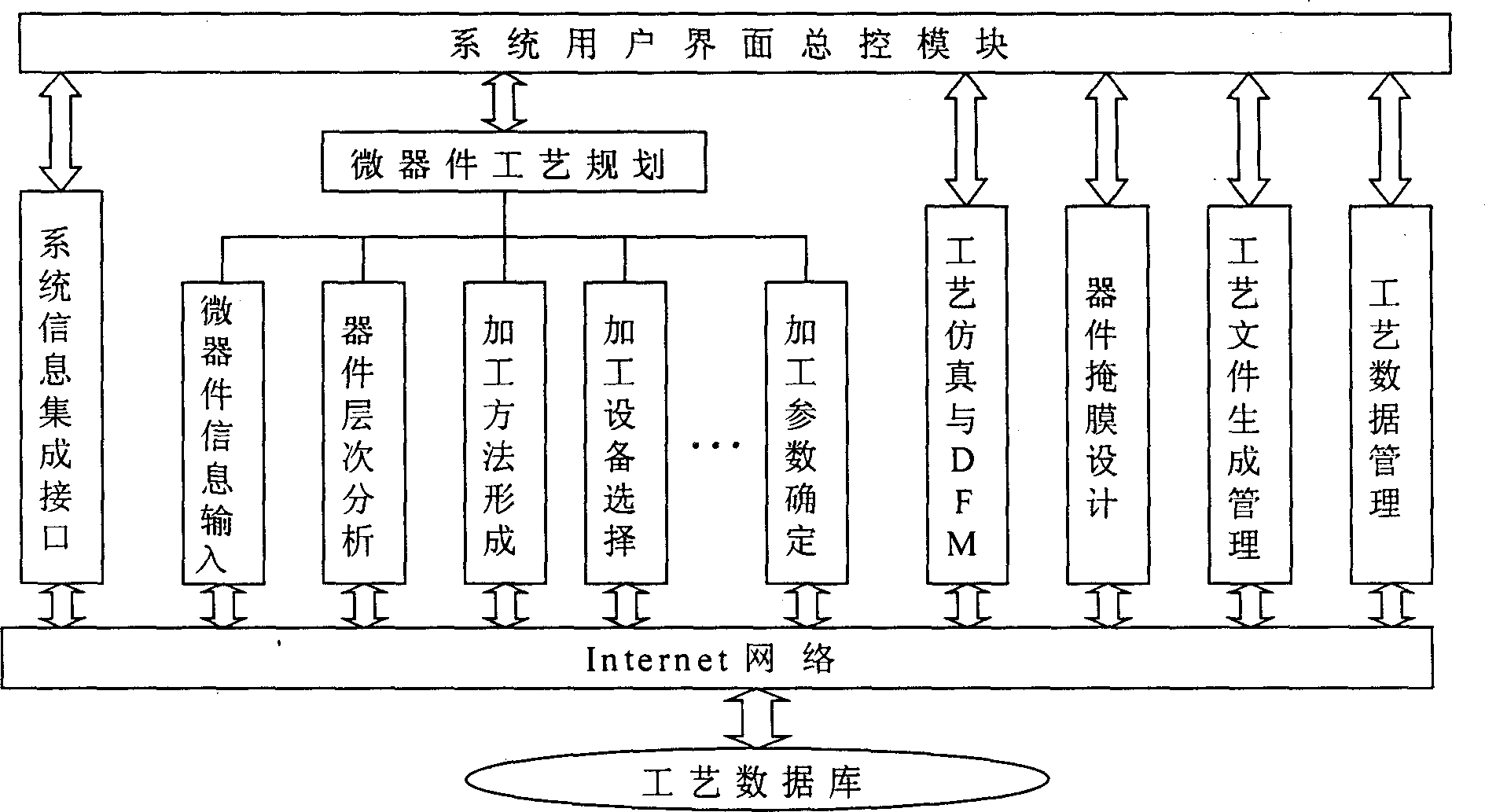

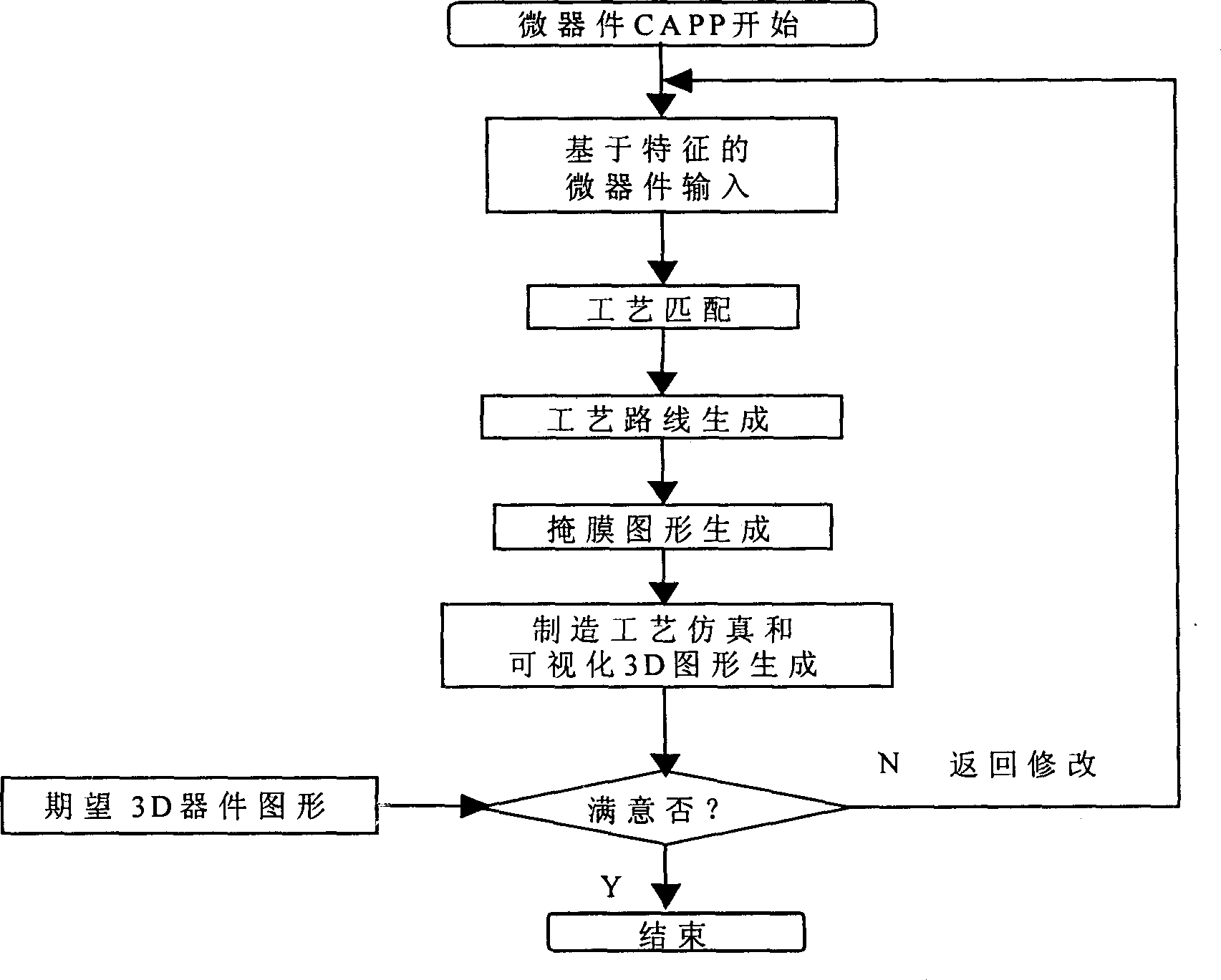

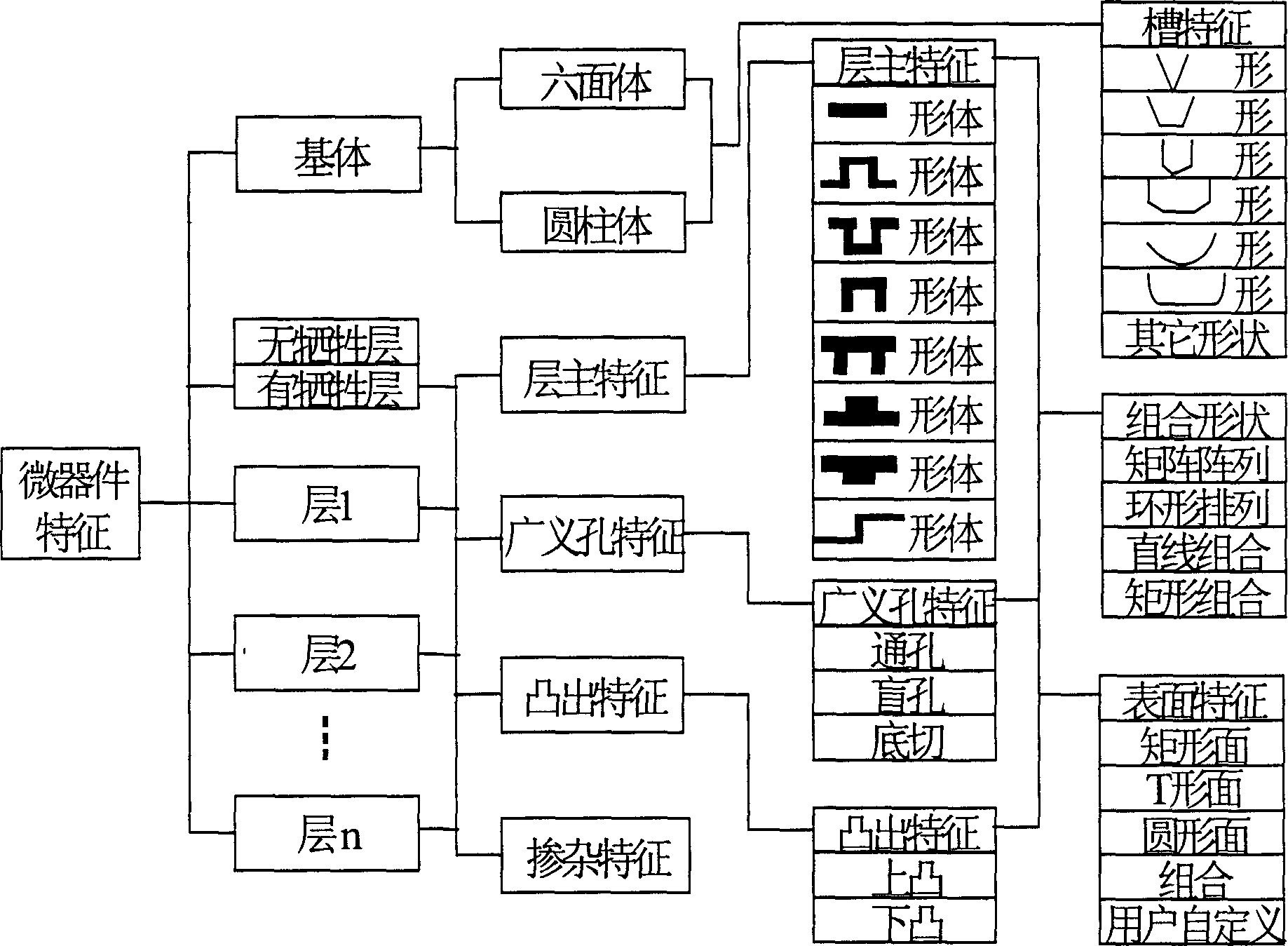

Computer-aided technique planning method for silicon micro-component

InactiveCN1448870AReduce the number of iterationsReduce errorsSpecial data processing applicationsSurface micromachiningComputer-aided

The present invention discloses the computer-aided technological planning method with stereo micro processing and surface micro processing as research object. The 3D geometrical structure of micro device is decomposed into several processing layers comprising main characteristic and auxiliary characteristics, and complete 3D and 2D manufacture characteristics of micro device are established with the manufacture characteristics being associated with the silicon-based micro processing method and reflecting the constraint condition of the micro processing. The relationship between MEMS layout and the mask and micro processing design is established. Via the three-dimensional micro device model, the numbers of processing steps and masks are decreased via the layer merging. The relationship between characteristic indexing tree and characteristics is formed and various models are established in technological process and mask pattern design. Technological data and CIF format mask files are finally created.

Owner:XI AN JIAOTONG UNIV

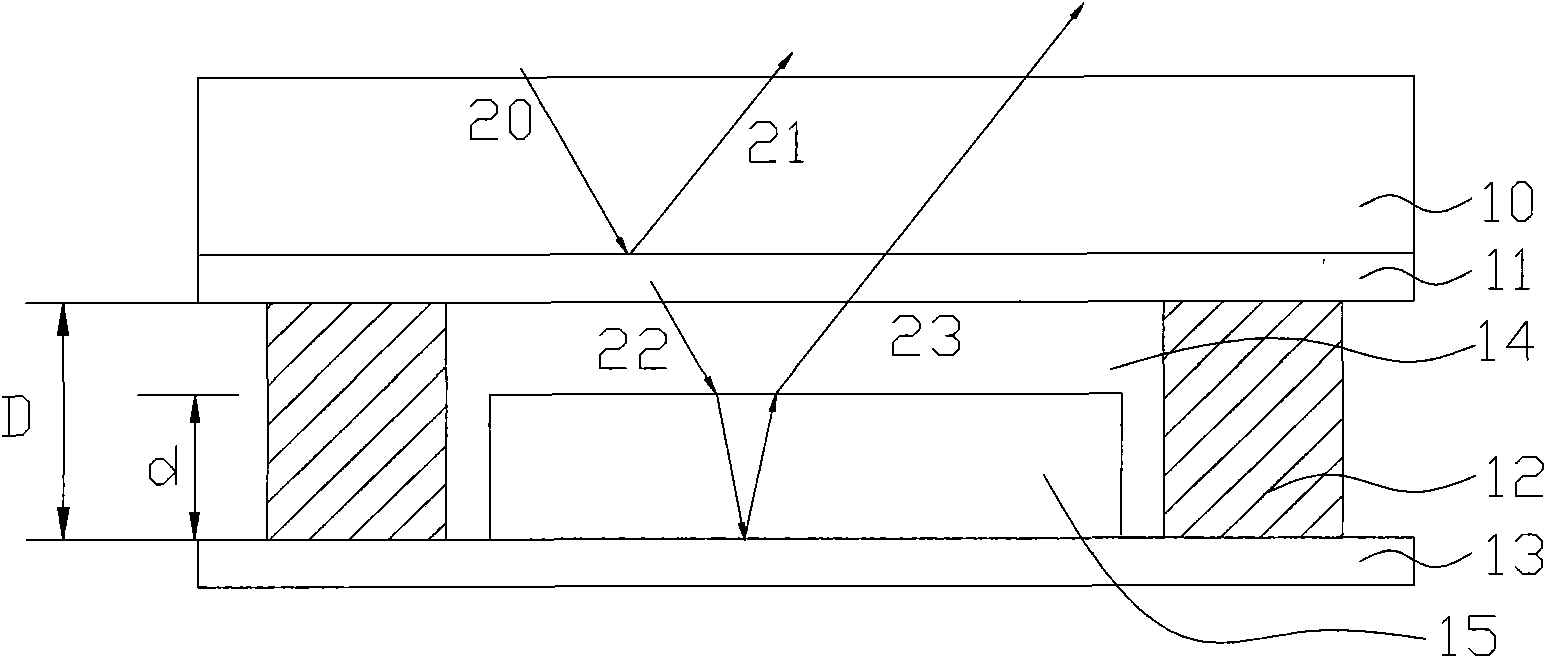

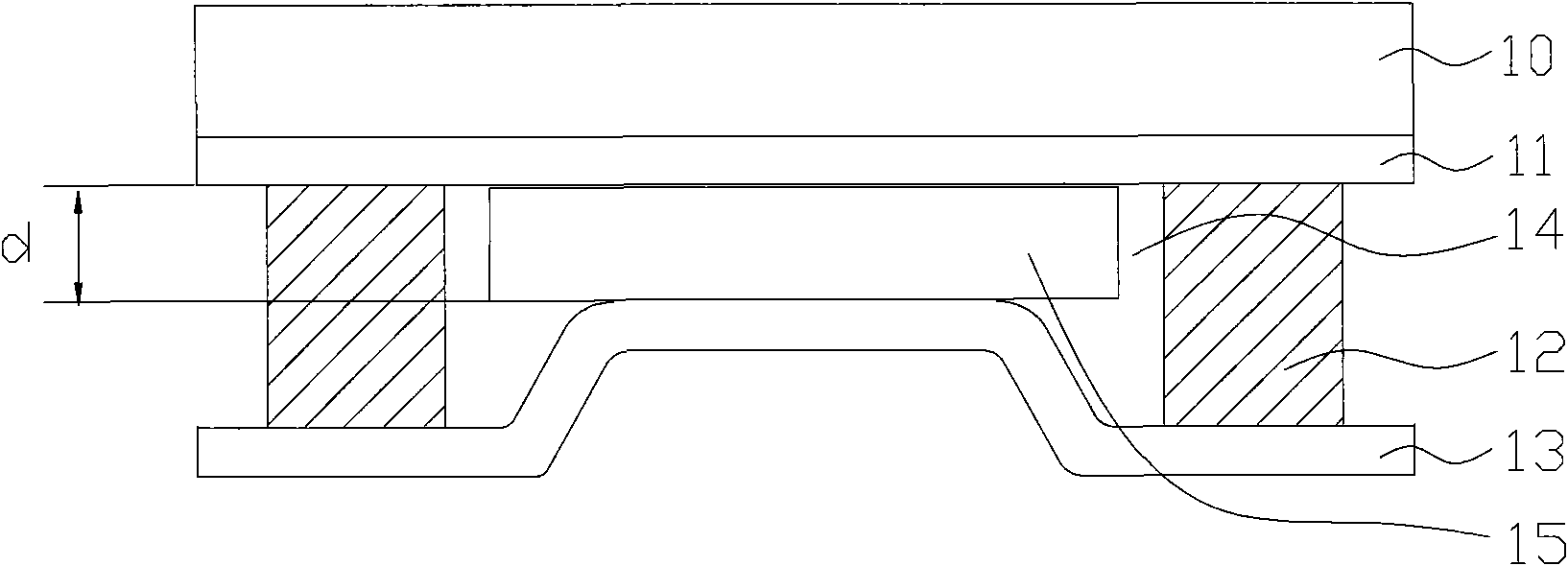

Display panel, display method, display device and color rendition method thereof

InactiveCN101872579AChange widthControl wavelengthStatic indicating devicesIdentification meansDisplay deviceTransmittance

The invention provides a display panel, which comprises a base plate. The base plate has a first reflecting layer and a second reflecting layer with specific light transmittance. The first reflecting layer comprises a reflecting unit array. Each reflecting unit comprises a reflecting plate which can continuously move along a direction perpendicular to the first reflecting layer, and a supporting beam connected with the reflecting plate and a connecting part. The invention additionally provides a display method, a display device and a color rendition method thereof. The display panel synthesizes color through time sequence color without distinguishing pixel color, the manufacturing process is only one third of the manufacturing process of a traditional display panel manufacturing method, the structure is simple and the manufacturing cost is low. The display device can compensate color drift caused by manufacturing error, the task of accurately realizing color rendition is transferred to the peripheral circuit of the display panel from the manufacturing process, and thereby the requirement on the precision of the manufacturing process is reduced.

Owner:季中

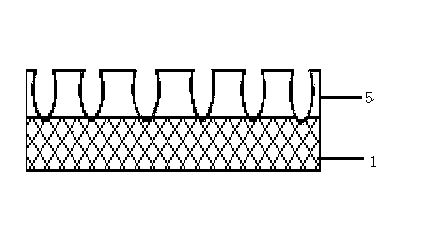

GaN base LED transparent electrode graphical preparation method

InactiveCN103633196AReduce Lithography Cost and Time ConsumptionReduce the harm to the human bodySemiconductor devicesPhysicsSingle layer graphene

The invention provides a GaN base LED transparent electrode graphical preparation method; the method comprises the steps of: vapor plating an ITO, ZnO or single layer graphene transparent electrode on a GaN base epitaxial layer; depositing a thin SiO2 layer on the transparent electrode; employing a crystallization graph formed by annealing of the SiO2 under different temperatures to serve as a mask layer; employing dry etching to etch exposed transparent electrode; using HF solution to remove the SiO2 crystallization graph so as to obtain a graphical transparent electrode. The method not only employs the graphical transparent electrode to improve light extraction efficiency in preparation, but also reduces cost and work time of a conventional lithography mask layer technology.

Owner:DALIAN MEIMING EPITAXIAL WAFER TECH

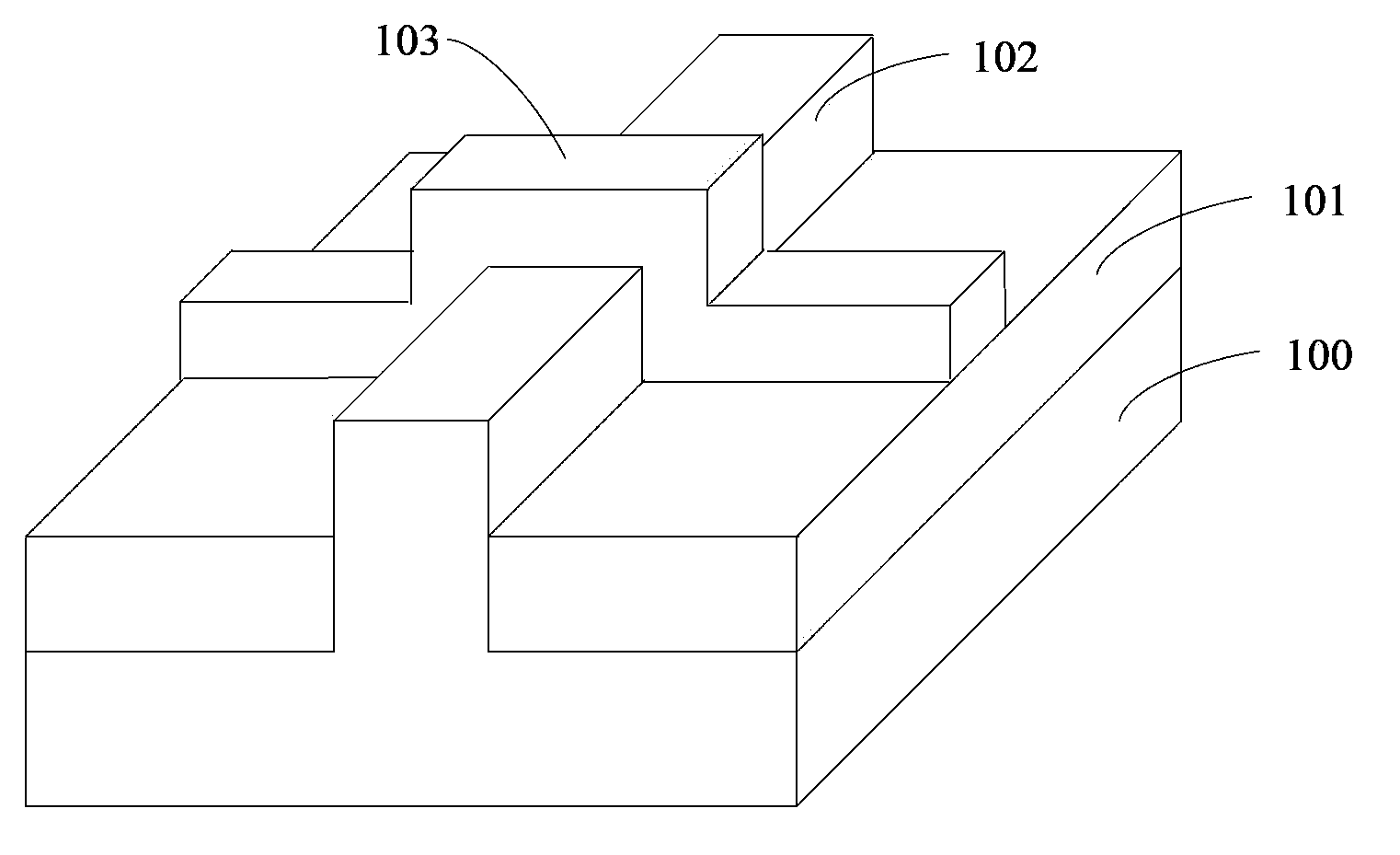

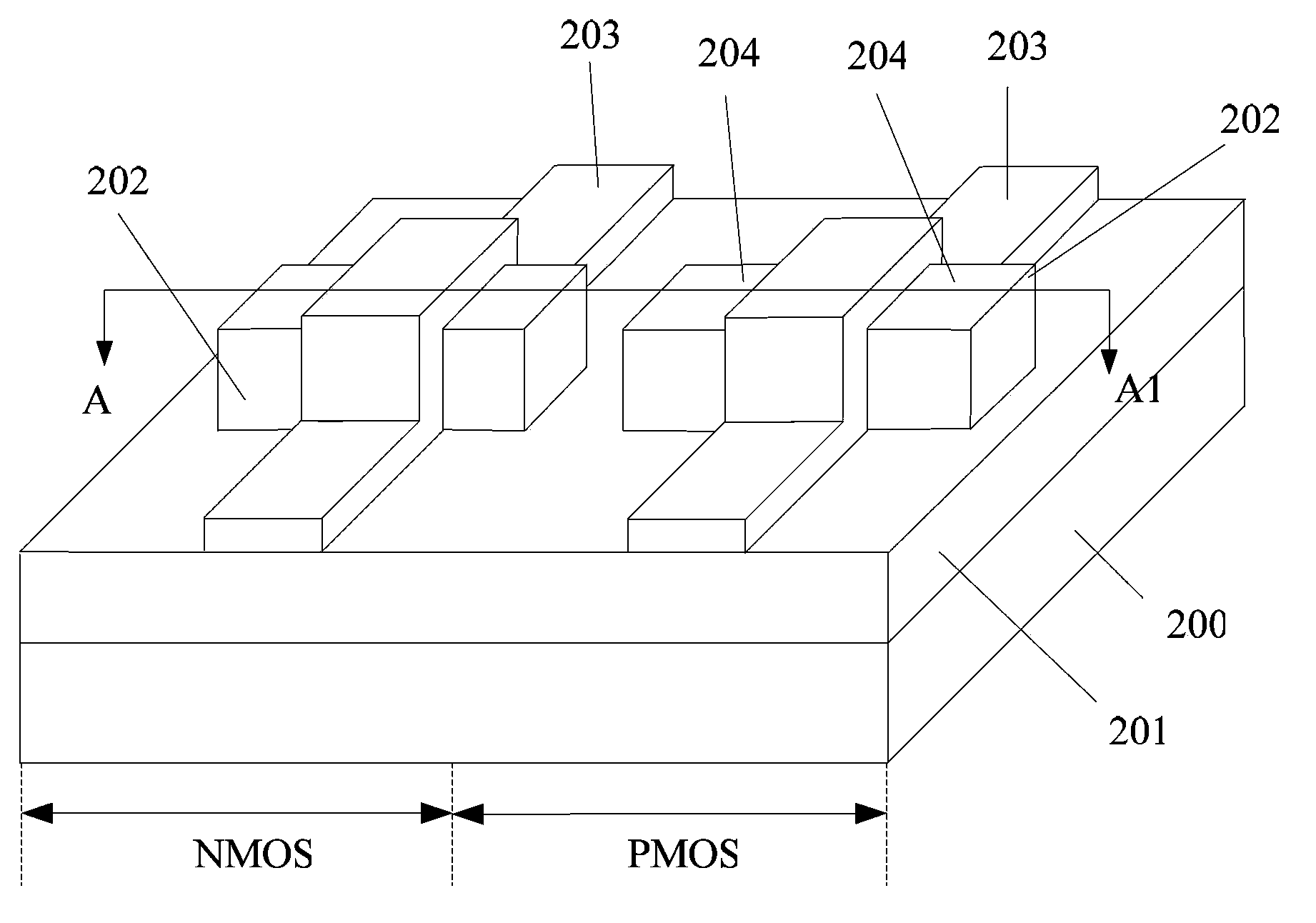

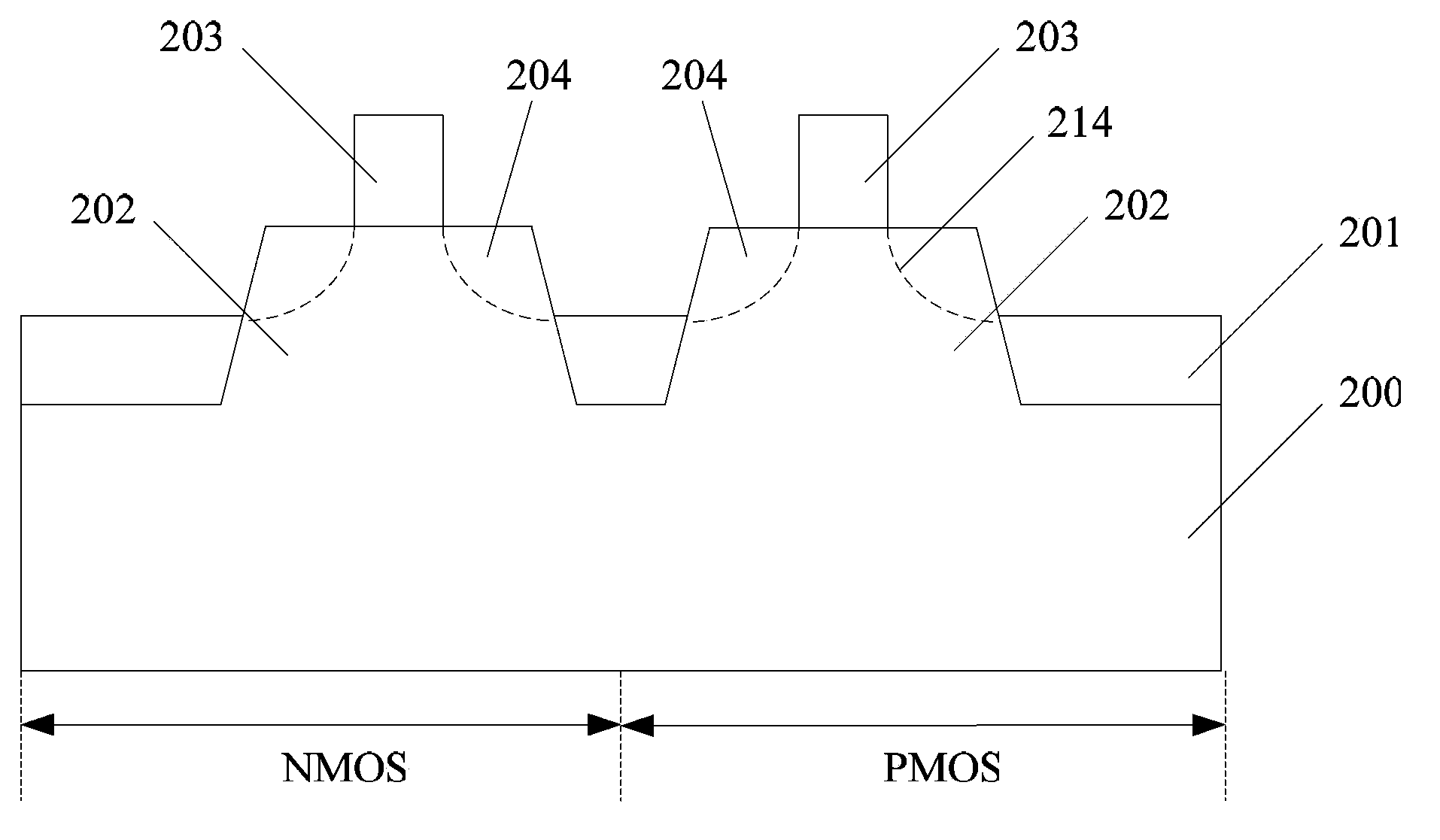

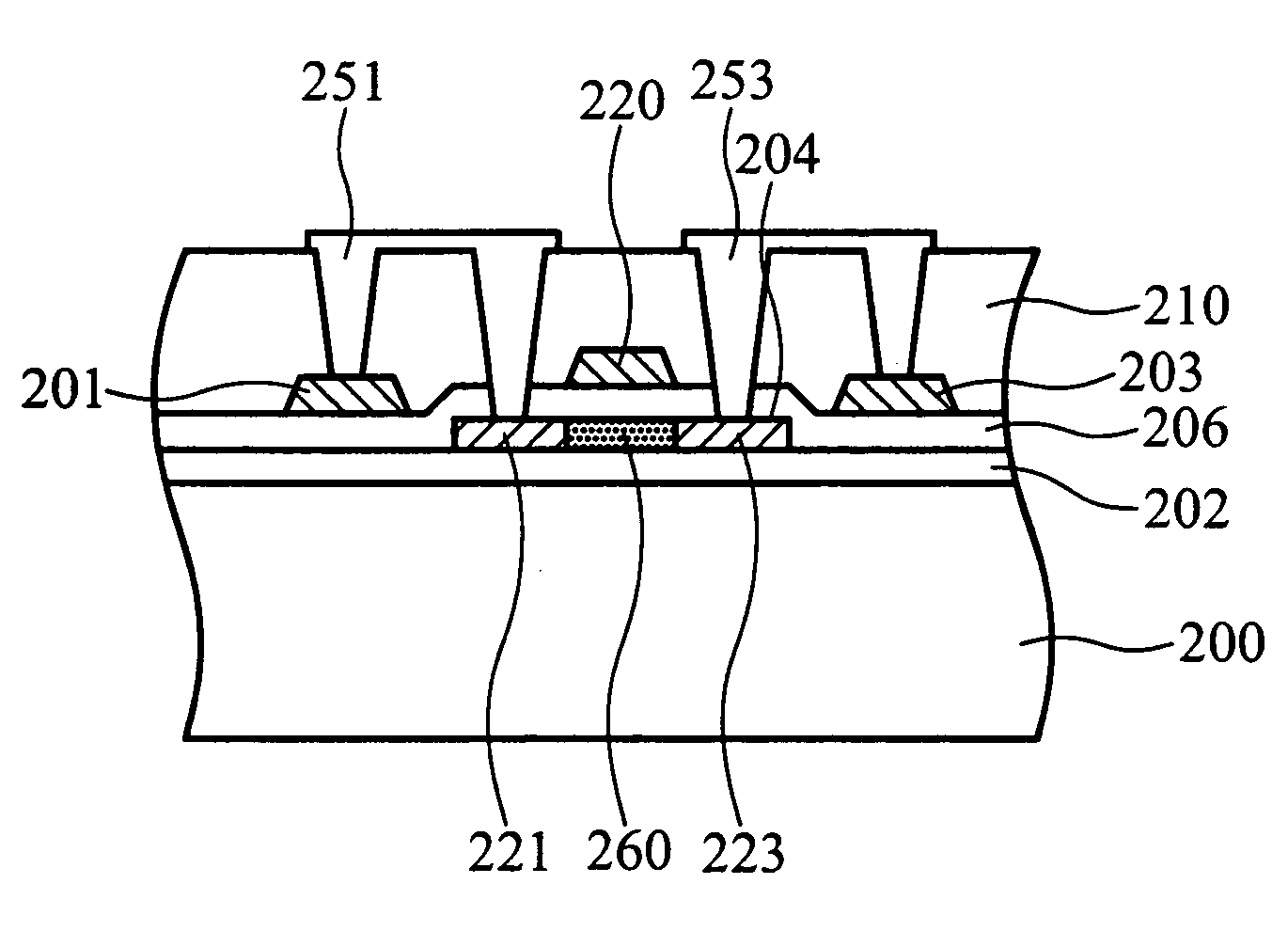

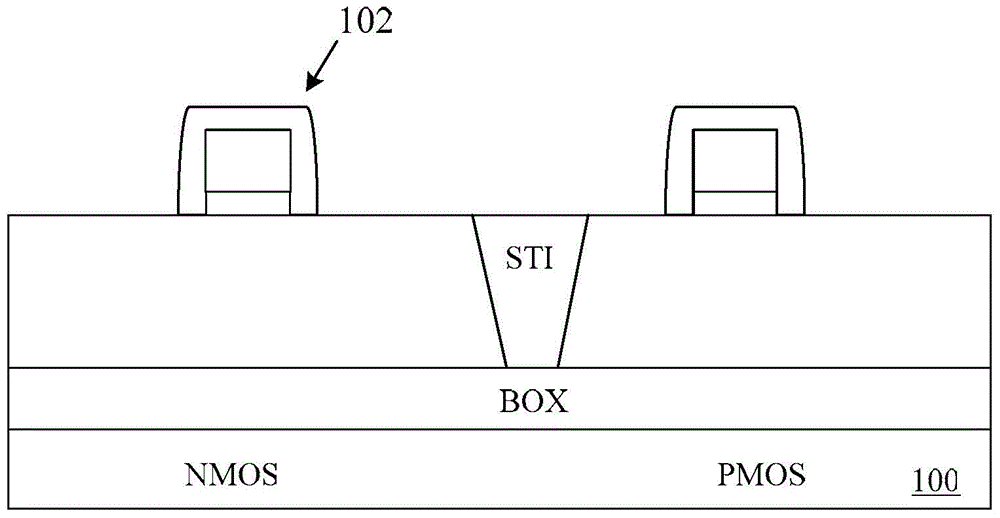

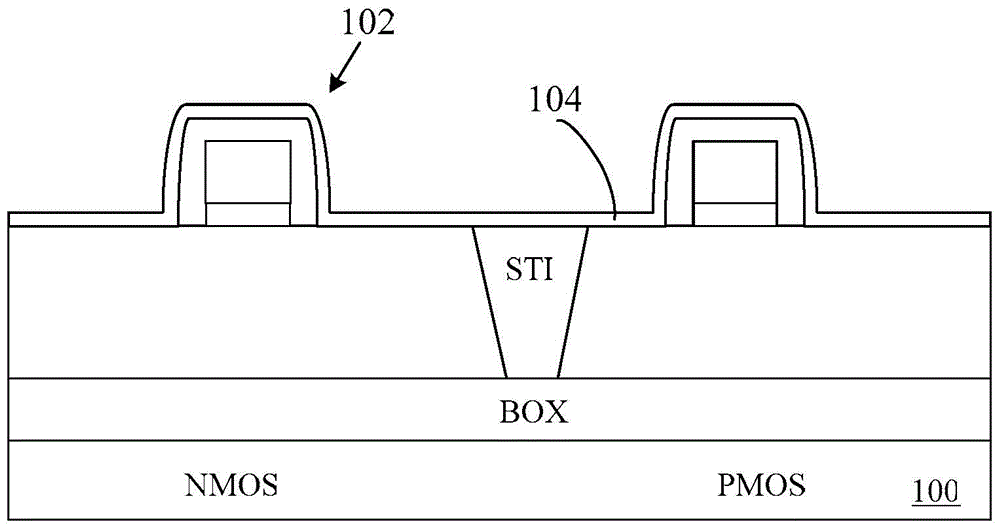

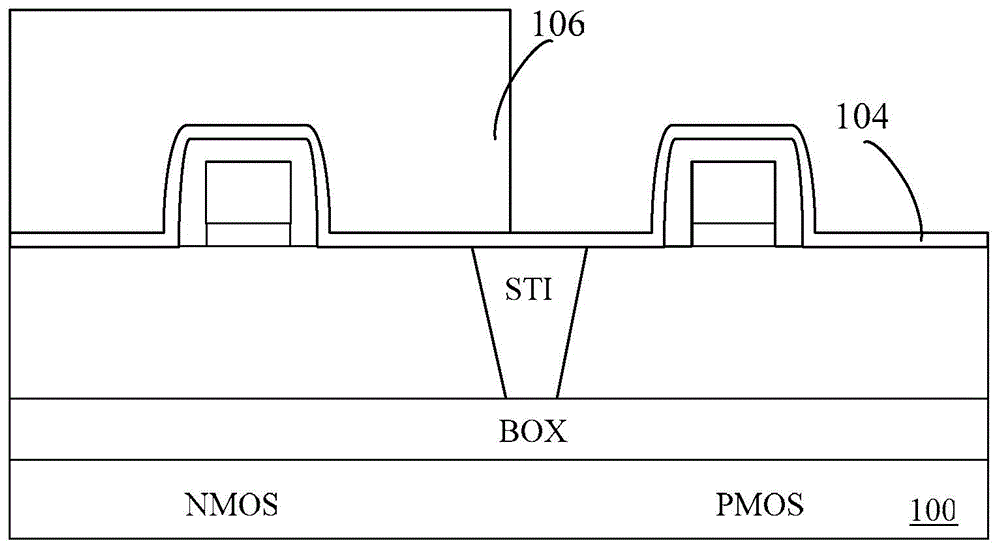

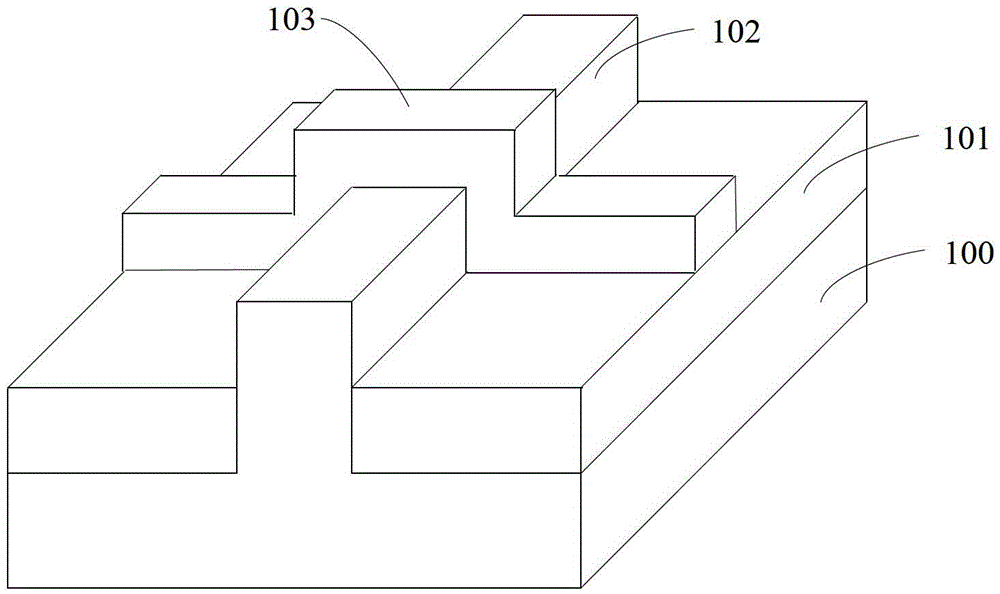

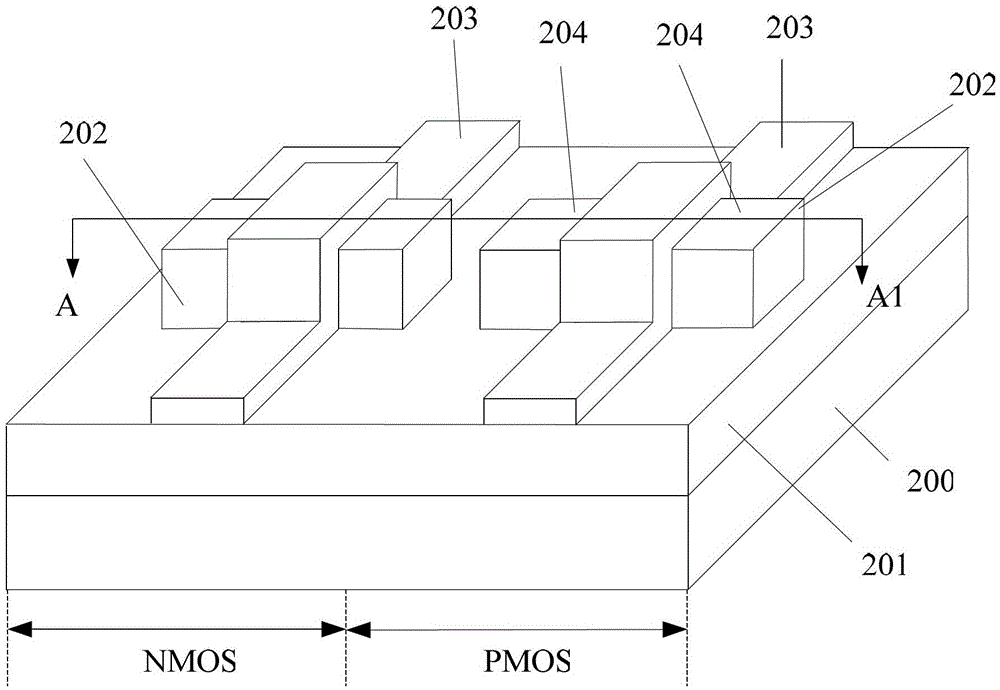

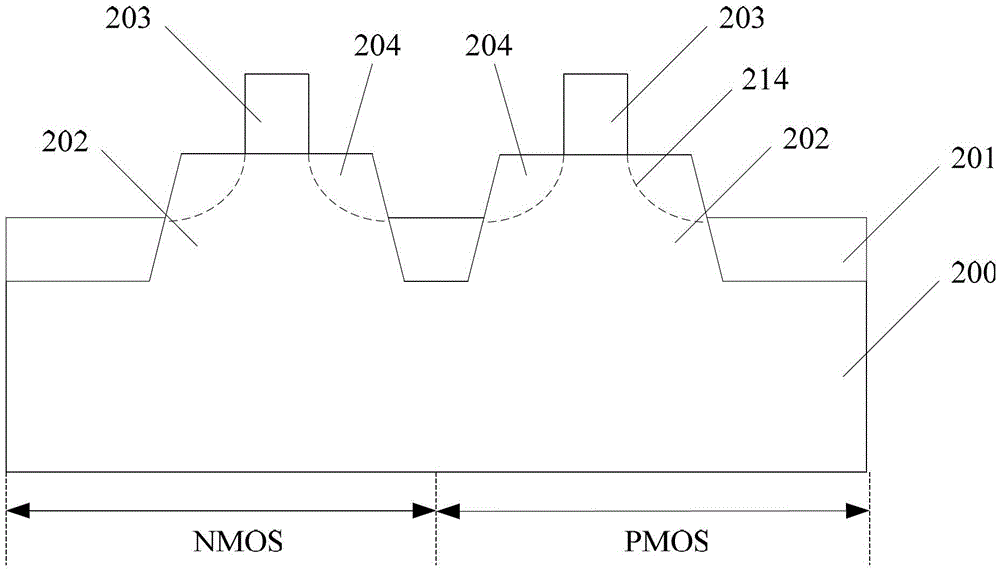

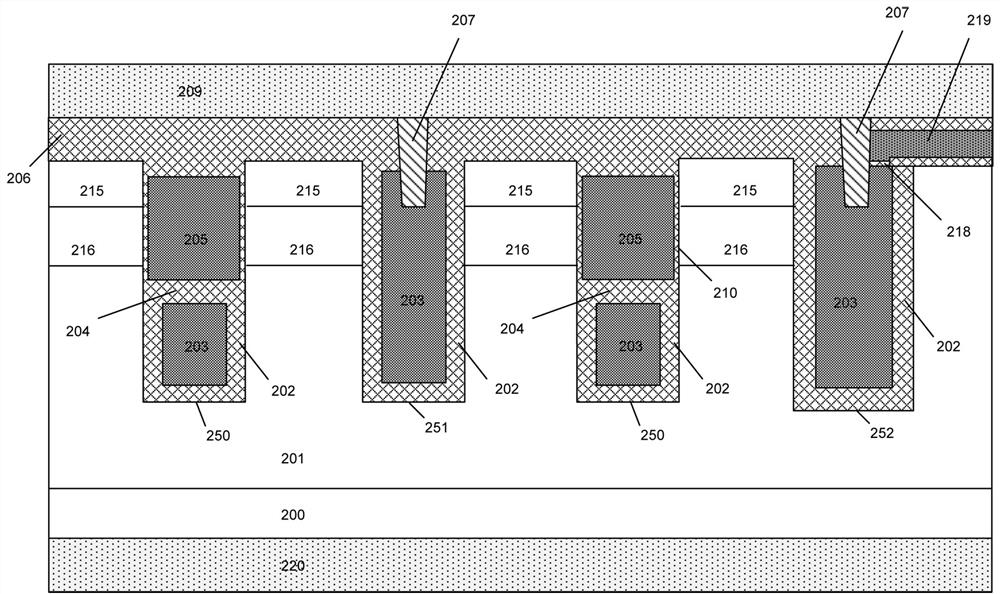

Forming method of CMOS transistor

ActiveCN103855096AReduce photolithography stepsImprove performanceSemiconductor/solid-state device manufacturingBlock layerCMOS

A forming method of a CMOS transistor comprises the steps that a semiconductor substrate is provided, and the semiconductor substrate comprises an NMOS area and a PMOS area; pre-decrystallization injection is conducted on the source region and the drain region of the NMOS area and the source region and the drain region of the PMOS area; the source region and the drain region of the NMOS area and the source region and the drain region of the PMOS area are etched to form a first opening, the depth of the first opening is smaller than the depth of pre-decrystallization injection, and an embedded source region and an embedded drain region of an NMOS are formed in the first opening; a blocking layer is formed, and the blocking layer is provided with a second opening exposing the PMOS area; the source region and the drain region of the PMOS area are etched along the second opening, the embedded source region and the embedded drain region of the NMOS and the pre-decrystallization injection area of the PMOS area are removed to form a third opening, and an embedded source region and an embedded drain region of the PMOS are formed in the third opening. The forming method of the CMOS transistor is simple in process.

Owner:SEMICON MFG INT (SHANGHAI) CORP

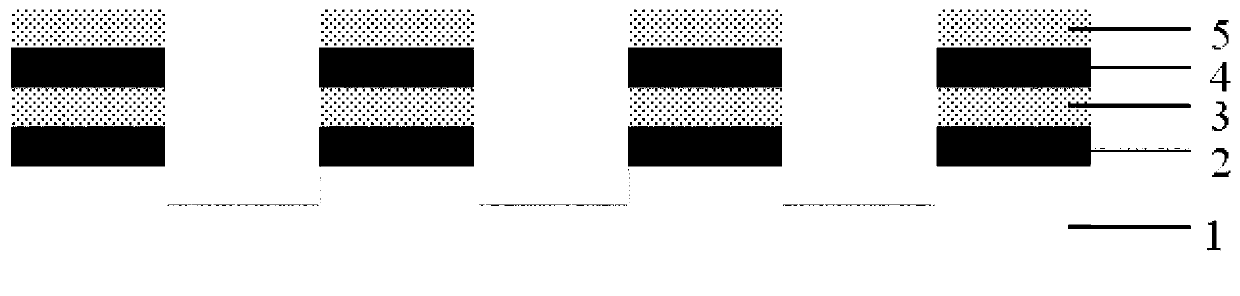

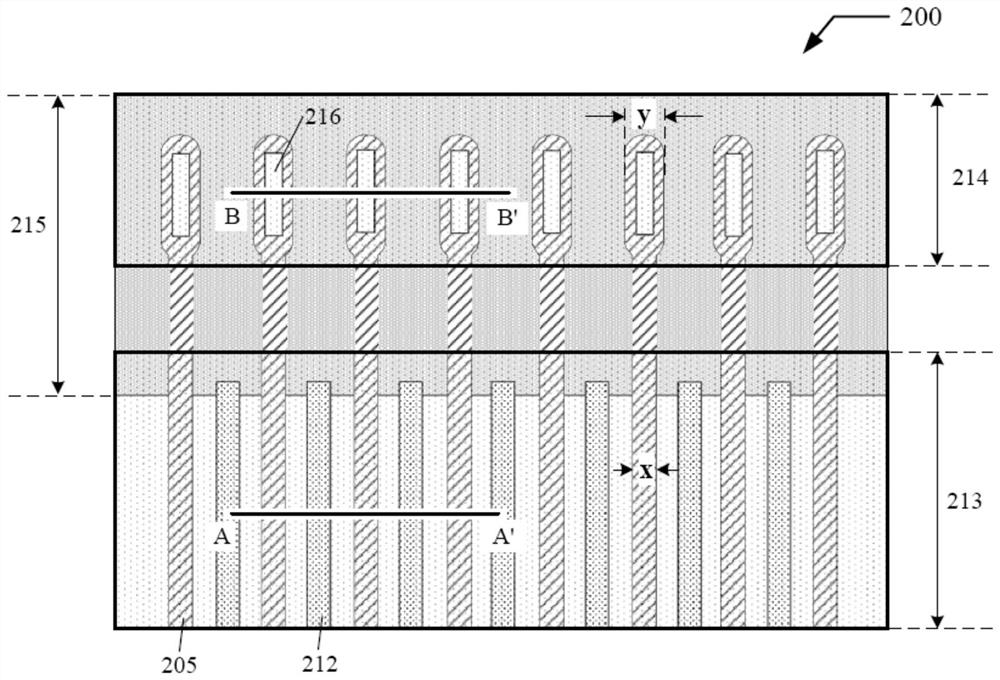

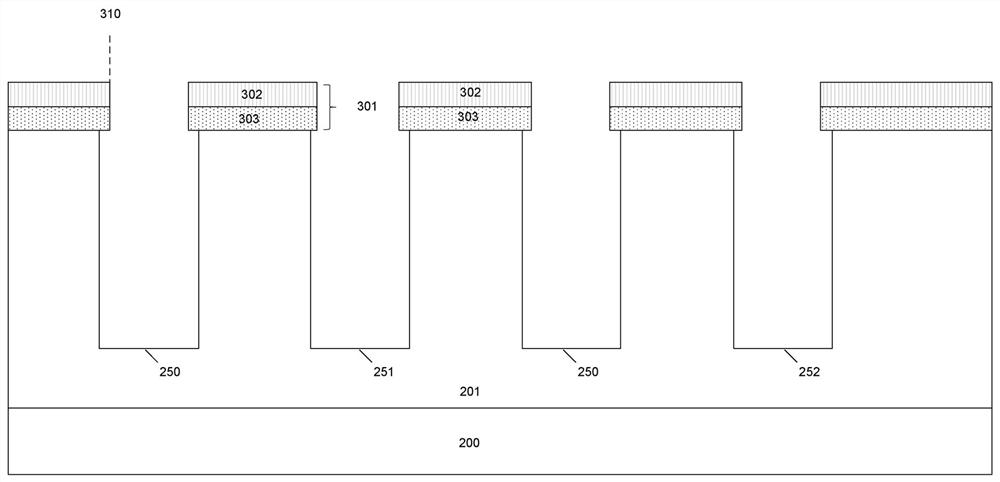

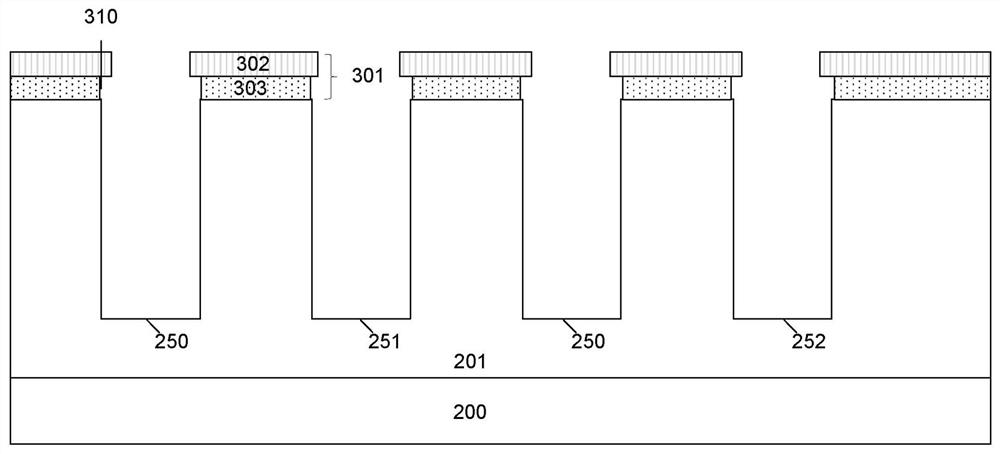

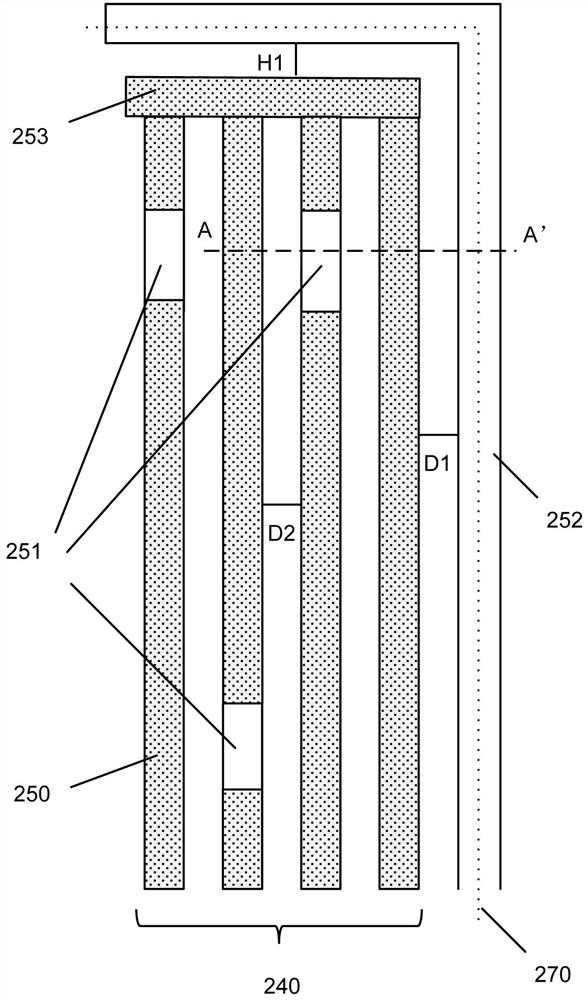

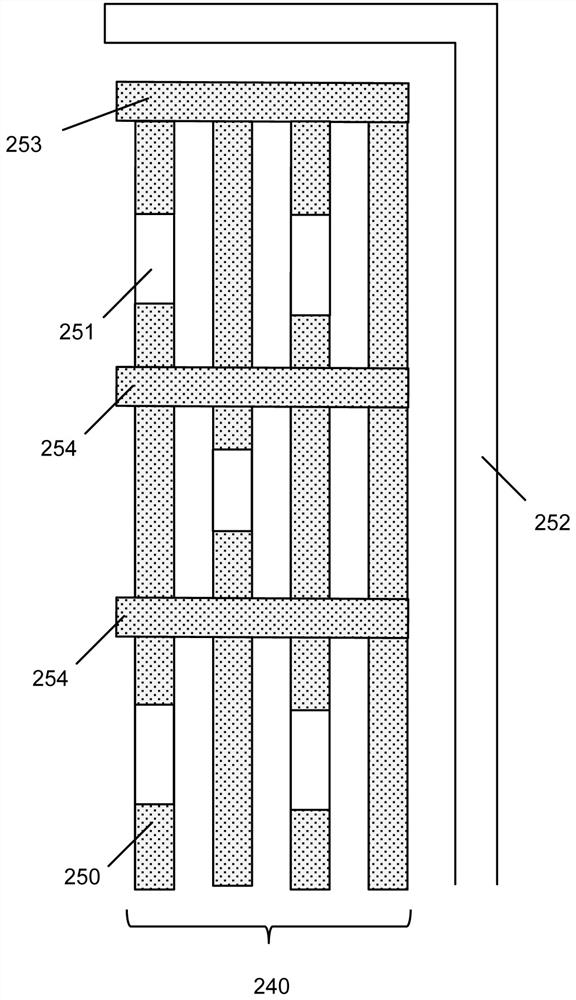

Three-dimensional stacked phase change memory and preparation method thereof

ActiveCN110707209AIncrease processing costReduce demandSolid-state devicesSemiconductor devicesPhase-change memoryPhysical chemistry

The invention belongs to the technical field of microelectronic devices and memories, and discloses a three-dimensional stacked phase change memory and a preparation method thereof. The preparation method specifically comprises the following steps of preparing a multi-layer structure on which a horizontal electrode layer and an insulating layer are crossly stacked, on a substrate; then etching toform a groove and a discrete three-dimensional strip-shaped electrode; filling an insulating medium in the groove, forming small holes in the boundary area of the three-dimensional strip-shaped electrode and the insulating medium, sequentially depositing a phase change material on the walls of the small holes, and filling an electrode material in the small holes to prepare a vertical electrode, thereby obtaining the multi-layer stacked three-dimensional stacked phase change memory. According to the present invention, by improving the whole flow process of the preparation method, a three-dimensional phase change memory array can be established by utilizing the vertical electrode structure, and compared with the prior art, the problems of complex multi-layer stacking steps, high process implementation difficulty, unit size miniaturization and the like of an existing three-dimensional stacked phase change memory in process preparation, can be effectively solved.

Owner:HUAZHONG UNIV OF SCI & TECH

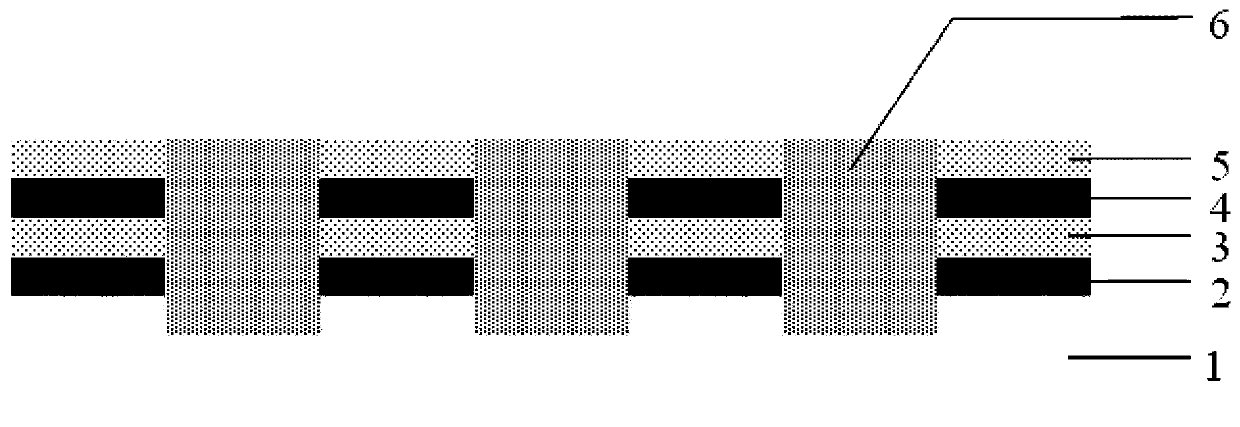

Semiconductor laser and manufacturing method thereof

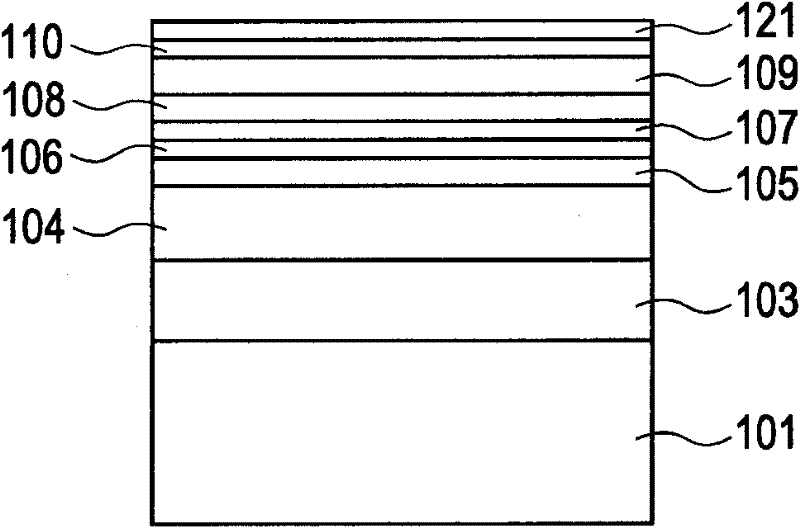

InactiveCN102237634AReduce strainLarge band gap when strainedOptical wave guidanceLaser detailsSemiconductor packageNitride semiconductors

The invention provides a semiconductor laser and a manufacturing method thereof. The semiconductor laser includes a semiconductor substrate and a resonator formed over the semiconductor substrate and containing a nitride semiconductor layer. A strain exerting on a region near the facet of the resonator is smaller than a strain exerting on the region between the regions near the facet.

Owner:RENESAS ELECTRONICS CORP

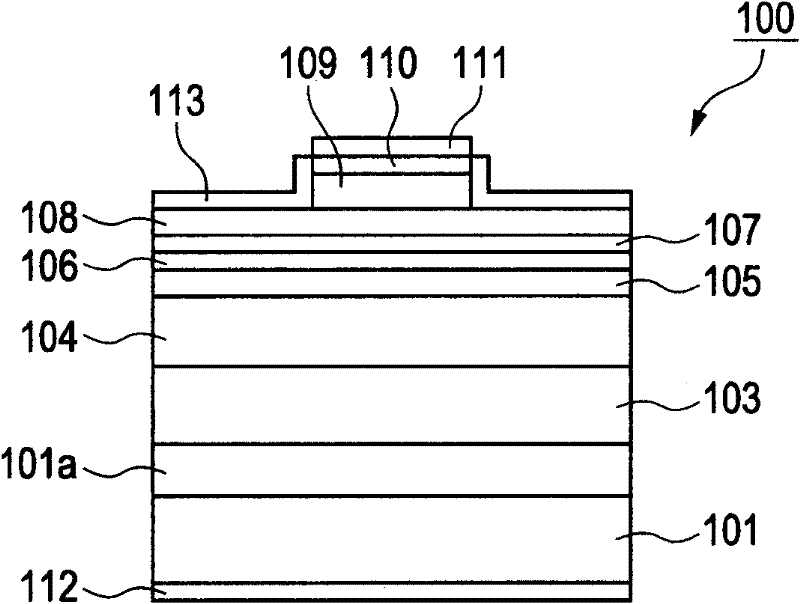

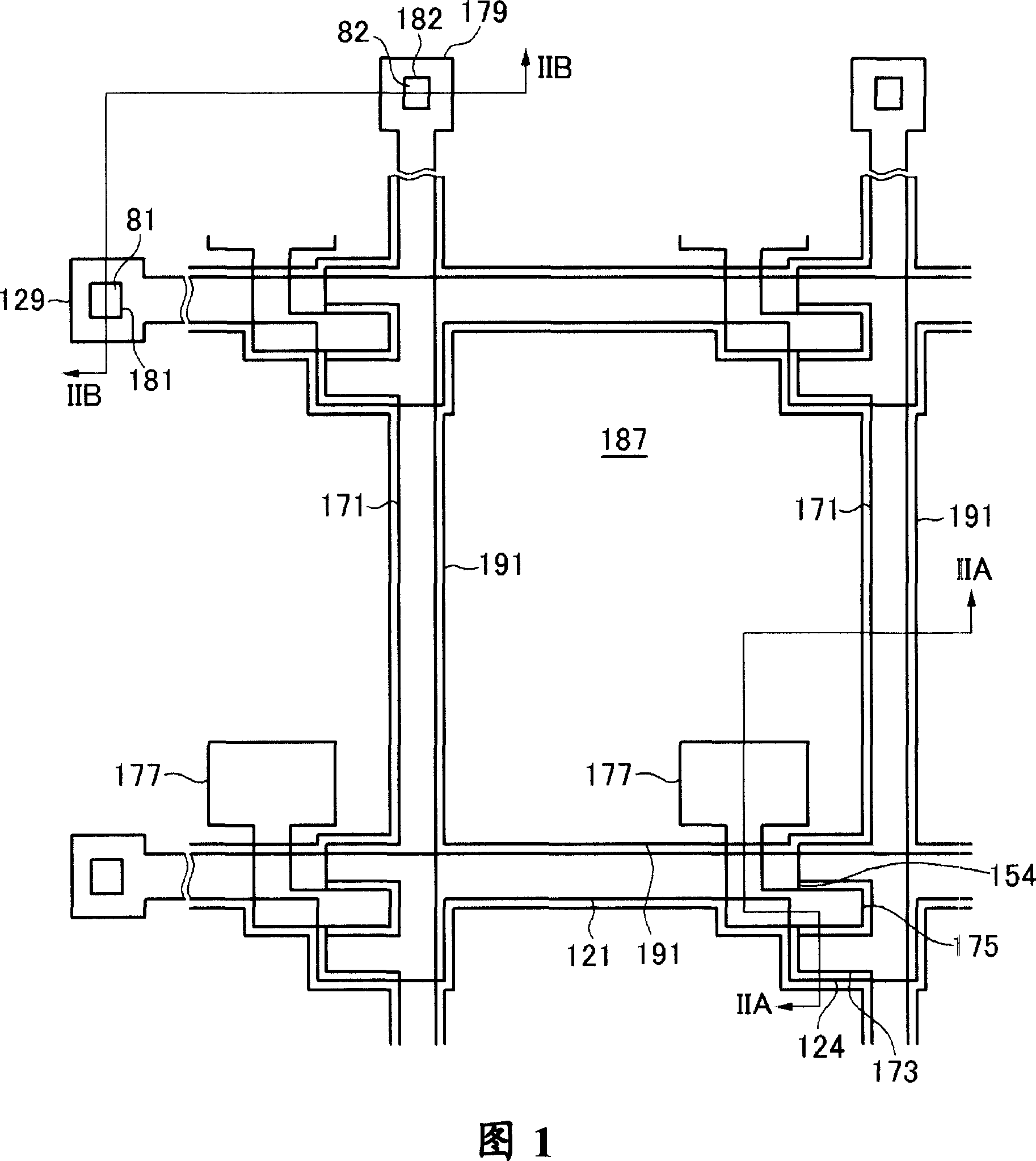

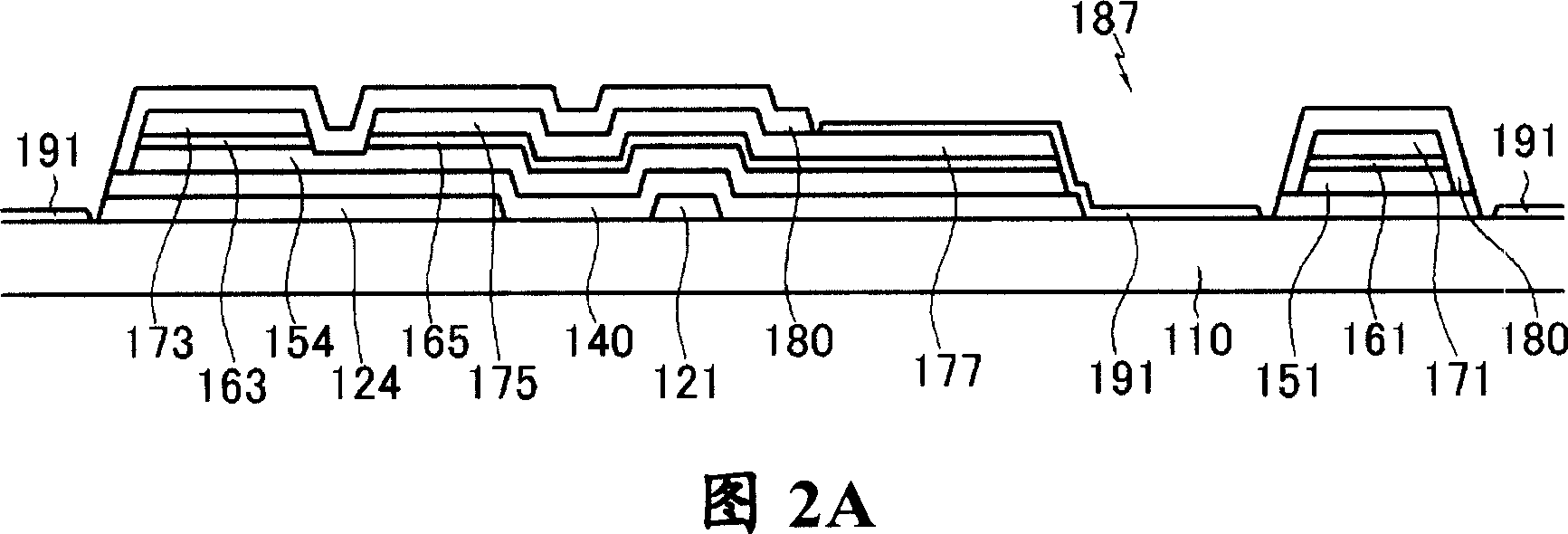

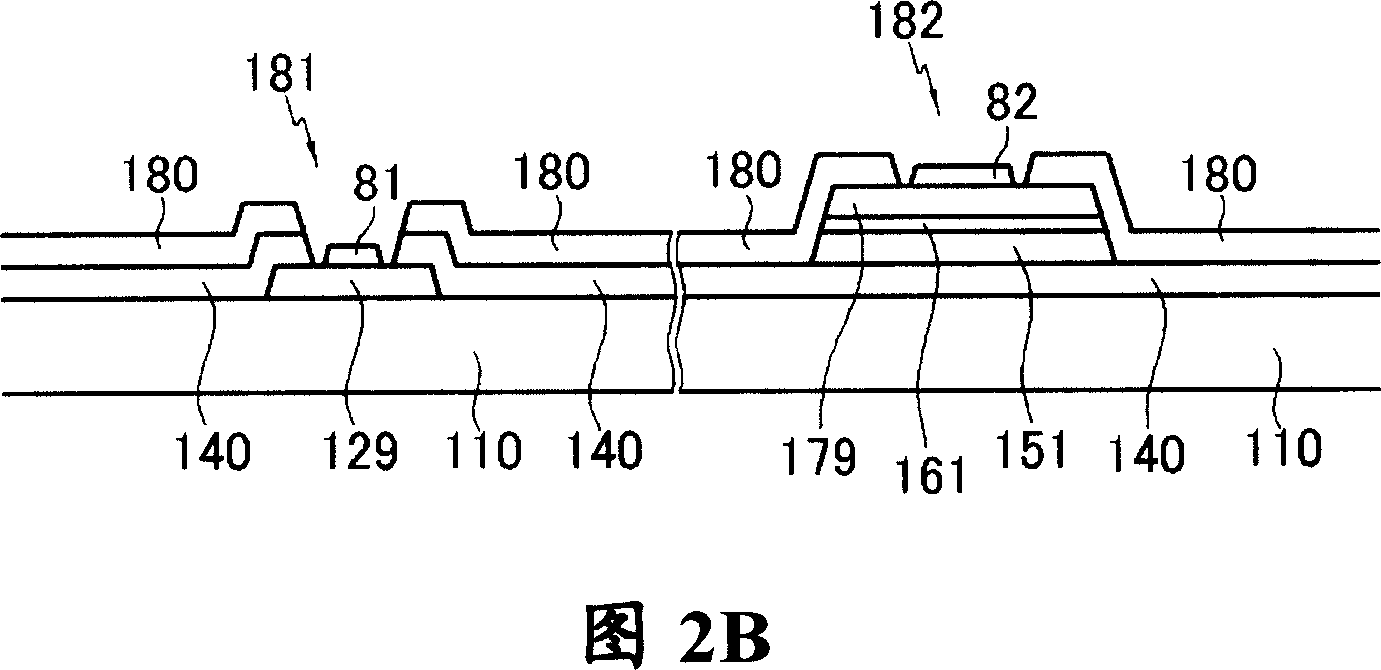

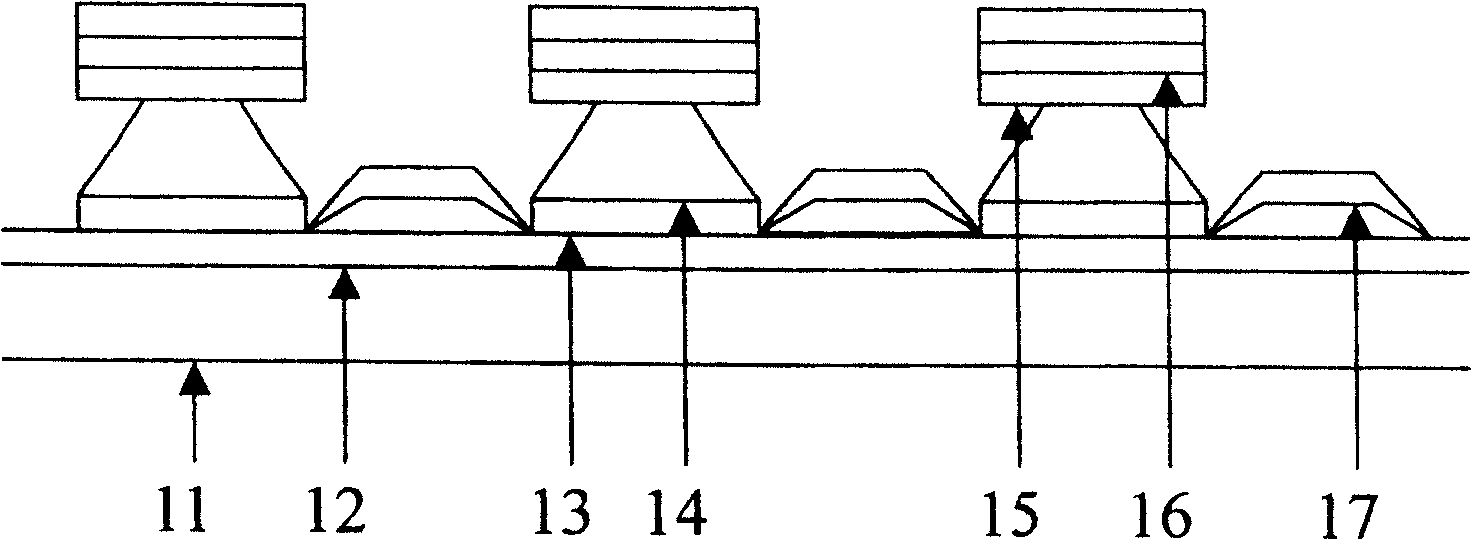

Manufacturing method of thin film transistor array panel

InactiveCN1945813AReduce photolithography stepsReduce manufacturing costsSolid-state devicesSemiconductor/solid-state device manufacturingOhmic contactSelective deposition

The present invention relates to a manufacturing method of a thin film transistor array panel. The method includes forming a gate line including a gate electrode on a substrate, forming a first insulating layer on the gate line, forming a semiconductor layer on the first insulating layer, forming an ohmic contact on the semiconductor layer, forming a data line including a source electrode and a drain electrode on the ohmic contact, depositing a second insulating layer, forming a first photoresist on the second insulating layer, etching the second insulating layer and the first insulating layer using the first photoresist as an etching mask to expose a portion of the drain electrode and a portion of the substrate, forming a pixel electrode connected to an exposed portion of the drain electrode using selective deposition, and removing the first photoresist.

Owner:SAMSUNG ELECTRONICS CO LTD

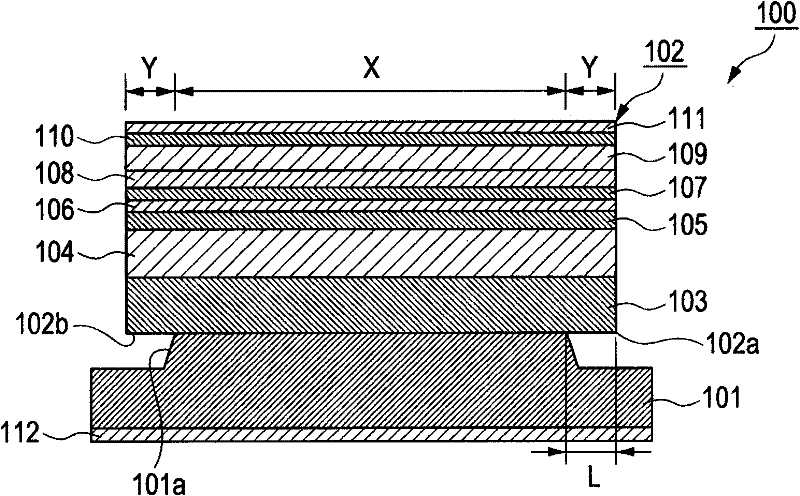

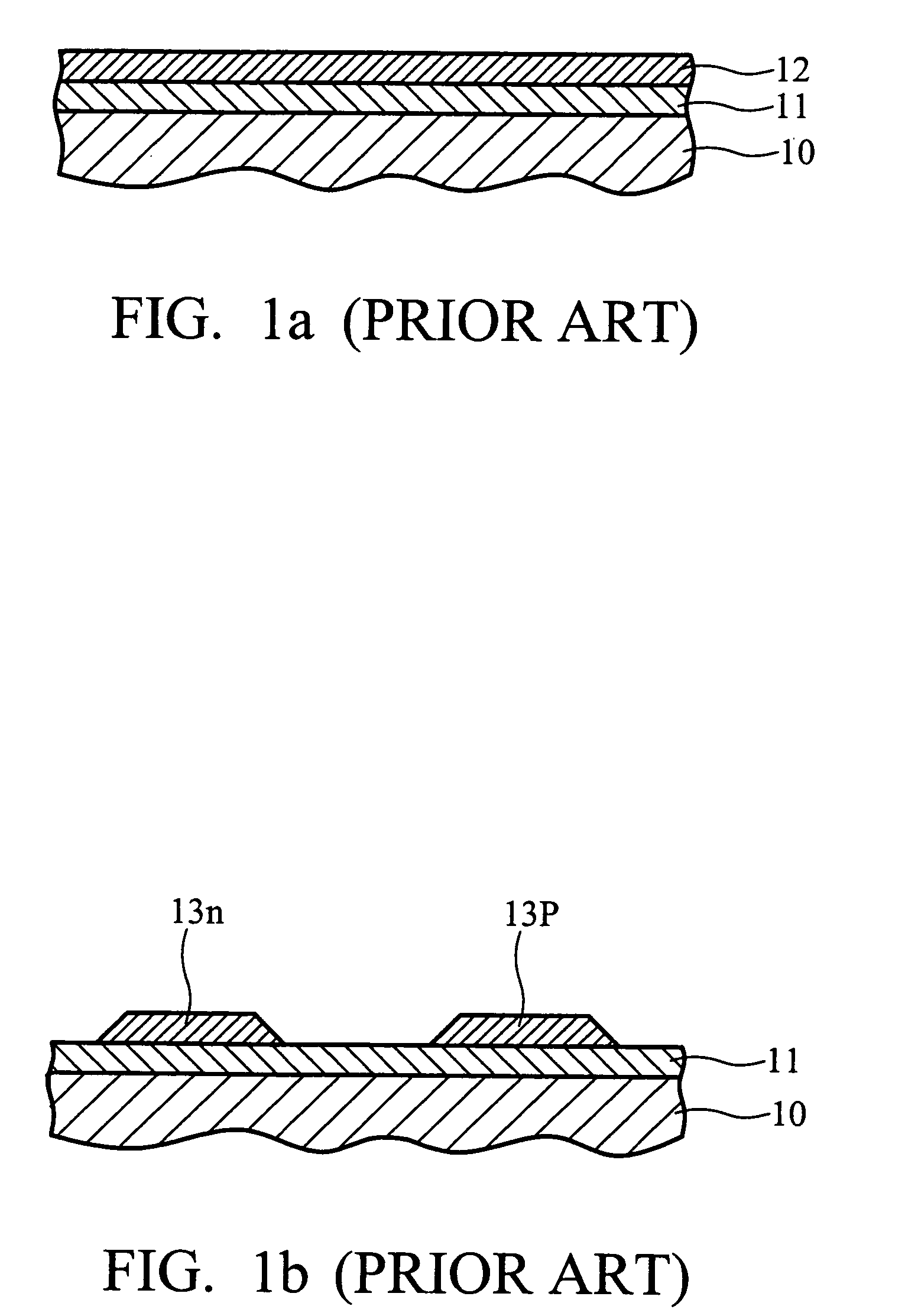

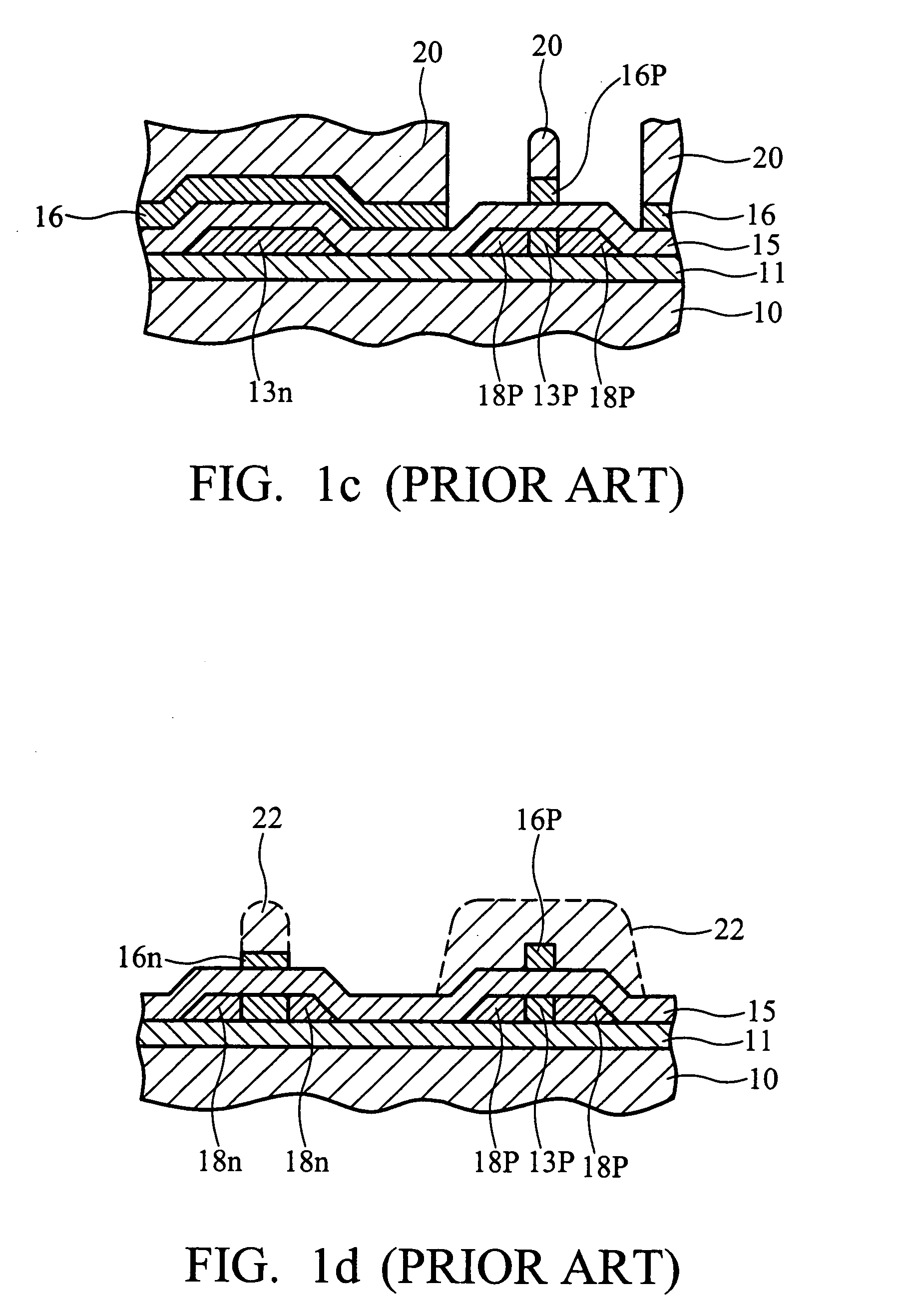

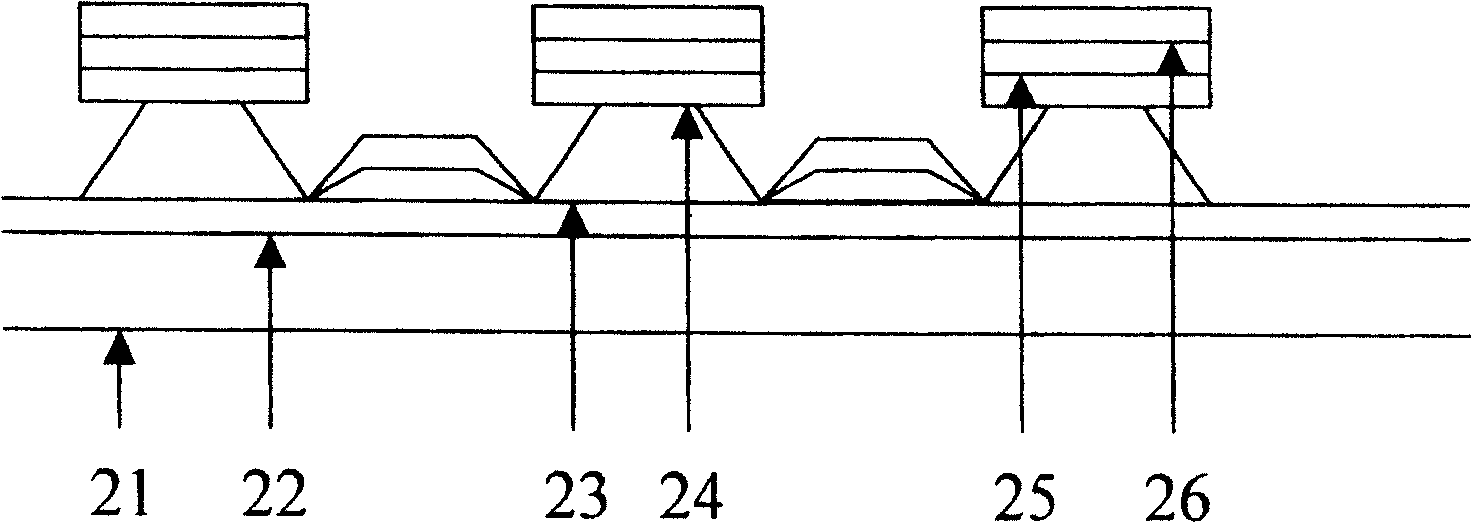

Thin film transistor and fabrication method for same

InactiveUS20050059227A1Reduce photolithography stepsAvoid alignmentTransistorSolid-state devicesDielectric layerSemiconductor

A thin film transistor and a method for fabricating the same. The thin film transistor comprises a substrate and a patterned semiconductive layer formed on the substrate, wherein the semiconductive layer comprises a channel region and doped regions adjacent to the channel region. A gate insulating layer is formed on the above structure. A gate electrode is located on the gate insulating layer above the channel region. Source and drain electrodes are located on the gate insulating layer adjacent to the semiconductive layer. A dielectric layer having contact holes is formed on the above structure and a patterned conductive layer is formed on predetermined parts of the dielectric layer electrically connecting the doped regions to the source and drain electrode through the contact holes.

Owner:CHINA STAR OPTOELECTRONICS INT HK

Transistor forming method

PendingCN112635401AReduce photolithography stepsReduce processing costsSemiconductor/solid-state device manufacturingEngineeringDielectric layer

The invention relates to a transistor forming method comprising the steps: providing a substrate comprising a first area and a second area; sequentially forming a high-K dielectric layer, a first type covering layer and a first gate layer on the first area and the second area; removing the first gate layer and the first covering layer on the surface of the second area; forming a second covering layer covering the remaining first gate layer and the high-K dielectric layer and a second gate layer located on the surface of the second covering layer; carrying out planarization processing on the second gate layer and the second covering layer until the first gate layer is exposed; and simultaneously patterning the first gate layer, the first covering layer and the high-K dielectric layer which are positioned on the first area to form a first gate structure, and simultaneously patterning the second gate layer, the second covering layer and the high-K dielectric layer which are positioned on the second area to form a second gate structure. The method of the transistor can reduce the process cost.

Owner:CHANGXIN MEMORY TECH INC

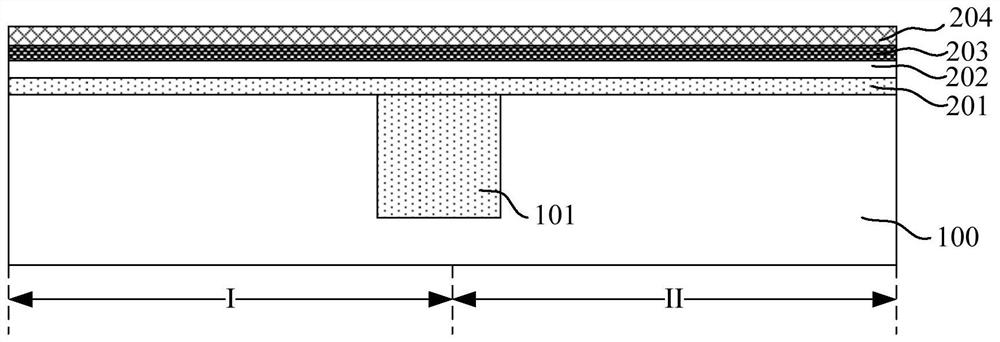

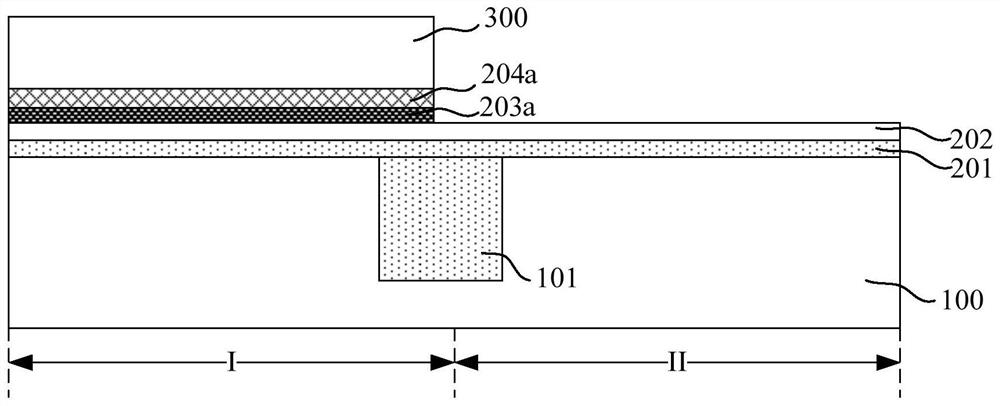

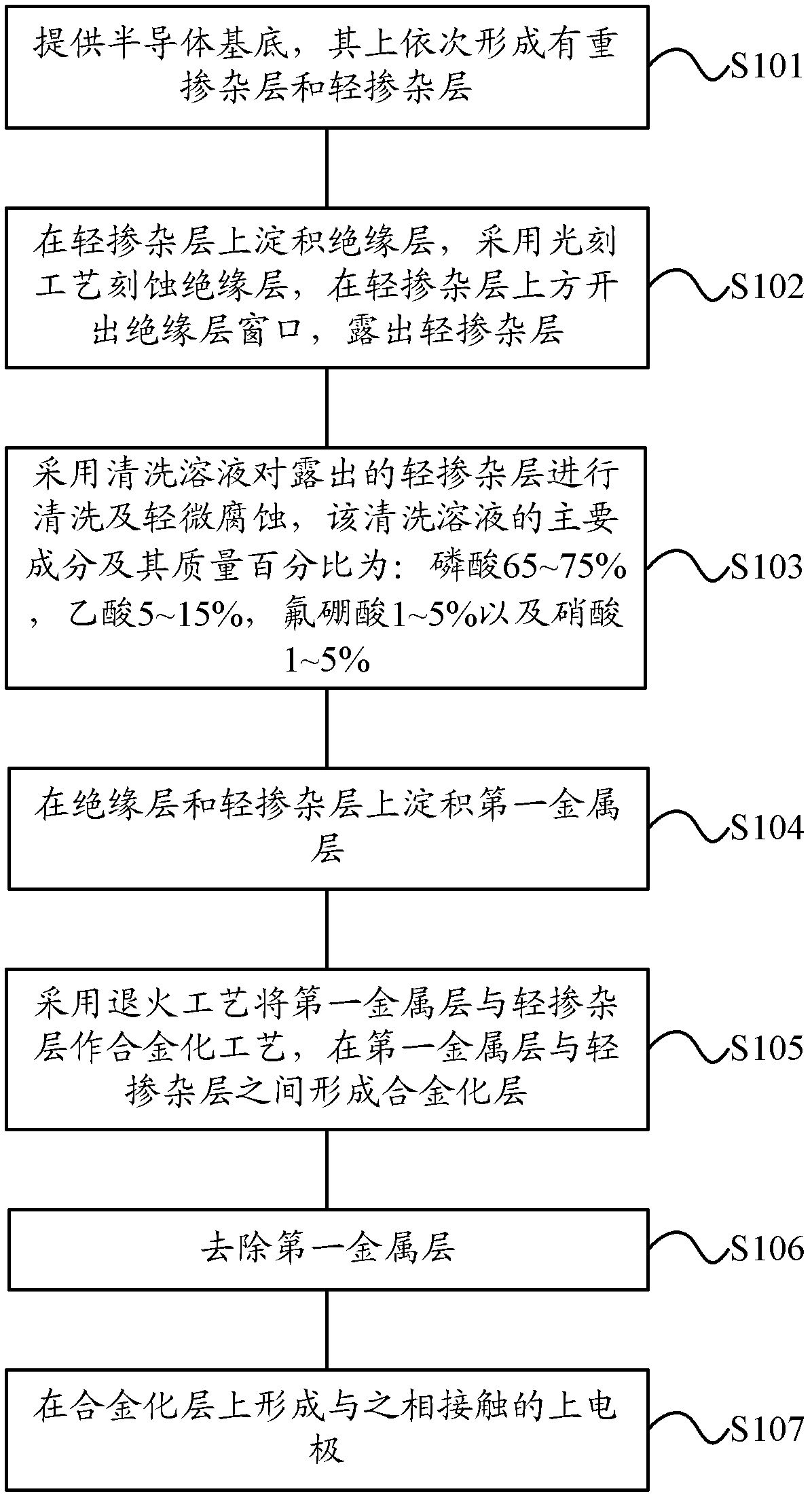

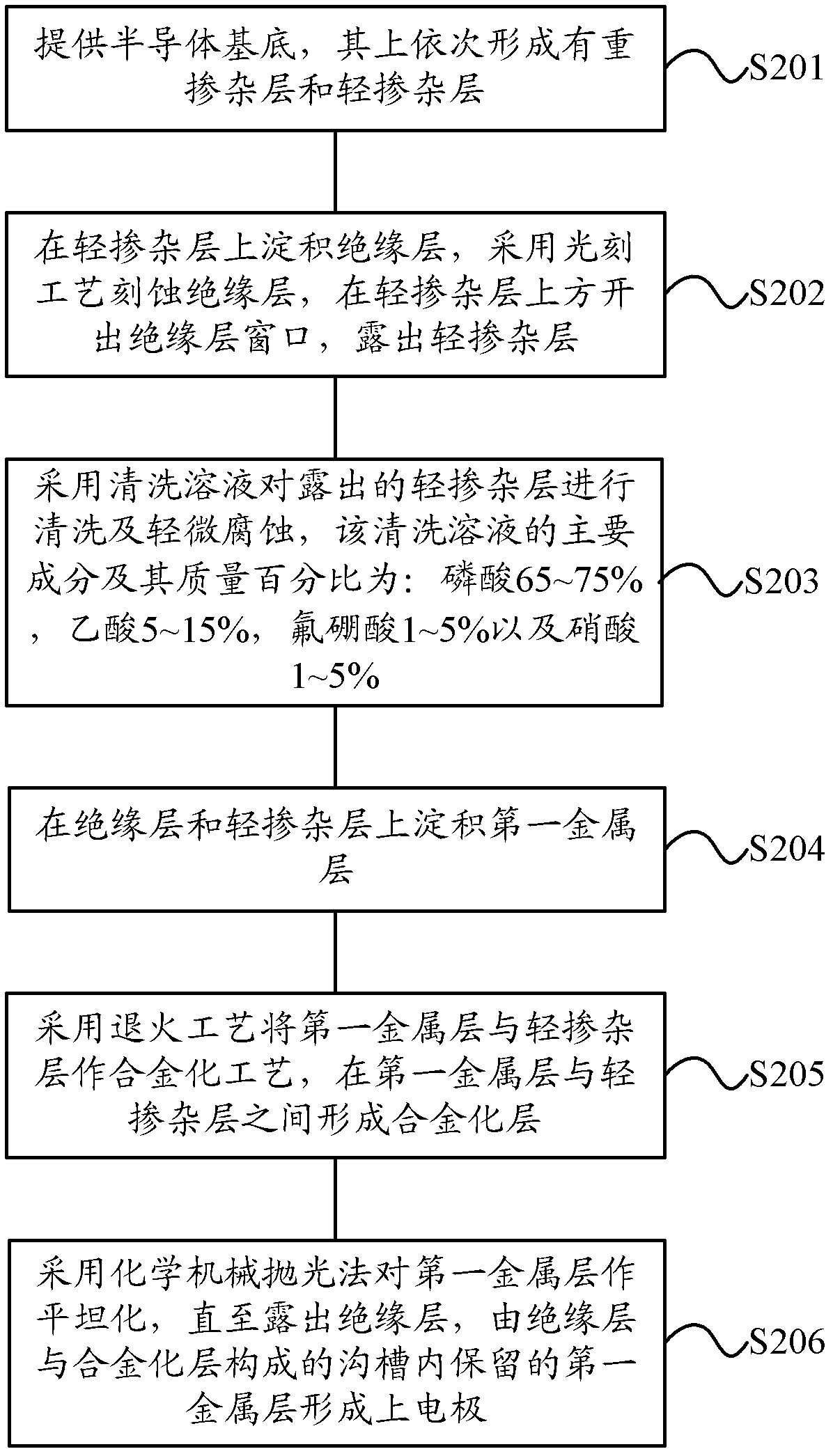

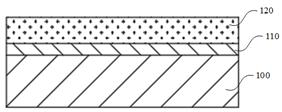

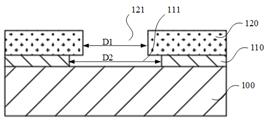

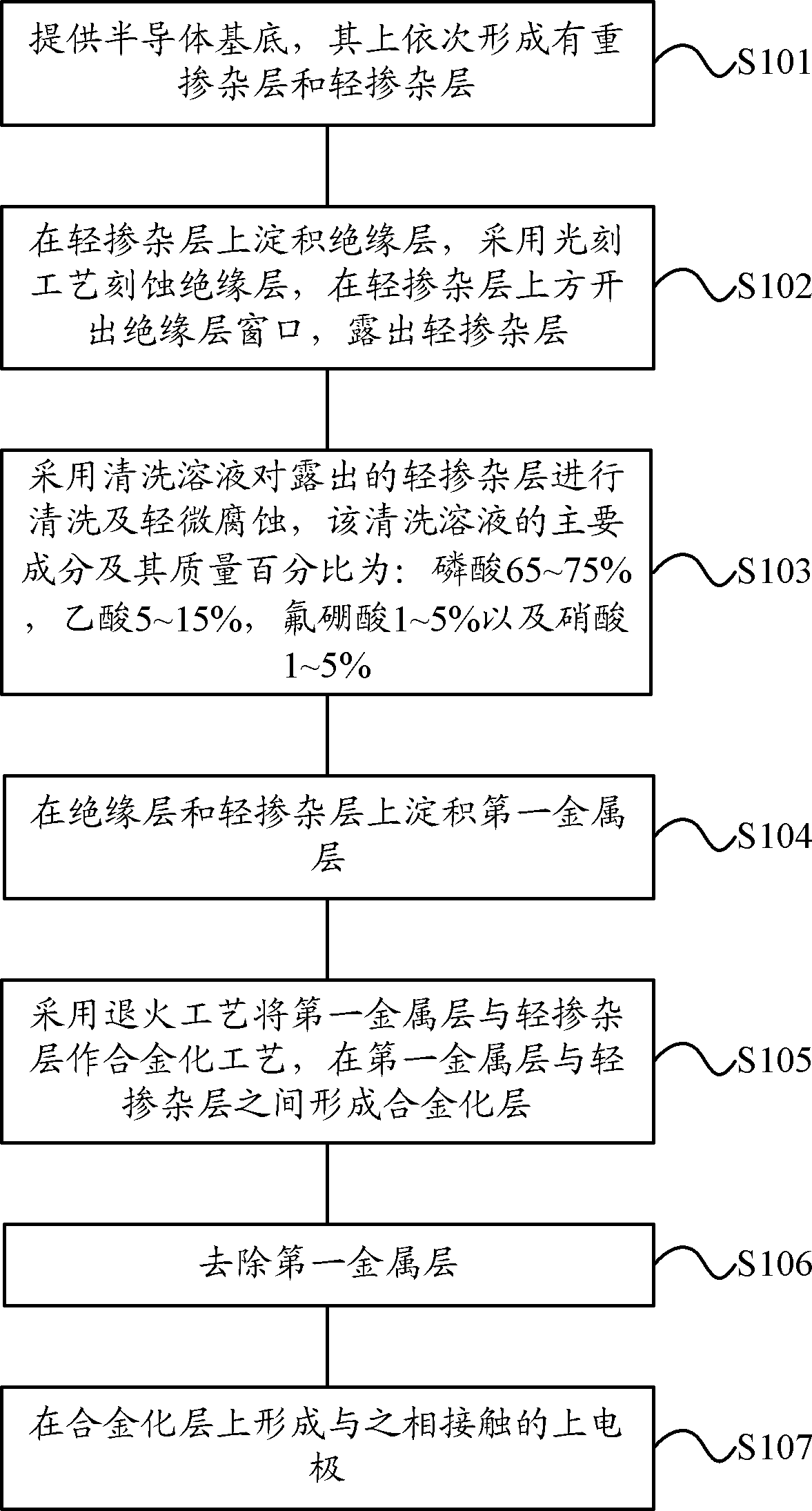

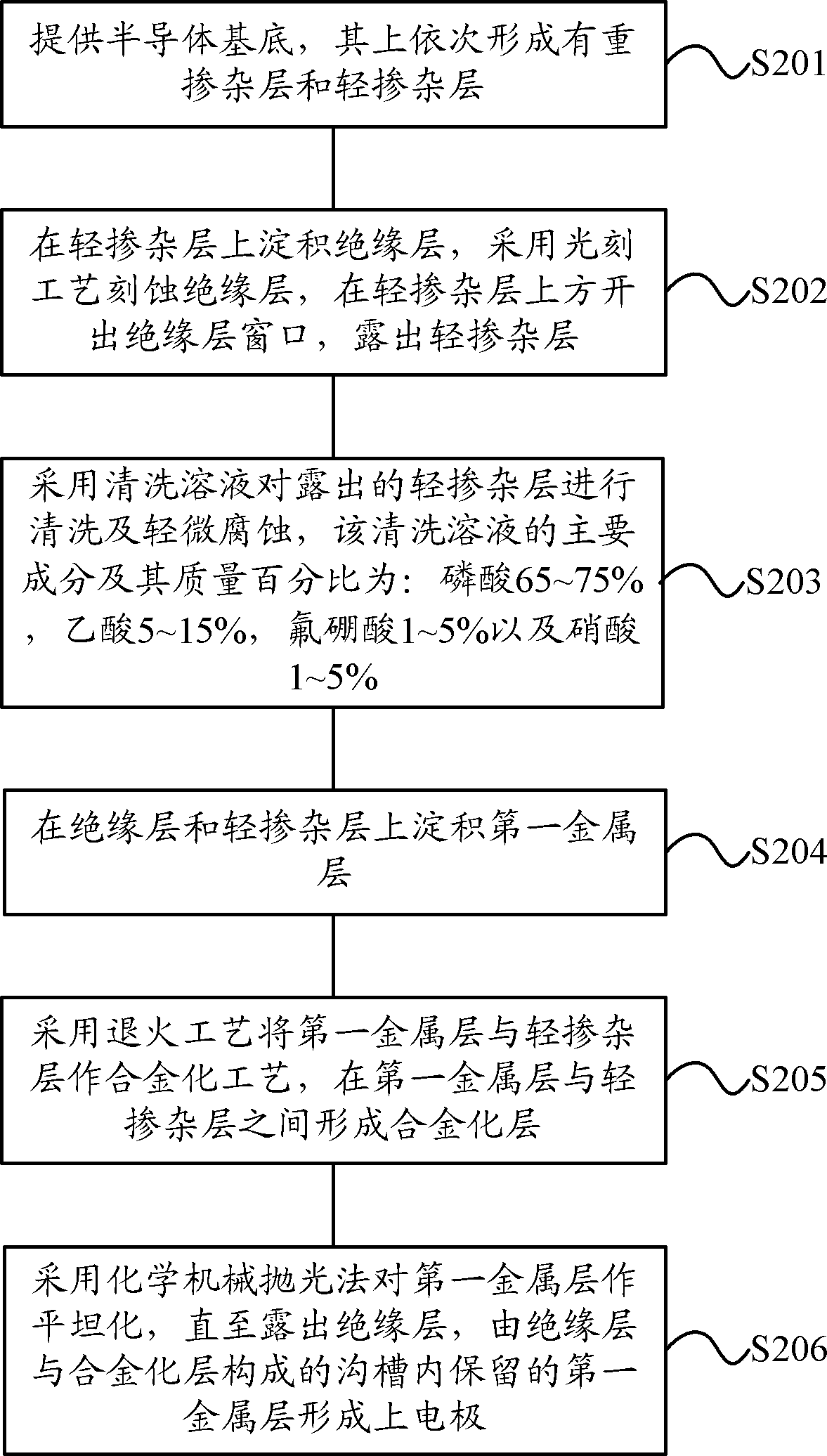

Manufacturing method of schottky diode with high performance

ActiveCN102427041AIncrease contactEliminate particlesSemiconductor/solid-state device manufacturingAcetic acidPhosphoric acid

The invention provides a manufacturing method of a schottky diode with high performance; the manufacturing method comprises the following steps of: providing a semiconductor substrate, and sequentially forming a heavily doped layer and a lightly doped layer on the semiconductor substrate; depositing an insulating layer on the lightly doped layer, and forming an insulating layer window above the lightly doped layer; washing the exposed lightly doped layer by adopting a washing solution; depositing a first metal layer on the insulating layer and the lightly doped layer; alloying the first metal layer and the lightly doped layer, and forming an alloying layer between the first metal layer and the lightly doped layer; removing the first metal layer; forming an upper electrode on the alloying layer, wherein the washing solution mainly comprises the following components in percent by weight: 65-75% of phosphoric acid, 5-15% of acetic acid, 1-5% of fluoboric acid and 1-5% of nitric acid. According to the manufacturing method, before the first metal layer of the schottky diode is deposited, the specific washing solution is used for washing and slightly corroding the lightly doped layer so that particles, stains and interface detects remained on the surface are eliminated, a contact junction of a metal semiconductor becomes better, thereby the schottky diode has more efficient and stable performance.

Owner:ADVANCED SEMICON MFG CO LTD

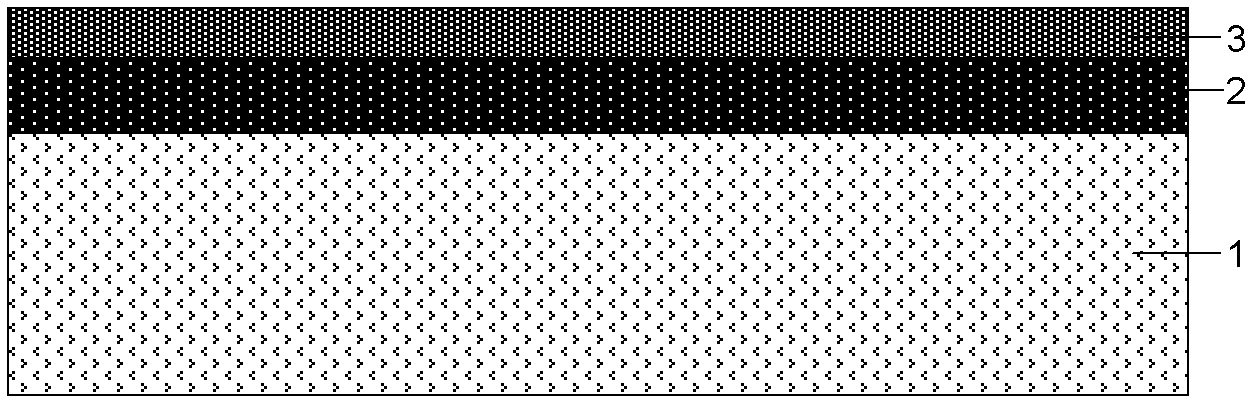

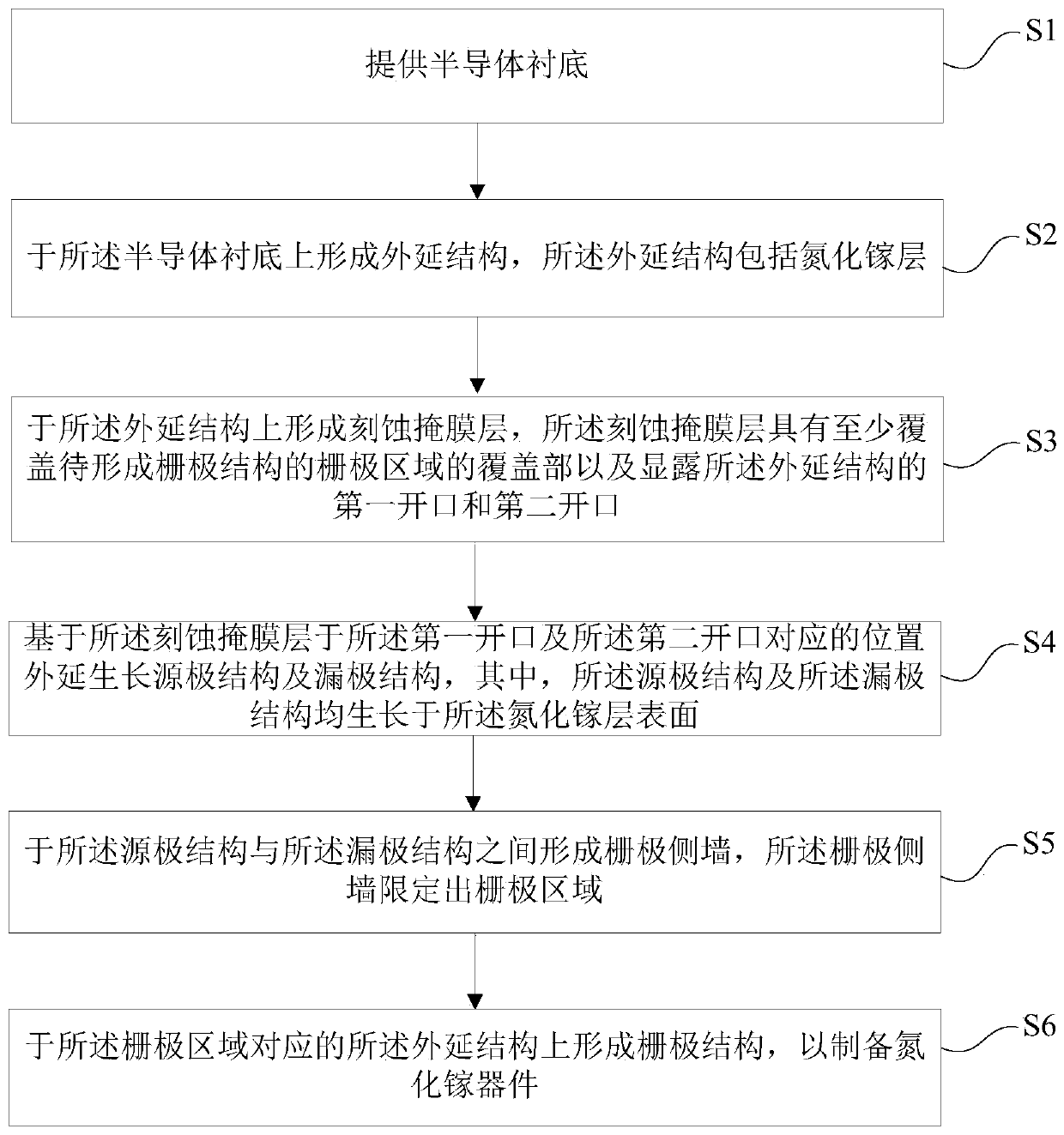

Gallium nitride device structure combining secondary epitaxy and self-alignment process and preparation method

ActiveCN111415987AReduce contact resistanceBalance impairmentSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringGallium nitride

The invention provides a gallium nitride device structure combining secondary epitaxy and a self-alignment process and a preparation method. The preparation method comprises the steps of: providing asemiconductor substrate; forming an epitaxial structure comprising a gallium nitride layer; forming a source structure and a drain structure through epitaxial growth under mask layer protection; forming a grid side wall; and forming a grid structure. According to the preparation method of the invention, the source electrode structure and the drain electrode structure are formed through secondary epitaxial growth, and therefore, ohmic contact resistance can be effectively reduced; the etching rate and material damage caused by etching are balanced through multi-step ion etching, oxidation and acid solvent digital etching before the secondary epitaxy, and process cost is considered while material quality is guaranteed; the self-alignment technology is adopted, errors caused by an alignment process in a photoetching process are avoided, and the size of a grid electrode is accurately defined; and the size of the grid electrode is controlled by utilizing the thickness of an isolation side wall, so that a grid pin photoetching step is omitted, and a technological process is simplified. With the preparation method adopted, the heteroepitaxy of GaN materials can be achieved on a large-sizewafer, and epitaxy cost per unit size is saved.

Owner:ZHEJIANG UNIV

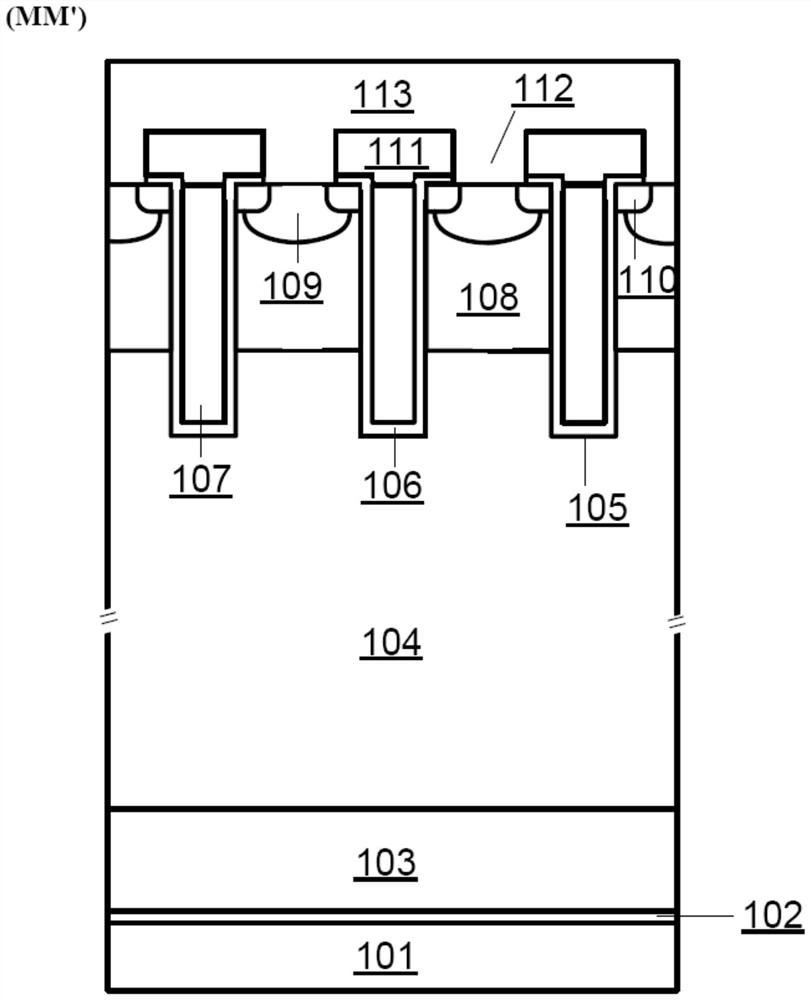

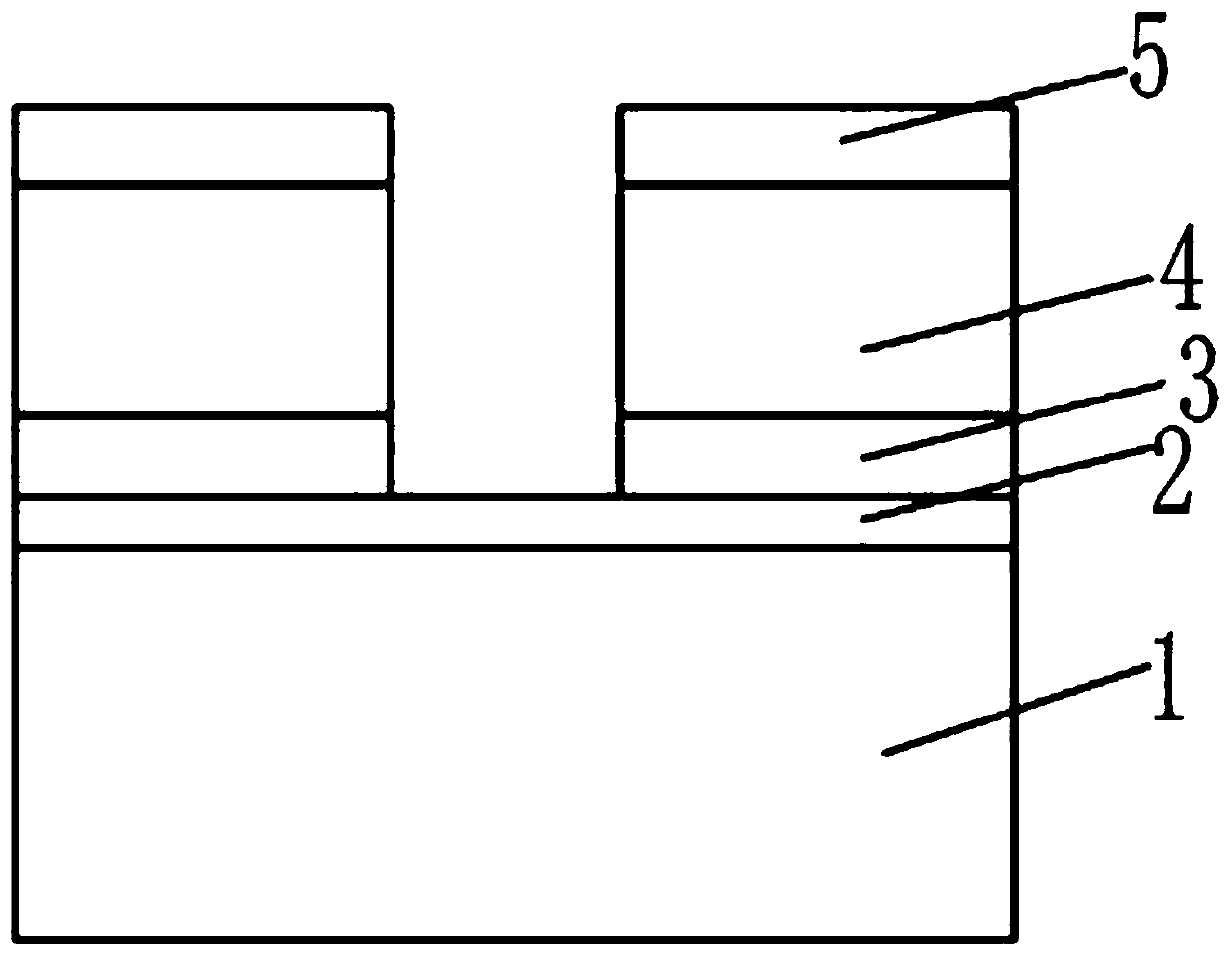

RC-IGBT structure and manufacturing method thereof

InactiveCN109817707AReduce photolithography stepsShort processSemiconductor/solid-state device manufacturingSemiconductor devicesGate oxideMetal electrodes

The invention discloses an RC-IGBT structure, comprising a collector electrode formed on a back metal electrode, wherein a buffer layer is formed on the collector electrode, a drift region is formed on the buffer layer, a body region is formed on the drift region, a trench is arranged in the body region and the drift region, an emitter is formed in the body region on two sides of the trench, a gate oxide layer is formed on the inner wall of the trench, a polycrystalline silicon gate is formed in the gate oxide layer, and an interlayer medium is arranged in a front metal electrode on the trench; a plurality of short circuit points are formed on the back metal electrode, and the short circuit points penetrate through the collector electrode and extend into the buffer layer. The invention also discloses a preparation method of the RC-IGBT structure. Compared with the existing RC-IGBT structure, the preparation method has the advantages that the function of the existing RC-IGBT structure is realized, and the production cost of the RC-IGBT structure is reduced.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

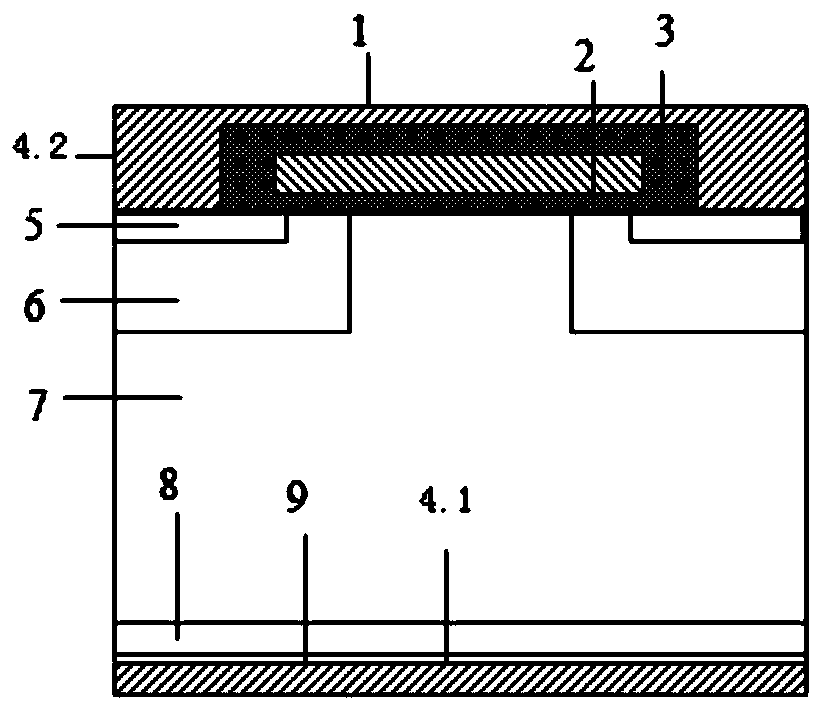

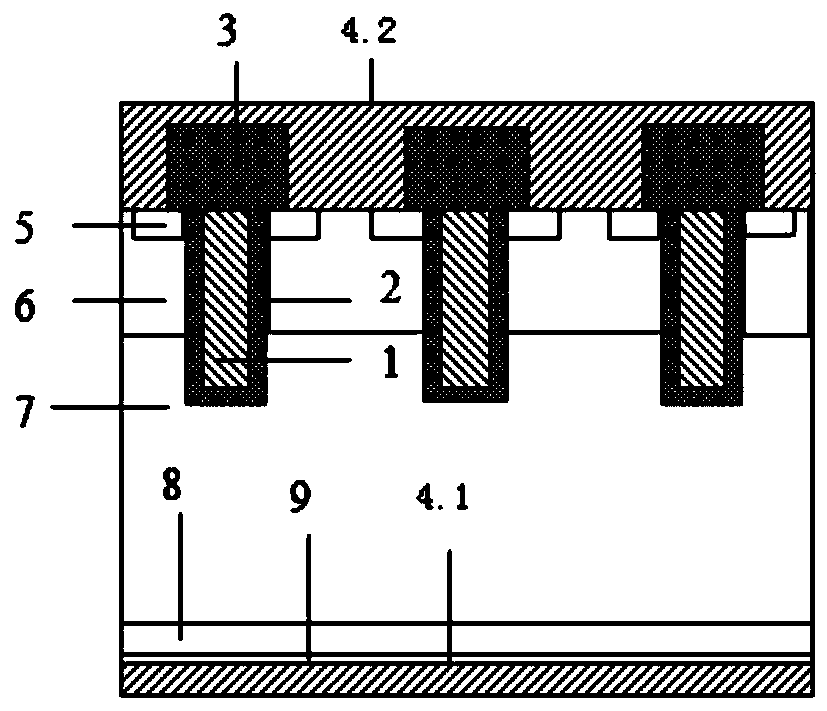

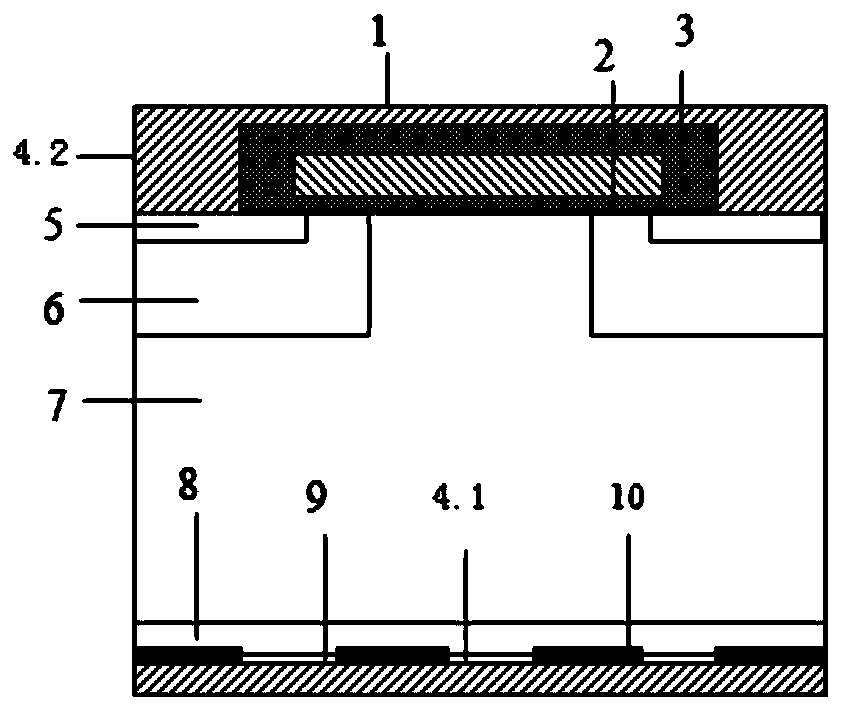

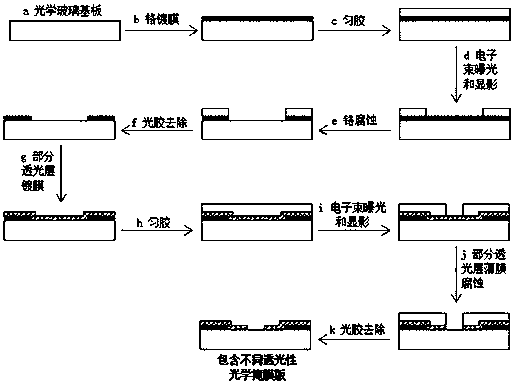

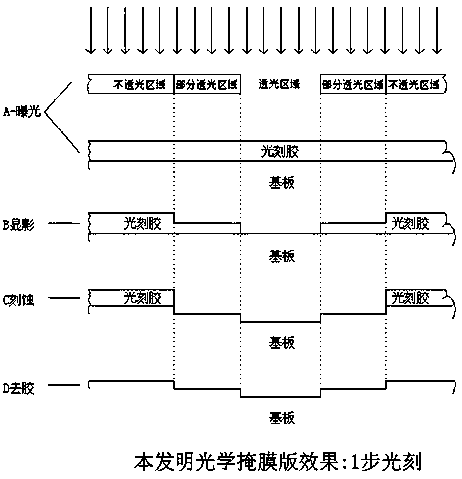

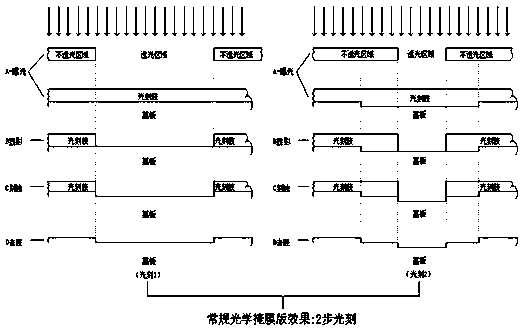

Novel optical mask plate with different light transmission properties

InactiveCN111367142AReduce photolithography stepsMeet photolithography mask requirementsOriginals for photomechanical treatmentTransmittanceChrome plating

The invention relates to the technical field of photoetching, particularly to a novel optical mask plate with different light transmittances. The preparation method of the novel optical mask plate comprises the following steps: a, selecting a substrate; b, plating the surface of the glass substrate with a chromium metal film layer on; c, coating the chromium film with a photoresist; d, exposing the photoresist in a set pattern area through an electron beam; e, soaking in an etching solution; f, removing the remaining photoresist; g, plating the glass substrate with a partial light-transmittingfilm; h, uniformly coating the partial light-transmitting film with a photoresist; i, exposing the photoresist in the set pattern area through an electron beam; j, carrying out etching solution soaking or dry etching; and k, removing the remaining photoresist to form a novel optical mask plate. The invention provides a novel optical mask plate with different light transmission properties, photoresist patterns with steps with different heights can be used manufactured by one-time photoetching according to actual requirements, photoetching steps can be ereduced, photoetching mask requirements are met, and the method can be further popularized in actual industrial production.

Owner:JUCAN PHOTOELECTRIC TECH (SUQIAN) CO LTD

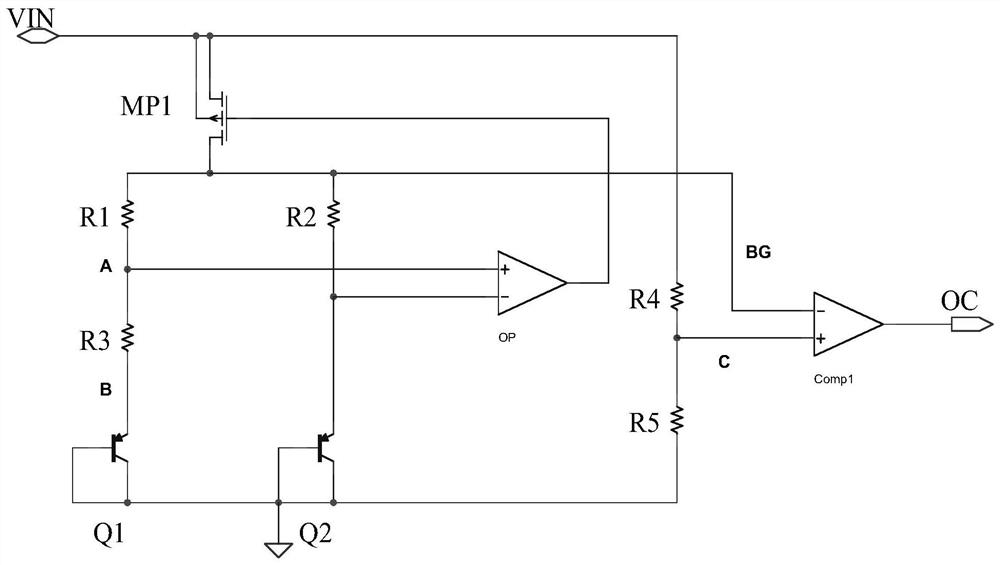

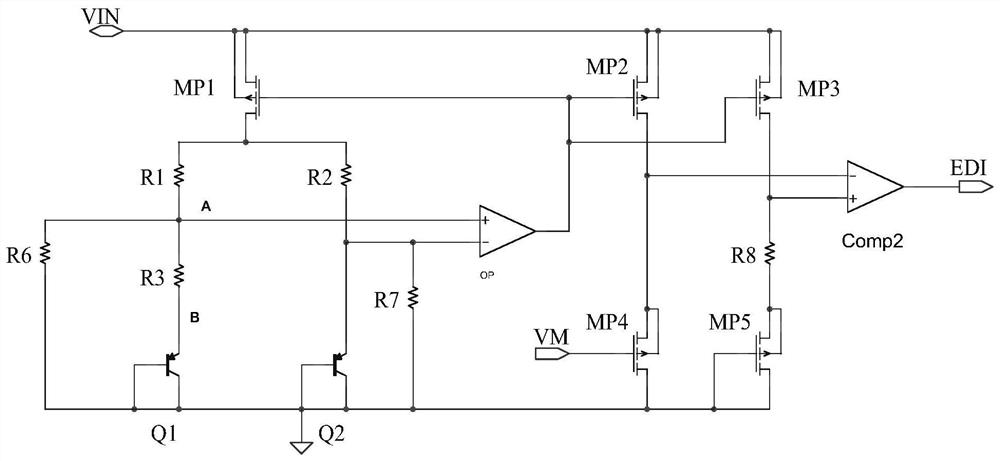

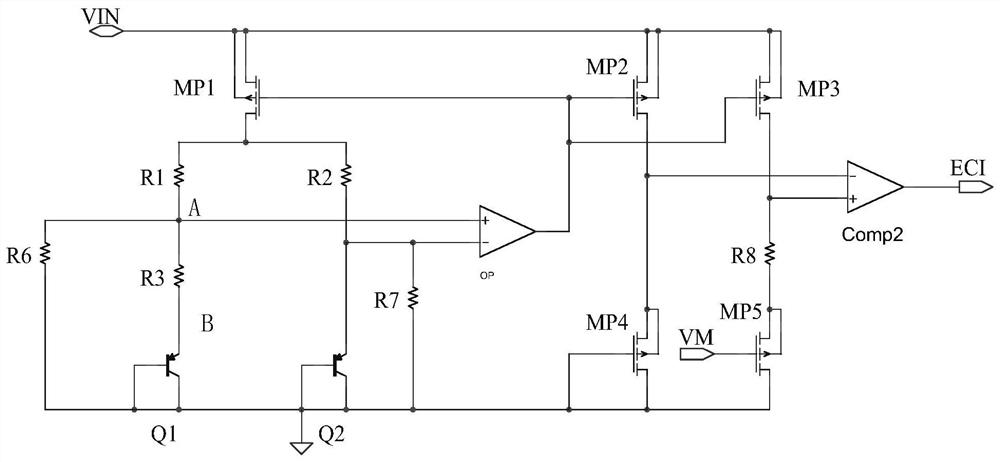

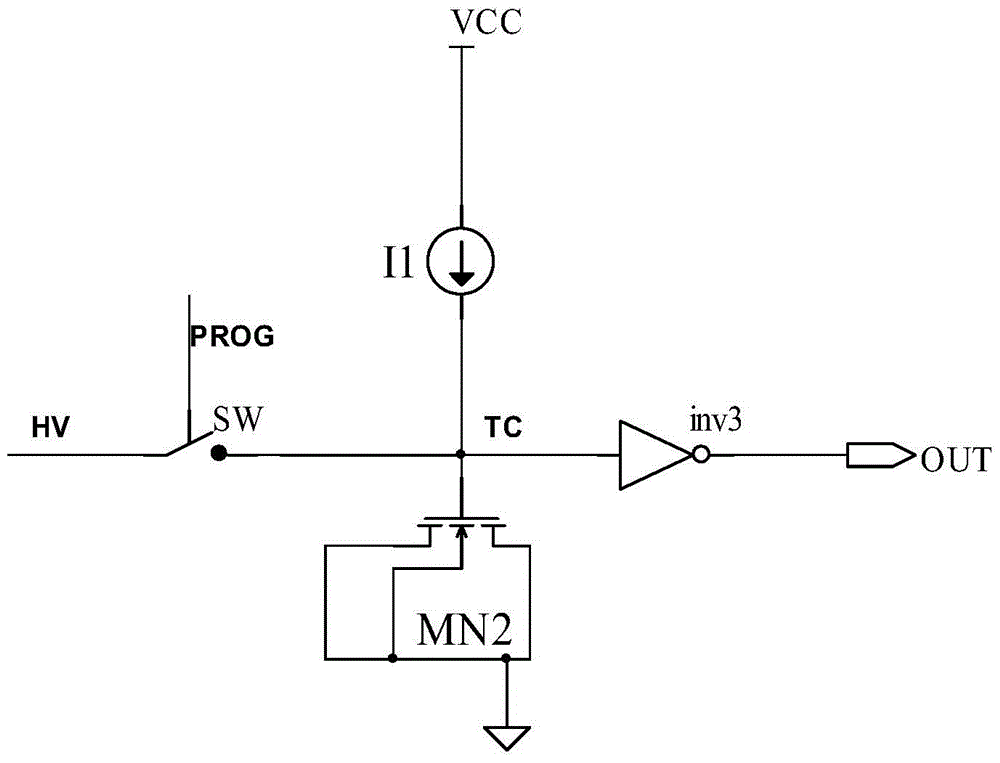

Overvoltage detection circuit, overcurrent detection circuit and protection detection circuit

PendingCN111856124AReduce manufacturing costReduce photolithography stepsCurrent/voltage measurementPhysicsCMOS

The invention provides an overvoltage detection circuit, an overcurrent detection circuit and a protection detection circuit, and the overvoltage detection circuit comprises a band-gap reference voltage generation circuit which is used for generating a band-gap reference voltage BG and comprises an operational amplifier OP, a first bipolar transistor Q1 and a second bipolar transistor Q2; the voltage division circuit is used for generating a first detection voltage based on the detected input voltage; the first input end of the comparator Comp1 receives the bandgap reference voltage BG, and the second input end of the comparator Comp1 receives the first detection voltage; wherein the first bipolar transistor and the second bipolar transistor are PNP bipolar transistors. Compared with the prior art, the bipolar transistor for realizing voltage detection and / or current detection can adopt a parasitic PNP type bipolar transistor in a common CMOS (Complementary Metal-Oxide-Semiconductor Transistor) process, so that photoetching steps are reduced, and the production cost of a chip is further reduced.

Owner:WUXI ZGMICRO ELECTRONICS CO LTD

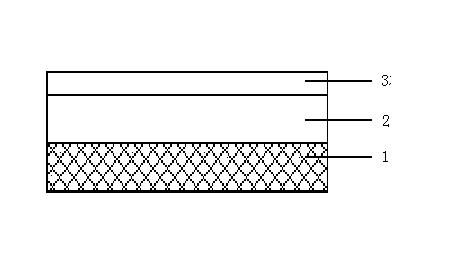

Thin film transistor comprising light shielding layer, and preparation method of thin film transistor

InactiveCN107611032AReduce pollutionPerformance is not affectedTransistorSolid-state devicesGate dielectricOptoelectronics

The invention discloses a thin film transistor. The thin film transistor comprises a substrate, a patterned light shielding layer formed on the substrate, an active layer formed on the light shieldinglayer, a gate dielectric layer formed on the active layer and a gate electrode formed on the gate dielectric layer, and a passivation layer formed on the active layer and the gate electrode, whereinthe light shielding layer adopts an insulating non-metal light shielding material; and the active layer comprises a channel, a source region and a drain region of the transistor. The invention also provides a preparation method of the thin film transistor.

Owner:PEKING UNIV SHENZHEN GRADUATE SCHOOL

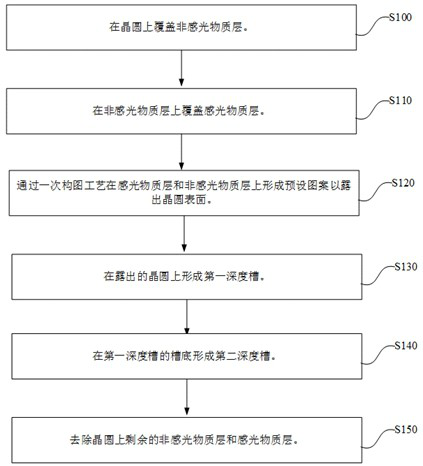

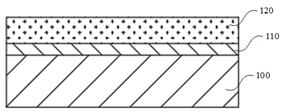

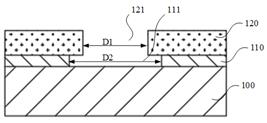

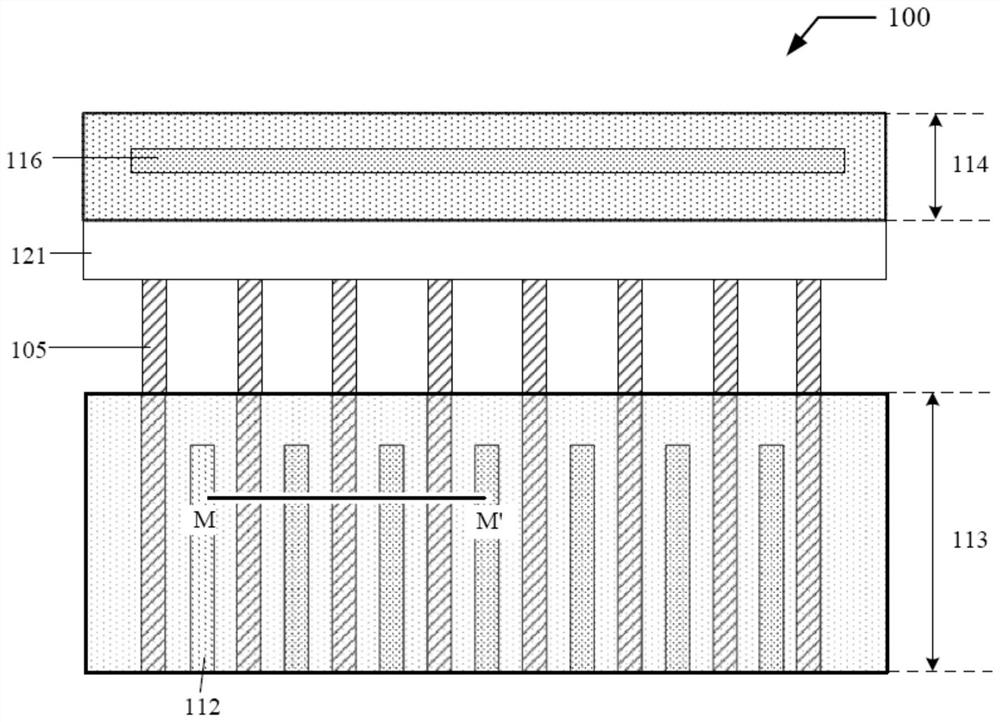

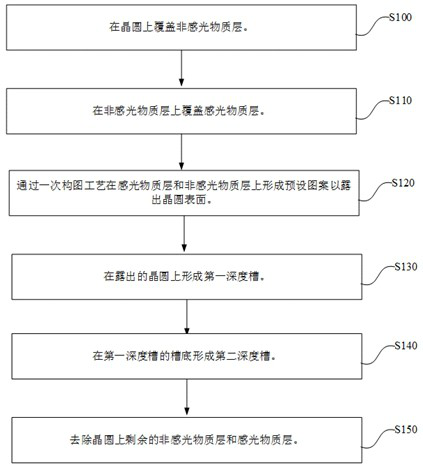

Preparation method of semiconductor device

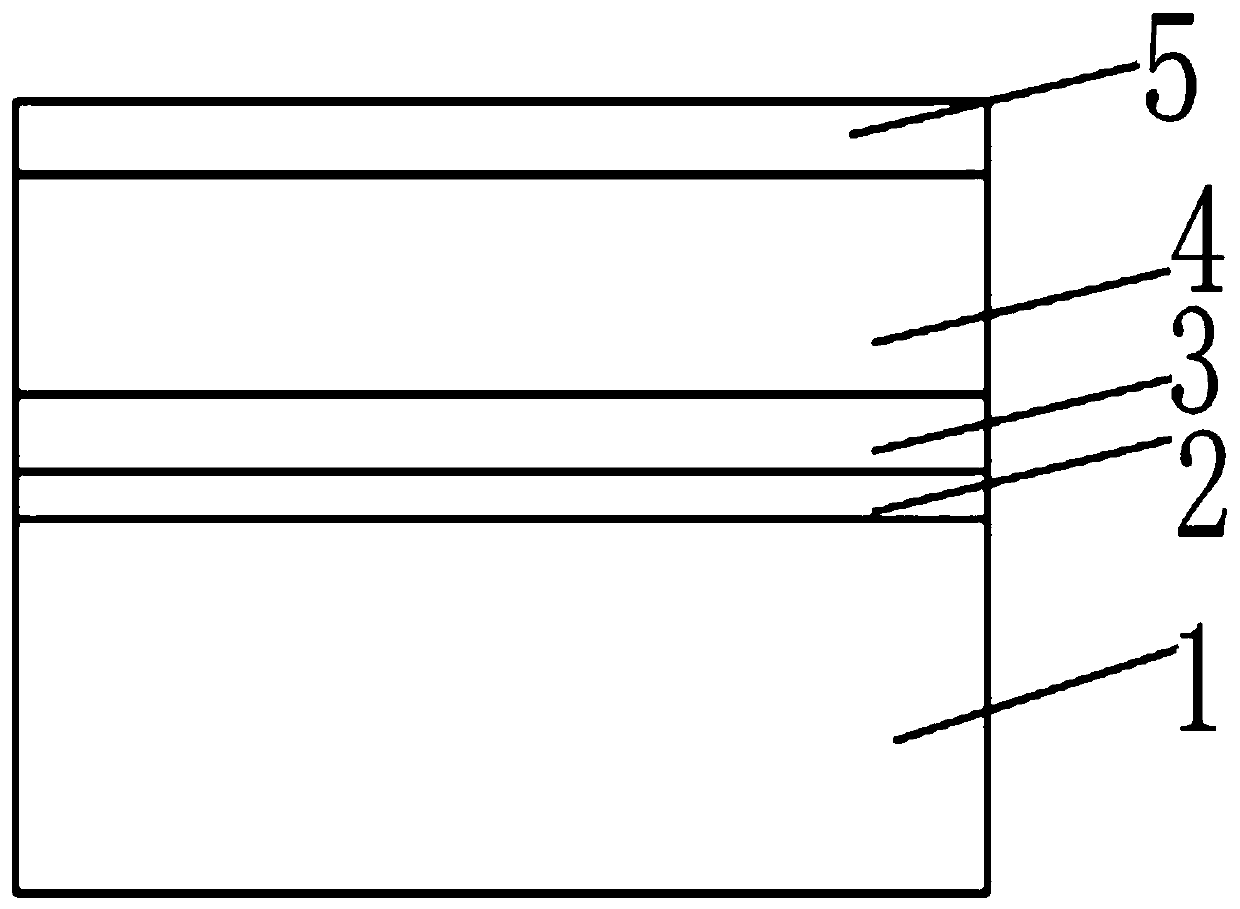

ActiveCN112802747AReduce photolithography stepsReduce the number of photolithographySemiconductor/solid-state device manufacturingPhysicsPhotoresist

The invention provides a preparation method of a semiconductor device, and relates to the technical field of a semiconductor preparation process, and the method comprises the steps of: covering a wafer with a non-photosensitive substance layer; covering the non-photosensitive substance layer with a photosensitive substance layer; forming preset patterns on the photosensitive substance layer and the non-photosensitive substance layer through a one-time composition process to expose the surface of the wafer, wherein a first opening is formed in the photosensitive substance layer, a second opening is formed in the non-photosensitive substance layer, and the caliber of the first opening is smaller than that of the second opening; forming a first depth groove in the exposed wafer; forming a second depth groove in the groove bottom of the first depth groove, wherein the width of the second depth groove is smaller than or equal to that of the first depth groove; and removing the remaining non-photosensitive substance layer and photosensitive substance layer on the wafer. The semiconductor device can be formed through a one-time composition process, thereby saving the photoetching step, reducing the step of removing photoresist, and improving the preparation efficiency by reducing the photoetching times.

Owner:度亘激光技术(苏州)有限公司

Trench type power semiconductor device and manufacturing method thereof

ActiveCN111725306AReduce manufacturing costReduce photolithography stepsSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceParasitic capacitance

The invention discloses a trench type power semiconductor device and a manufacturing method thereof, and relates to a power semiconductor device. In order to solve the problems that the manufacturingcost of a device is increased and the parasitic gate capacitance is increased due to the presence of a gate bus, the invention provides the following technical scheme: a gate contact hole is formed inan interlayer dielectric layer above the initial section of a trench, the gate conductive material in the trench is connected with the gate electrode metal layer above the gate conductive material through the gate contact hole, the width of the gate contact hole is smaller than that of the initial section of the trench, and the width of the initial section of the trench is larger than that of theextension section of the trench. The beneficial effects of the invention are that: according to the trench type power semiconductor device, stable and reliable grid connection can be realized on thebasis of not causing negative influence on the performance of the device; and by omitting a gate bus board, the photoetching process steps of the device are reduced, and the manufacturing cost of thedevice is reduced; and meanwhile, the gate parasitic capacitance introduced by the gate bus board is reduced, and the switching speed of the device is improved.

Owner:安建科技(深圳)有限公司

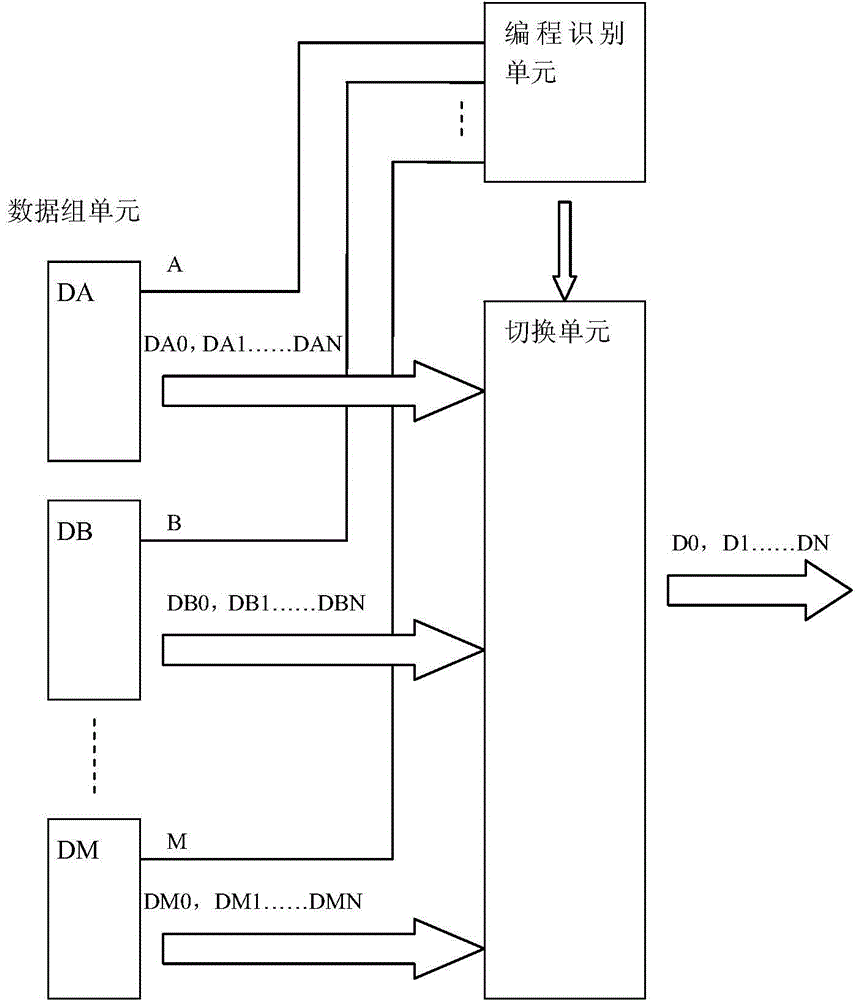

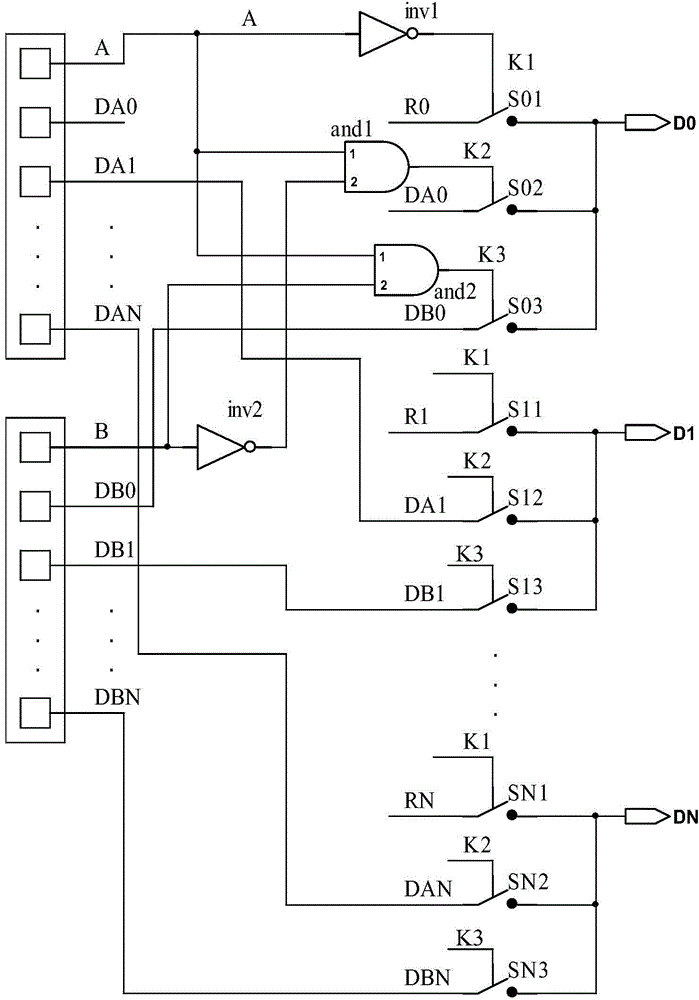

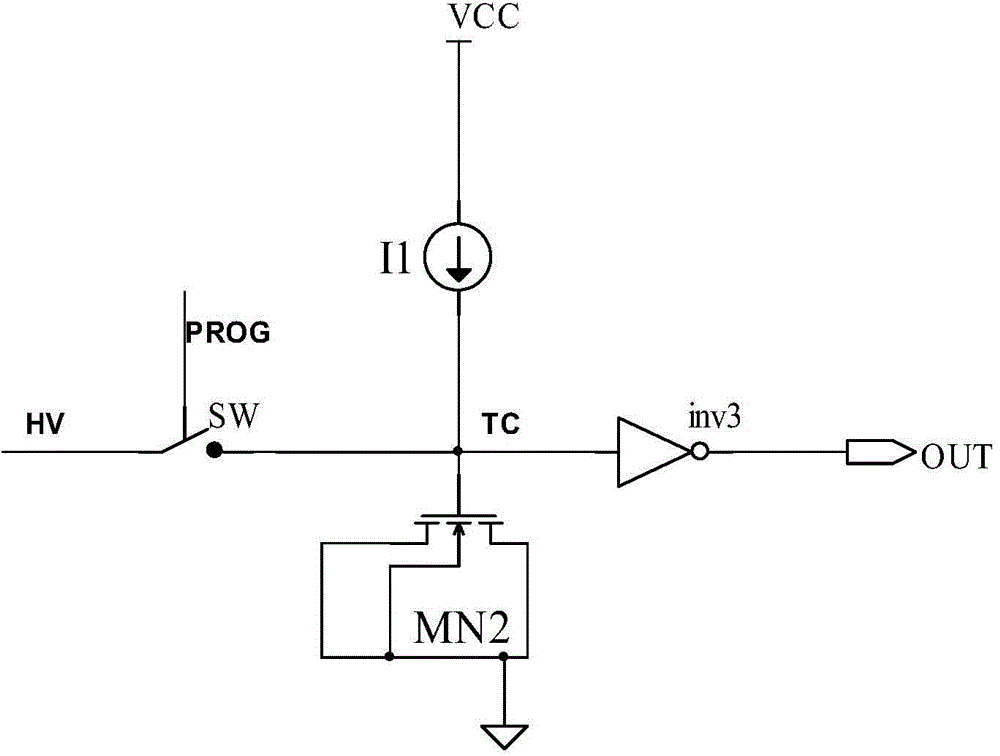

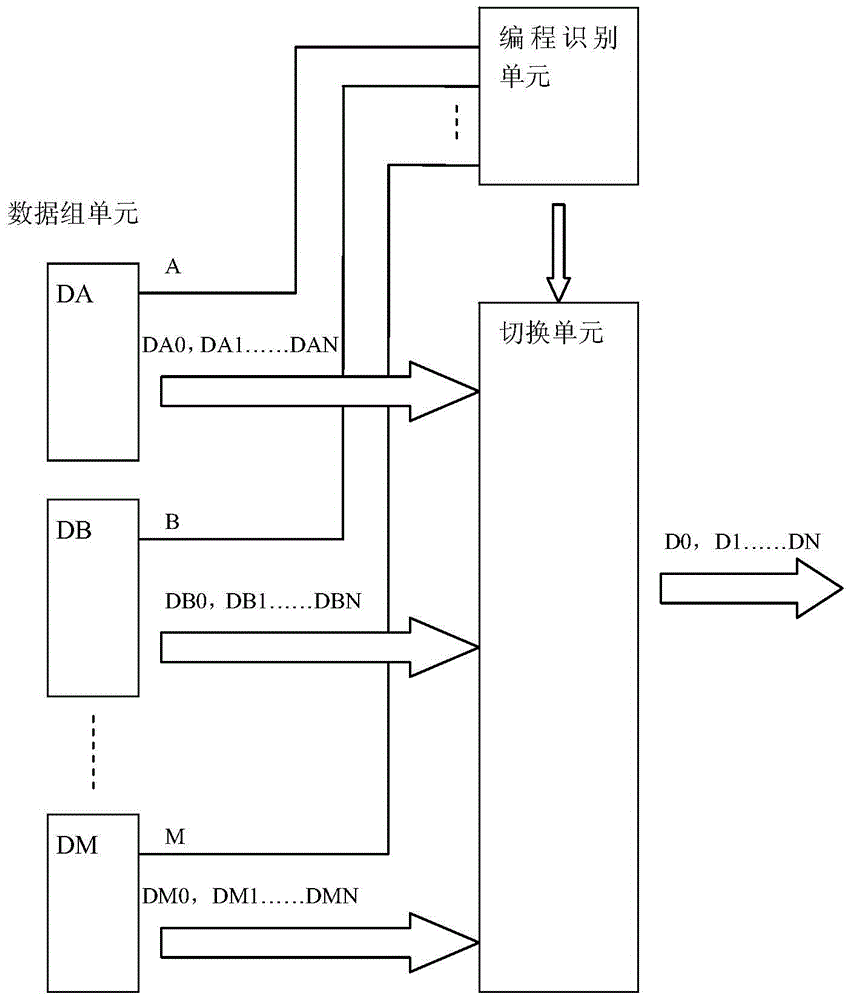

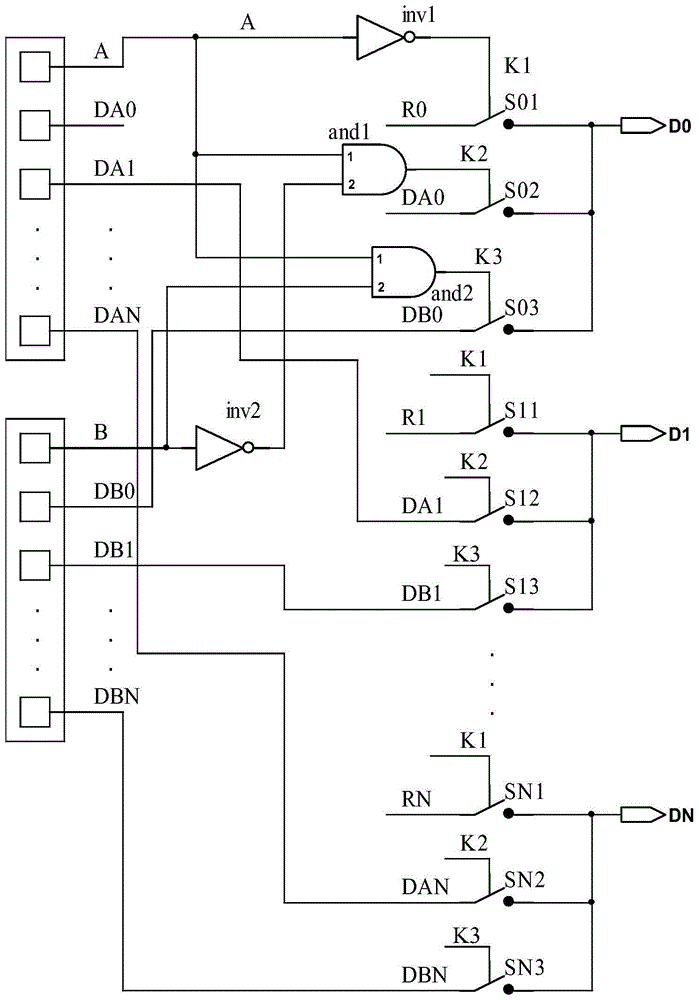

Programming control circuit for programmable chip

ActiveCN104375429AIncrease or decrease the numberReduce photolithography stepsProgramme control in sequence/logic controllersData setControl circuit

The invention relates to the field of intelligent chips, in particular to a programming control circuit for a programmable chip. The programming control circuit comprises a plurality of data set units, a programming recognition unit and a switching unit. Each data set unit comprises a flag bit subunit and a plurality of programming data bit subunits; the programming recognition unit used for recognizing programming times is respectively connected with the flag bit subunit in each data set unit to recognize flag bit signals of the flag bit subunits and control the switching unit; the switching unit is connected with the programming data bit subunits of each data set unit and communicated with the corresponding programming data bit subunits under the control of the programming recognition unit to output corresponding programming data bit signals. The programming control circuit for the programmable chip has the advantages that programming for multiple times can be realized with no need of special processes, so that a step of photoetching in chip production is omitted, and cost is reduced; further, quantity of the data set units can be increased or decreased according to needs to realize programming for multiple times.

Owner:WUXI ZGMICRO ELECTRONICS CO LTD

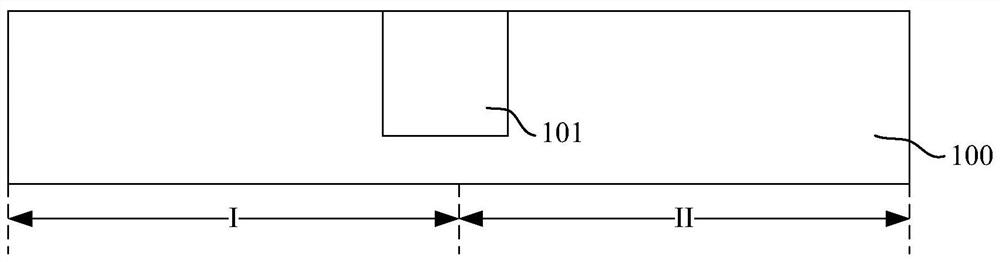

Method for manufacturing embedded source/drain MOS transistors

InactiveCN104465388AReduce photolithography stepsSemiconductor/solid-state device manufacturingSemiconductor devicesManufacturing cost reductionElectrical conductor

The invention provides a method for manufacturing embedded source / drain MOS transistors. The method comprises the steps that gate structures are formed on a PMOS transistor area and an NMOS transistor area formed on a semiconductor substrate respectively, and an STI is arranged between the PMOS transistor area and the NMOS transistor area; channels adjacent to the two sides of each gate structure are synchronously formed on the PMOS transistor area and the NMOS transistor area; after first strained silicon grows in the channels of the PMOS transistor area and the NMOS transistor area, first embedded source / drain electrodes are synchronously formed; a barrier layer is disposed on the PMOS transistor area; after acid gas is used for etching the first embedded source / drain electrode in the NMOS transistor area so that second strained silicon can grow in the channels in the totally exposed PMOS pipe area, second embedded source / drain electrodes are formed; the barrier layer disposed on the PMOS transistor area is removed. According to the method, the existing technological steps of manufacturing the embedded source / drain MOS transistors can be optimized, and manufacturing cost can also be lowered.

Owner:SEMICON MFG INT (SHANGHAI) CORP

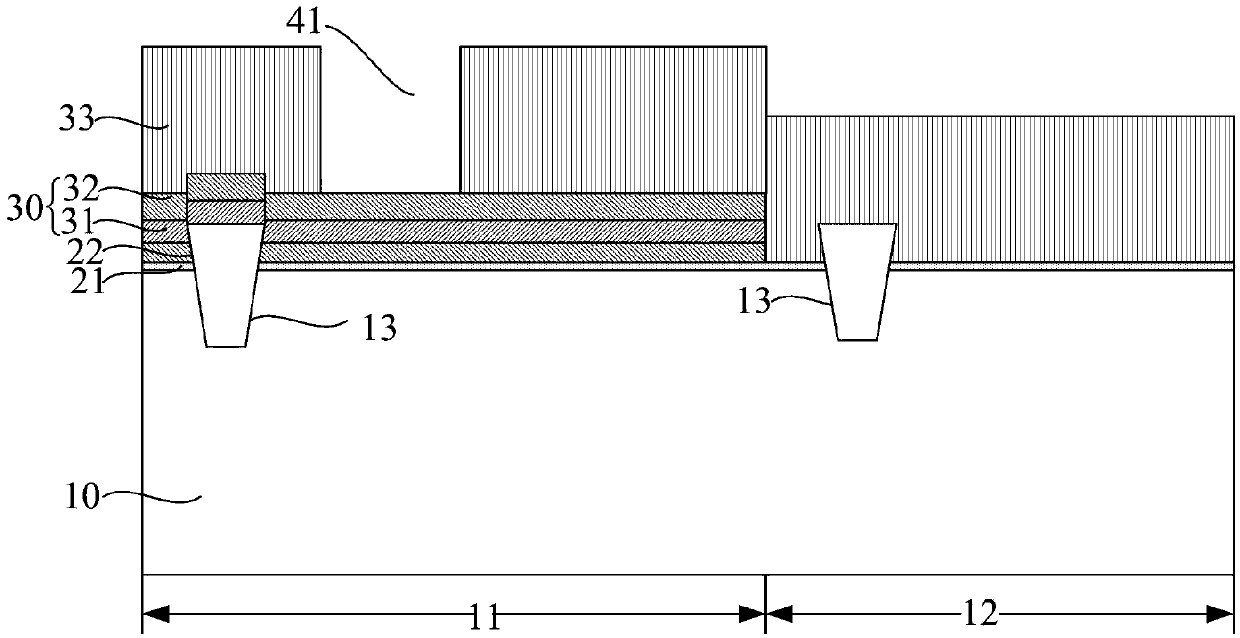

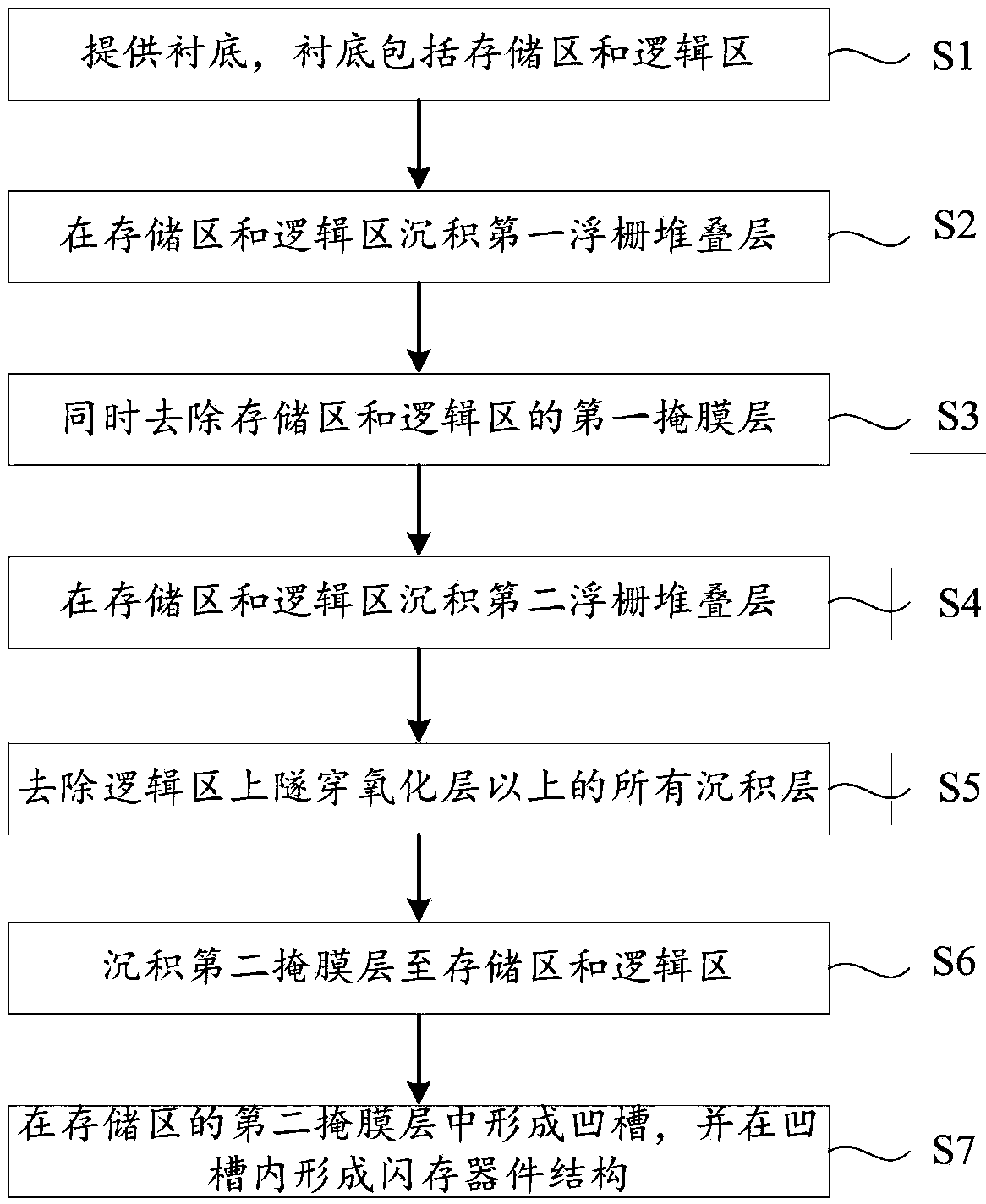

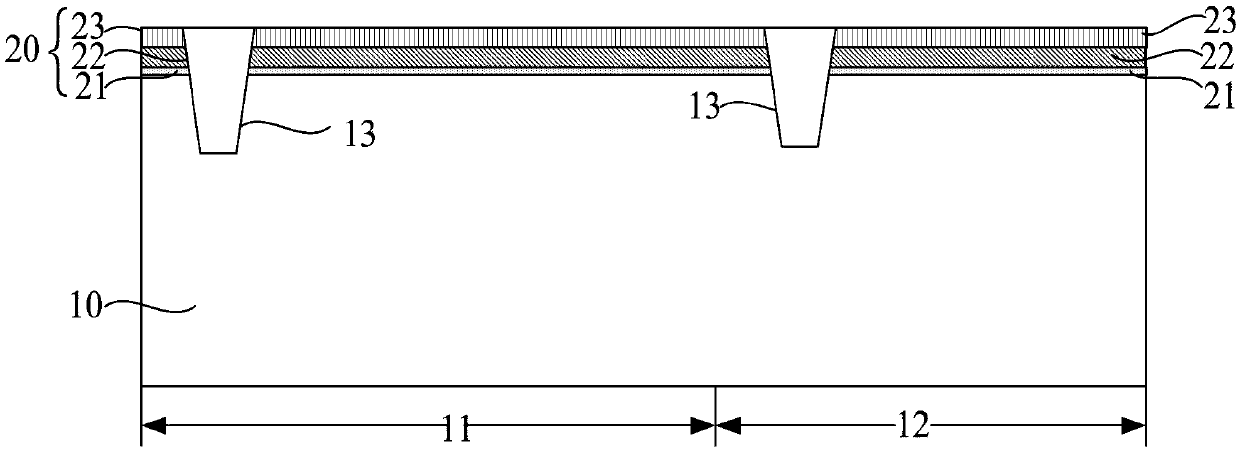

Method for forming embedded flash memory structure

ActiveCN109524406AReduce frequency of useShorten the timeSolid-state devicesSemiconductor devicesLithographic artistGate stack

The invention relates to a method for forming an embedded flash memory structure. The method comprises a steps of providing a substrate comprising a memory area and a logic area, a step of depositinga first floating gate stack layer in the memory area and the logic area, wherein the first floating gate stack layer includes a tunneling oxide layer, a first floating gate layer and a first mask layer deposited in sequence, a step of simultaneously removing the first mask layer of the memory region and the logic region, a step of depositing a second floating gate stack layer on the memory regionand the logic region, a step of removing all deposited layers above the tunneling oxide layer on the logic region, a step of depositing a second mask layer to the memory region and the logic region, astep of forming a recess in the second mask layer of the memory region to form a flash memory device structure in the groove. In the invention, the second mask layer of the memory region and the logic region is simultaneously removed by using one wet etching, and a lithography step used in removing all deposited layers of the logic region is reduced. The process steps of the method for forming the embedded flash memory structure are reduced, and the cost is saved.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

A kind of preparation method of semiconductor device

ActiveCN112802747BReduce photolithography stepsReduce the number of photolithographySemiconductor/solid-state device manufacturingWaferDevice material

Owner:DOGAIN LASER TECH (SUZHOU) CO LTD

Manufacturing method of schottky diode with high performance

ActiveCN102427041BIncrease contactEliminate particlesSemiconductor/solid-state device manufacturingAcetic acidPhosphoric acid

The invention provides a manufacturing method of a schottky diode with high performance; the manufacturing method comprises the following steps of: providing a semiconductor substrate, and sequentially forming a heavily doped layer and a lightly doped layer on the semiconductor substrate; depositing an insulating layer on the lightly doped layer, and forming an insulating layer window above the lightly doped layer; washing the exposed lightly doped layer by adopting a washing solution; depositing a first metal layer on the insulating layer and the lightly doped layer; alloying the first metal layer and the lightly doped layer, and forming an alloying layer between the first metal layer and the lightly doped layer; removing the first metal layer; forming an upper electrode on the alloying layer, wherein the washing solution mainly comprises the following components in percent by weight: 65-75% of phosphoric acid, 5-15% of acetic acid, 1-5% of fluoboric acid and 1-5% of nitric acid. According to the manufacturing method, before the first metal layer of the schottky diode is deposited, the specific washing solution is used for washing and slightly corroding the lightly doped layer so that particles, stains and interface detects remained on the surface are eliminated, a contact junction of a metal semiconductor becomes better, thereby the schottky diode has more efficient and stable performance.

Owner:ADVANCED SEMICON MFG CO LTD

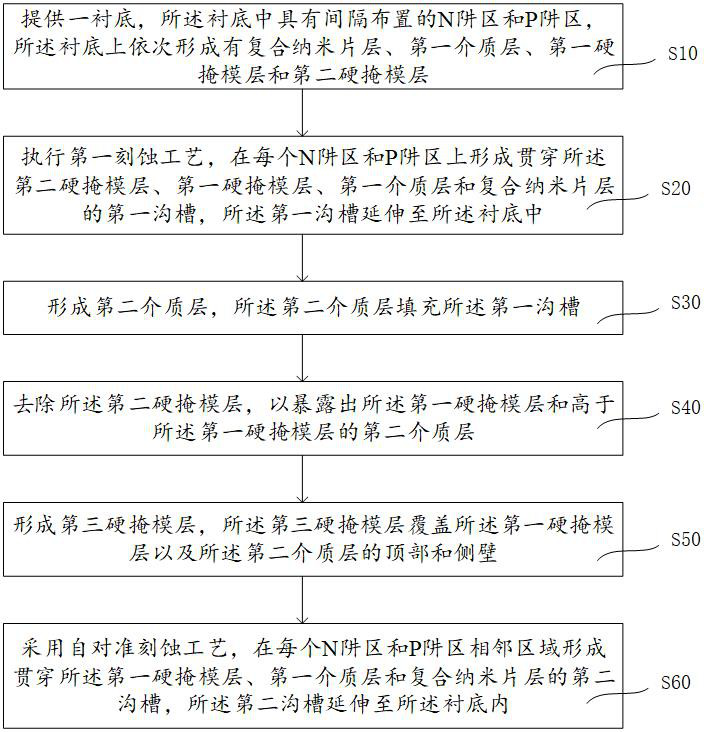

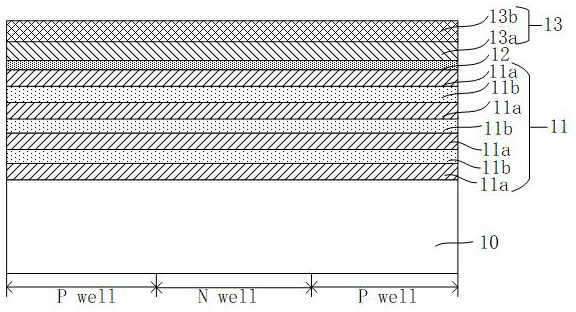

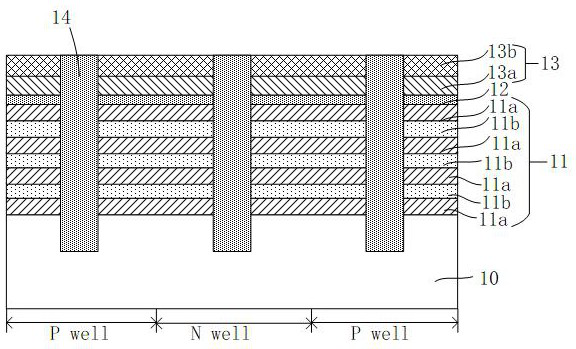

Method of forming semiconductor device

ActiveCN114203636BAchieve the purpose of isolationReduce photolithography stepsSemiconductor/solid-state device manufacturingDevice materialEngineering

The present invention provides a method for forming a semiconductor device, comprising: performing a first etching process, forming a second hard mask layer, a first hard mask layer, The first dielectric layer and the first groove of the composite nanosheet layer, the first groove extends into the substrate; a second dielectric layer is formed, and the second dielectric layer fills the first groove; removing The second hard mask layer to expose the first hard mask layer and the second dielectric layer higher than the first hard mask layer; forming a third hard mask layer, the third hard mask layer The mask layer covers the first hard mask layer and the top and sidewalls of the second dielectric layer; a self-aligned etching process is used to form through the adjacent regions of each N well region and P well region. The first hard mask layer, the first dielectric layer and the second groove of the composite nanosheet layer. A self-aligned etching process is adopted to reduce photolithography steps, reduce costs, and improve transistor performance.

Owner:GUANGZHOU CANSEMI TECH INC

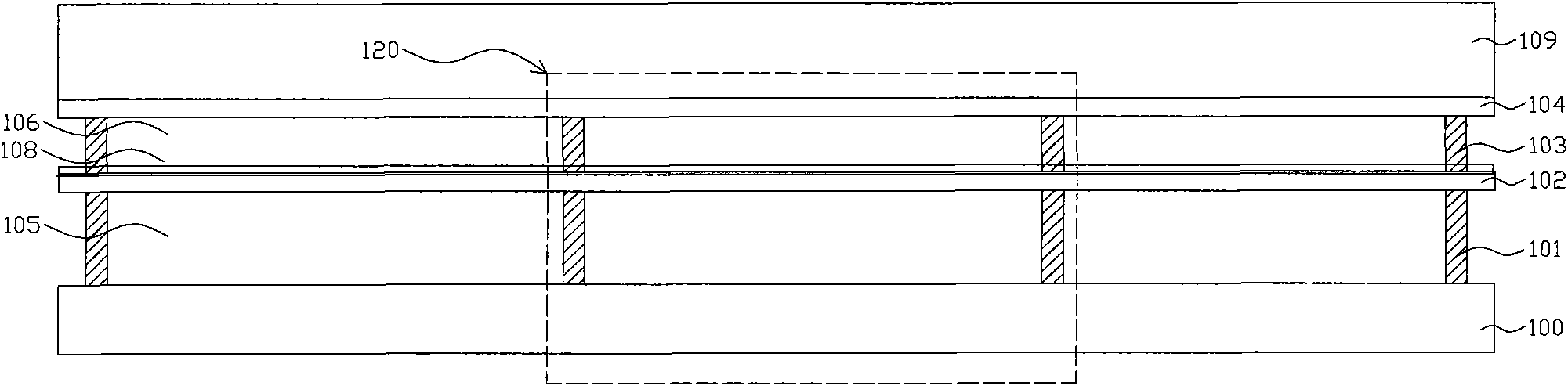

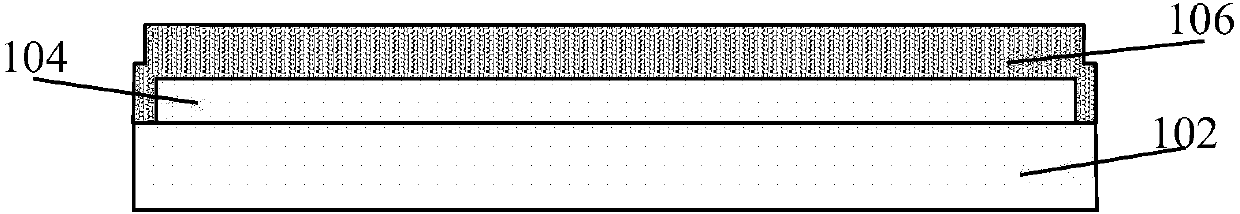

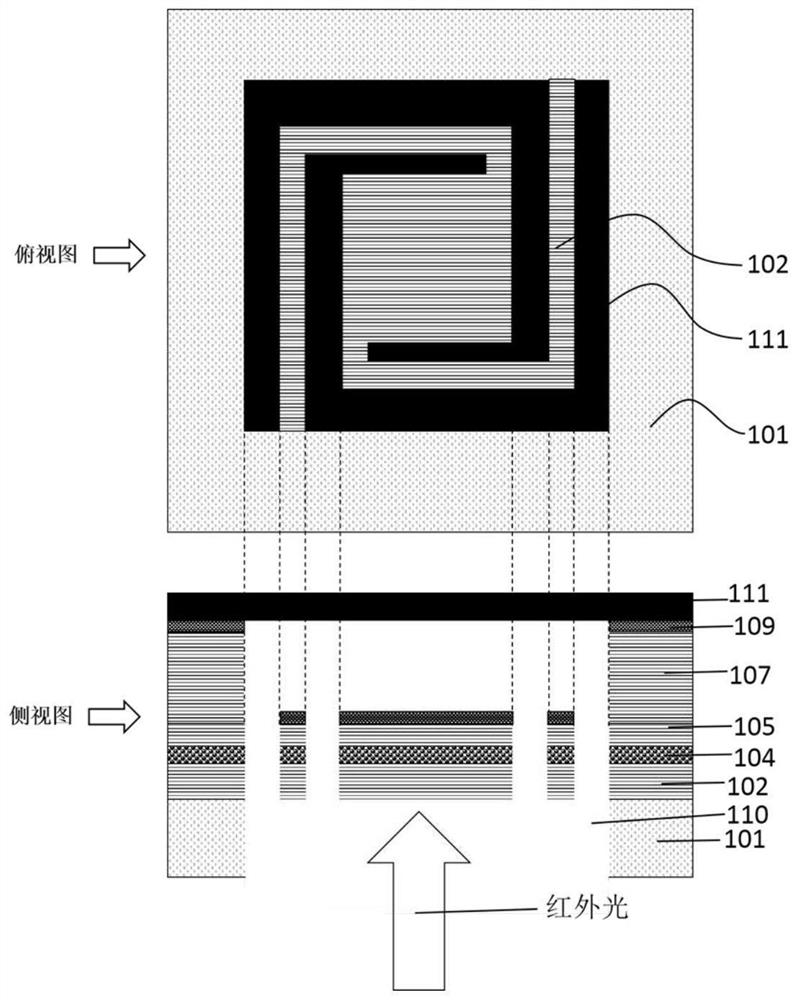

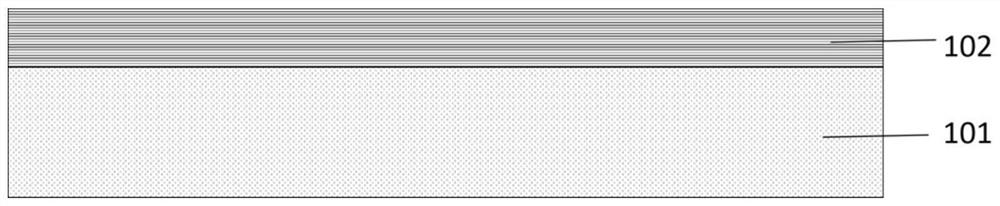

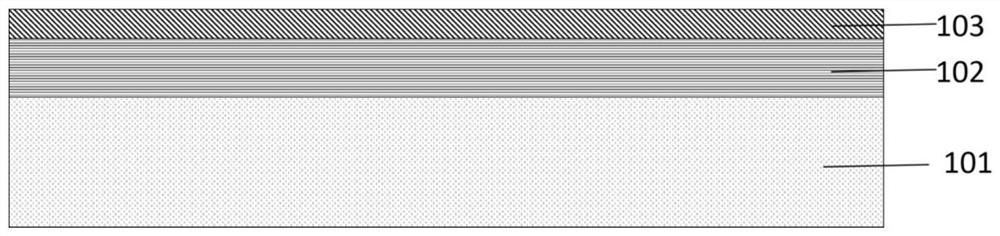

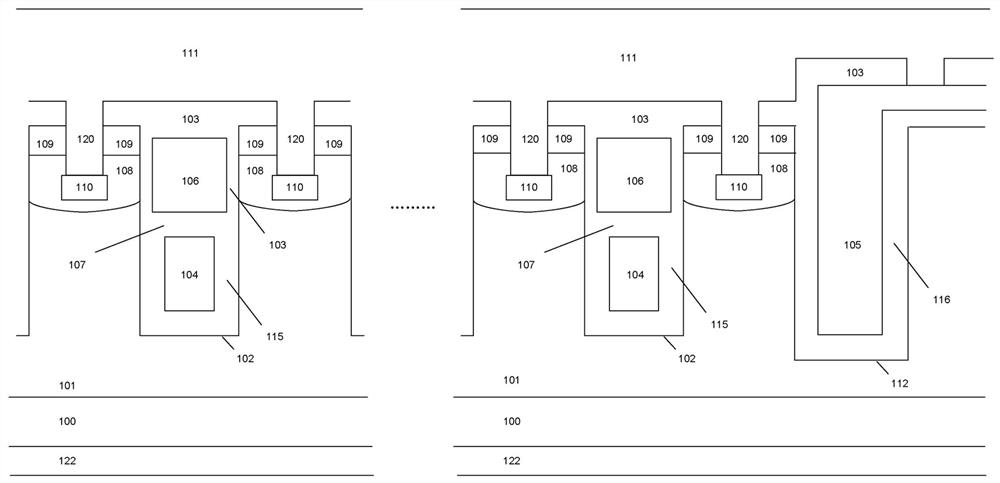

Metallized polycrystalline silicon infrared micro-bolometer and preparation method thereof

ActiveCN113130693AReduce electronic noiseHigh resistivityFinal product manufactureSemiconductor devicesEngineeringSilicon oxide

The invention discloses a metalized polycrystalline silicon infrared micro-bolometer and a preparation method thereof. The micro-bolometer comprises a silicon substrate, an absorbing body and a reflecting layer, wherein the absorbing body is located above the silicon substrate, and is of a stacked structure composed of silicon dioxide / metalized polycrystalline silicon / silicon dioxide / silicon nitride, the reflecting layer is arranged above the absorbing body, and a cavity is formed between the reflecting layer and the absorbing body. The absorption-enhanced metalized polycrystalline silicon infrared micro-bolometer can be prepared by a standard integrated circuit process technology, can realize high integration of functions, is low in power consumption, and has a cost advantage.

Owner:NANJING UNIV

Manufacturing method of shield gate MOSFET device

ActiveCN113990755AUnique structureUnique craftEfficient power electronics conversionSemiconductor/solid-state device manufacturingPower semiconductor deviceMOSFET

The invention relates to a power semiconductor device, in particular to a manufacturing method of a shield gate MOSFET device. According to the invention, through reasonable means, a hard mask is utilized to the greatest extent in different manufacturing steps, a unique manufacturing process flow is formed, one to two photoetching steps can be saved, and the manufacturing cost is effectively reduced.

Owner:安建科技有限公司

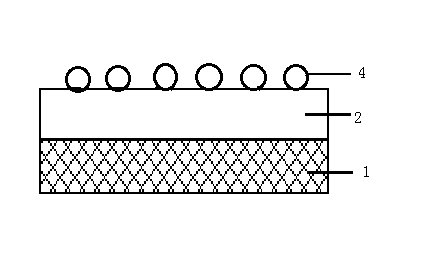

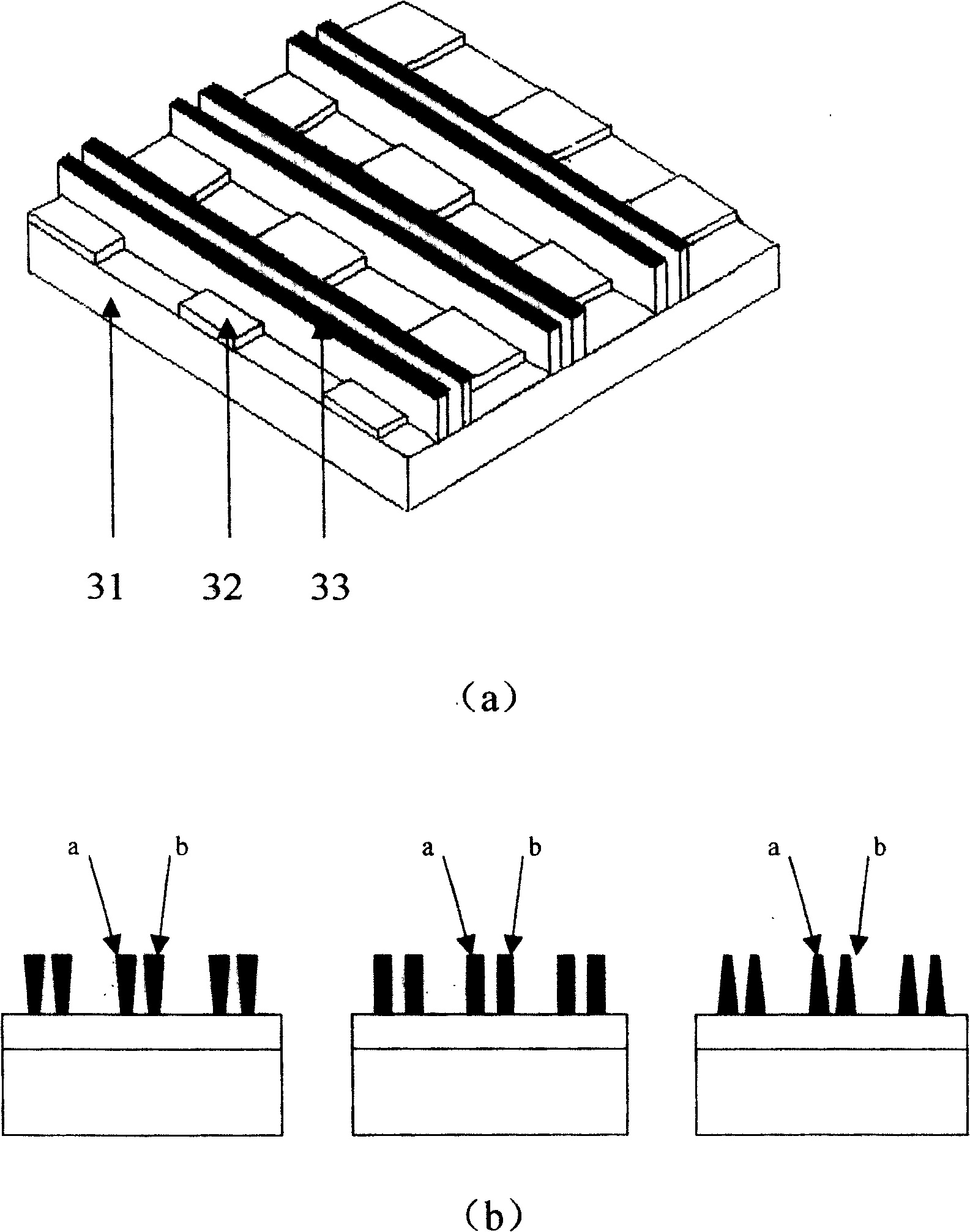

Production of isolating column of organic electroluminescent device

InactiveCN100446632CSimple processReduce usageElectrical apparatusElectroluminescent light sourcesOrganic light emitting deviceSingle exposure

The invention discloses a preparation method of a cathode isolation column of an organic electroluminescent device, which is completed by coating an organic insulating film, exposing once, and developing once. In this method, two adjacent raised columns are used to replace the original inverted trapezoidal isolation columns, so as to realize the effective isolation of adjacent pixel electrodes of the organic light-emitting device. The preparation method of the cathode isolation column in the organic electroluminescence device provided by the invention has the advantages of simplifying the process flow, saving development and corrosion materials, improving production efficiency, reducing environmental pollution, preventing device cross-effects, and the like.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

A programming control circuit of a programmable chip

ActiveCN104375429BIncrease or decrease the numberReduce photolithography stepsProgramme control in sequence/logic controllersData setControl circuit

The present invention relates to a smart chip, and in particular relates to a chip control program A programmable circuit comprising a plurality of data group unit, program identification unit and the switching unit, each data group unit including a seat unit and a plurality of flag data programming unit seat, the program identification number for identifying the programming unit, are connected with each data group unit flag seat unit, the identification flag signal flag seat unit, and controls the switching unit, the switching unit connection said seat unit program data each data group unit, and under control of the program unit identification, program data corresponding to oN seat unit, an output signal corresponding to program data. The present invention does not require special technology, can achieve the effect of many times programming to save chip photolithography step during production, reduces costs, and need to be increased or decreased according to the number of the data group unit, programmed to achieve several purposes.

Owner:WUXI ZGMICRO ELECTRONICS CO LTD

How to form a CMOS transistor

ActiveCN103855096BImprove performanceImprove etch selectivitySemiconductor/solid-state device manufacturingCMOSBlocking layer

A forming method of a CMOS transistor comprises the steps that a semiconductor substrate is provided, and the semiconductor substrate comprises an NMOS area and a PMOS area; pre-decrystallization injection is conducted on the source region and the drain region of the NMOS area and the source region and the drain region of the PMOS area; the source region and the drain region of the NMOS area and the source region and the drain region of the PMOS area are etched to form a first opening, the depth of the first opening is smaller than the depth of pre-decrystallization injection, and an embedded source region and an embedded drain region of an NMOS are formed in the first opening; a blocking layer is formed, and the blocking layer is provided with a second opening exposing the PMOS area; the source region and the drain region of the PMOS area are etched along the second opening, the embedded source region and the embedded drain region of the NMOS and the pre-decrystallization injection area of the PMOS area are removed to form a third opening, and an embedded source region and an embedded drain region of the PMOS are formed in the third opening. The forming method of the CMOS transistor is simple in process.

Owner:SEMICON MFG INT (SHANGHAI) CORP

A shielded gate mosfet device and its preparation method

ActiveCN111415992BUnique structureUnique craftSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceMOSFET

Owner:安建科技(深圳)有限公司

Manufacturing method of LED chip electrode mask pattern capable of being directly stripped

PendingCN111487845AReduce photolithography stepsSimple processSemiconductor/solid-state device manufacturingPhotomechanical coating apparatusAdhesiveMetal electrodes

The invention discloses a manufacturing method of an LED chip electrode mask pattern capable of being directly stripped. Two adhesive film layers formed by negative photoresist and a filling layer arranged between a first adhesive film layer and a second adhesive film layer are prepared on an LED crystal to obtain the suitable metal electrode mask pattern; the first adhesive film layer and the second adhesive film layer are thinner, so that the mask pattern meeting thicker requirements is manufactured by using less photoresist, the obtained metal electrode pattern can be directly subjected tometal tearing stripping on the premise of completeness, and additional treatment is not needed. Through cooperation of the two photoresist layers and a silicon dioxide layer with proper thicknesses, the effect of directly stripping the metal electrode mask pattern which can only be manufactured by using thick adhesive can be achieved; the first adhesive film layer, the filling layer and the secondadhesive film layer are sequentially manufactured, and then the electrode mask pattern is prepared, so that two photoetching steps can be reduced, the whole process is simple and easy to implement, and the cost is relatively low.

Owner:SHANDONG INSPUR HUAGUANG OPTOELECTRONICS