Three-dimensional stacked phase change memory and preparation method thereof

A technology of phase-change memory and three-dimensional stacking, which is applied in semiconductor devices, electric solid-state devices, electrical components, etc., can solve the problems of reducing unit phase-change operation current, complex multi-layer stacking steps, and difficult process realization, etc., reaching the surface The effect of small unevenness, low power consumption, and small unevenness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

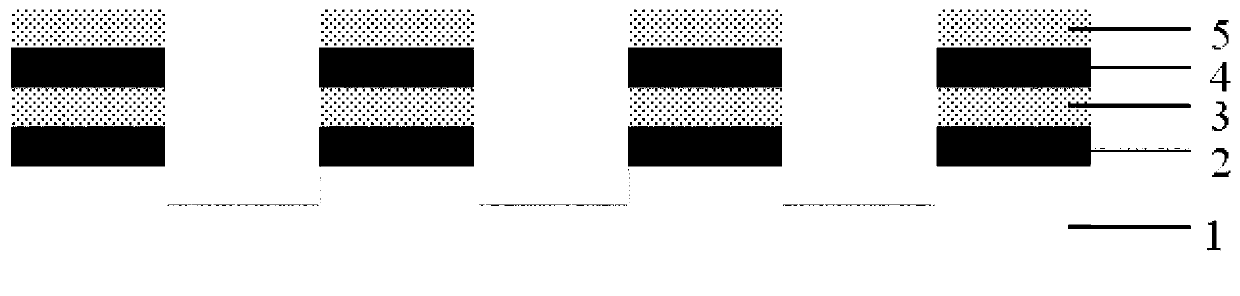

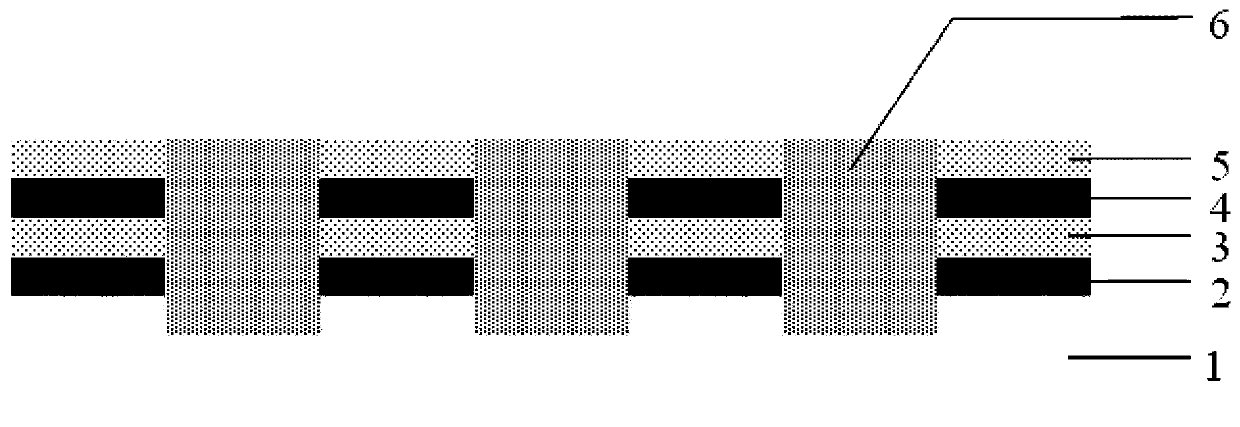

[0042] Such as Figure 1 to Figure 6 As shown, the present invention provides a method for preparing a three-dimensional stacked phase change memory, which specifically includes the following steps:

[0043] (1) A whole layer of electrode material is used as the first horizontal electrode on the substrate;

[0044] (2) Prepare a first insulating layer slightly smaller than the first horizontal electrode in a certain direction (such as the length direction or width direction of the square substrate) on the entire layer of the first horizontal electrode;

[0045] (3) preparing a second horizontal electrode of the same size on the first insulating layer;

[0046] (4) On the above structure, prepare an insulating layer slightly smaller than the second electrode in a certain direction, for example, prepare a second insulating layer smaller than the second horizontal electrode in the same direction as the first insulating layer;

[0047] (5) If more layers are to be stacked, repeat...

Embodiment 1

[0055] This embodiment comprises the following steps:

[0056] Step 1: On the single crystal silicon substrate 1 with SiO2 insulating layer on the surface, deposit 100nm Al as the first layer electrode 2 by electron beam evaporation process.

[0057] Step 2: On the basis of Step 1, use PECVD to deposit 100nm SiO 2 It serves as the first insulating layer 3 and exposes the electrode pins of the first layer.

[0058]Step 3: On the basis of Step 2, electron beam evaporation is used to deposit 100nm Al as the second layer of electrode 4, completely located on the first layer of insulating layer.

[0059] Step 4: PECVD growth of 100nm SiO on the basis of Step 3 2 As the second insulating layer 5 and expose the second layer of electrode pins (such as figure 1 shown; figure 1 The exposed pins are not shown in , for details, please refer to Figure 7 ).

[0060] Step 5: Repeat the above steps for more layers of stacking.

[0061] Step 6: Use ICP etching equipment to regularly ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More