Split gate power MOSFET device with highly doped layer and preparation method thereof

A split gate, highly doped technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electric solid-state devices, etc. The effect of increasing the pressure capacity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

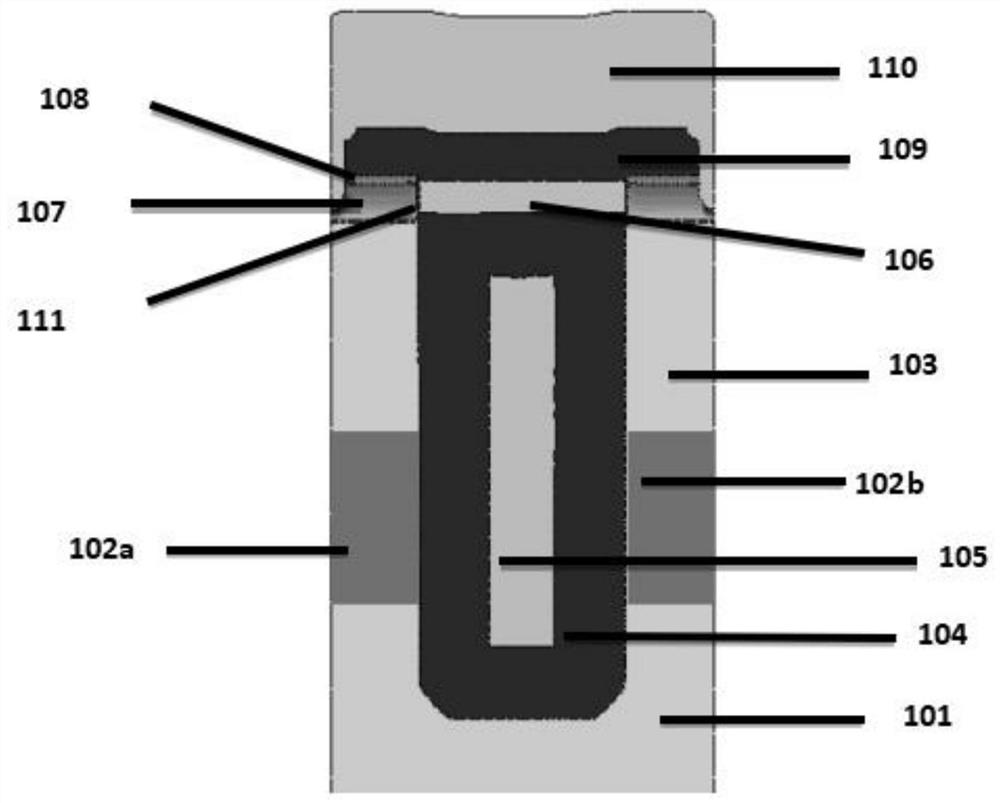

[0052] A specific embodiment of the present invention discloses a split gate power MOSFET device with a highly doped layer, such as figure 1 As shown, the conduction region of the MOSFET device includes several primitive cells arranged periodically, each of which includes a trench, a shielding electrode 105 and a trench gate electrode 106 . Wherein, the trench is disposed in the epitaxial layer of the semiconductor substrate of the first conductivity type; the shielding electrode is disposed in the trench, and the trench gate electrode is disposed on the top of the trench; the Both the shielding electrode and the trench gate electrode are made of the second conductivity type material, and are separated from each other by a dielectric layer; the epitaxial layer is made of the first conductivity type material, including doped and doped layers sequentially stacked on the semiconductor substrate The first epitaxial layer 101, the second epitaxial layer (102a, 102b) and the third e...

Embodiment 2

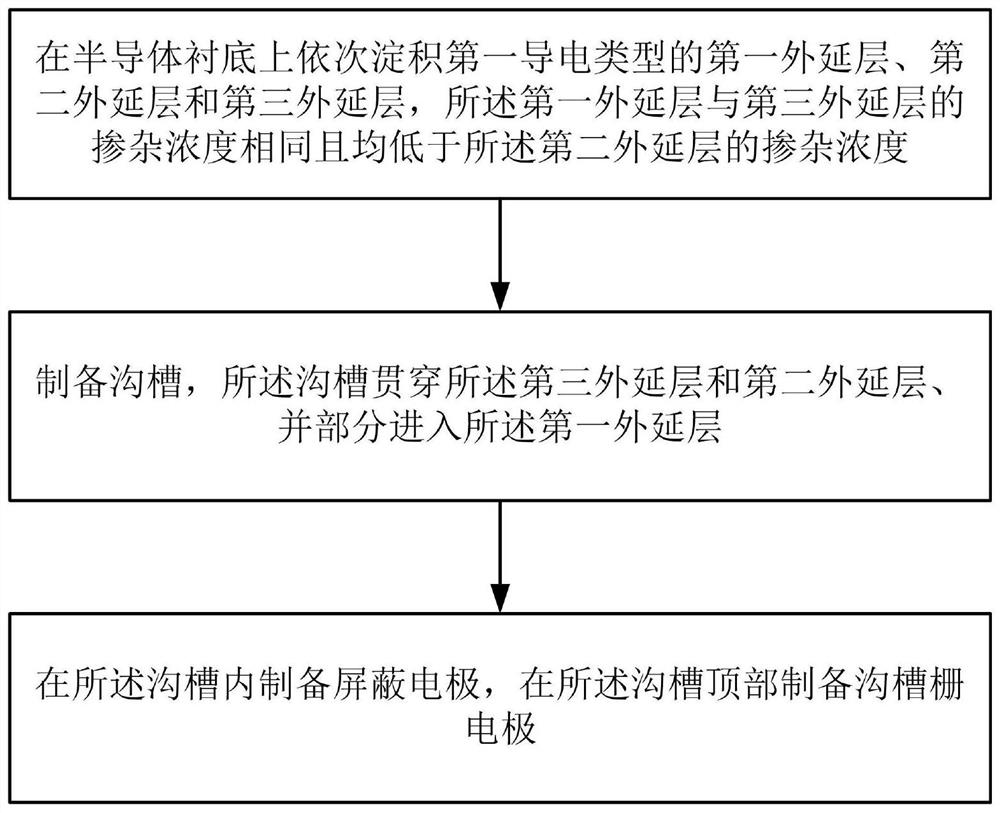

[0066] Another specific embodiment of the present invention discloses a method for preparing the split gate power MOSFET device with a highly doped layer described in Embodiment 1, the flow chart is as follows image 3 As shown, the steps are as follows:

[0067] Step S1: sequentially depositing a first epitaxial layer, a second epitaxial layer and a third epitaxial layer of the first conductivity type on the semiconductor substrate, the first epitaxial layer and the third epitaxial layer have the same and low doping concentration a doping concentration in the second epitaxial layer;

[0068] Step S2: preparing a trench, the trench penetrates the third epitaxial layer and the second epitaxial layer, and partially enters the first epitaxial layer;

[0069] There are many ways to form grooves. In this embodiment, the grooves are specifically formed by a photolithography process;

[0070] Step S3: preparing a shielding electrode in the trench, and preparing a trench gate electr...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More