A gan field effect transistor with source-connected p-buried layer and drain field plate

A technology of drain field plate and source electrode, applied in the direction of semiconductor devices, electrical components, circuits, etc., can solve the problems of damage to device reliability, large leakage current, deterioration of device performance, etc. Pressure-resistant effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

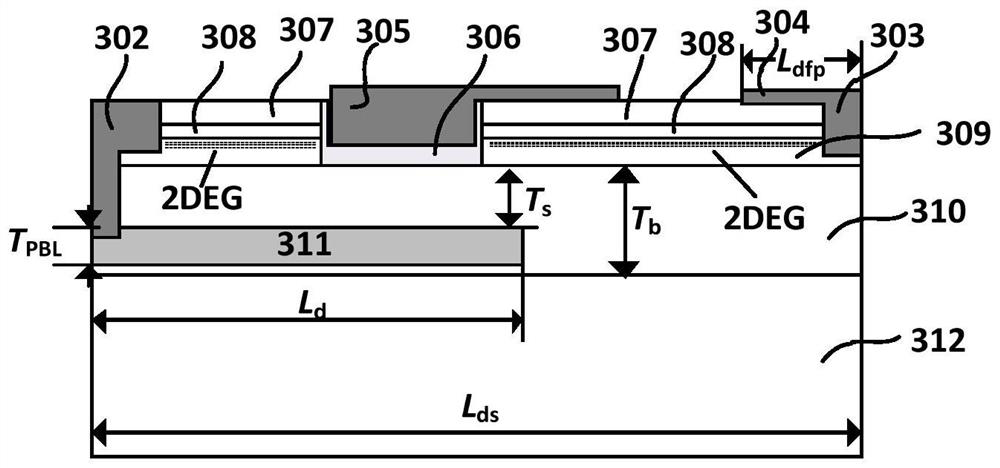

[0015] In order to make the purpose, technical solution and advantages of the present invention clearer, the present invention will be described in detail below in conjunction with the accompanying drawings.

[0016] The invention is a voltage-resistant AlGaN / GaN insulated gate field-effect transistor with a source-connected P-type buried layer and a drain field plate, such as image 3 As shown, it includes a source electrode 302, a drain electrode 303, a drain field plate 304, a gate electrode 305, a gate dielectric layer 306, a passivation layer 307, a barrier layer 308, a channel layer 309, a low-concentration trap-doped buffer layer 310, It is connected to the source electrode with a P-type buried layer 311 and a high-concentration trap-doped buffer layer 312 .

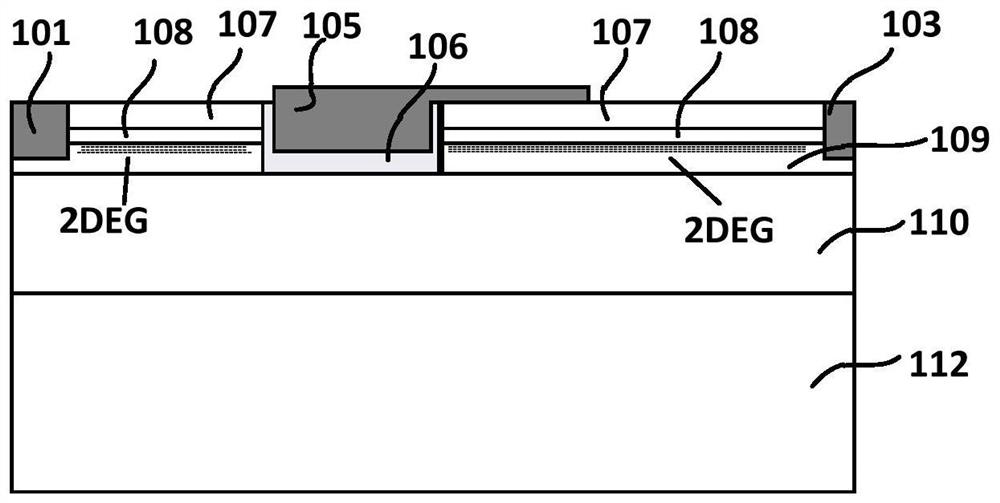

[0017] like figure 1 Shown is a schematic structural diagram of a traditional gate field plate insulated gate AlGaN / GaN field effect transistor, which can be used as one of the comparison devices of the present i...

PUM

| Property | Measurement | Unit |

|---|---|---|

| length | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More