Dynamic threshold voltage MOSFET on SOI

a threshold voltage and dynamic technology, applied in the direction of transistors, electrical apparatus, semiconductor devices, etc., can solve the problems of increasing the integration density compromising the quality of portability, and putting severe constraints on the power consumption of the integrated circuit, etc., to achieve high performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

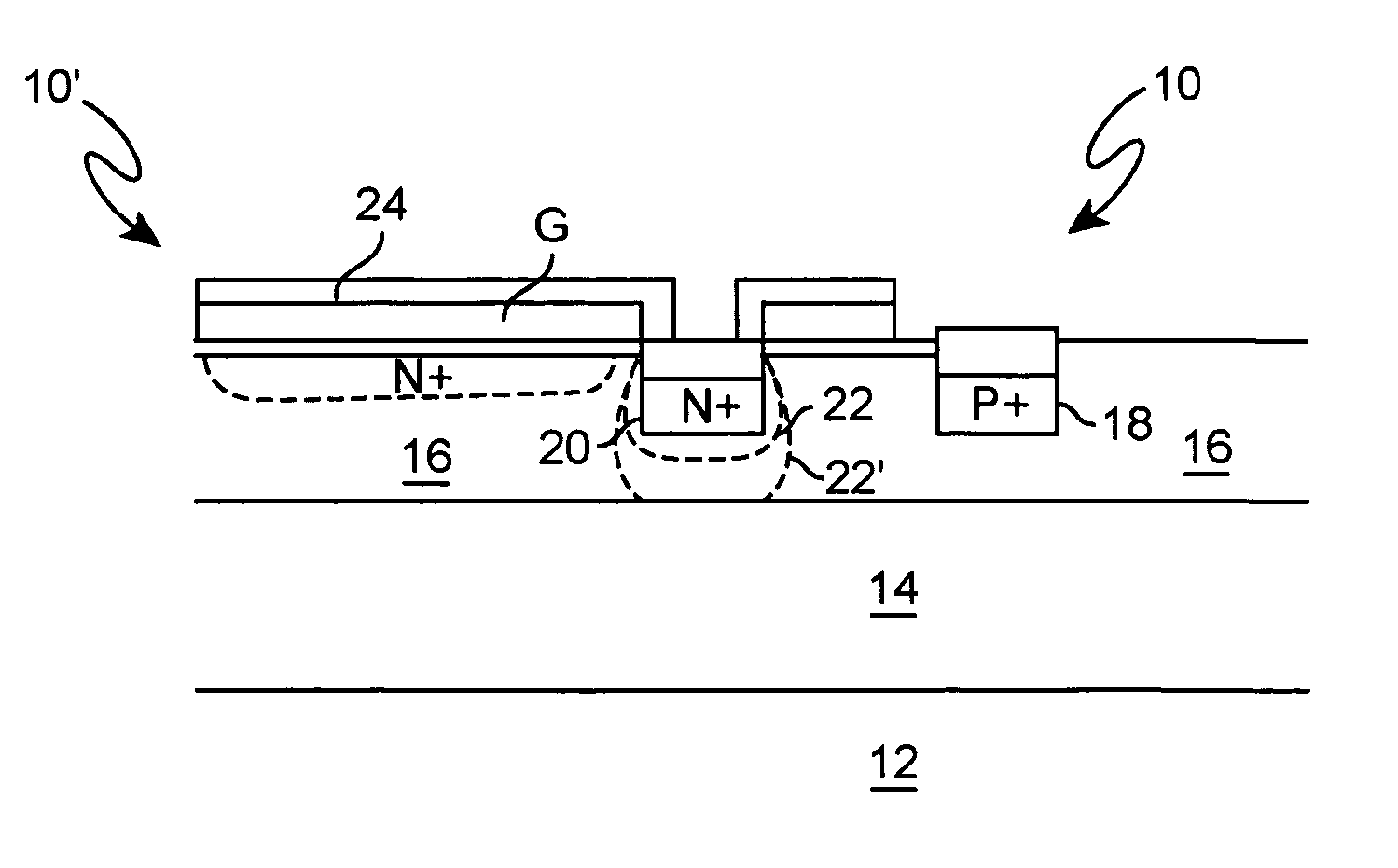

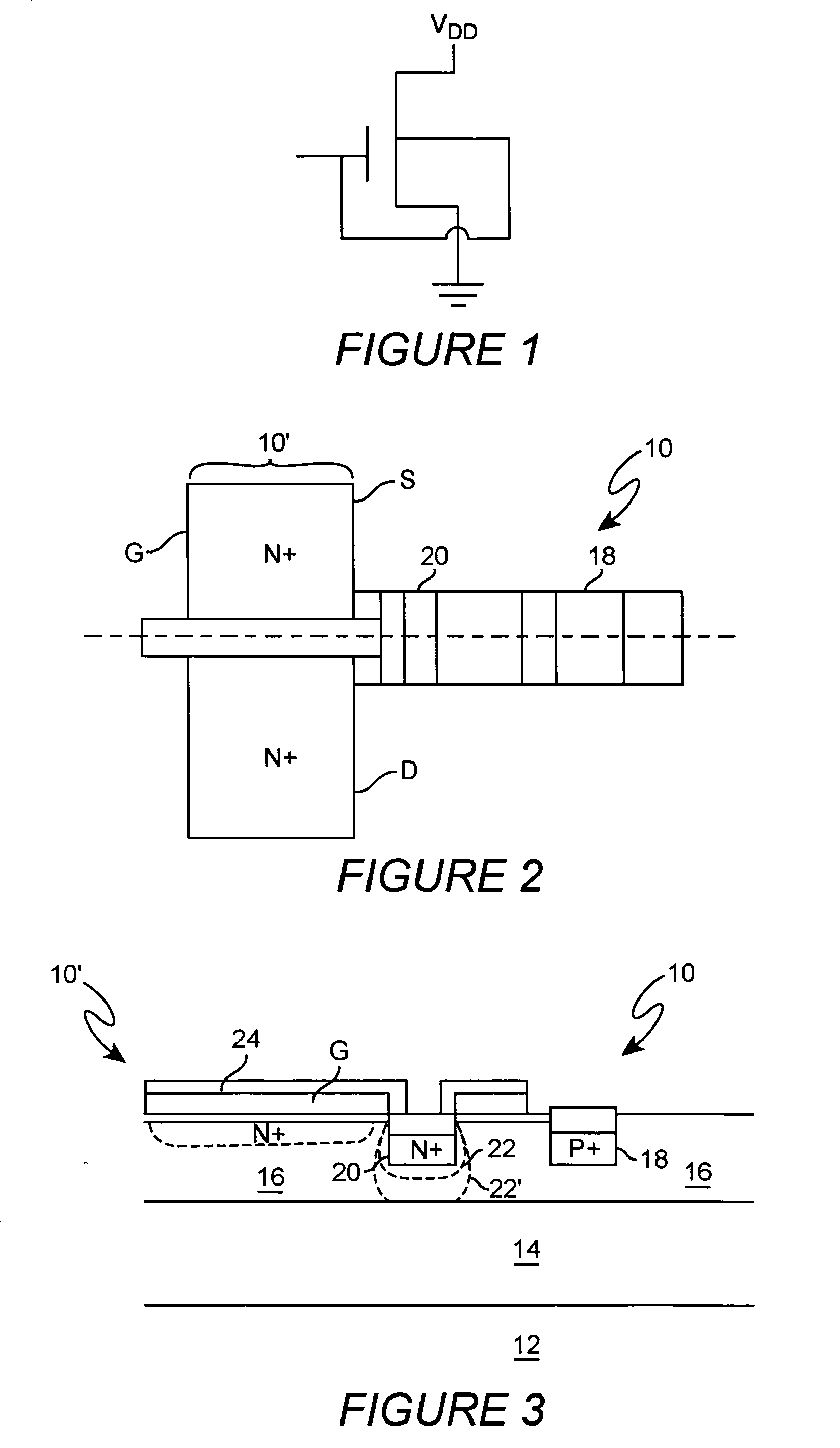

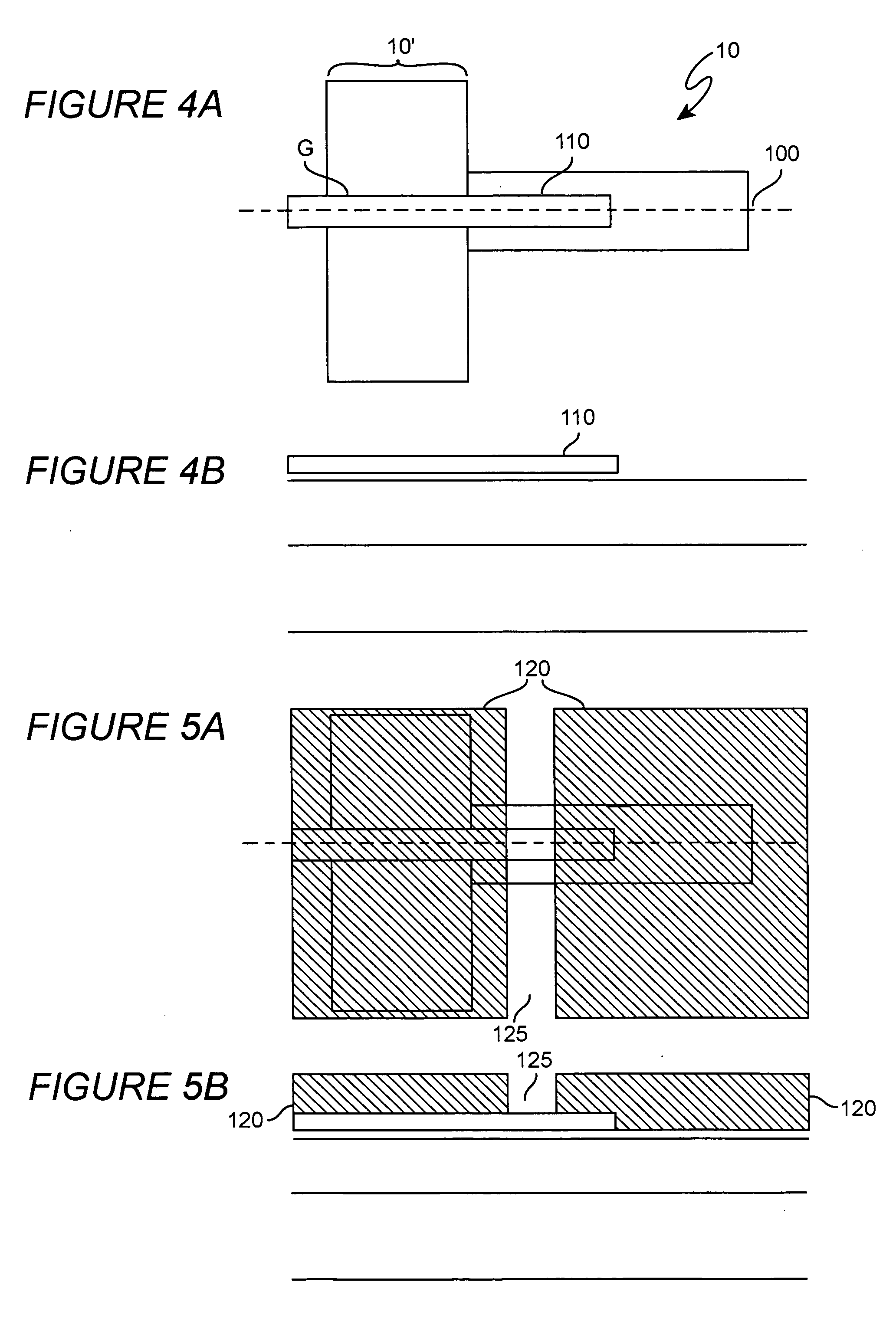

[0017] Referring now to the drawings, and more particularly to FIG. 2 and FIG. 3, plan and cross-sectional views of a DTMOSFET in accordance with the invention is shown. While a PMOS transistor is shown, it is to be understood that the principles of the invention are equally applicable to NMOS devices simply by reversing the conductivity types of the illustrated regions. It should also be appreciated that the principles of the invention and the implementation thereof is completely independent of the design of the remainder of the transistor and performance enhancing structures such as halo and extension implants can be designed and implemented freely, consistent with the practice of the invention. Therefore, such possible structures which are not important to the practice of the invention are to be considered as represented in the simplified form of the source S and drain D illustrated in the Figures.

[0018] The transistor in accordance with the invention is preferably formed on a s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More