Patents

Literature

56results about How to "Minimize skew" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Method and apparatus for reducing power consumption in digital electronic circuits

InactiveUSRE36839E1Reduce power consumptionMinimize powerEnergy efficient ICTSolid-state devicesPower controllerData stream

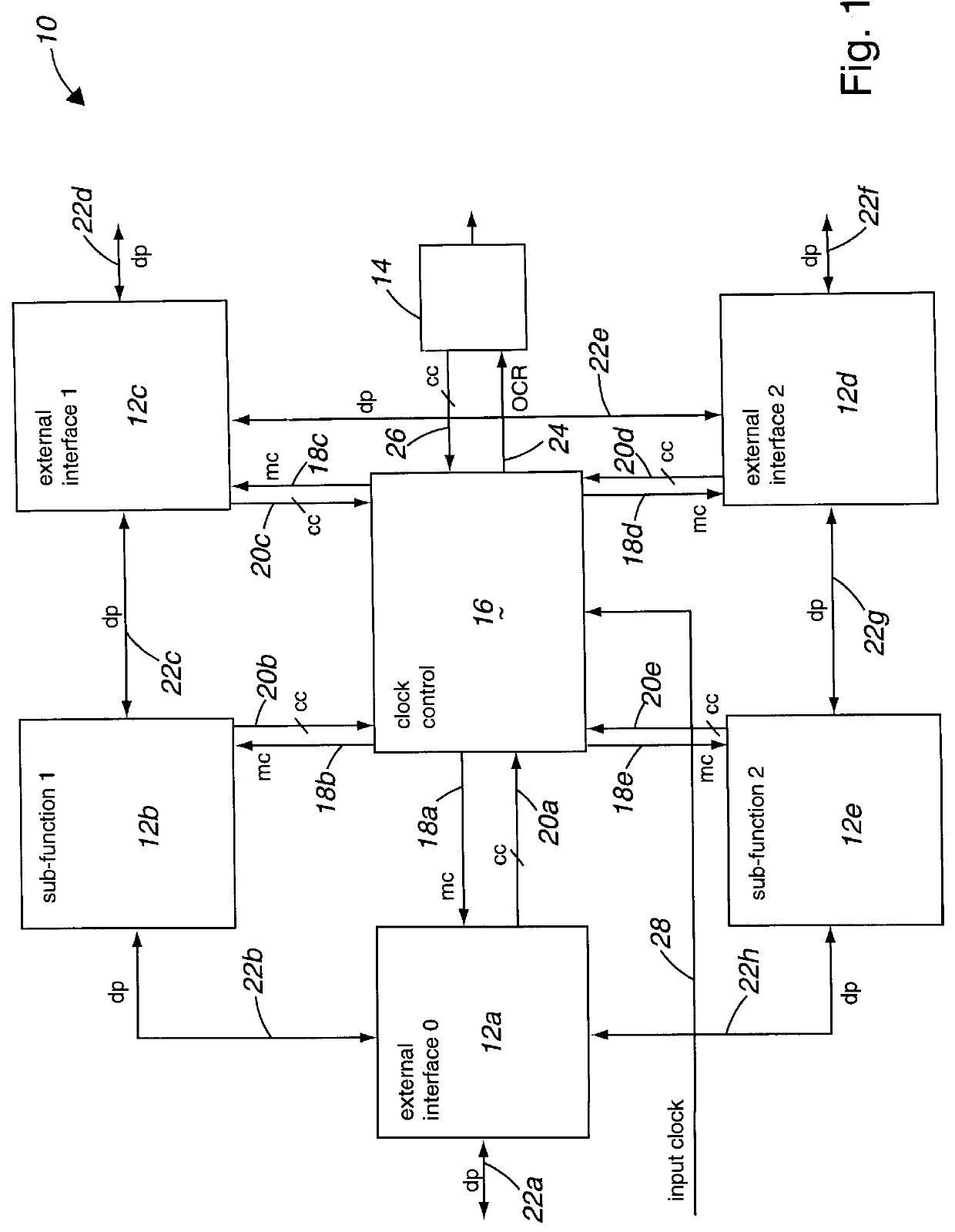

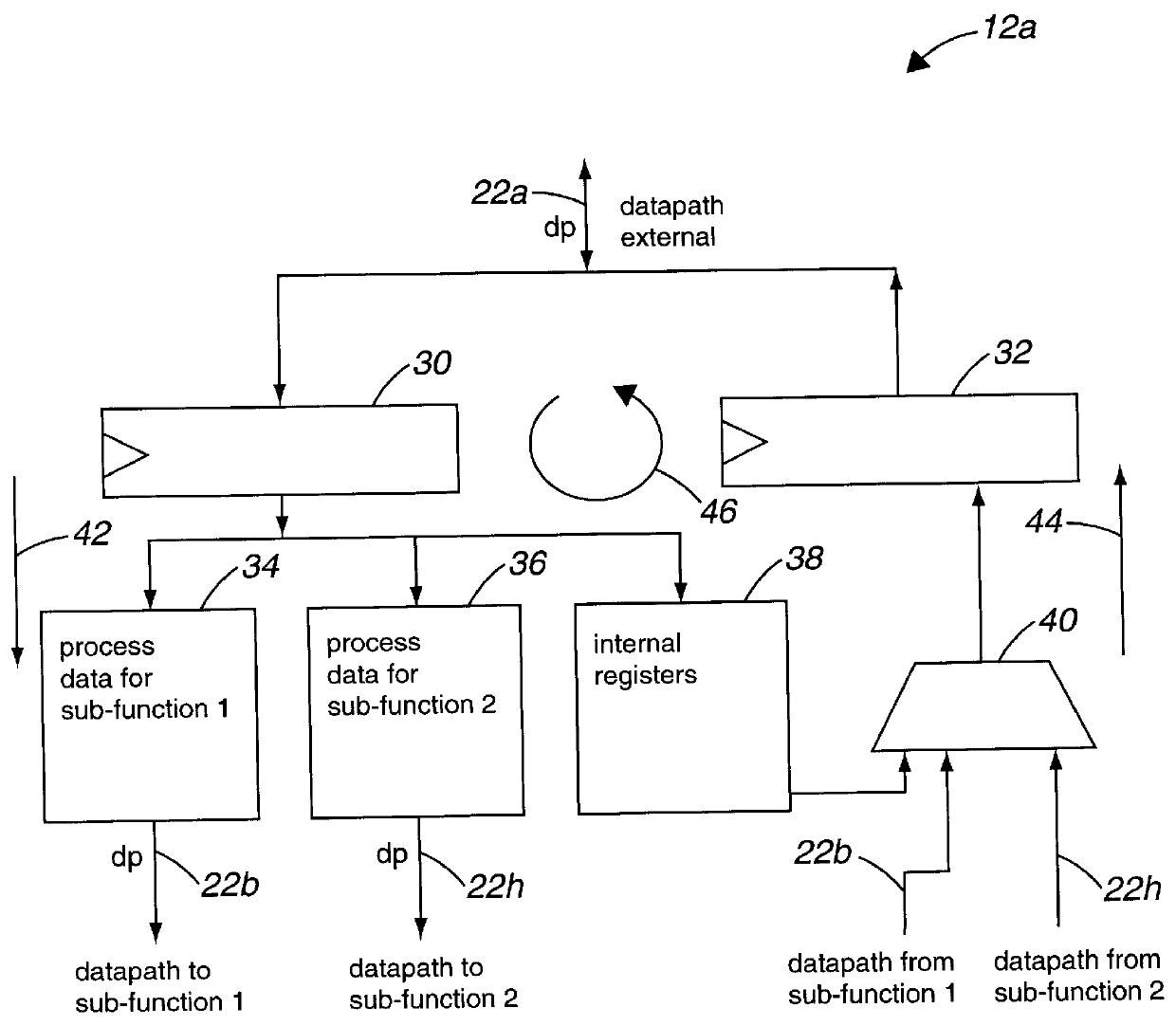

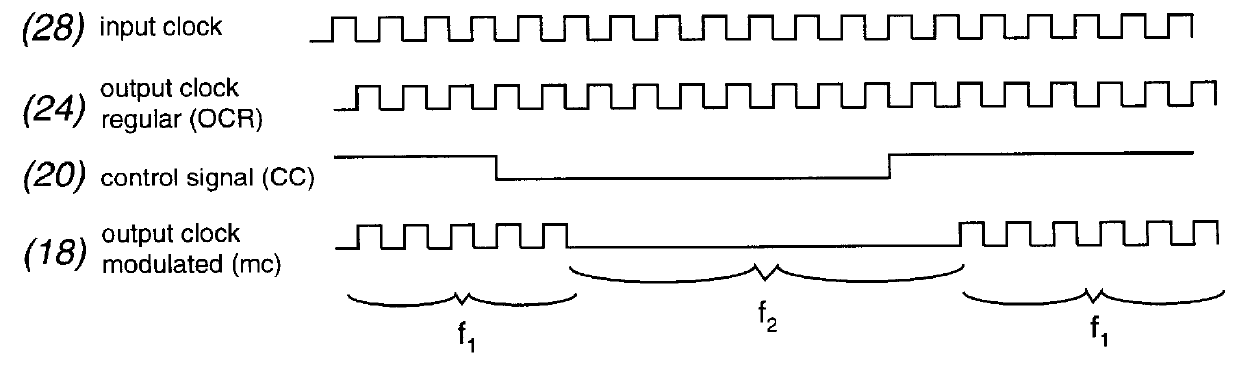

An integrated circuit with power conservation includes a number of functional blocks, each of which includes a digital circuitry and at least one output control line, and a power controller coupled to the control lines. The output control lines develop clock control signals based upon a functional block's knowledge of the direction of data flow. The power controller the reduces power by deactivating functional blocks that are not needed as indicated by the clock control signals. More specifically, a system with power conservation includes a number of functional blocks capable of processing data, each of the functional blocks including a modulated clock input and N+1 clock control lines which reflect the direction of data flow, where N is a number of neighbors of a particular functional block, and a clock controller having an input clock, the clock controller being coupled to the modulated clock inputs and the clock control lines of the functional blocks. The clock controller is operative to modulate the input clock in accordance with the signals on the clock control lines to provide modulated clocks to each of the plurality of functional blocks. A method for reducing power consumption includes the steps of: a) receiving control signals from a number of functional blocks; b) selectively deactivating a particular functional block upon a request from that functional block or from another functional block; and c) activating the particular functional block upon a request from another functional block.

Owner:CONVERSANT INTPROP MANAGEMENT INC

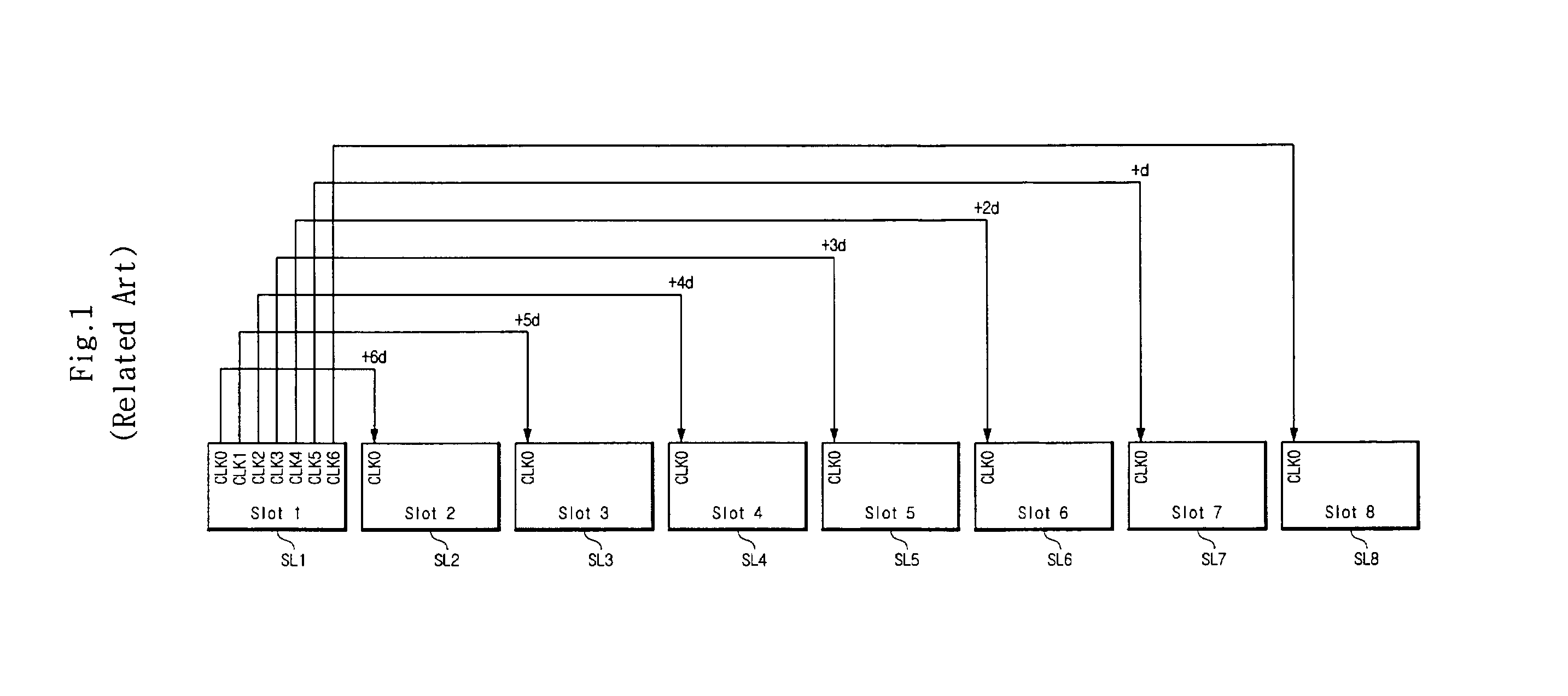

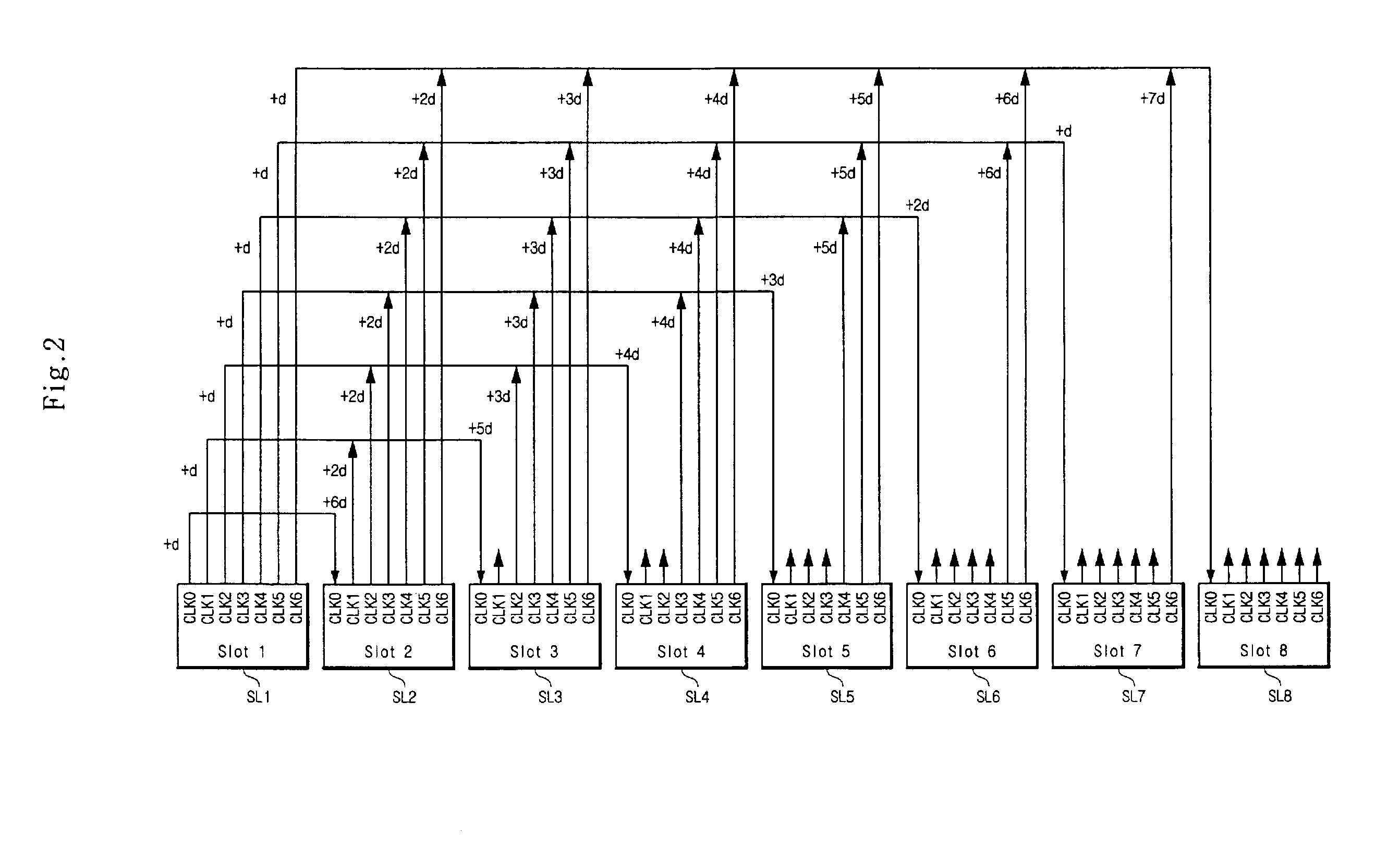

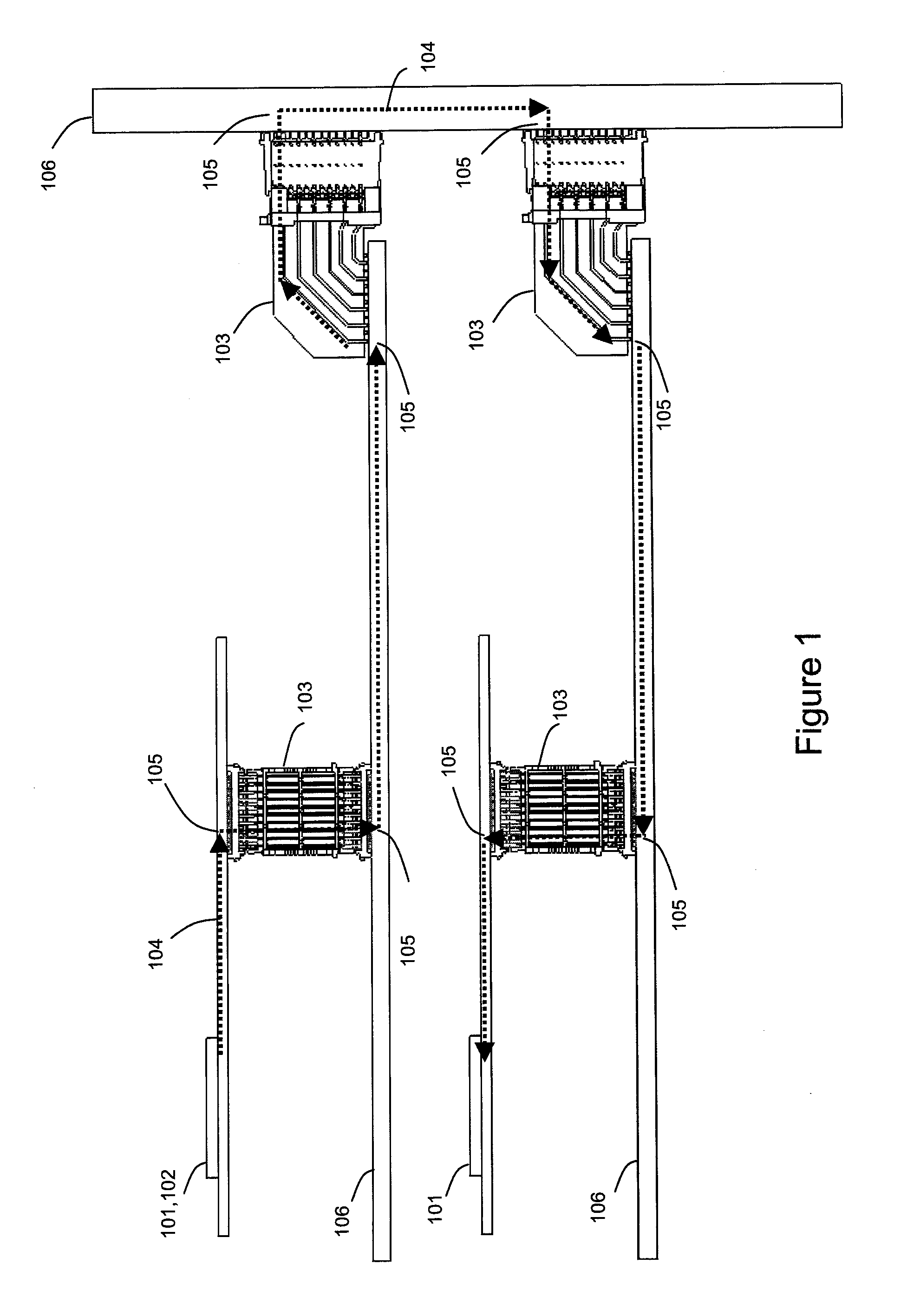

Clock distribution device and method in compact PCI based multi-processing system

InactiveUS7100066B2Skew of the clock transmitted to each slot may be minimizedMinimize skewTelevision system detailsPulse automatic controlHandling systemEmbedded system

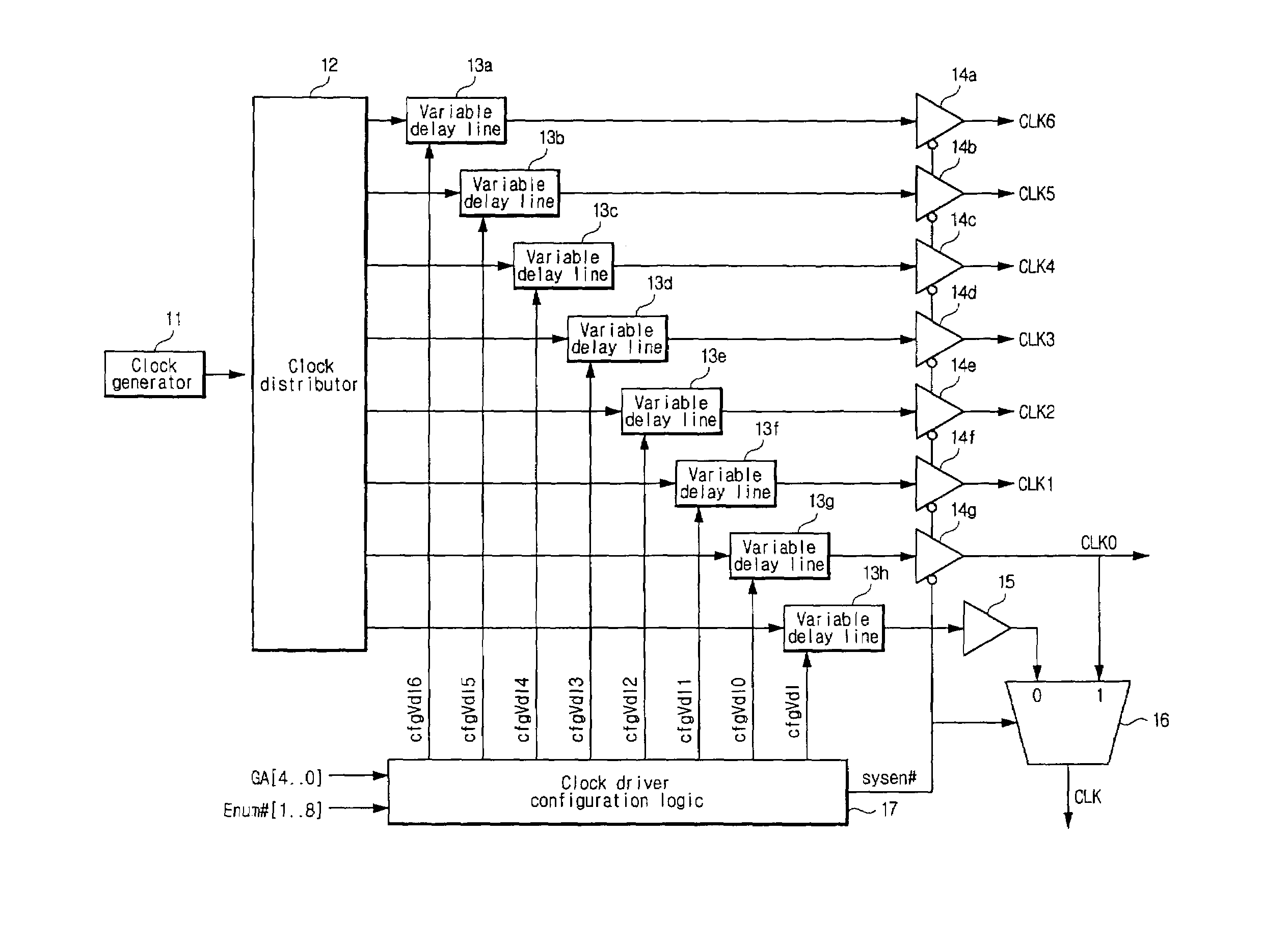

Disclosed is a clock distribution device and method in a compact PCI system based multi-processing system. A compact PCI based multi-processing system preferably includes processing signals upon mounting various circuit boards on multiple slots, even if the location of the system slot is varied, the skew of clocks transmitted to the other slots may be minimized. Accordingly, the system may be configured in a flexible manner because of such variability of the system slot's location. Further, the system may be efficiently repaired and maintained because it is possible to easily and quickly take measures in response to any failure occurring on the board mounted on the system slot.

Owner:LG ERICSSON

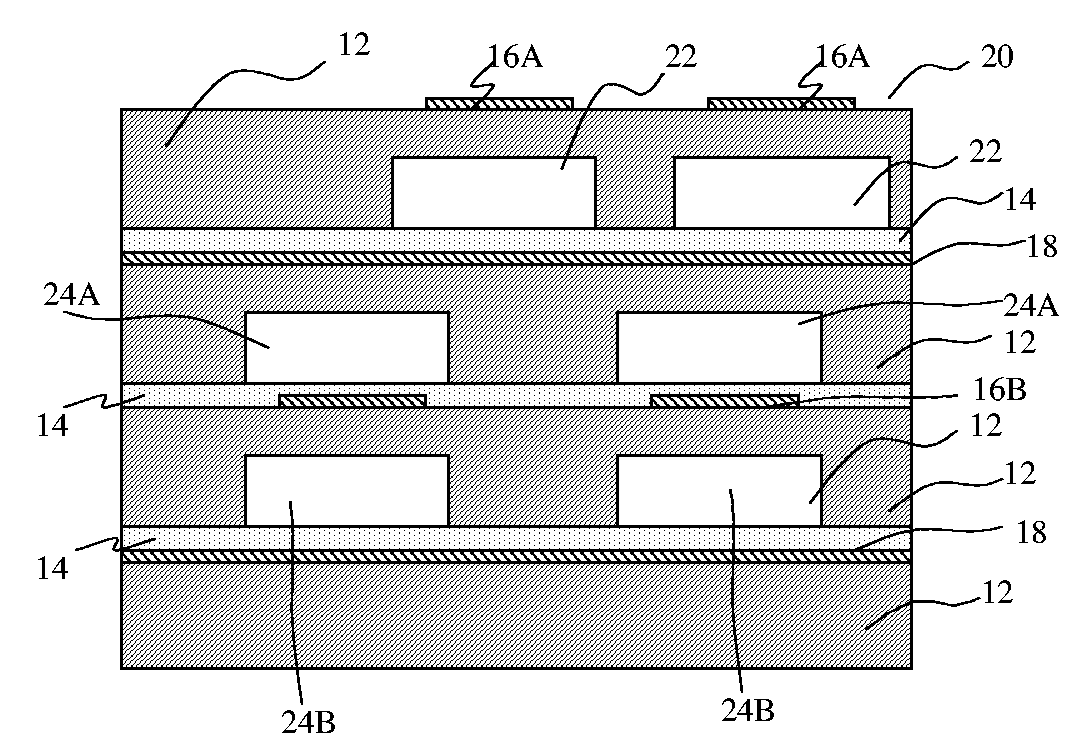

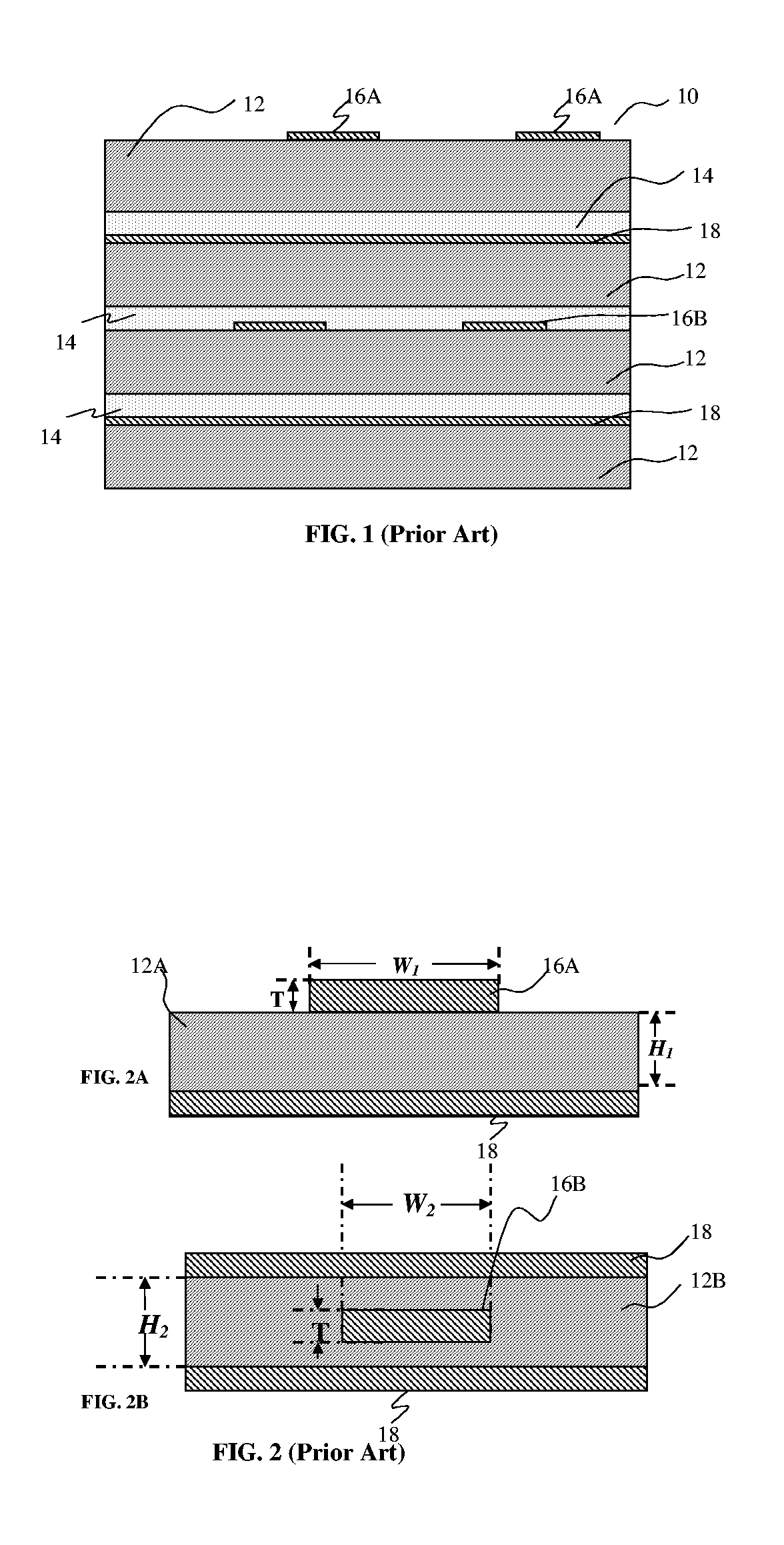

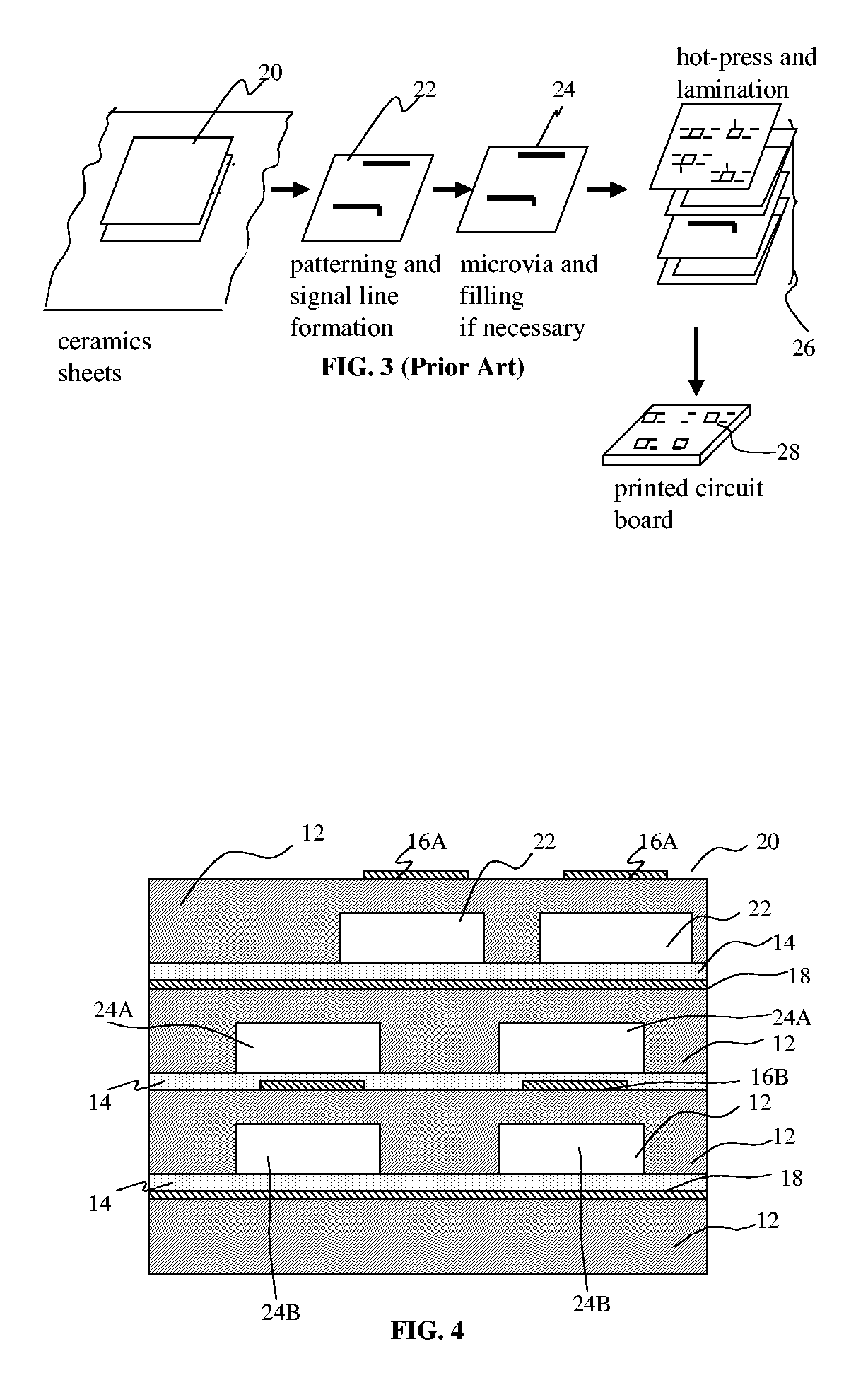

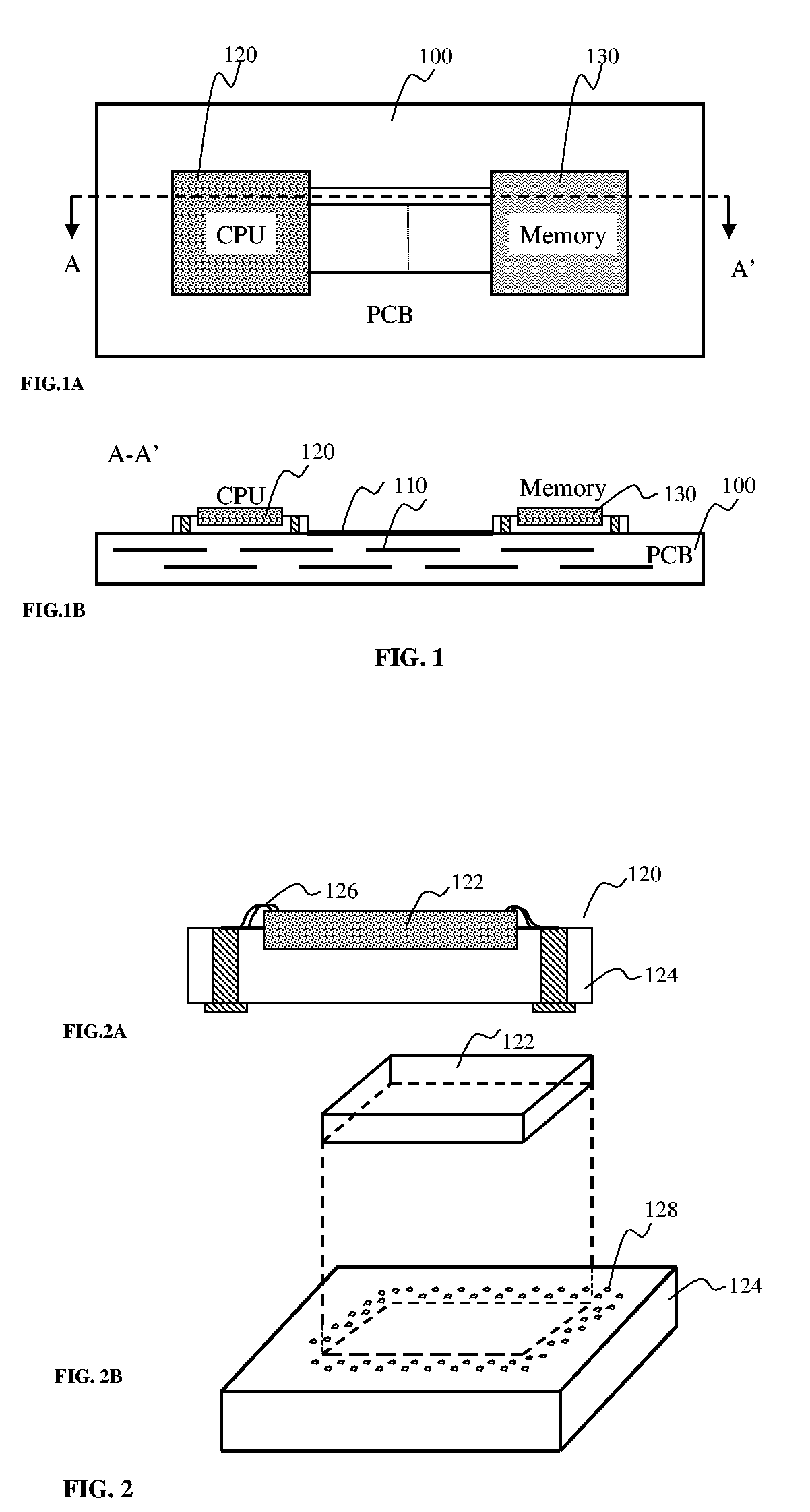

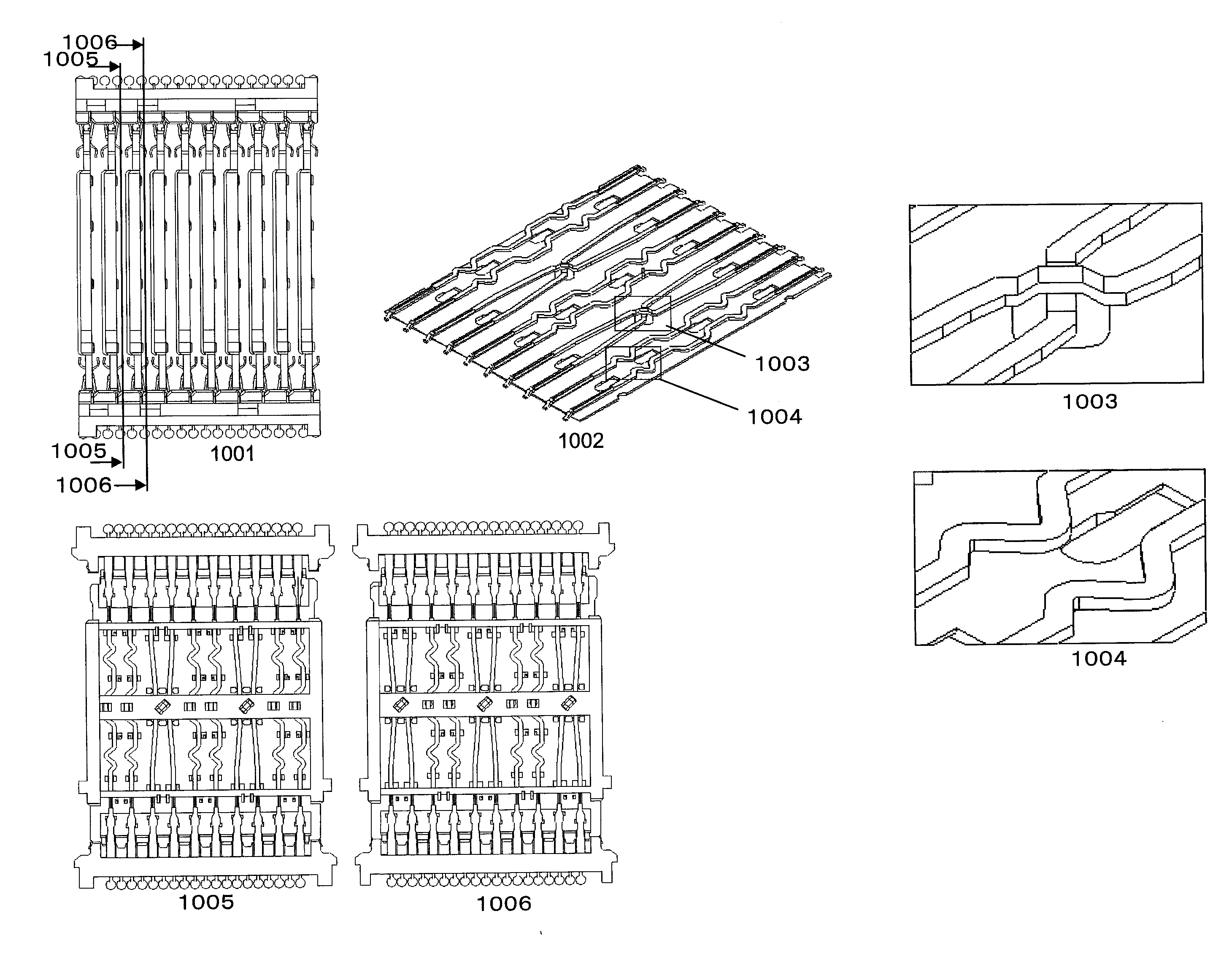

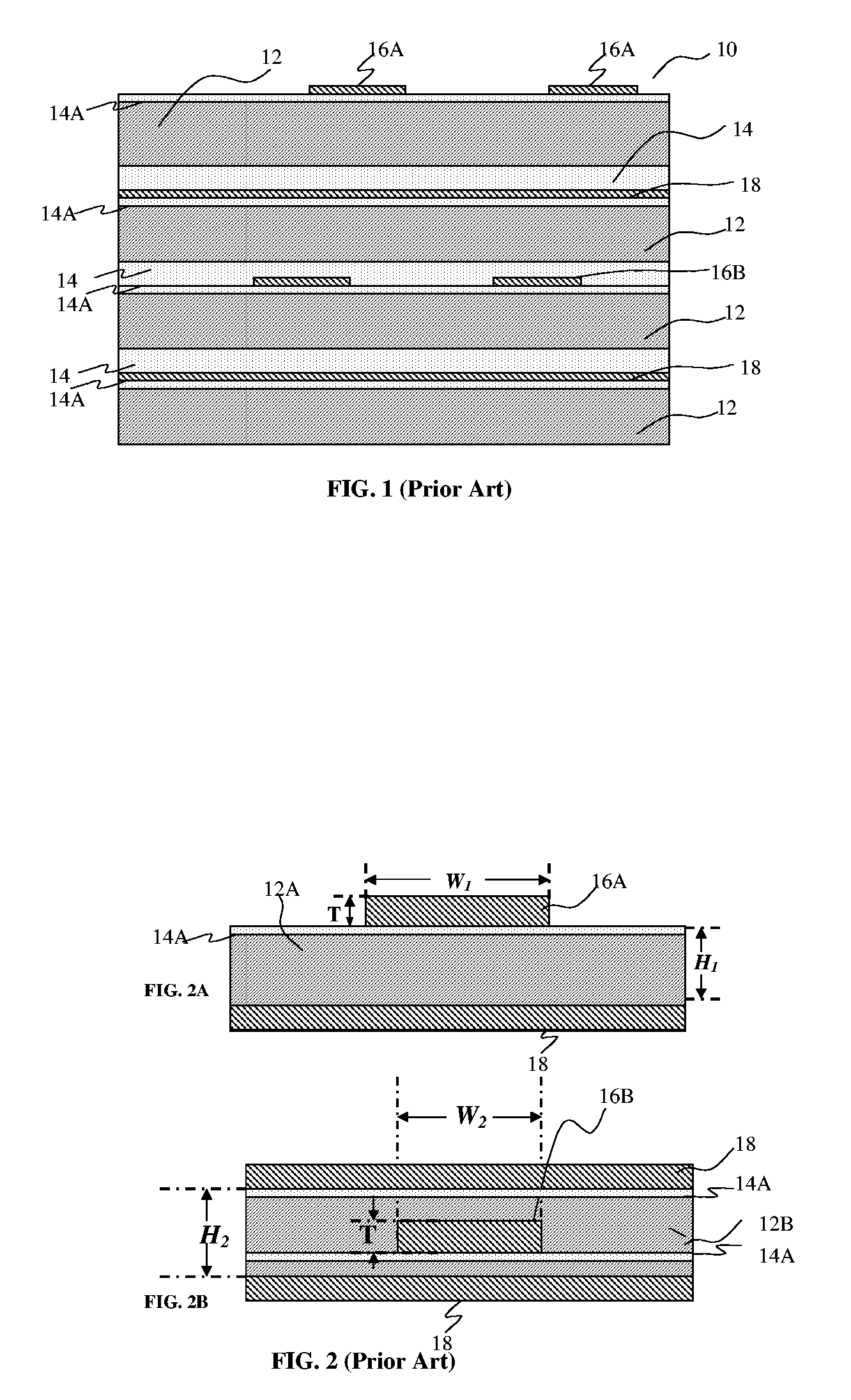

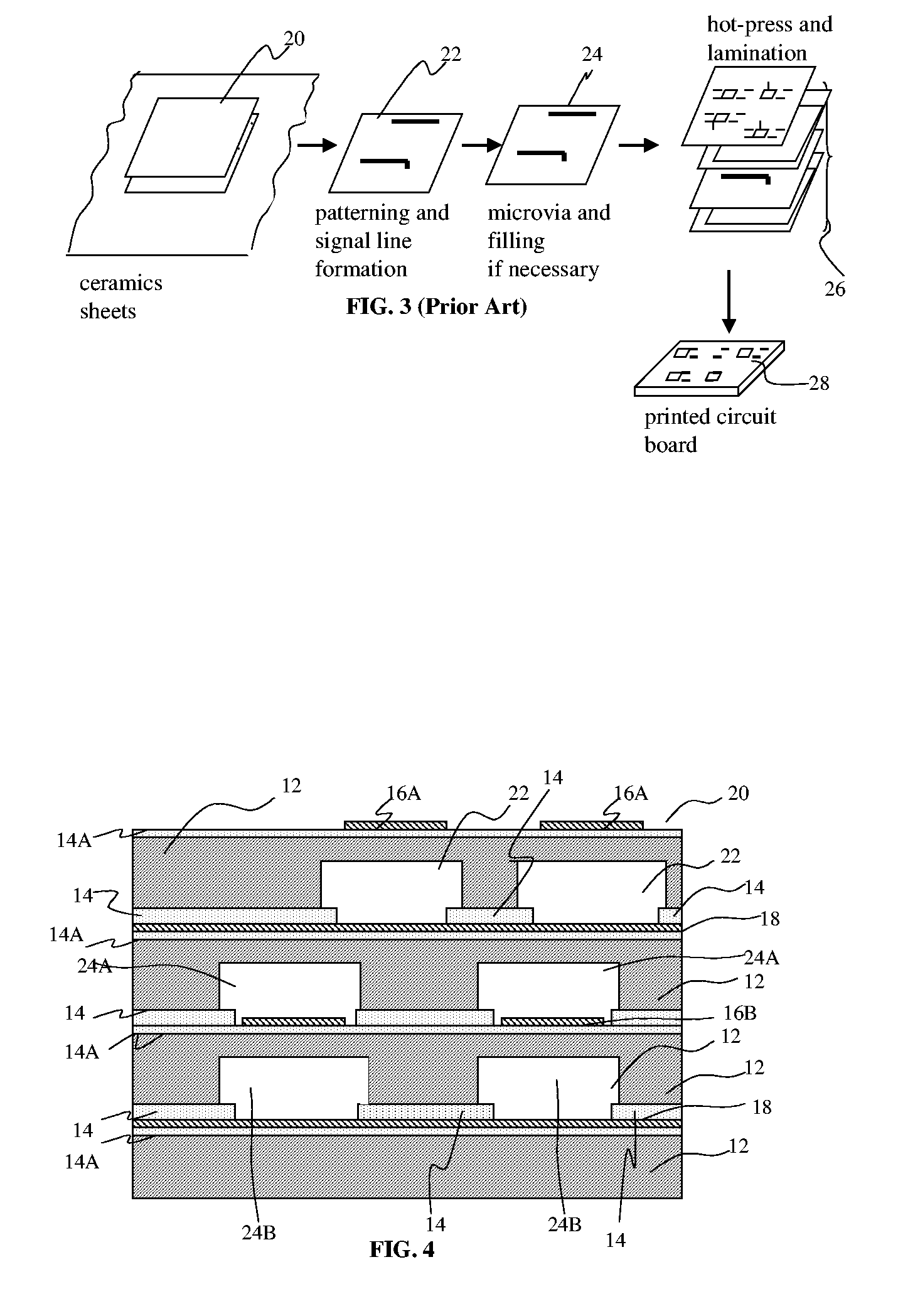

High-Speed Printed Circuit Boards (PCBs) and Manufacturing

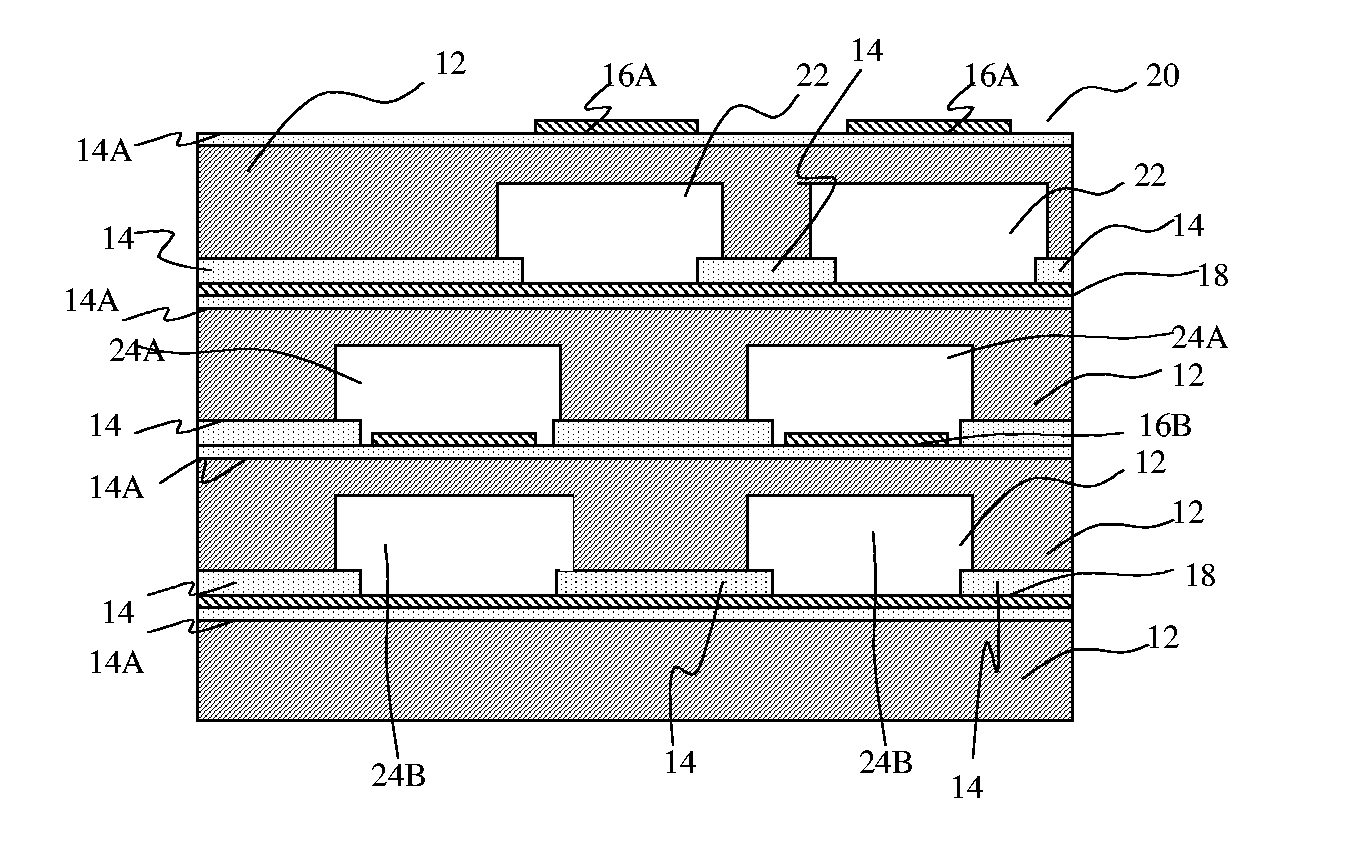

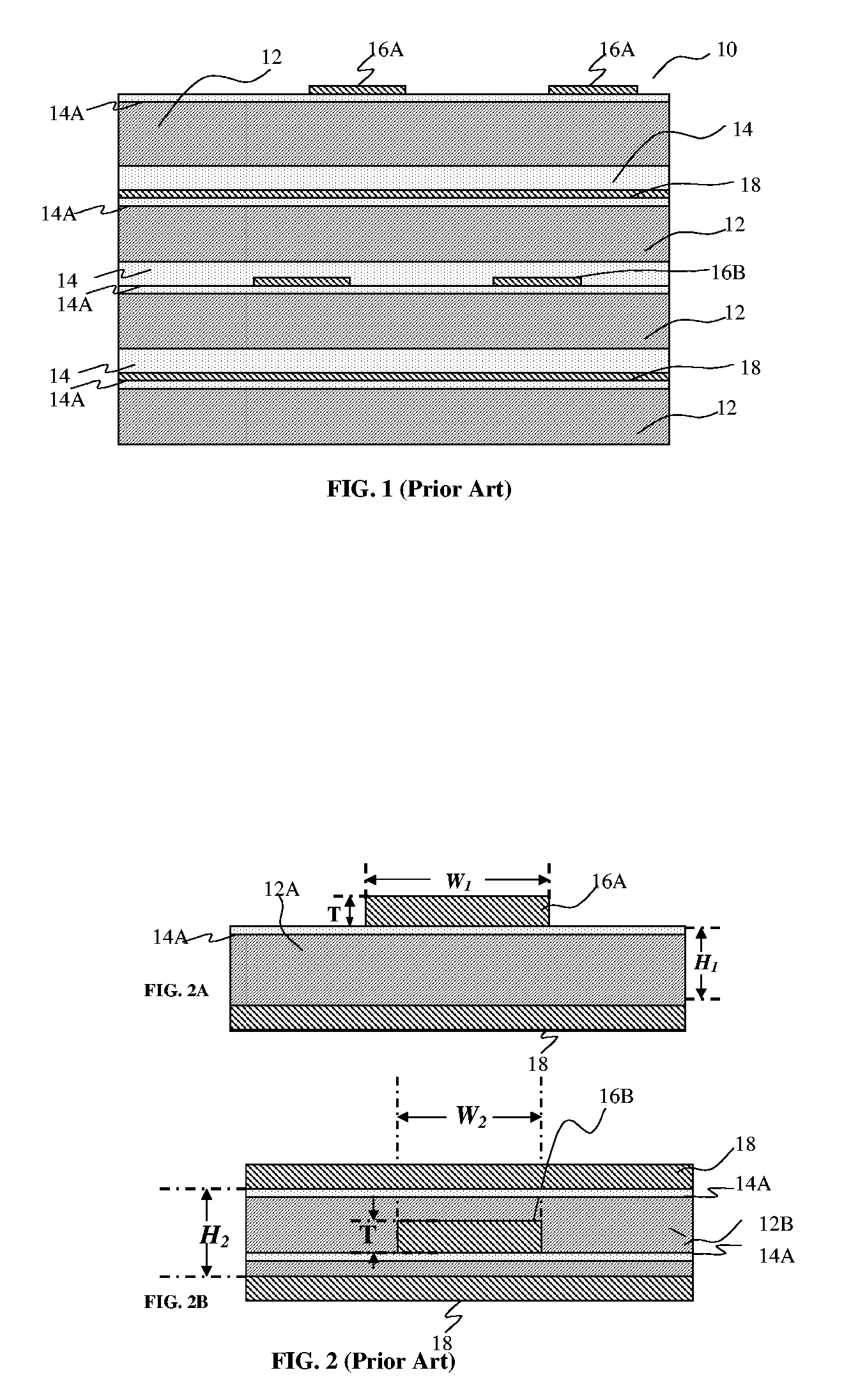

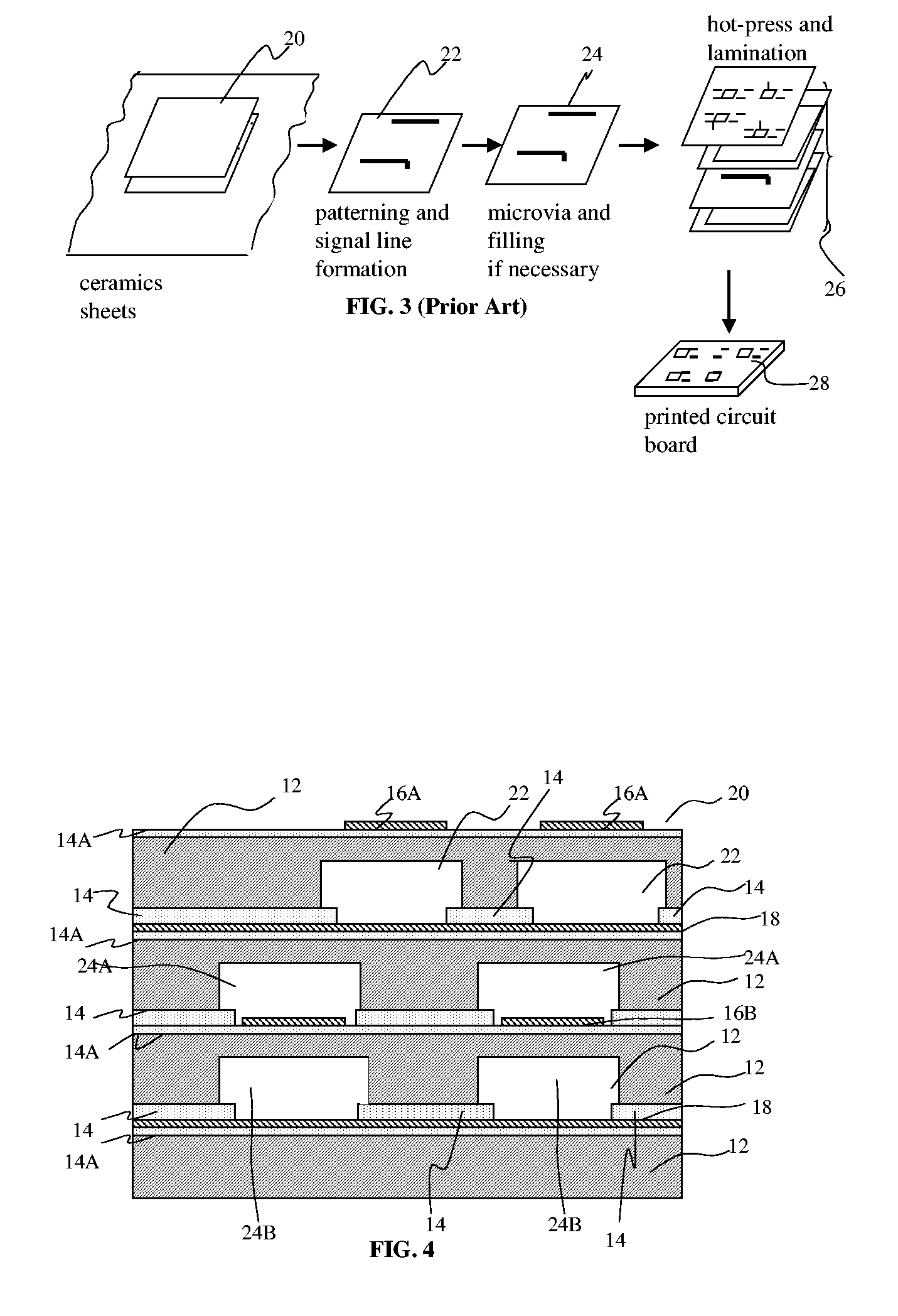

ActiveUS20060028305A1Reduce effective dielectric constant effective dielectricReduce effective dielectric effective dielectric lossMultiple-port networksHigh frequency circuit adaptationsDielectricEngineering

High speed printed circuit boards (PCBs) are disclosed comprising a dielectrics systems with the back-side trenches, prepregs, signal lines and ground-plans, wherein the signal line and ground-plan are located on the dielectrics. Using of the open trenches in the substrate help to reduce the microwave loss and dielectric constant and thus increasing the signal carrying speed of the interconnects. Thus, according to the present invention, it is possible to provide a simple high speed PCB using the conventional material and conventional PCB manufacturing which facilitates the design of circuits with controlled bandwidth based on the trench opening in the dielectrics, and affords excellent reliability. According to this present invention, high speed PCB with the interconnect system contains whole portion or portion of interconnects for high speed chips interconnects and that have have the dielectric system with opened trench or slot to reduce the microwave loss.

Owner:BANPIL PHOTONICS

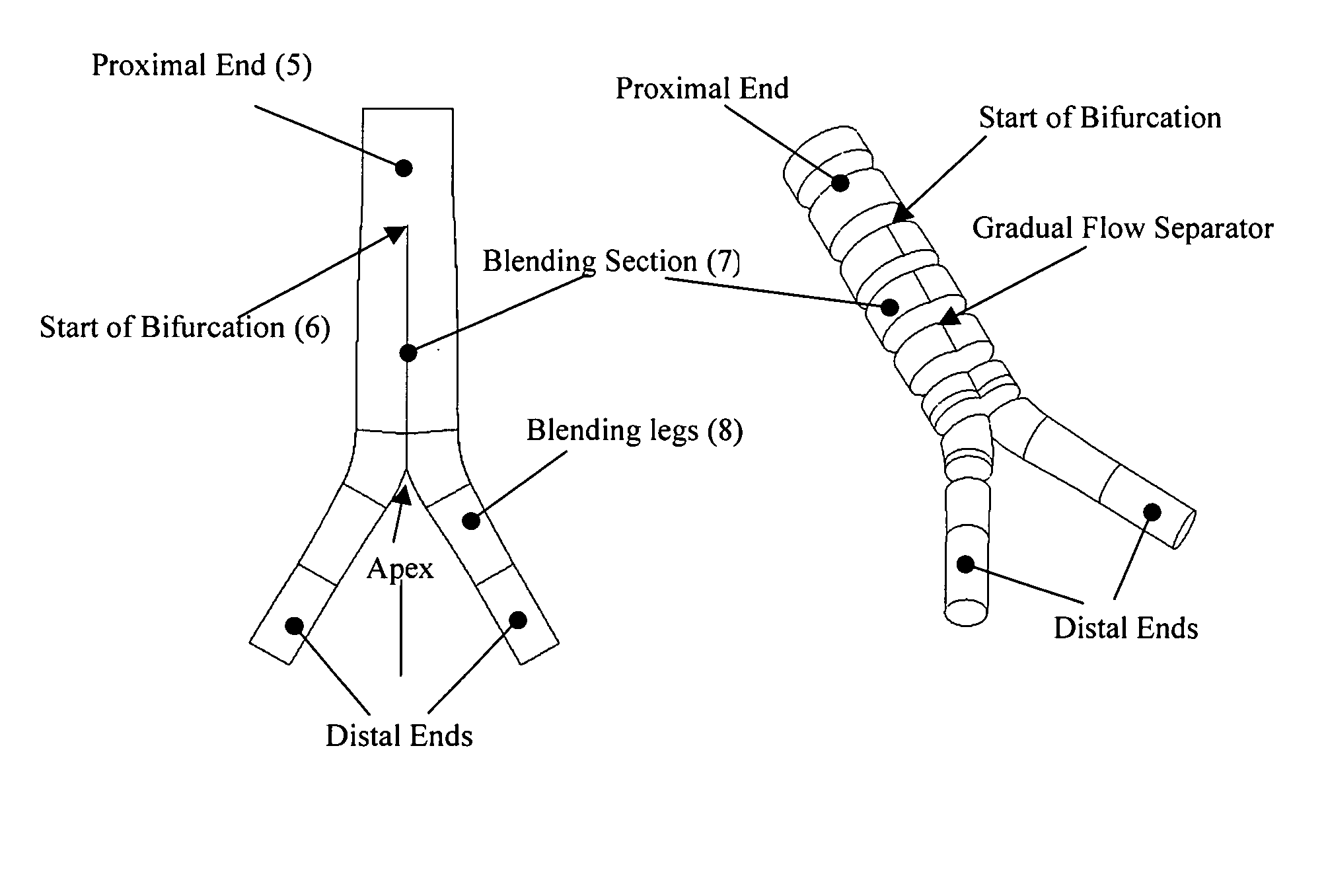

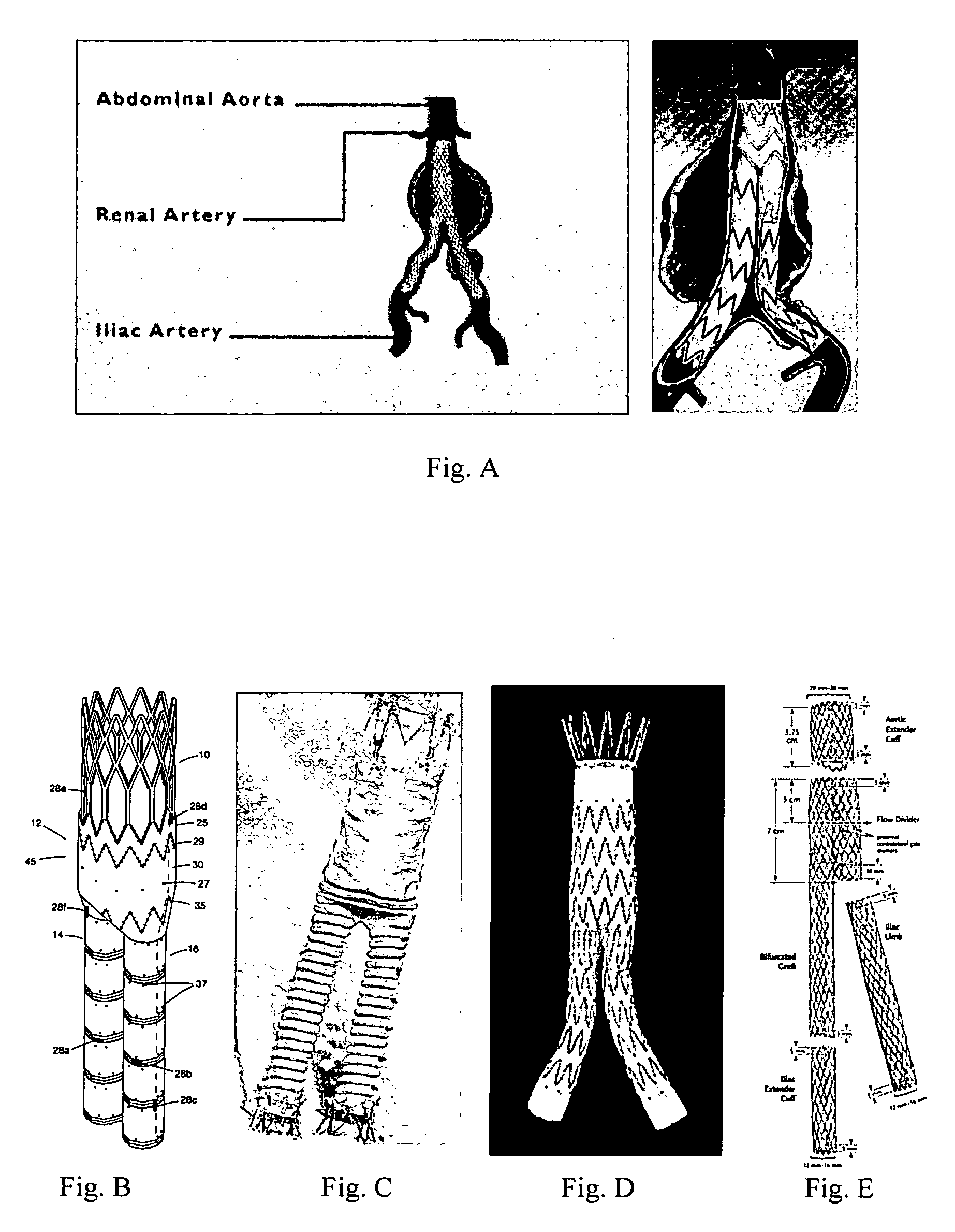

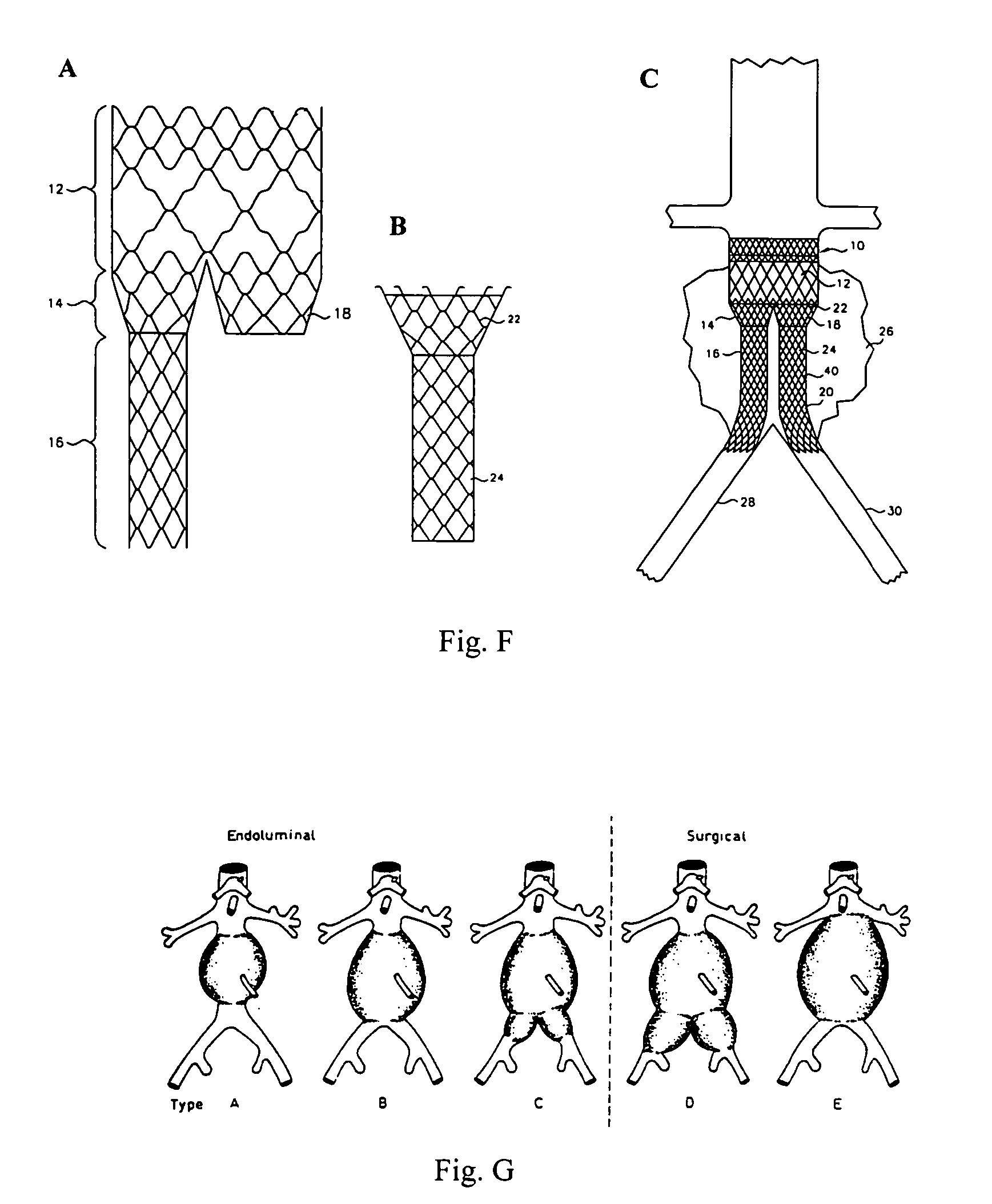

Vascular graft

InactiveUS20060229709A1Reduce the cross-sectional areaEliminate needStentsBlood vesselsVascular graftingVascular graft

A vascular graft comprising a proximal section, iliac distal legs and a bifurcation blending section (7) between the proximal section and the distal legs. The cross-sectional area of the proximal section at the bifurcation point is less than or equal to the sum of the two cross sectional areas of both iliac legs. The blending section (7) generates a smooth transition from the proximal section to both iliac legs which minimizes wave reflections by ensuring that the area ratio at the bifurcated junction (7) is as close to unity or greater than unity as possible. The blending section (7) defines a first lumen for fluid flow from the proximal section into the first distal leg, and a separate second lumen for fluid flow from the proximal section into the second distal leg. The two lumen are separated by means of a gradual flow which separates the fluid flow from the proximal section into each lumen. The distal legs are connected to the blending section (7) at the bifurcation region to form a substantially “Y”-shaped graft.

Owner:LIMERICK UNIV OF

High-speed flex printed circuit and method of manufacturing

ActiveUS7663064B2Reduce effective dielectric constant and effective dielectric lossHigh bandwidthPrinted circuit assemblingPrinted circuit aspectsElectricityMicrowave

Multilayer high speed flex printed circuit boards (FLEX-PCBs) are disclosed including a dielectrics systems with the back-side trenches, adhesives, signal lines and ground planes, wherein the signal line and ground plane lane are located on the dielectrics. Using of the open trenches in the substrate help to reduce the microwave loss and dielectric constant and thus increasing the signal carrying speed of the interconnects. Thus, according to the present invention, it is possible to provide a simply constructed multiplayer high speed FLEX-PCB using the conventional material and conventional FLEX-PCB manufacturing which facilitates the design of circuits with controlled bandwidth based on the trench opening in the dielectrics, and affords excellent connection reliability. As the effective dielectric constant is reduced, the signal width is required to make wider or the dielectric thickness is required to make thinner keeping fixed characteristics impedance. The fundamental techniques disclosed here can also be used for high-speed packaging.

Owner:BANPIL PHOTONICS

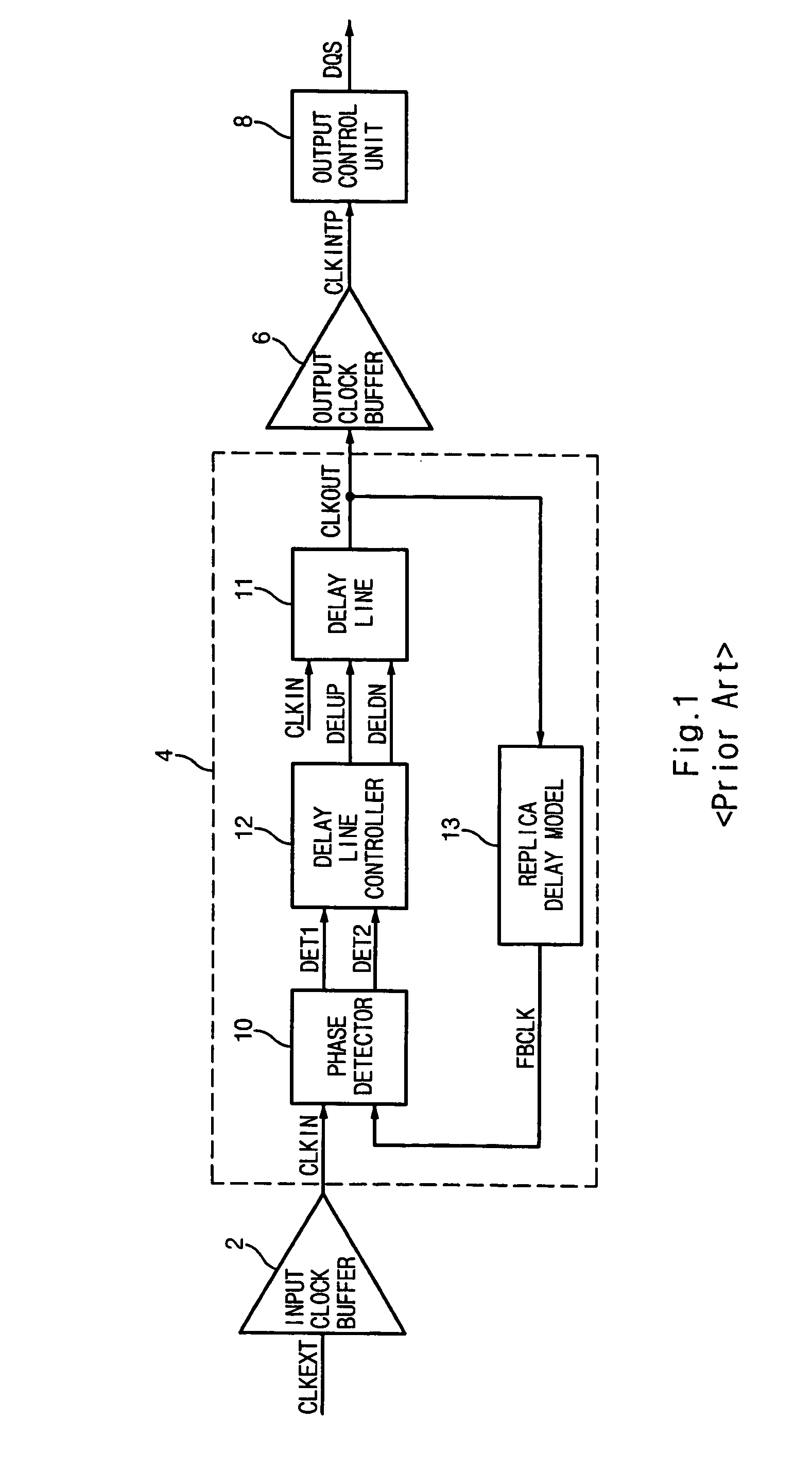

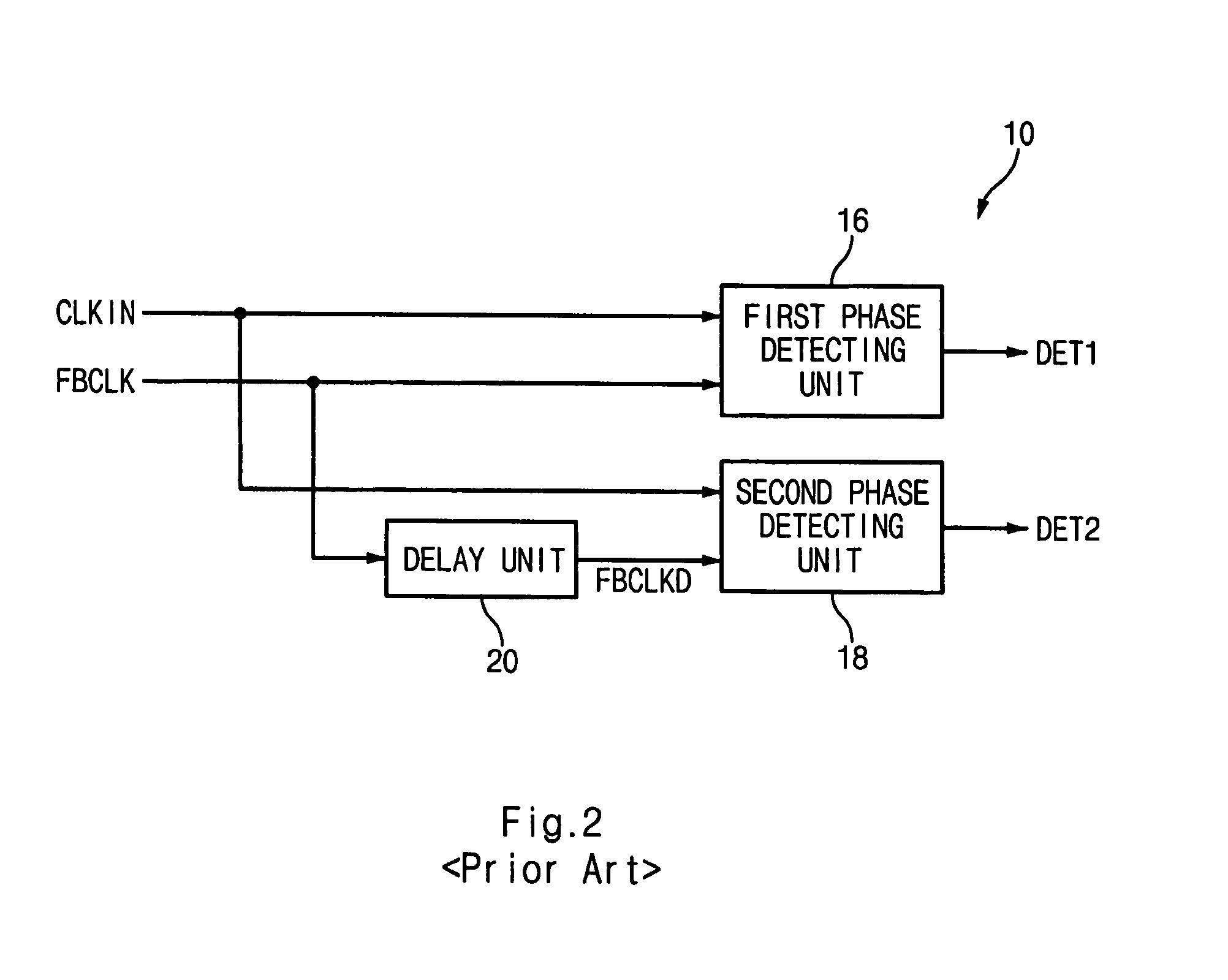

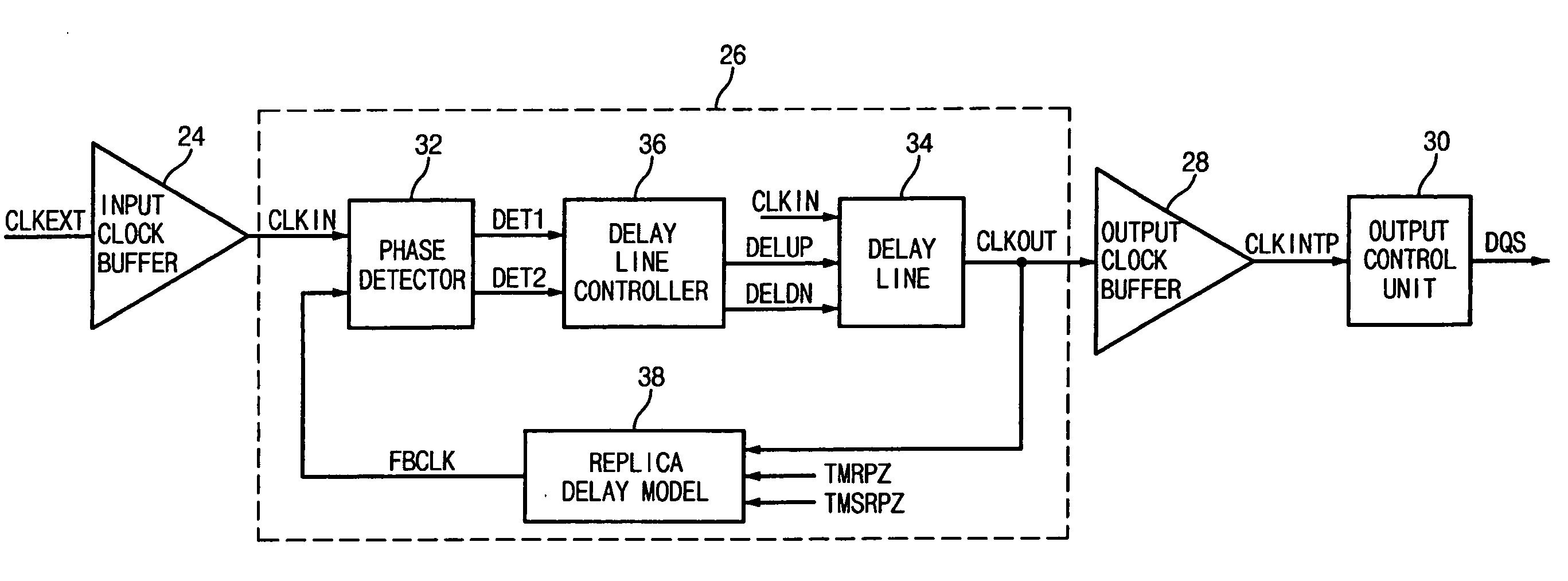

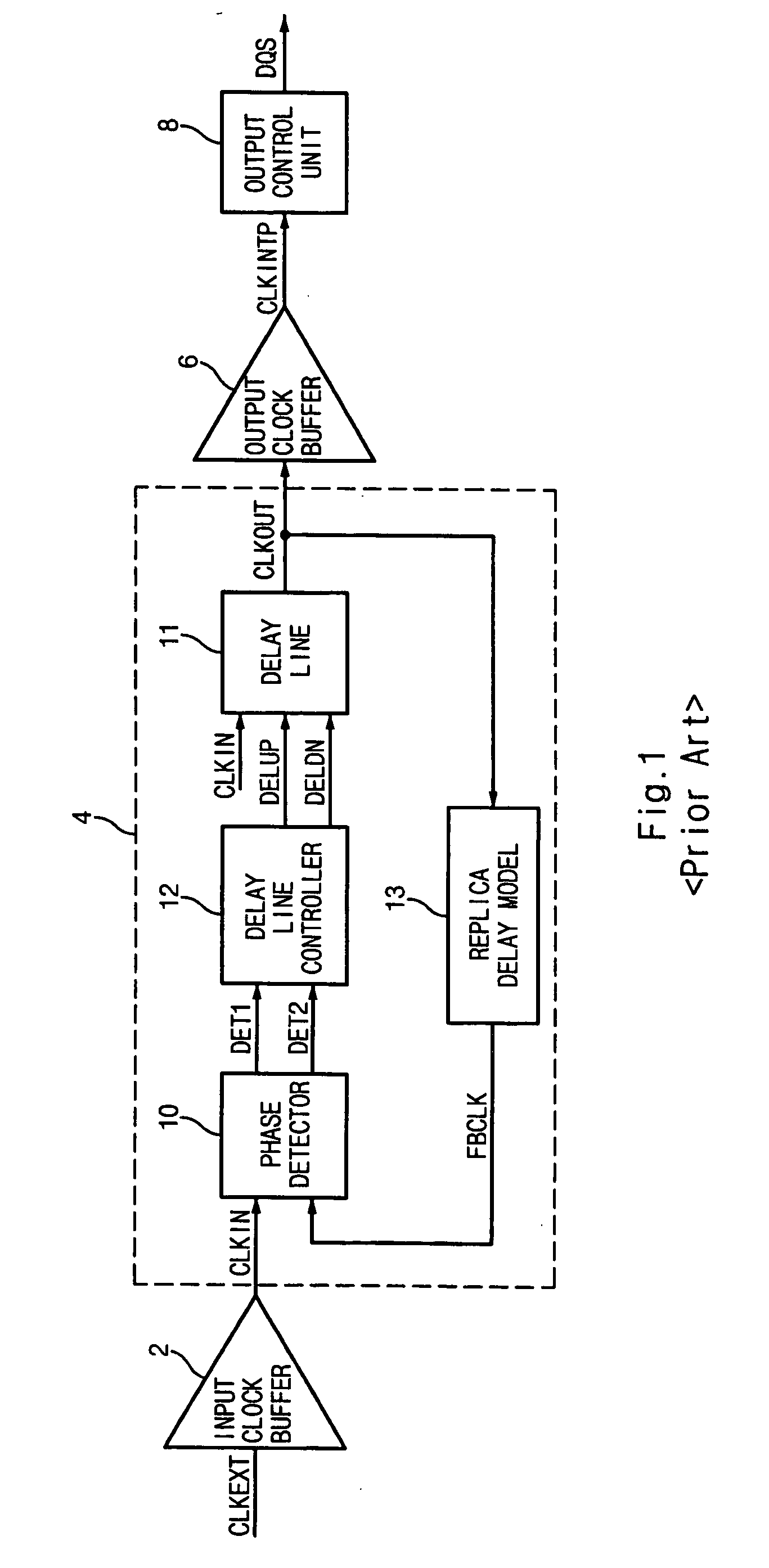

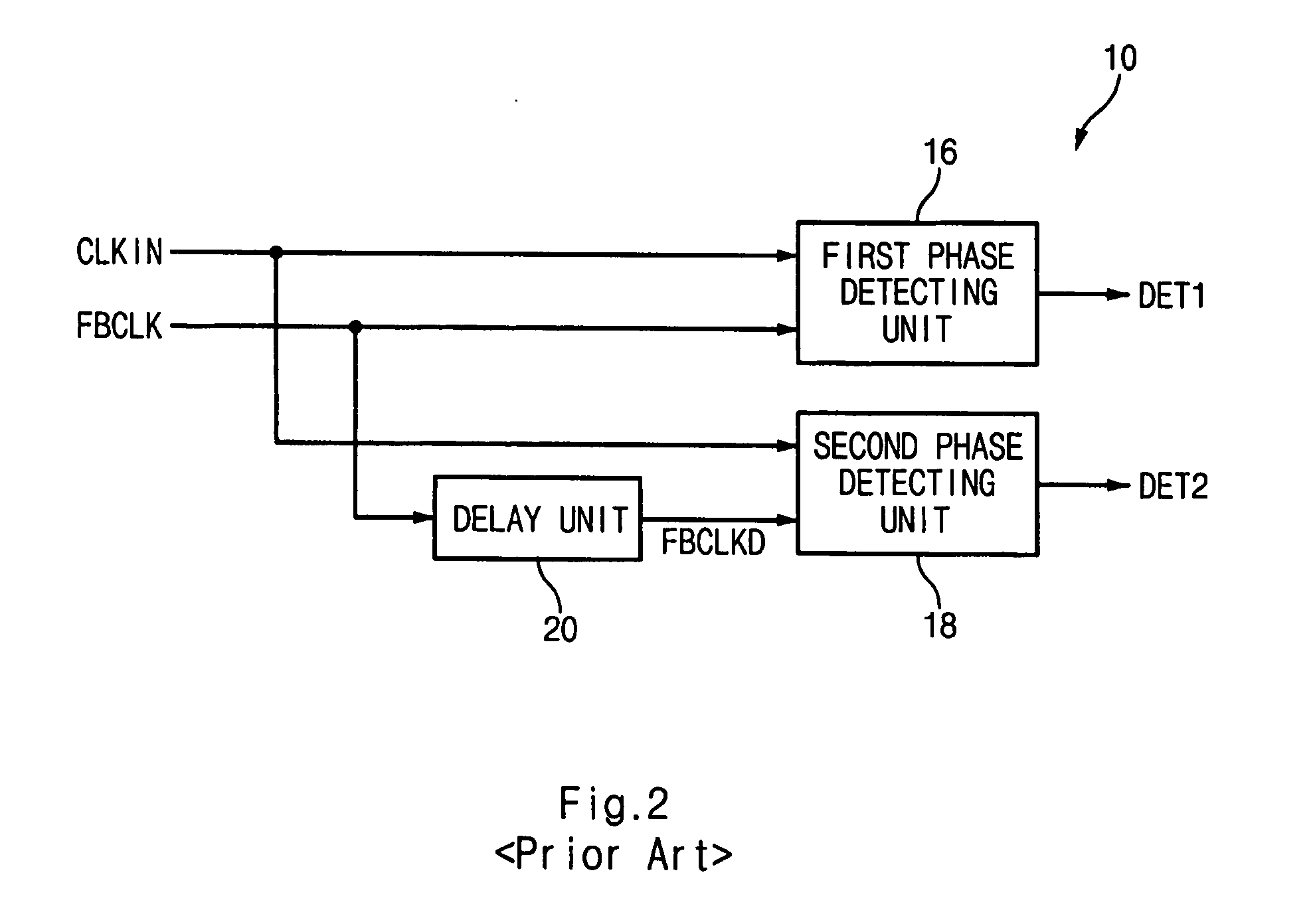

Memory device having delay locked loop

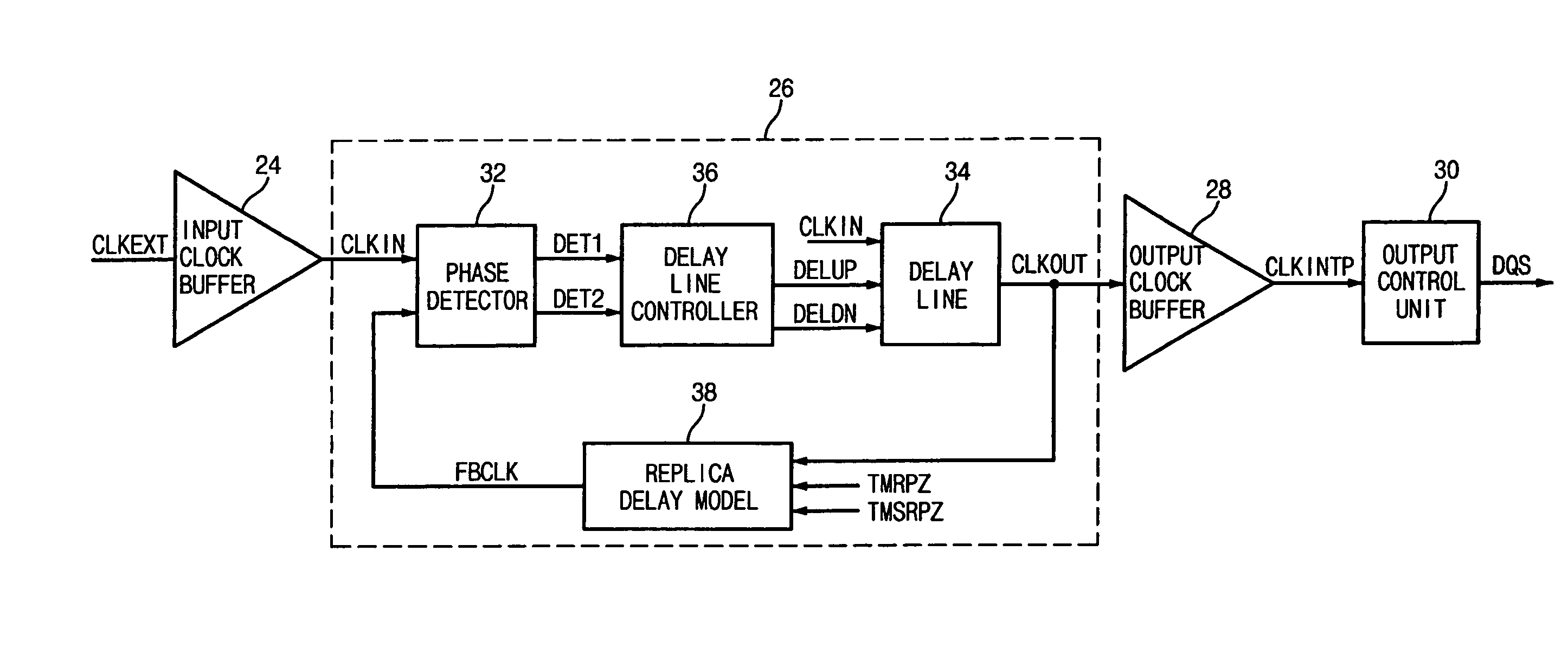

ActiveUS6985401B2Minimize skewPulse automatic controlServometer circuitsControl signalDelay-locked loop

A memory device minimizes the skew between an external clock and a DQS (or DQ) after the locking state by regulating a delay ratio of a replica delay model to compensate errors of process, temperature or voltage change. The memory device comprises: an input clock buffer for buffering an externally inputted external clock to generate an internal clock; a DLL for delaying the internal clock to synchronize a phase of the external clock with that of a DQS; an output clock buffer for buffering an output clock outputted from the DLL; and an output control unit for generating the DQS using a clock outputted from the output clock buffer. Here, the DLL comprises a replica delay model for modeling delay factors of the input clock buffer and other delay factors until the output clock outputted from the delay line is outputted to the outside of a chip, and for regulating a delay ratio in response to a plurality of control signals inputted externally in a test mode.

Owner:SK HYNIX INC

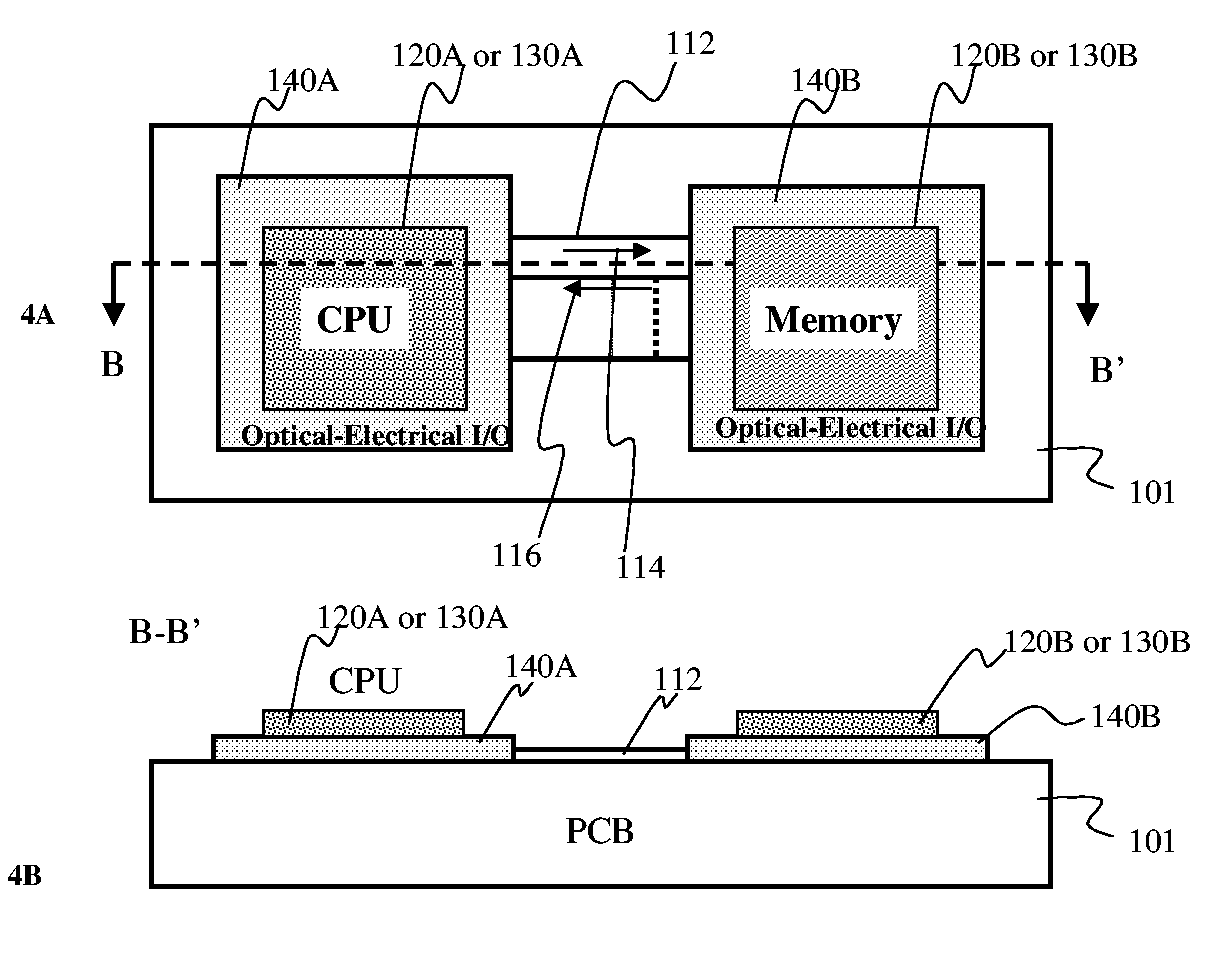

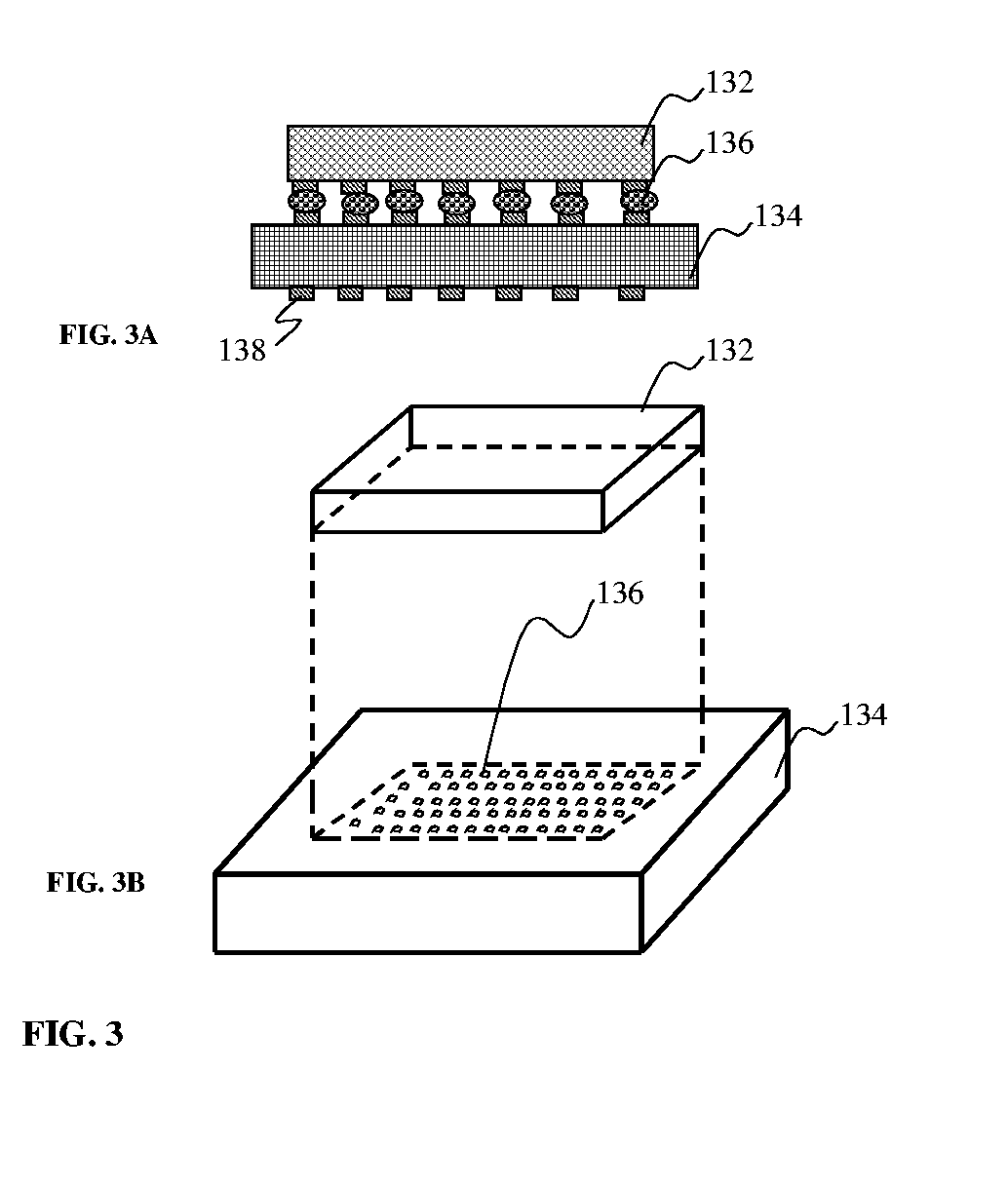

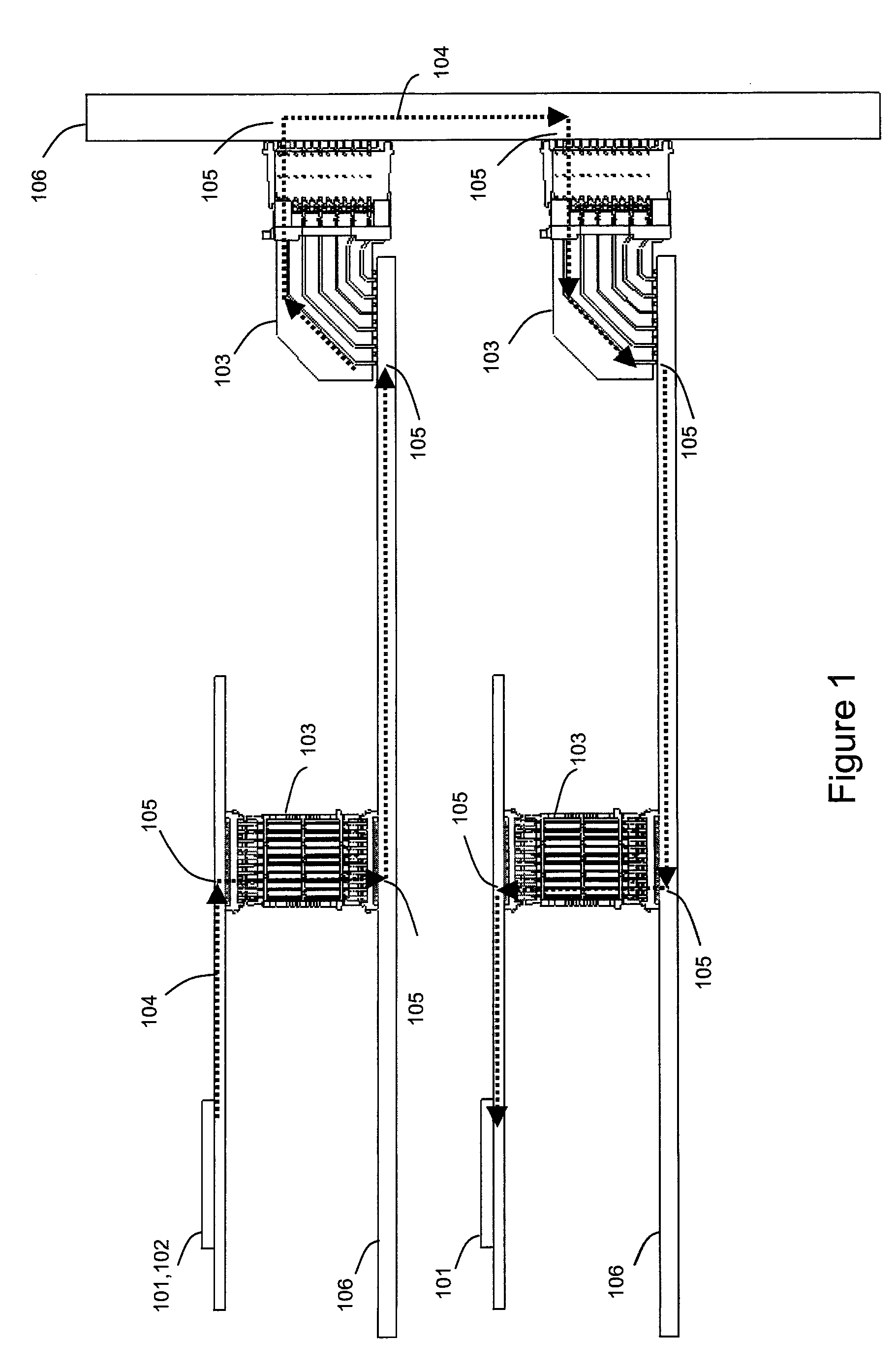

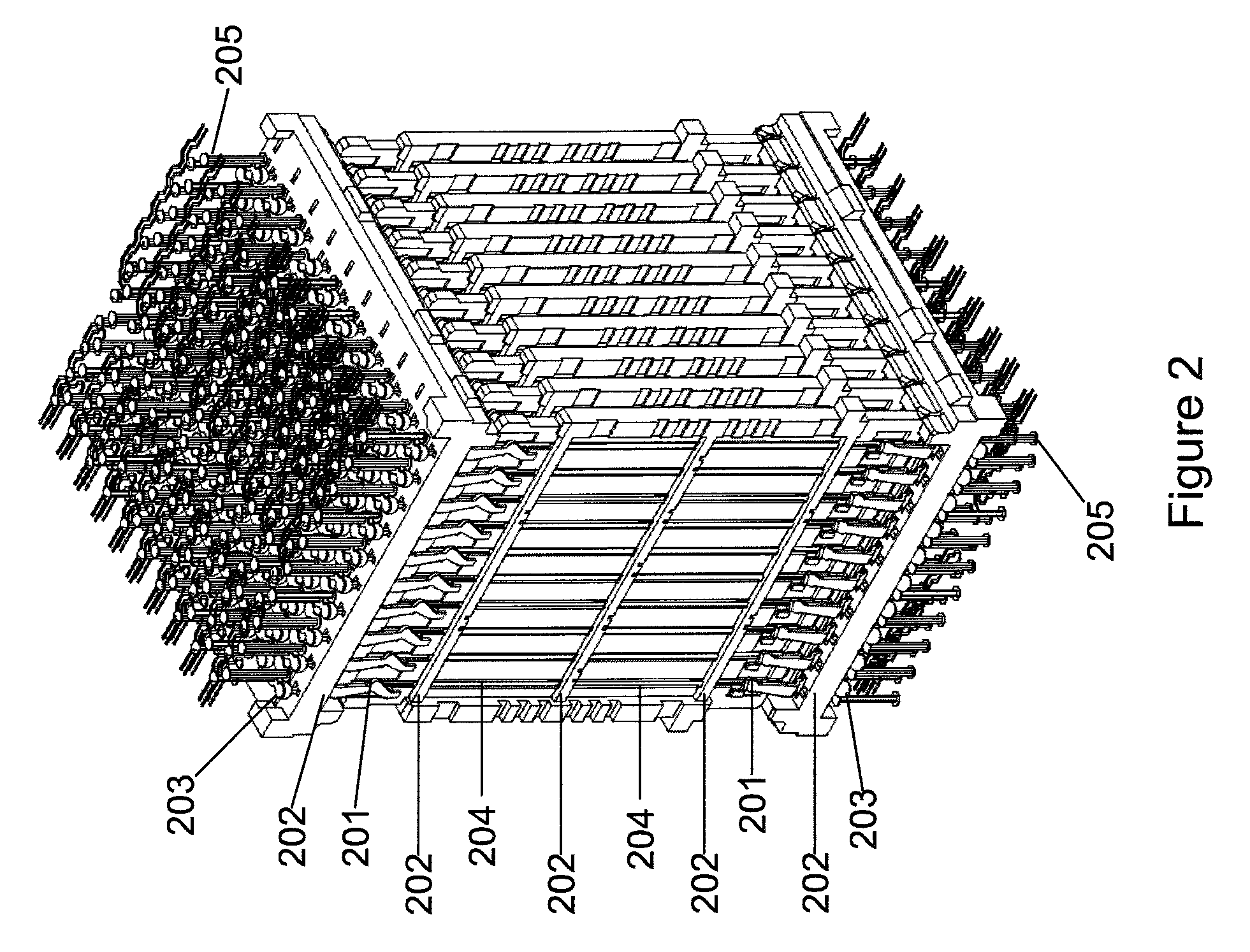

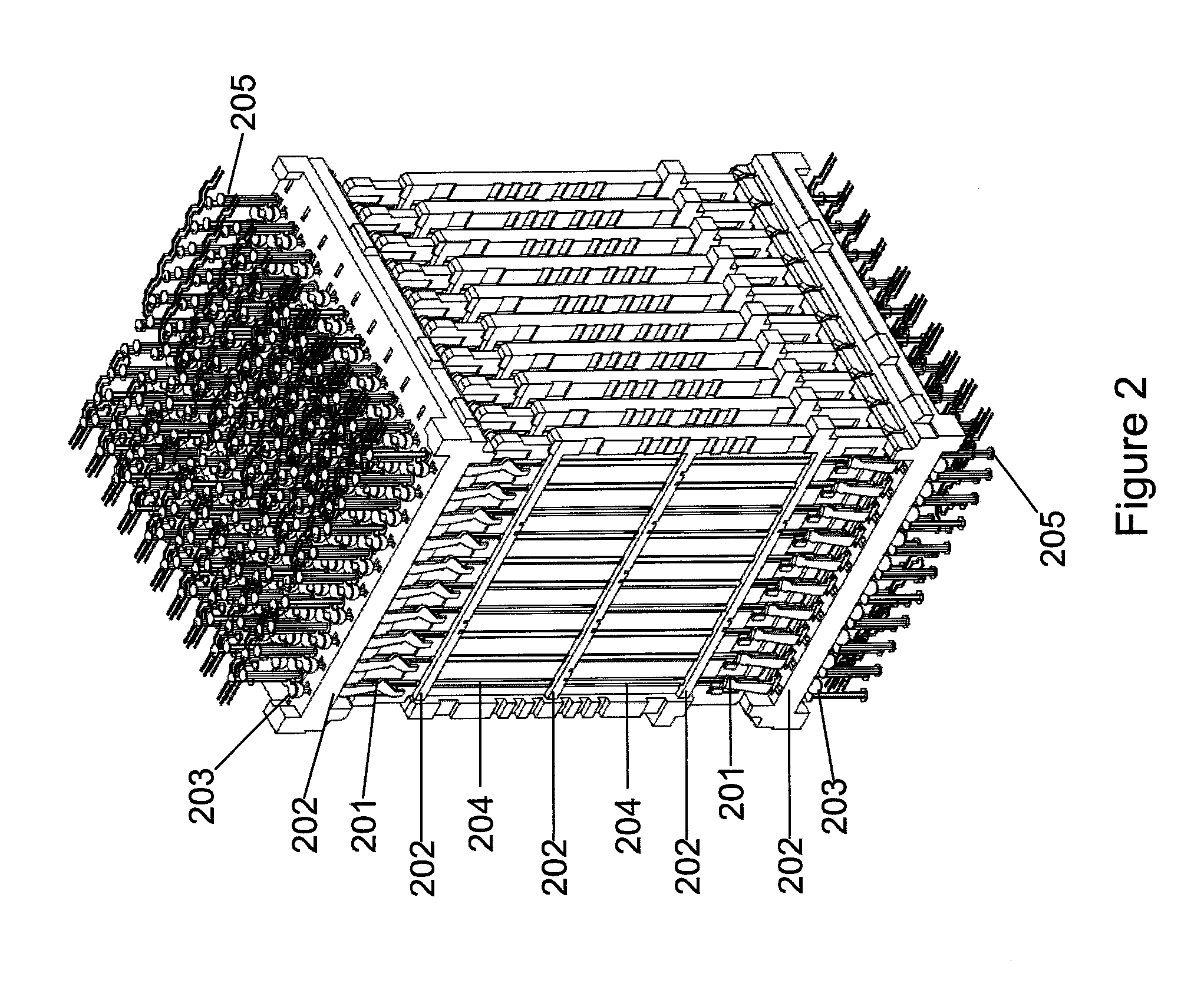

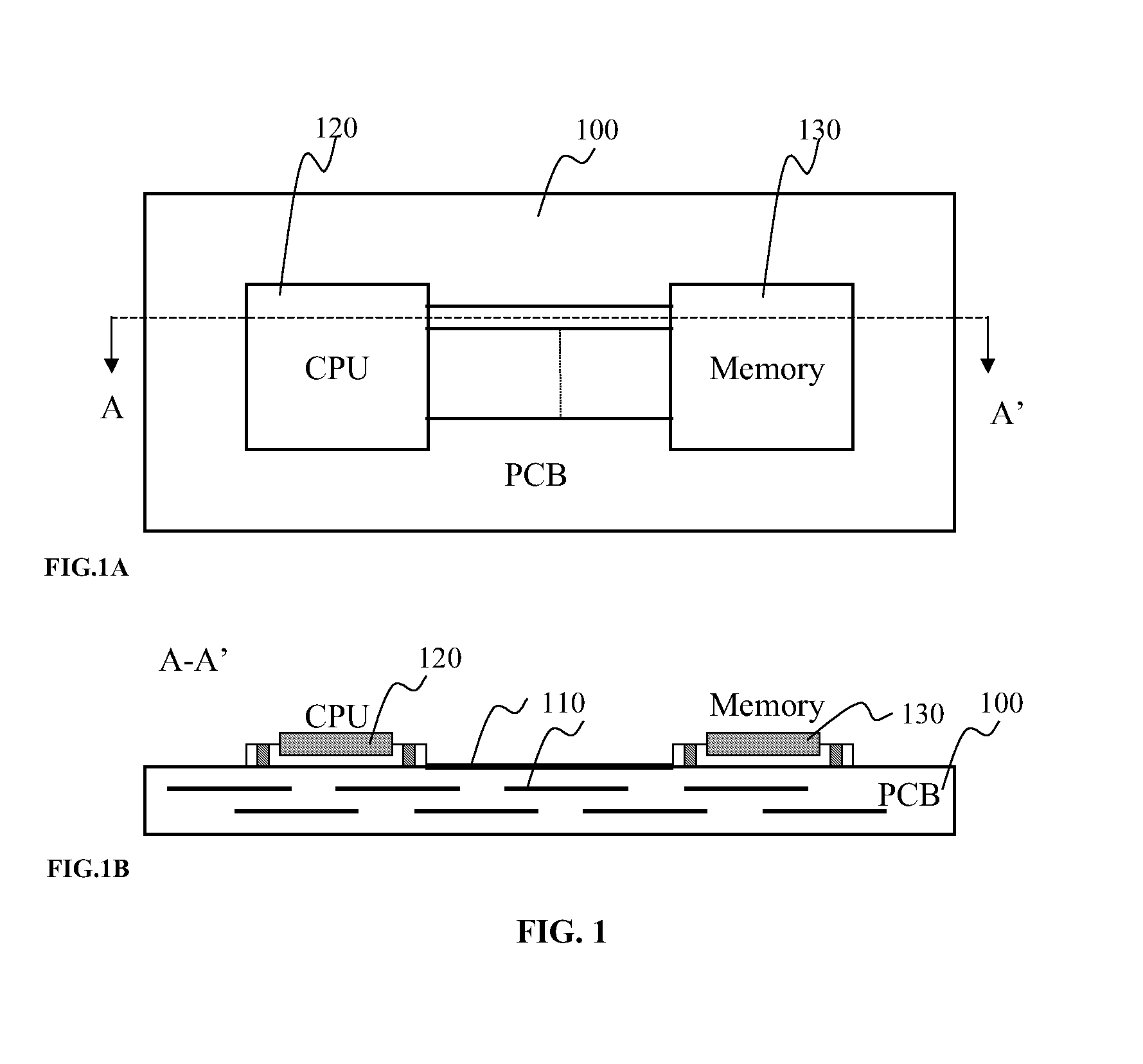

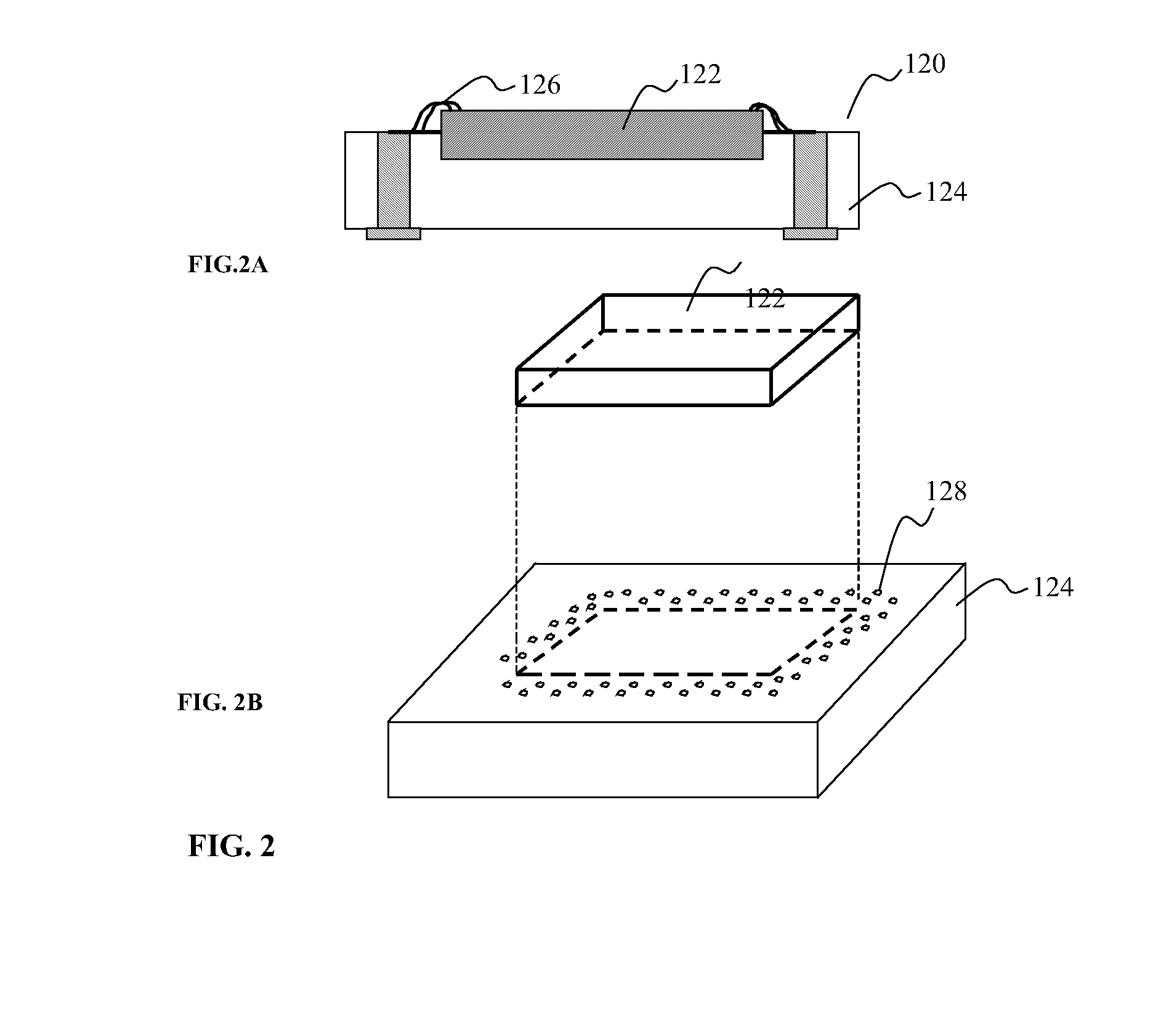

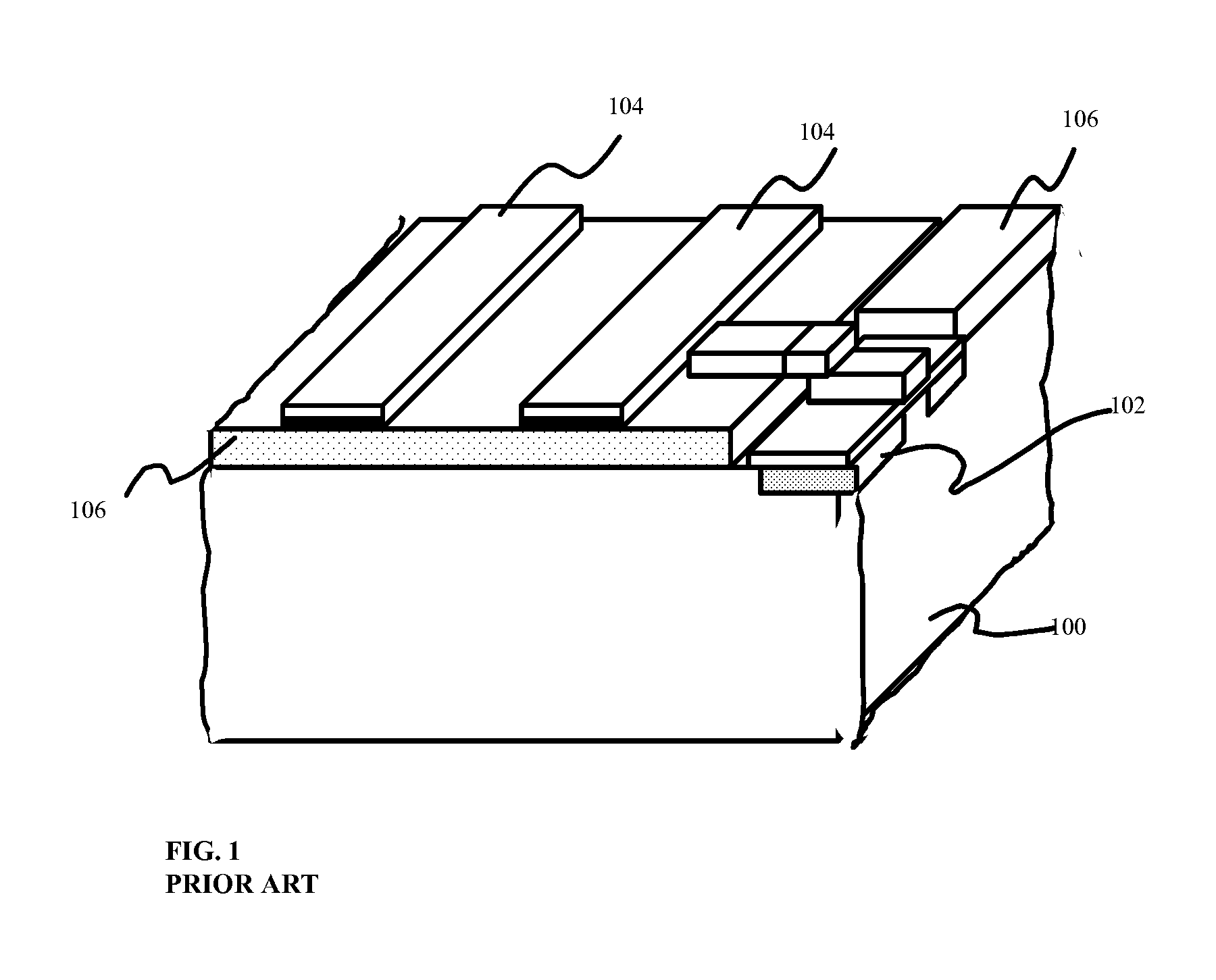

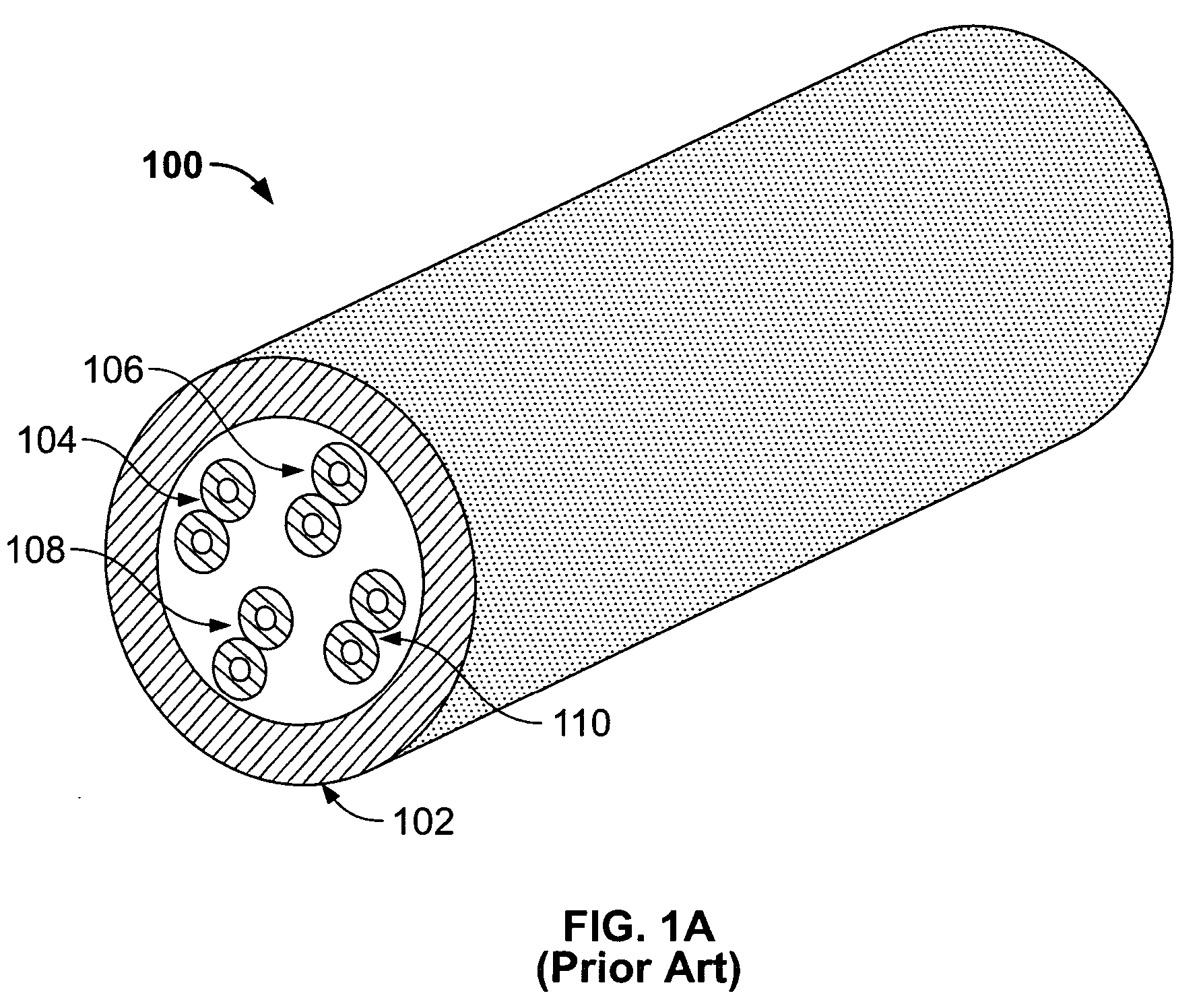

Stackable optoelectronics chip-to-chip interconnects and method of manufacturing

ActiveUS7271461B2Easily stackable/mountableImprove toleranceCircuit optical detailsFinal product manufactureLow speedElectrical conductor

An optoelectronics chip-to-chip interconnects system is provided, including packaged chips to be connected on printed-circuit-board (PCB), multiple-packaged chip, optical-electrical(O-E) conversion means, waveguide-board, and PCB. Single to multiple chips interconnects can be possible using this technique. The packaged-chip includes semiconductor-die and its package based on the ball-grid array or chip-scale-package. The O-E board includes the optoelectronics components and multiple electrical contacts. The waveguide board includes electrical conductors transferring signal from O-E board to PCB and the flex optical waveguide easily stackable onto the PCB, to guide optical signal from one chip-to-other chip. The chip-to-chip interconnects system is pin-free and compatible with the PCB. The main advantages are that standard packaged-chip and conventional PCB technology can be used for low speed electrical signal connection. Also, the part of the heat from the packaged chip can be transmitted to PCB through conductors, so that complex cooling system can be avoided.

Owner:BANPIL PHOTONICS

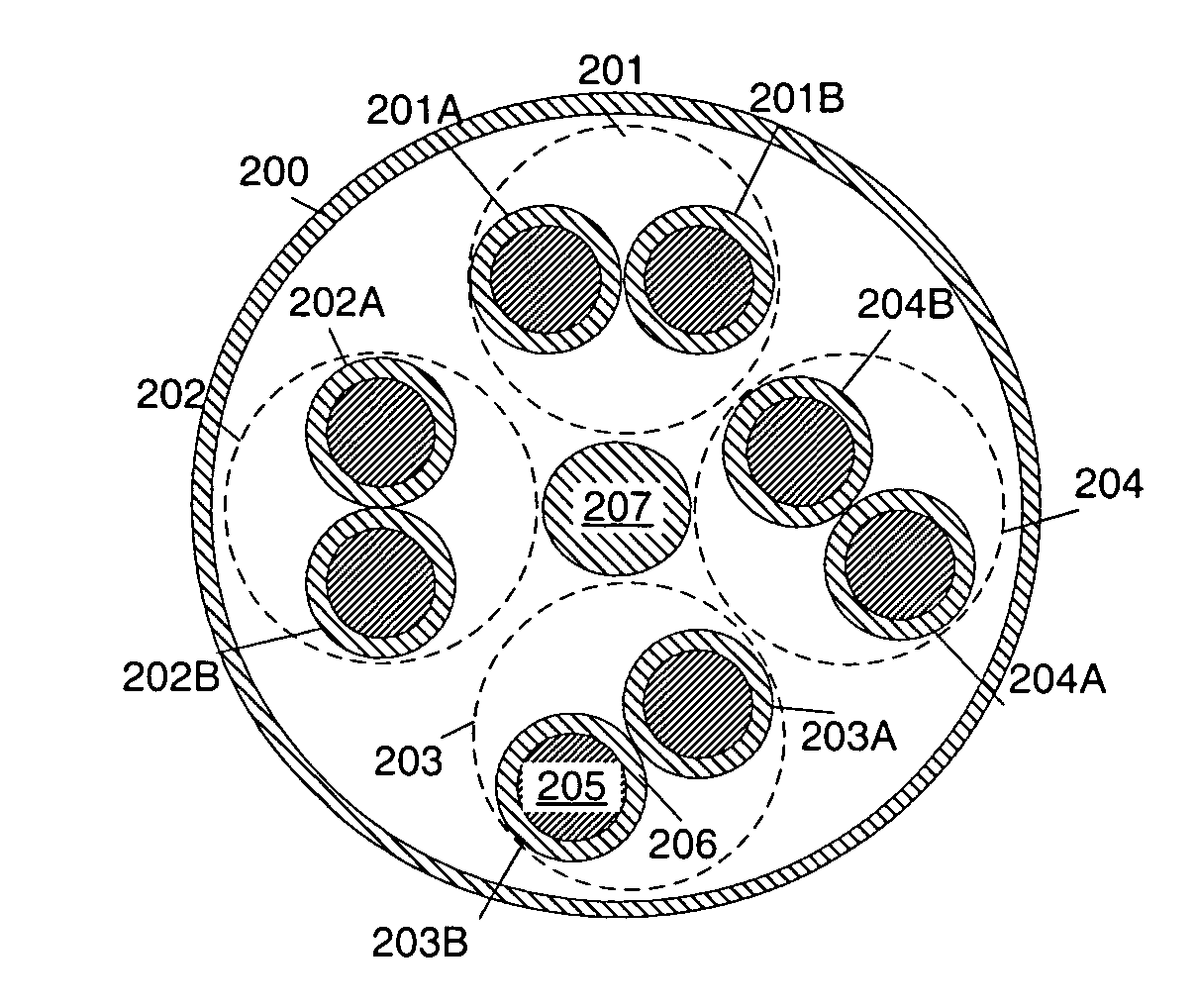

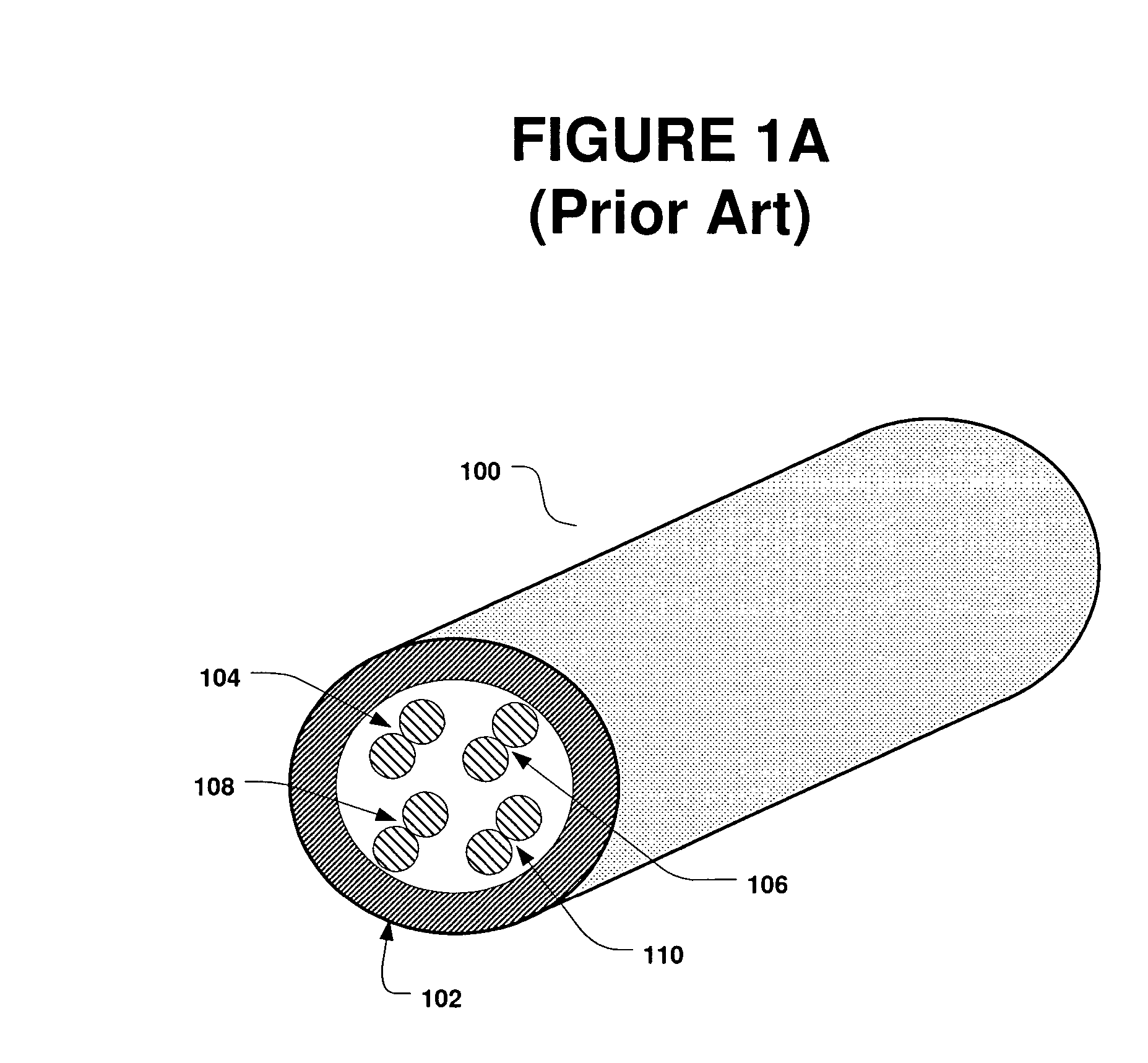

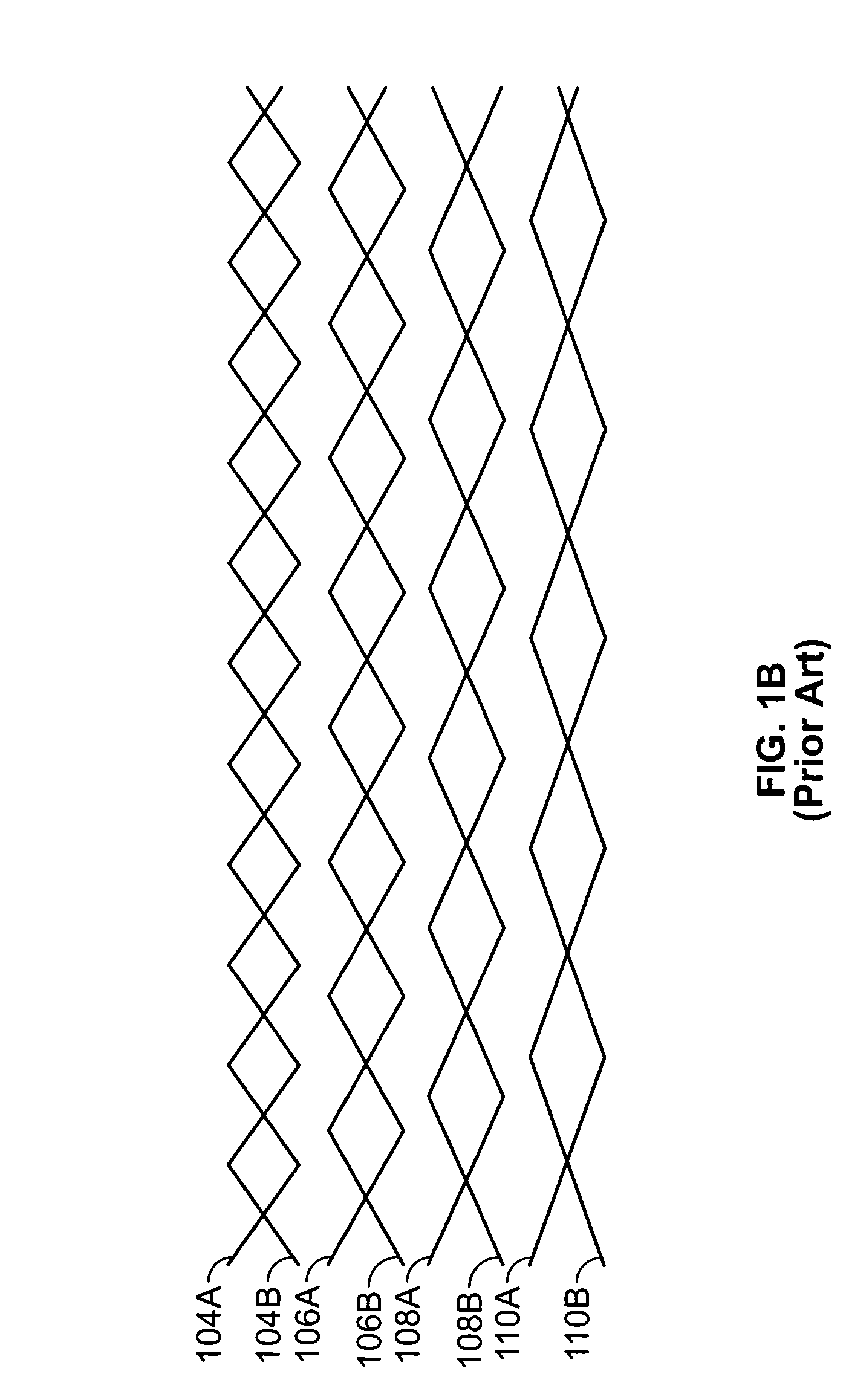

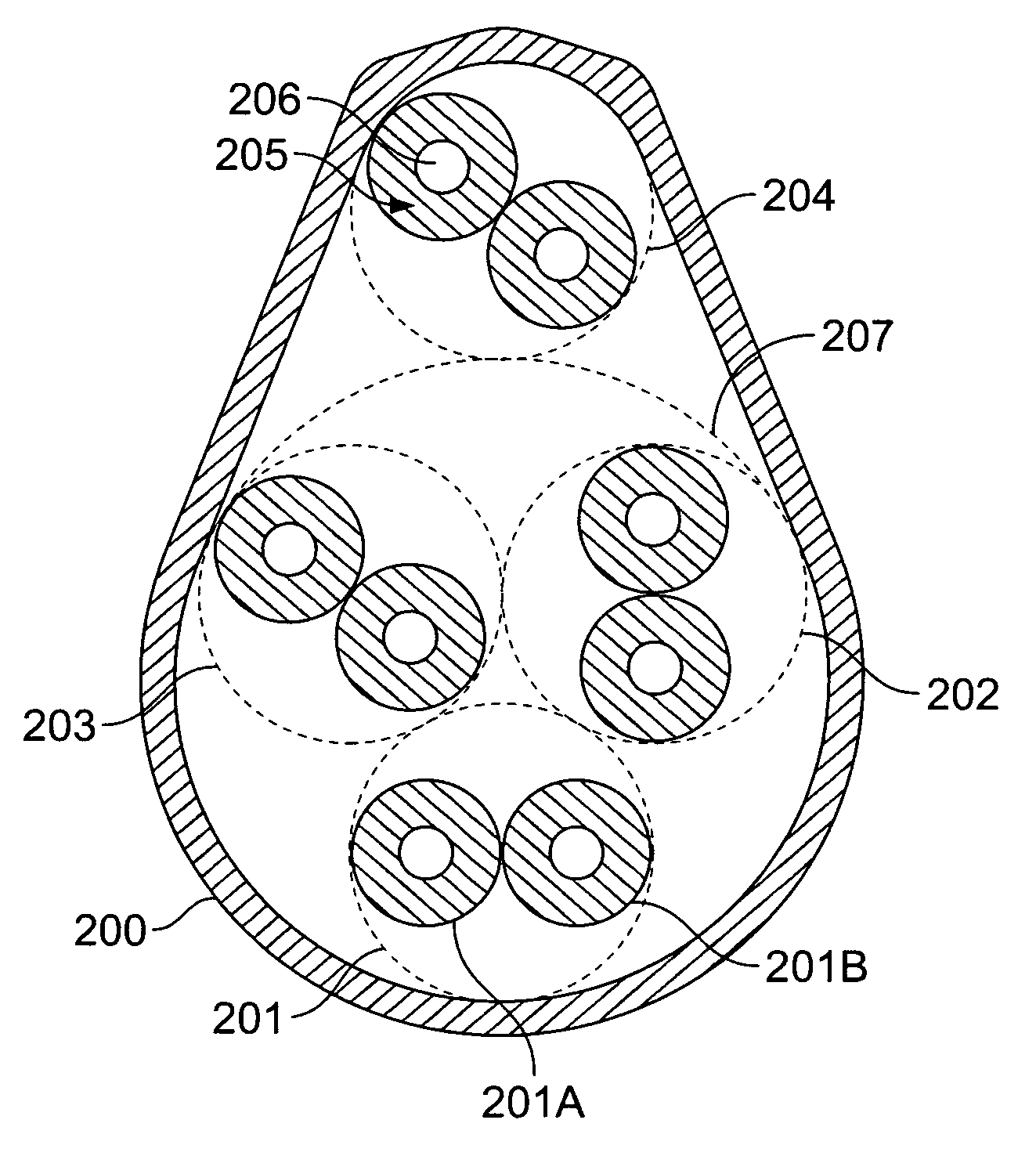

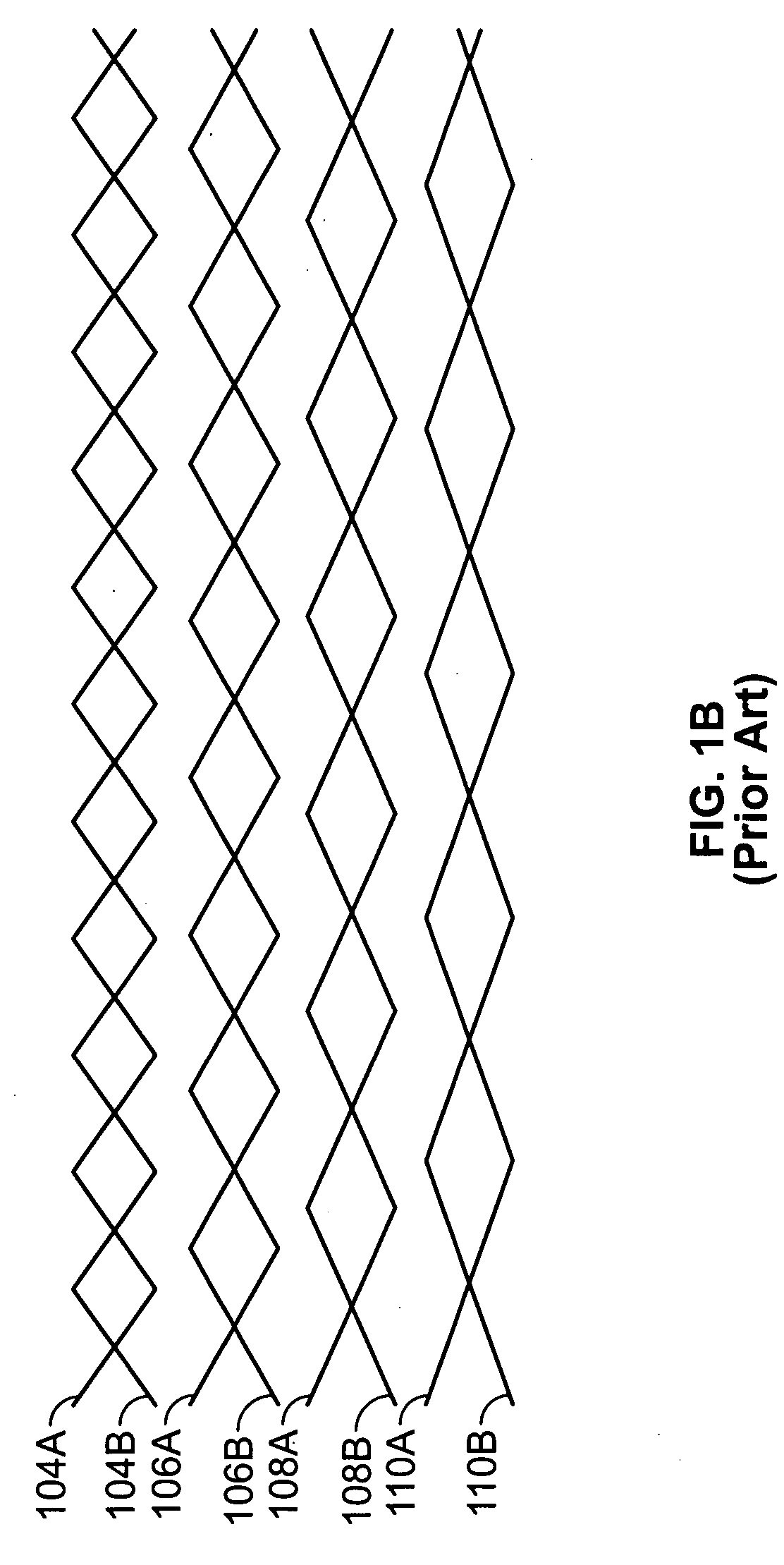

UTP cable apparatus with nonconducting core, and method of making same

InactiveUS20050045367A1Improve signal qualityReduce crosstalkCables with twisted pairs/quadsEngineeringAnalog signal

An unshielded twisted pair (UTP) cable minimizes skew delay of analog signals by enforcing a common electrical length among twisted pairs that carry those analog signals. By applying a different lay length and lay direction to the twisted pair that carries the digital signal, cross-talk from the digital signal onto the analog signals is minimized. A nonconductive filler provides a central core about which the twisted pairs are wound during the bundling process. The presence of the nonconductive core ensures that a minimum distance (i.e., the diameter of the core) is maintained between non-adjacent pairs for the length of the cable.

Owner:RGB SYST INC

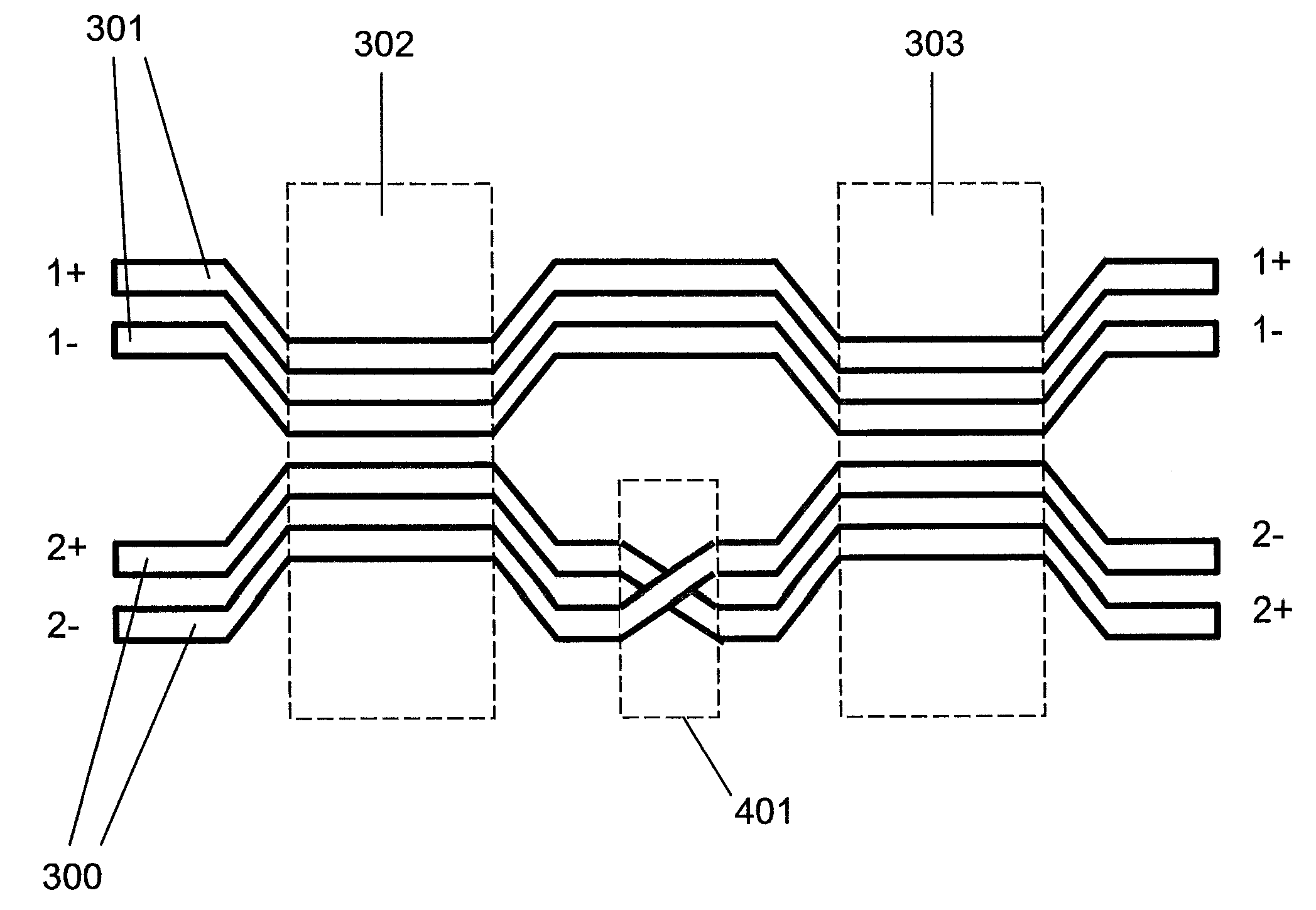

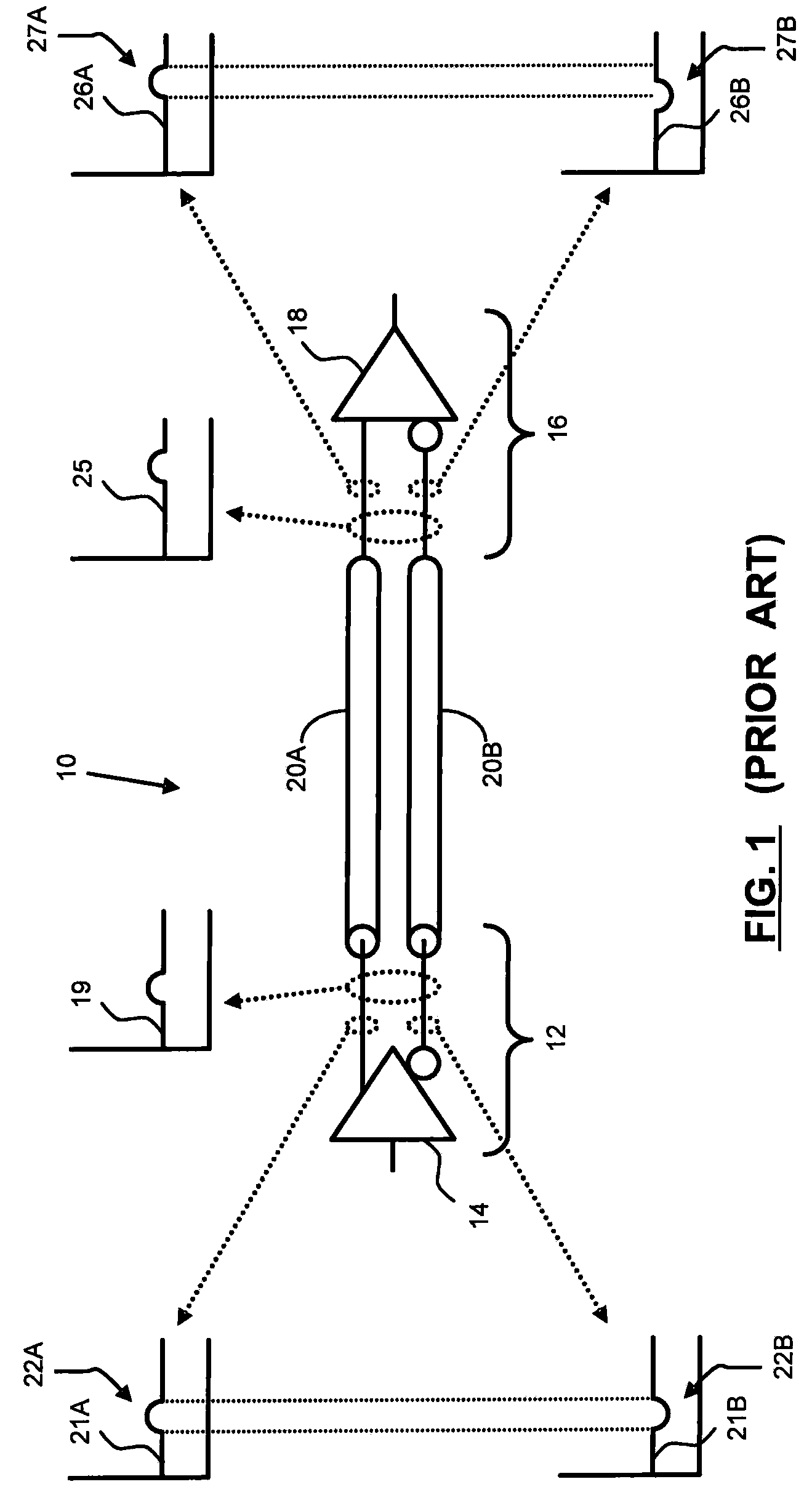

Reducing far-end crosstalk in chip-to-chip communication systems and components

InactiveUS20100183141A1Big improvements in total FEXTCancel improvementSubstations coupling interface circuitsInterconnection arrangementsCommunications systemElectrical polarity

The present invention involves chip-to-chip communication systems for reducing Far-End Crosstalk (FEXT) through the use of novel polarity swapping to negate the cumulative effect of FEXT. Skew adjustment is used to improve the FEXT cancellation from polarity swapping. The polarity reversal location or locations among FEXT sources are optimized to achieve maximum FEXT cancellation. The novelty polarity swapping technique can be applied to a wide variety of systems that can benefit from FEXT reduction.

Owner:HIROSE ELECTRIC GROUP

Reducing far-end crosstalk in electrical connectors

ActiveUS20100184307A1Big improvements in total FEXTCancel improvementInterconnection arrangementsSubstations coupling interface circuitsElectricityElectrical polarity

The present invention involves connectors for reducing Far-End Crosstalk (FEXT) through the use of novel polarity swapping to negate the cumulative effect of FEXT. Skew adjustment is used to improve the FEXT cancellation from polarity swapping. The polarity reversal location or locations among FEXT sources are optimized to achieve maximum FEXT cancellation. The novelty polarity swapping technique can be applied to a wide variety of connectors, such as mezzanine connectors, backplane connectors, and any other connectors that can benefit from FEXT reduction.

Owner:HIROSE ELECTRIC GROUP

High-speed flex printed circuit and method of manufacturing

ActiveUS20070066126A1Reduce effective dielectric constant effective dielectricReduce effective dielectric effective dielectric lossPrinted circuit assemblingHigh frequency circuit adaptationsAdhesiveEngineering

High speed flex printed circuit boards (FLEX-PCBs) are disclosed comprising a dielectrics systems with the back-side trenches, adhesives, signal lines and ground-plans, wherein the signal line and ground-plan are located on the dielectrics. Using of the open trenches in the substrate help to reduce the microwave loss and dielectric constant and thus increasing the signal carrying speed of the interconnects. Thus, according to the present invention, it is possible to provide a simply constructed high speed FLEX-PCB using the conventional material and conventional FLEX-PCB manufacturing which facilitates the design of circuits with controlled bandwidth based on the trench opening in the dielectrics, and affords excellent connection reliability. As the effective dielectric constant is reduced, the signal width is required to make wider or the dielectric thickness is required to make thinner keeping fixed characteristics impedance. The fundamental techniques disclosed here can also be used for high-speed packaging.

Owner:BANPIL PHOTONICS

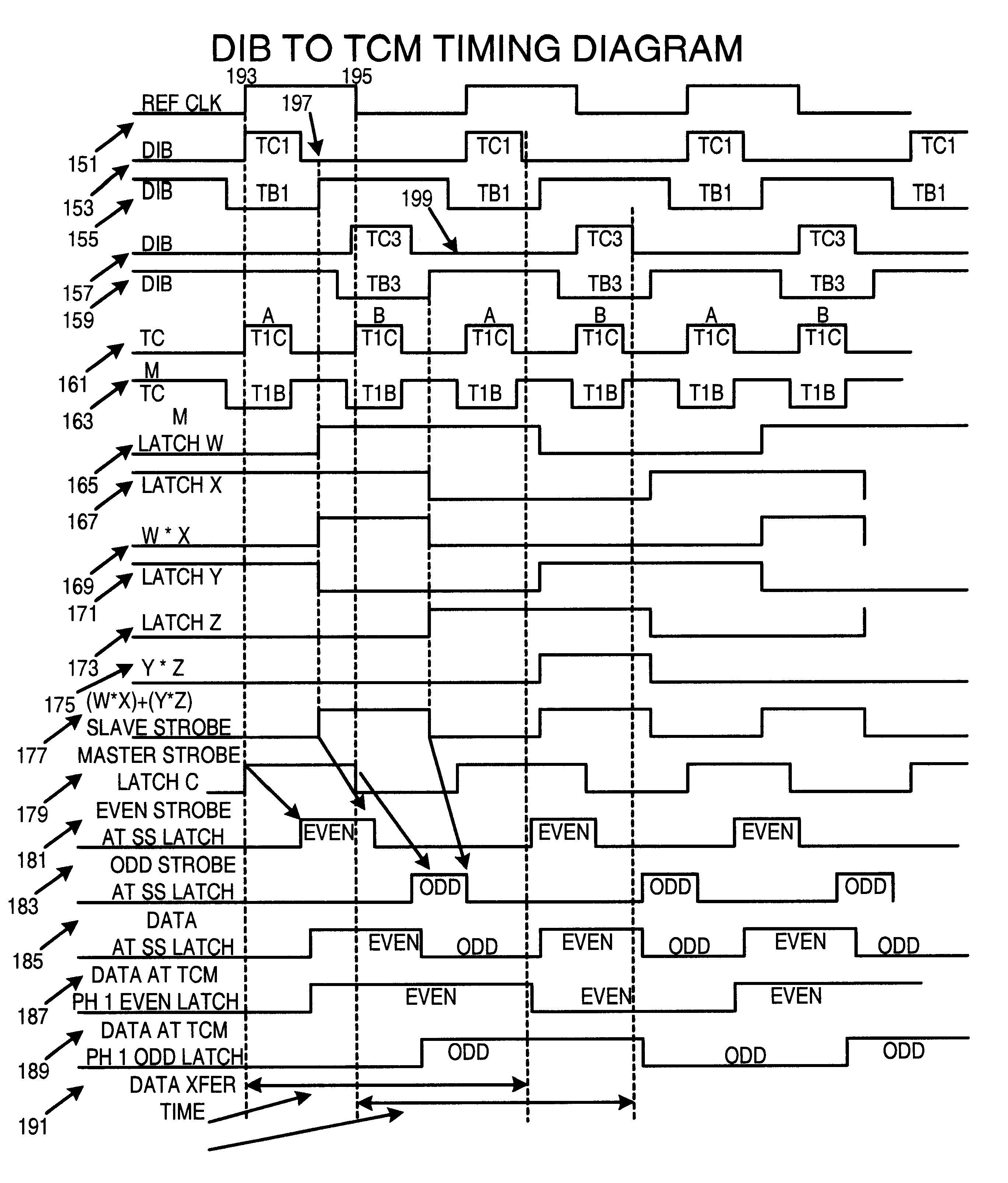

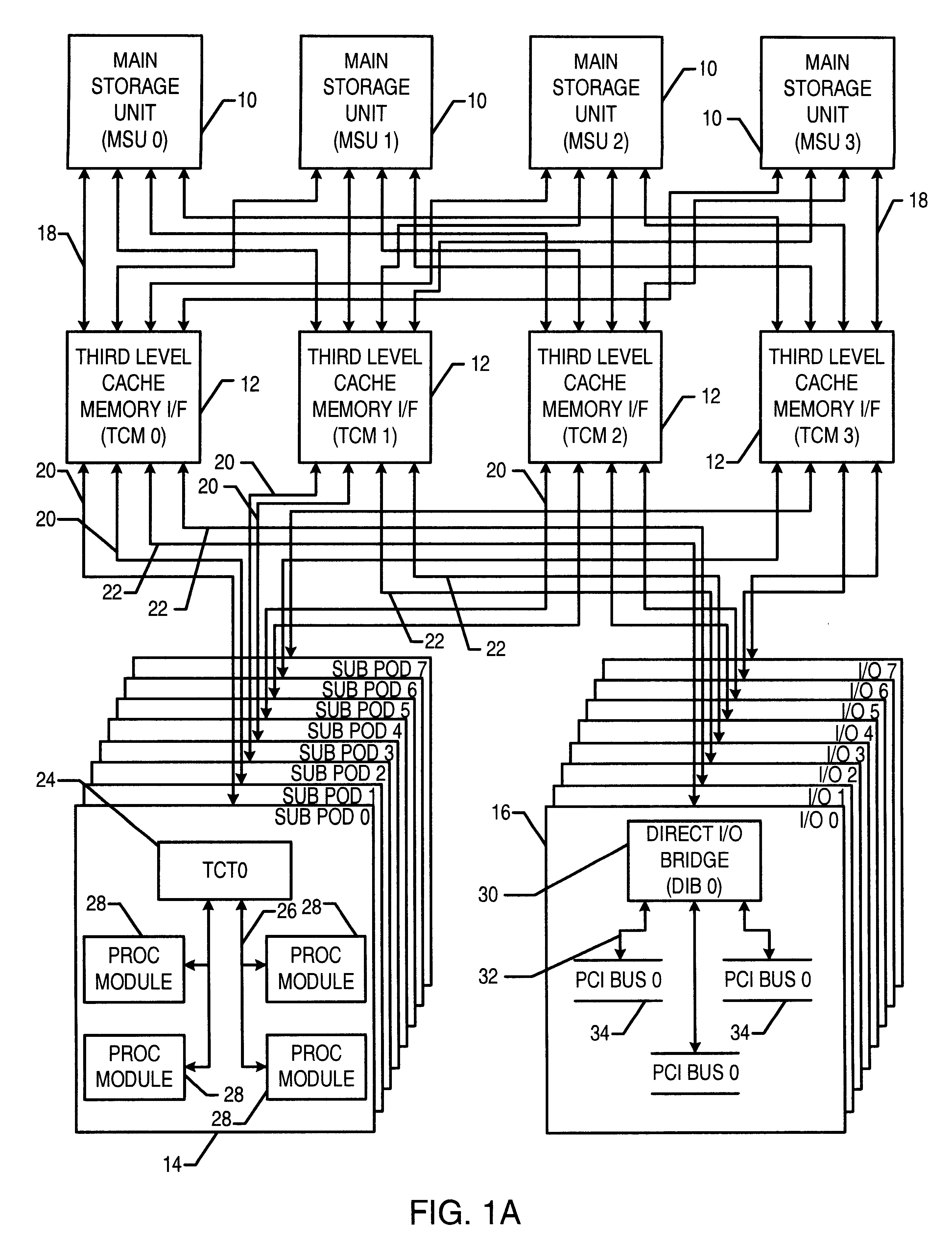

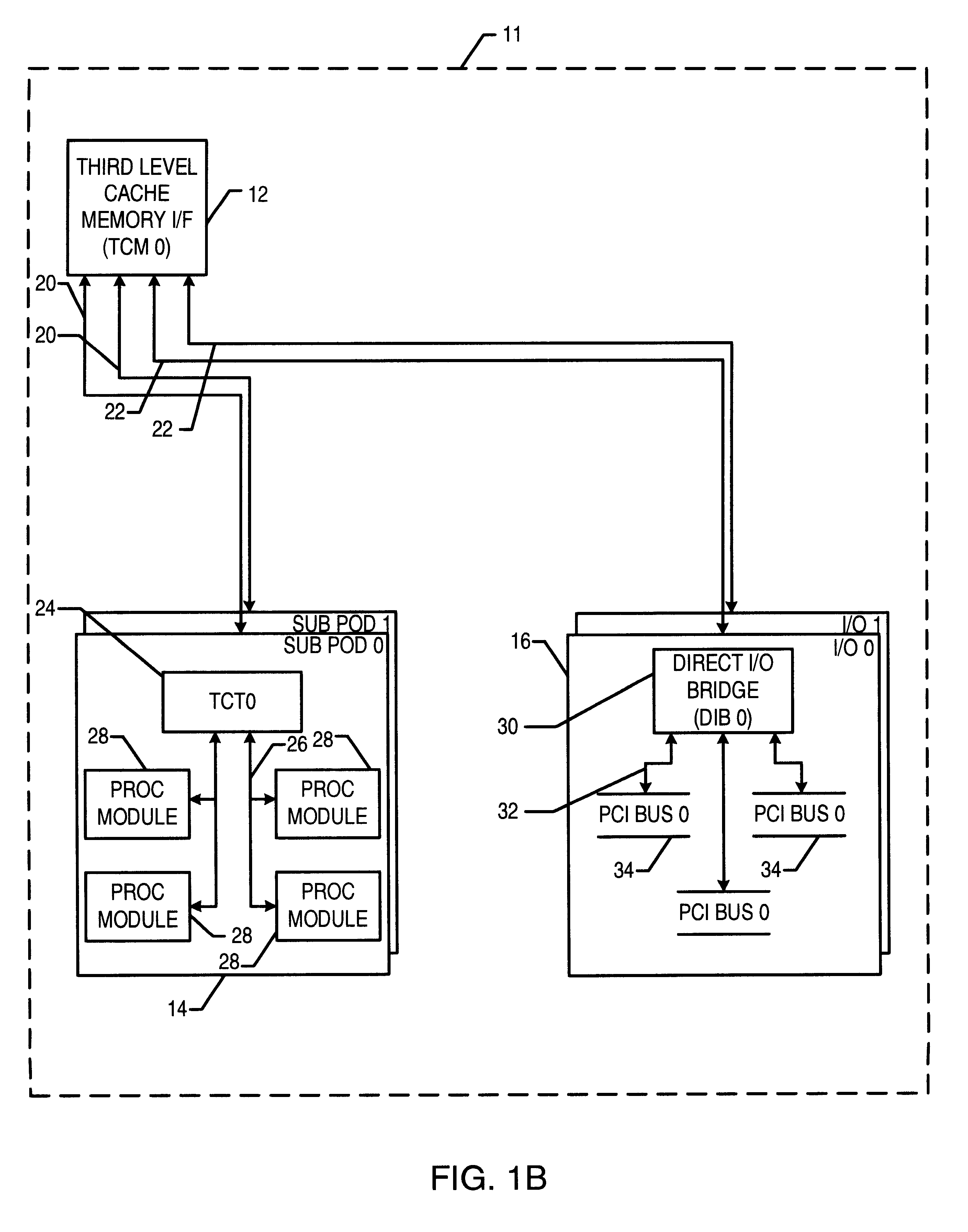

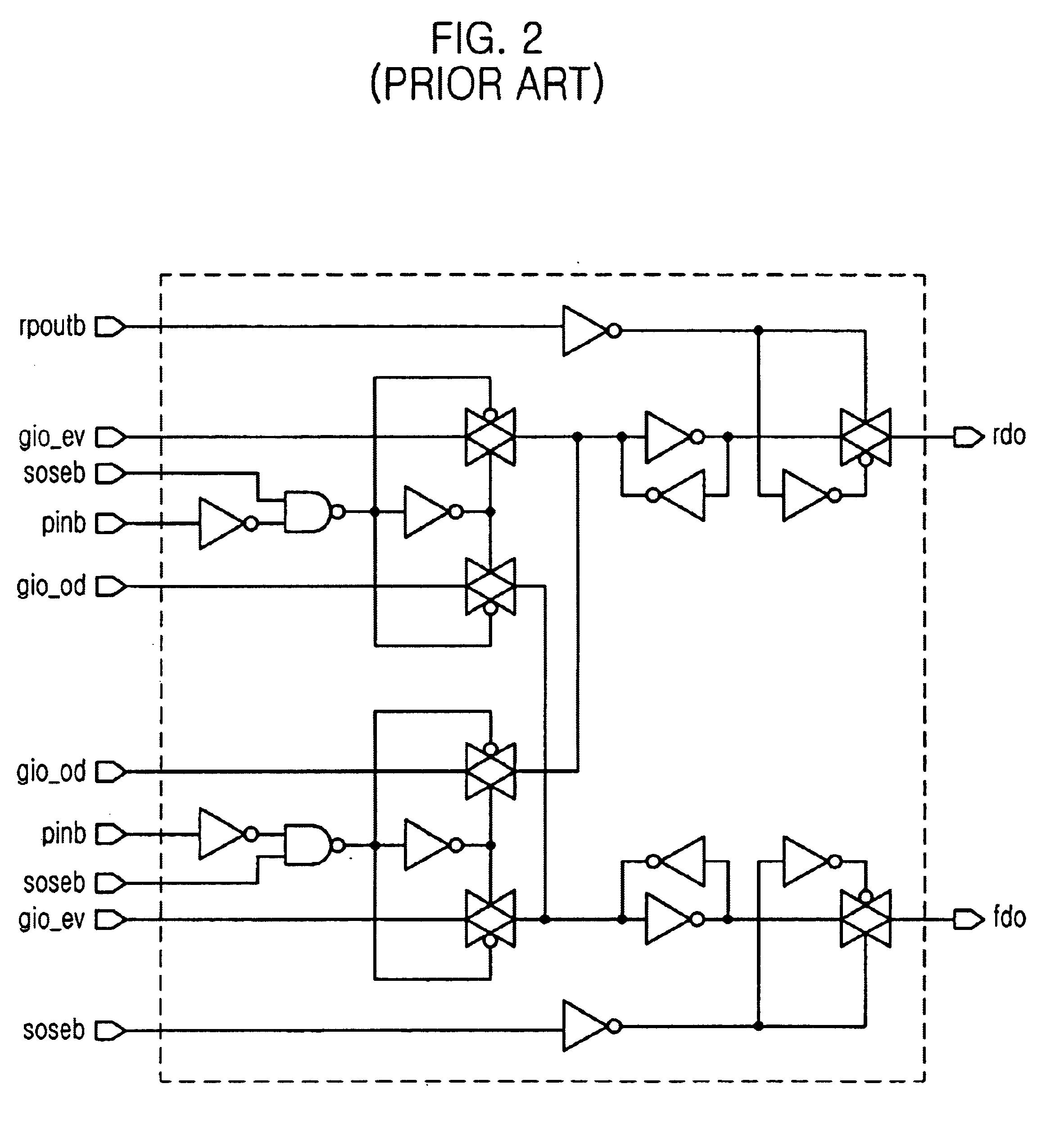

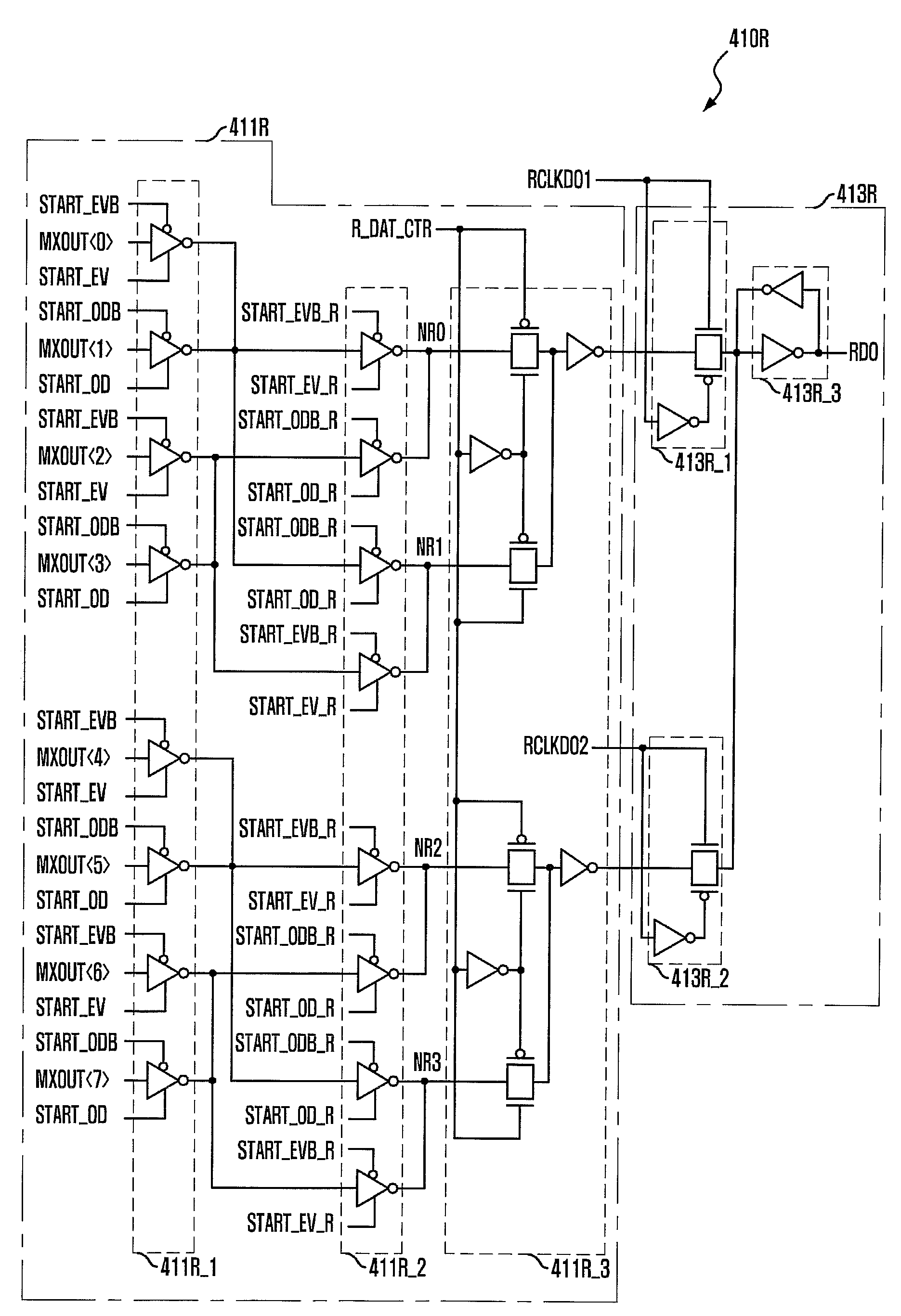

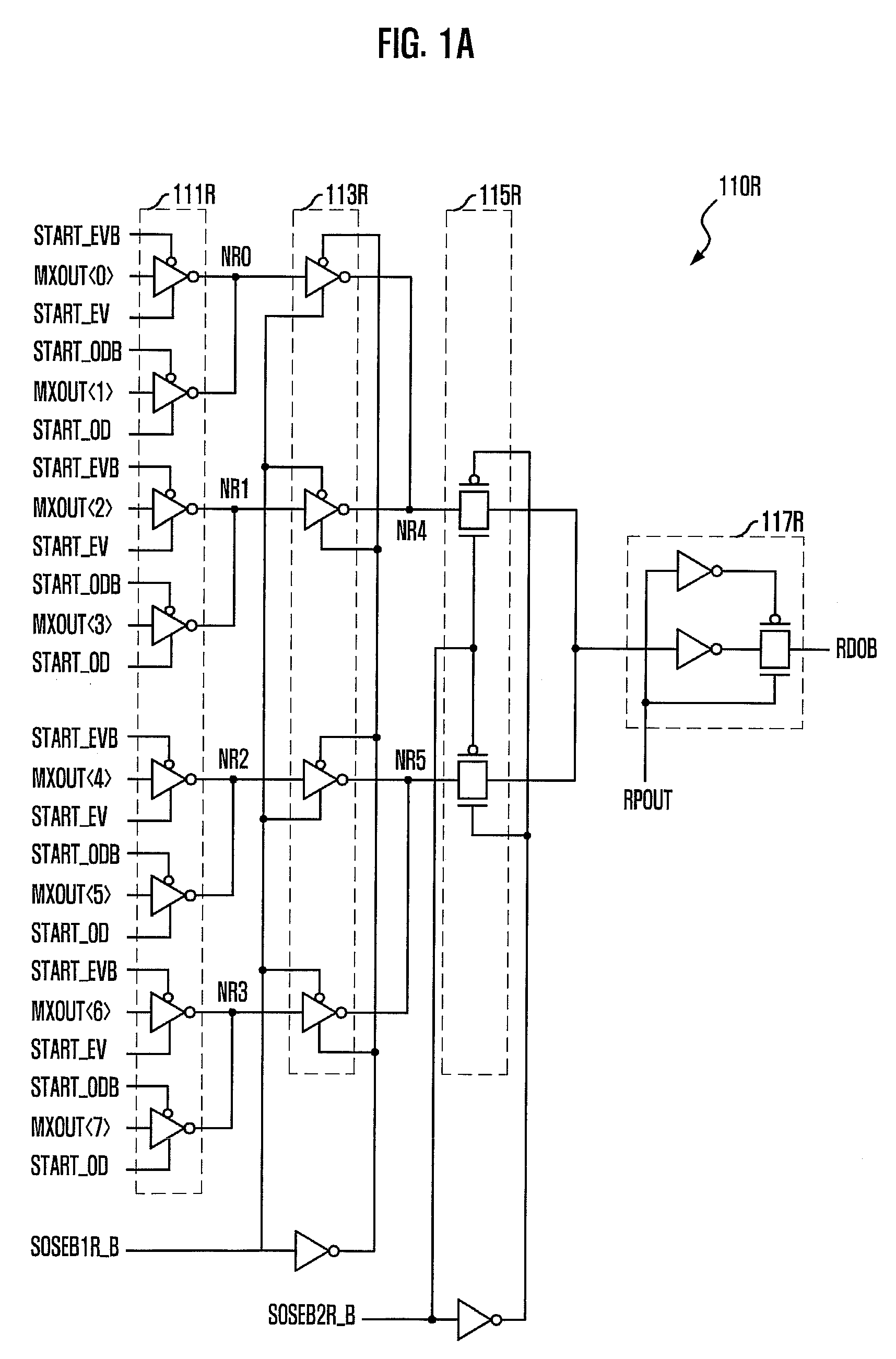

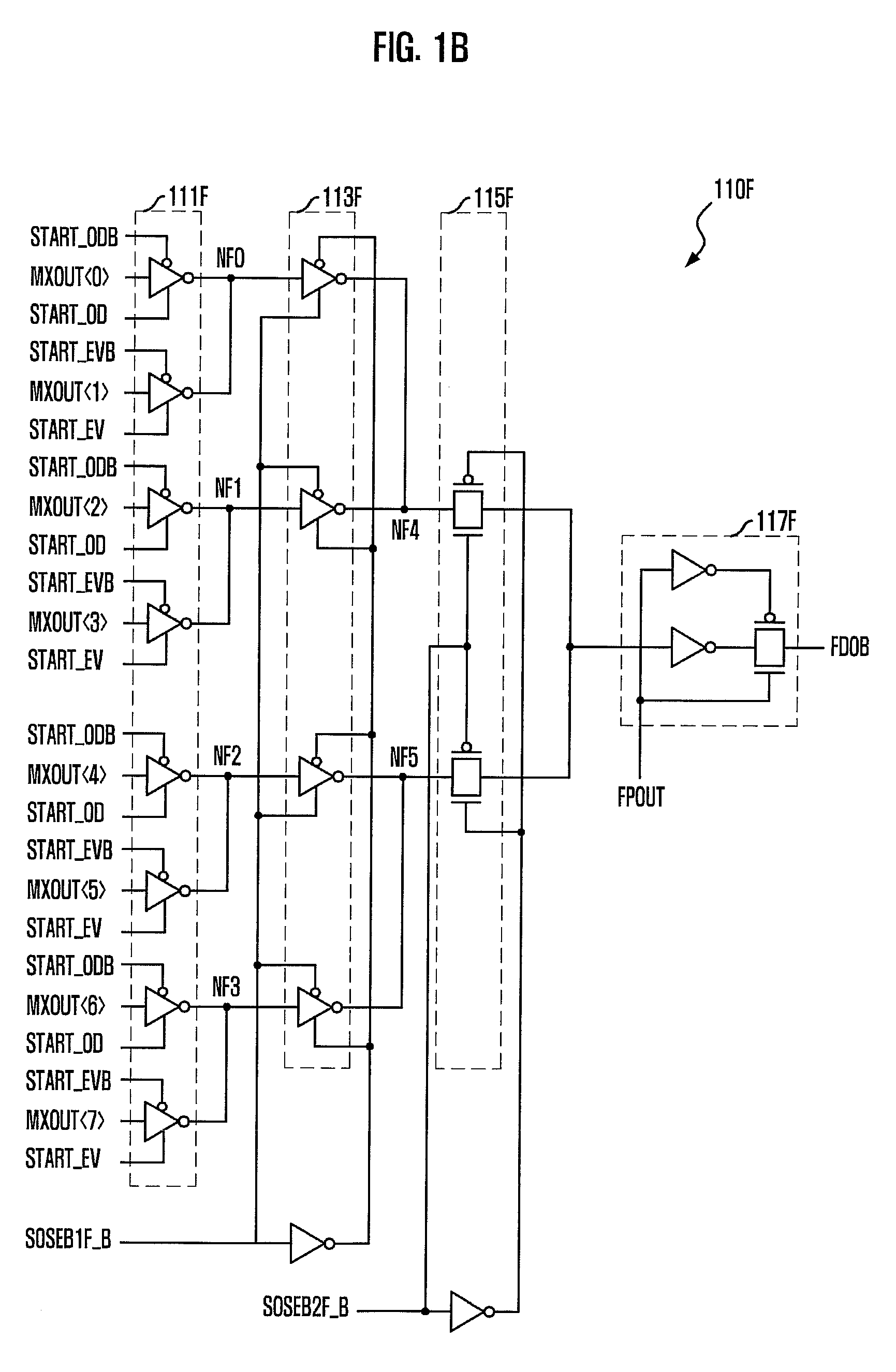

Source synchronous transfer scheme for a high speed memory interface

InactiveUS6199135B1Increase transfer rateReduce offsetData switching by path configurationMultiple digital computer combinationsMultiplexingHigh speed memory

Data transfer scheme wherein data transfer rates can be effectively doubled with no increase in the clock speed of the interface. This is accomplished by allowing more than one data transfer to occur on a single clock cycle. This transfer scheme increases the transfer rate of the interface by multiplexing two data groups on the same interface. These data groups are transmitted from a source phase latch at approximately the same time as two strobe signals which have low skew with respect to the data. The master and slave strobe signals are logically combined to create an even latch enable signal and an odd latch enable signal that are used to latch and de-multiplex the multiplexed data groups at a receiving end of a pair of flow-though source synchronous latches.

Owner:CHARLES A JOHNSON

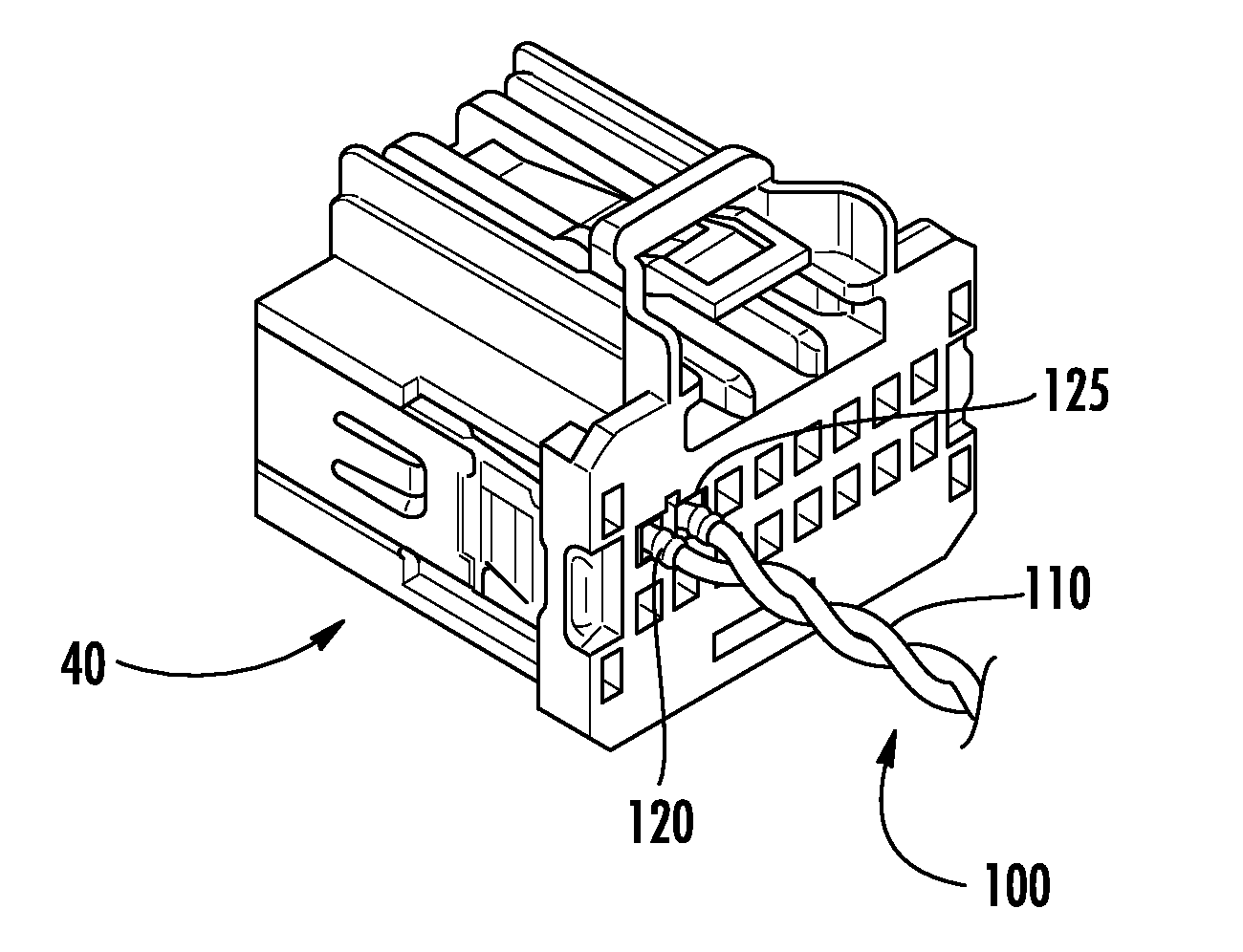

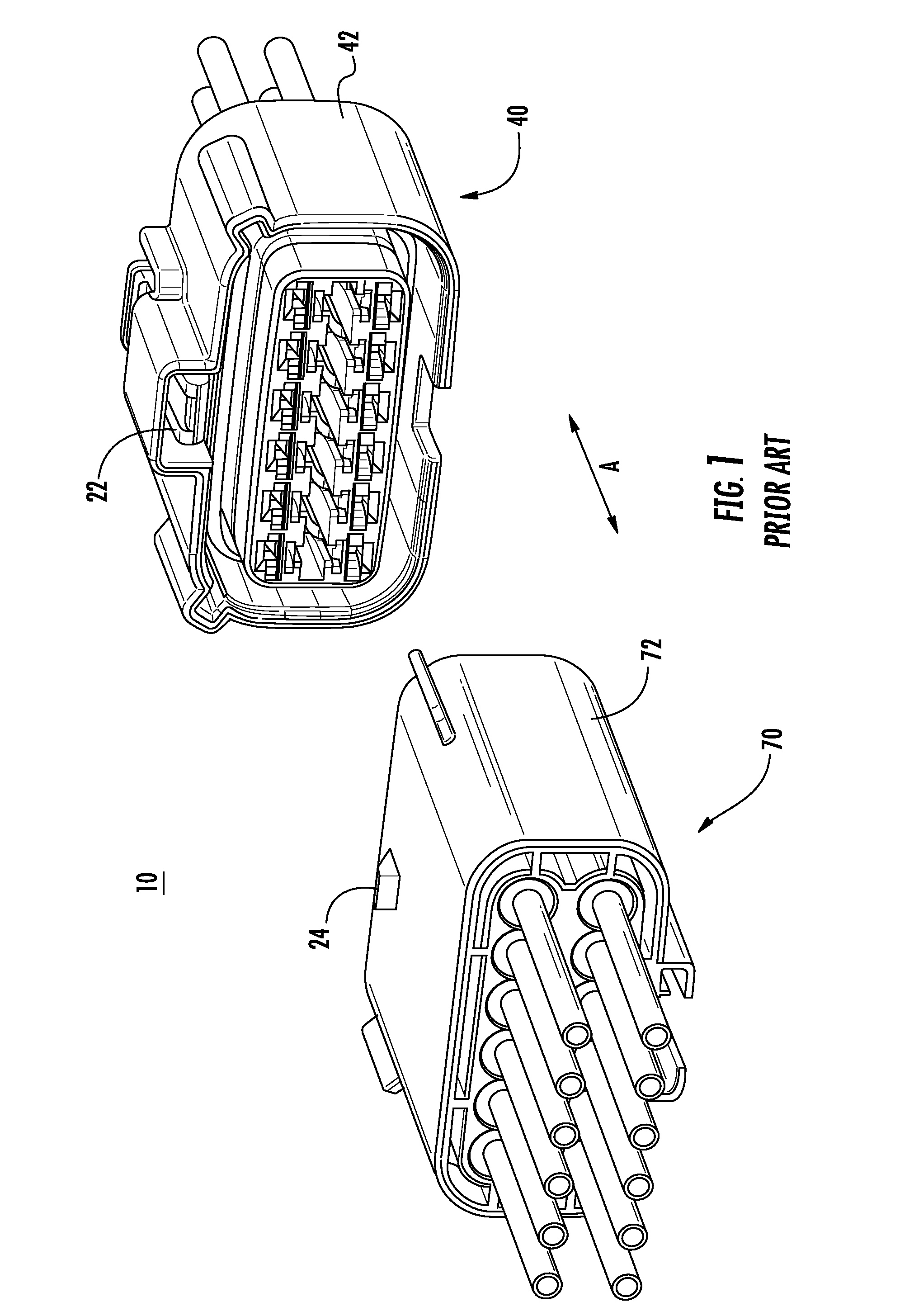

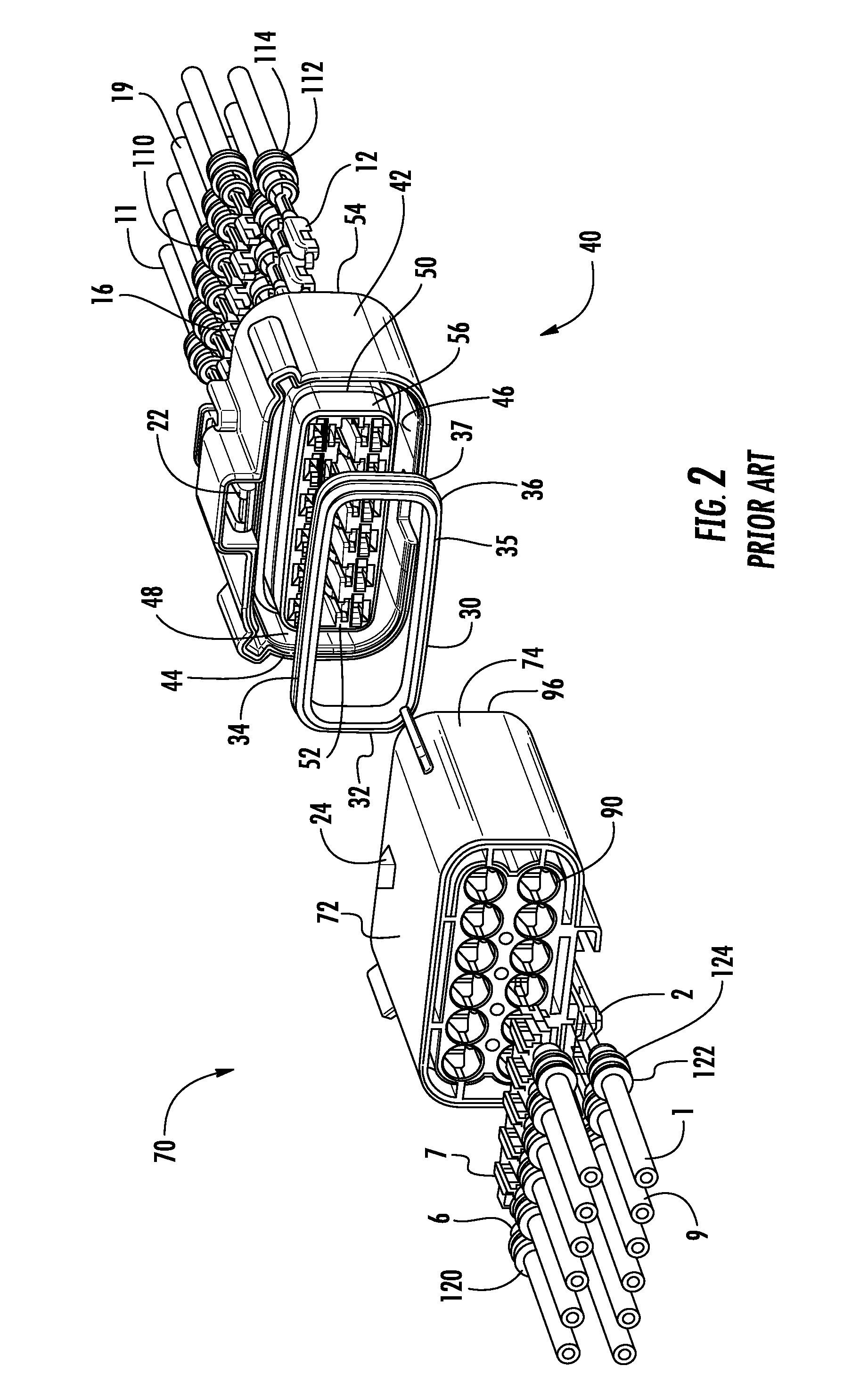

Electrical harness connector system with differential pair connection link

ActiveUS20150155670A1Minimize skewMaximize balanceElectric discharge tubesSecuring/insulating coupling contact membersElectricityData rate

An electrical connector system includes a plug connector and a receptacle connector, each of which include a plurality of terminal receiving cavities for receiving a plurality of terminal lead wires. The electrical connector system further includes a connector link comprising a twisted pair differential cable for providing a data rate high data rate signal transmission transfer with the connector system, in addition to standard power and signal transmission, wherein the connector link is modularly connected within the electrical connector system.

Owner:MOLEX INC

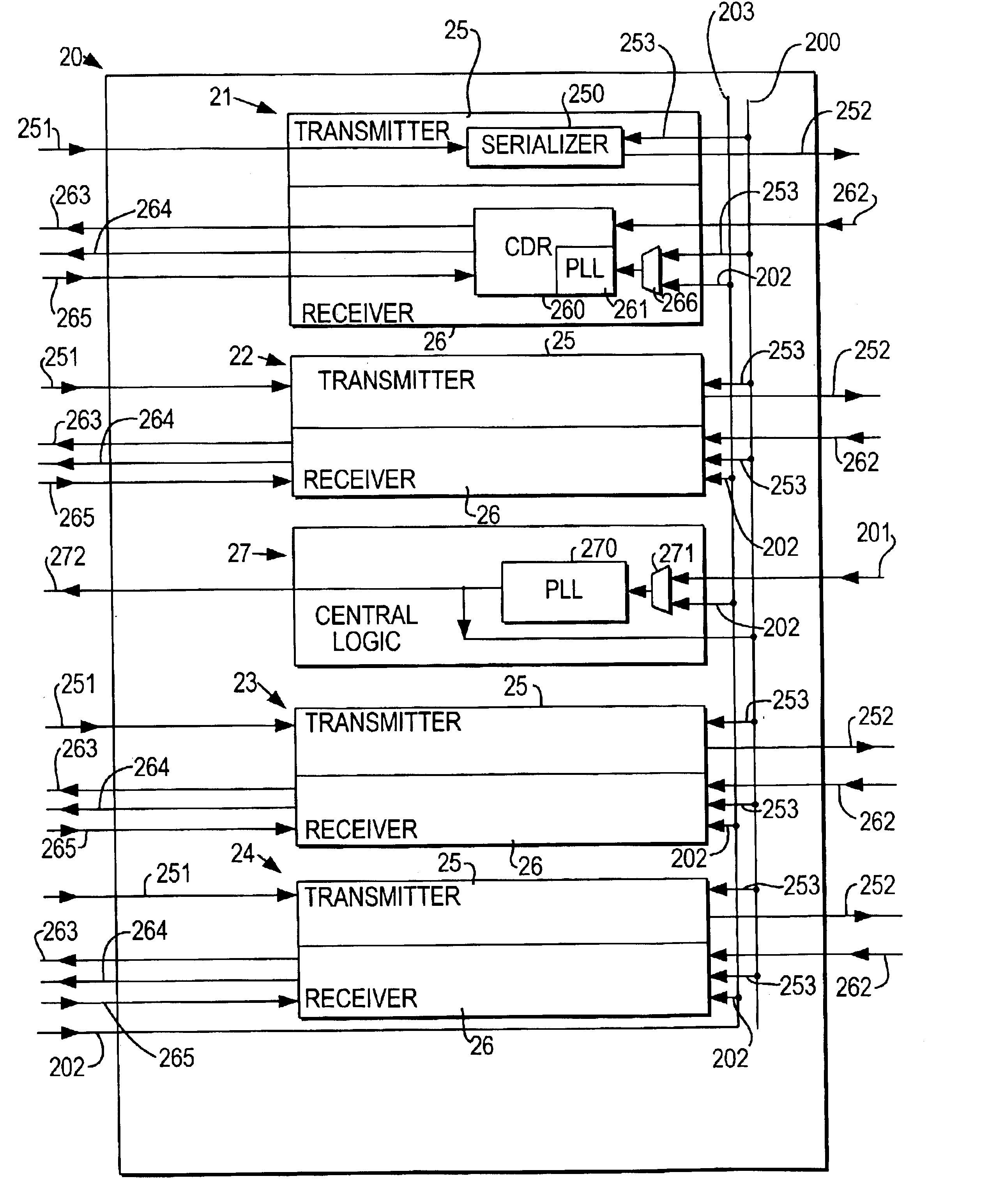

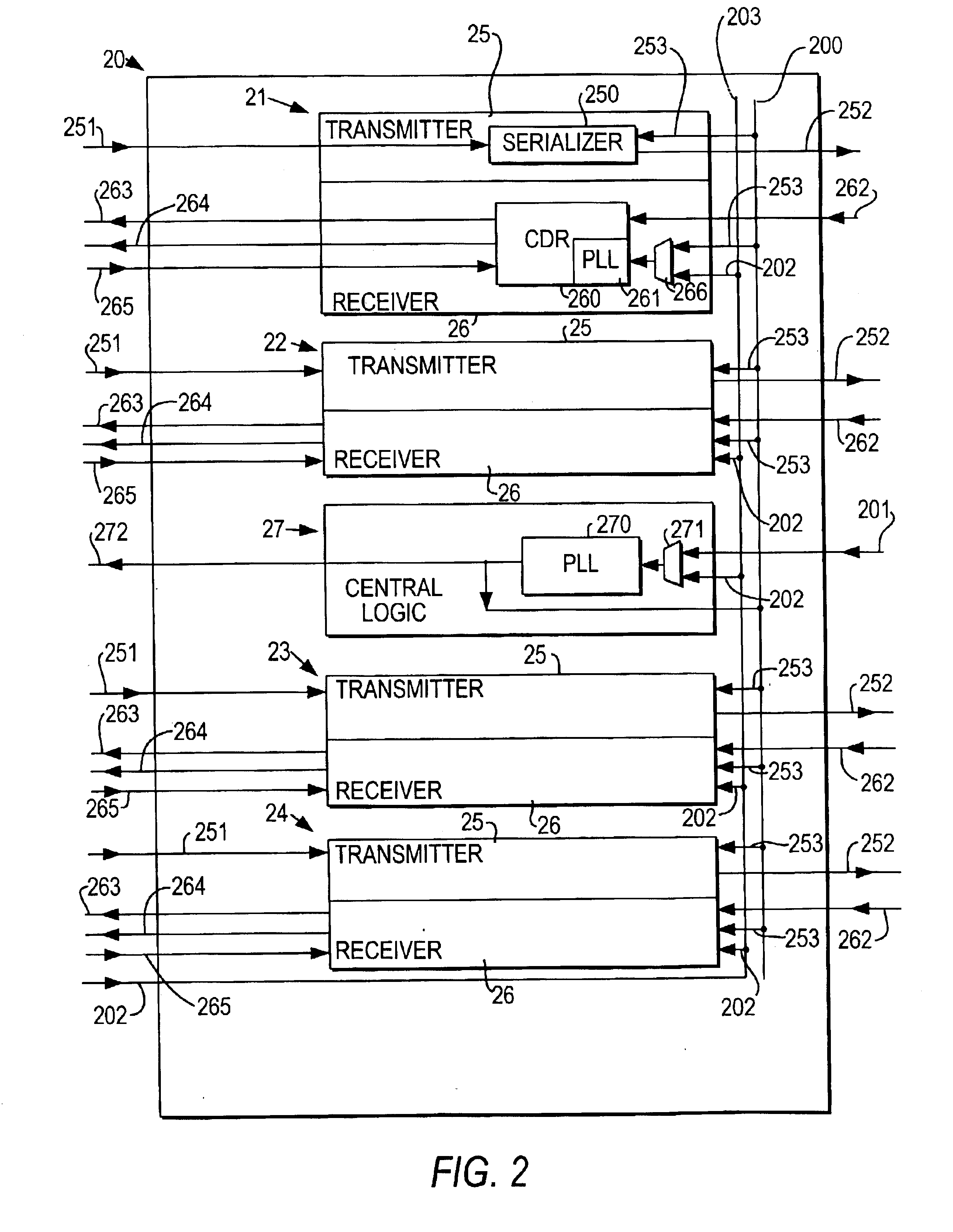

Programmable logic device serial interface having dual-use phase-locked loop circuitry

InactiveUS6867616B1Minimize skewSolid-state devicesAngle demodulation by phase difference detectionGeneral purposeElectrical conductor

In a programmable logic device (“PLD”), a serial interface incorporating phase-locked loops (“PLLs”) is provided with connections that allow one or more of the PLLs to be used as general purpose PLLs in the PLD. The connections include conductors to allow reference clock signals from the PLD logic core, or from outside the PLL, to be used by the PLLS, as well as conductors that allow the PLD core to control the phases of the PLLs. For some of the PLLs, conductors to allow the PLL output clock to be used by the PLD are also provided, where such output conductors do not normally exist in such a serial interface.

Owner:TAHOE RES LTD

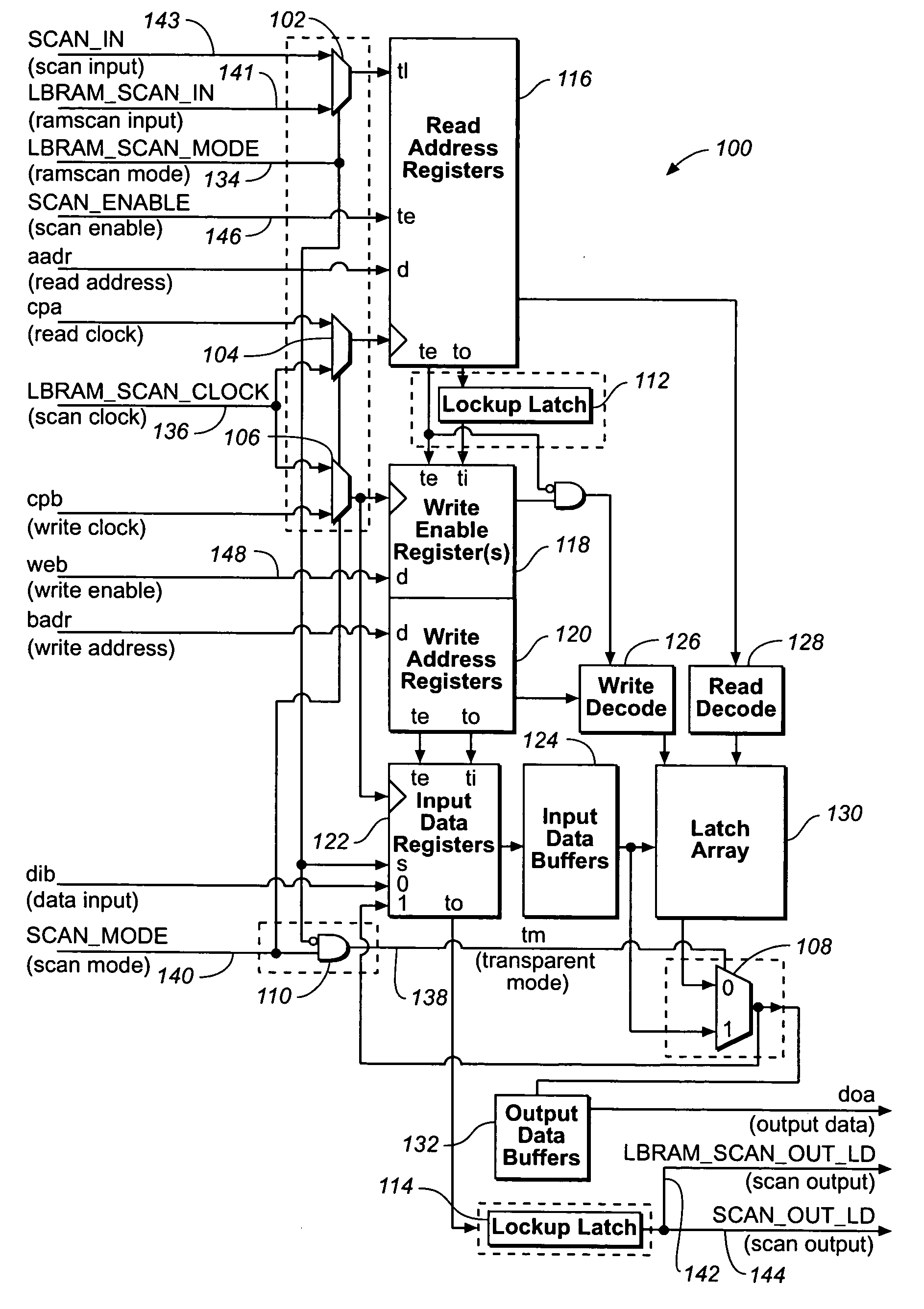

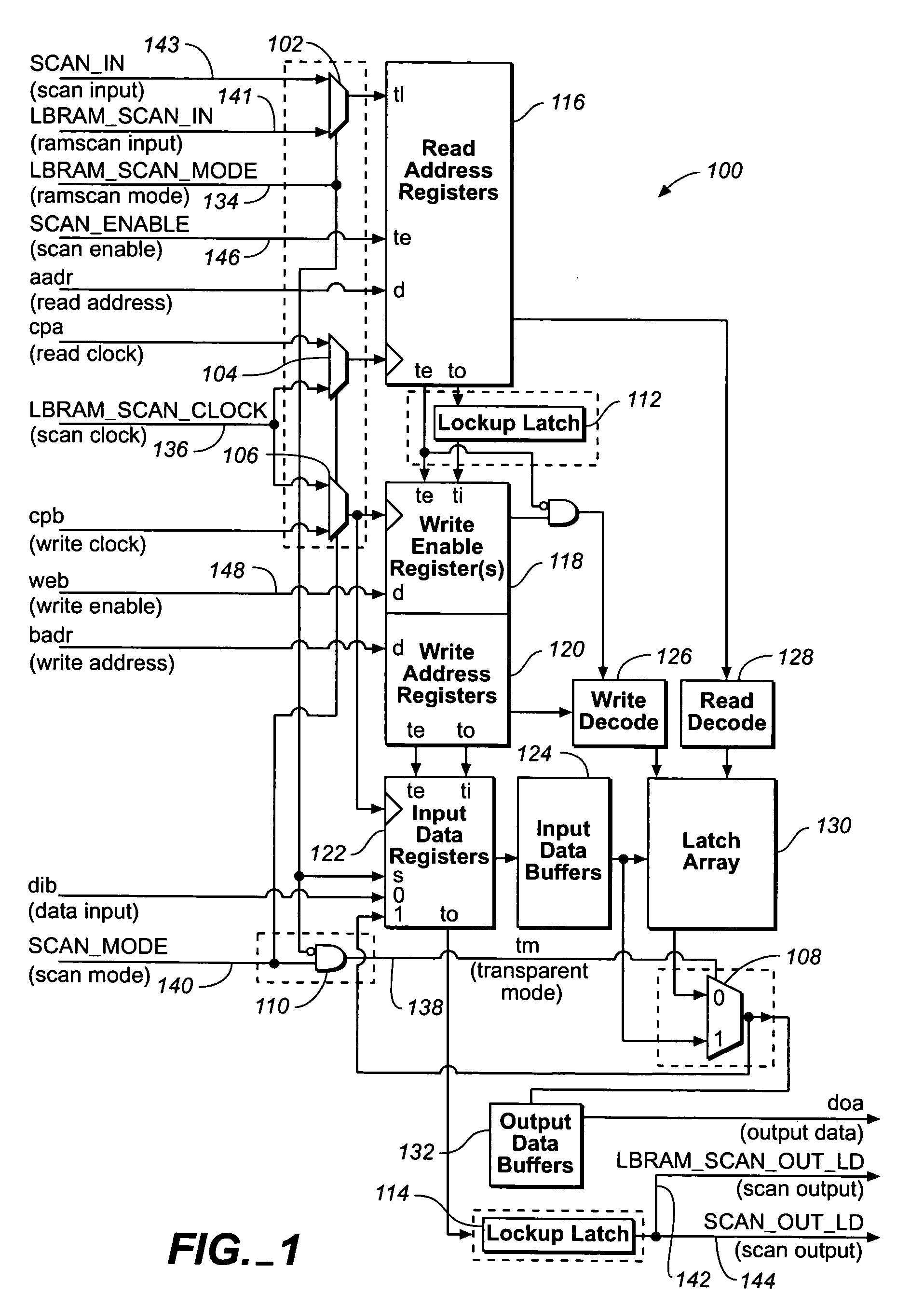

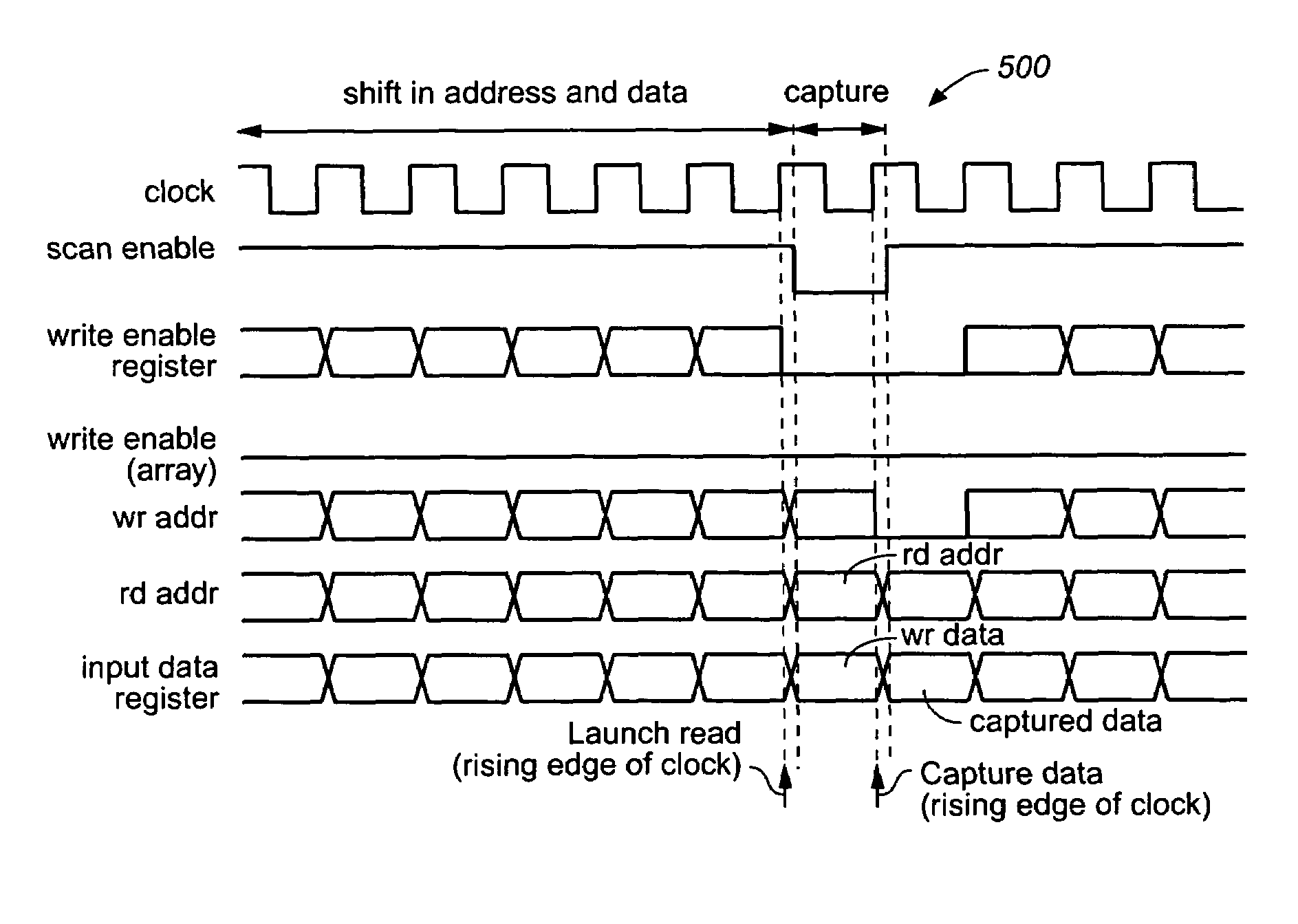

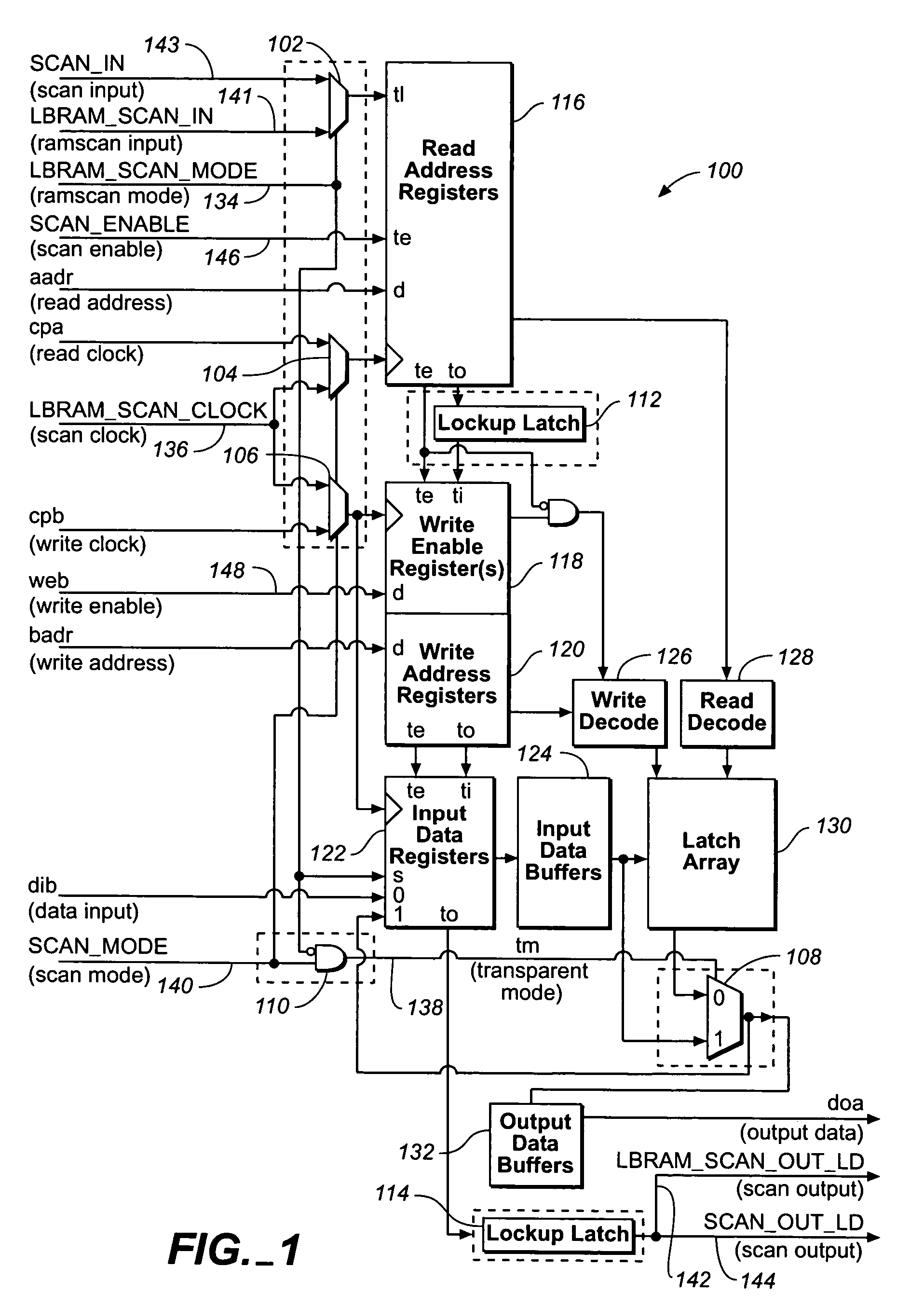

Method and apparatus for high speed testing of latch based random access memory

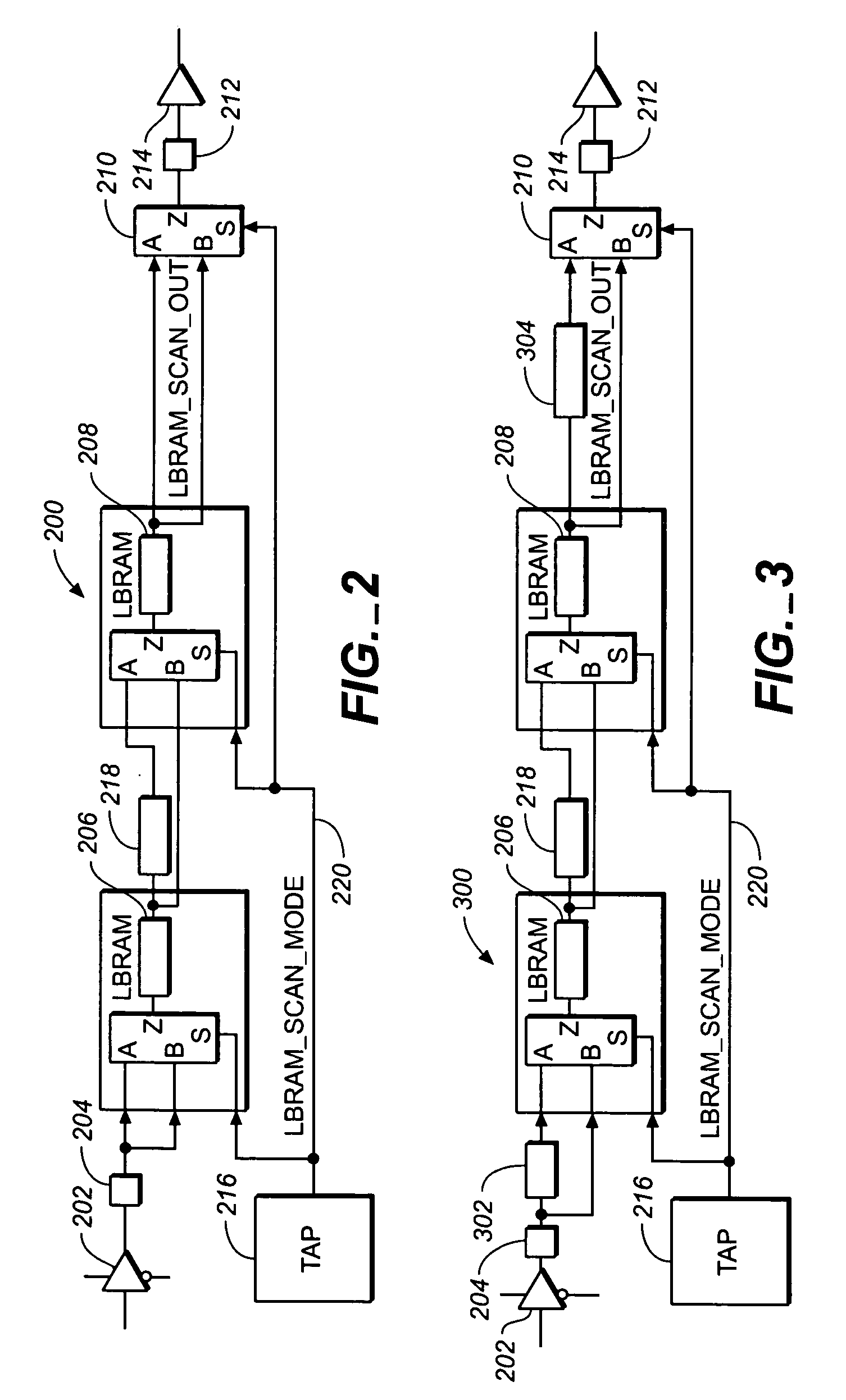

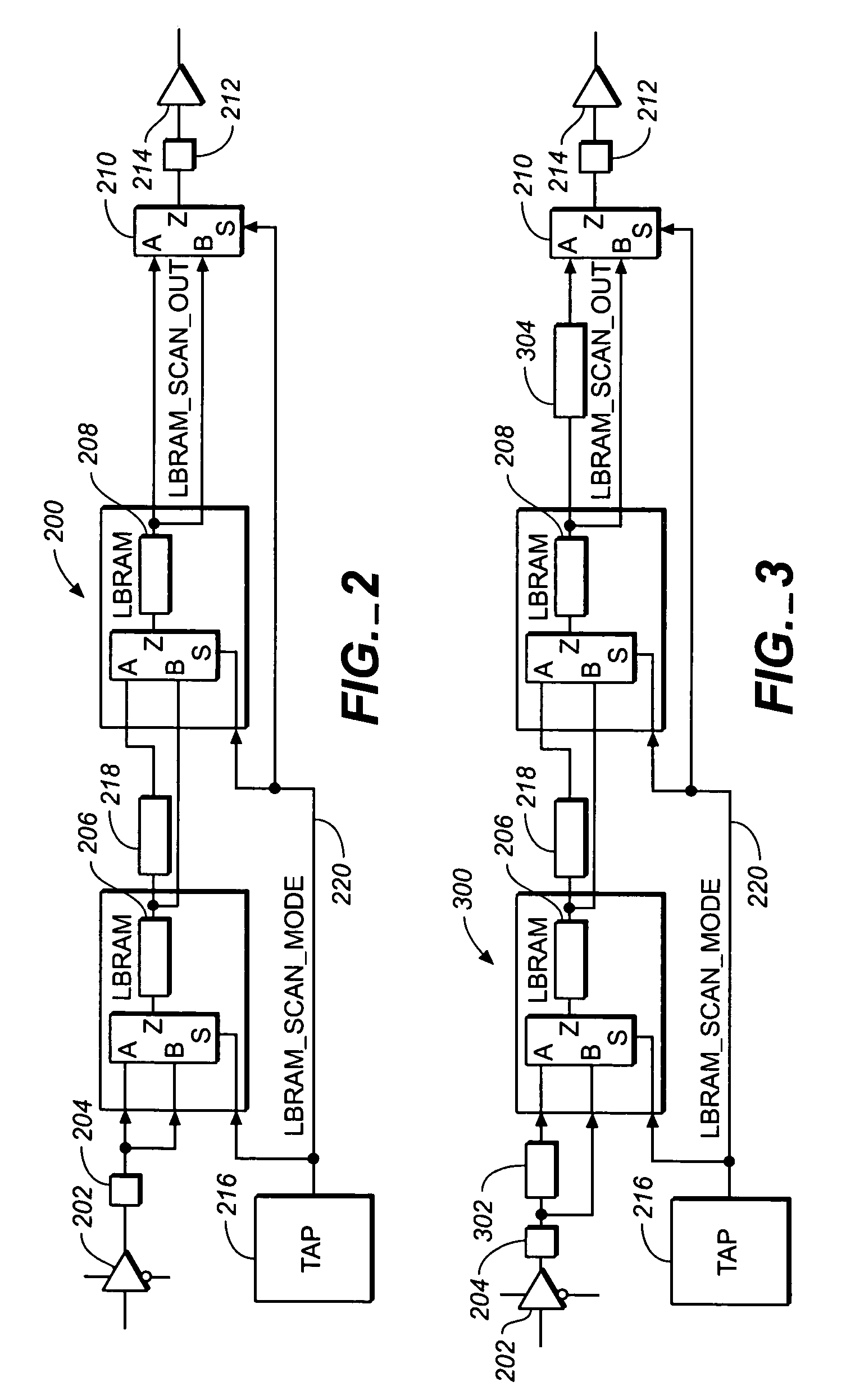

InactiveUS20050268185A1Minimize skewMinimize skew of the scan enable signalElectronic circuit testingDigital storageRandom access memoryClock signal

A method and apparatus for testing latch based random access memory includes steps of generating a scan enable signal for testing latch based random access memory and generating a scan clock signal for testing the latch based random access memory wherein the scan clock signal has a first scan clock period for a shift cycle and a second scan clock period for a capture cycle.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

Stackable optoelectronics chip-to-chip interconnects and method of manufacturing

ActiveUS20100027947A1Easily stackable/mountableImprove toleranceSemiconductor/solid-state device detailsFinal product manufactureElectricityLow speed

An optoelectronics chip-to-chip interconnects system is provided, including at least one packaged chip to be connected on the printed-circuit-board with at least one other packaged chip, optical-electrical (O-E) conversion mean, waveguide-board, and (PCB). Single to multiple chips interconnects can be interconnected provided using the technique disclosed in this invention. The packaged chip includes semiconductor die and its package based on the ball-grid array or chip-scale-package. The O-E board includes the optoelectronics components and multiple electrical contacts on both sides of the O-E substrate. The waveguide board includes the electrical conductor transferring the signal from O-E board to PCB and the flex optical waveguide easily stackable onto the PCB to guide optical signal from one chip-to-other chip. Alternatively, the electrode can be directly connected to the PCB instead of including in the waveguide board. The chip-to-chip interconnections system is pin-free and compatible with the PCB. The main advantages of this invention are to use the packaged chip for interconnection and the conventional PCB technology can be used for low speed electrical signal connection. Also, the part of the heat from the packaged chip can be transmitted to the PCB through the conductors, so that complex cooling system can be avoided.

Owner:BANPIL PHOTONICS

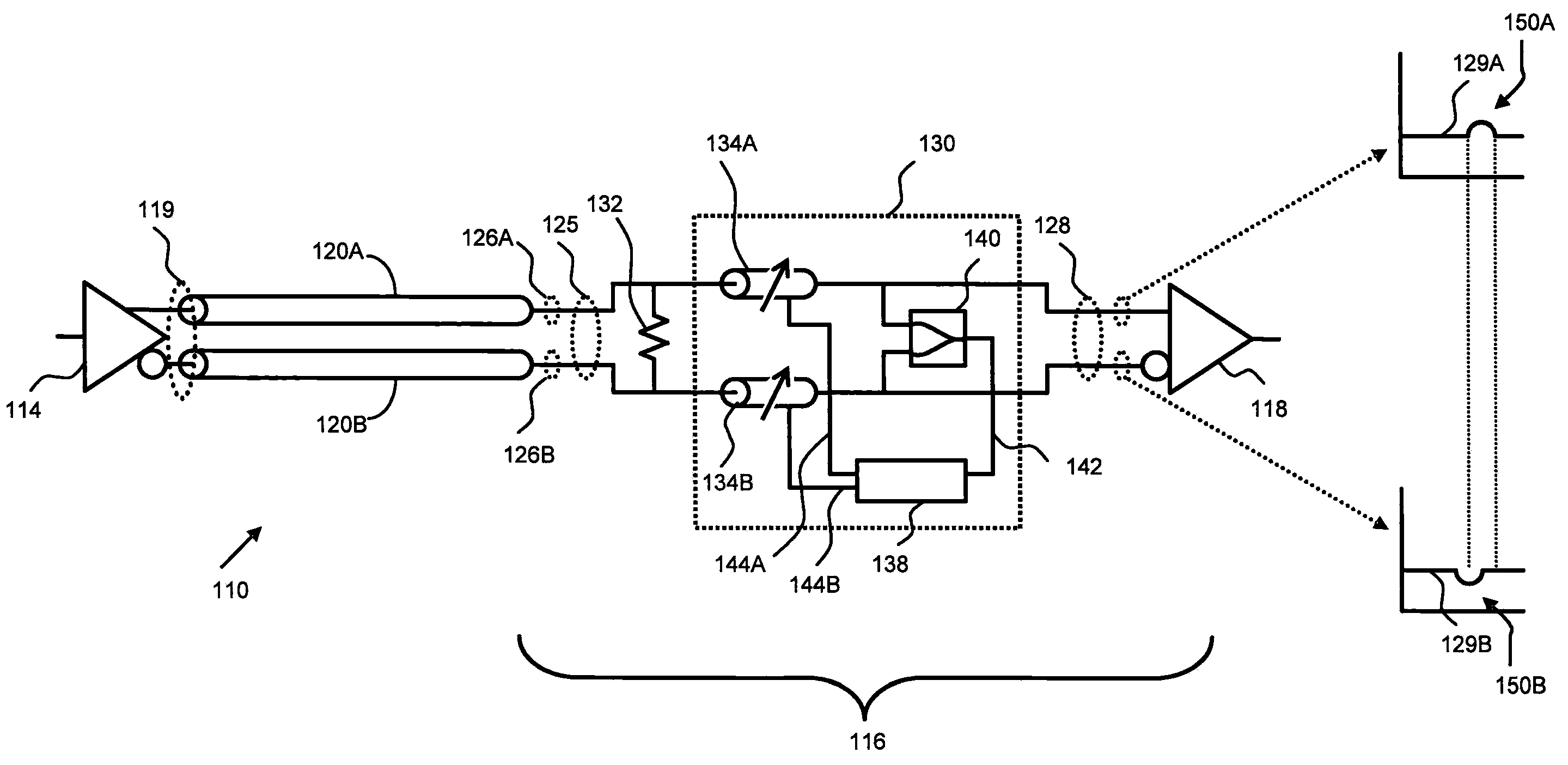

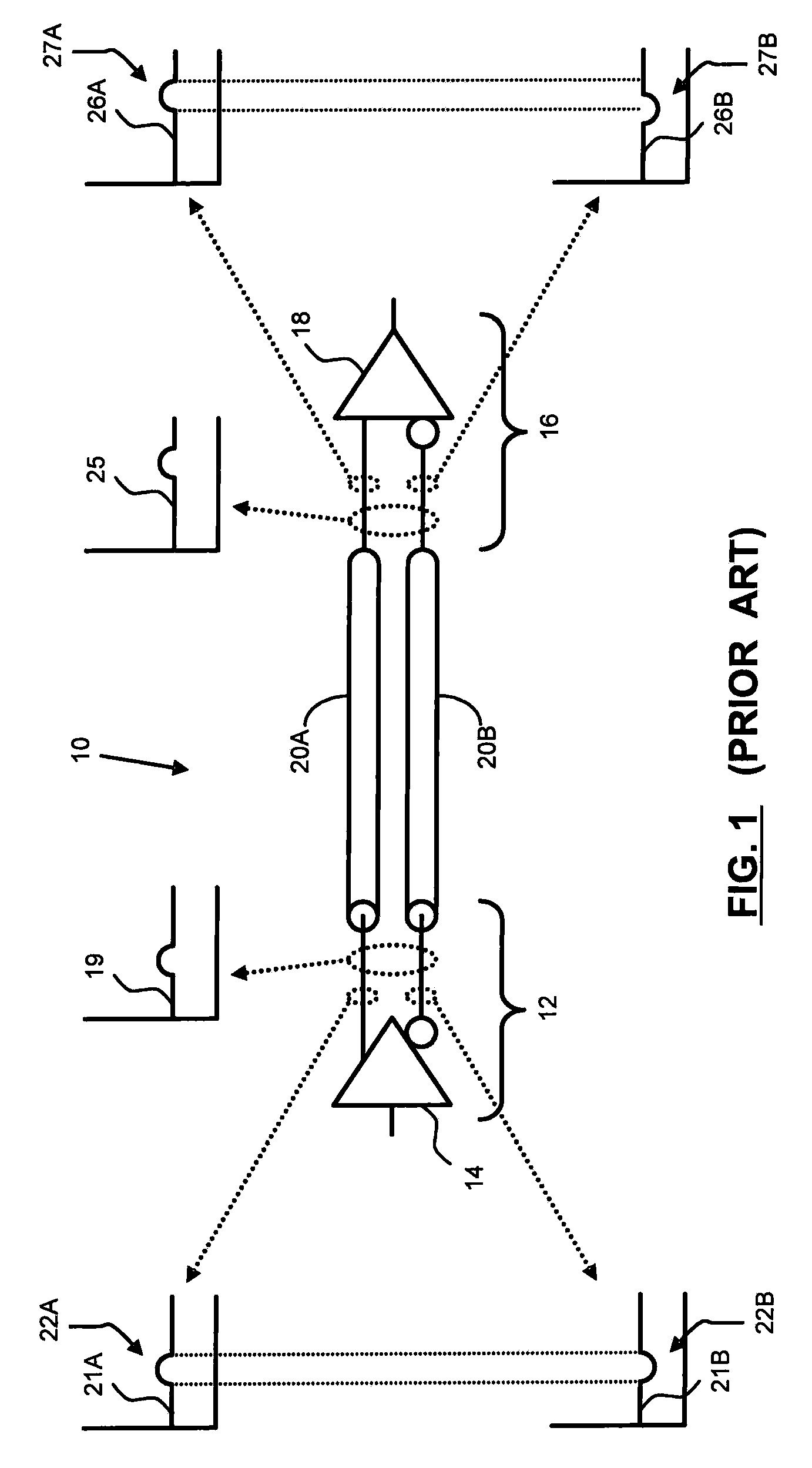

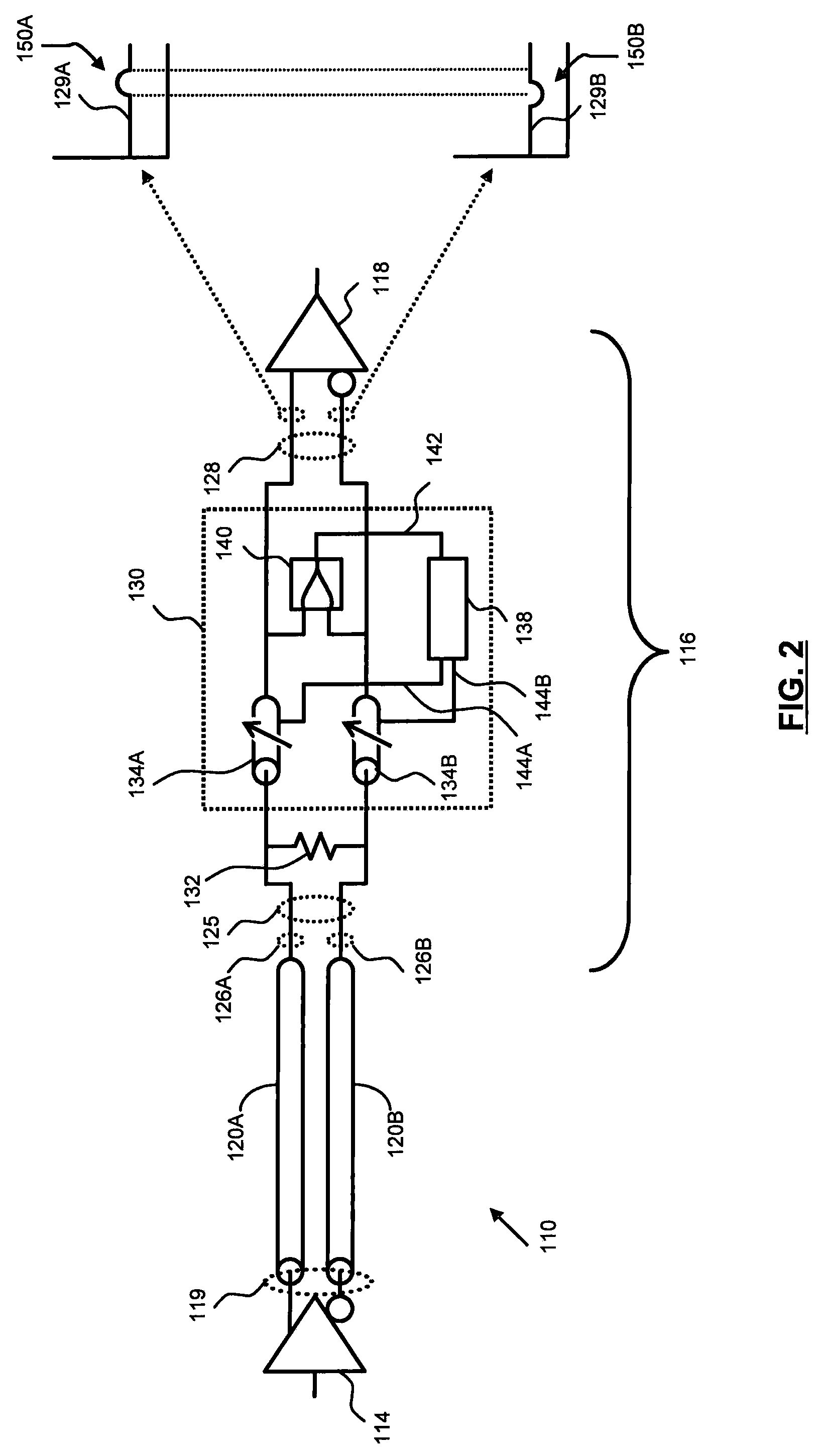

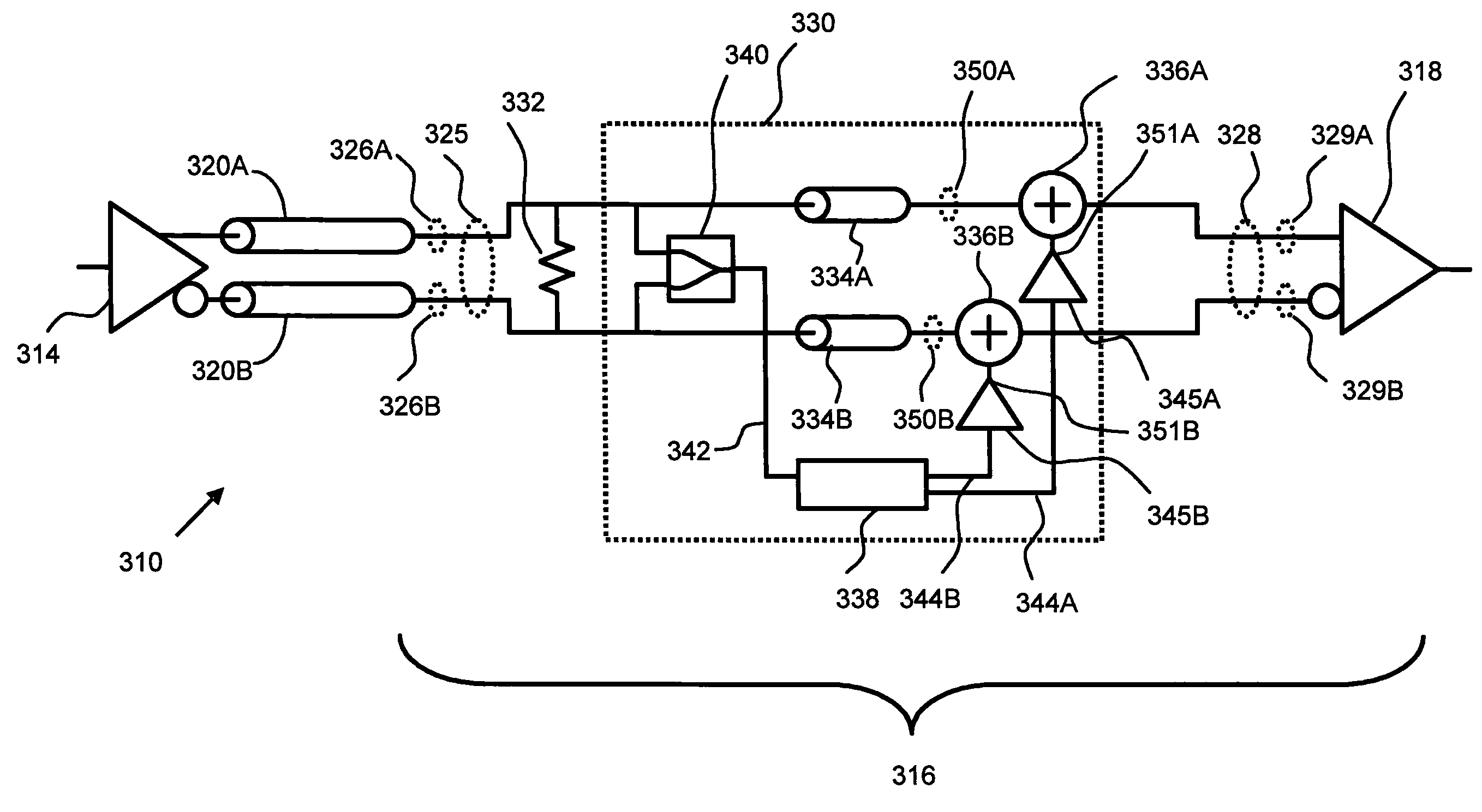

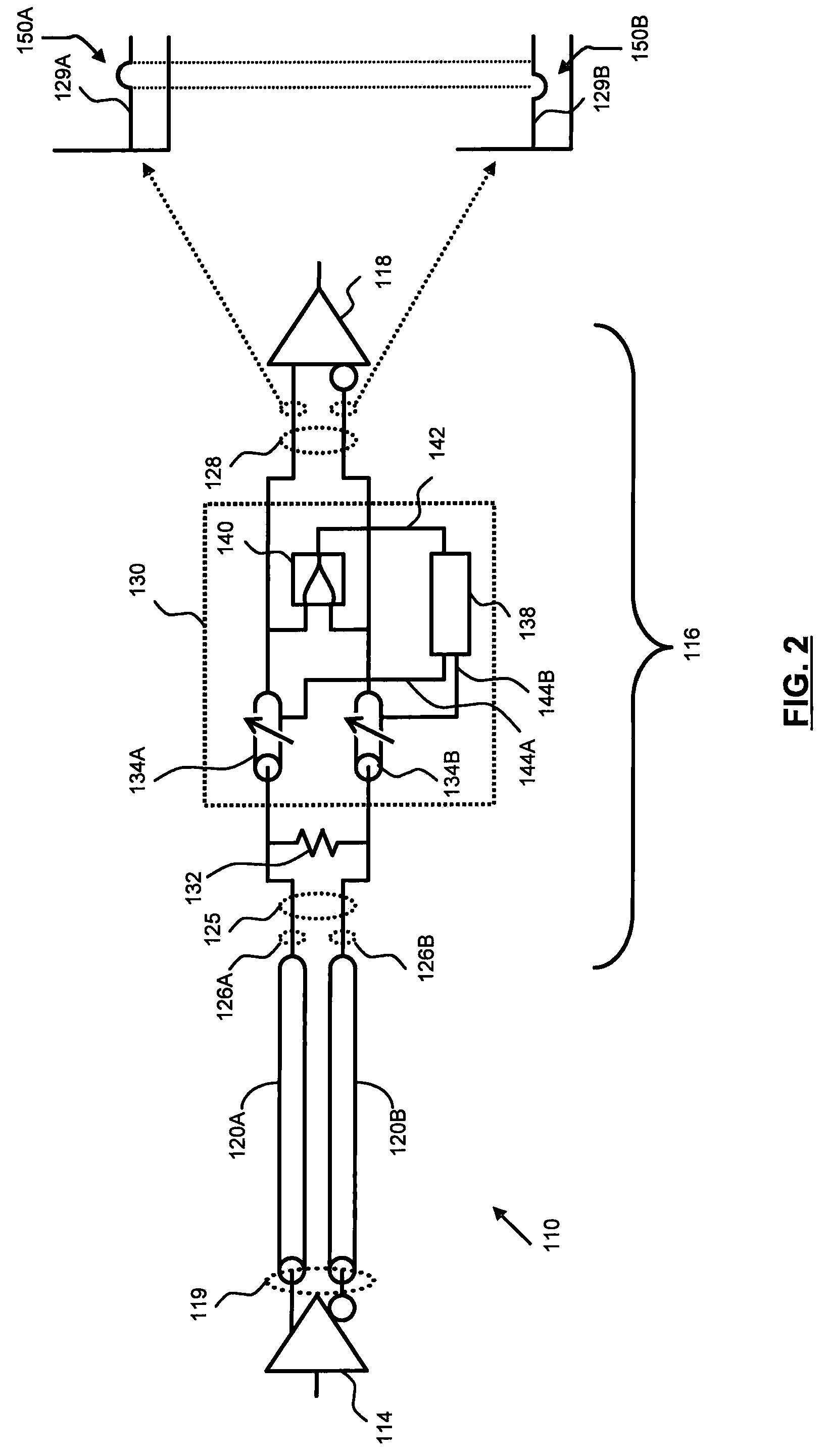

Differential communication link with skew compensation circuit

ActiveUS20090174448A1Minimize skewReduce signal reflectionPulse automatic controlError detection/correctionTelecommunications linkDifferential signaling

A system and method is presented for reducing skew between the positive and negative components of a differential signal in a high speed communications link. The communications link includes a signal generator producing and transmitting complementary positive and negative signals over separate transmission lines and a receiver receiving the complementary signals. The communication link further includes a skew compensation circuit having a skew detector, a controller, and separate delay and buffer elements for both the positive and negative component of the differential signal. The controller separately controls each of the delay or buffer elements in response to the detected skew between differential signal components.

Owner:MAYO FOUND FOR MEDICAL EDUCATION & RES

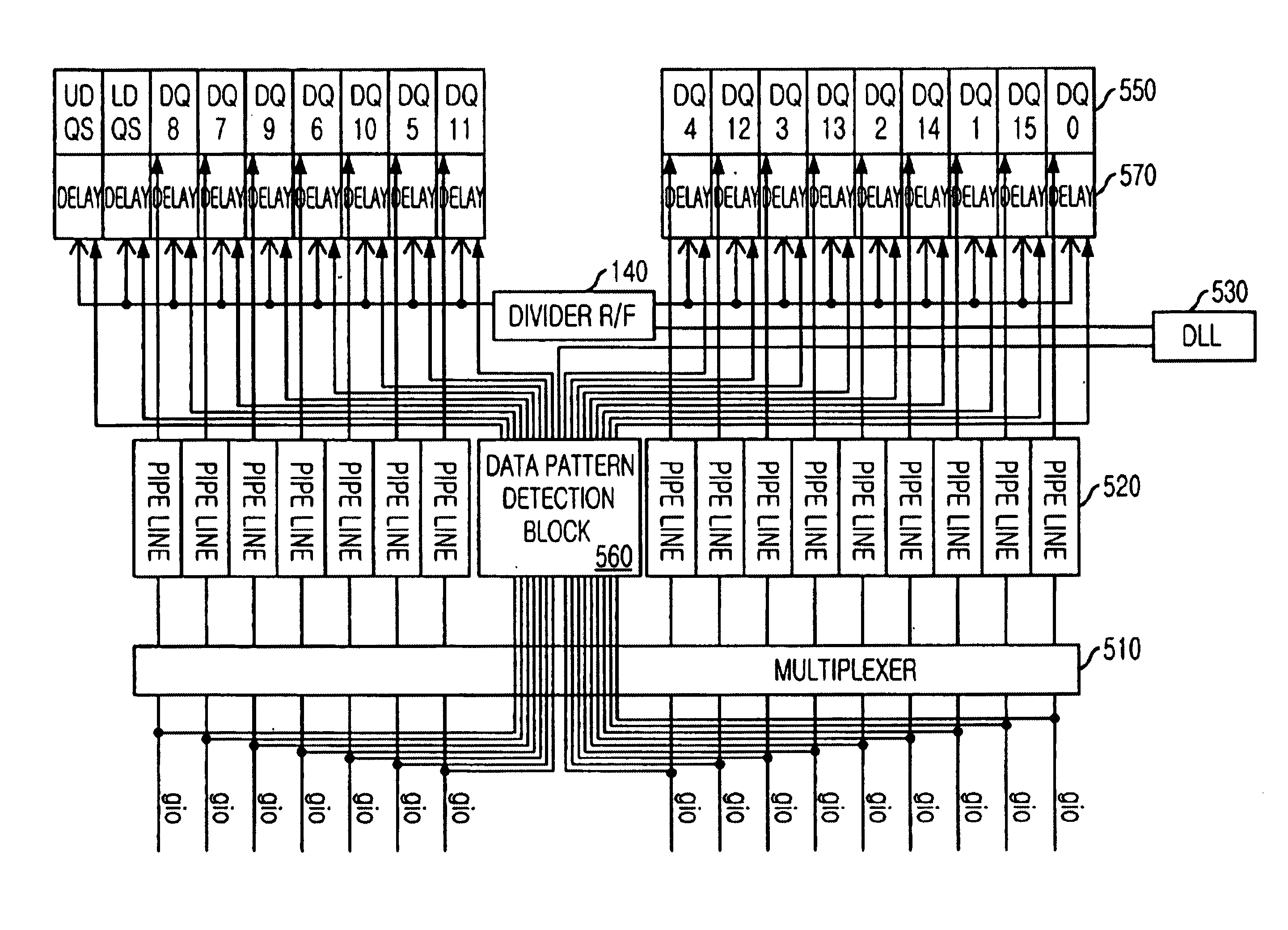

Apparatus and method of compensating for phase delay in semiconductor device

ActiveUS6859404B1Avoid it happening againMinimize skewPulse automatic controlSingle output arrangementsDelay-locked loopComputer science

An apparatus for minimizing a skew occurring due to a change of data pattern by previously recognizing data pattern before data is outputted from the semiconductor device. The apparatus of compensating for a phase delay in a semiconductor device having a delay locked loop (DLL) for generating DLL clock includes: a data pattern detection block for detecting patterns of data loaded on data line and determining delay compensation amount of the data inputted to data output driver based on the detected data patterns; and a delay compensation block for compensating for phase delay of clock relating to the DLL clock inputted to the data output driver under a control of an output signal of the data pattern detection block.

Owner:CONVERSANT INTPROP MANAGEMENT INC

Method and apparatus for high speed testing of latch based random access memory

InactiveUS7231563B2Minimize skewMinimize skew of the scan enable signalElectronic circuit testingDigital storageStatic random-access memoryRandom access memory

A method and apparatus for testing latch based random access memory includes steps of generating a scan enable signal for testing latch based random access memory and generating a scan clock signal for testing the latch based random access memory wherein the scan clock signal has a first scan clock period for a shift cycle and a second scan clock period for a capture cycle.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

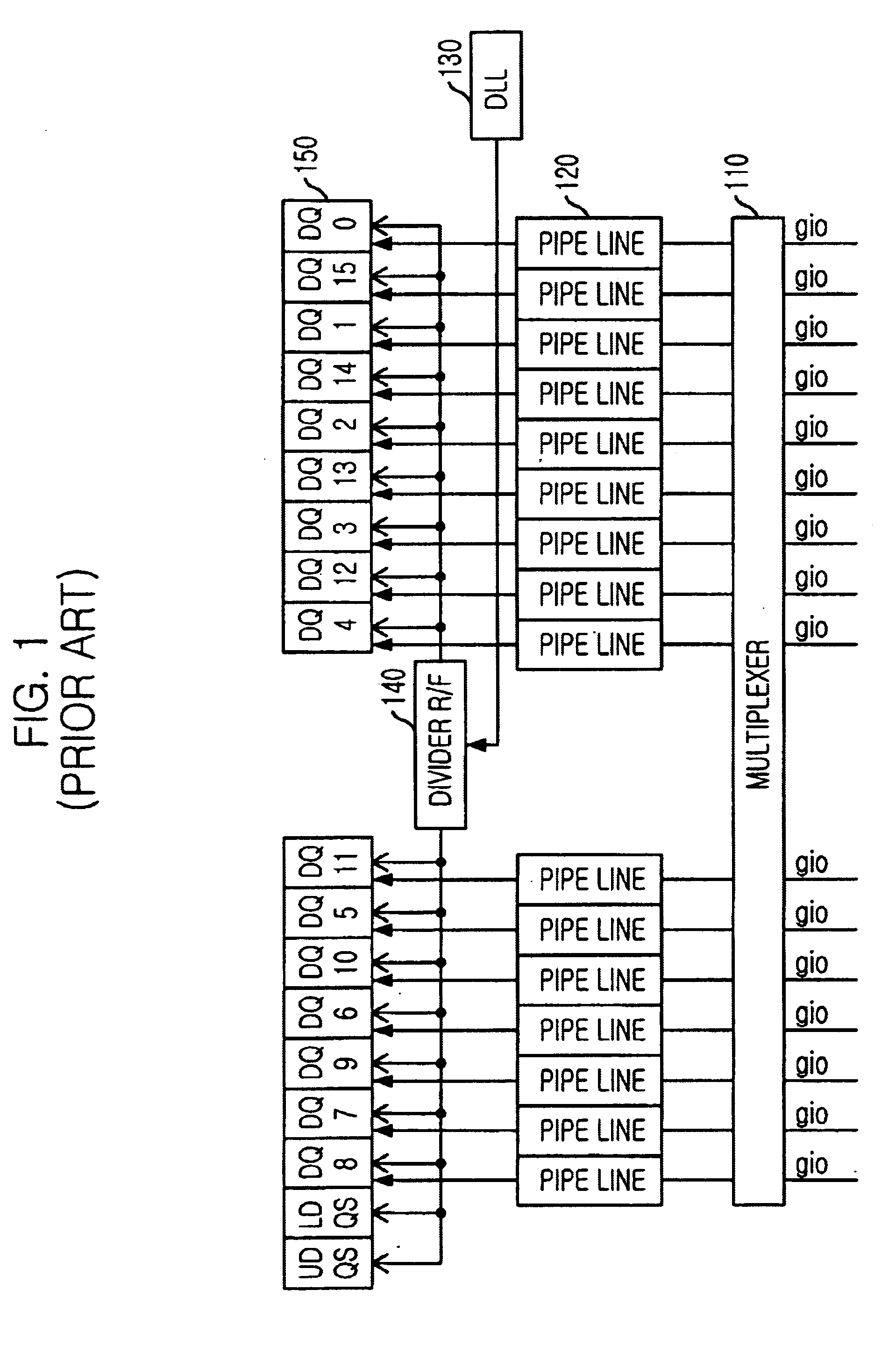

Pipe latch circuit and driving method thereof

ActiveUS20100142308A1Minimize the numberIncrease marginDigital storageElectric pulse generatorControl signalEngineering

A pipe latch circuit includes a pipe input unit configured to receive a plurality of data in an order corresponding to address information, a control signal generator configured to generate first and second control clock signals by using the address information, where the first and second control clock signals correspond to a synchronization clock signal, and a pipe output unit configured to synchronize an output signal of the pipe input unit with the first and second control clock signals and output the synchronized output signal.

Owner:SK HYNIX INC

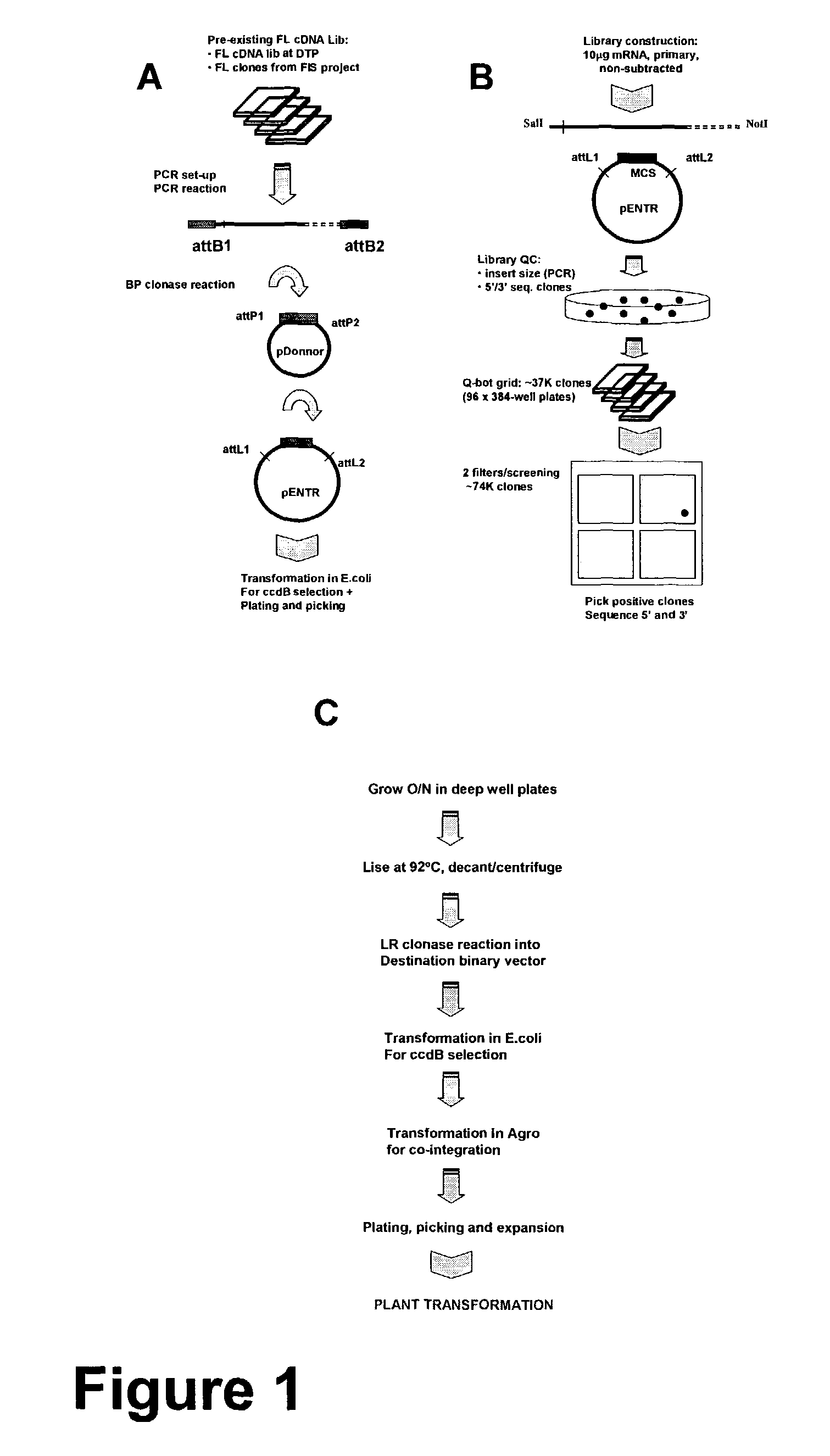

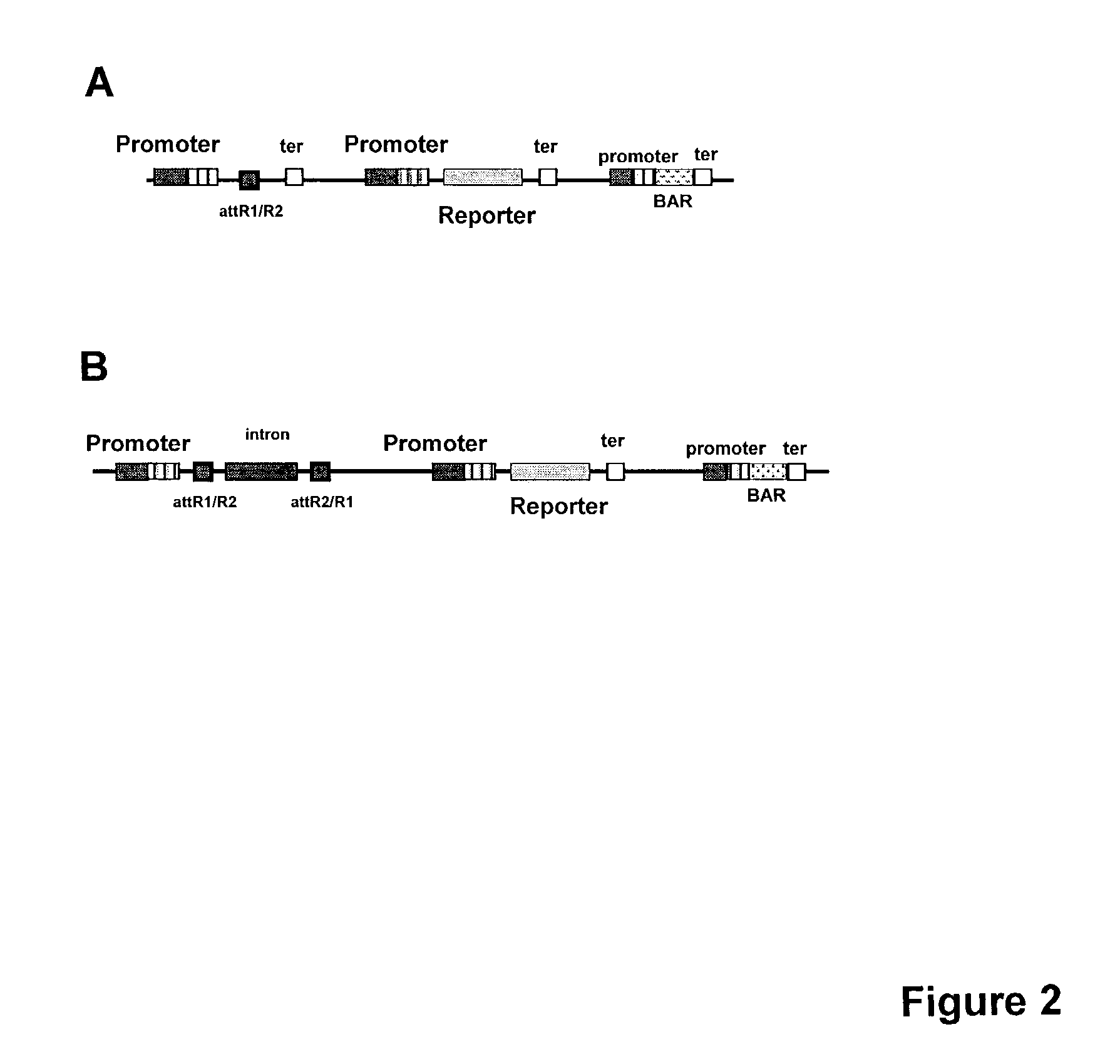

Methods for large scale functional evaluation of nucleotide sequences in plants

InactiveUS7928287B2Rapidly and efficiently designRapidly and efficiently and constructLibrary screeningFermentationNucleotideMass scale

The present invention provides for rapid and large scale evaluation of expression of, or function of, nucleotide sequences in plants. The invention comprises three specific components which provide for fast and large scale evaluation of nucleotide sequences. The first component includes delivery in either a single event a library of different engineered vectors or a single engineered vector for a single target nucleotide sequence comprising sequences the function of which is desired to be known in plant cells. Surprisingly, applicants have discovered that, the introduction of multiple vectors to plant cells predominantly results in individual transgenic plants which contain only a single transformation event. The second feature of the invention involves a highly transformable, fast cycling and / or miniature size plant and the final step involves mass scale analysis of T0 plants for various phenotypes and plasmid rescue to identify the nucleotide sequence present in a particular phenotype.

Owner:PIONEER HI BRED INT INC

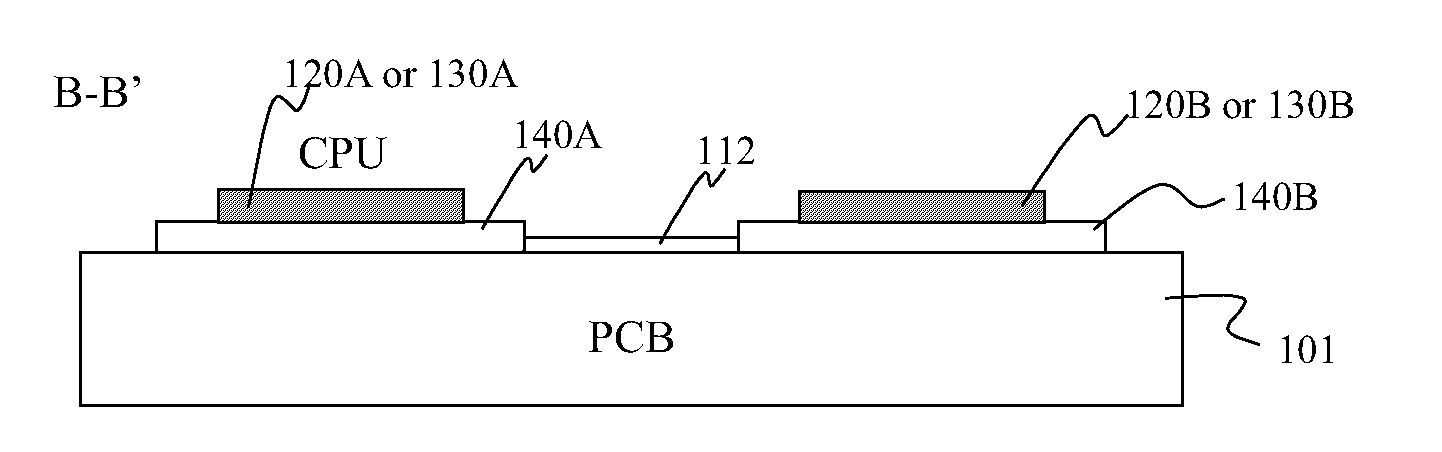

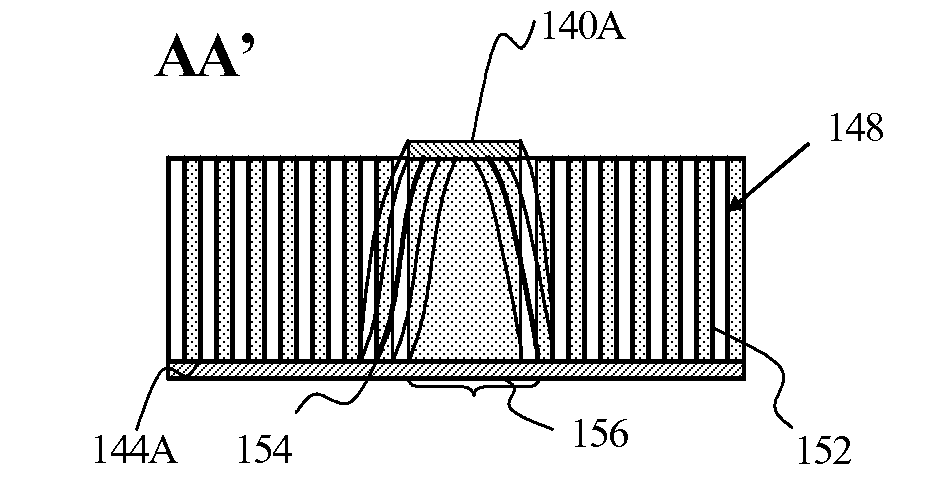

High speed electronics interconnect and method of manufacture

ActiveUS20090058567A1Effective dielectric constantIncrease bandwidth of interconnectionMultiple-port networksSemiconductor/solid-state device detailsElectricityDielectric loss

Fundamental interconnect systems for connecting high-speed electronics elements are provided. The interconnect systems consists of signal line, dielectric system with open trench or slot filled up with air or lower dielectric loss material, and the ground plane. The signal line could be for example, microstripline, strip line, coplanar line, single line or differential pairs. The interconnect system can be used for on-chip interconnects or can also be used for off-chip interconnects. The fundamental techniques provided in this invention can also be used for high-speed connectors and high-speed cables.

Owner:BANPIL PHOTONICS

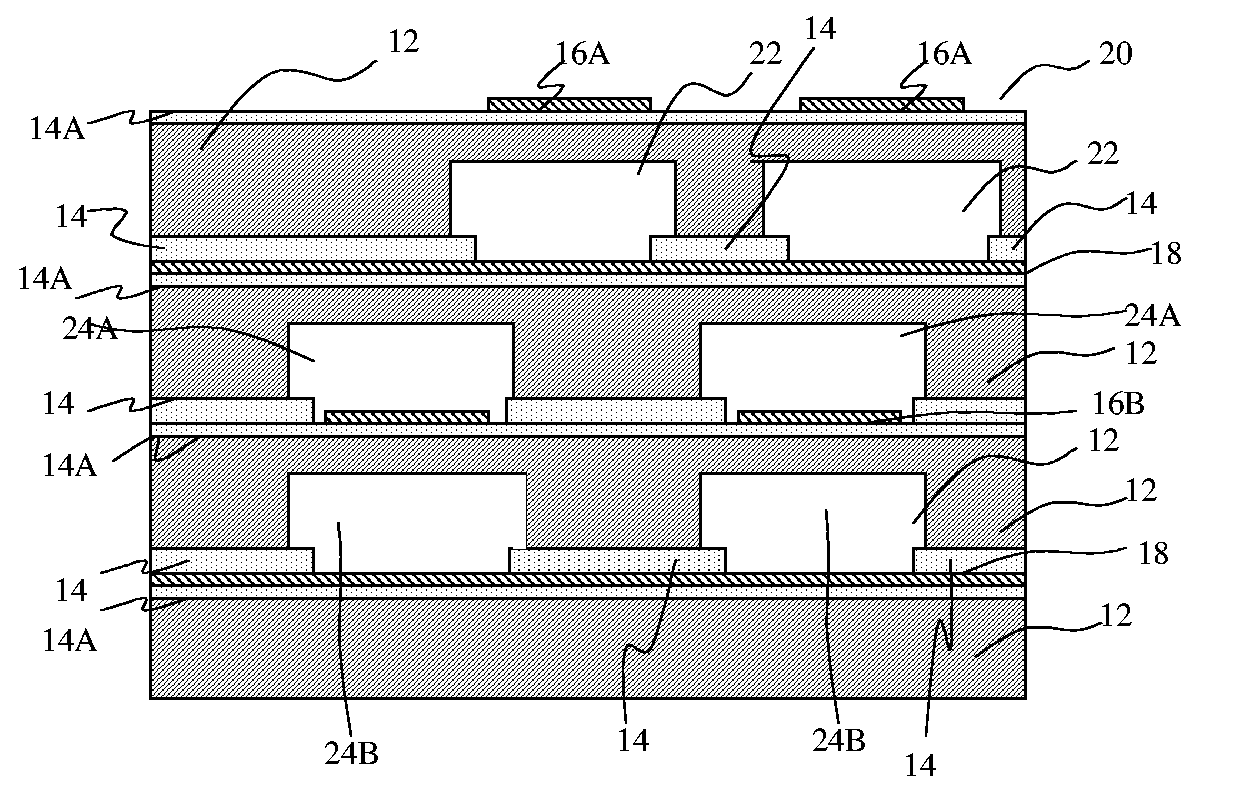

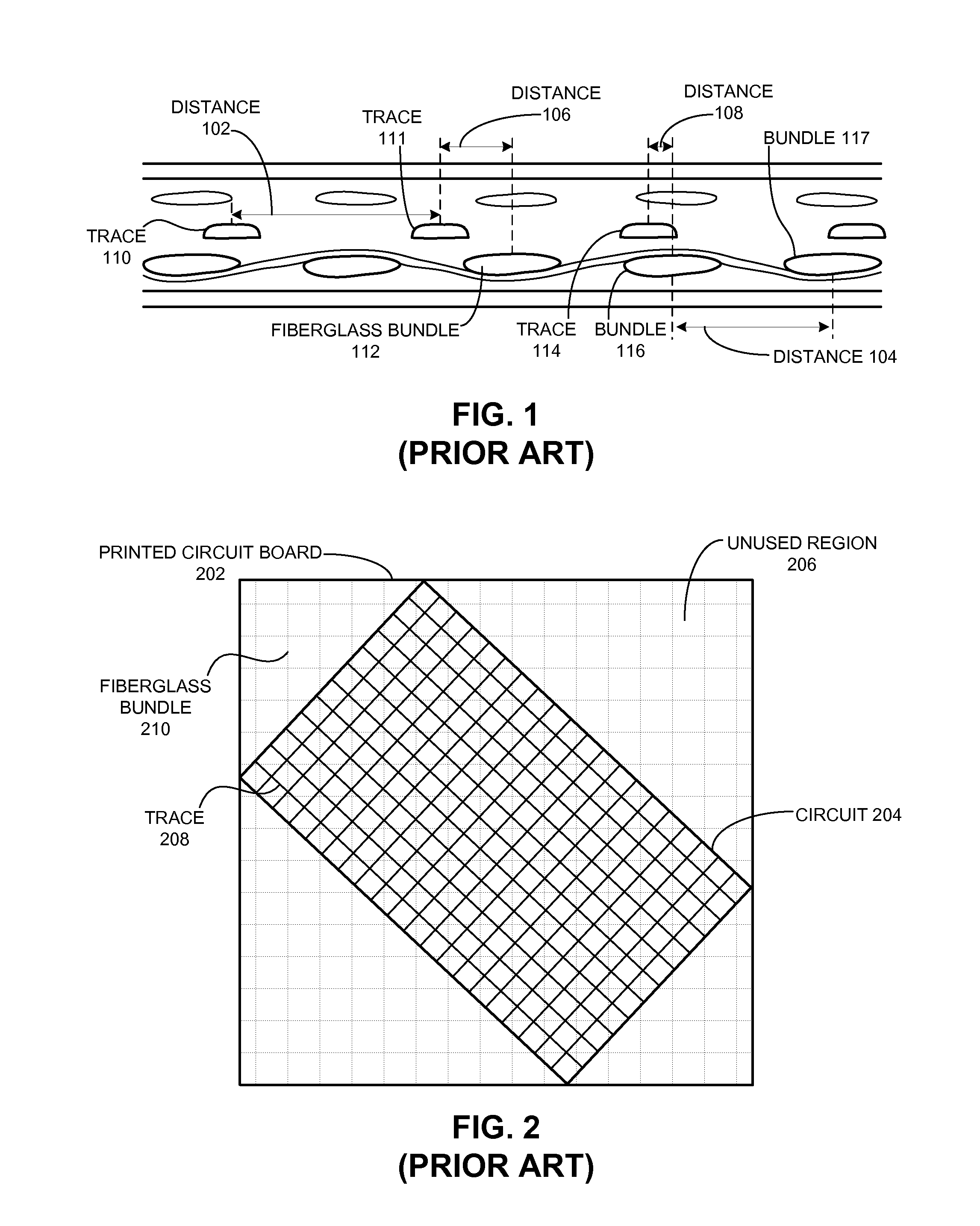

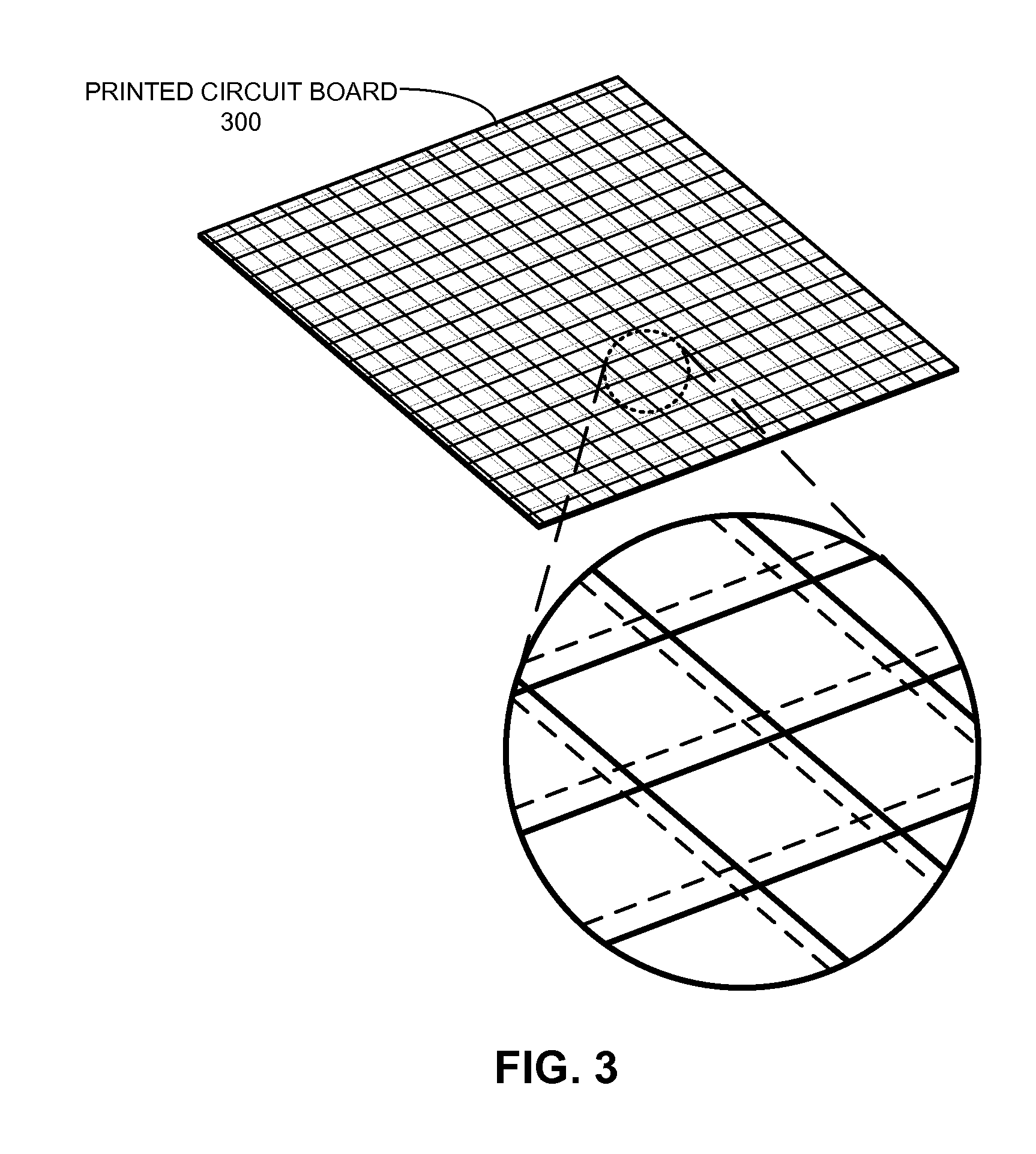

Printed circuit board with low propagation skew between signal traces

ActiveUS20110272186A1Minimize skewPrinted circuit aspectsConductive pattern formationGlass fiberEngineering

A printed circuit board (PCB) is configured to minimize skew between two parallel signal trace portions. The PCB comprises a laminate layer, which includes a fiberglass weave and includes a plastic resin deposited on each face of the fiberglass weave to form a first face and second face of the laminate layer. The fiberglass weave comprises a first set of fiberglass bundles in a first orientation interwoven with a second set of fiberglass bundles in a second orientation. Moreover, the PCB comprises trace a layer that is coupled to the first face of the laminate layer, and includes two or more signal traces. Two parallel trace portions of the two or more signal traces are configured to have a matching orientation and separation distance to a neighboring fiberglass bundle of the fiberglass weave, thereby ensuring that the two parallel trace portions encounter matching dielectric constants from the laminate layer.

Owner:ORACLE INT CORP

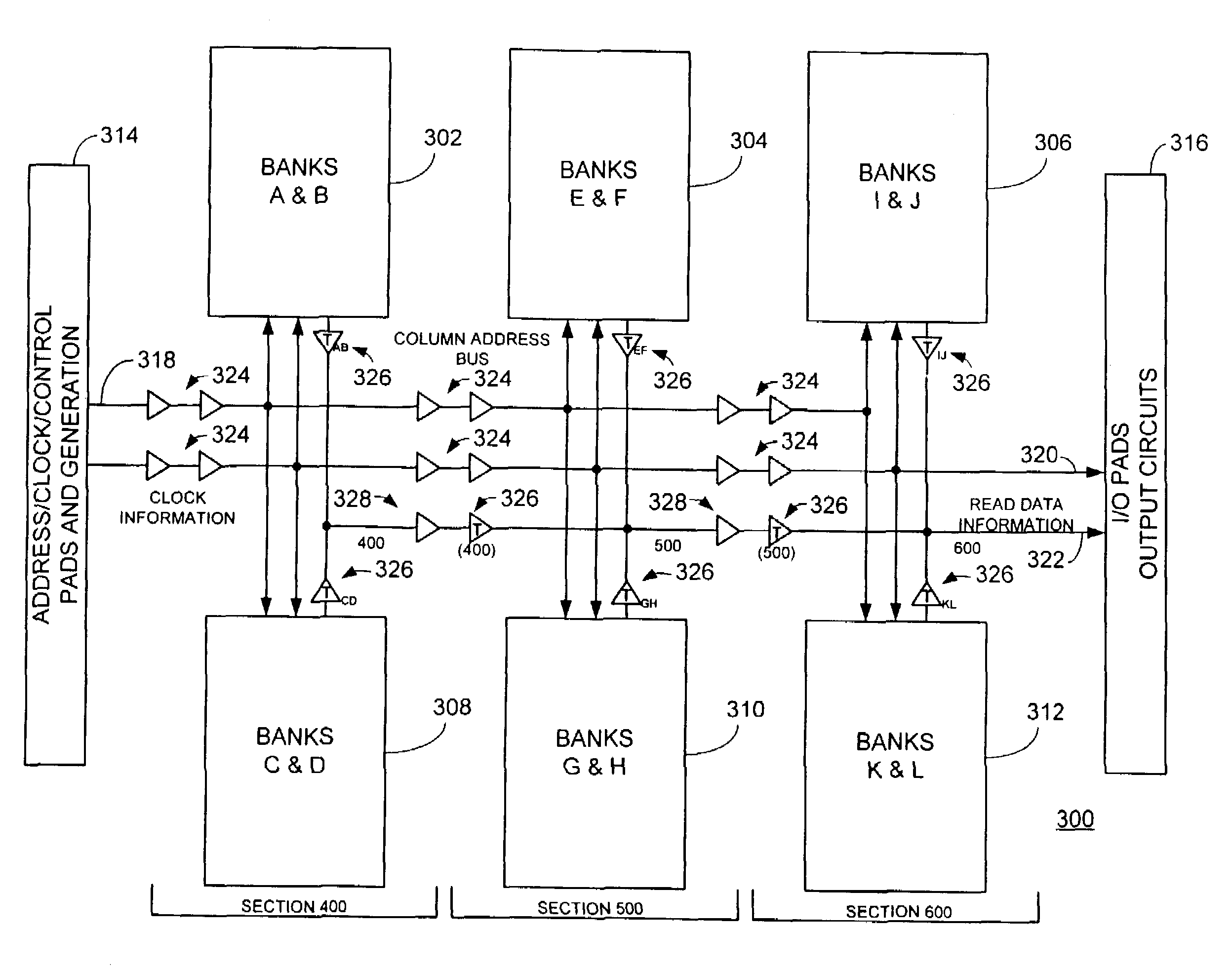

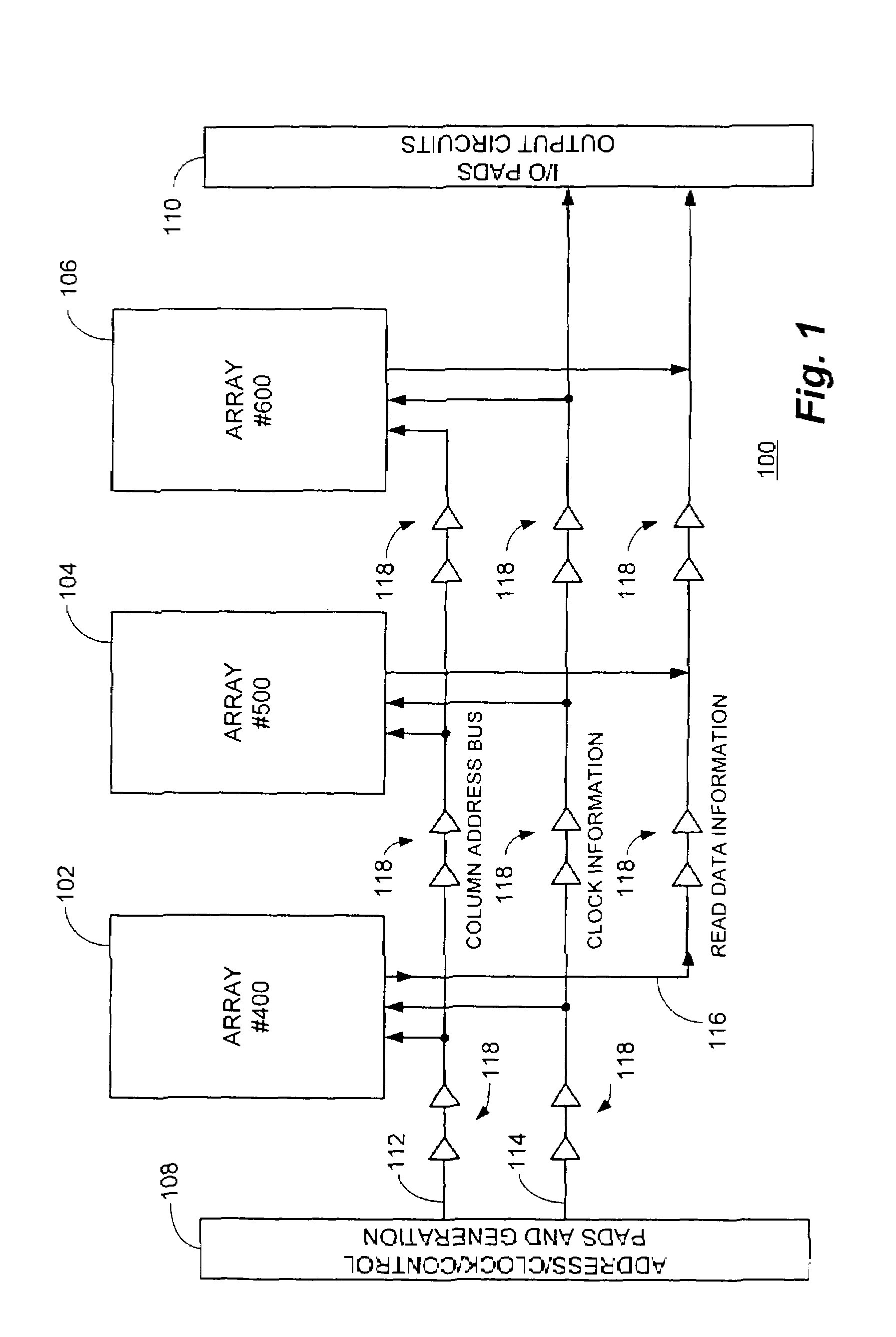

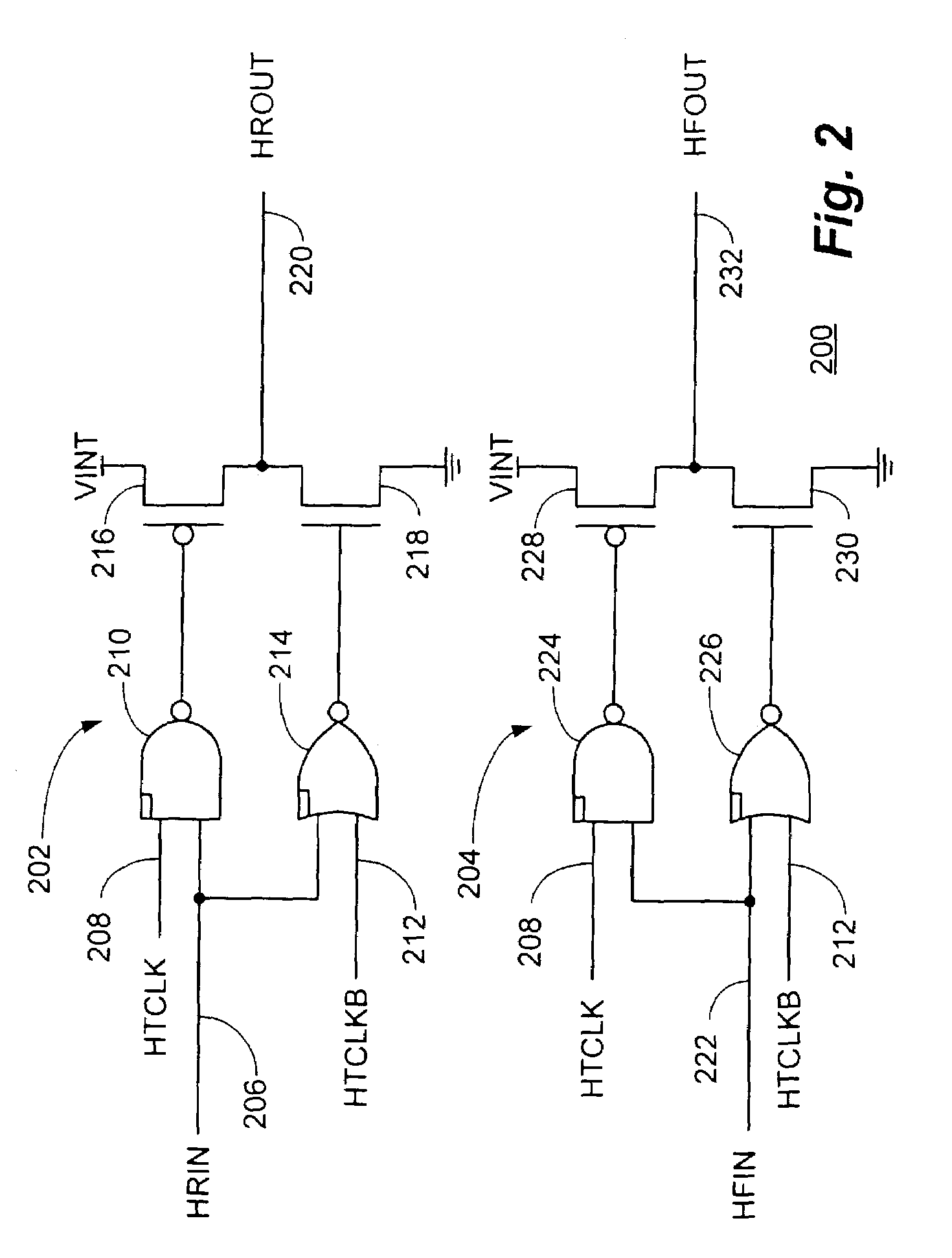

Integrated circuit memory architecture with selectively offset data and address delays to minimize skew and provide synchronization of signals at the input/output section

ActiveUS7039822B2Minimize skewEfficient additionDigital storageGenerating/distributing signalsMemory architectureDatapath

An integrated circuit memory architecture with selectively offset data and address delays to minimize skew and provide synchronization of signals at the input / output section in which the architecture is divided into memory sections, depending upon their distance from the address / control generation block. The address and clock information is re-driven between these sections, which effectively serves to add a quantized number of gate delays in the address path between the sections while concomitantly minimizing skew. A corresponding number of gate delays is also added to the “read” data path for each section such that the number of delays in the address / clock path plus the number of delays in the “read” data path is substantially constant.

Owner:PROMOS TECH INC

Memory device having delay locked loop

ActiveUS20050254318A1Minimize skewPulse automatic controlSingle output arrangementsControl signalDelay-locked loop

A memory device minimizes the skew between an external clock and a DQS (or DQ) after the locking state by regulating a delay ratio of a replica delay model to compensate errors of process, temperature or voltage change. The memory device comprises: an input clock buffer for buffering an externally inputted external clock to generate an internal clock; a DLL for delaying the internal clock to synchronize a phase of the external clock with that of a DQS; an output clock buffer for buffering an output clock outputted from the DLL; and an output control unit for generating the DQS using a clock outputted from the output clock buffer. Here, the DLL comprises a replica delay model for modeling delay factors of the input clock buffer and other delay factors until the output clock outputted from the delay line is outputted to the outside of a chip, and for regulating a delay ratio in response to a plurality of control signals inputted externally in a test mode.

Owner:SK HYNIX INC

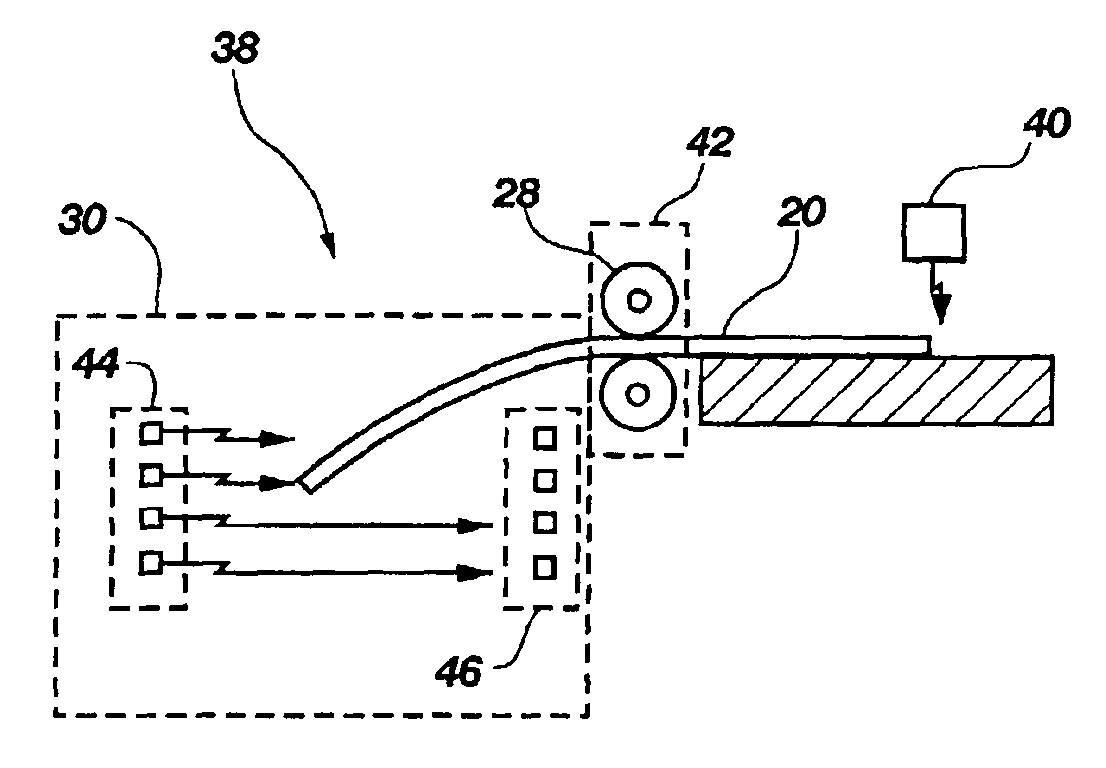

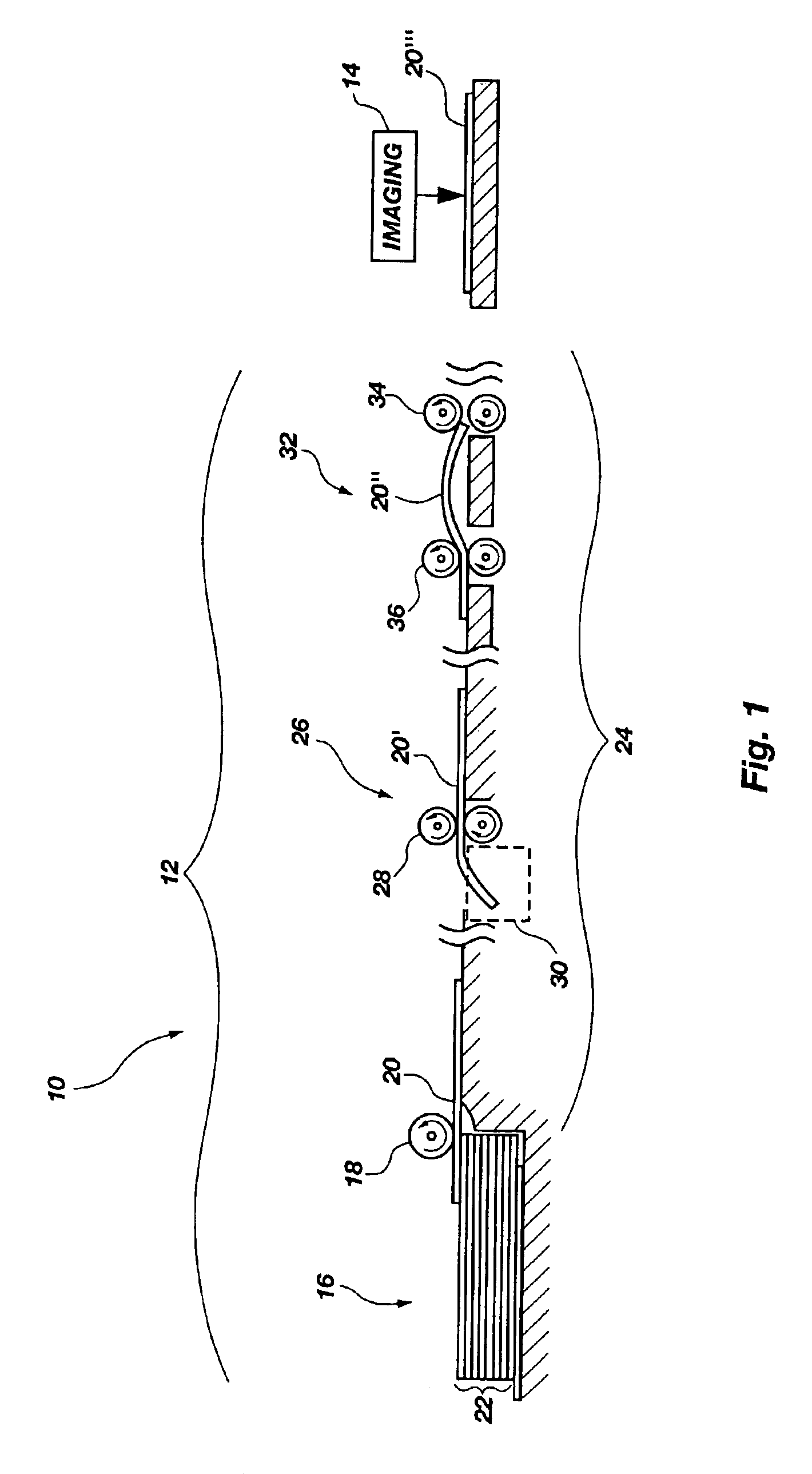

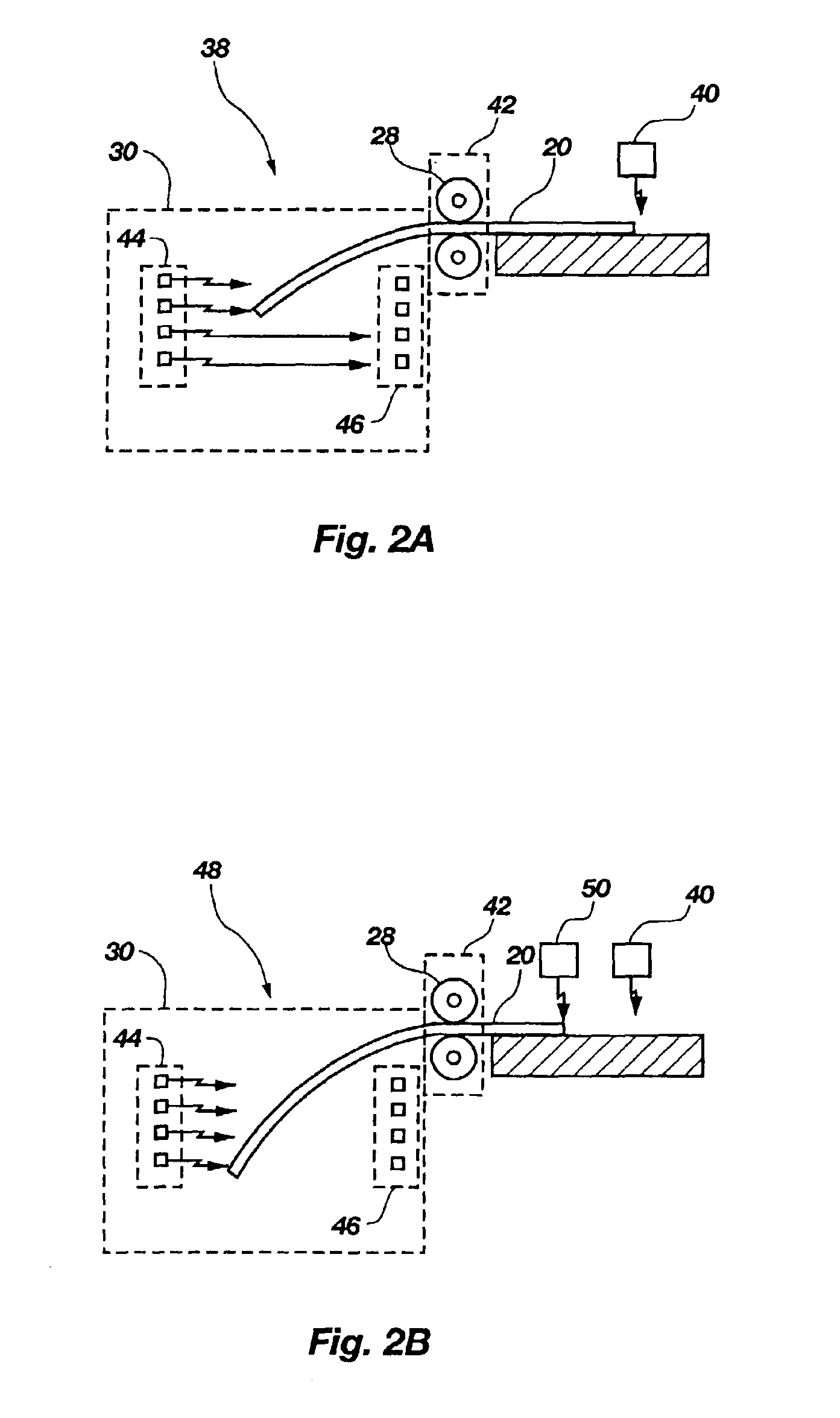

Media stiffness detection device and method therefor

ActiveUS6881972B2Improve performanceMinimize skewRegistering devicesForce measurementTrailing edgeHandling system

A media processing system retrieves a sheet of media and transports it to an imaging process. Misalignment of media from retrieving and transporting is removed by a media realignment process which wedges the leading edge of the media into stopped rollers while additionally advancing the trailing edge of the media for a predetermined distance. The media flexes and forms an arching buckle which aligns parallel to the leading edge of the media with the stopped rollers, thereby removing the skew of the media in relationship with the stopped rollers. The amount of over-advancement of the trailing edge of the media is modified according to the stiffness of the media. A media stiffness sensor measures the media stiffness by quantifying the deflection of the media when a portion of the media is cantilevered into deflection-measuring sensors. Imaging processes are also improved by employing media stiffness measurements to modify imaging processes.

Owner:HEWLETT PACKARD DEV CO LP

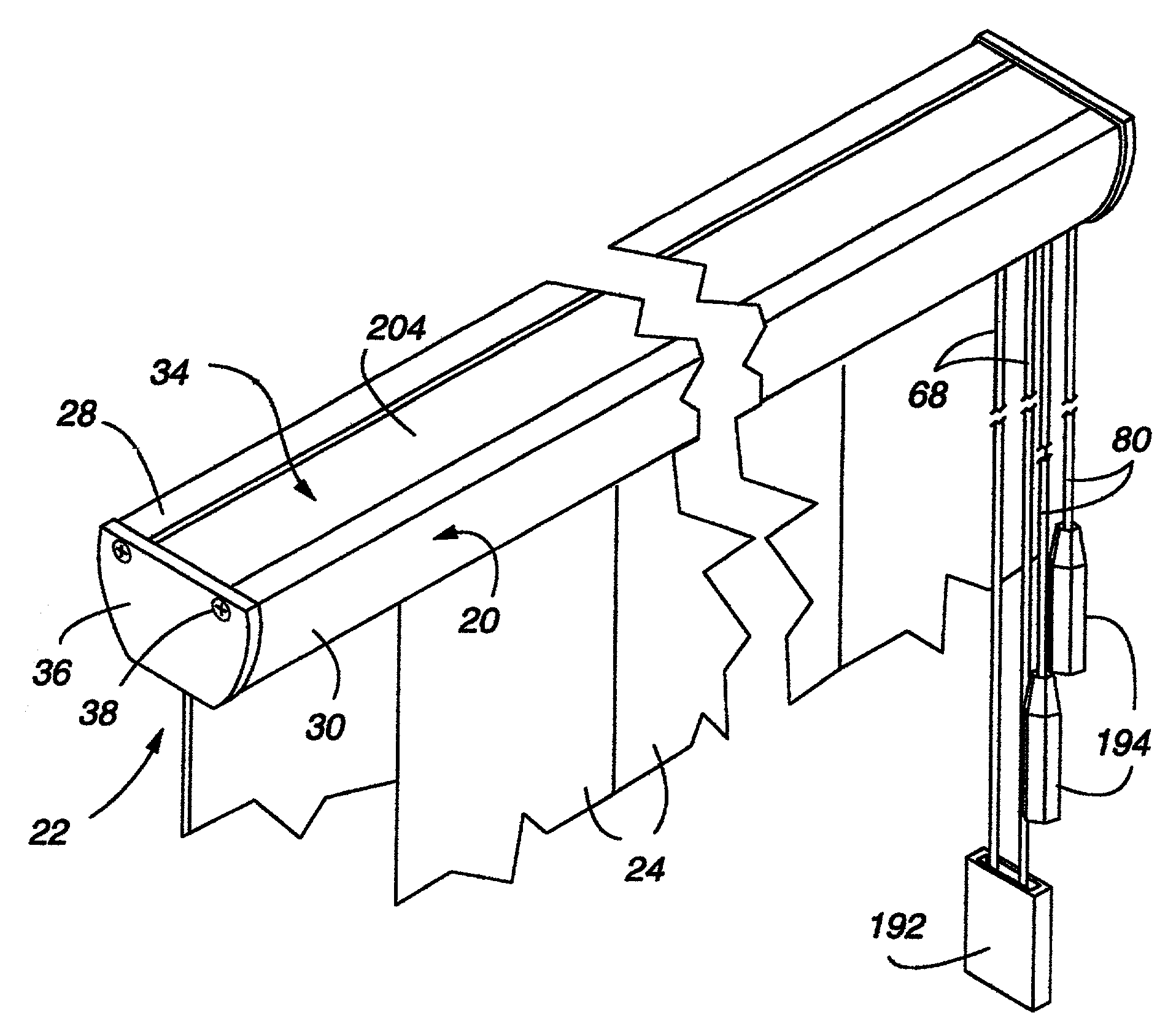

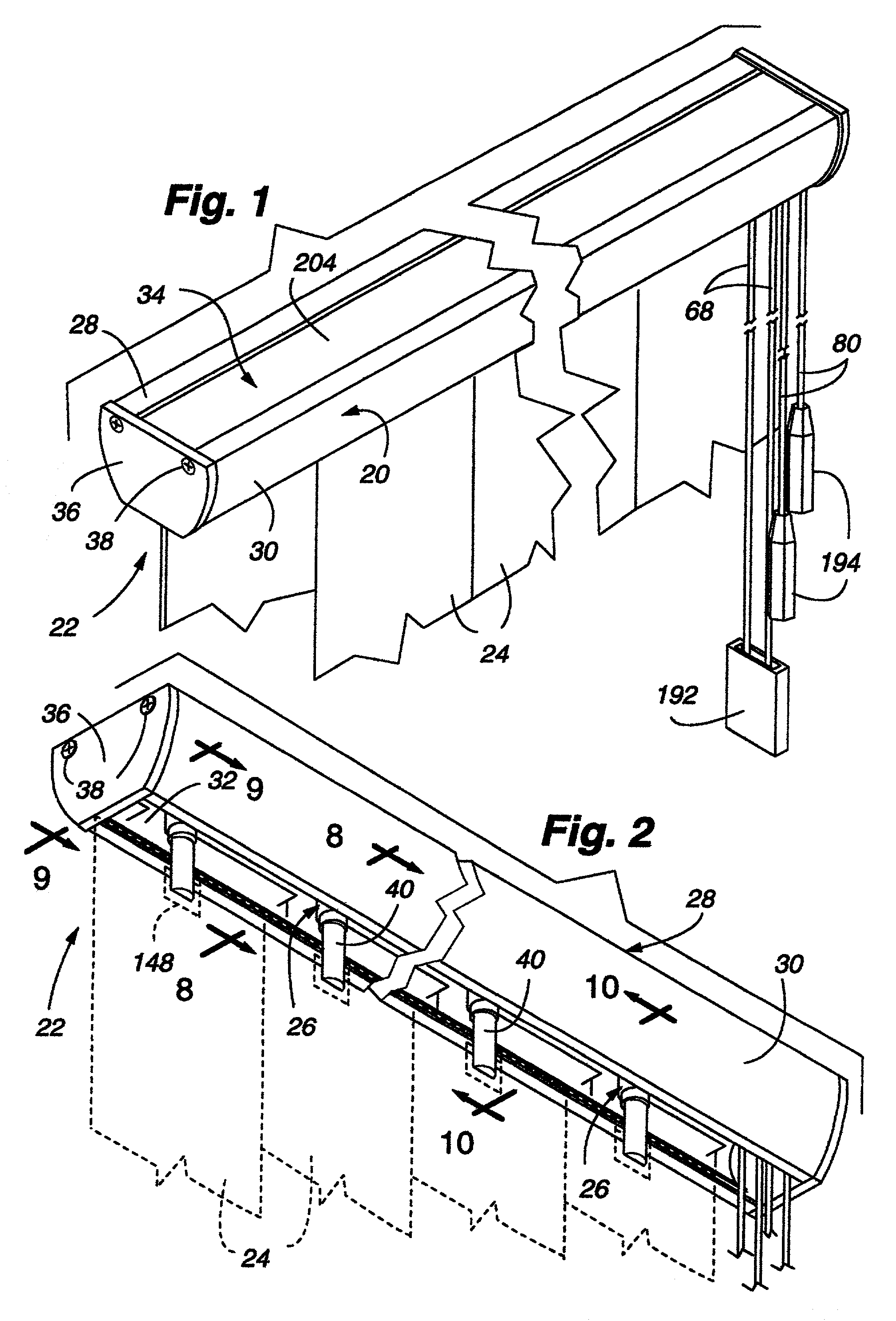

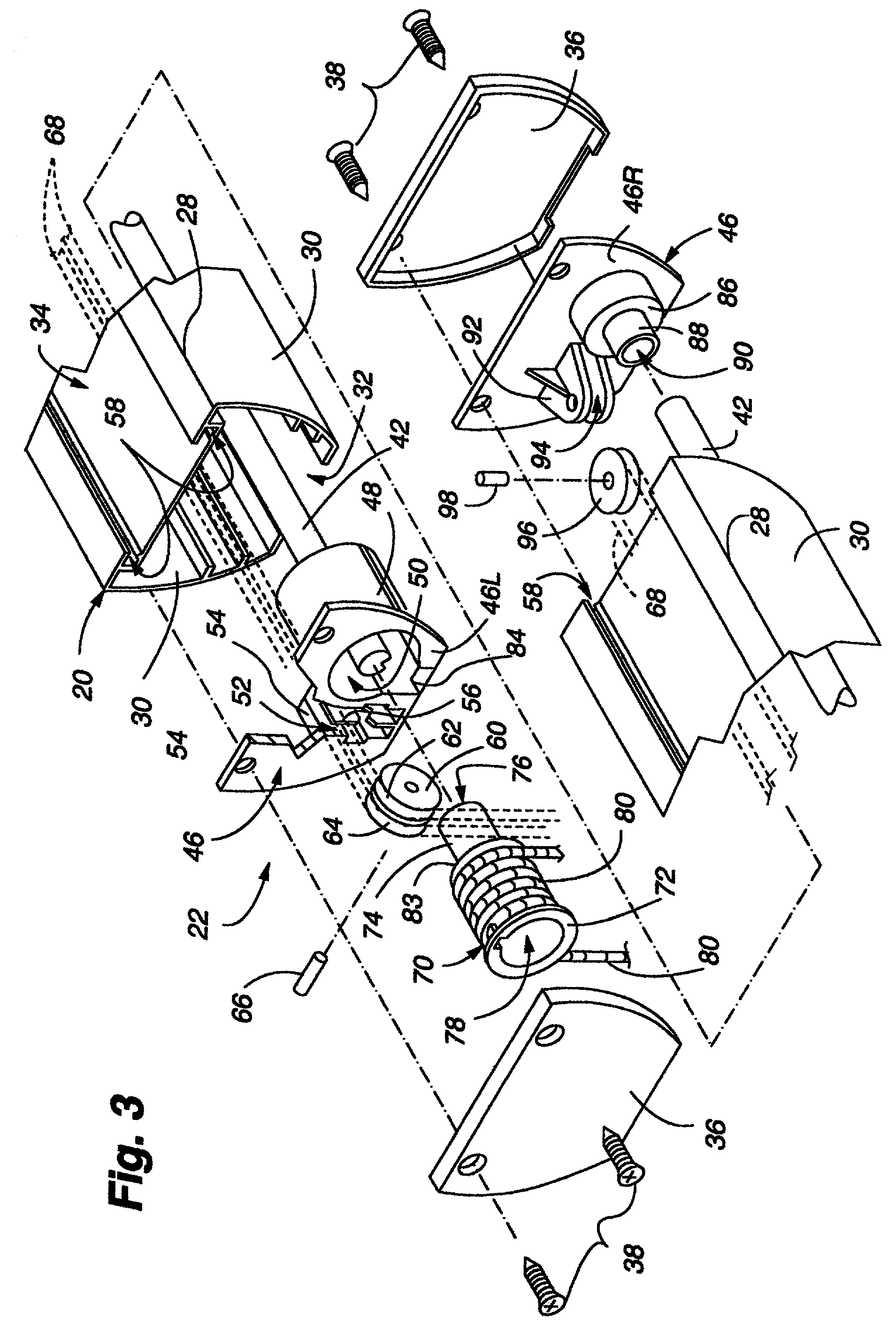

Control system for a vertical vane covering for architectural openings

InactiveUS6983784B2Minimize skewReduce weightScreensCurtain suspension devicesControl systemEngineering

A control system for a vertical vane covering for an architectural opening includes a new and improved symmetric headrail having uniquely designed carriers for suspending individual vanes wherein the carriers are designed to minimize skewing relative to a tilt rod as they are moved along the headrail. A pantograph system is utilized to interconnect the carriers, and is connected to the carriers in alignment with the tilt rod so as to minimize skewing. The carriers have pockets formed therein through which the traverse cord extends so that the traverse cord, which moves the carriers along the tilt rod, is secured to a lead carrier closely adjacent to the tilt rod to, again, minimize skewing. Light blocking rails are also attachable to the headrail to substantially bridge the gap between the headrail and the top of the suspended vanes to prevent light from passing therebetween. The tilt rod is keyed to gears in the carriers to facilitate assembly of the control system with all vanes properly aligned.

Owner:HUNTER DOUGLAS INC

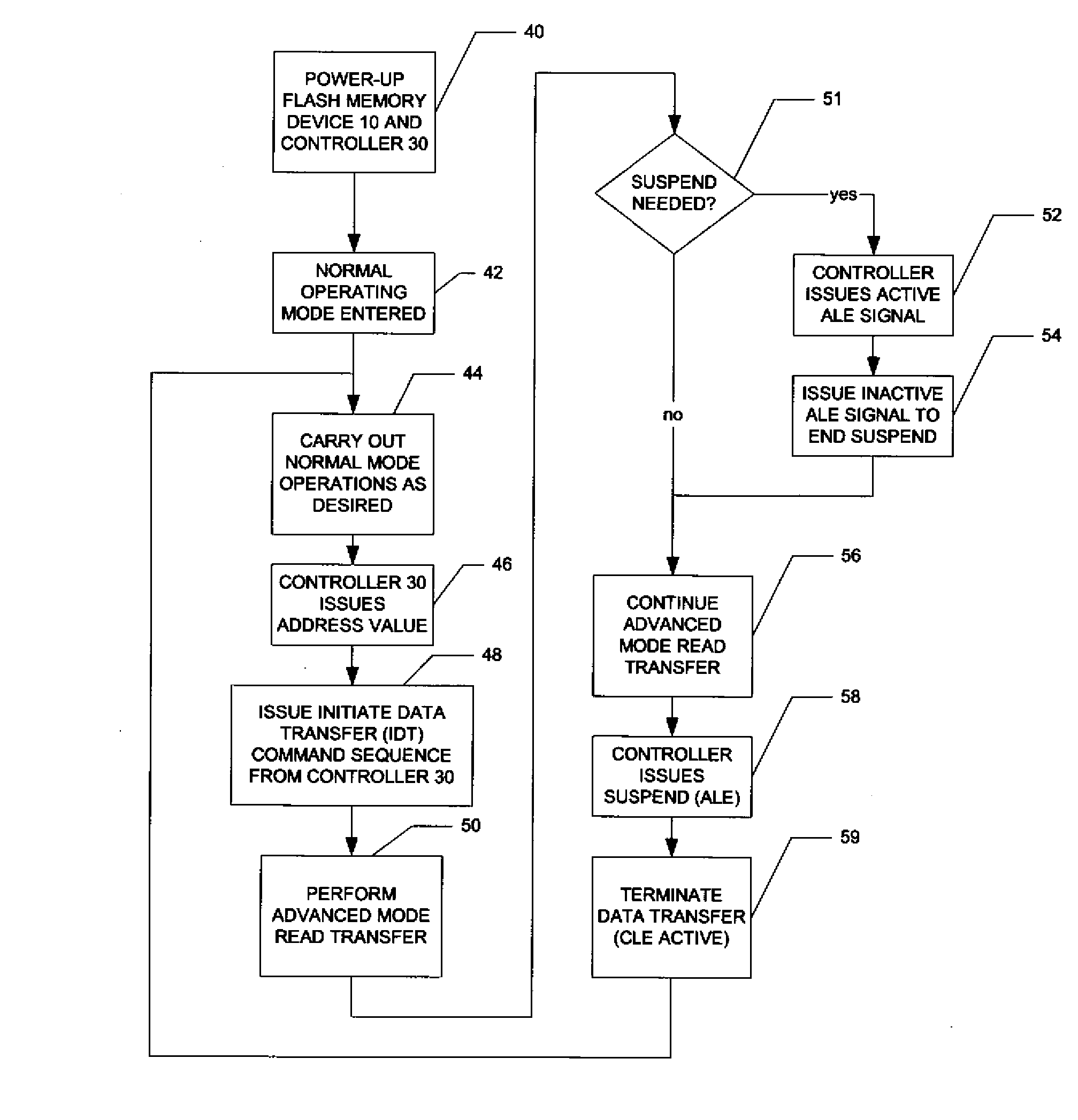

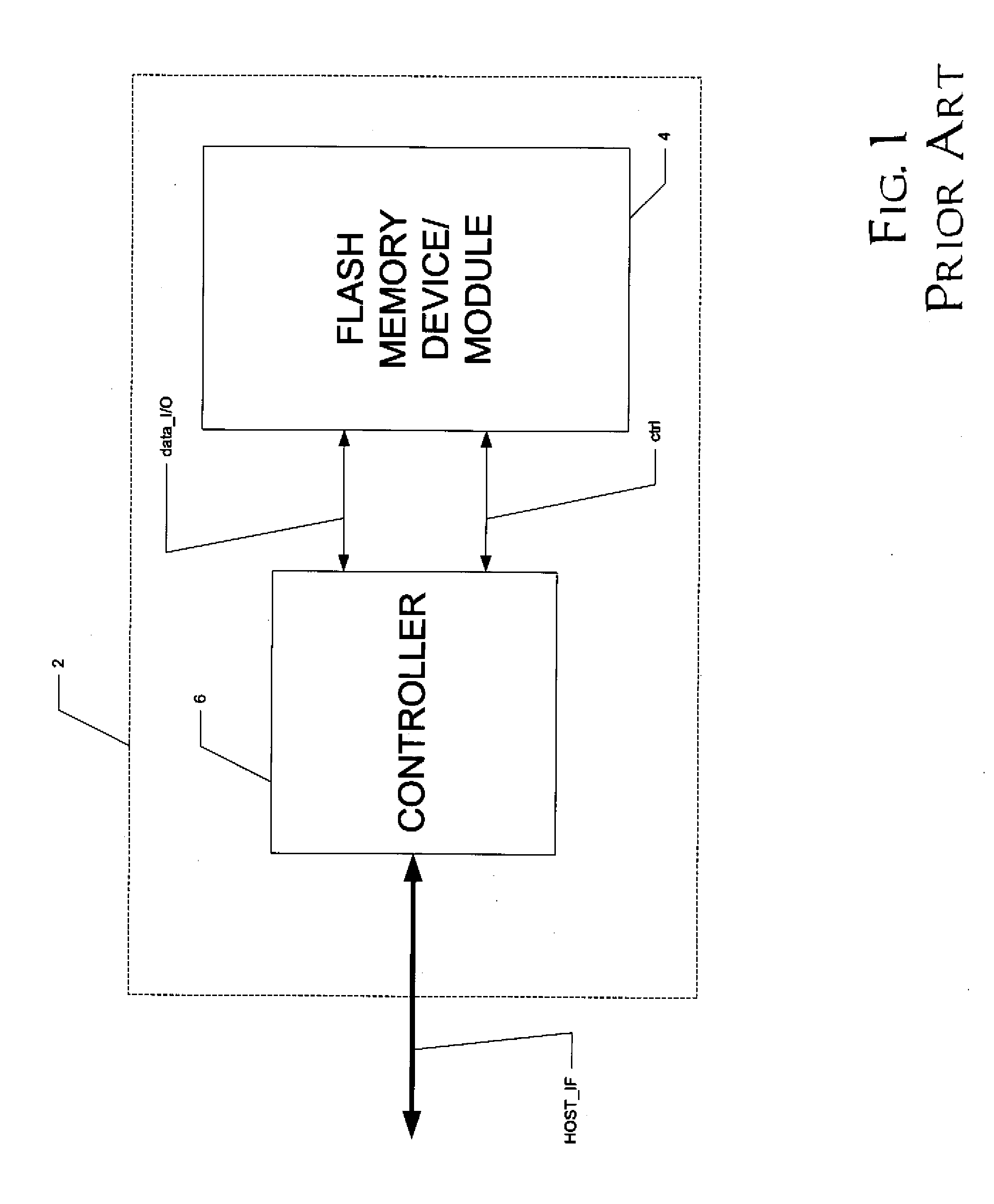

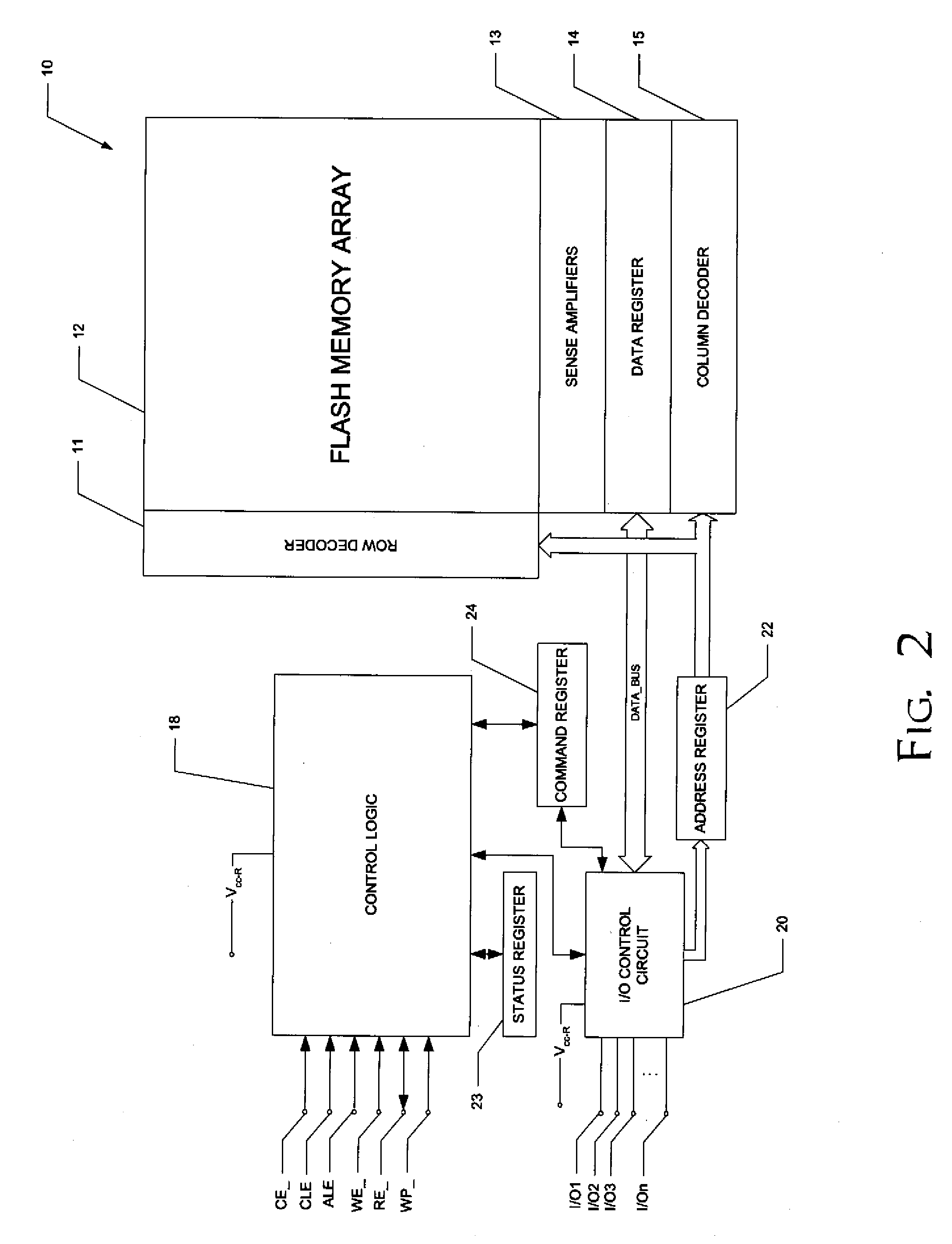

High-Performance Flash Memory Data Transfer

ActiveUS20070245065A1Reduce power consumptionMinimize data transferRead-only memoriesDigital storageControl signalTransfer mode

A flash memory system including a flash memory device and a controller, operable according to an advanced data transfer mode is disclosed. The flash memory device is operable both in a “legacy” mode, in which read data is presented by the memory synchronously with each cycle of a read data strobe from the controller, and in which input data is latched by the memory synchronously with each cycle of a write data strobe from the controller. In the advanced mode, which can be initiated by the controller forwarding an initiation command to the memory, the flash memory itself sources the read data strobe, and presents data synchronously with both the falling and rising edges of that read data strobe. In the advanced mode, the input data is presented by the controller synchronously with both edges of the write data strobe. The voltage swing of the data and control signals is reduced from conventional standards, to reduce power consumption.

Owner:SANDISK TECH LLC

Differential communication link with skew compensation circuit

ActiveUS8108710B2Minimize skewReduce signal reflectionPulse automatic controlError detection/correctionTelecommunications linkDifferential signaling

A system and method is presented for reducing skew between the positive and negative components of a differential signal in a high speed communications link. The communications link includes a signal generator producing and transmitting complementary positive and negative signals over separate transmission lines and a receiver receiving the complementary signals. The communication link further includes a skew compensation circuit having a skew detector, a controller, and separate delay and buffer elements for both the positive and negative component of the differential signal. The controller separately controls each of the delay or buffer elements in response to the detected skew between differential signal components.

Owner:MAYO FOUND FOR MEDICAL EDUCATION & RES

Cable apparatus for minimizing skew delay of analog signals and cross-talk from digital signals and method of making same

ActiveUS20050199416A1Minimizing skew delayUniform electrical lengthCables with twisted pairs/quadsAnalog signalDigital control

An unshielded twisted pair (UTP) cable minimizes skew delay of analog signals by enforcing a common electrical length among twisted pairs that carry those analog signals. By applying a different lay length and lay direction to the twisted pair that carries the digital signal, cross-talk from the digital signal onto the analog signals is minimized. The twisted pairs for carrying the analog signals may be bundled together, with the twisted pair for carrying the digital signal placed alongside the bundled pairs during the final extraction process, during which the outer insulator is formed around all of the pairs. The bundled pairs may be used for the transmission of analog video signals (e.g., R, G and B), with the remaining pair used for transmission of digital control or digital audio signals.

Owner:RGB SYST INC