Method and apparatus for reducing power consumption in digital electronic circuits

a technology of digital electronic circuits and power consumption reduction functions, applied in the field of digital electronic equipment, can solve the problems of not being immediately available when needed, time-consuming procedure of powering up the required peripheral, and valuable computational time being lost in the power consumption reduction function, etc., and achieve the effect of reducing power consumption in digital electronic circuits

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

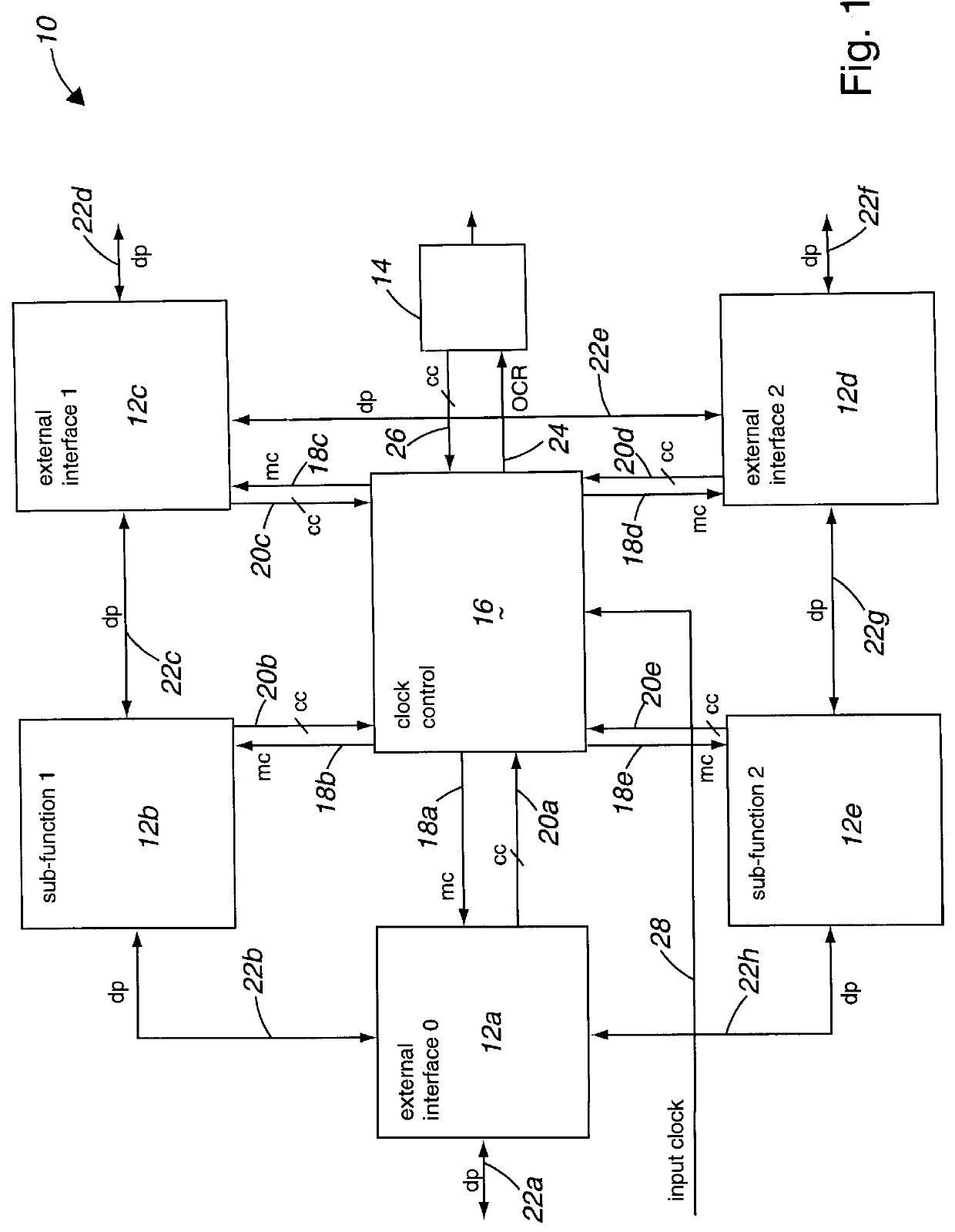

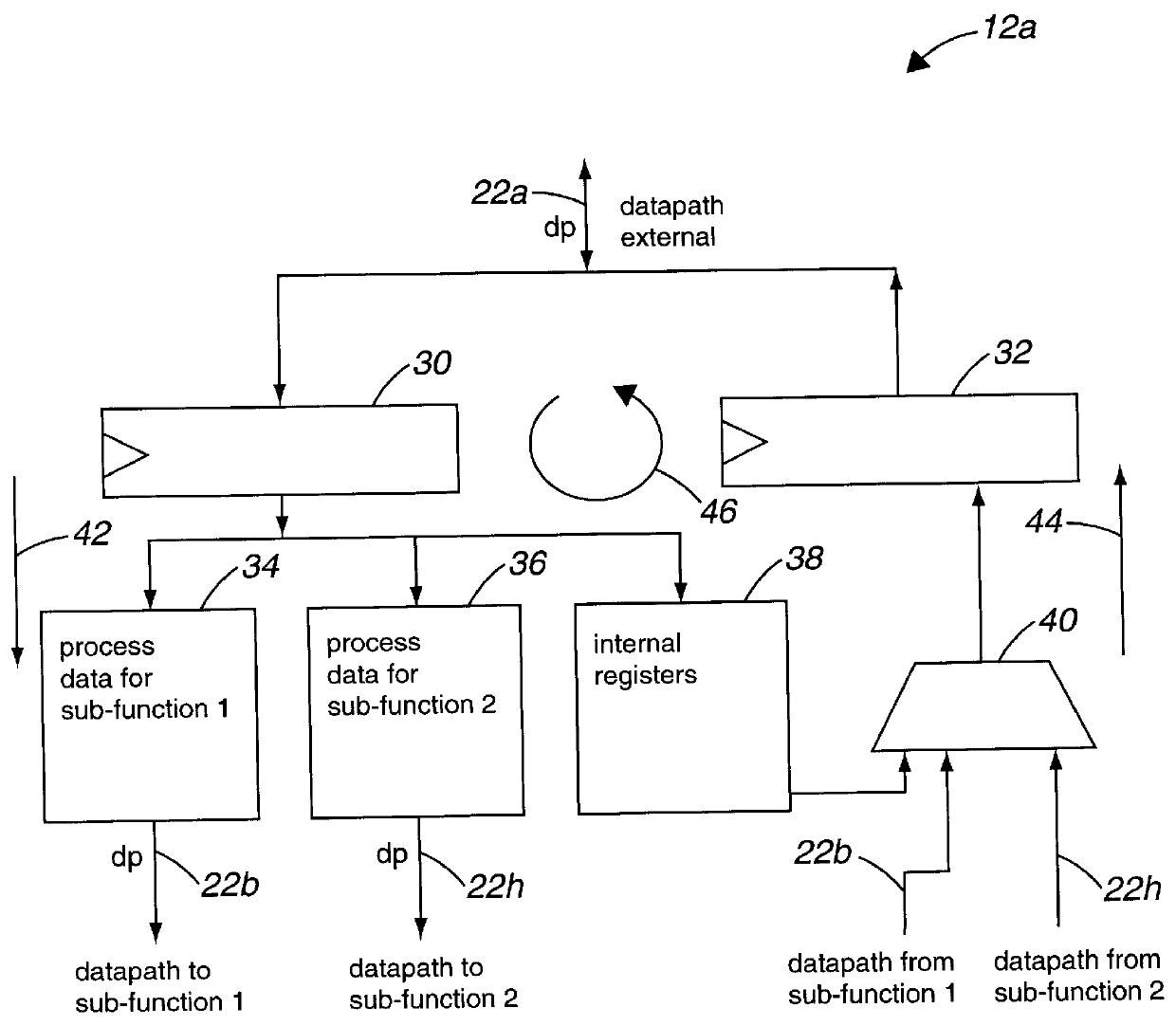

In FIG. 1, a system 10 with power conservation includes a number of functional blocks 12 including blocks 12a, 12b, 12c, 12d, and 12e. The system 10 with power conservation also includes a special block 14 and a clock control 16. Preferably, the system 10 with power conservation is implemented as part of an integrated circuit. Alternatively, the system 10 can be implemented as a number of integrated circuits, or with discrete electronic devices.

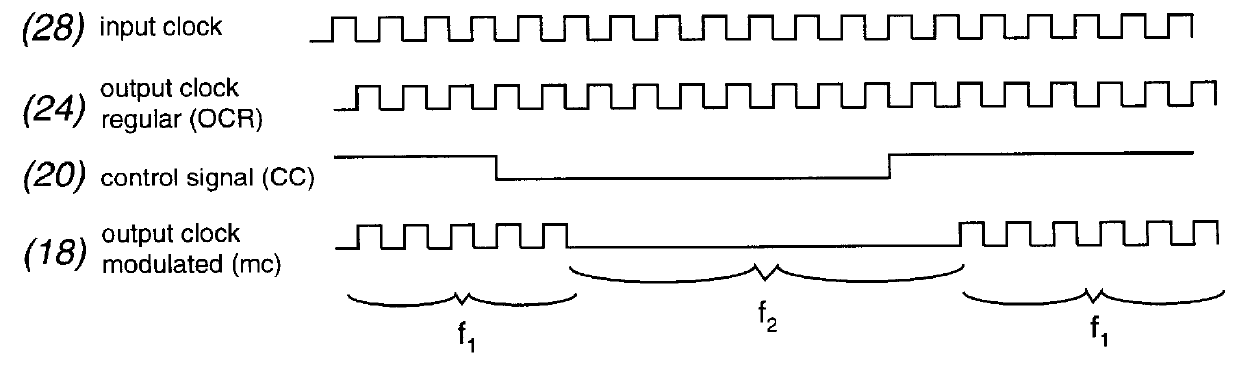

The functional blocks 12 all include digital circuitry that are capable of processing data. Each of the functional blocks 12 include a modulated clock input line 18a, 18b, 18c, 18d, and 18e, respectively, for the functional blocks 12a-12e. The signal carried by the modulated clock inputs 18a14 18e are designated as "mc." Each of the functional blocks 12 also include clock control buses 20a, 20b, 20c, 20d, and 20e, respectively, for each of the functional blocks 12a-12e. The clock control buses 20a-20e are buses in that they typically include ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More