Patents

Literature

48results about How to "Minimize data transfer" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

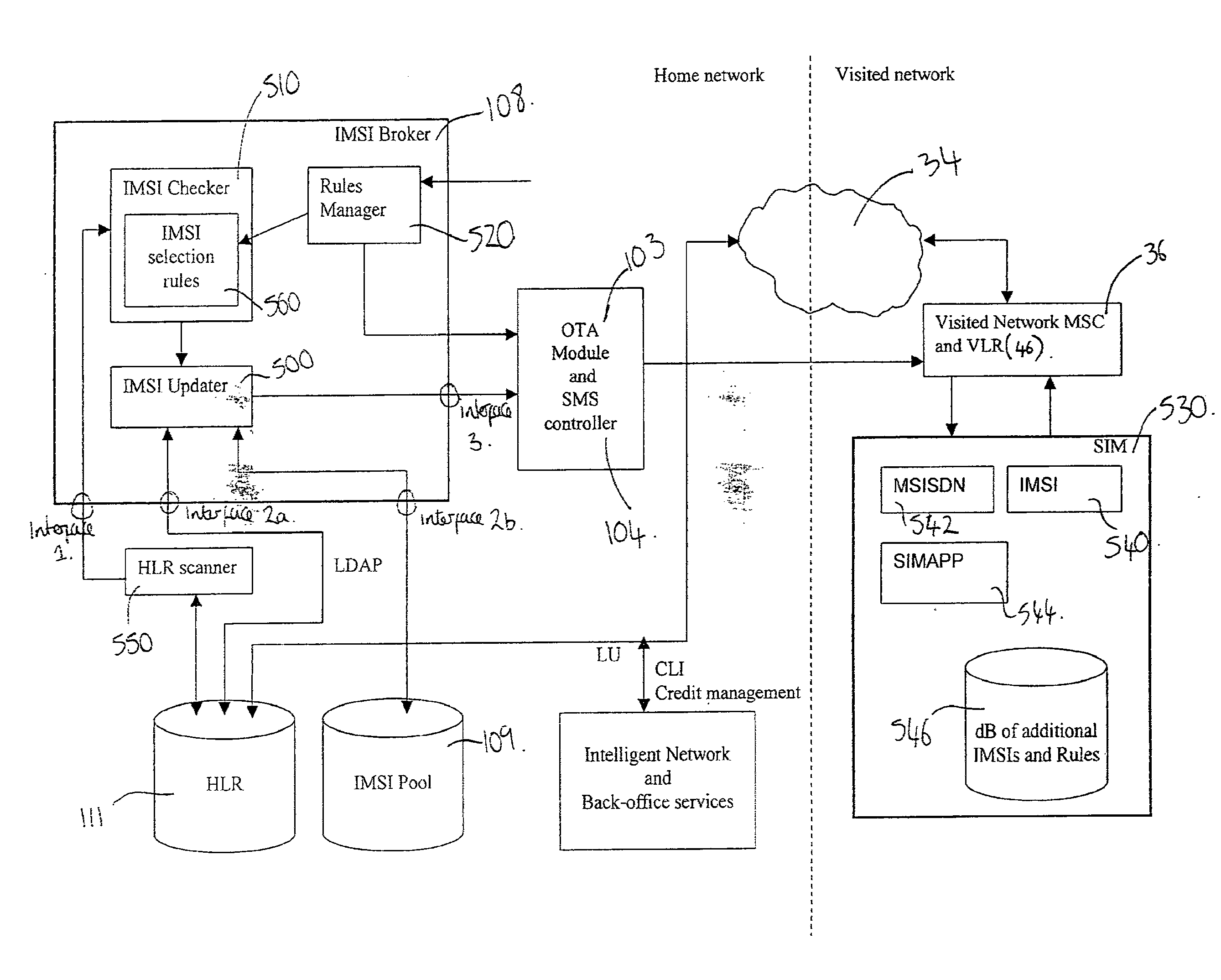

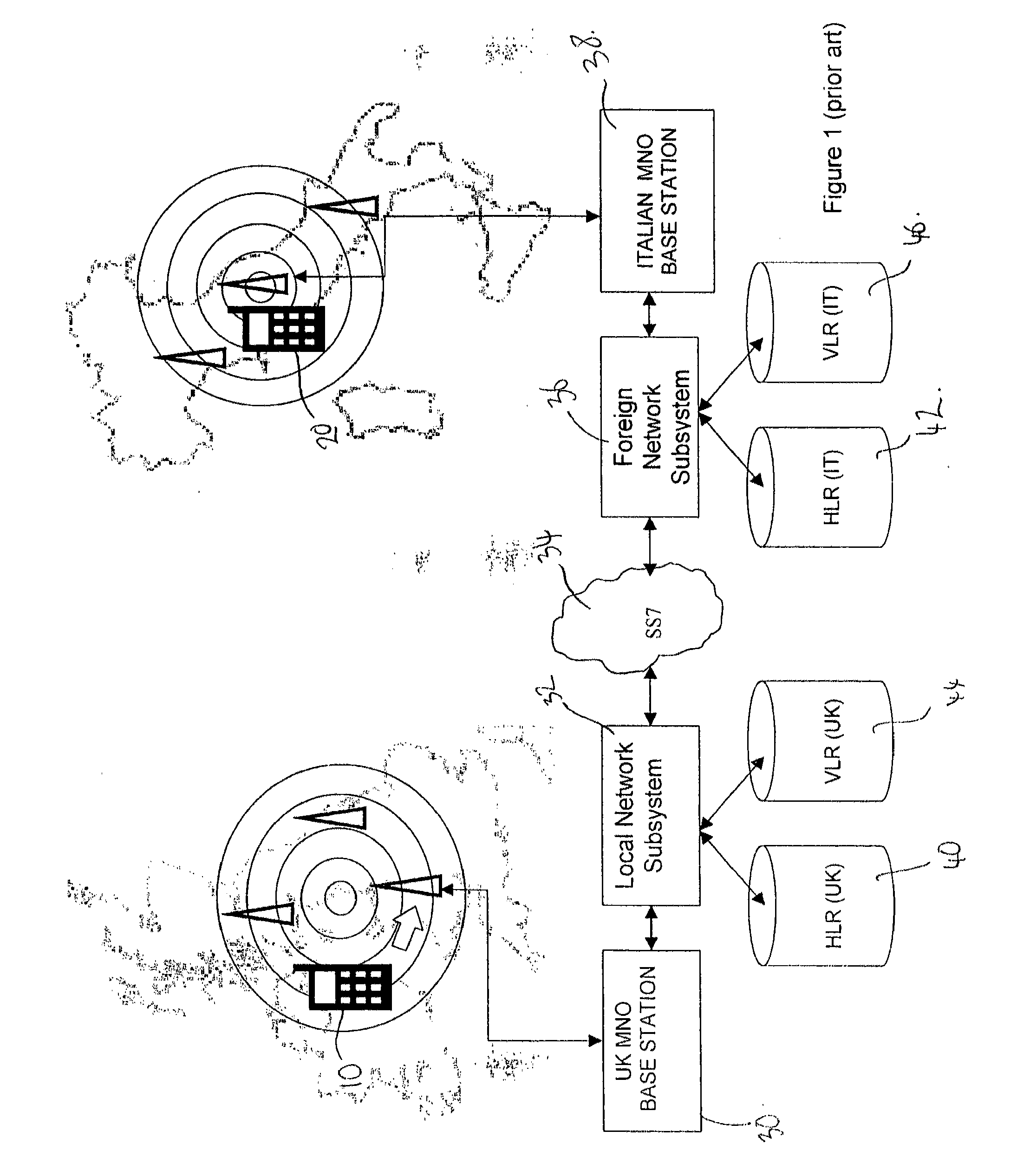

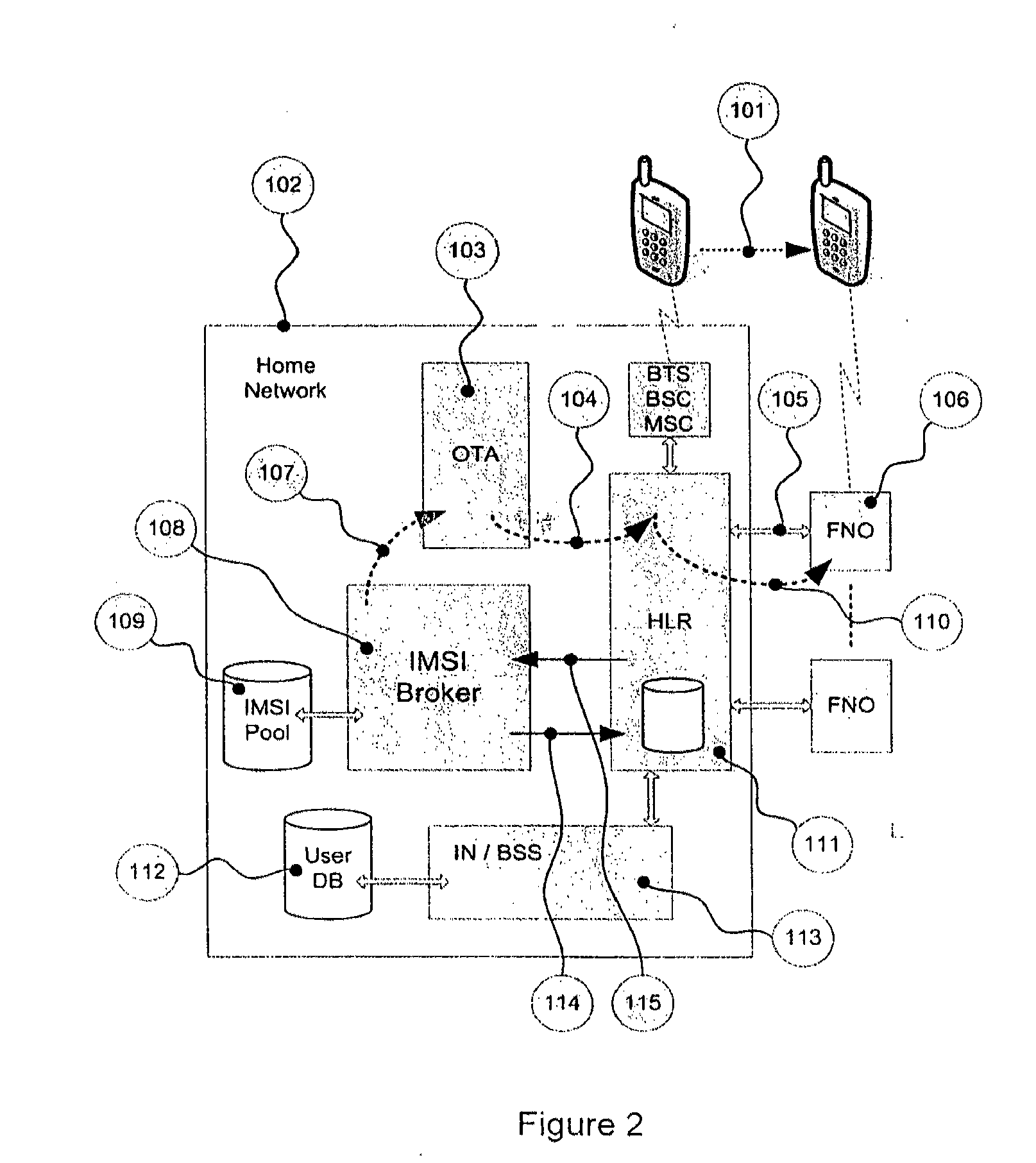

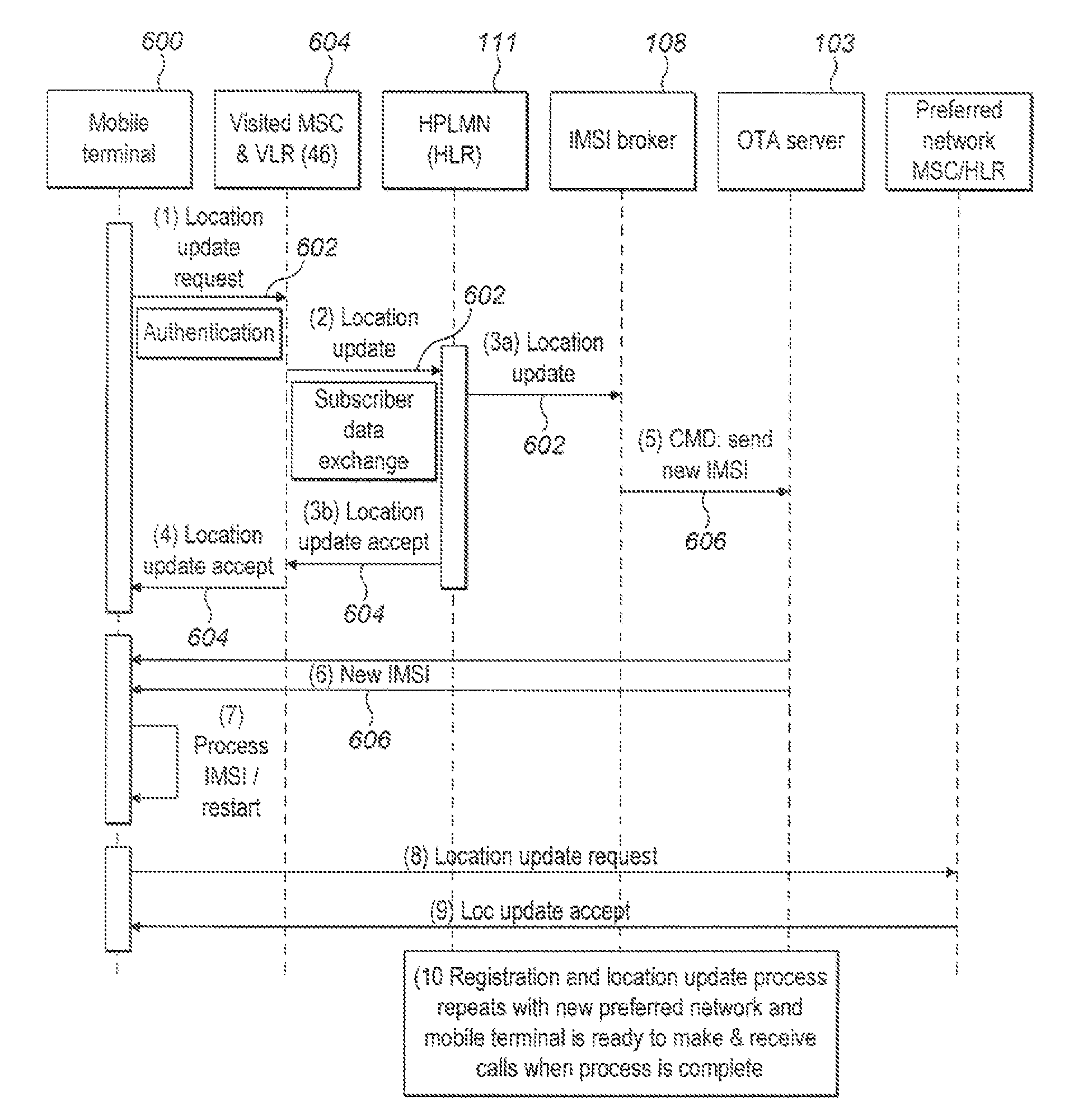

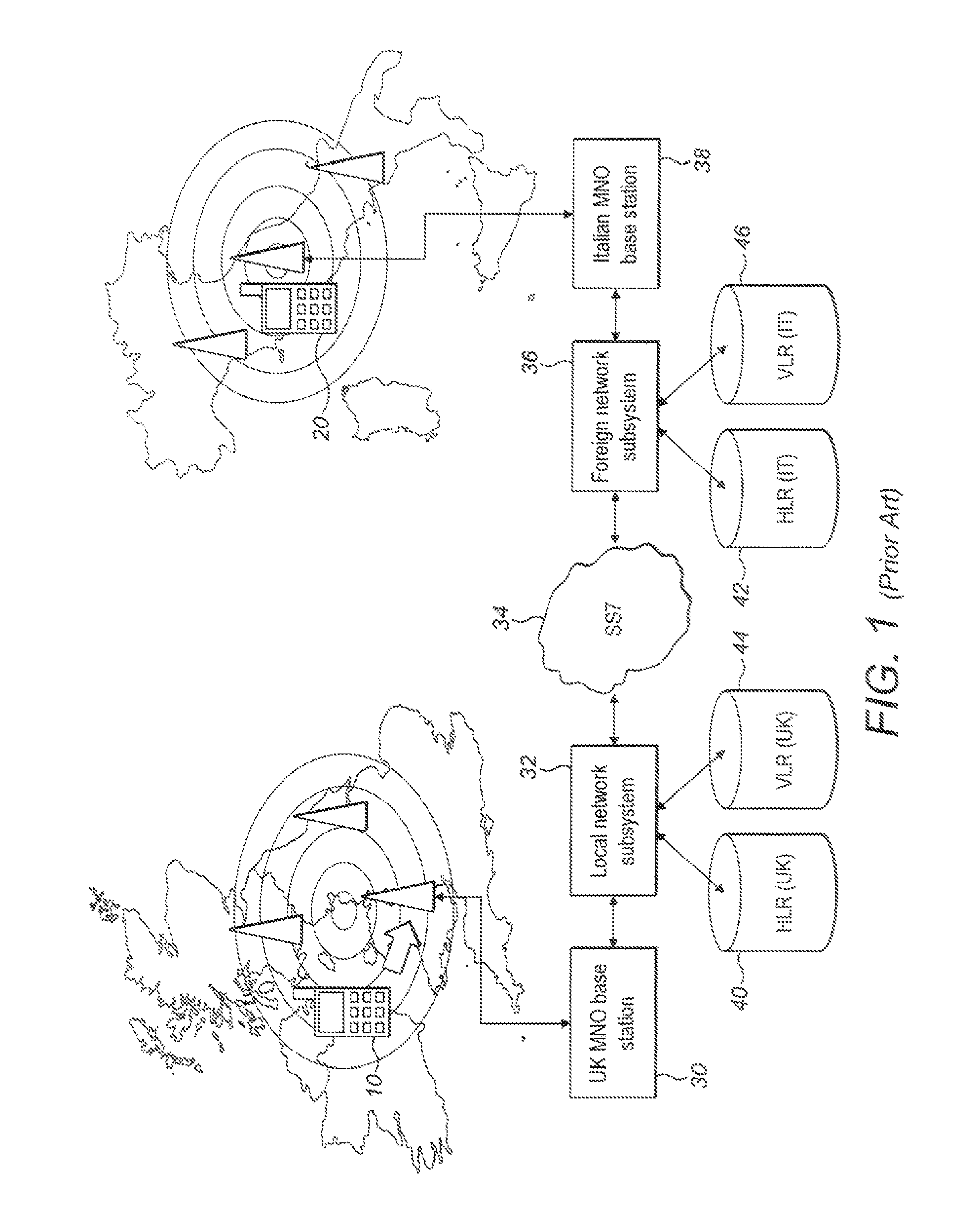

Subscriber Identification Management Broker for Fixed/Mobile Networks

ActiveUS20120282924A1Low rateLow amountAssess restrictionWireless commuication servicesMobile WebManagement agent

There present invention relates to a method for managing the automatic provision of a subscriber network identifier from a central network server to a subscribed communication device, the method comprising receiving notification at the central server relating to a change in the current location for the subscribed device, and determining from the notification whether a new subscriber network identifier is to be provisioned from the central server. The method further comprises selecting a subscriber network identifier on the basis of the current location, if the determining step has determined that a new subscriber network identifier is to be provisioned, and outputting the selected subscriber network identifier for transmission to the subscribed device. The present invention also relates to managing the automatic connection of a subscribed communication device to a network, where a preferred network and preferred subscriber network identifier may be used.

Owner:TRUPHONE

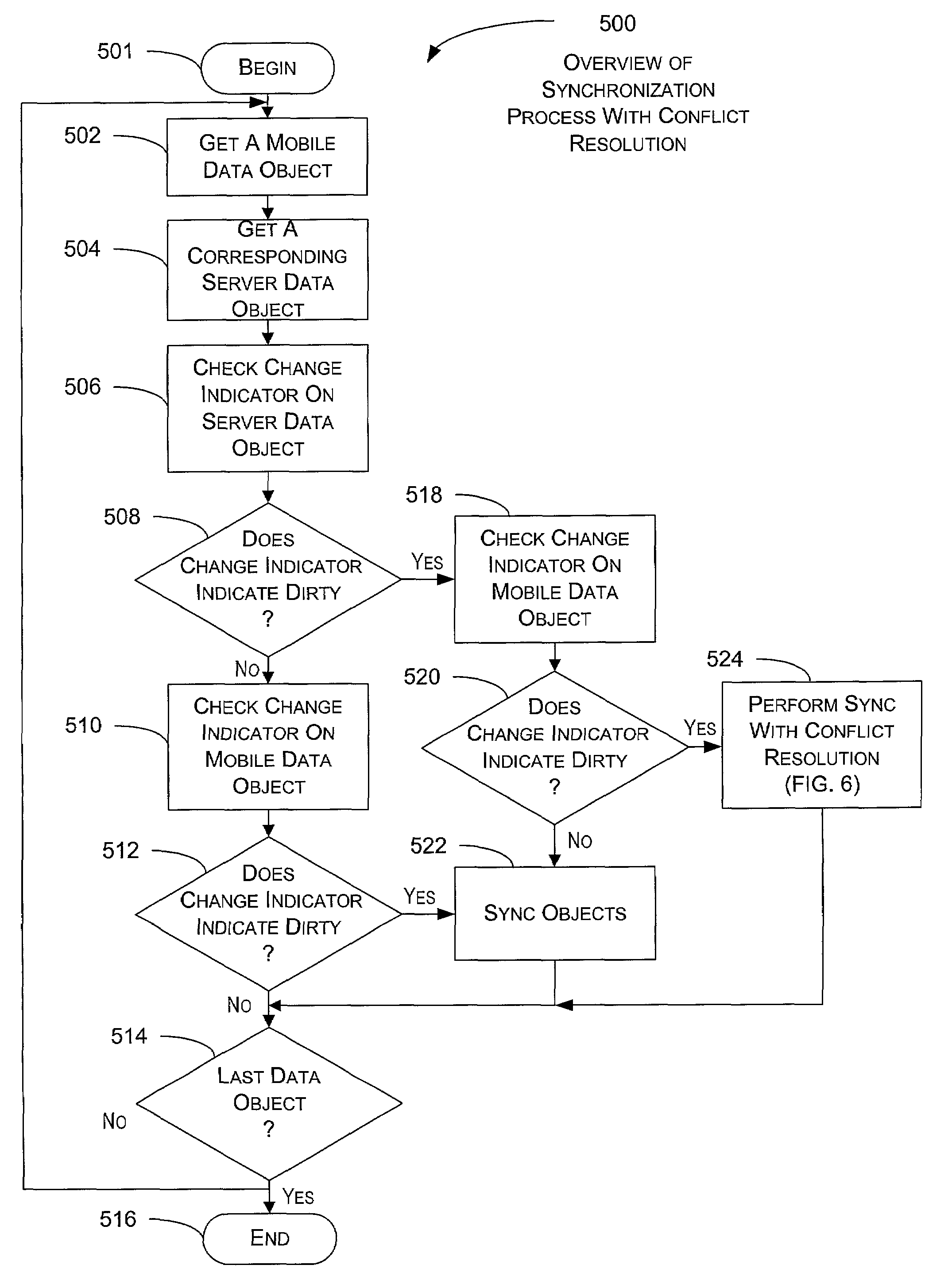

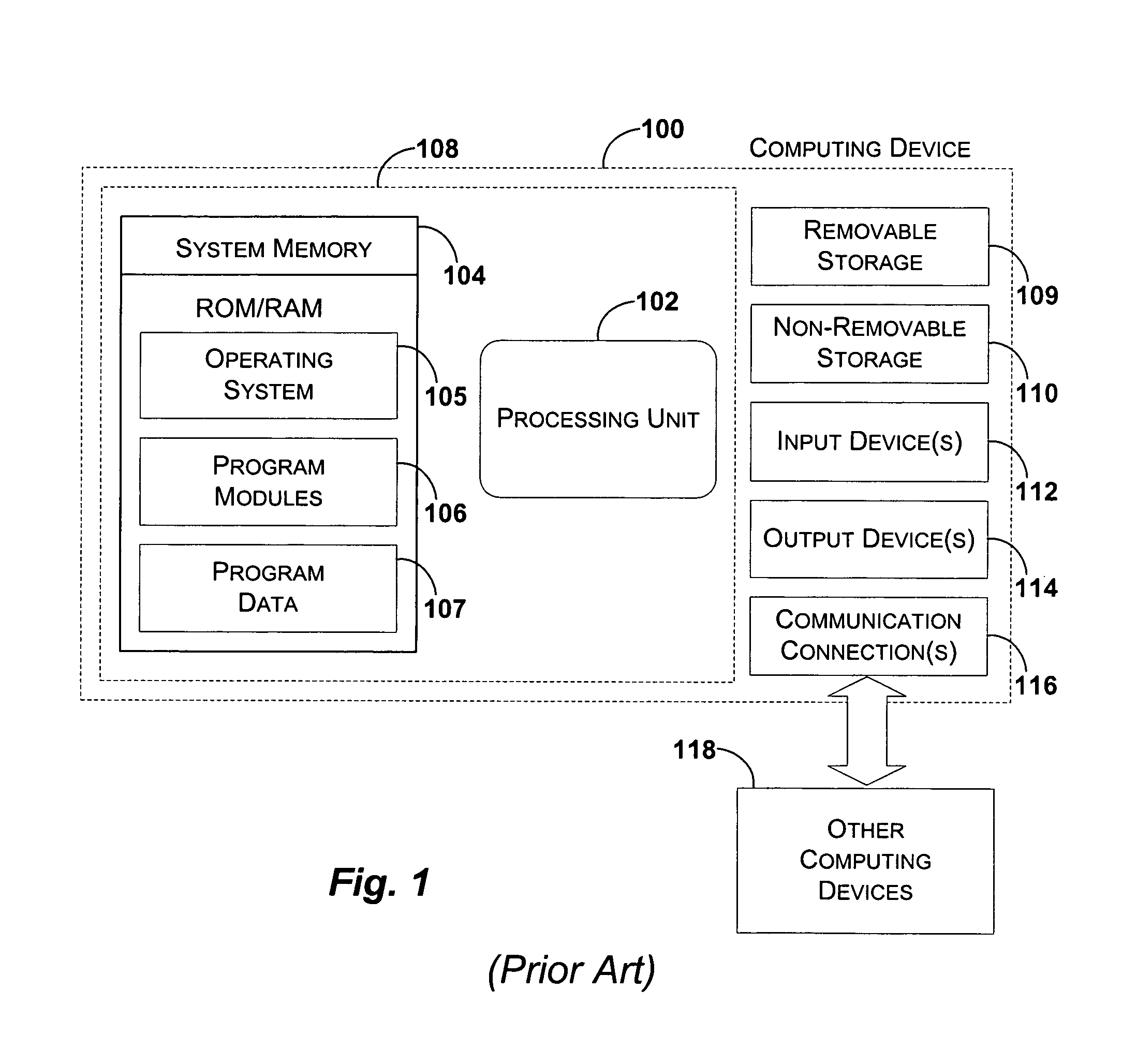

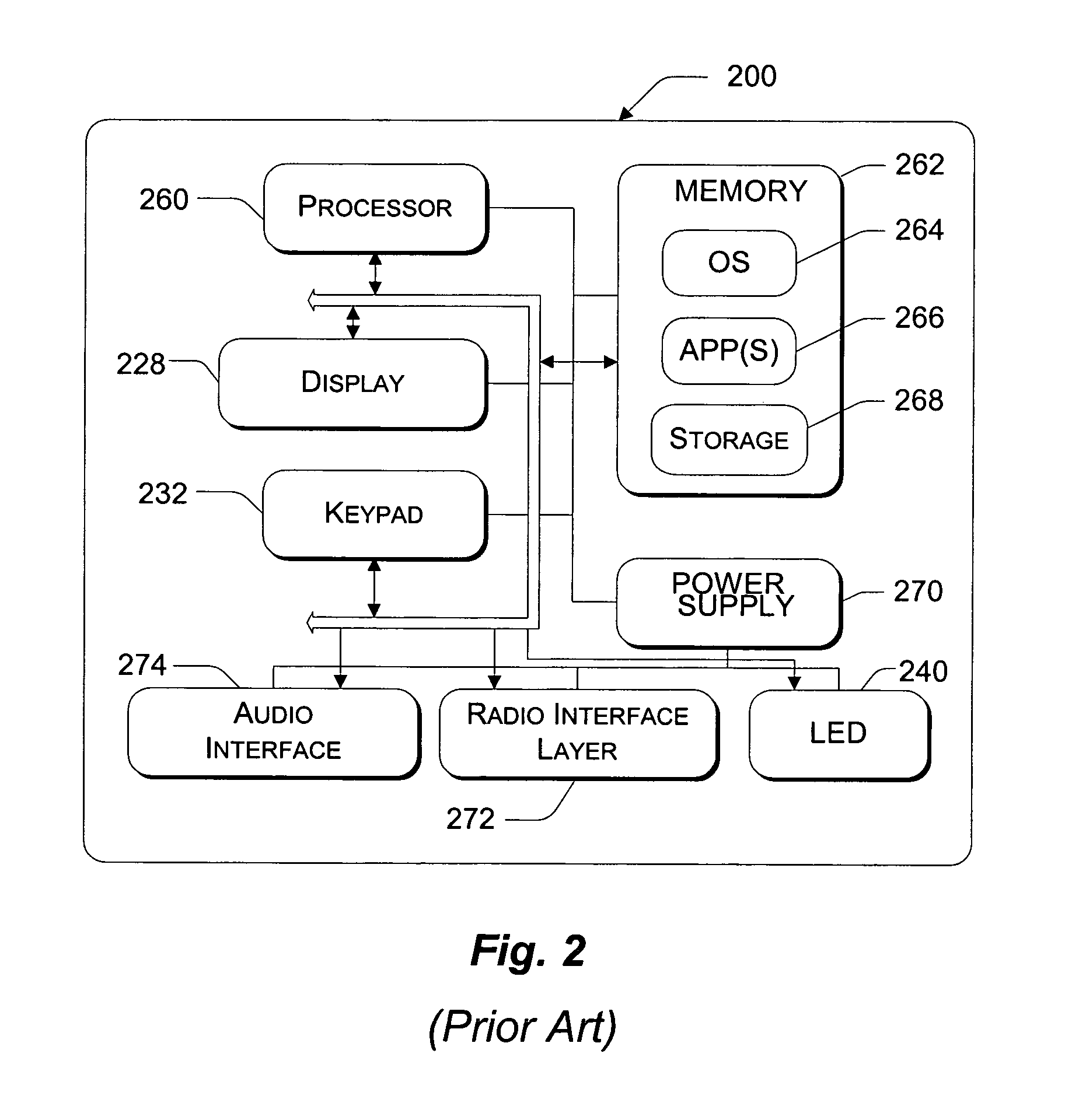

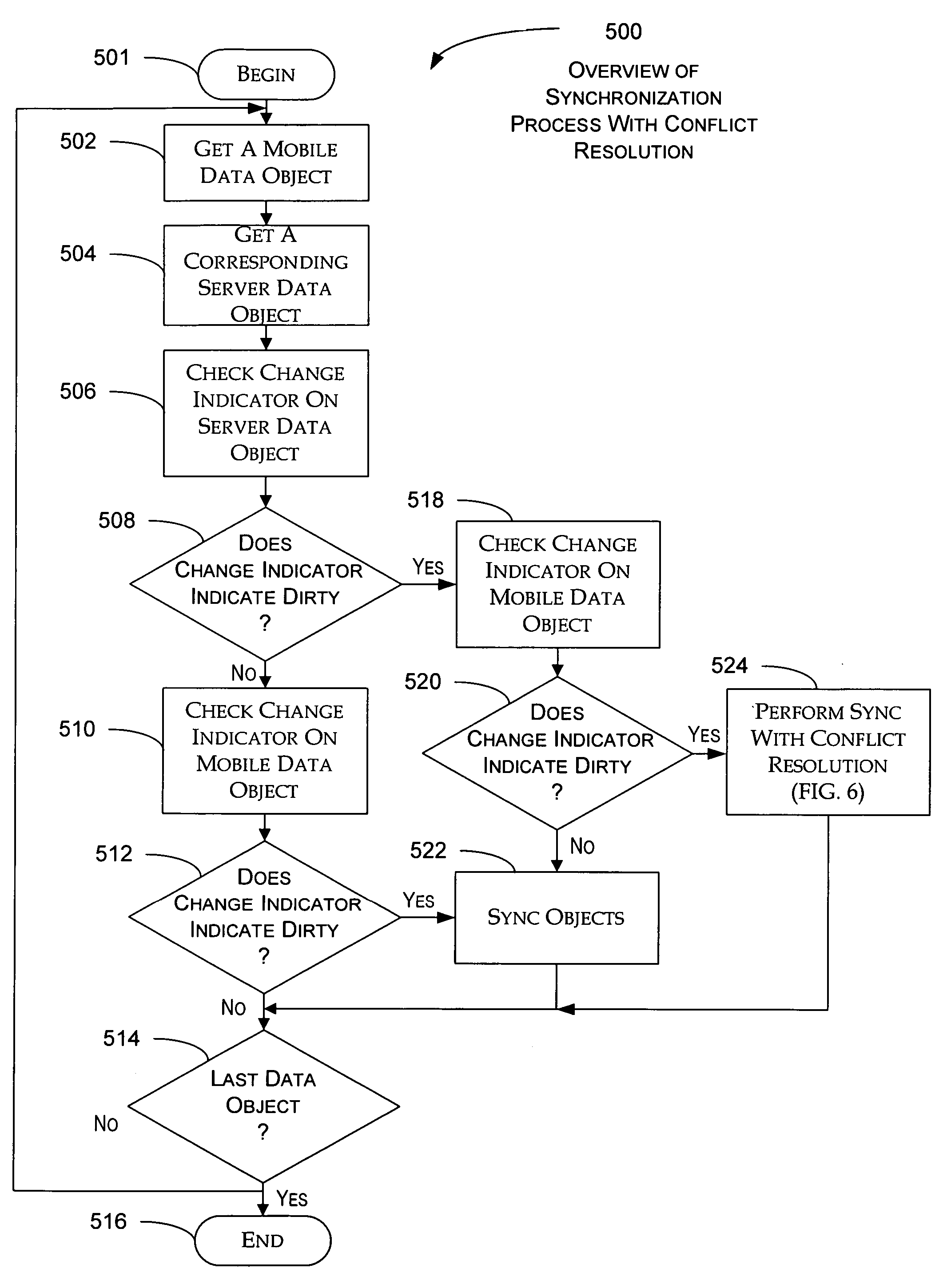

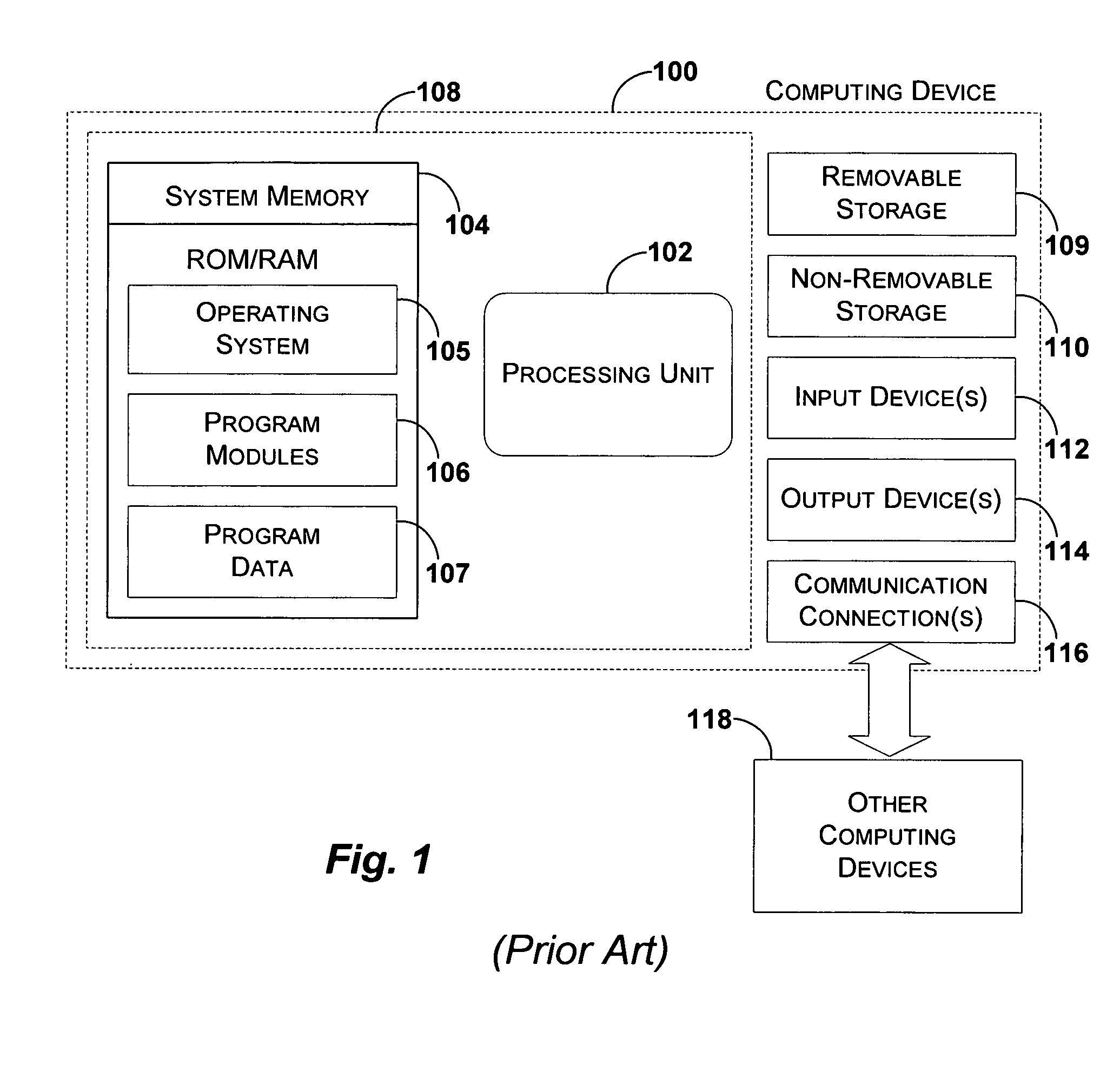

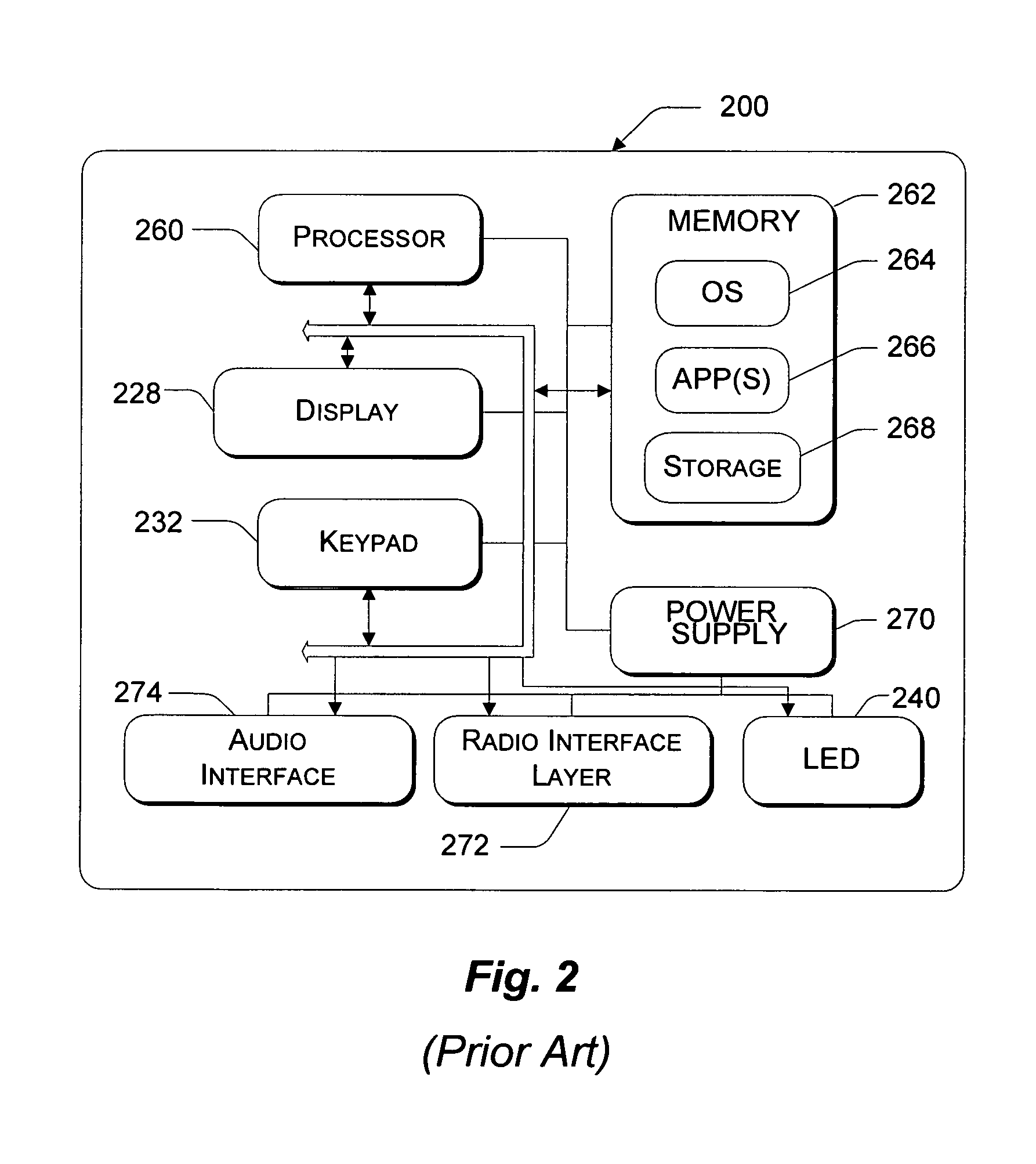

System and method for resolving conflicts detected during a synchronization session

InactiveUS6993522B2Conflict detectedReduce riskData processing applicationsDatabase distribution/replicationData transmissionData objects

A system and method is described for resolving a conflict detected while synchronizing a first data object in a first store associated with a mobile device and a second data object in a second store associated with a server. Once the conflict is detected, properties of the first data object are compared with corresponding properties of the second data object. If the properties and the corresponding properties that differ are designated as mergeable properties, the properties and the corresponding properties are merged. Merging the properties involves sending a preferred state associated with each of the properties and the corresponding properties to the mobile device and the server for updating the first data object and second data object, respectively, when an initial state for the properties and the corresponding properties is different than the preferred state. The preferred state is based on a likelihood that vital information would be lost if the preferred state did not replace the initial state of the property or the corresponding property. The merging is performed without user-intervention on the mobile device. In addition, the entire first data object or second data object is not sent to the mobile device to achieve the merge, thereby minimizing the data transfer to the mobile device.

Owner:MICROSOFT TECH LICENSING LLC

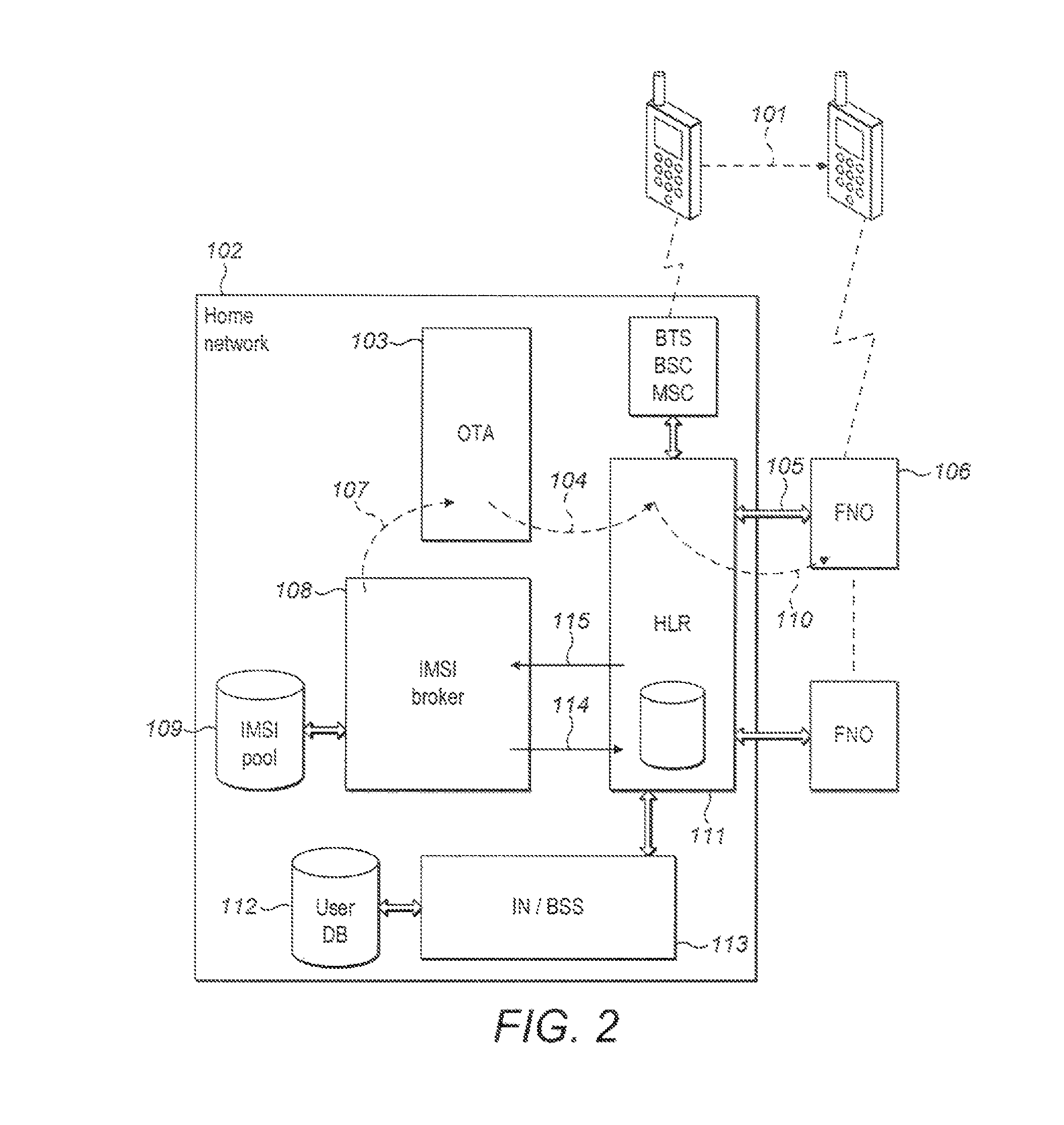

Subscriber identification management broker for fixed/mobile networks

ActiveUS8406758B2Low costEliminate chargeAssess restrictionWireless commuication servicesMobile WebCommunication device

There present invention relates to a method for managing the automatic provision of a subscriber network identifier from a central network server to a subscribed communication device, the method comprising receiving notification at the central server relating to a change in the current location for the subscribed device, and determining from the notification whether a new subscriber network identifier is to be provisioned from the central server. The method further comprises selecting a subscriber network identifier on the basis of the current location, if the determining step has determined that a new subscriber network identifier is to be provisioned, and outputting the selected subscriber network identifier for transmission to the subscribed device. The present invention also relates to managing the automatic connection of a subscribed communication device to a network, where a preferred network and preferred subscriber network identifier may be used.

Owner:TRUPHONE

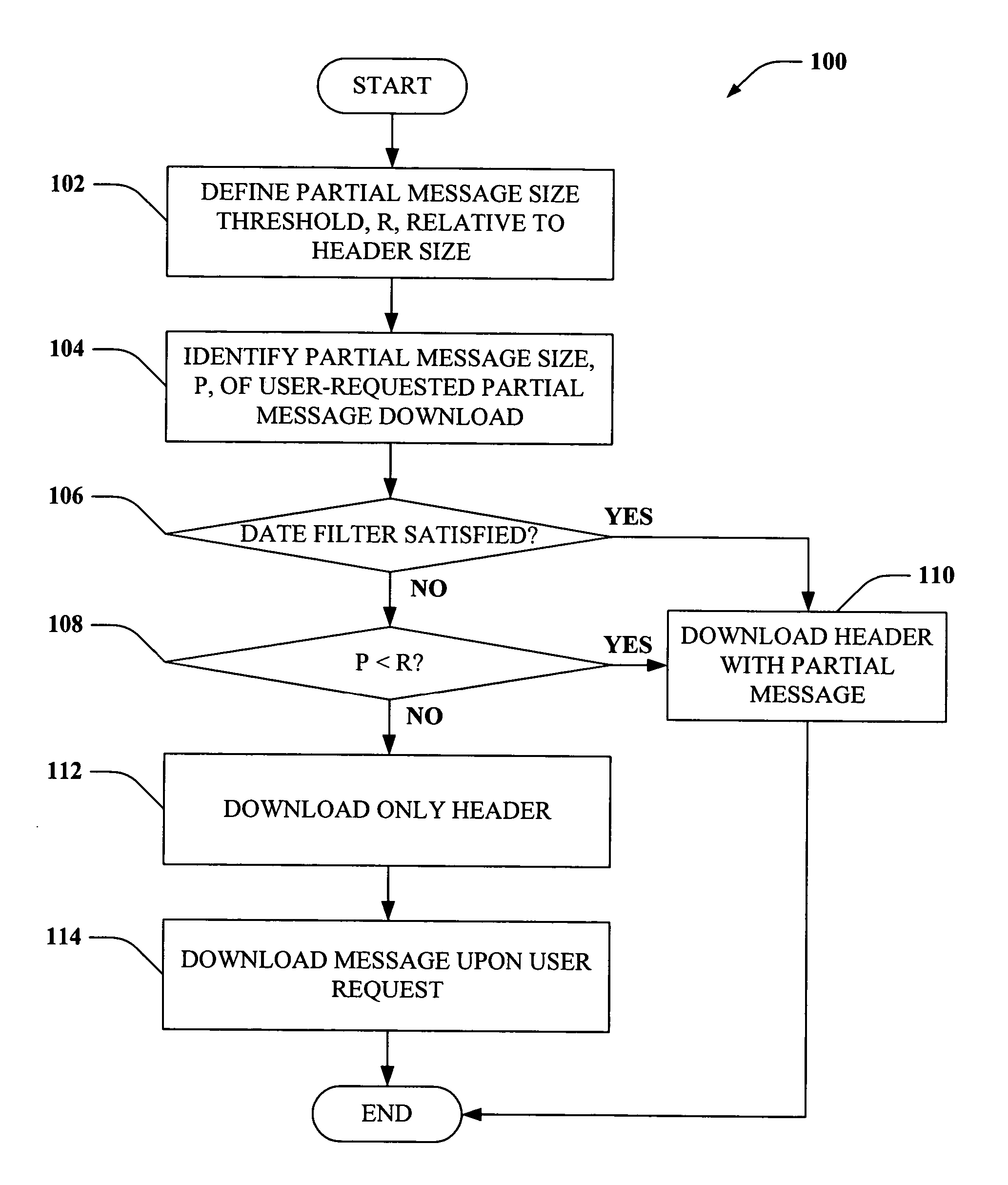

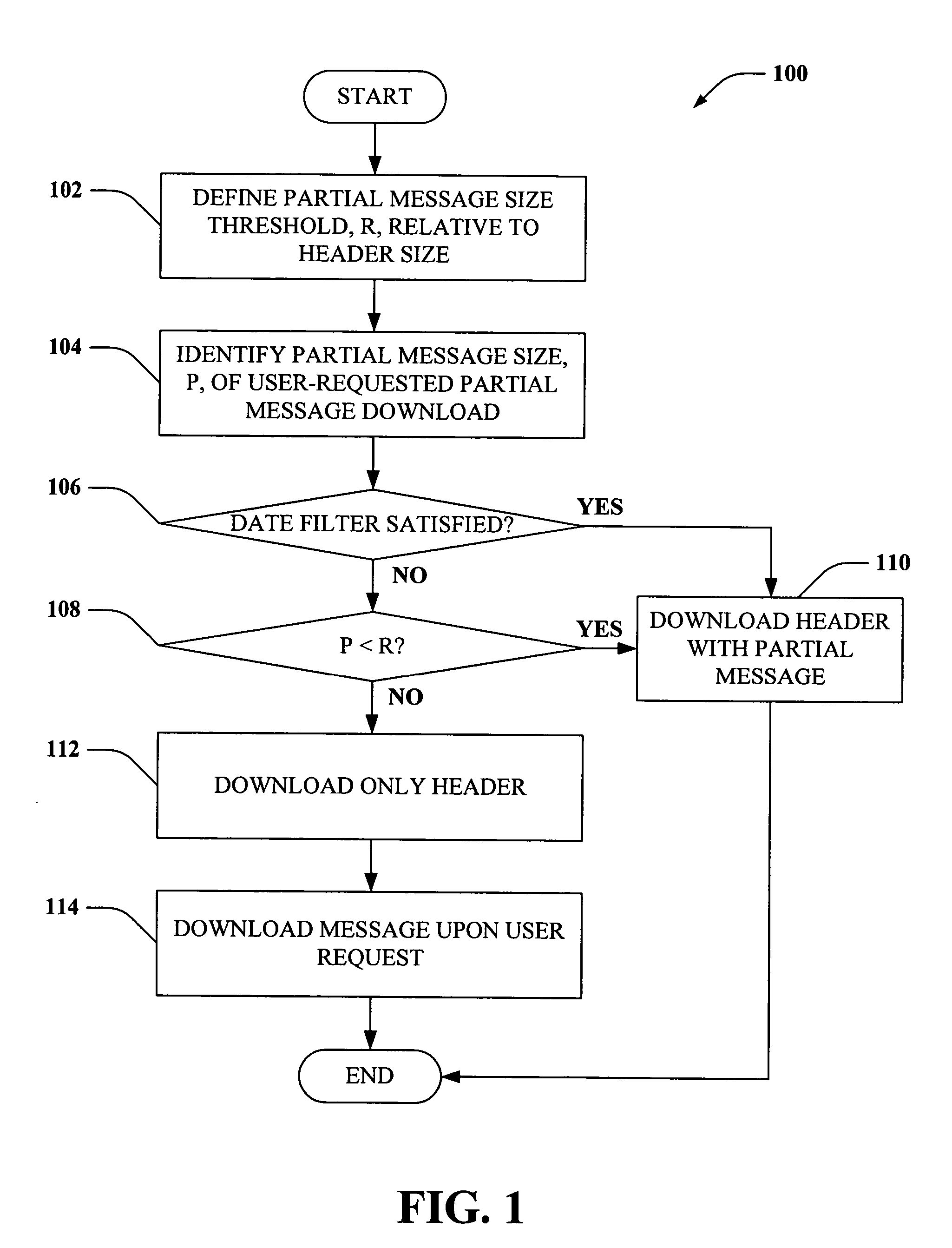

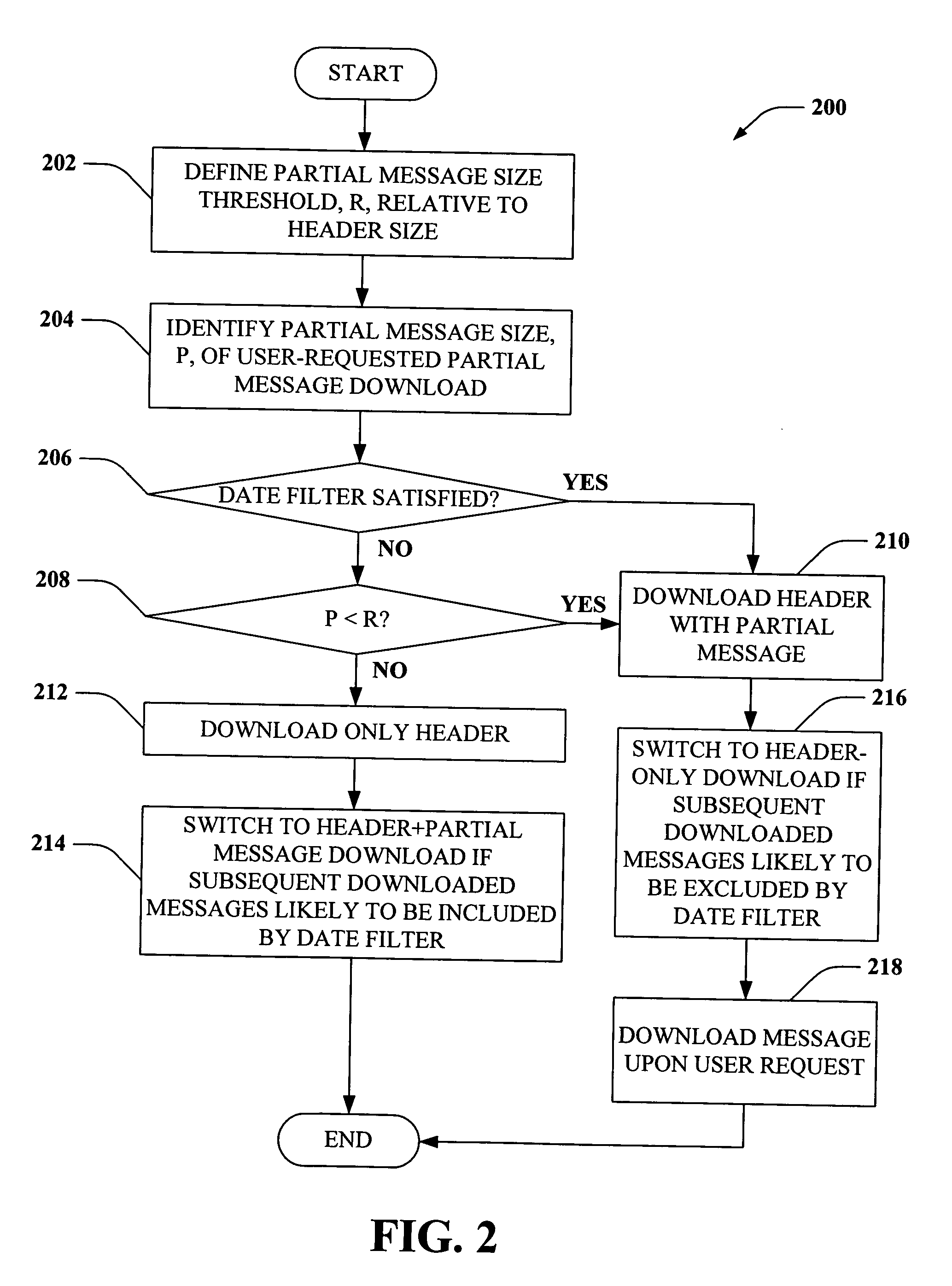

Minimizing data transfer from POP3 servers

InactiveUS20060277257A1Minimize bandwidthMinimize storage requirementMultiple digital computer combinationsData switching networksDate RangeBody size

Systems and methods are disclosed that facilitate minimizing data transfer from a post office protocol (POP) server to a client device by employing a date filter with a predefined date range and applying a message body size threshold above which only a message header will be downloaded to conserve bandwidth and / or memory space on the client device. A user can request download of a message for which only a message header was originally downloaded if the header comprises information of interest to the user.

Owner:MICROSOFT TECH LICENSING LLC

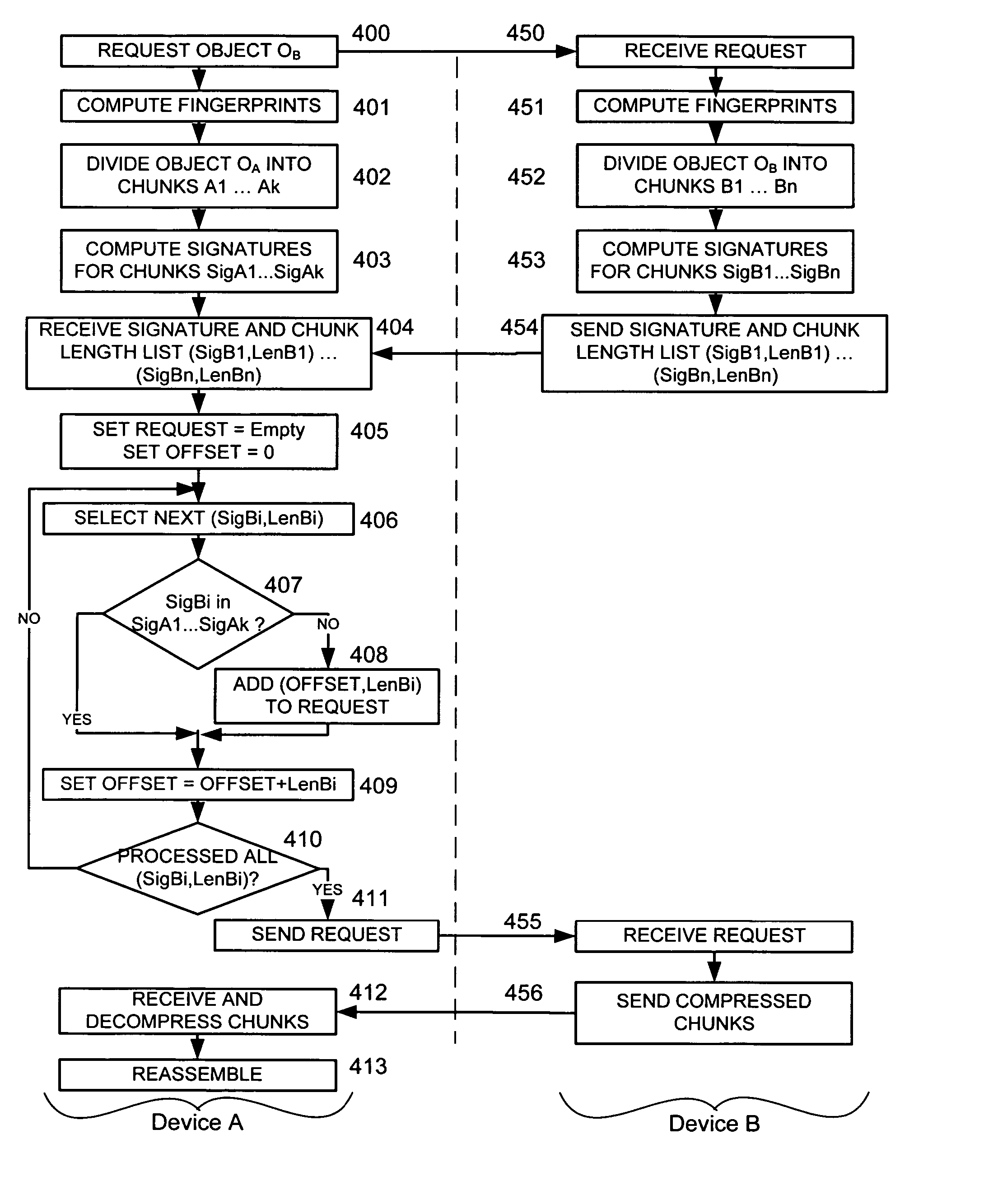

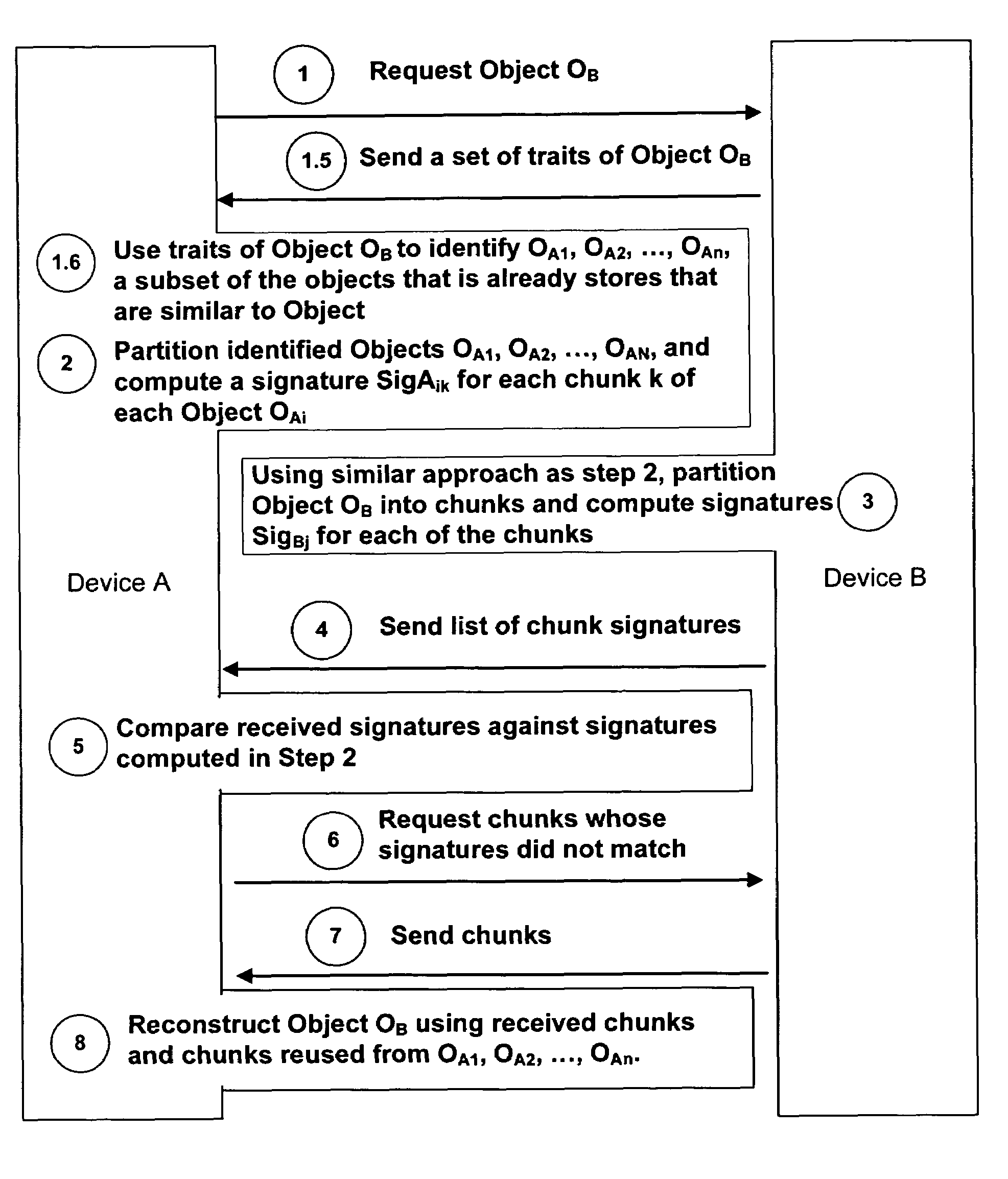

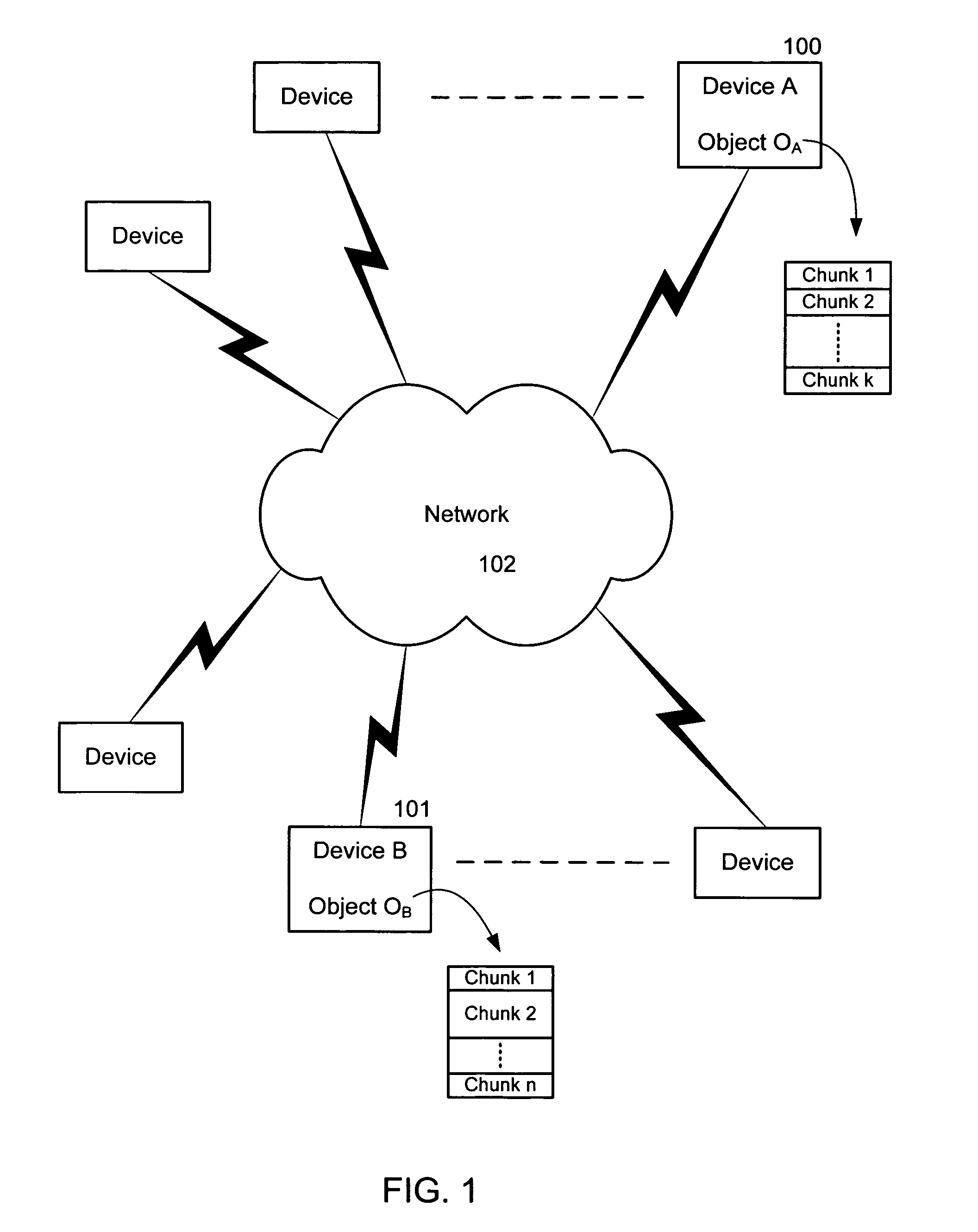

Efficient algorithm for finding candidate objects for remote differential compression

ActiveUS20060085561A1Improve efficiencyMinimize data transferDigital data information retrievalMultiple digital computer combinationsData transmissionEfficient algorithm

The present invention finds candidate objects for remote differential compression. Objects are updated between two or more computing devices using remote differential compression (RDC) techniques such that required data transfers are minimized. An algorithm provides enhanced efficiencies for allowing the receiver to locate a set of objects that are similar to the object that needs to be transferred from the sender. Once this set of similar objects has been found, the receiver may reuse any chunks from these objects during the RDC algorithm.

Owner:MICROSOFT TECH LICENSING LLC

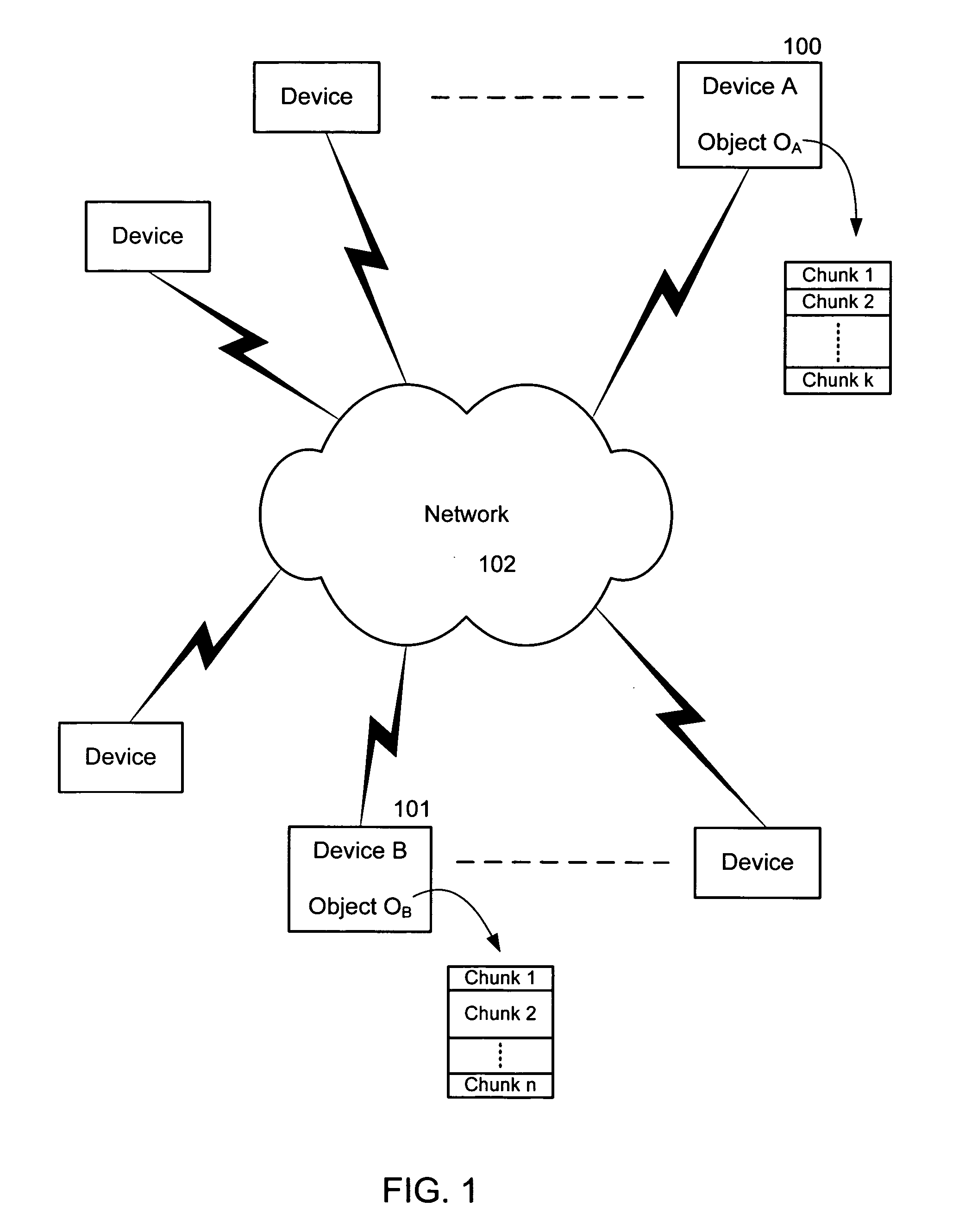

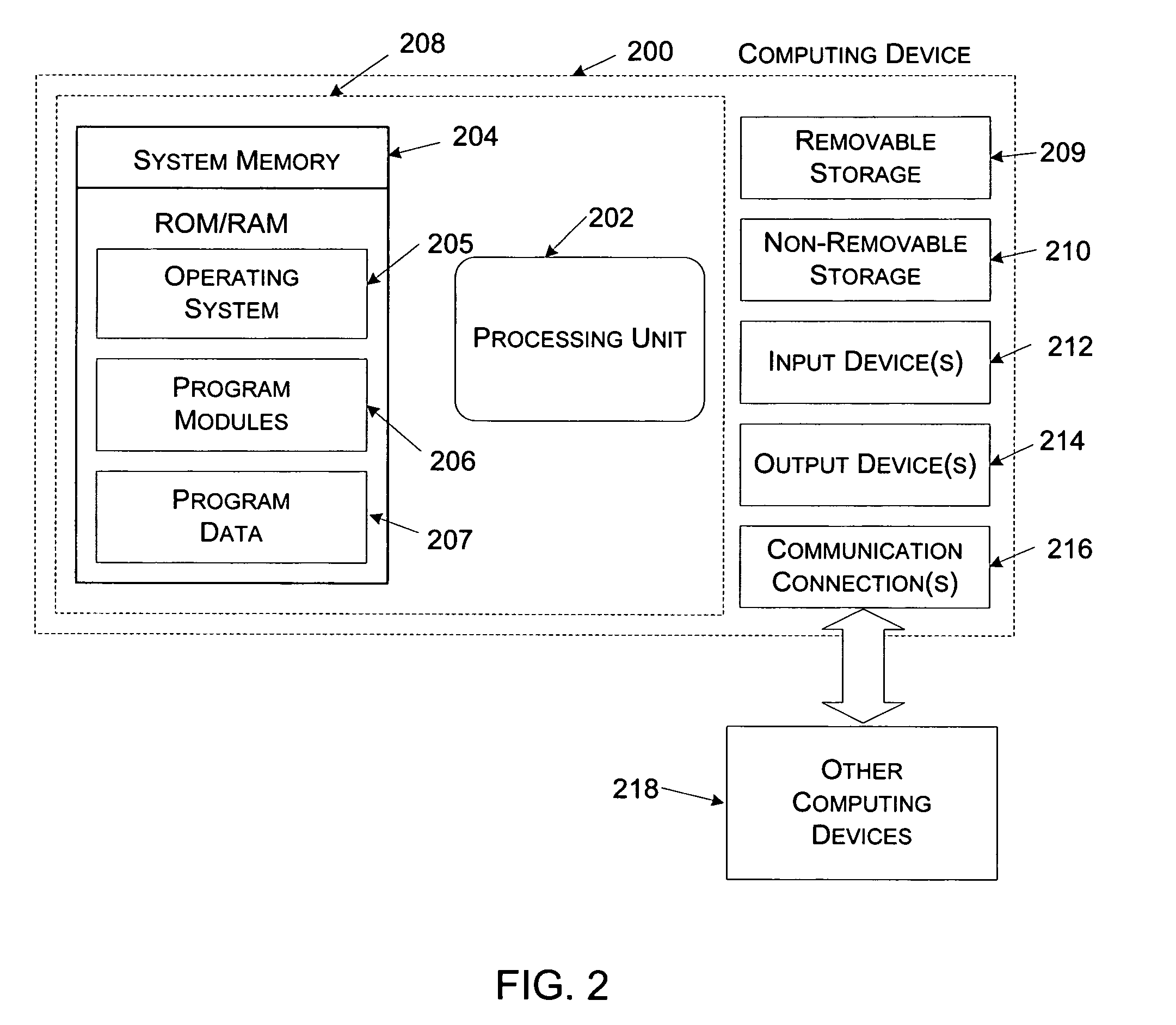

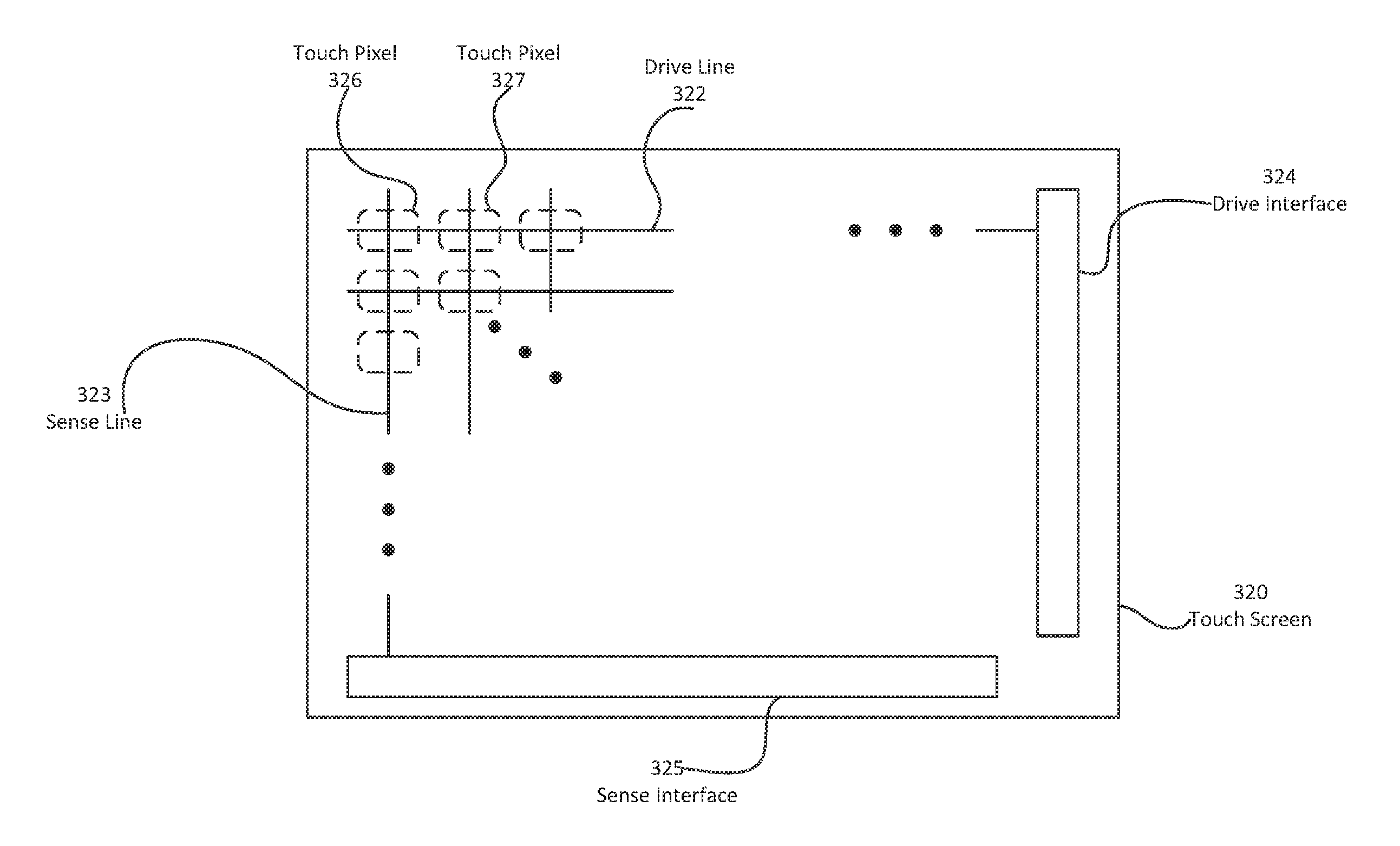

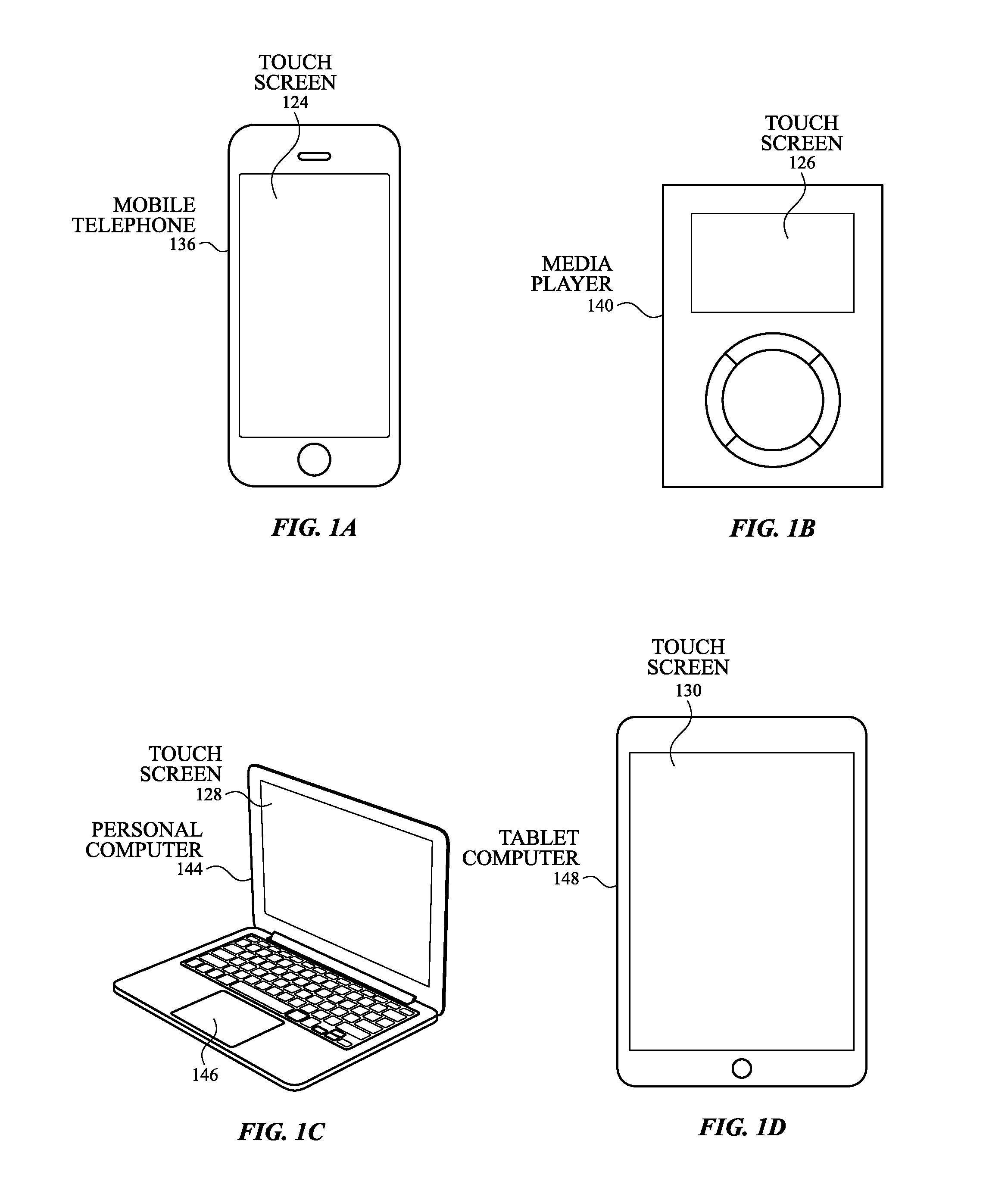

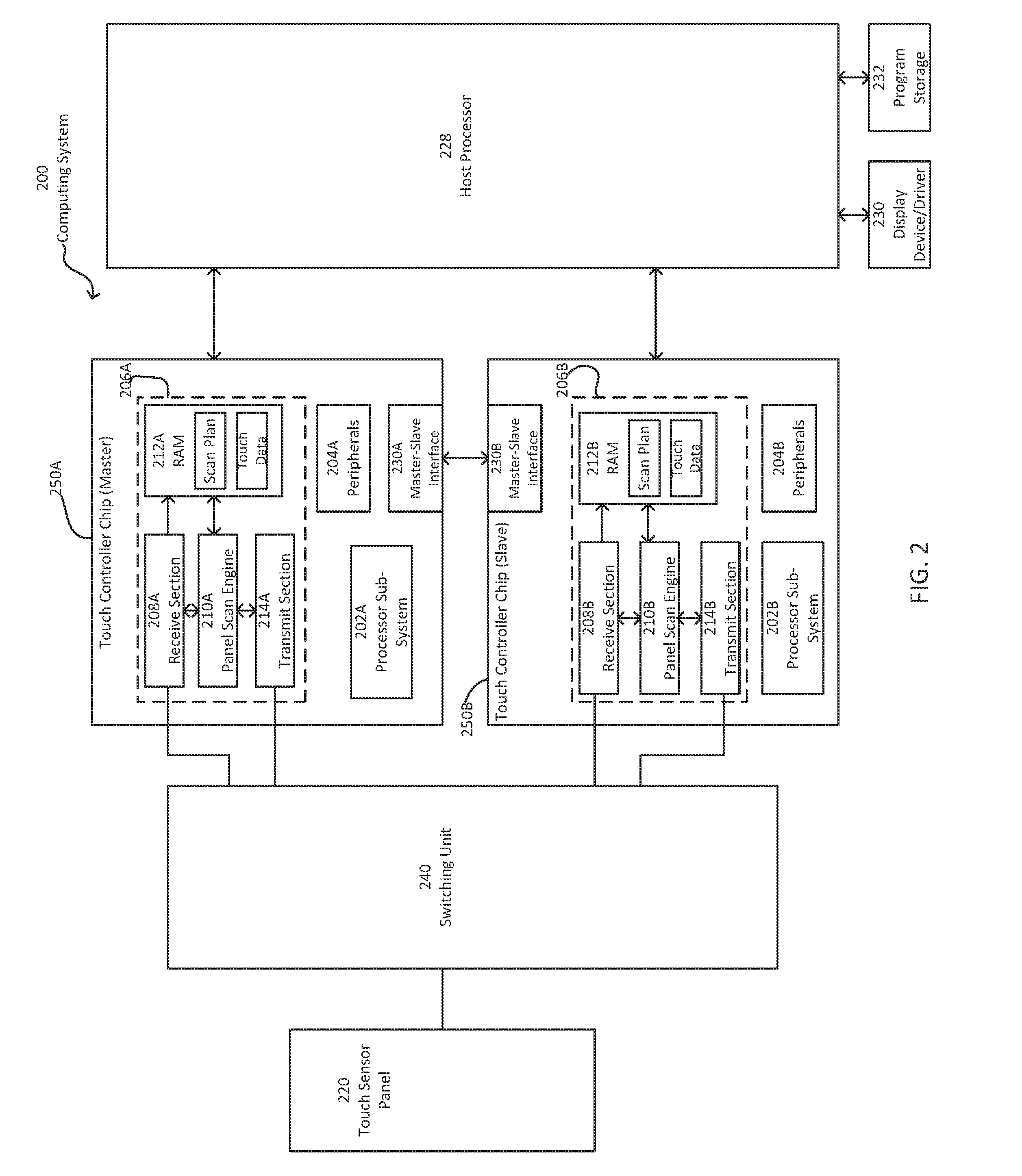

Multi-chip touch architecture for scalability

ActiveUS20160266679A1Generate accuratelyImprove processing speedInput/output processes for data processingCouplingApplication specific

A multi-chip touch architecture for scalability can include one or more touch controller application specific integrated circuits (ASICs), and one or more switching circuits coupled between the one or more touch controller ASICs and the touch sensor panel. The number of touch controller ASICs and switching circuits can be scaled based on the size of the touch sensor panel. The touch controller ASICs can include an interface for data transfer between the touch controller ASICs to allow for parallel processing of an image of touch by more than one touch controller ASIC. The touch controller ASIC can also include a memory directly accessible by more than one processing circuit (e.g., hardware accelerators), and circuitry to dynamically adjust the coupling between portions (e.g., banks) of memory and inputs of the one or more processing circuits to minimize data transfer and improve processing speeds.

Owner:APPLE INC

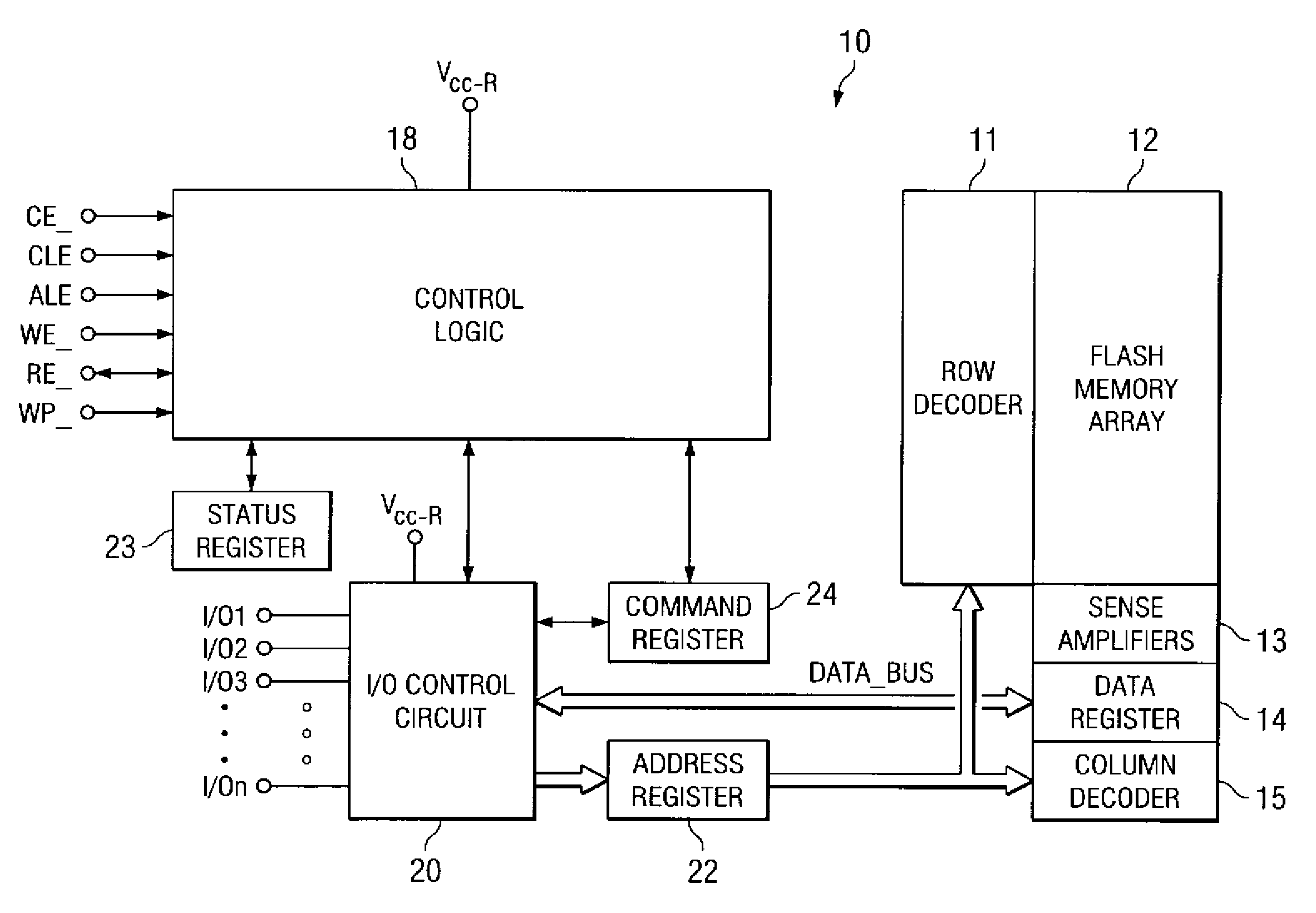

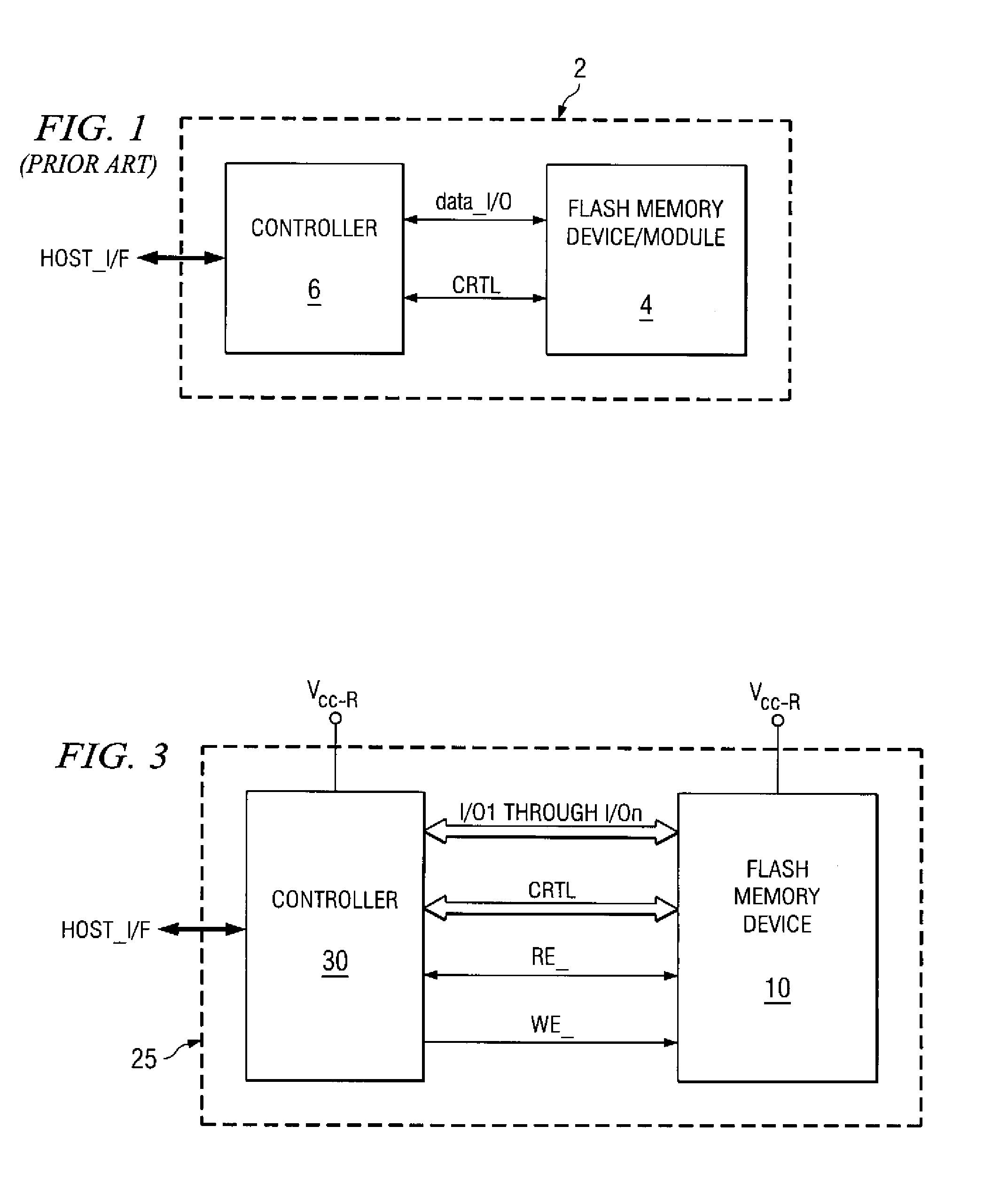

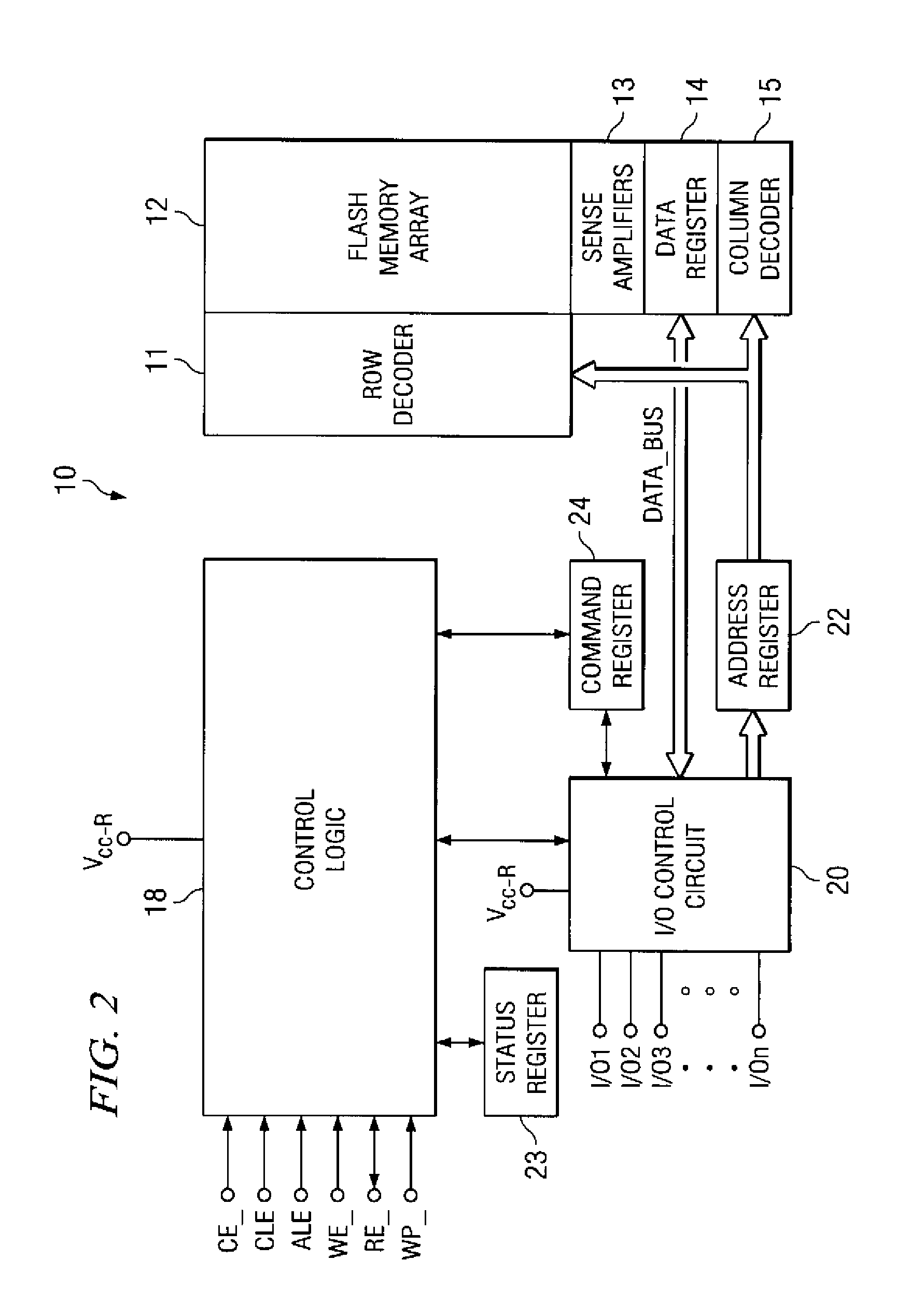

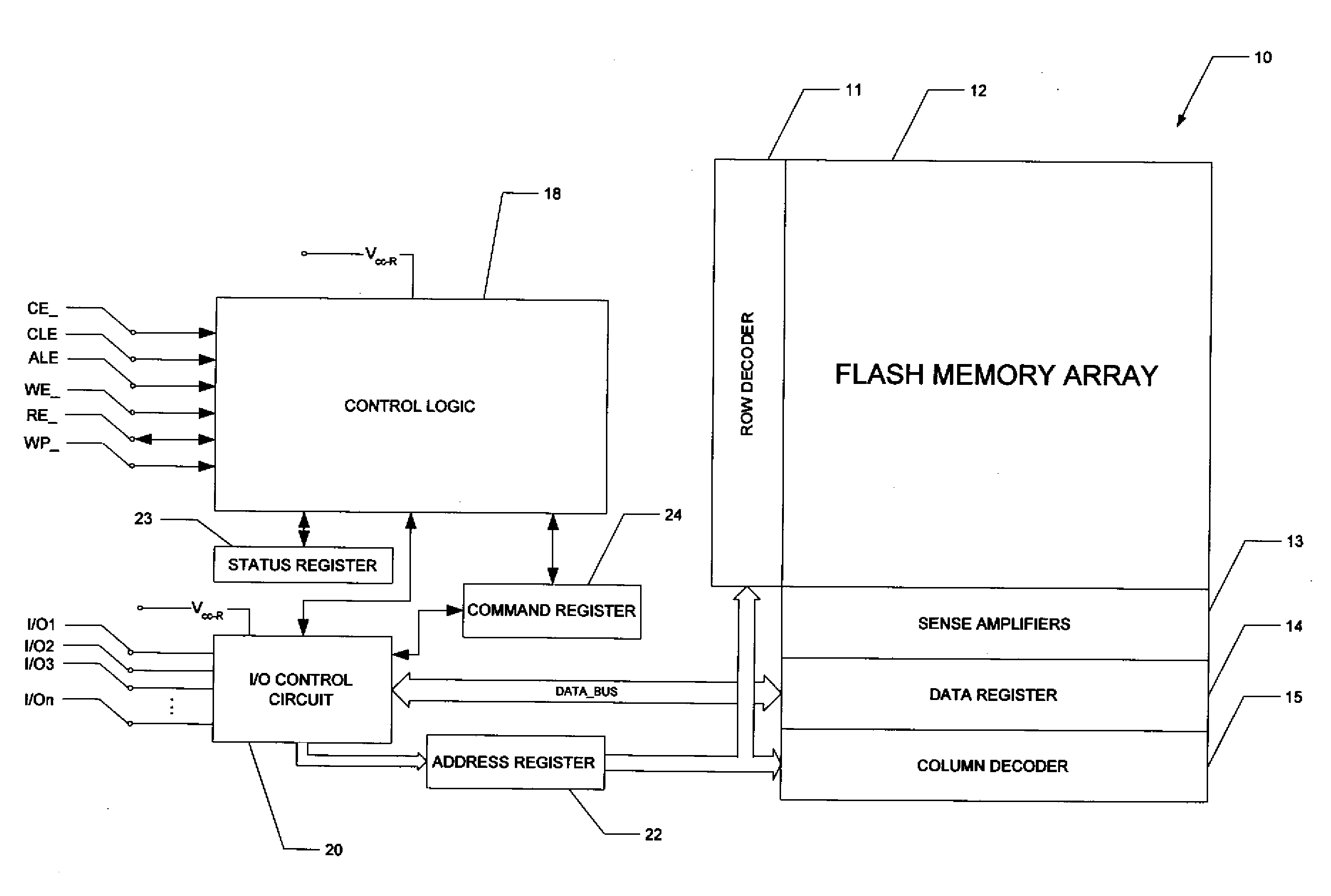

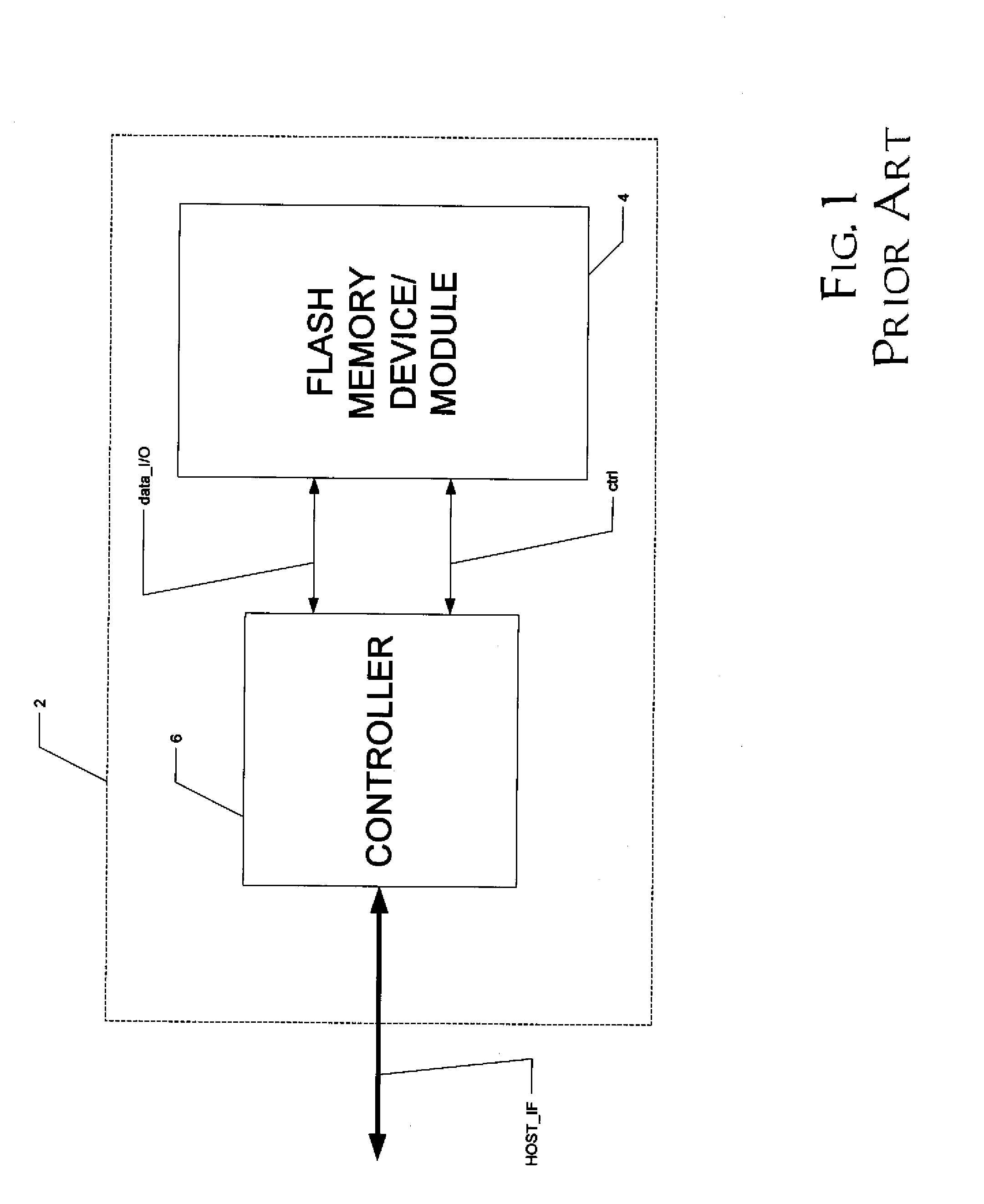

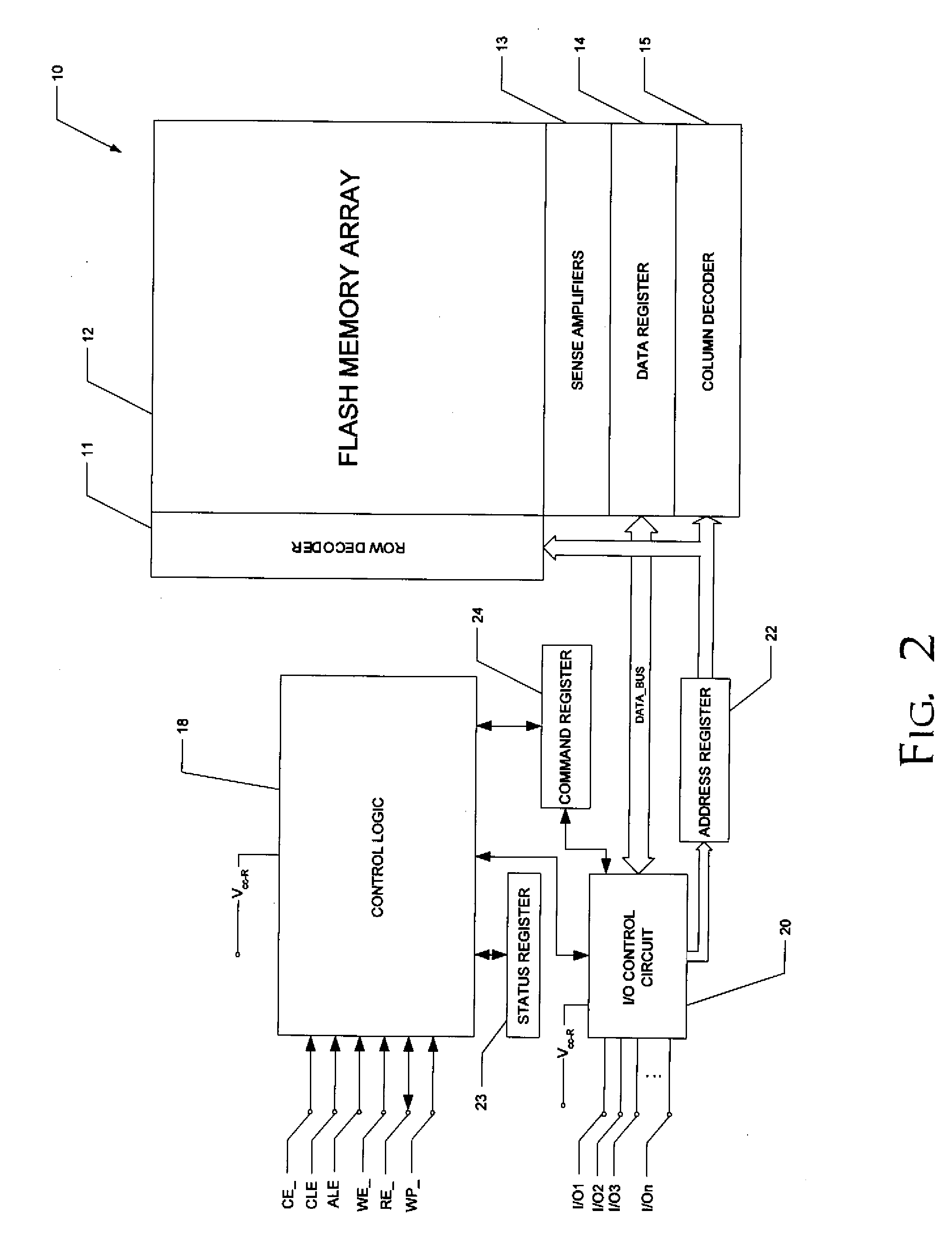

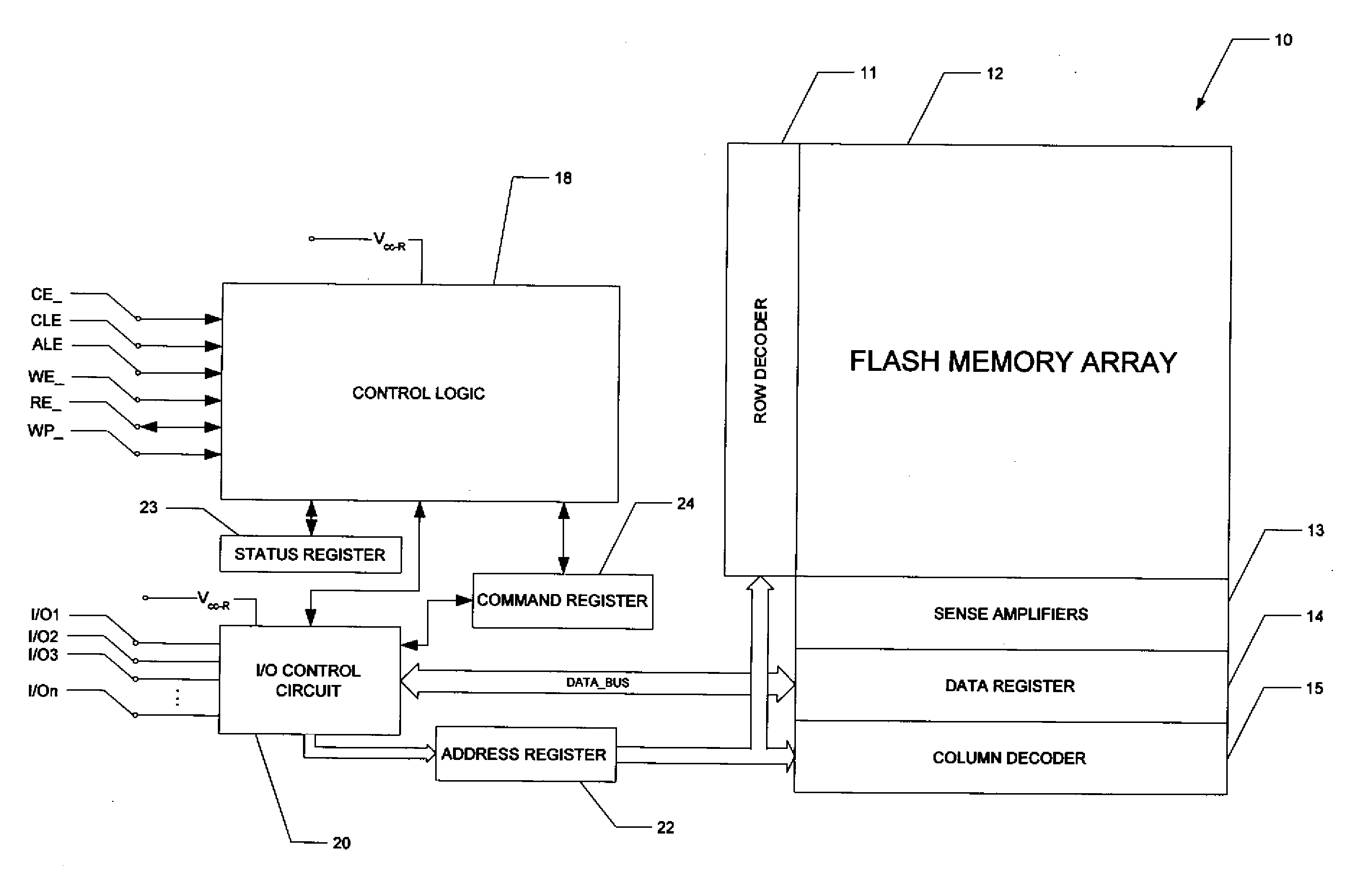

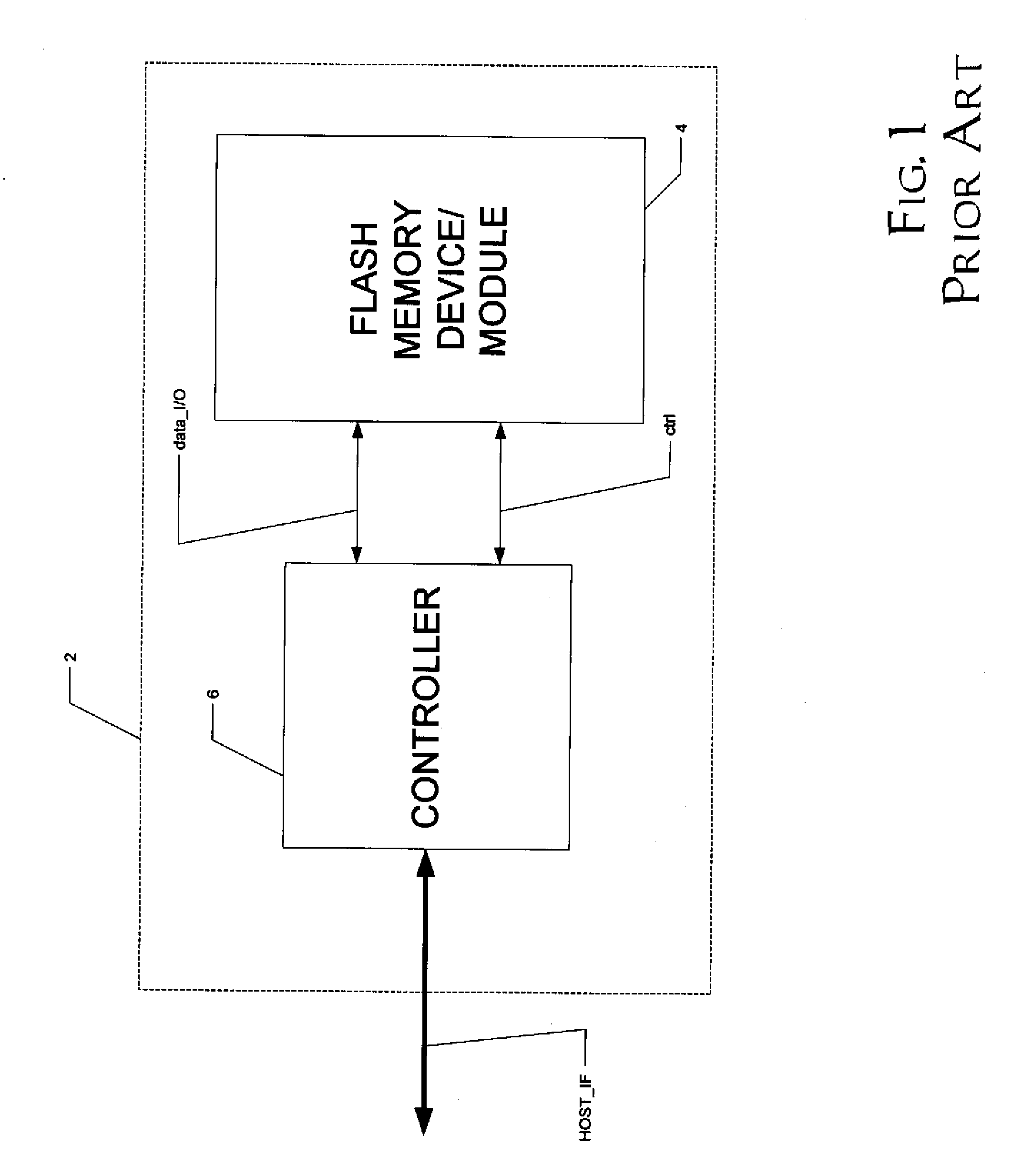

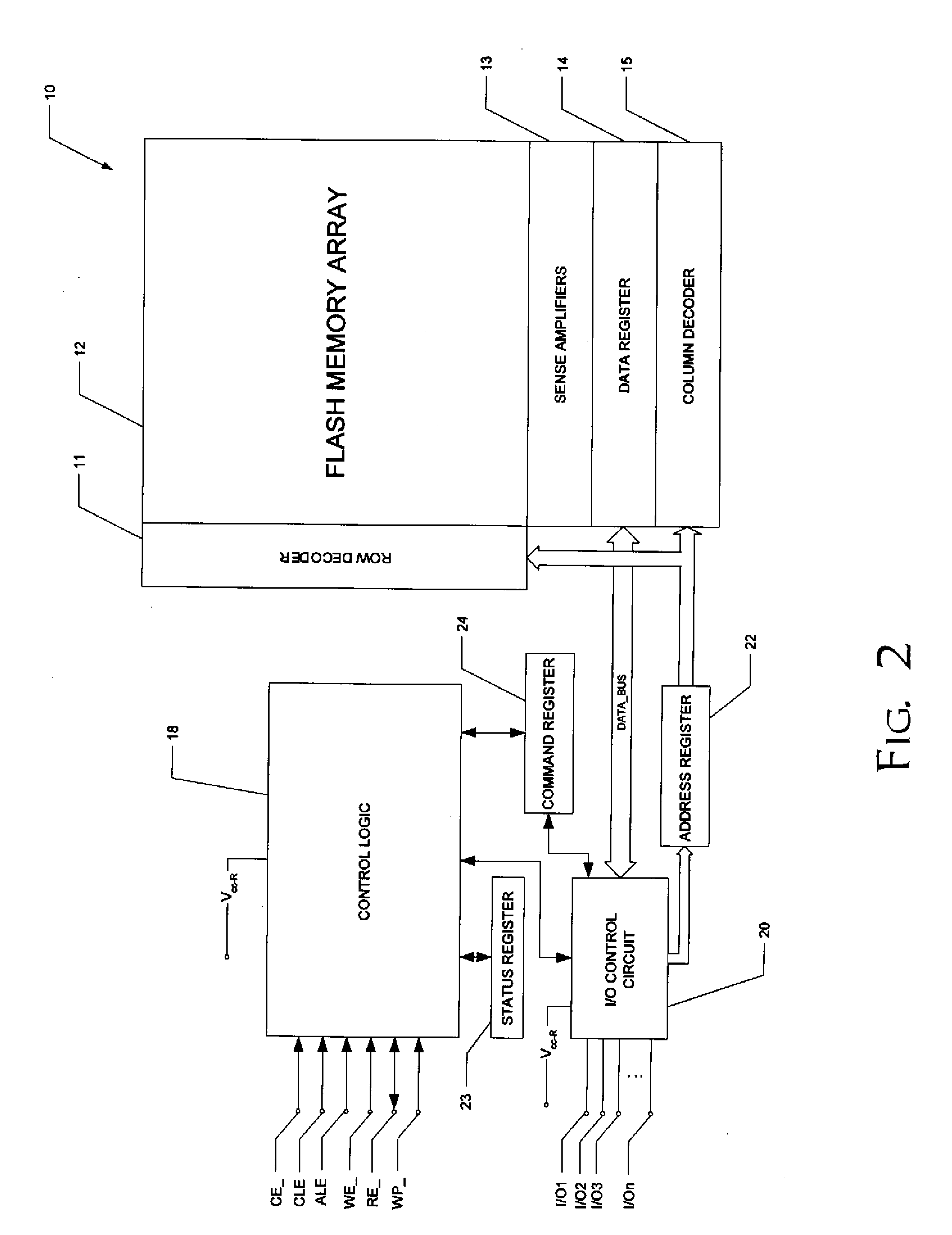

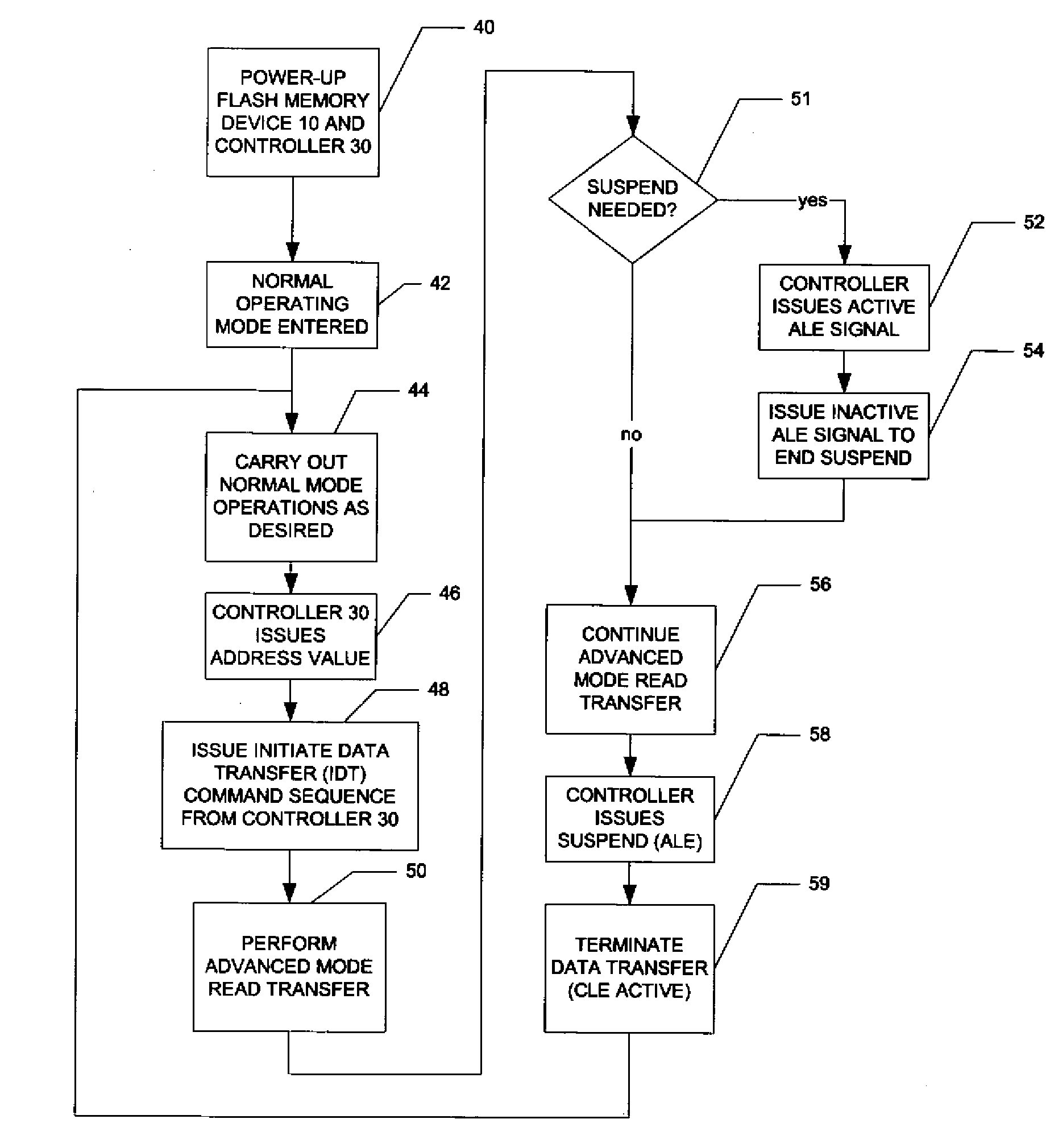

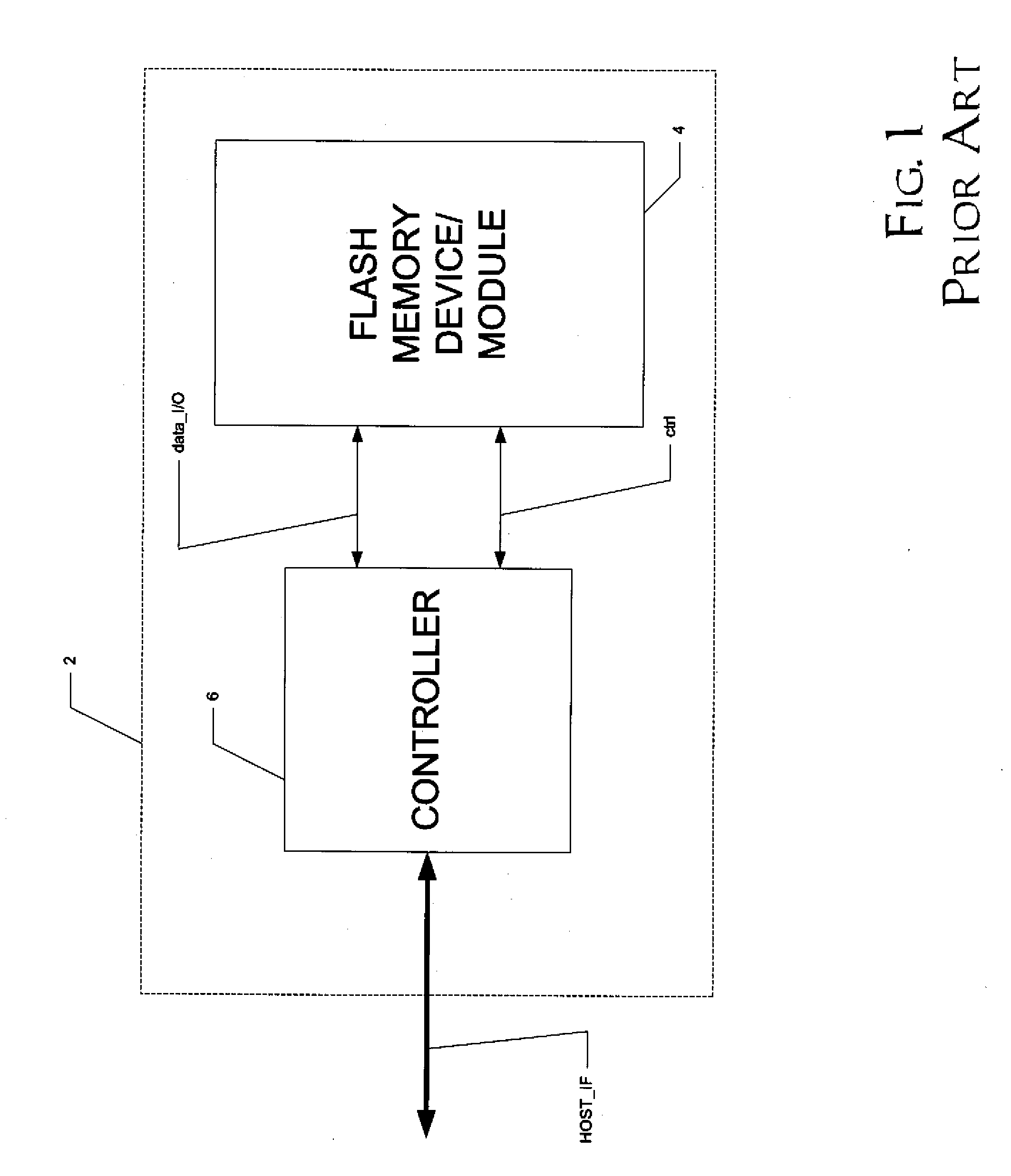

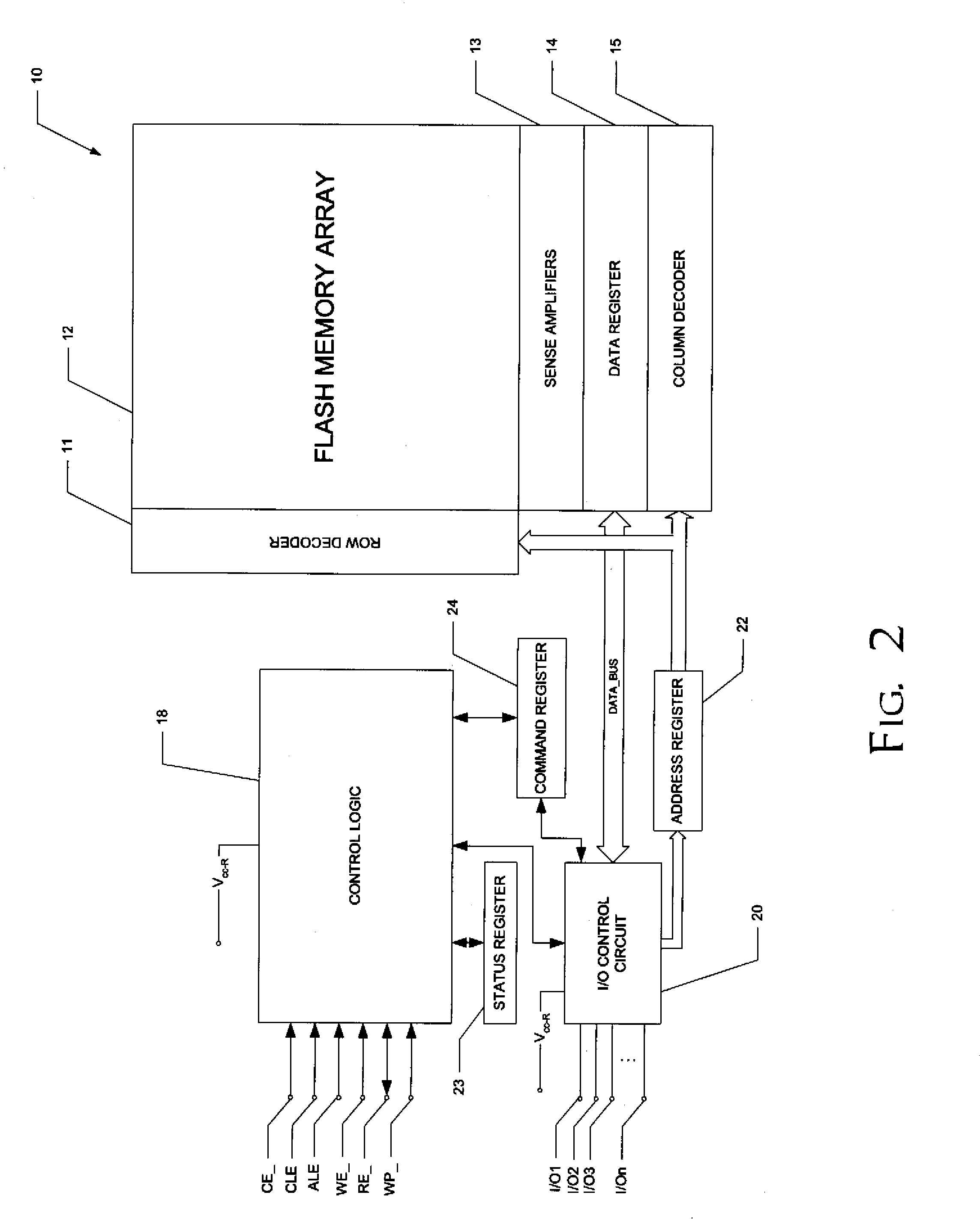

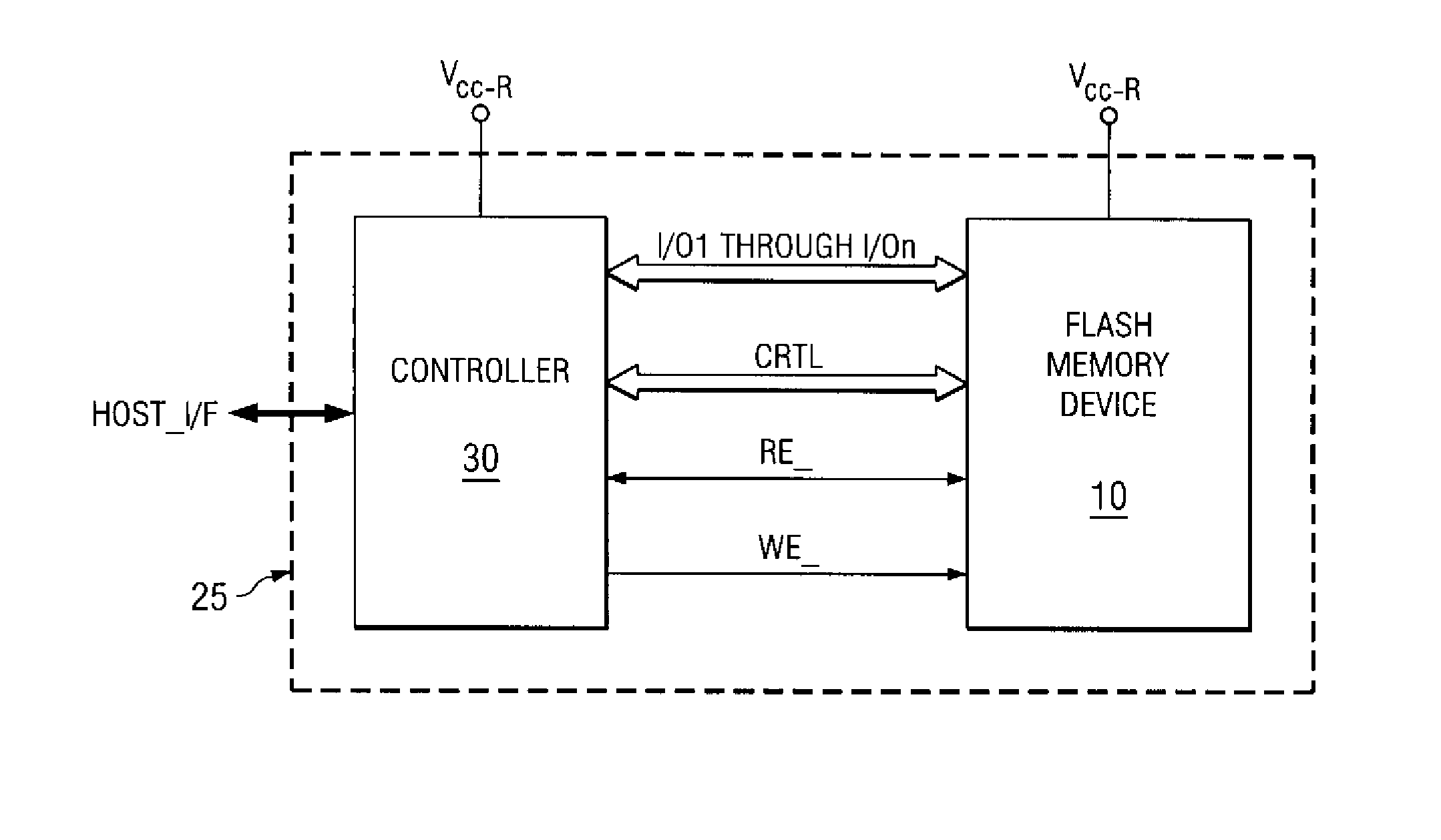

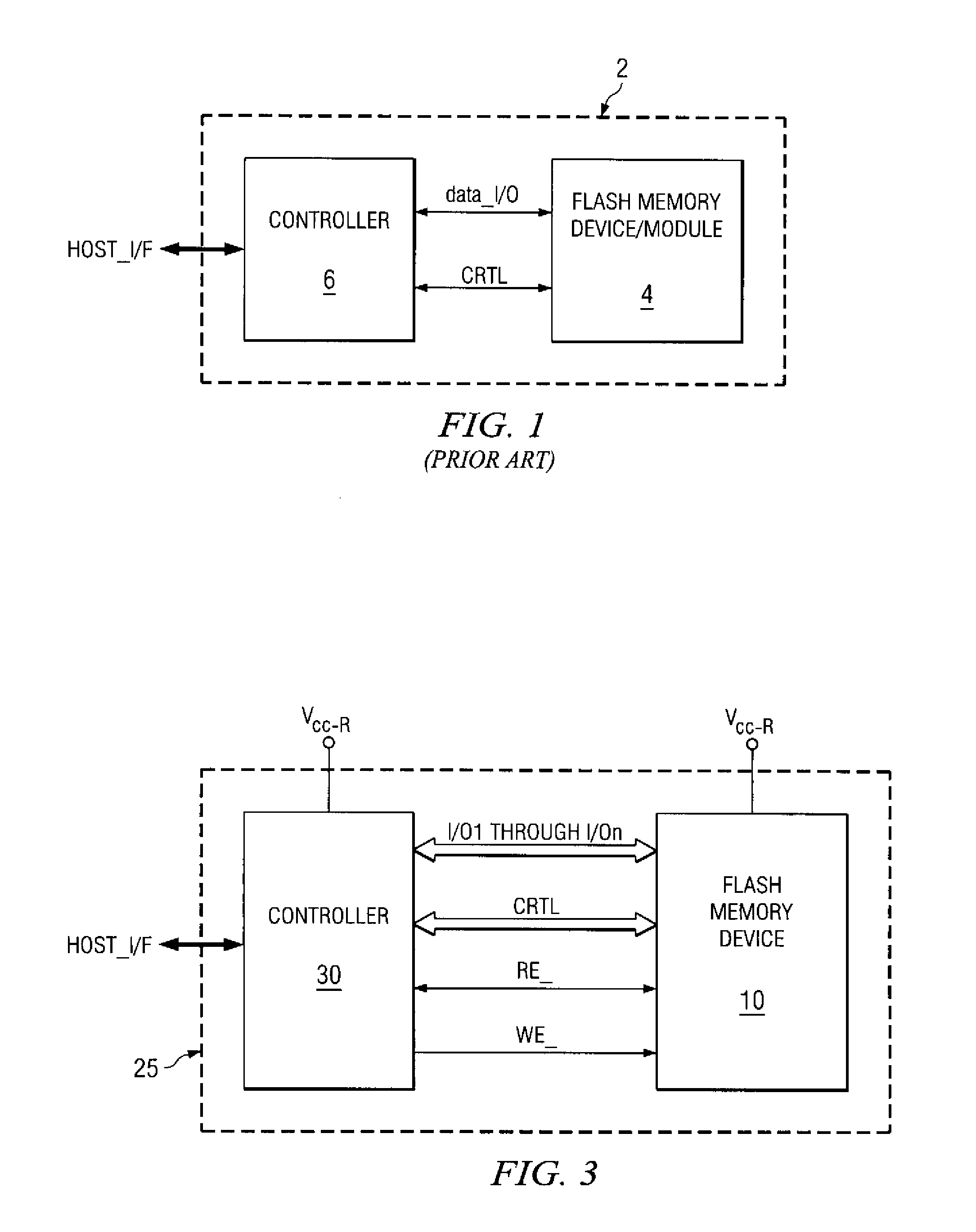

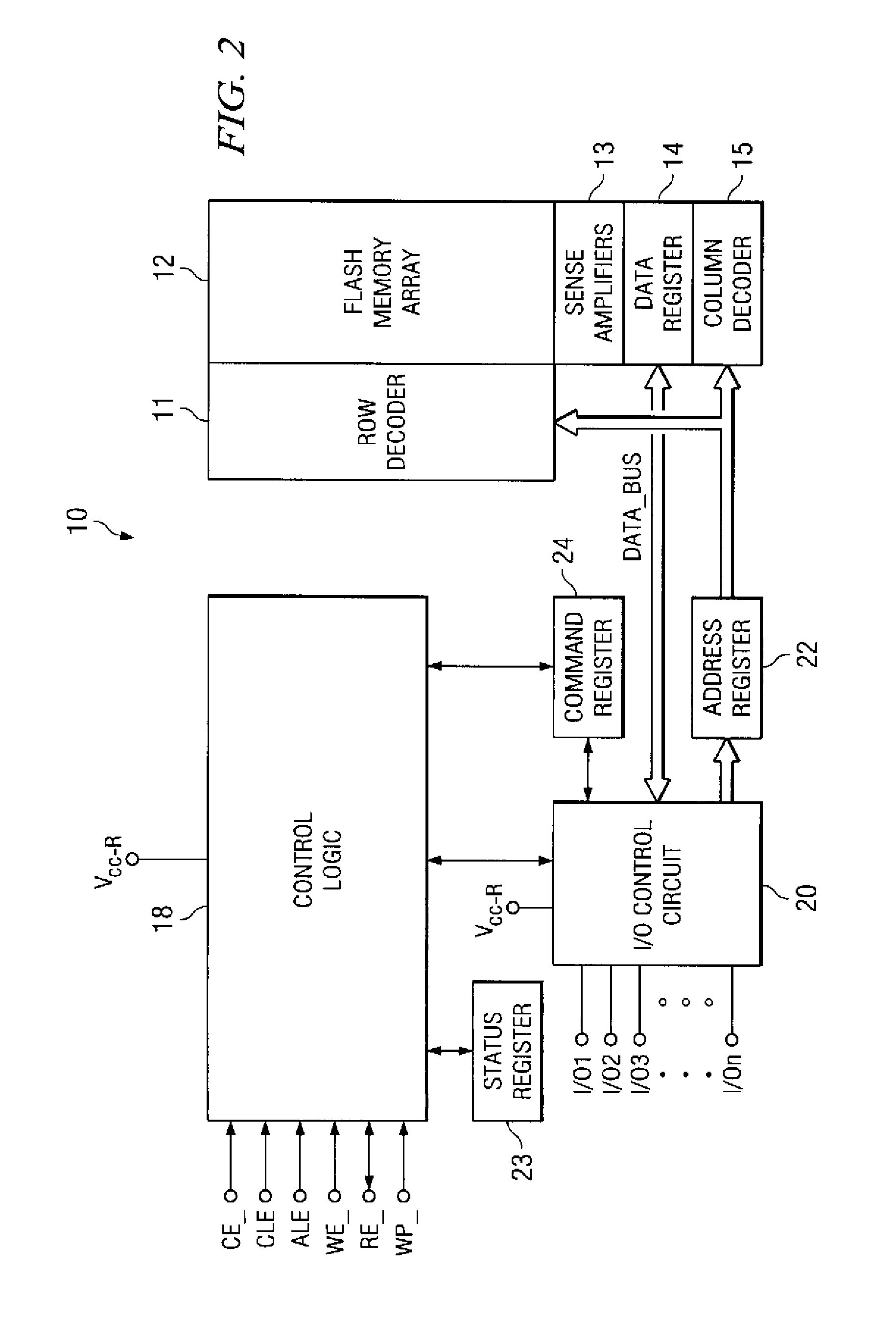

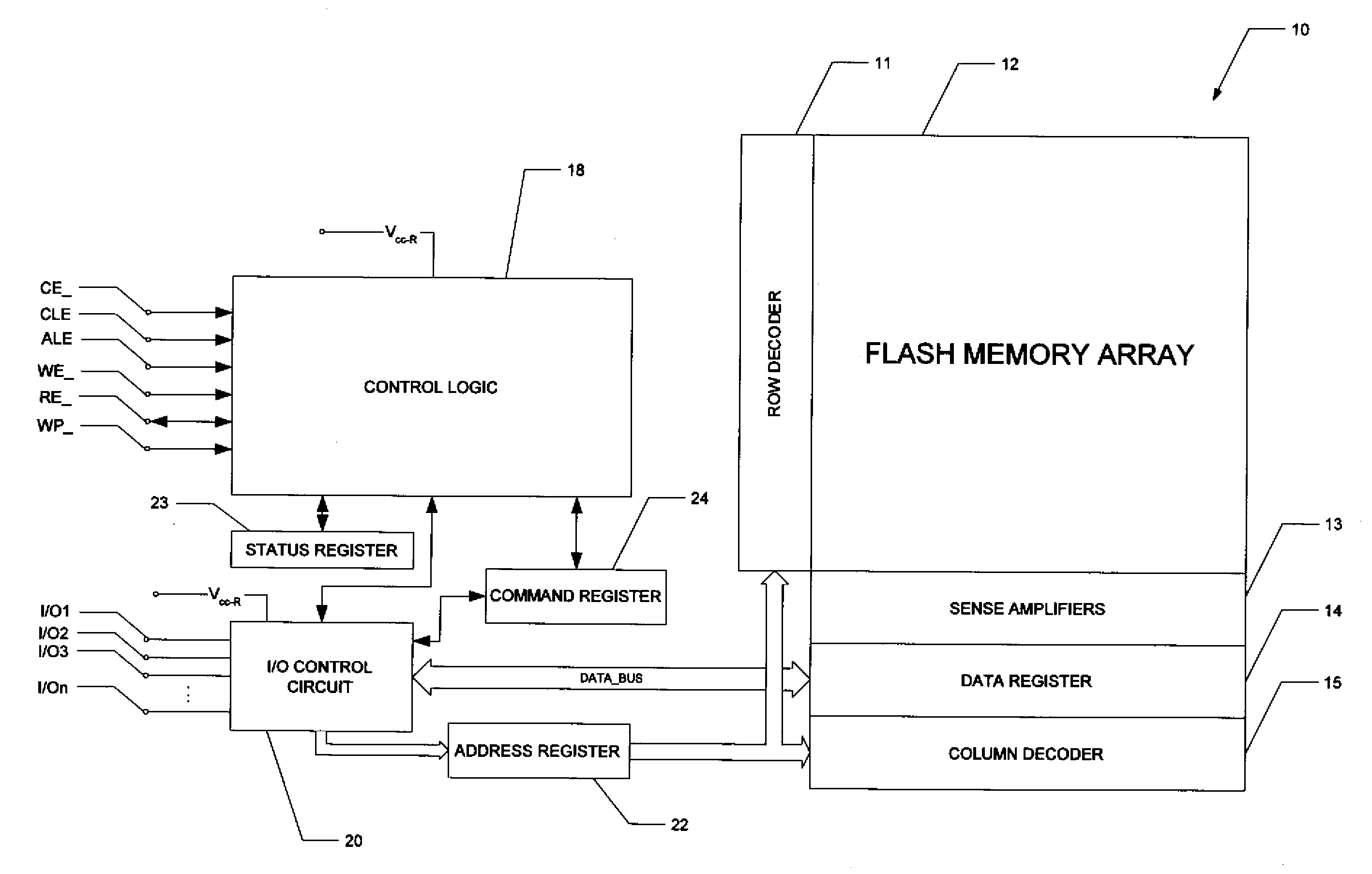

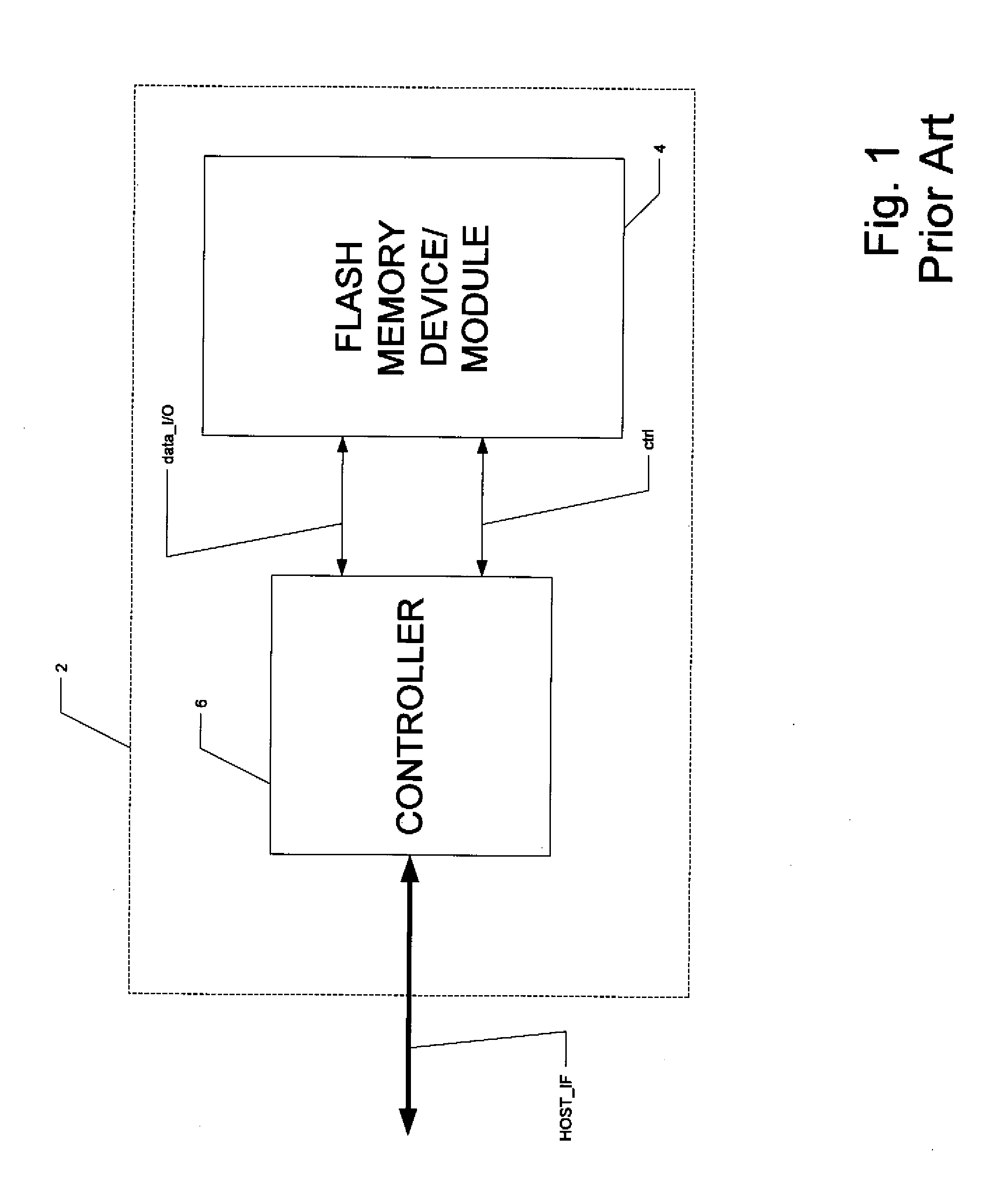

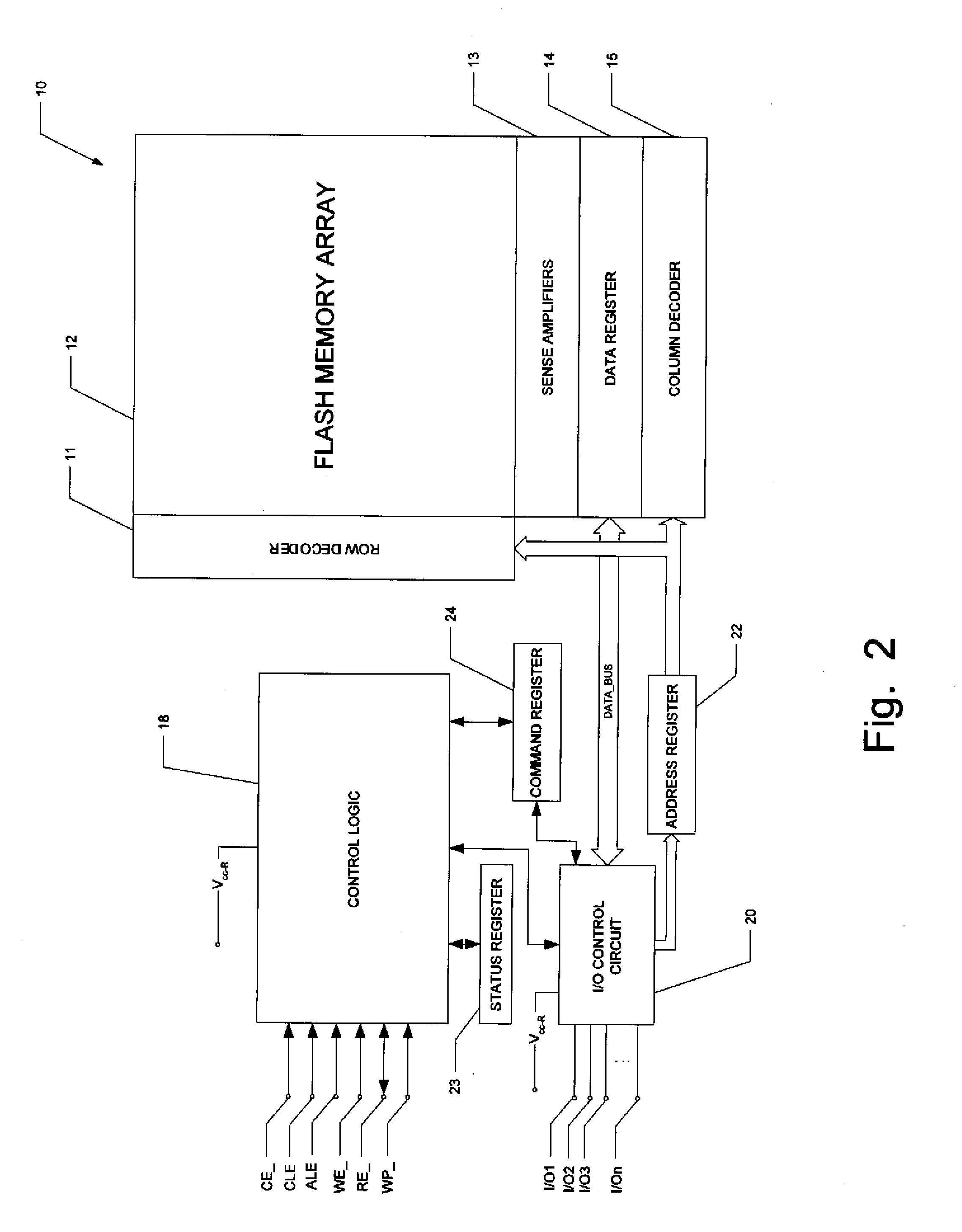

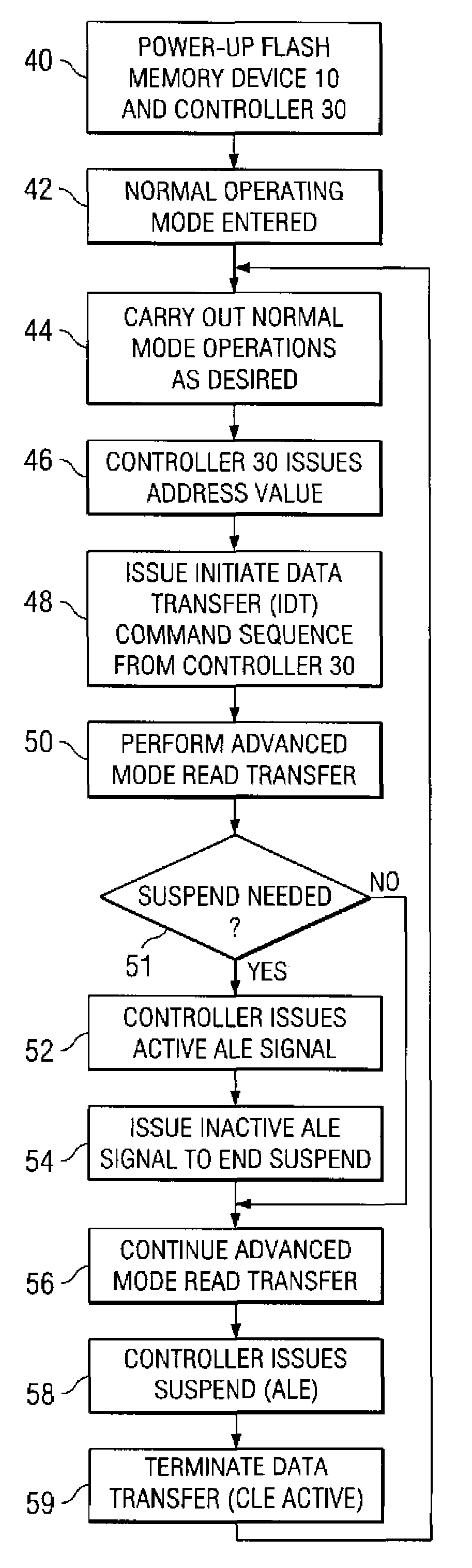

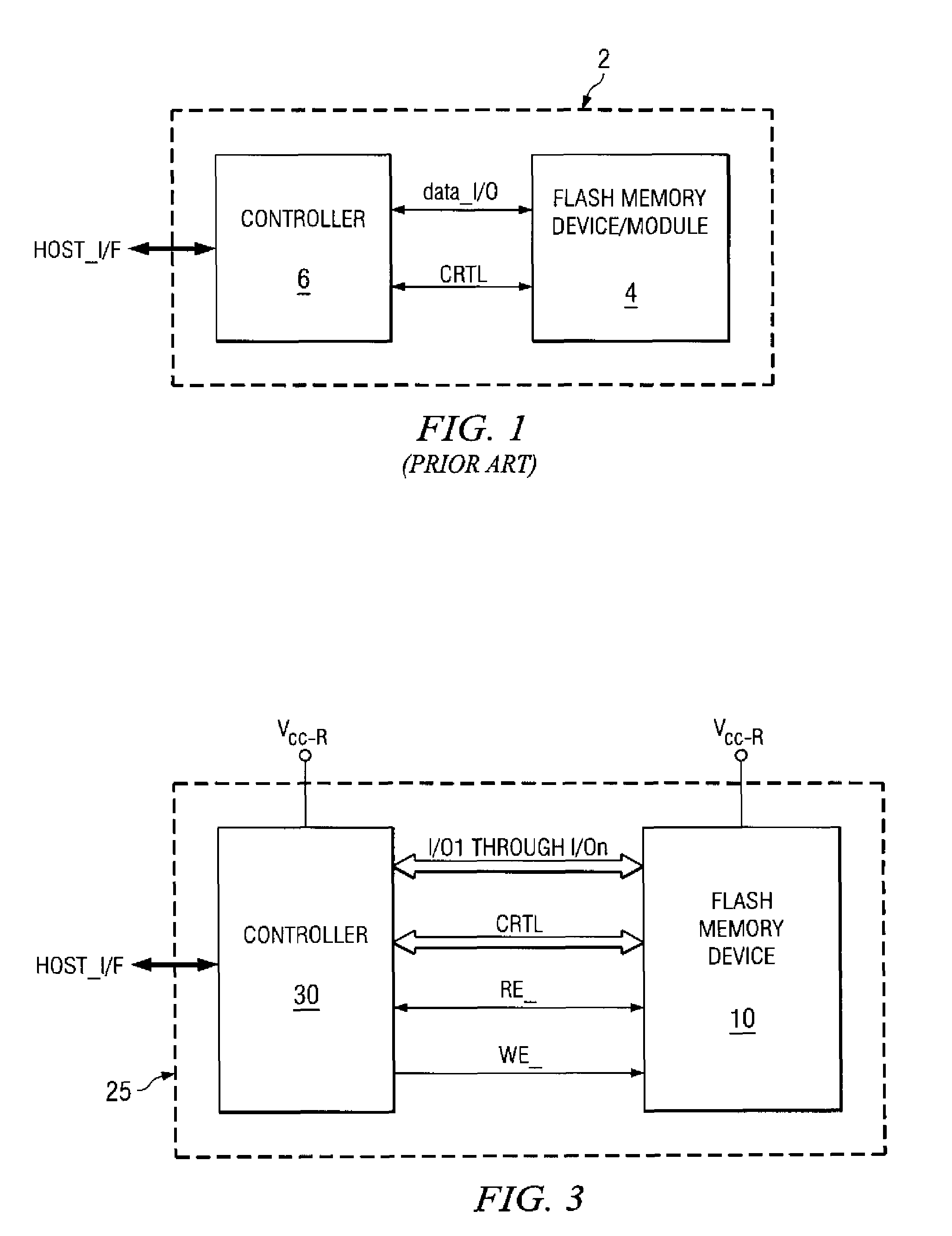

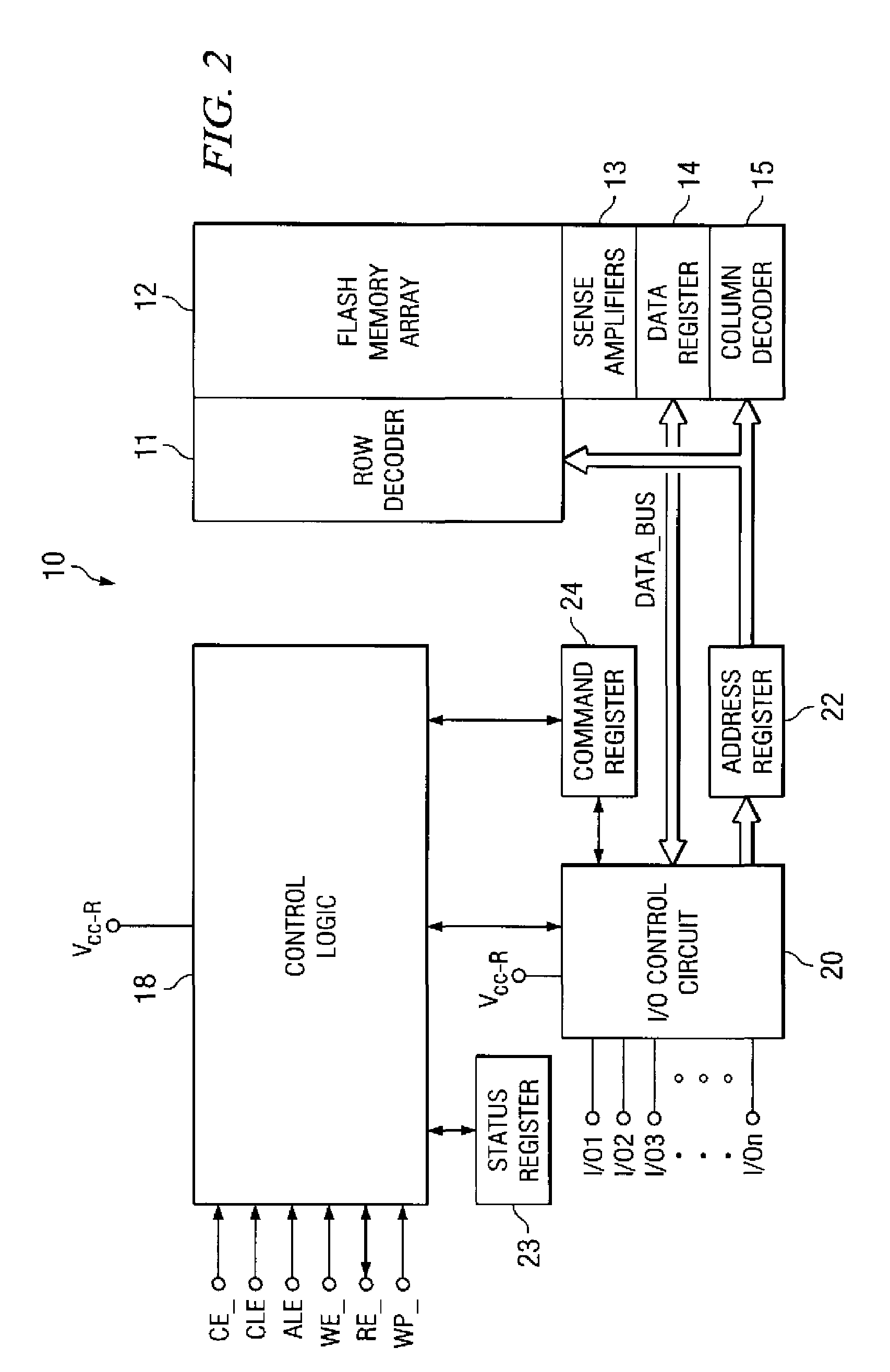

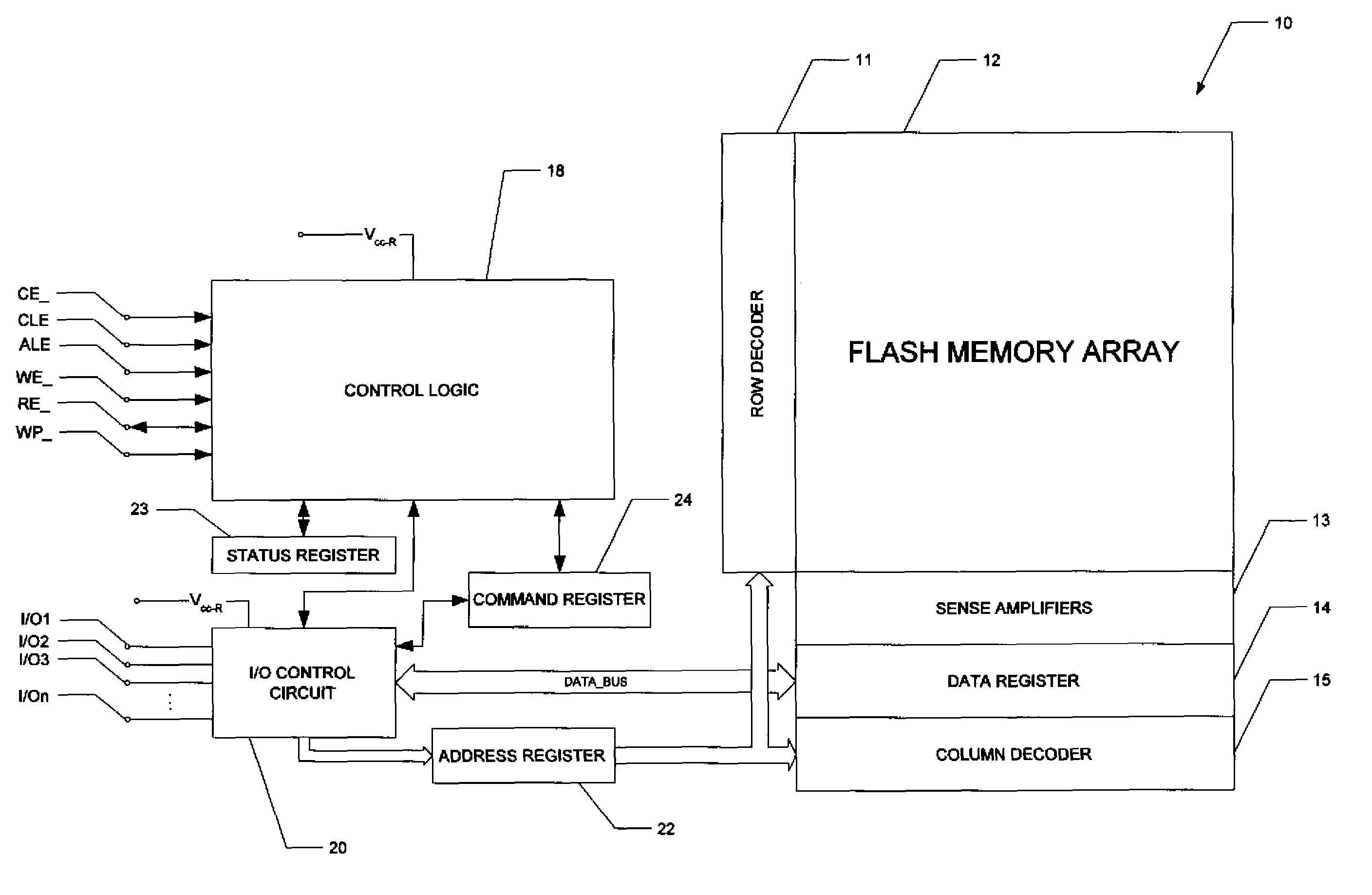

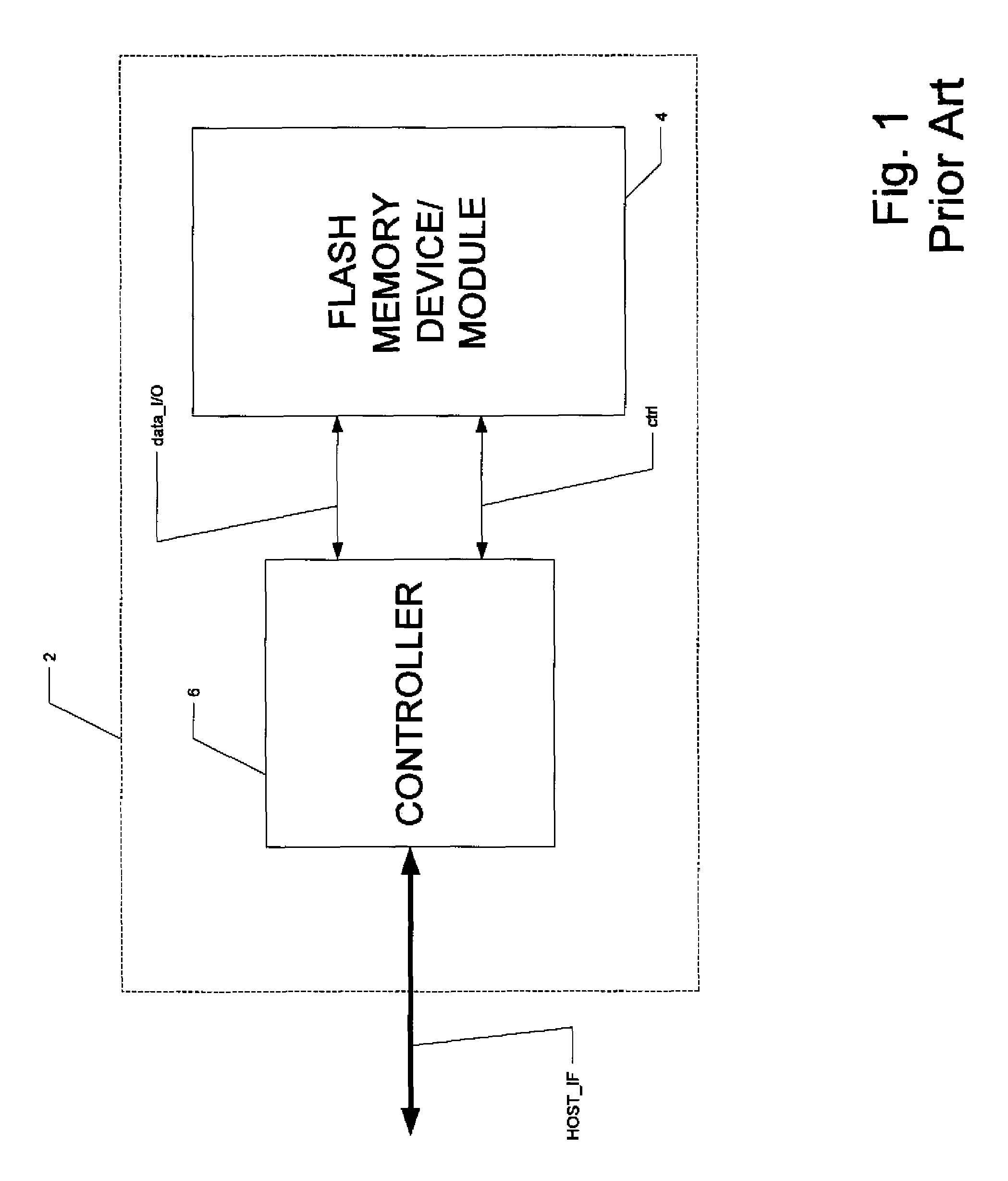

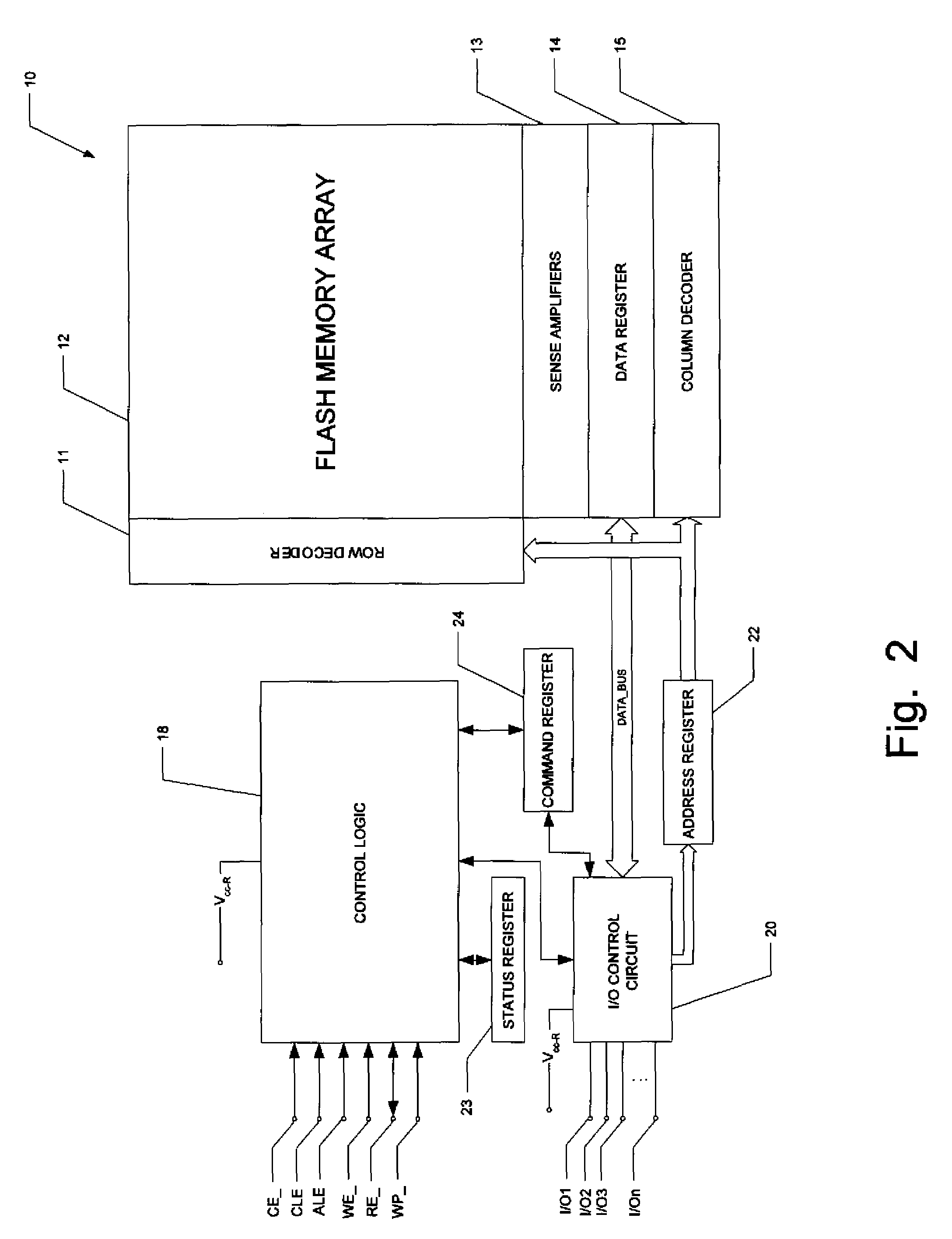

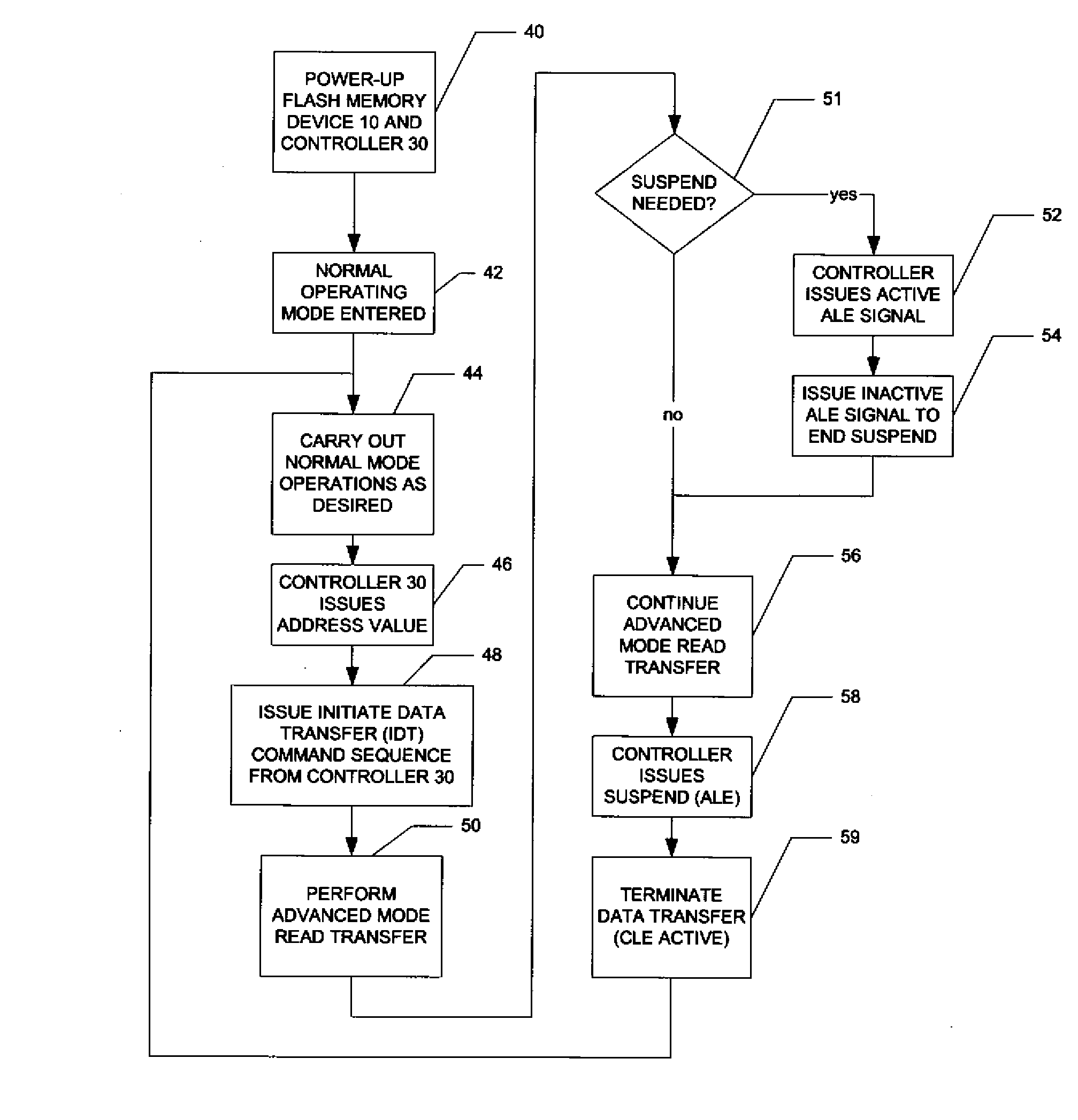

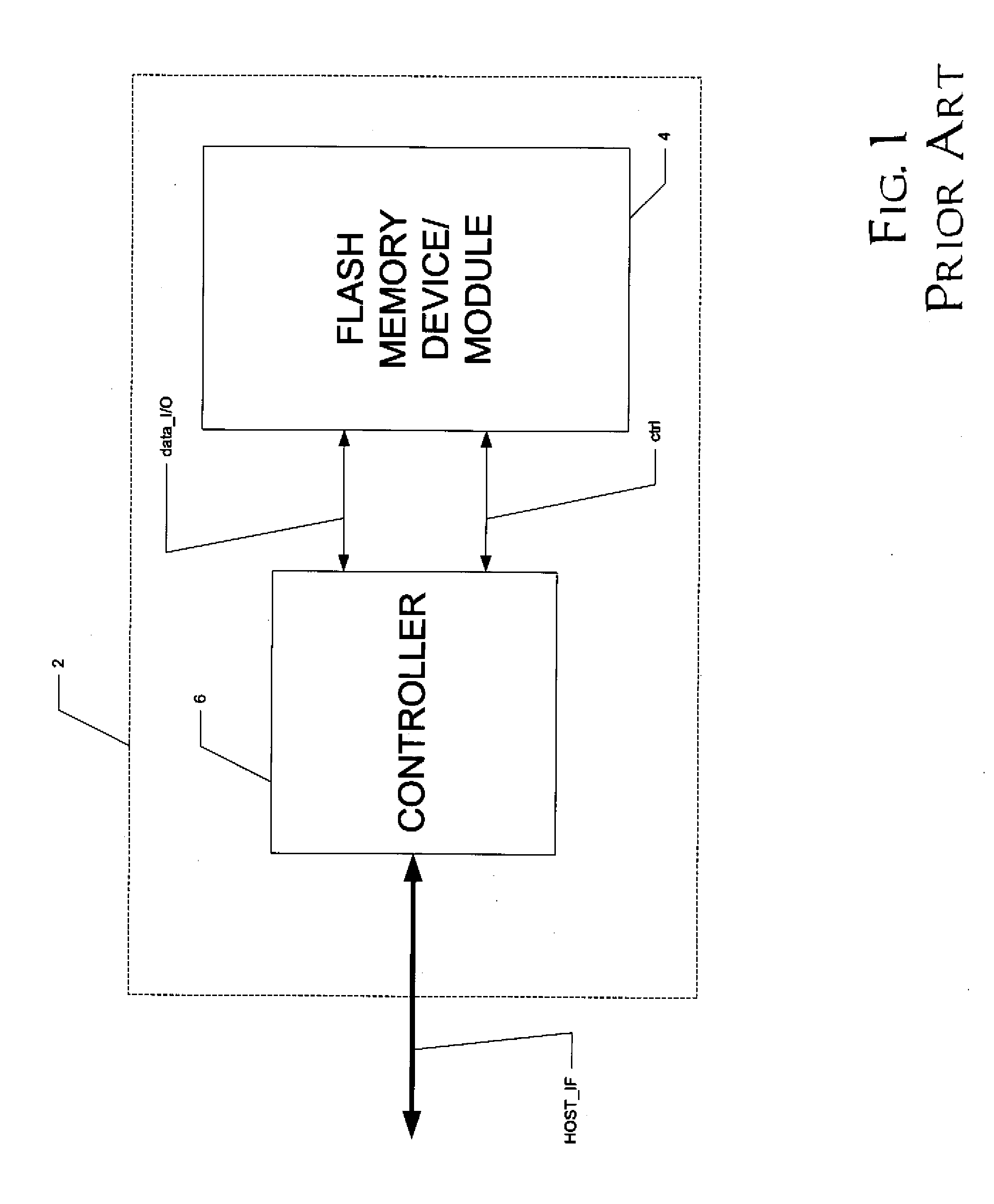

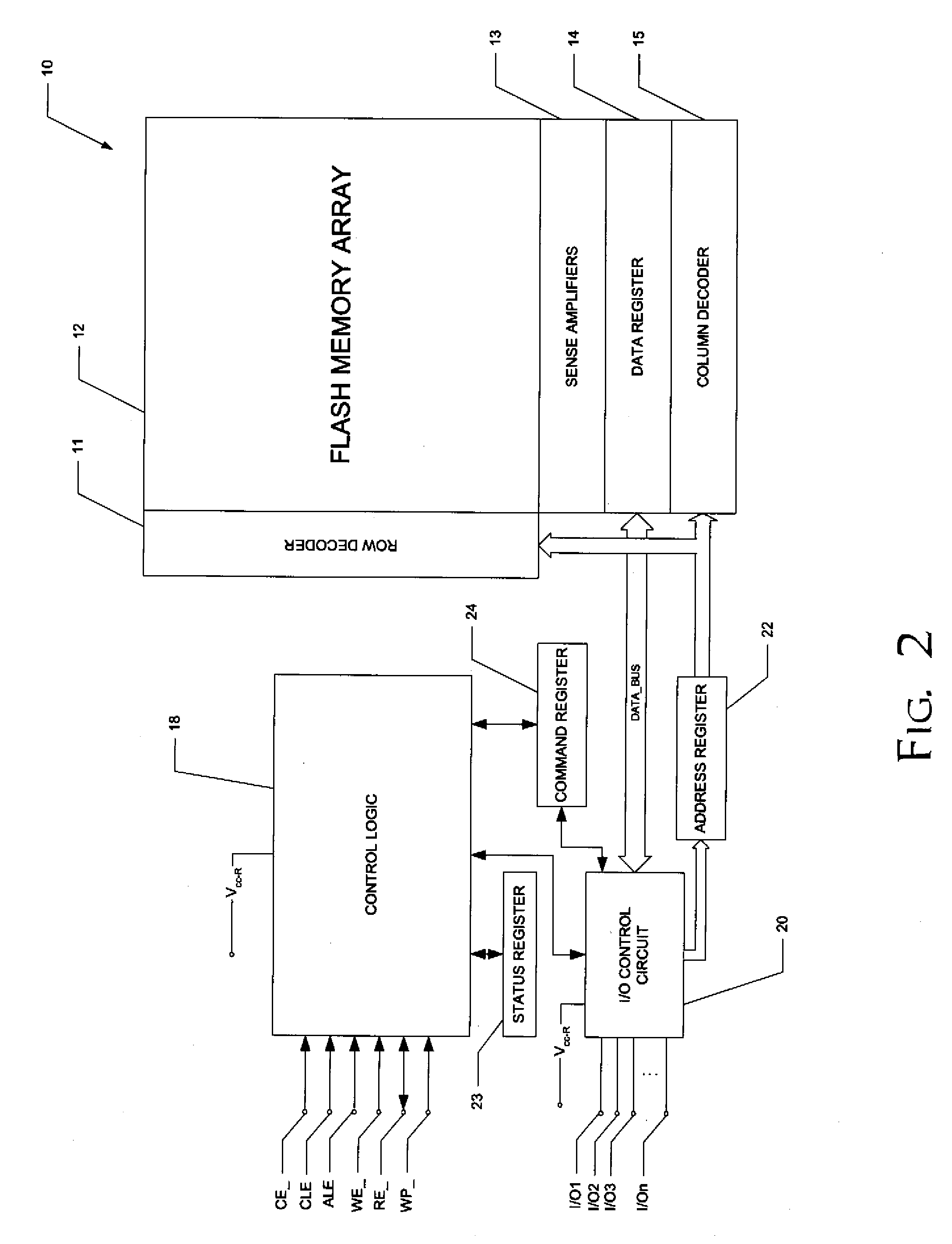

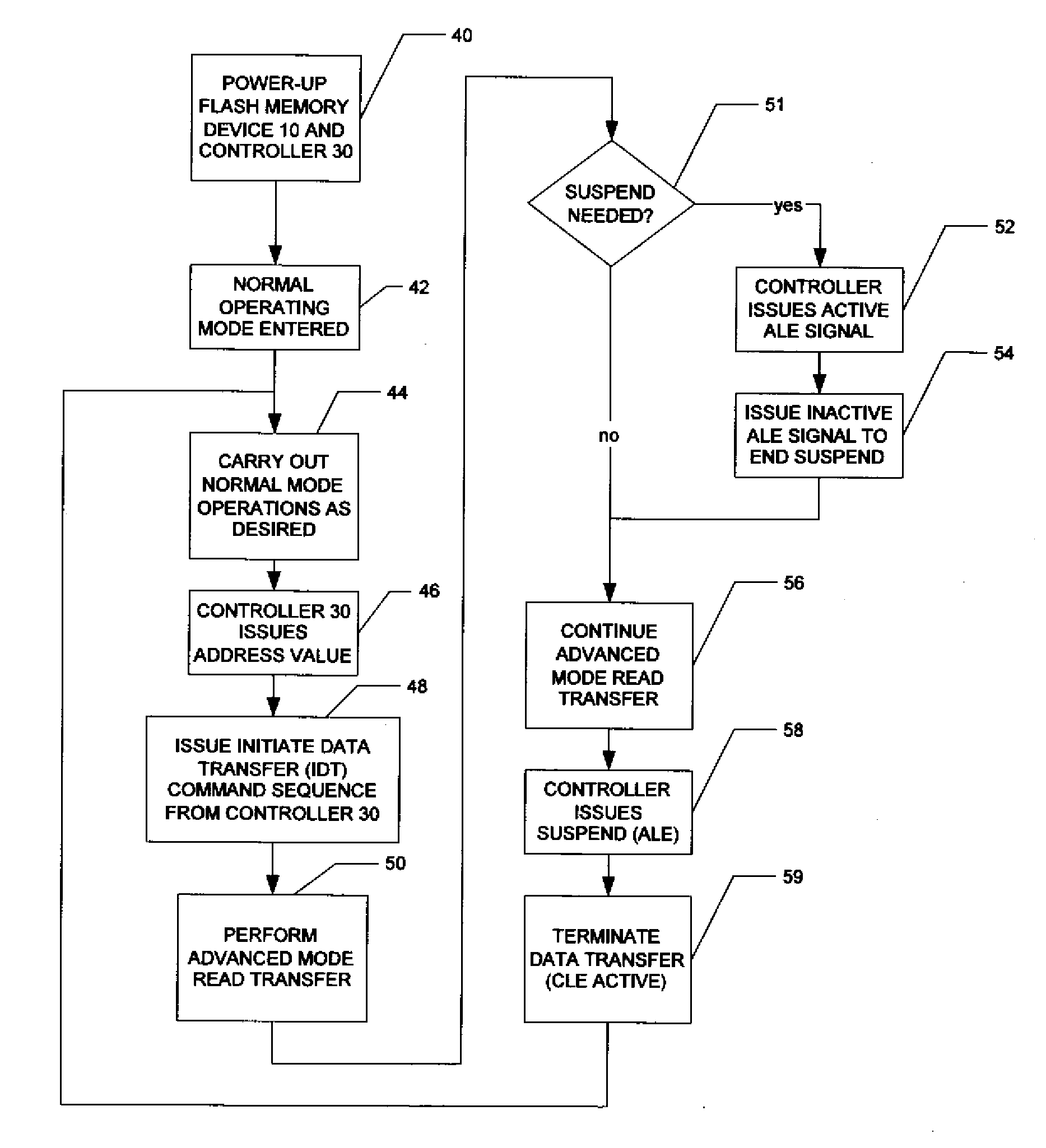

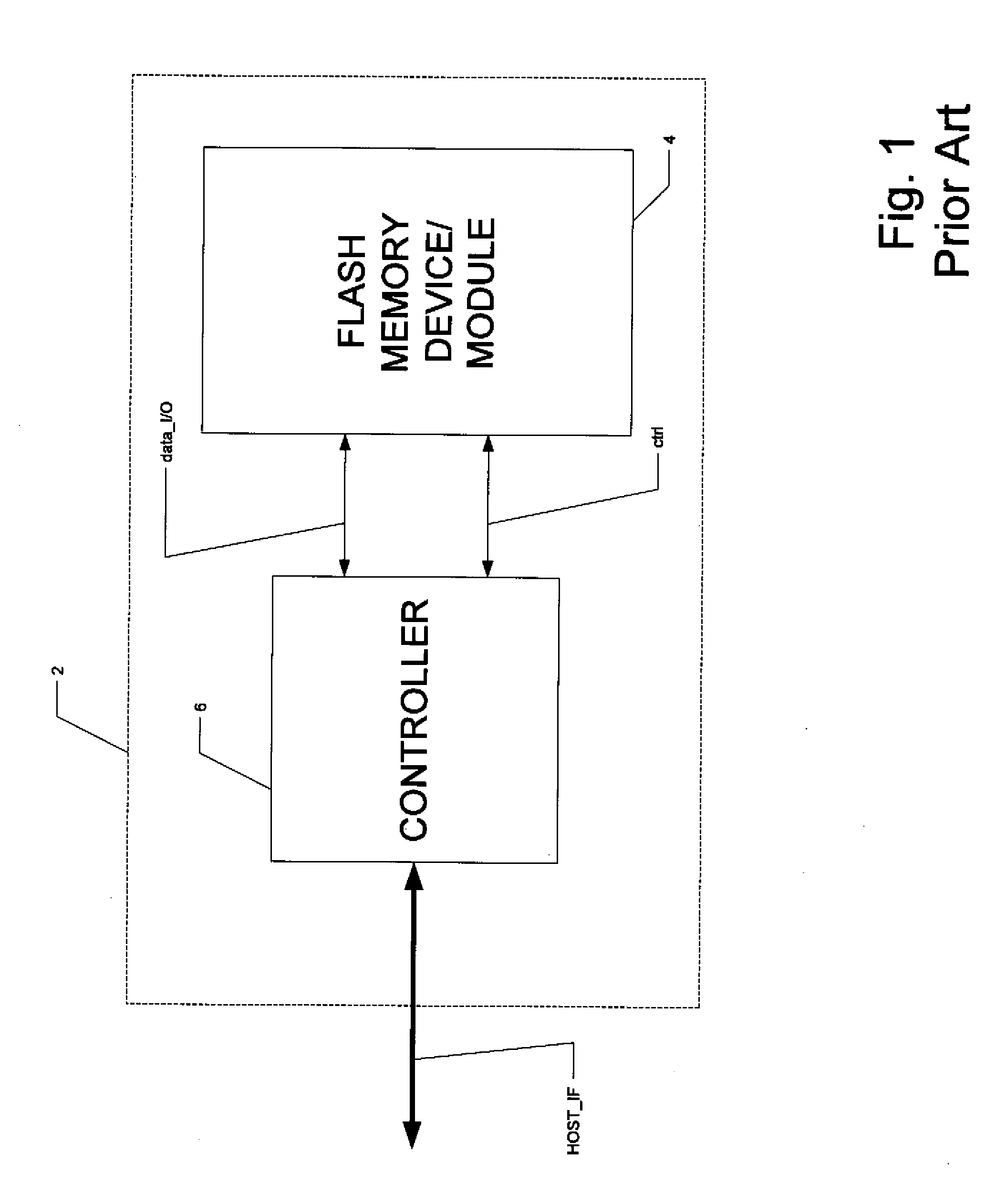

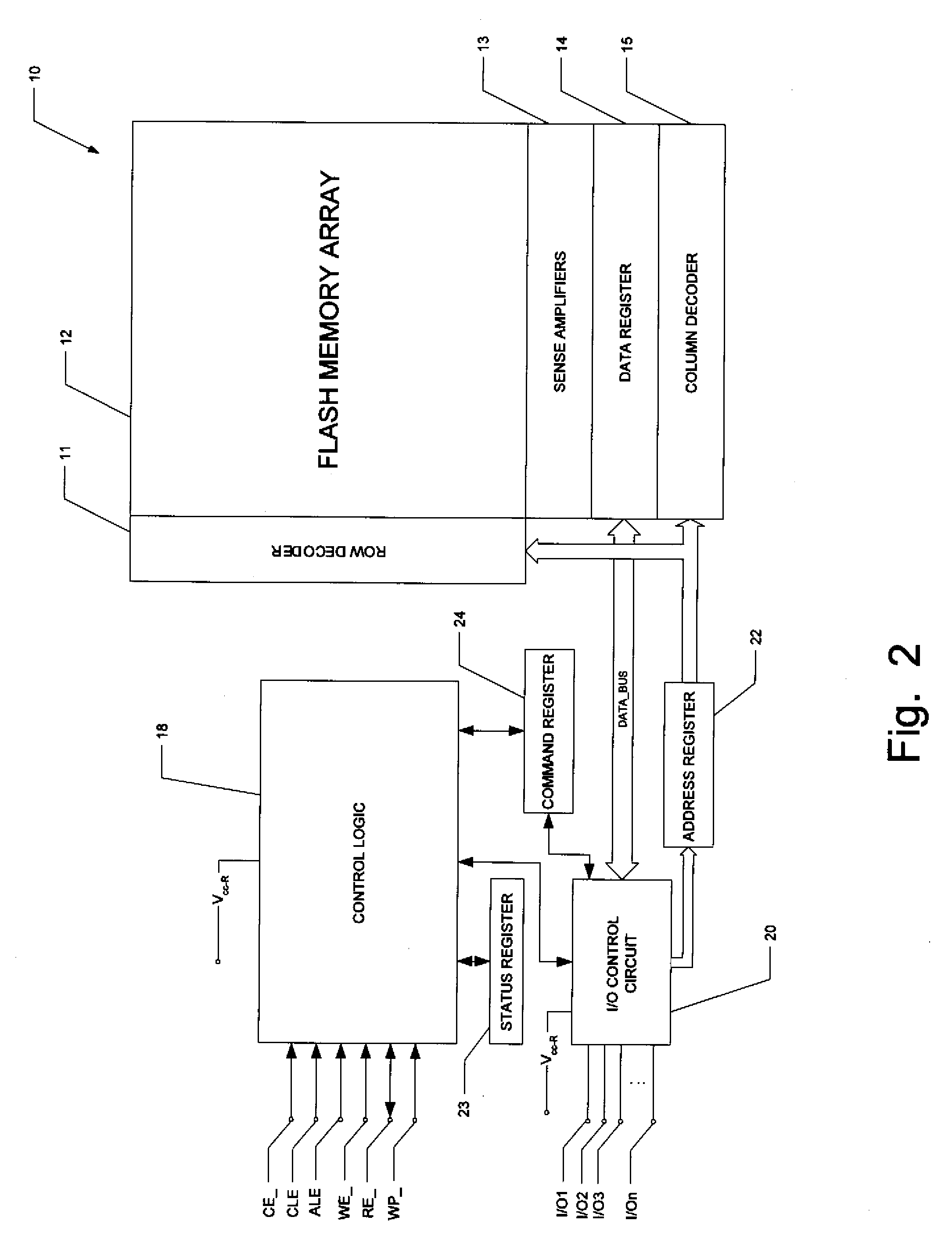

High-performance flash memory data transfer

ActiveUS7366029B2Minimize data transferMinimize data skewRead-only memoriesDigital storageControl signalNormal mode

A flash memory system including a flash memory device and a controller, operable according to an advanced data transfer mode is disclosed. The flash memory device is operable both in a “legacy” mode, in which read data is presented by the memory synchronously with each cycle of a read data strobe from the controller, and in which input data is latched by the memory synchronously with each cycle of a write data strobe from the controller. In the advanced mode, which can be initiated by the controller forwarding an initiation command to the memory, the flash memory itself sources the read data strobe at a higher frequency, for example at twice the frequency, of that available in the normal mode. In the advanced mode, the input data is presented by the controller synchronously with a higher frequency write data strobe than is available in the normal mode. The voltage swing of the data and control signals is reduced from conventional standards, to reduce power consumption.

Owner:SANDISK TECH LLC

System and method for resolving conflicts detected during a synchronization session

InactiveUS20060059208A1Conflict detectedReduce riskData processing applicationsDatabase distribution/replicationMobile deviceData transmission

A system and method is described for resolving a conflict detected while synchronizing a first data object in a first store associated with a mobile device and a second data object in a second store associated with a server. Once the conflict is detected, properties of the first data object are compared with corresponding properties of the second data object. If the properties and the corresponding properties that differ are designated as mergeable properties, the properties and the corresponding properties are merged. Merging the properties involves sending a preferred state associated with each of the properties and the corresponding properties to the mobile device and the server for updating the first data object and second data object, respectively, when an initial state for the properties and the corresponding properties is different than the preferred state. The preferred state is based on a likelihood that vital information would be lost if the preferred state did not replace the initial state of the property or the corresponding property. The merging is performed without user-intervention on the mobile device. In addition, the entire first data object or second data object is not sent to the mobile device to achieve the merge, thereby minimizing the data transfer to the mobile device.

Owner:MICROSOFT TECH LICENSING LLC

High-Performance Flash Memory Data Transfer

ActiveUS20080019196A1Reduce power consumptionMinimize data transferRead-only memoriesDigital storageControl signalTransfer mode

A flash memory system including a flash memory device and a controller, operable according to an advanced data transfer mode is disclosed. The flash memory device is operable both in a “legacy” mode, in which read data is presented by the memory synchronously with each cycle of a read data strobe from the controller, and in which input data is latched by the memory synchronously with each cycle of a write data strobe from the controller. In the advanced mode, which can be initiated by the controller forwarding an initiation command to the memory, the flash memory itself sources the read data strobe and also a write data strobe that is out-of-phase relative to the read data strobe, and presents data synchronously with one of the edges of that read data strobe. In the advanced mode for a data write, the input data is presented by the controller synchronously with a selected edge of both the write data strobe and the read data strobe. The voltage swing of the data and control signals is reduced from conventional standards, to reduce power consumption.

Owner:SANDISK TECH LLC

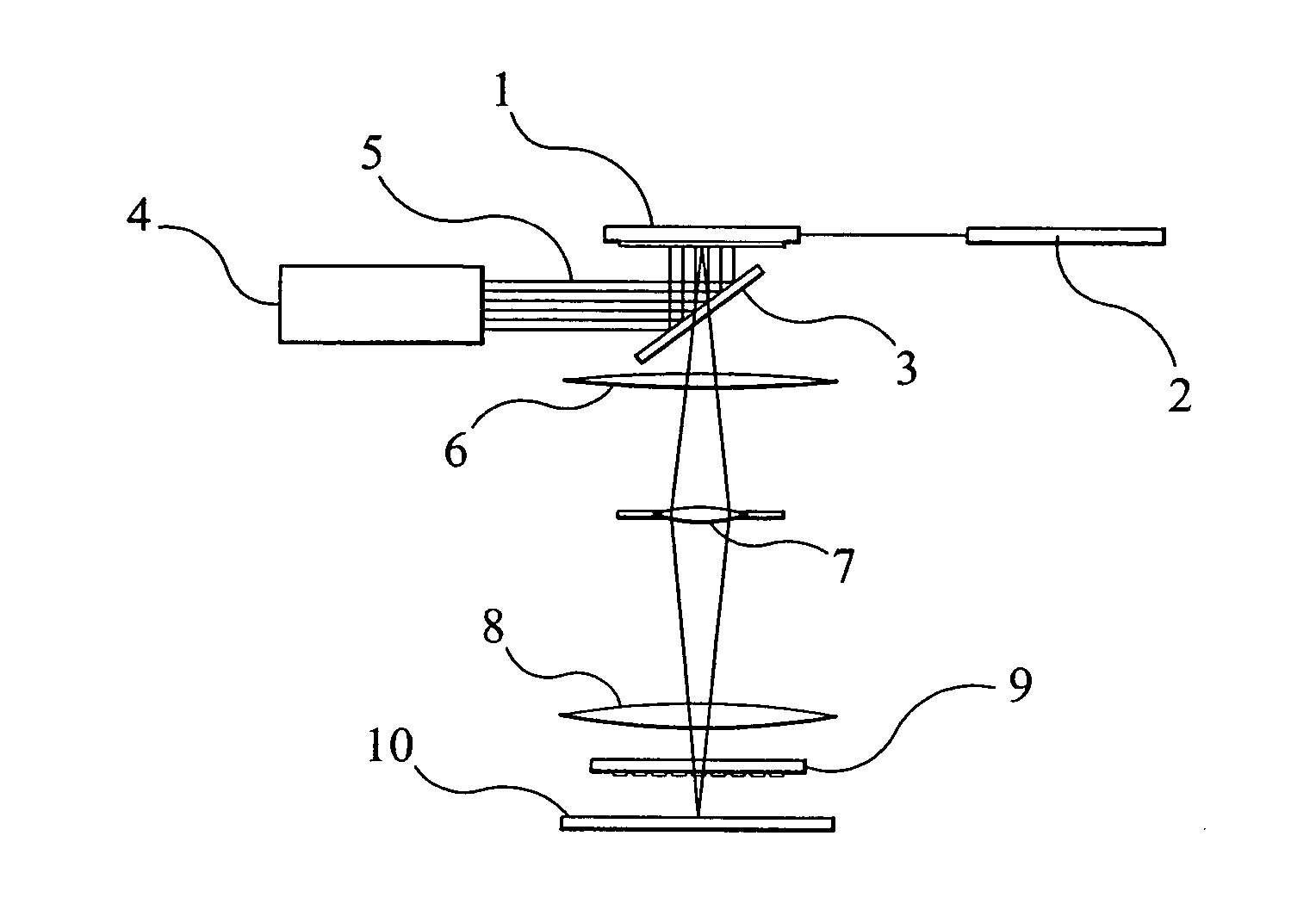

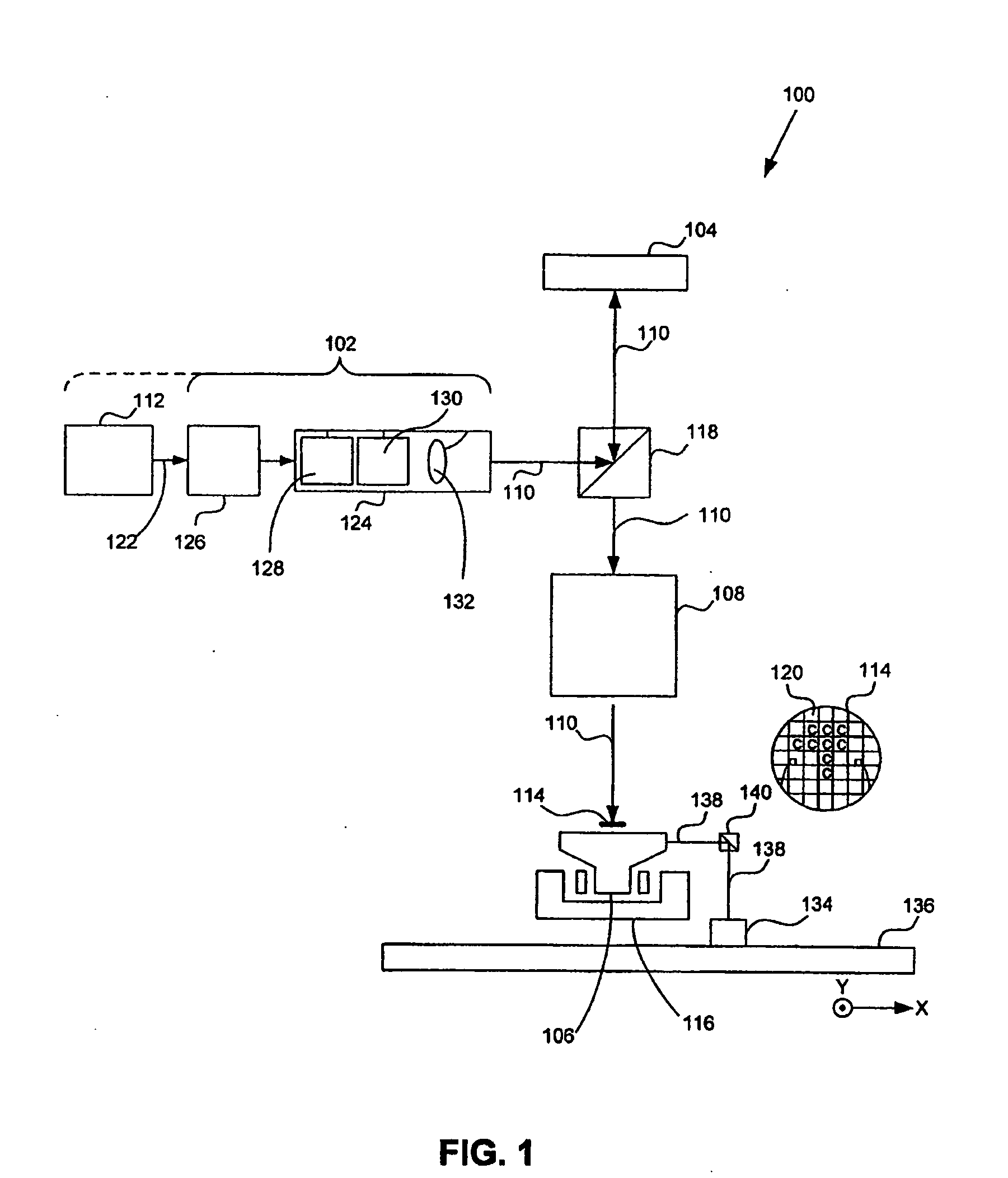

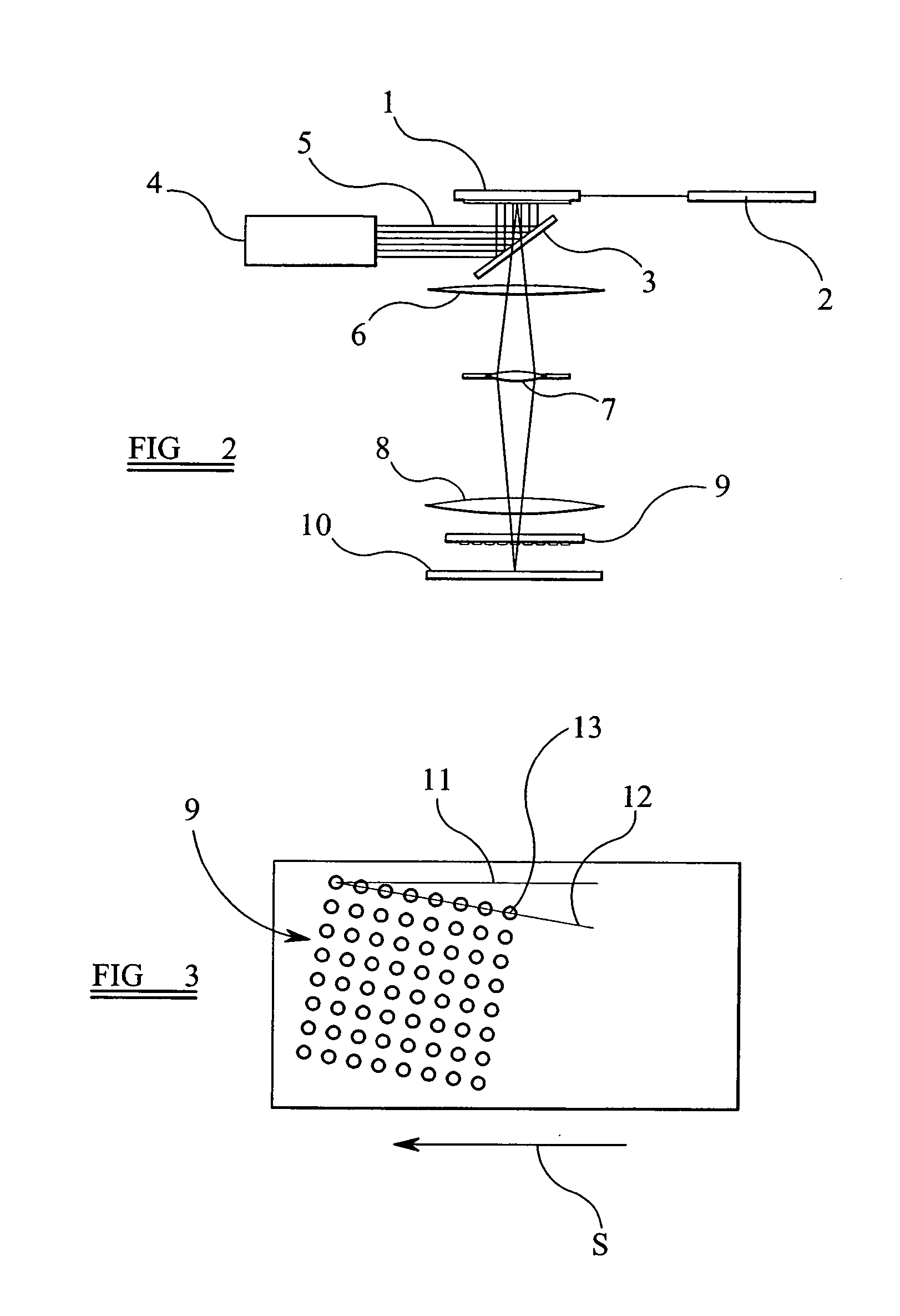

Lithographic apparatus and device manufacturing method

ActiveUS20060114446A1Minimize the numberLow data requirementsPhotomechanical apparatusPhotographic printingLight beamComputational physics

A lithographic method and apparatus used to pattern an object. An illumination system supplies a beam of radiation. An array of individually controllable elements patterns the beam. The patterned beam is projected by a projection system on to a substrate supported on a substrate table. Individual elements of the array are periodically addressed to load an image frame on to the array appropriate to the pattern to be imparted to the beam at any given instant in time taking into account the image to be projected onto the substrate. In any given frame loading operation, only those individual controllable elements that must change state are addressed to reduce the amount of data required to be transferred during the frame loading operation.

Owner:ASML NETHERLANDS BV

Method of High-Performance Flash Memory Data Transfer

ActiveUS20080019189A1Reduce power consumptionData skewRead-only memoriesDigital storageControl signalTransfer mode

A flash memory system including a flash memory device and a controller, operable according to an advanced data transfer mode is disclosed. The flash memory device is operable both in a “legacy” mode, in which read data is presented by the memory synchronously with each cycle of a read data strobe from the controller, and in which input data is latched by the memory synchronously with each cycle of a write data strobe from the controller. In the advanced mode, which can be initiated by the controller forwarding an initiation command to the memory, the flash memory itself sources the read data strobe and also a write data strobe that is out-of-phase relative to the read data strobe, and presents data synchronously with one of the edges of that read data strobe. In the advanced mode for a data write, the input data is presented by the controller synchronously with a selected edge of both the write data strobe and the read data strobe. The voltage swing of the data and control signals is reduced from conventional standards, to reduce power consumption.

Owner:SANDISK TECH LLC

Apparatus with an infrared sensor and magnetic near field communication properties for monitoring activity in a selected area

InactiveUS20100182153A1Reduce radiation levelsSave powerElectric testing/monitoringBurglar alarm short radiation actuationTransceiverElectronic communication

An electronic communication apparatus comprising an electronic communication apparatus comprising a control unit with a digital processor electronically coupled to an infrared sensor and to a wireless near field magnetic transceiver for communication with a portable electronic device. The infrared sensor is configured for detection of infrared radiation in a selected area in the vicinity of the detector and for creating an activity signal upon detection of movement of an infrared radiation source in the area. The activity mode implies causing the transceiver to transmit a wireless data signal as a request for receiving a wireless response signal with an ID from a portable electronic device.

Owner:YES GROUP

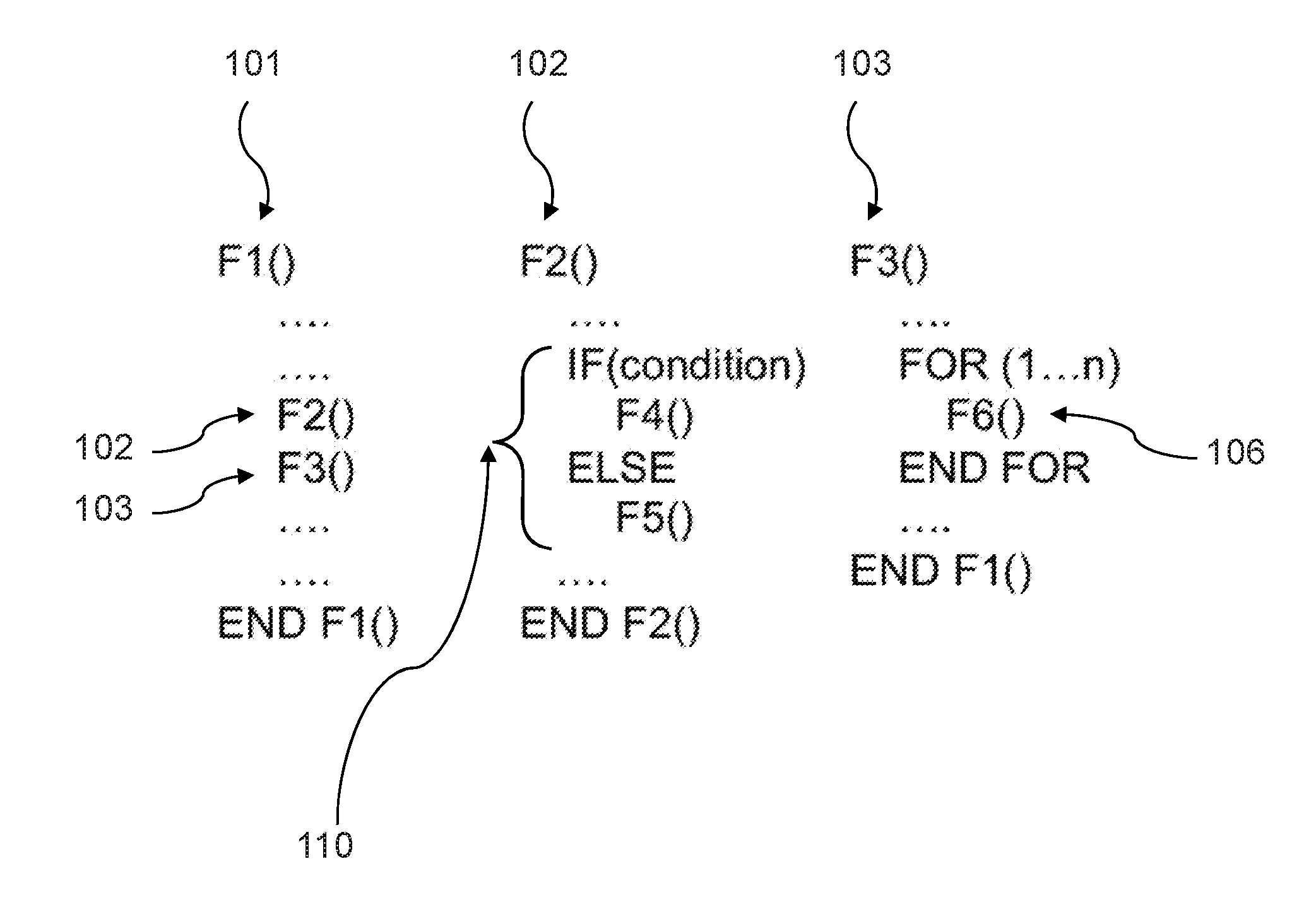

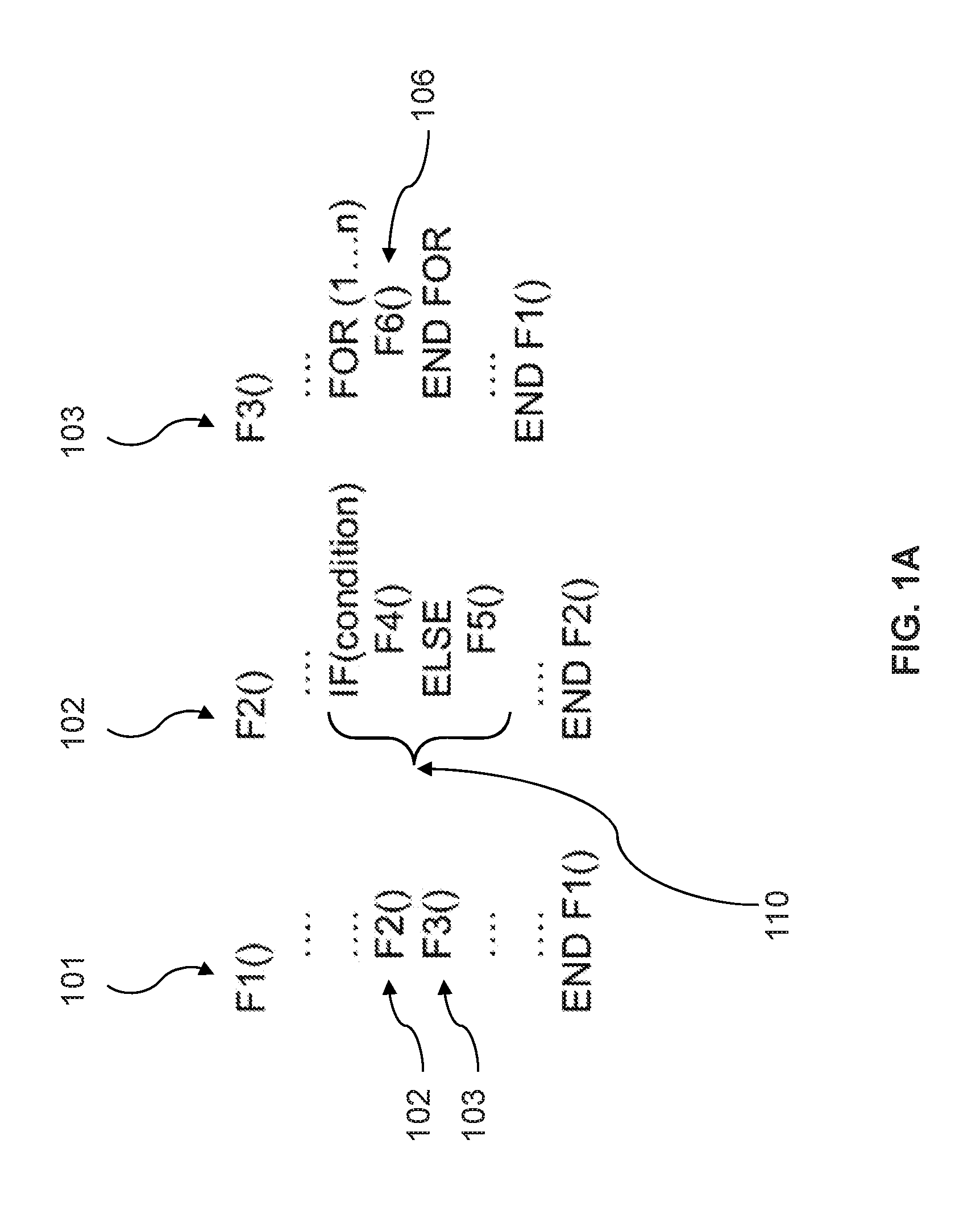

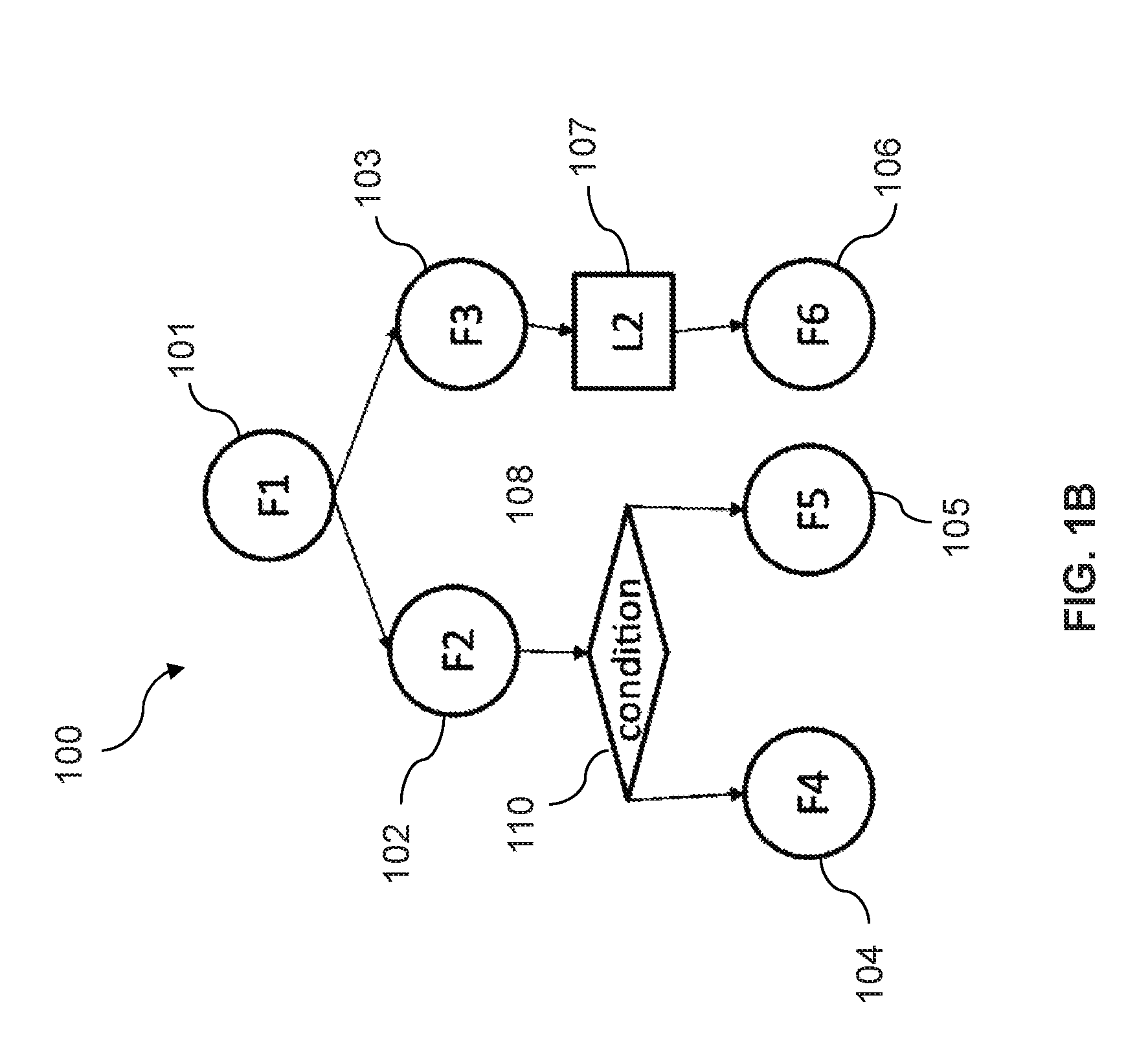

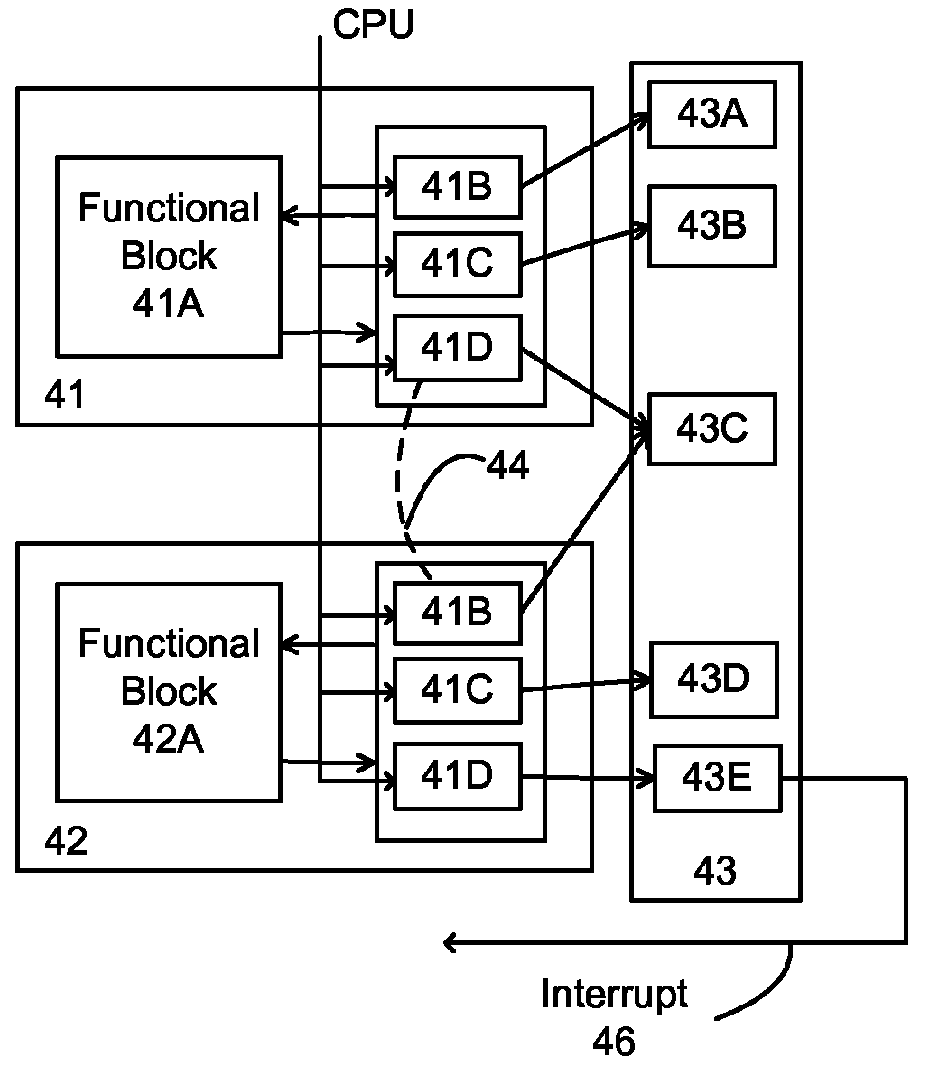

Global call control flow graph for optimizing software managed manycore architectures

InactiveUS20160170725A1Easy to useEfficient implementationSoftware engineeringProgram controlControl flowGraphics

Software Managed Manycore (SMM) architectures with scratch pad memory for reach core are a promising solution for scaling memory. In these architectures the code and data of the tasks mapped to the cores is explicitly managed by the compiler and often require inter-procedural information and analysis. But, a call graph of the program does not have enough information, and the Global CFG has too much information. Most new techniques informally define and use GCCFG (Global Call Control Flow Graph)—a whole program representation that succinctly captures the control-flow and function call information—to perform inter-procedural analysis. Constructing GCCFGs for several cases in common applications. The present disclosure provides unique graph transformations to formally and correctly construct GCCFGs for optimal compiler management of manycore systems.

Owner:ARIZONA STATE UNIVERSITY

Method of High-Performance Flash Memory Data Transfer

ActiveUS20070258295A1Reduce voltage swingReduce consumptionRead-only memoriesDigital storageData transmissionVoltage swing

A flash memory system including a flash memory device and a controller, operable according to an advanced data transfer mode is disclosed. The flash memory device is operable both in a “legacy” mode, in which read data is presented by the memory synchronously with each cycle of a read data strobe from the controller, and in which input data is latched by the memory synchronously with each cycle of a write data strobe from the controller. In the advanced mode, which can be initiated by the controller forwarding an initiation command to the memory, the flash memory itself sources the read data strobe, and presents data synchronously with both the falling and rising edges of that read data strobe. In the advanced mode, the input data is presented by the controller synchronously with both edges of the write data strobe. The voltage swing of the data and control signals is reduced from conventional standards, to reduce power consumption.

Owner:SANDISK TECH LLC

High-performance flash memory data transfer

ActiveUS7345926B2Minimize data transferMinimize data skewRead-only memoriesDigital storageControl signalTransfer mode

A flash memory system including a flash memory device and a controller, operable according to an advanced data transfer mode is disclosed. The flash memory device is operable both in a “legacy” mode, in which read data is presented by the memory synchronously with each cycle of a read data strobe from the controller, and in which input data is latched by the memory synchronously with each cycle of a write data strobe from the controller. In the advanced mode, which can be initiated by the controller forwarding an initiation command to the memory, the flash memory itself sources the read data strobe, and presents data synchronously with both the falling and rising edges of that read data strobe. In the advanced mode, the input data is presented by the controller synchronously with both edges of the write data strobe. The voltage swing of the data and control signals is reduced from conventional standards, to reduce power consumption.

Owner:SANDISK TECH LLC

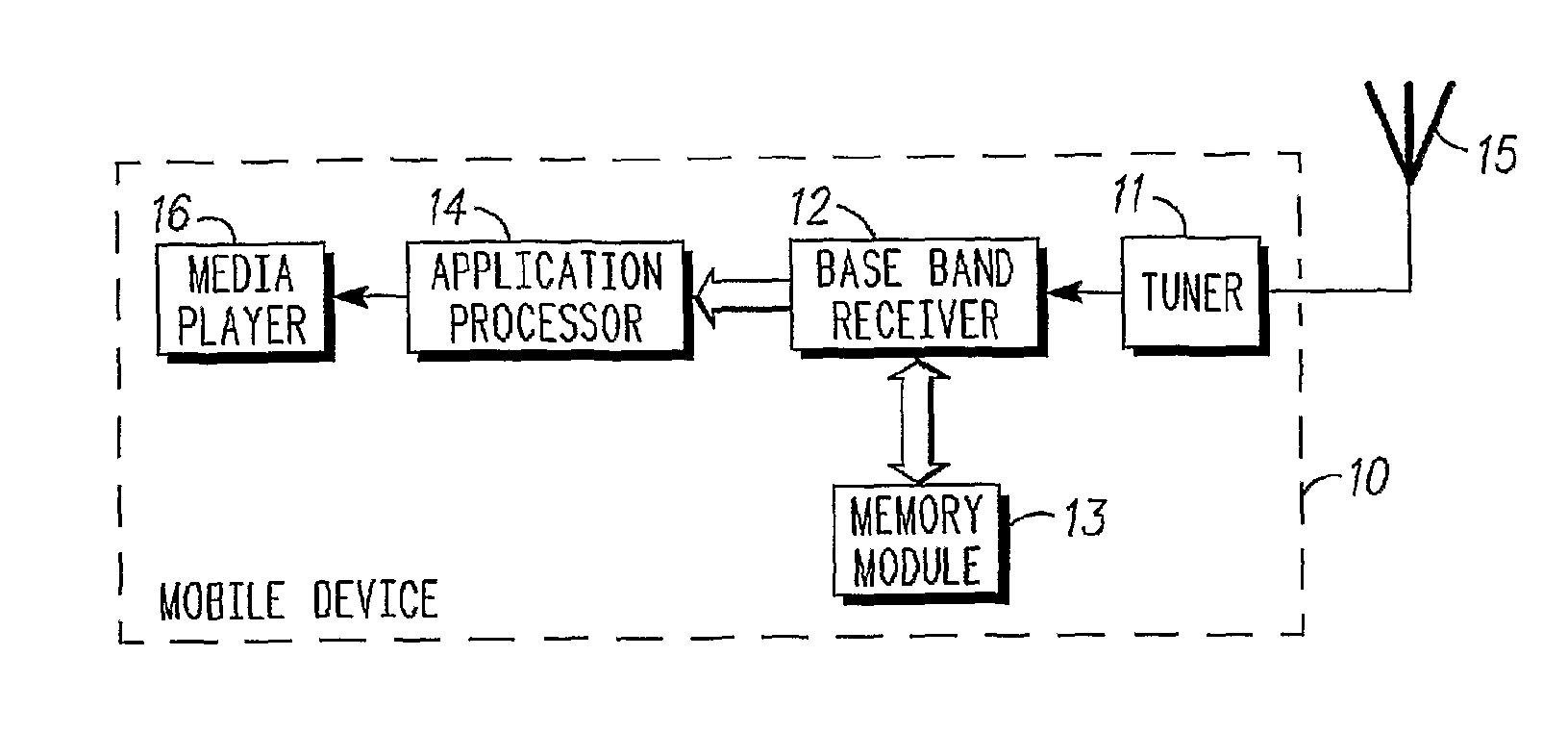

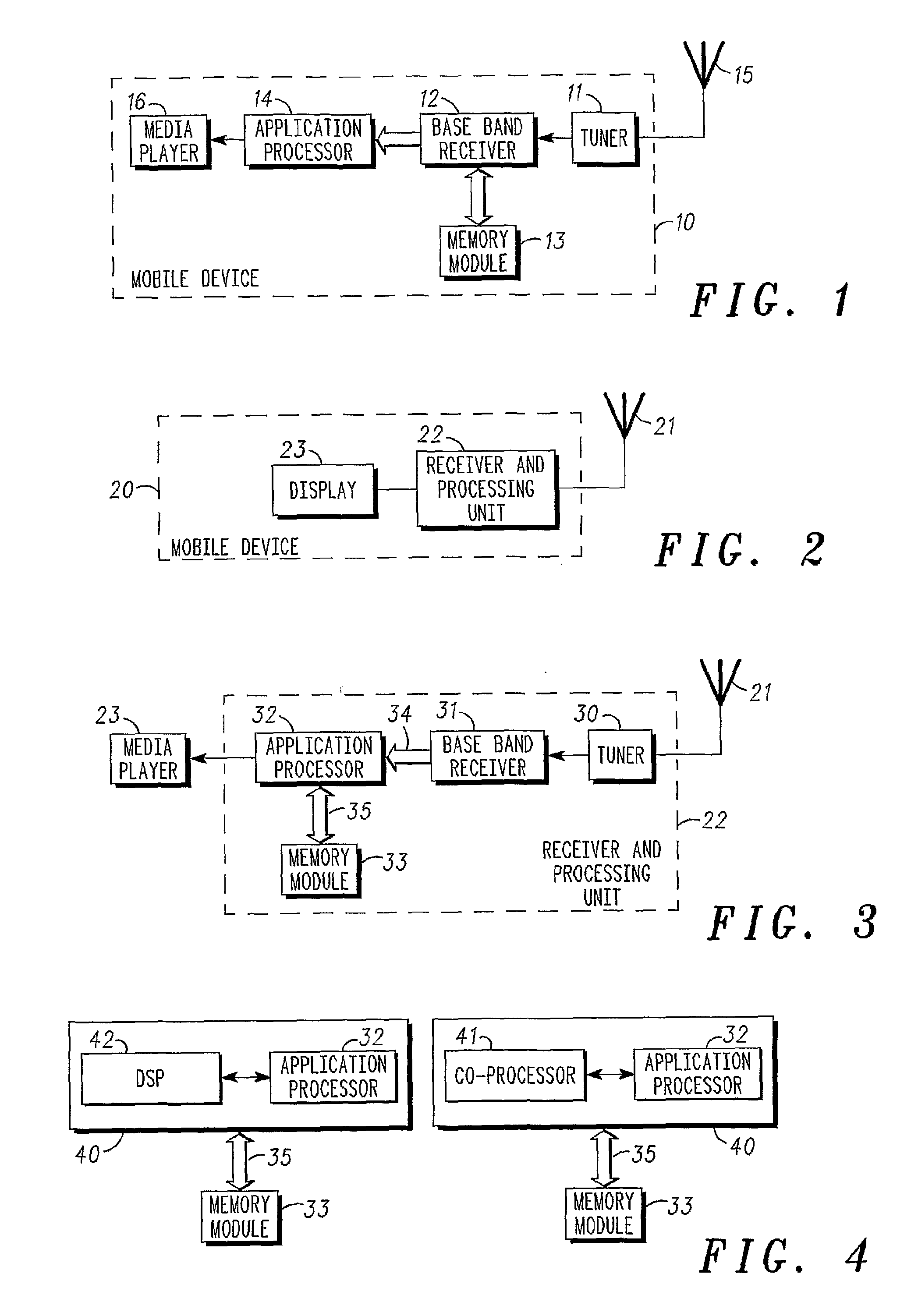

Wireless Mobile Device

ActiveUS20080009251A1Minimize data transferMinimizing transferTelevision system detailsCode conversionIntermediate frequencyRadio frequency signal

A wireless mobile device comprising a tuner for converting a received radio frequency signal to a base band signal or intermediate frequency signal and providing the base band signal or intermediate frequency signal to a receiver, wherein the receiver is arranged to provide received data associated with the base band signal or intermediate frequency signal to an application processor for storage in memory, wherein the application processor is arranged to extract the data from memory in an interleaved form and perform error correction on the interleaved data.

Owner:DIBCOM +1

Method of High-Performance Flash Memory Data Transfer

ActiveUS20070247933A1Reduce power consumptionData skewRead-only memoriesDigital storageData transmissionVoltage swing

A flash memory system including a flash memory device and a controller, operable according to an advanced data transfer mode is disclosed. The flash memory device is operable both in a “legacy” mode, in which read data is presented by the memory synchronously with each cycle of a read data strobe from the controller, and in which input data is latched by the memory synchronously with each cycle of a write data strobe from the controller. In the advanced mode, which can be initiated by the controller forwarding an initiation command to the memory, the flash memory itself sources the read data strobe at a higher frequency, for example at twice the frequency, of that available in the normal mode. In the advanced mode, the input data is presented by the controller synchronously with a higher frequency write data strobe than is available in the normal mode. The voltage swing of the data and control signals is reduced from conventional standards, to reduce power consumption.

Owner:SANDISK TECH LLC

Method of high-performance flash memory data transfer

ActiveUS7366028B2Data skewMinimize data transferRead-only memoriesDigital storageControl signalTransfer mode

A flash memory system including a flash memory device and a controller, operable according to an advanced data transfer mode is disclosed. The flash memory device is operable both in a “legacy” mode, in which read data is presented by the memory synchronously with each cycle of a read data strobe from the controller, and in which input data is latched by the memory synchronously with each cycle of a write data strobe from the controller. In the advanced mode, which can be initiated by the controller forwarding an initiation command to the memory, the flash memory itself sources the read data strobe, and presents data synchronously with both the falling and rising edges of that read data strobe. In the advanced mode, the input data is presented by the controller synchronously with both edges of the write data strobe. The voltage swing of the data and control signals is reduced from conventional standards, to reduce power consumption.

Owner:SANDISK TECH LLC

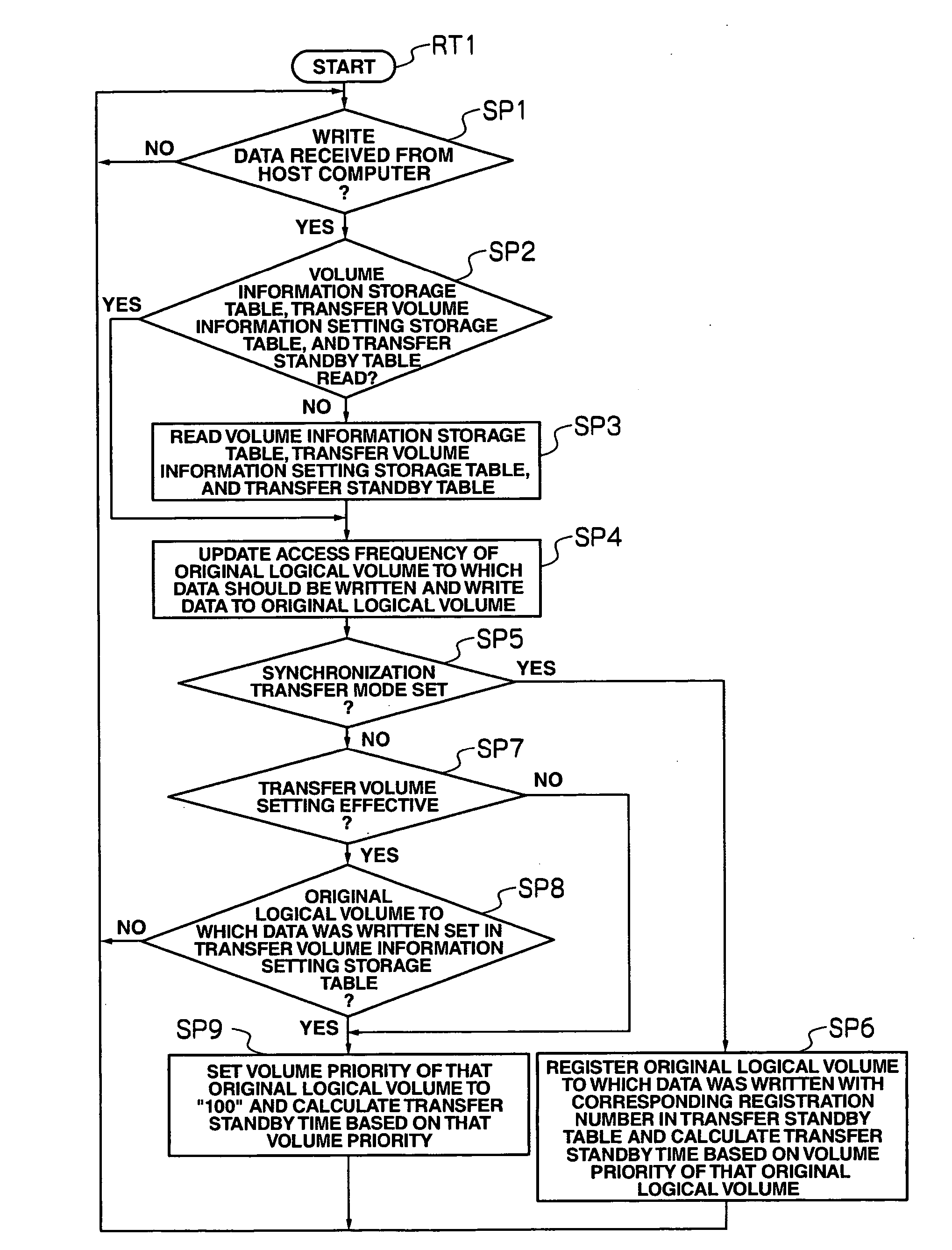

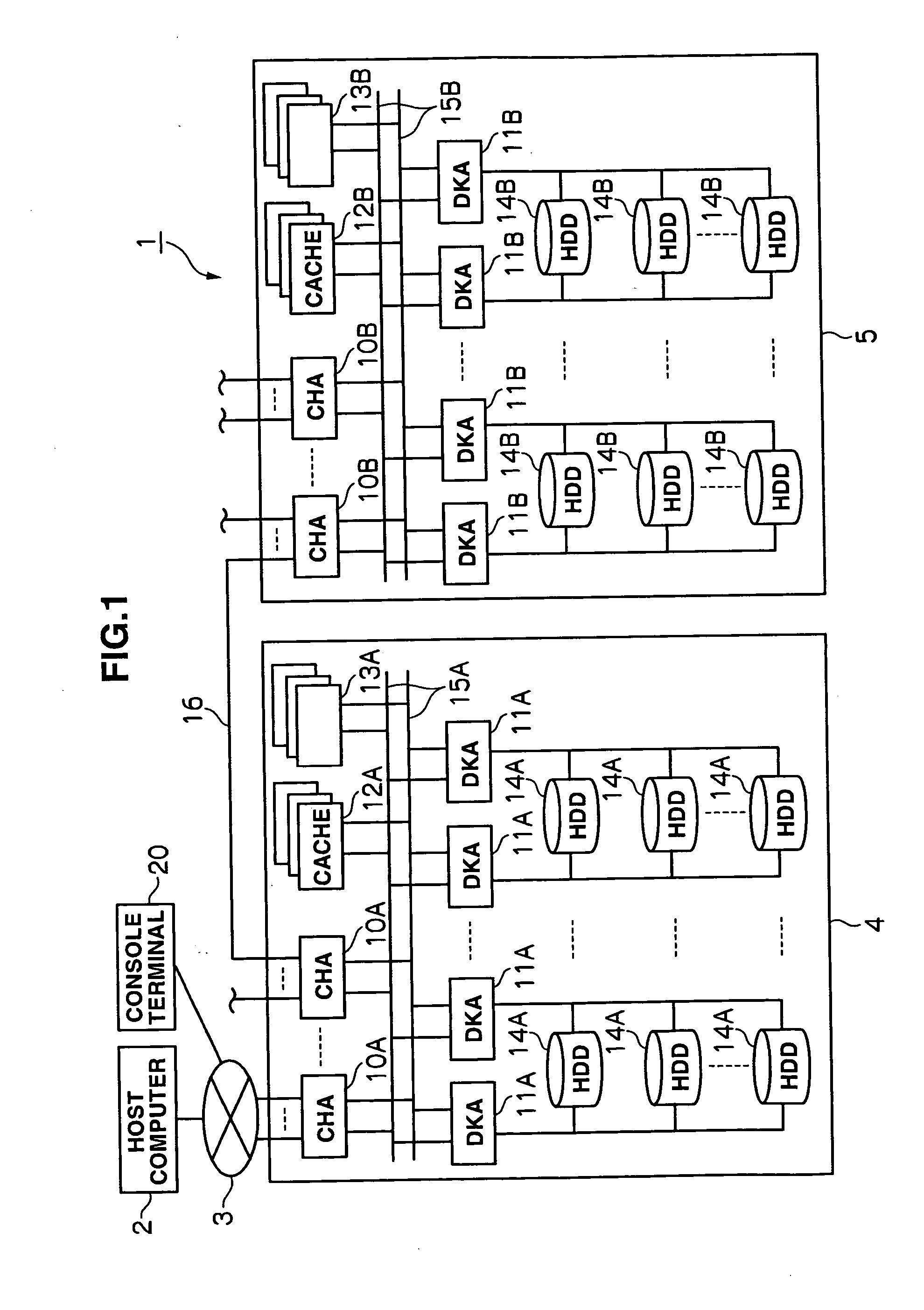

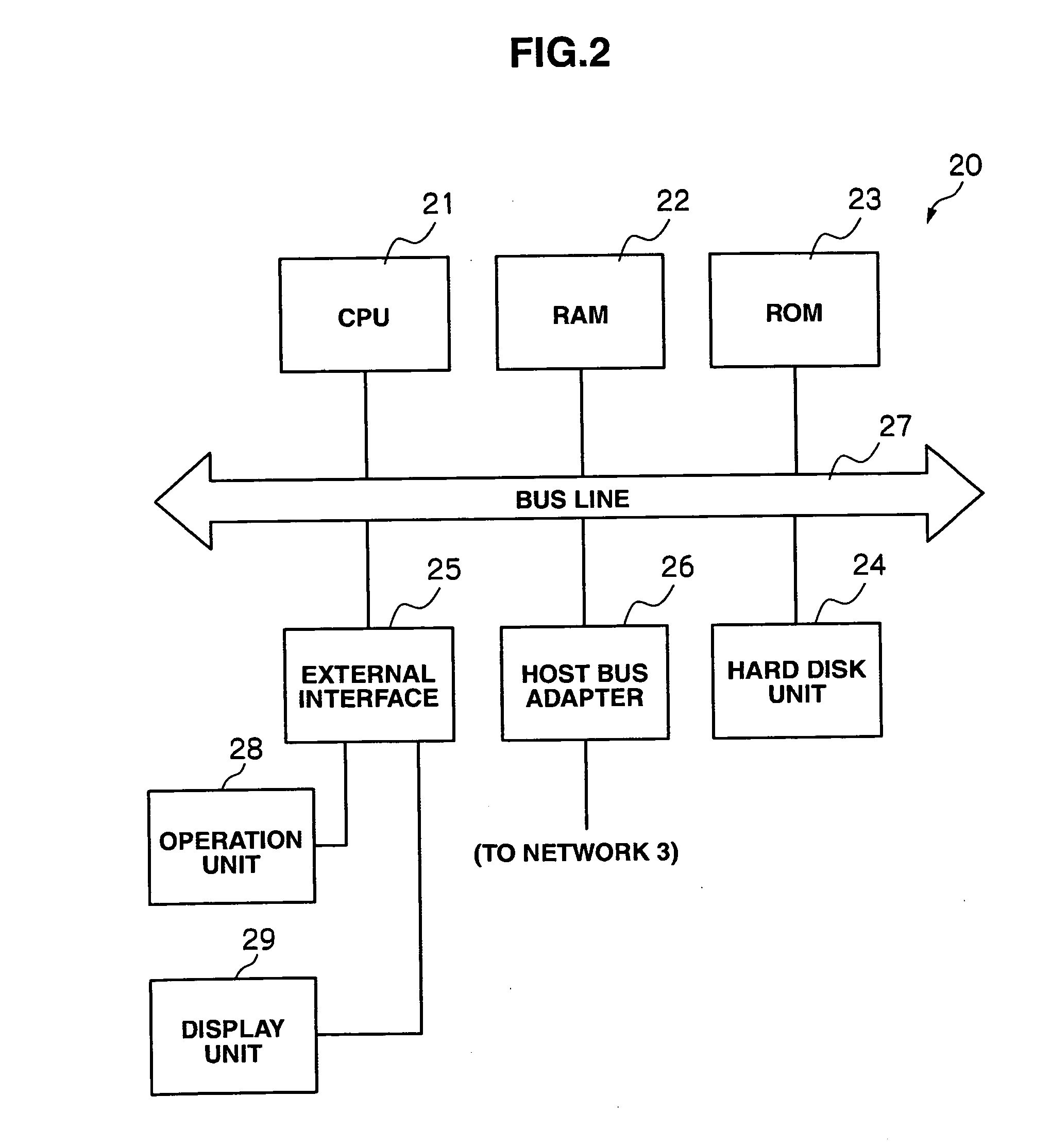

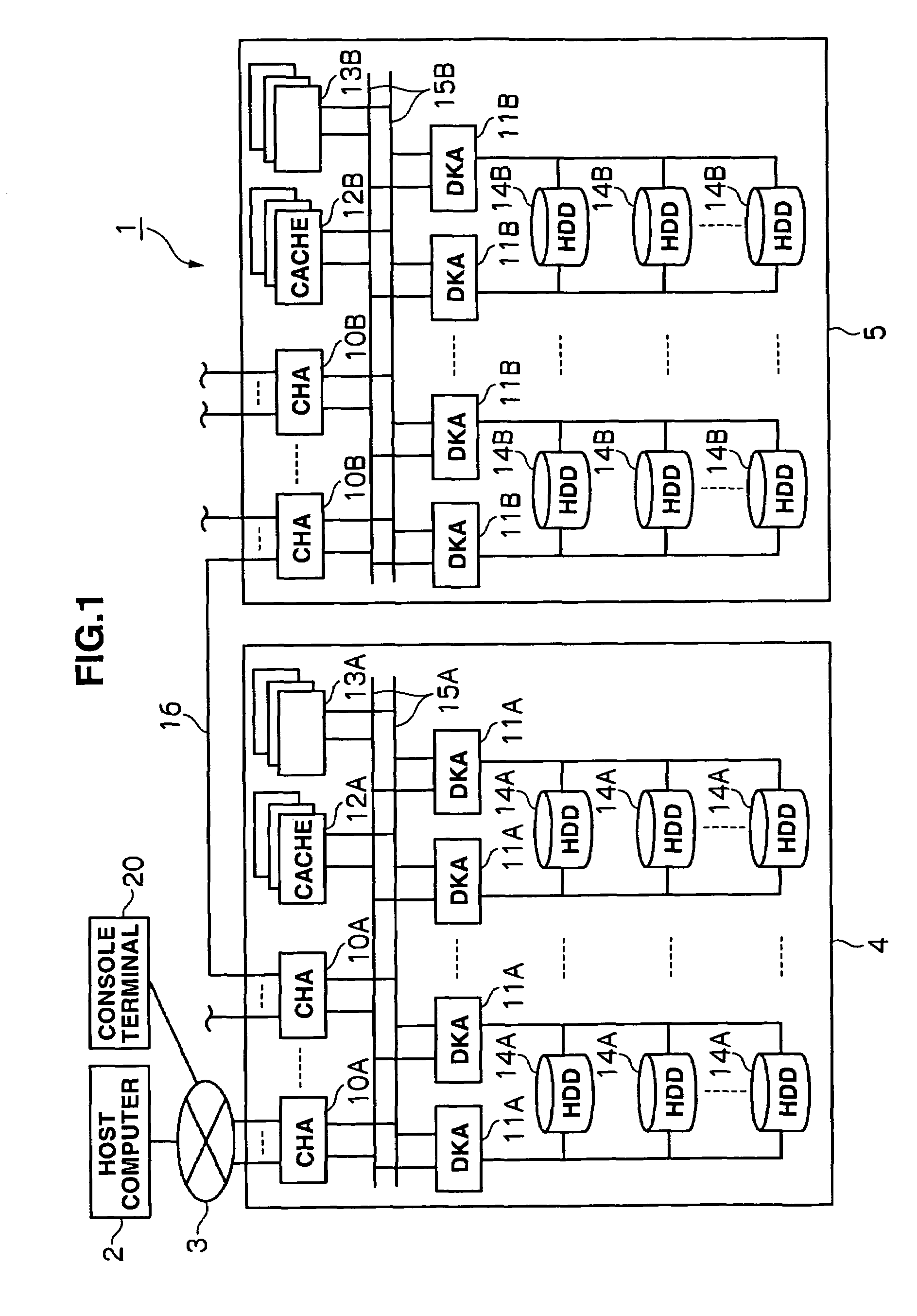

Storage system, data transfer method, and program

InactiveUS20070050545A1Highly-reliable data backupRaise priorityMemory loss protectionError detection/correctionPriority settingDisk array

The present invention suggests a storage system capable of realizing highly reliable data back-up. The storage system includes: a first disk array apparatus for providing first volumes for storing data sent from a host system; a second disk array apparatus for providing second volumes for storing back-up data of the first volumes; and a console terminal for operating the first disk array apparatus. The console terminal is equipped with a setting unit for setting a priority for each first volume in accordance with an external command. The first disk array apparatus is equipped with: a storage unit for storing the priorities set by the priority setting unit; and a transfer unit for reading the priorities from the storage unit upon receiving the data and transferring the data stored in the first volumes to the second volumes of the second disk array apparatus in order of descending priority of the first volumes that store the data.

Owner:HITACHI LTD

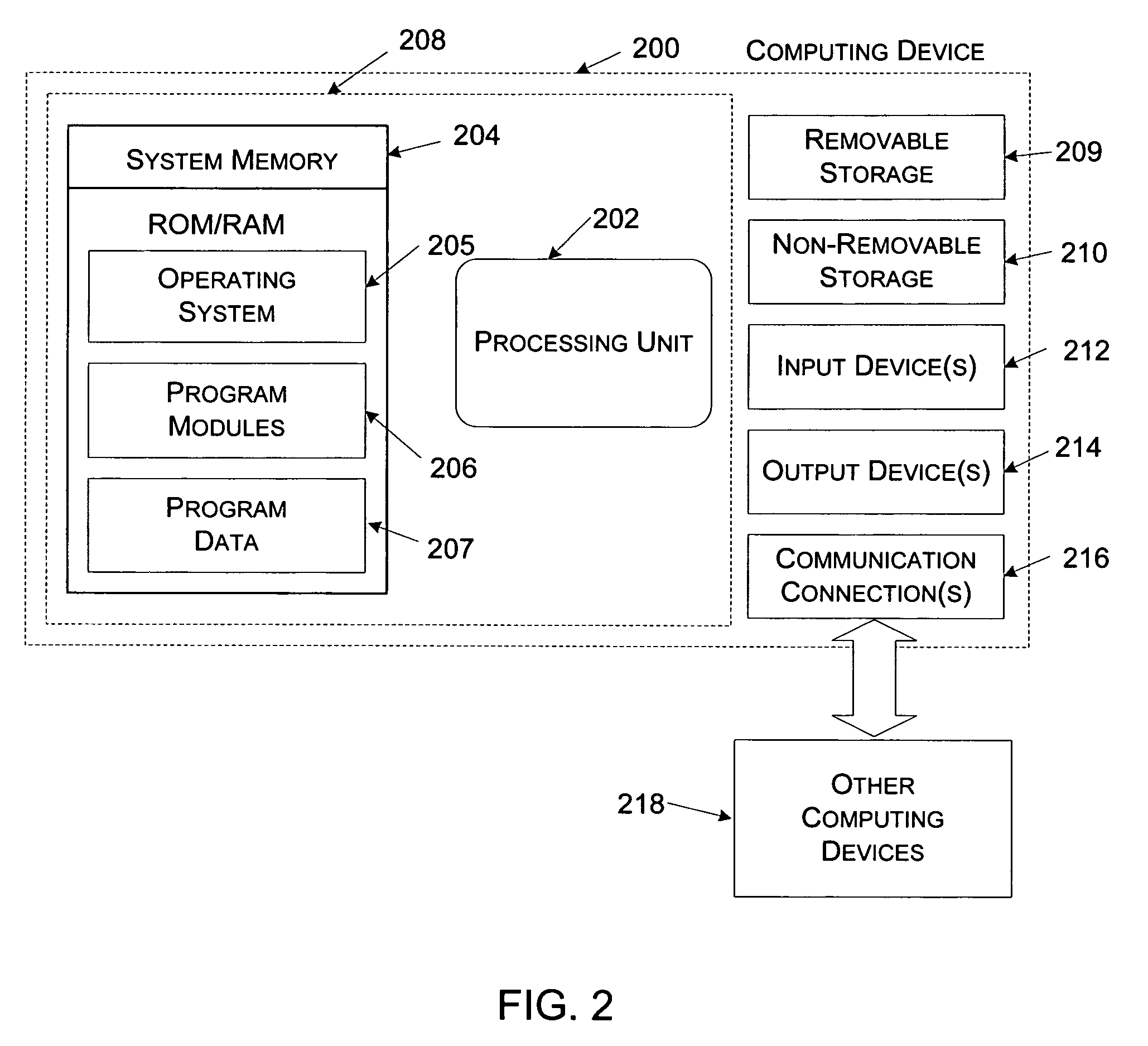

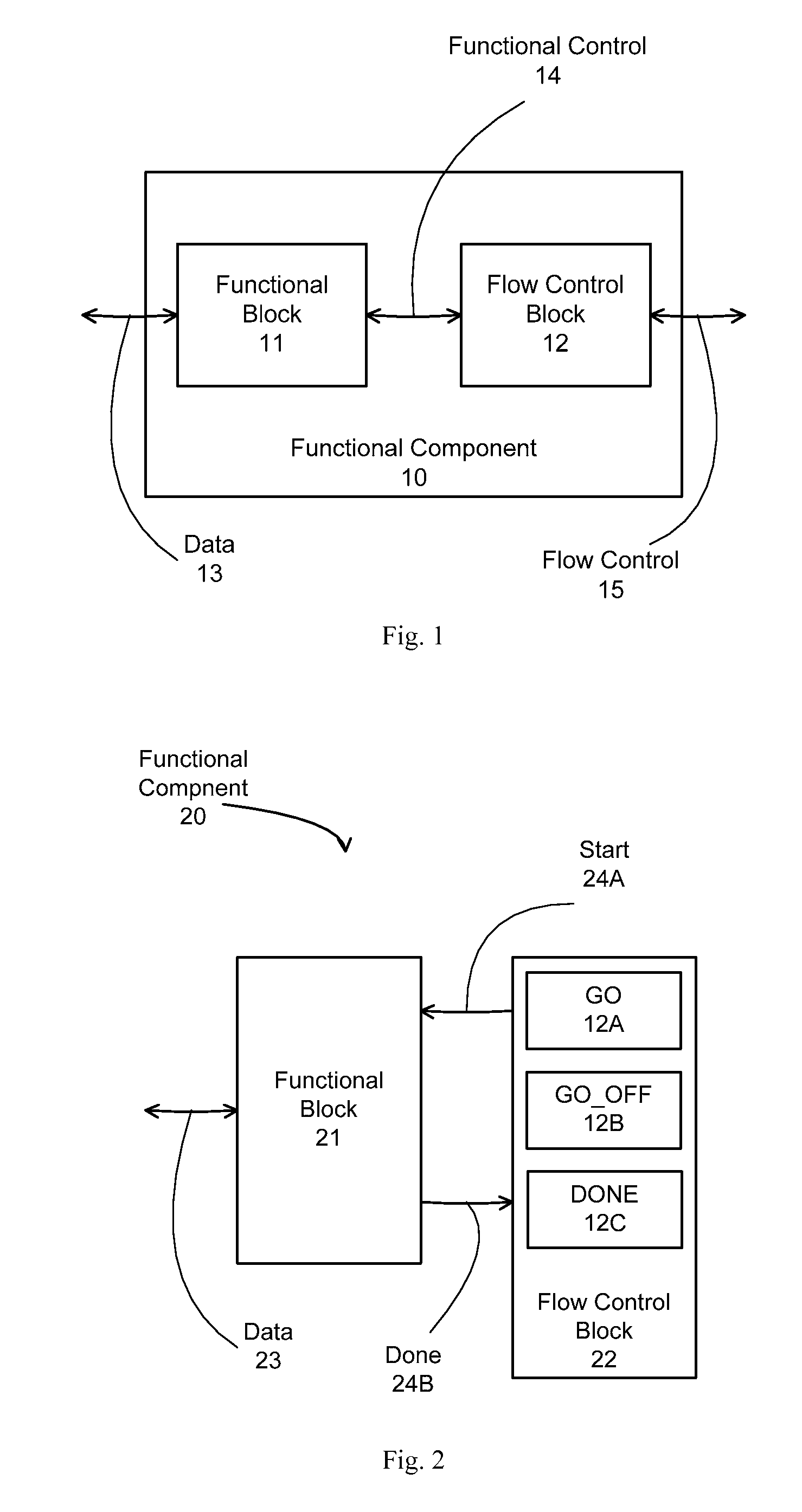

Re-configurable bus fabric for integrated circuits

InactiveUS20090083460A1Efficient memory data managementEfficient data transferEnergy efficient ICTDigital computer detailsEmbedded systemData transmission

The present invention relates to a flexible and reconfigurable bus fabric for microelectronic processing units, which can offer efficient memory data management, together with efficient data transfer and relieving data transfer congestion in an integrated circuit. In an embodiment, the present reconfigurable bus fabric comprises a multistate intersection between two data buses. Preferably, the multistate intersection comprises at least two states, a connecting state connecting the two data buses, and a disconnecting state disconnecting the two data buses. The multistate intersection provides a reconfigurable bus fabric, allowing different connection configuration for the data buses. This reconfigurable bus fabric offers soft-configurability and soft-reconfigurability, using software programming to arrange the circuits' interconnections. Other configurations are also disclosed in exemplary embodiments.

Owner:MITRA HIRAK +3

Efficient algorithm for finding candidate objects for remote differential compression

ActiveUS7613787B2Minimize data transferImprove efficiencyDigital data information retrievalMultiple digital computer combinationsData transmissionEfficient algorithm

The present invention finds candidate objects for remote differential compression. Objects are updated between two or more computing devices using remote differential compression (RDC) techniques such that required data transfers are minimized. An algorithm provides enhanced efficiencies for allowing the receiver to locate a set of objects that are similar to the object that needs to be transferred from the sender. Once this set of similar objects has been found, the receiver may reuse any chunks from these objects during the RDC algorithm.

Owner:MICROSOFT TECH LICENSING LLC

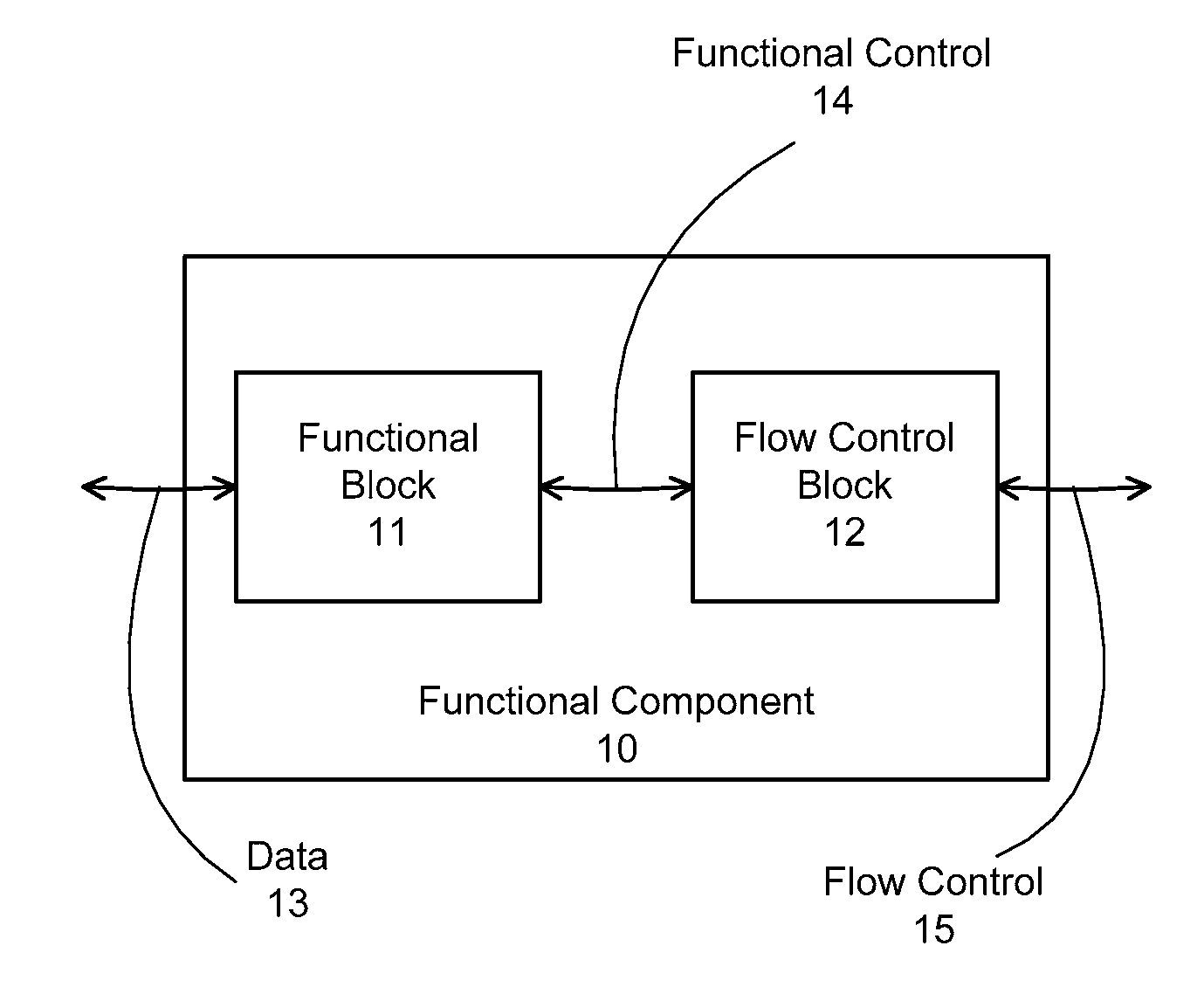

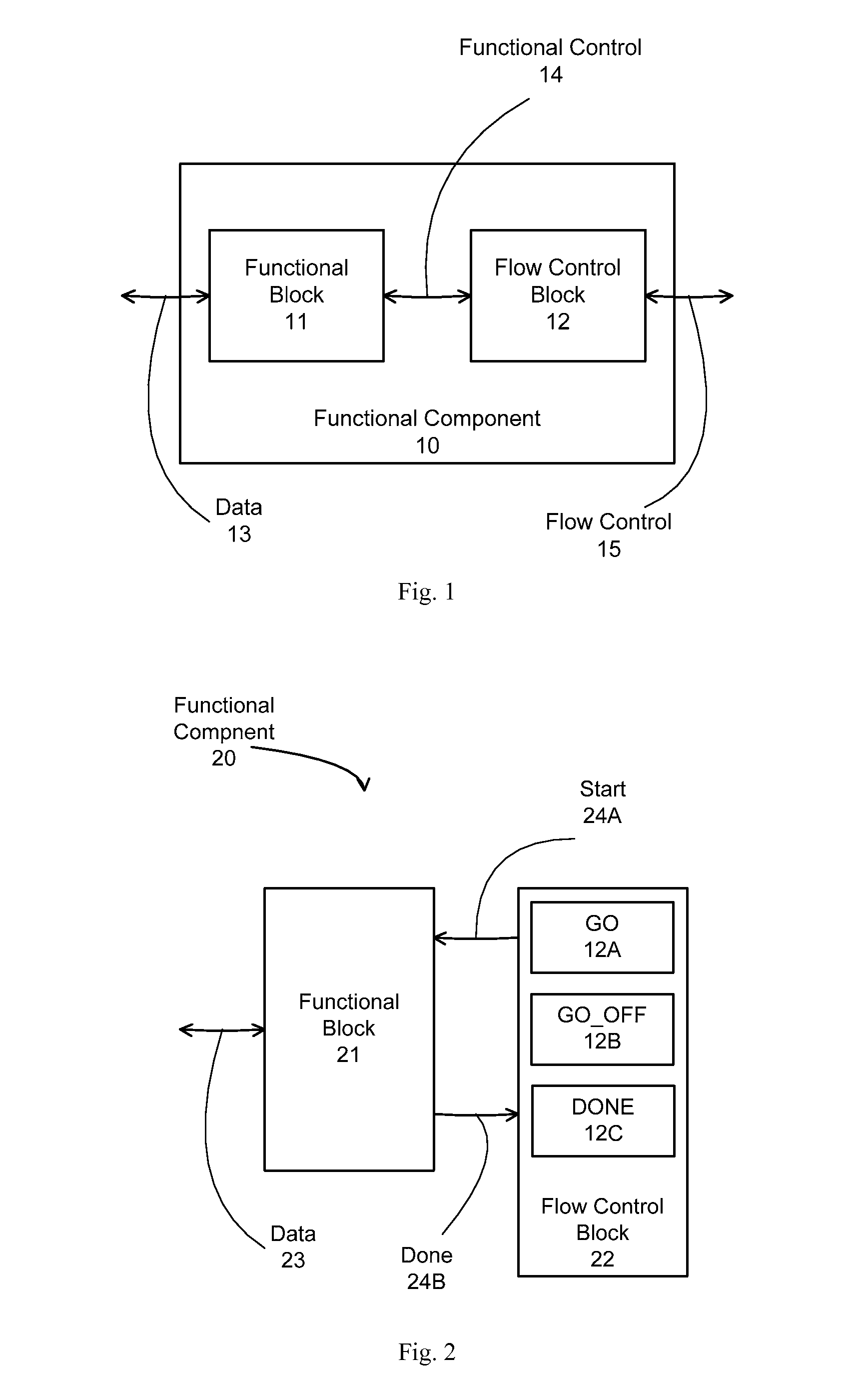

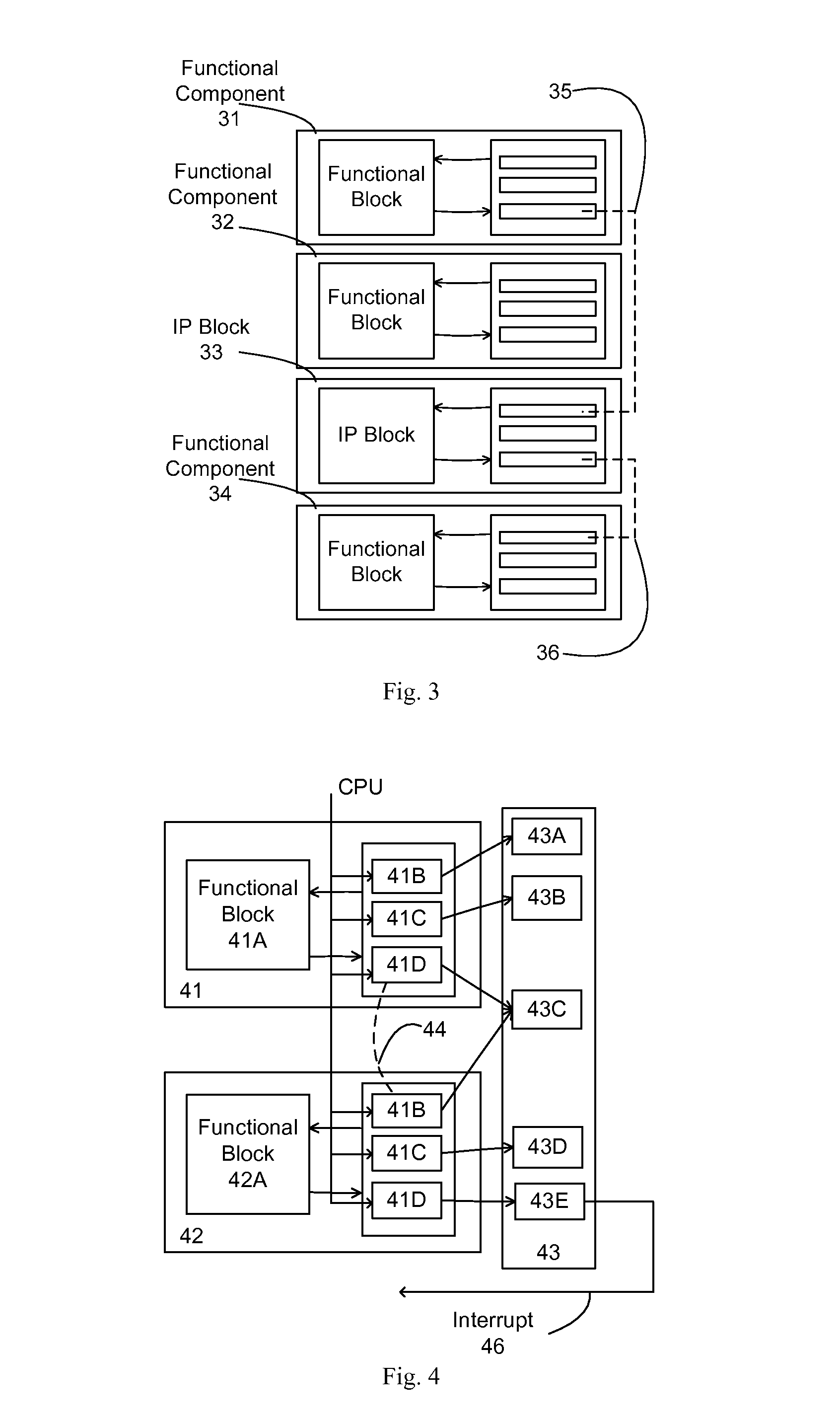

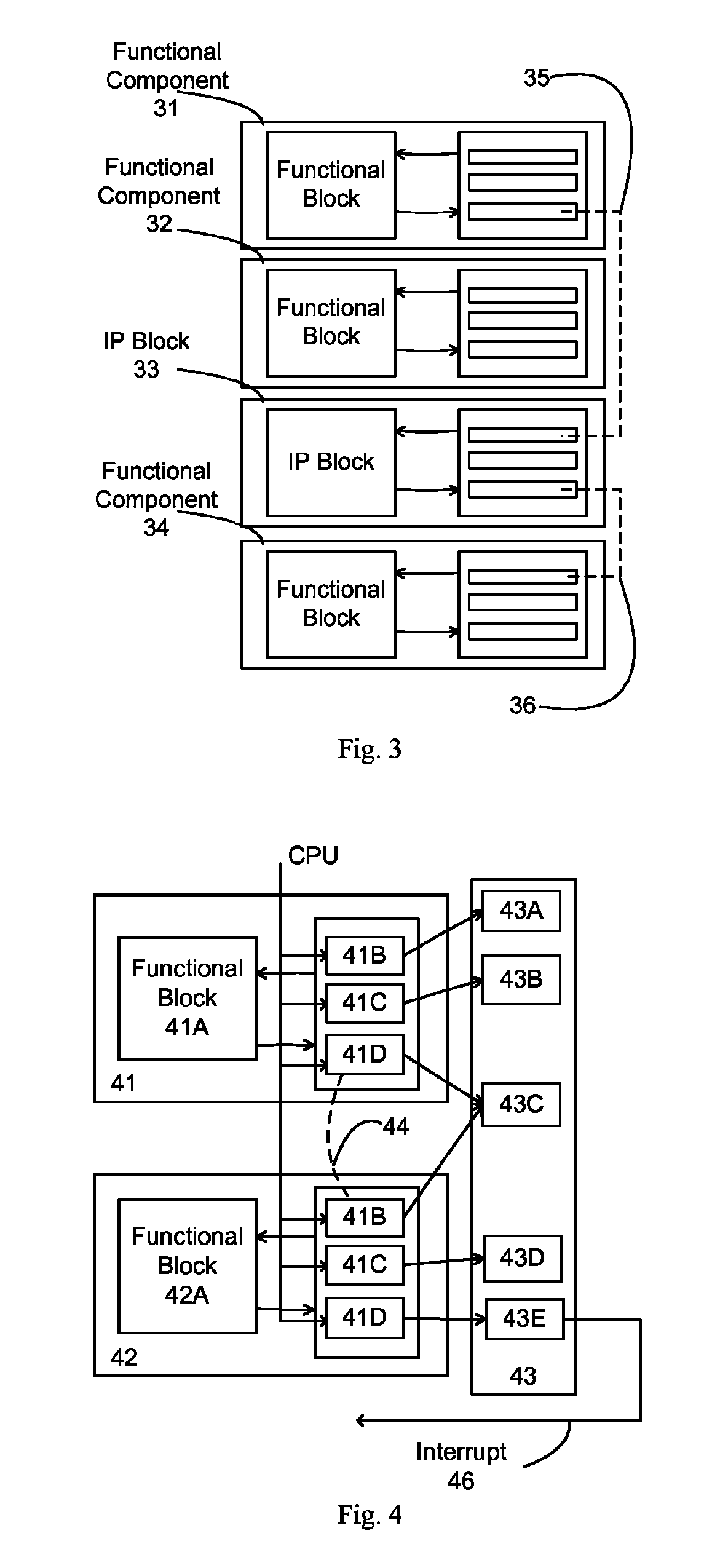

System and methods for connecting multiple functional components

InactiveUS7822897B2Efficient managementRelieving data transfer congestion in an integrated circuitEnergy efficient ICTDigital computer detailsReconfigurabilityInterconnection

The present invention relates to a flexible and reconfigurable bus fabric for microelectronic processing units, which can offer efficient memory data management, together with efficient data transfer and relieving data transfer congestion in an integrated circuit. In an embodiment, the present reconfigurable bus fabric comprises a multistate intersection between two data buses. Preferably, the multistate intersection comprises at least two states, a connecting state connecting the two data buses, and a disconnecting state disconnecting the two data buses. The multistate intersection provides a reconfigurable bus fabric, allowing different connection configuration for the data buses. This reconfigurable bus fabric offers soft-configurability and soft-reconfigurability, using software programming to arrange the circuits' interconnections. Other configurations are also disclosed in exemplary embodiments.

Owner:MITRA HIRAK +3

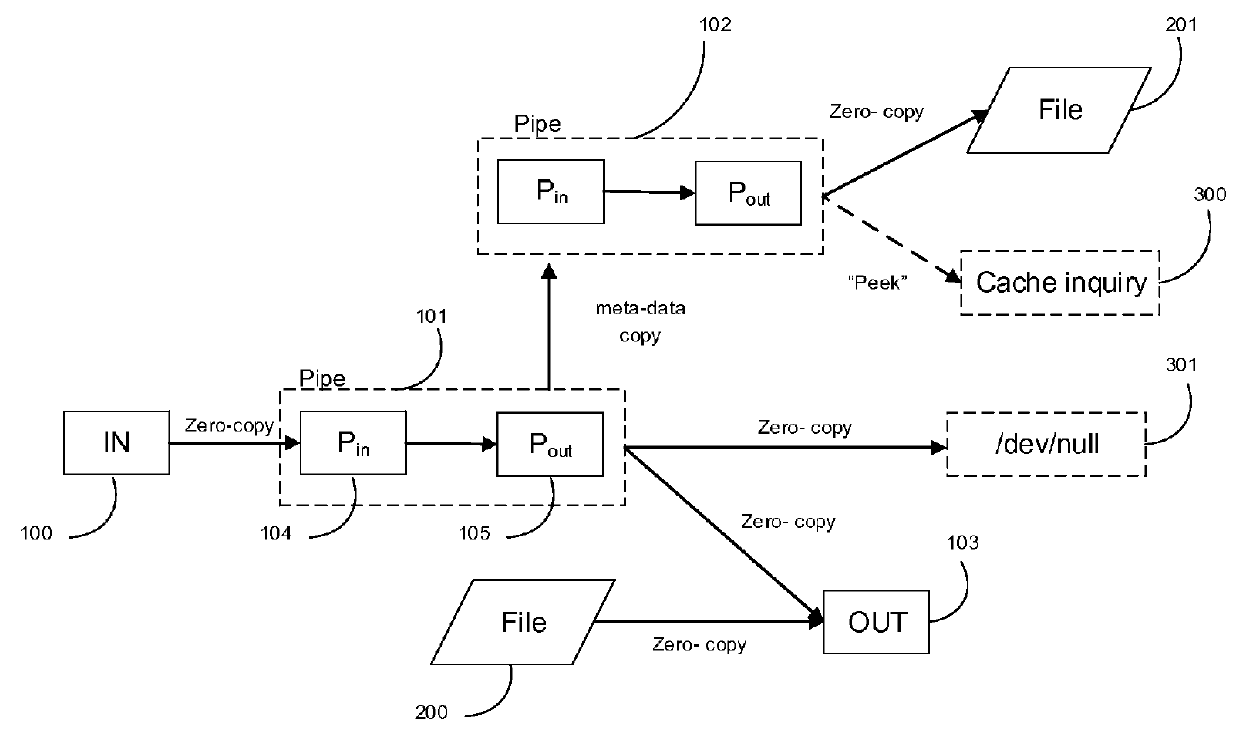

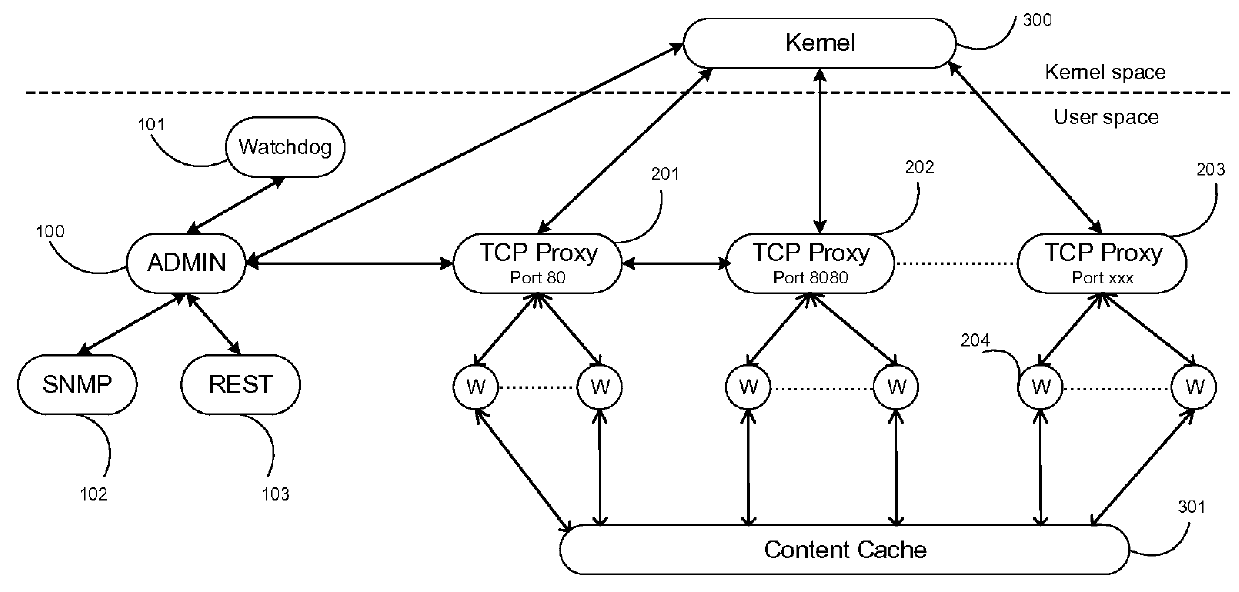

Optimizing stream-mode content cache

ActiveUS20160036879A1Delay minimizationZero copyingProgram initiation/switchingMultiple digital computer combinationsCache accessMulti core computing

A system and method, called ADD (adaptive data descriptor) and FP (functional proximity), optimizes data transfer between inbound and outbound streams for TCP or other data transfer mechanisms. ADD minimizes data copying in the steam mode, while allowing simultaneous reading from the inbound stream, and writing into the outbound stream from a stored file. ADD and FP jointly minimize total latency in stream-mode data transfer, with or without caching, over multi-core computing systems.FP assigns processes in a multi-core computing system to minimize cache misses and cache access in shared on-chip caches. FP also assigns threads in a TCP splicing box that provides TCP splicing between a plurality of senders and a plurality of receivers, by assigning one thread or 2 threads per TCP connection. The threads are assigned to thread groups so that each thread group is assigned to a single CPU or core. This assignment maximizes cache hits in shared on-chip caches in a multi-core computing system.

Owner:BADU NETWORKS

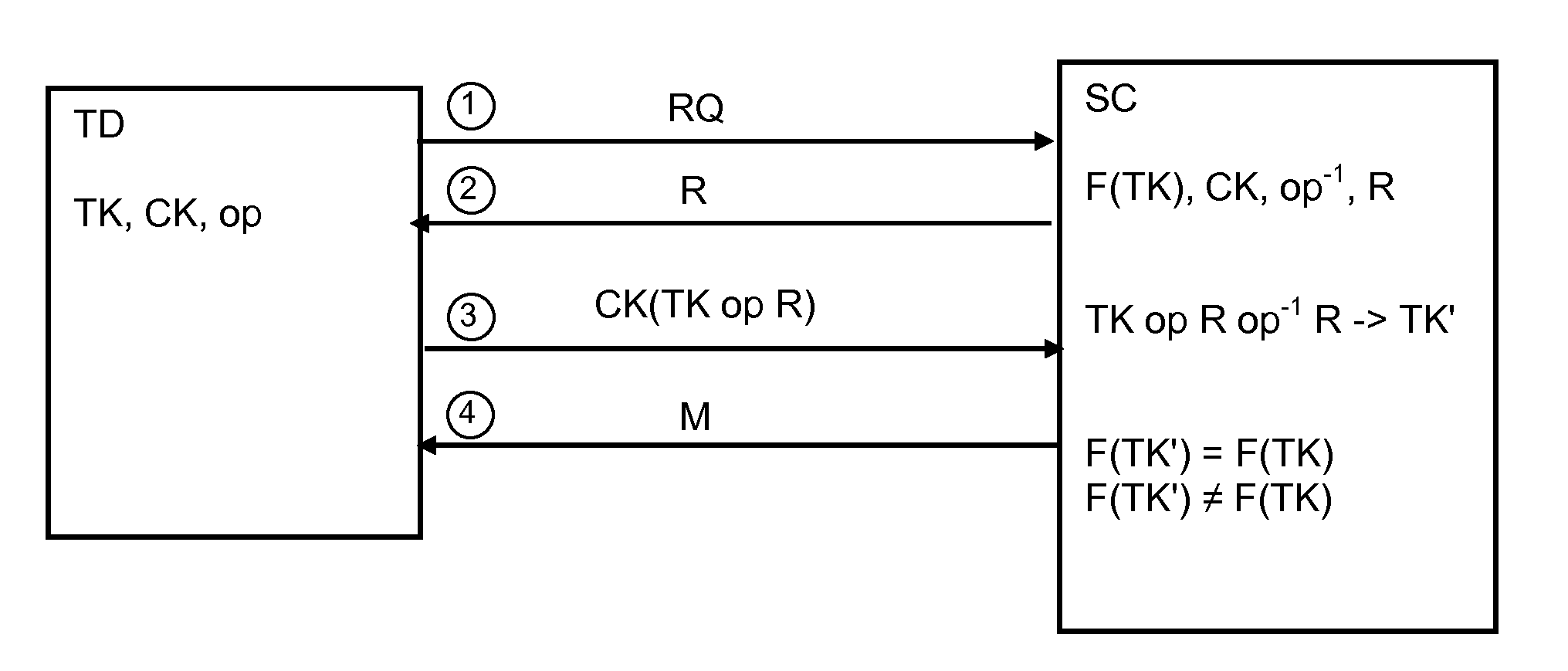

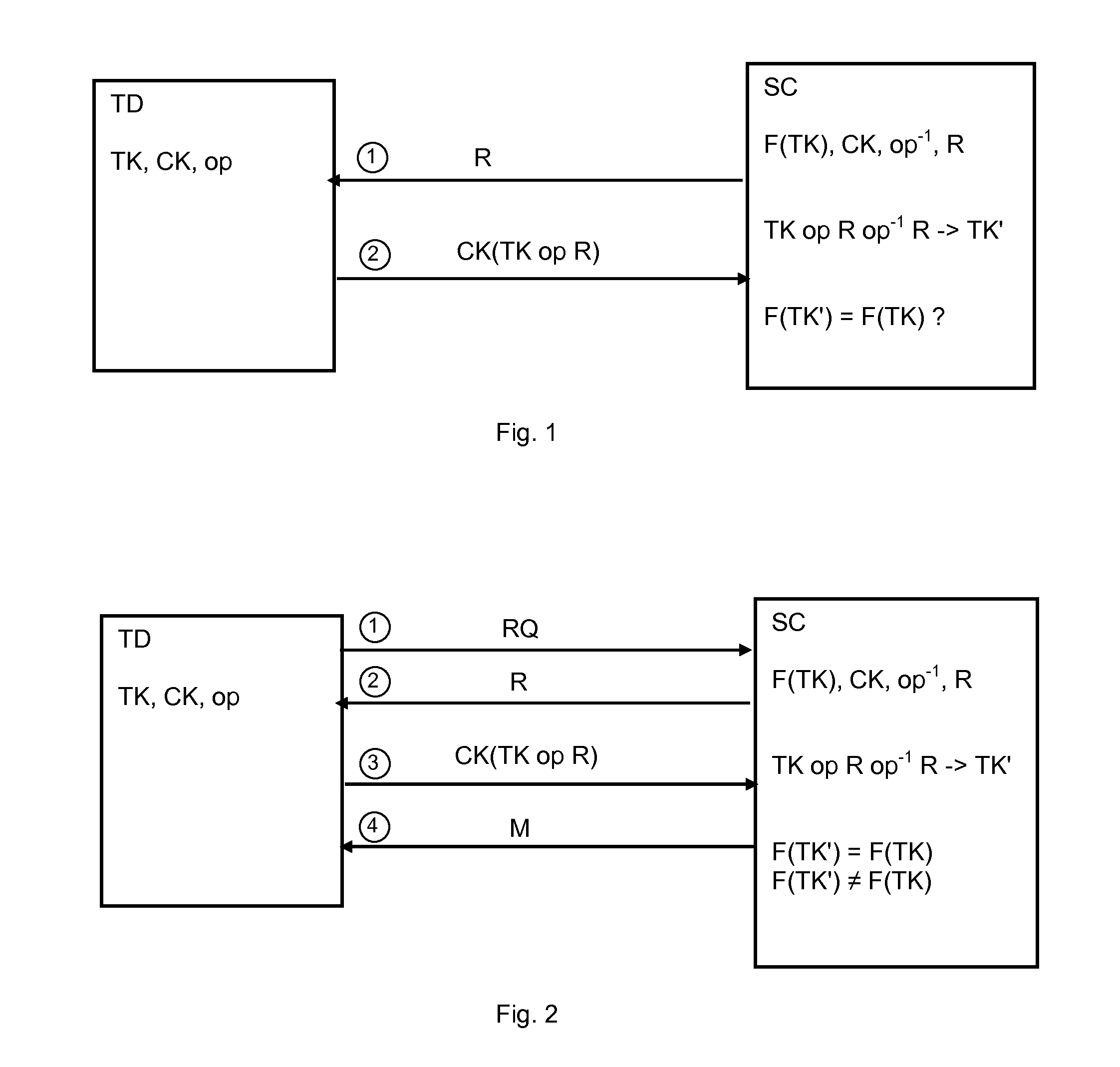

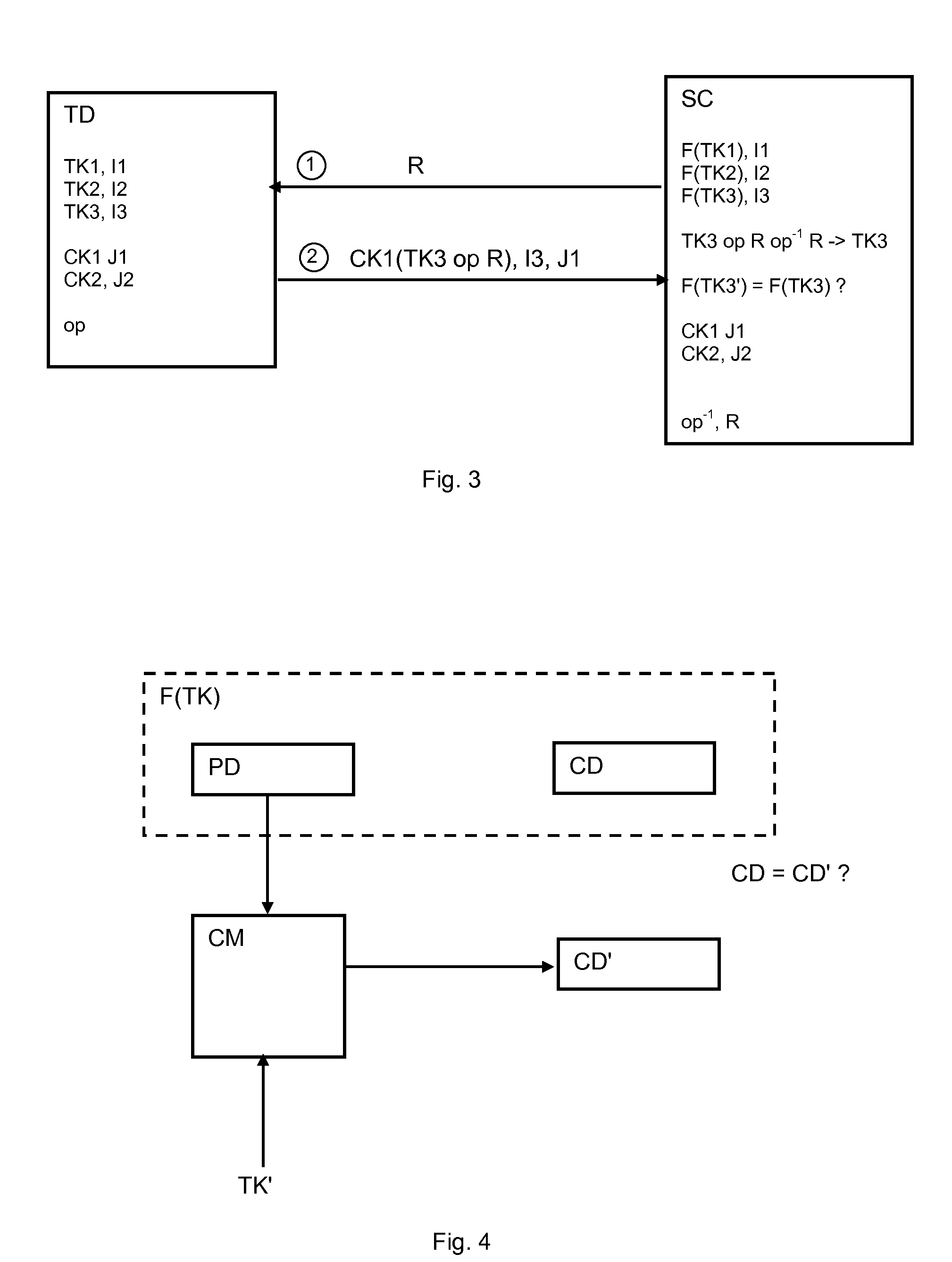

Method for authenticating access to a secured chip by test device

InactiveUS20120069991A1Minimize data transferRandom number generatorsMultiple keys/algorithms usageComputer hardwareOne-way function

A method for authenticating access to a secured chip SC by a test device TD, the test device storing at least one common key CK and one test key TK, the secured chip SC storing the same common key CK and a reference digest F(TK) resulting from a cryptographic function on the test key TK, the method comprising the steps of:—receiving, by the test device TD, a challenge R produced by the secured chip SC,—combining, by the test device TD, the received challenge R with the test key TK by applying a bidirectional mathematical operation (op), encrypting the result (TK op R) with the common key CK, obtaining a cryptogram CK(TK op R),—sending the cryptogram CK(TK op R) to the secured chip SC—decrypting, by the secured chip SC, the cryptogram CK(TK op R) with the common key CK, obtaining an image key TK′ representing the test key TK by applying, with the challenge R, the reverse operation (op-1) of the mathematical operation (op) previously used by the test device TD,—calculating an expected digest F(TK′) of the image key TK′ with a cryptographic one-way function,—verifying validity by comparing the expected digest F(TK′) with the reference digest F(TK),—if the result of the comparison between the digest F(TK′) of the image key TK′ and the reference digest F(TK) is positive, accessing, by the test device TD, the secure chip SC in a test mode.

Owner:NAGRAVISION SA

Method of high-performance flash memory data transfer

ActiveUS7525855B2Data skewMinimize data transferRead-only memoriesDigital storageControl signalTransfer mode

A flash memory system includes a flash memory device and a controller, operable according to an advanced data transfer mode. The flash memory device is operable both in a “legacy” mode, in which read data is presented by the memory synchronously with each cycle of a read data strobe from the controller, and in which input data is latched by the memory synchronously with each cycle of a write data strobe from the controller. In the advanced mode, which can be initiated by the controller forwarding an initiation command to the memory, the flash memory itself sources the read data strobe at a higher frequency, for example at twice the frequency, of that available in the normal mode. In the advanced mode, the input data is presented by the controller synchronously with a higher frequency write data strobe than is available in the normal mode. The voltage swing of the data and control signals is reduced from conventional standards, to reduce power consumption.

Owner:SANDISK TECH LLC

High-Performance Flash Memory Data Transfer

ActiveUS20070245065A1Reduce power consumptionMinimize data transferRead-only memoriesDigital storageControl signalTransfer mode

A flash memory system including a flash memory device and a controller, operable according to an advanced data transfer mode is disclosed. The flash memory device is operable both in a “legacy” mode, in which read data is presented by the memory synchronously with each cycle of a read data strobe from the controller, and in which input data is latched by the memory synchronously with each cycle of a write data strobe from the controller. In the advanced mode, which can be initiated by the controller forwarding an initiation command to the memory, the flash memory itself sources the read data strobe, and presents data synchronously with both the falling and rising edges of that read data strobe. In the advanced mode, the input data is presented by the controller synchronously with both edges of the write data strobe. The voltage swing of the data and control signals is reduced from conventional standards, to reduce power consumption.

Owner:SANDISK TECH LLC

High-Performance Flash Memory Data Transfer

ActiveUS20070247934A1Reduce power consumptionMinimize data transferRead-only memoriesDigital storageData transmissionVoltage swing

A flash memory system including a flash memory device and a controller, operable according to an advanced data transfer mode is disclosed. The flash memory device is operable both in a “legacy” mode, in which read data is presented by the memory synchronously with each cycle of a read data strobe from the controller, and in which input data is latched by the memory synchronously with each cycle of a write data strobe from the controller. In the advanced mode, which can be initiated by the controller forwarding an initiation command to the memory, the flash memory itself sources the read data strobe at a higher frequency, for example at twice the frequency, of that available in the normal mode. In the advanced mode, the input data is presented by the controller synchronously with a higher frequency write data strobe than is available in the normal mode. The voltage swing of the data and control signals is reduced from conventional standards, to reduce power consumption.

Owner:SANDISK TECH LLC

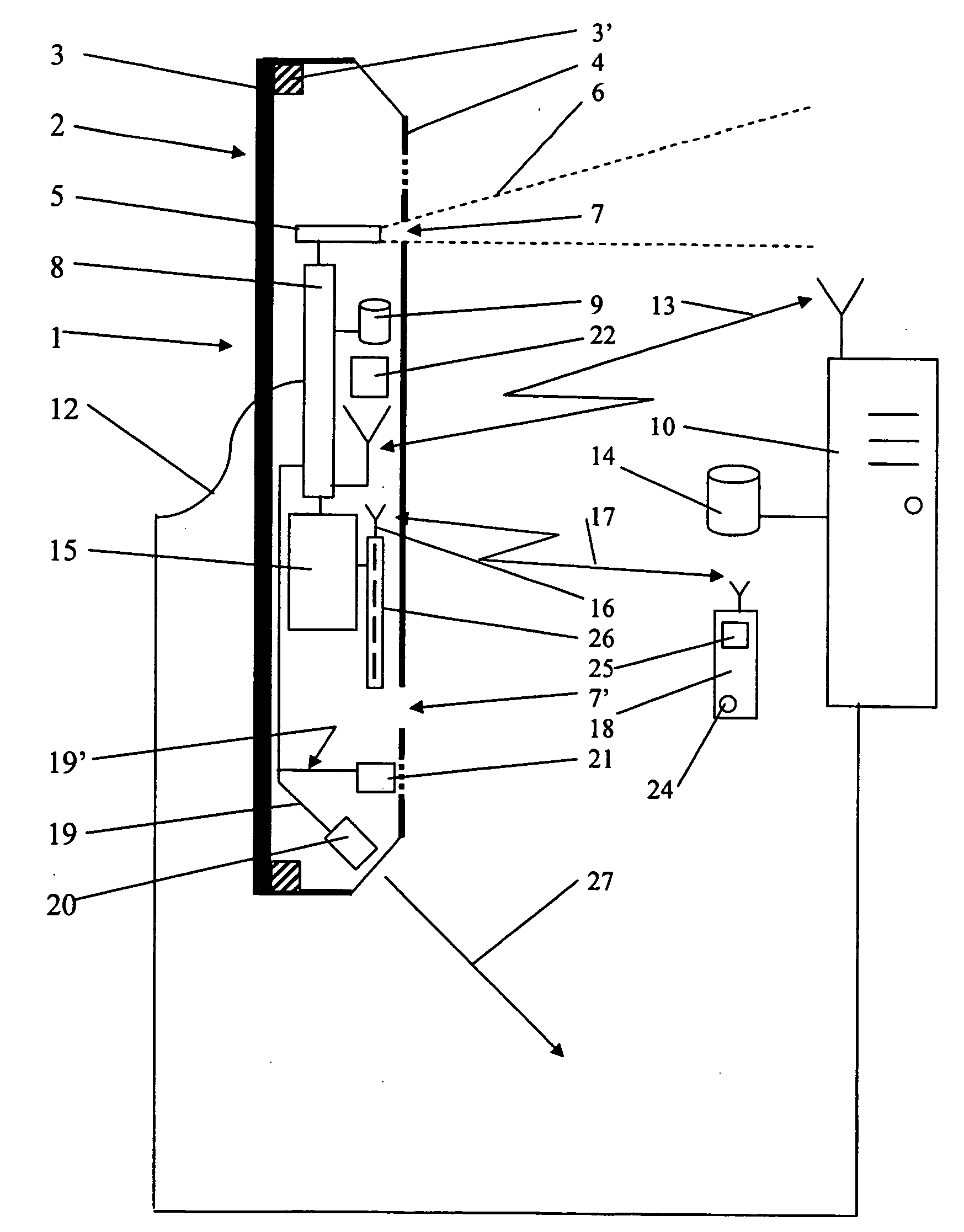

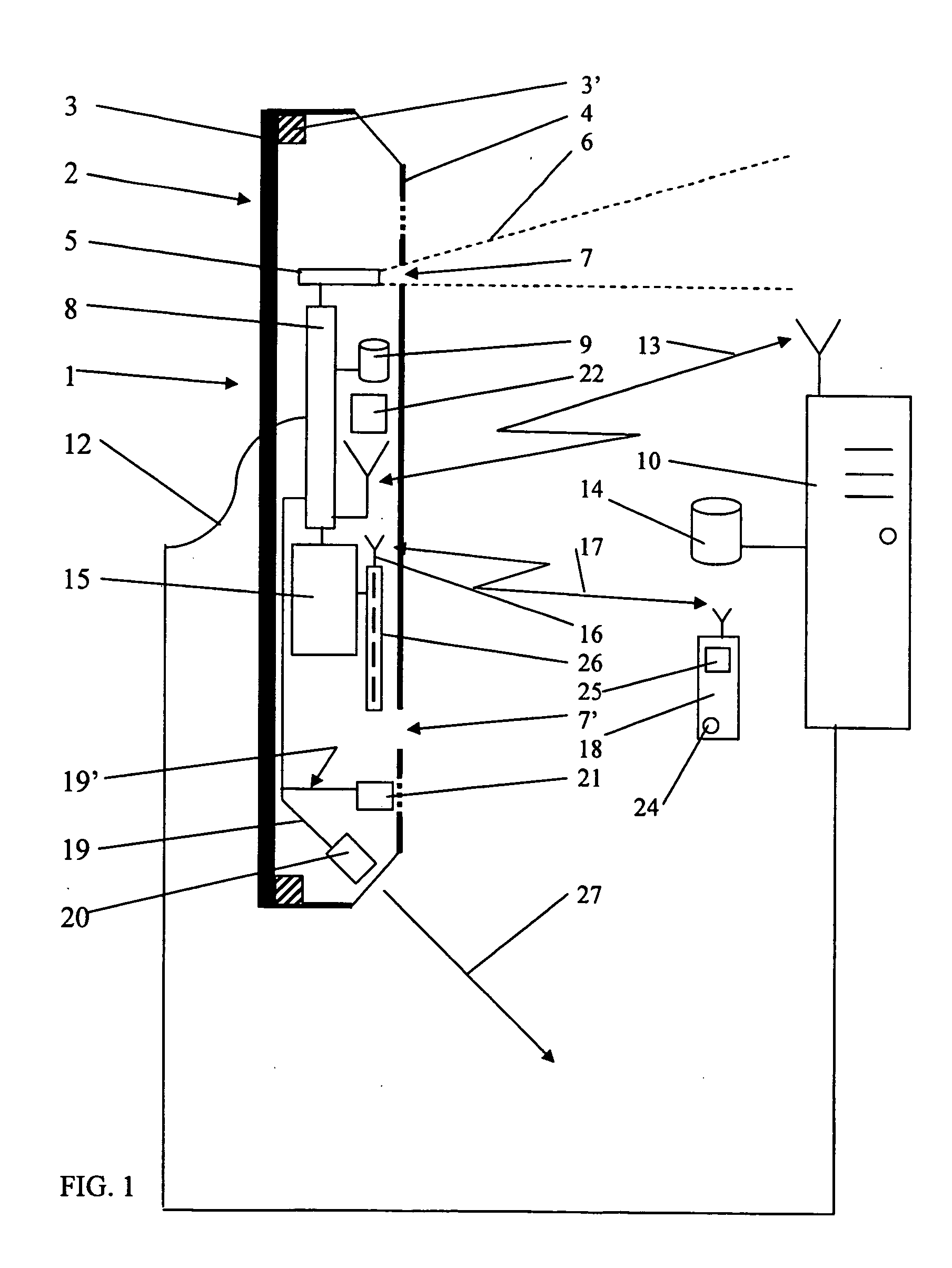

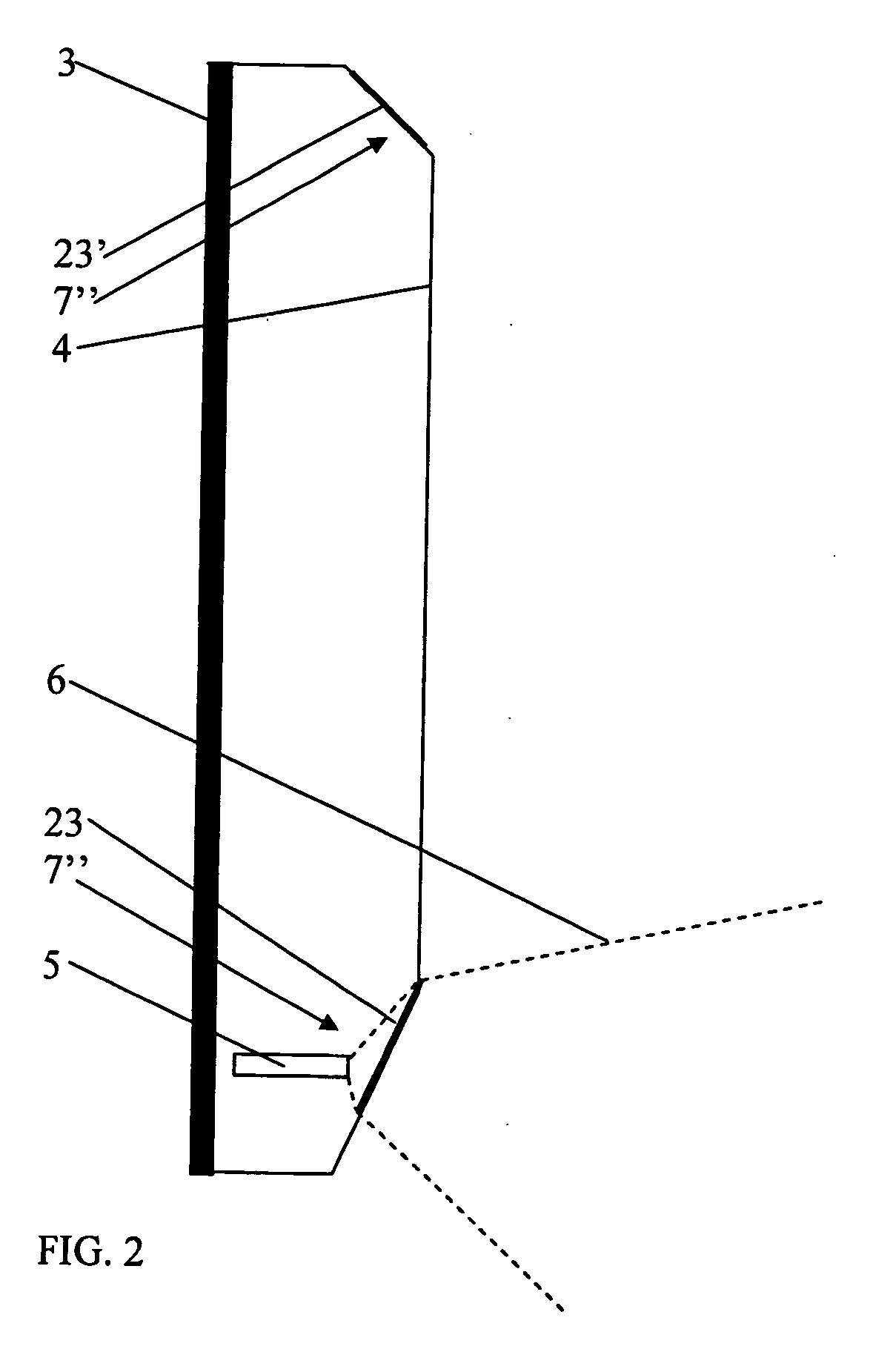

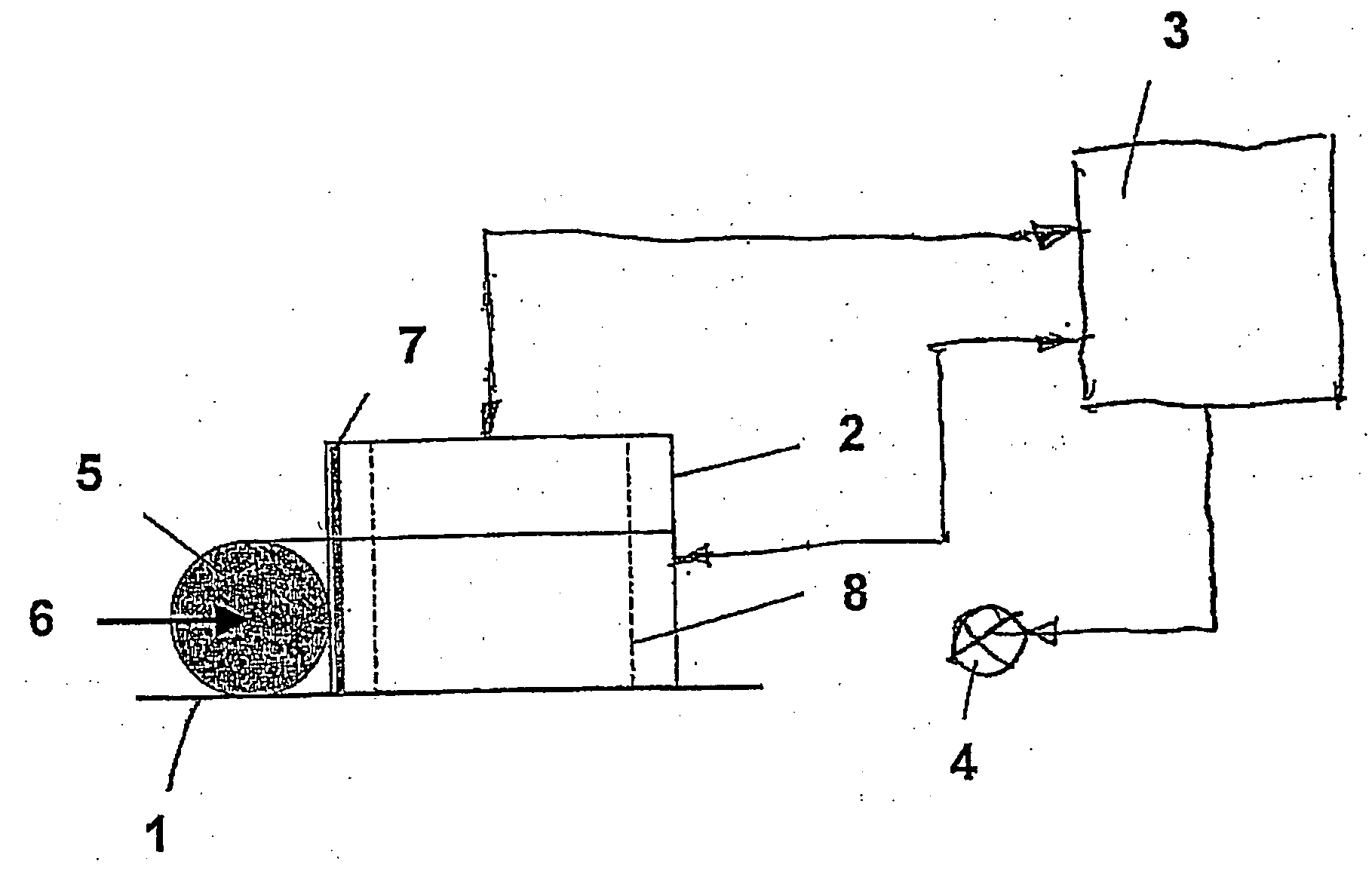

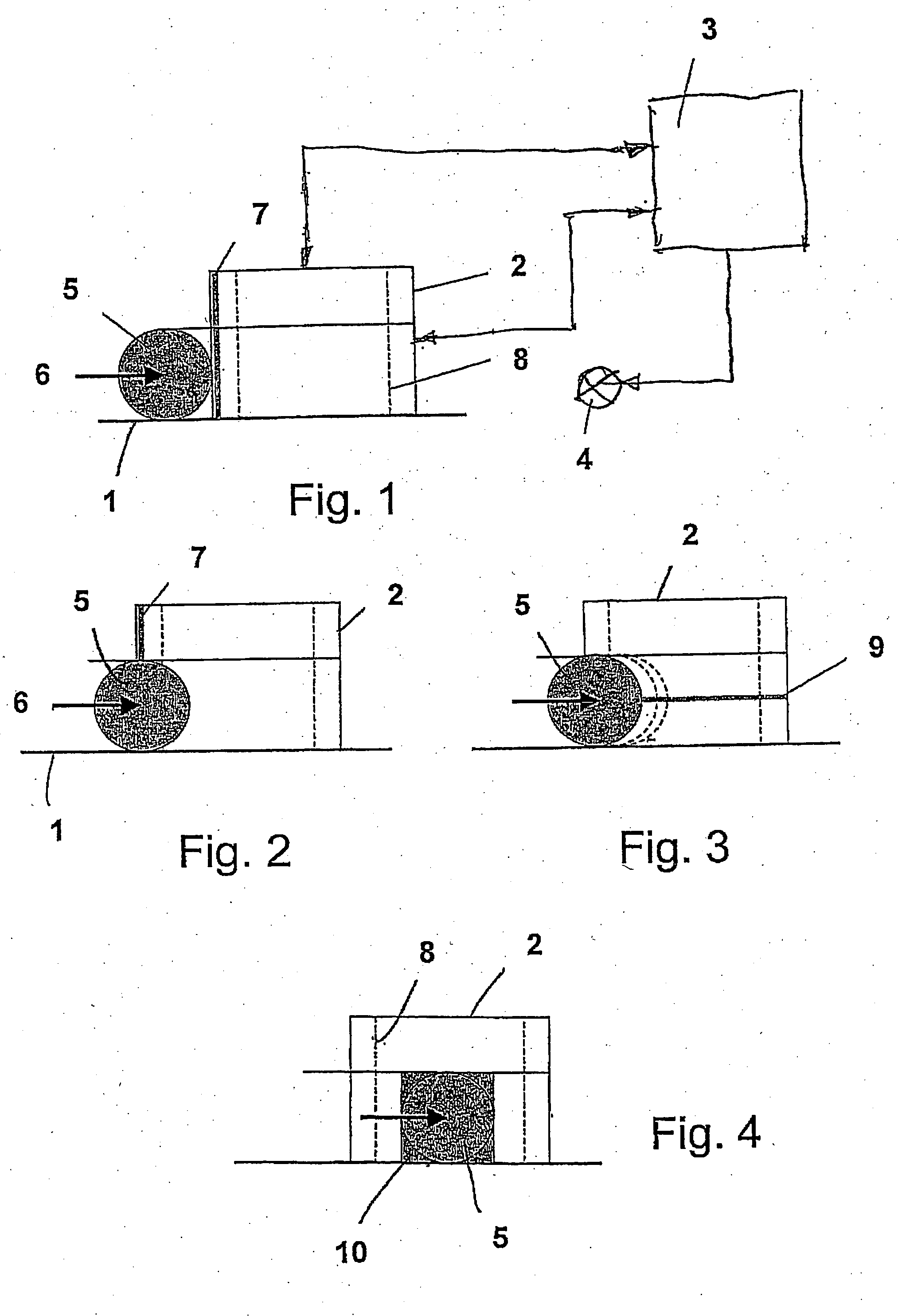

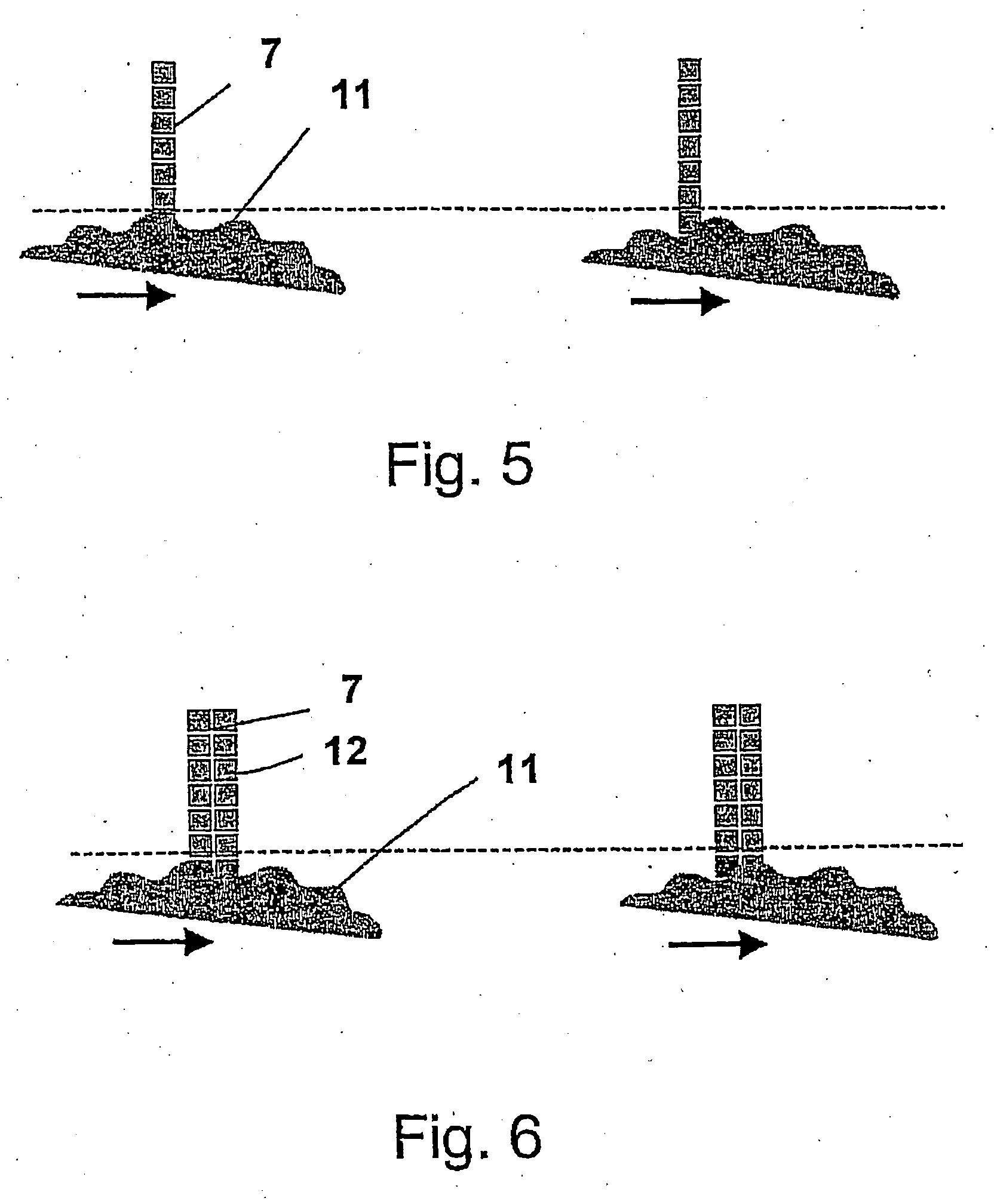

Method and device for testing coins

InactiveUS20060163029A1Convenient lightingMinimize data transferCoin testingComputer graphics (images)Biological activation

Disclosed is a method and device for testing coins which are placed in a coin acceptor unit and which are displaced in front of an image sensor consisting of lines and columns, whereby said image sensor records an image of the coins that are to be tested. At least one of the front columns in the direction of movement of said coins and / or at least one line of the image sensor captures parameters, which in conjunction with the temporal detection information, are used to provide information on the movement of said coins. It is determined independently from said parameters when the coin will appear in a desired overlap area for recording, whereby the image sensor is shifted into an activation mode of the columns and lines of the overlap area and recording is triggered.

Owner:WALTER HANKE MECHANISCHE WERKSTATTEN

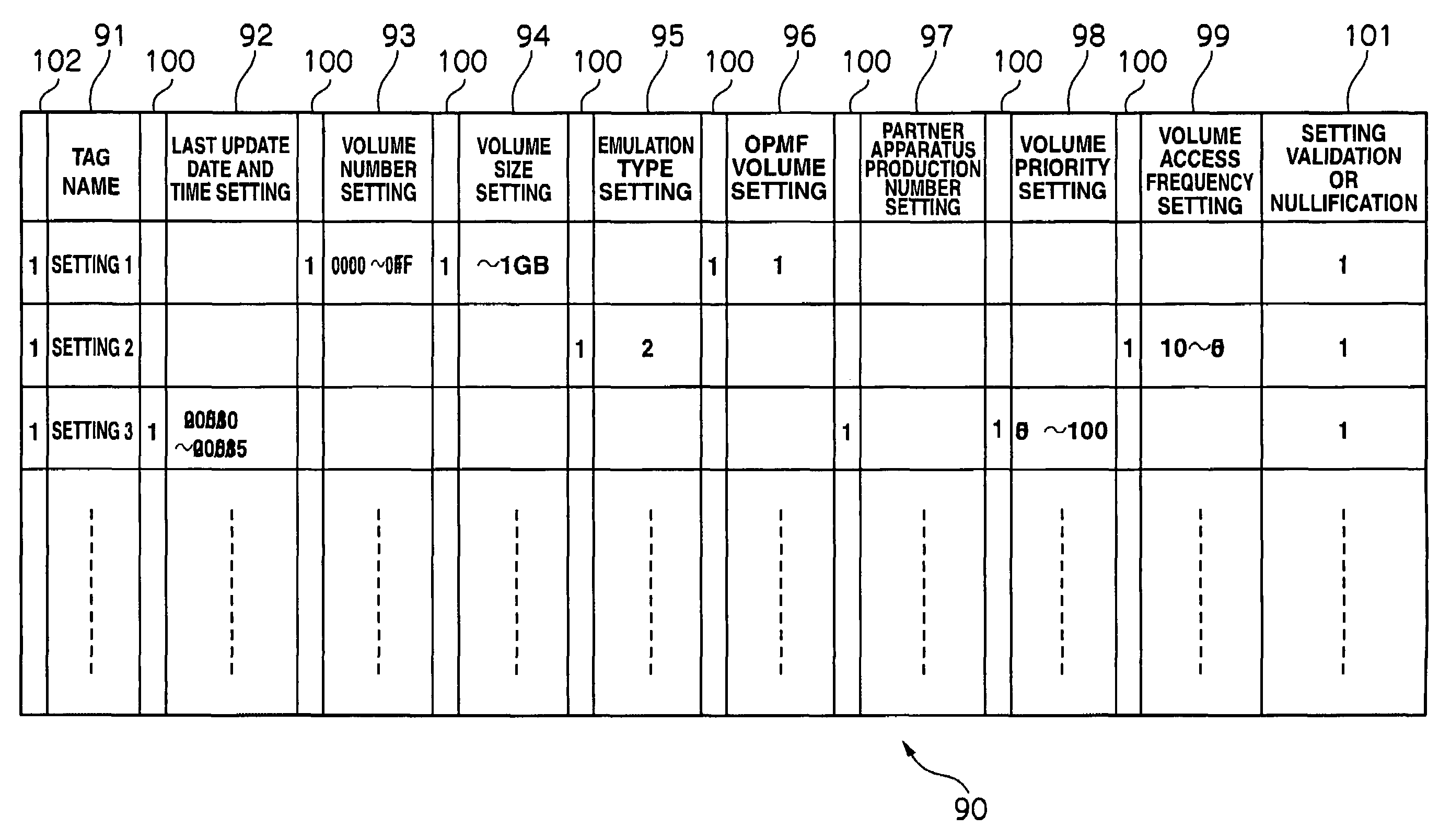

Storage system, data transfer method according to volume priority

InactiveUS7424583B2Minimize data transferShorten the timeError detection/correctionMemory systemsPriority settingDisk array

The present invention suggests a storage system capable of realizing highly reliable data back-up.The storage system includes: a first disk array apparatus for providing first volumes for storing data sent from a host system; a second disk array apparatus for providing second volumes for storing back-up data of the first volumes; and a console terminal for operating the first disk array apparatus. The console terminal is equipped with a setting unit for setting a priority for each first volume in accordance with an external command. The first disk array apparatus is equipped with: a storage unit for storing the priorities set by the priority setting unit; and a transfer unit for reading the priorities from the storage unit upon receiving the data and transferring the data stored in the first volumes to the second volumes of the second disk array apparatus in order of descending priority of the first volumes that store the data.

Owner:HITACHI LTD

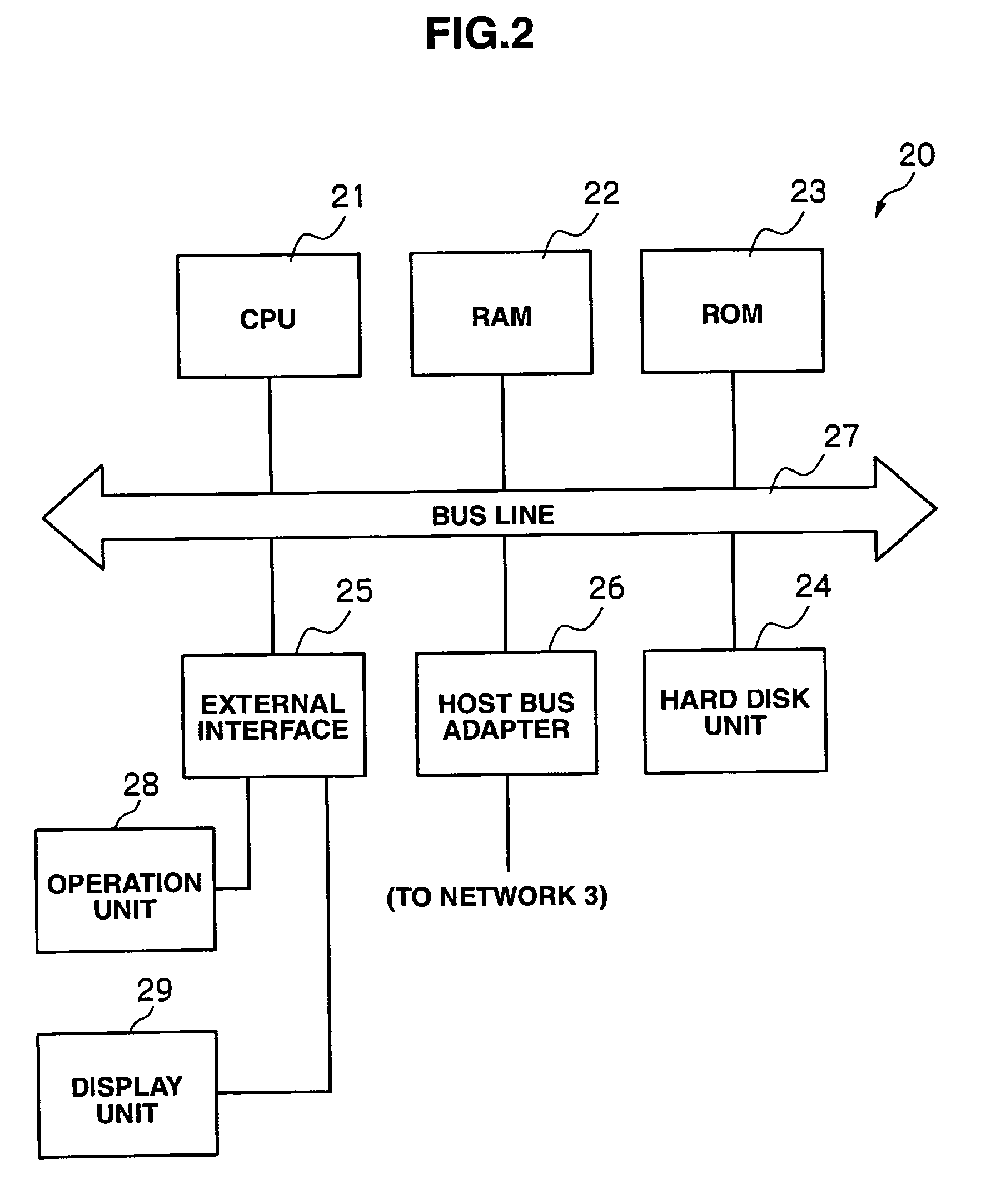

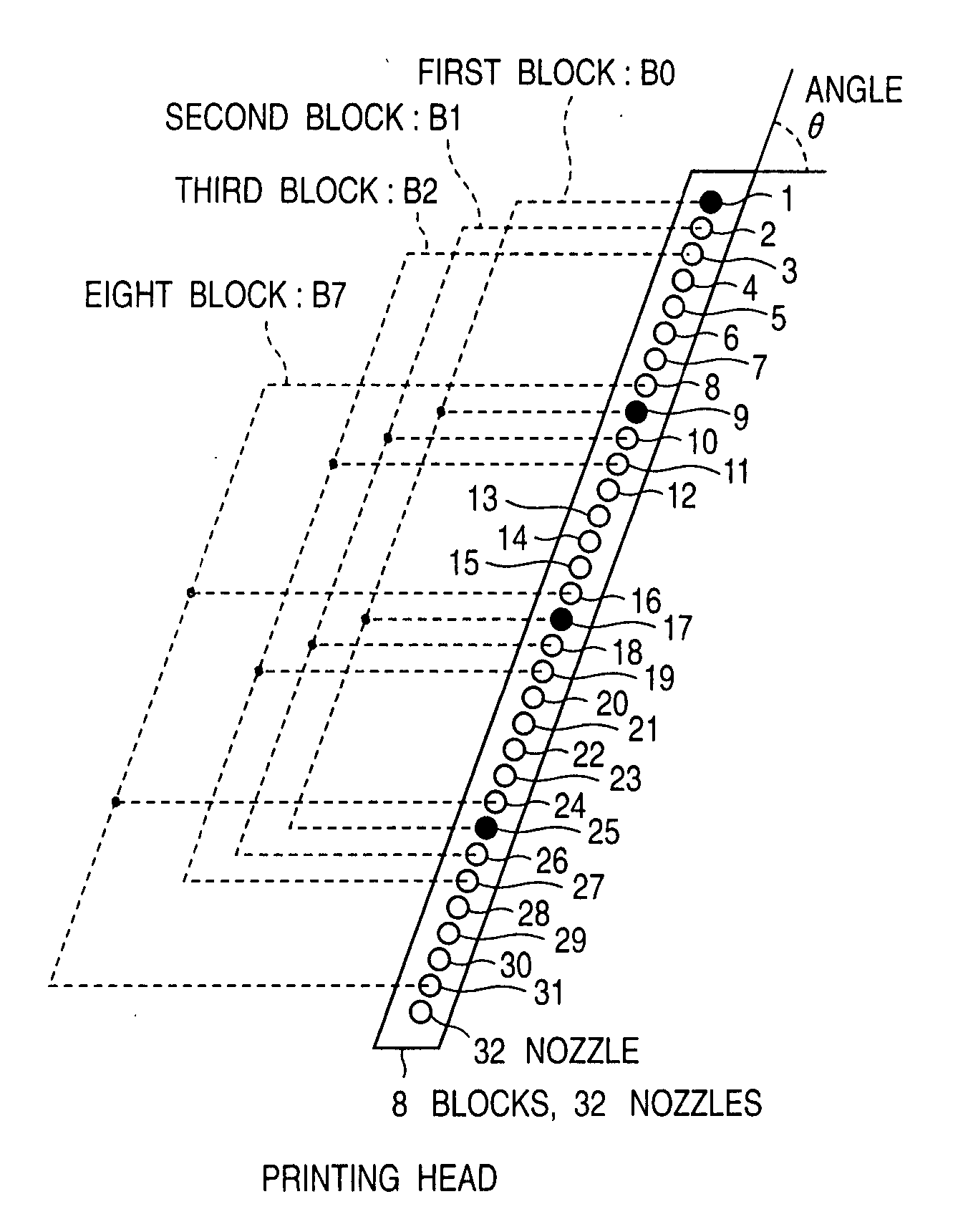

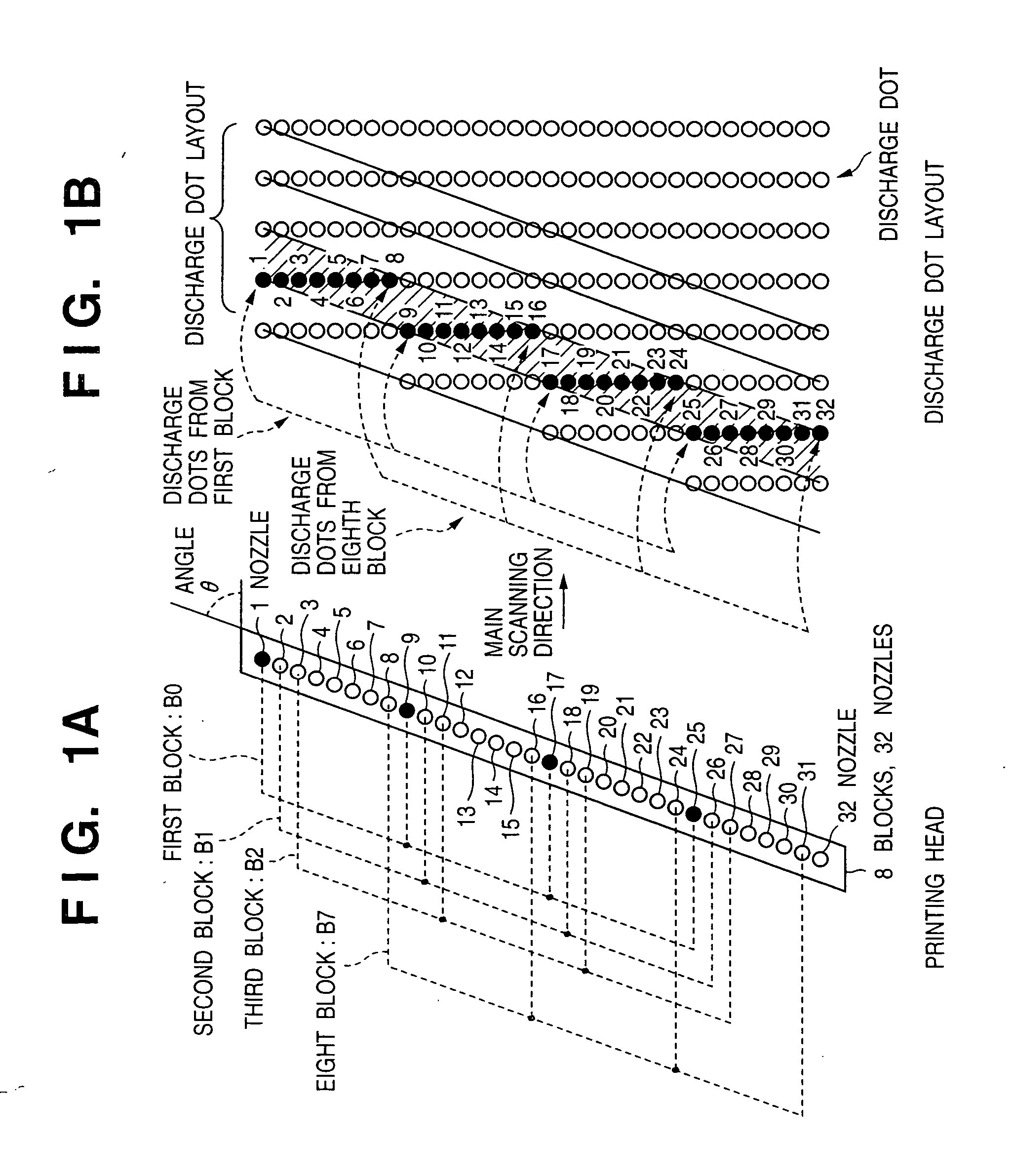

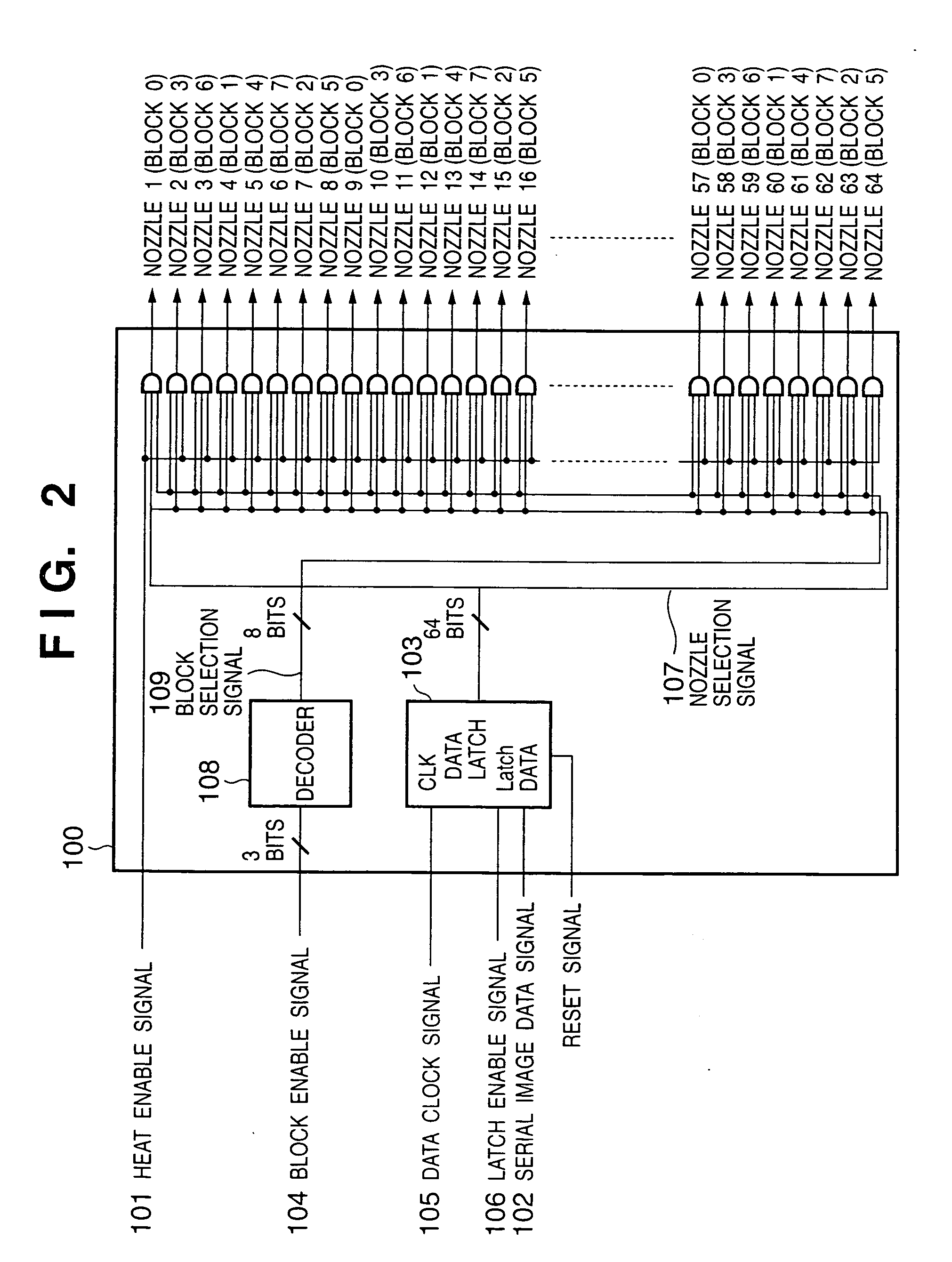

Printing head, image printing apparatus using the same, and control method therefor

InactiveUS20050243128A1Increase the number ofReduce degradationPrintingRing counterRelative pressure

This invention provides a printing head which can prevent an increase in the number of block enable signal lines, and can prevent changes in printing ink density caused by interference due to the relative pressures of nozzles generated in ink discharge, and an image printing apparatus using the printing head. For this purpose, an increase in the number of input signal lines along with an increase in the number of blocks is prevented using a block clock signal or the like instead of a block enable signal as an input signal to the printing head. Three ring counters generate signals having different nozzle driving orders. These signals are selectively used by a ring counter selection signal. Ink is not always discharged from the nozzles in the same output order. This can prevent changes in ink density caused by pressure interference.

Owner:CANON KK