Patents

Literature

67 results about "Ring counter" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

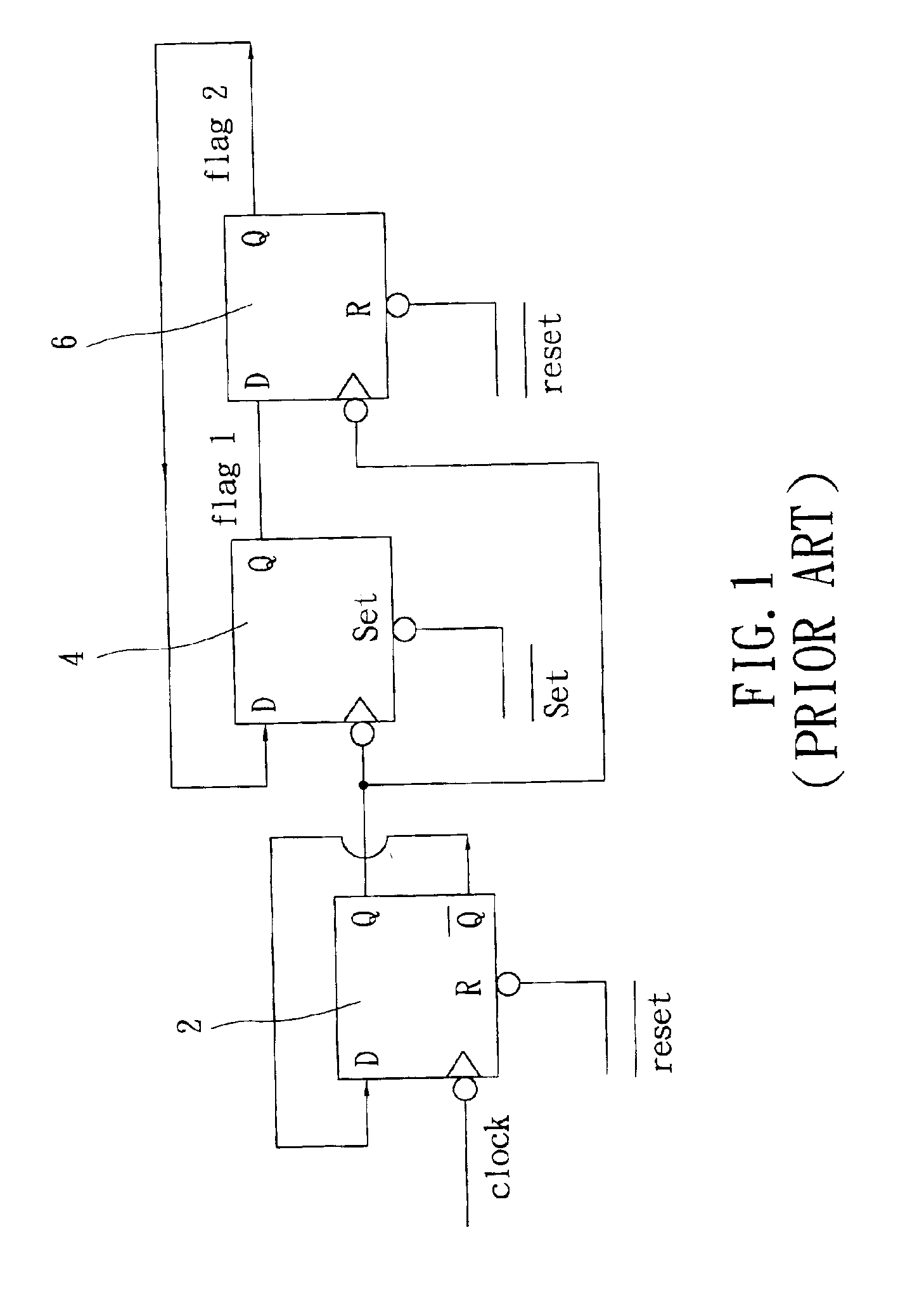

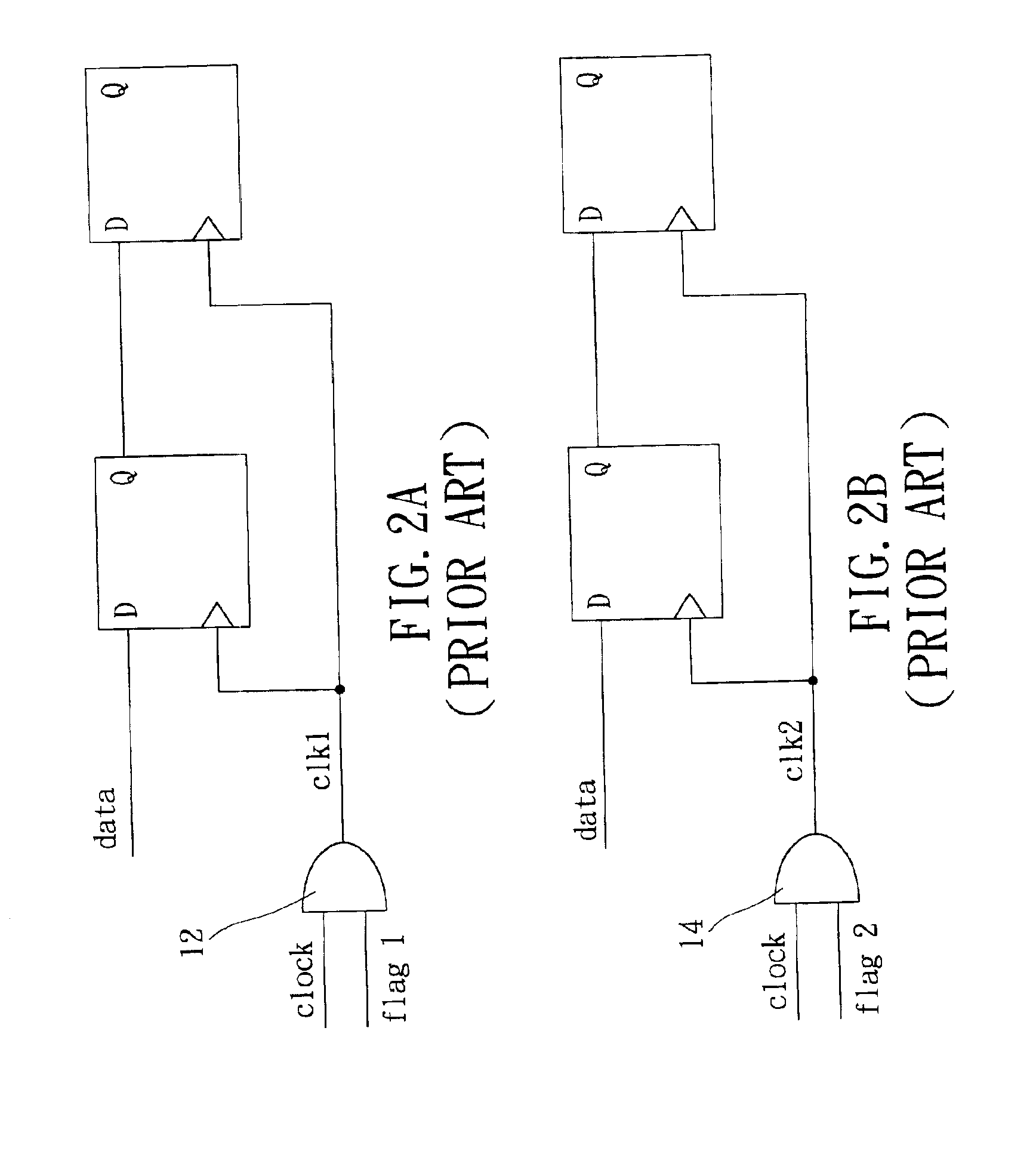

A ring counter is a type of counter composed of flip-flops connected into a shift register, with the output of the last flip-flop fed to the input of the first, making a "circular" or "ring" structure. The output of the 1 flipflop acts as the input of the another flipflop.

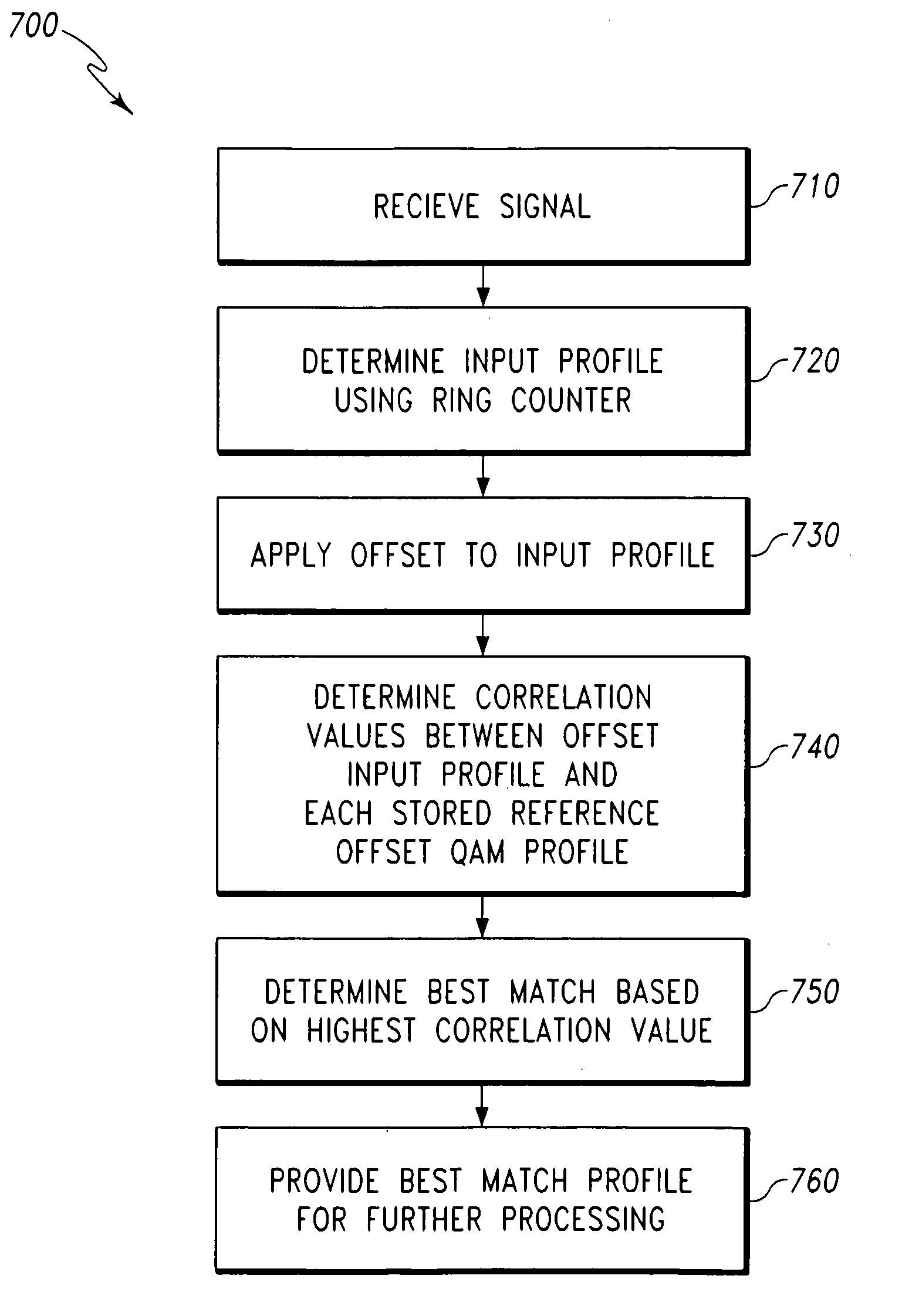

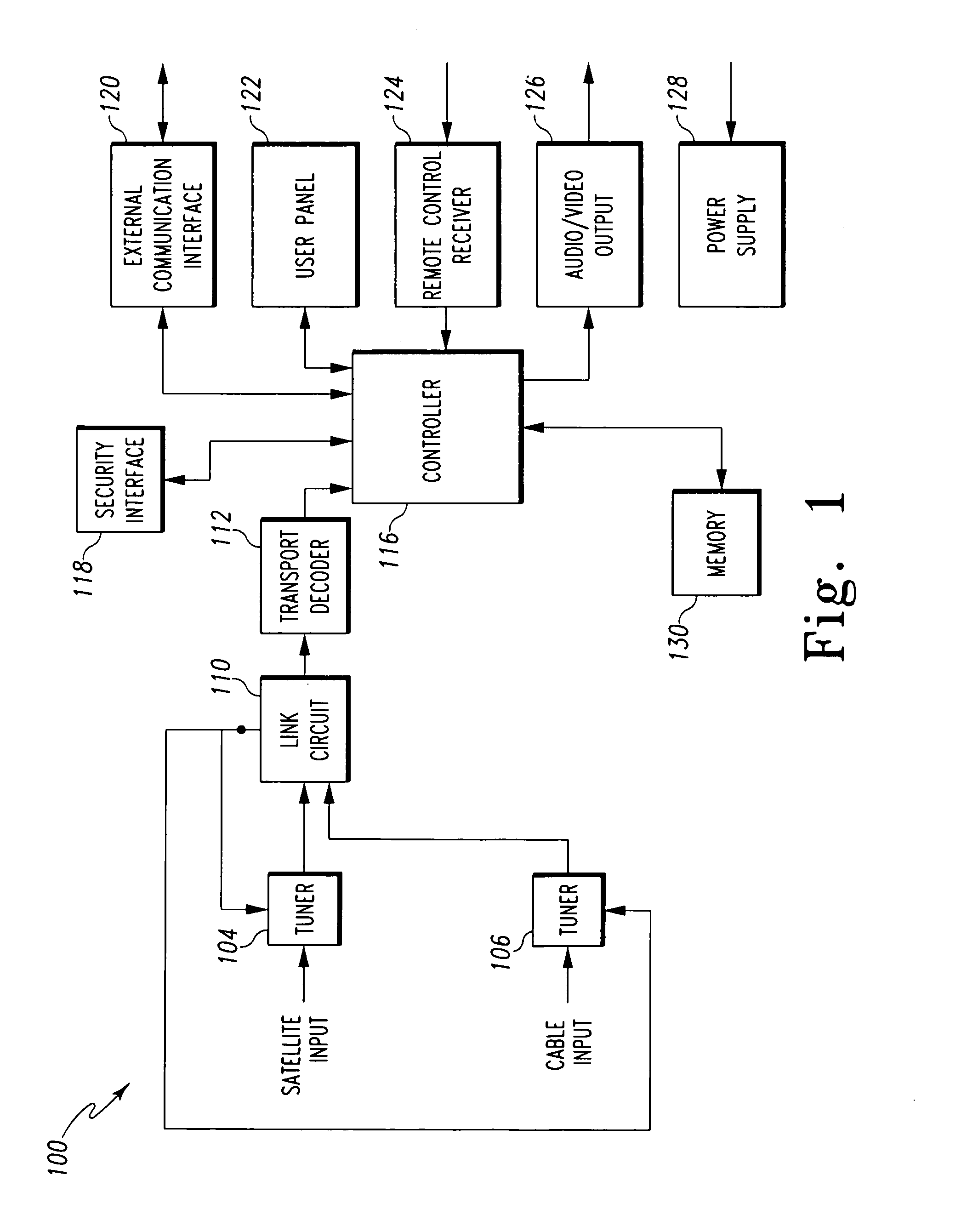

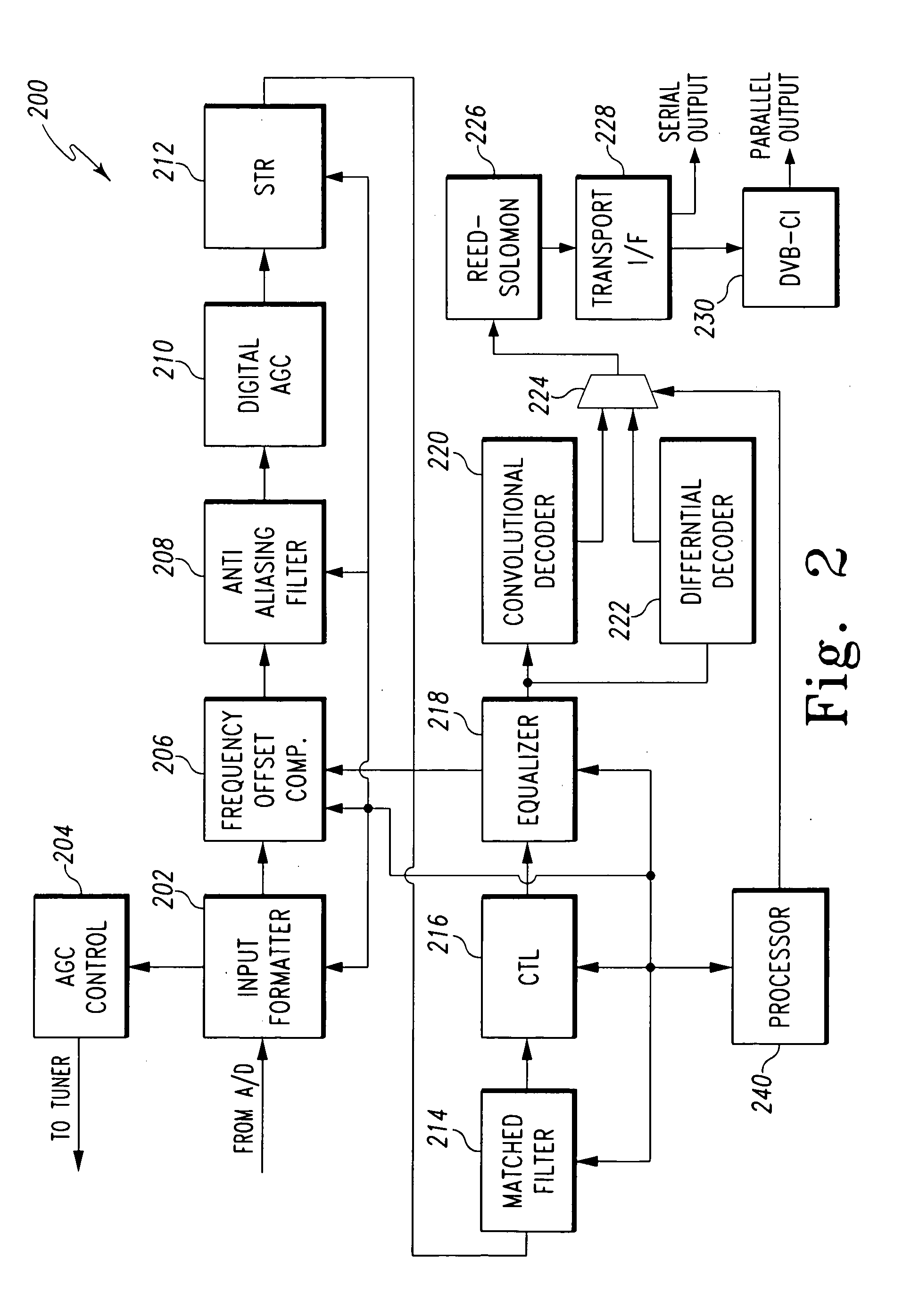

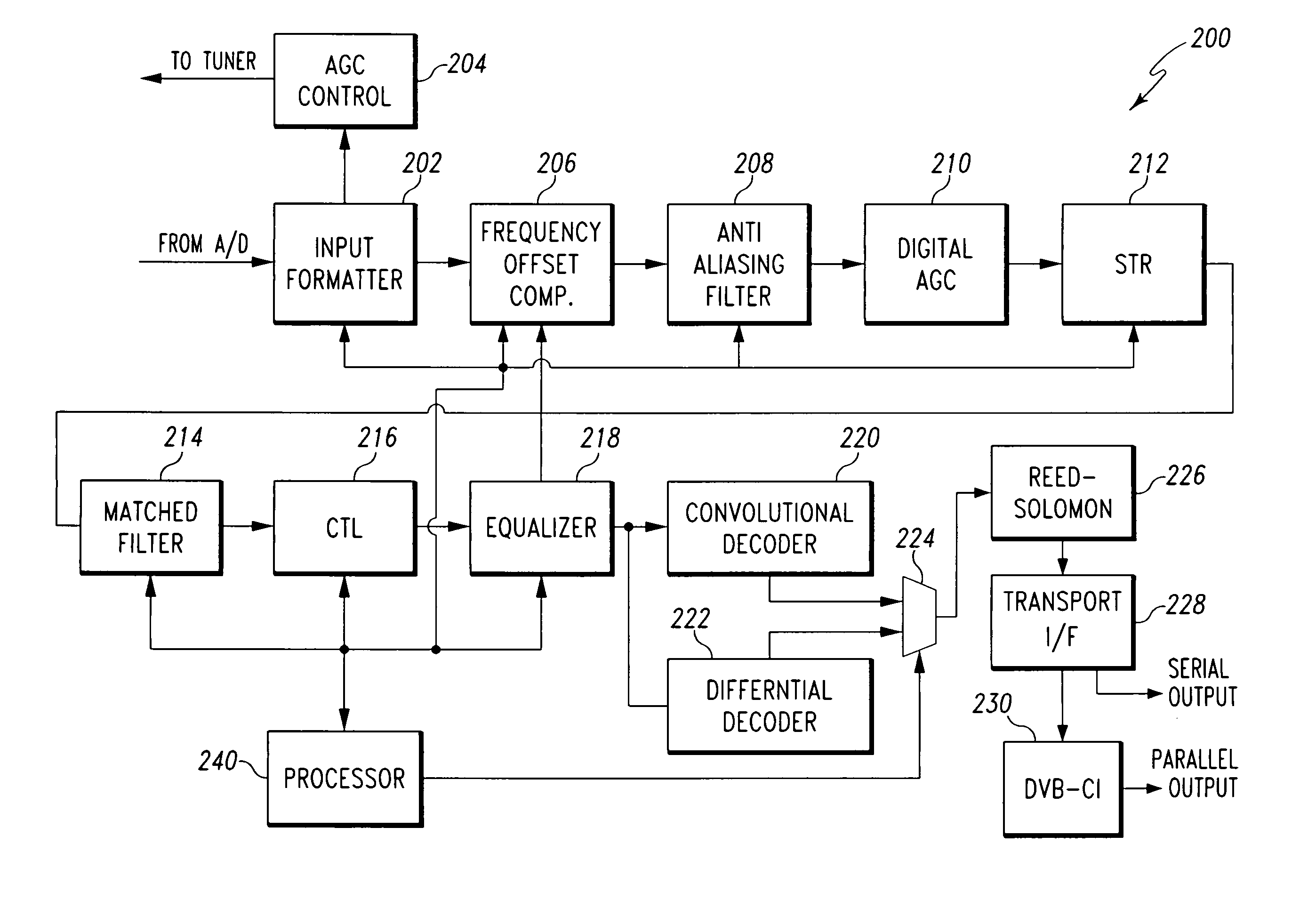

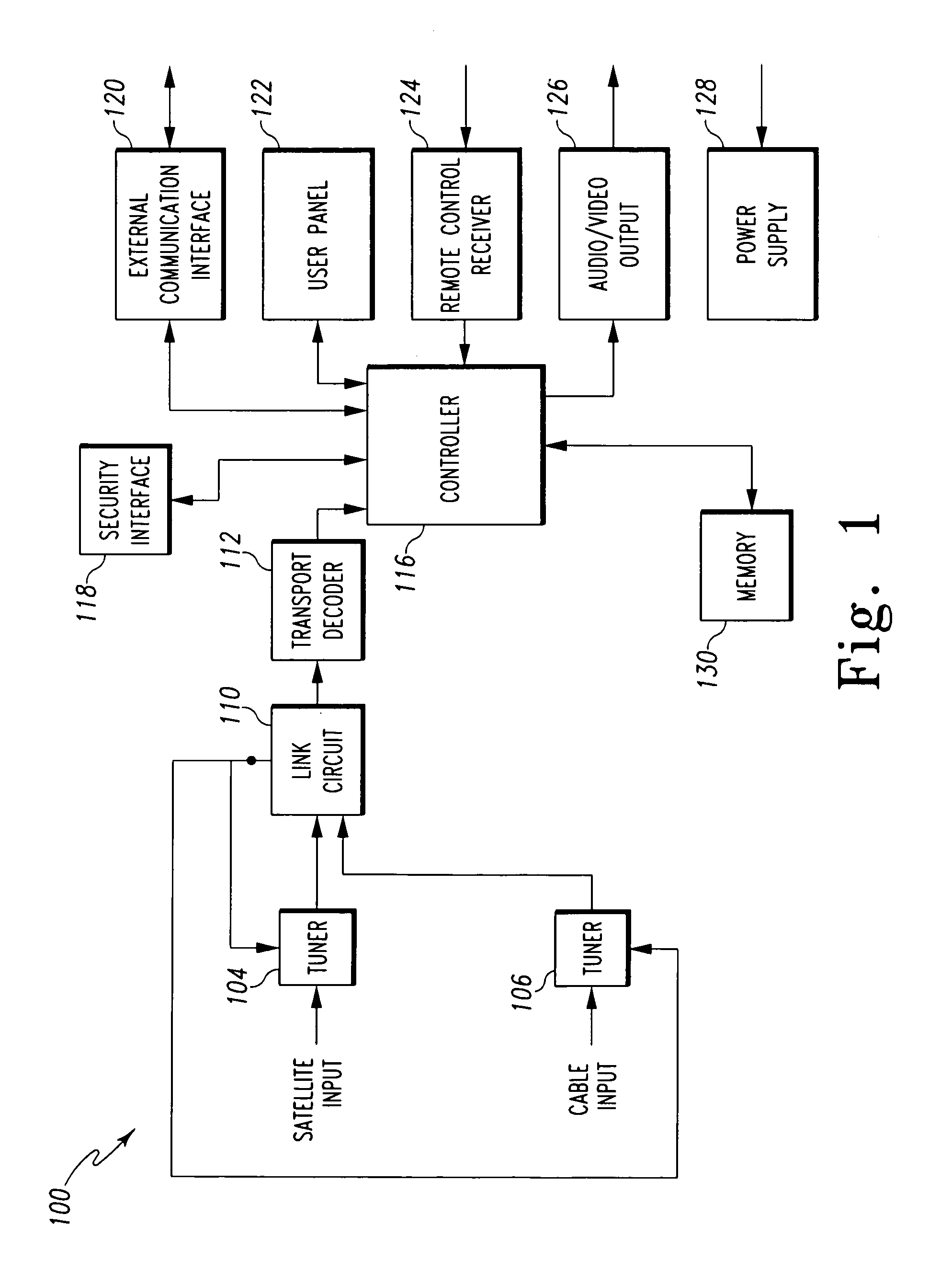

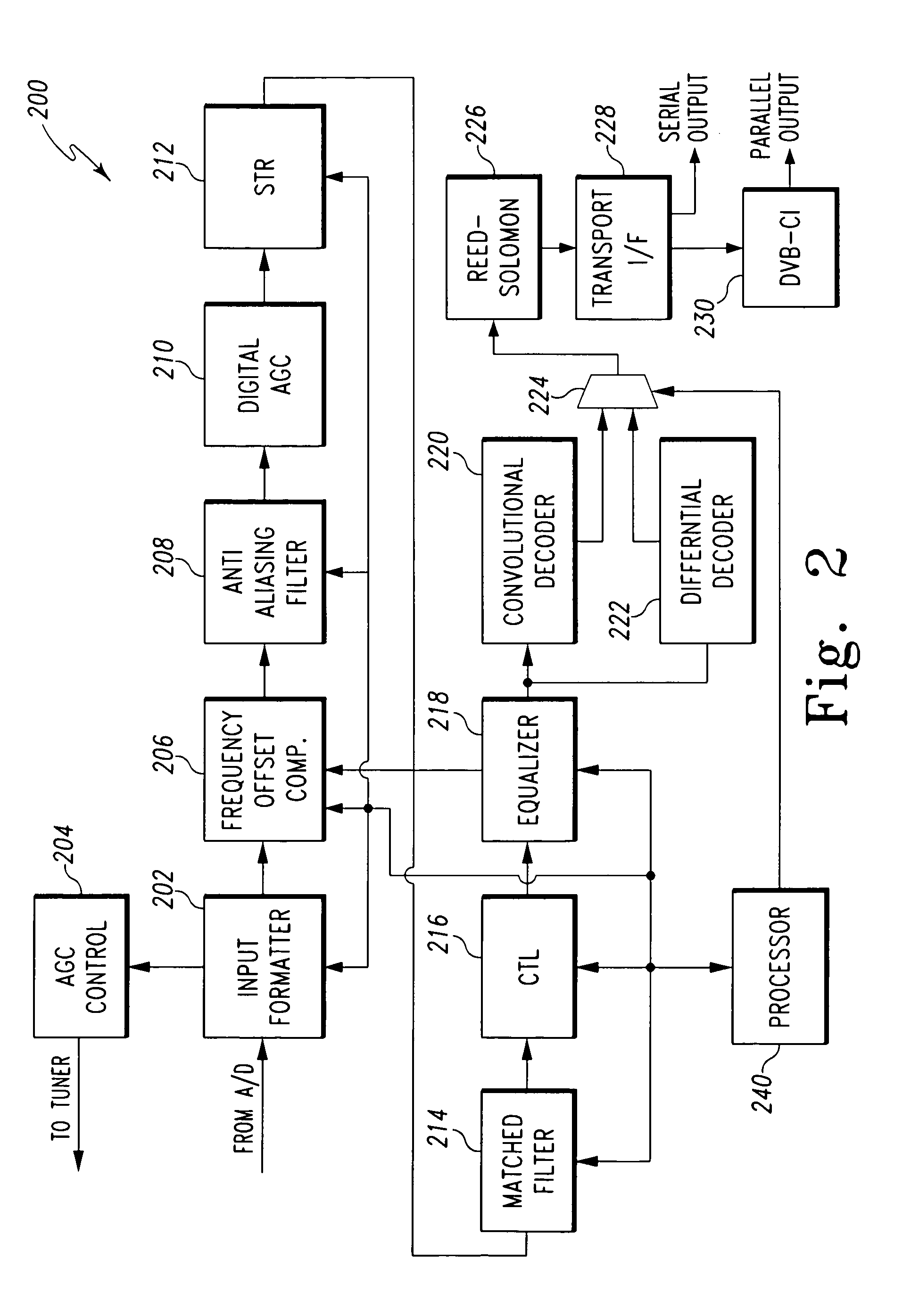

Apparatus and method for determination of signal format

InactiveUS20110074500A1Multiple input and output pulse circuitsMultiple modulation transmitter/receiver arrangementsRing counterSignal analyzer

The determination of the signal modulation format for a channel is an important aspect of the operation of a signal receiver. A method (700) is described including the steps of receiving (710) a signal, comparing (720) a sample of the received signal to a first threshold value and a second threshold value, creating (720) a signal profile based on the comparison, and selecting (750) a modulation format for the received signal based on the signal profile. An apparatus (500) is also described including a ring counter (510) that receives a sample of an input signal, compares the sample to a first threshold value and a second threshold value, and creates a signal profile for the input signal, a signal profiler (550) that compares the signal profile for the input signal to at least two reference profiles, and a detector (560) that determines a modulation format for the input signal based on the comparison in the signal profiler (550).

Owner:MAGNOLIA LICENSING LLC

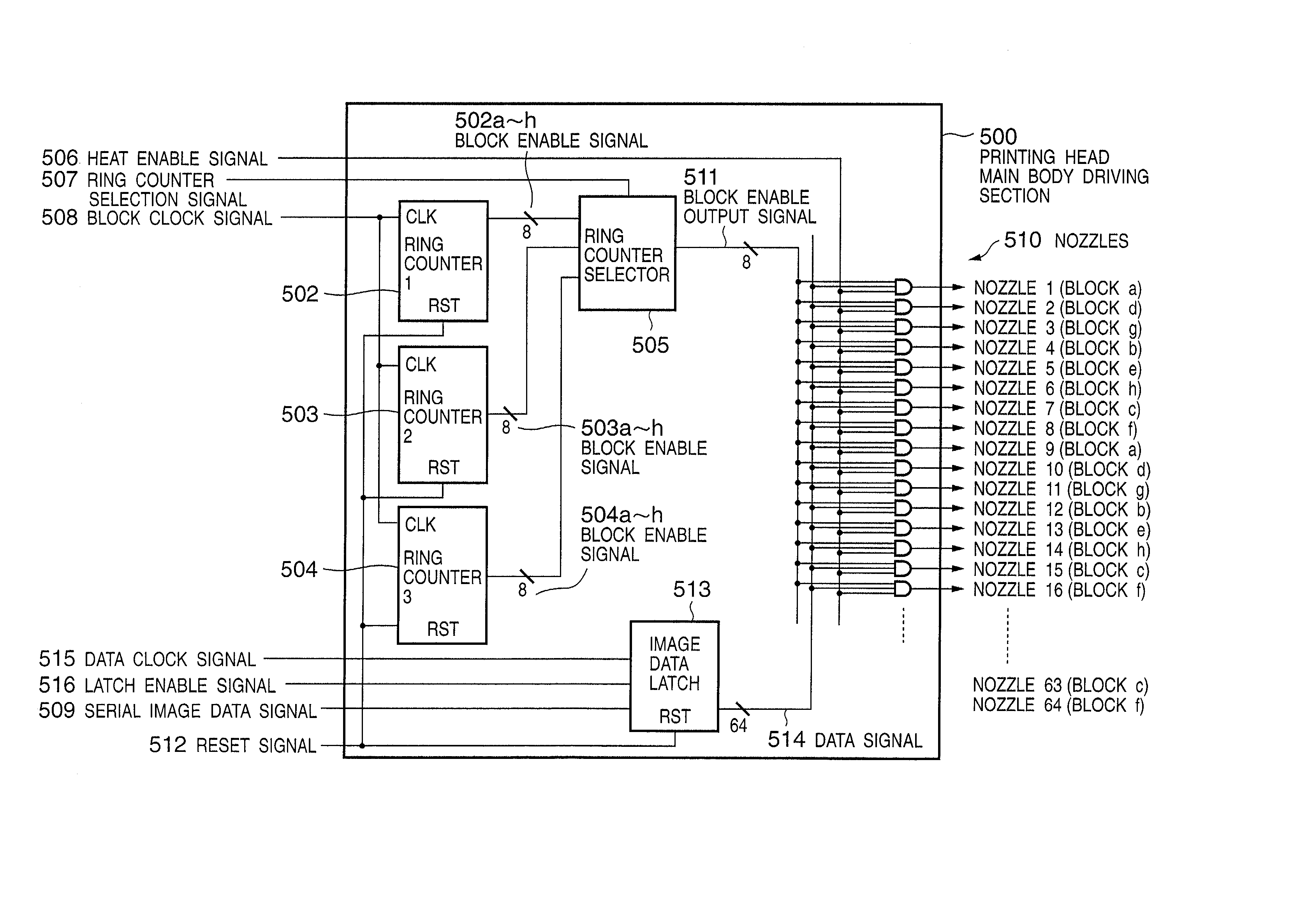

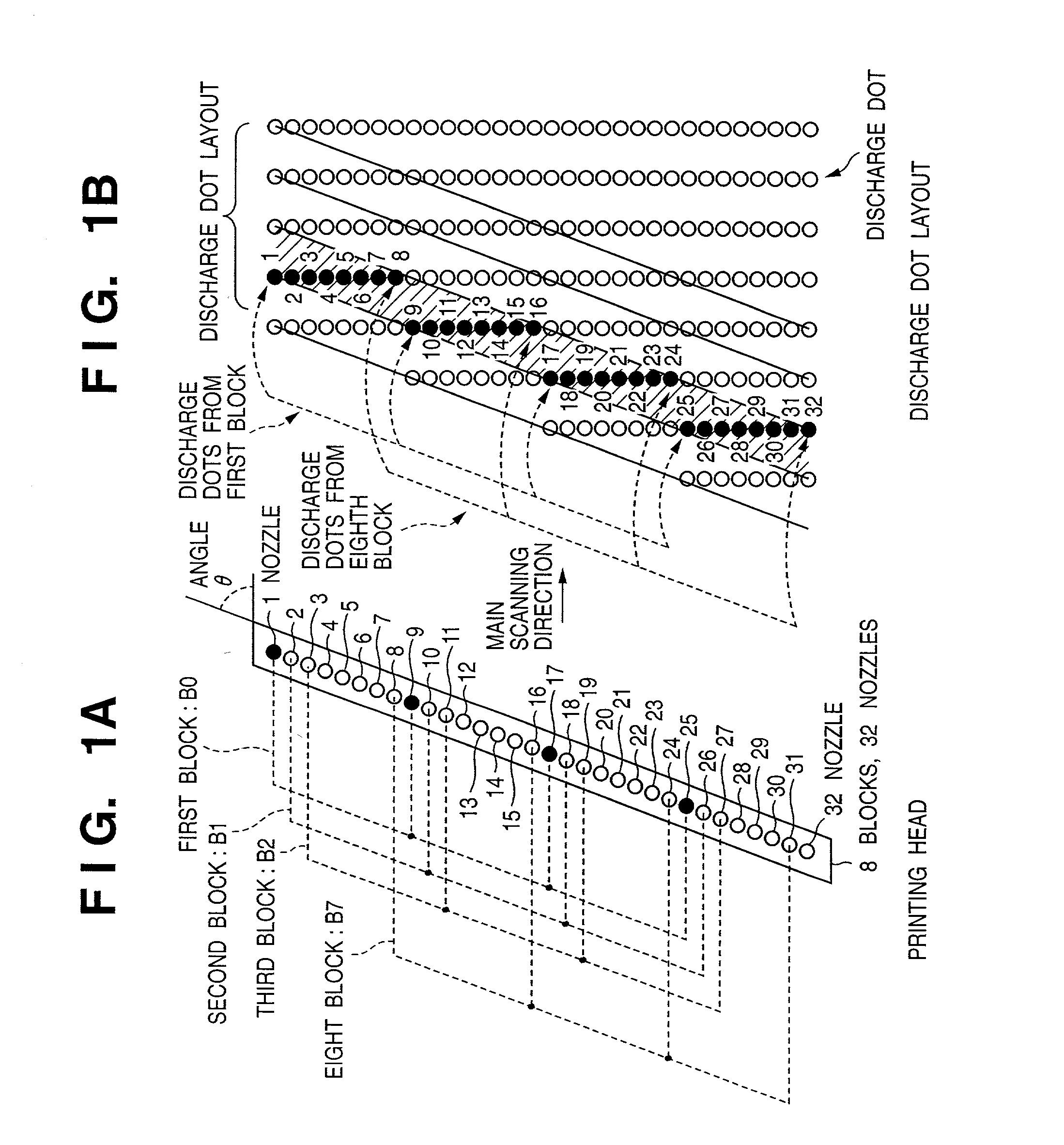

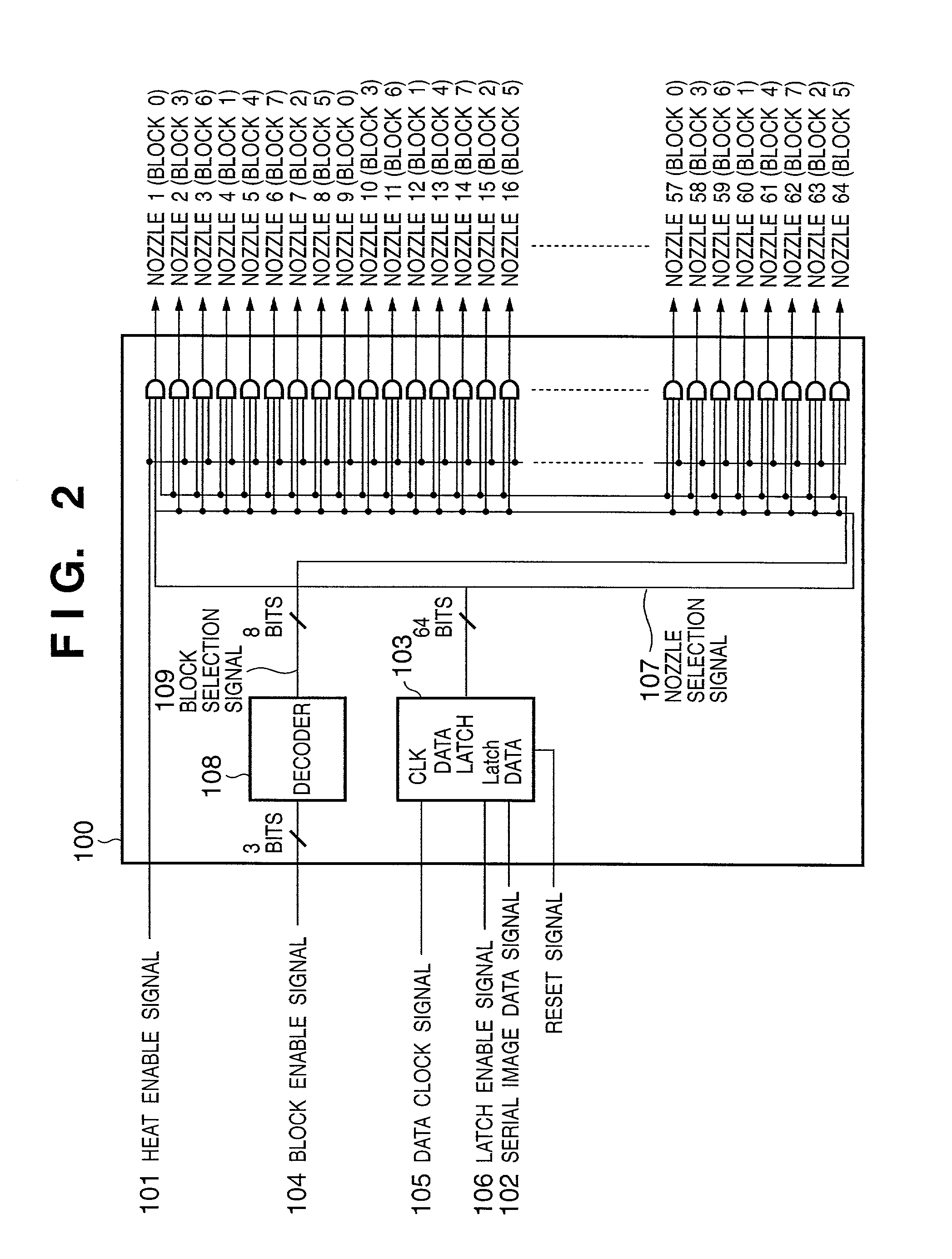

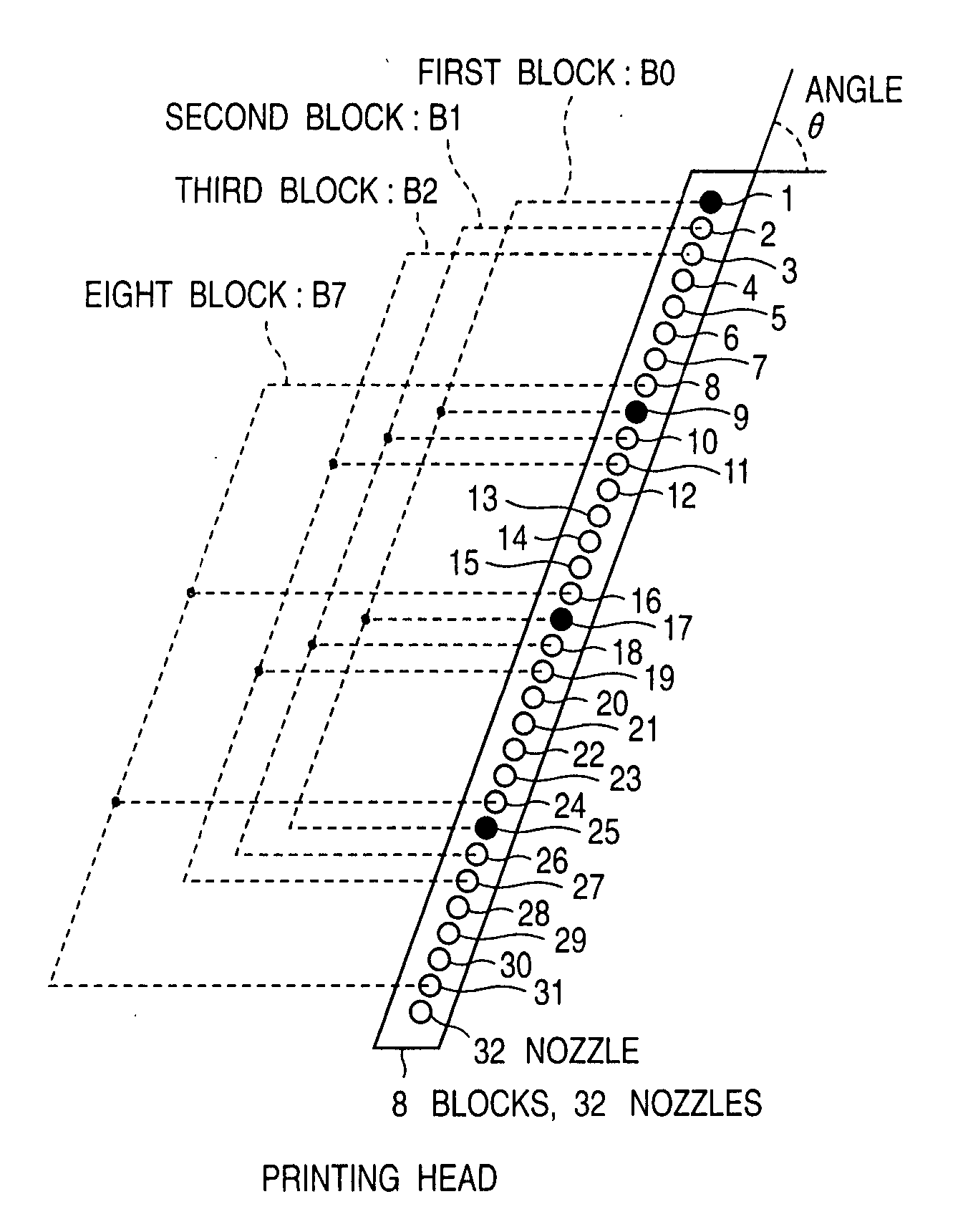

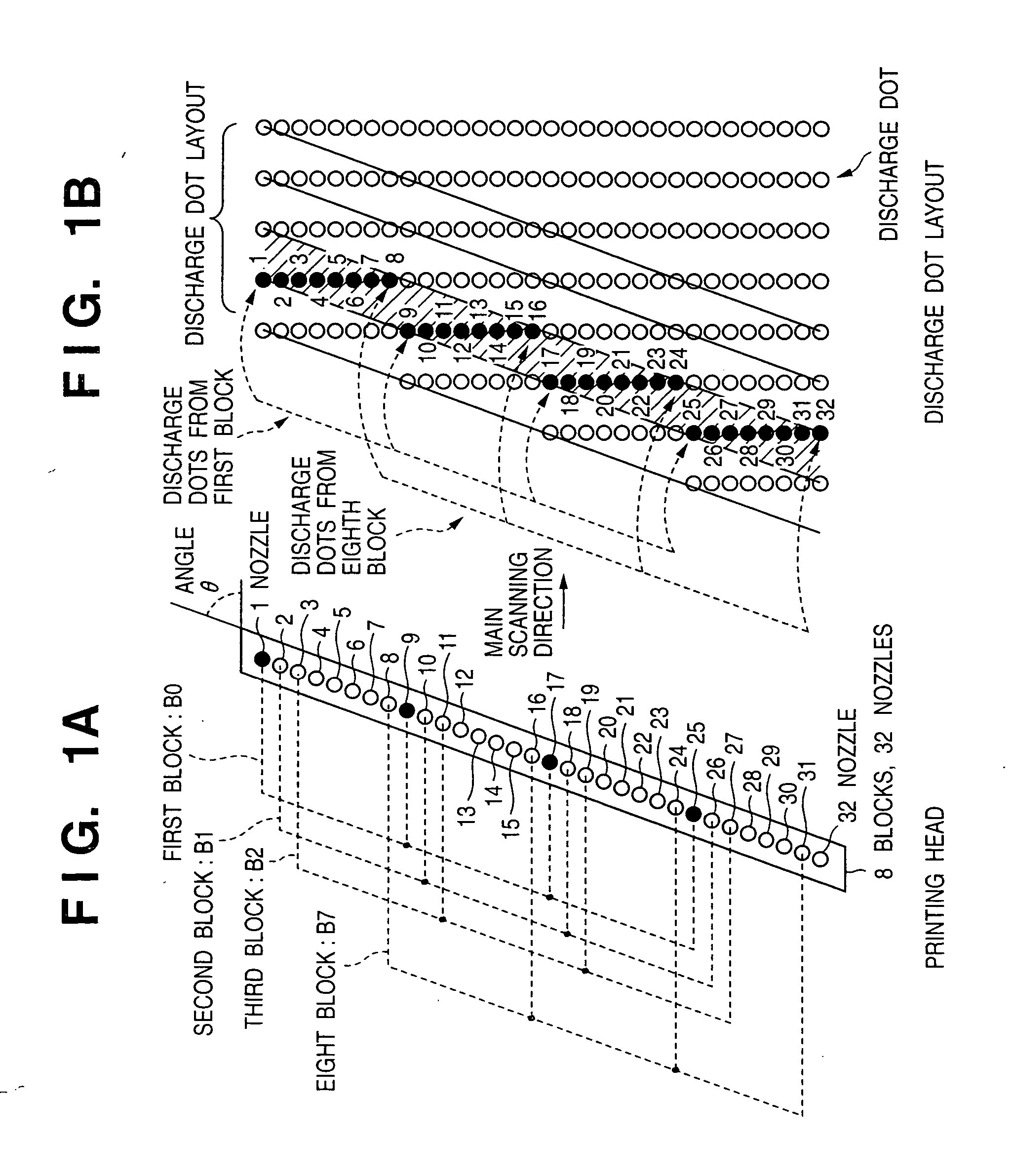

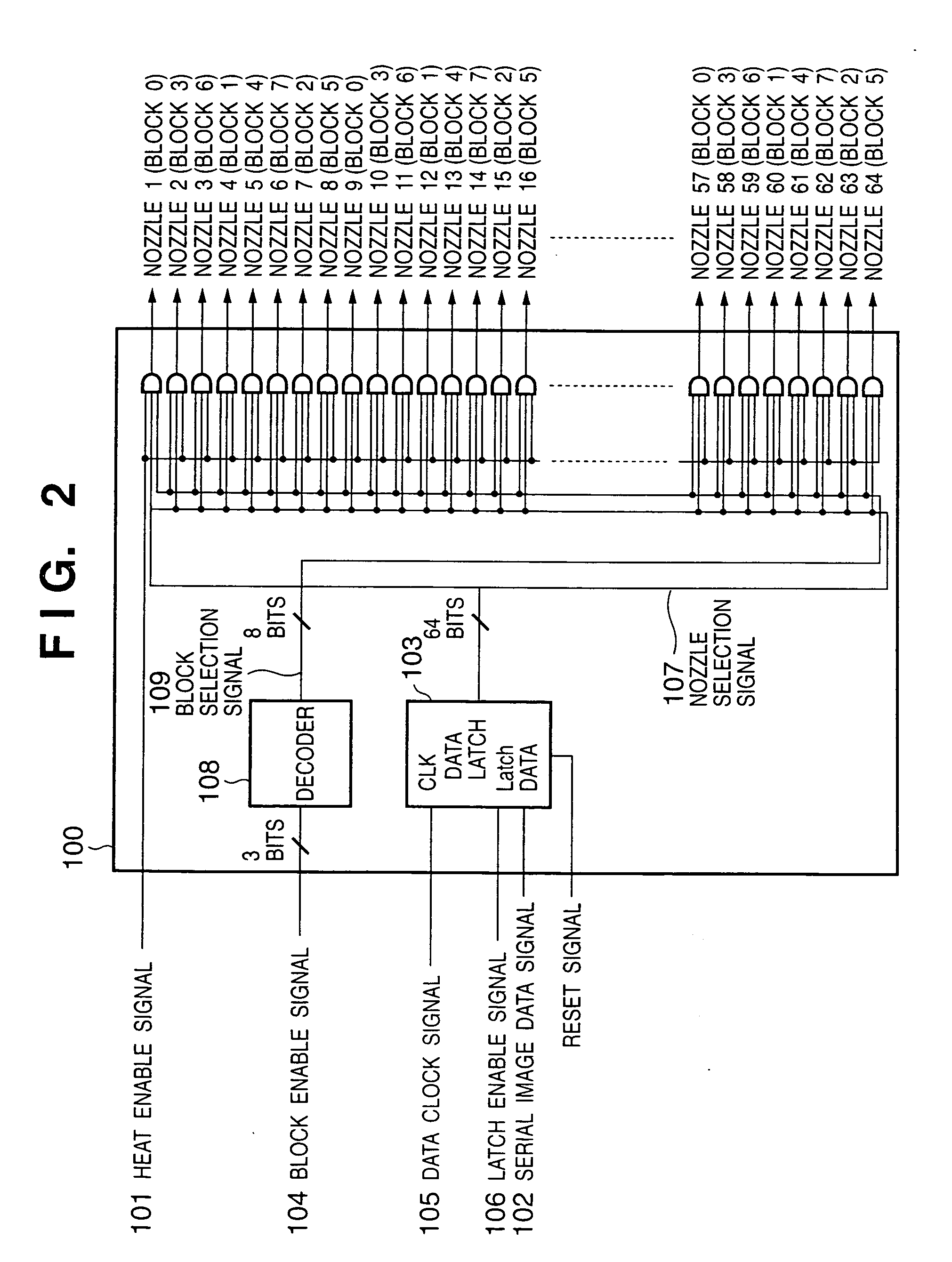

Printing head, image printing apparatus using the same, and control method therefor

InactiveUS20030142153A1Improve image qualityMinimize impactOther printing apparatusRing counterRelative pressure

This invention provides a printing head which can prevent an increase in the number of block enable signal lines, and can prevent changes in printing ink density caused by interference due to the relative pressures of nozzles generated in ink discharge, and an image printing apparatus using the printing head. For this purpose, an increase in the number of input signal lines along with an increase in the number of blocks is prevented using a block clock signal or the like instead of a block enable signal as an input signal to the printing head. Three ring counters generate signals having different nozzle driving orders. These signals are selectively used by a ring counter selection signal. Ink is not always discharged from the nozzles in the same output order. This can prevent changes in ink density caused by pressure interference.

Owner:CANON KK

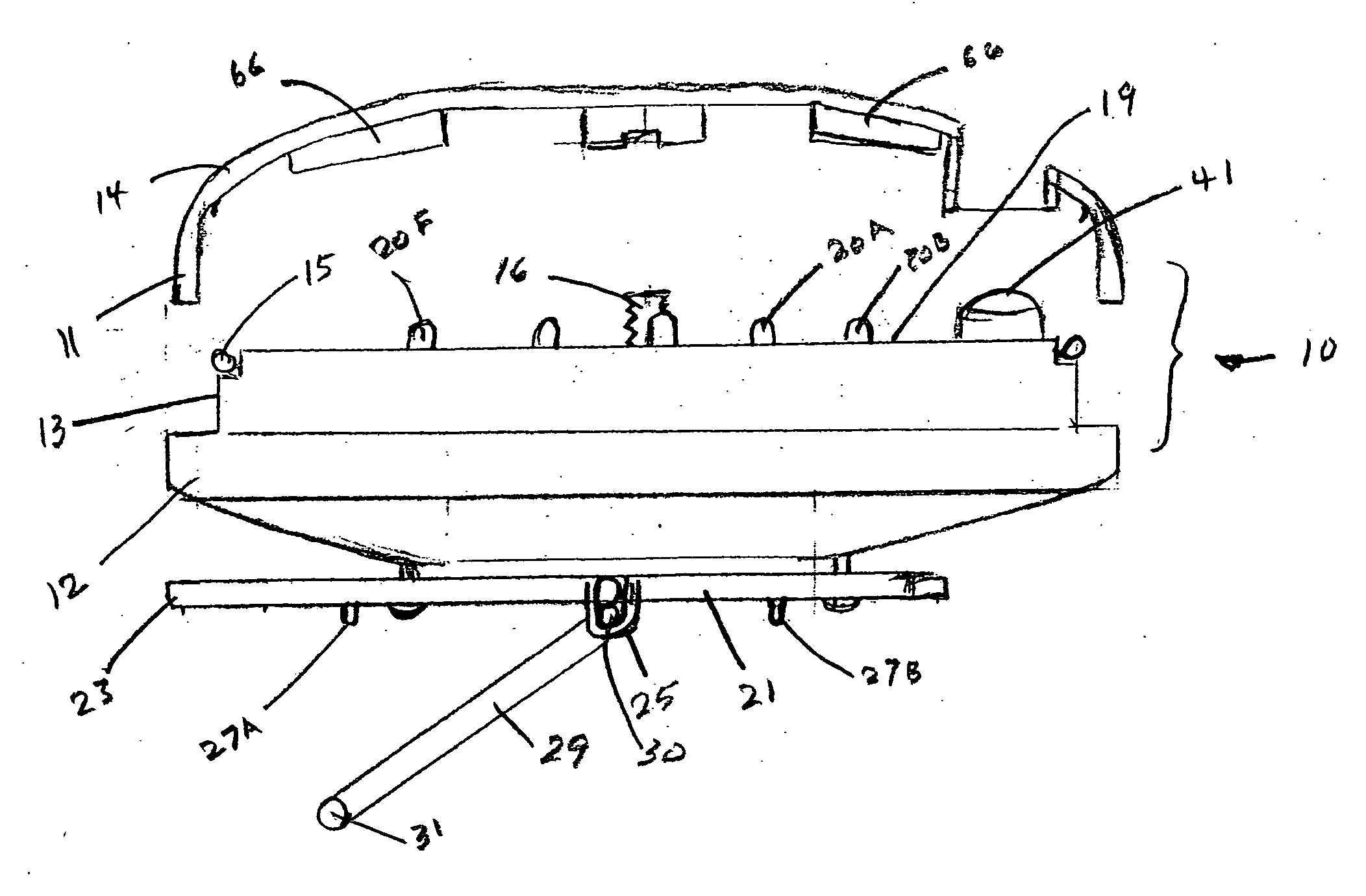

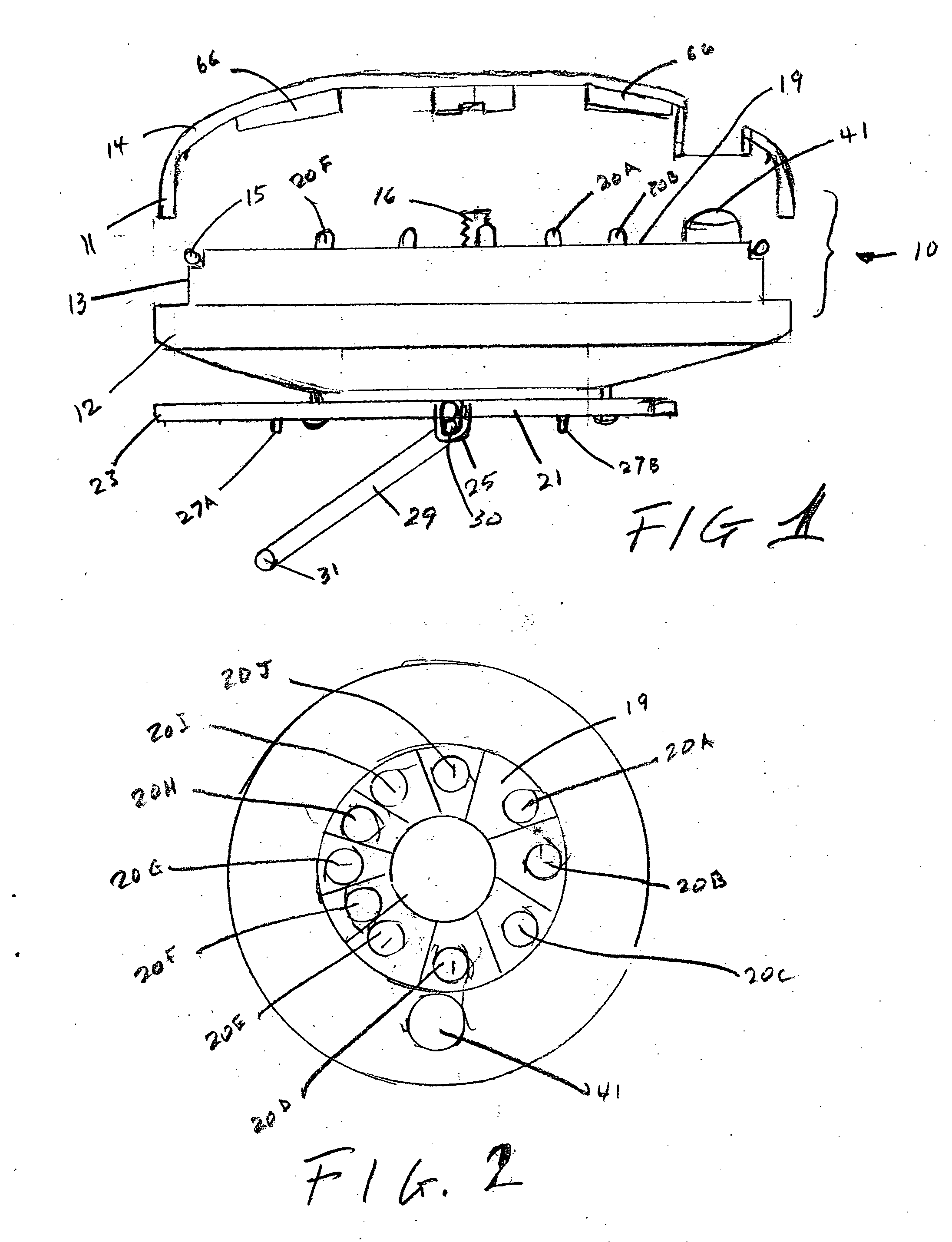

Hazard marker kit

A hazard marker kit has several components including a hazard light, a base for supporting the light in different angular orientations on different surfaces, a translucent cone, and a staff with attached pennant. The hazard light is housed within a disc shaped high impact plastic housing, an upper portion of which is transparent. A plurality of LEDs are circularly disposed proximal to the side of the upper portion. A ring counter provides signals to transistors that sequentially drive the LEDs. Excitation provided to the ring counter is controlled to cause a desired current through the LEDs to simulate a rotating beacon, a flashing beacon or a continuous light.

Owner:SAFE & SOUND SAFETY CORP

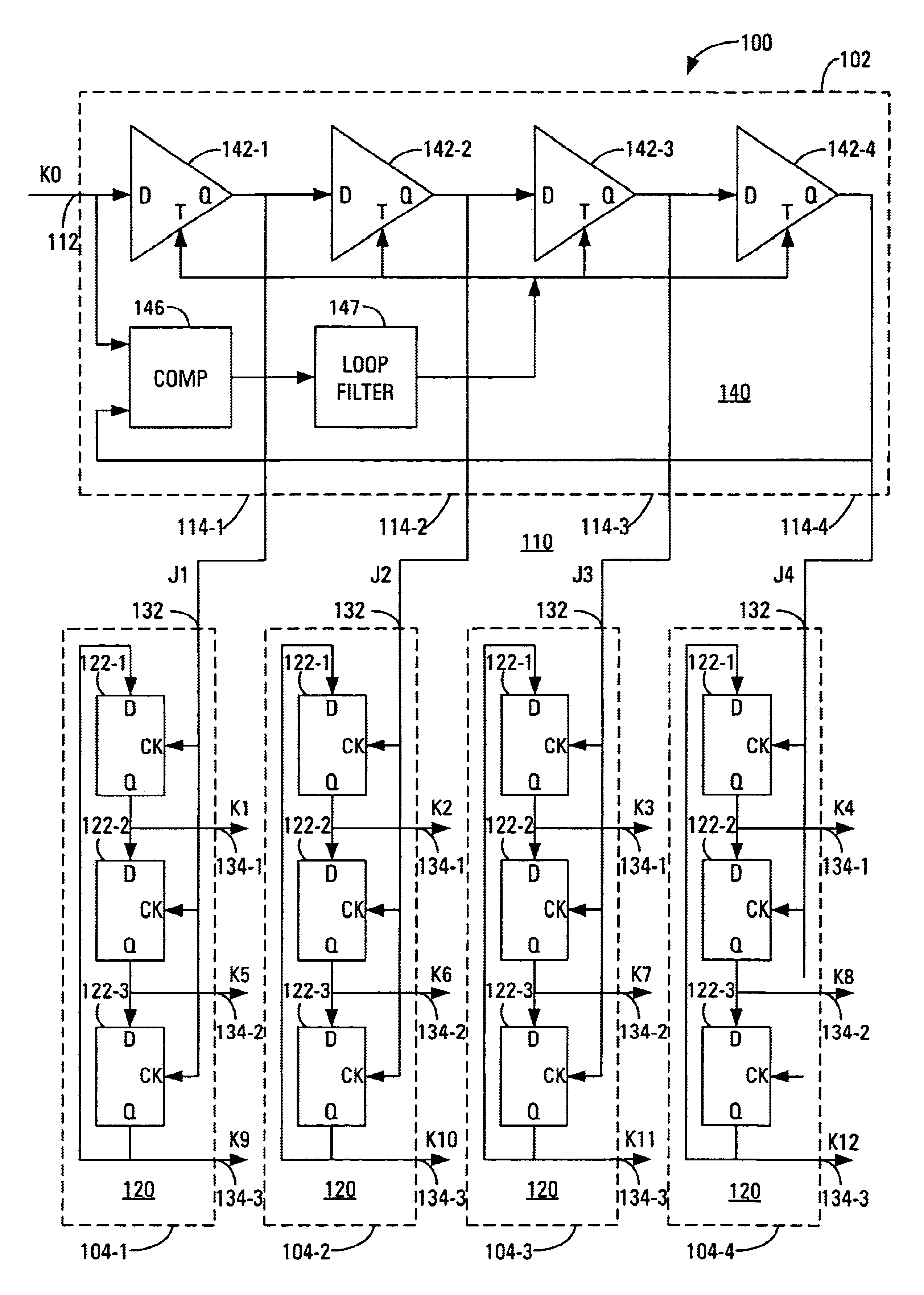

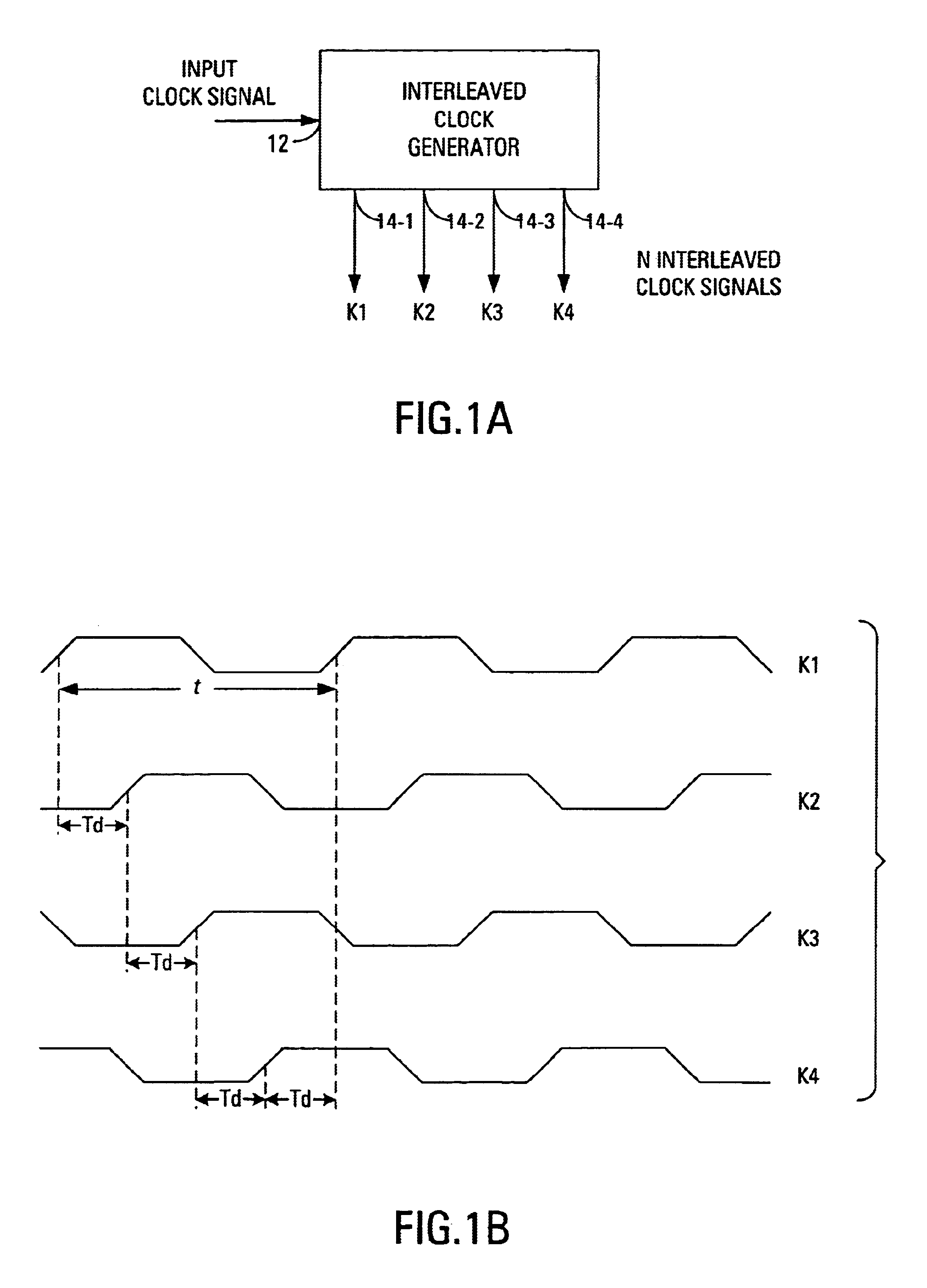

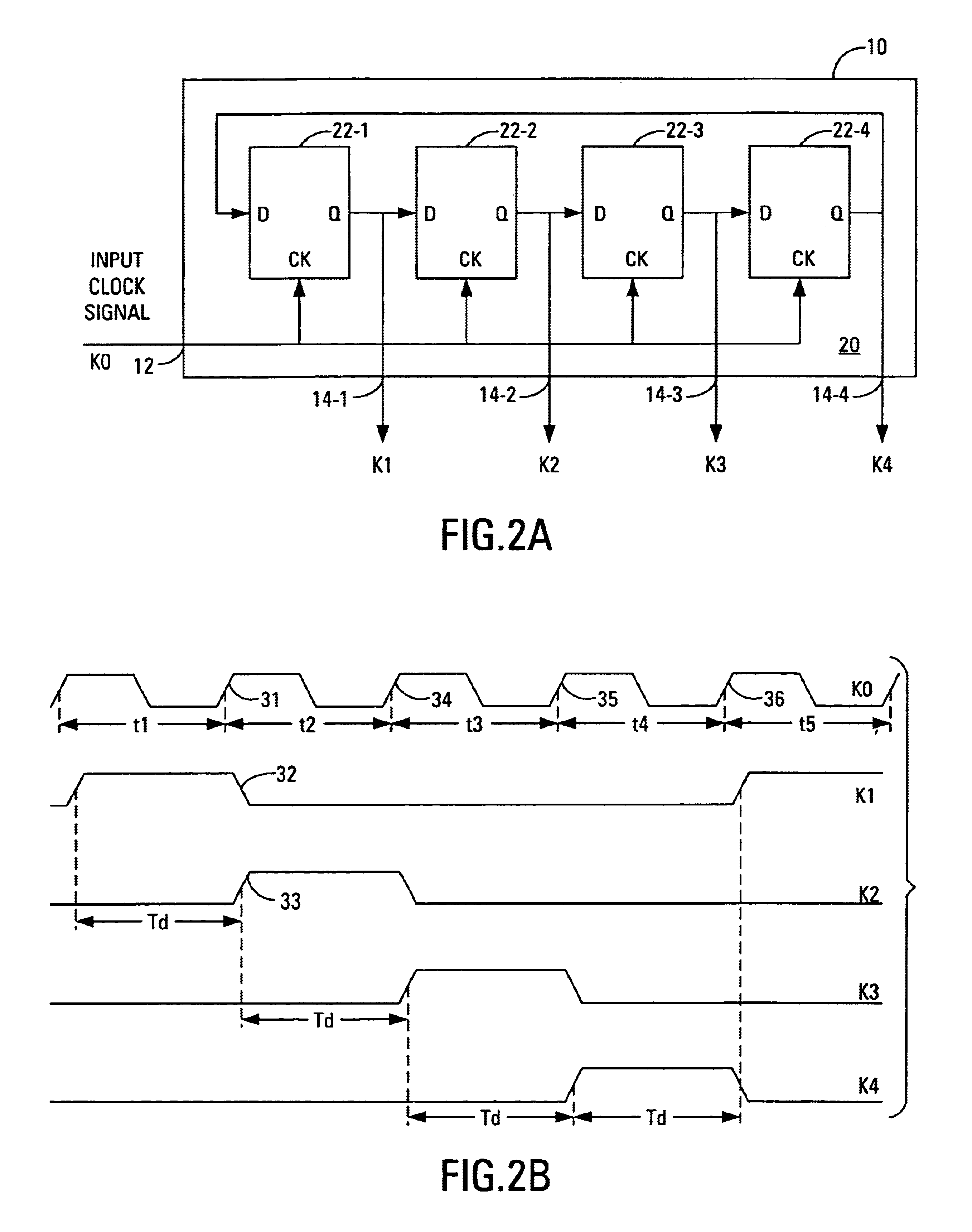

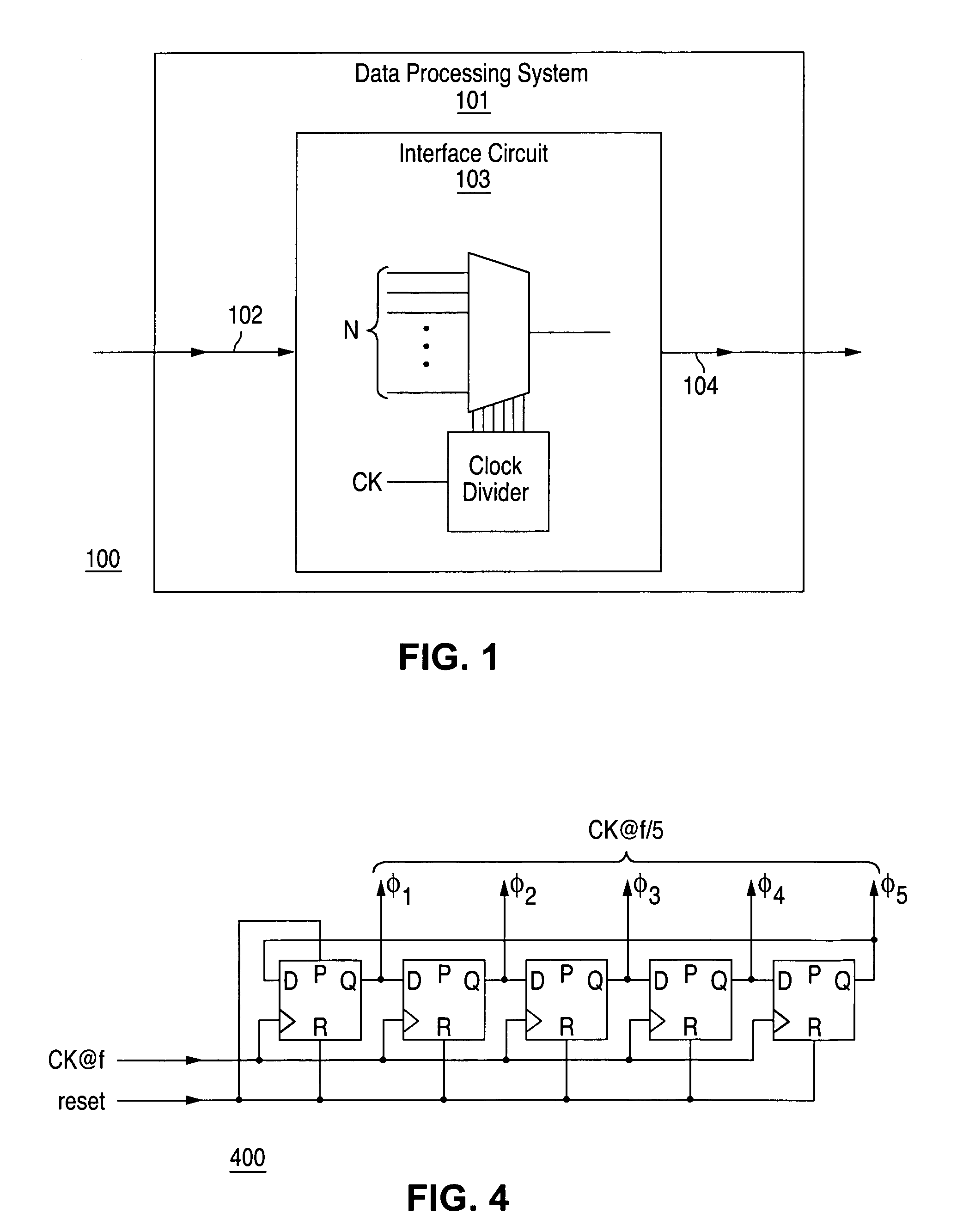

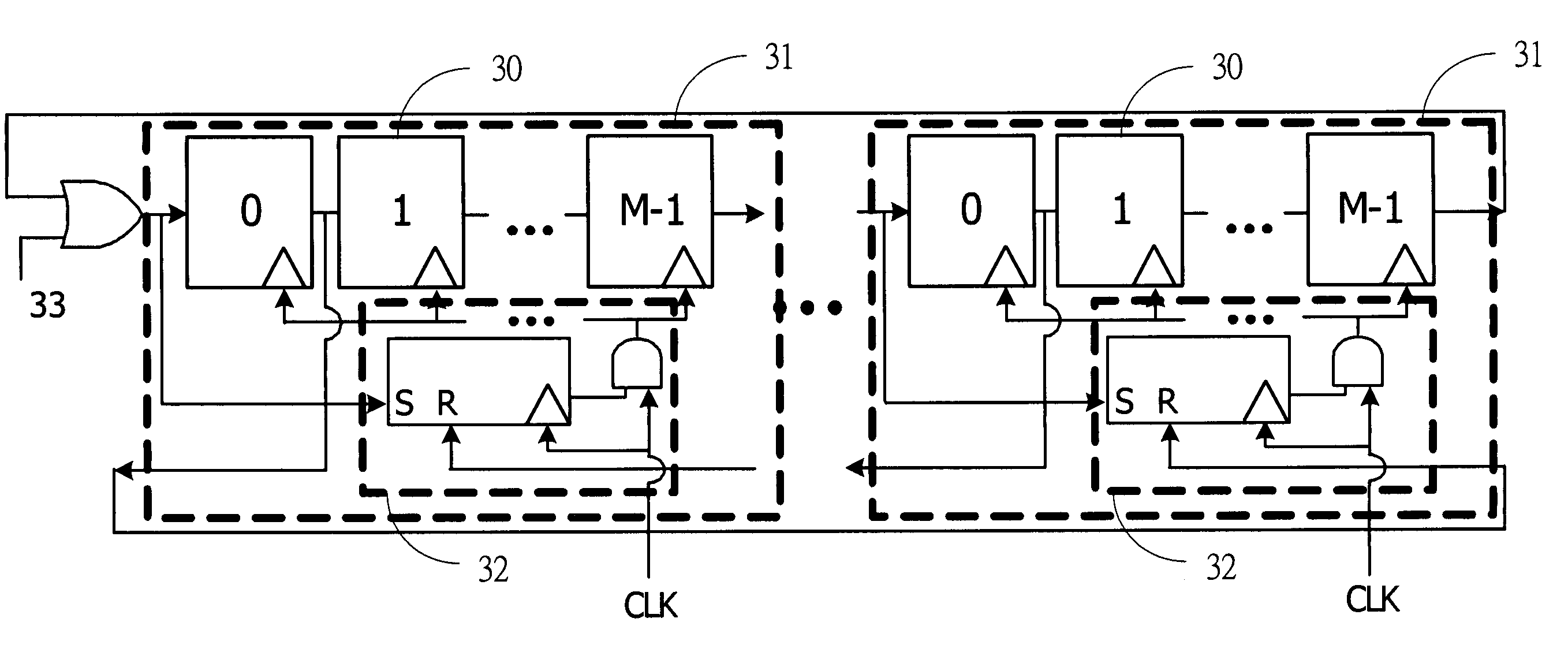

Interleaved clock signal generator having serial delay and ring counter architecture

InactiveUS6956423B2Less jitterLittle timePulse automatic controlContinuous to patterned pulse manipulationRing counterClock generator

Owner:KEYSIGHT TECH

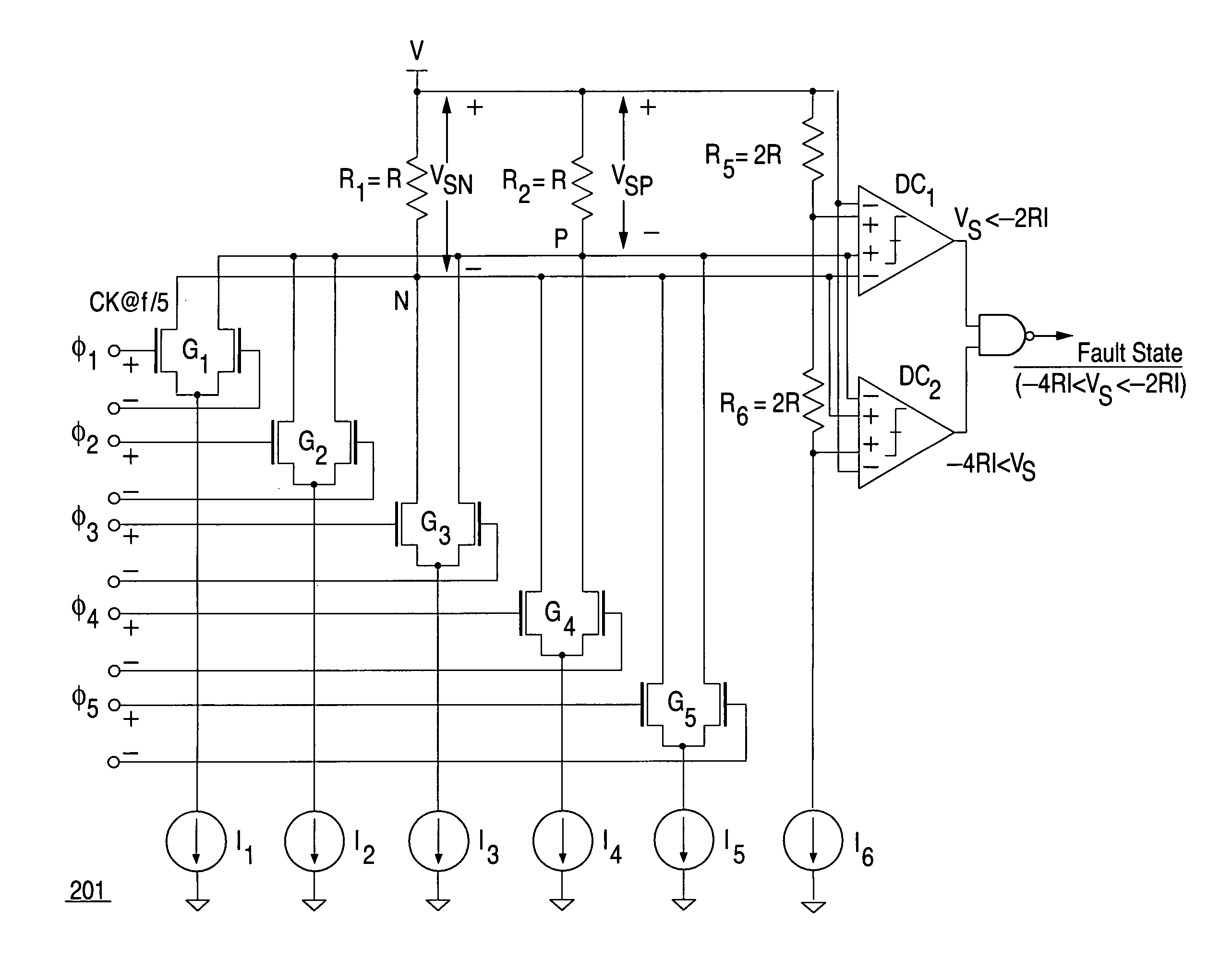

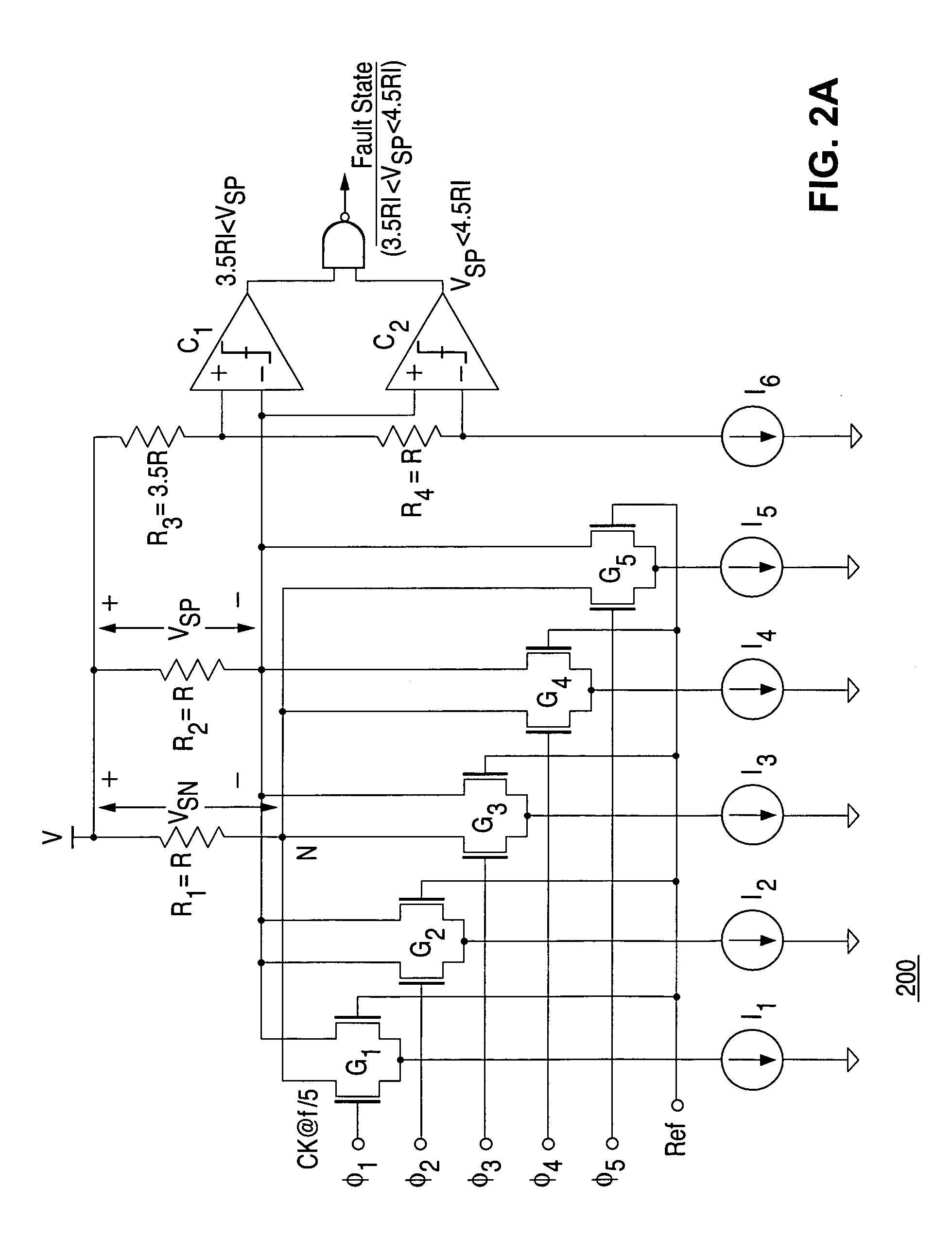

Fault state detection mechanism for a ring-counter-based frequency divider-by-N that generates non-overlapping N-phases of divide-by-N clocks with 1/N duty ratio

ActiveUS6950490B1Continuously circulated pulse countersCounting chain synchronous pulse countersRing counterEngineering

A fault state detector for a ring counter is formed from unit current sources each switched under the control of a different one of the outputs of the ring counter. The currents switched in that manner are passed through a unit resistance to generate a voltage signal proportional to the number of asserted outputs from the ring counter. The voltage signal is compared to boundary reference values for valid states of the ring counter outputs and, if the voltage signal is not between the boundary reference values, a fault state is indicated.

Owner:NAT SEMICON CORP

High-speed data buffer

InactiveUS6882192B2Increase speedImprove Timing MarginPulse automatic controlGenerating/distributing signalsTiming marginRing counter

Disclosed is a high-speed data buffer, wherein a buffer circuit composed of a ring counter is divided into two sampling circuits composed of a rising-edge portion and a falling-edge portion, and both of the two sampling circuits comprises a trigger circuit and a sampling clock generation circuit. In such a manner, the excess pulse edge can be ensured to occur before the correct edge so that the error data caused by the excess pulse can be over-written with the correct data input afterwards. Therefore, a clock cycle of timing margin can be obtained and the data stored in the data buffer can be ensured to be correct.

Owner:VIA TECH INC

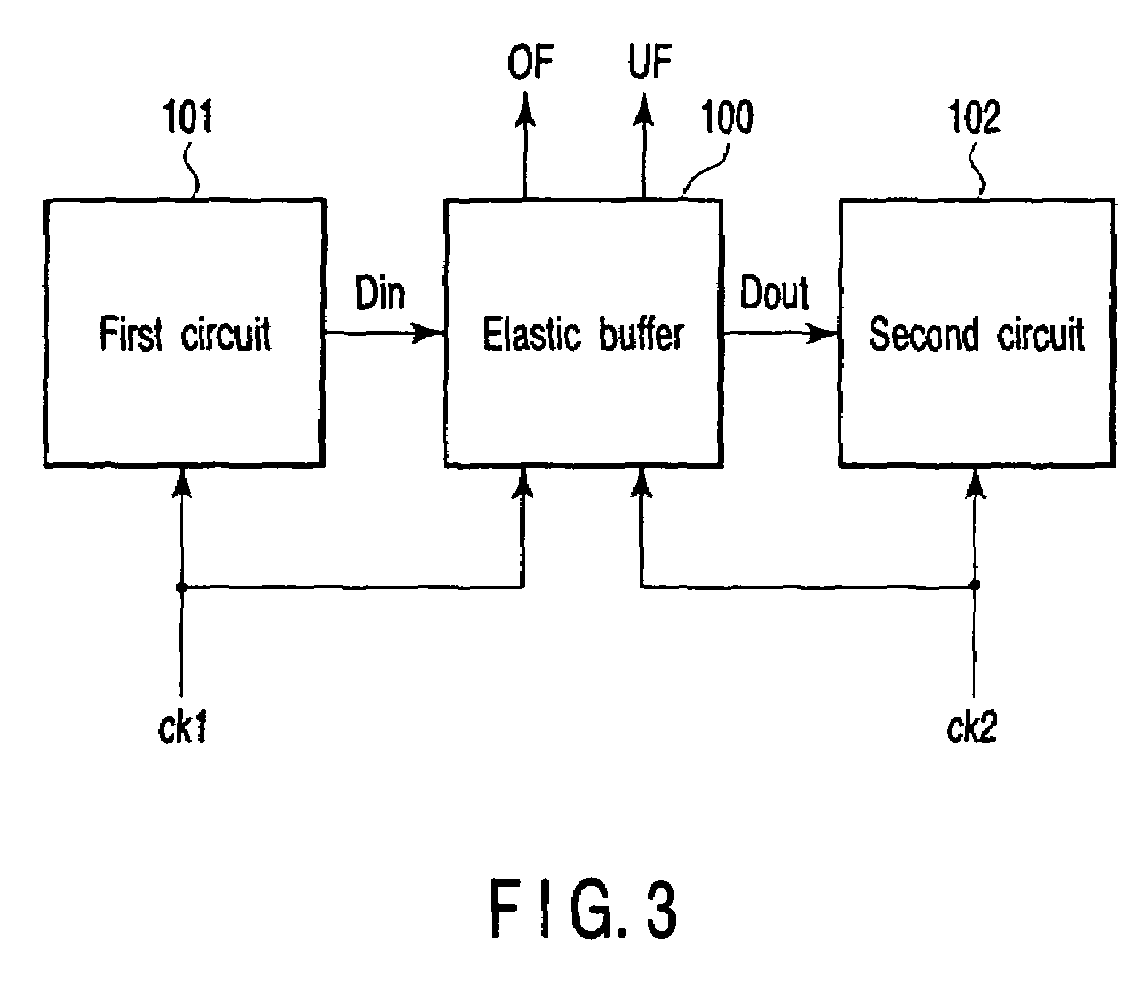

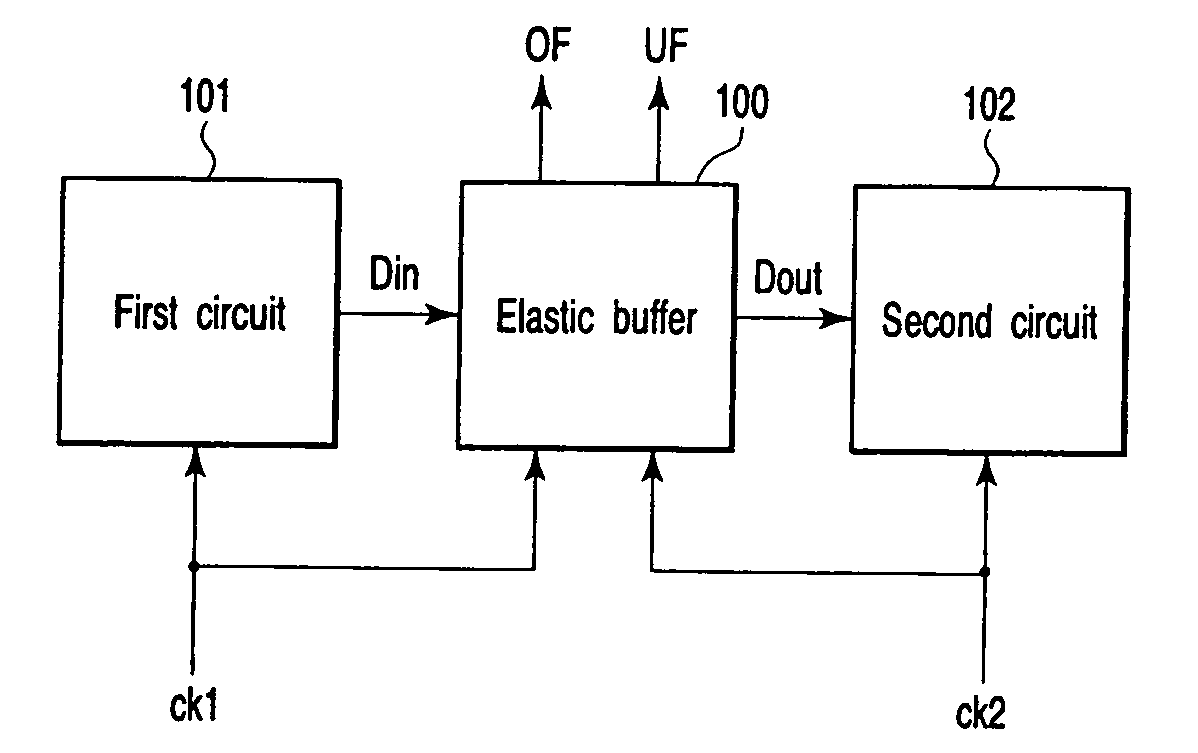

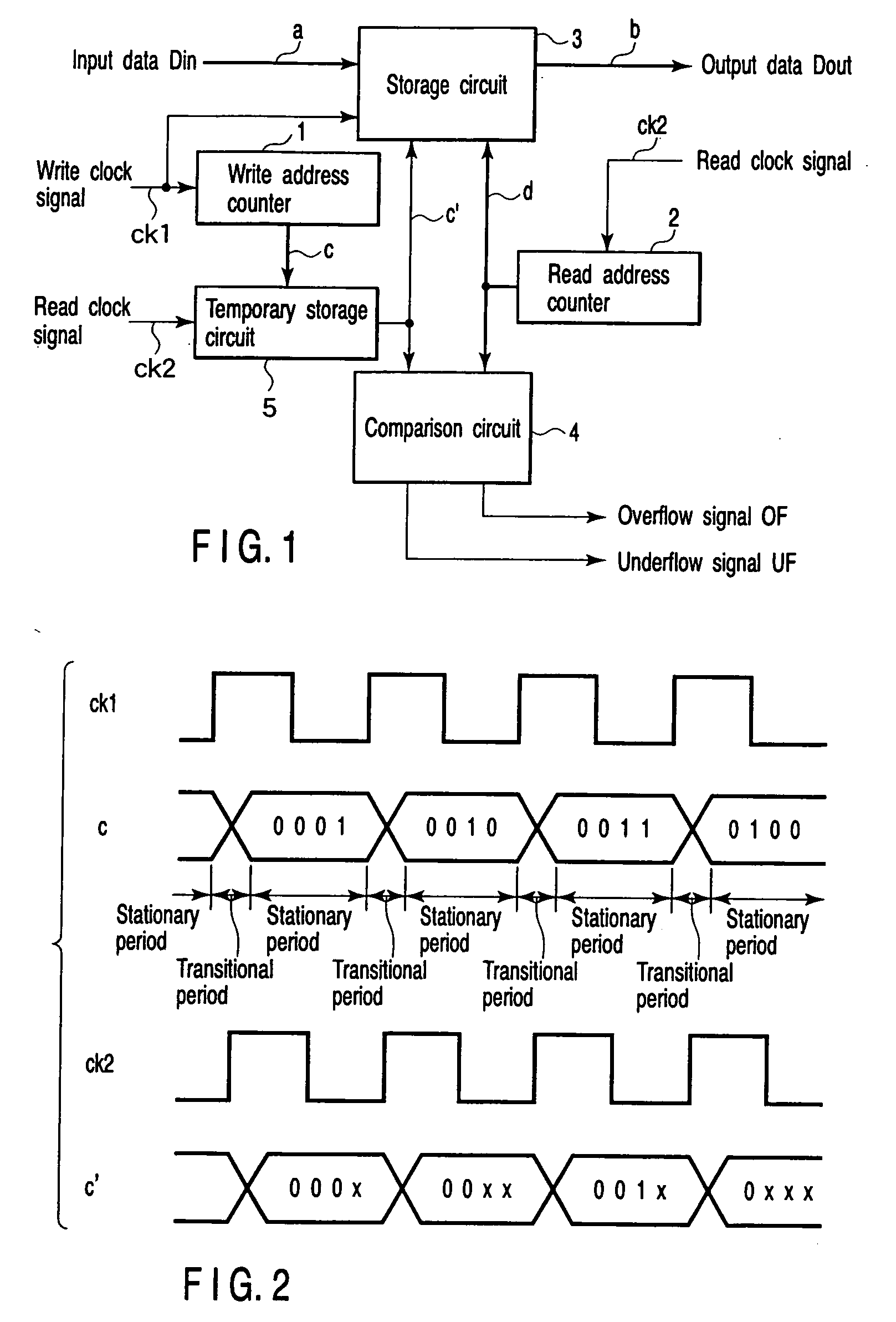

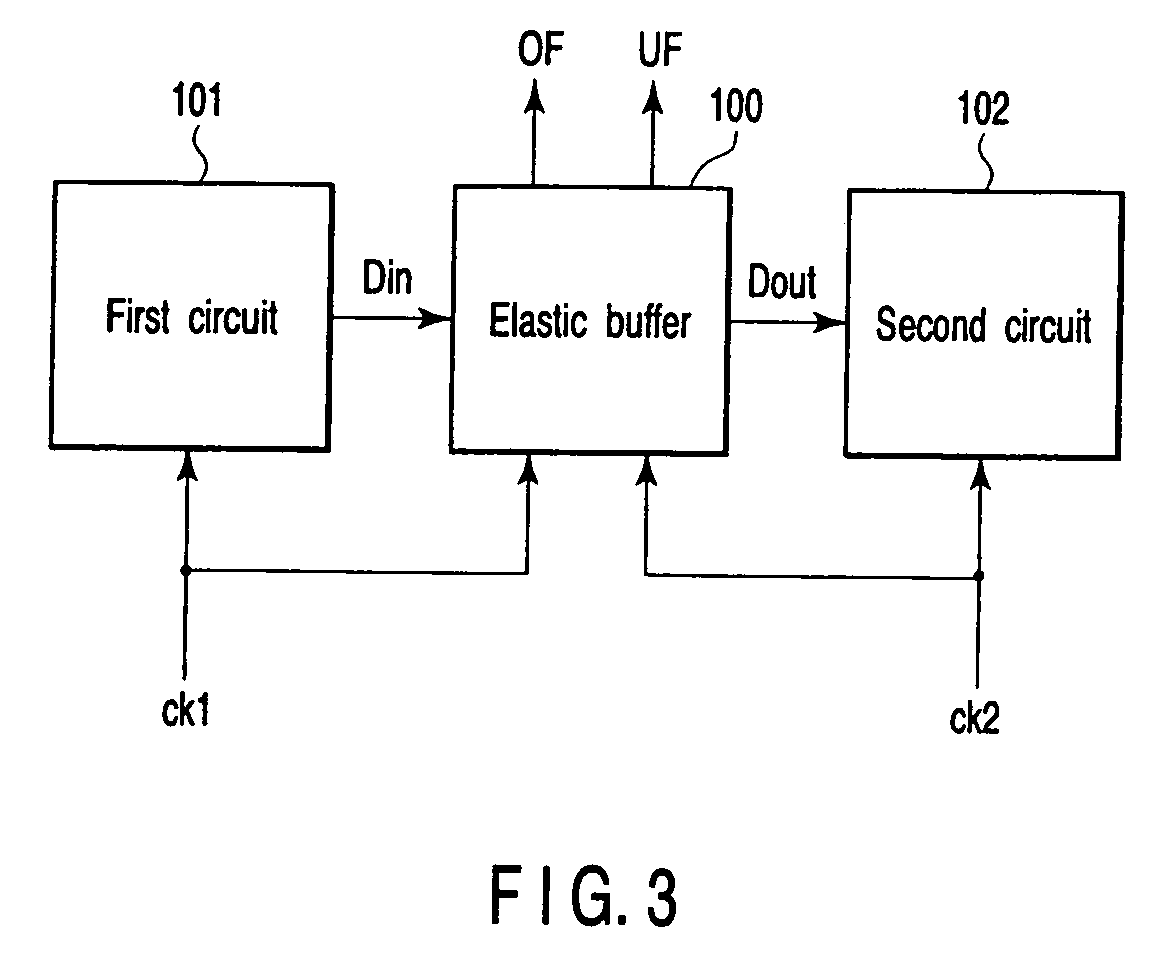

Elastic buffer

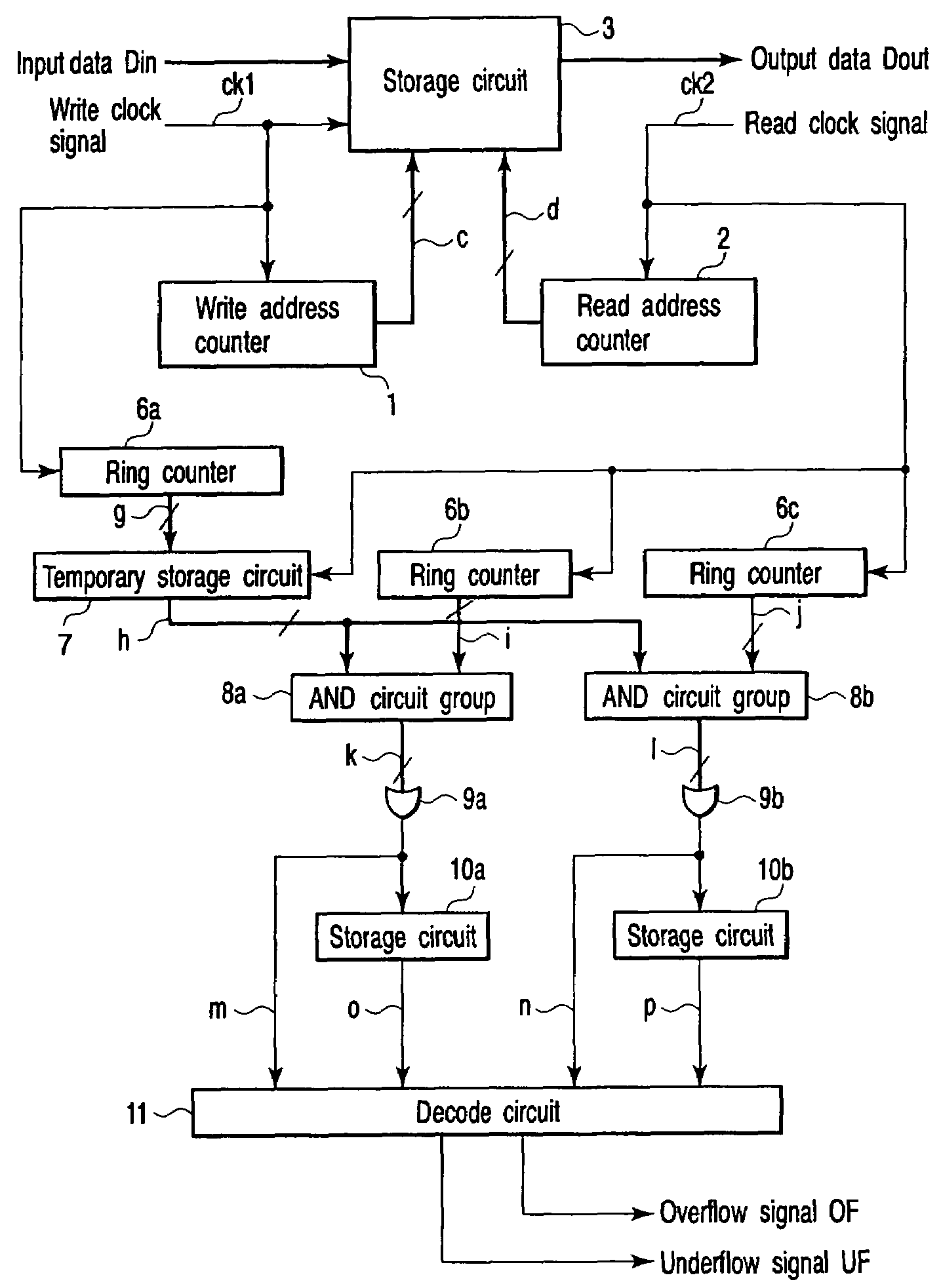

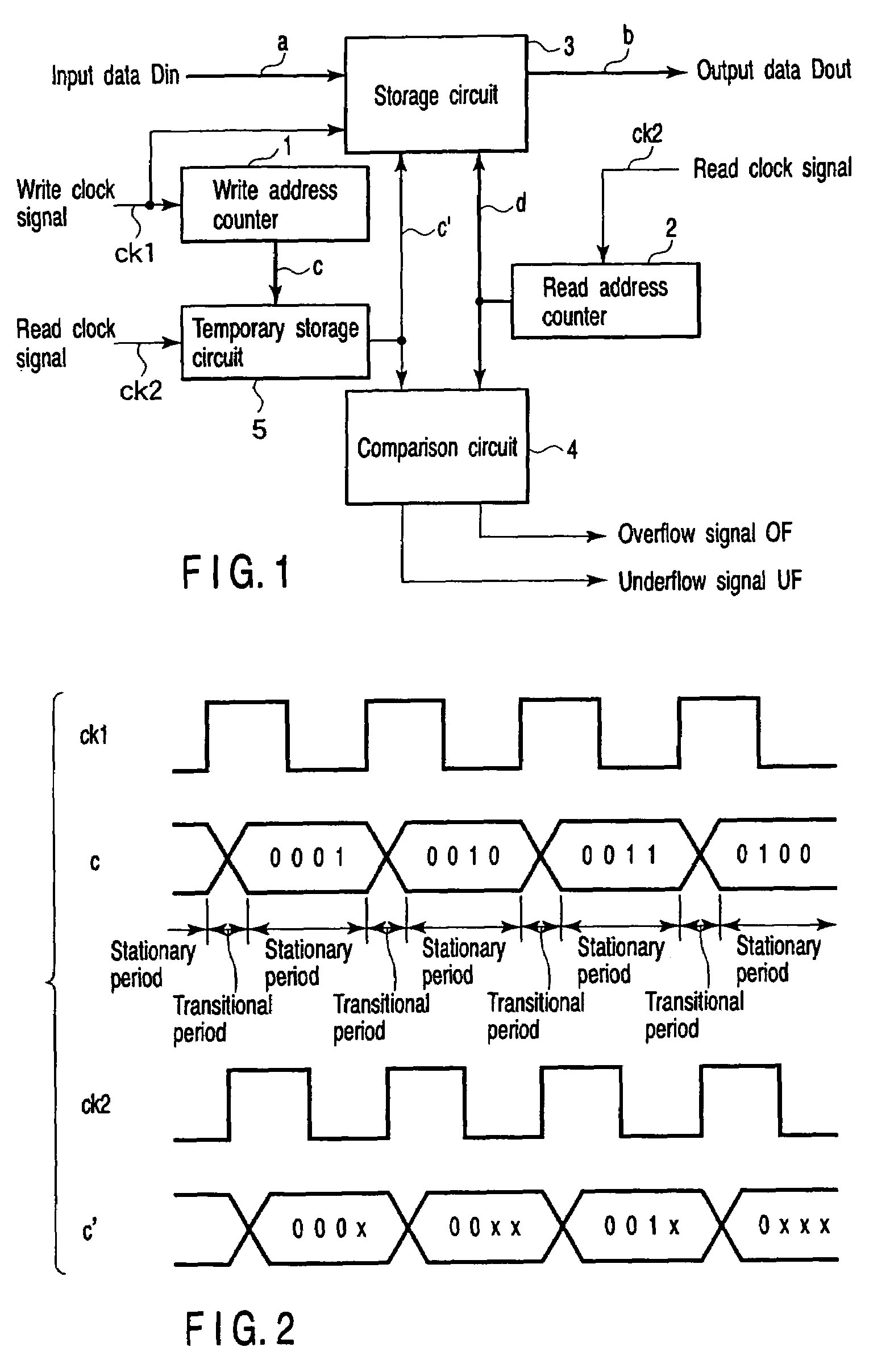

ActiveUS7519746B2Input/output processes for data processingData conversionRing counterTertiary storage

An output of a first ring counter is held in a first storage circuit. Outputs of a second ring counter and the first storage circuit are input to a first AND circuit group. An output of a third ring counter and an output of the first storage circuit are input to a second AND circuit group. Outputs of the first AND circuit group are input to a first OR circuit. Outputs of the second AND circuit group are input to a second OR circuit. An output of the first OR circuit is stored in a second storage circuit. An output of the second OR circuit is stored in a third storage circuit. Outputs of the first and second OR circuits and outputs of the second and third storage circuits are supplied to a decode circuit, and are decoded to output an overflow signal and an underflow signal.

Owner:KK TOSHIBA

Printing head, image printing apparatus using the same, and control method therefor

InactiveUS20050243128A1Increase the number ofReduce degradationPrintingRing counterRelative pressure

This invention provides a printing head which can prevent an increase in the number of block enable signal lines, and can prevent changes in printing ink density caused by interference due to the relative pressures of nozzles generated in ink discharge, and an image printing apparatus using the printing head. For this purpose, an increase in the number of input signal lines along with an increase in the number of blocks is prevented using a block clock signal or the like instead of a block enable signal as an input signal to the printing head. Three ring counters generate signals having different nozzle driving orders. These signals are selectively used by a ring counter selection signal. Ink is not always discharged from the nozzles in the same output order. This can prevent changes in ink density caused by pressure interference.

Owner:CANON KK

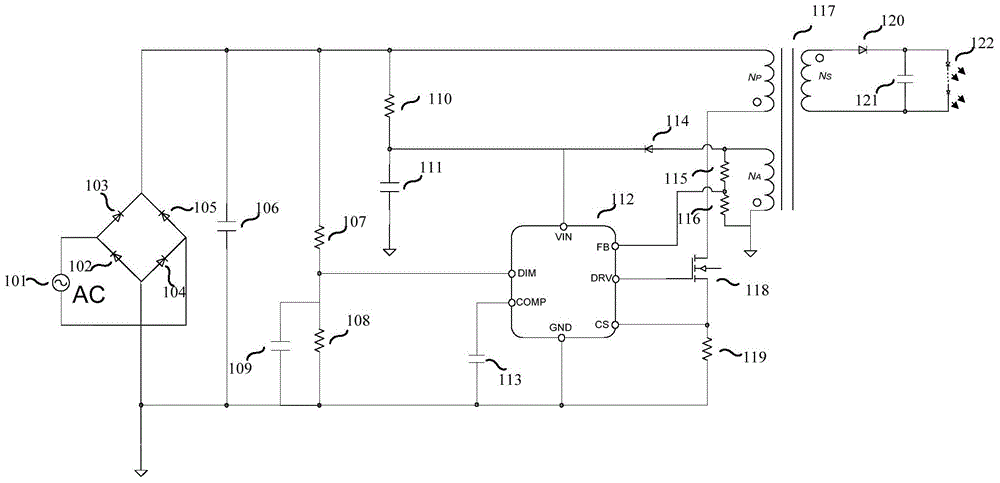

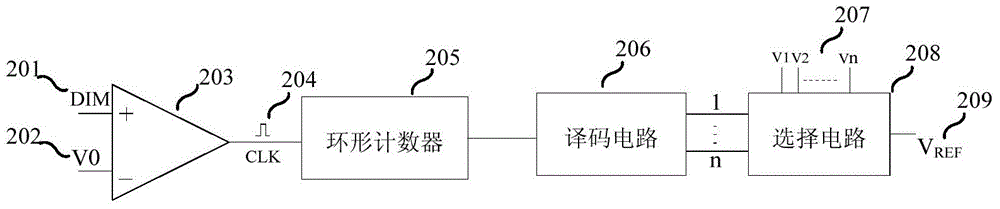

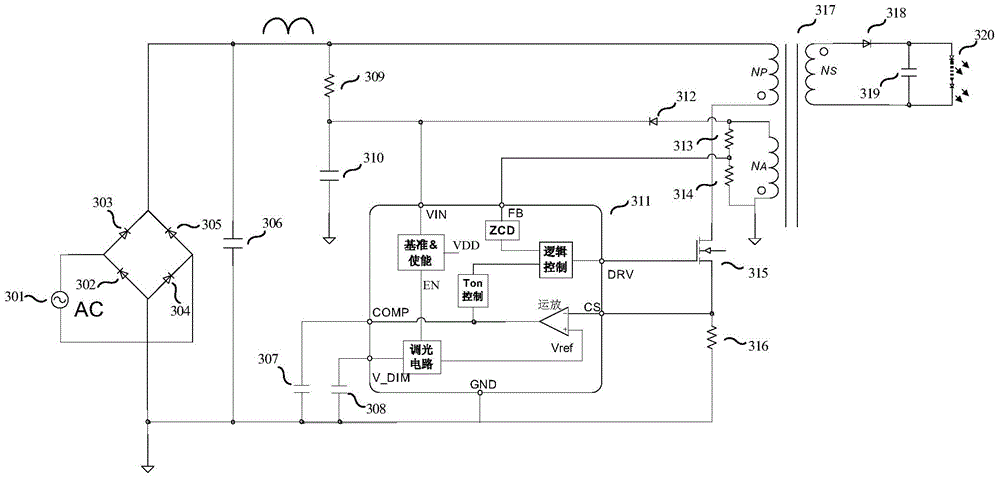

LED sectional dimming circuit

The invention provides an LED sectional dimming circuit which comprises a dimming detection end, a power source generation circuit, an annular counter, a decoder and a selection circuit, wherein the dimming detection end is connected with an enable signal En in an LED driving chip and is used for detecting power failure and power on, caused by a dimming switch, of a system; the power source generation circuit is used for providing a power source for circuits in the LED sectional dimming circuit; the output end of the power source generation circuit is connected with the annular counter and the decoder; the input end of the annular counter is connected with the dimming detection end, and the annular counter is used for calculating the frequency of pressing the dimming switch; the input end of the decoder is connected with the annular counter, and the decoder is used for decoding an output signal of the annular counter to control the output of the selection circuit; the selection signal end of the selection circuit is connected with the decoder, the input end of the selection circuit is connected with reference voltage of each section, and the selection circuit is used for selecting the needed reference voltage as output. The LED sectional dimming circuit is wide in application range and can be applied to isolating, non-isolating and floating LED driving circuits and LED driving circuits with various frameworks of PFC (power factor correction) and the like.

Owner:WUXI SI POWER MICRO ELECTRONICS

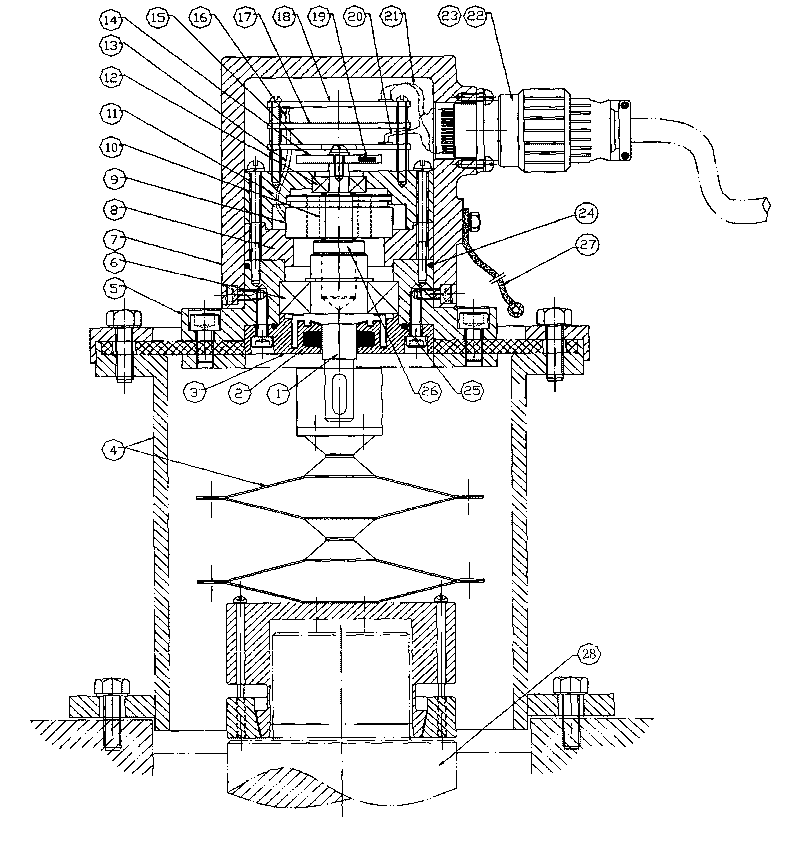

Sealing ring machining method

InactiveCN105563030AEasy to processGuaranteed machining accuracyEngine sealsRing counterMachining process

The invention discloses relates to the field of machining, in particular to a sealing ring machining method. The method includes the following steps that a lathe supporting clamp is used for clamping blanks, rough machining and finish machining are performed on the front side of a sealing ring through an end face tool till the required size is achieved; rough machining and finish machining are performed on the outer circle of the sealing ring through an outer circle tool, and chamfering is performed; a lathe holding clamp is used for holding the outer circle of the sealing ring, and the inner circle of the sealing ring is machined through an inner circle tool; rough machining and finish machining are performed on the back side of the sealing ring through the end face tool till the required size is achieved, and chamfering is performed through a chamfering tool; a workpiece is clamped through a soft claw, and rough machining and finish machining are performed on the back side of the sealing ring; the workpiece is disassembled, an inner hole of the workpiece is supported through the lathe supporting clamp, and the outer circle of the sealing ring is turned through the outer circle tool; semi-finish machining and finish machining are performed on the front side of the sealing ring through the end face tool till the required thickness size is achieved; the workpiece is installed on a drilling machine, and a sealing ring front side hole is drilled; and a sealing ring counter bore is milled. By means of the sealing ring machining method, the machining process is simple, machining precision can be guaranteed, production efficiency is improved, and production cost is reduced.

Owner:SHAANXI HI-TECH IND CO LTD

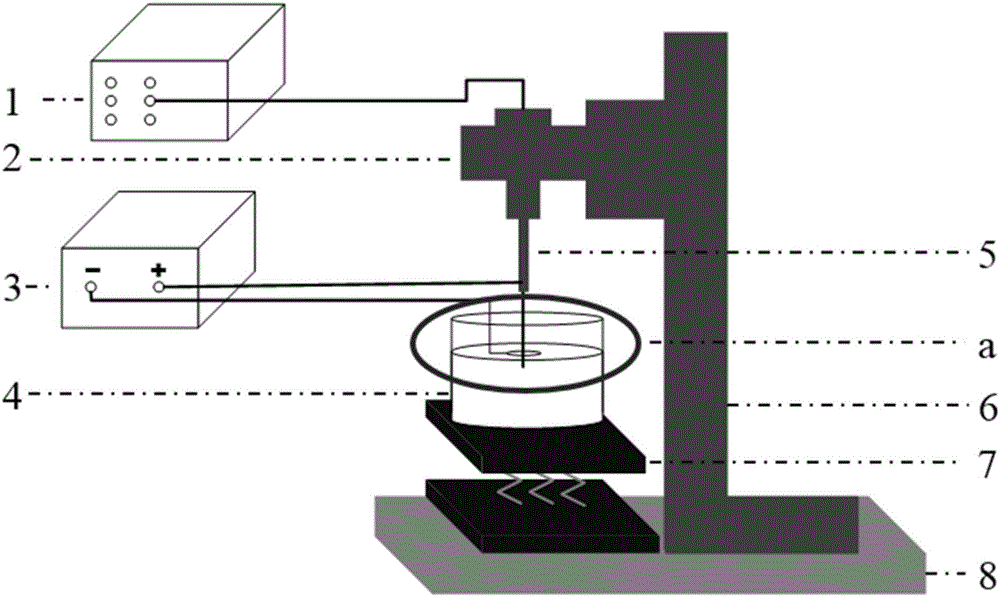

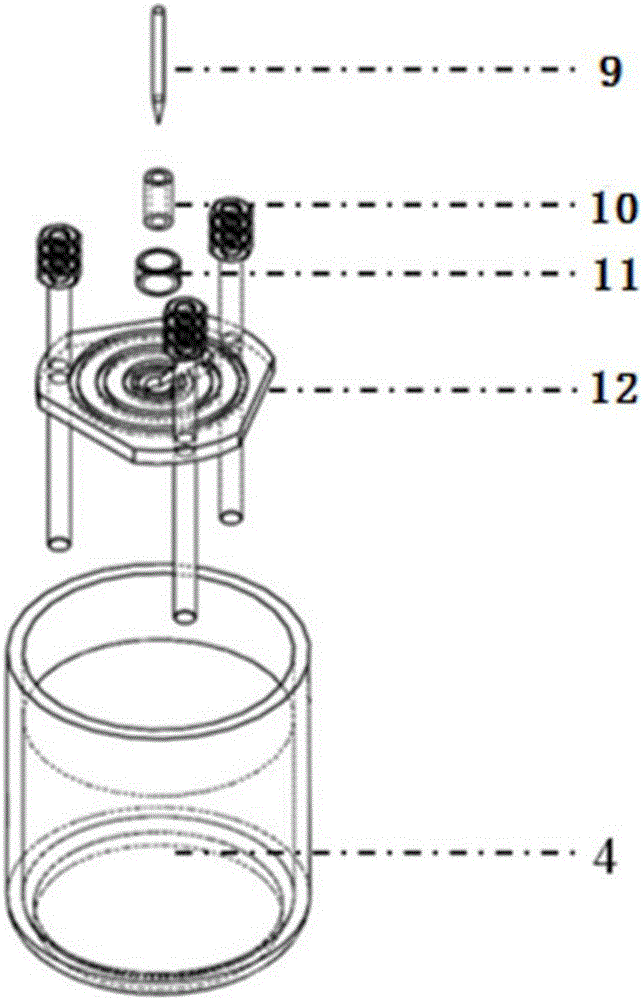

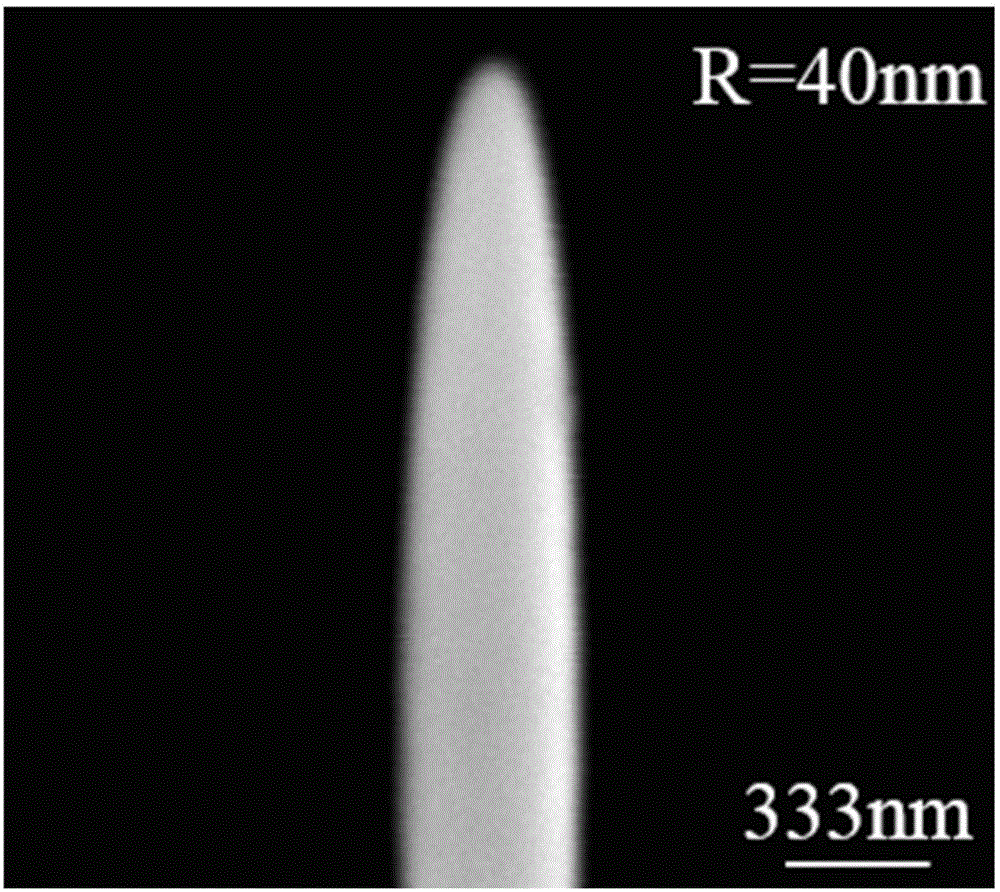

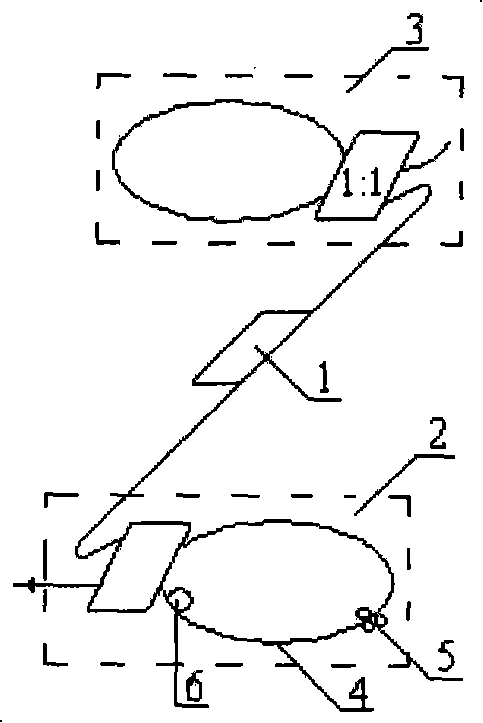

Preparation apparatus and method of ultra-low roughness tungsten probe

InactiveCN106501555AControl lengthEfficient separationScanning probe microscopyEngineeringElectrochemical corrosion

The invention discloses a preparation apparatus and method of an ultra-low roughness tungsten probe. The preparation apparatus of an ultra-low roughness tungsten probe includes a damping platform, wherein the damping platform is connected with an L type fixed support; the L type fixed support is connected with a motion control system for driving motion of a tungsten filament; the damping platform is also provided with a container filled with etchant solution; the container filled with etchant solution is arranged just below the tungsten filament; a copper ring counter electrode is arranged in the container filled with etchant solution; a counter electrode isolation system is also arranged in the container filled with etchant solution, and is used for isolating the copper ring counter electrode from the tungsten filament; and the copper ring counter electrode and the tungsten filament are respectively connected with the cathode and anode of a digital control DC source. Based on a dynamic electrochemical corrosion principle, the preparation apparatus and method of an ultra-low roughness tungsten probe. The preparation apparatus of an ultra-low roughness tungsten probe can prepare an ultra-low roughness tungsten probe on the premise of effectively controlling the contour and the ratio length / diameter ratio of the probe point.

Owner:XI AN JIAOTONG UNIV

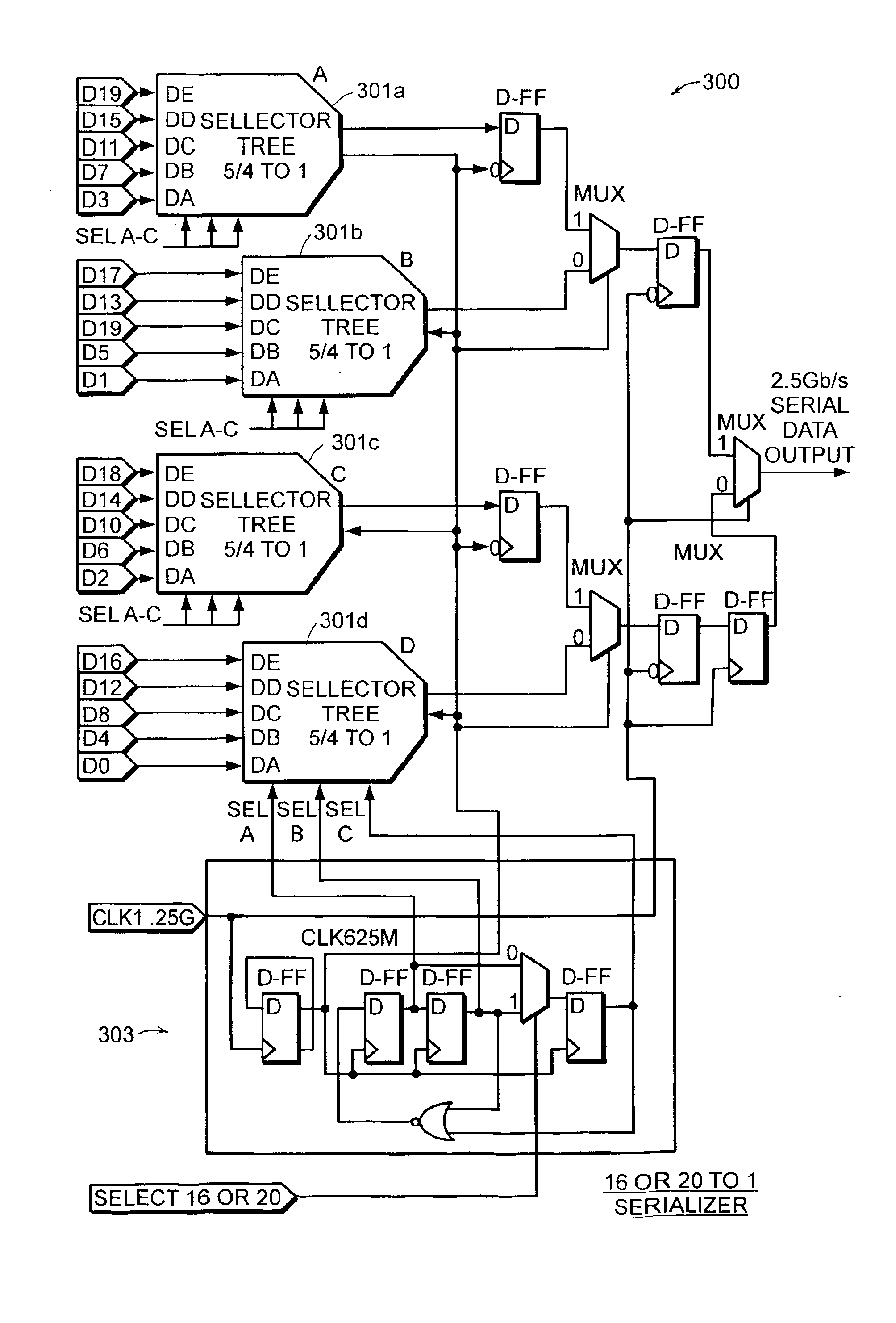

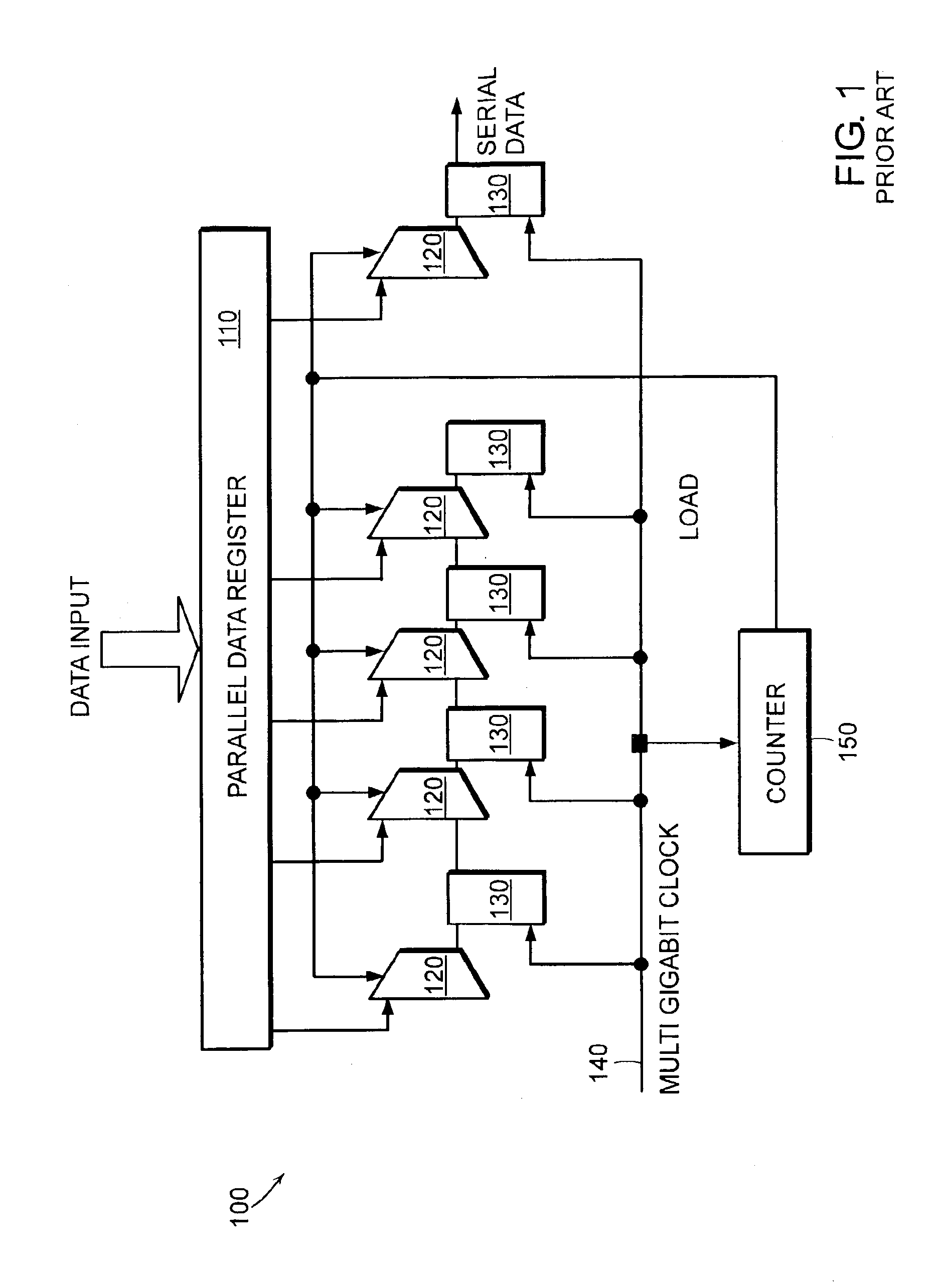

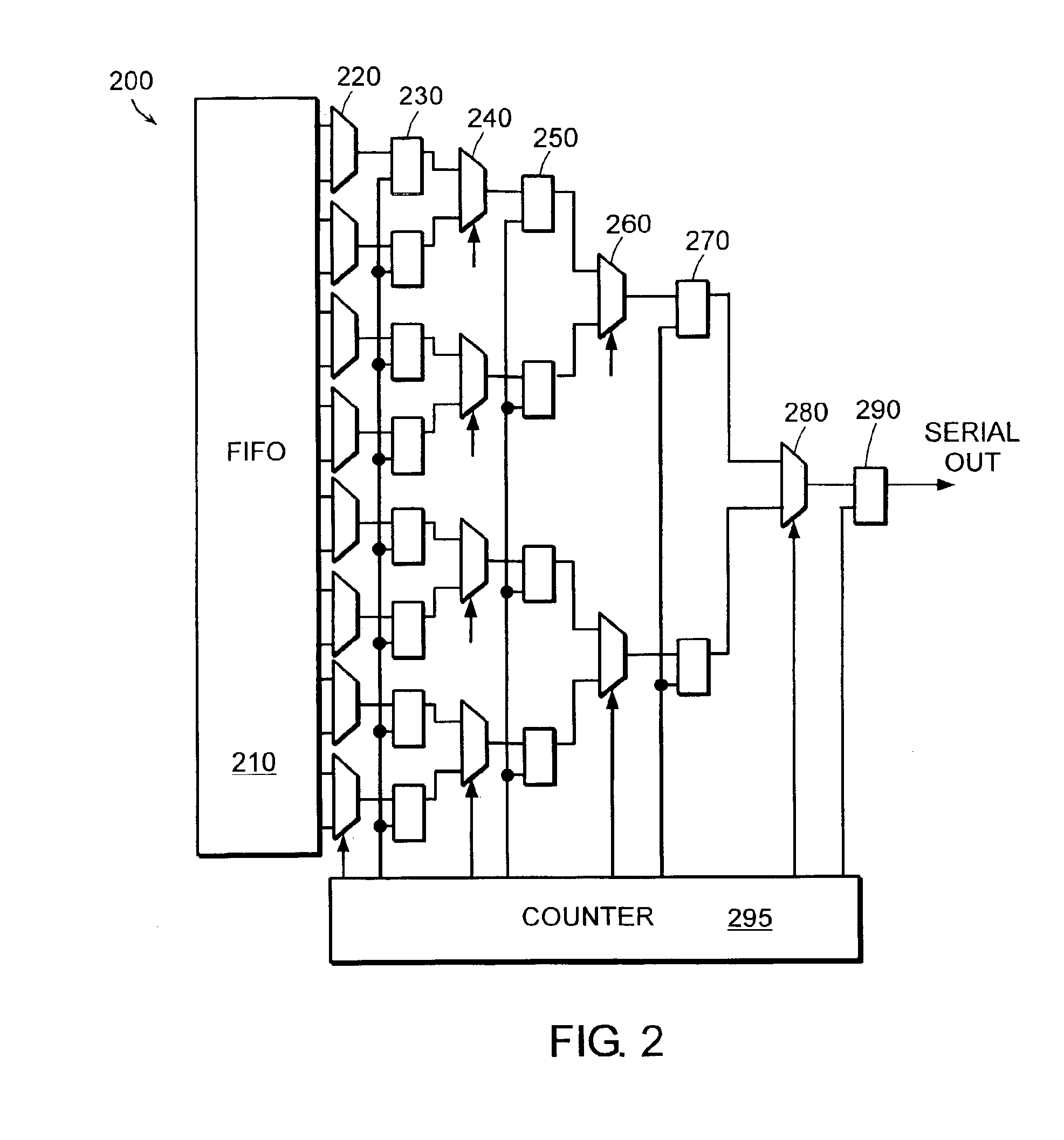

Method and apparatus for reducing power requirements in a multi gigabit parallel to serial converter

InactiveUS6977981B2Reduced Power RequirementsReduce bit widthTime-division multiplexSynchronisation signal speed/phase controlMultiplexingRing counter

A variable-mode digital logic circuit is provided for accepting and serializing a parallel data word, so that the parallel data word may be transmitted from the digital logic circuit over a single one-bit wide trace. In some embodiments, the variable-mode digital logic circuit may include a plurality of parallel data traces for receiving the parallel dataword, a plurality of select-capable multiplexor circuits for sequentially activating certain ones of the parallel data traces and for multiplexing the received data into a serial data stream, a ring counter for controlling a frequency of specific operations performed within the circuit, and at least one additional multiplexor circuit array for receiving data output from the plurality of select-capable multiplexor circuits and for further serializing the received data for output on the single one-bit wide trace. The digital logic circuit may be adapted to operate according to one of a plurality of variable modes.

Owner:GULA CONSULTING LLC

Elastic buffer

ActiveUS20060075162A1Input/output processes for data processingData conversionRing counterEngineering

An output of a first ring counter is held in a first storage circuit. Outputs of a second ring counter and the first storage circuit are input to a first AND circuit group. An output of a third ring counter and an output of the first storage circuit are input to a second AND circuit group. Outputs of the first AND circuit group are input to a first OR circuit. Outputs of the second AND circuit group are input to a second OR circuit. An output of the first OR circuit is stored in a second storage circuit. An output of the second OR circuit is stored in a third storage circuit. Outputs of the first and second OR circuits and outputs of the second and third storage circuits are supplied to a decode circuit, and are decoded to output an overflow signal and an underflow signal.

Owner:KK TOSHIBA

Gain enhancement type N-channel active band-pass filter adopting differential clock

InactiveCN104953981AHigh gainEliminate even harmonicsFrequency selective two-port networksCapacitanceBand-pass filter

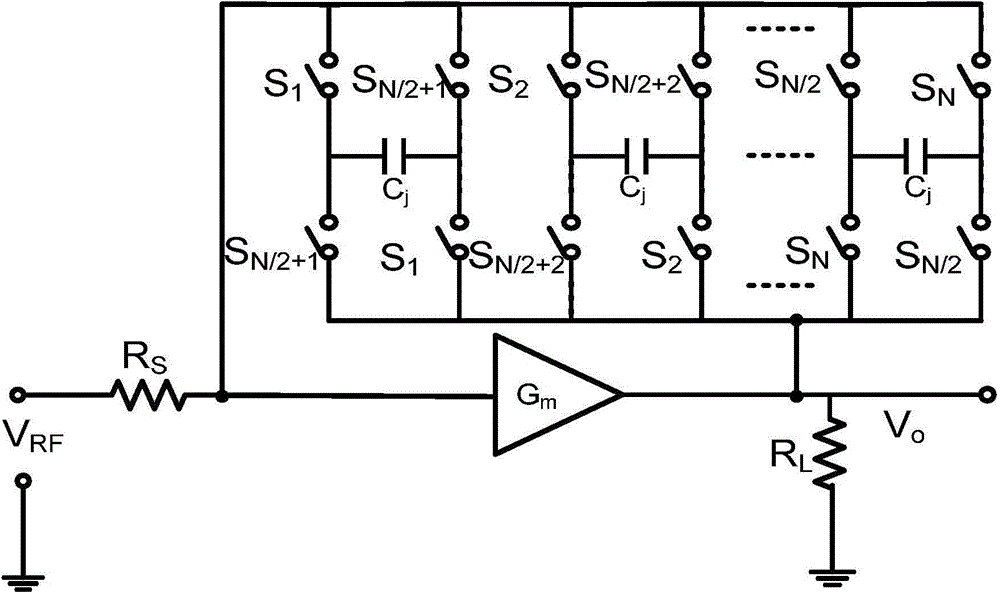

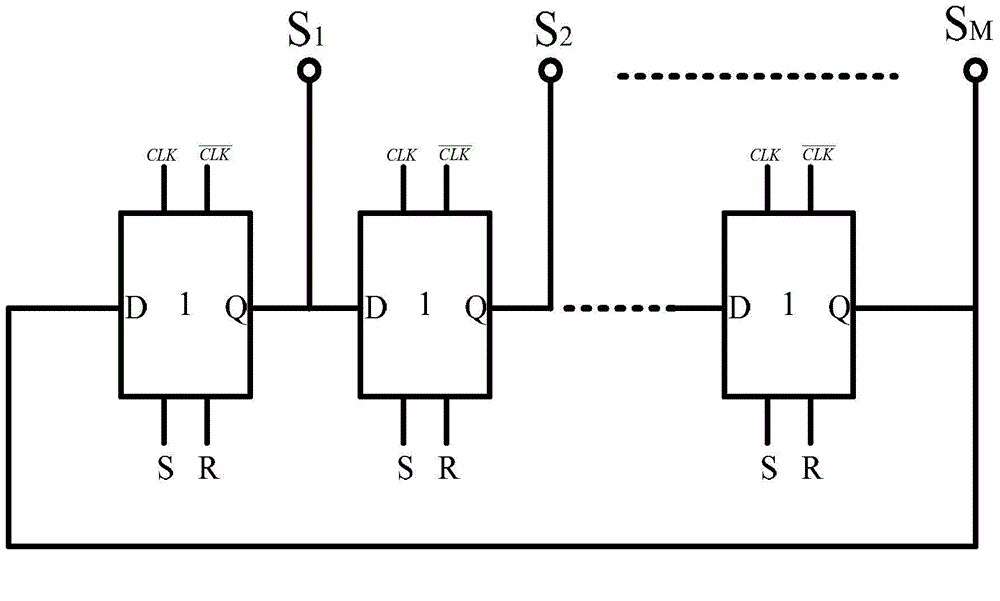

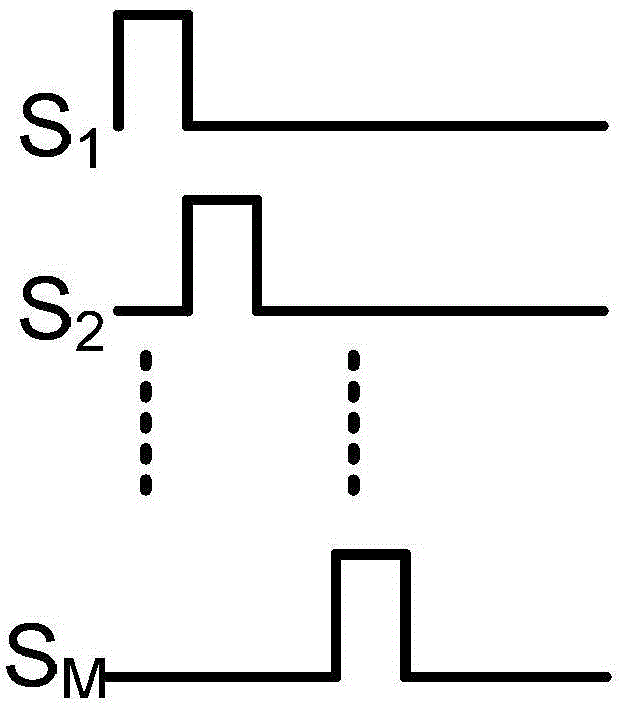

The invention discloses a gain enhancement type N-channel active band-pass filter adopting a differential clock. The gain enhancement type N-channel active band-pass filter comprises an N frequency-division ring counter, a differential clock circuit and an operational transconductance amplifier, wherein the N frequency-division ring counter is formed by annularly connecting N D triggers; a sampling pulse sequence is output from the Q end of each D trigger; the differential clock circuit comprises N switch branches and N / 2 capacitors, and every two switch branches and one capacitor constitute an H-shaped circuit structure; switches in the upper left position and the lower right position of each H-shaped circuit structure are simultaneously connected with the Q end of one D trigger of the N frequency-division ring counter, and switches in the lower left position and the upper right position of each H-shaped circuit structure are simultaneously connected with the Q end of another D trigger of the N frequency-division ring counter; two ends of the operational transconductance amplifier are connected to two ends of the differential clock circuit respectively. The gain enhancement type N-channel active band-pass filter has the characteristics of large adjustable range of center frequency and large gain.

Owner:GUANGXI NORMAL UNIV

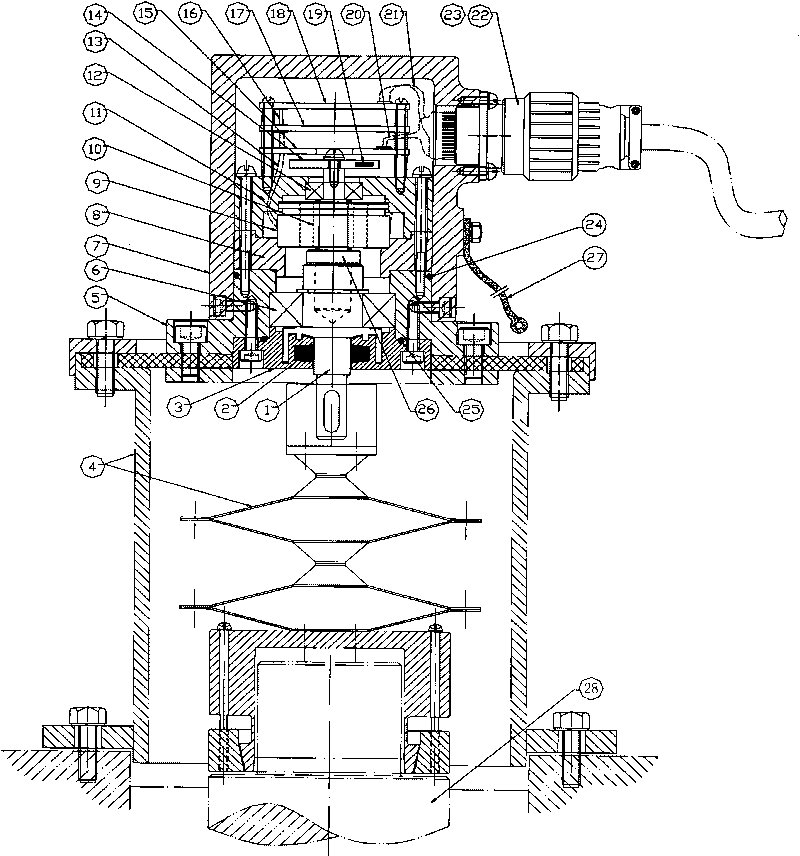

Heavy load absolute type multi-ring resolving encoder

InactiveCN101750106AImprove reliabilityHigh precisionConverting sensor output electrically/magneticallyRing counterEngineering

The invention discloses a heavy load absolute type multi-ring resolving encoder, comprising an input shaft, a high-speed sealing ring, a heavy load labyrinth bearing cap; a heavy load bearing support, a heavy load bearing, a heavy load casing; a resolving base; a resolving stator, a resolving rotor, a resolving bearing cap, a precision bearing, a ring-number sending disk, a multi-ring counter PCB board, an RD connecting wire, an RD intelligent decoder PCB board, a data output PCN board, a bearing support O-shaped sealing ring, a bearing cap O-shaped sealing ring, an insulating shaft and a grounded braid. According to the invention, by perfectly combining resolver with microprocessor decoding chip and heavy load structure, the heavy load absolute type multi-ring resolving encoder which completely overcomes all the deficiencies existing in photoelectric encoder is formed with the characteristics of small size, good integration, high reliability and high precision. Compared with the photoelectric encoder, the heavy load absolute type multi-ring resolving encoder is especially prominently superior in position / speed feedback systems requiring high precision and high reliability.

Owner:BEIJING ARITIME INTELLIGENT CONTROL

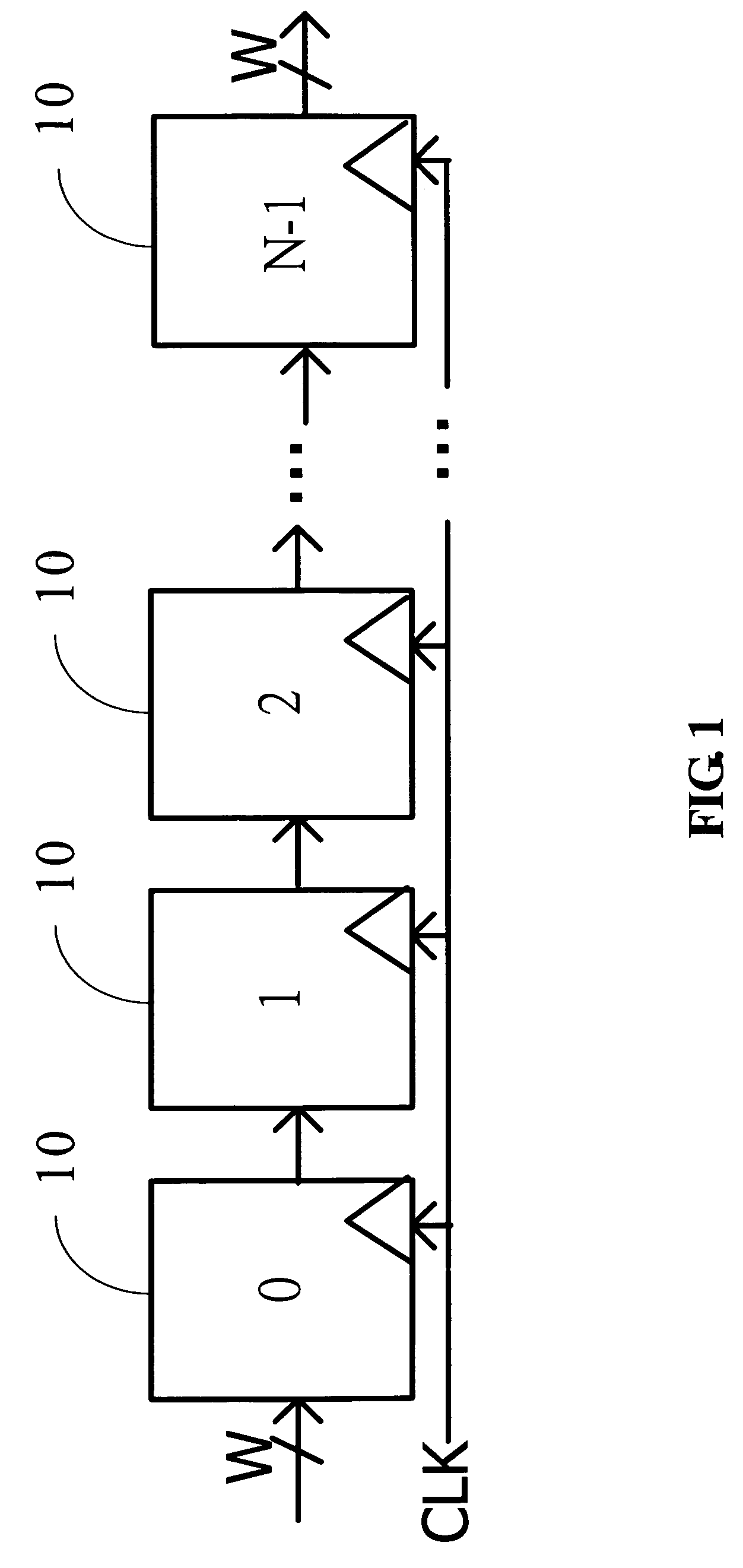

Low-power delay buffer circuit

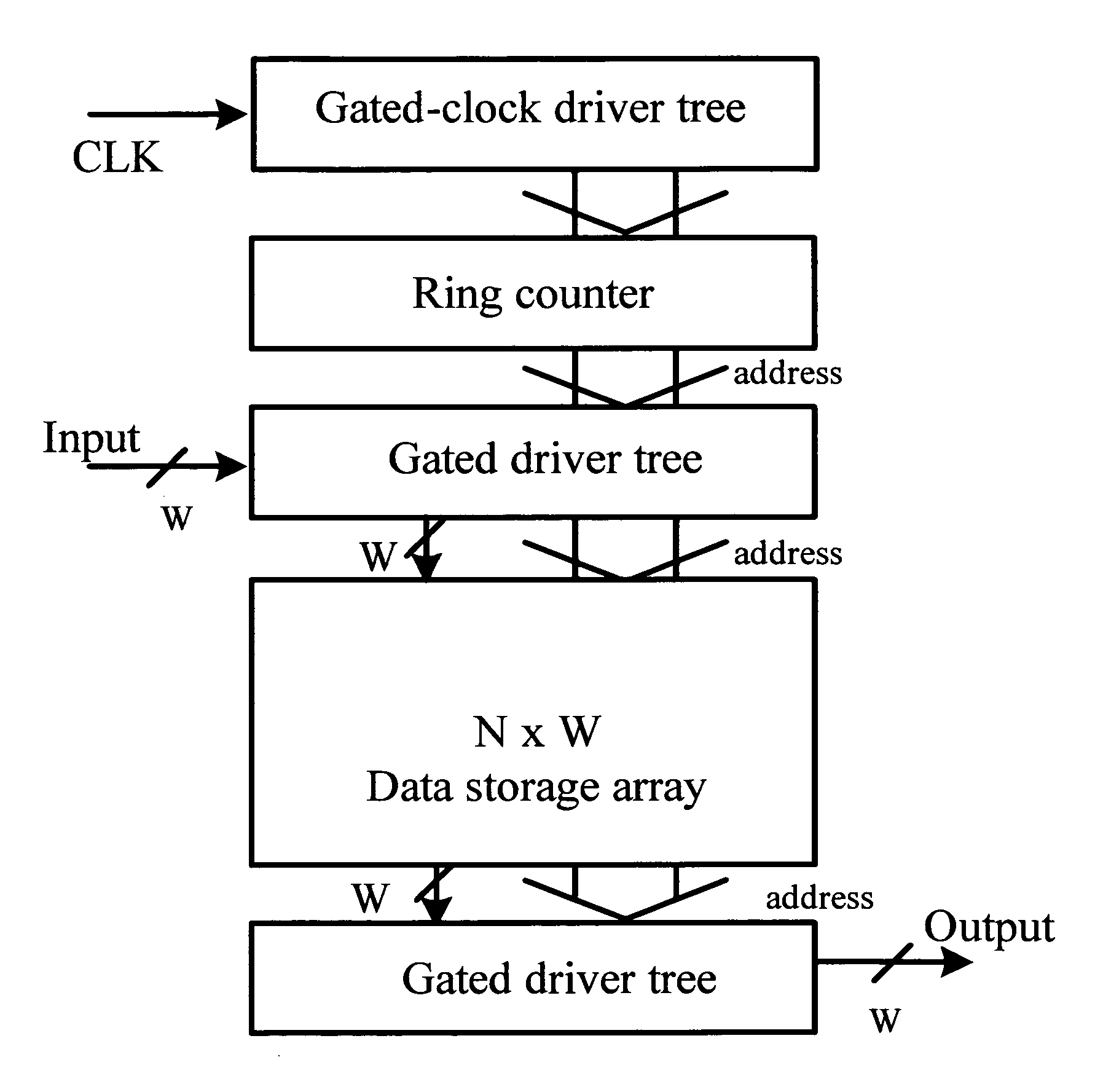

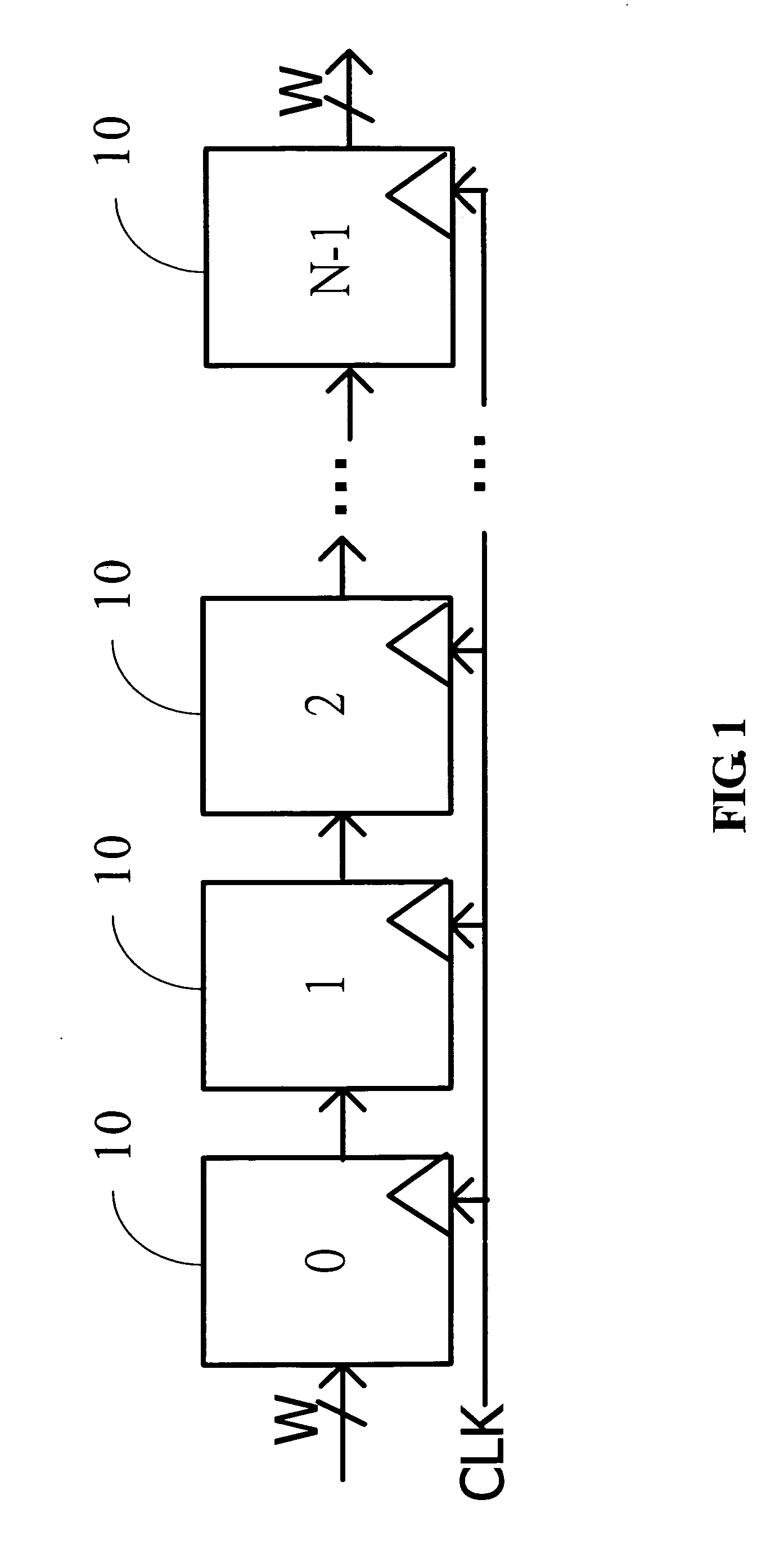

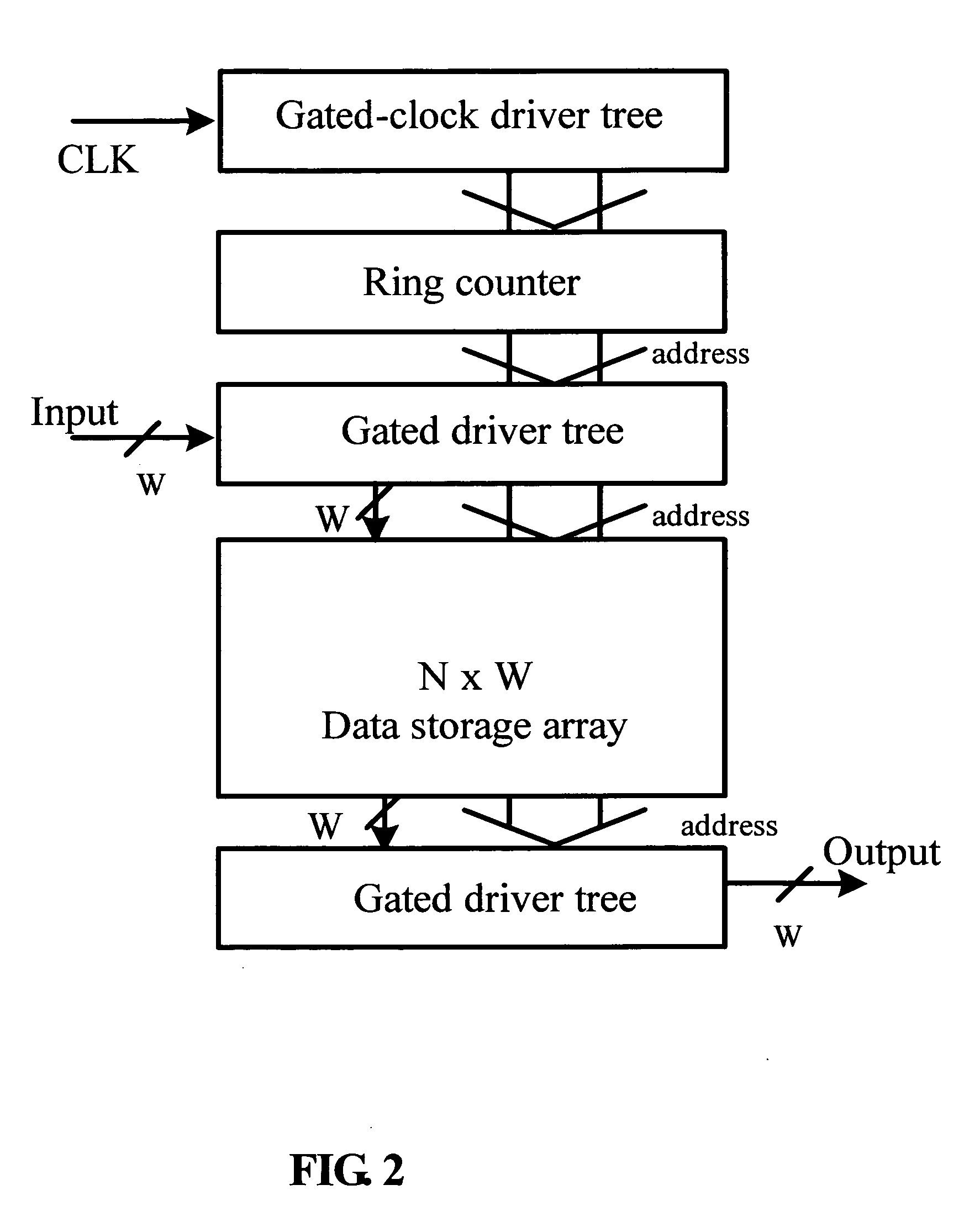

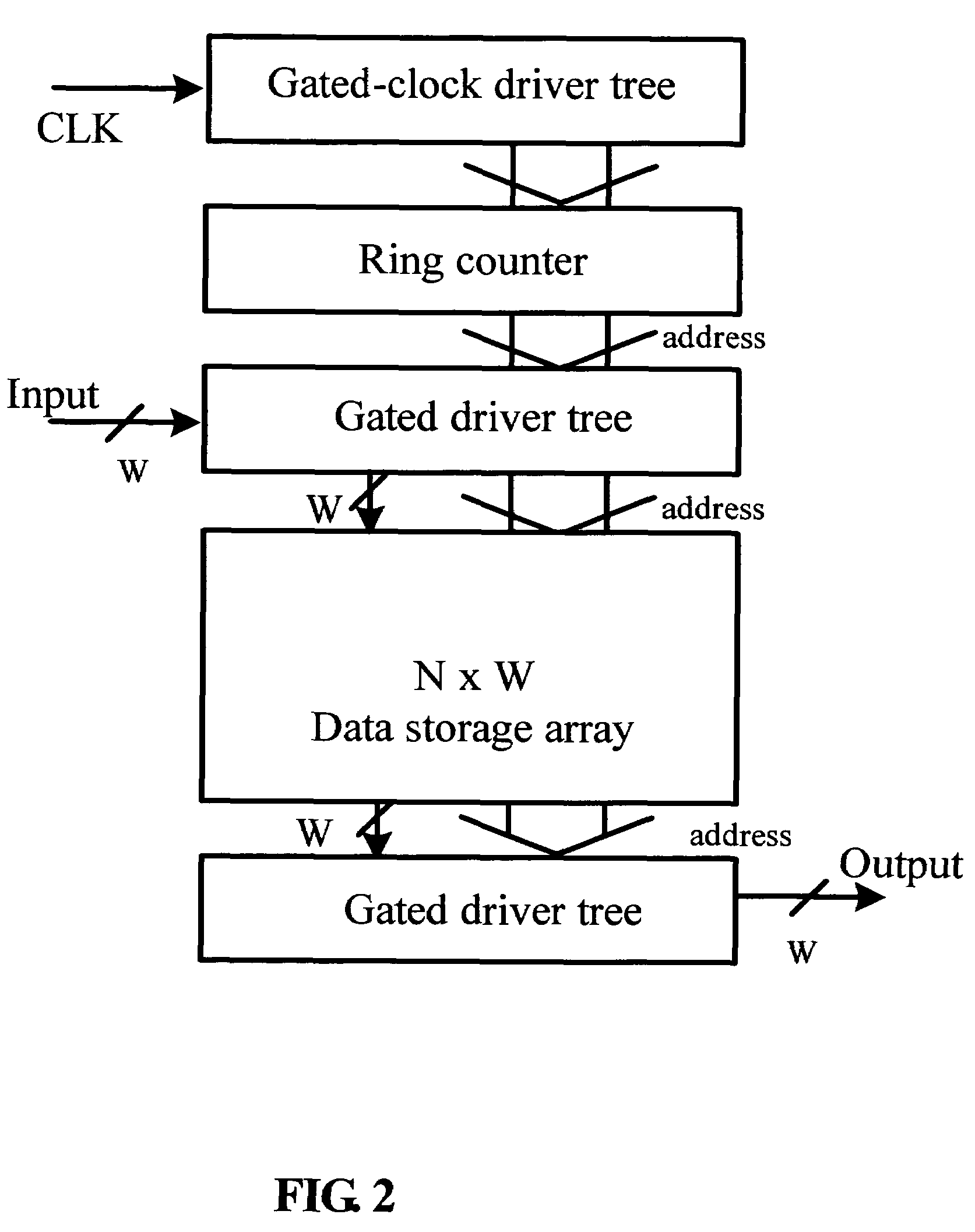

ActiveUS20060152980A1Less layout areaReduce power consumptionPulse automatic controlDigital storageRing counterAddress decoder

A low-power delay buffer circuit is provided, which utilizes a ring counter as address decoder and a latch array for memory. To reduce power consumption, a gated-clock driver tree is applied to the ring-counter addressing architecture. Moreover, a similar gated-driver tree is applied to the input and output ports of the latch array. The delay buffer circuit not only could achieve a power consumption lower than SRAM-based delay buffers, but also could operation under high frequencies and take up less layout area than SRAM-based delay buffers.

Owner:NAT TAIWAN UNIV

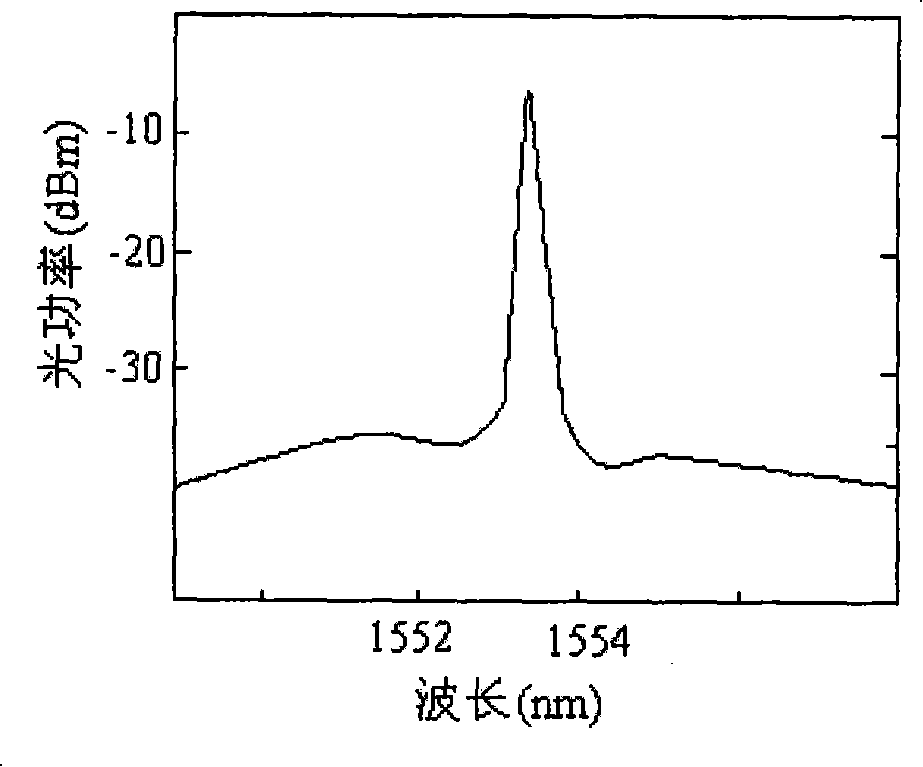

Haracter cavity passive mode-locking optical fiber laser

InactiveCN101252249AStable light pulse outputCompact structureOptical resonator shape and constructionActive medium materialMode locked fiber laserRing counter

The invention disclose a 'percent sign' counter passive mode-locking optical fiber laser, comprising an optical fiber amplifier and two non-linear optical fiber ring mirrors, wherein the two non-linear optical fiber ring mirrors are welded at an input port and an output port of the optical fiber amplifier to form a 'percent sign' counter structure. The two non-linear optical fiber ring mirrors and the optical fiber amplifier compose a F-P cavity which can realize an optical pulse output with stable line width; through the output of the non-linear optical fiber ring mirrors and by launching a feedback loop technology, the optical pulse output with stable line width can be realized; configurations of the non-linear optical fiber ring mirrors enable the light transited in the ring counter clockwise and clockwise to obtain different non-linear phase shift when reaching a coupler, only a phase shift difference rate of the central wavelength reaching pi first and a starting mode-locking forms.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

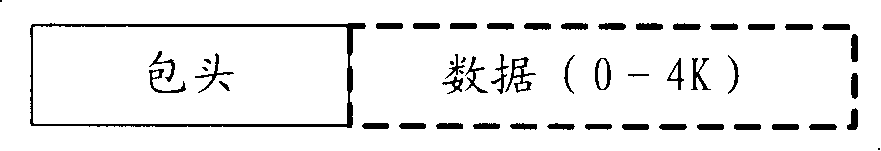

Credit processing equipment and flow control transmission apparatus and method thereof

ActiveCN101184022ACalculation speedReduce computing latencyEnergy efficient ICTData switching networksRing counterTransport system

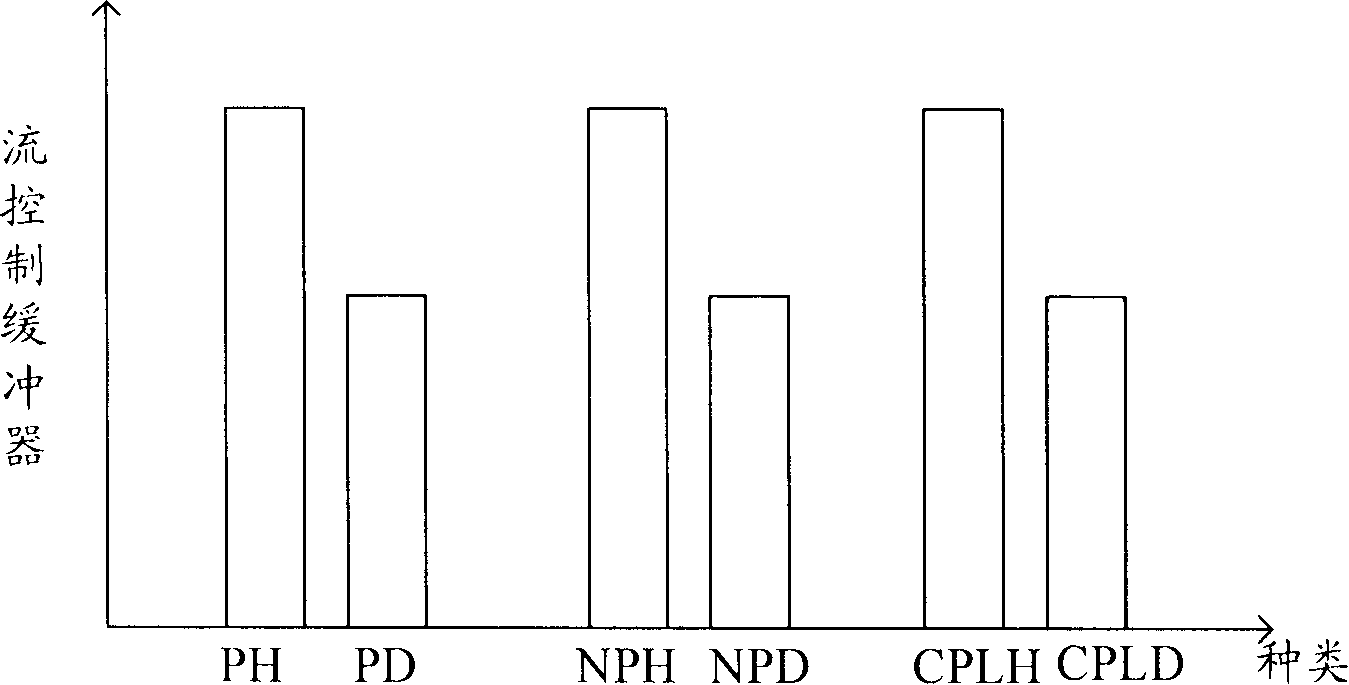

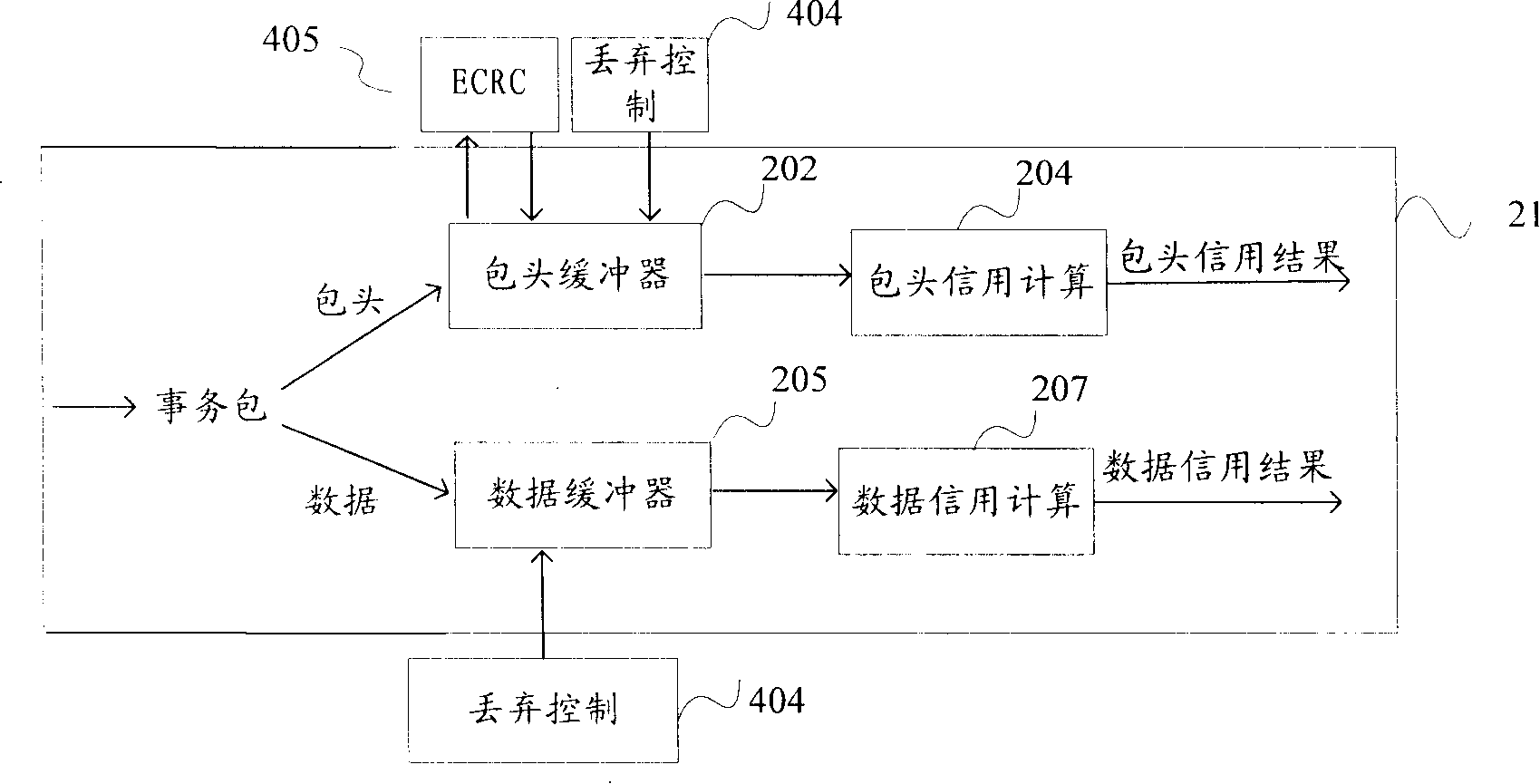

The invention discloses a stream packet header credit processing device, comprising a packet header buffer unit and a packet header credit calculation unit, which is characterized in that: the packet header credit is calculated directly according to the amount of the packet header credit received, recorded and transmitted by a writing pointer and a reading pointer, so that delay-time is reduced; meanwhile, a credit processing device is provided in the invention and the credit processing device comprises the packet header credit processing device and a data credit calculation unit; wherein, in the data calculation circuit a ring counter control unit and a controlling table unit are used to choose different types of data; the data credit is calculated via the shared circuit, so that circuit area is saved and calculation speed is raised; the invention also provides a sending device, a receiving device, a transmission system and a processing and transmitting method using the receiving and sending devices and transmission system, so that credit processing is optimized; efficiency is increased and power consumption is reduced with the stream control device and stream control method in the invention.

Owner:SEMICON MFG INT (SHANGHAI) CORP

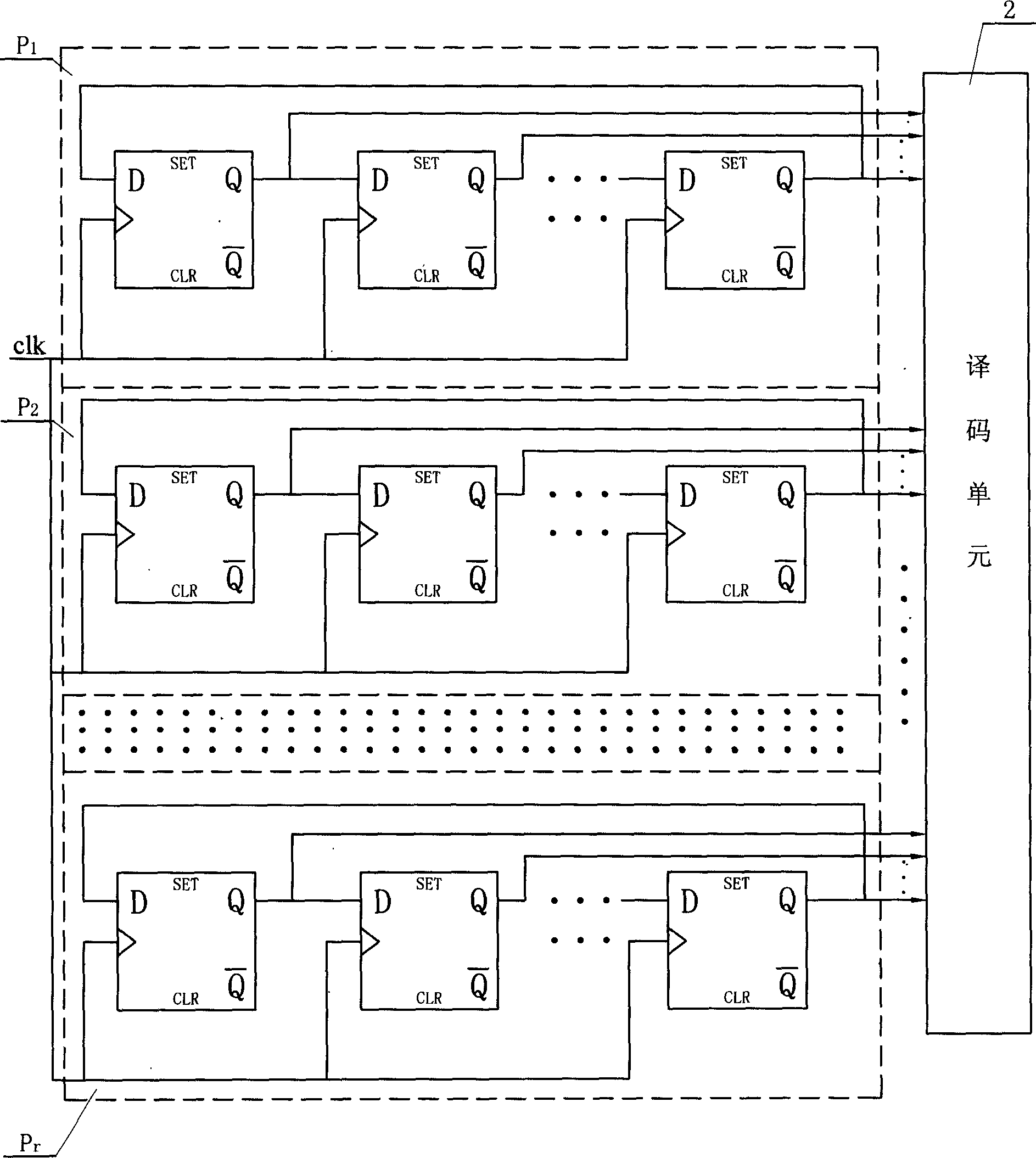

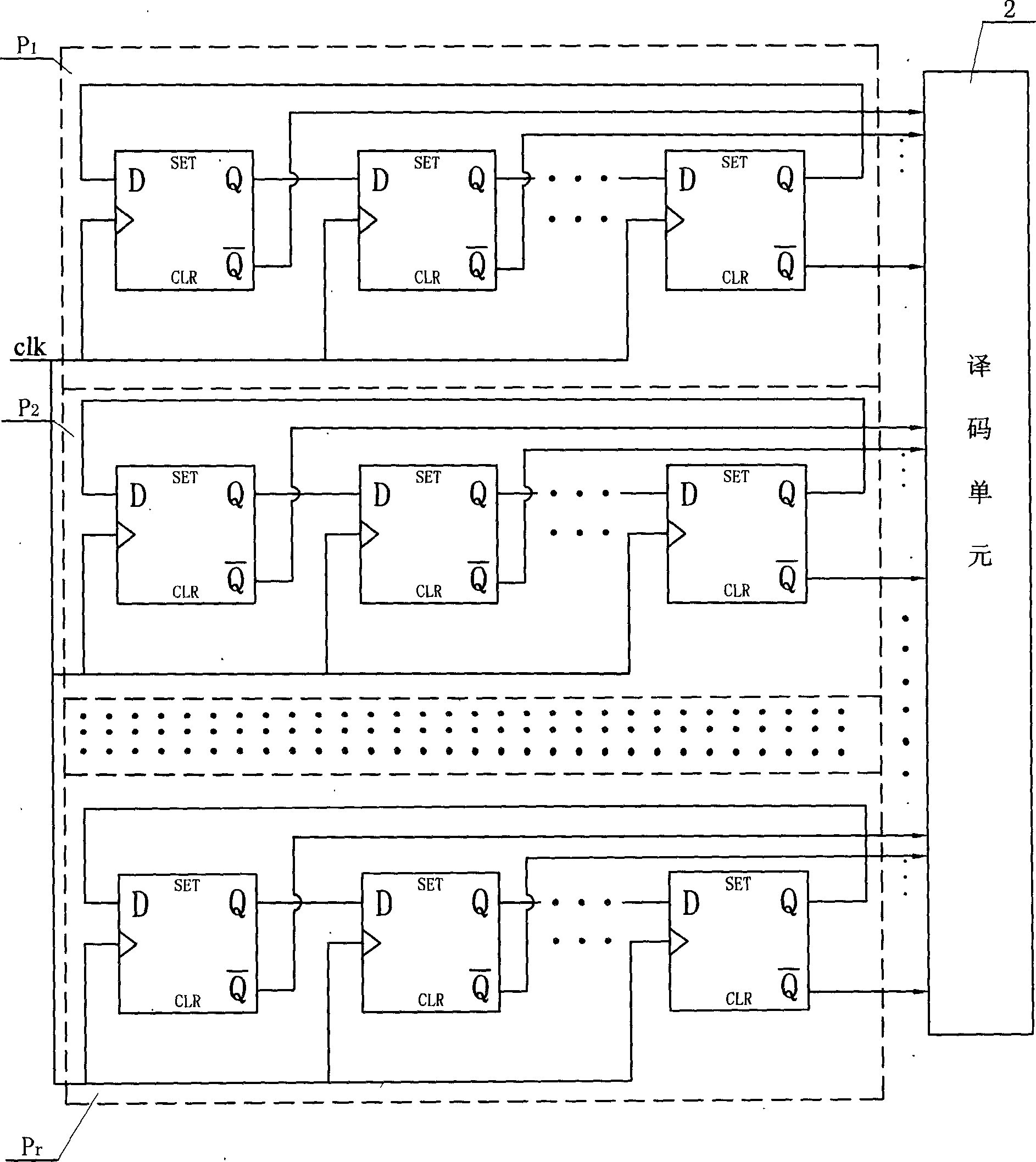

Relatively prime mode parallel frequency divider based on congruence theory

InactiveCN1688108AEnable Programmable PerformanceSimple structurePulse automatic controlCounting chain synchronous pulse countersRing counterHigh Frequency Waves

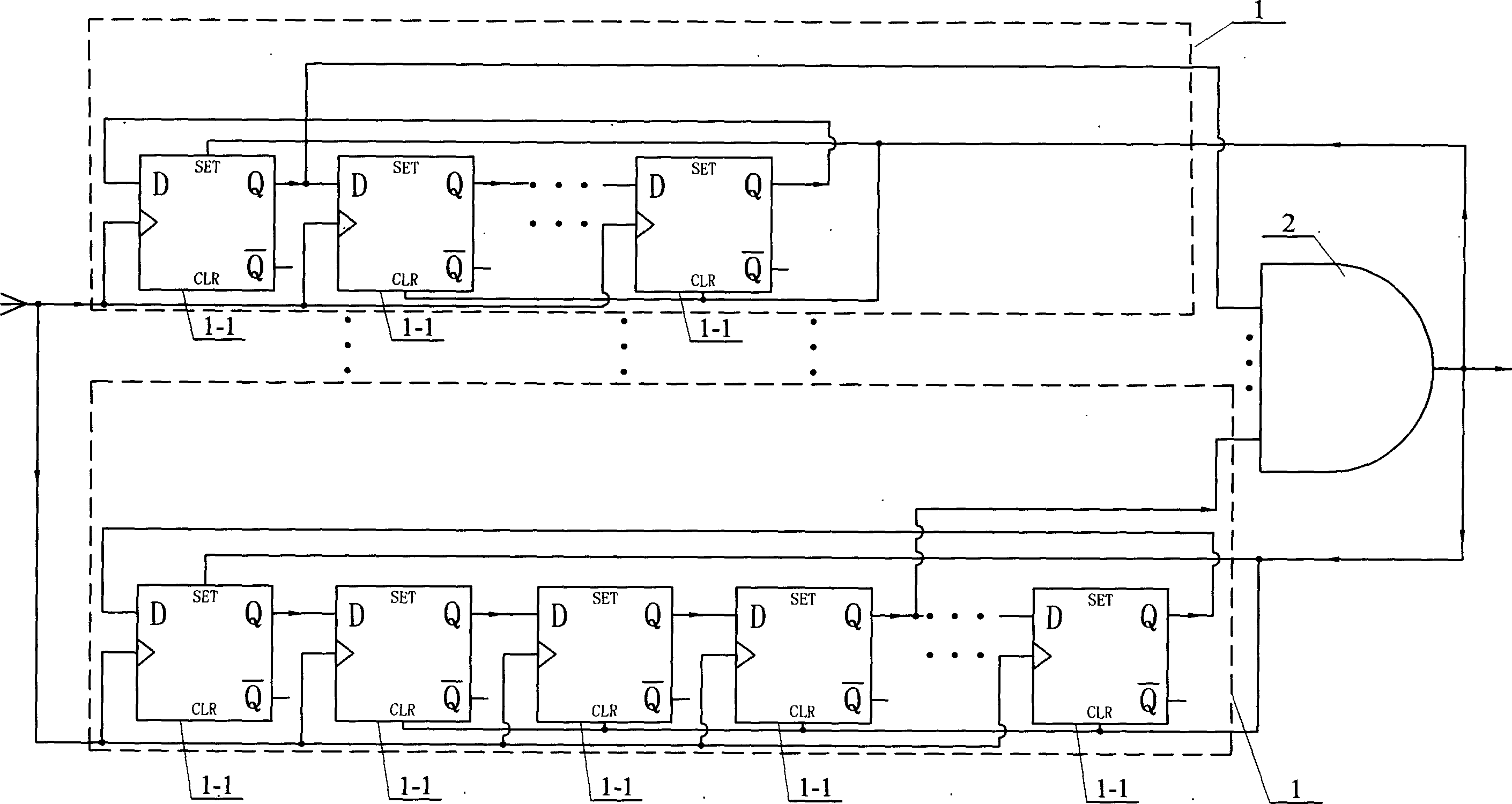

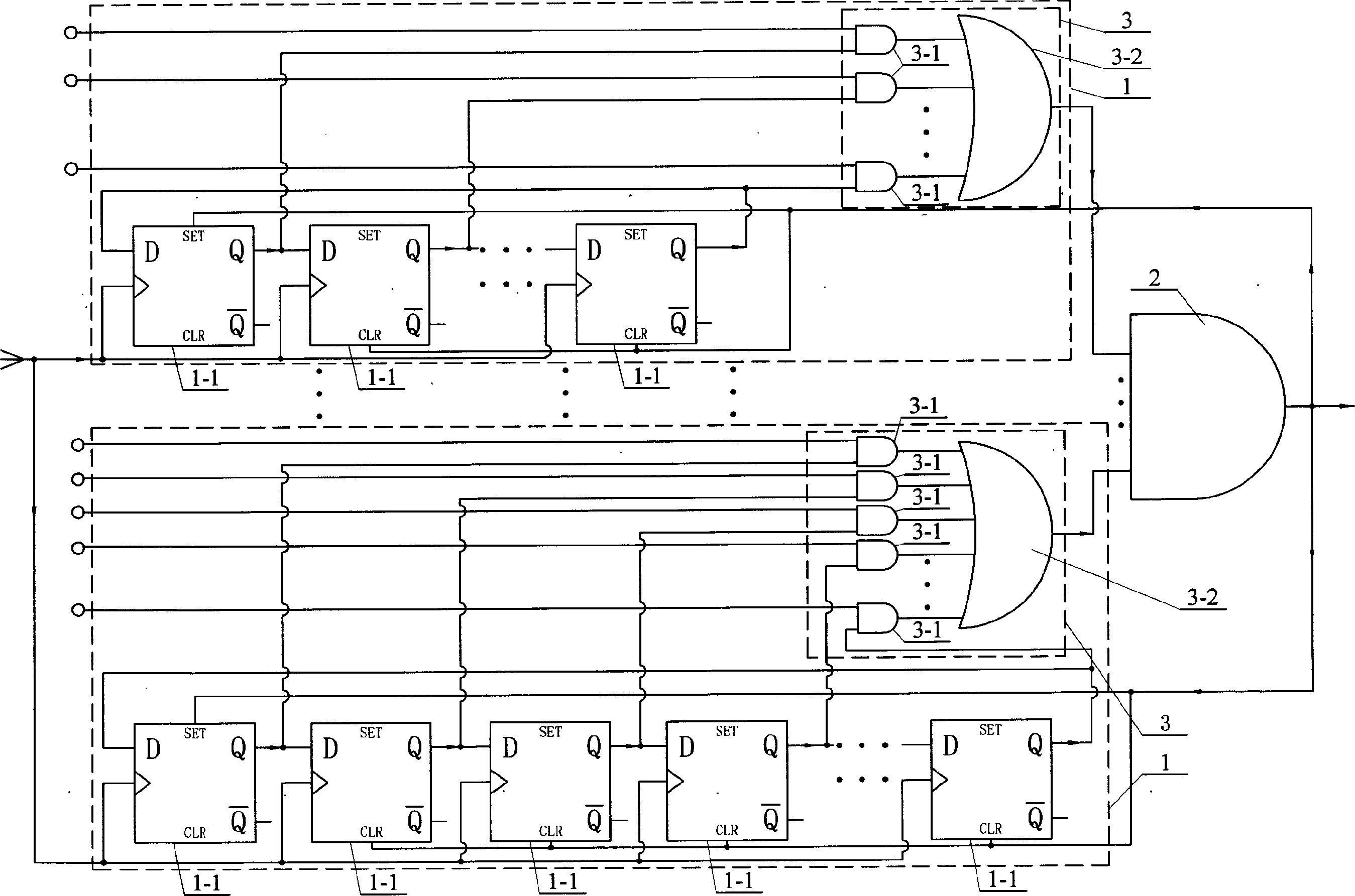

A relative prime modulo parallel divider based on the congruent theory relates to the high-speed digital divider field. An output corresponding to the dividing number in each synchronous ring counter is connected to an input of 2, each clock signal input end of every type-D trigger in each counter is interconnected to be the input of the divider. The first SET end and all other CLR reset ends are connected to the output of 2 to be the output of the divider, the number of type D trigger in any two synchronous ring counters are primes mutually.

Owner:HARBIN INST OF TECH

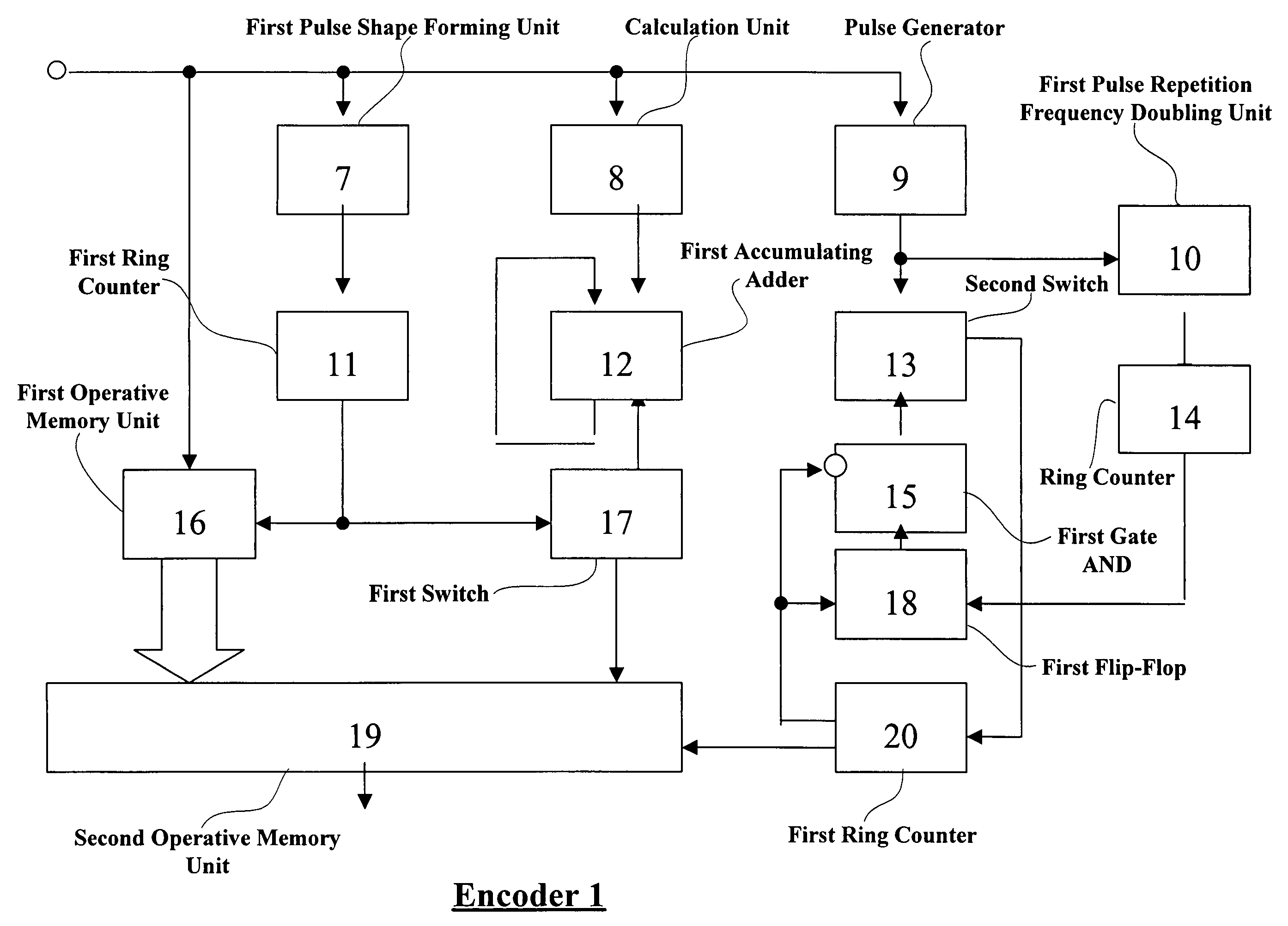

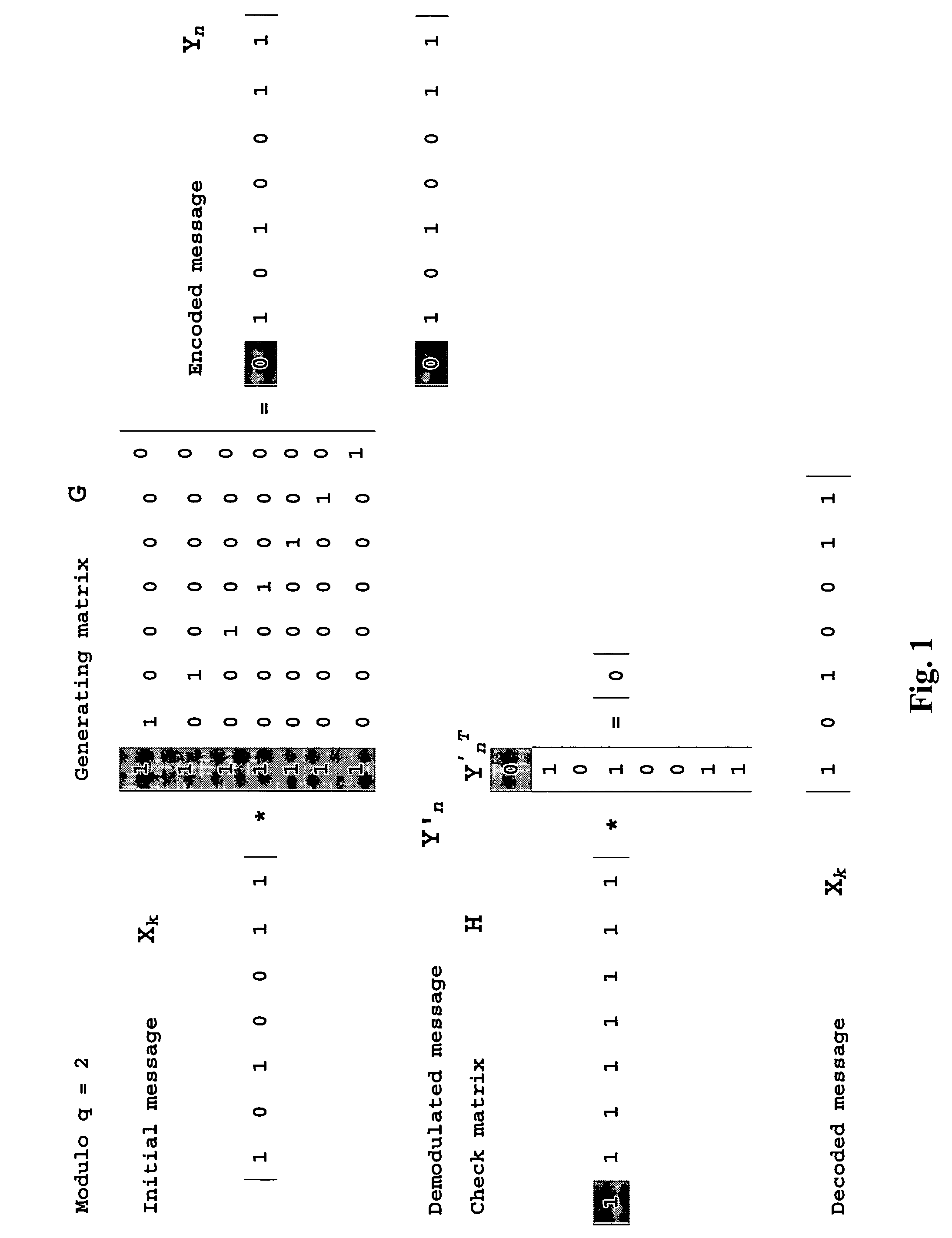

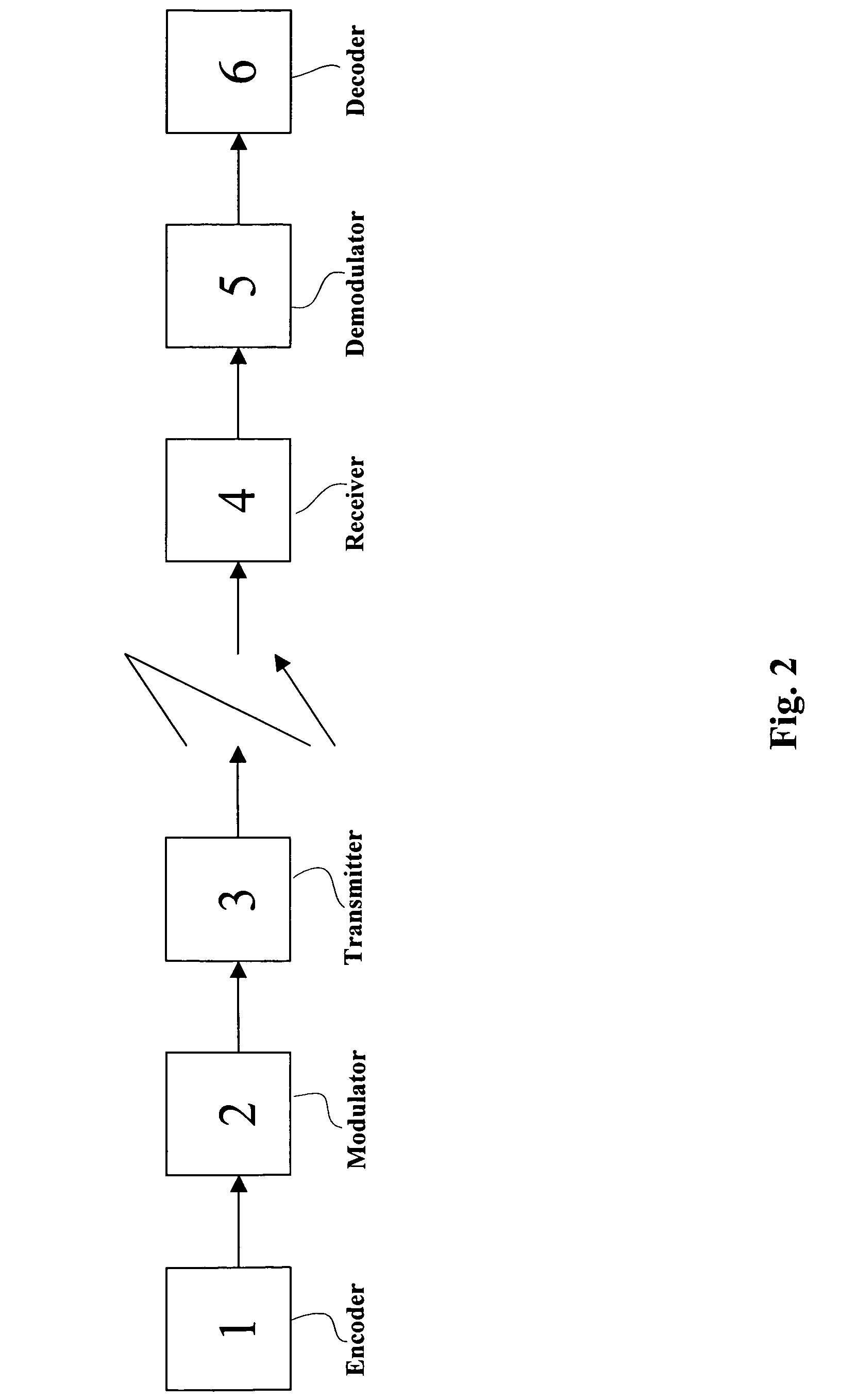

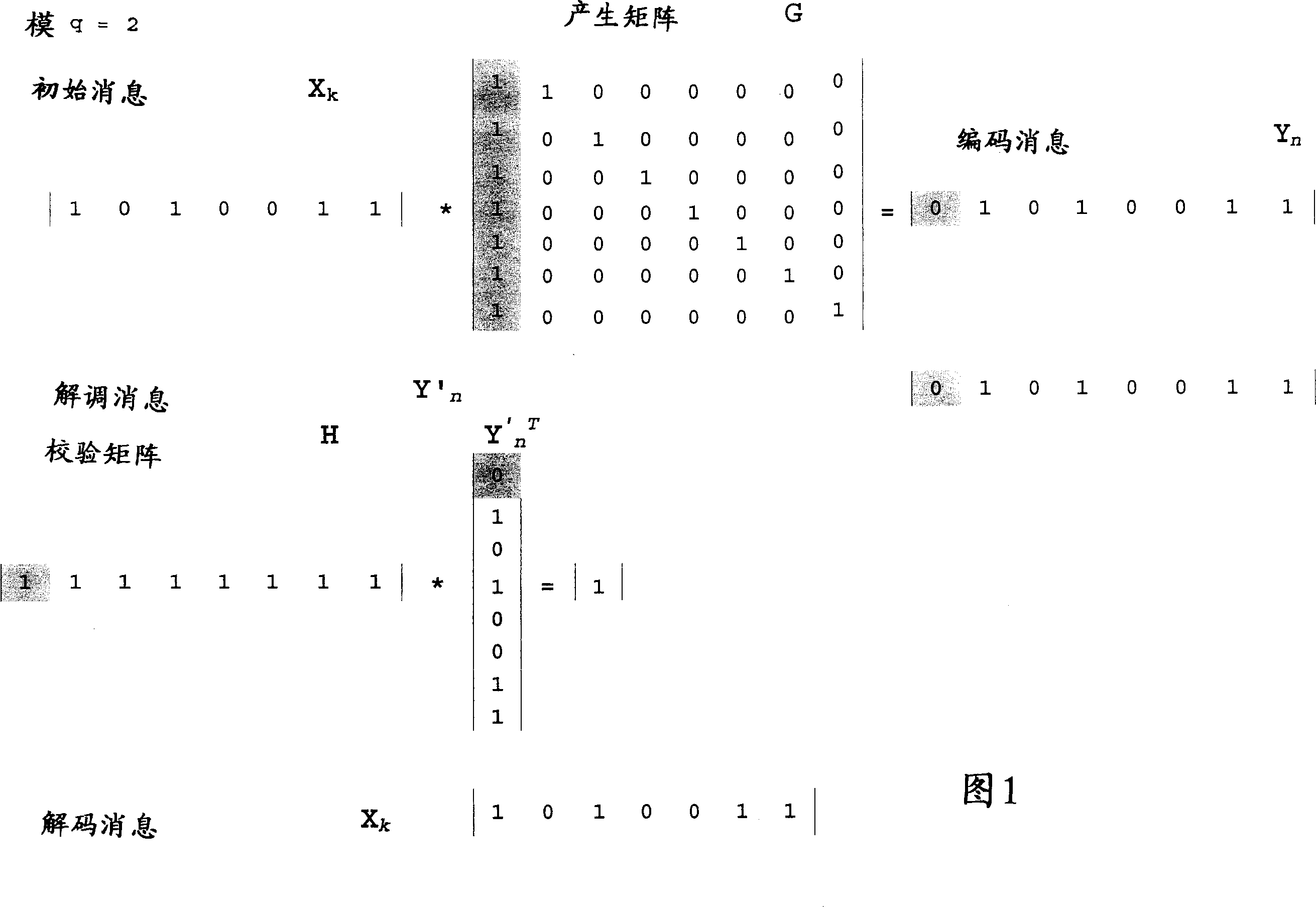

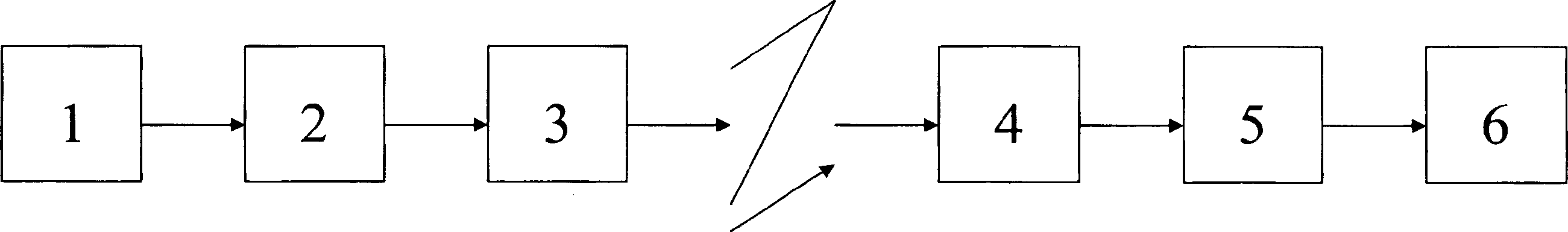

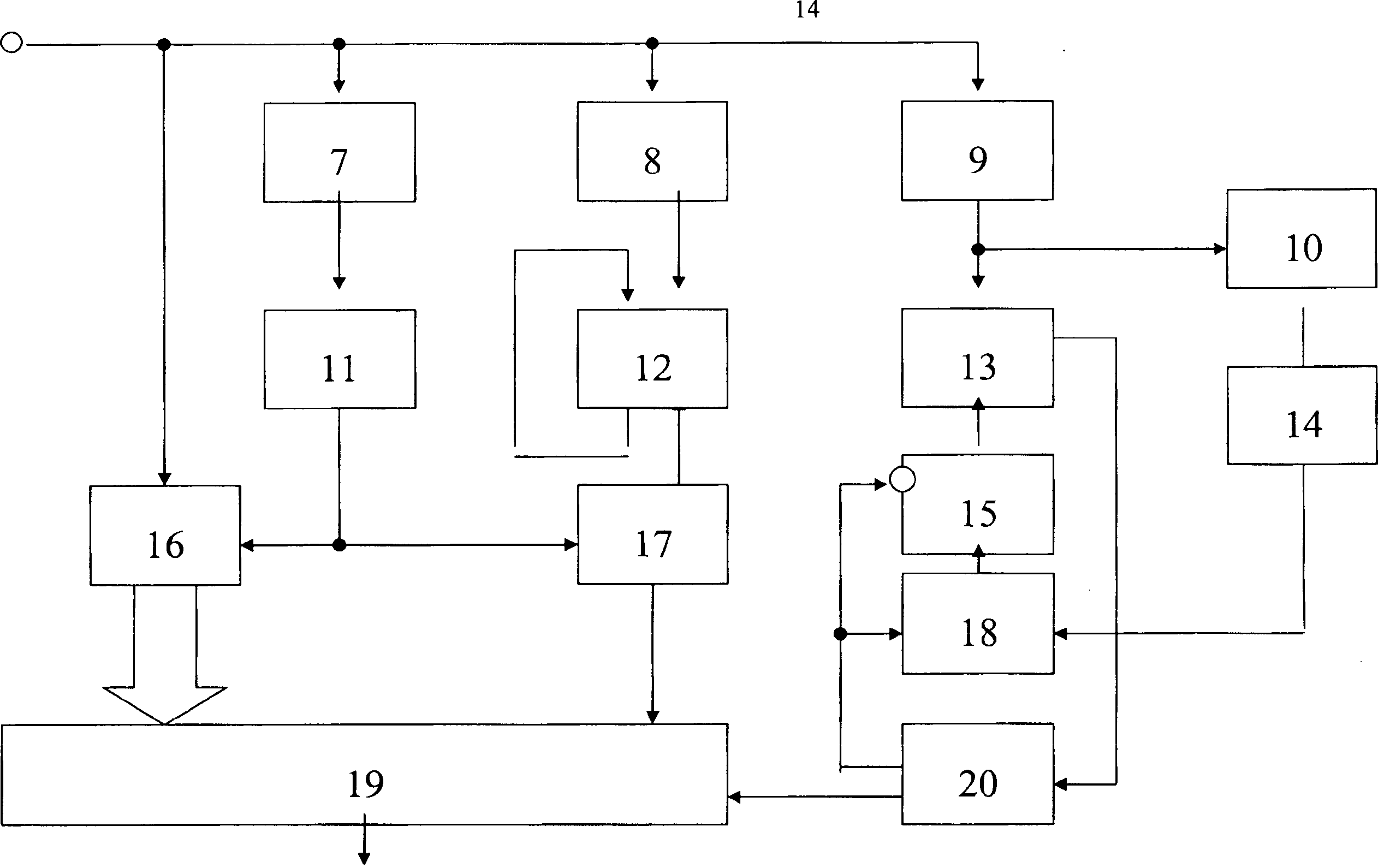

Method for transmitting a digital message and system for carrying out said method

InactiveUS6970112B2Easy to implementCode conversionError correction/detection using linear codesRing counterSingle element

Described are a system and method for transmitting digital messages through wire channels and telecommunication channels using electromagnetic waves. The use of the channels is simplified by excluding multiplication and division operators from the coding and a decoding process. The system and method allows to transmit any messages from elements of Abelian group including code words whose elements are matrixes, polynomials, numbers of mixed-base notation and nonpositional notation. An encoder of the system may include a driver clock, a function g<2> calculator, a pulse generator having recurrent frequency of f(k+1) / k, a pulse recurrent frequency doubler, a ring counter up to k, an adder-accumulator of elements of Abelian group, a key, a ring counter up to (2k+1), an AND component, a main memory unit, a key, a trigger, a main memory unit and a ring counter up to (k+1). A decoder of the system may include a driver clock, an adder-accumulator of elements of Abelin groupoid, a pulse generator having recurrent frequency of fk(k+1) / k, a pulse recurrent frequency doubler, a ring counter up to (k+1), a key, a main memory unit, a key, an AND component, a ring counter up to [2(k+1)+1], an identification unit provided with a single element of Abelian group, a trigger, a main memory unit a key, a ring counter up to k.

Owner:MORTON FINANCE SA

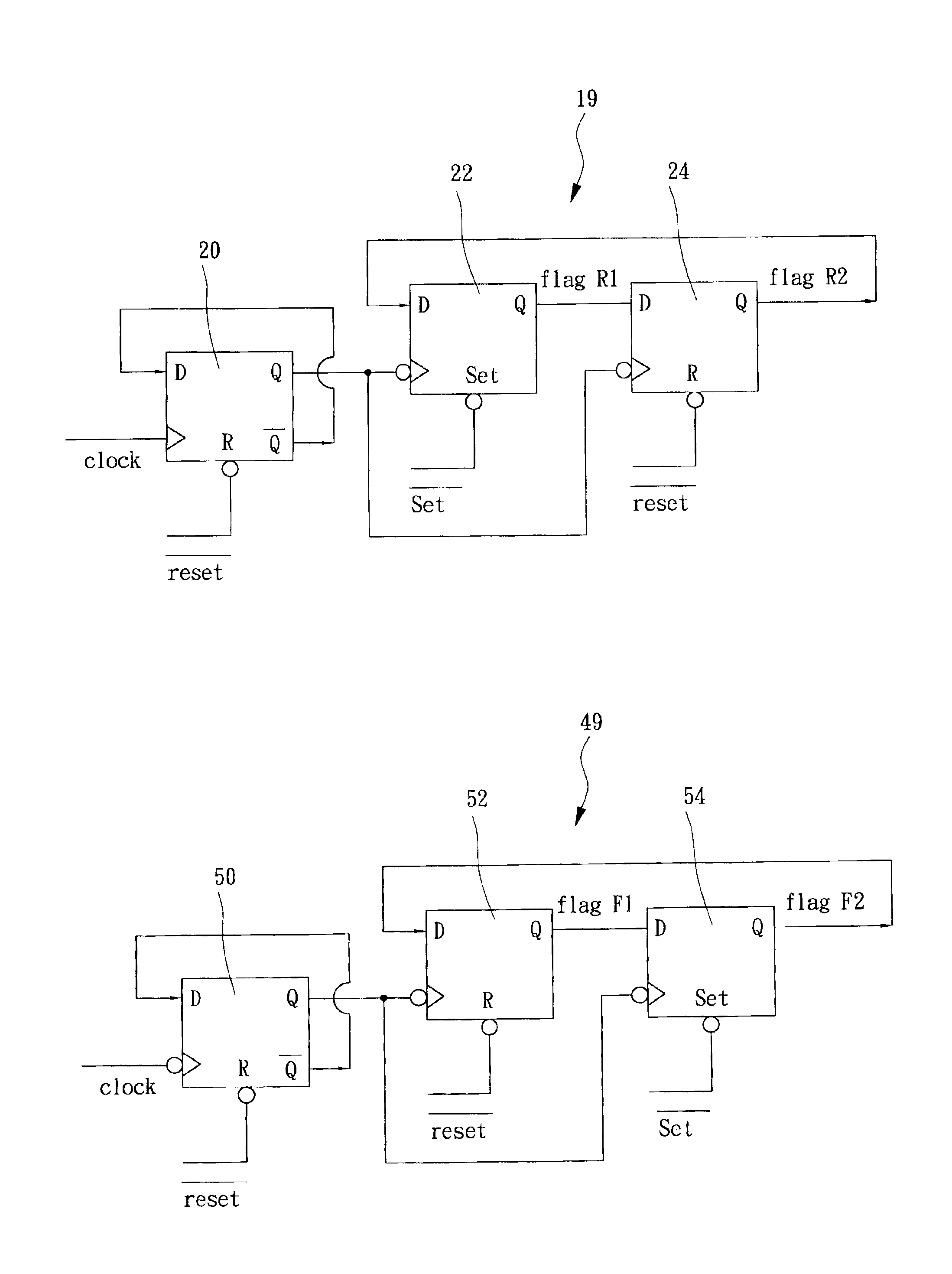

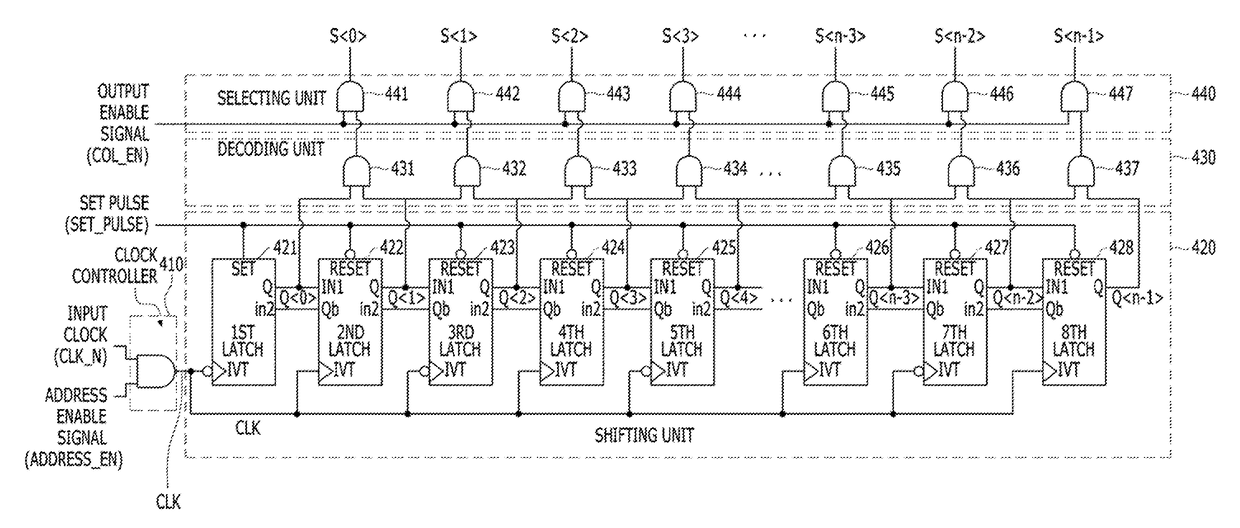

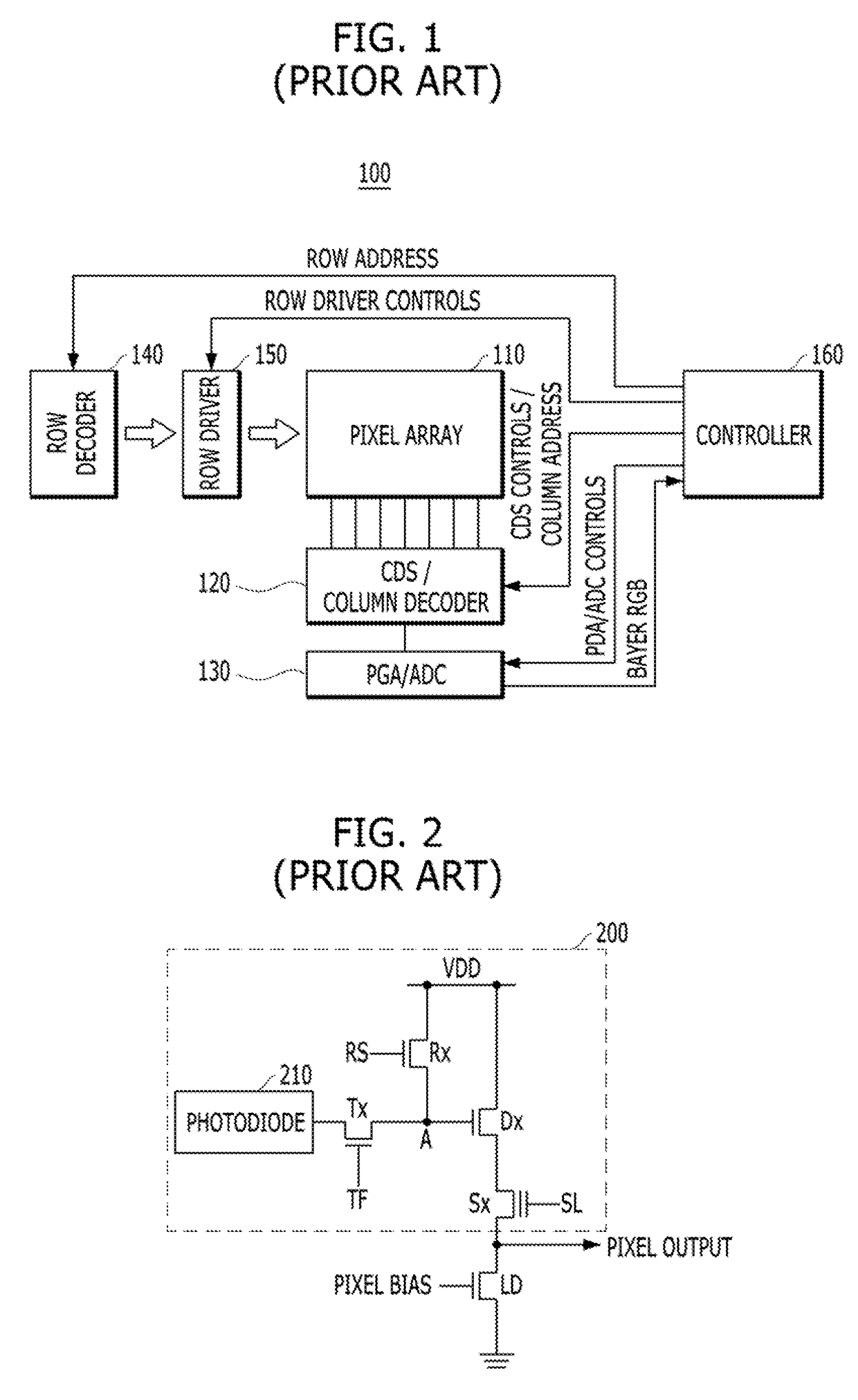

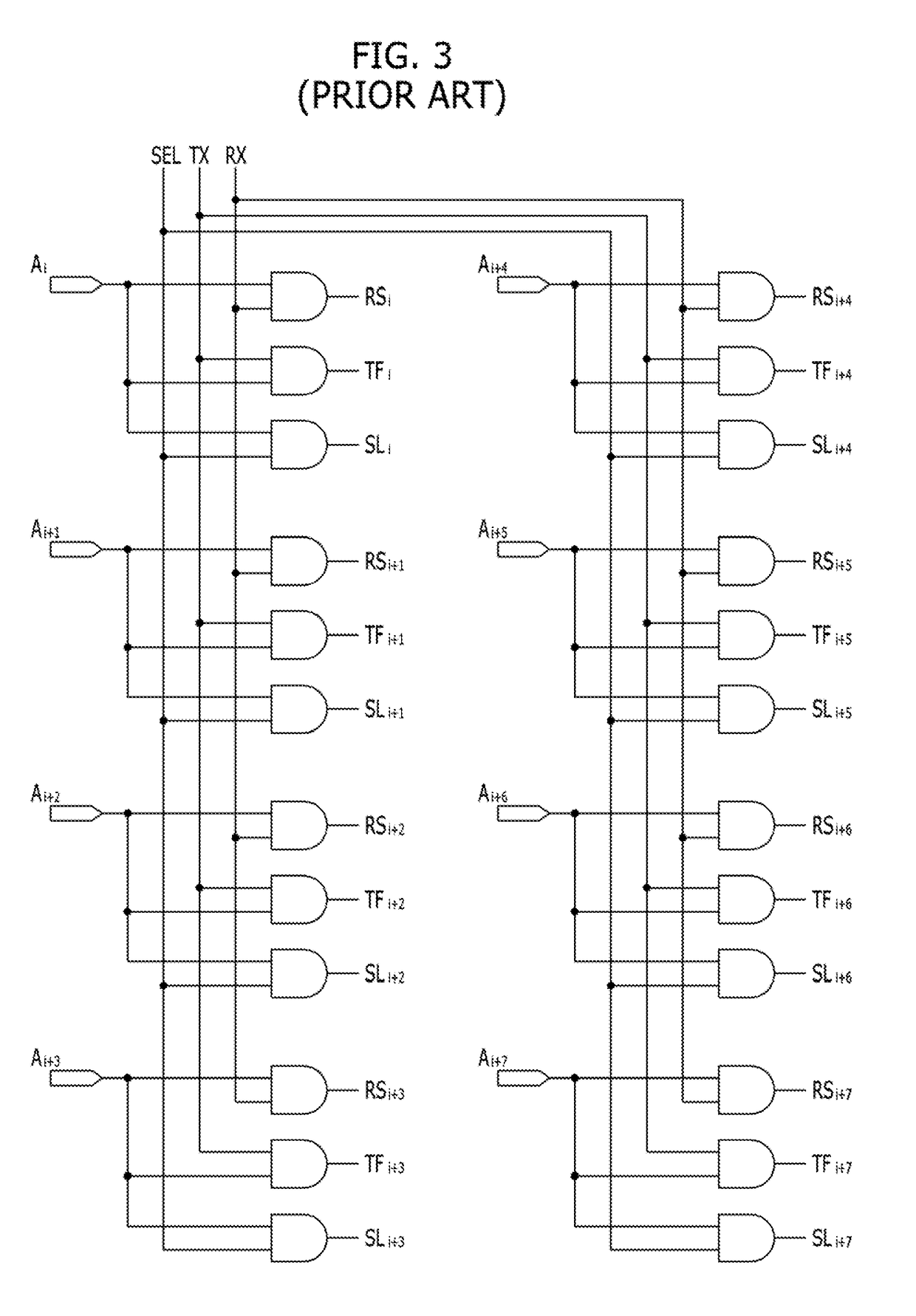

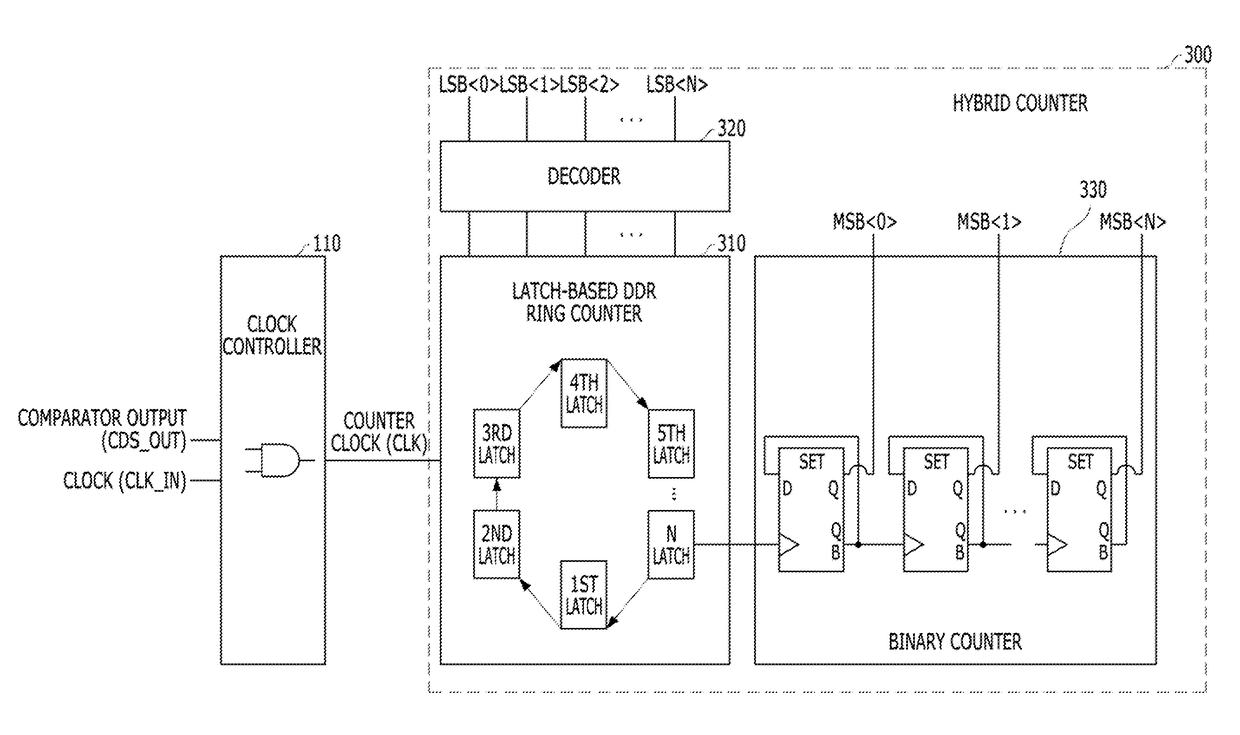

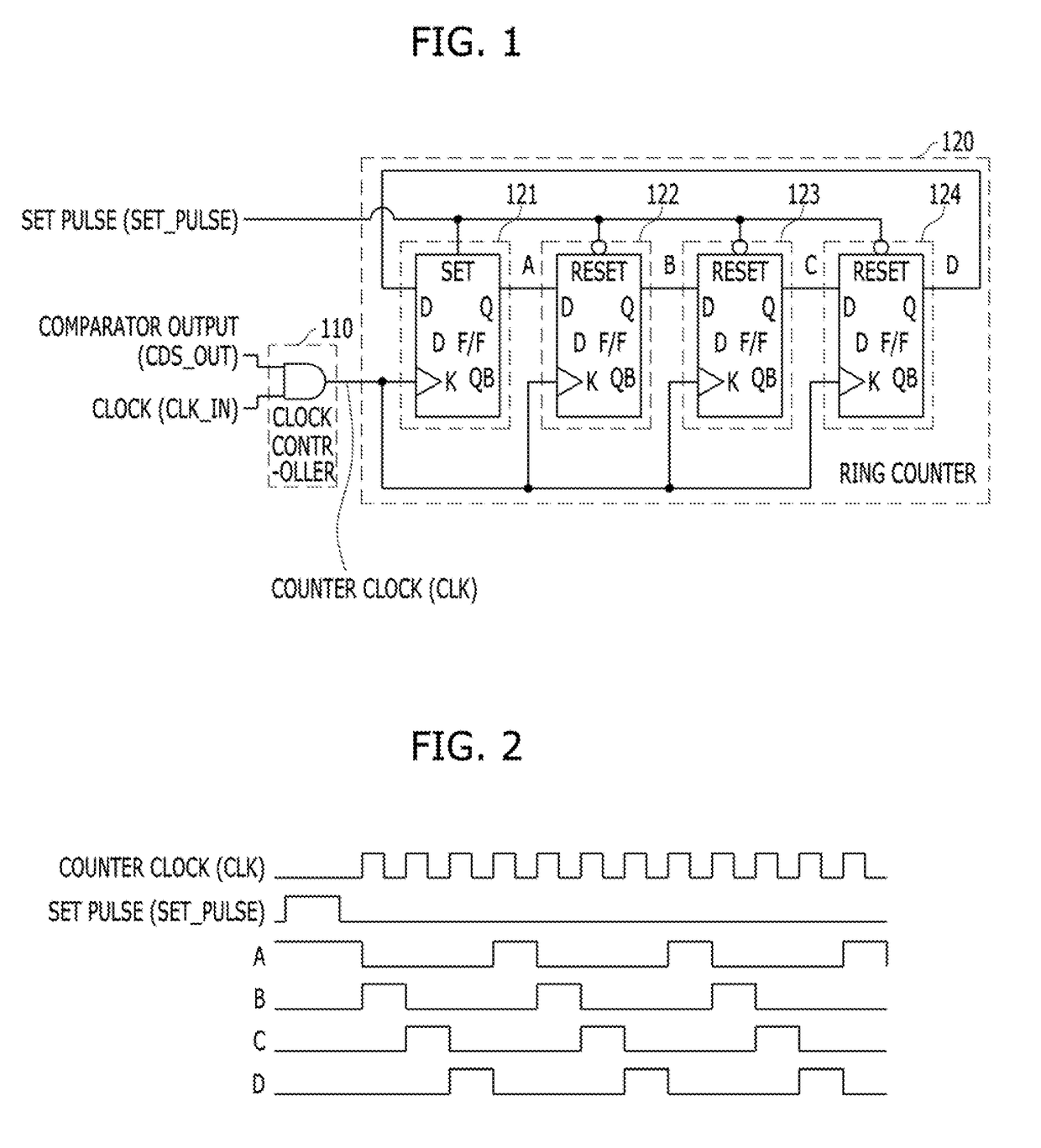

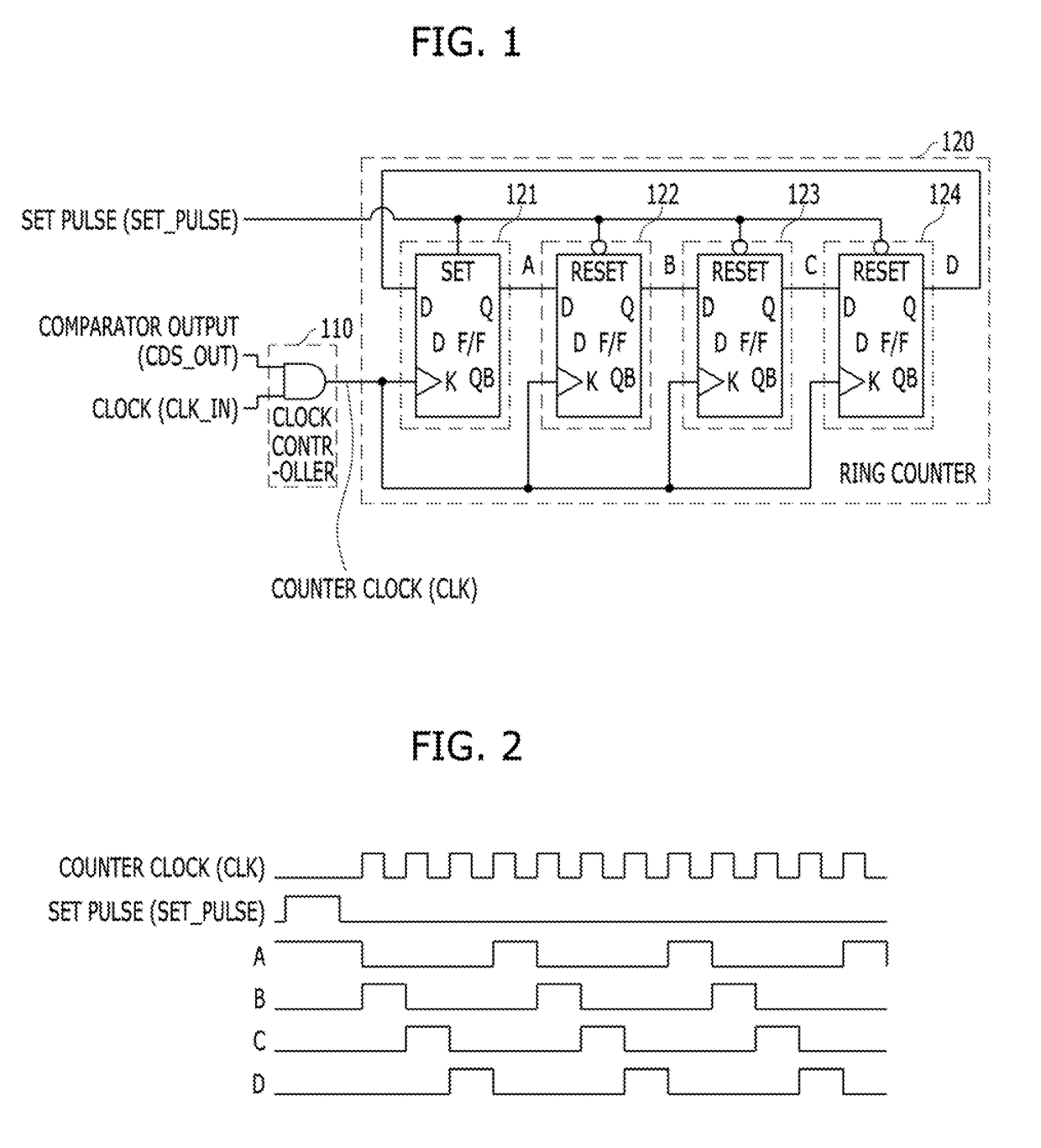

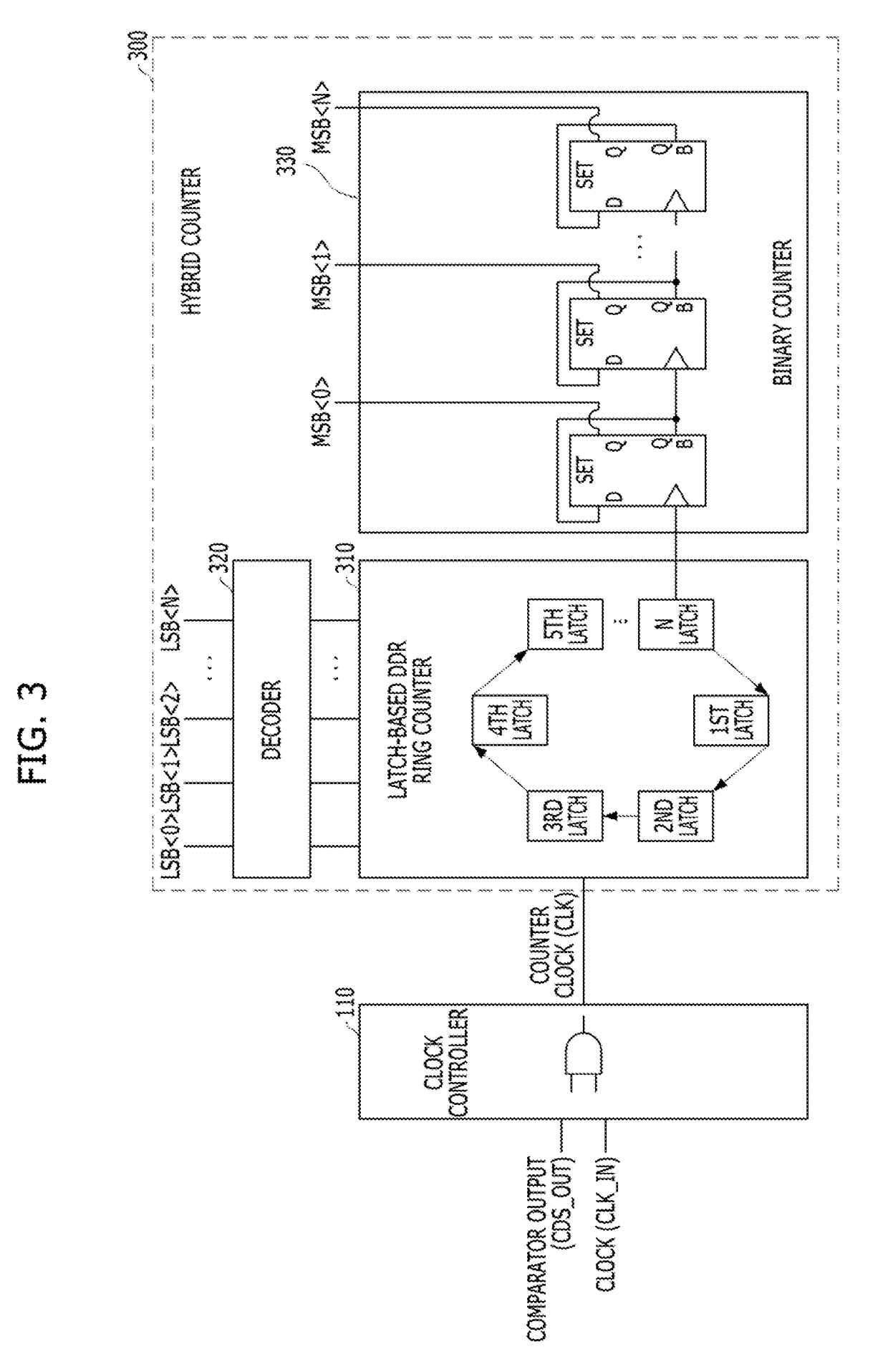

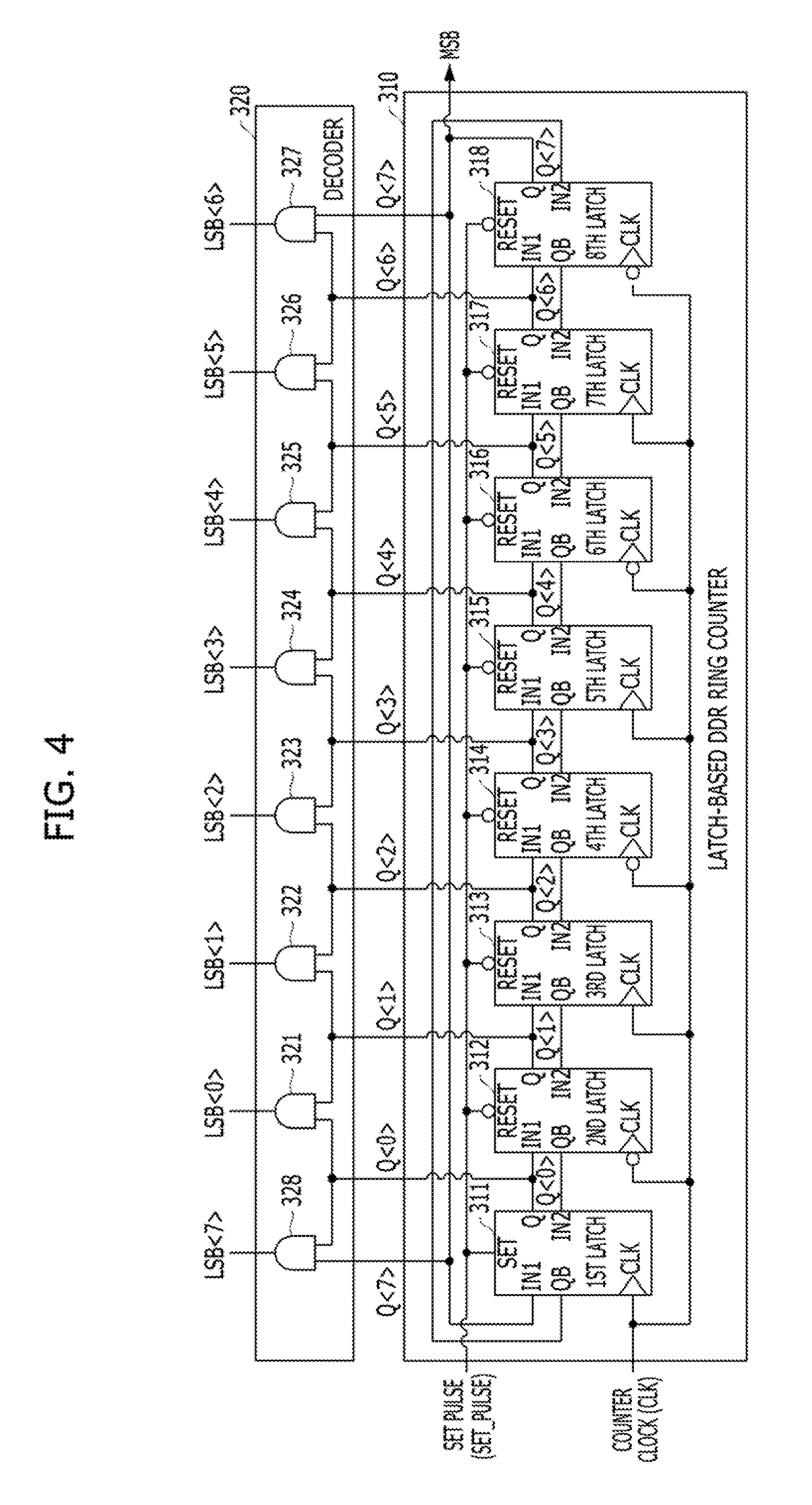

Latch circuit and double data rate decoding device based on the same

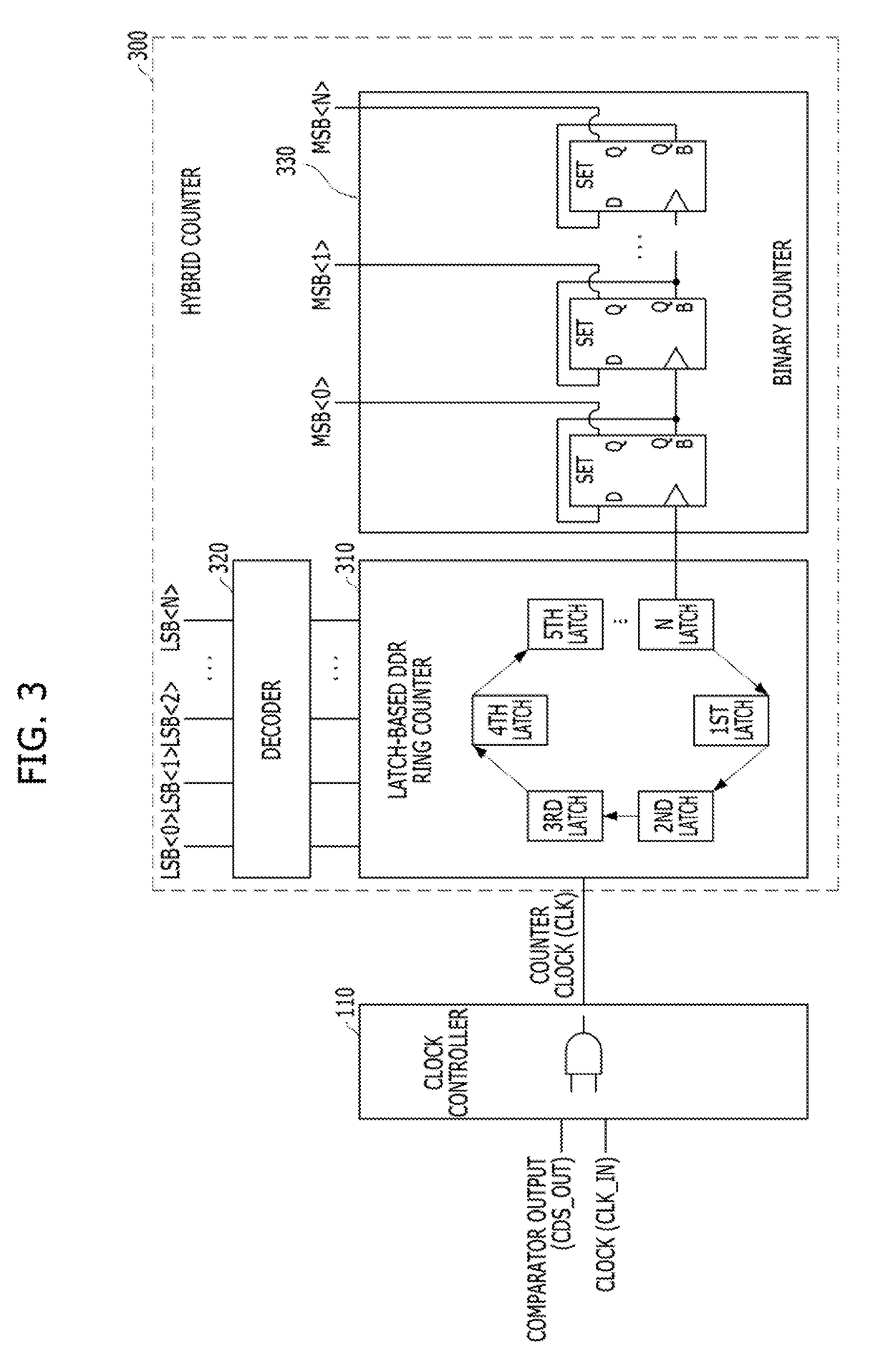

Disclosed are a latch circuit receiving a negative output of a next latch stage circuit as a feedback input, a double data rate (DDR) ring counter based on the latch circuit to perform DDR counting of pulse periods and reduce the number of toggles, a hybrid counting device counting lower-bit portion by using the latch-based DDR ring counter and upper-bit portion by using a binary counter, and an analog-to-digital converting device and a CMOS image sensor employing the hybrid counting device. A double data rate ring counter may include a plurality of latches coupled in a form of a ring. The plurality of latches may include positive-edge-triggered latches and negative-edge-triggered latches arranged alternately. A current latch stage receives an output of a preceding latch stage to shift to a next latch stage according to a counter clock, receives an output of the next latch stage to check a data shift to the next latch stage, and falls to a low level if the data shift is checked.

Owner:SK HYNIX INC

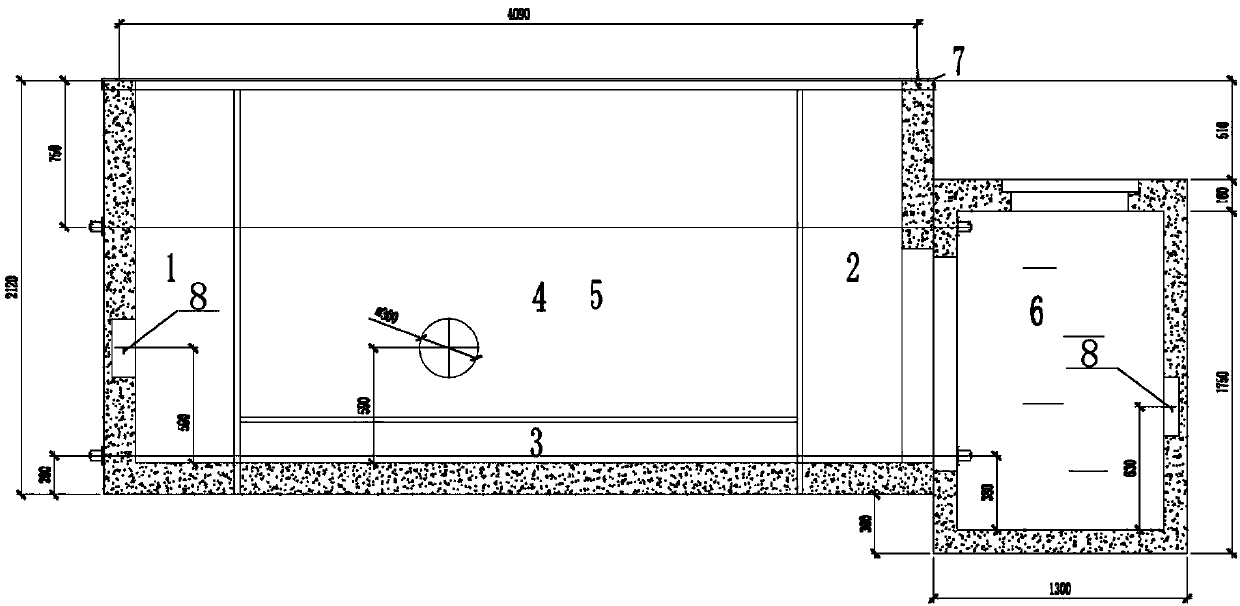

Prefabricated-type ring main unit foundation

PendingCN107742830ASimple structureReasonable designSubstation/switching arrangement casingsFoundation engineeringRing counterArchitectural engineering

The invention discloses a prefabricated-type ring main unit foundation. The foundation comprises a left end plate, a right end plate, a bottom plate, a front side wall, a rear side wall and a ring main unit base; the left end plate is located at the left end of the bottom plate, the left end plate and the bottom plate are of an integrated structure, the right end plate is arranged at the right endof the bottom plate, and the left end plate and the right end plate are identical in height; the front side wall is located at the front side of the bottom plate, the rear side wall is located at therear side of the bottom plate, the front side wall and the rear side wall are identical in height, the top surface of the left end plate, the top surface of the right end plate, the top surface of the front side wall and the top surface of the rear side wall are located on the same plane, the ring main unit base is installed on the plane, and the ring main unit base and the bottom plate are identical in length and width; the right side of the right end plate is provided with a manhole, and the lower portion of the right end plate is provided with a through hole communicated with the manhole.According to the prefabricated-type ring main unit foundation, by adopting seven components, the installation convenience is ensured, the production and transportation efficiency is taken into account, and the whole project progress is accelerated. By externally embedding an angle steel frame on a combined foundation body, not only is the stability of a structure ensured, but also a very good sensory effect can be achieved.

Owner:内蒙古利元管涵工程有限责任公司

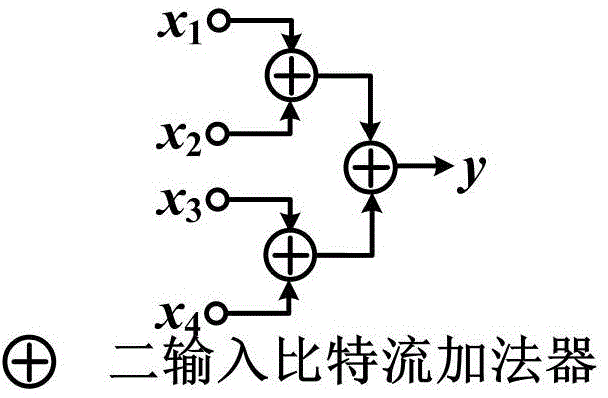

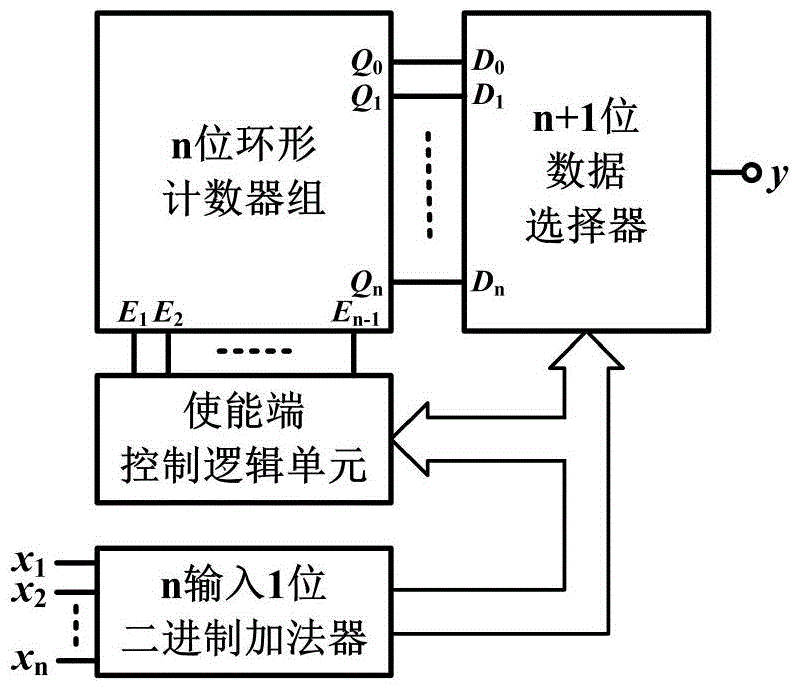

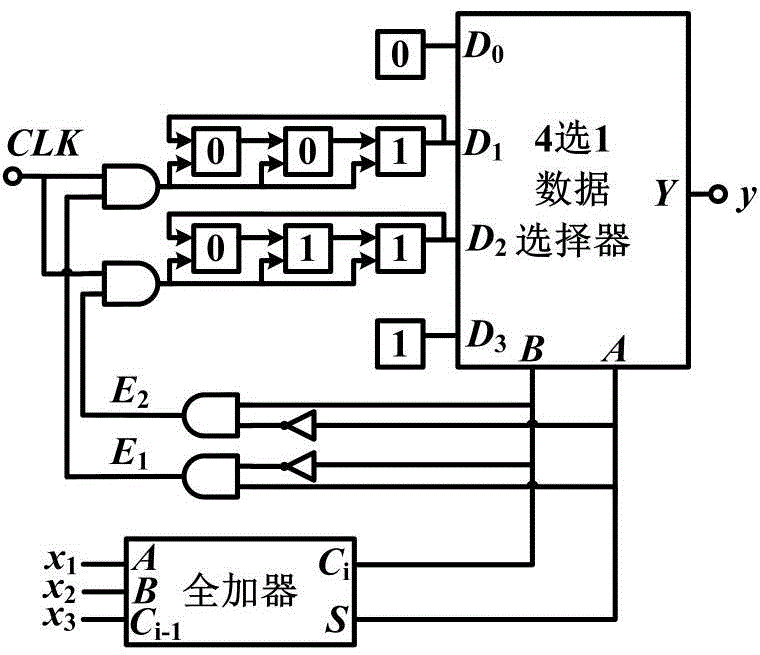

Any input signal bit stream adder based on sigma-delta modulation

InactiveCN105718240AImprove operation accuracyComputation using non-contact making devicesAnalogue-digital convertersRing counterMultiplexer

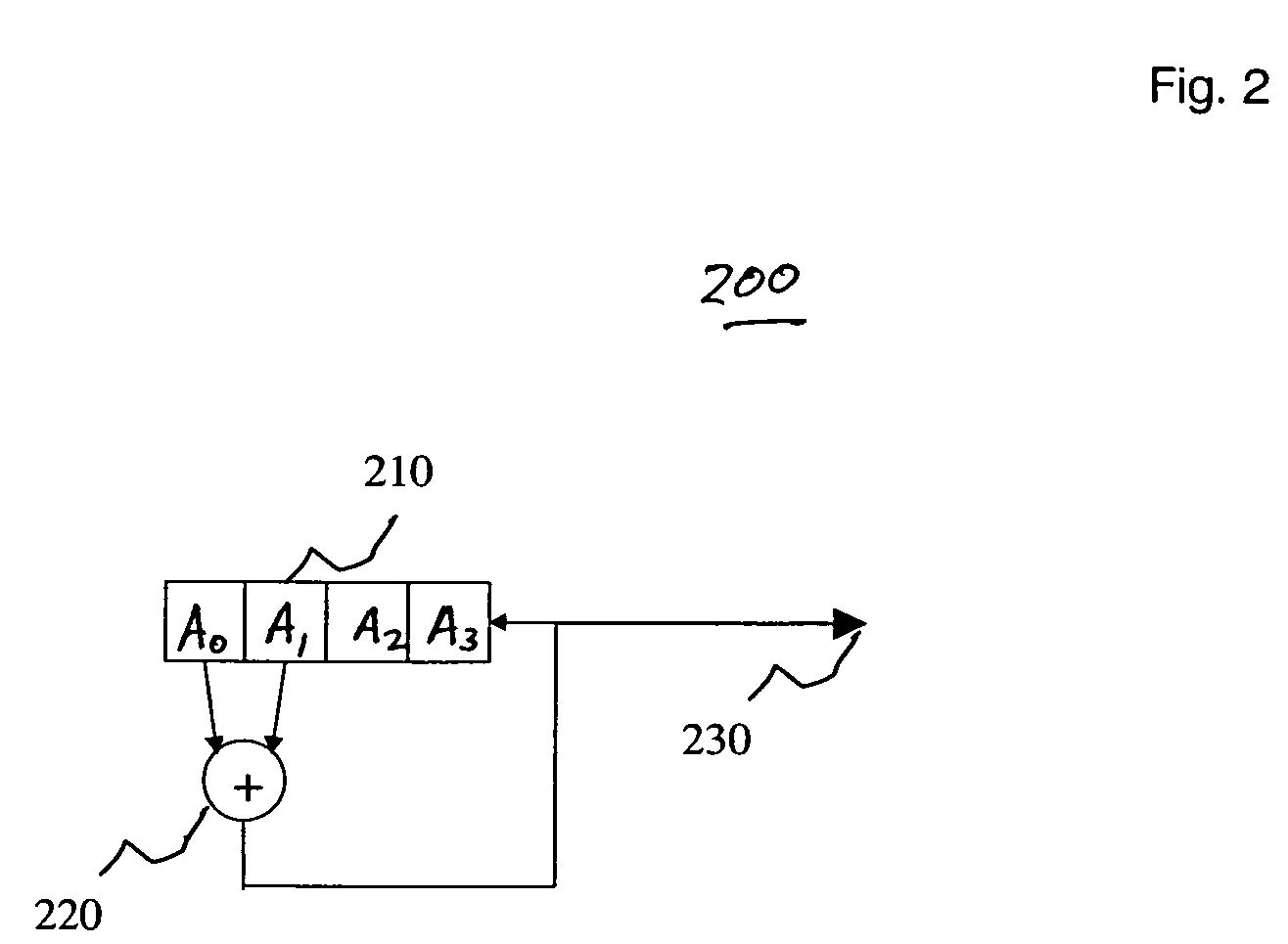

The invention discloses an any input signal bit stream adder based on sigma-delta modulation. The any input signal bit stream adder comprises a n input 1-bit binary adder, an enabling end control logic unit, a n-bit ring counter set and a n+1-bit data selector; the output end of the n input 1-bit binary adder is respectively connected with the enabling end control logic unit and the n+1-bit data selector; and the enabling end control logic unit, the n-bit ring counter set and the n+1-bit data selector are sequentially connected. According to the any input signal bit stream adder based on sigma-delta modulation disclosed by the invention, a n-bit code is used for representing an intermediate value required by a n input bit stream adder (n is an any value); the n-bit ring counter set is used for storing the intermediate value; corresponding ring counters are selected and driven under corresponding conditions to circularly output sequentially; the any input signal bit stream adder based on sigma-delta modulation is finally realized; and thus, the any input signal bit stream adder based on sigma-delta modulation has high operation precision.

Owner:NANJING UNIV OF FINANCE & ECONOMICS

Latch circuit, double data rate ring counter based on the latch circuit, hybrid counting device, analog-digital converting device, and CMOS image sensor

ActiveUS10103184B2Reduce in quantityHigh data rateElectric signal transmission systemsContinuously circulated pulse countersCMOSRing counter

Owner:SK HYNIX INC

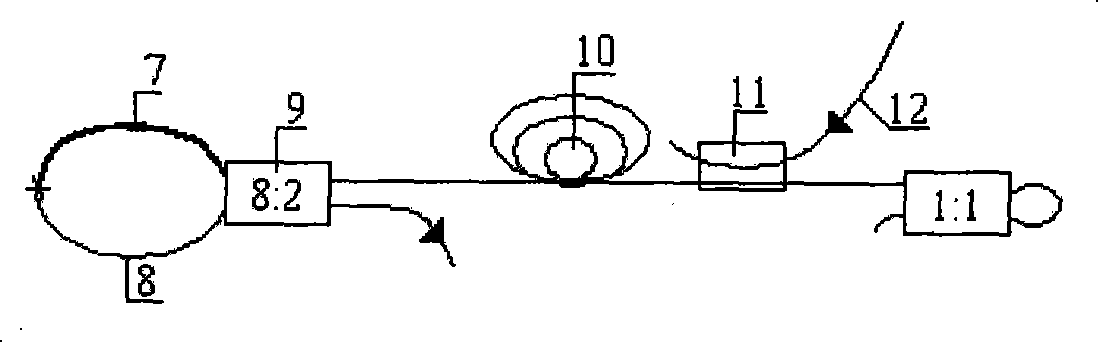

Method for transmitting a digital massage and system for carrying out said method

The invention relates to telecommunications, in particular to methods and means for transmitting digital messages and can be used for transmitting information through wire channels and telecommunication channels using electromagnetic waves. The use of said channels is simplified by excluding multiplication and division operators from the coding and a decoding process. Said invention makes it possible to transmit any messages from elements of Abelian group including code words whose elements are matrixes, polynomials, numbers of mixed-base notation and nonpositional notation. The inventive encoder comprises a driver clock (7), a function g<2> calculator (8), a pulse generator (9) having recurrent frequency of f(k+1) / k, a pulse recurrent frequency doubler (10), a ring counter (11) up to k, an adder-accumulator of elements of Abelian group (12), a key (13), a ring counter (14) up to (2k+1), an AND component (15), a main memory unit (16), a key (17), a trigger (18), a main memory unit (19) and a ring counter (20) up to (k+1). The inventive decoder comprises a driver clock (21), an adder-accumulator of elements of Abelin groupoid (21), a pulse generator (23) having recurrent frequency of fk(k+1) / k, a pulse recurrent frequency doubler (24), a ring counter (25) up to (k+1), a key (26), a main memory unit (27), a key (28), an AND component (29), a ring counter up to [2(k+1)+1] (30), an identification unit provided with a single element of Abelian group (31), a trigger (32), a main memory unit (33) a key (34), a ring counter (35) up to k.

Owner:MORTON FINANCE SA

Latch circuit, double data rate ring counter based on the latch circuit, hybrid counting device, analog-digital converting device, and CMOS image sensor

ActiveUS20170133418A1High data rateReduce the numberContinuously circulated pulse countersCounting chain synchronous pulse countersCMOSRing counter

Disclosed are a latch circuit receiving a negative output of a next stage latch circuit as a feedback input, a double data rate (DDR) ring counter based on the latch circuit to perform DDR counting of pulse periods and reduce the number of toggles, a hybrid counting device counting lower-bit portion by using the latch-based DDR ring counter and upper-bit portion by using a binary counter, and an analog-to-digital converting device and a CMOS image sensor employing the hybrid counting device. A double data rate ring counter may include a plurality of latches coupled in a ring type. The plurality of latches may include positive-edge-triggered latches and negative-edge-triggered latches arranged alternately. A current stage latch receives an output of a previous latch stage to shift to a next latch stage according to a counter clock, receives an output of the next latch stage to check a data shift to the next latch stage, and falls to a low level if the data shift is checked.

Owner:SK HYNIX INC

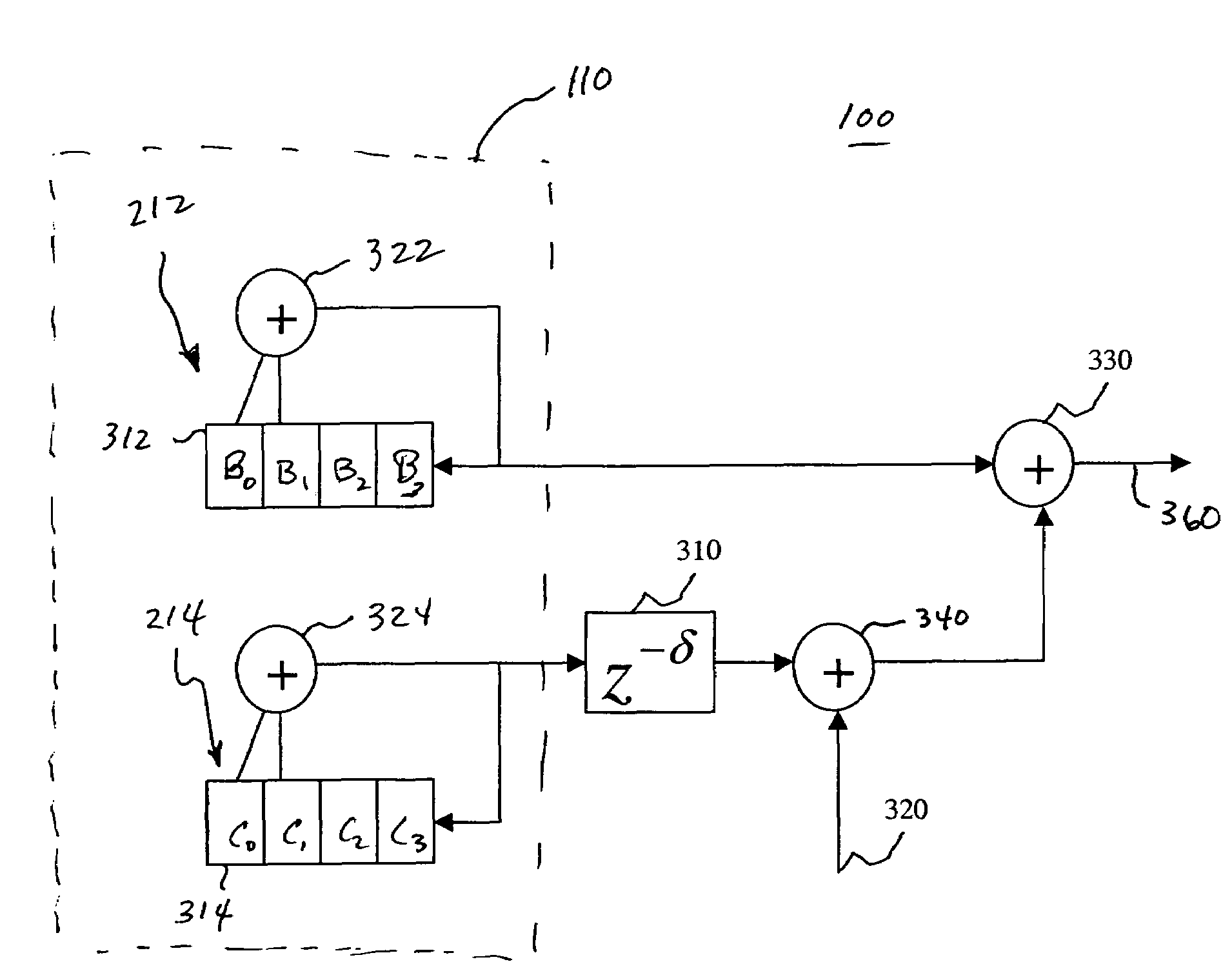

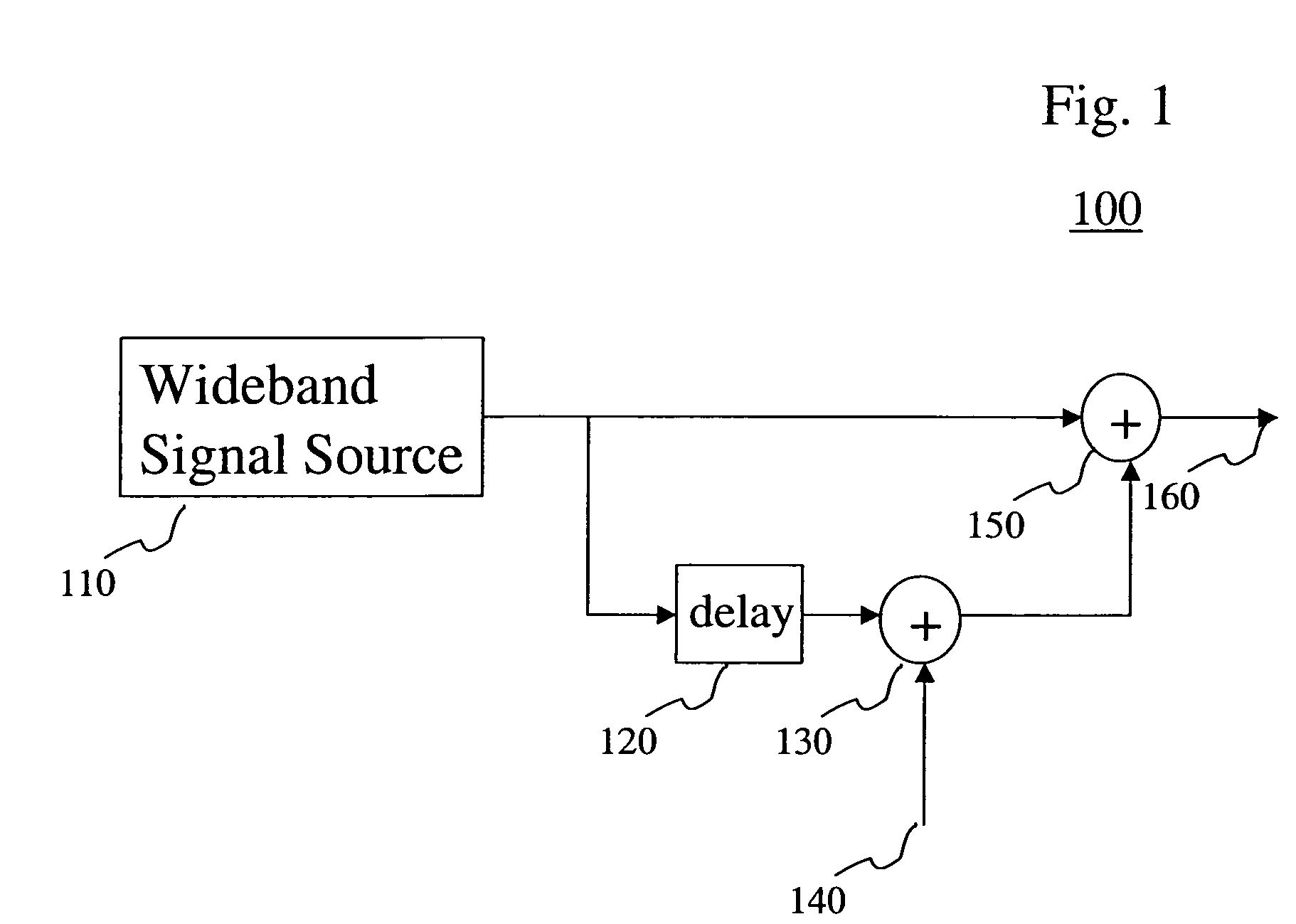

Time-delayed transmitted reference spread spectrum transmitter with digital noise generator

Circuits are provided for transmitted reference spread spectrum systems using a noise-like digital sequence with delayed replica. The circuits produce the digital spreading sequences at extremely high speed, and are capable of providing a great degree of signal spreading. A first embodiment is composed of a low speed section and a high-speed section. This embodiment allows for greater power efficiency without sacrificing sequence speed. In addition, the embodiment also allows shaping of the spectrum of the high-speed digital sequence. Further, this embodiment generates an m-sequence and its near delay by storing decimated pieces of the entire m-sequence over a plurality of end-around circulating shift registers or so-called ring counters. The ring counters can be run at low speed and there is no exclusive-oring operation. A time-delayed transmitted reference spread spectrum transmitter is provided using digital noise generators that are capable of very high speed operation.

Owner:ABB (SCHWEIZ) AG

Low-power delay buffer circuit

ActiveUS7170800B2Reduce power consumptionPulse automatic controlDigital storageAddress decoderRing counter

Owner:NAT TAIWAN UNIV

Relatively prime mode parallel counter based on congruence theory

InactiveCN1688109AOvercoming common problemsAvoid situations where the state is not uniqueContinuously circulated pulse countersCounting chain synchronous pulse countersShift registerRing counter

A relative prime modulo parallel counter based on the congruent theory relates to a counter of synchronous shift register type composed of a first, a second synchronous ring counters, and a decode unit, among which, the numbers of triggers in any two synchronous ring counters from the first to r are prime mutually, the clock pulse input ends of all synchronous ring counters are connected and linked to the clock pulse signals, the positive output or negative output end of each trigger in all said counters are connected to an input end of the decode unit. It uses the counter as its basic component and numbers of triggers in each are prime mutually, so a large count can be got with only a few ring counters.

Owner:HARBIN INST OF TECH

Apparatus and method for determination of signal format

InactiveUS8237494B2Multiple input and output pulse circuitsMultiple modulation transmitter/receiver arrangementsRing counterSignal analyzer

The determination of the signal modulation format for a channel is an important aspect of the operation of a signal receiver. A method (700) is described including the steps of receiving (710) a signal, comparing (720) a sample of the received signal to a first threshold value and a second threshold value, creating (720) a signal profile based on the comparison, and selecting (750) a modulation format for the received signal based on the signal profile. An apparatus (500) is also described including a ring counter (510) that receives a sample of an input signal, compares the sample to a first threshold value and a second threshold value, and creates a signal profile for the input signal, a signal profiler (550) that compares the signal profile for the input signal to at least two reference profiles, and a detector (560) that determines a modulation format for the input signal based on the comparison in the signal profiler (550).

Owner:MAGNOLIA LICENSING LLC