Relatively prime mode parallel frequency divider based on congruence theory

A frequency divider, theoretical technology, applied in the field of high-speed digital frequency divider, can solve problems such as low failure frequency and complex control logic

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

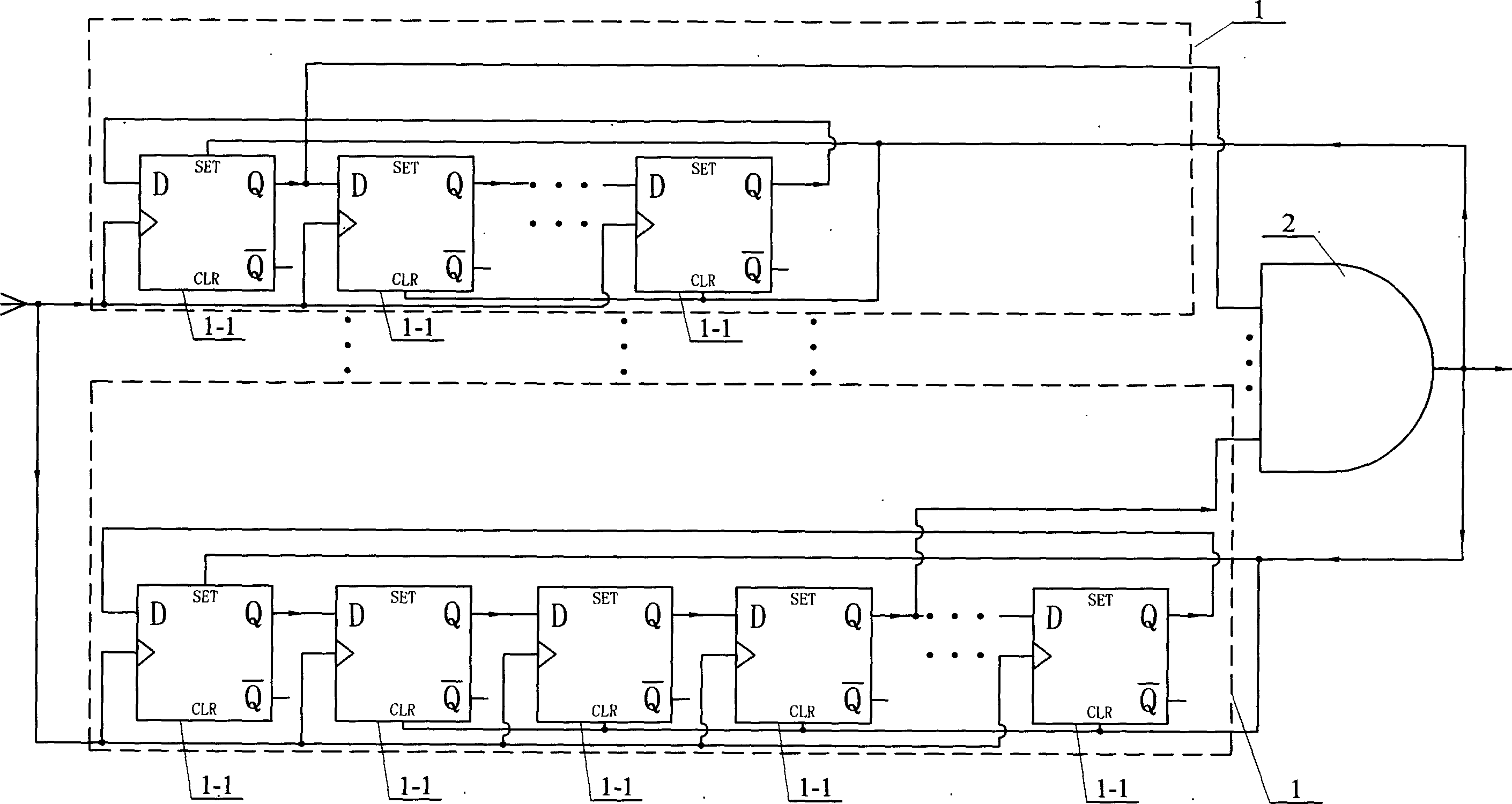

[0007] Specific implementation mode one: combine figure 1 Describe the present embodiment, it is made up of a plurality of synchronous ring counters 1, multi-input AND gate 2; In each synchronous ring counter 1, the Q output end of a D-type flip-flop 1-1 corresponding to the frequency division number is connected to multiple On one input end of the input AND gate 2; the clock signal input ends of each D-type flip-flop 1-1 in each synchronous ring counter 1 are all connected to each other and are frequency divider input ends; in each synchronous ring counter 1 The SET setting terminal of the first D-type flip-flop 1-1 of the D-type flip-flop 1-1 and the CLR reset terminal of all other D-type flip-flops 1-1 are connected to the output terminal of the multi-input AND gate 2 and are the output terminals of the frequency divider. The numbers of D-type flip-flops 1-1 in the two synchronous ring counters 1 are all mutually prime numbers. The components in this embodiment can be comp...

specific Embodiment approach 2

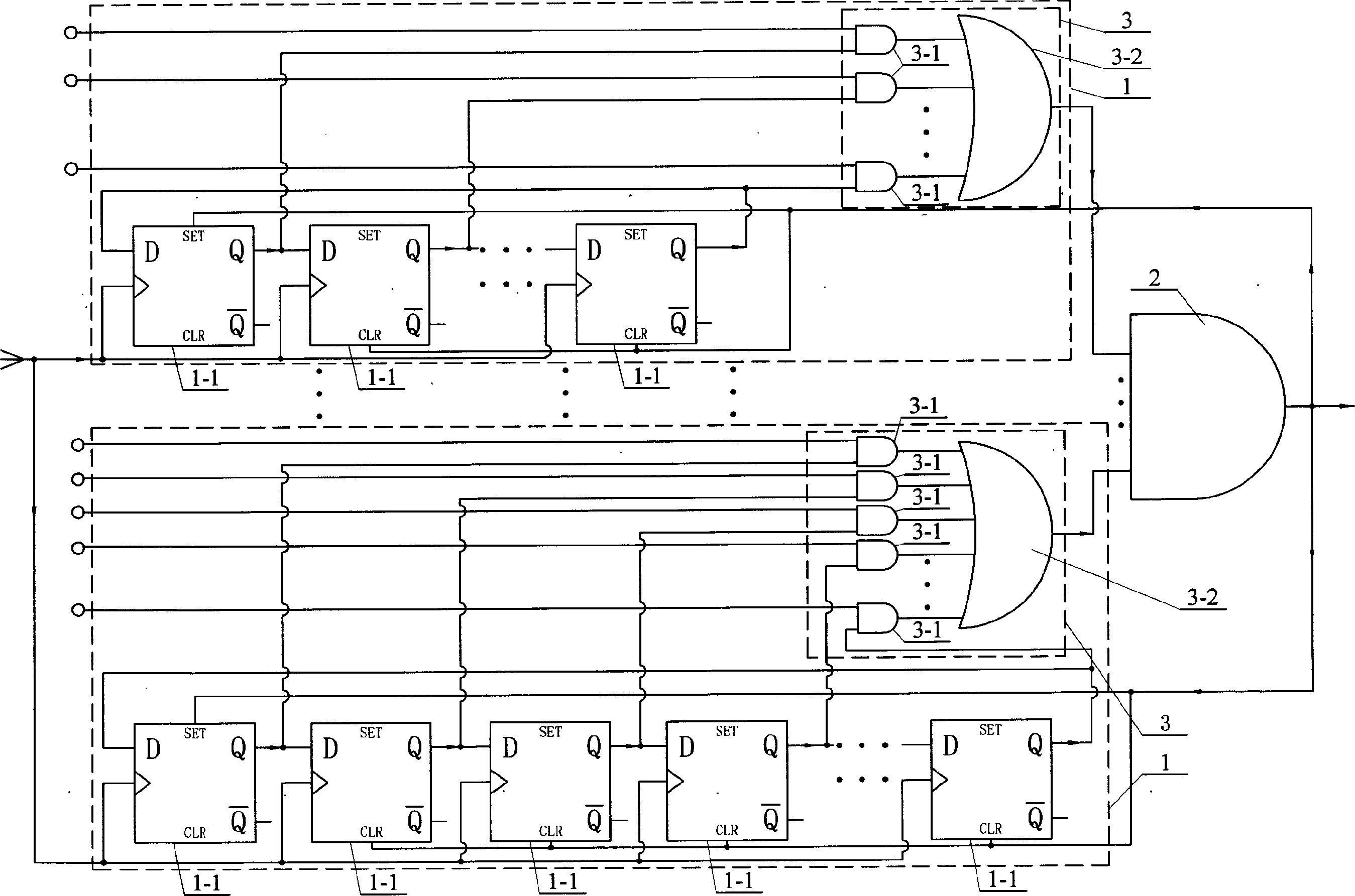

[0008] Specific implementation mode two: combination figure 2 Illustrate this embodiment mode, present embodiment mode is increased in each synchronous ring counter 1 on the basis of specific embodiment one and has frequency division number programmable control circuit 3; Frequency division number programmable control circuit 3 is made of a plurality of two input AND gate 3-1, composed of multi-input OR gate 3-2; the Q output terminal of each D-type flip-flop 1-1 is respectively connected with one input terminal of a two-input AND gate 3-1, and each two-input AND gate The other input terminal of 3-1 is the frequency division number setting terminal, and the output terminals of each two-input AND gate 3-1 are all respectively connected with an input terminal of the multi-input OR gate 3-2, and the multi-input OR gate 3-2 The output terminals of -2 are respectively connected with one input terminal of the multi-input AND gate 2 . Other compositions and connections are the same...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More