OR logic circuit and chip

A logic circuit and voltage technology, applied in the electronic field, can solve problems such as the size limitation of MOS tube storage devices, and achieve the effects of good scalability, high performance, and strong endurance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] The technical solutions in the embodiments of the present invention will be clearly and completely described below in conjunction with the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without creative efforts fall within the protection scope of the present invention.

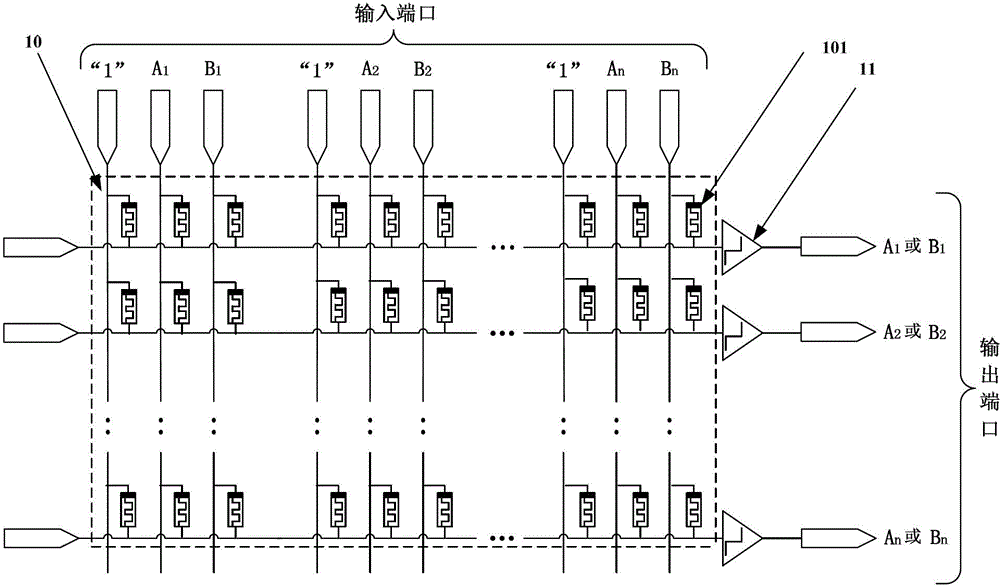

[0025] Such as figure 1 Shown is a schematic diagram of an OR logic circuit in an embodiment of the present invention.

[0026] The OR logic circuit may include a resistive memristor array 10 and a comparator 11 . In the resistive memristor array 10, the positive phase input terminals of the same column resistance variable memristor 101 are connected, so that the positive phase input terminal of the same column resistance variable memristor 101 is used as a signal i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More