Silicon-based photoelectric detector for photoelectric monolithic integration and preparation method thereof

A photodetector and monolithic integration technology, which is applied in semiconductor/solid-state device manufacturing, circuits, electrical components, etc., can solve problems such as low frequency response, poor short-wave response, and incomplete compatibility between preparation technology and standard technology, and achieve good results. Isolation effect, compatibility of preparation process, and the effect of overcoming poor short-wave response

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0054] The following embodiments will further illustrate the present invention in conjunction with the accompanying drawings.

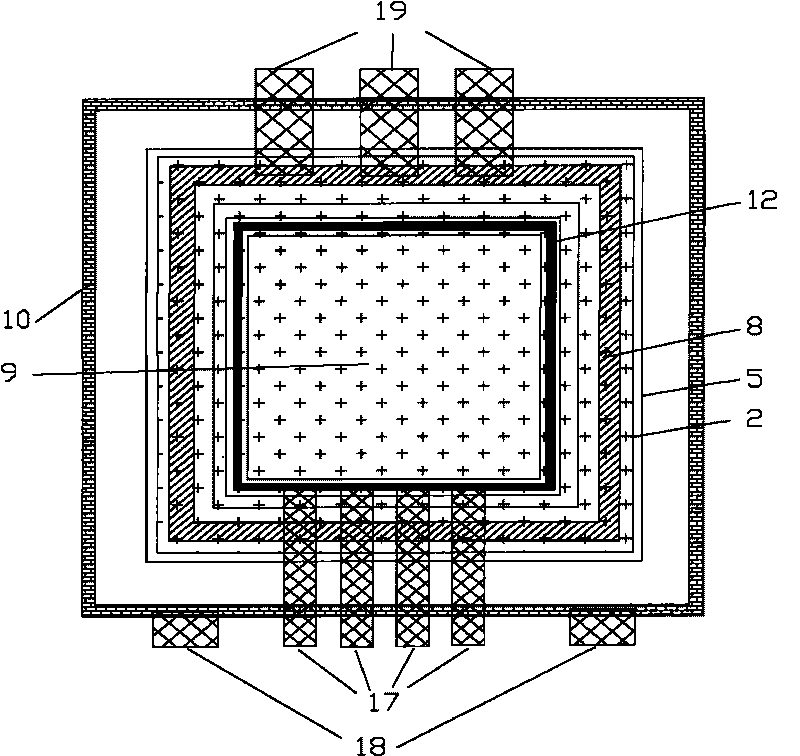

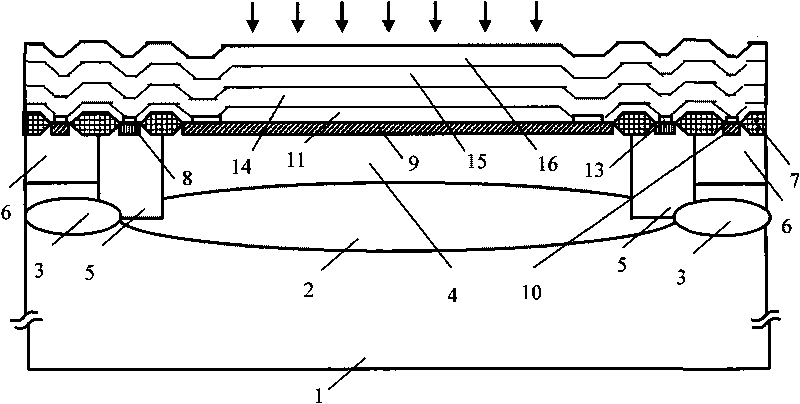

[0055] figure 1 and figure 2 The manufacturing process flow of the silicon-based photodetector under the BCD standard process shown is as follows: first, BN is photolithographically etched on a P-type silicon substrate 1 with a resistivity of 15-25Ωcm. + The buried layer region, and the implantation dose is about 1×10 by ion implantation process 15 Antimony forms BN + Buried layer 2. The implantation dose by ion implantation process is about 4×10 12 The boron forms BP + Buried layer 3. in BN + Buried layer 2 and BP + An N-EPI epitaxial layer 4 is grown on the buried layer 3 . The resistivity of the N-EPI epitaxial layer 4 is 3.5 Ωcm, and the thickness is 4.5 μm. The N well region is photolithographically etched on the epitaxial layer 4, and the implantation dose is about 6.5×10 by ion implantation process. 12 Phosphorus is used to realize...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More