Silicon-based monolithic optoelectronic integrated receiver chip for automatic power meter reading system

A meter reading system, a silicon-based monolithic technology, applied in circuits, electrical components, semiconductor devices, etc., can solve problems such as unfavorable promotion and popularization of plastic optical fiber communication technology, complicated manufacturing and assembly processes, and affecting system reliability, etc. Poor short-wave response, reducing junction capacitance, and overcoming the effect of large junction capacitance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] The following embodiments will further illustrate the present invention in conjunction with the accompanying drawings.

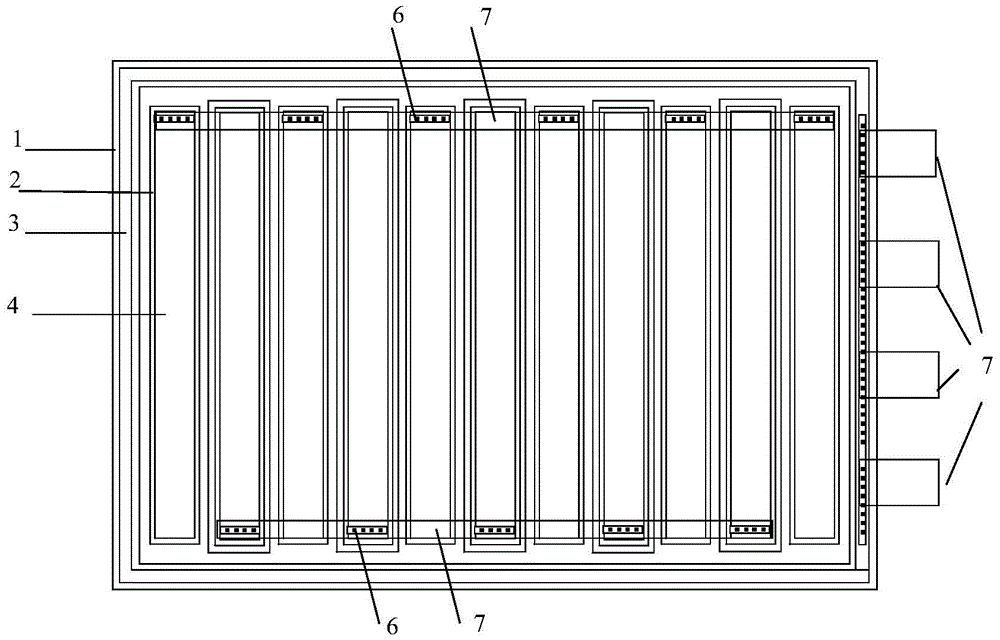

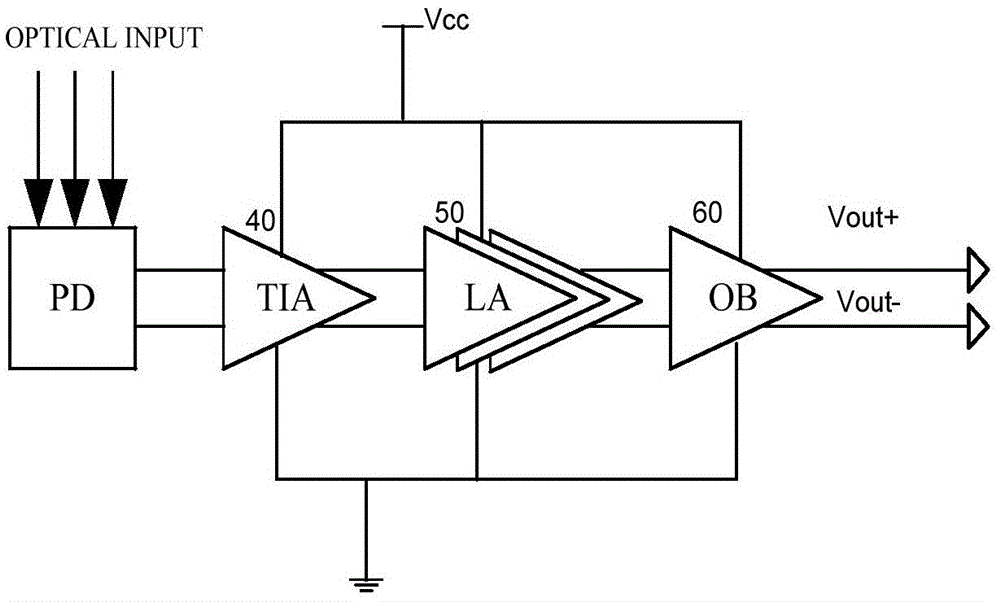

[0030] see Figure 1~6 , the embodiment of the present invention is provided with a silicon-based photodetector and an amplifying integrated circuit followed by the silicon-based photodetector;

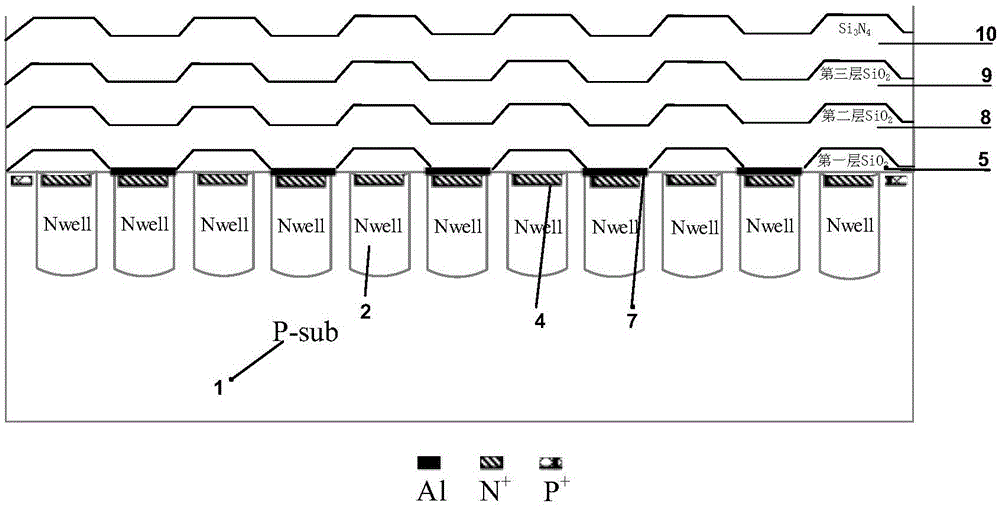

[0031] The silicon-based photodetector adopts an "N+ / N-Well / P-Sub" structure, and the vertical structure of the silicon-based photodetector is as follows from bottom to top: the first layer is a low-doped P-type silicon substrate ( P-Substrate) 1; the second layer is N well (N-Well) 2; the third layer is N-type heavily doped silicon (N+) 4, P-type heavily doped silicon (P+) 3, metal aluminum (Al) 7; The fourth to sixth layers are three-layer SiO 2 Insulating dielectric layers 5, 8, 9; the seventh layer is Si 3 N 4 Surface passivation layer 10; the P-type silicon substrate (P-Substrate) 1, N well (N-Well) 2, N-type heavily doped silicon (N+) 4, P-type heav...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More