Ring gate field effect transistor and preparation method thereof

A field-effect transistor and gate-all-around technology, applied in the field of semiconductor integrated devices, can solve problems affecting the performance of CMOS devices, and achieve the effects of suppressing short-channel effects, improving gate control capability and current driving capability, and improving mobility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

[0049] The invention discloses a method for preparing a gate-around field effect transistor, which comprises the following steps:

[0050] Step 1, forming a bonding metal layer, a first gate dielectric layer, a first interface control layer, a channel layer, a second interface control layer, a source-drain layer and a semiconductor material layer on the substrate;

[0051] Step 2, etching to remove the semiconductor material layer, and etching to form a convex structure in the channel region, the convex part is etched to the second interface control layer, and both sides of the convex part are etched to the first gate dielectric layer;

[0052] Step 3, growing a third interface control layer on both side walls of the protruding part of the channel region, and forming a second gate dielectric layer from bottom to top on the upper surface of the protruding part separated by a certain distance from the source region and the drain region and a second gate metal layer, extending to...

Embodiment 1

[0077] This embodiment proposes a method for manufacturing a gate-all-around field effect transistor, including the following steps:

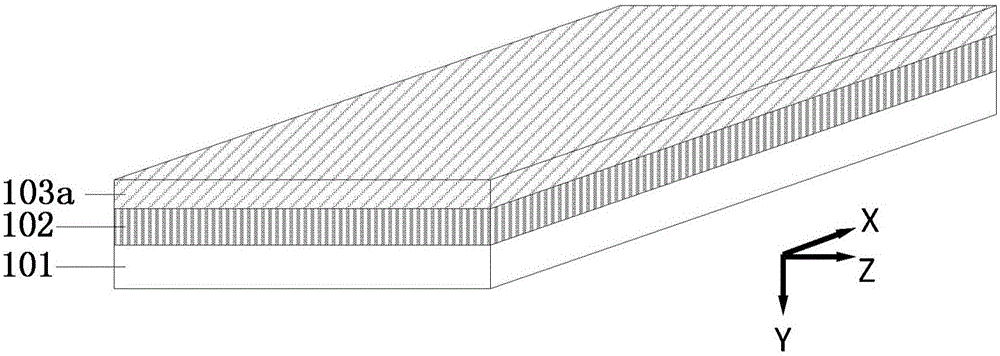

[0078] Step 1, forming a bonding metal layer 103, a first gate dielectric layer 105a, a first interface control layer 106a, a channel layer 107, a second interface control layer 106b, a source-drain layer 108 and a semiconductor material layer on the substrate 101 110;

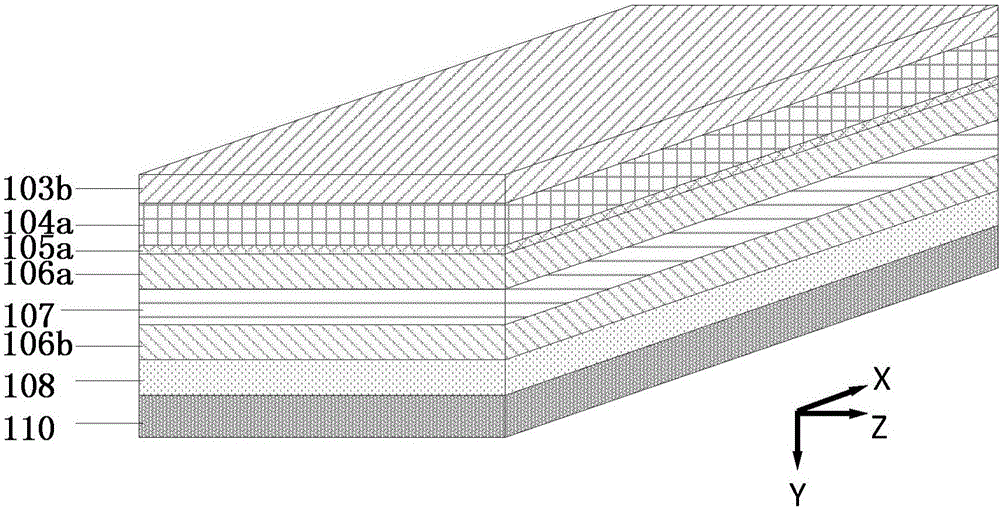

[0079] Step 2, such as Figure 5 As shown, the semiconductor material layer 110 is removed by etching, and as Figure 6 As shown, a convex-shaped structure is formed by etching in the channel region, the protruding part is etched to the second interface control layer 106b, and both sides of the protruding part are etched to the first gate dielectric layer 105a. After etching, the channel region Cross section as Figure 7 shown;

[0080] Step 3, if Figure 8 As shown, a third interface control layer 106c is grown on both side walls of the protruding part of the channel regi...

Embodiment 2

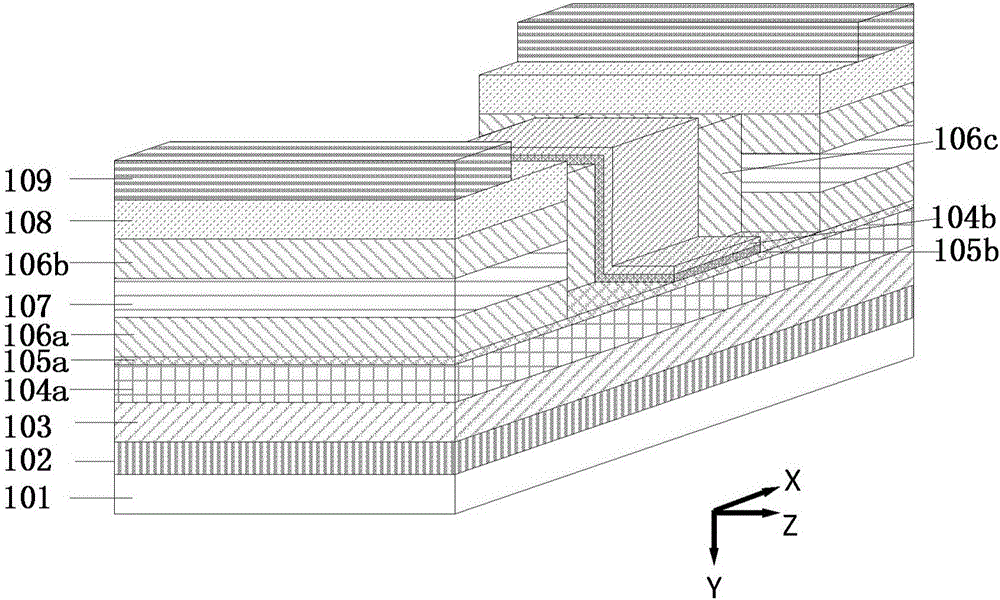

[0103] Such as figure 1 As shown, this embodiment proposes a gate-all-around field effect transistor, which is prepared by the preparation method in Example 1, and includes a source region, a drain region and a channel region, and the channel region is located between the source region and the drain region Between and integral molding, it is characterized in that:

[0104] The longitudinal direction of the channel region is convex; the protruding parts of the source region, the drain region and the channel region are successively stacked with a substrate 101, a first gate dielectric layer 105a, a first interface control layer 106a, a A channel layer 107, a second interface control layer 106b; a substrate 101 and a first gate dielectric layer 105a are sequentially stacked on the platforms on both sides of the protruding part of the channel region;

[0105] The left and right side walls of the protruding part of the channel region have a third interface control layer 106c, and ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More