Patents

Literature

224results about "Impedence convertors" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

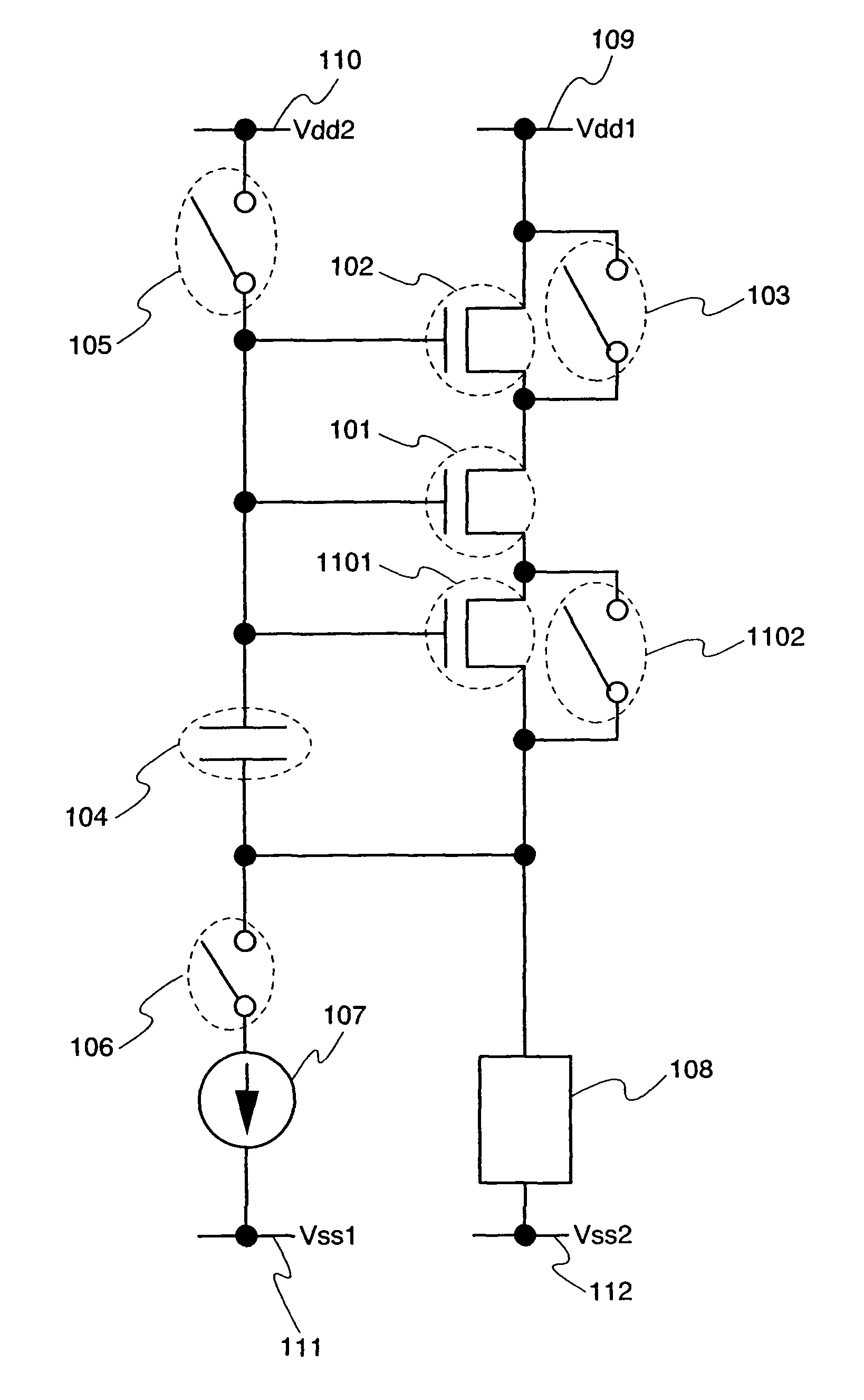

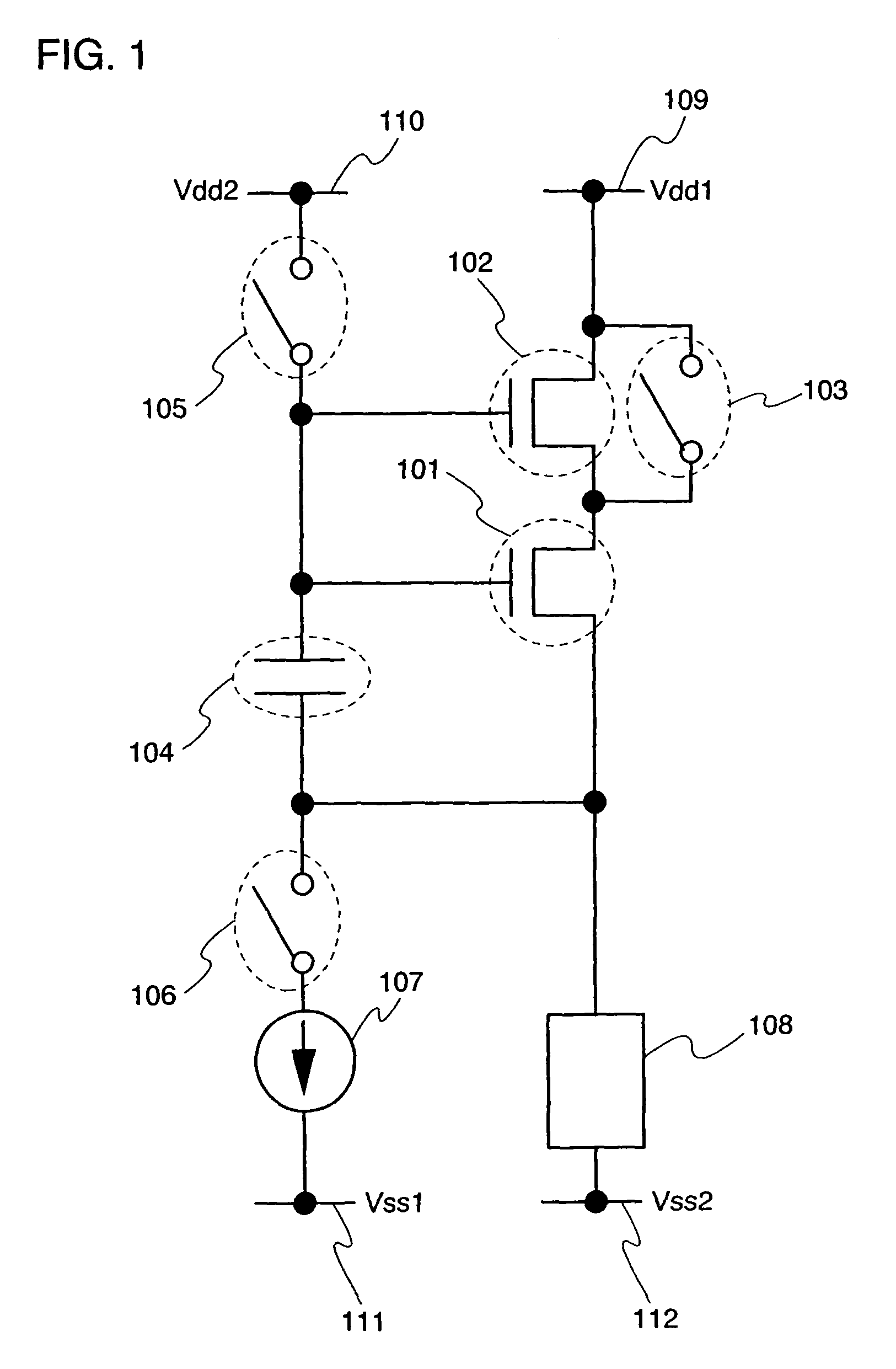

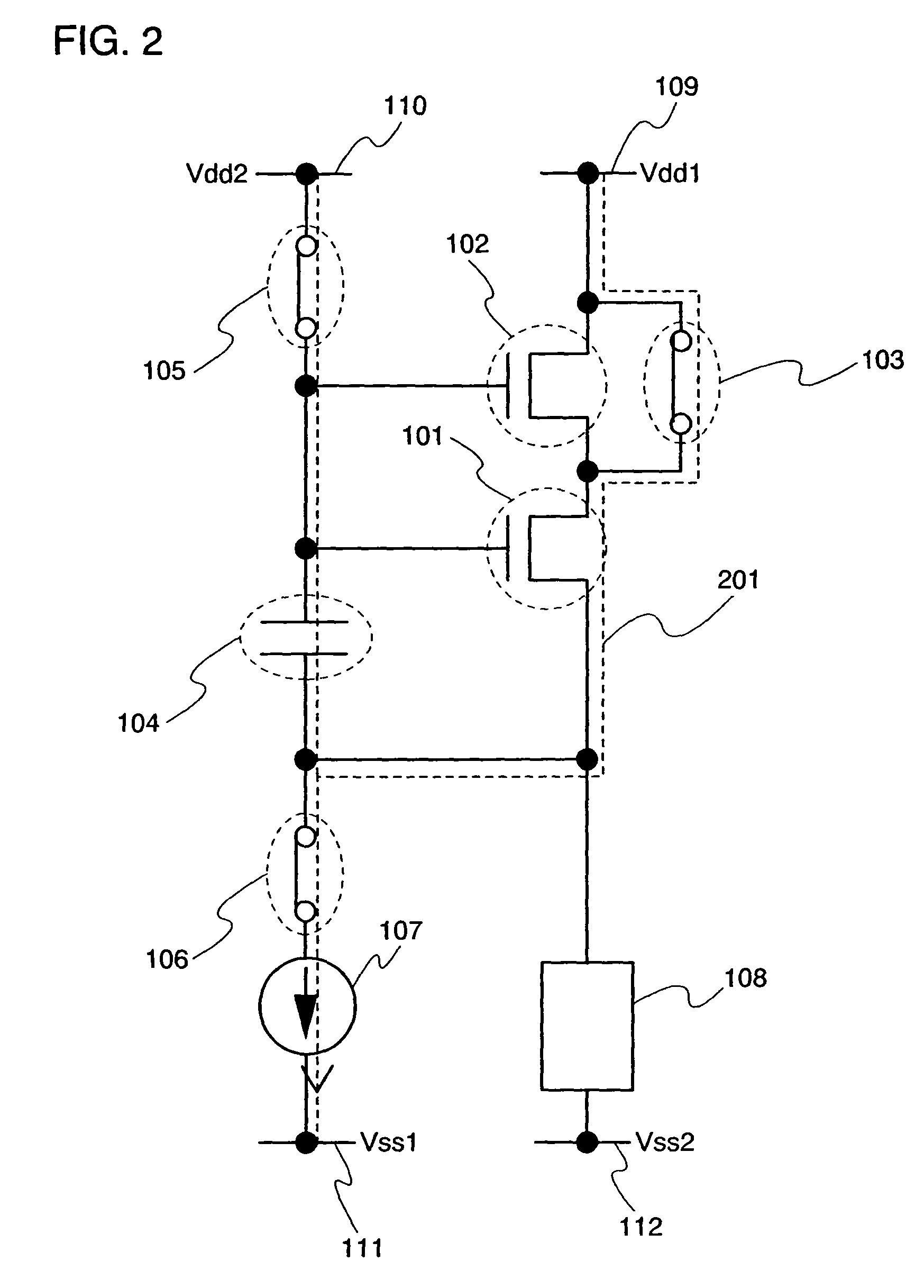

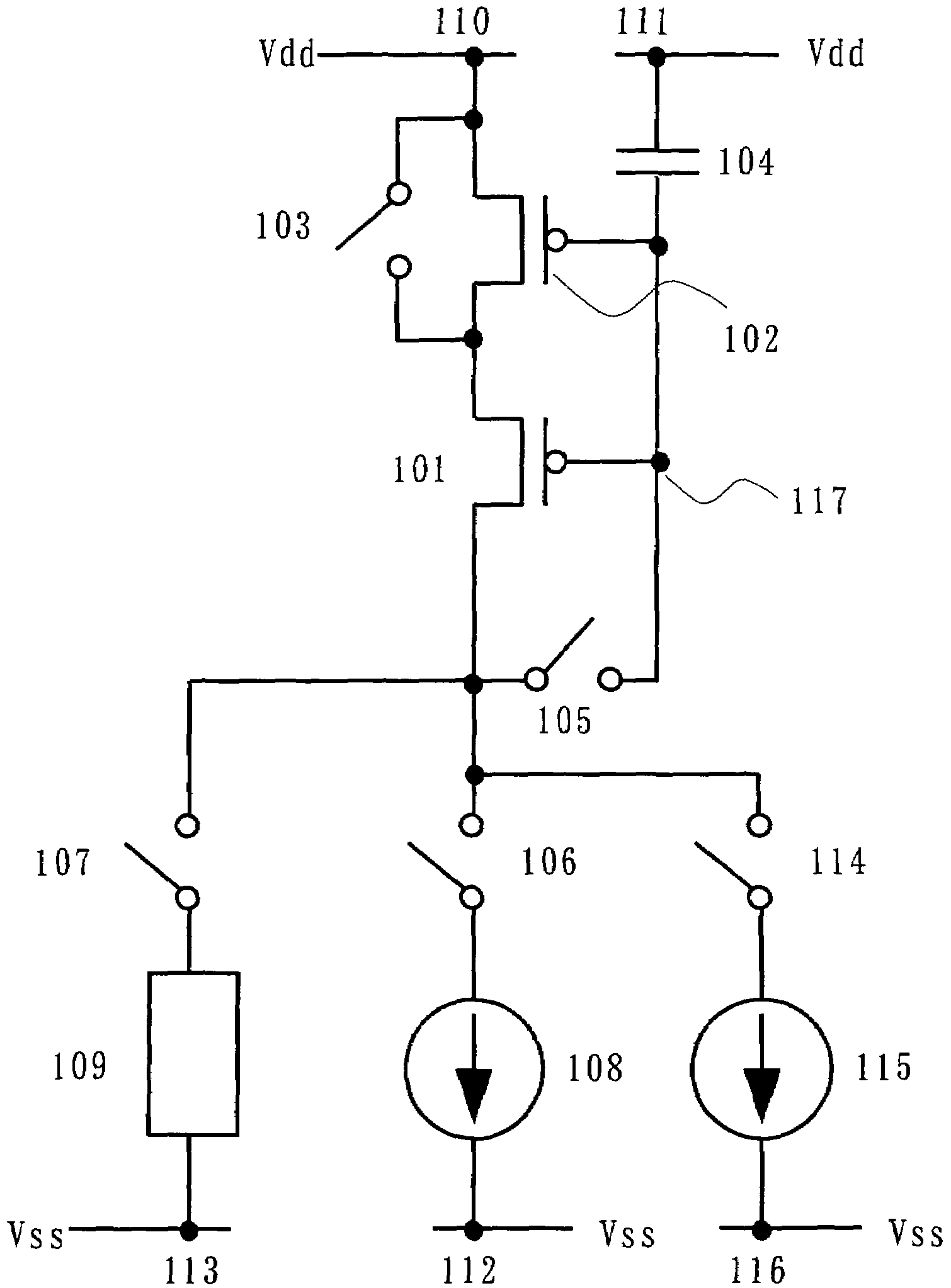

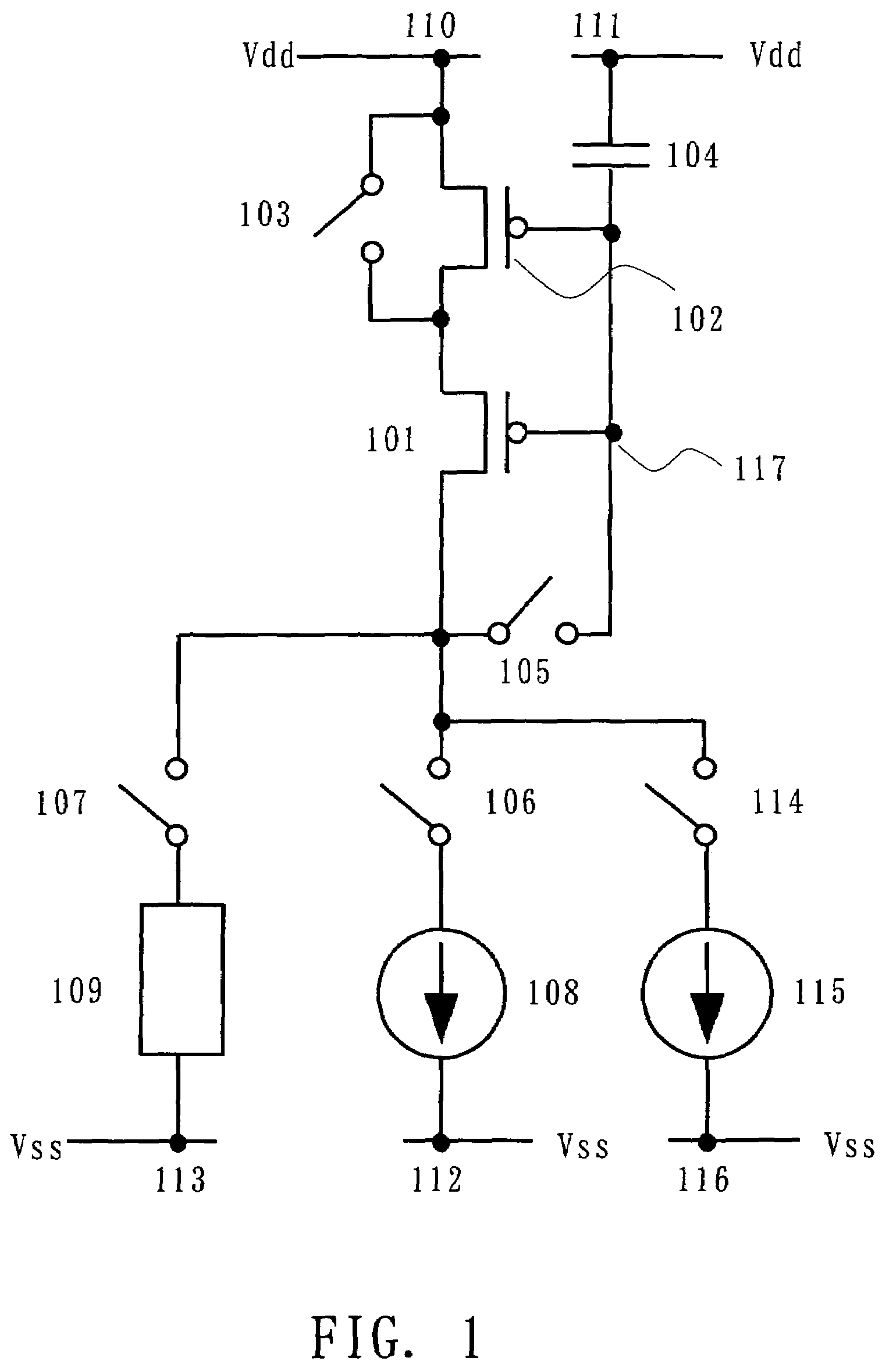

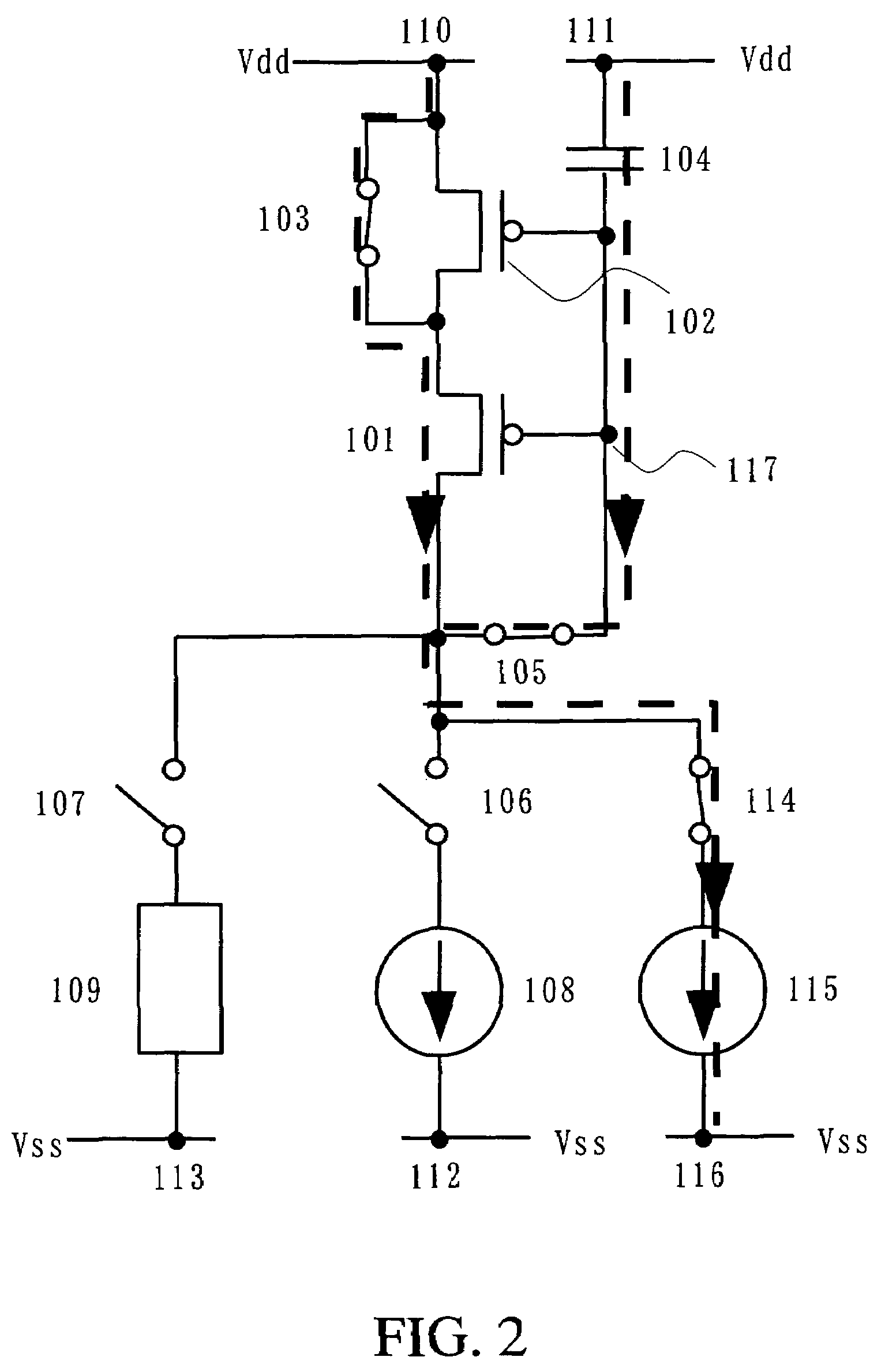

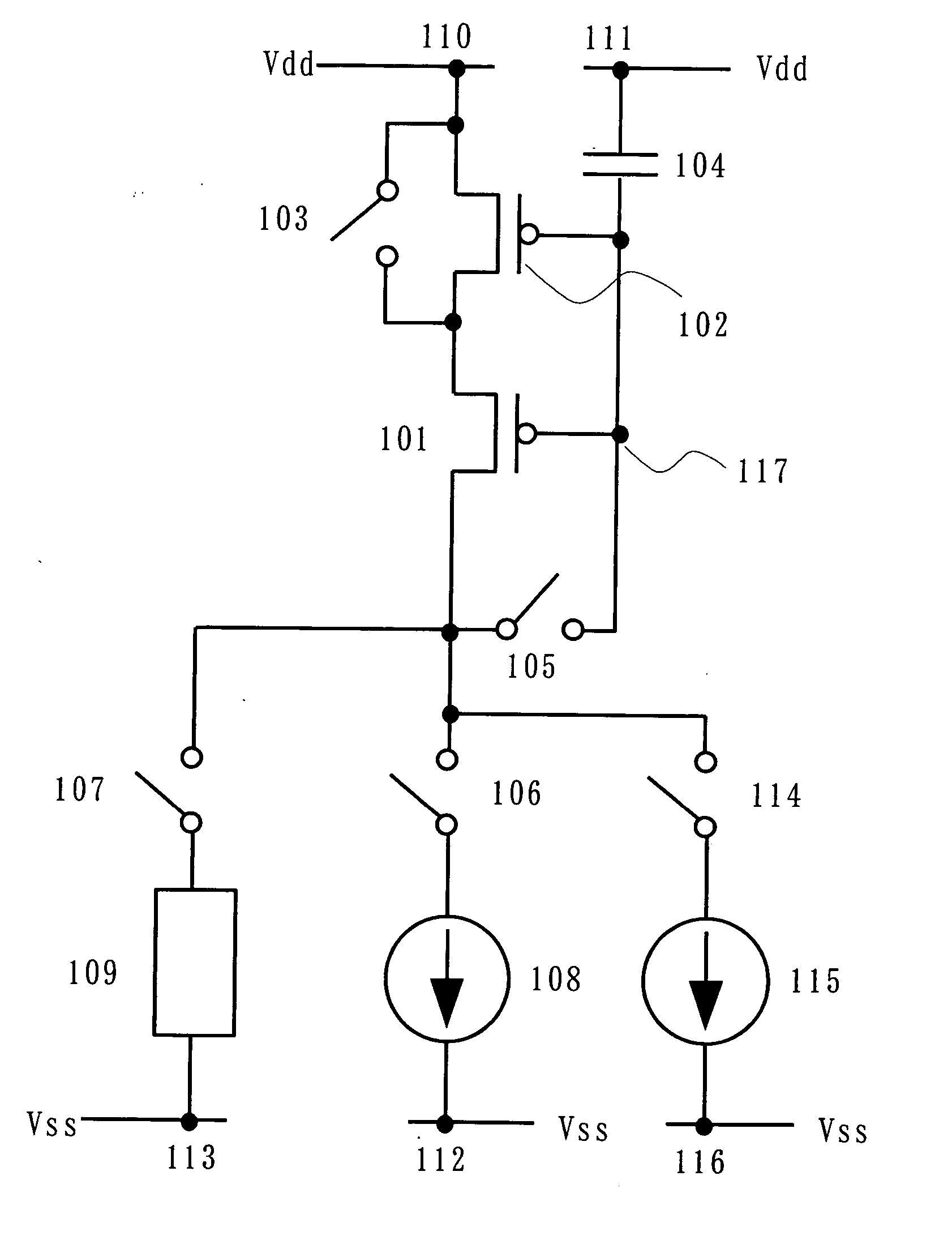

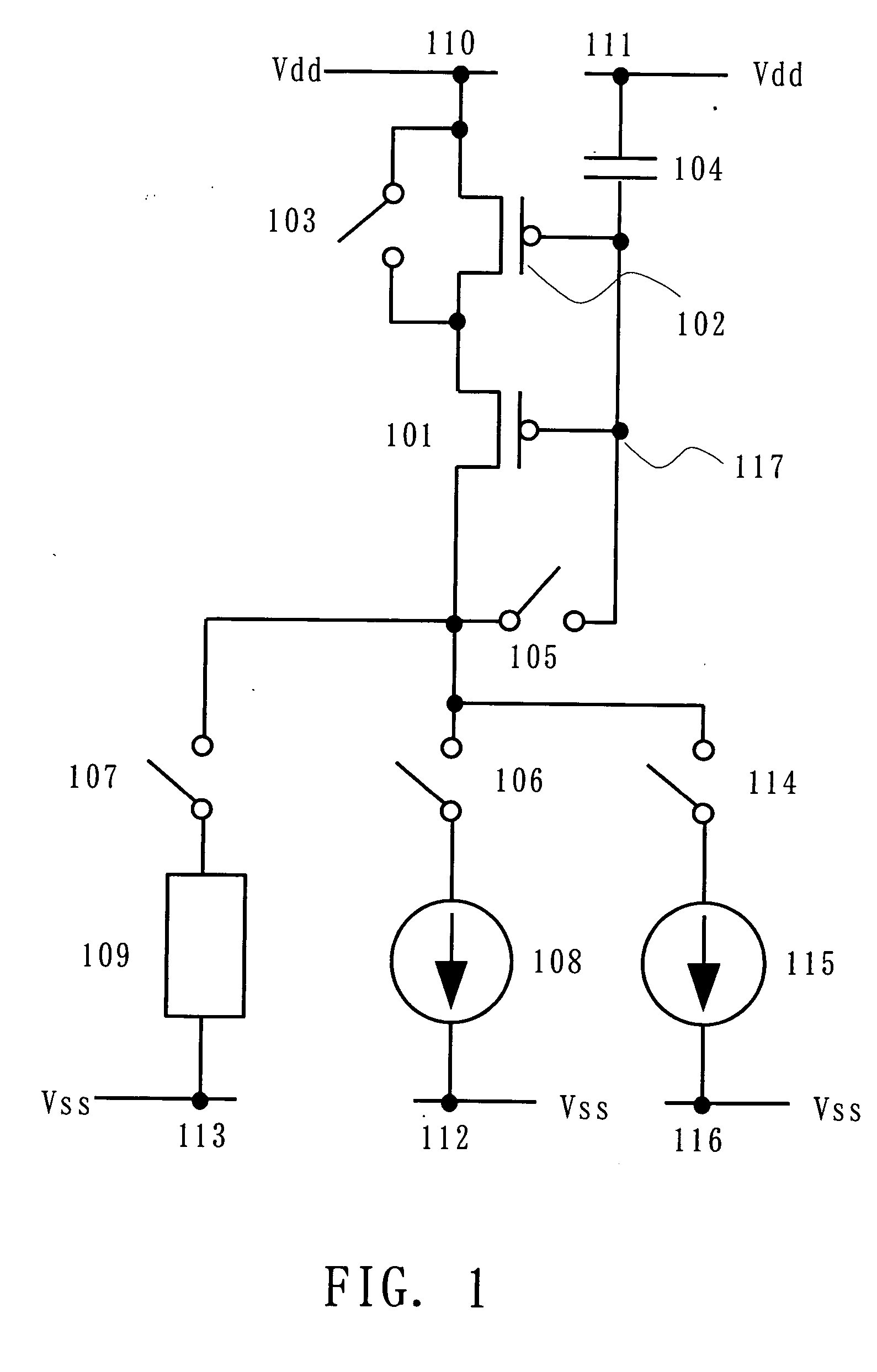

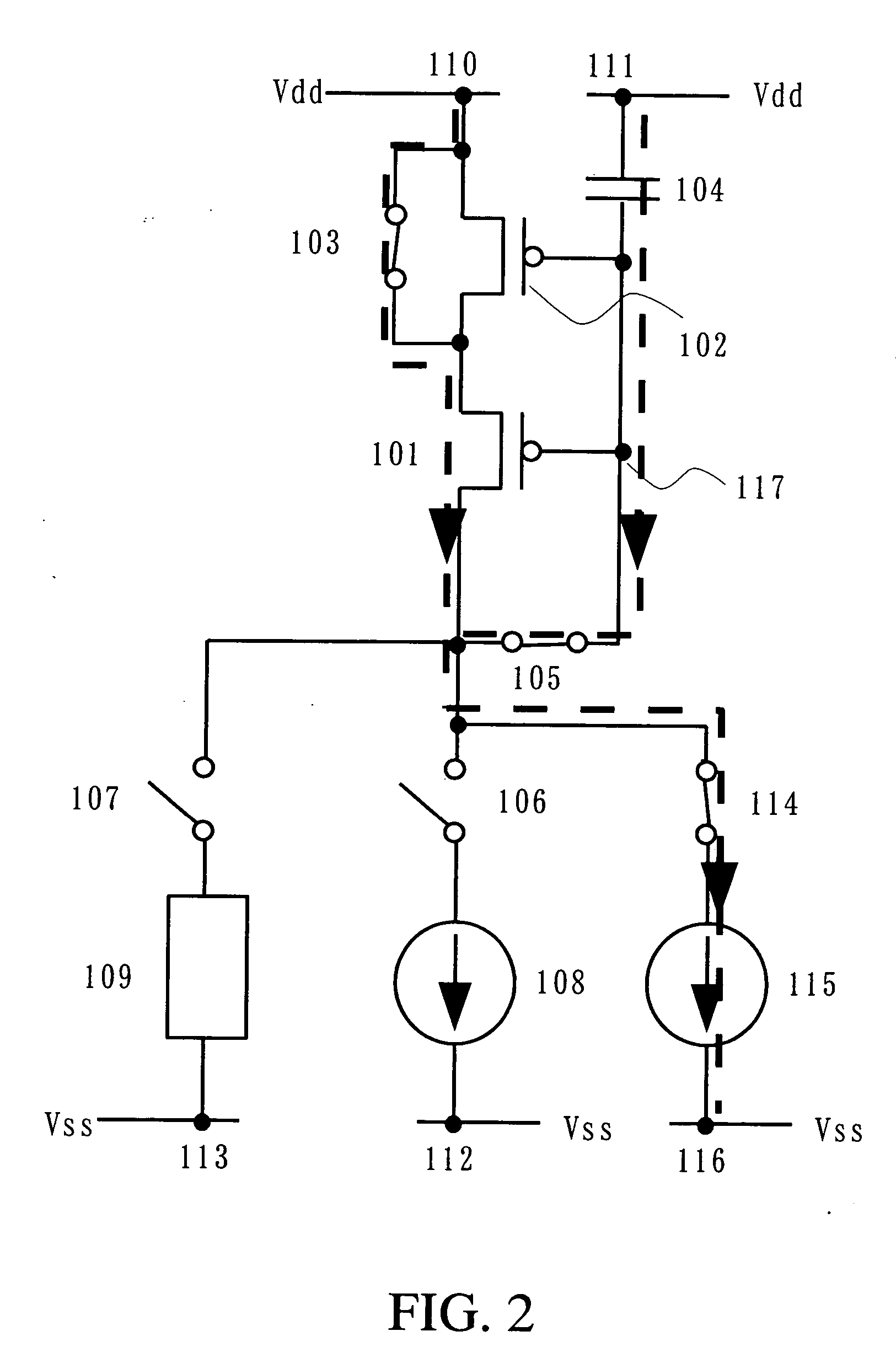

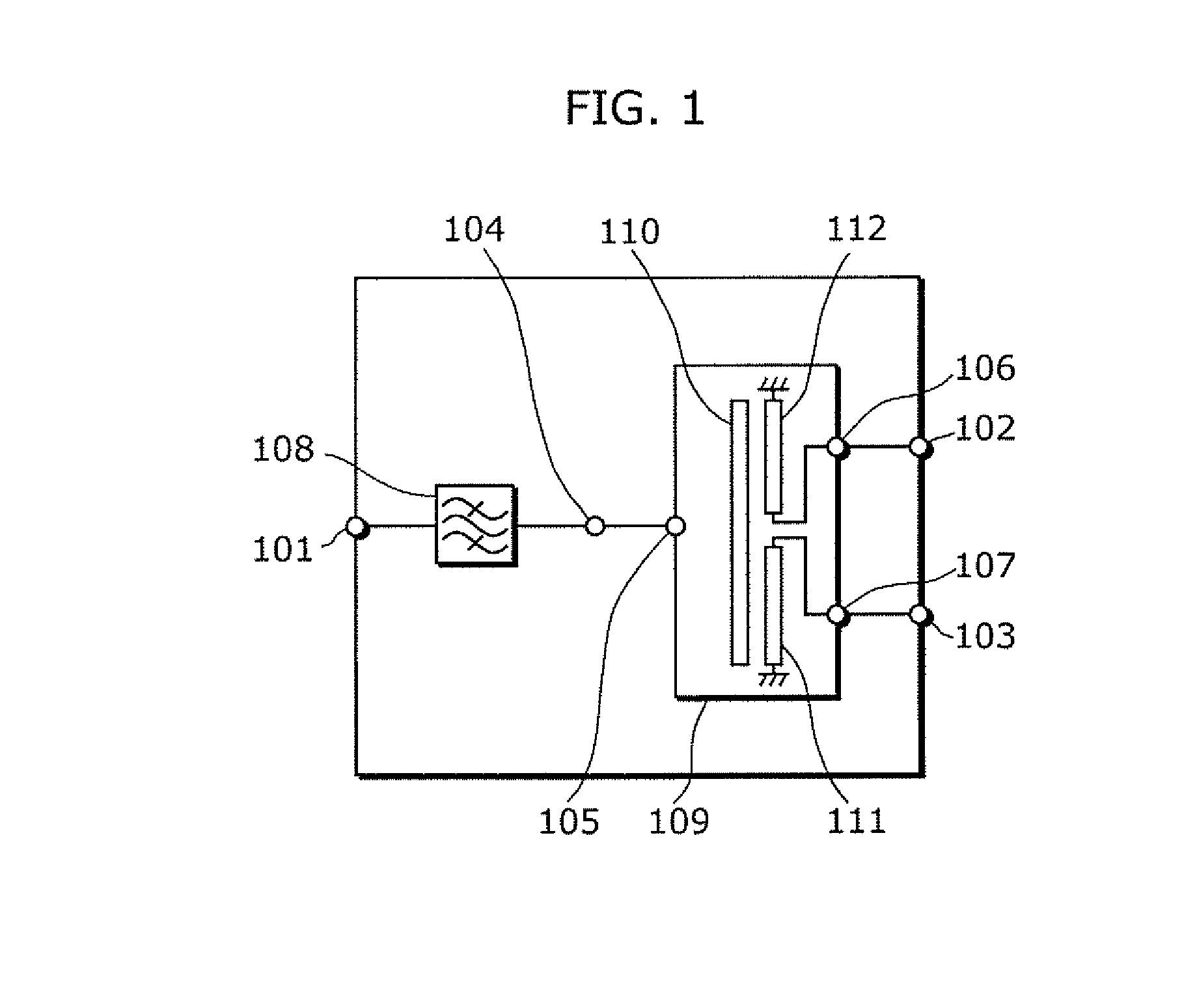

Semiconductor device, display device and electronic device equipped with the semiconductor device

InactiveUS20070035340A1Reduce power consumptionAvoid flowImpedence convertorsElectroluminescent light sourcesCapacitanceElectrical resistance and conductance

The present invention provides a semiconductor device which can prevent a current from flowing into a display element at a signal writing operation, without increasing power consumption and without changing a potential of a power supply for supplying a current to a load in each row. When a predetermined current is supplied to a transistor to set a gate-source voltage of the transistor, a potential of a gate terminal of the transistor is adjusted so as to prevent a current from flowing into a load which is connected to a source terminal of the transistor. Thus, a potential of a wire connected to the gate terminal of the transistor is made different from that of a wire connected to a drain terminal of the transistor. At that time, an operation of a transistor is shifted so as to allow a large amount of current to flow, and influences by intersection capacitance parasitic to a wire or the like or wire resistance are hardly caused, and a set operation is conducted quickly.

Owner:SEMICON ENERGY LAB CO LTD

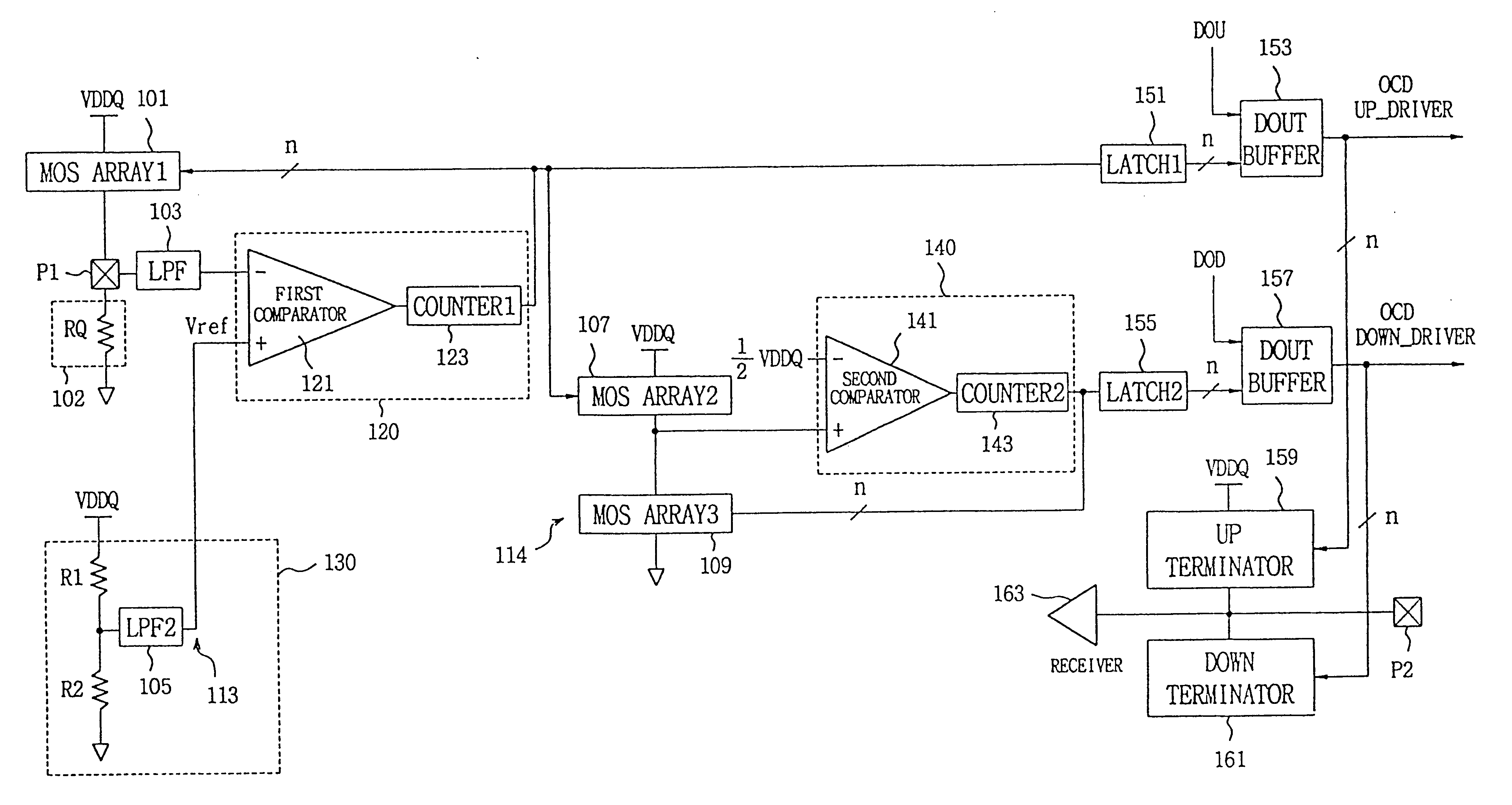

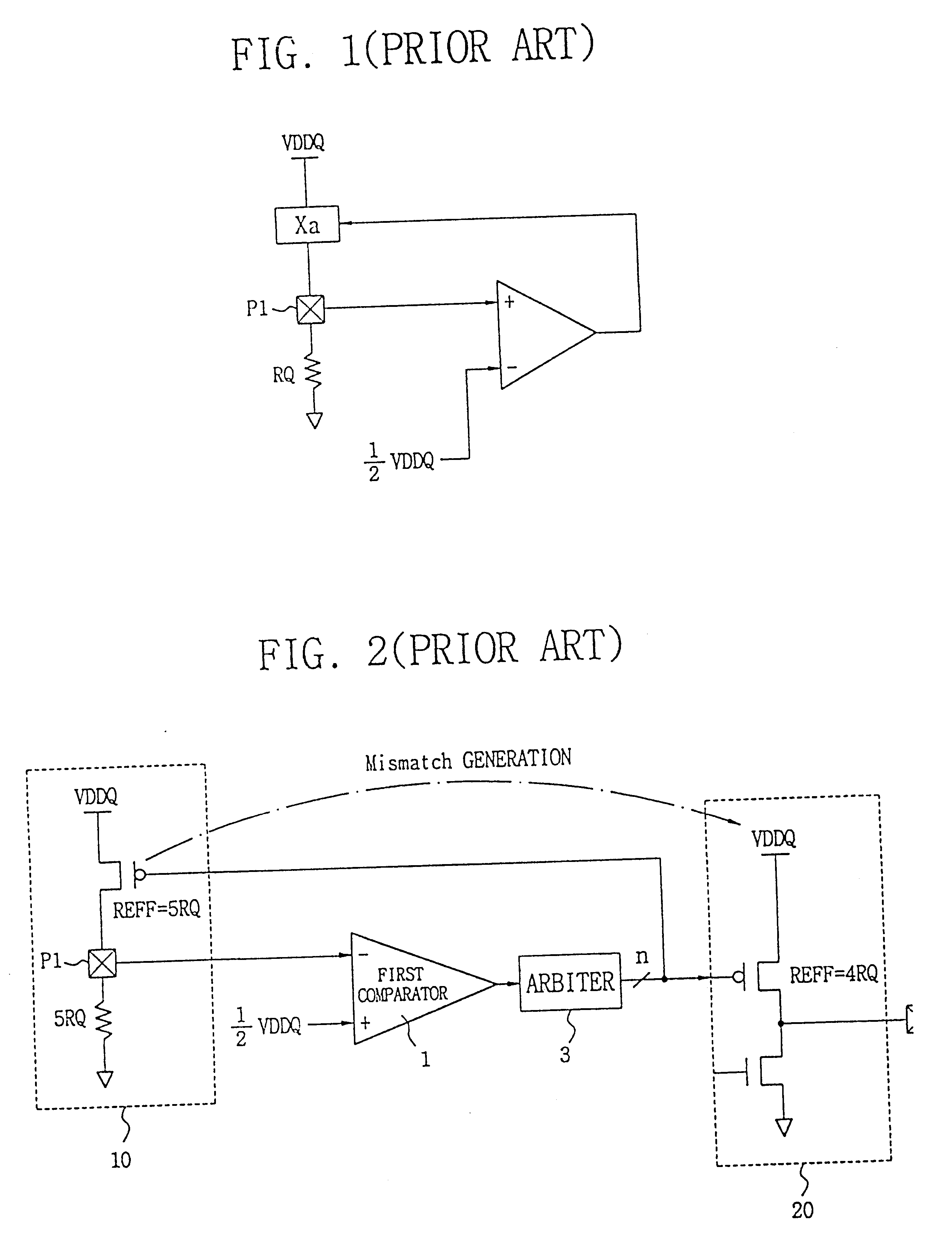

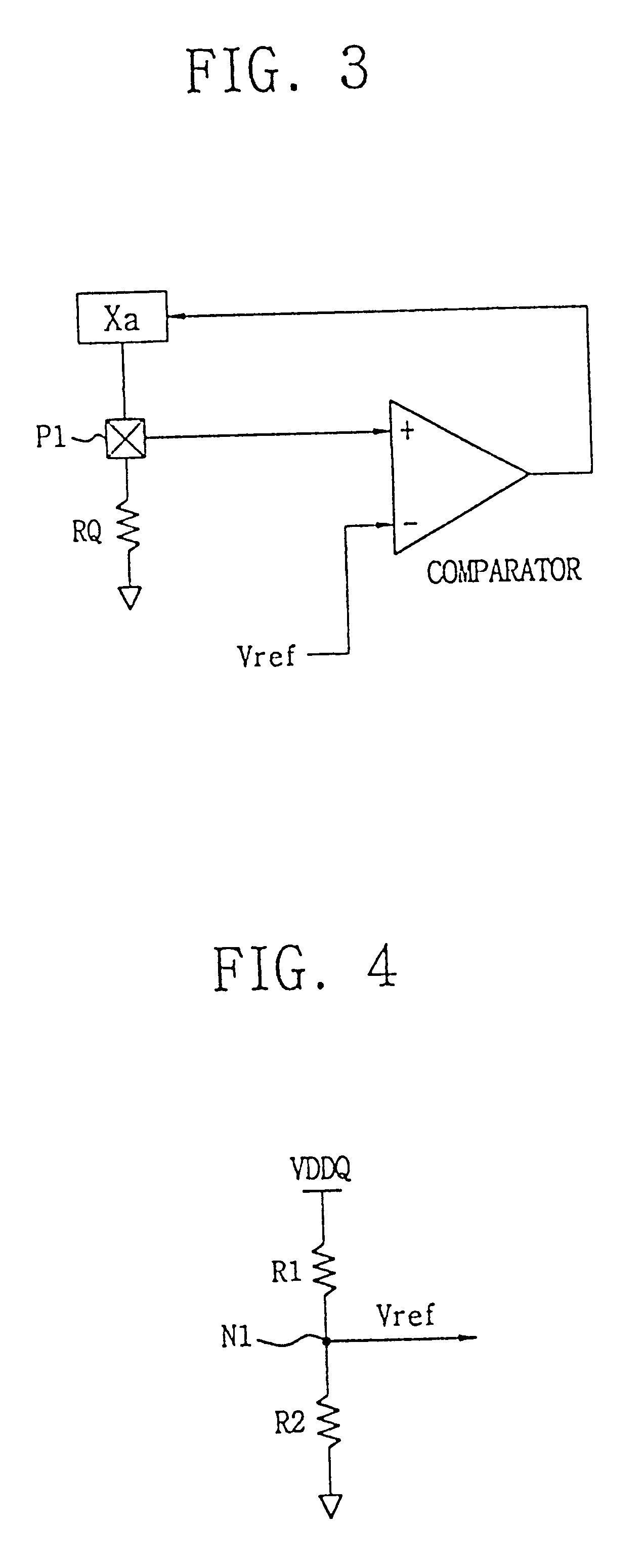

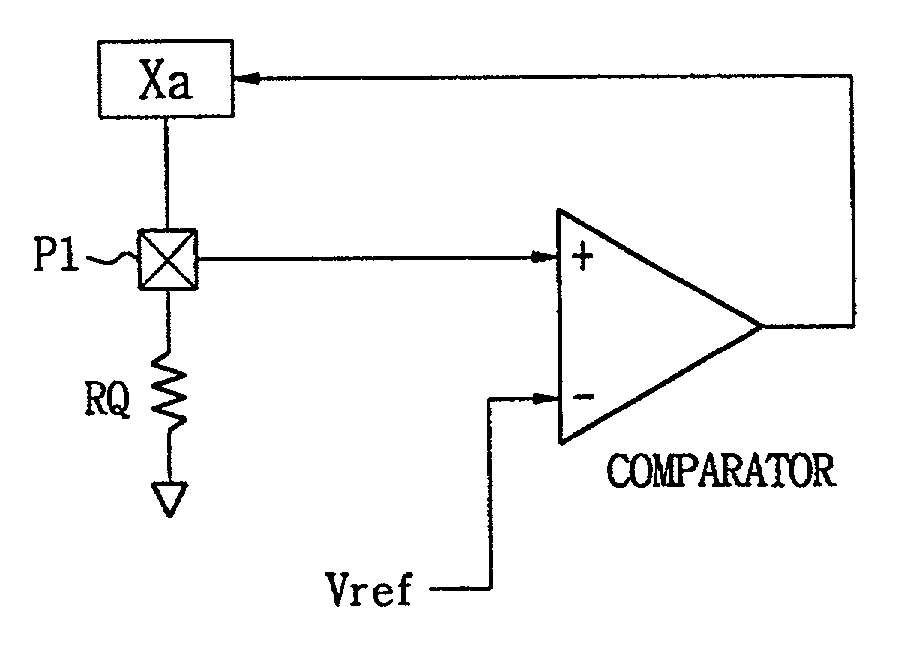

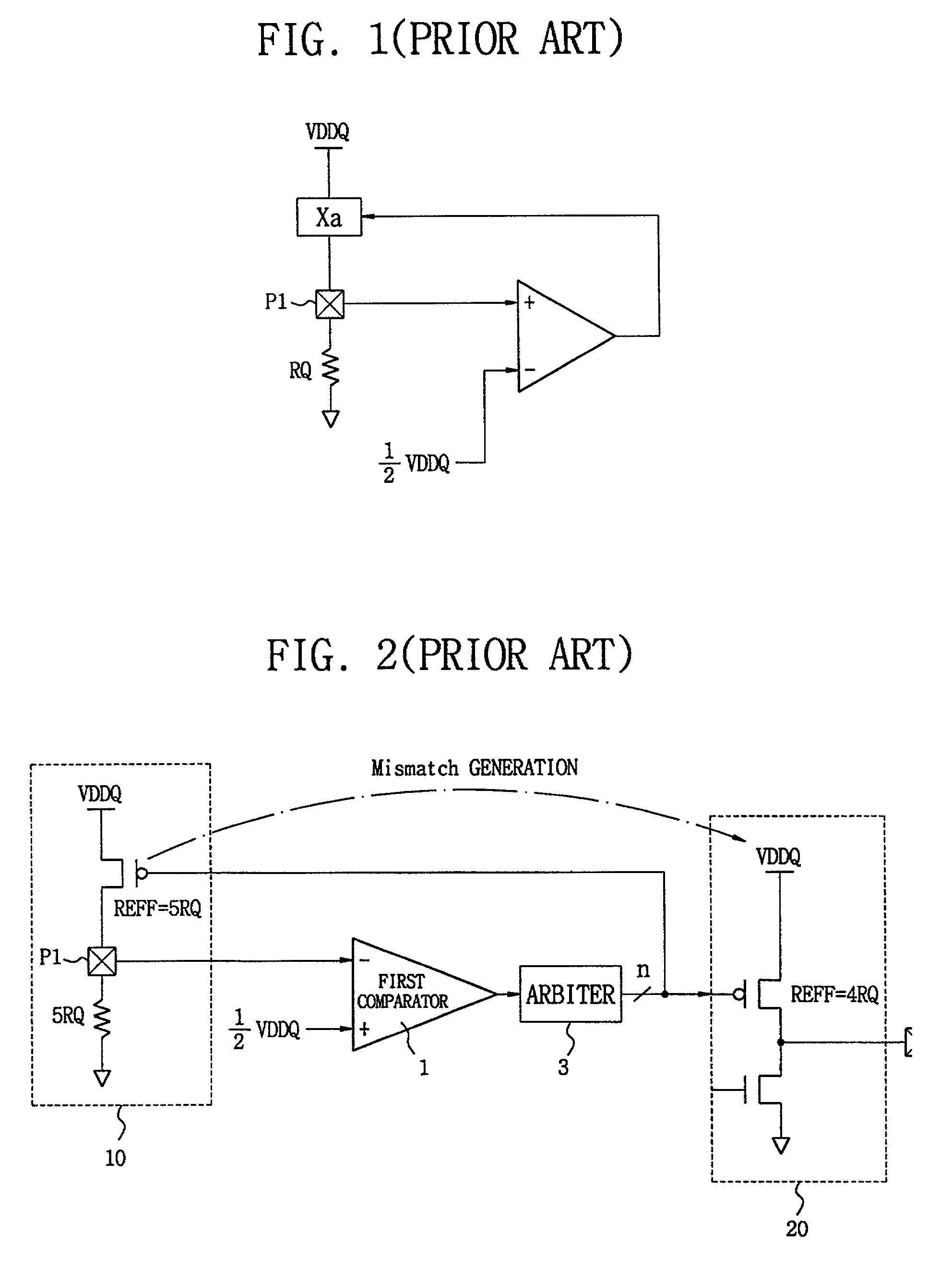

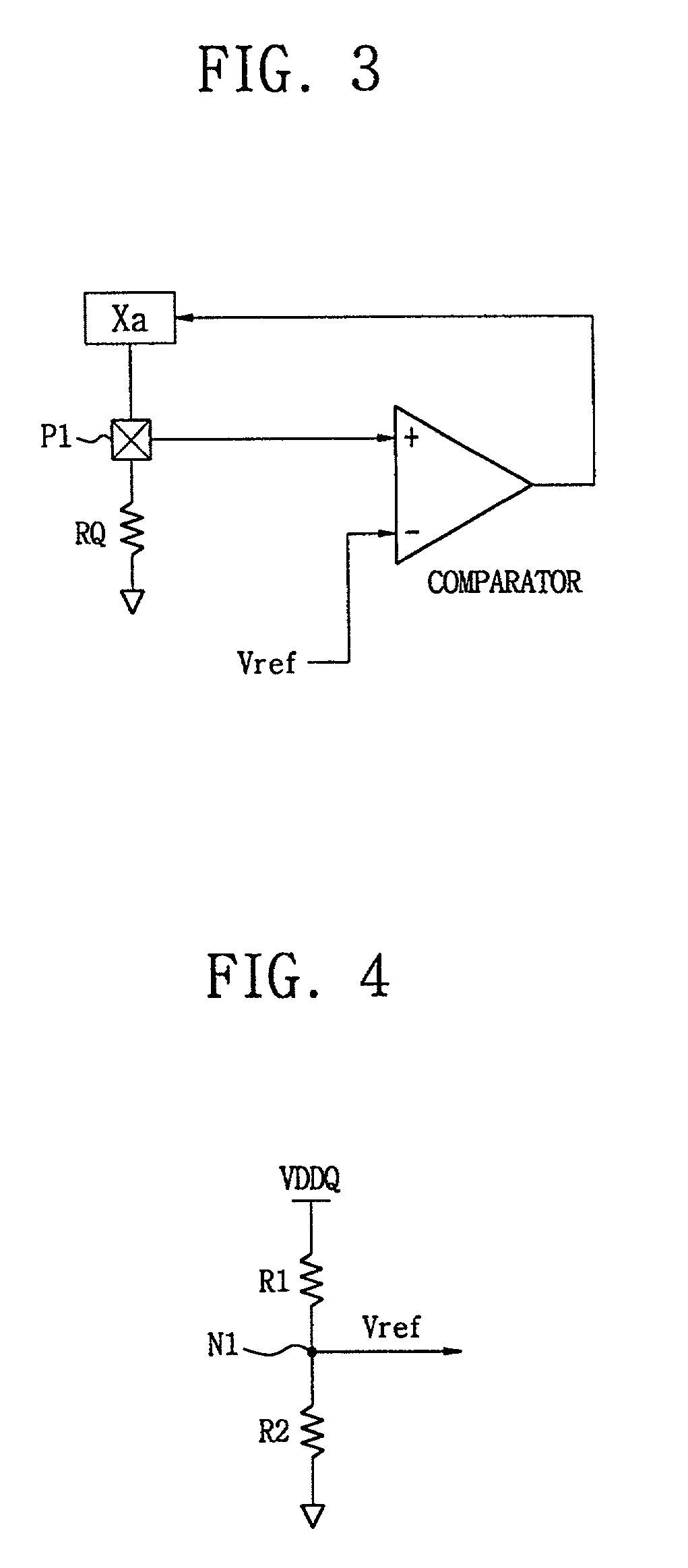

Programmable impedance control circuit

InactiveUS6525558B2Multiple-port networksImpedence matching networksElectrical resistance and conductanceVoltage generator

Disclosed is a programmable impedance control circuit, comprising a voltage divider, the voltage divider comprising an MOS array supplied with a first voltage and an external resistance having an external impedance equal to N times said external resistance. The voltage divider outputs a second voltage. A reference voltage generator is provided for generating a third voltage corresponding to N / (N+M) times said first voltage as a reference voltage for said second voltage, and wherein M times internal impedance is used for N times external impedance (N=M or N<> M).

Owner:SAMSUNG ELECTRONICS CO LTD

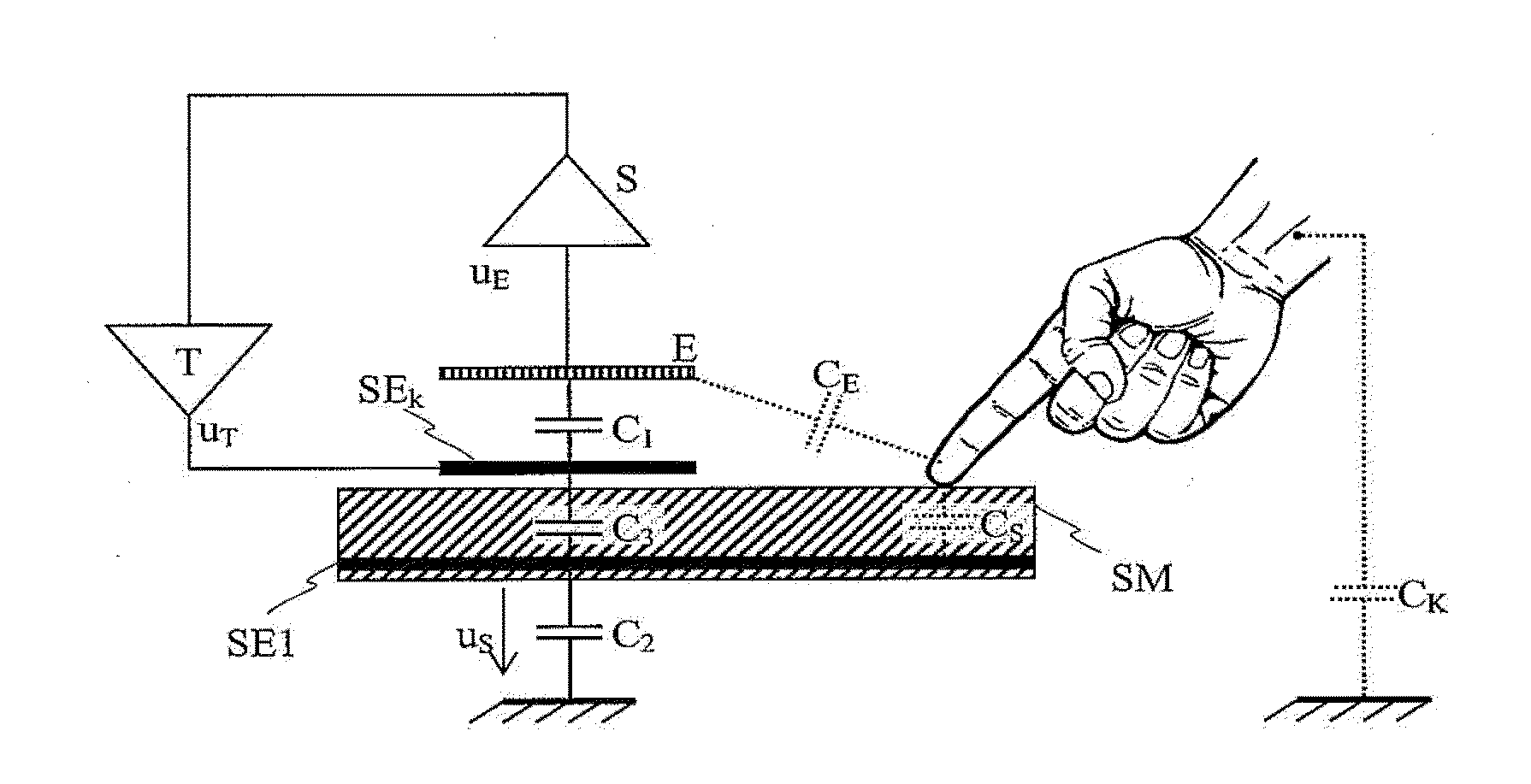

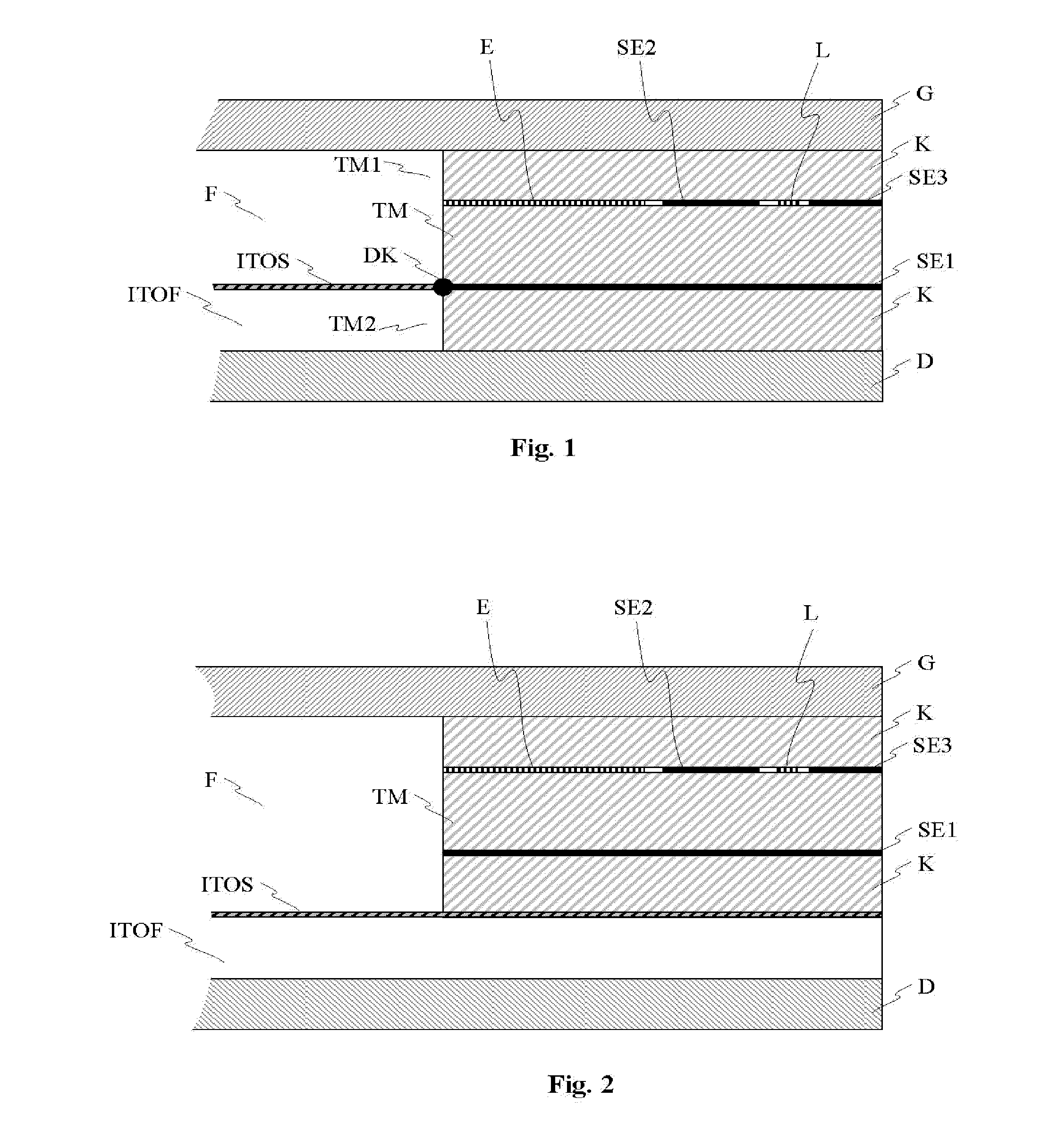

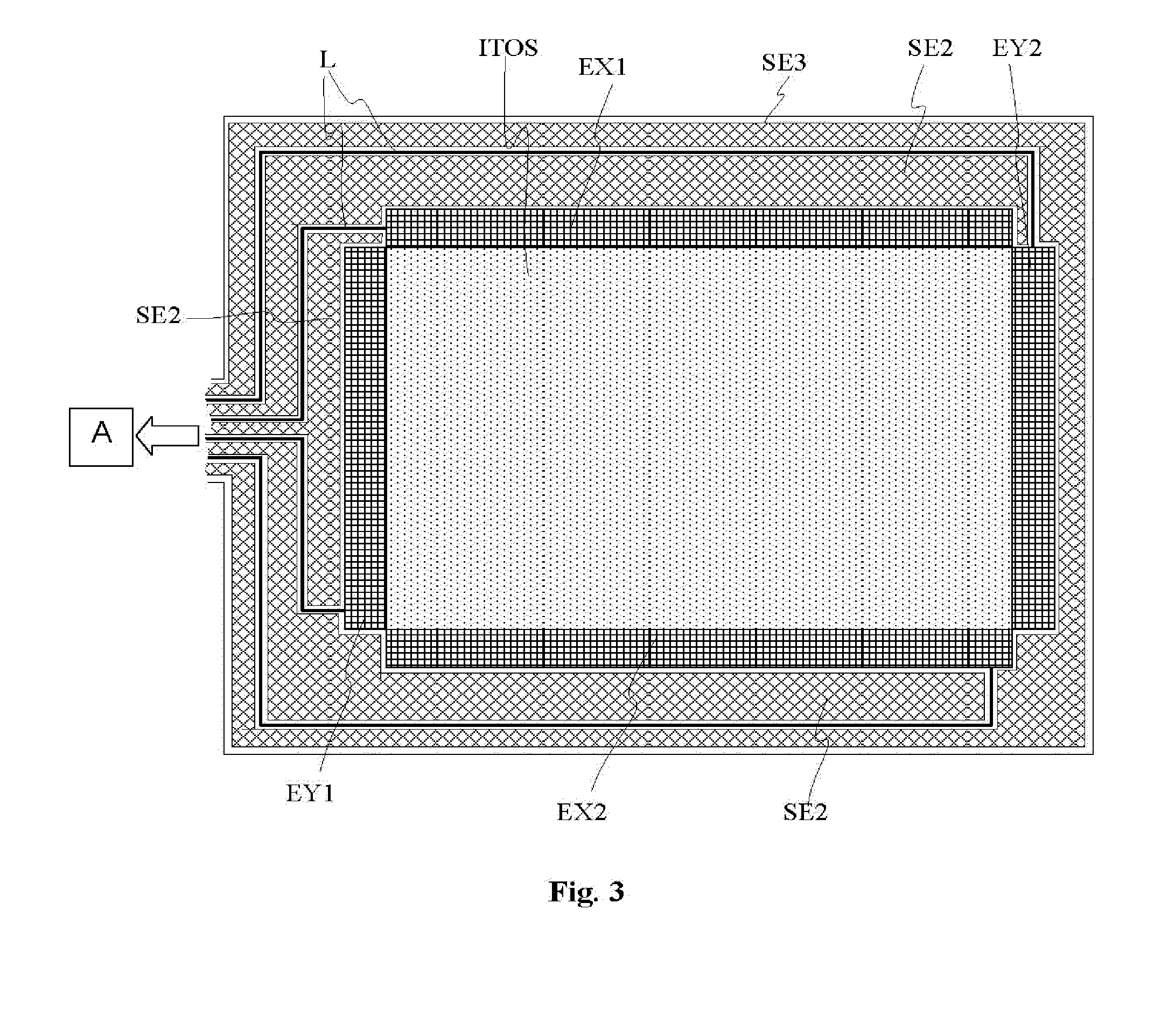

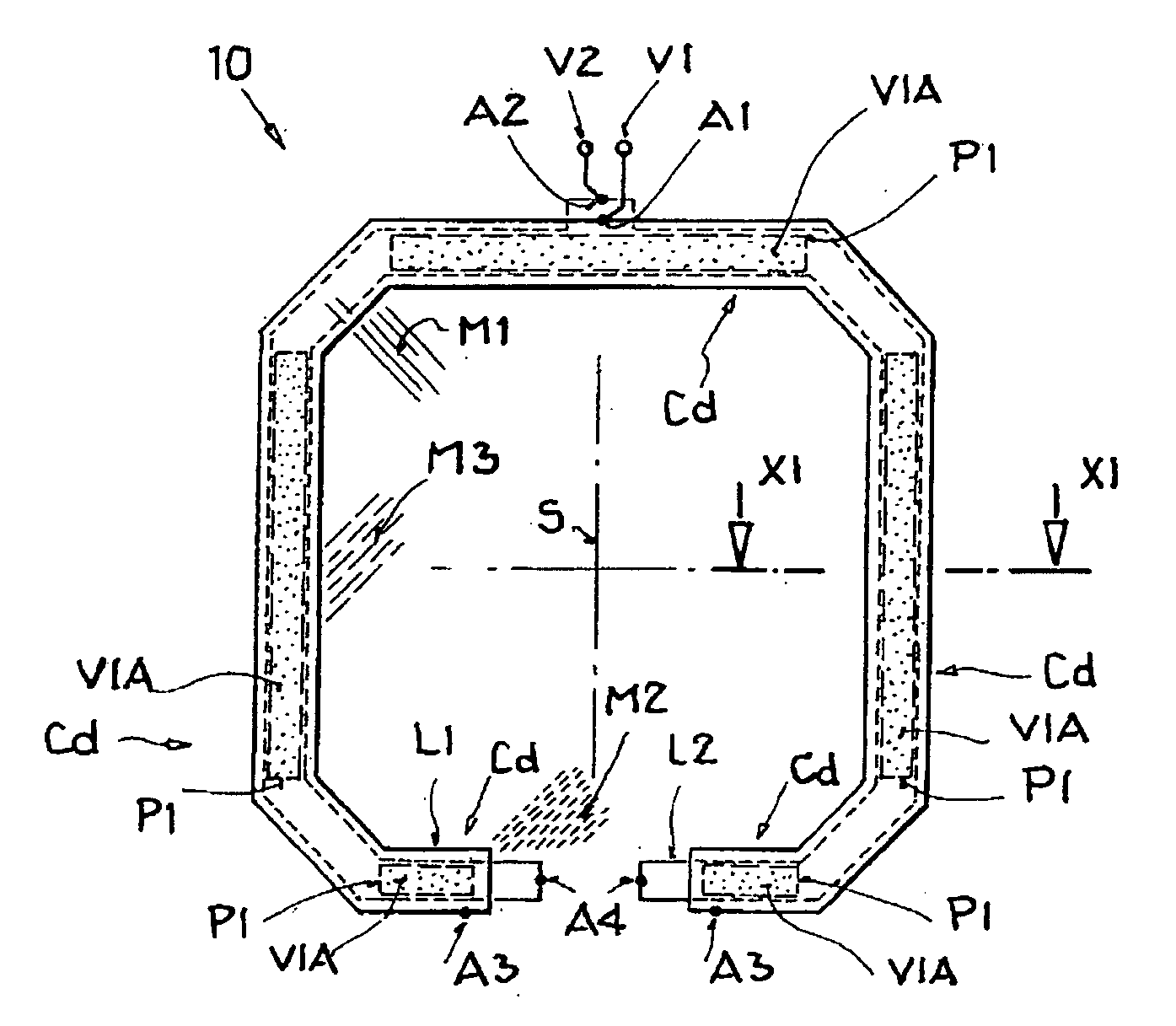

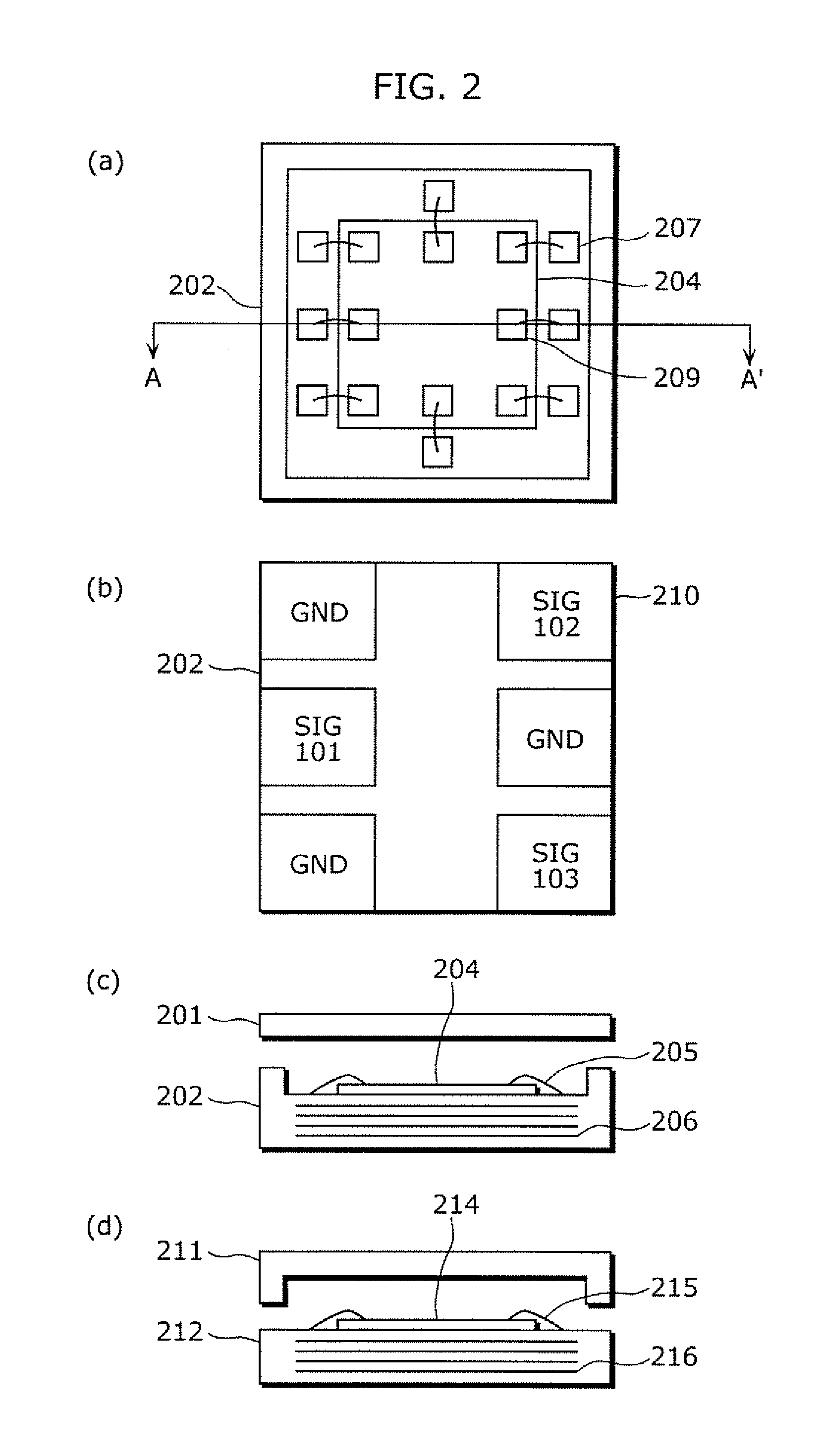

Electrode arrangement for display device

ActiveUS20120081328A1High sensitivityReduce impactMultiple-port networksPrinted circuit assemblingDisplay deviceEngineering

The invention provides an electrode arrangement for a capacitive sensor device and for a capacitive sensor, respectively, for detecting a position and / or an approach of an object, which comprises a sensor electrode and a first shield electrode, wherein the sensor electrode is arranged on a first side of a substantially flat substrate with a first side and a second side, and wherein the first shield electrode is arranged on the second side of the substrate and serves for shielding the alternating electric field emitted by the sensor electrode from ground. There is also provided a foil with an electrode arrangement according to the invention as well as a method for the production of a display arrangement with an electrode arrangement according to the invention.

Owner:MICROCHIP TECH GERMANY II

Semiconductor device and driving method thereof

InactiveUS7253665B2Addressing slow performanceResonant circuit tuningImpedence convertorsSemiconductorElectrical current

Owner:SEMICON ENERGY LAB CO LTD

Programmable impedance control circuit

InactiveUS20020063576A1Multiple-port networksReliability increasing modificationsVoltage generatorElectrical resistance and conductance

Disclosed is a programmable impedance control circuit, comprising a voltage divider, the voltage divider comprising an MOS array supplied with a first voltage and an external resistance having an external impedance equal to N times said external resistance. The voltage divider outputs a second voltage. A reference voltage generator is provided for generating a third voltage corresponding to N / (N+M) times said first voltage as a reference voltage for said second voltage, and wherein M times internal impedance is used for N times external impedance (N=M or N<> M).

Owner:SAMSUNG ELECTRONICS CO LTD

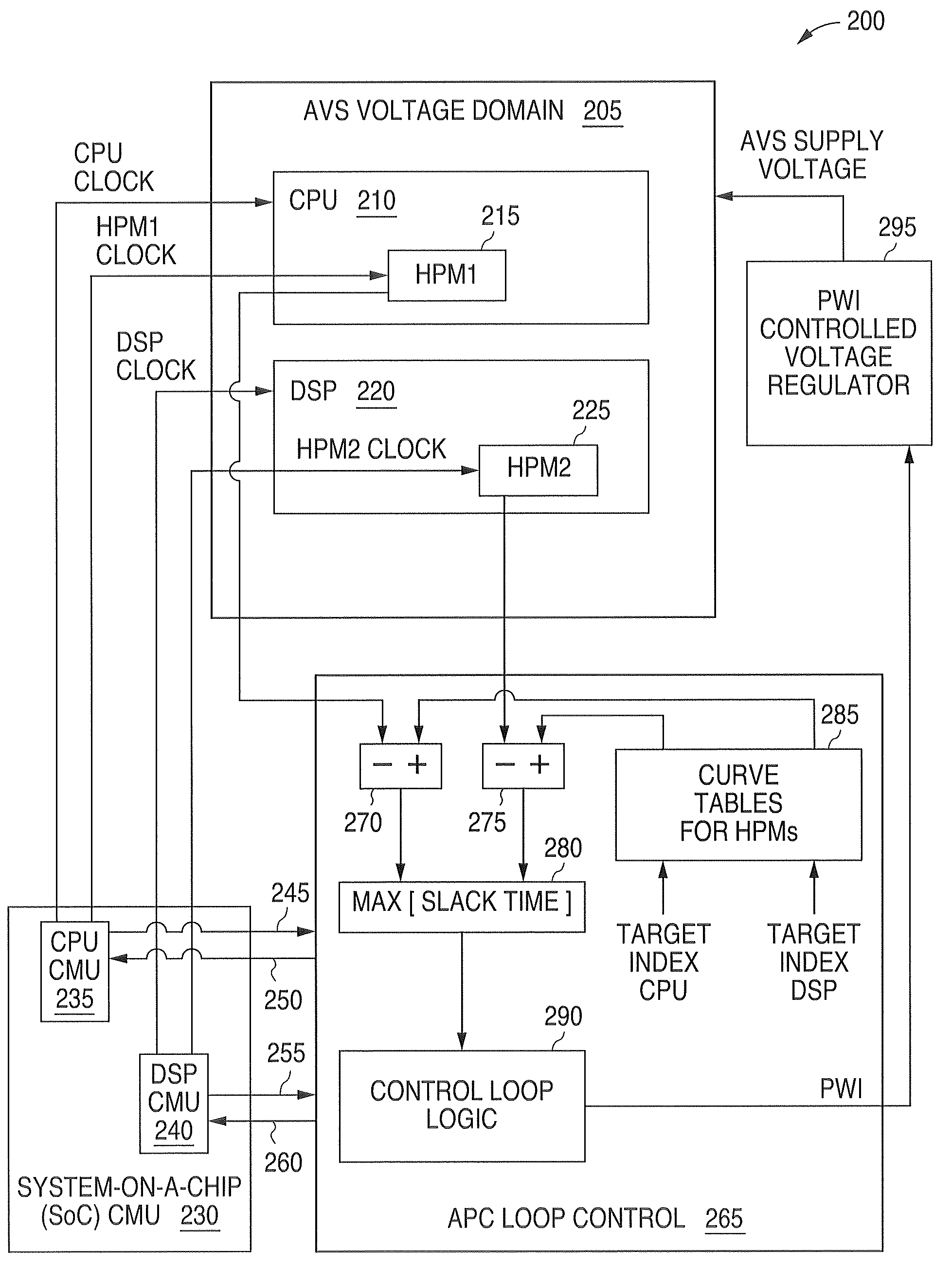

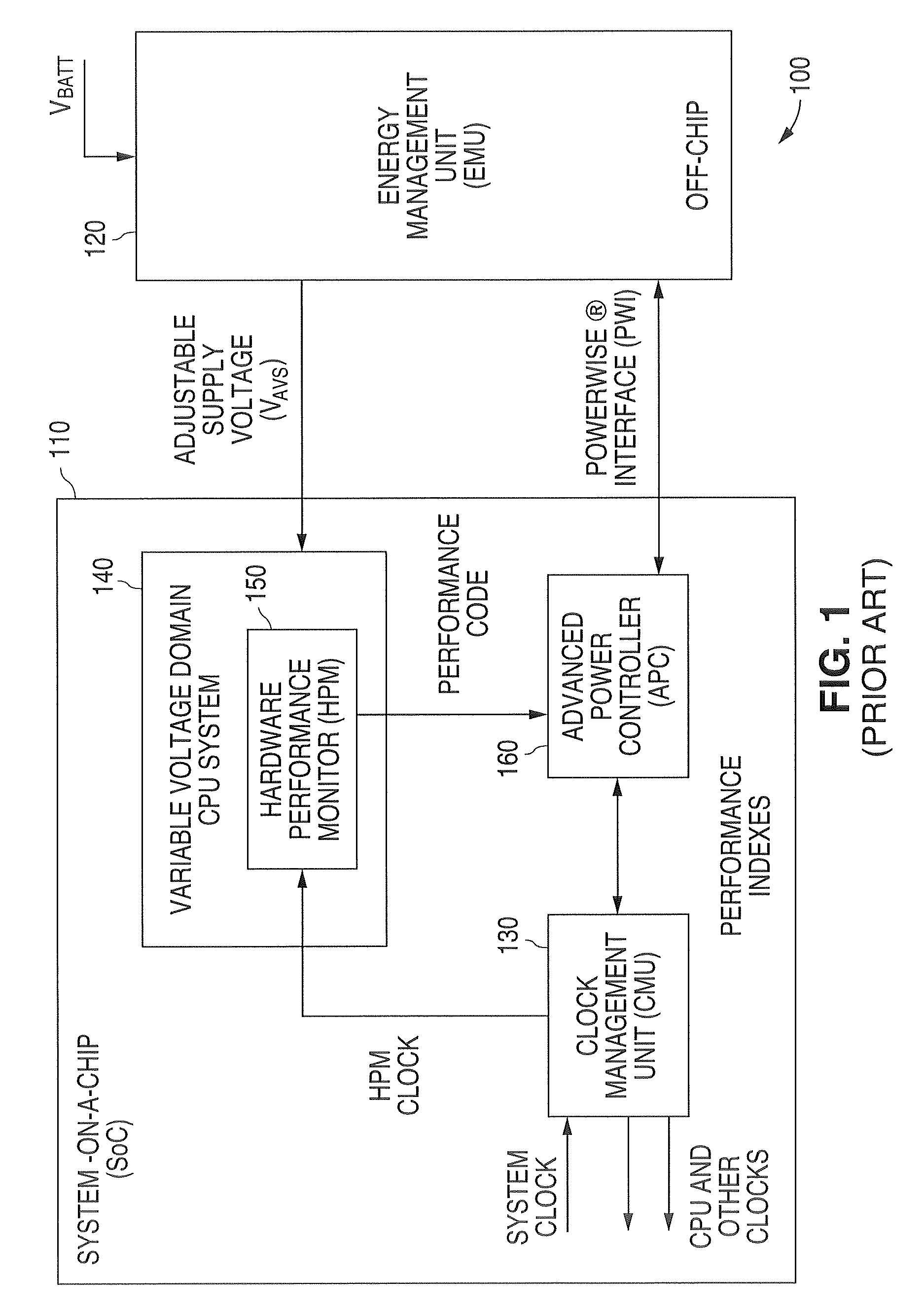

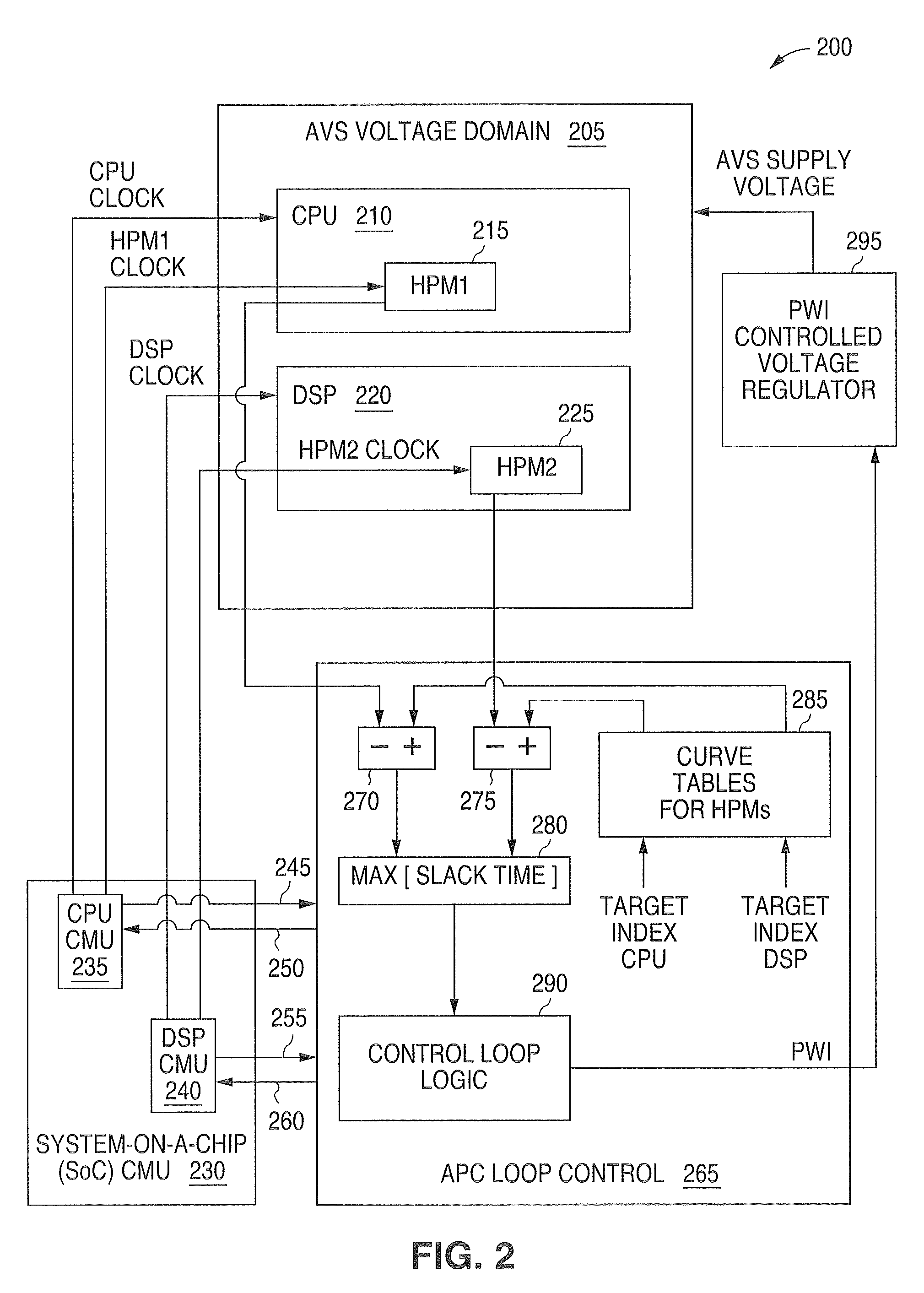

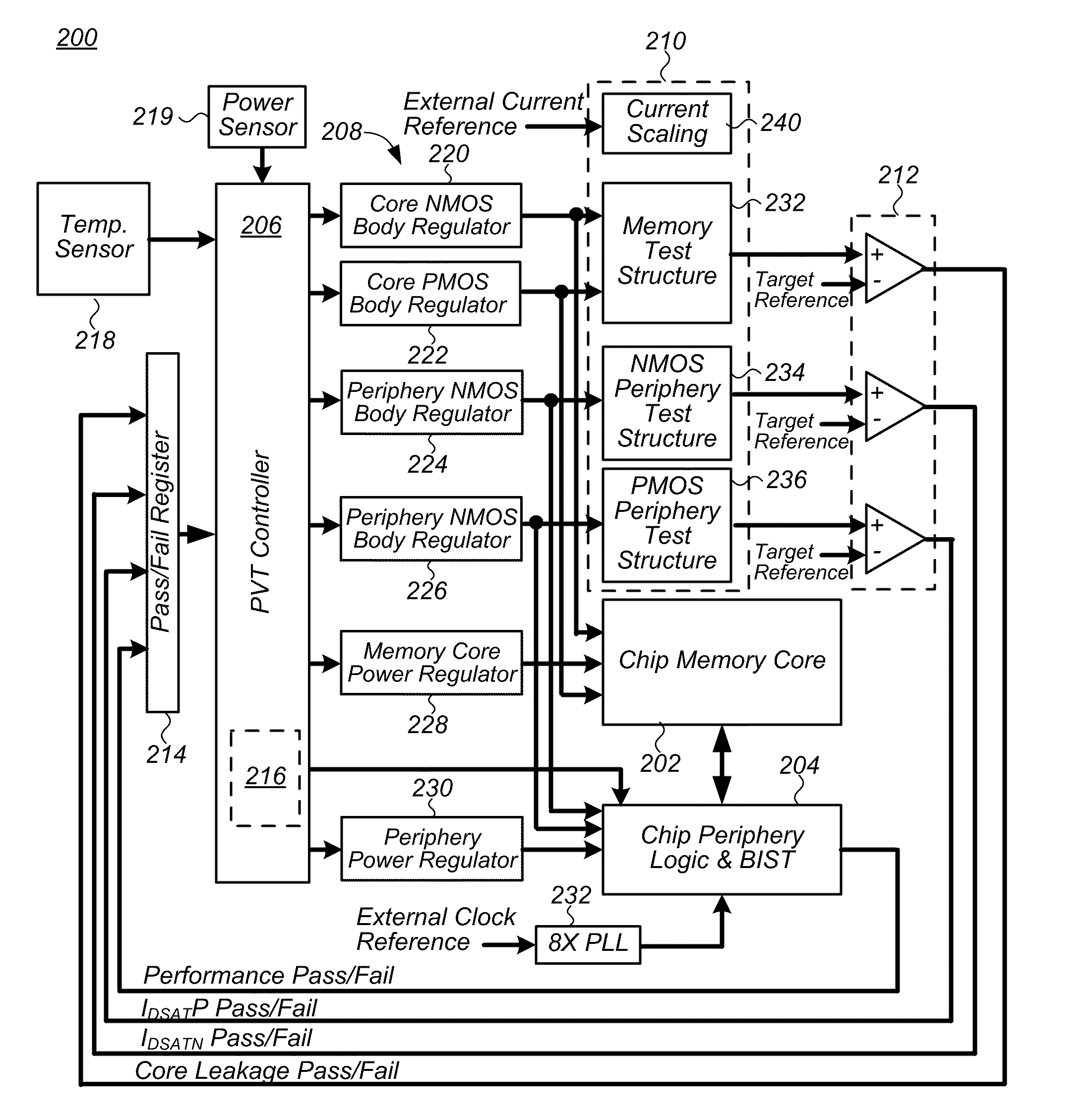

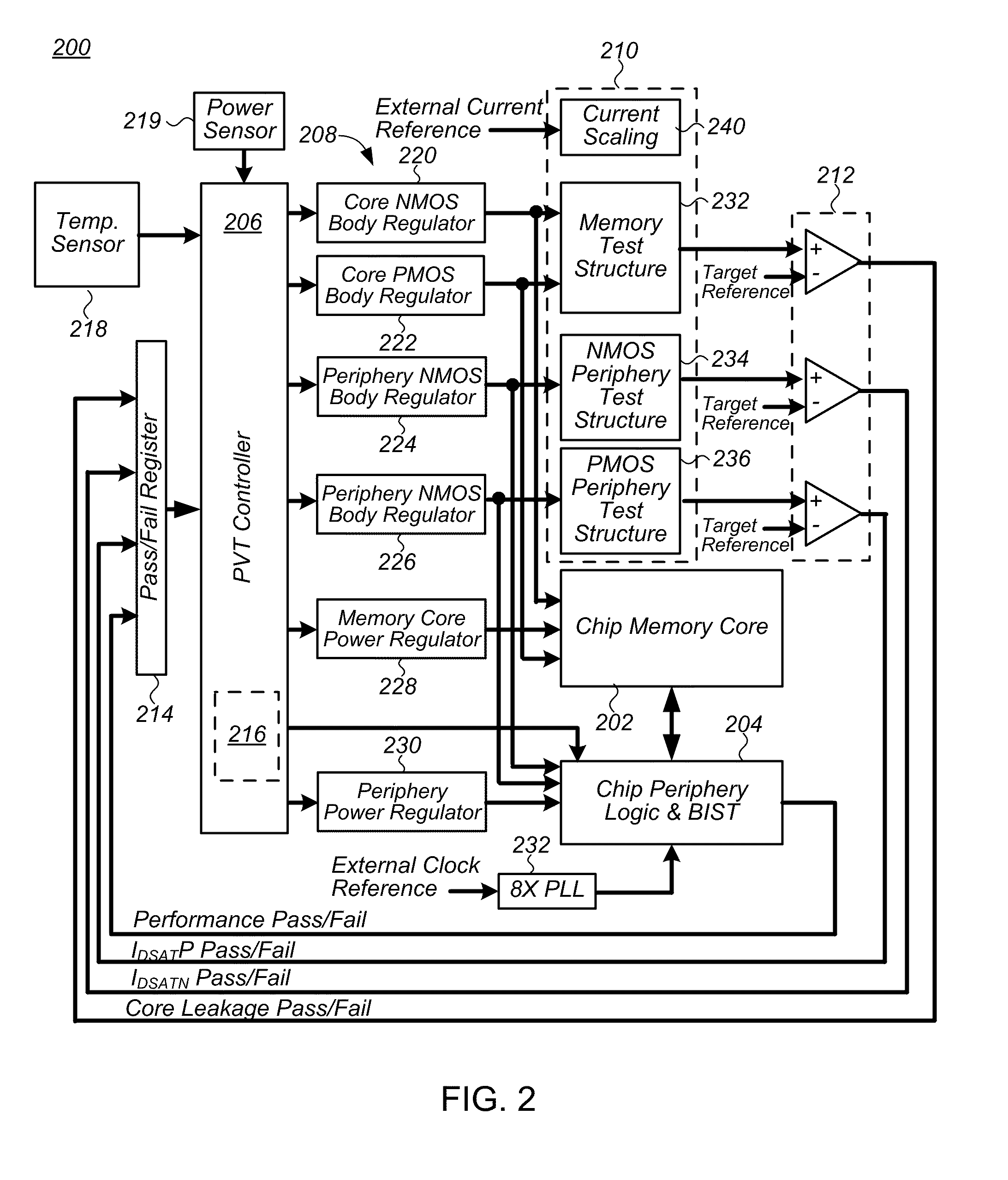

System and method for providing adaptive voltage scaling with multiple clock domains inside a single voltage domain

ActiveUS7921312B1Accurate scaleEnergy efficient ICTImpedence convertorsPower controllerSoftware engineering

A system and method is disclosed for providing a plurality of hardware performance monitors for adaptive voltage scaling in an integrated circuit system that comprises a plurality of clock domains. Each hardware performance monitor is associated with one of the plurality of clock domains and provides a signal that measures a performance of its respective clock domain temperature, process corner and supply voltage. The difference between the measured performance and a nominal expected performance for each hardware performance monitor is determined. The largest of the plurality of difference signals is selected and used in an advanced power controller to provide adaptive voltage scaling for the integrated circuit system.

Owner:NAT SEMICON CORP

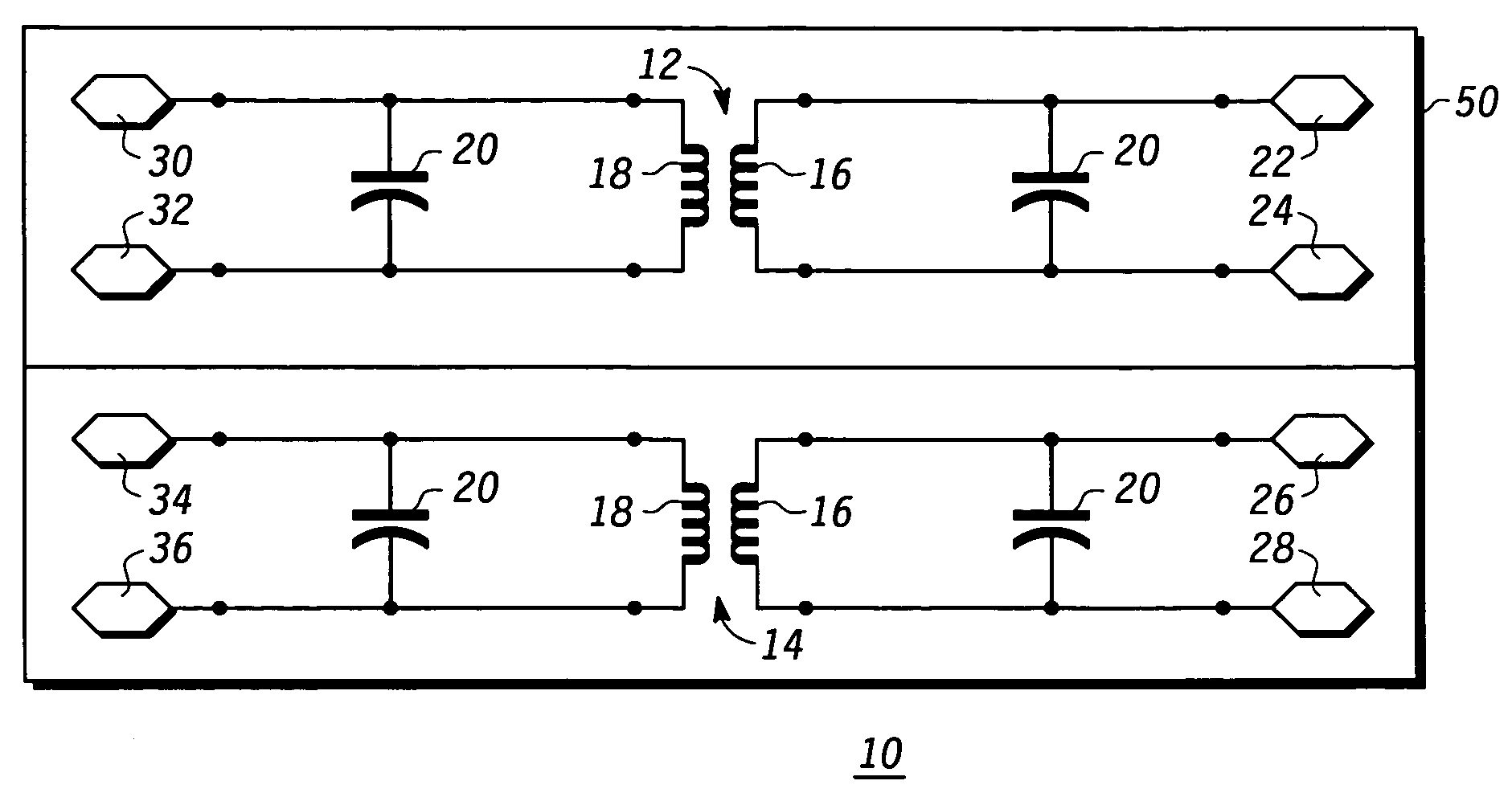

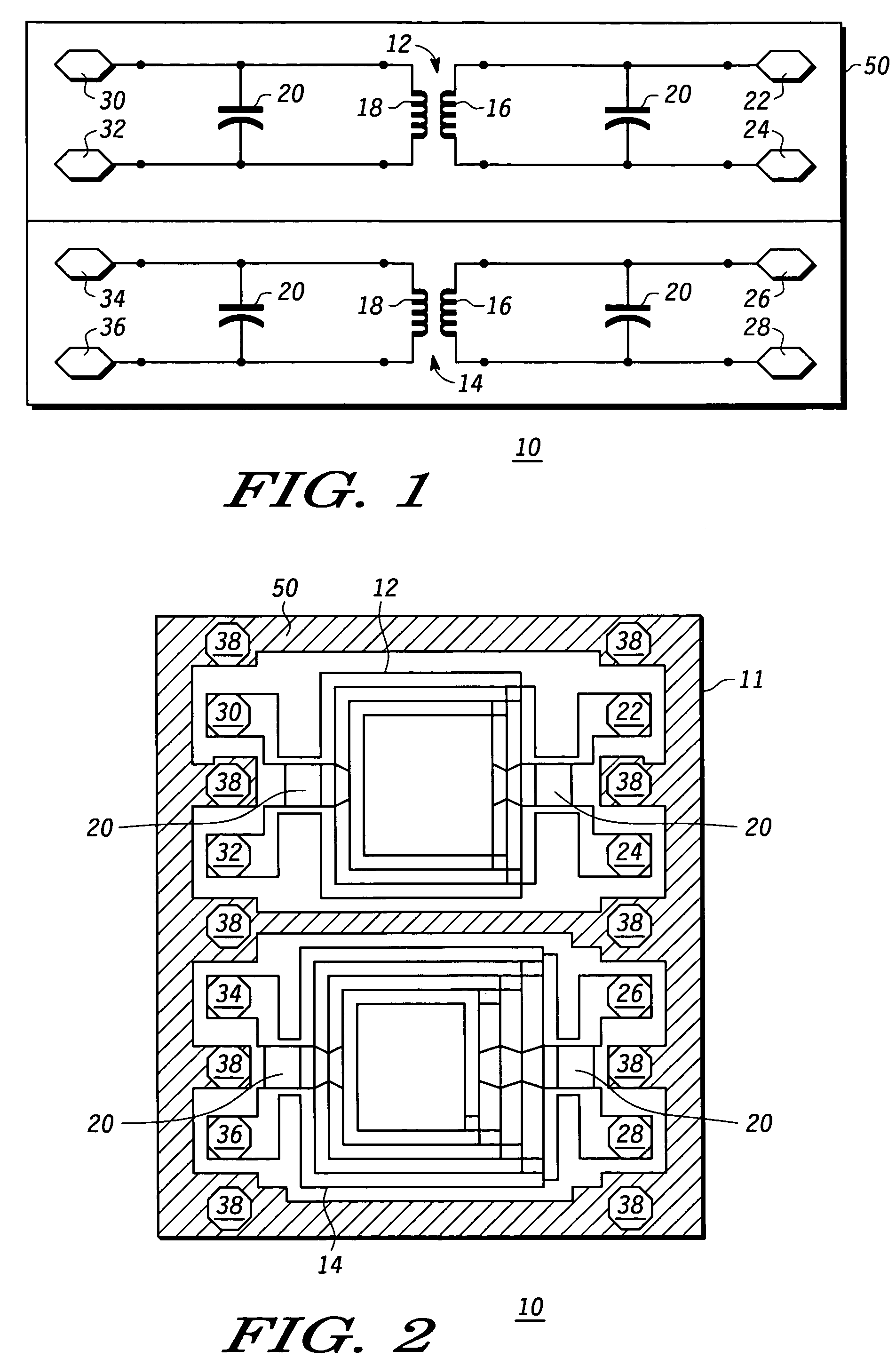

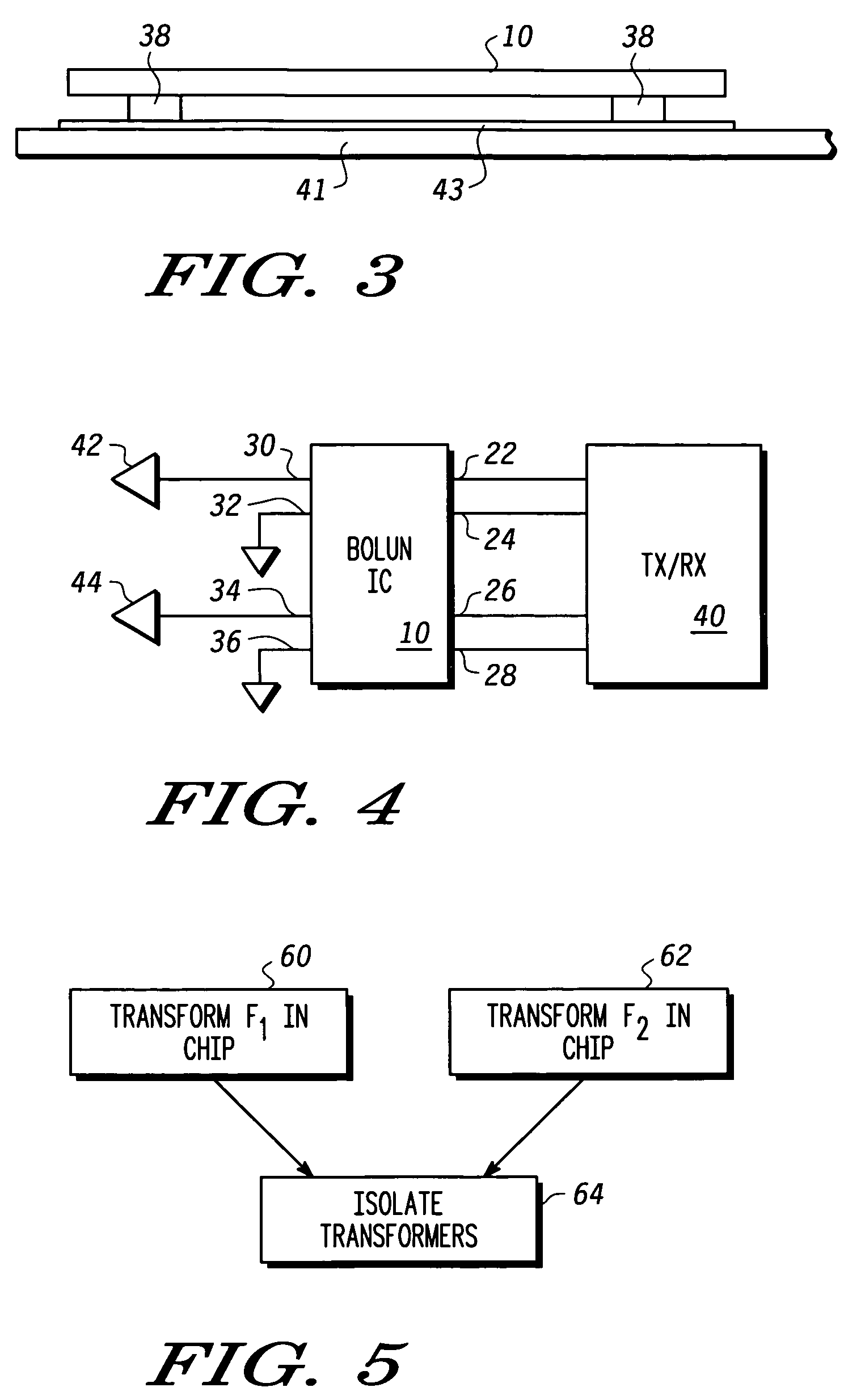

Baluns for multiple band operation

Owner:HUAWEI TECH CO LTD

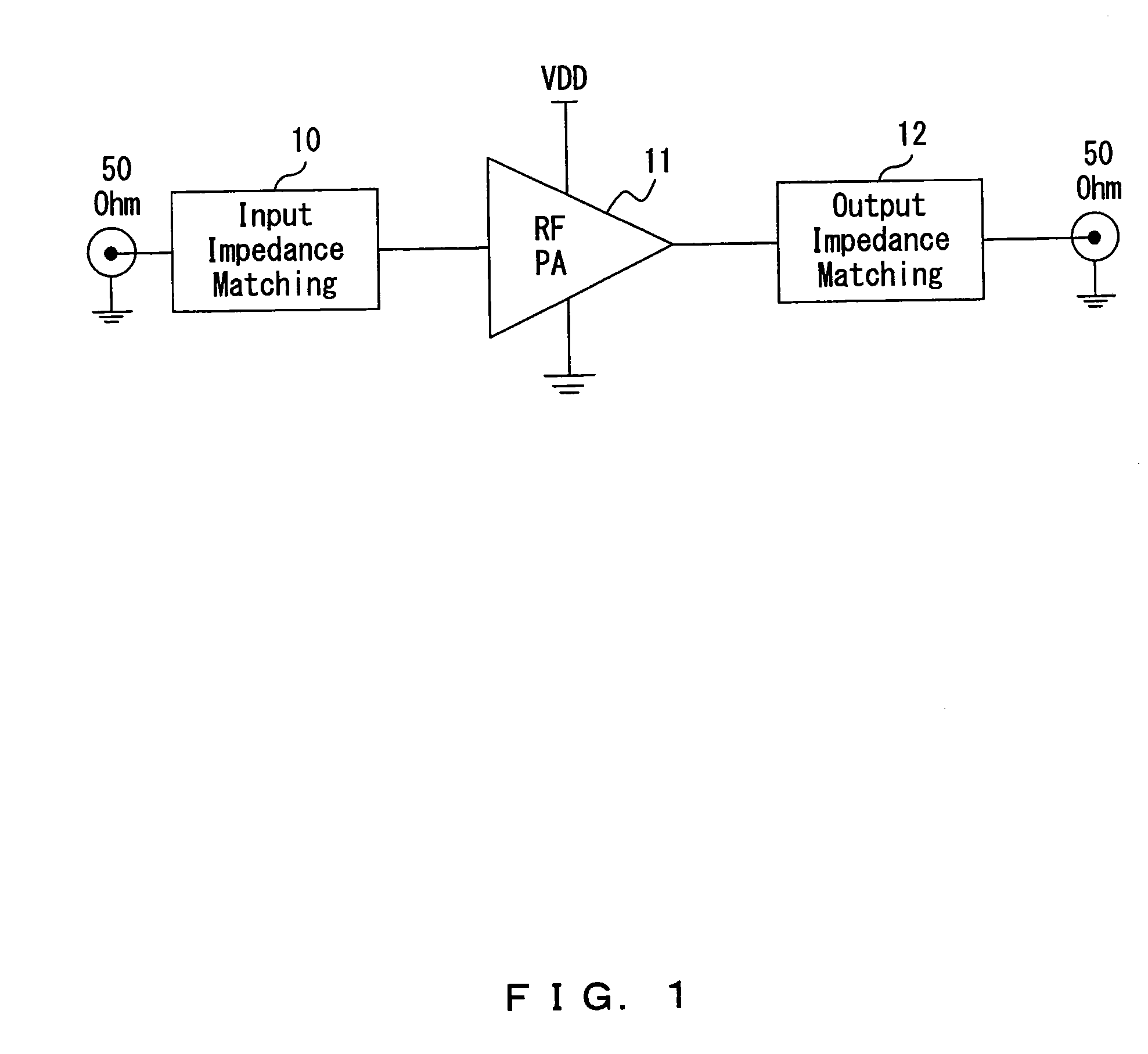

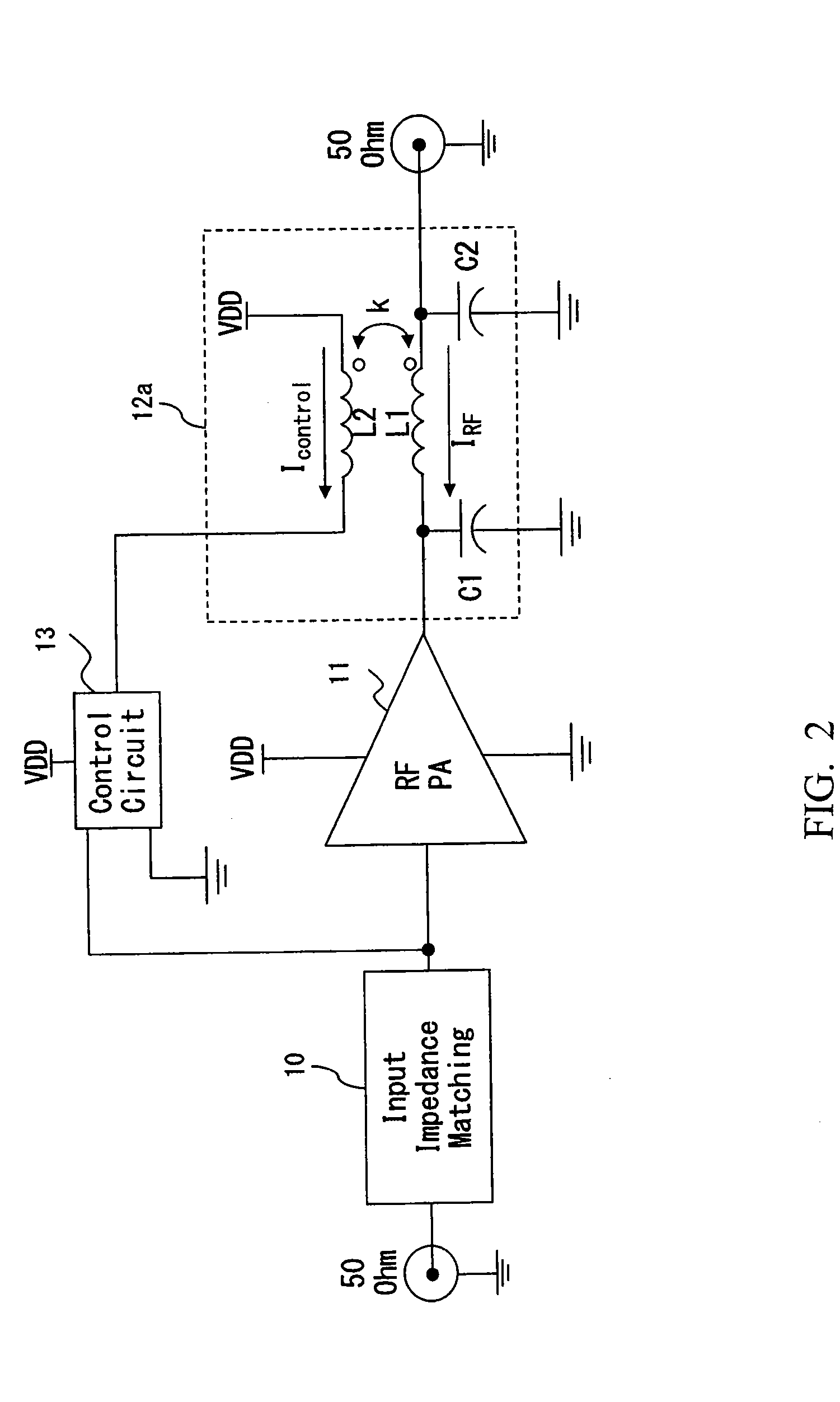

Tunable Impedance Matching Circuit

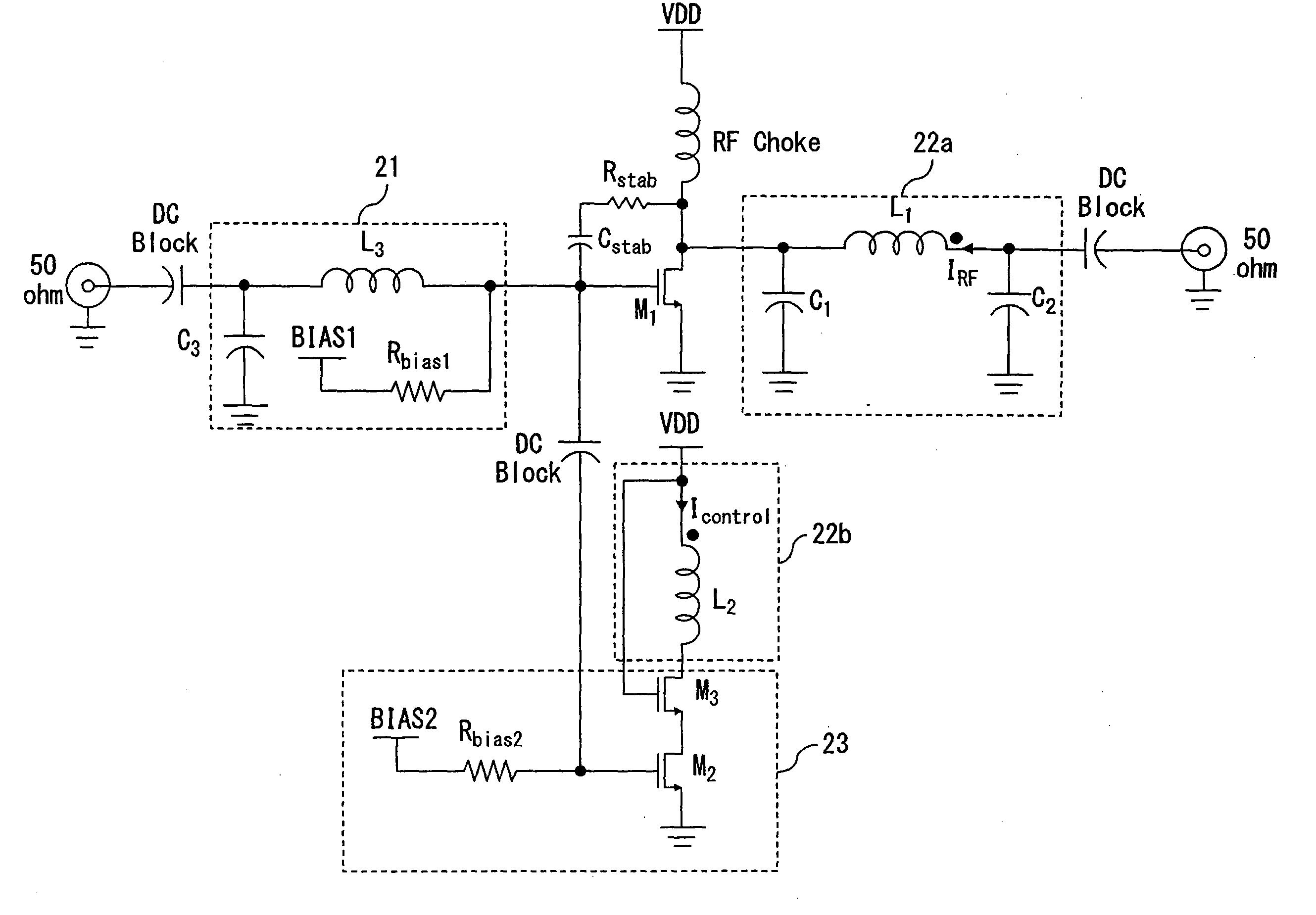

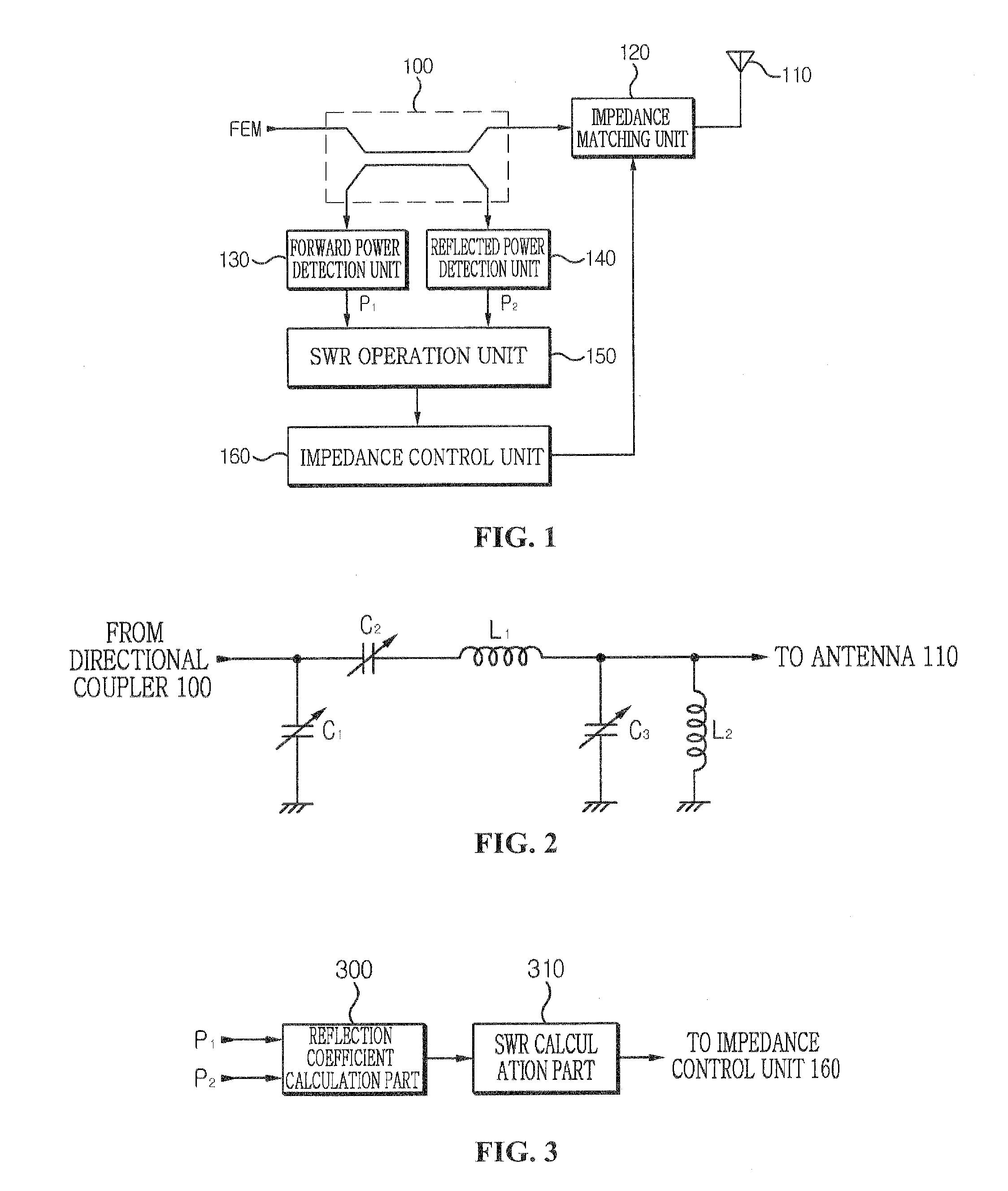

InactiveUS20100164645A1Easy to integrateSimple and easy configurationMultiple-port networksImpedence convertorsImpedance matchingInductor

The tunable impedance circuit comprises capacitors C1 and C2, an inductor L1, and an inductor L2 magnetically coupled with the inductor L1. The control current Icontrol with variable phase and amplitude from the control circuit 13 flows in the inductor L2. The impedance of the inductor L1 is changed by changing the phase and amplitude of the control current Icontrol. The output impedance is set to an optimum level by setting an effective inductance and an effective quality factor of the tunable impedance circuit 12a to be optimum by means of the phase and amplitude of the control current Icontrol relative to output current IRF of RF PA 11.

Owner:FUJITSU LTD

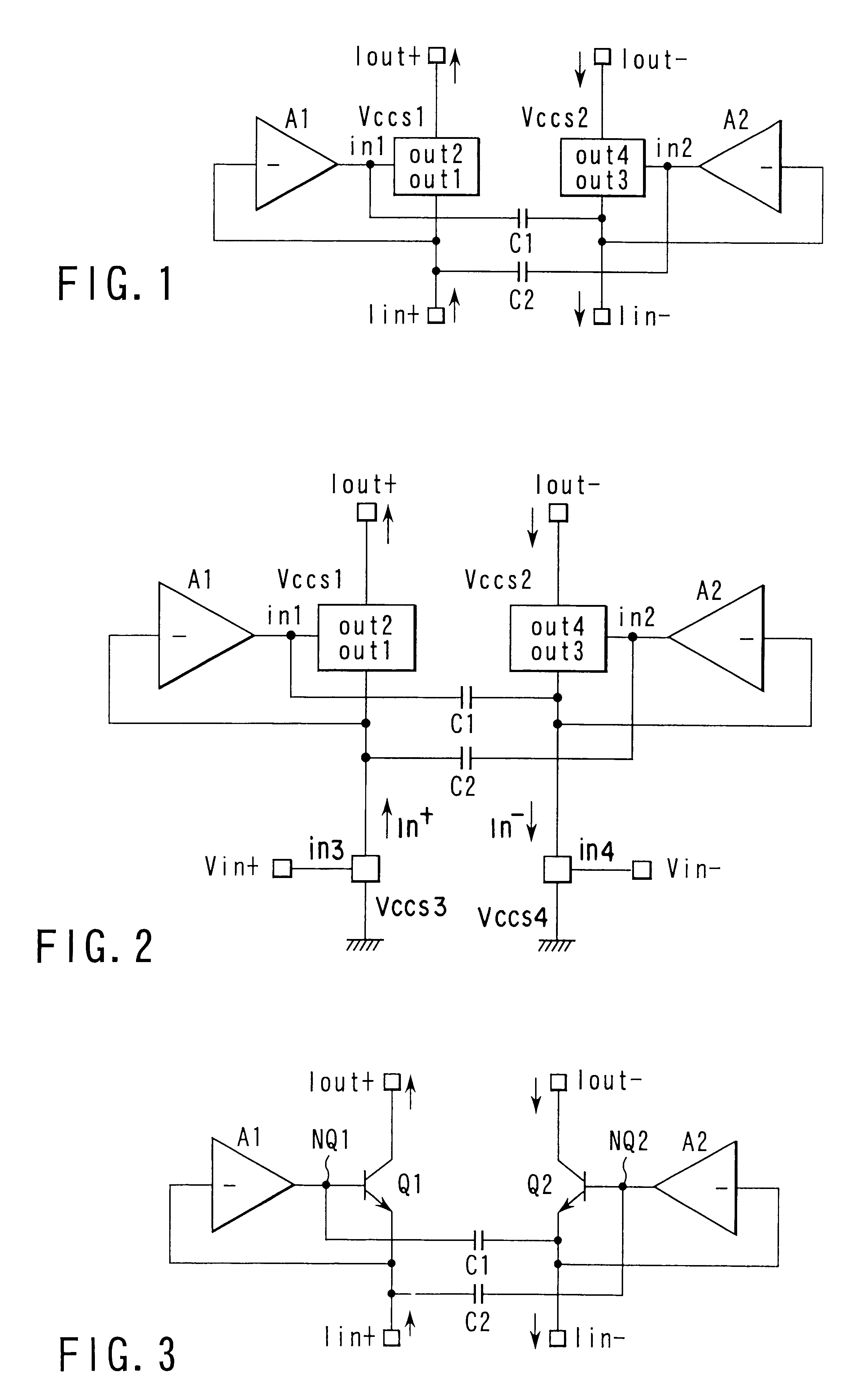

Semiconductor device and driving method thereof

InactiveUS20050007181A1Addressing slow performanceAccurate currentResonant circuit tuningImpedence convertorsDevice materialEngineering

The invention provides a semiconductor device which performs a write operation of a signal current rapidly to a current input type pixel. Before inputting a signal current, a precharge operation is performed by flowing a large current. After that, a signal current is inputted to perform the set operation. A predetermined potential can be obtained rapidly as the precharge operation is performed before the set operation. The predetermined potential is approximately equal to a potential after completing the set operation. Therefore, the set operation can be rapidly performed and a write operation of a signal current can be rapidly performed. By using two transistors, a gate width W can be long or a gate length L can be short in the precharge operation or the gate width W can be short and the gate length L can be long in the set operation.

Owner:SEMICON ENERGY LAB CO LTD

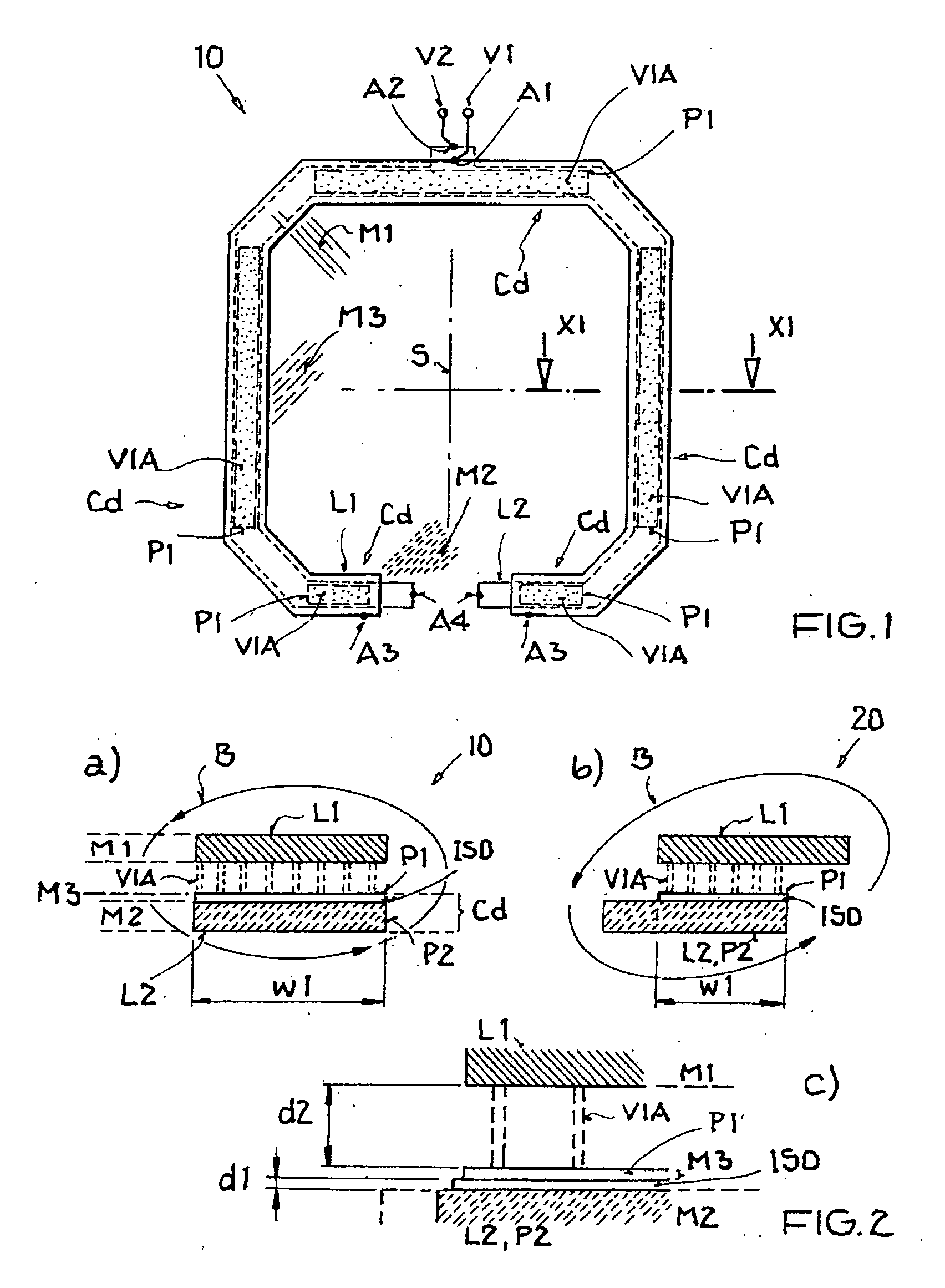

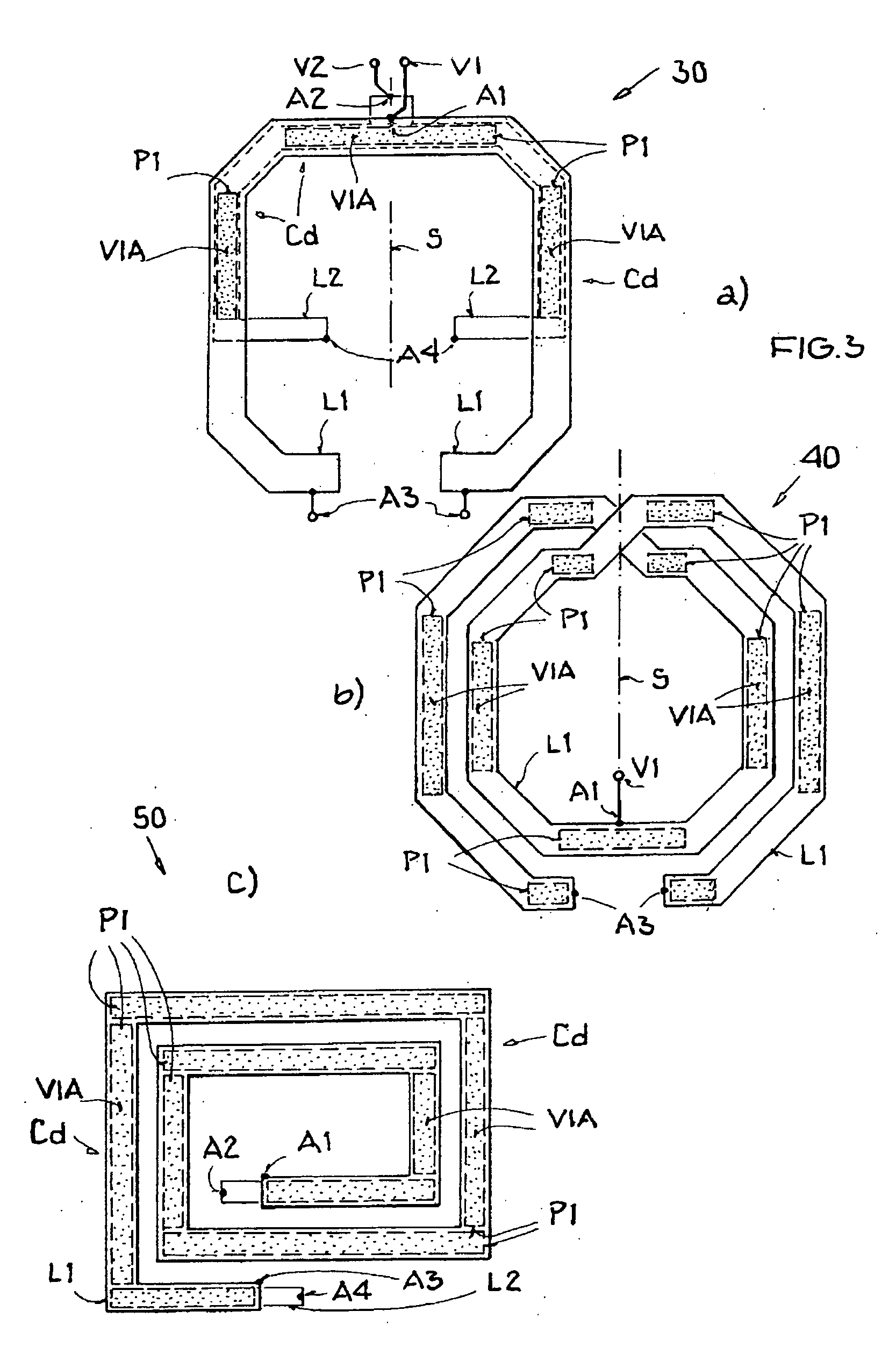

Monolithically integratable circuit arrangement

InactiveUS20080048760A1Simple and cost-effective to implementReduced space requirementsMultiple-port networksImpedence convertorsElectrical conductorInductor

A monolithically integratable circuit arrangement is provided, which has at least one inductor, formed as a conductor loop, and at least one capacitor, connected to the conductor loop. According to the invention, the circuit arrangement comprises (a) at least one first conductor loop placed in at least one first metallization level and having a first DC terminal for applying a first DC potential, (b) at least one second conductor loop placed in at least one second metallization level and having a second DC terminal for applying a second DC potential, (c) at least one metal-isolator-metal capacitor with a capacitor plate, which is placed in a third metallization level between the first and second metallization level, and (d) at least one metallic connecting means placed between the capacitor plate and the first conductor loop, said means which connects the capacitor plate in an electrically conducting manner to the first conductor loop. The invention relates furthermore to an integrated circuit having a circuit arrangement of this type.

Owner:ATMEL CORP

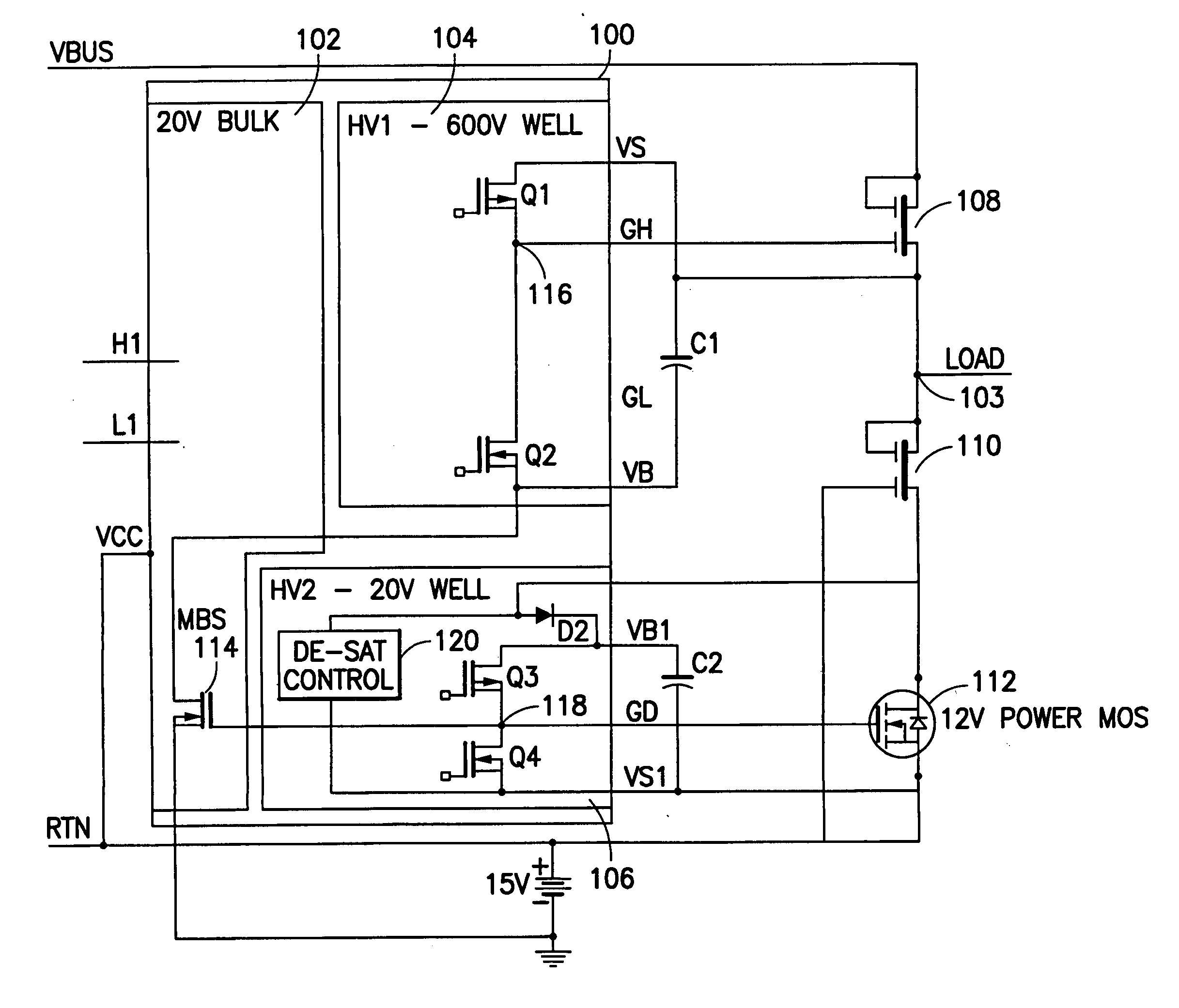

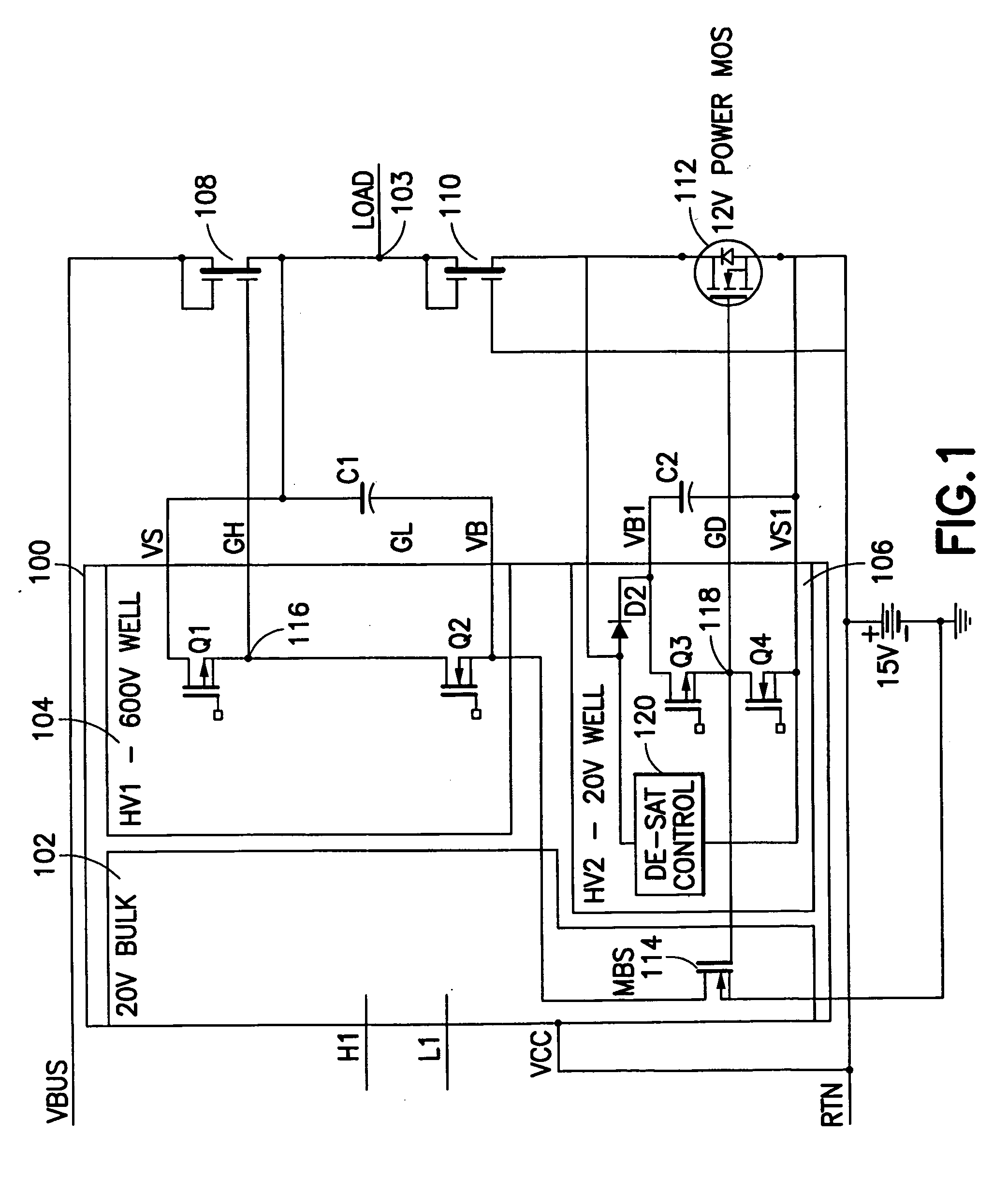

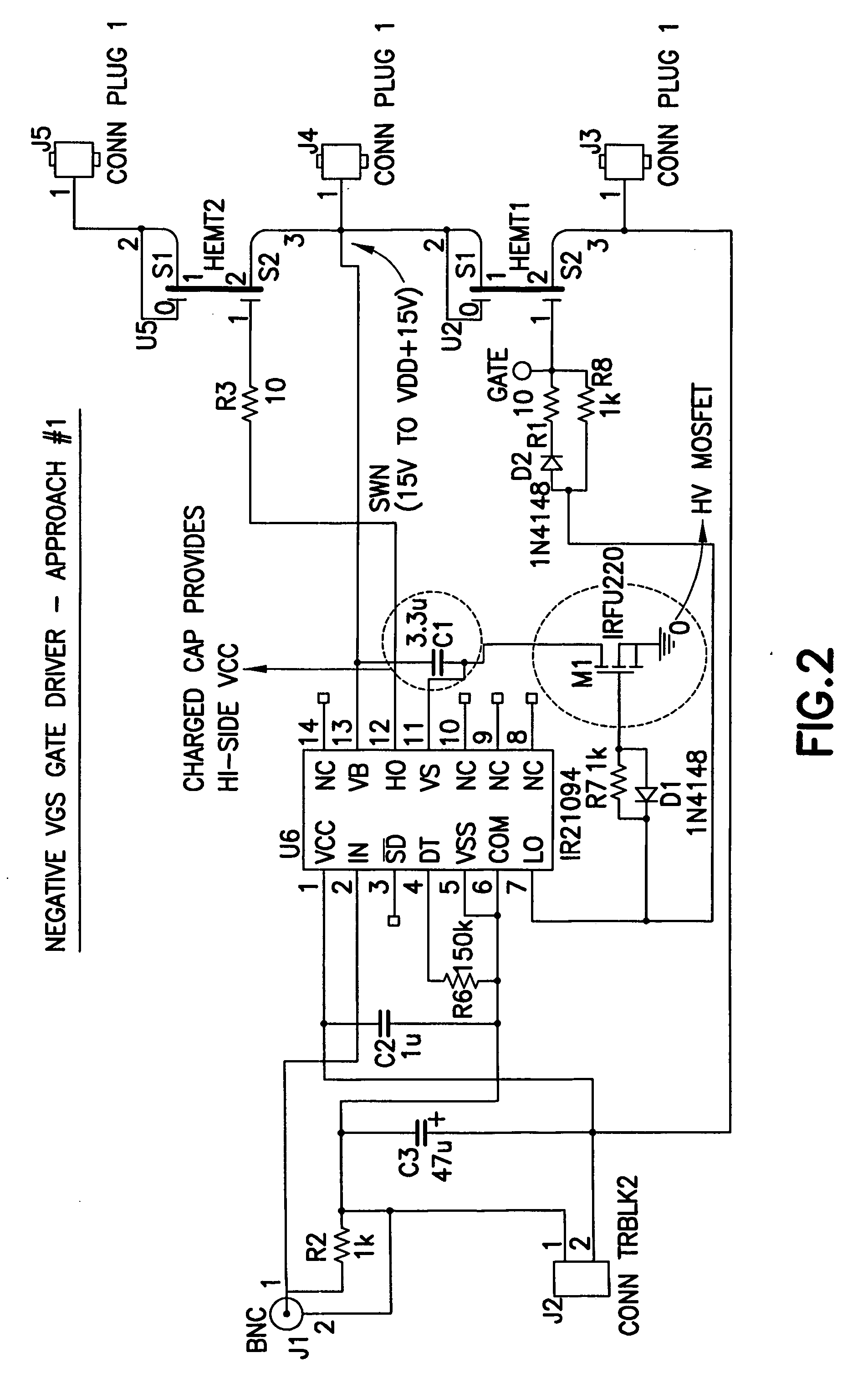

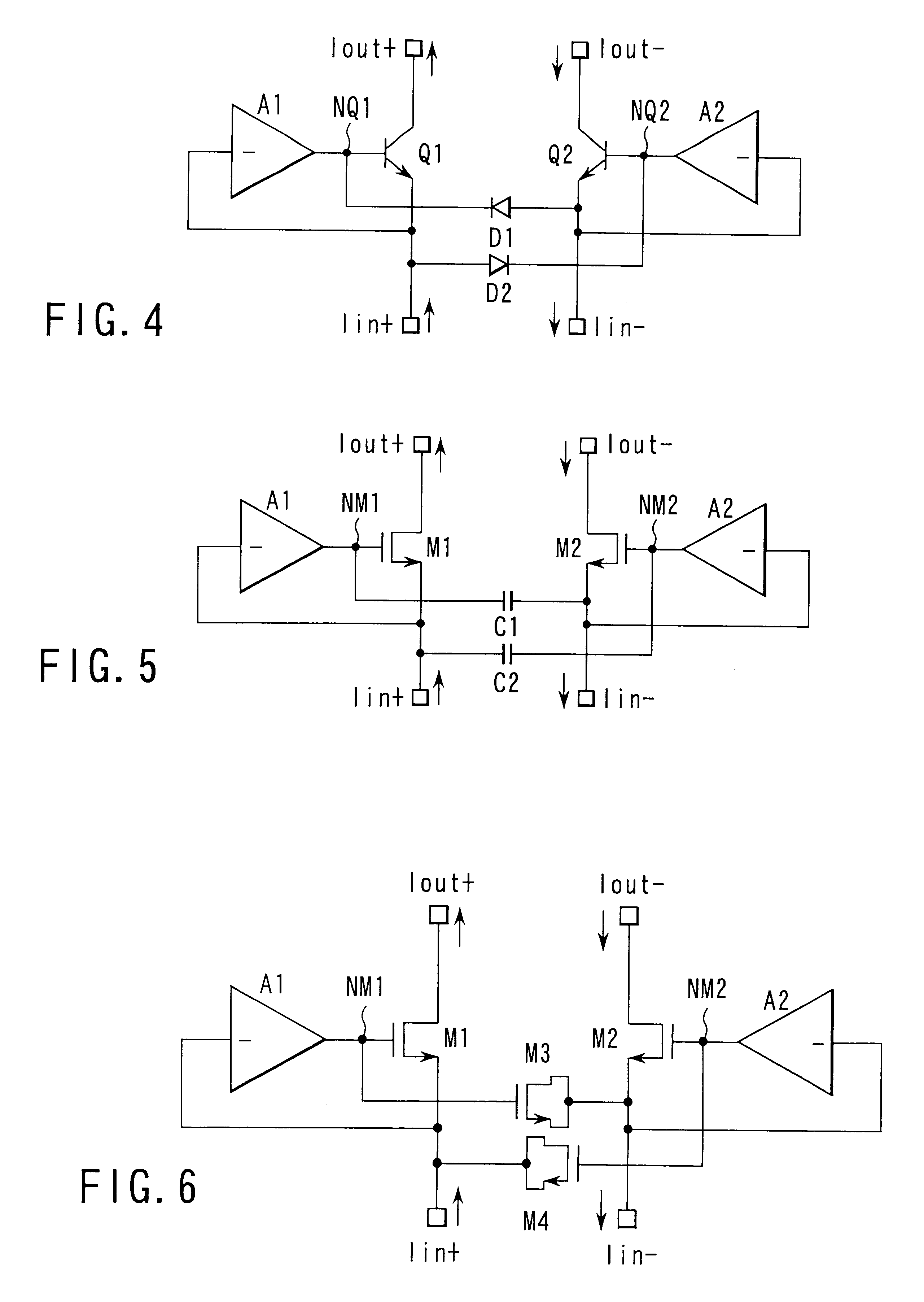

Driving circuit for use with high voltage bidirectional semiconductor switches

A driving circuit for a half bridge utilizing bidirectional semiconductor switches in accordance with an embodiment of the present application includes a high side driver operable to control a high side bidirectional semiconductor switch, wherein the high side driver provides a negative bias voltage to the bidirectional semiconductor switch to turn the high side bidirectional semiconductor switch OFF. A low side driver may be operable to control a low side bidirectional semiconductor switch. An external voltage source with a negative terminal of the voltage source connected to the high side driver may be provided. A high side driving switch may be positioned between the negative terminal of the voltage source and the high side driver and operable to connect the high side driver to the negative terminal of the voltage source when the low side driver turns the low side bidirectional semiconductor switch ON.

Owner:INFINEON TECH AMERICAS CORP

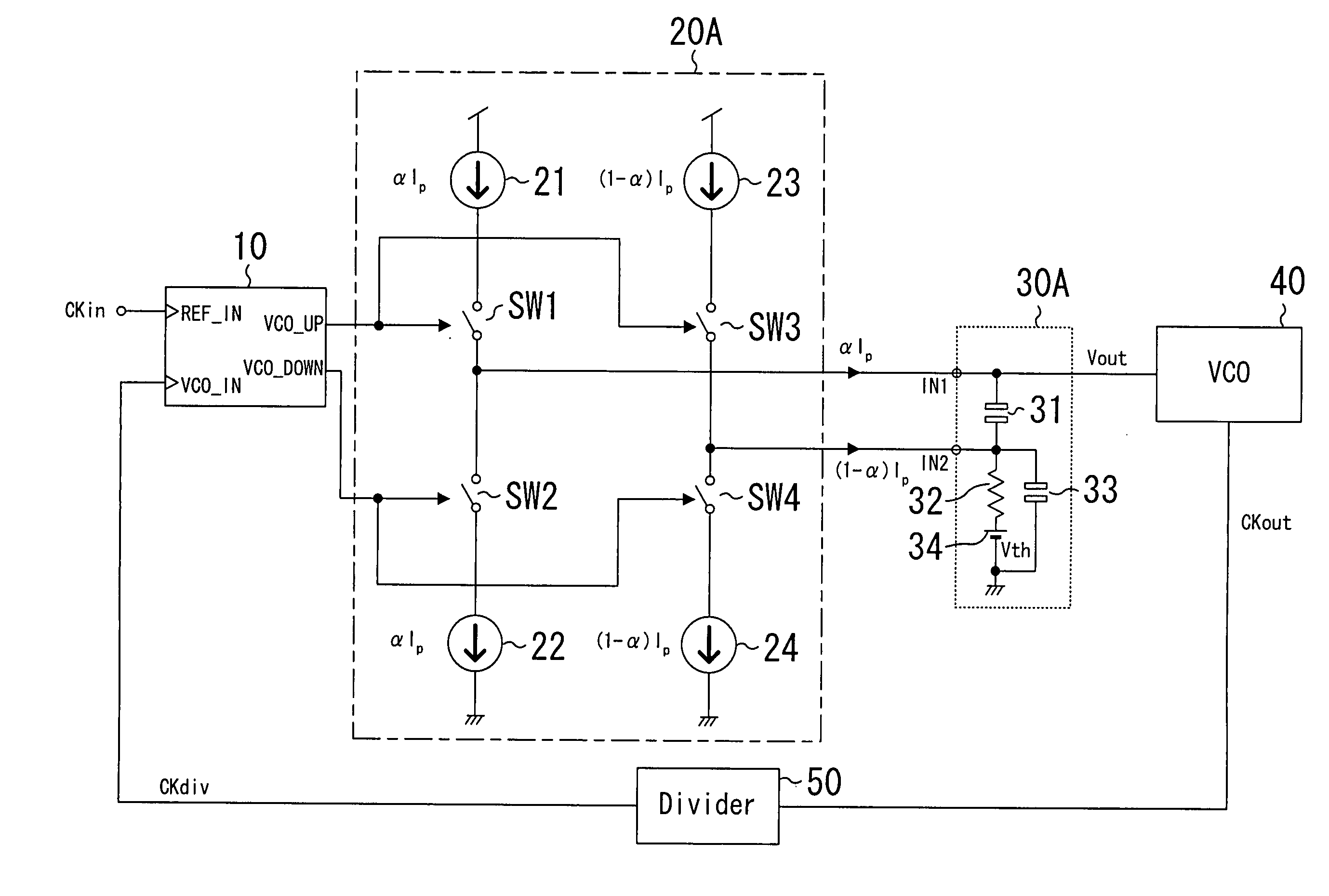

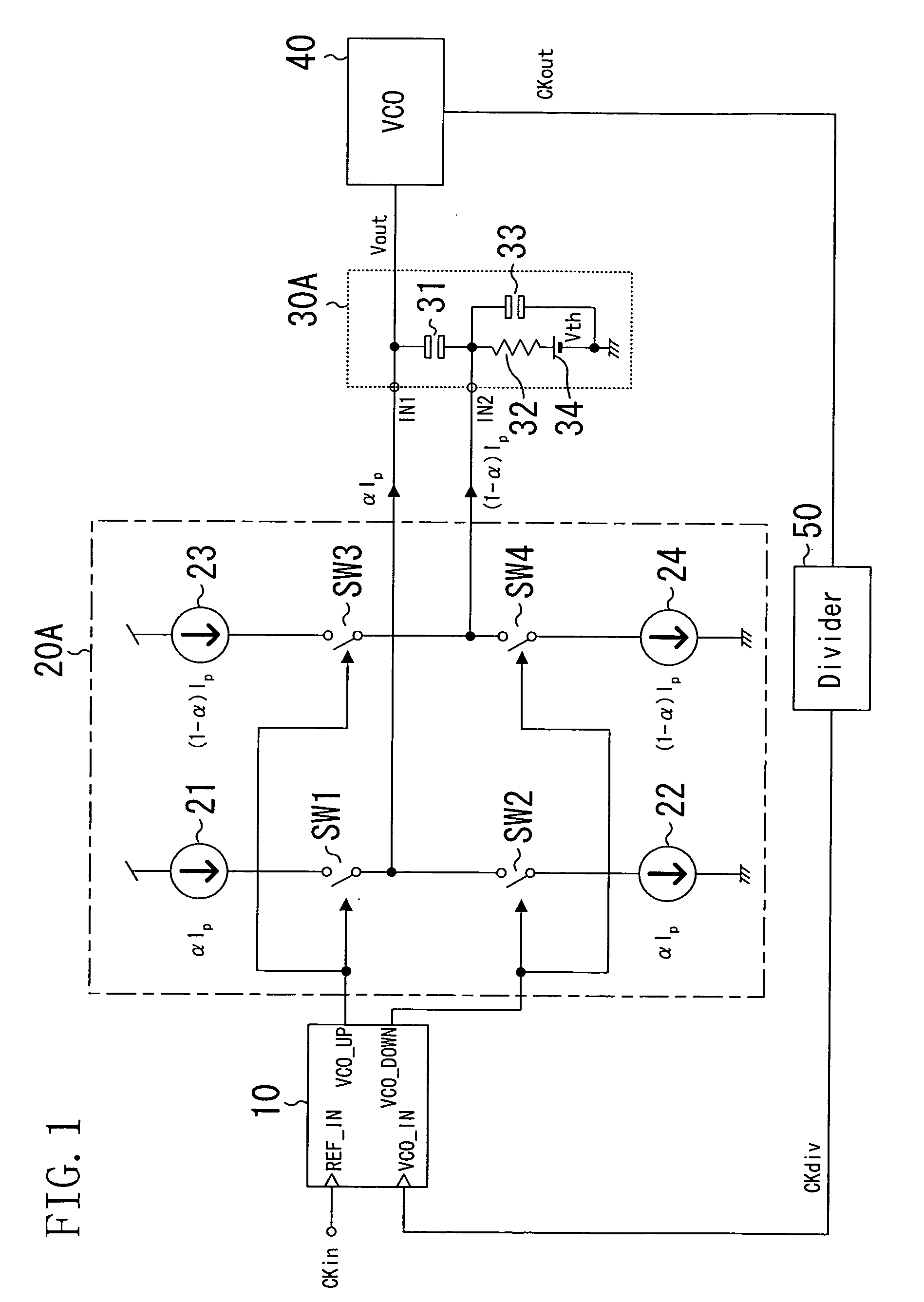

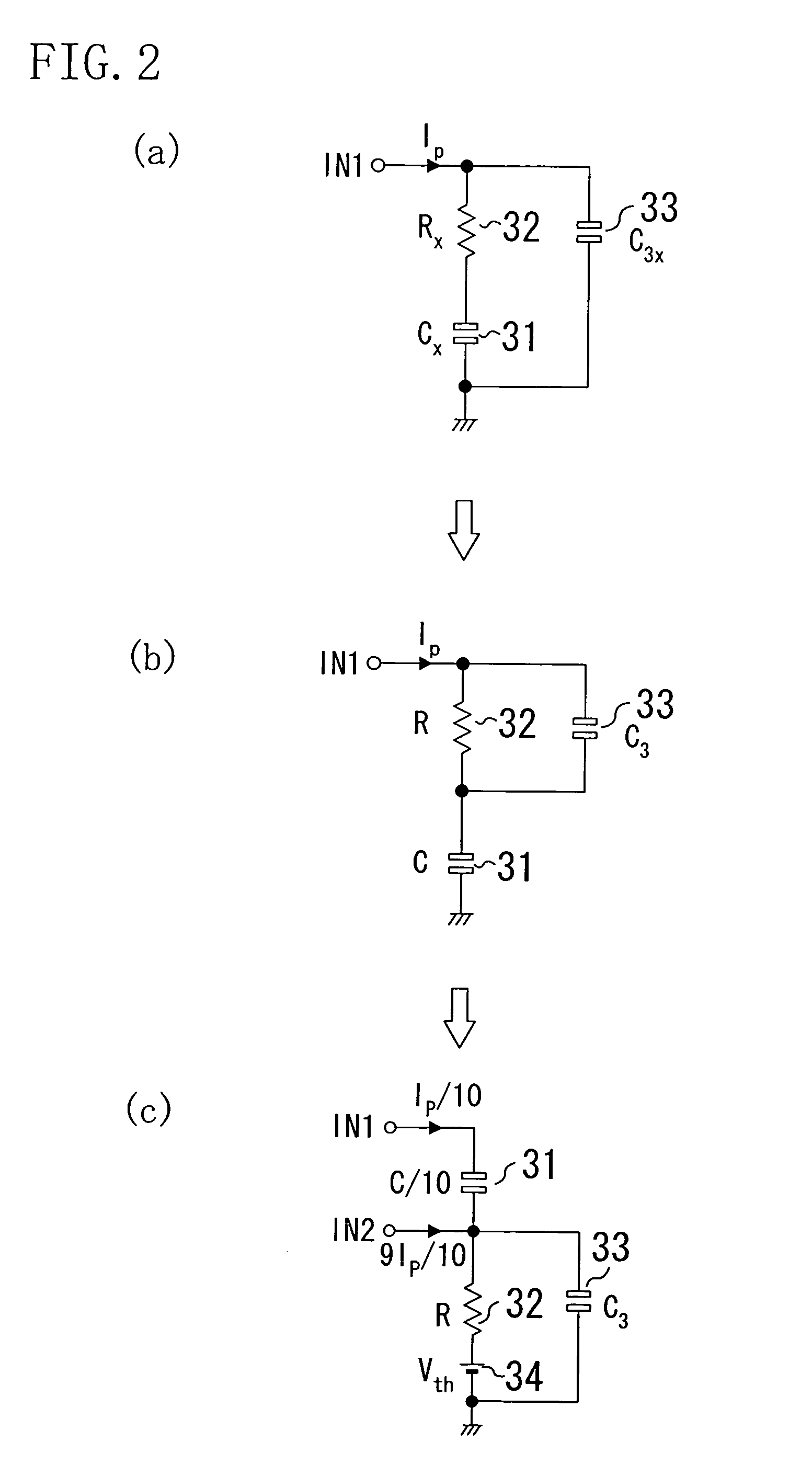

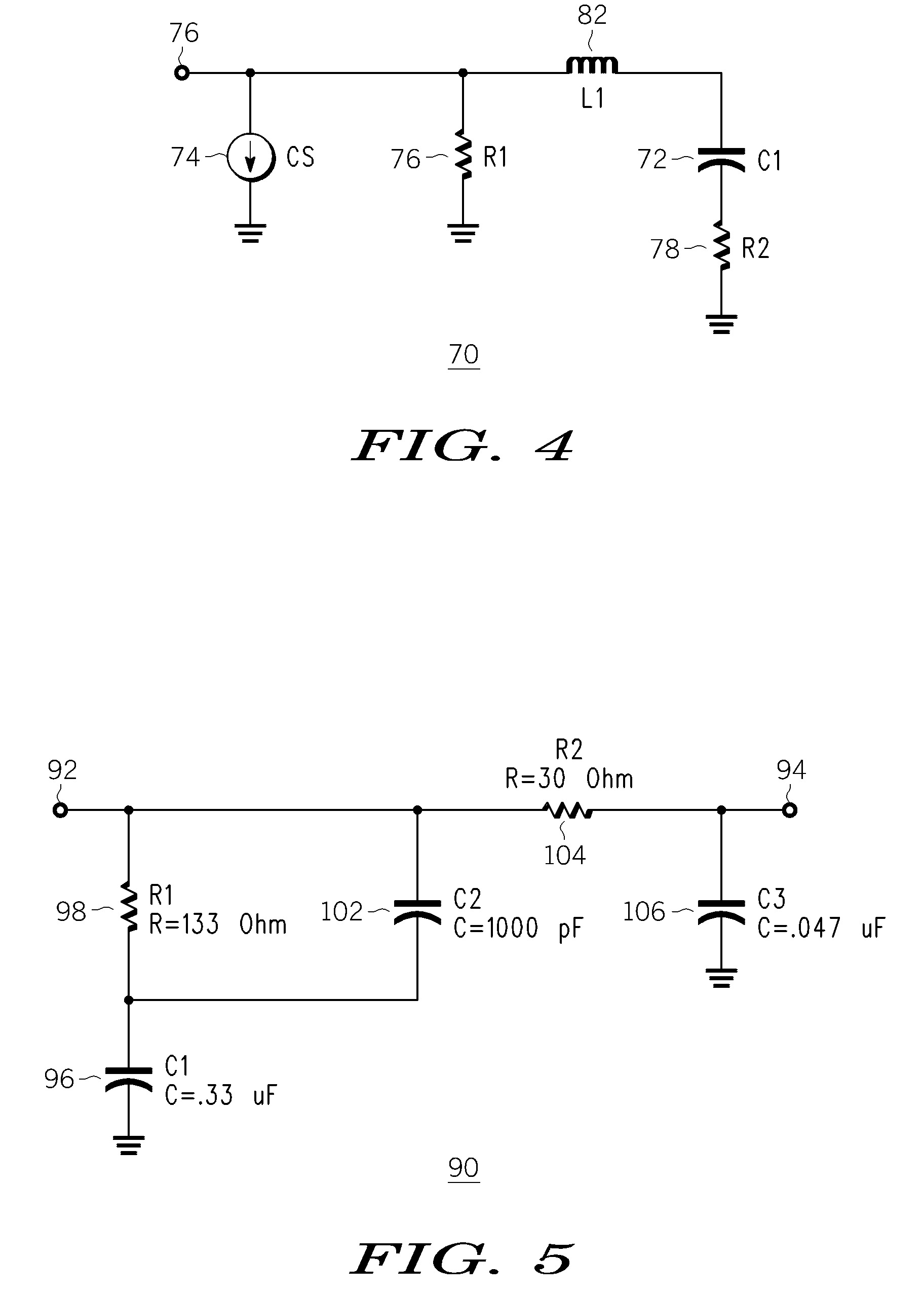

Low-pass filter and feedback system

InactiveUS6995607B2Easy to useSmall sizeMultiple-port networksPulse automatic controlCapacitanceBand-pass filter

In a low-pass filter, the filter characteristics equivalent to those of a conventional low-pass filter are maintained, the size of a capacitive element is decreased, and the low-pass filter operates stably. Further, a MOS capacitor is used as a capacitive element. For such purposes, in a low-pass filter including a first capacitive element, and a resistive element and a second capacitive element which are connected in series to the first capacitive element, a first electric current is supplied to the first input terminal connected to one end of the first capacitive element, and a second electric current is supplied to the second input terminal connected to the other end of the first capacitive element. Herein, the capacitance value of the first capacitive element is set according to the magnitude of the first electric current. Further, the resistive element is provided with a power supply that is connected in series to the resistive element, and a voltage equal to or higher than the threshold voltage of a MOS transistor is always applied between the second input terminal and the ground.

Owner:PANASONIC CORP

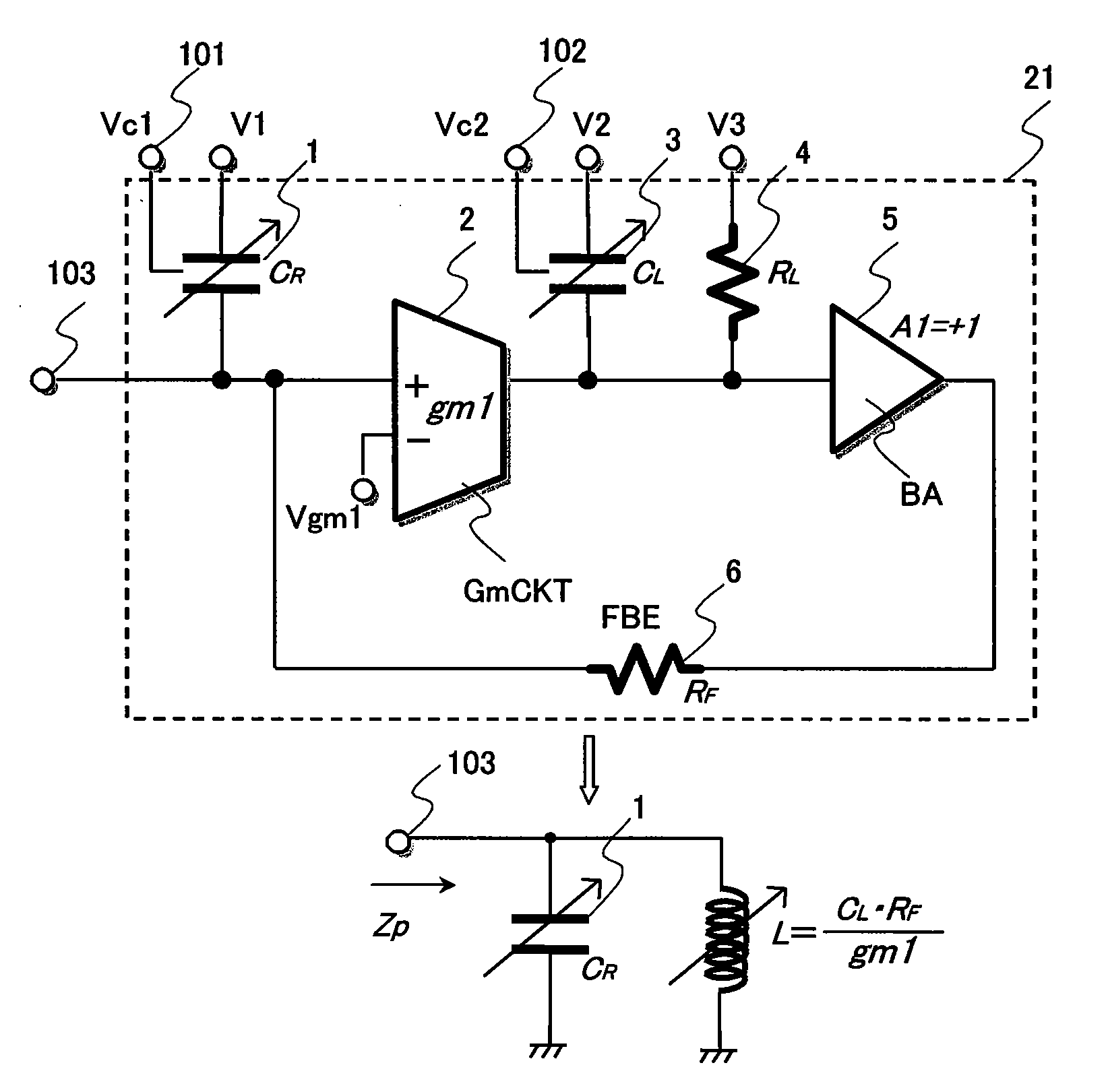

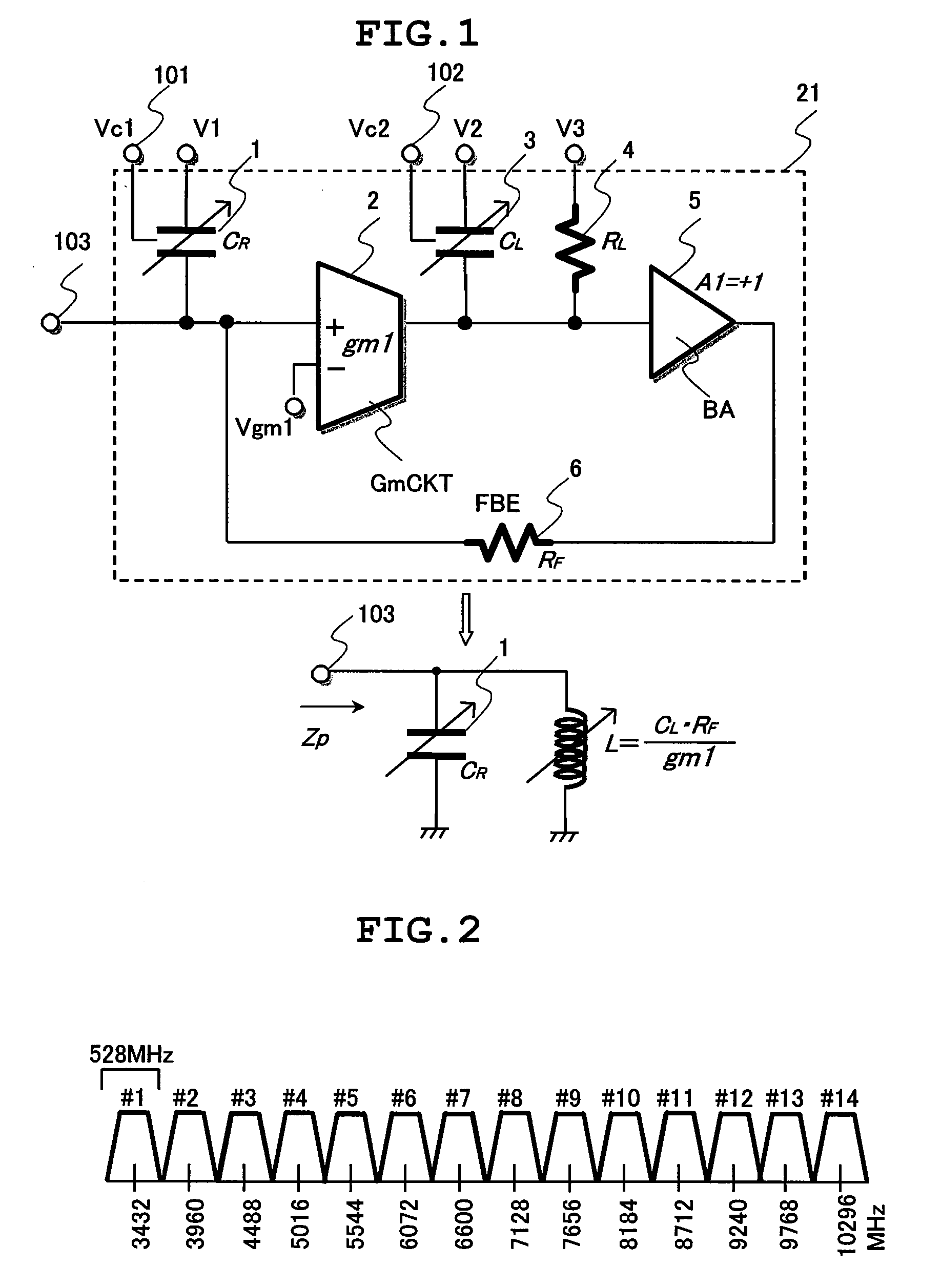

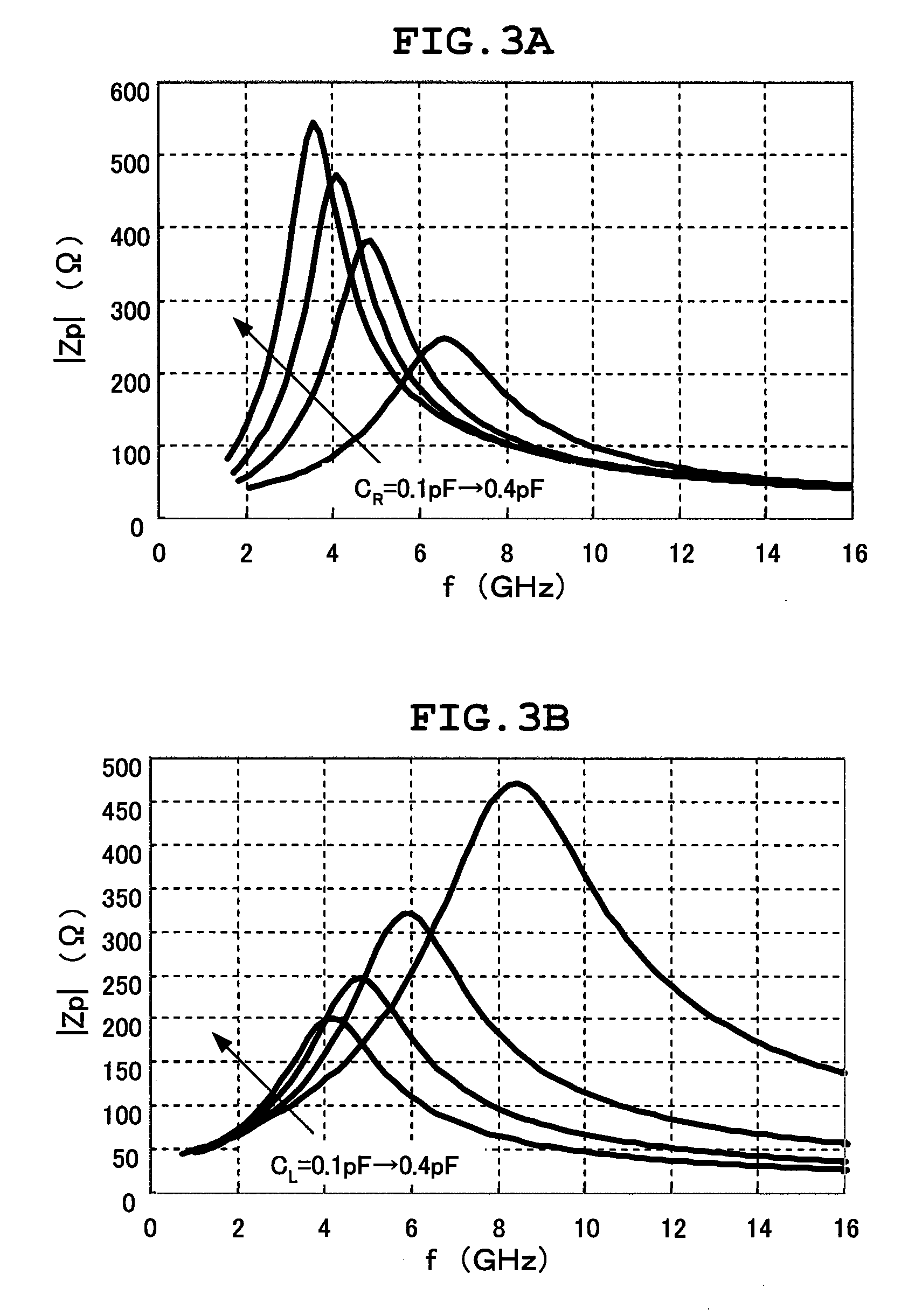

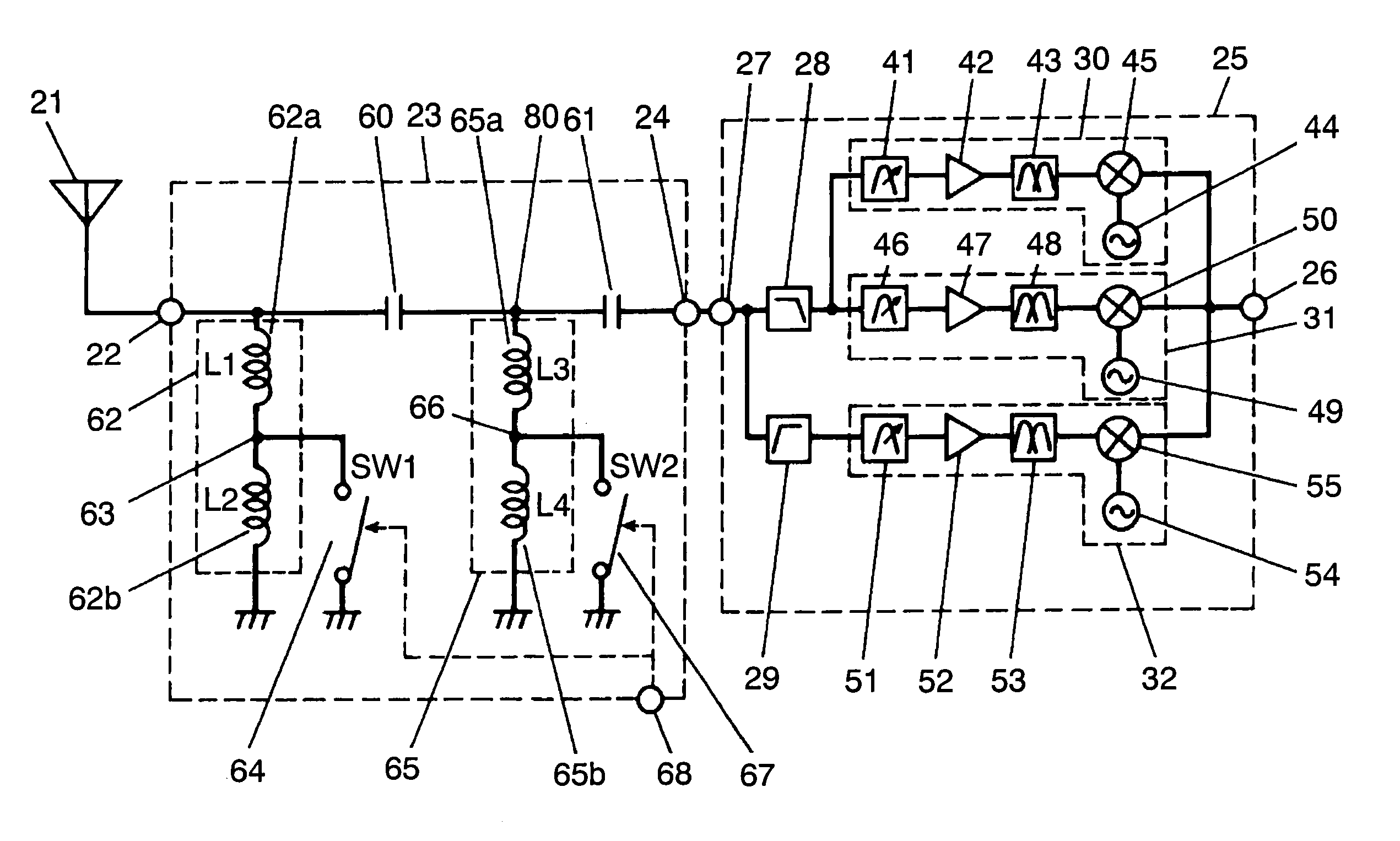

Active resonant circuit with resonant-frequency tunability

The present invention is directed to provide a low-power-consumption wide-range RF signal processing unit having a small chip occupation area. A semiconductor integrated circuit has, on a semiconductor chip, a resonant circuit including a first capacitor having a capacitance which can be controlled by a first control signal of a first control terminal, and a gyrator for equivalently emulating an inductor by including a second capacitor having a capacitance which can be controlled by a second control signal of a second control terminal. The capacitance and the inductor form a parallel resonant circuit. At the time of changing parallel resonant frequency, the capacitances of the first and second capacitors are coordinately changed. The parallel resonant circuit is suitable for an active load which is connected to an output node of an amplifier.

Owner:RENESAS ELECTRONICS CORP

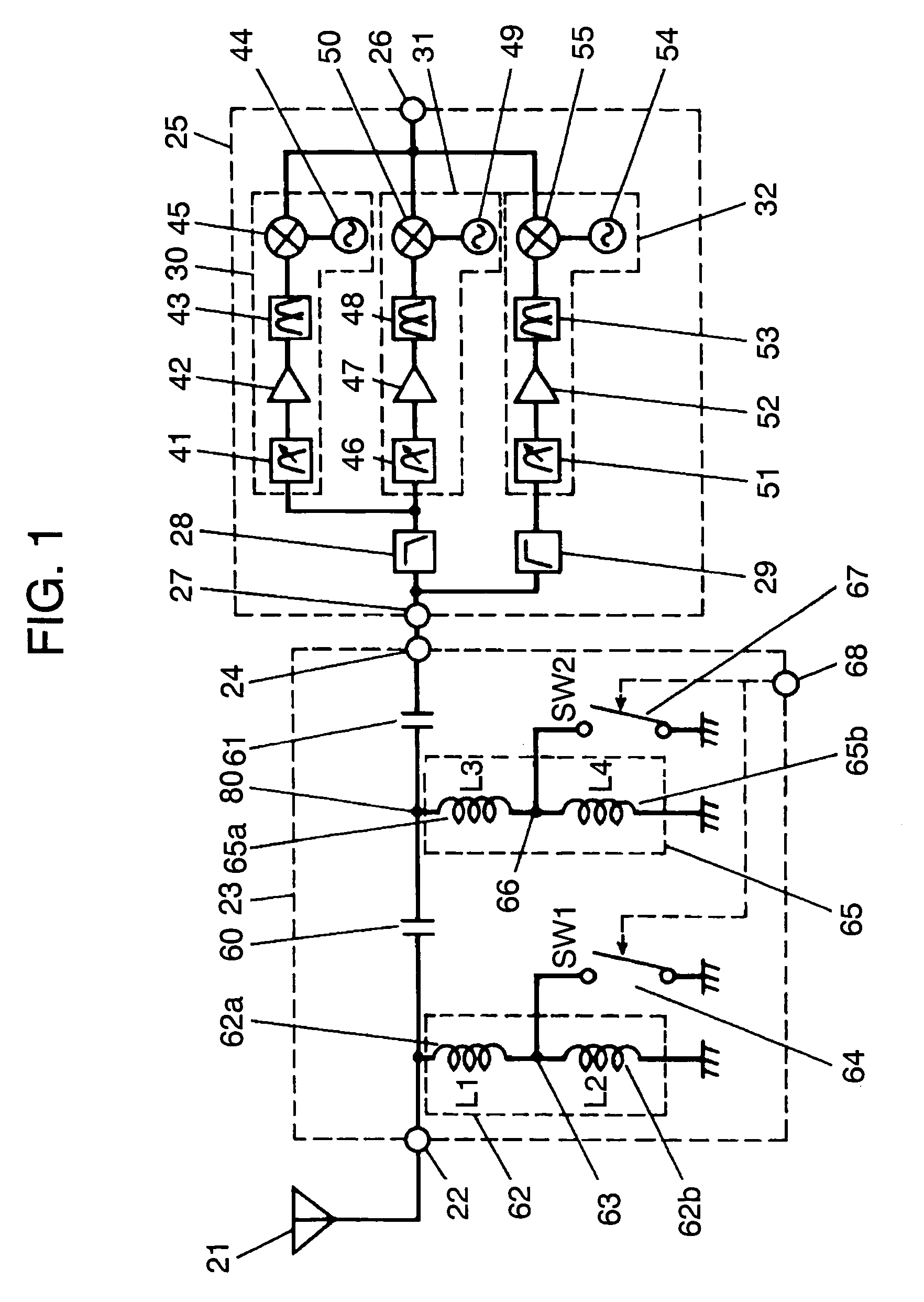

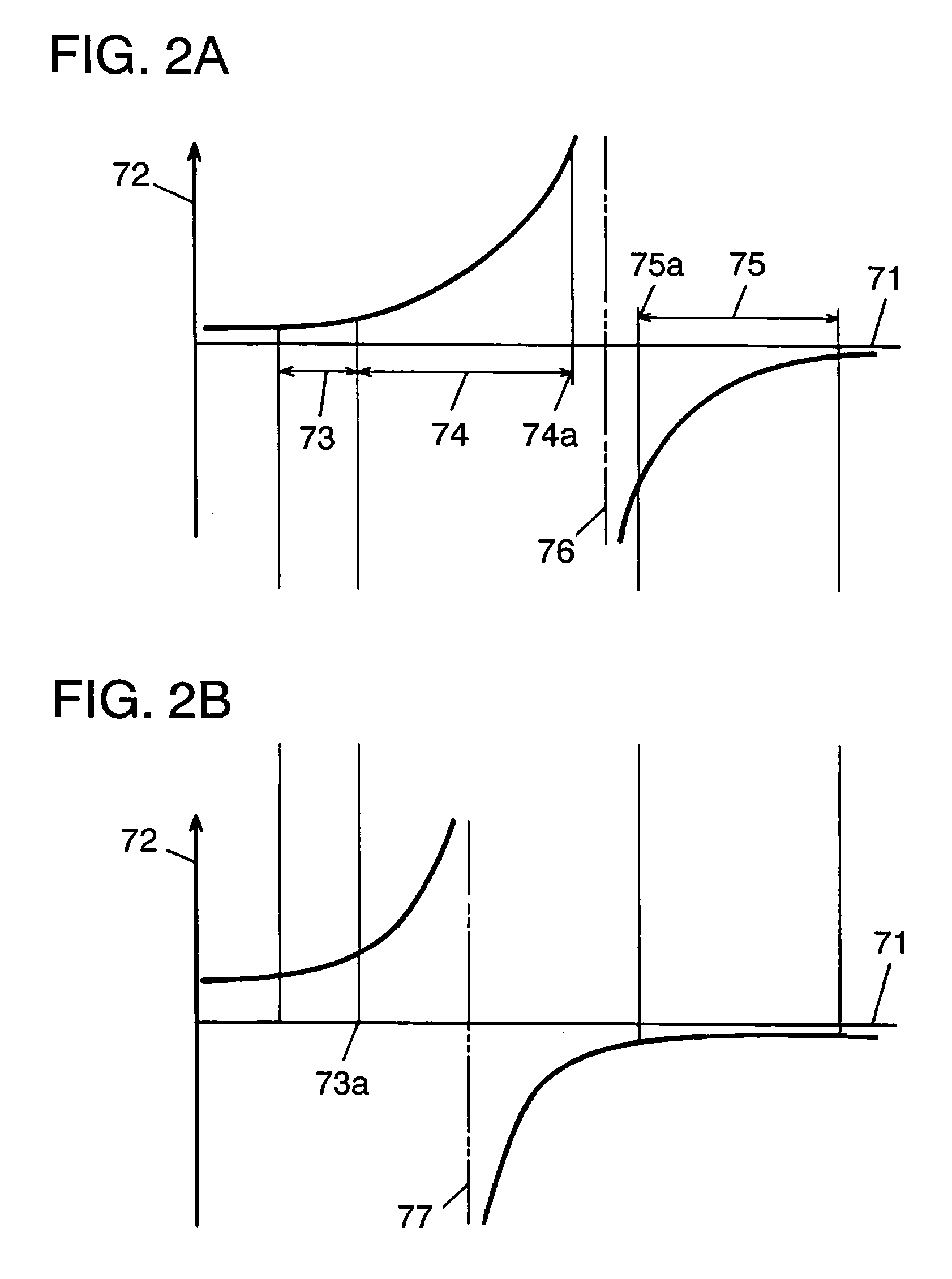

Matching unit

InactiveUS7142833B2Simple circuitLow costTelevision system detailsMultiple-port networksCapacitanceInductor

A matching unit includes a switching means for switching an inductance of a first inductor. This switching means sets an inductance such that a first inductor shows an inductance property to both of the VHF low-band and high-band, and shows a capacitance property to the UHF band. This structure allows the matching unit to achieve the matching for both the VHF low-band and high-band by just switching the two circuits of the VHF low-band and high-band, also allows the matching unit to show a capacitance property to the UHF band. Thus the loss produced in transmitting signals can be reduced, and the circuit can be simplified. As a result, the matching unit can be downsized, and the cost can be reduced.

Owner:PANASONIC CORP

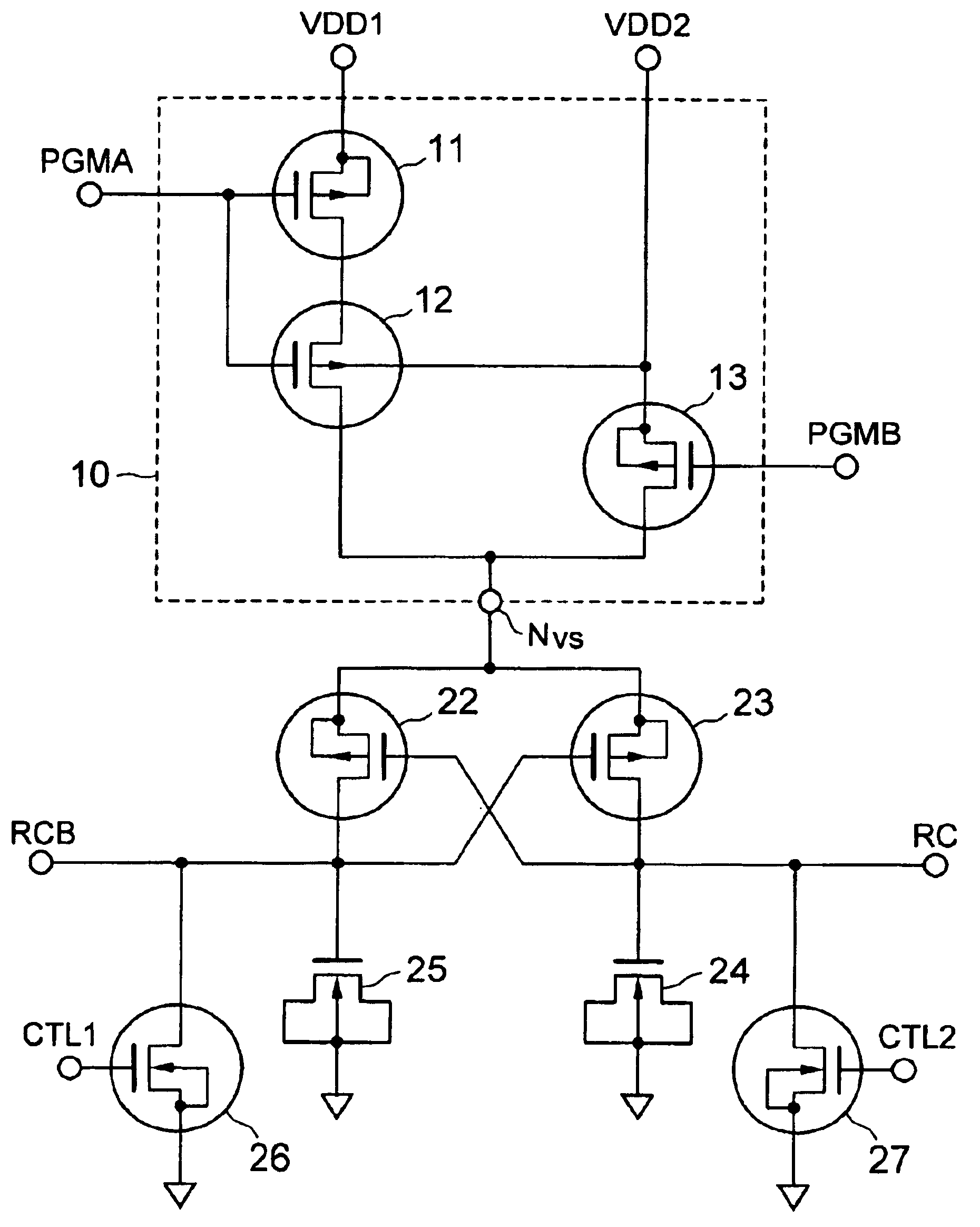

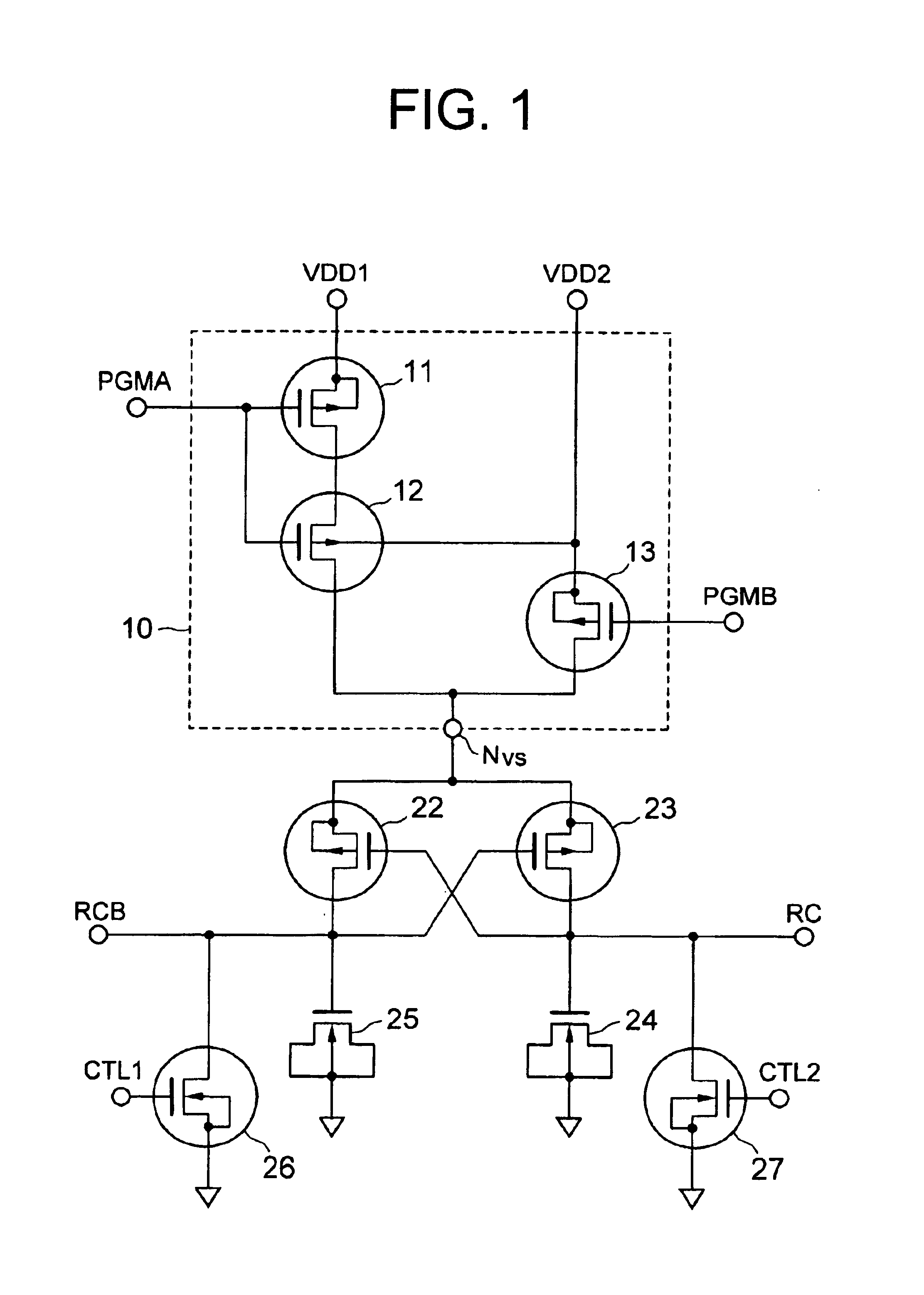

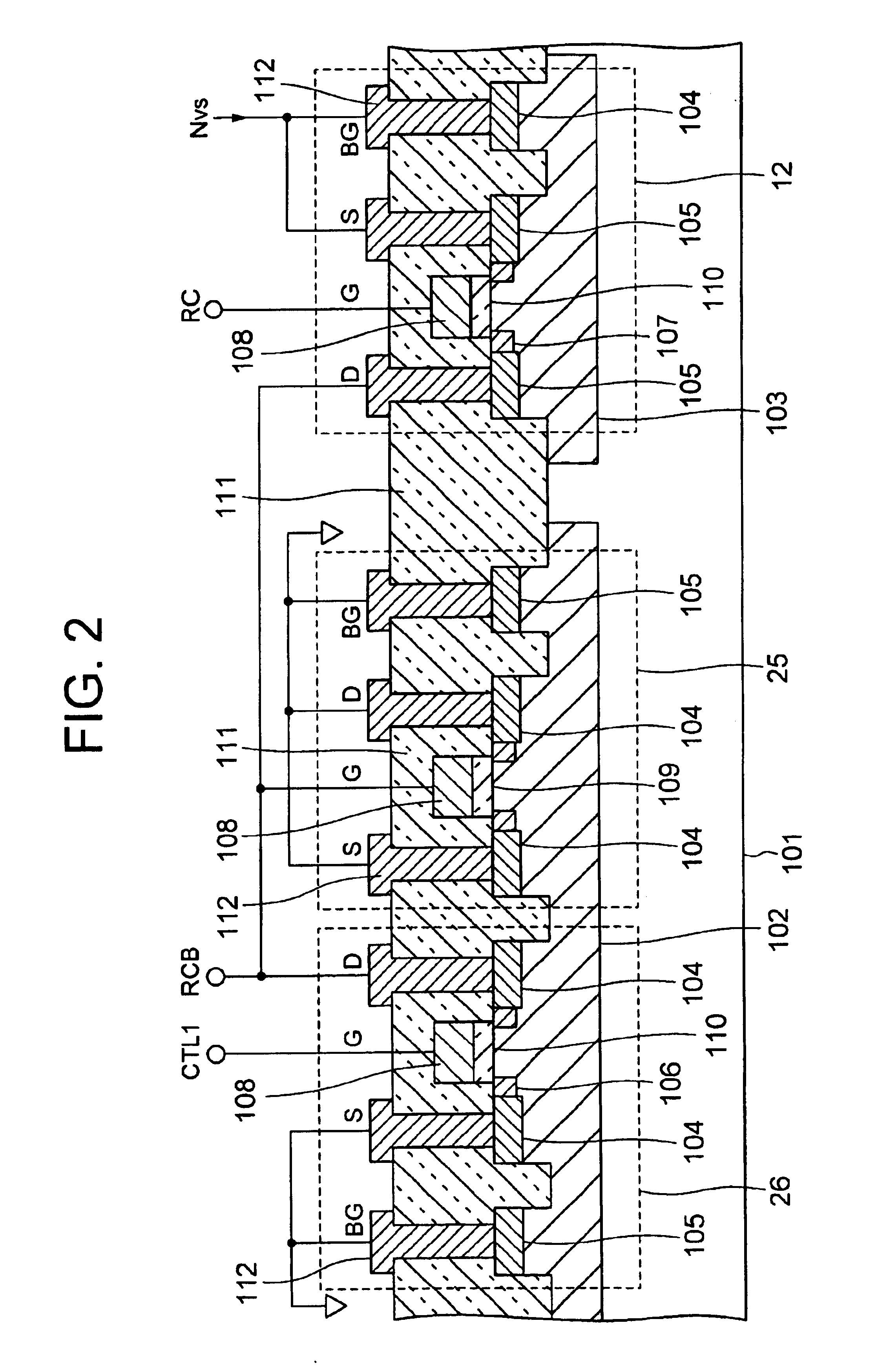

Data latch circuit having anti-fuse elements

A data latch circuit includes anti-fuse elements for storing remedy information therein as to replacement of defective memory cells by redundant memory cells. For programming the anti-fuse elements to a logic level "1" in a programming mode, control signals CTL1 and CTL2 are set at a low level and a high level, respectively, and programming control signals PGMA and PGMB are set at a high level and a low level, respectively. A voltage selection node Nvs delivers a programming voltage Vpp, lowering an output terminal RCB to effect dielectric breakdown of anti-fuse element 25, which assumes a low resistance. In a normal operation mode, programming voltages PUMA and PGMB are set at a low level and a high level, respectively, and both control signals CTL1 and CTL2 are set at a low level Voltage output node Nvs delivers the normal operating voltage, raising output terminal RC to a high level to thereby deliver the stored logic level "1".

Owner:NEC ELECTRONICS CORP

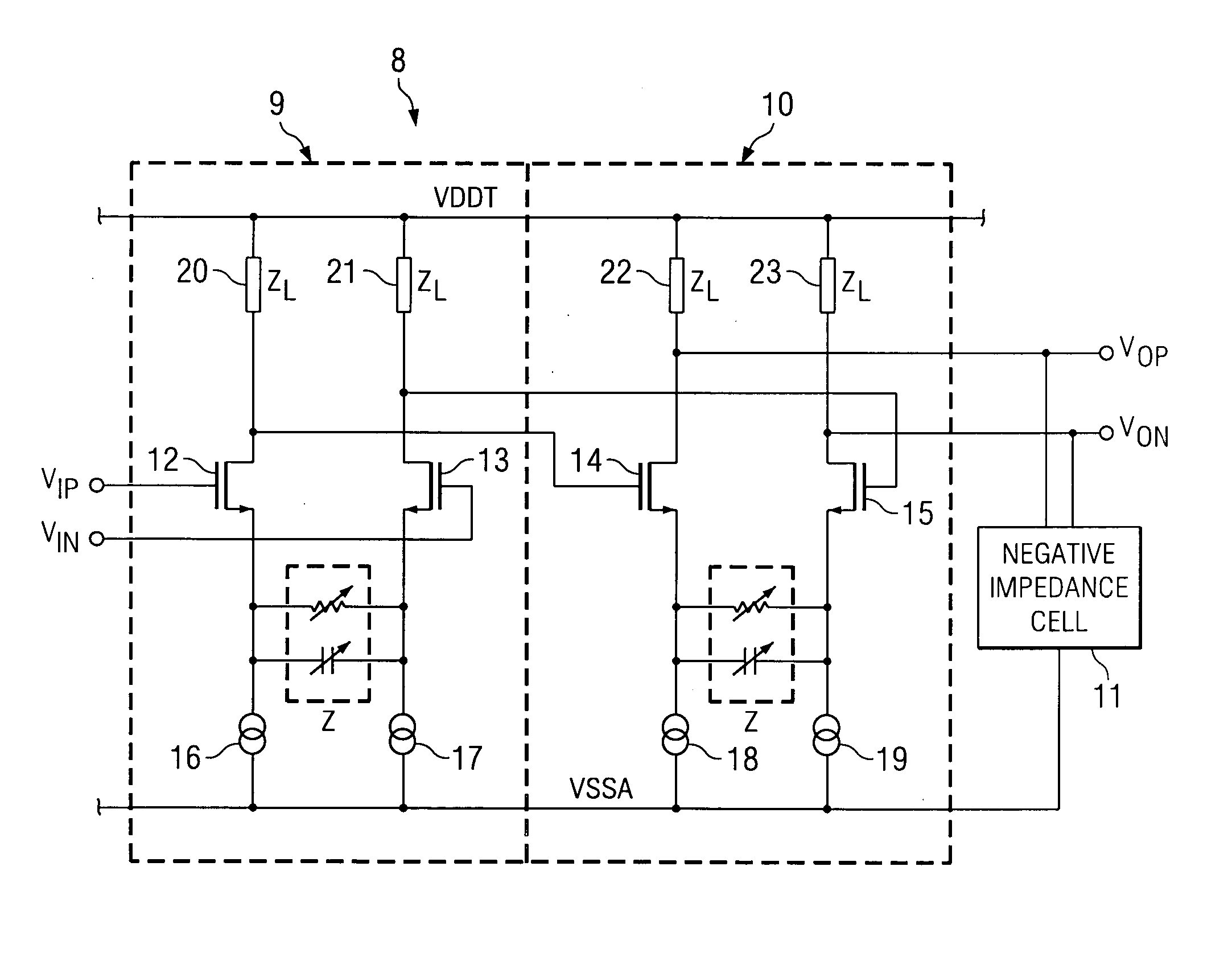

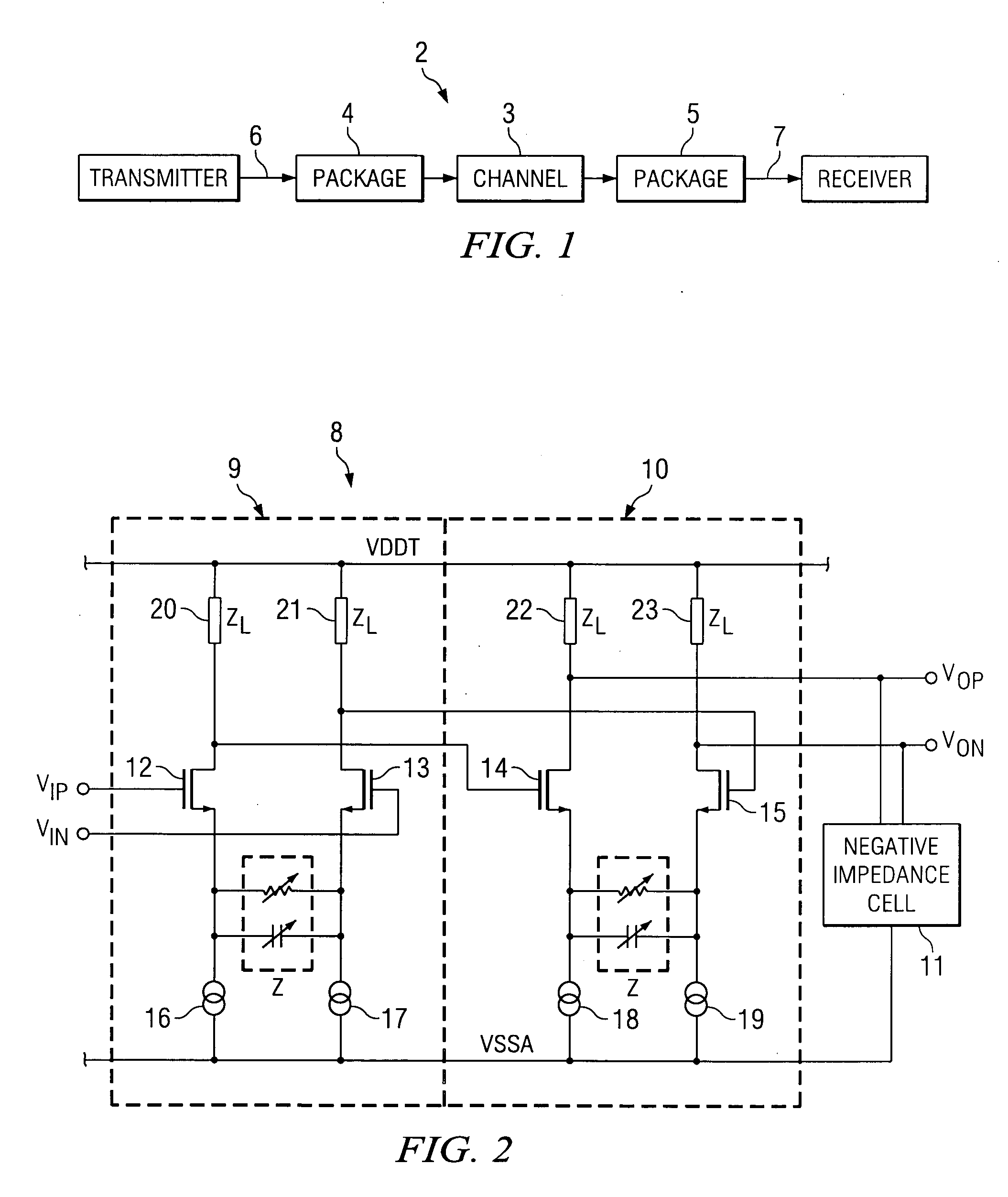

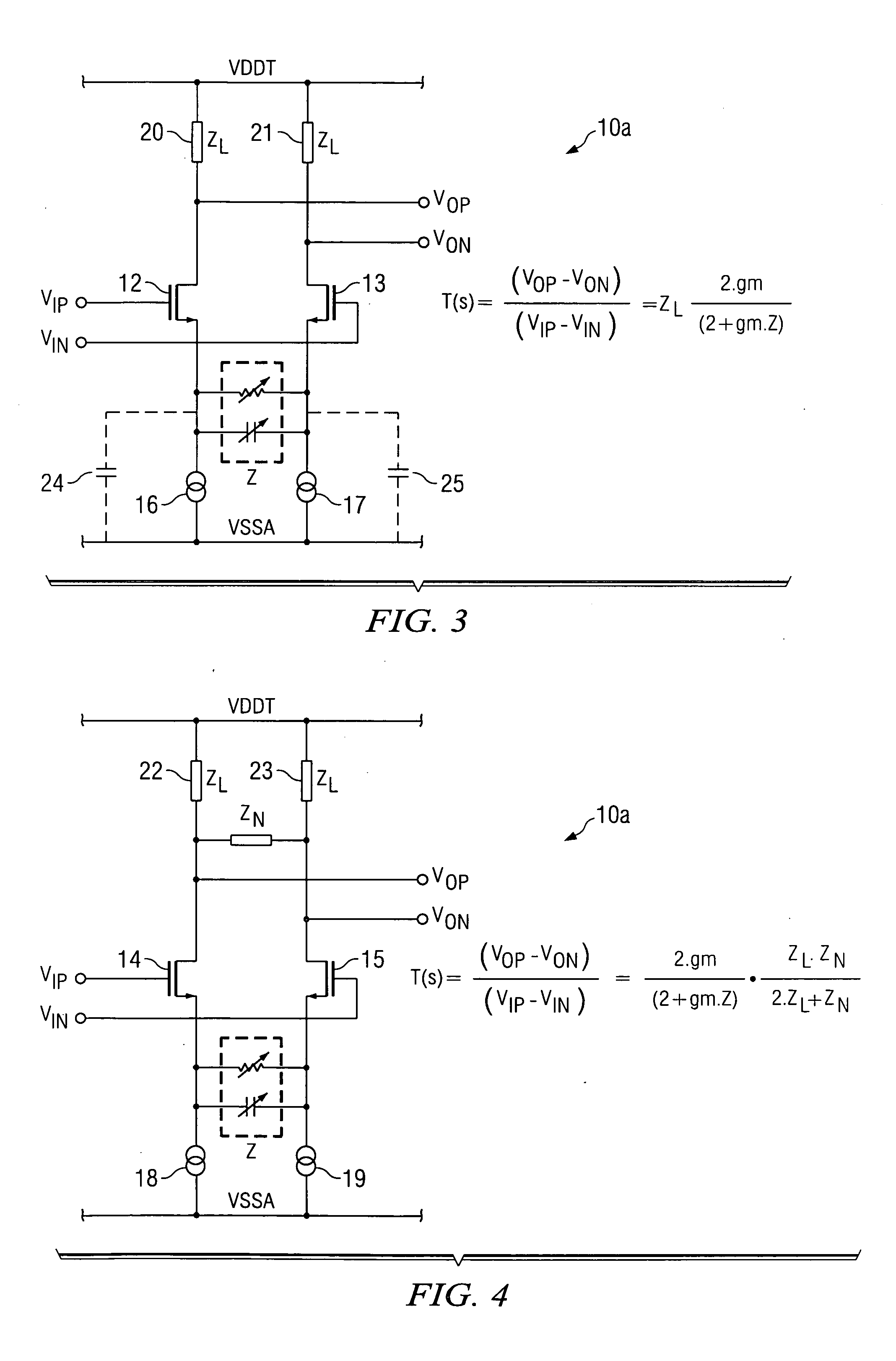

High bandwidth high gain receiver equalizer

There is provided a receiver equalizer comprising, a first equalizer unit having a basic equalizer stage and a negative impedance cell connected to said basic equalizer stage. Preferably the negative impedance cell comprises a pair of back to back transistors, and connected thereto a parallel resistor capacitor RC network. The basic equalizer stage comprises: a pair of current sources; a pair of transistors arranged as a differential pair, each transistor connected to a different one of the current sources; and a degeneration impedance connected in between the two current sources, and the transistors, wherein the negative impedance cell is connected across the outputs of the pair of transistors.

Owner:TEXAS INSTR INC

Multiple-phase frequency translated filter

A frequency translation filter includes a baseband filter circuit, a clock generator, and a switching circuit. The baseband filter circuit is operable to provide a baseband filter response. The clock generator is operable to generate multiple-phase clock signals at a desired frequency. The switching circuit is operable to frequency translate the baseband filter response of the baseband filter circuit to a high frequency filter response in accordance with the multiple-phase clock signals.

Owner:AVAGO TECH INT SALES PTE LTD

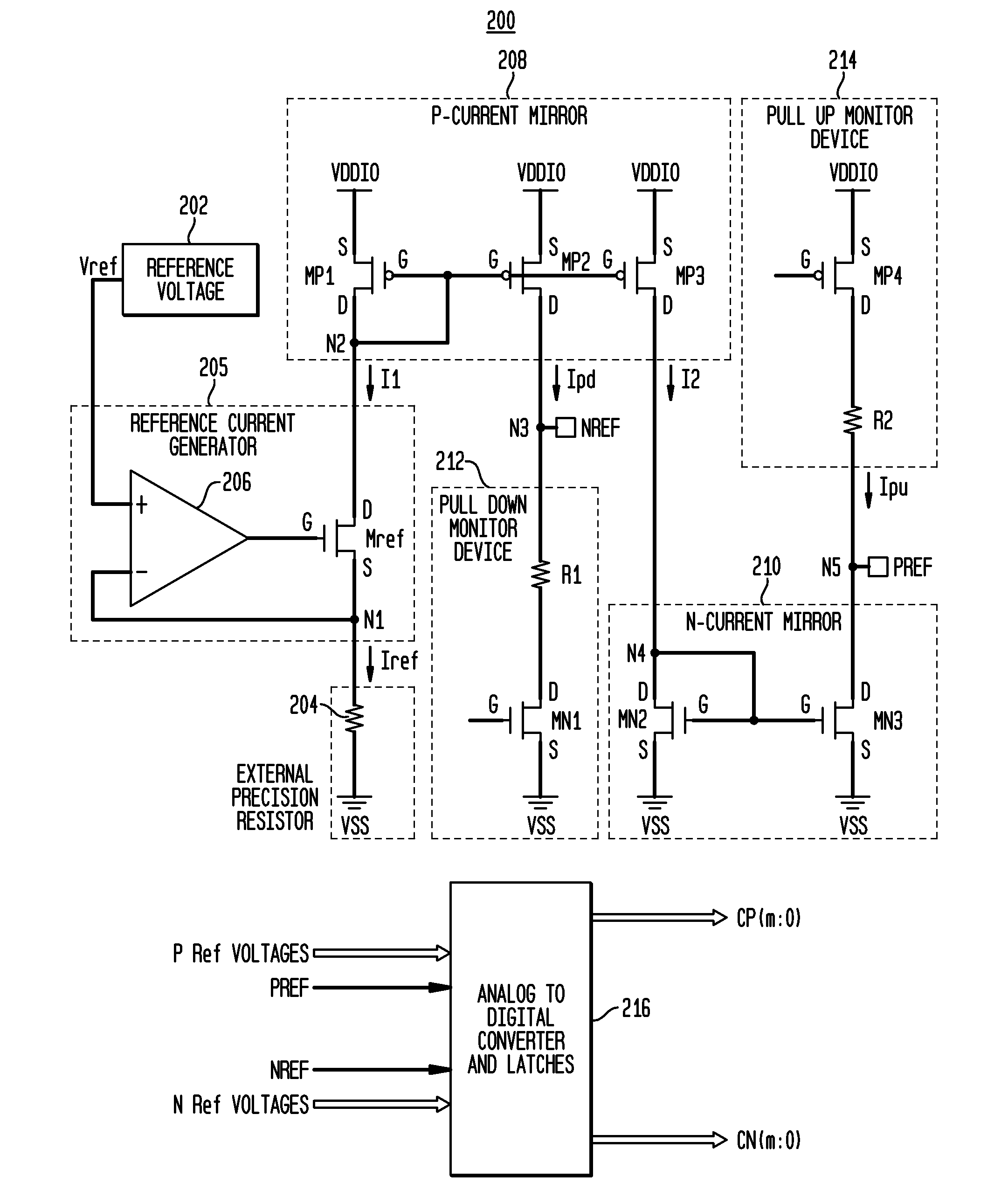

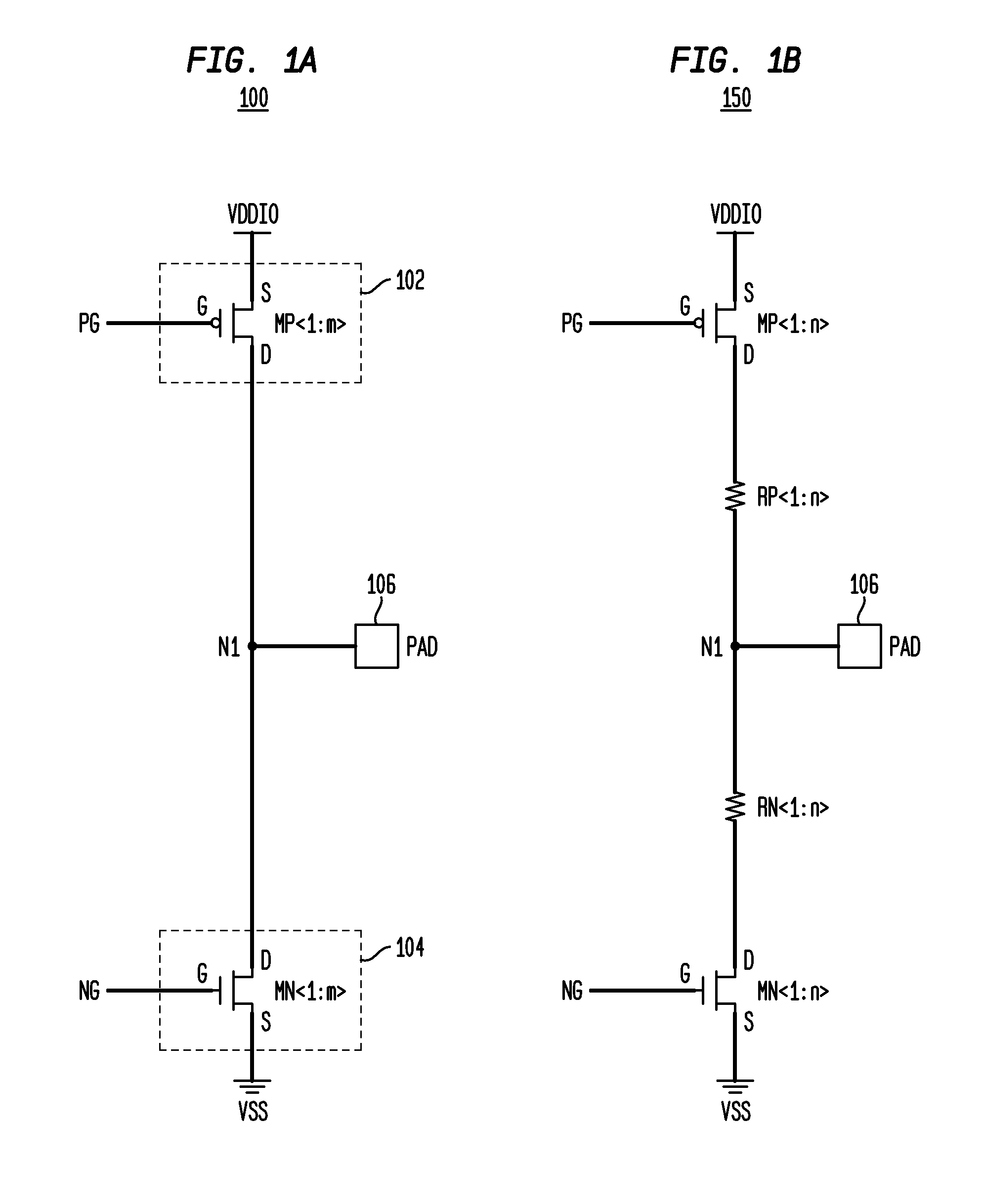

Hybrid Impedance Compensation in a Buffer Circuit

ActiveUS20120326768A1Impedence convertorsAmplifier with semiconductor-devices/discharge-tubesControl signalDigital control

A compensation circuit for controlling a variation in output impedance of at least one buffer circuit includes a monitor circuit and a control circuit coupled with the monitor circuit. The monitor circuit includes a pull-up portion including at least one PMOS transistor and a pull-down portion comprising at least one NMOS transistor. The monitor circuit is configured to track an operation of an output stage of the buffer circuit and is operative to generate at least a first control signal indicative of a status of at least one characteristic of corresponding pull-up and pull-down portions in the output stage of the buffer circuit over variations in PVT conditions to which the buffer circuit may be subjected. The control circuit is operative to generate a set of digital control bits as a function of the first control signal. The set of digital control bits is operative to compensate the pull-up and pull-down portions in the output stage of the buffer circuit over prescribed variations in PVT conditions.

Owner:AVAGO TECH INT SALES PTE LTD

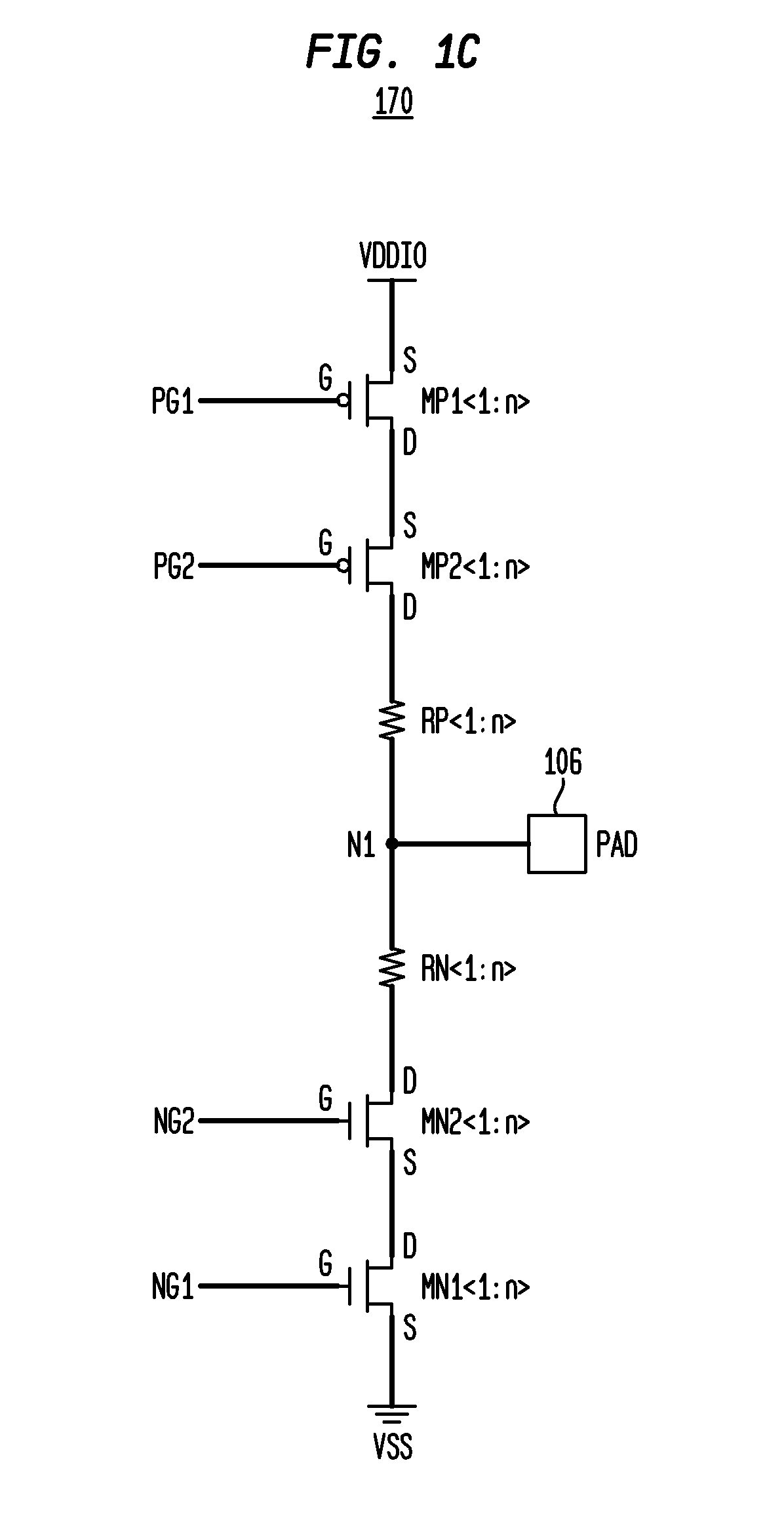

System and method to compensate for process and environmental variations in semiconductor devices

ActiveUS20110063937A1Improve data retentionIncrease frequencyImpedence convertorsElectronic switchingElectric forceDevice material

An integrated circuit (IC) including a controller integrally formed on a shared die with the IC and method of operating the same to compensate for process and environmental variations in the IC are provided. In one embodiment the IC is comprised of device and sub-circuits, and the method includes: receiving in the IC electrical power and information on at least one of one or more operational parameters of the IC; and adjusting one or more operating characteristics of at least one of the devices and sub-circuits in the IC based on the received information using a controller integrally formed on a shared die with the IC. Other embodiments are also disclosed.

Owner:INFINEON TECH LLC

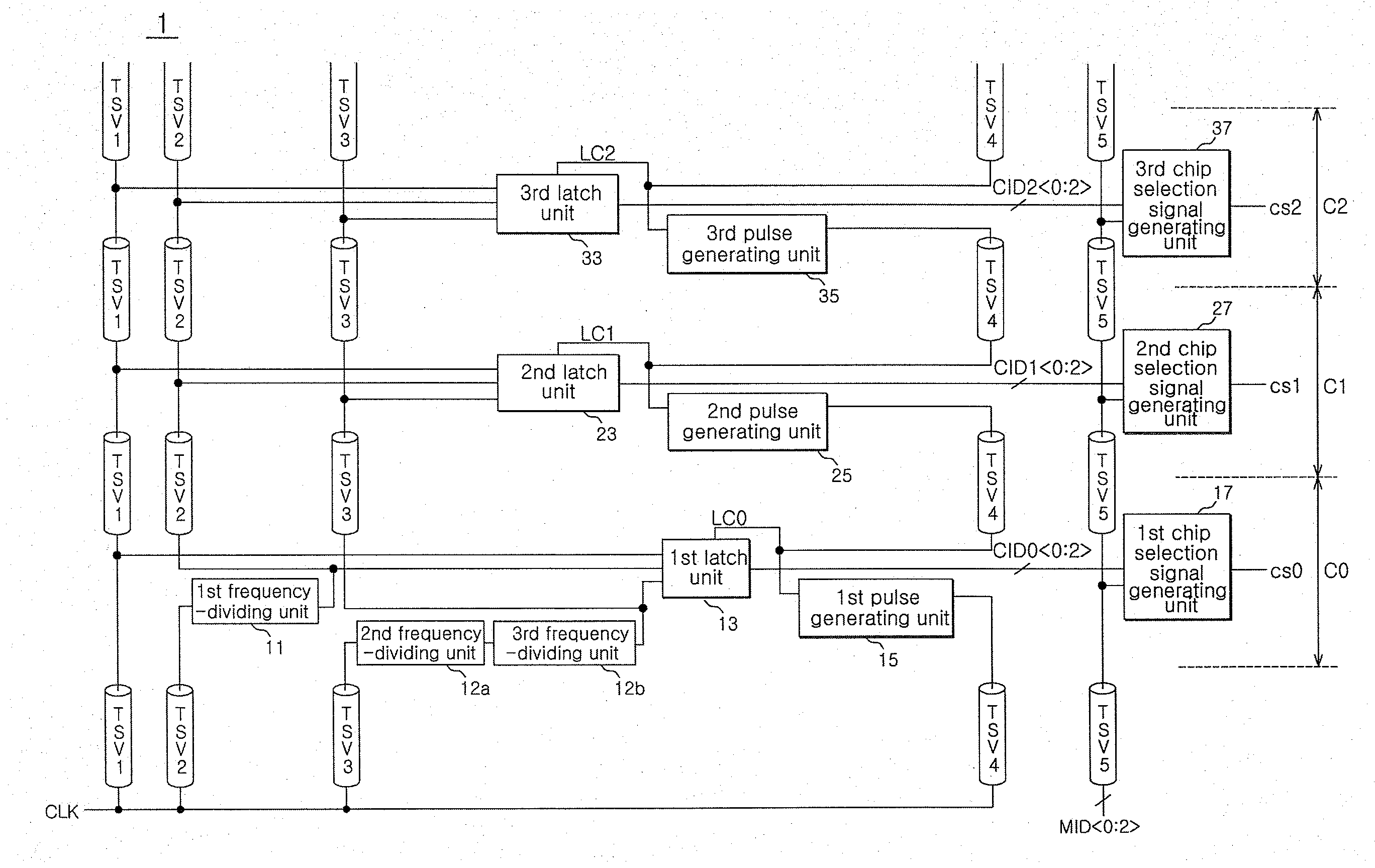

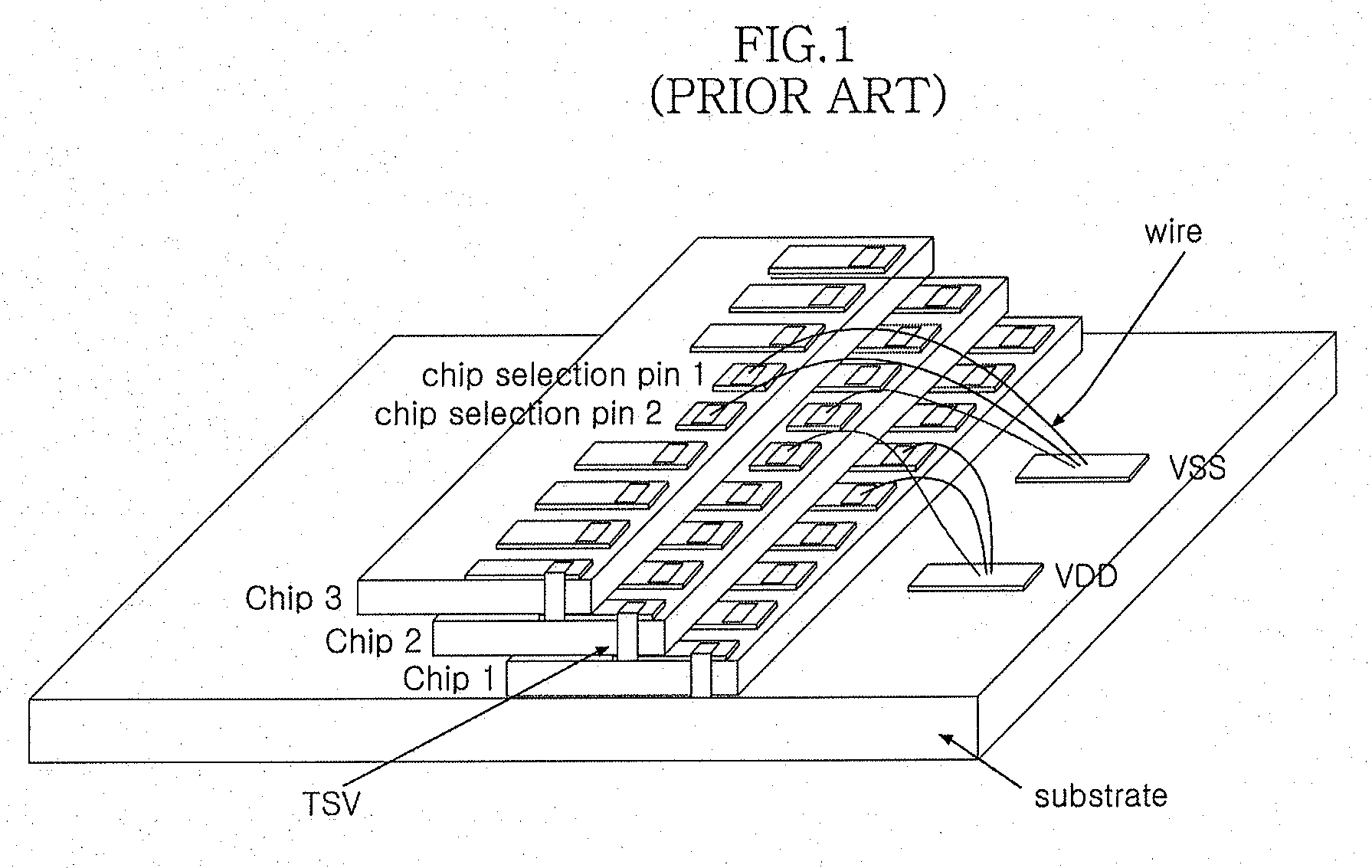

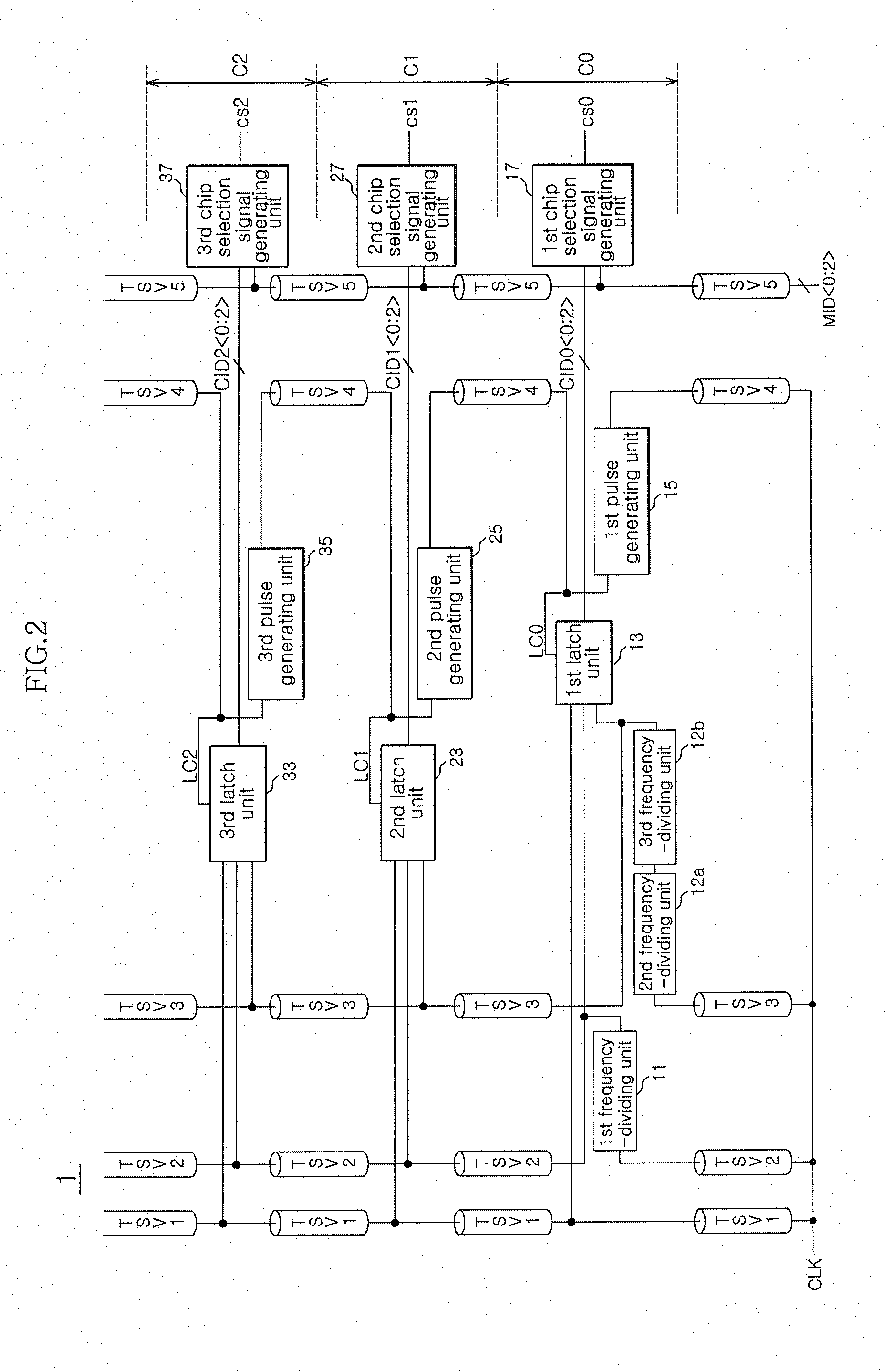

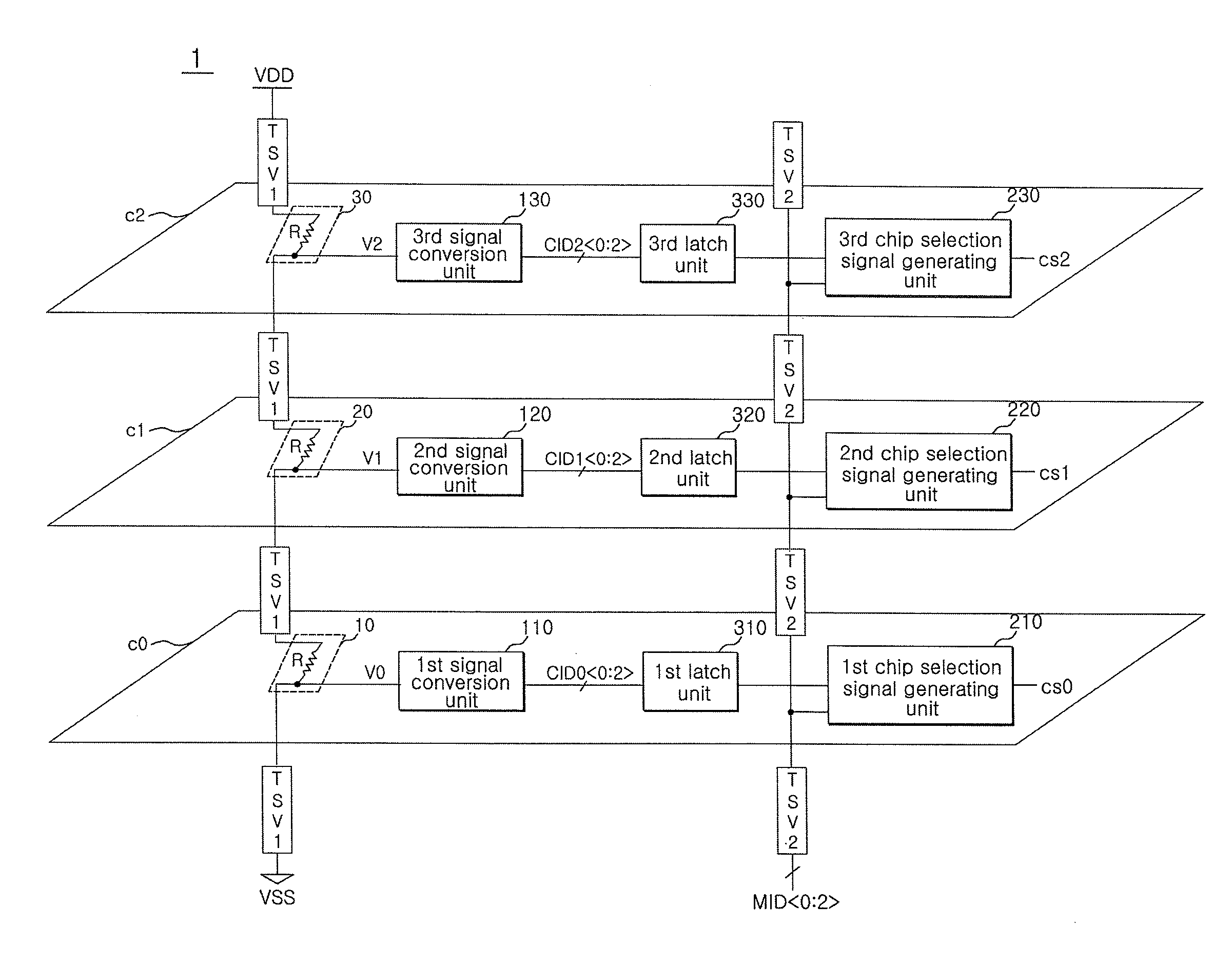

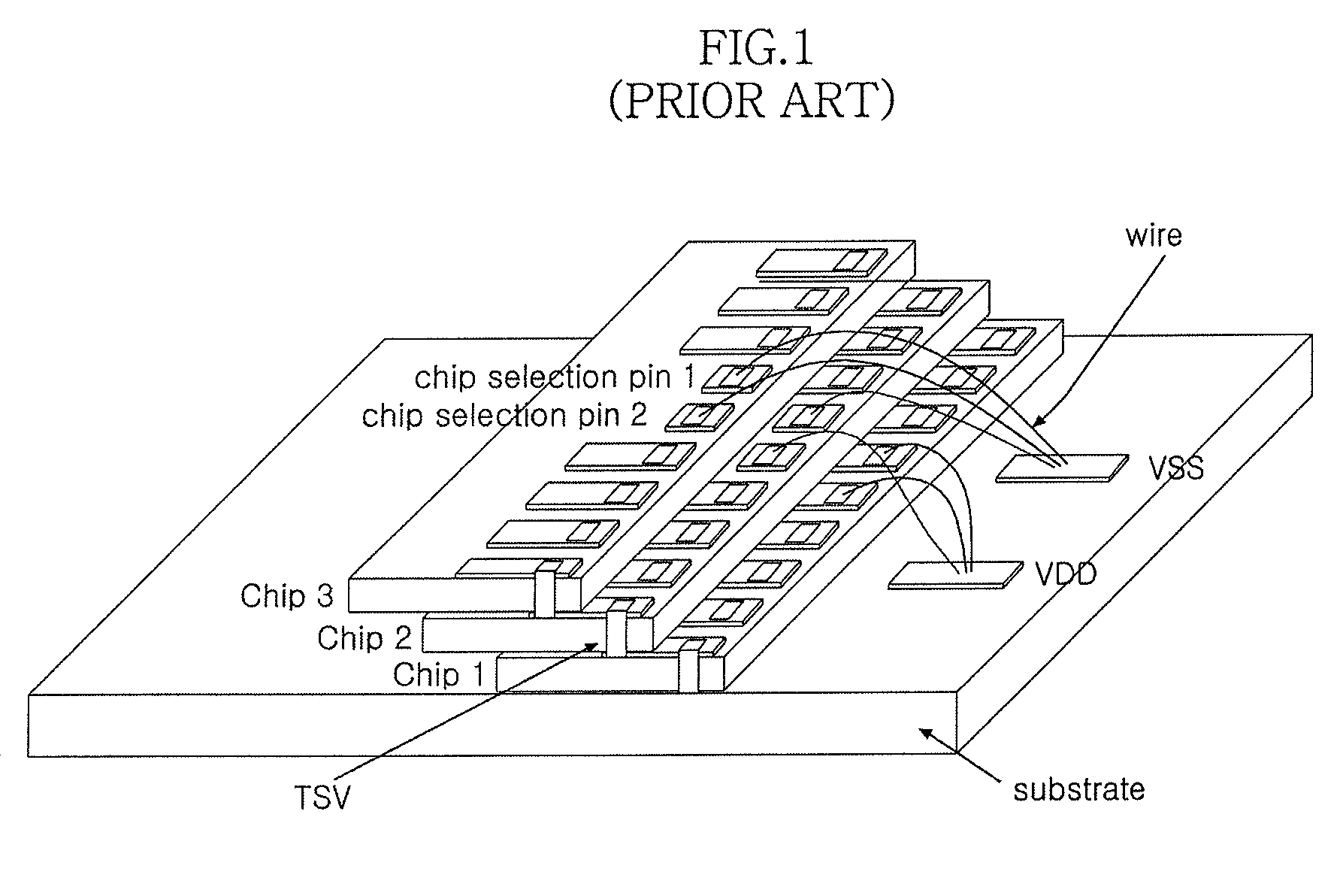

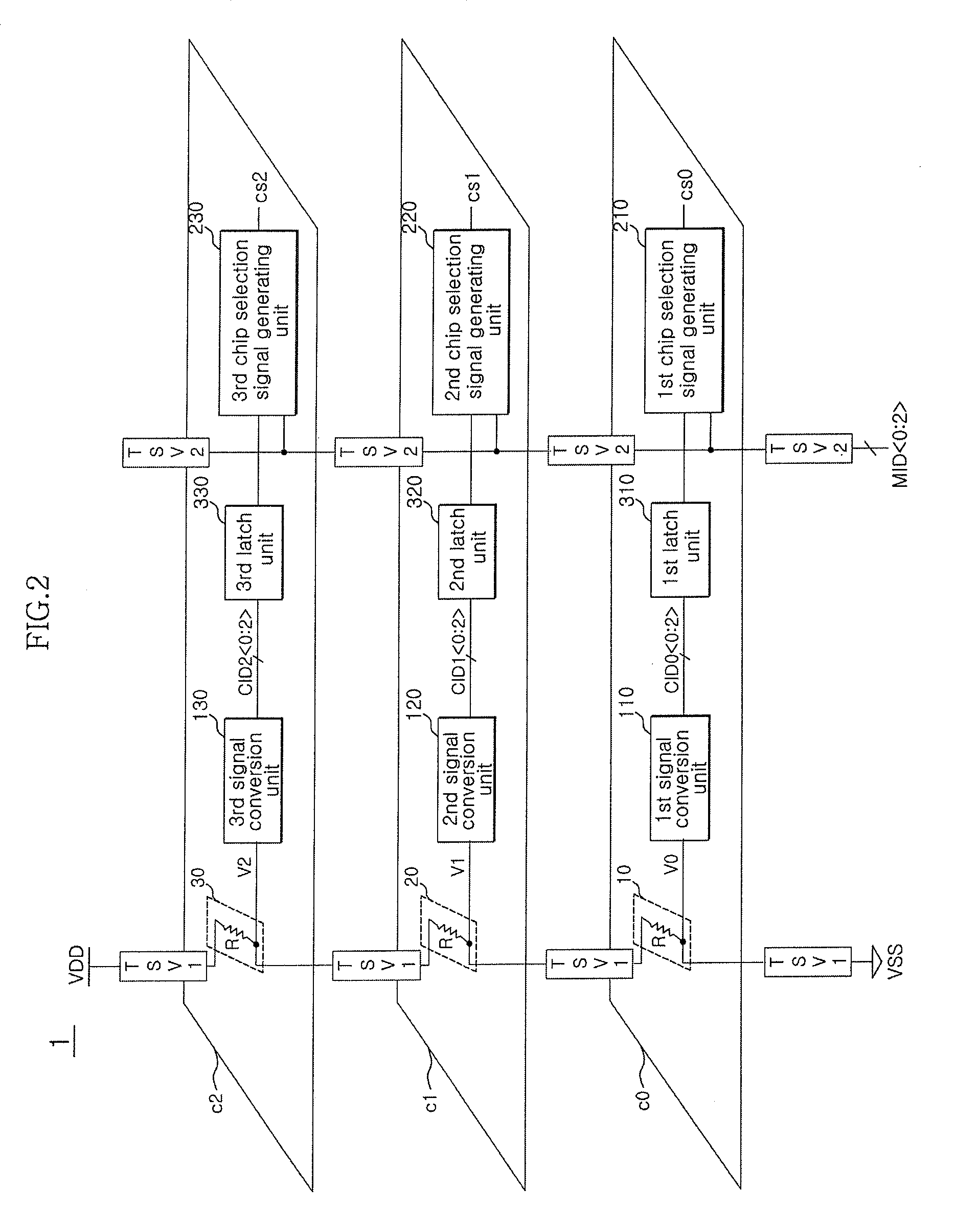

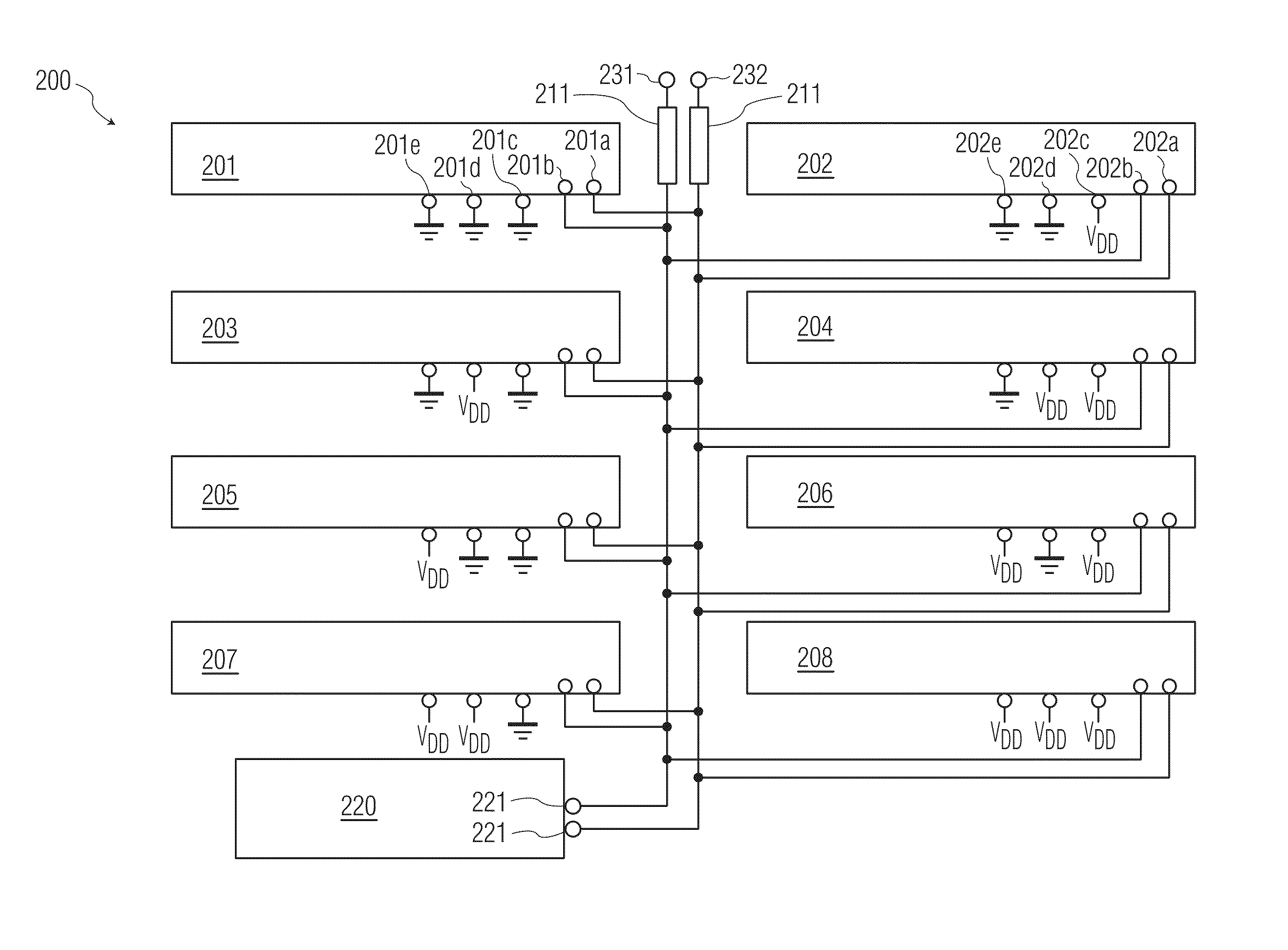

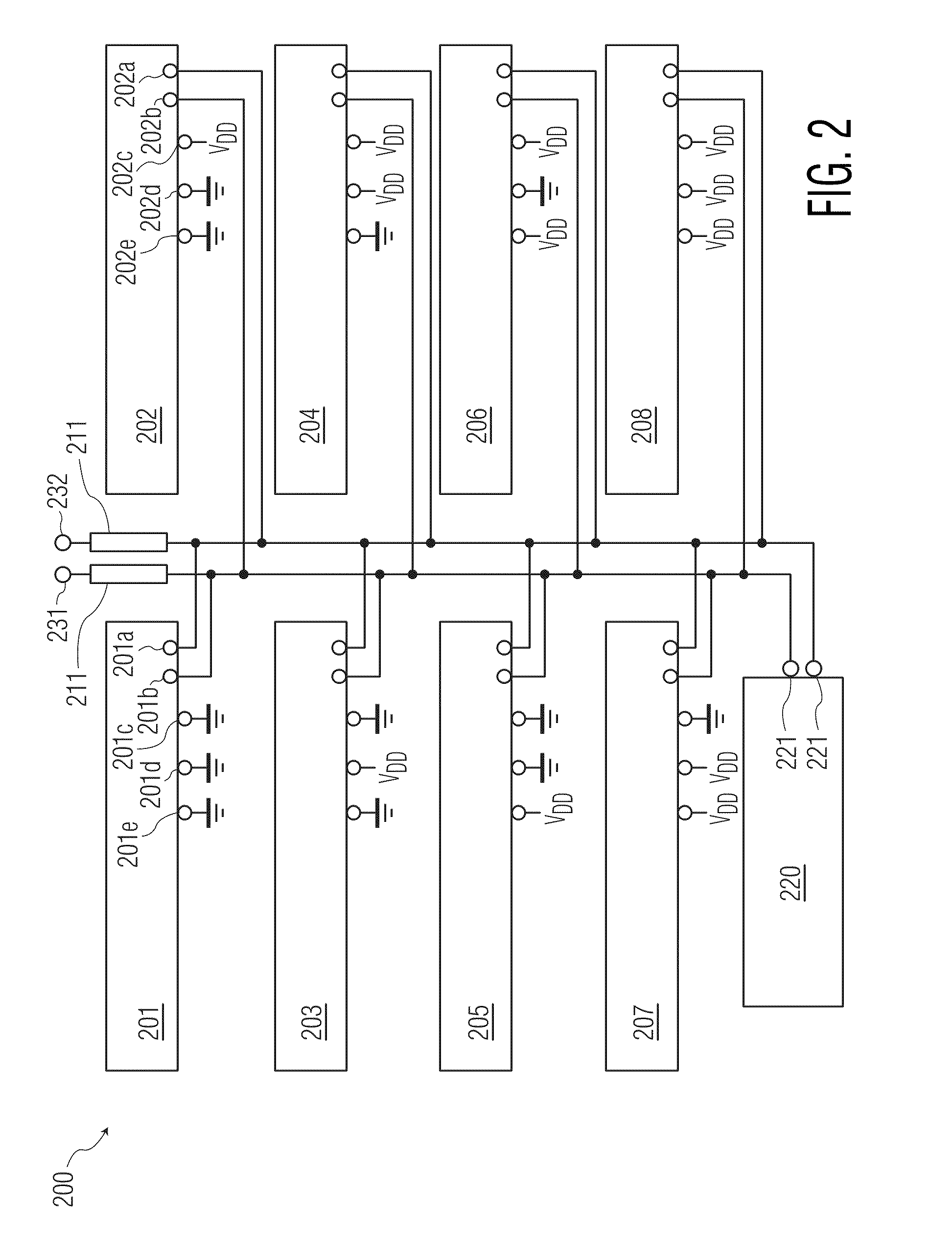

Semiconductor apparatus and chip selection method thereof

ActiveUS20110102065A1Impedence convertorsSemiconductor/solid-state device detailsChip selectEngineering

A semiconductor apparatus having a plurality of stacked chips includes: a plurality of latch units, each of which is disposed in a corresponding one of the plurality of chips and is configured to latch a clock signal and a frequency-divided signal at mutually different points of time to generate an chip identification signal of the corresponding one of the plurality of chips; and a plurality of chip selection signal generating units, each of which is disposed in the corresponding one of the plurality of chips and is configured to compare the chip identification signal of the corresponding one of the plurality of chips with a chip selection identification signal to generate a chip selection signal of the corresponding one of the plurality of chips, wherein the chip selection signal is configured to enable the corresponding one of the plurality of chips when the chip identification signal matches the chip selection identification signal.

Owner:SK HYNIX INC

Semiconductor apparatus and chip selection method thereof

InactiveUS8223523B2Impedence convertorsSemiconductor/solid-state device detailsVoltage dropEngineering

A semiconductor apparatus having a plurality of stacked chips includes: a through silicon via (TSV) configured to couple the plurality of chips together and configured to be coupled in series to a plurality of voltage drop units; a plurality of signal conversion units, each of which is configured to convert a voltage outputted from the voltage drop unit of the corresponding one of the plurality of chips to a digital code signal and provide the digital code signal as chip identification signal of the corresponding one of the plurality of chips; and a plurality of chip selection signal generating units, each of which is configured to compare the chip identification signal with a chip selection identification signal to generate a chip selection signal of the corresponding one of the plurality of chips.

Owner:SK HYNIX INC

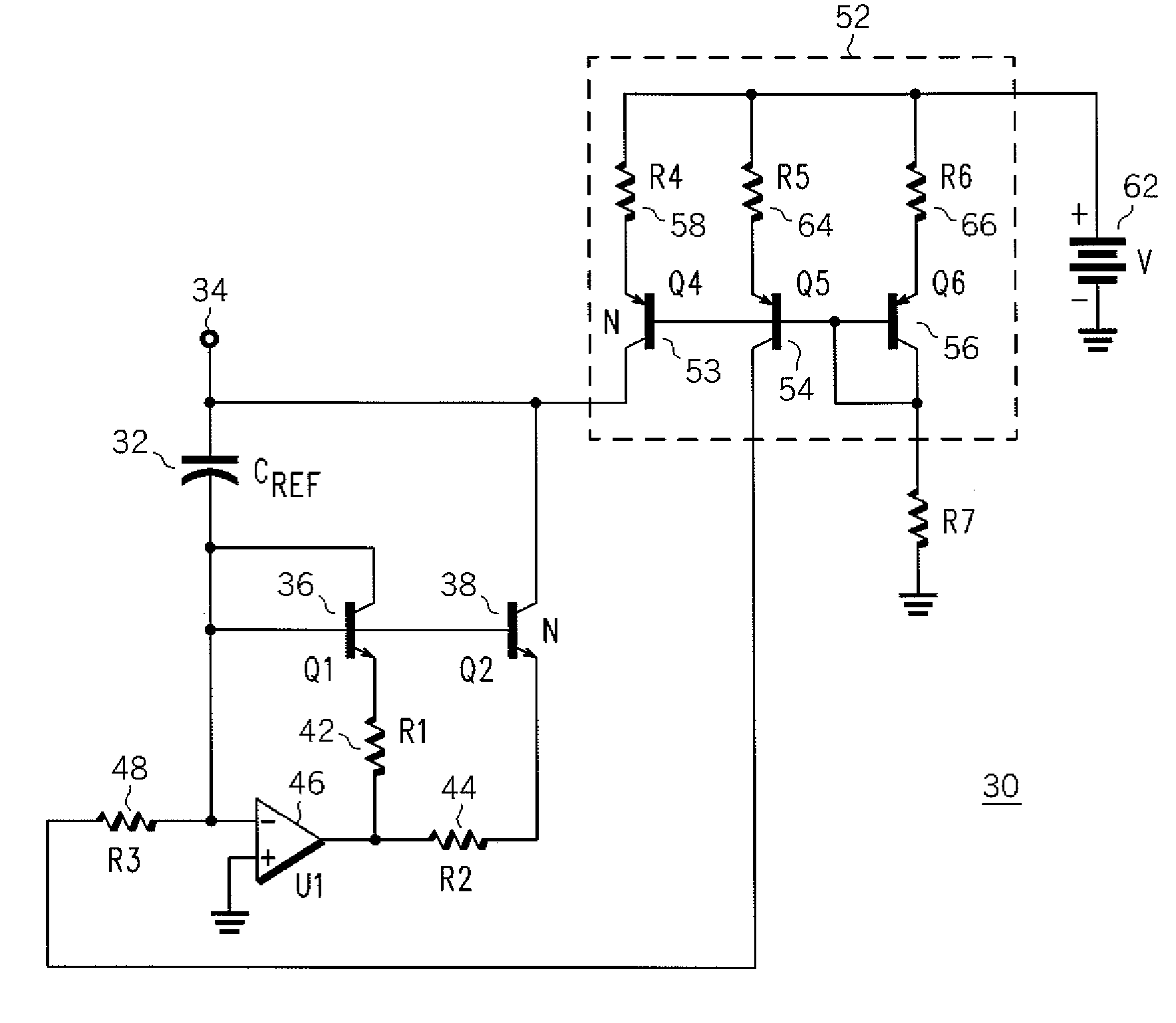

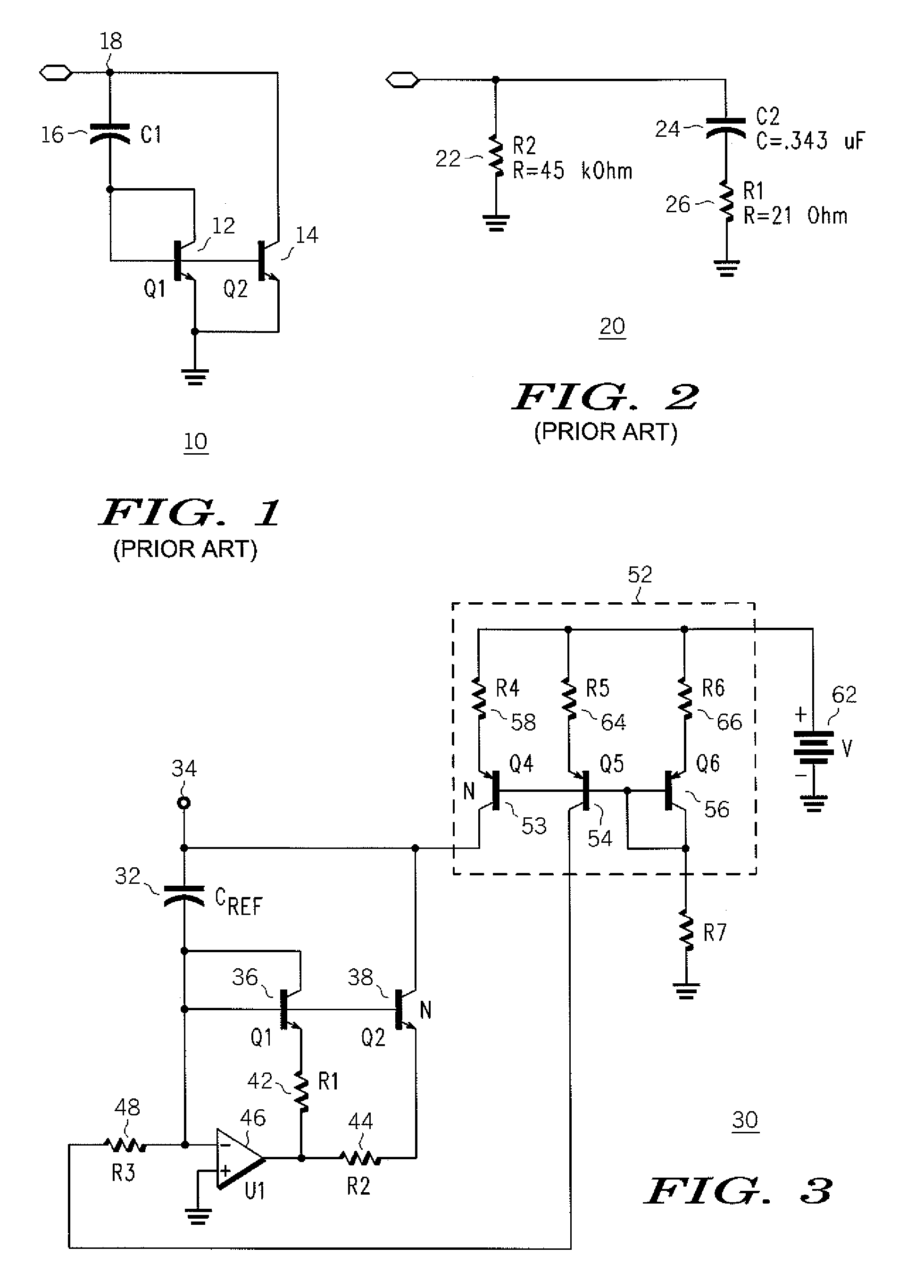

Capacitance multiplier circuit

An integrated circuit including a capacitance multiplier having reduced parasitics and injected noise compared to conventional multiplier methods. The integrated circuit includes a reference capacitor and a current mirror arrangement coupled to the reference capacitor. The current mirror arrangement, which includes a current gain factor N, varies the capacitance of the reference capacitor by a factor of N+1, based on the reference capacitor current. The current mirror arrangement includes an operational amplifier operating in conjunction with two mirror transistors to form a current mirror arrangement having little or no series resistance. The current mirror also can include a plurality of resistors configured to reduce the noise from the capacitance multiplier, thus making the capacitance multiplier useful for applications that may require relatively low noise.

Owner:INTEL CORP

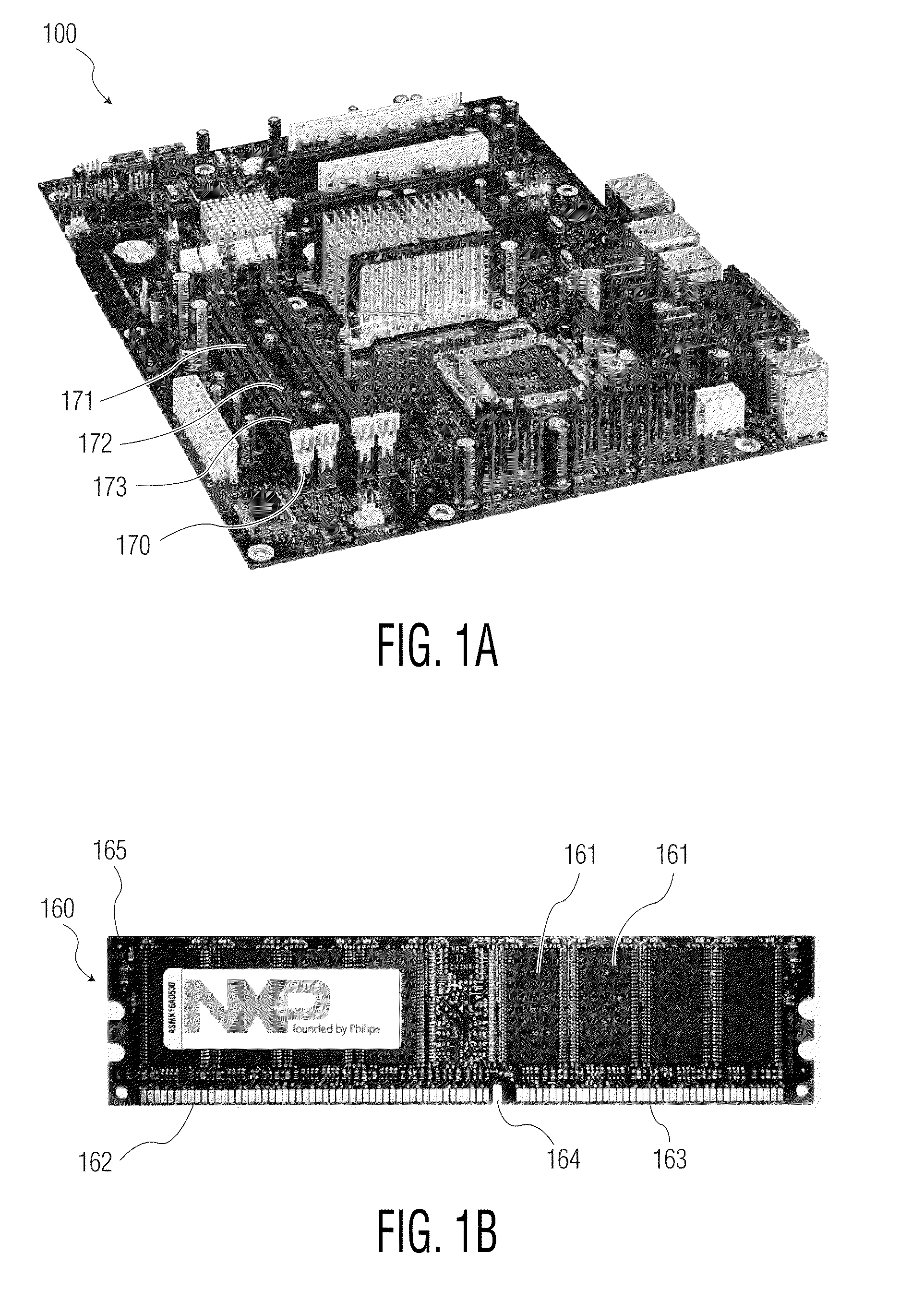

Clock generation for memory access without a local oscillator

A method of accessing electronic memory is provided in electronic circuits where it is desired to lower power consumption and hence there is no active oscillator at the time when access to data within the electronic memory is required. The invention provides a method therefore for accessing the electronic memory from a controller, which generates its own clock signals from a data, communications bus electrically coupled to the controller. Advantageously the method allows for memory access to be continued in integrated circuits where a subset of circuits are powered down to reduce power consumption, and one of the subset of circuits is an oscillator.

Owner:NXP BV

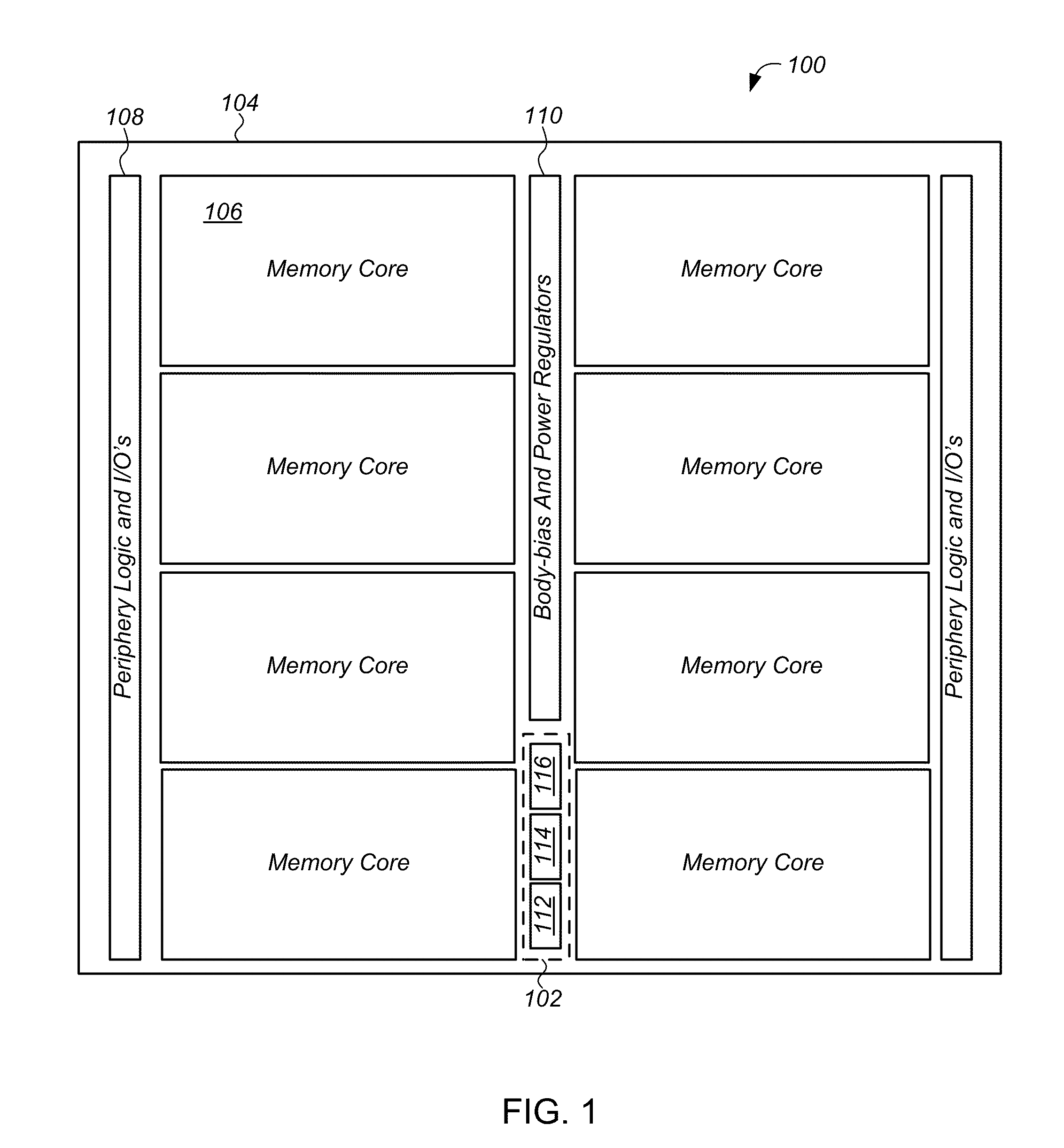

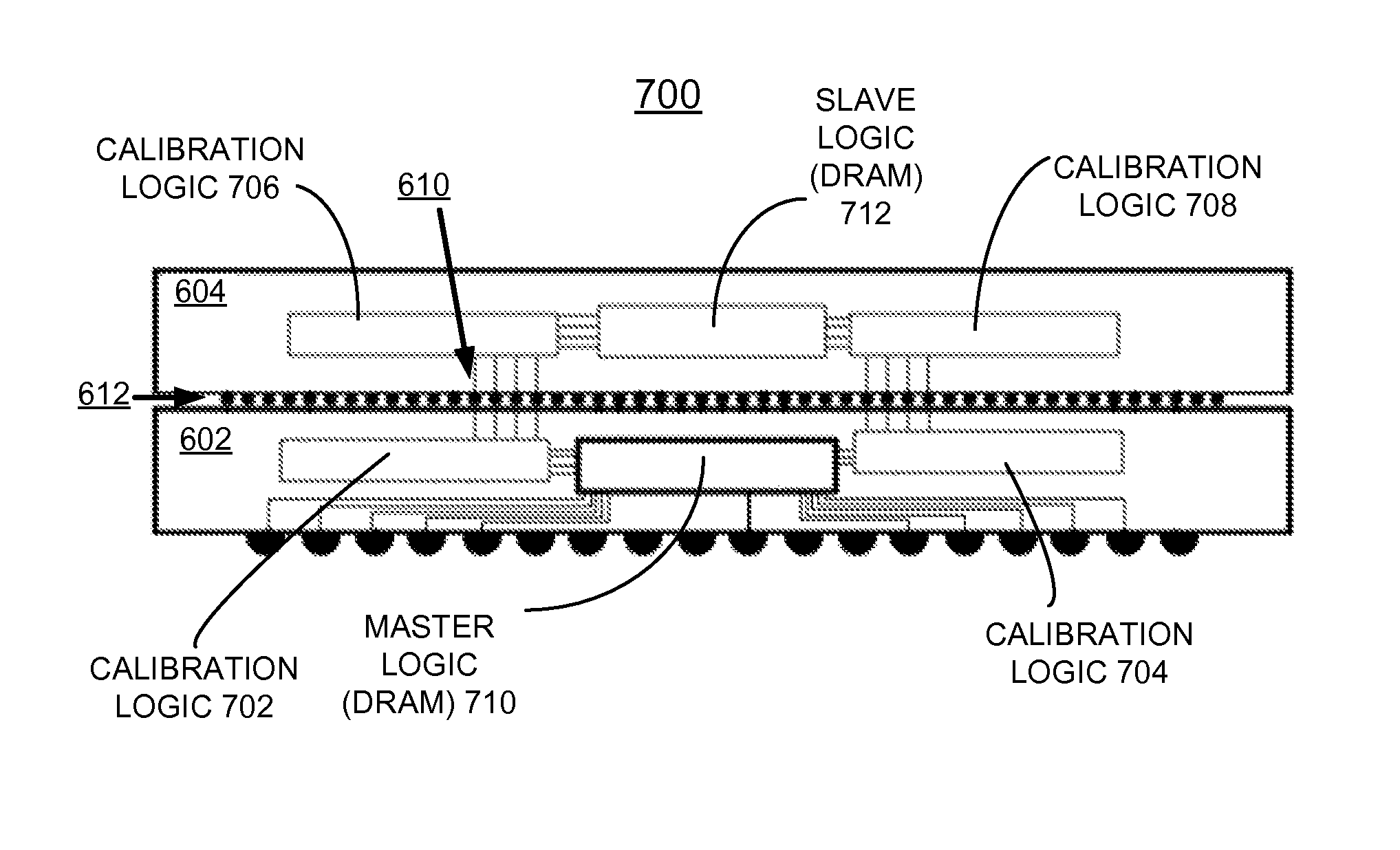

Implementing chip to chip calibration within a TSV stack

ActiveUS8692561B2Overcome disadvantagesImprove reliability and performanceImpedence convertorsSolid-state devicesSemiconductor chipEngineering

A method and circuit for implementing a chip to chip calibration in a chip stack, for example, with through silicon vias (TSV) stack, and a design structure on which the subject circuit resides are provided. A first chip and a second chip are included within a semiconductor chip stack. The semiconductor chip stack includes a vertical stack optionally provided with Though Silicon Via (TSV) stacking of the chips. At least one of the first chip and the second chip includes a calibration control circuit and a performance indicator circuit coupled to the calibration control circuit to train and calibrate at least one of the first chip and the second chip to provide enhanced performance and reliability for the semiconductor chip stack.

Owner:INT BUSINESS MASCH CORP

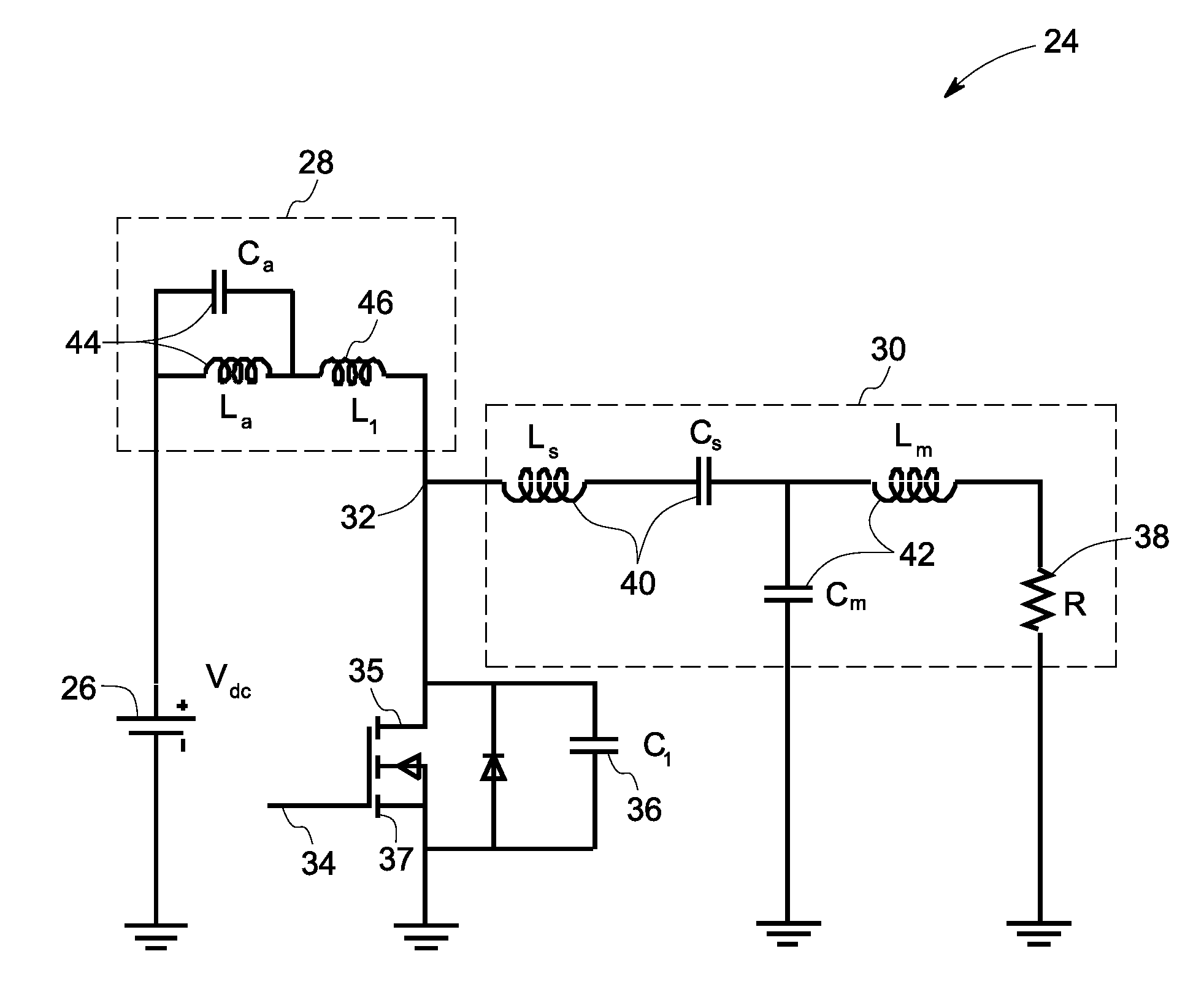

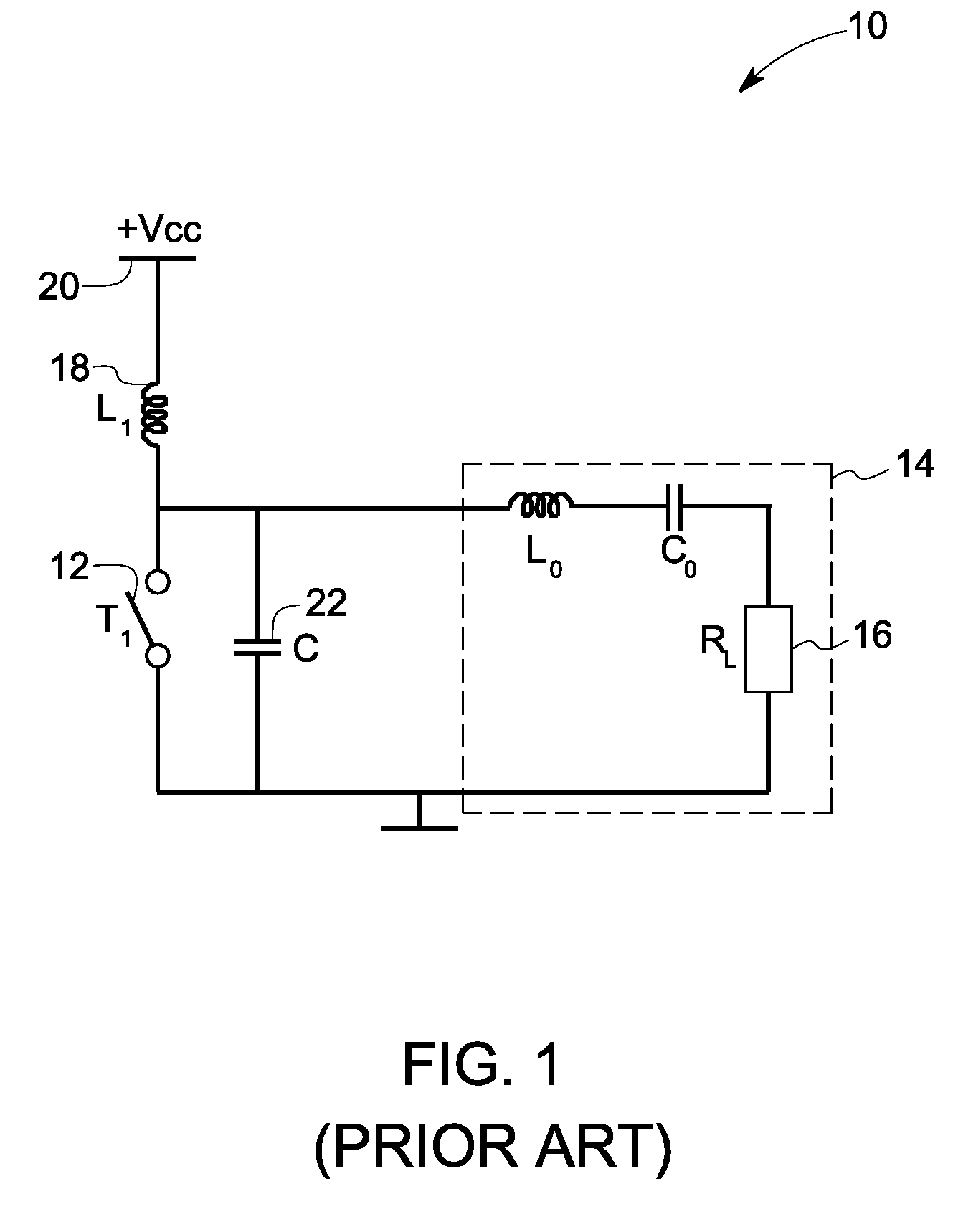

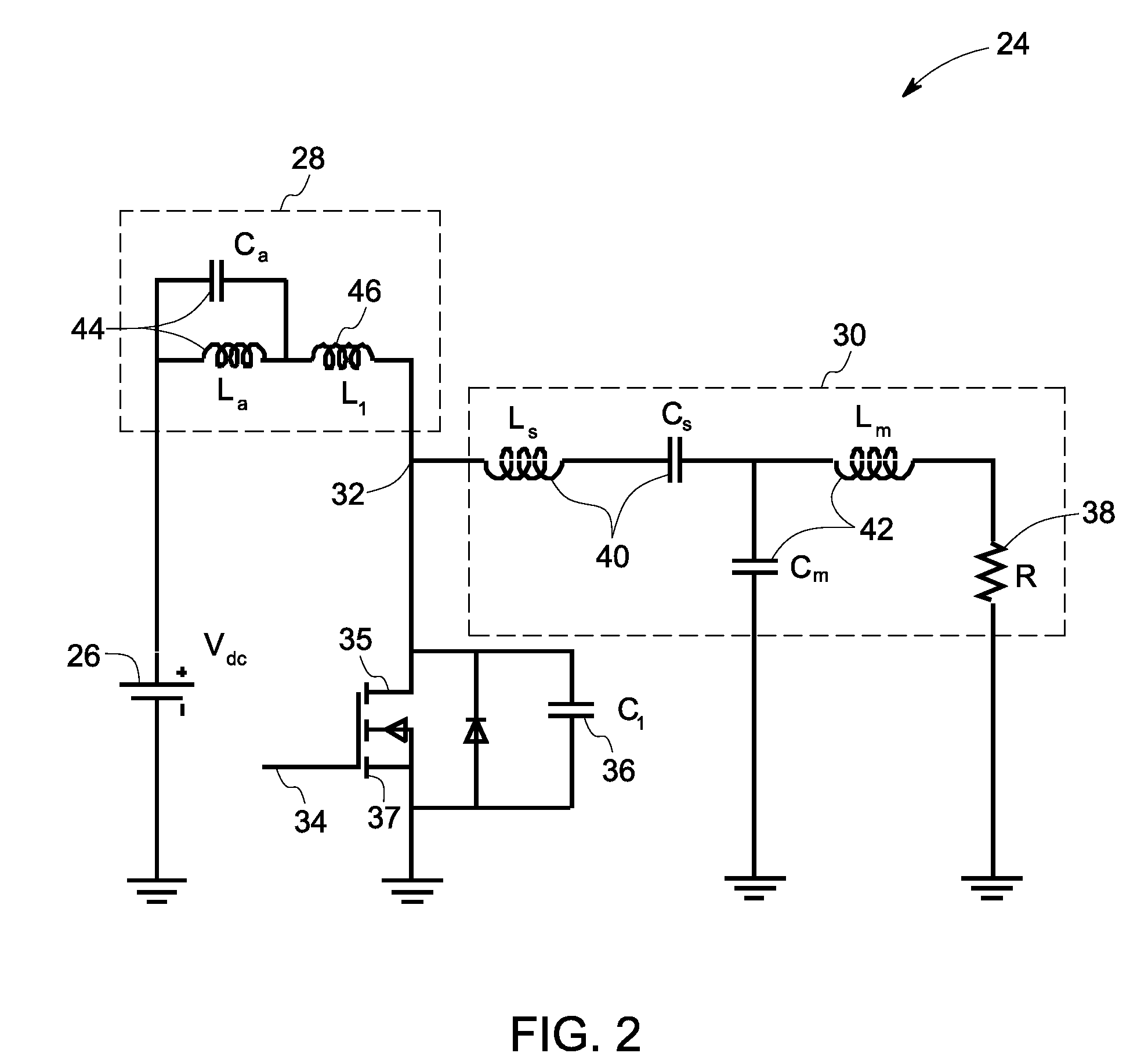

Class-e amplifier and lighting ballast using the amplifier

InactiveUS20100141168A1Impedence convertorsAmplifiers wit coupling networksAudio power amplifierElectrical ballast

An amplifier comprises a power source, a load network comprising a load and a resonance circuit, an input branch having a first end electrically coupled to the power source and a second end electrically coupled to the load network, and an active switch having one terminal electrically coupled to the second end of the input branch. The input branch including at least one parallel-LC-circuit configured to provide an infinitely large impedance at harmonics of a determined order.

Owner:GENERAL ELECTRIC CO

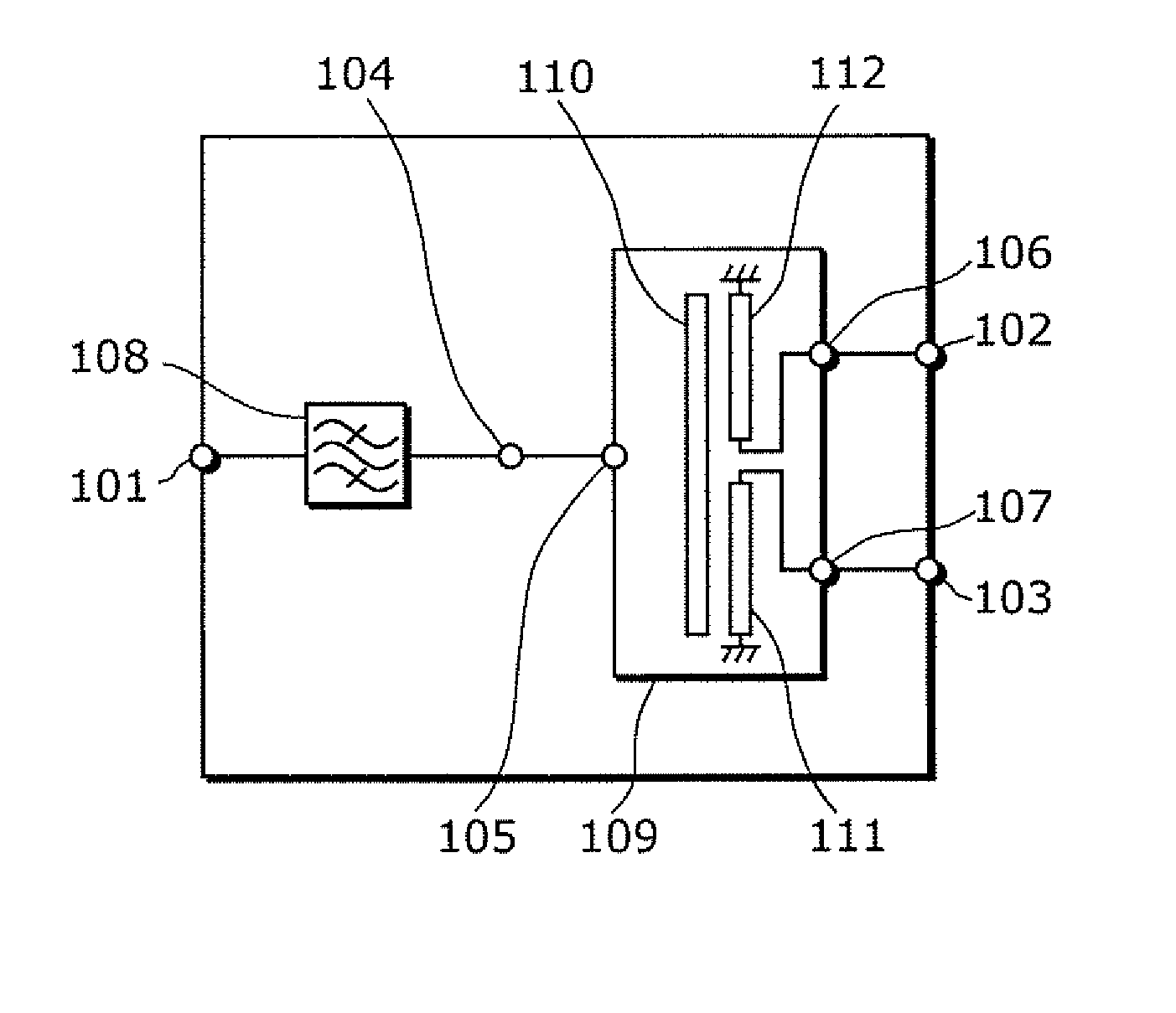

Fbar Filter

An FBAR filter added with a balance-unbalance conversion function is provided. The FBAR filter includes: an FBAR filter device having two unbalanced terminals, and which performs filtering of a signal between such terminals; and a balance-unbalance converter having one unbalanced terminal and one pair of balanced terminals, and which performs balance-unbalance conversion of the signal. The unbalanced terminal and the unbalanced terminal are connected, and filtering and balance-unbalance conversion of the signal is performed between the unbalanced terminal and the balanced terminals. The characteristics of the FBAR filter device are brought forth in the filtering of the signal. The FBAR filter device 108 and the balance-unbalance converter are integrated, and provided as a single component which is compact and low-cost,

Owner:PANASONIC CORP

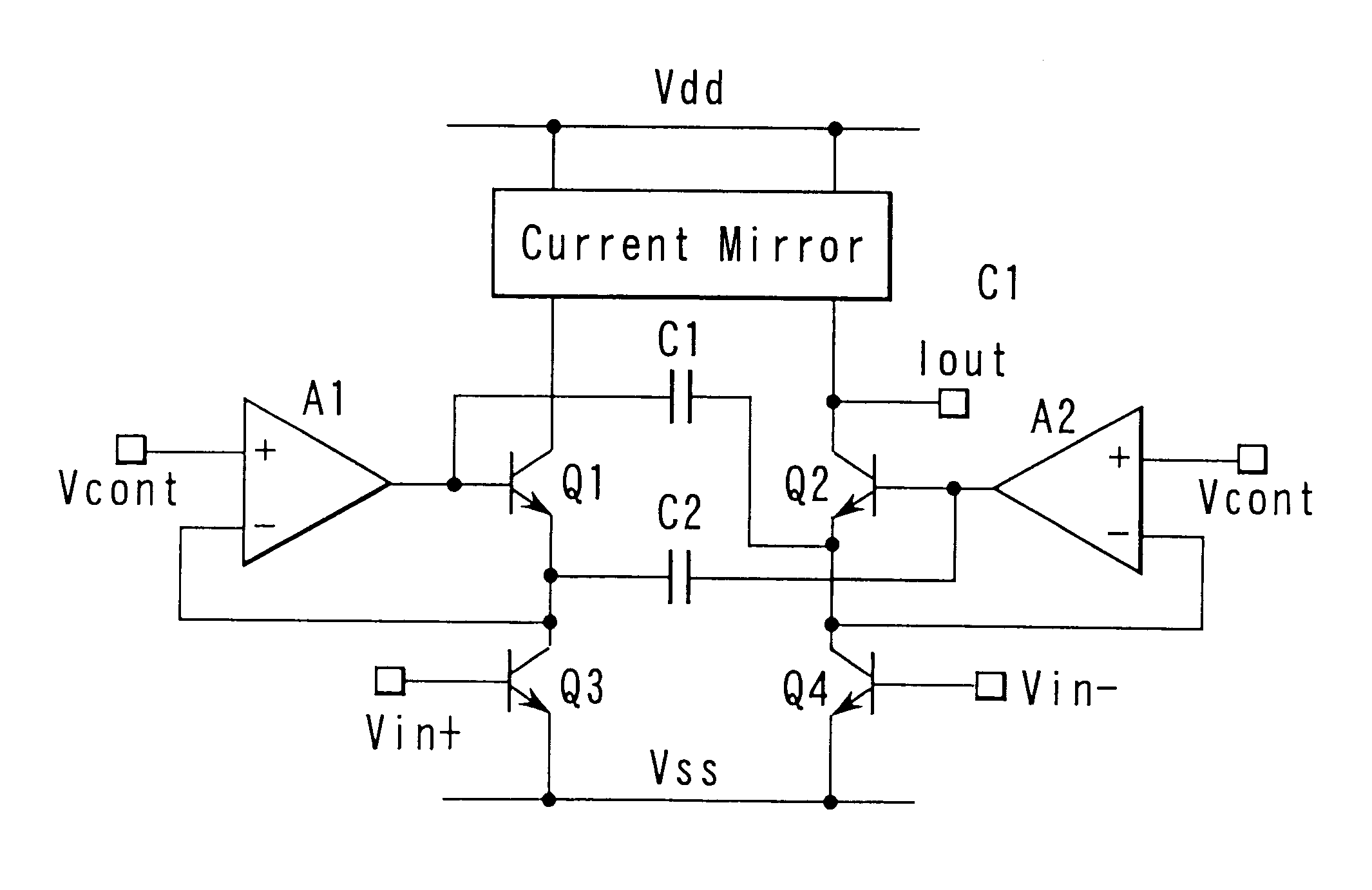

Impedance conversion circuit

There is disclosed an impedance conversion circuit called a regulated cascode circuit in which a parasitic capacity deteriorating frequency characteristics is reduced during operation up to about several hundreds of megahertz or higher frequencies. In the impedance conversion circuit comprising two regulated cascode circuits in which active elements and reverse amplifiers are interconnected with a feedback applied thereto, a capacity element is disposed between a control end of one active element and an output end of the other active element.

Owner:KK TOSHIBA

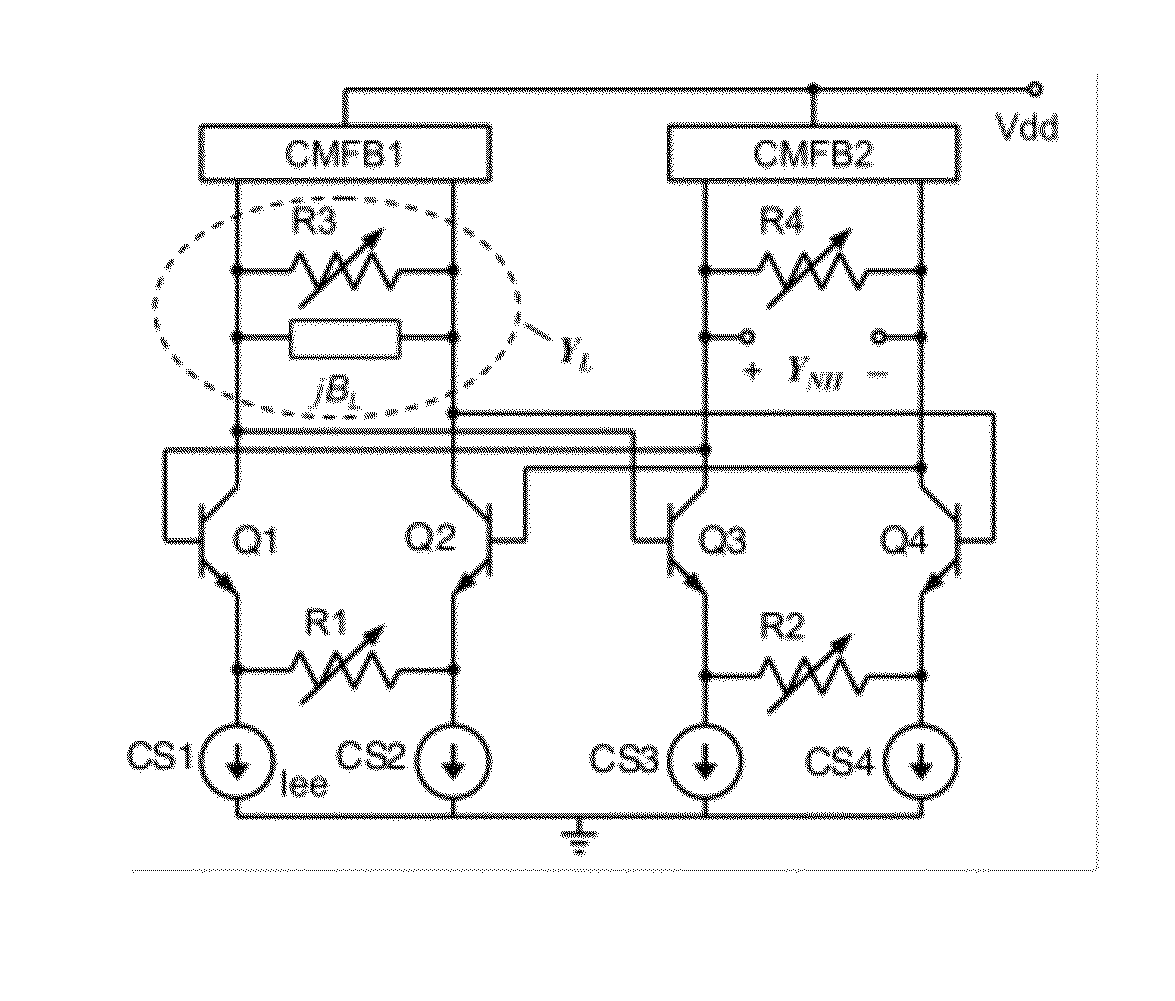

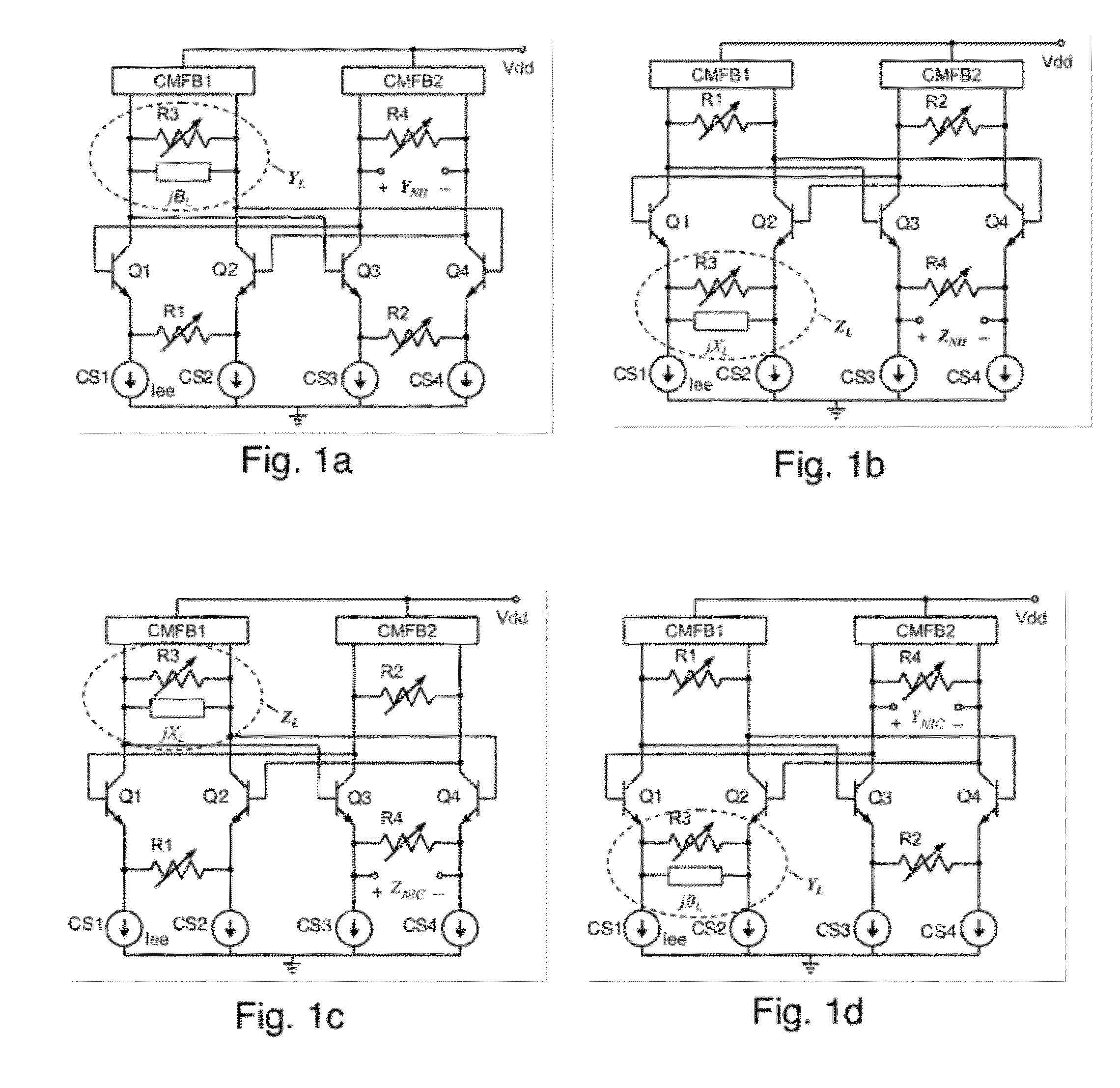

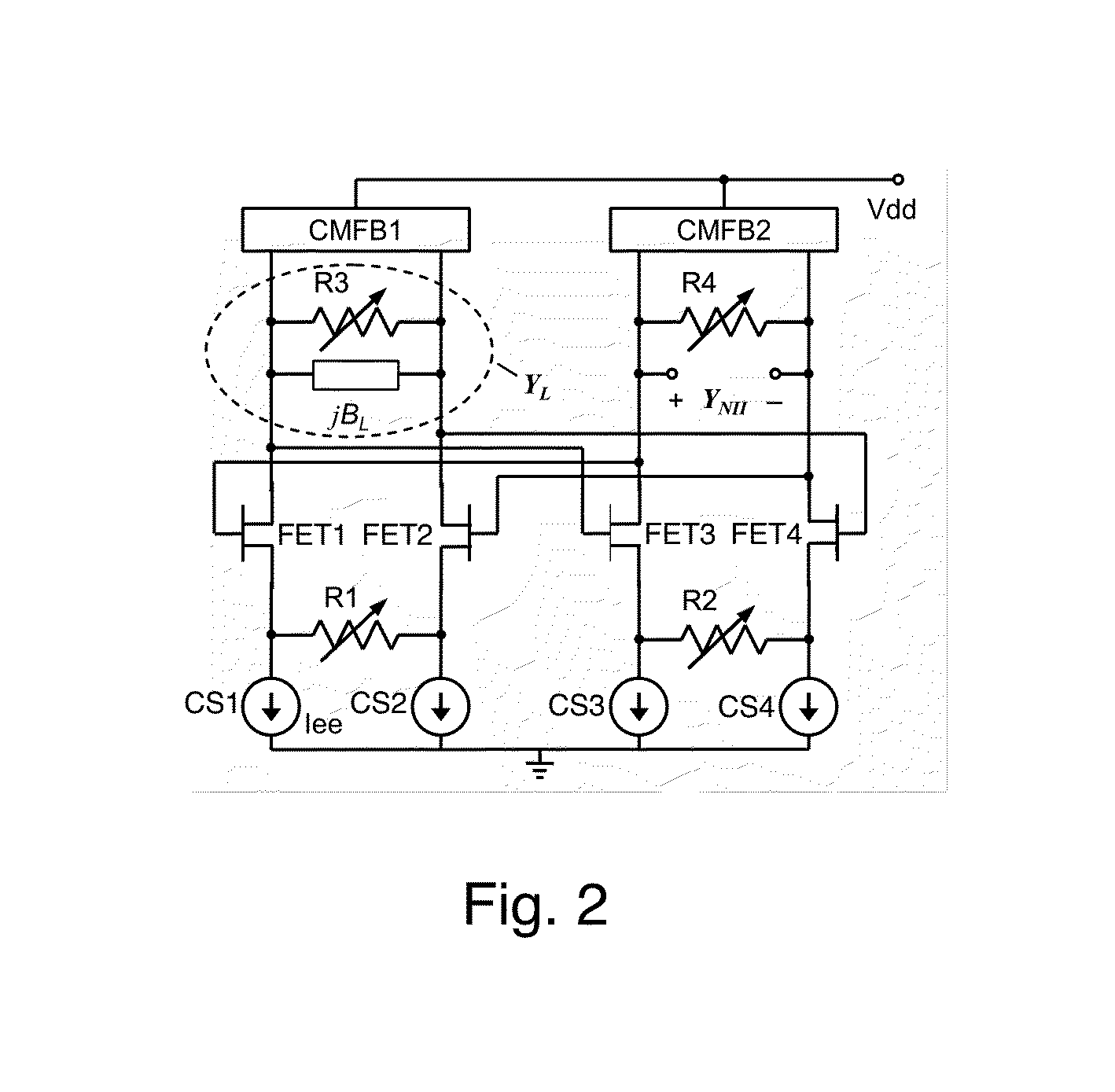

Differential negative impedance converters and inverters with variable or tunable conversion ratios

ActiveUS8988173B2Reduce parasitismImprove matchImpedence convertorsNetwork simulating reactancesCapacitanceEngineering

A differential circuit topology that produces a tunable floating negative inductance, negative capacitance, negative resistance / conductance, or a combination of the three. These circuits are commonly referred to as “non-Foster circuits.” The disclosed embodiments of the circuits comprises two differential pairs of transistors that are cross-coupled, a load immittance, multiple current sources, two Common-Mode FeedBack (CMFB) networks, at least one tunable (variable) resistance, and two terminals across which the desired immittance is present. The disclosed embodiments of the circuits may be configured as either a Negative Impedance Inverter (NII) or a Negative Impedance Converter (NIC) and as either Open-Circuit-Stable (OCS) and Short-Circuit-Stable (SCS).

Owner:HRL LAB

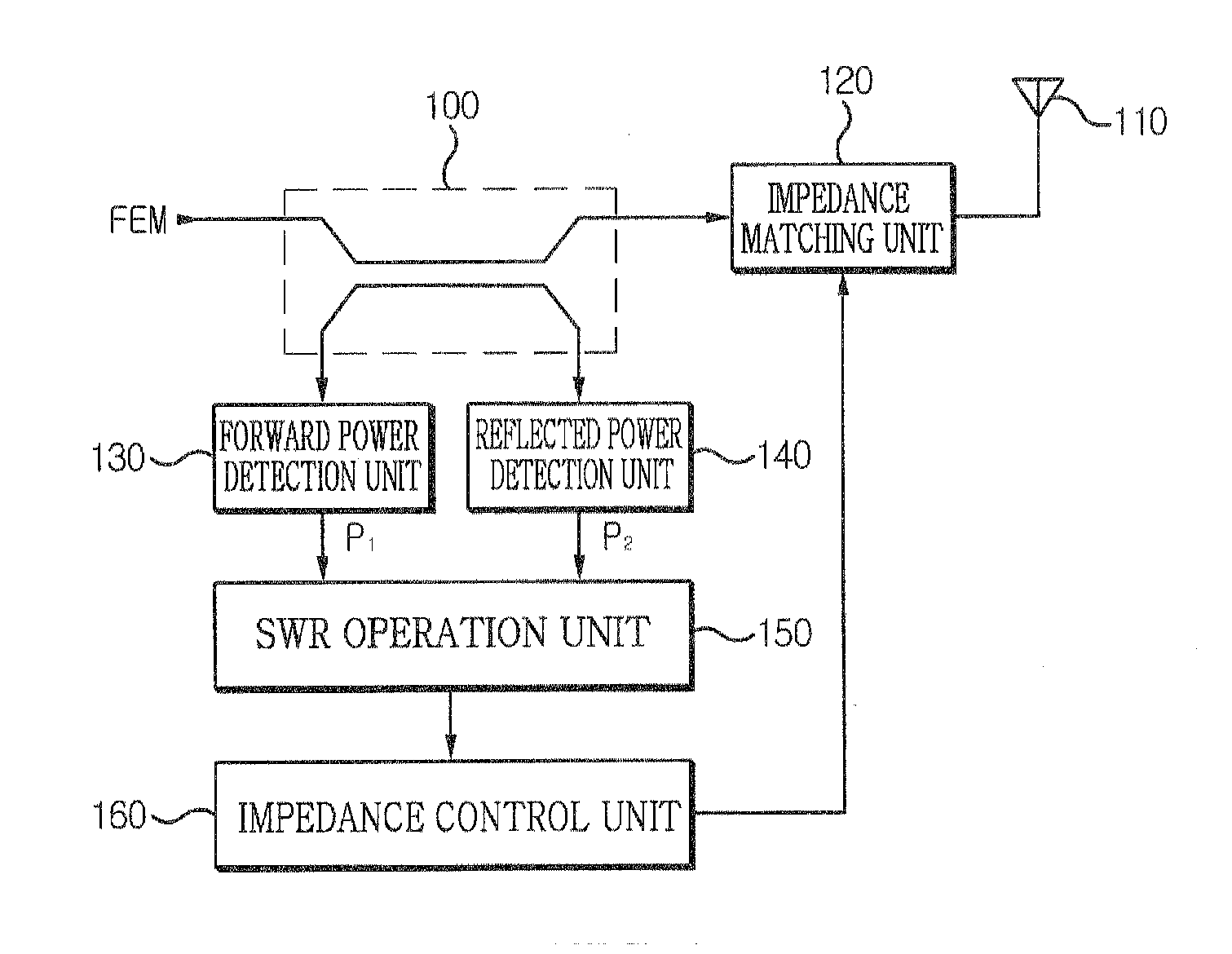

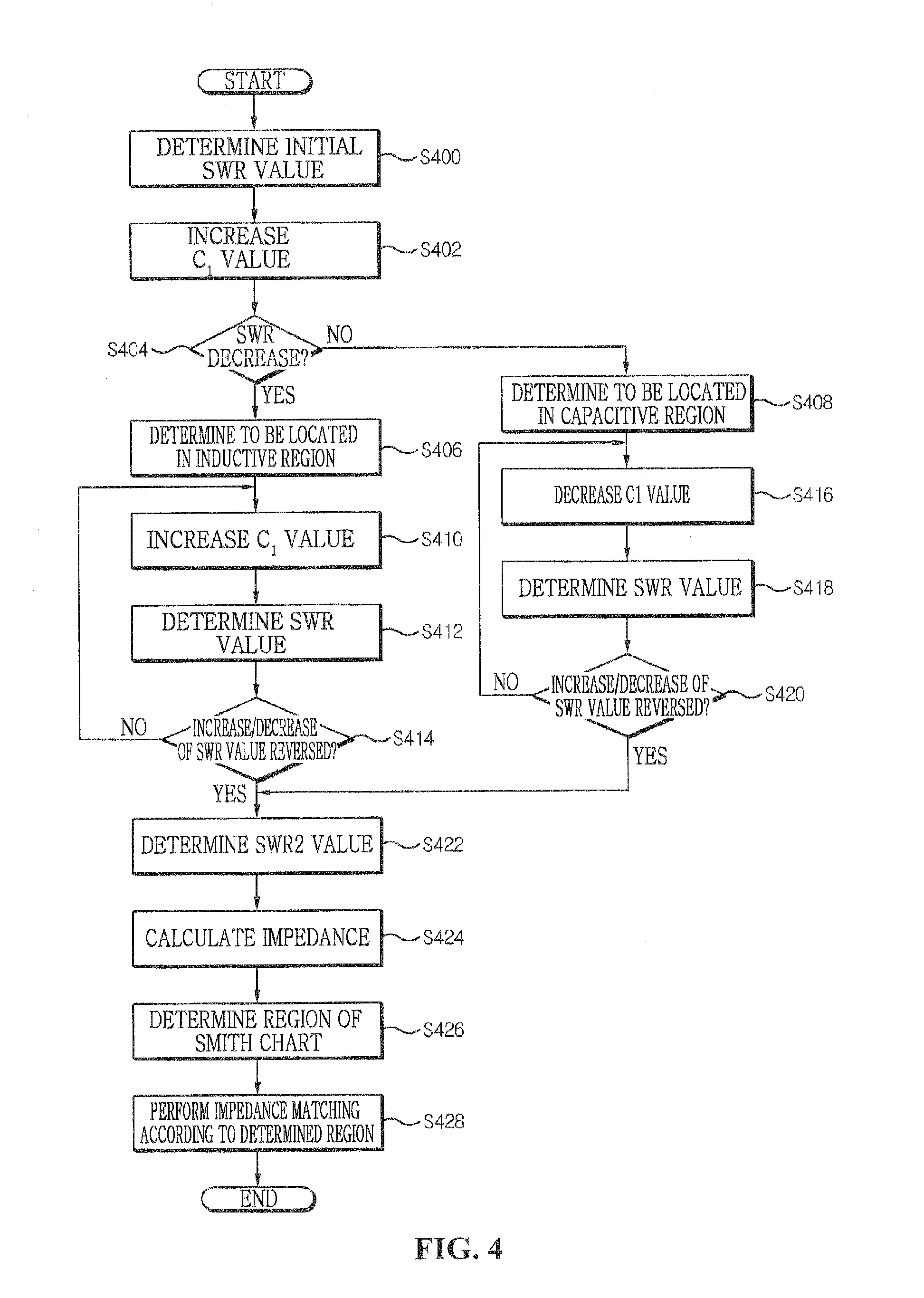

Apparatus and method for matching impedance using standing wave ratio information

An apparatus and method for matching impedance of an antenna by using Standing Wave Ratio (SWR) information is provided. While the impedance of the impedance matching unit is controlled, a region of a Smith chart in which initial total impedance of the impedance matching unit and the antenna is located by using an SWR calculated by an SWR operation unit, and the impedance of the impedance matching unit is controlled according to the determined region, thus correctly matching the impedance of the antenna.

Owner:KOREA ADVANCED INST OF SCI & TECH +1

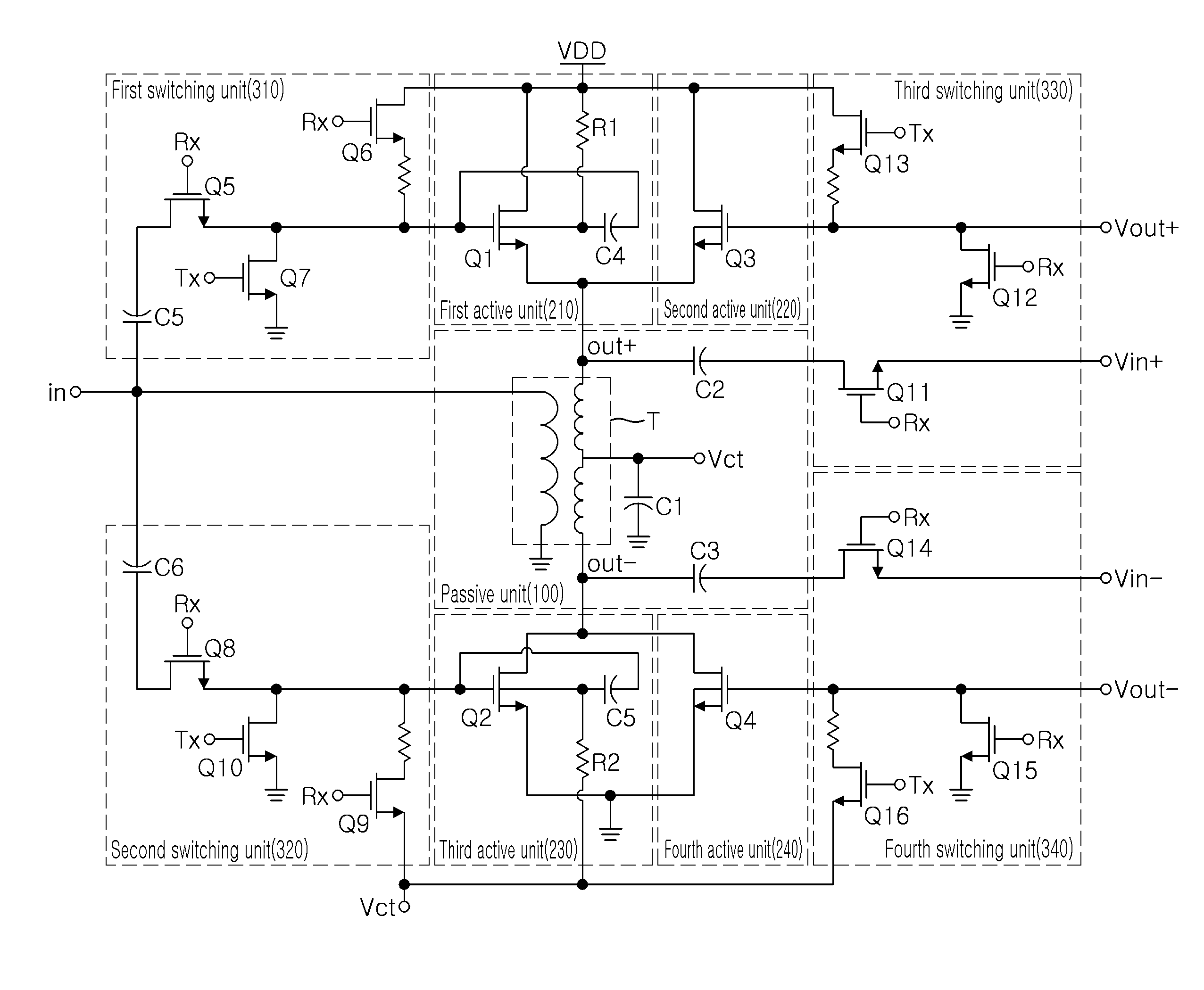

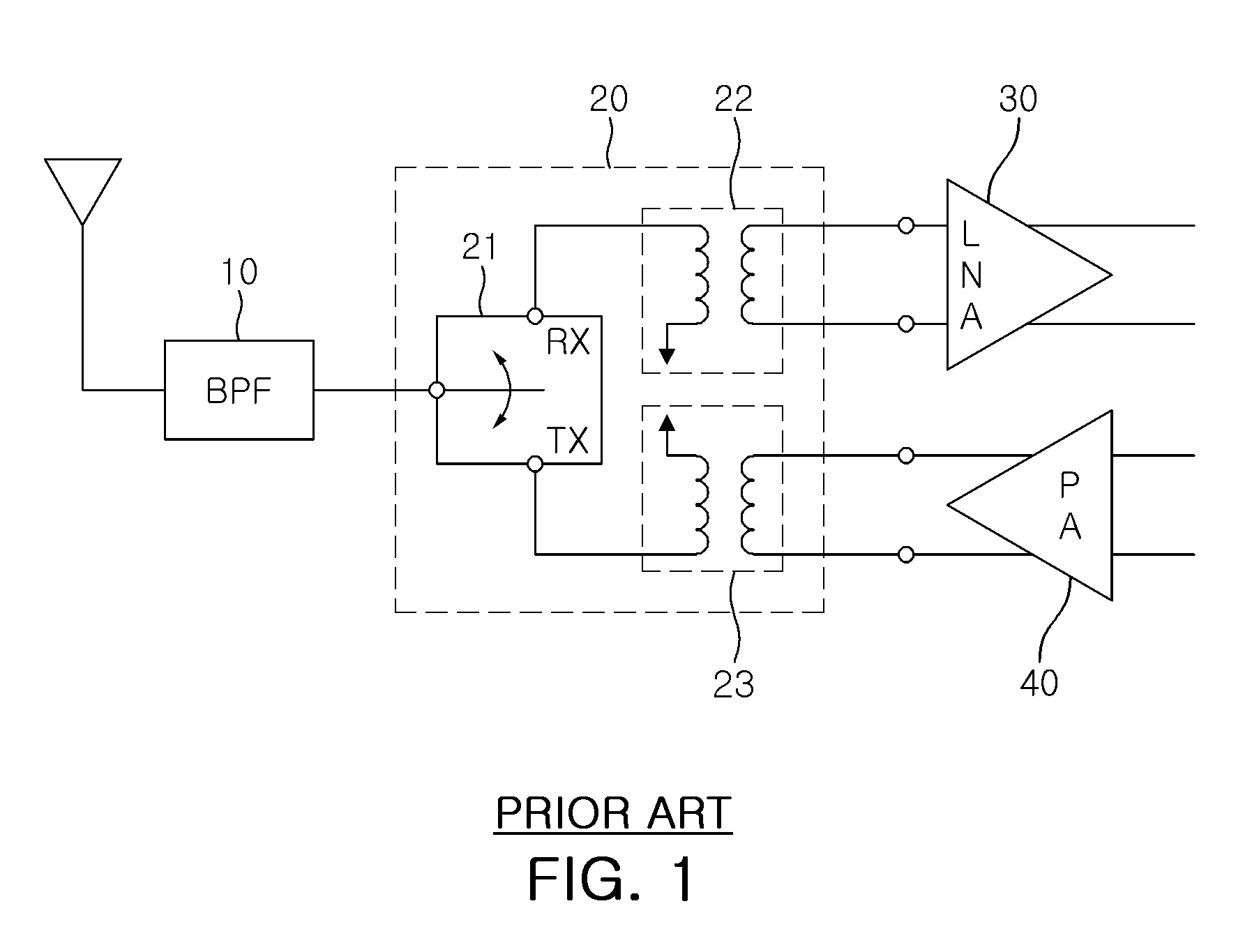

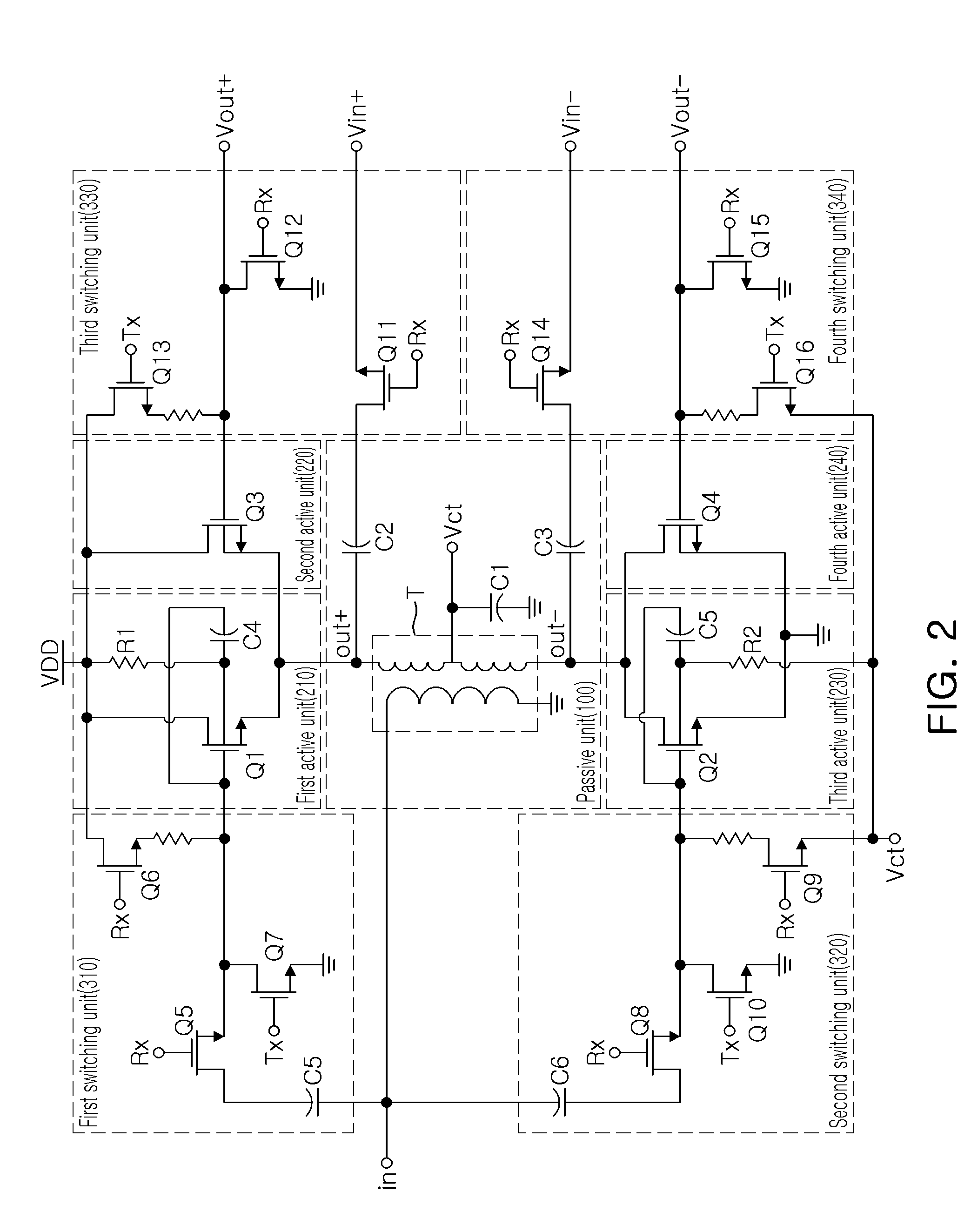

Hybrid balun apparatus

A hybrid balun apparatus are disclosed. The hybrid balun apparatus can support both the reception mode and the transmission mode and be advantageous for a high level of integration, by replacing two transformers disposed at a reception path and a transmission path with a single transformer and integrating a T / R switch and a balun into a one chip. Therefore, an IC according to integration extends to a front stage of an antenna to facilitate interfacing between elements, and a burden for designing at a rear stage (i.e., LNA in the reception mode, and PA in the transmission mode) can be reduced.

Owner:ELECTRONICS & TELECOMM RES INST

Popular searches

Cathode-ray tube indicators Input/output processes for data processing Organic semiconductor devices Analogue adaptive filters Semiconductor/solid-state device manufacturing Digital storage Oscillations generators Semiconductor devices Electric pulse generator Logic circuit coupling/interface arrangements