Patents

Literature

48 results about "Capacitance multiplier" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A capacitance multiplier is designed to make a capacitor function like a capacitor that is much larger. This can be achieved in at least two ways. Capacitor multipliers make low-frequency filter and long-duration timing circuits possible that would be impractical with actual capacitors. Another application is in DC power supplies where very low ripple voltage (under load) is of paramount importance, such as in class-A amplifiers.

System and method for varying low audio frequencies inversely with audio signal level

InactiveUS7016509B1Increase contentEasy to removeCombination control in untuned amplifierAutomatic tone/bandwidth controlCapacitanceResistance capacitance

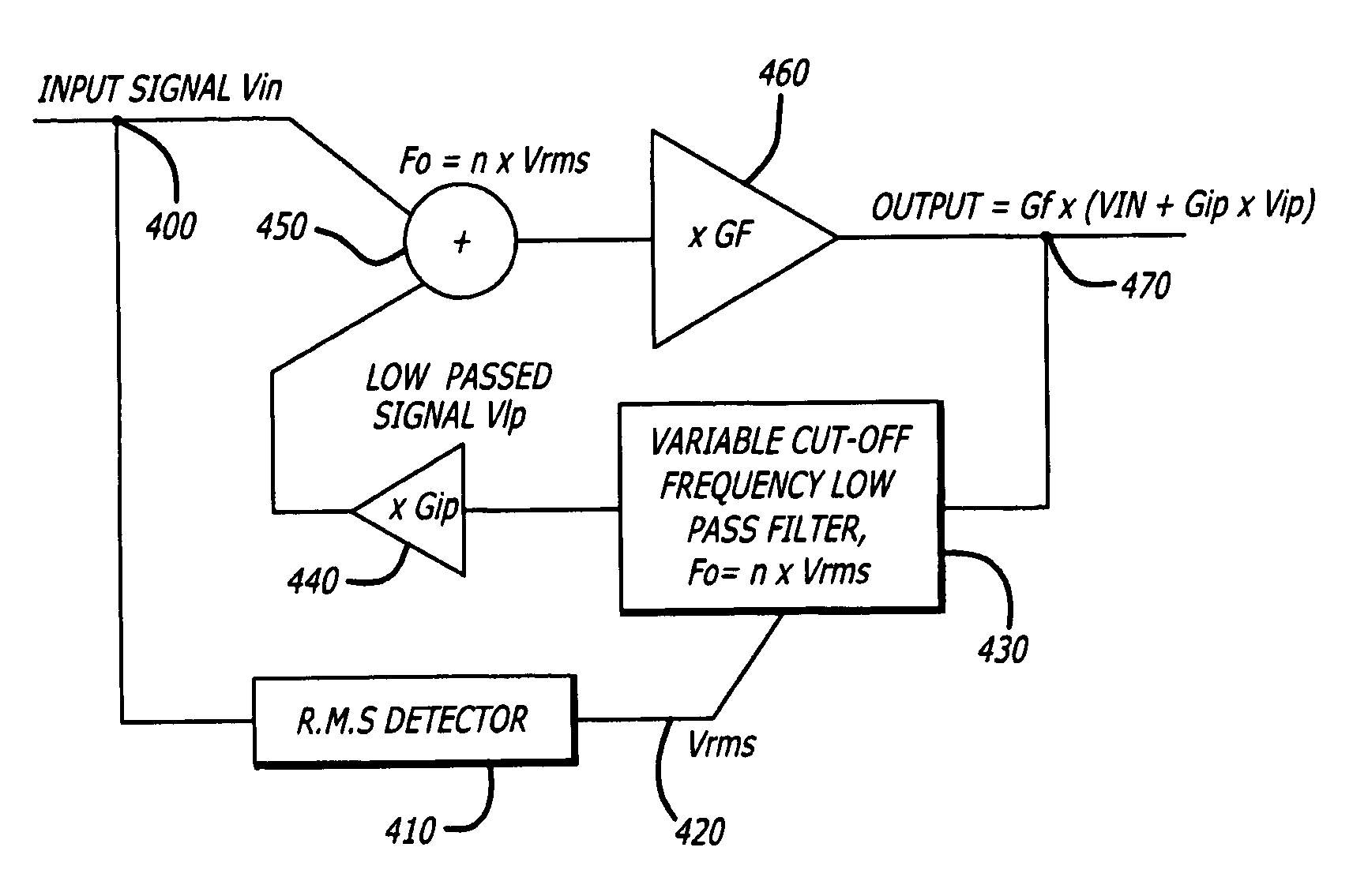

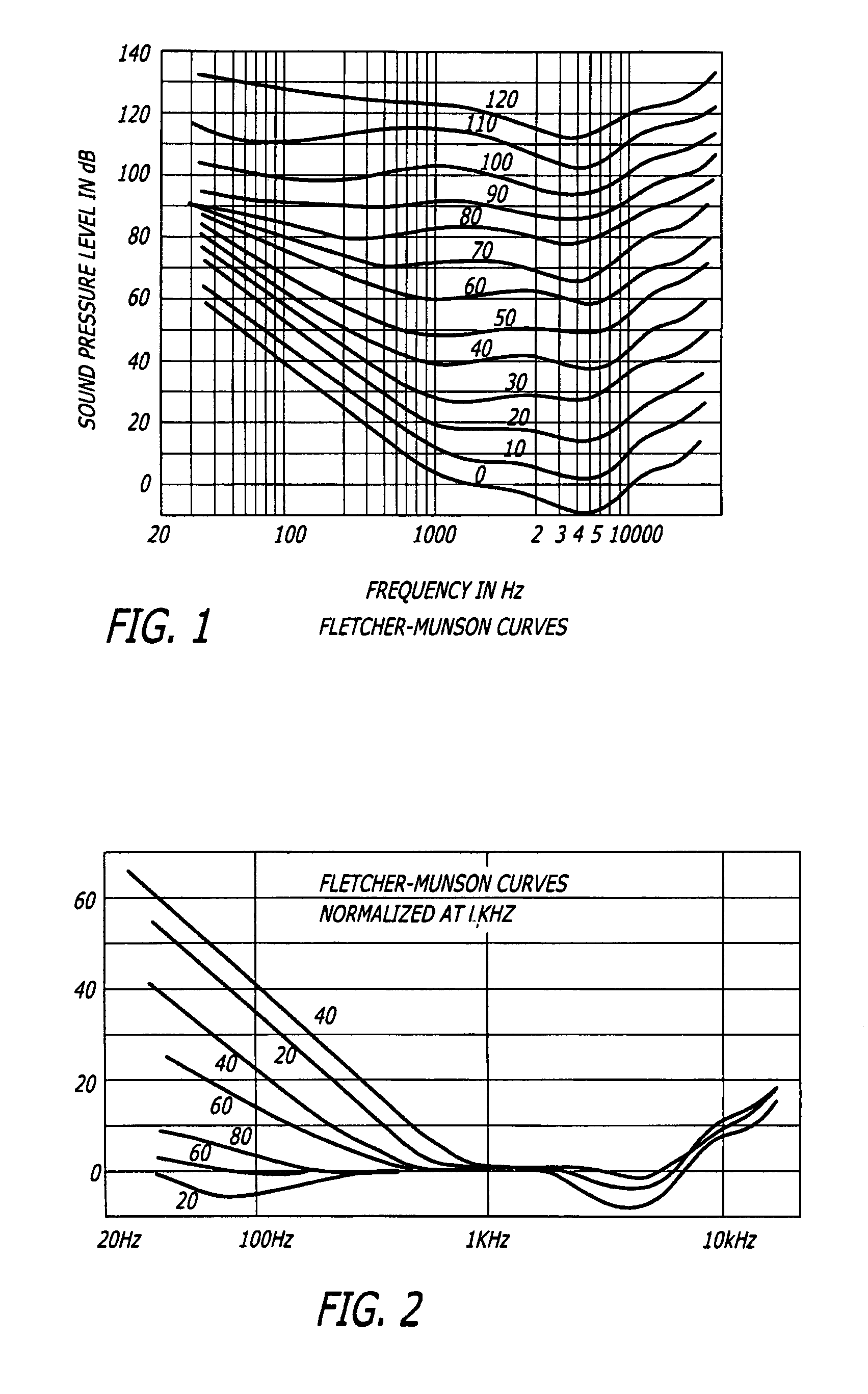

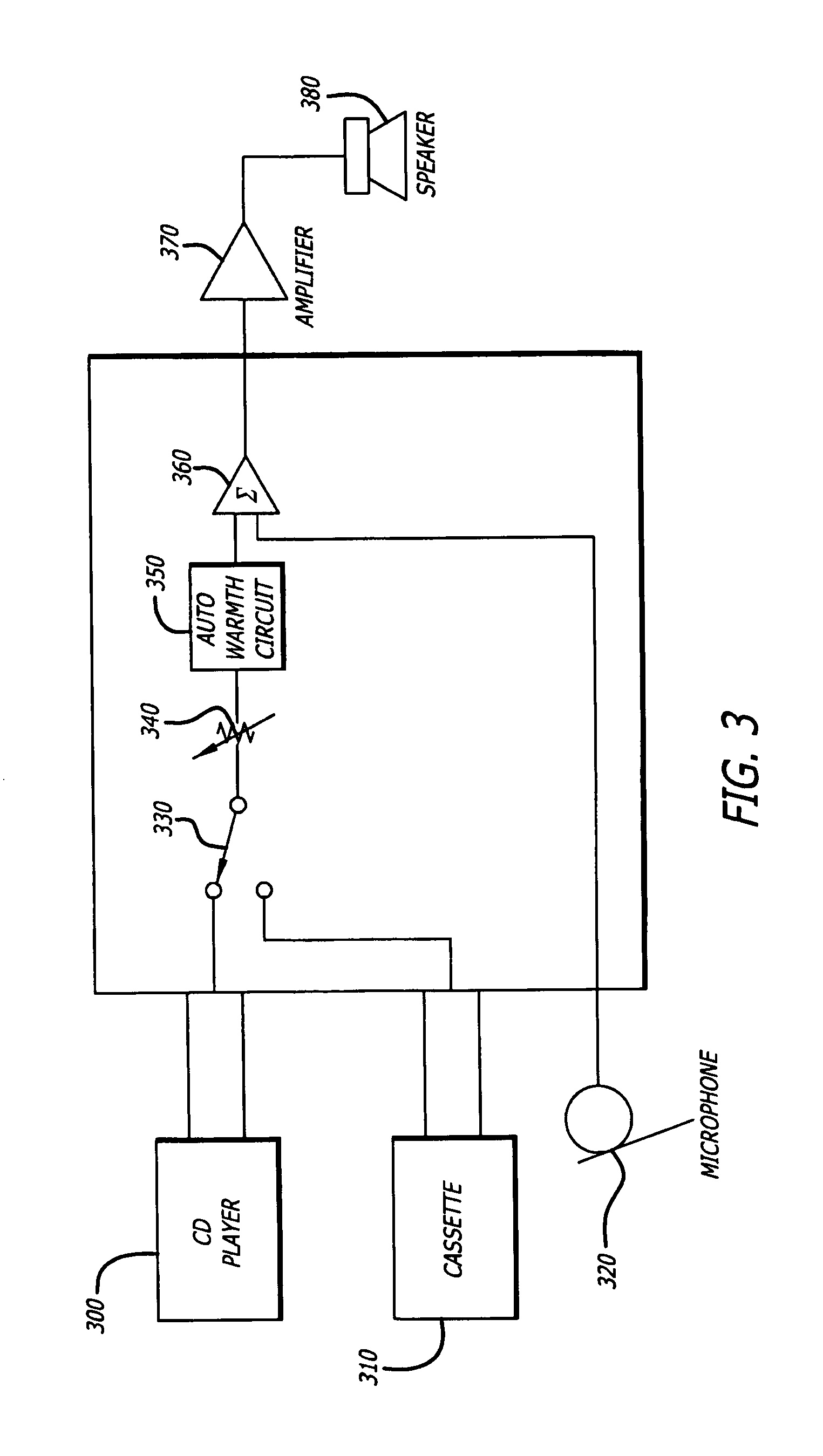

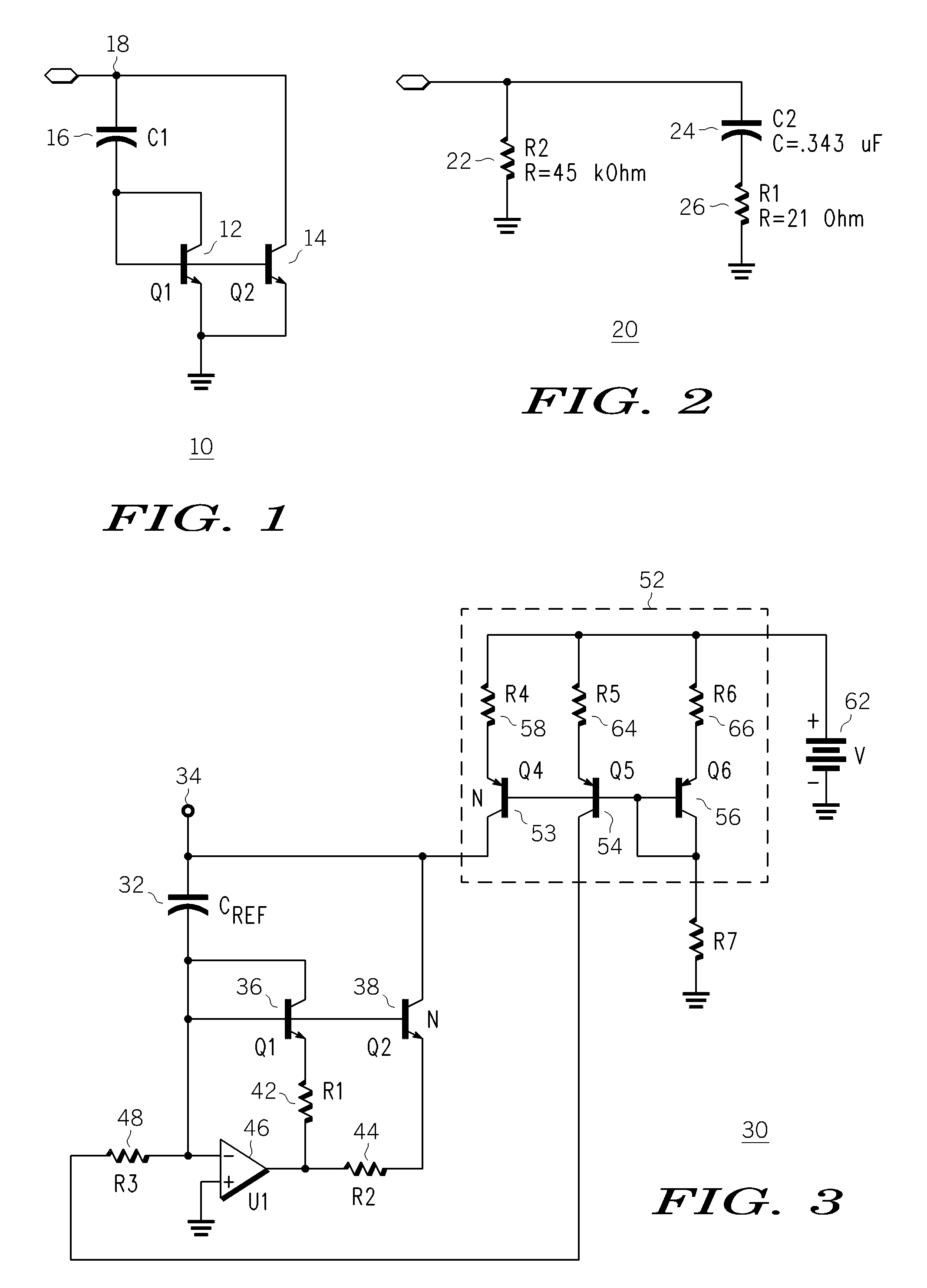

The present invention relates to an auto loudness circuit for performing loudness compensation automatically depending on the signal level. When the signal level decreases, loudness compensation is slowly introduced and as the signal level increases, loudness compensation is quickly removed. To do so, the auto loudness circuit utilizes a filter circuit with the characteristic of a first order bass boost. The filter circuit maintains a corner frequency which is proportional to the inverse of audio level in order to mimic the Fletcher-Munson curves. Because the circuit employs a capacitance-multiplier with a first order resistance capacitance filter, the bass boost is inversely proportional to the signal level. Thus, bass boost is achieved automatically as the program content changes so that the listener is unaware of significant changes in program material as signal levels change either through increase or decrease in volume, crescendo or new material.

Owner:HARMAN INT IND INC

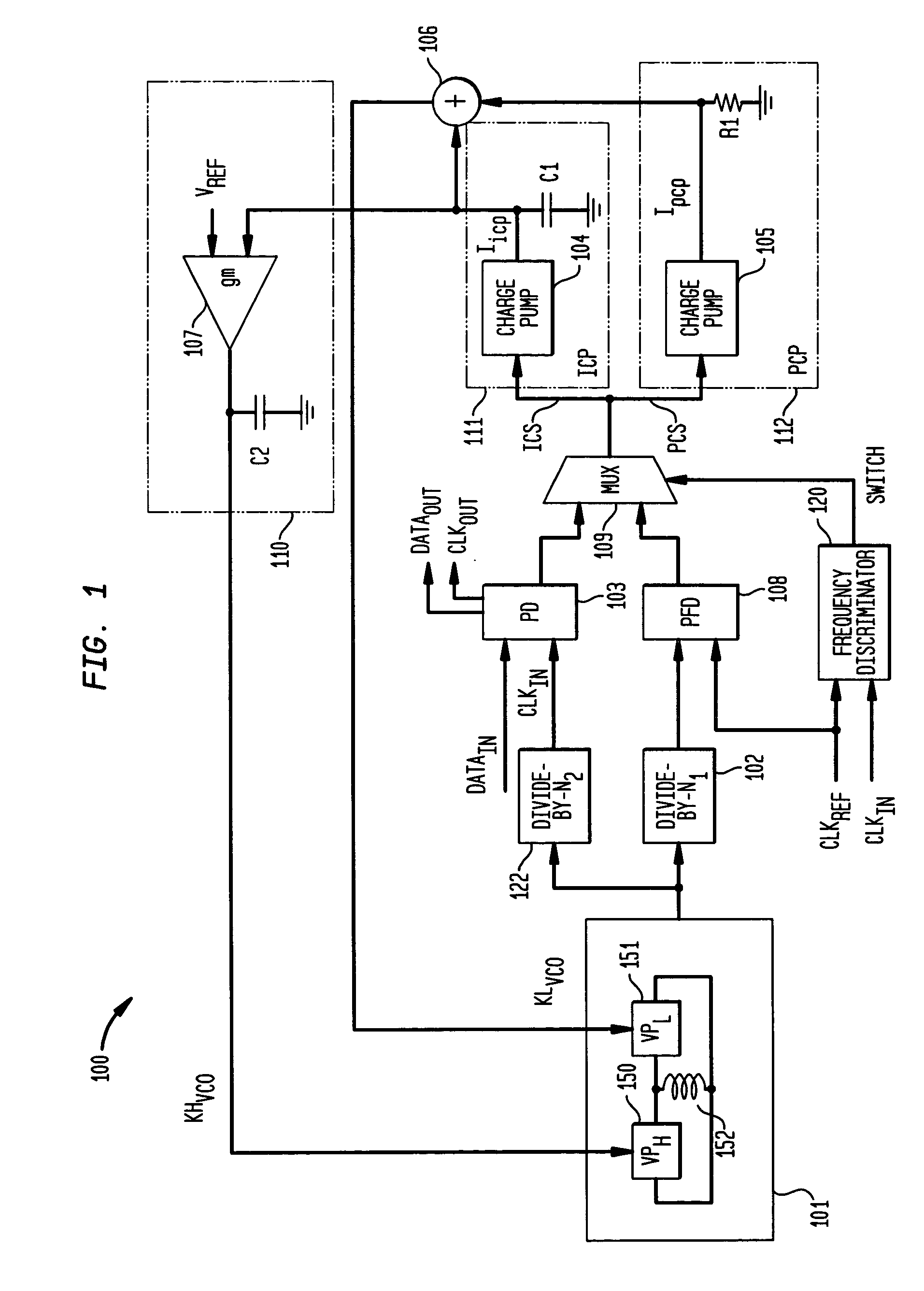

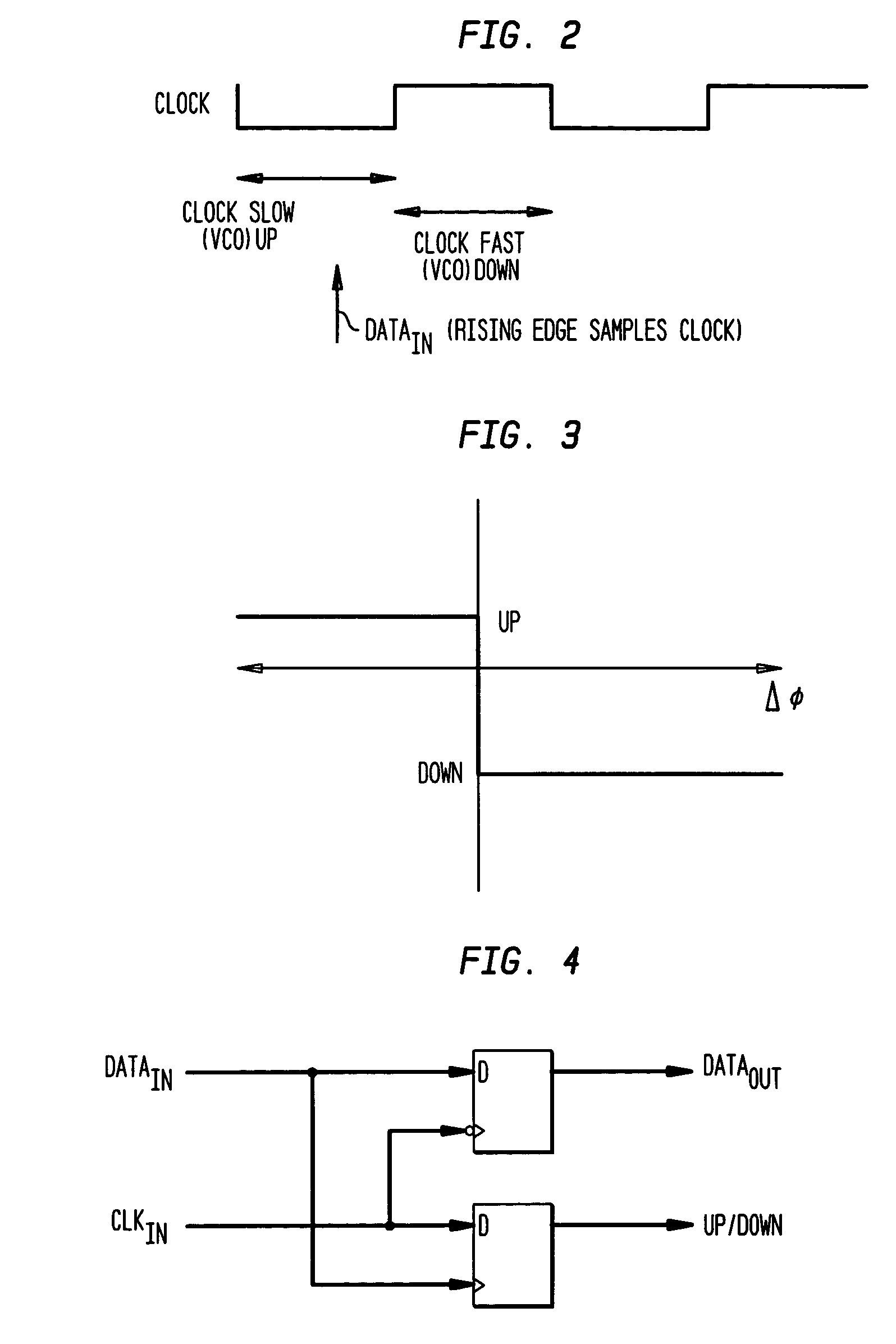

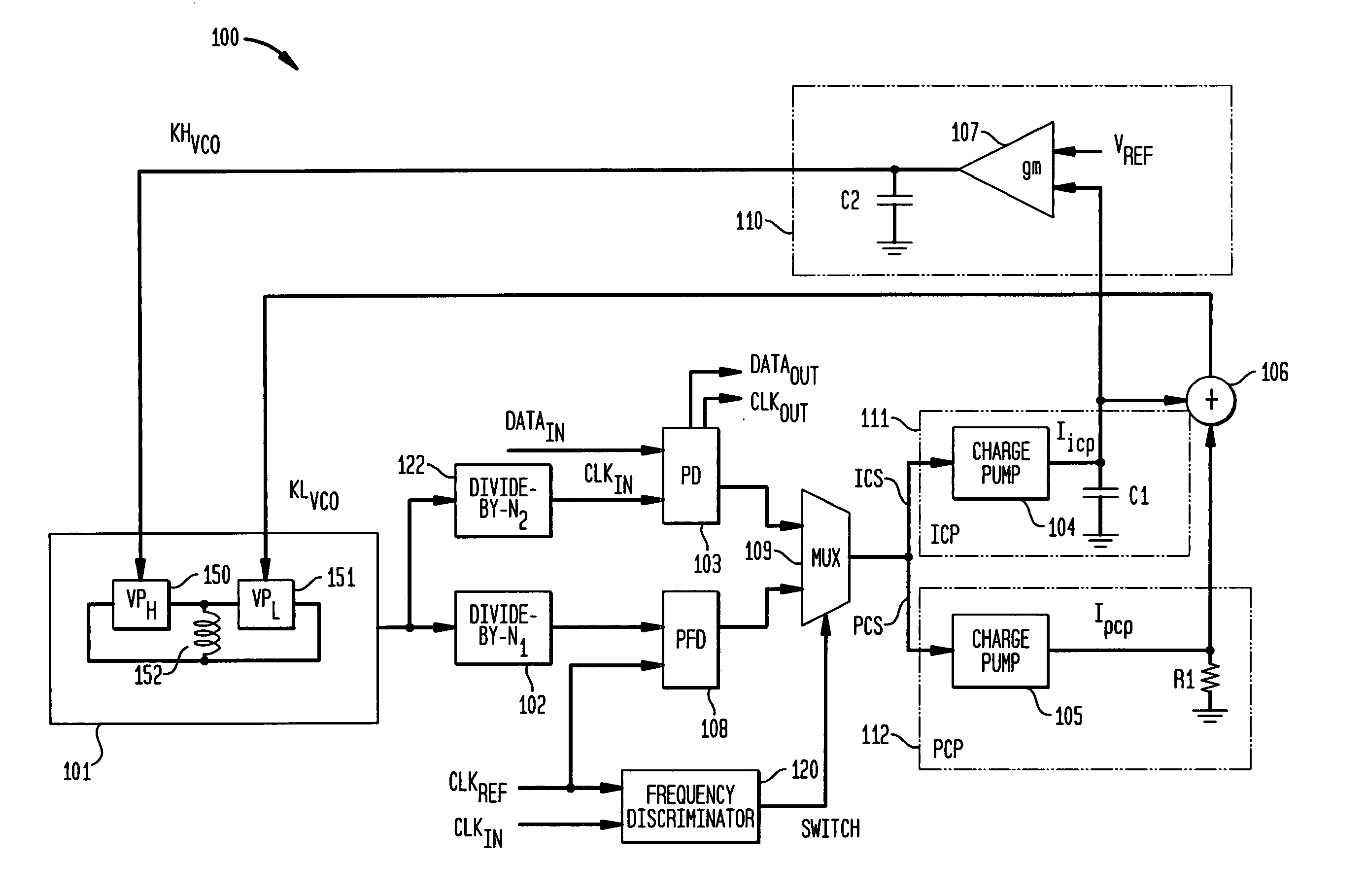

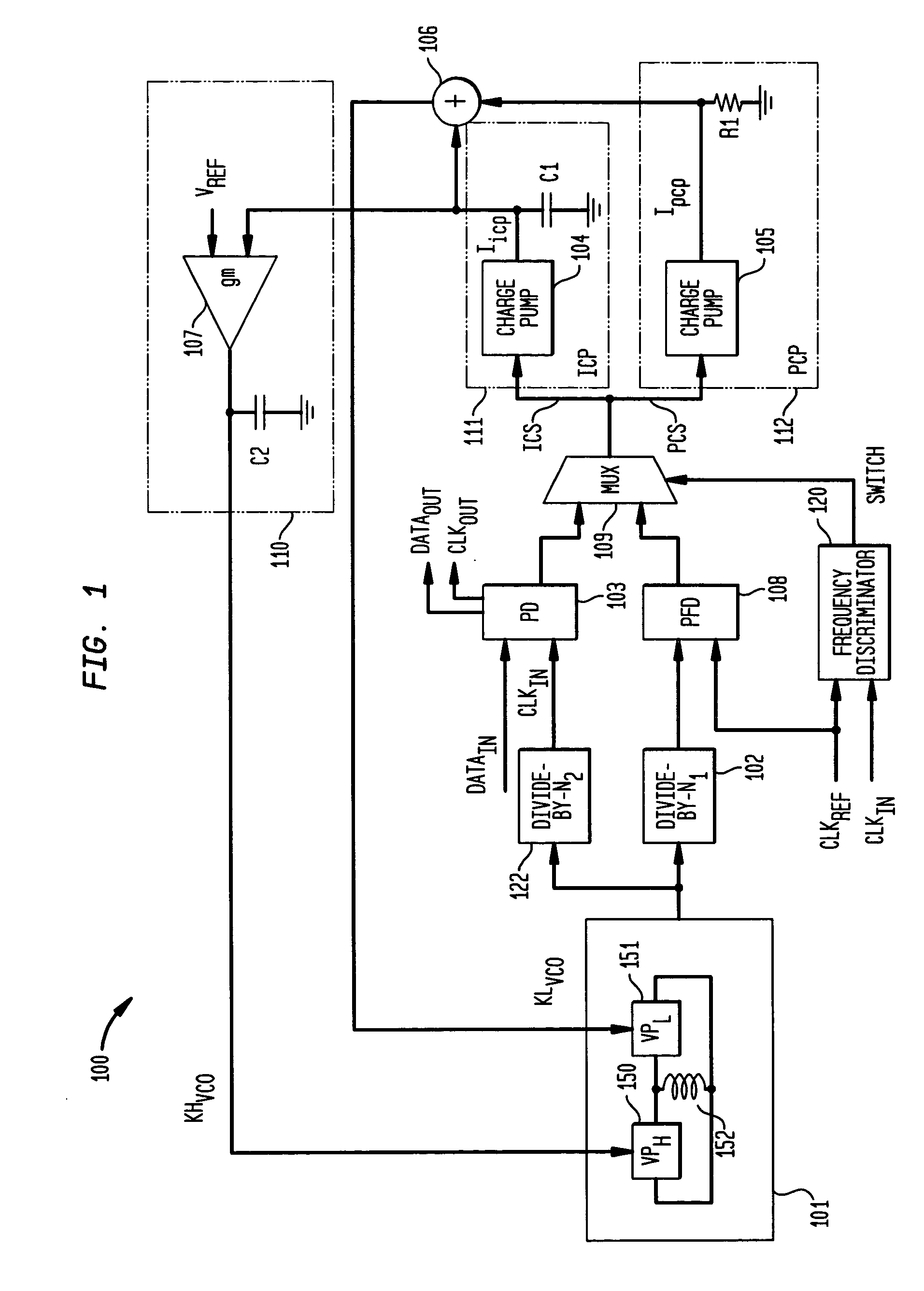

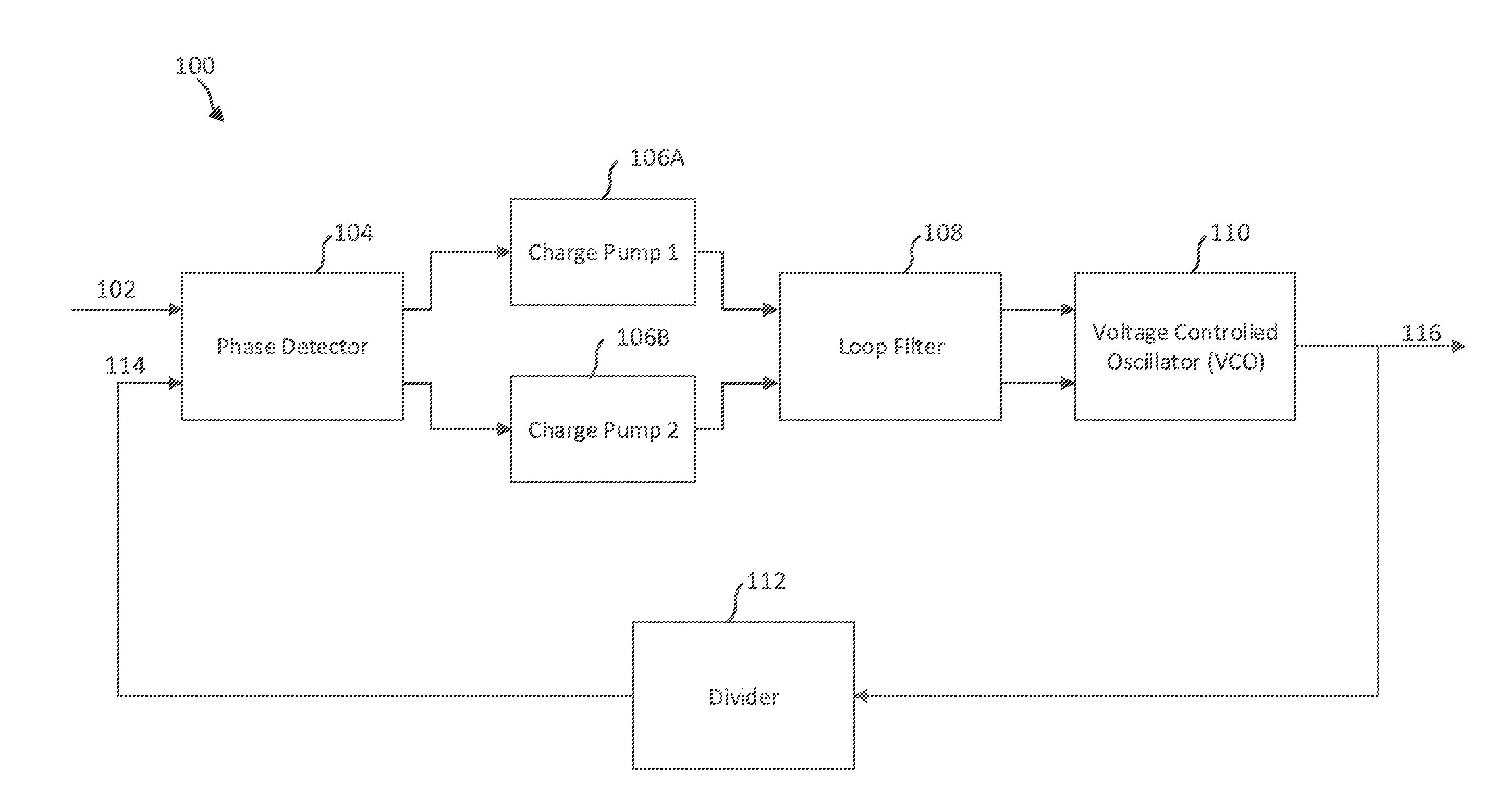

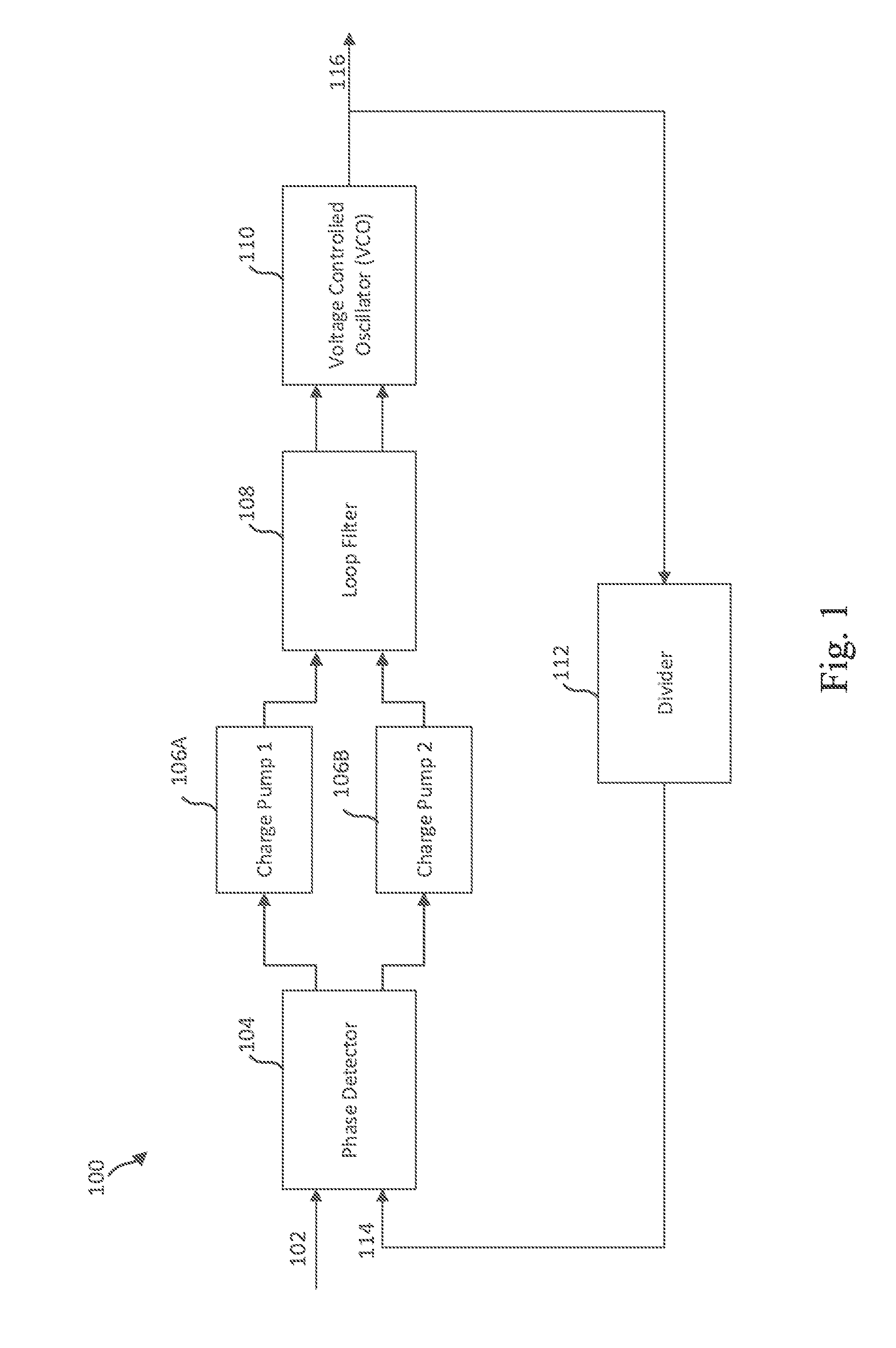

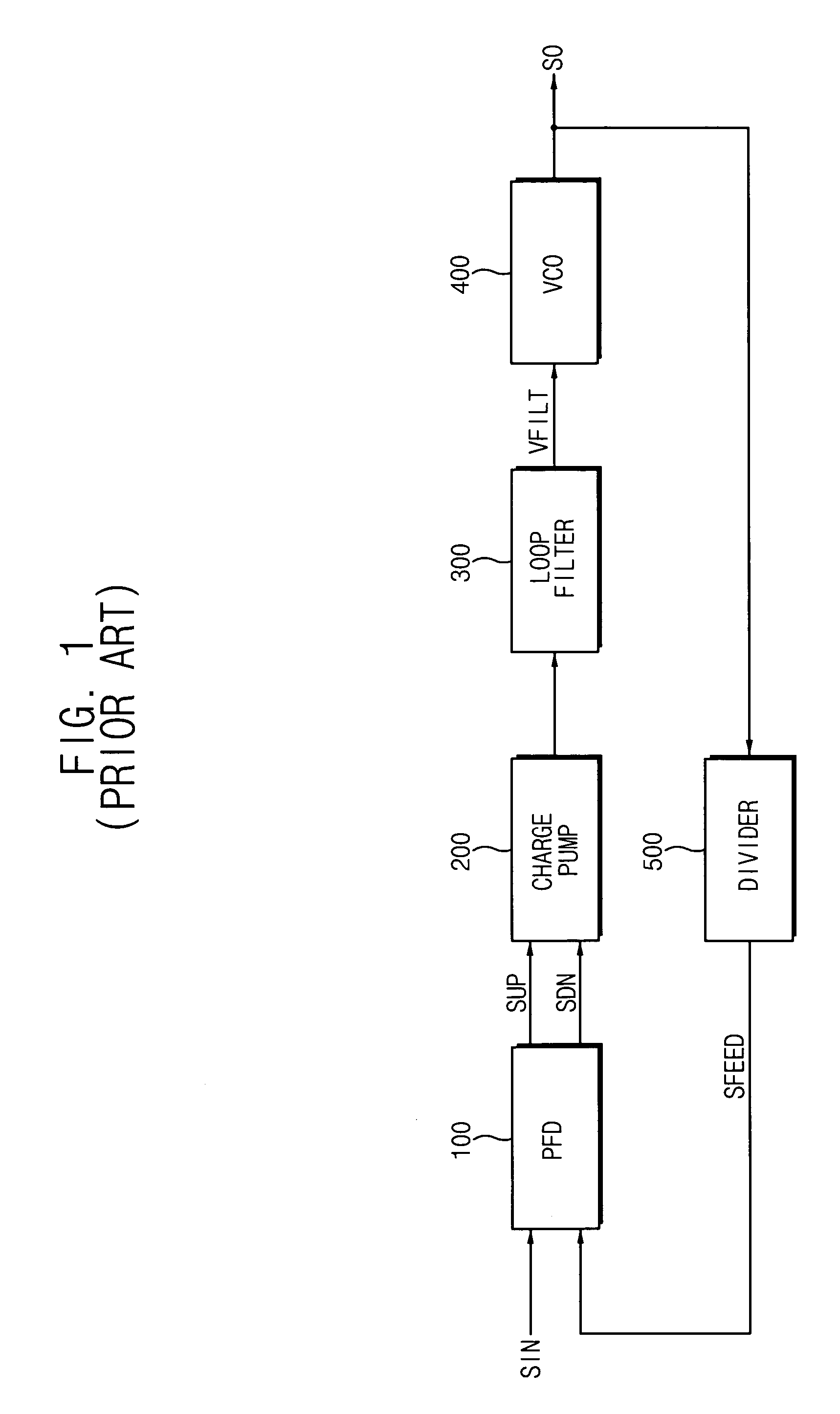

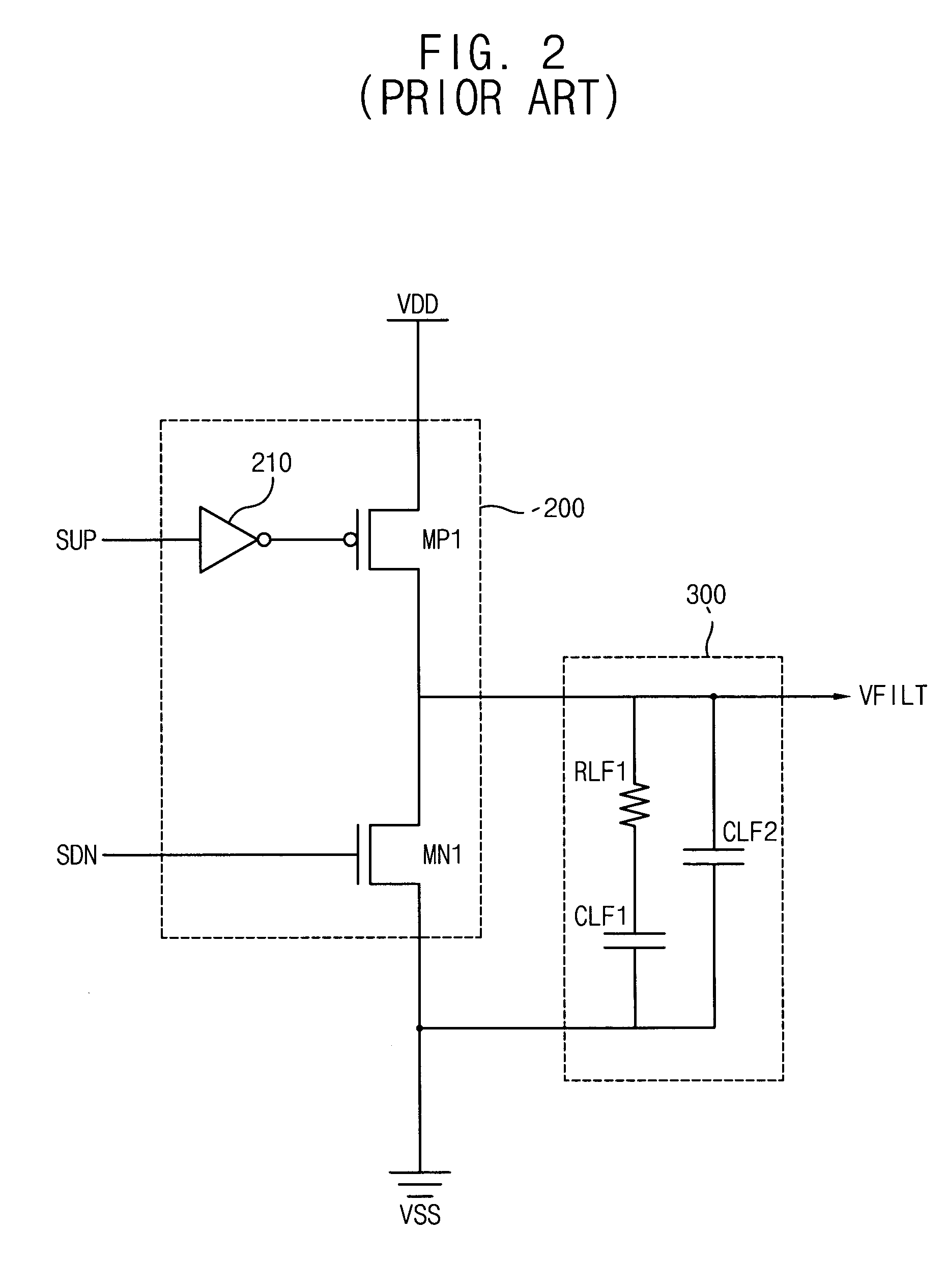

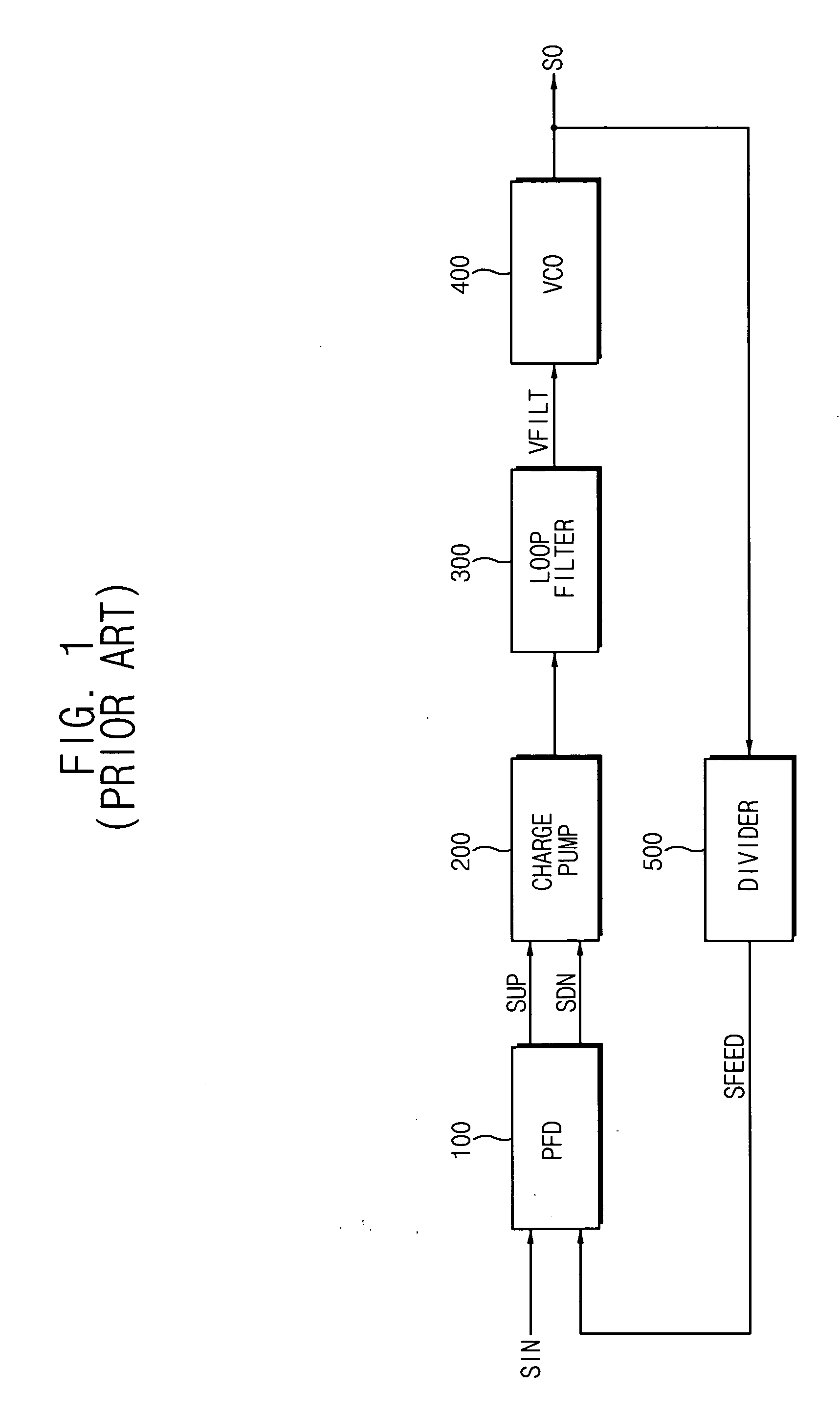

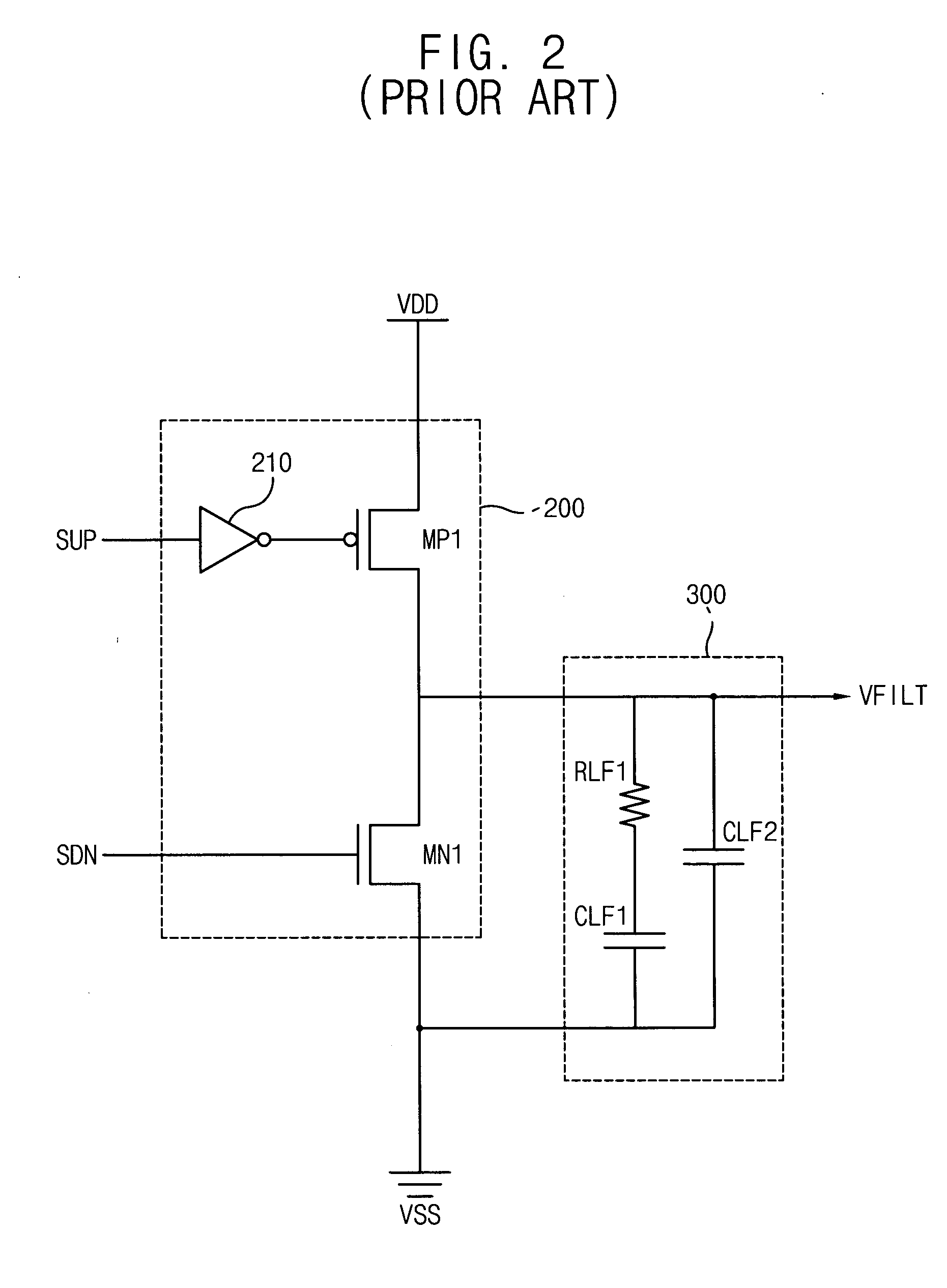

PLL employing a sample-based capacitance multiplier

ActiveUS7009456B2Angle modulation by variable impedencePulse automatic controlCapacitanceData synchronization

Owner:AVAGO TECH INT SALES PTE LTD

PLL employing a sample-based capacitance multiplier

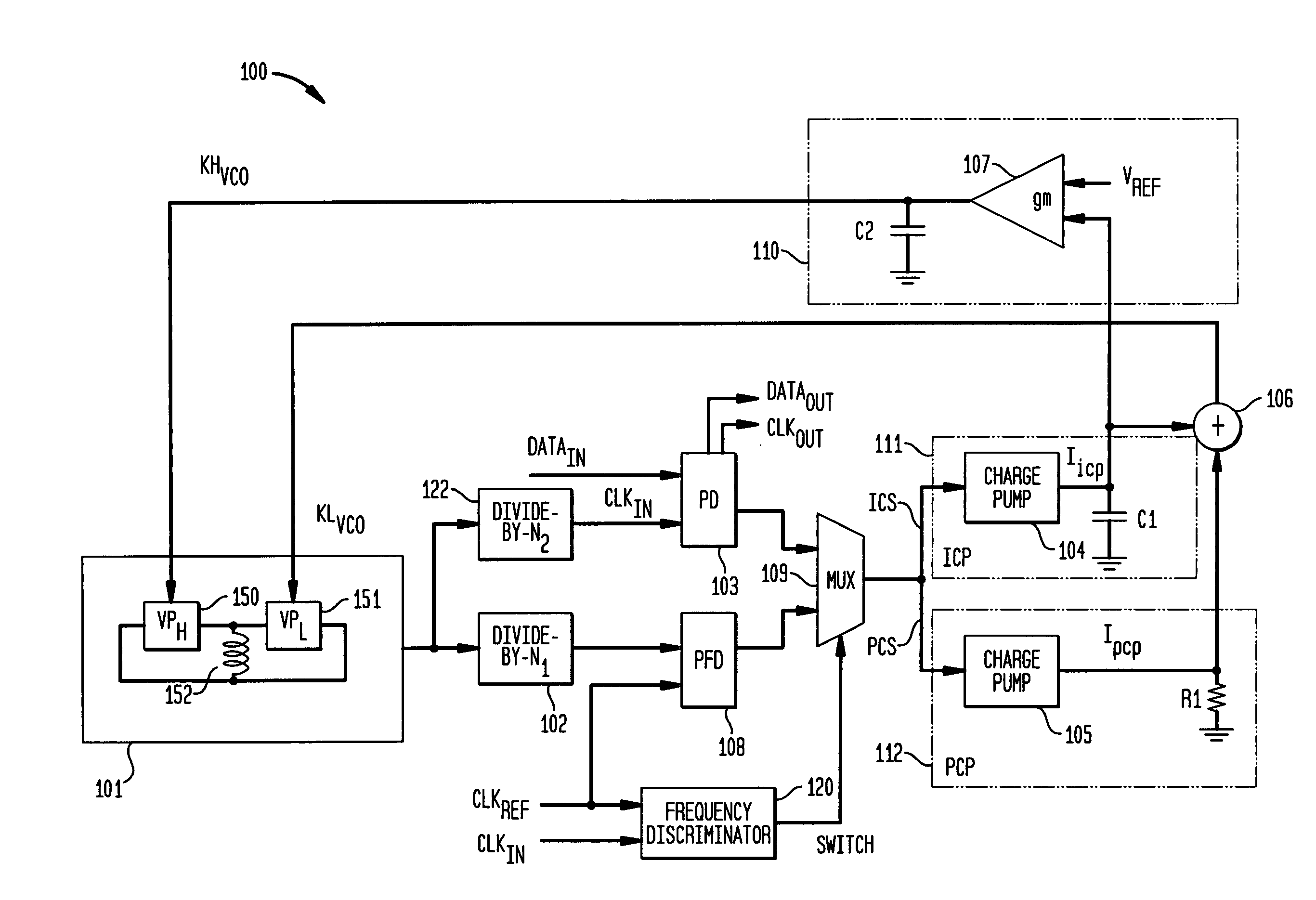

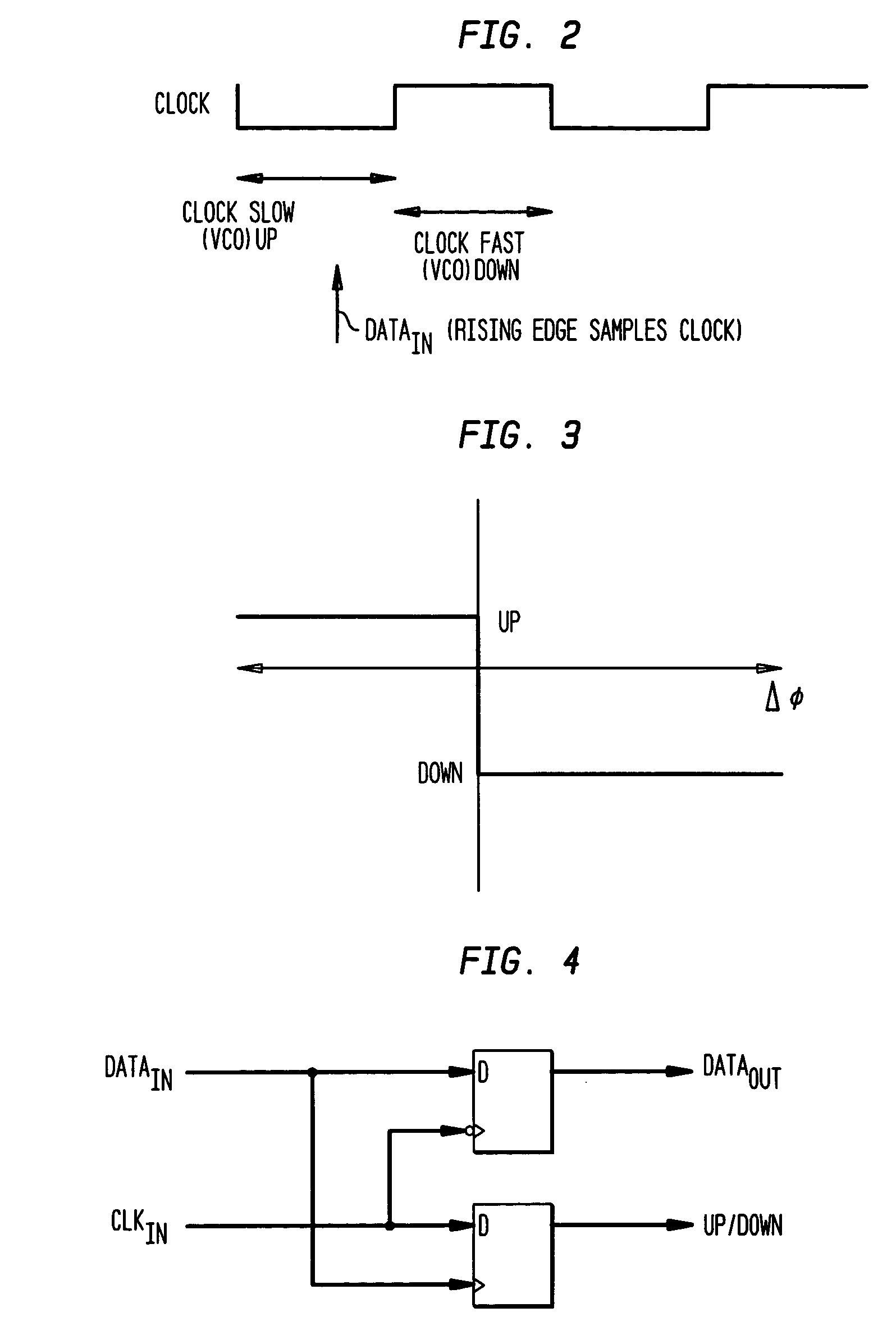

A phase detector (PD) generates an up / down signal based on the phase error between data and clock signals input to the phase detector. A voltage controlled oscillator (VCO) generates the clock signal. The up / down signal is applied to a proportional charge pump and a truncated version of the up / down signal is applied to an integral charge pump. The proportional charge pump generates a first voltage for a first time period across a resistor based on the up / down signal, while the integral charge pump generates a second voltage for a second time period across a capacitor based upon the truncated version of the up / down signal and the sampling rate of the data signal by the PD. The second time period is less than the first time period. The first and second voltages are combined and applied to the VCO to drive the clock signal to synchronization with the data.

Owner:AVAGO TECH INT SALES PTE LTD

Capacitance multiplier circuit

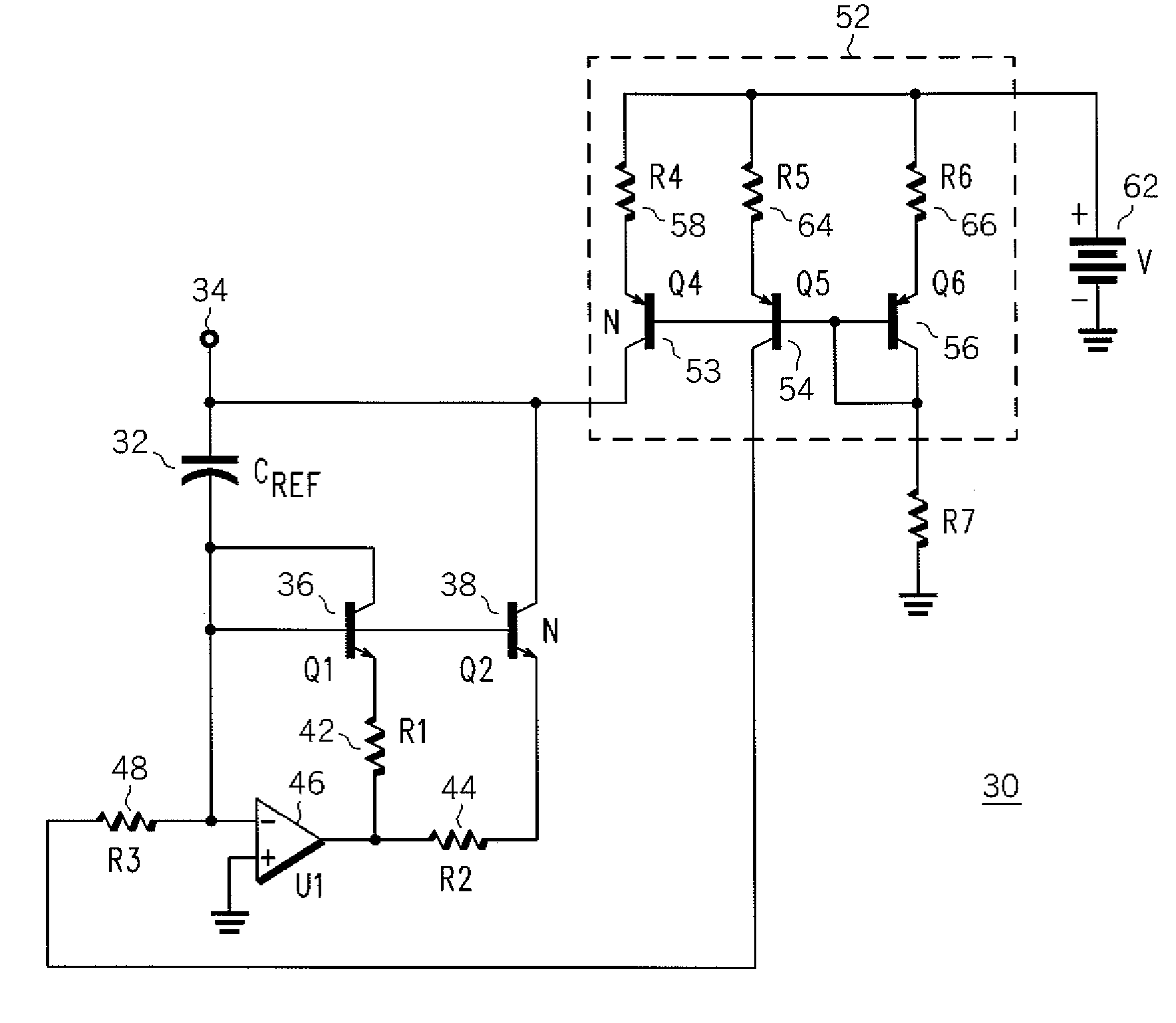

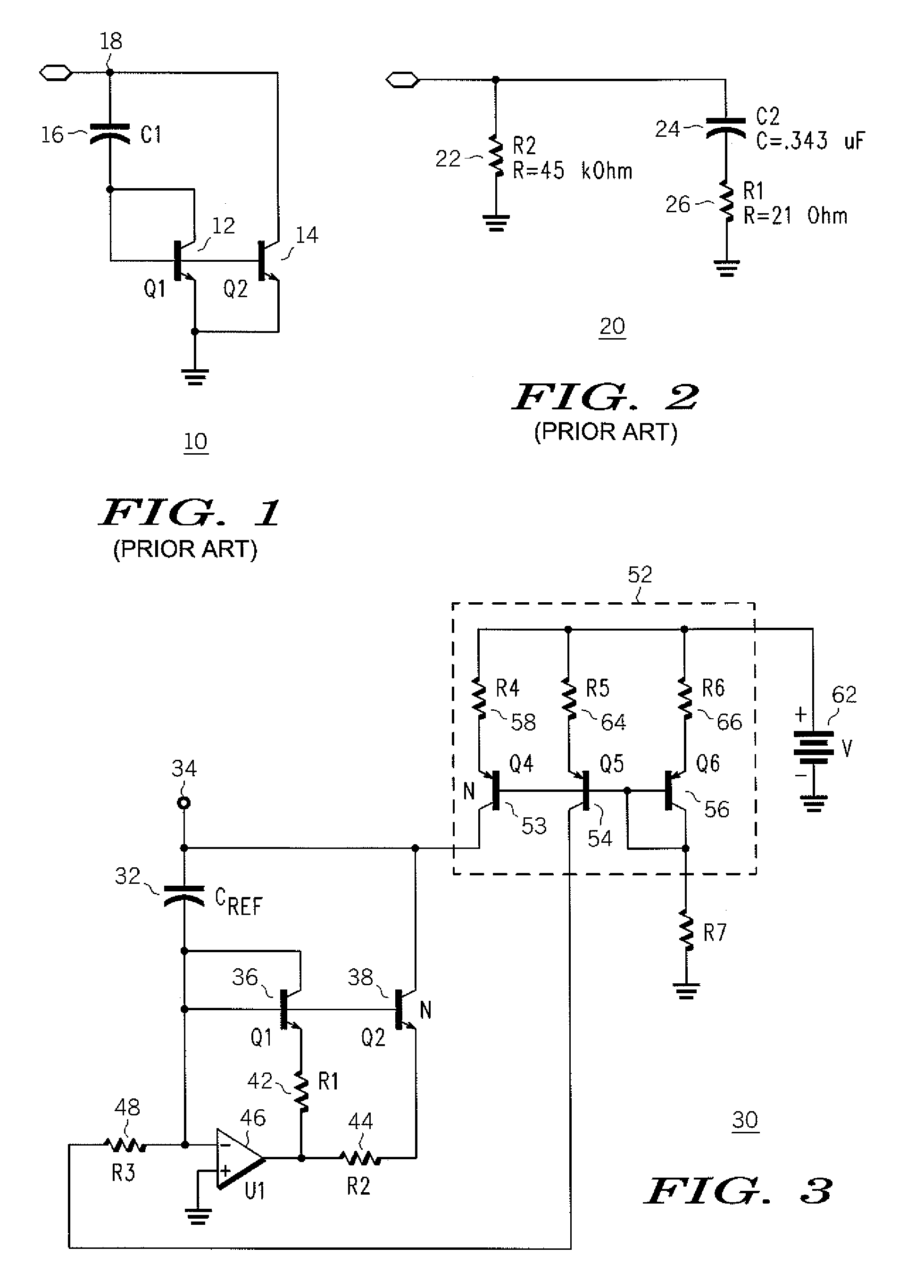

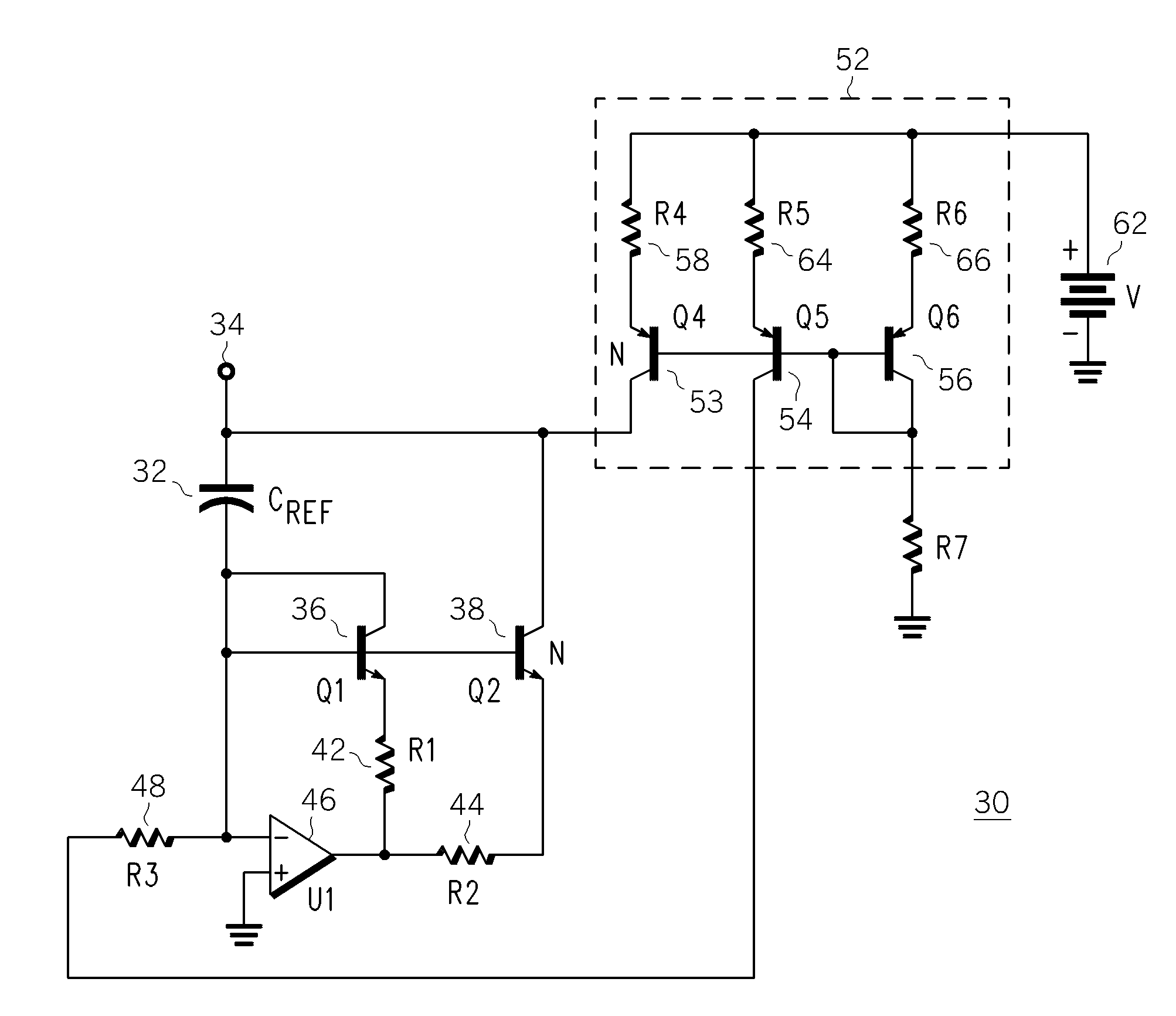

An integrated circuit including a capacitance multiplier having reduced parasitics and injected noise compared to conventional multiplier methods. The integrated circuit includes a reference capacitor and a current mirror arrangement coupled to the reference capacitor. The current mirror arrangement, which includes a current gain factor N, varies the capacitance of the reference capacitor by a factor of N+1, based on the reference capacitor current. The current mirror arrangement includes an operational amplifier operating in conjunction with two mirror transistors to form a current mirror arrangement having little or no series resistance. The current mirror also can include a plurality of resistors configured to reduce the noise from the capacitance multiplier, thus making the capacitance multiplier useful for applications that may require relatively low noise.

Owner:INTEL CORP

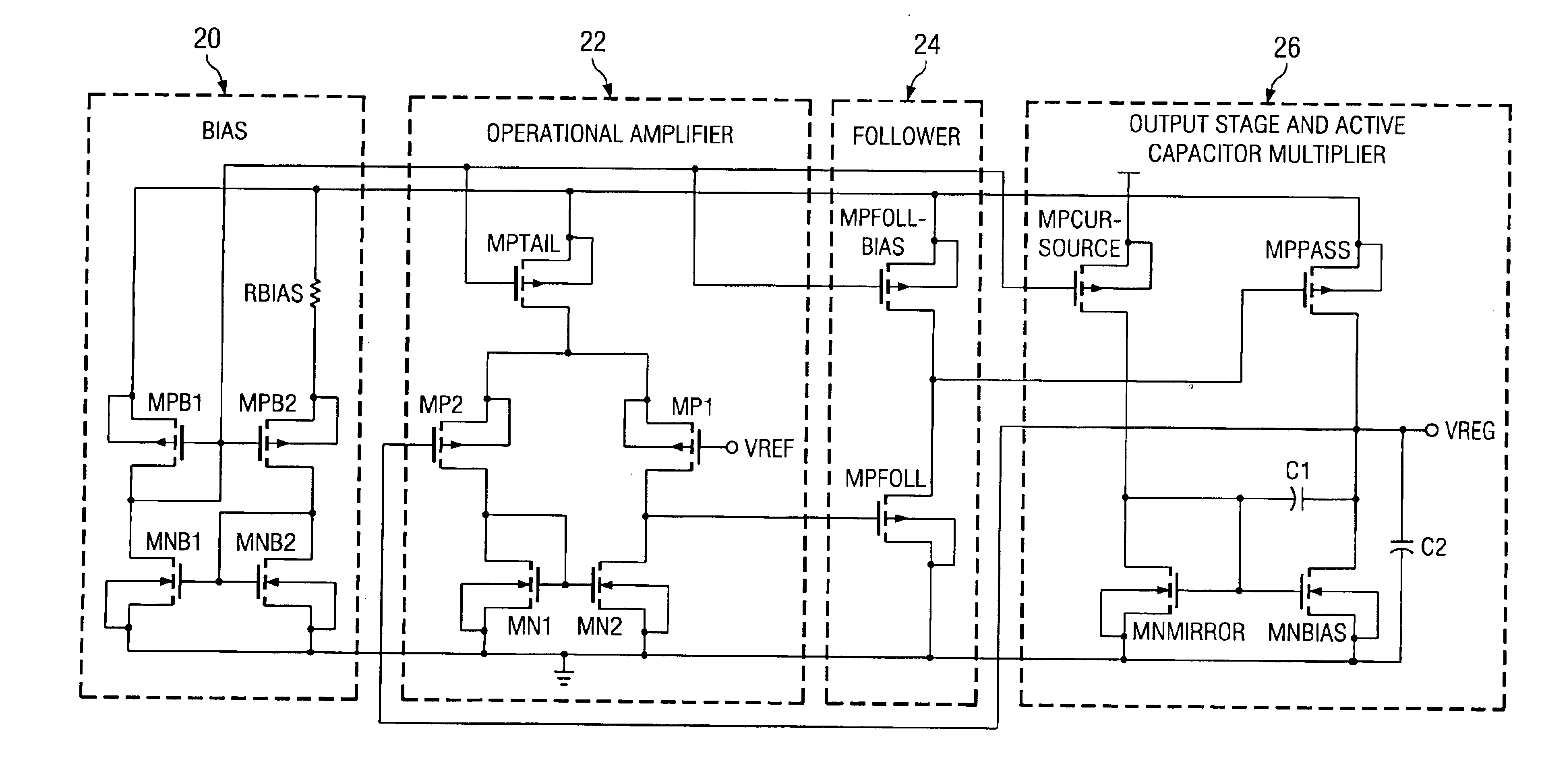

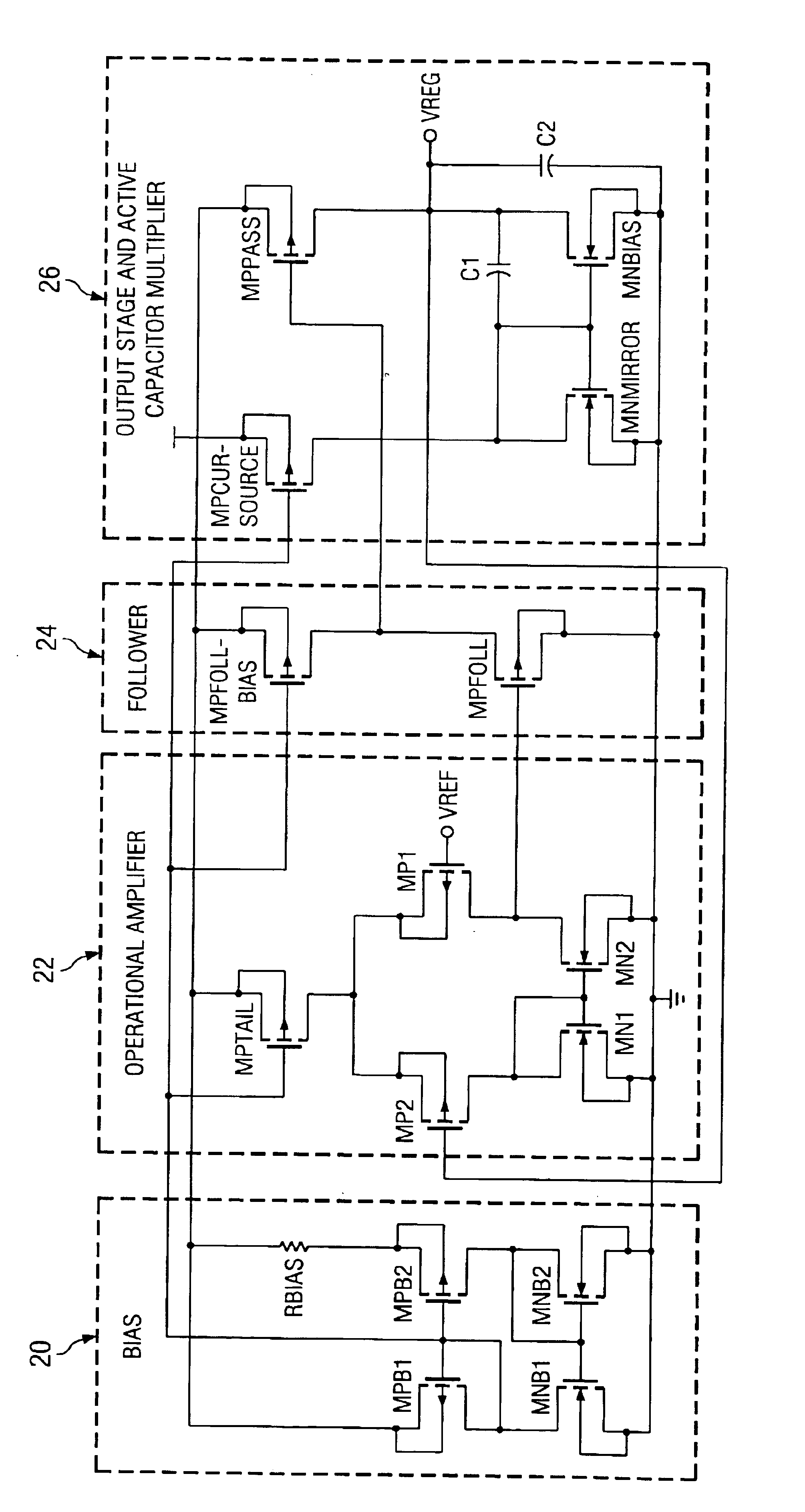

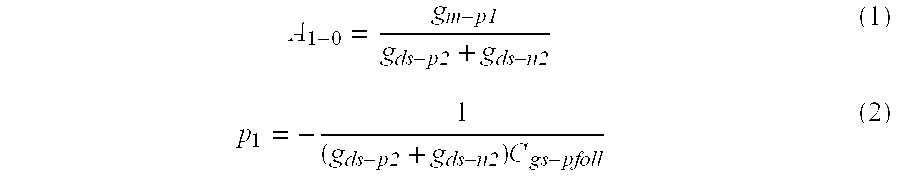

Low dropout monolithic linear regulator having wide operating load range

InactiveUS6847260B2System stabilityAmplifier modifications to reduce detrimental impedenceDifferential amplifiersLinear regulatorHigh frequency power

A monolithic low dropout regulator includes an active capacitor multiplier that is used to form the dominant pole of the regulator, thereby yielding stability. This decouples the system stability from the high-frequency power supply rejection ratio (PSRR). The PSRR at high frequencies is tuned independently using a reasonable on-chip capacitor C2.

Owner:TEXAS INSTR INC

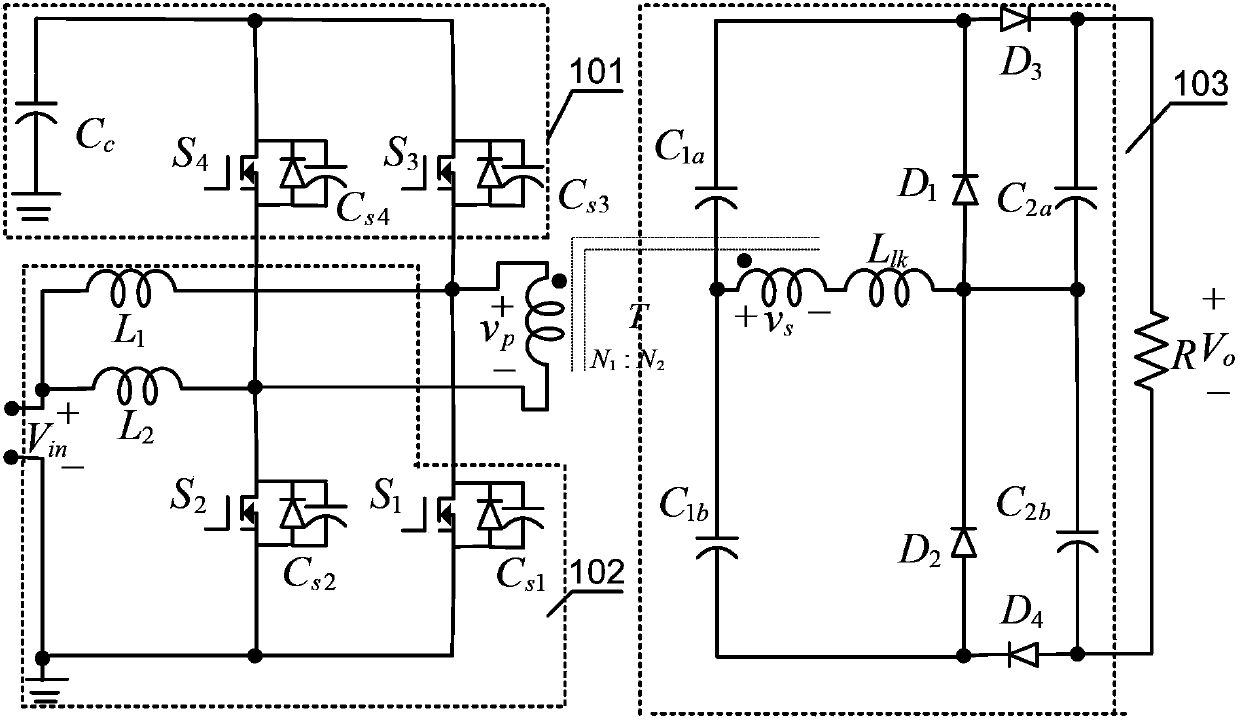

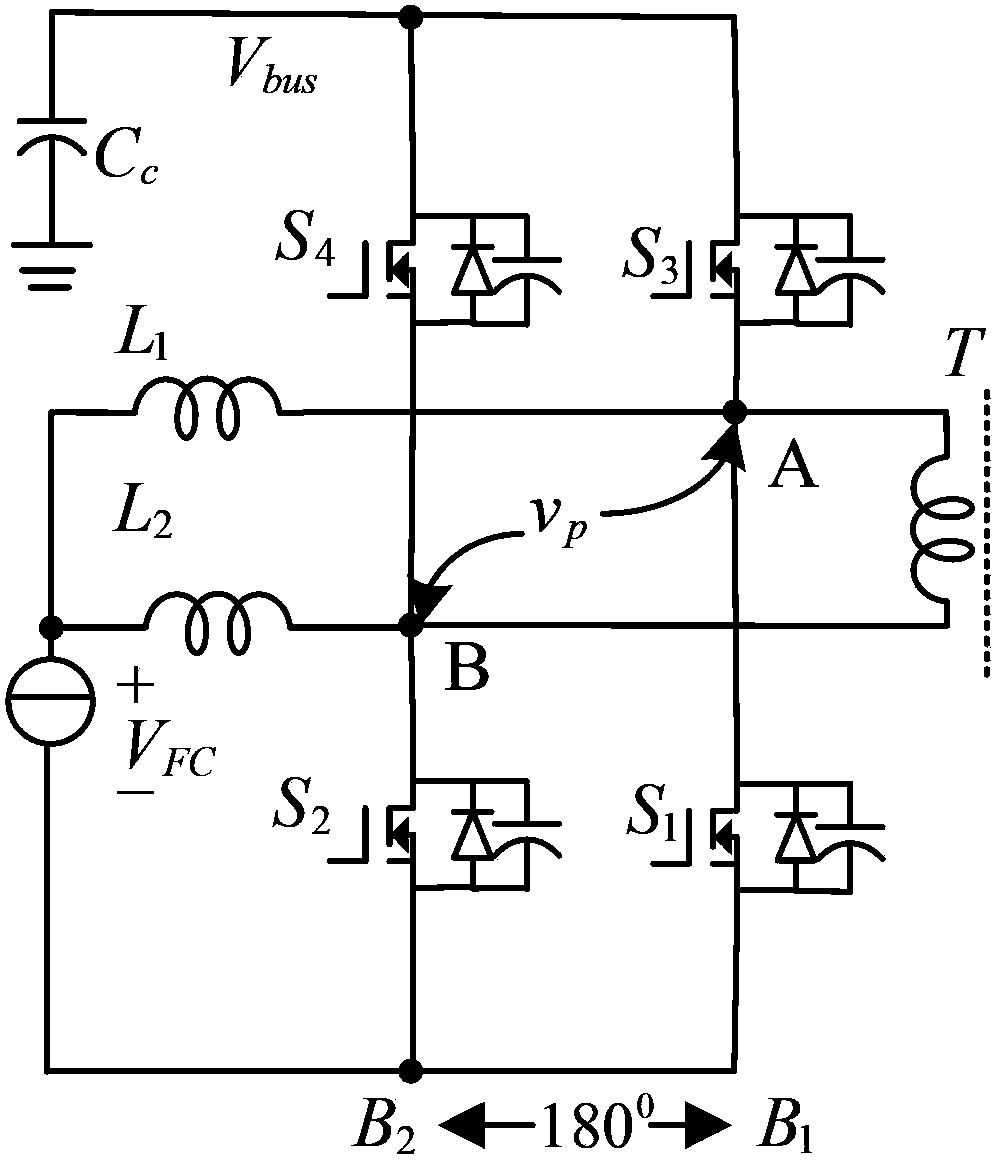

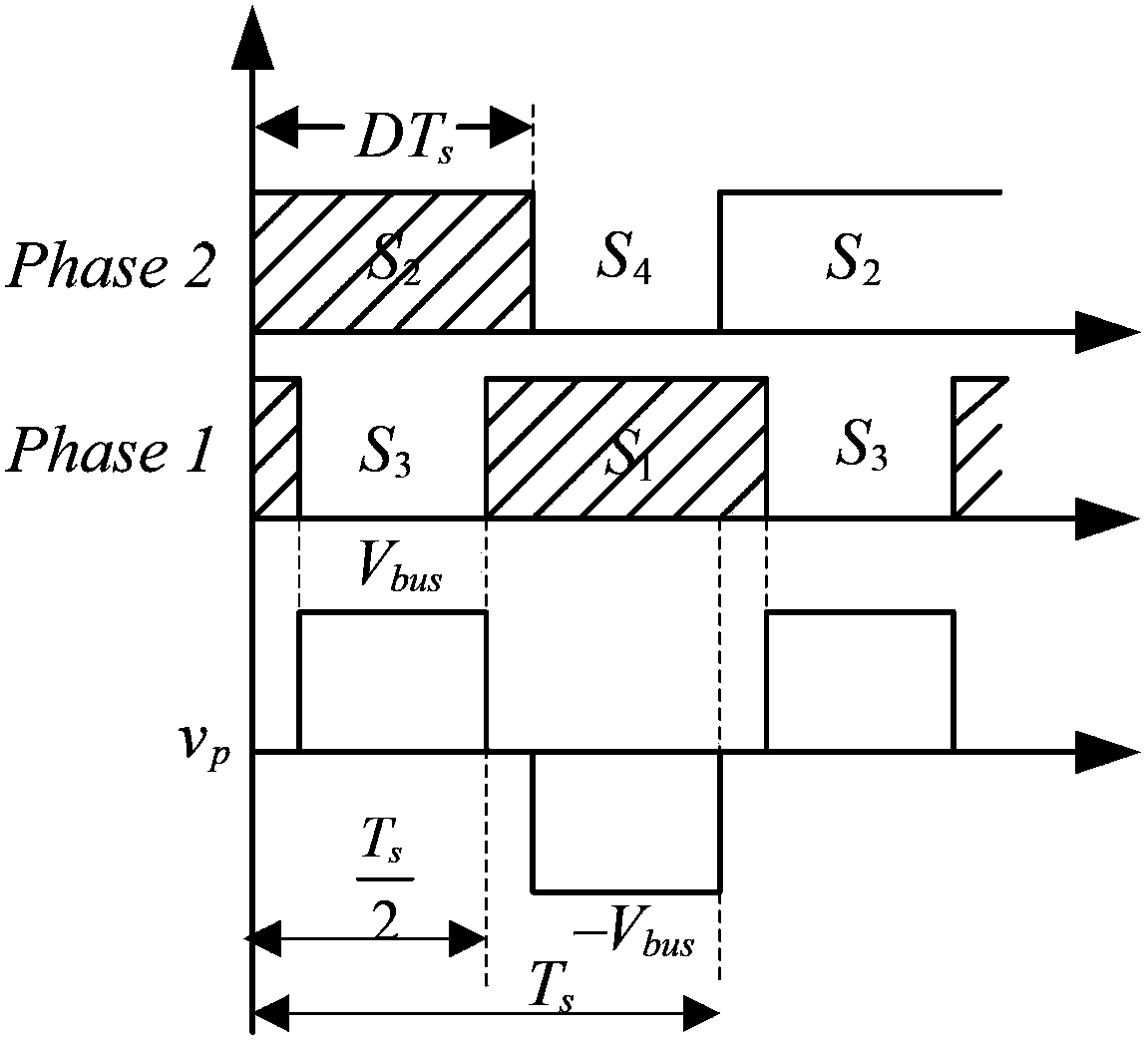

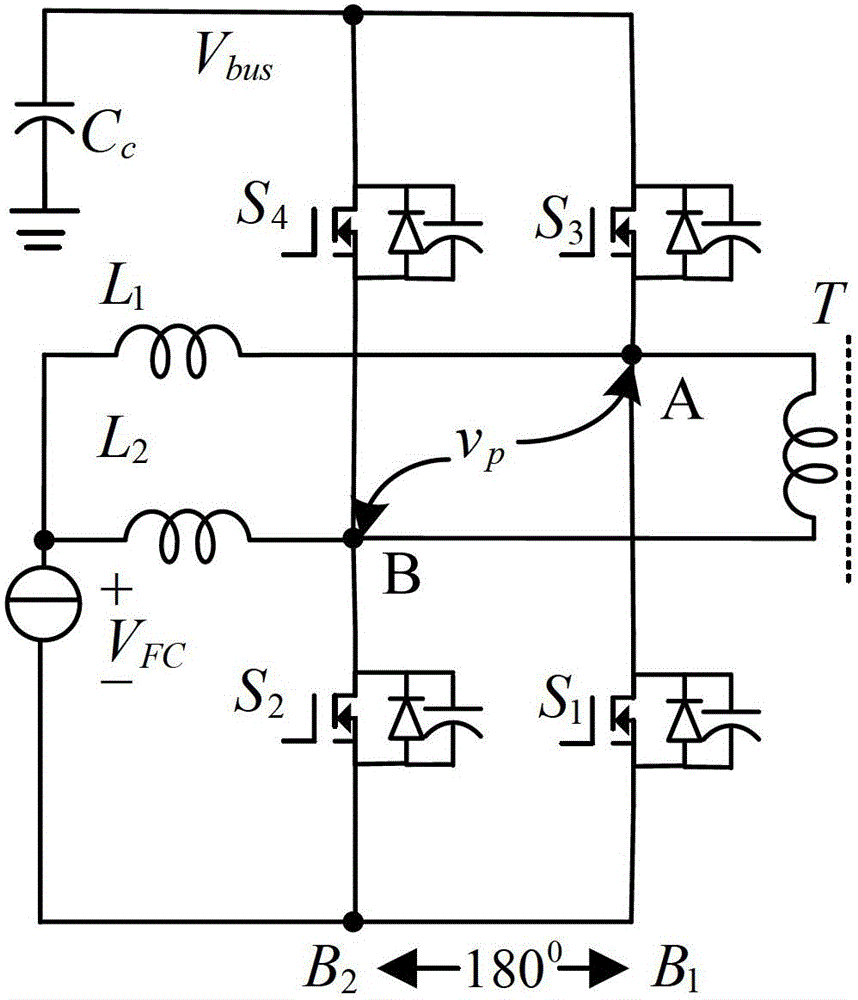

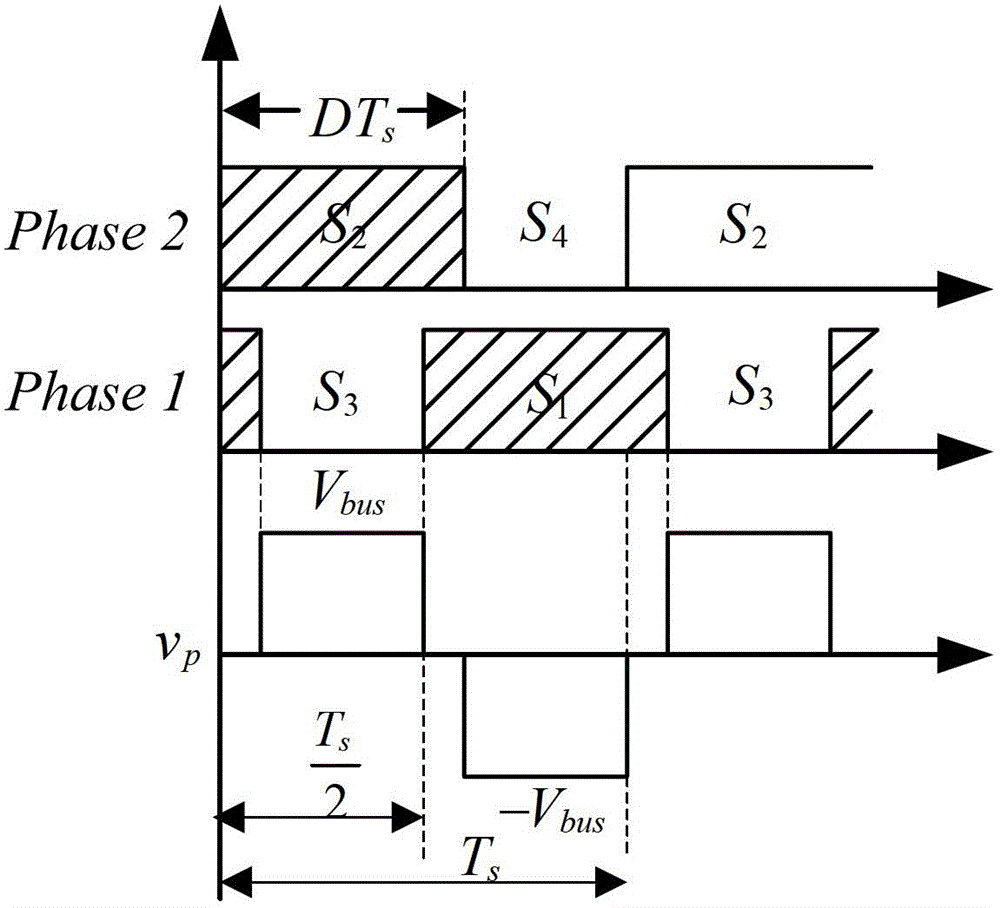

High-gain isolated type direct current-direct current (DC-DC) convertor

ActiveCN103391009ALow costImprove system efficiencyAc-dc conversion without reversalEfficient power electronics conversionCapacitanceFuel cells

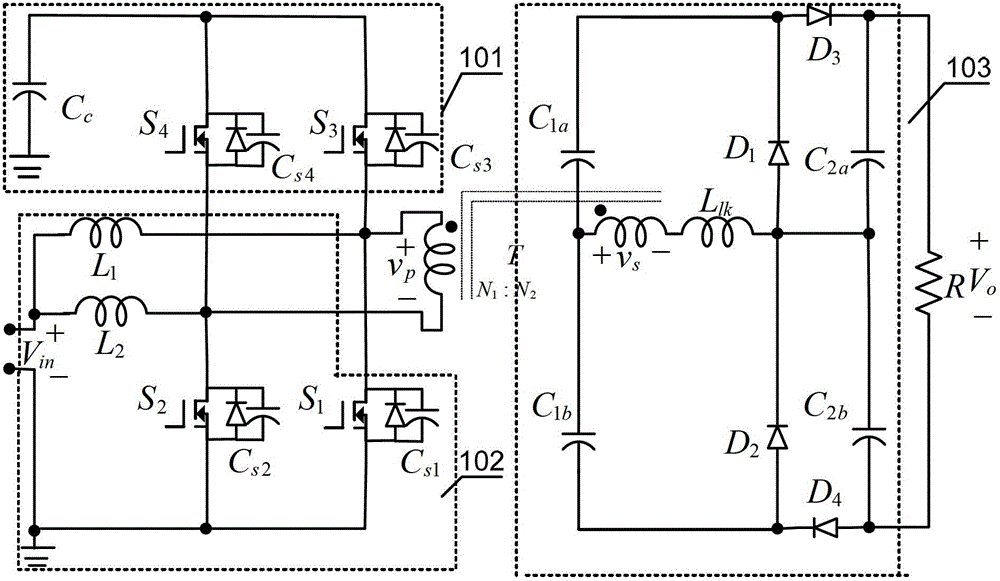

The invention discloses a high-gain isolated type direct current-direct current (DC-DC) convertor for fuel-cell power generation and belongs to the technical field of convertors. The convertor comprises an input current multiplier, a switch capacity multiplier, a clamping circuit and a transformer. The input current multiplier comprises a first input inductor, a second input inductor, a first switch tube and a second switch tube. The clamping circuit comprises a clamping capacitor Cc, a first clamping switch tube and a second clamping switch tube. The switch capacity multiplier comprises a first resonant capacitor, a second resonant capacitor, a first output capacitor C2a, a second output capacitor C2b and four rectifier tubes. The primary side of the transformer is connected with the input current multiplier and the clamping circuit respectively, and the secondary side of the transformer is connected with the switch capacity multiplier. When high-gain isolated type DC-DC convertor is applicable to the fuel-cell power generation and grid connection, the convertor needs an occasion with high gain, small input current ripple and high efficiency, and the convertor is also applicable to other types of new energy power generation including low-output-voltage power generation and the like.

Owner:厦门市爱维达电子有限公司

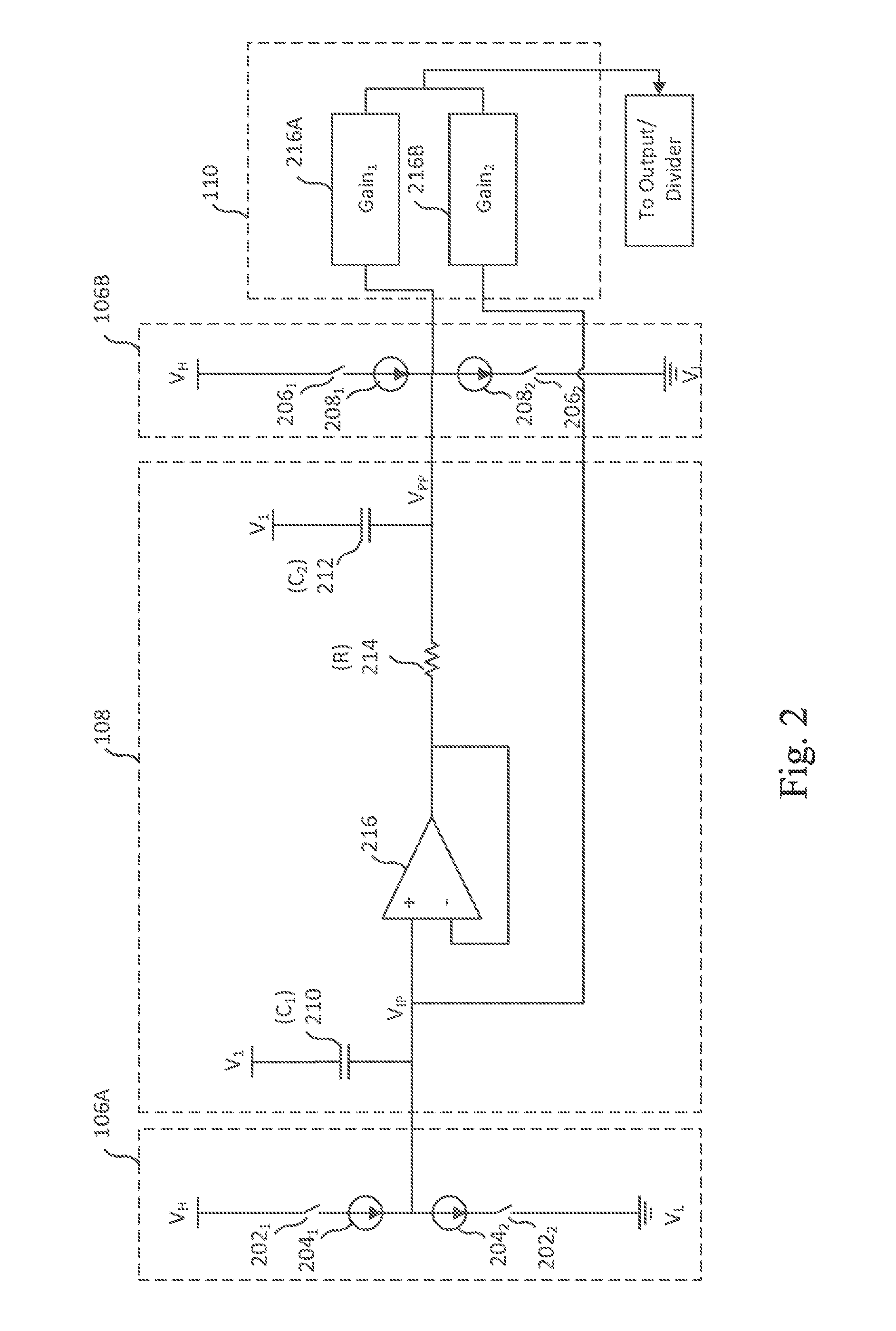

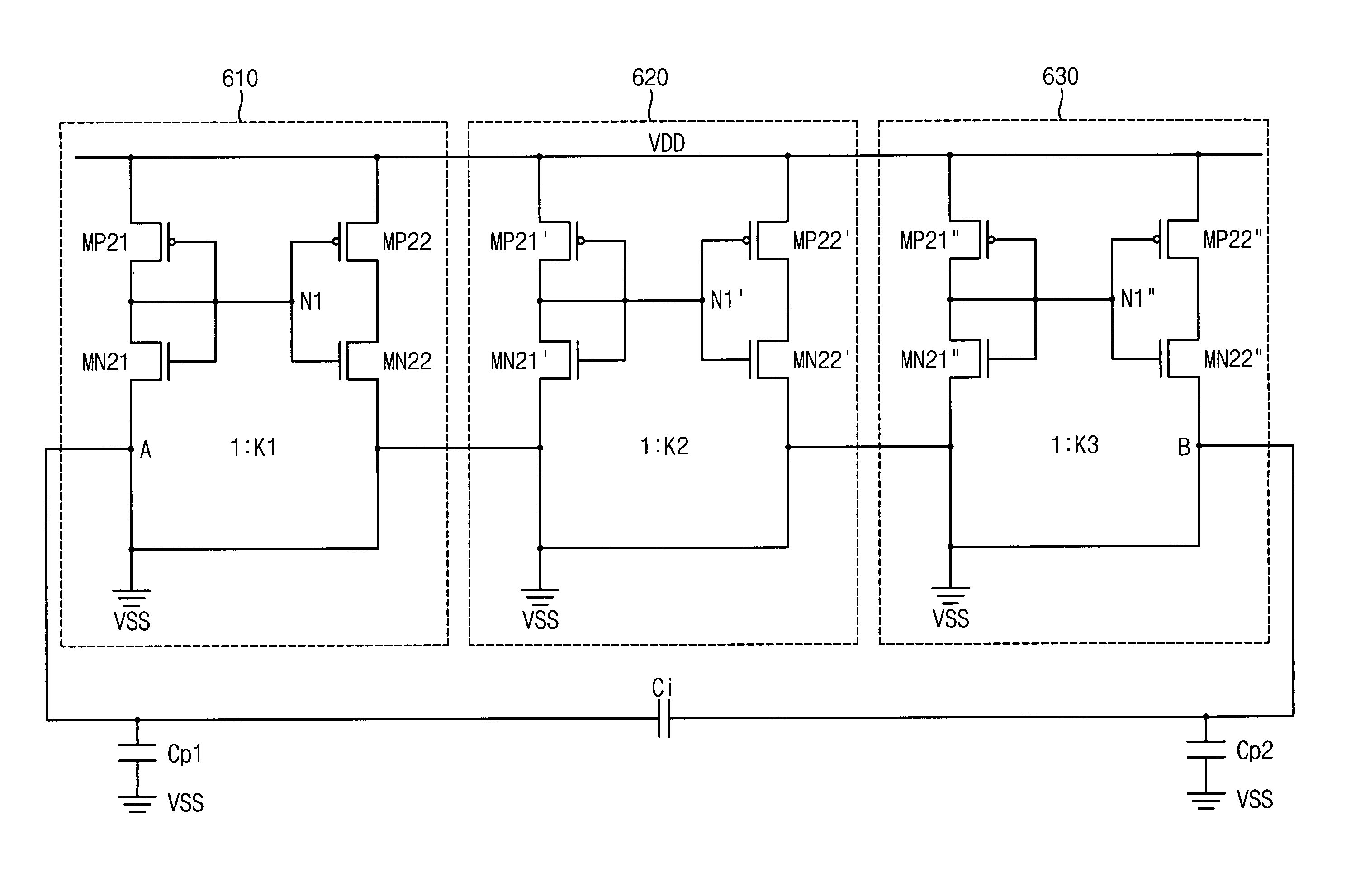

Capacitance Multiplier and Loop Filter Noise Reduction in a PLL

According to an embodiment, a circuit includes a first charge pump configured to generate a first current at a first node, a second charge pump configured to generate a second current at a second node, a loop filter coupled between the first and second nodes, the loop filter including a first filter path coupled to the first node, a second filter path coupled to the second node, and an isolation buffer interposed between the first and second filter paths. The second current at the second node is different than the first current at the first node. The circuit further includes an oscillator configured to apply a first gain to an output of the first filter path and a second gain to an output of the second filter path.

Owner:STMICROELECTRONICS INT NV

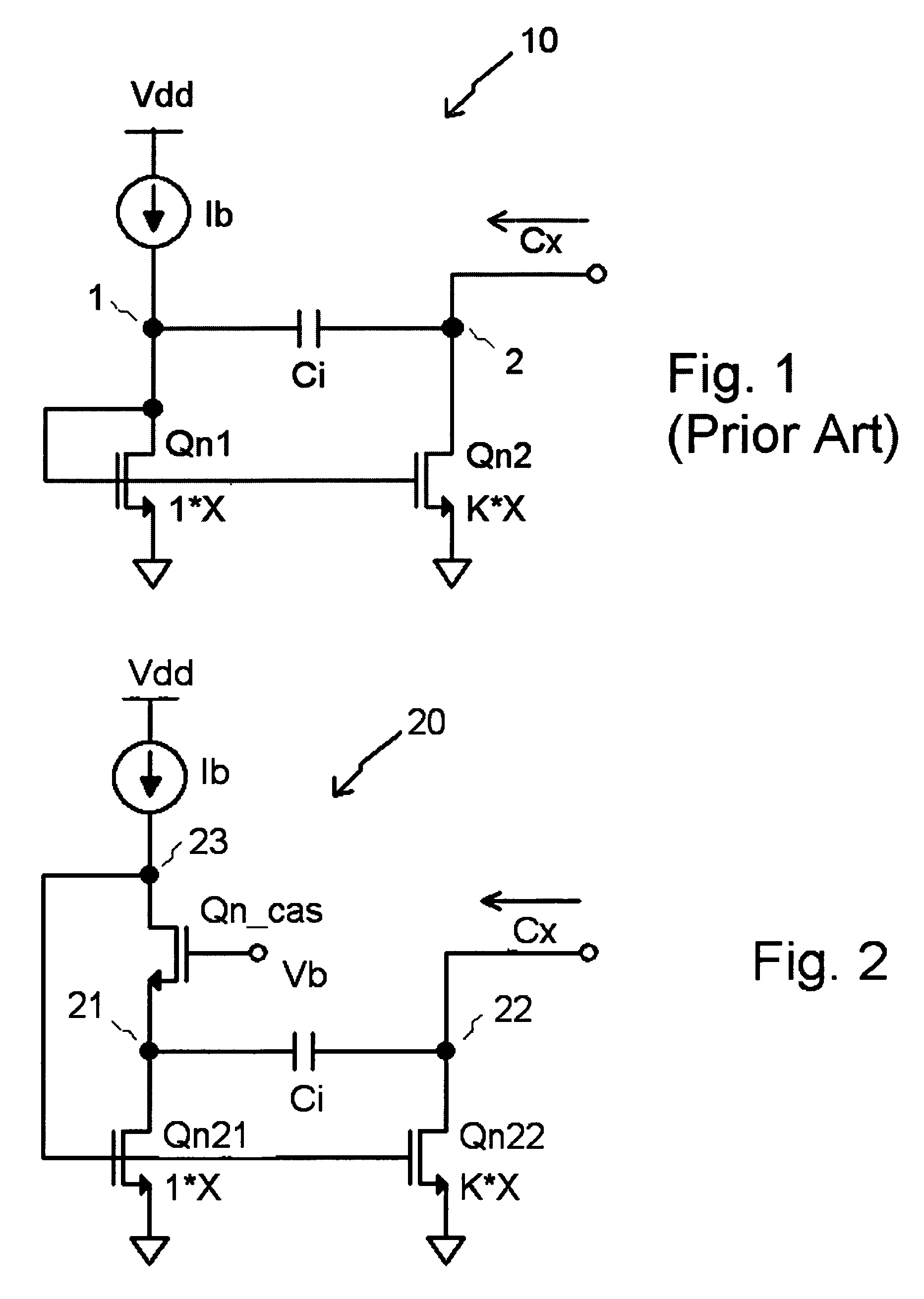

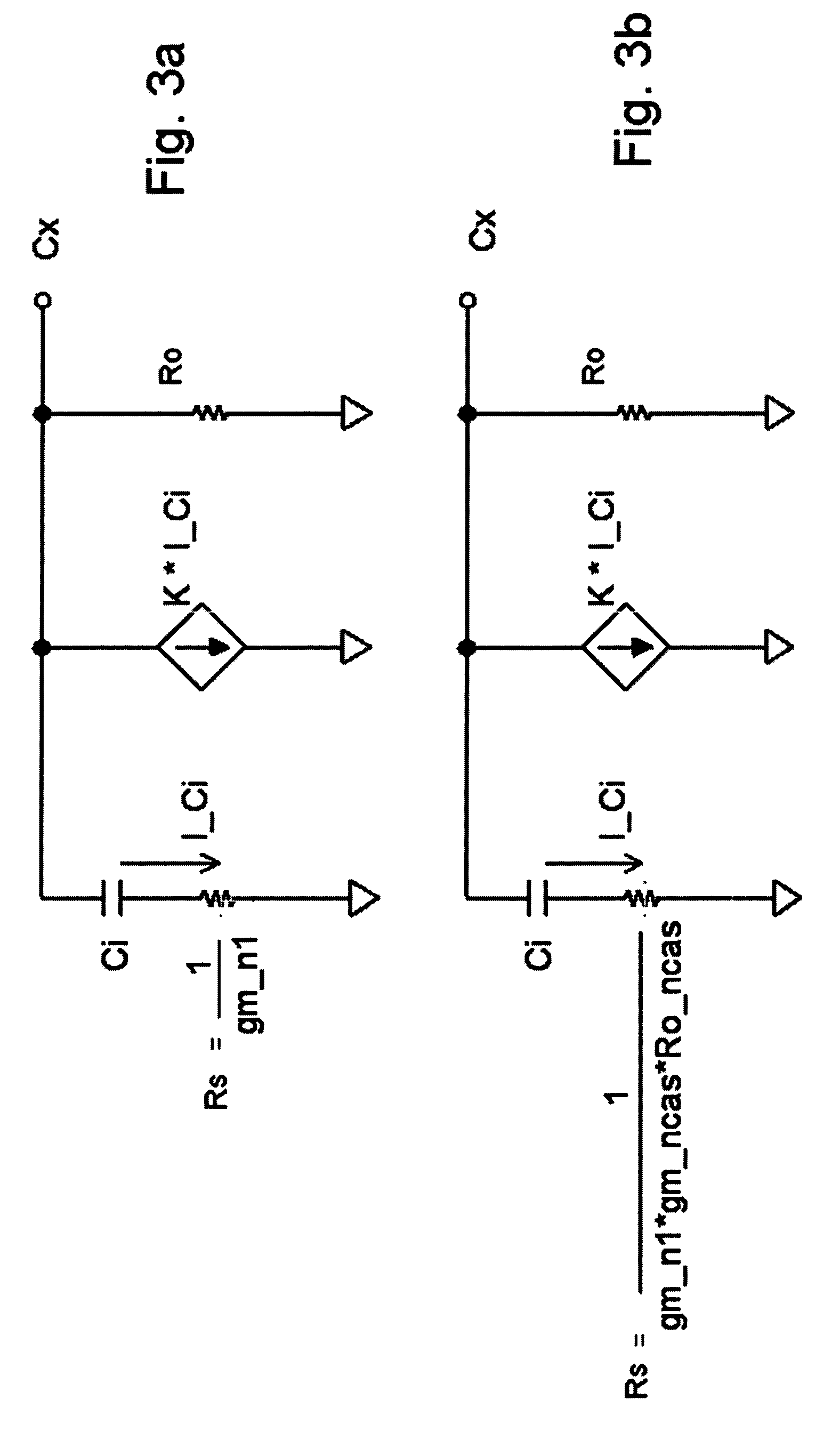

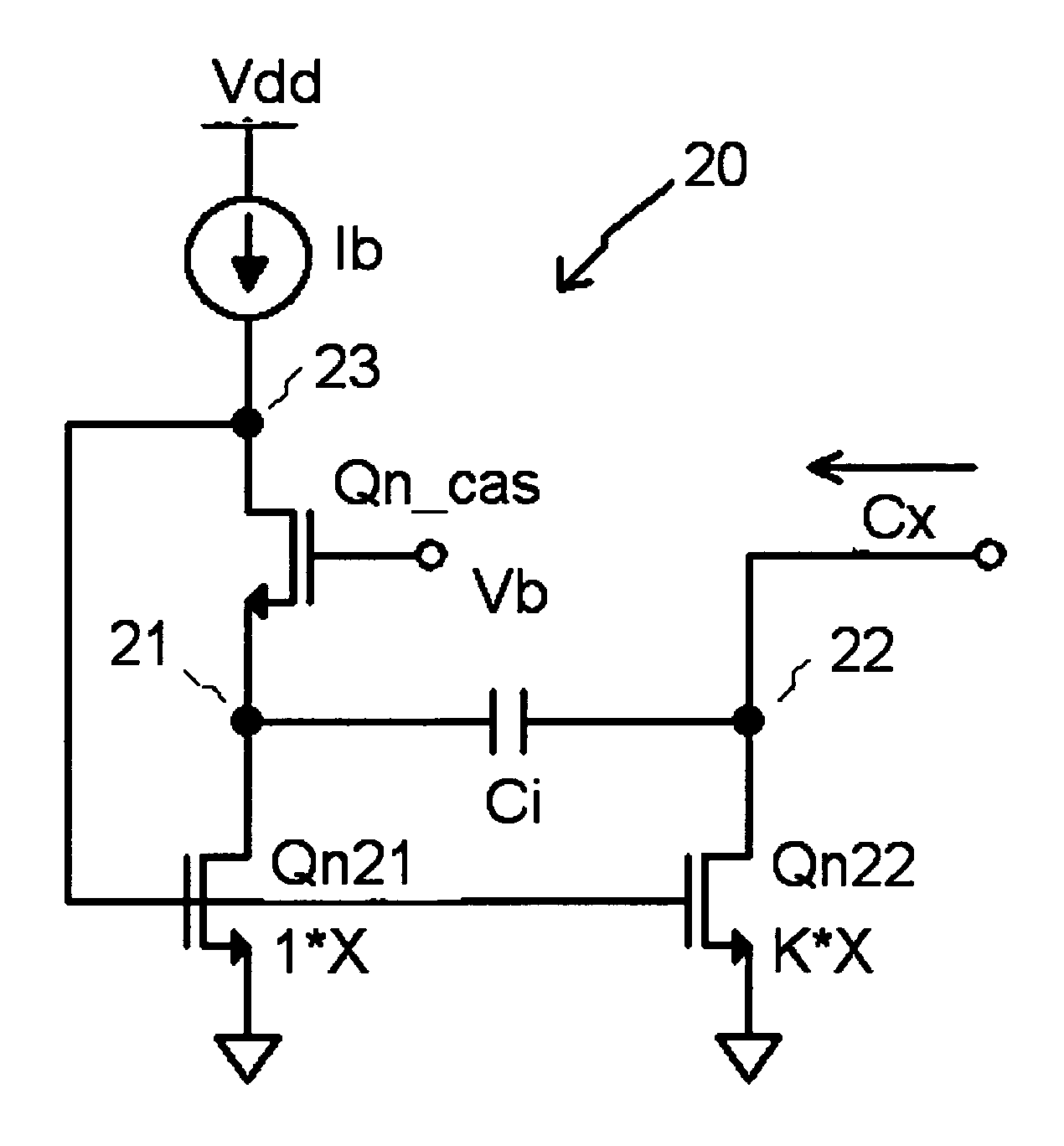

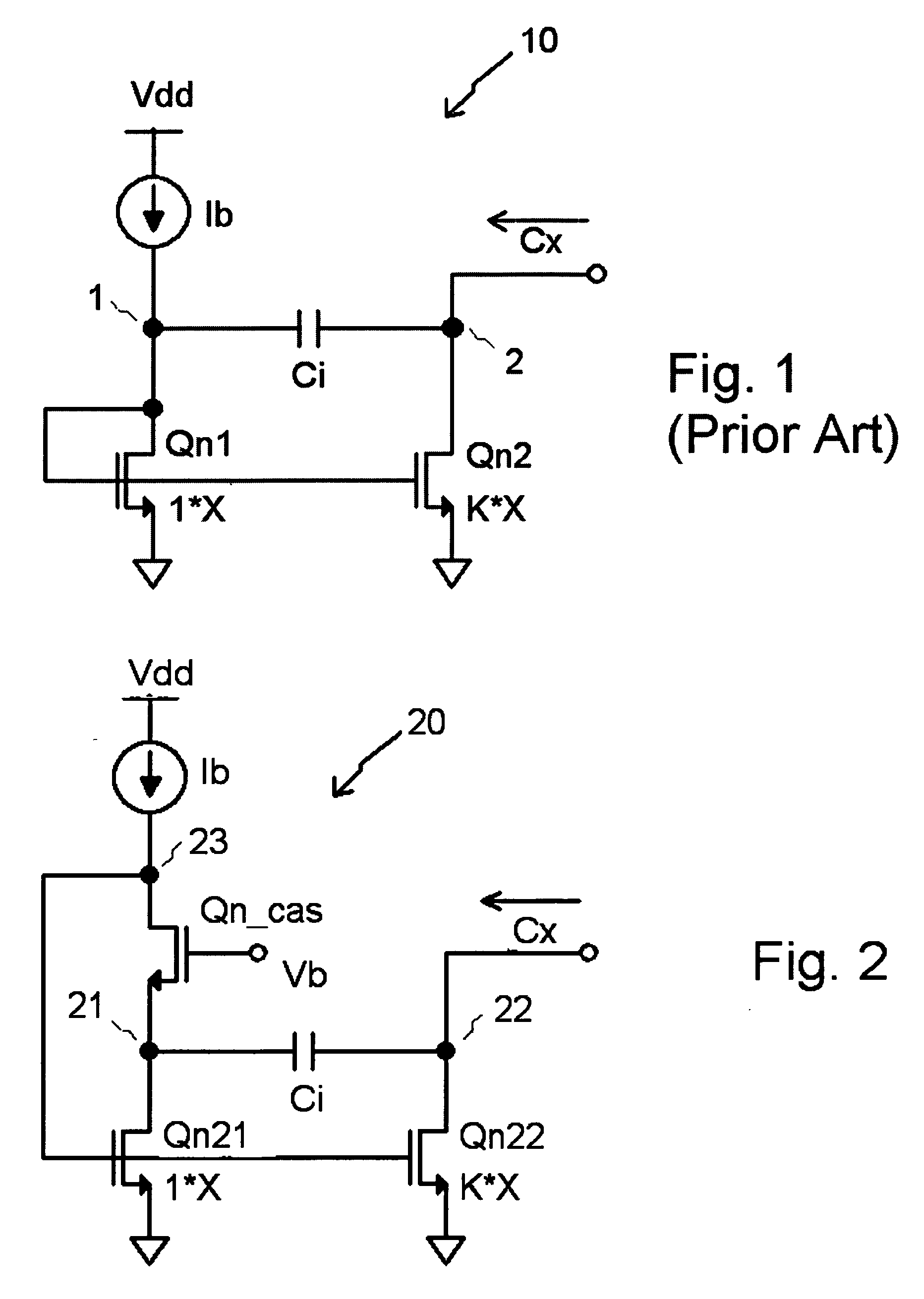

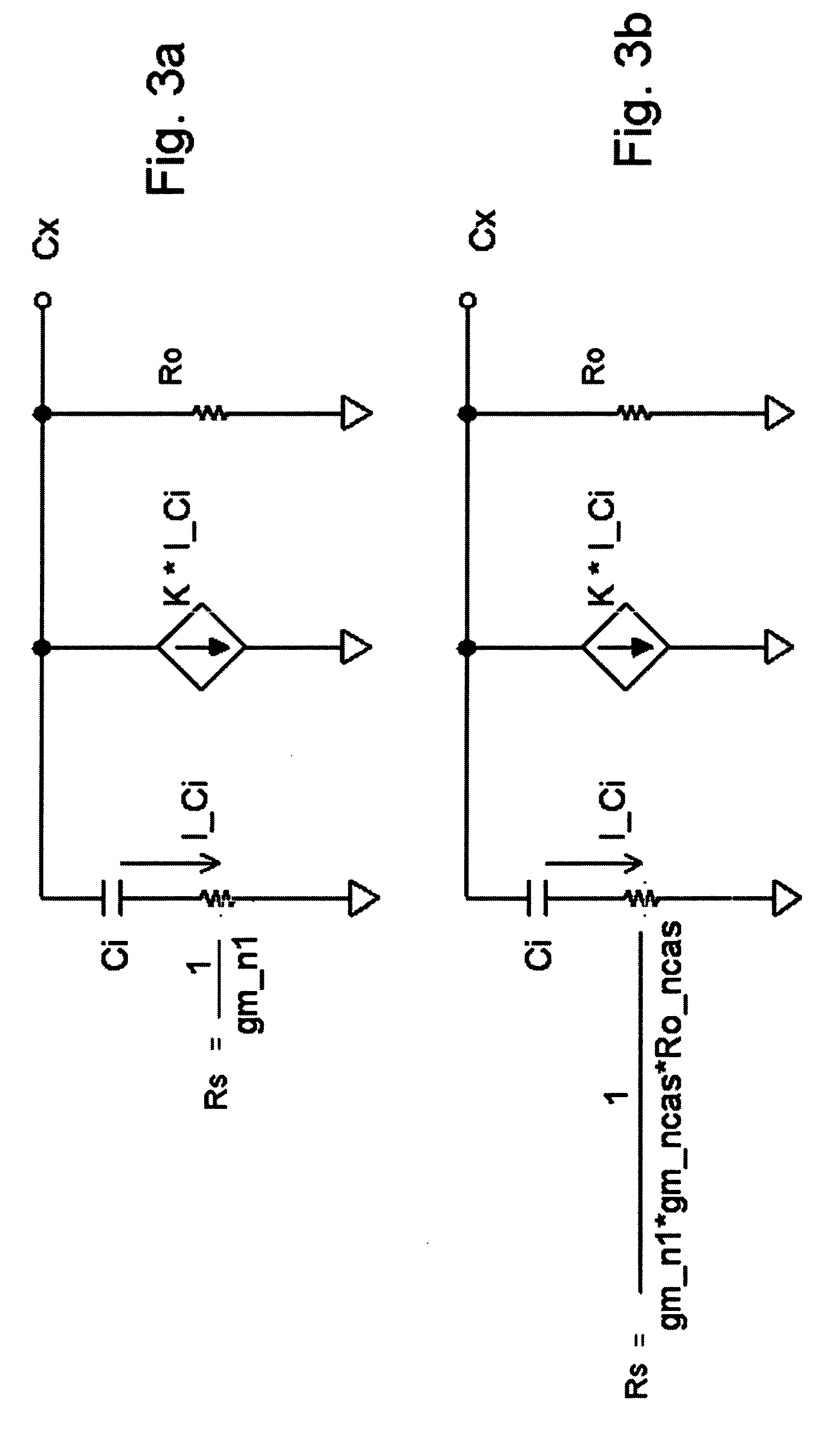

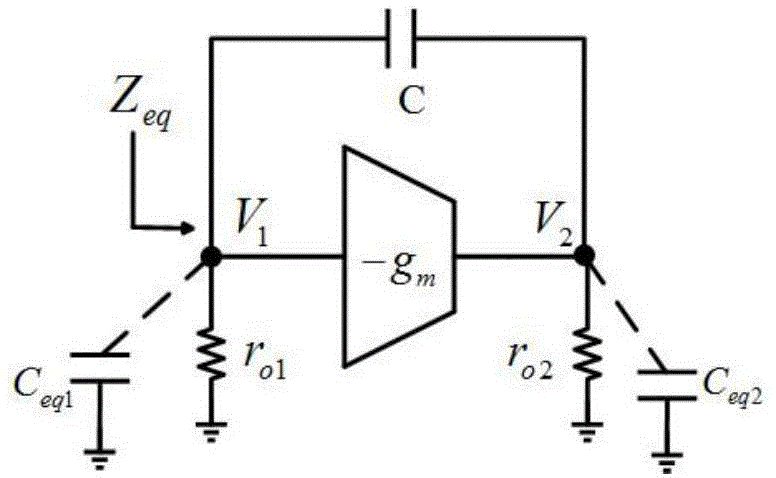

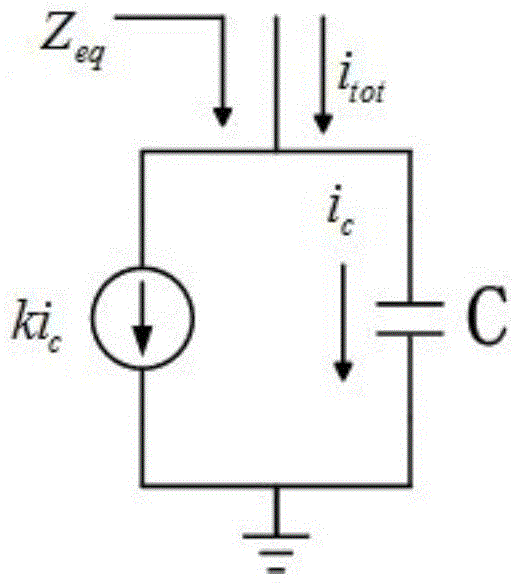

Capacitance multiplier circuit exhibiting improving bandwidth

InactiveUS7113020B2Reduce chip areaLow costNegative-feedback-circuit arrangementsLogic circuits characterised by logic functionCapacitanceFrequency compensation

A monolithic capacitance multiplication circuit serves to reduce the required die area when larger capacitance values are needed such as in filter and loop frequency compensation circuits. A current mirror / cascoding device arrangement reduces the effective series resistance of the multiplier capacitor. As a result, the multiplier topology exhibits improved bandwidth over prior art capacitance multiplier circuits.

Owner:ASAHI KASEI TOKO POWER DEVICE

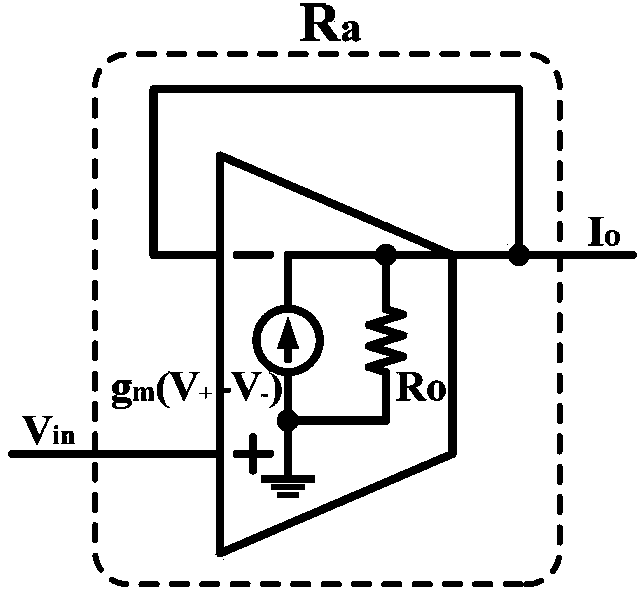

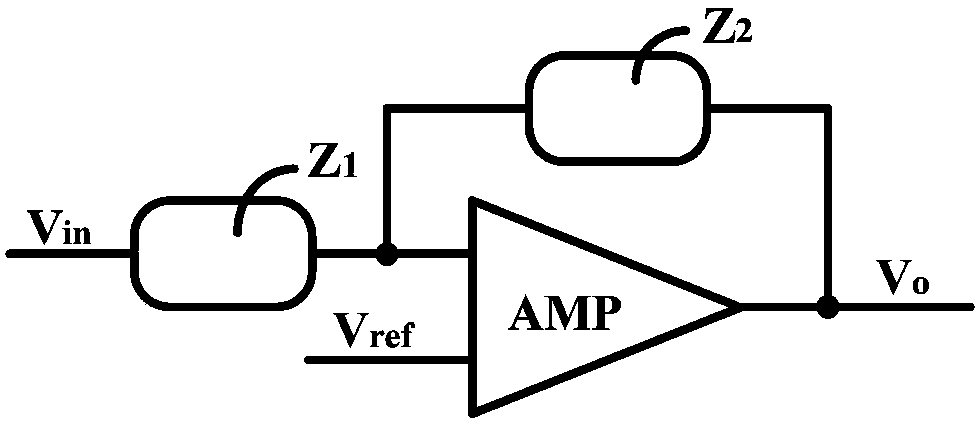

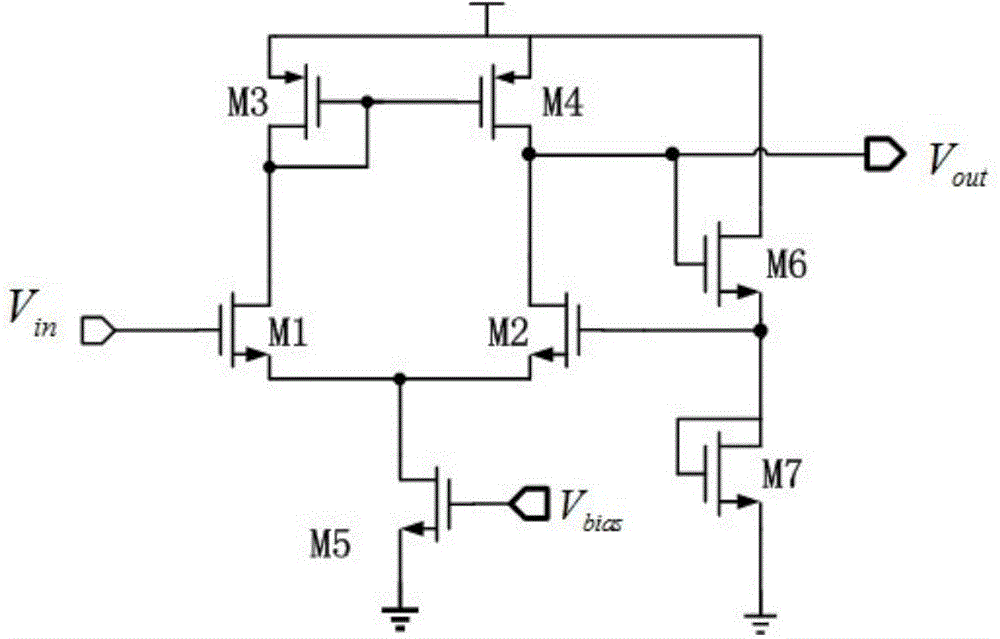

On-chip full integration compensation network based on constant transconductance amplifier and capacitance multiplier

ActiveCN103354419AEasy to adjust the resistanceEasy to adjust capacitanceDc-dc conversionElectric variable regulationCapacitanceResistance capacitance

The invention discloses an on-chip full integration compensation network based on a constant transconductance amplifier and a capacitance multiplier, which can be flexibly applied to a TYPE-I, a TYPE-II and a TYPE-III compensation network structure of a switching DC-DC converter. The on-chip full integration compensation network comprises an impedor Z1, an impedor Z2 and an operational amplifier AMP, wherein an input end of the impedor Z1 is connected to input voltage Vin, and an output end of the impedor Z1 is connected to a first input end of the operational amplifier AMP; an input end of the impedor Z2 is connected to the first input end of the operational amplifier AMP, and an output end of the impedor Z2 is connected to an output end of the operational amplifier AMP; and a second input end of the operational amplifier AMP is connected to reference voltage Vref. According to the invention, the constant transconductance amplifier is adopted to act as an active resistor, the capacitance multiplier acts as an active capacitor, discrete devices such as a passive resistor, a capacitor and the like adopted by the impedor Z1 and the impedor Z2 in a traditional compensation network, thereby realizing on-chip integration, and improving the system integration degree; the on-chip full integration compensation network is simple in structure and easy to design, and has excellent process corner resisting stability; and the design is universal, thereby being convenient for popularization and expansion.

Owner:XI AN JIAOTONG UNIV

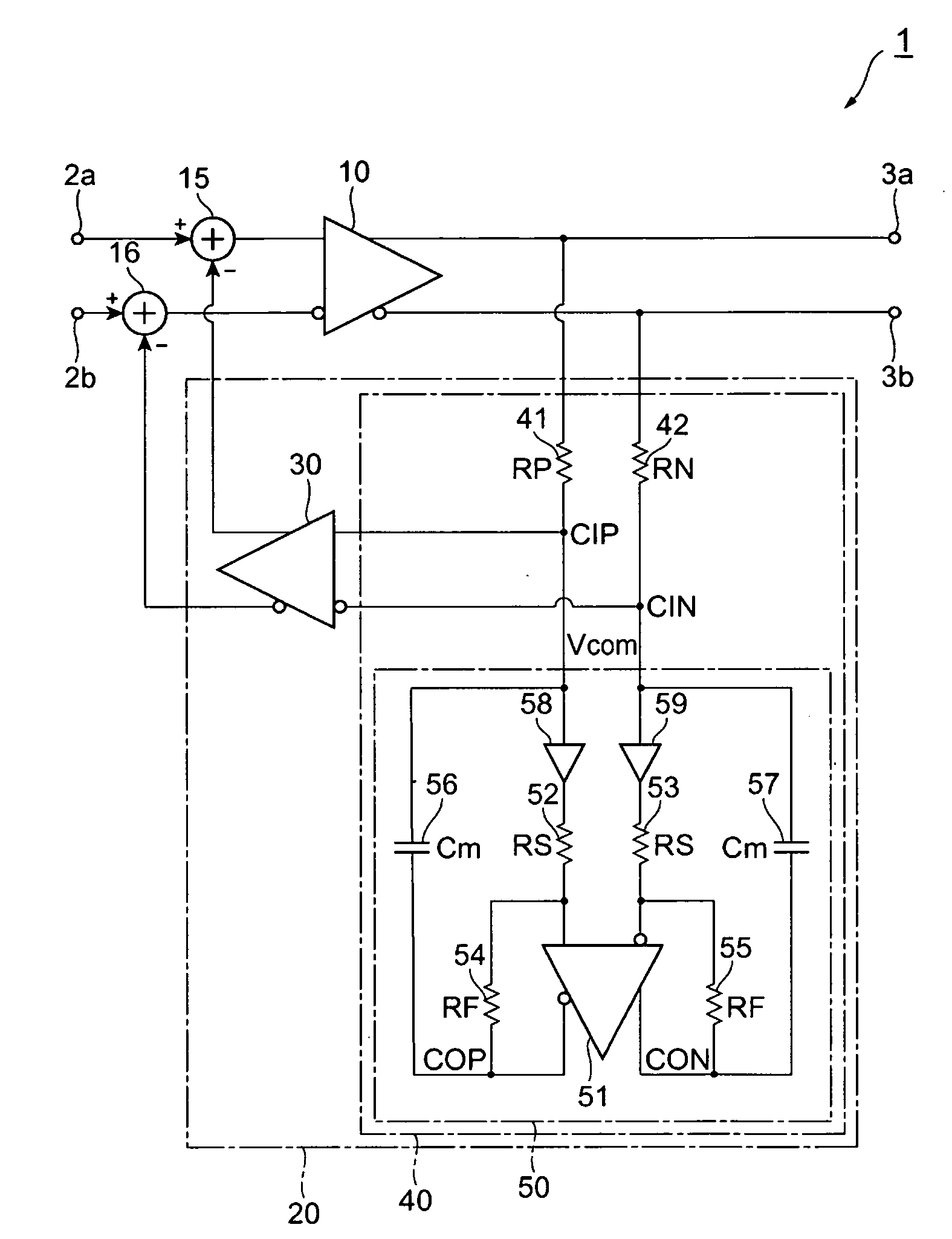

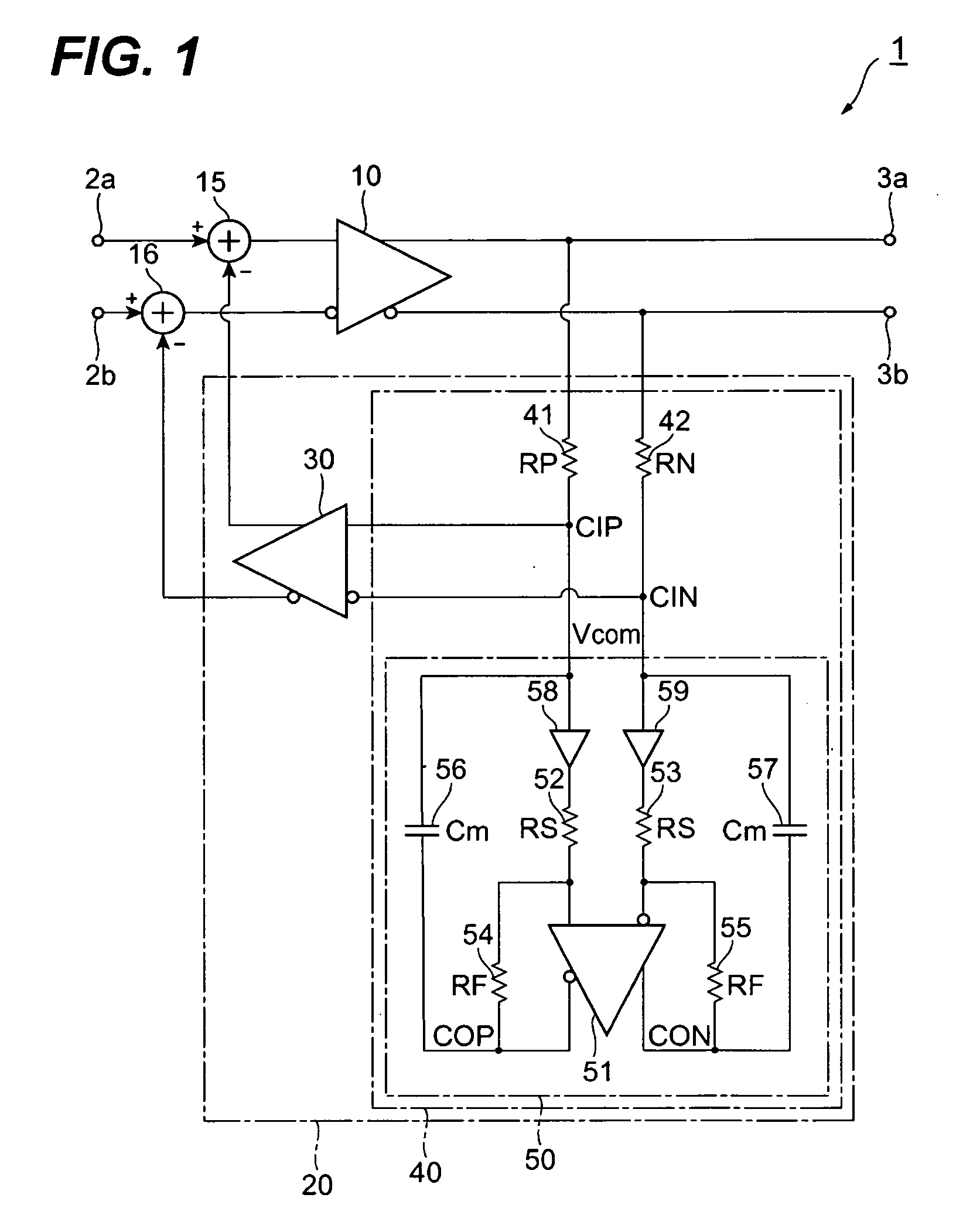

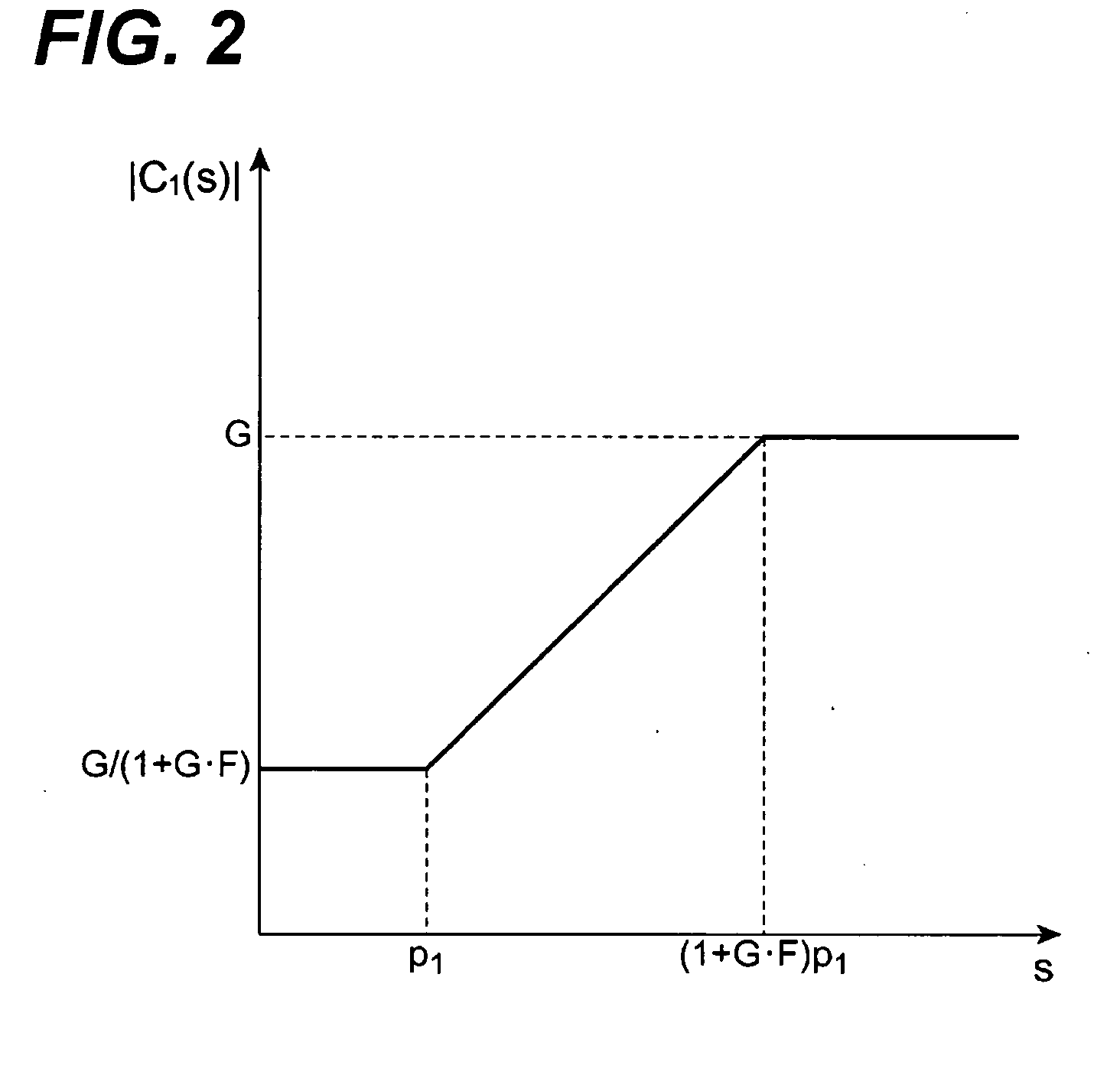

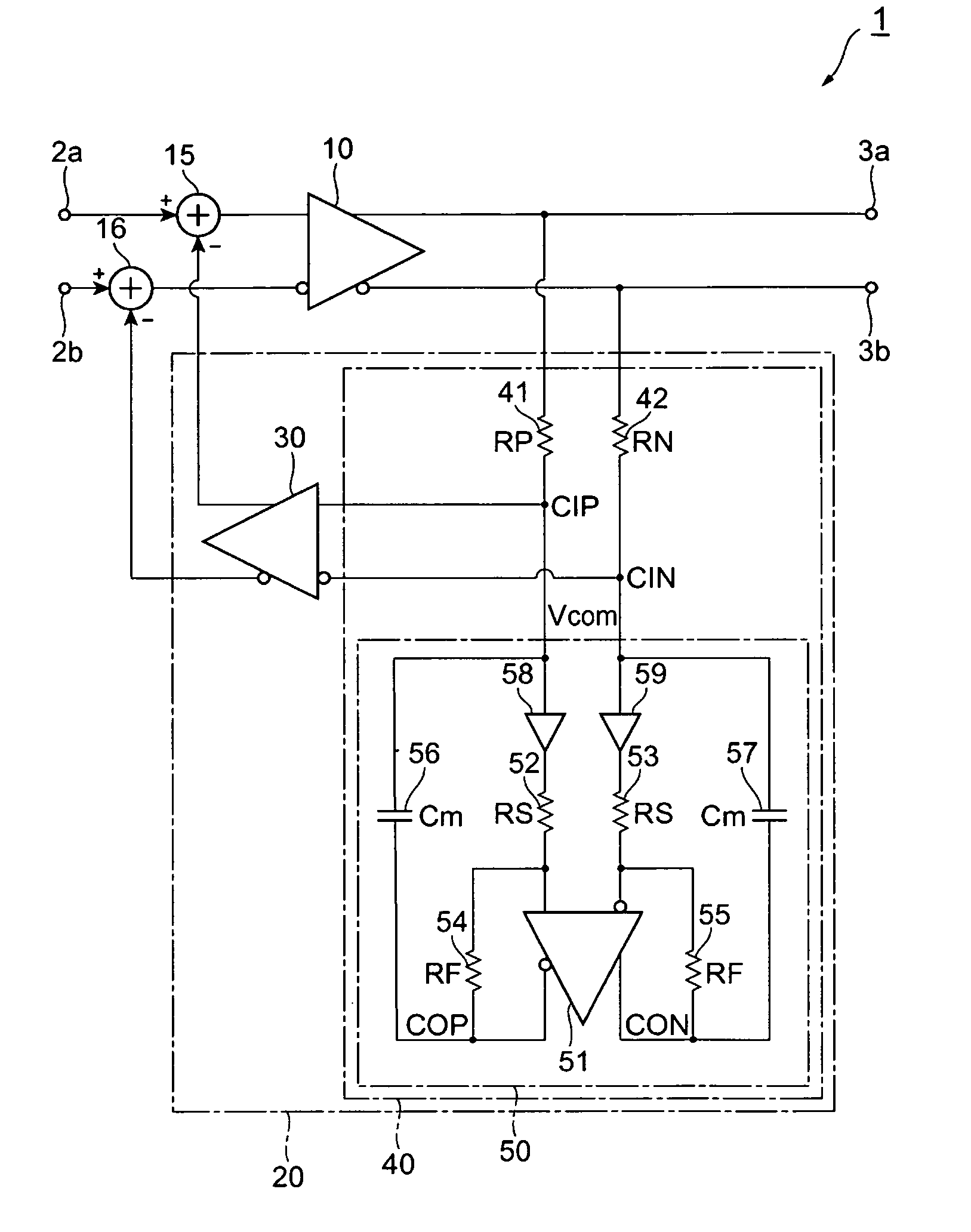

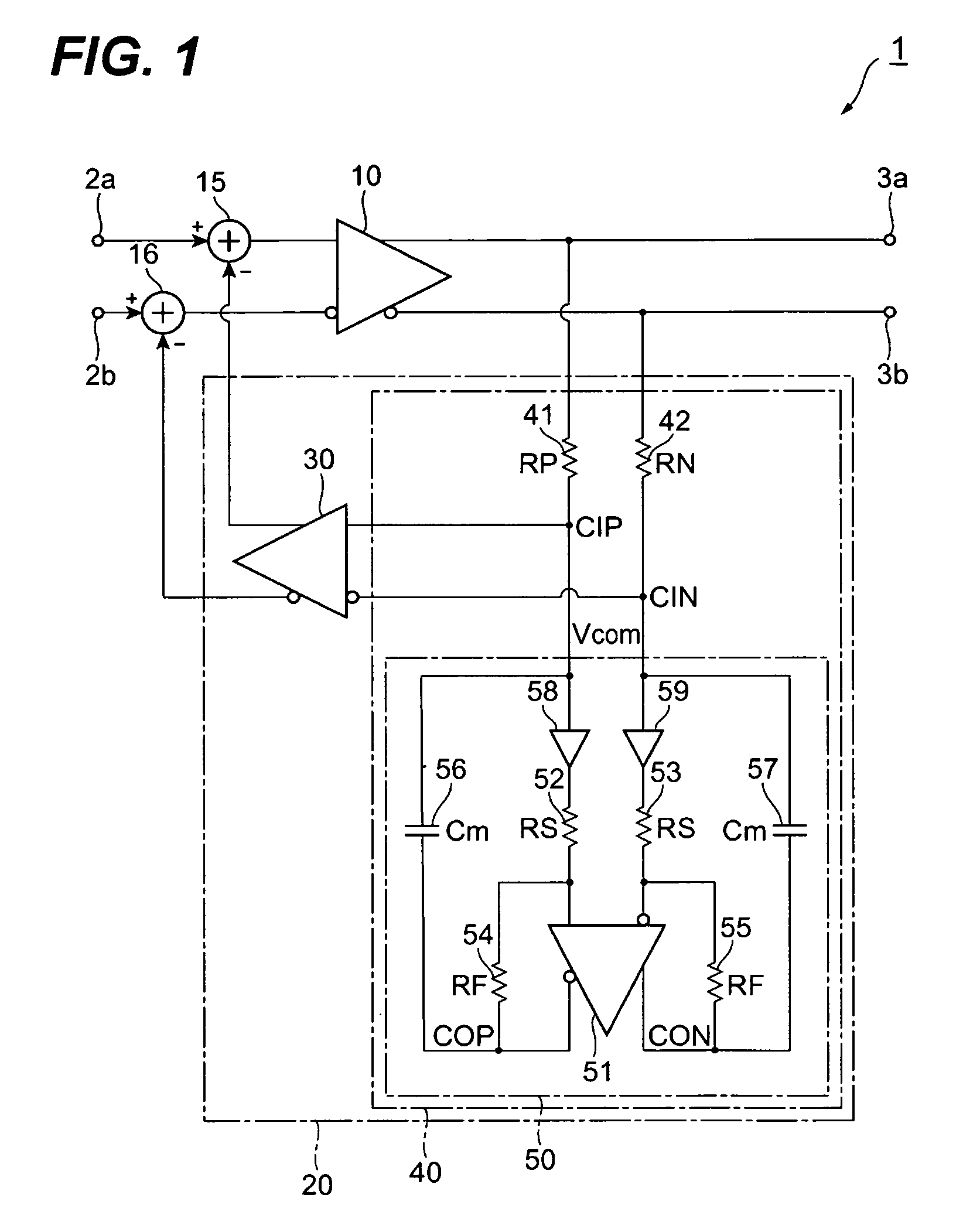

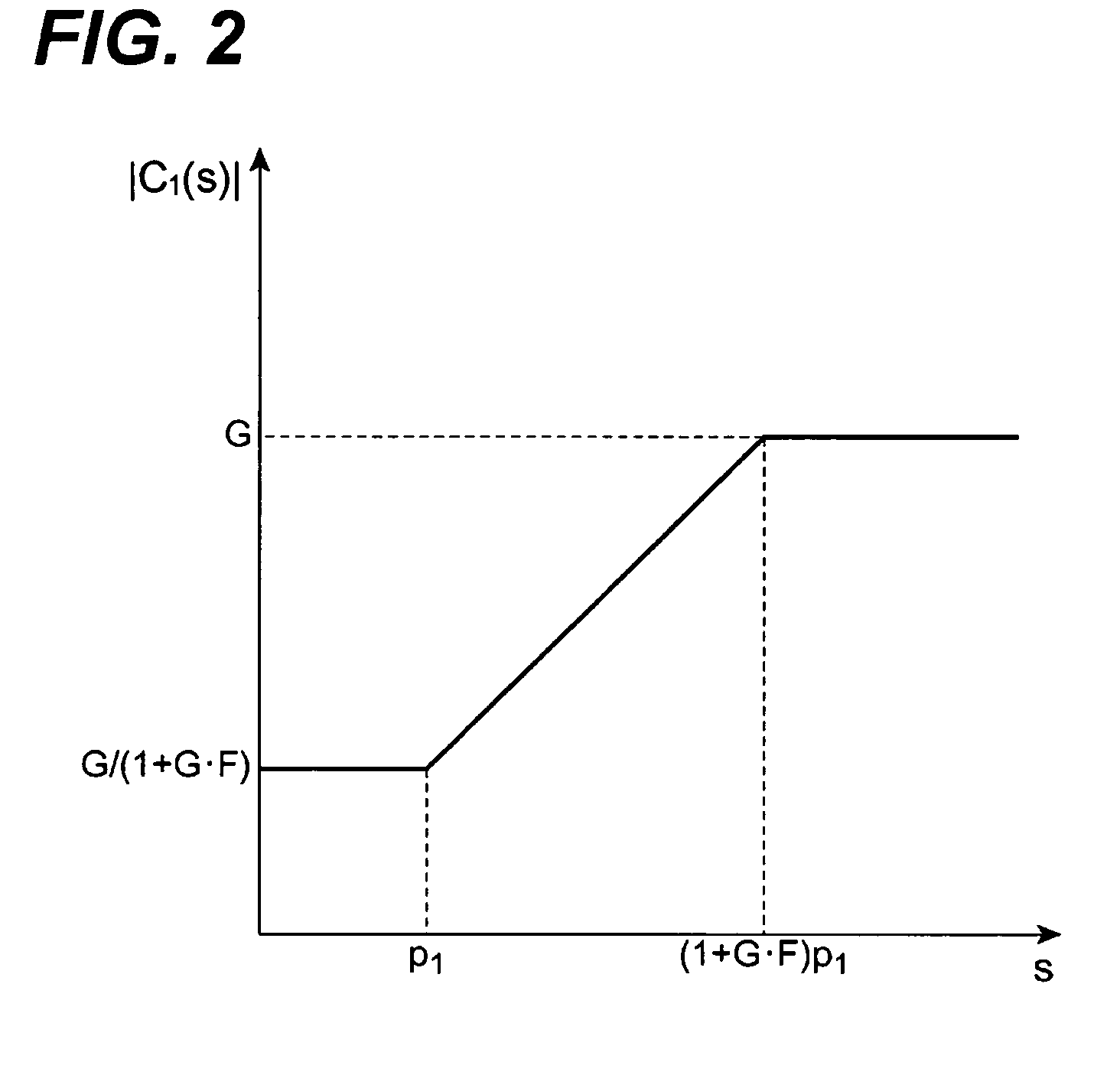

Differential circuit providing a function to cancel input offset voltage

ActiveUS20090079502A1Amplifier modifications to raise efficiencyDifferential amplifiersCapacitanceOffset cancellation

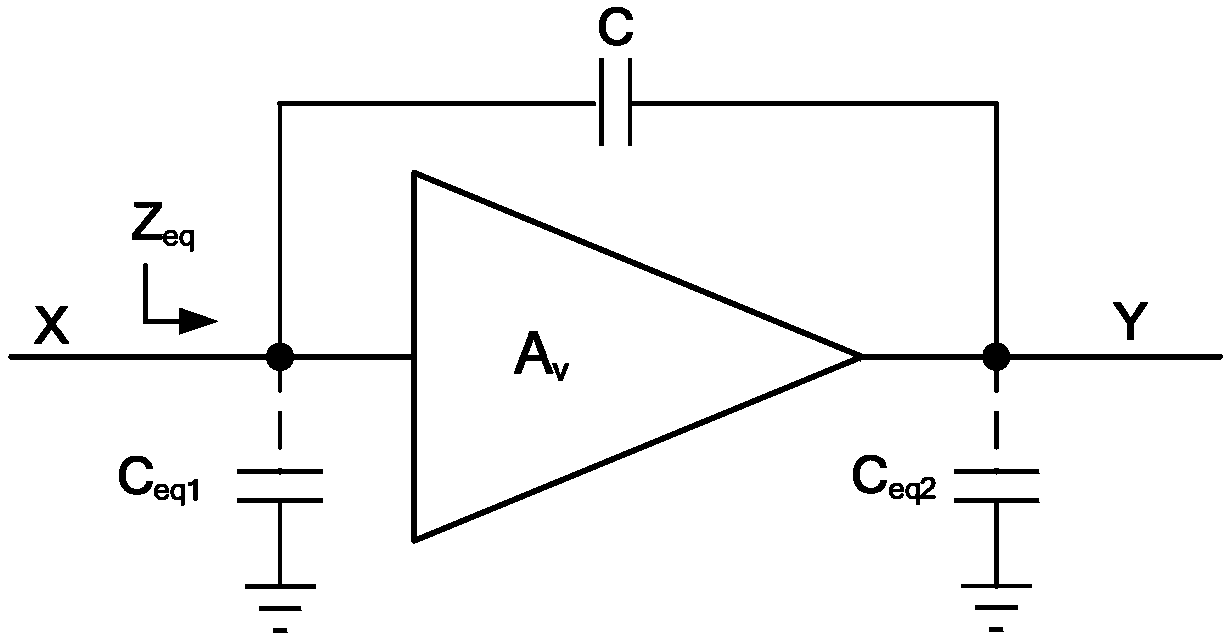

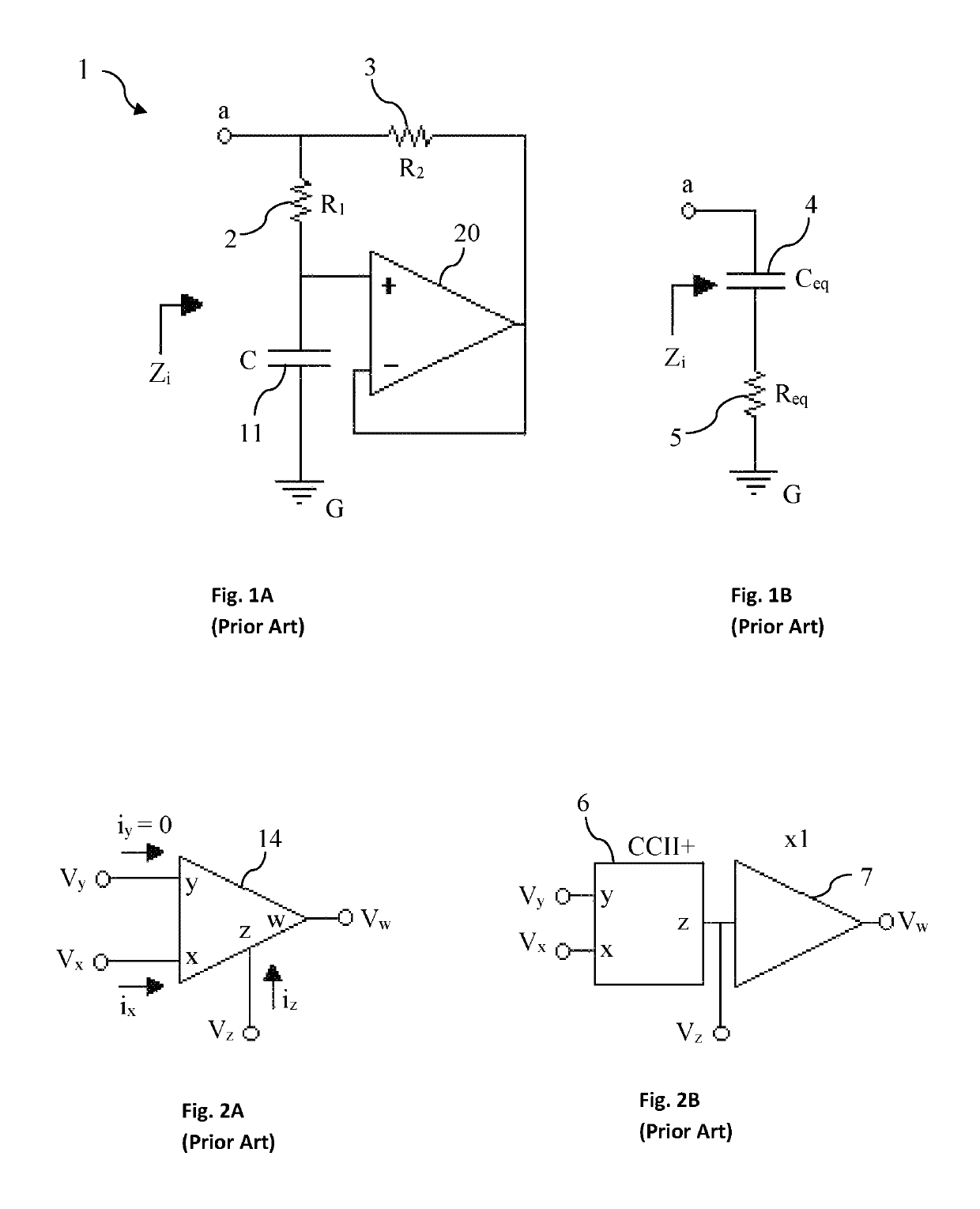

A new offset canceling circuit for a differential circuit is disclosed whose input offset voltage may be cancelled independent of the variation of the input level, accordingly, enables the cut-off frequency of the canceling circuit unchanged. The offset canceller of the invention provides a buffer amplifier and a filter. The filter includes a capacitance multiplier including an operational amplifier (Op-Amp) operating in the inverting mode and a capacitor connected between the input and output of the Op-Amp. The Op-Amp operating in the inverting mode whose closed loop gain is solely determined by resistors, and the capacitance of the capacitor is multiplied by the closed loop gain of the Op-Amp by the Miller effect.

Owner:SUMITOMO ELECTRIC IND LTD

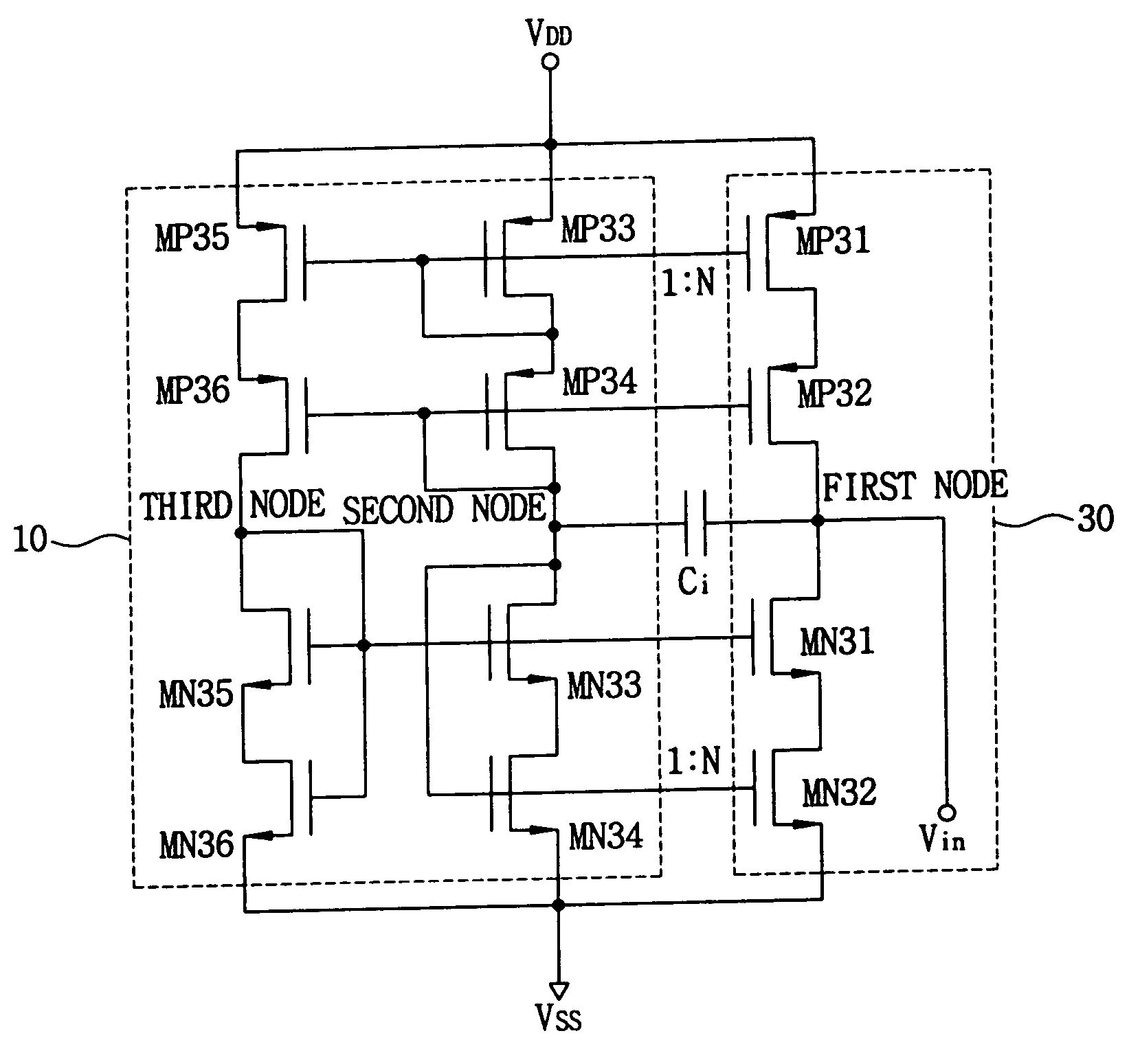

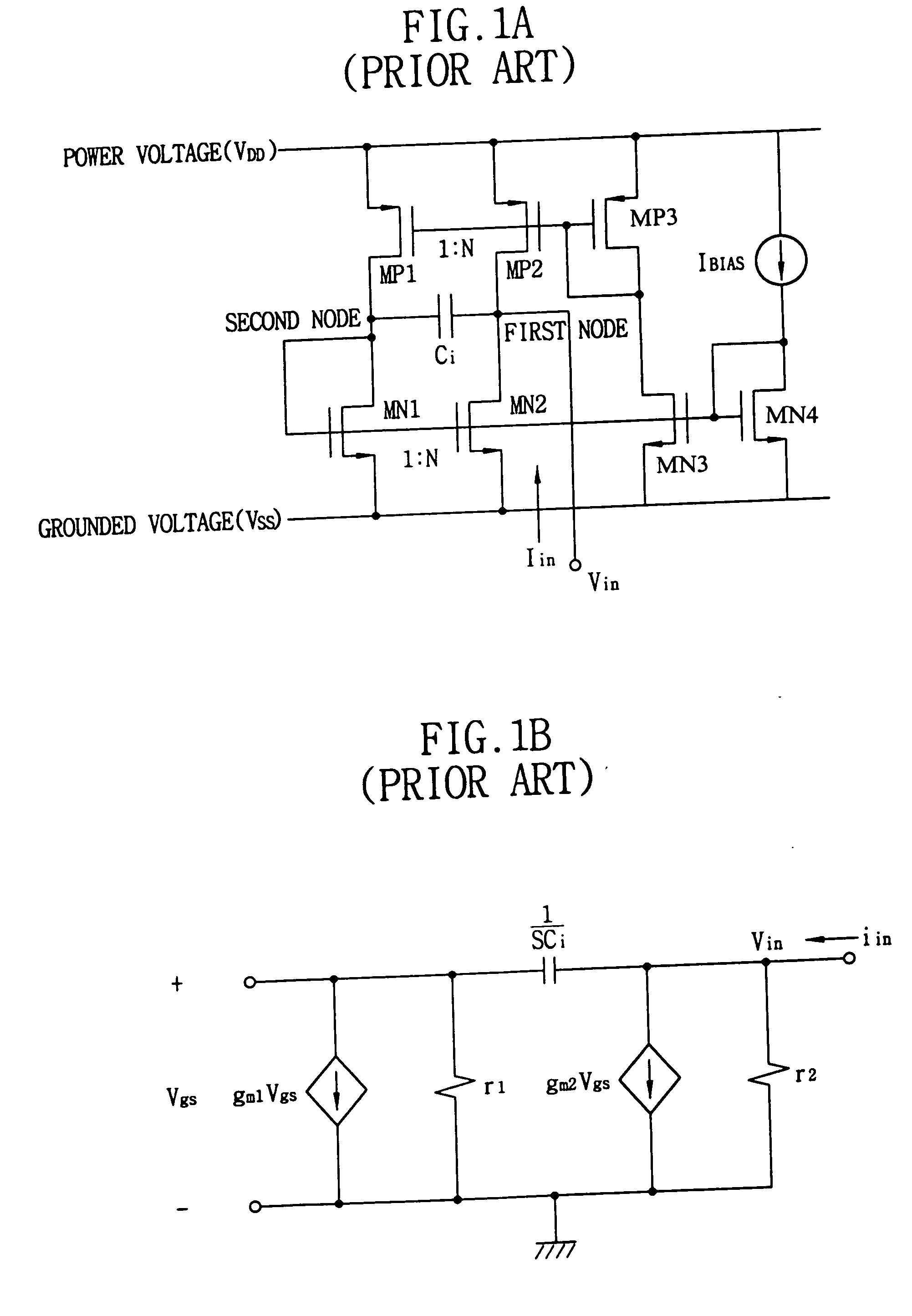

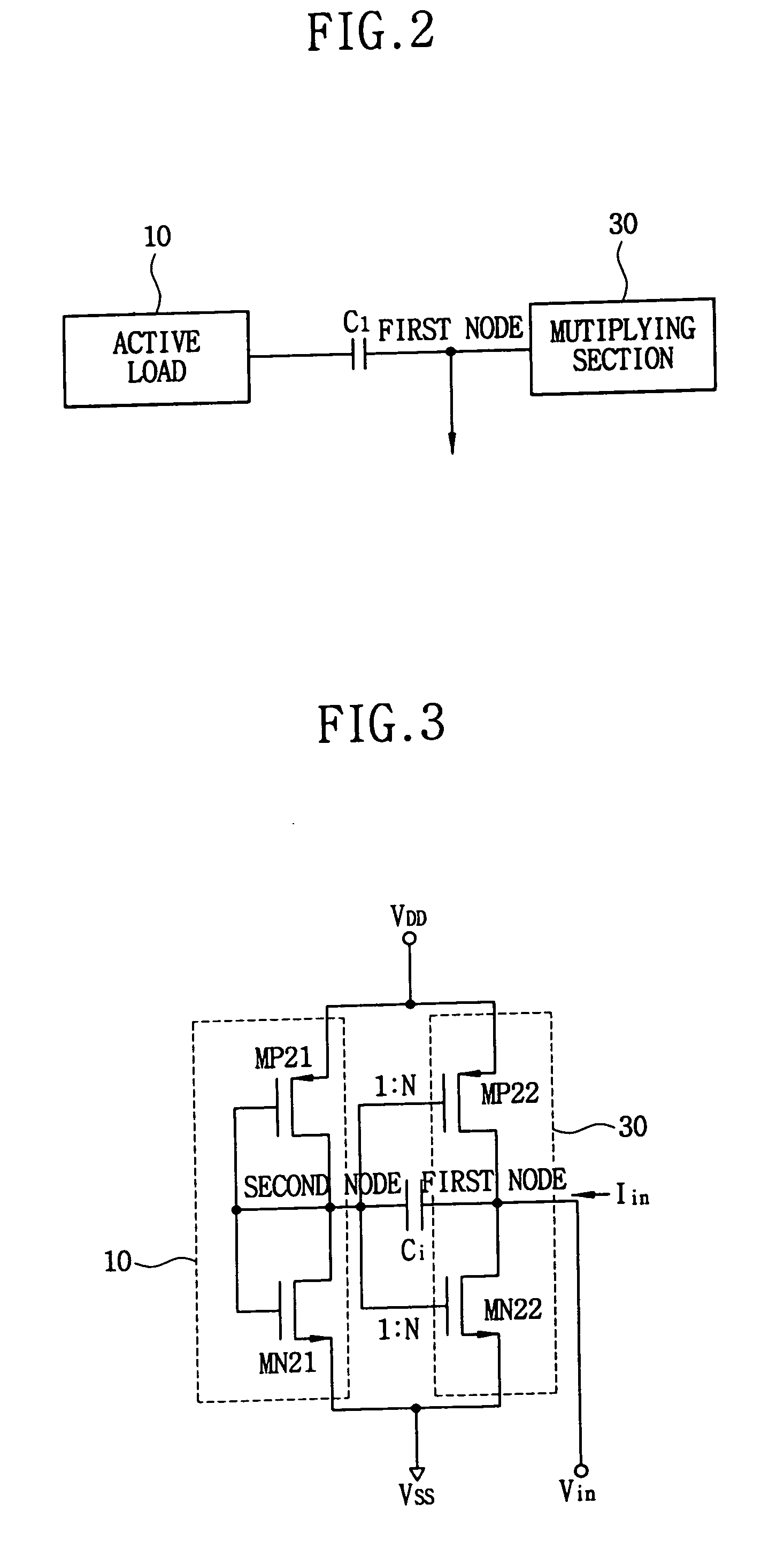

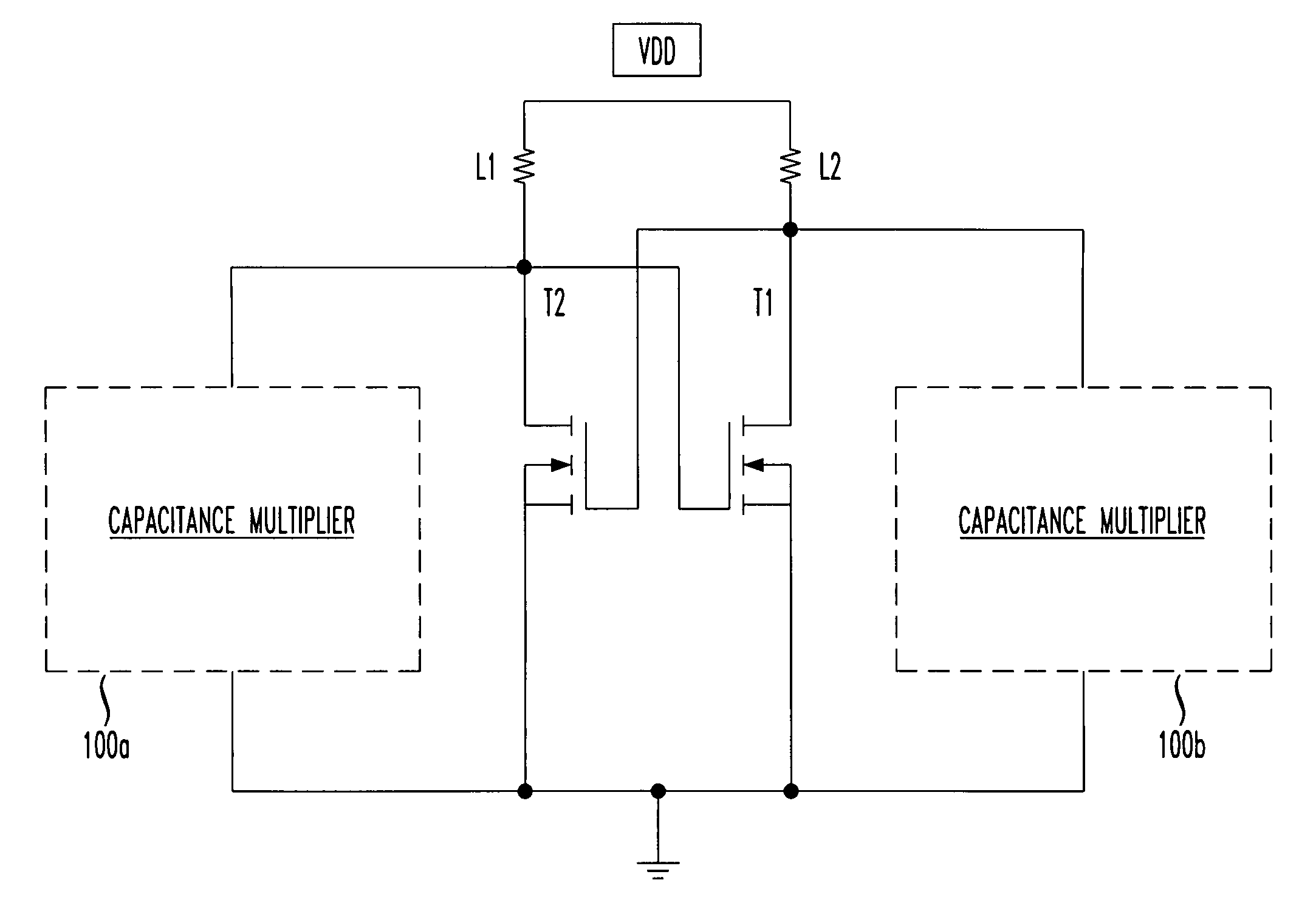

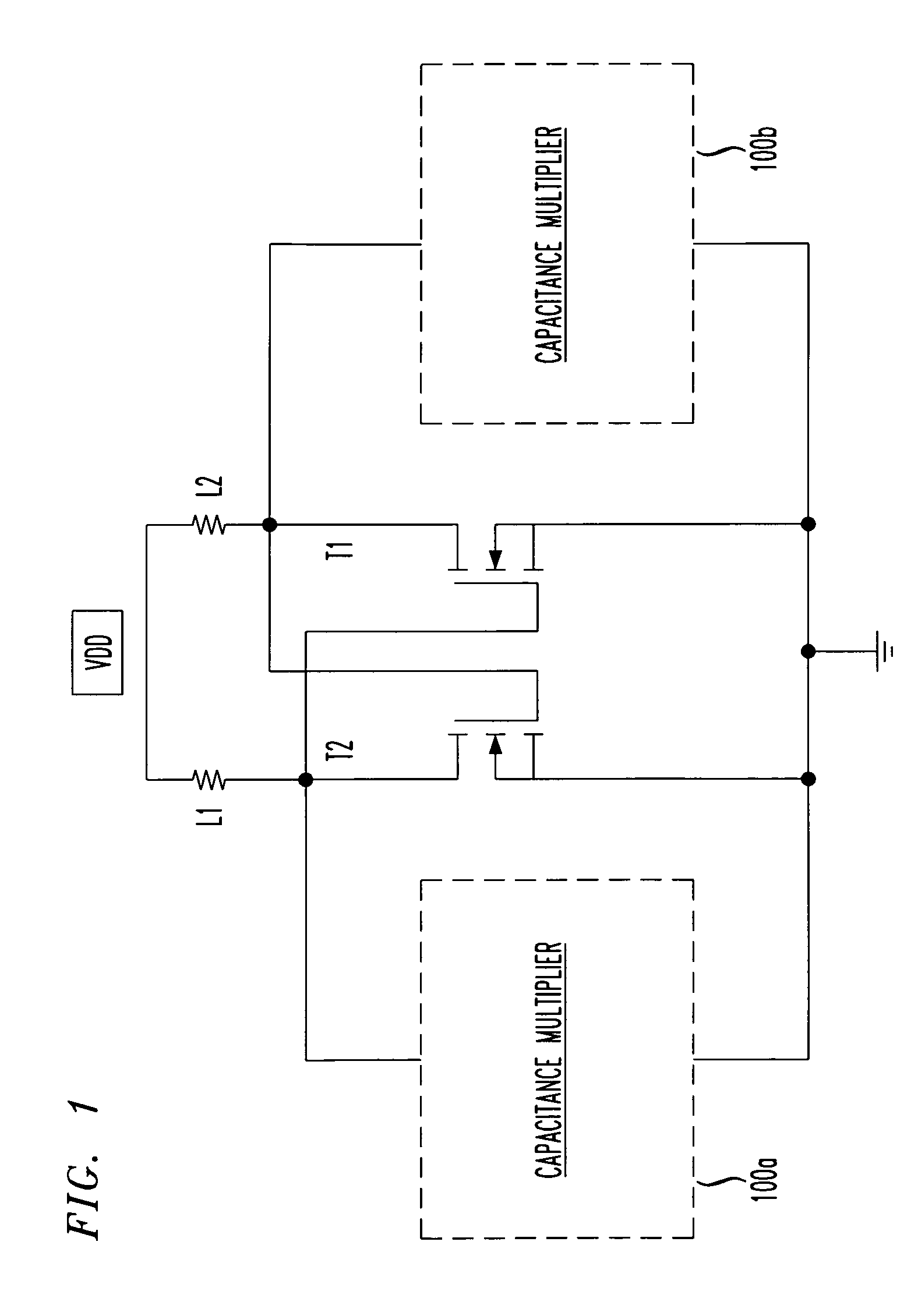

Capacitance multiplier

ActiveUS20050099221A1High bandwidthReduce areaComputations using contact-making devicesNetwork simulating reactancesCapacitanceDischarge efficiency

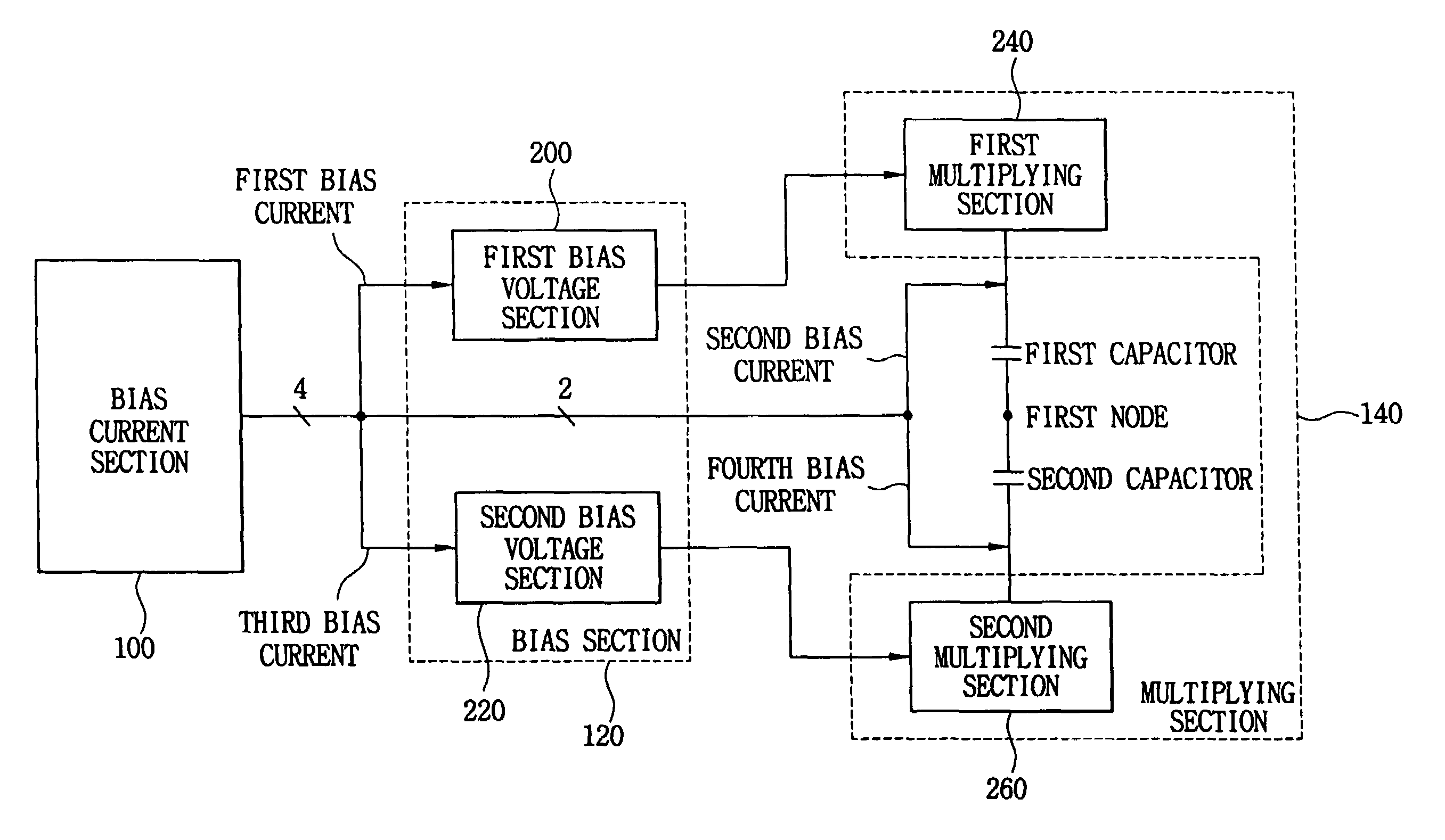

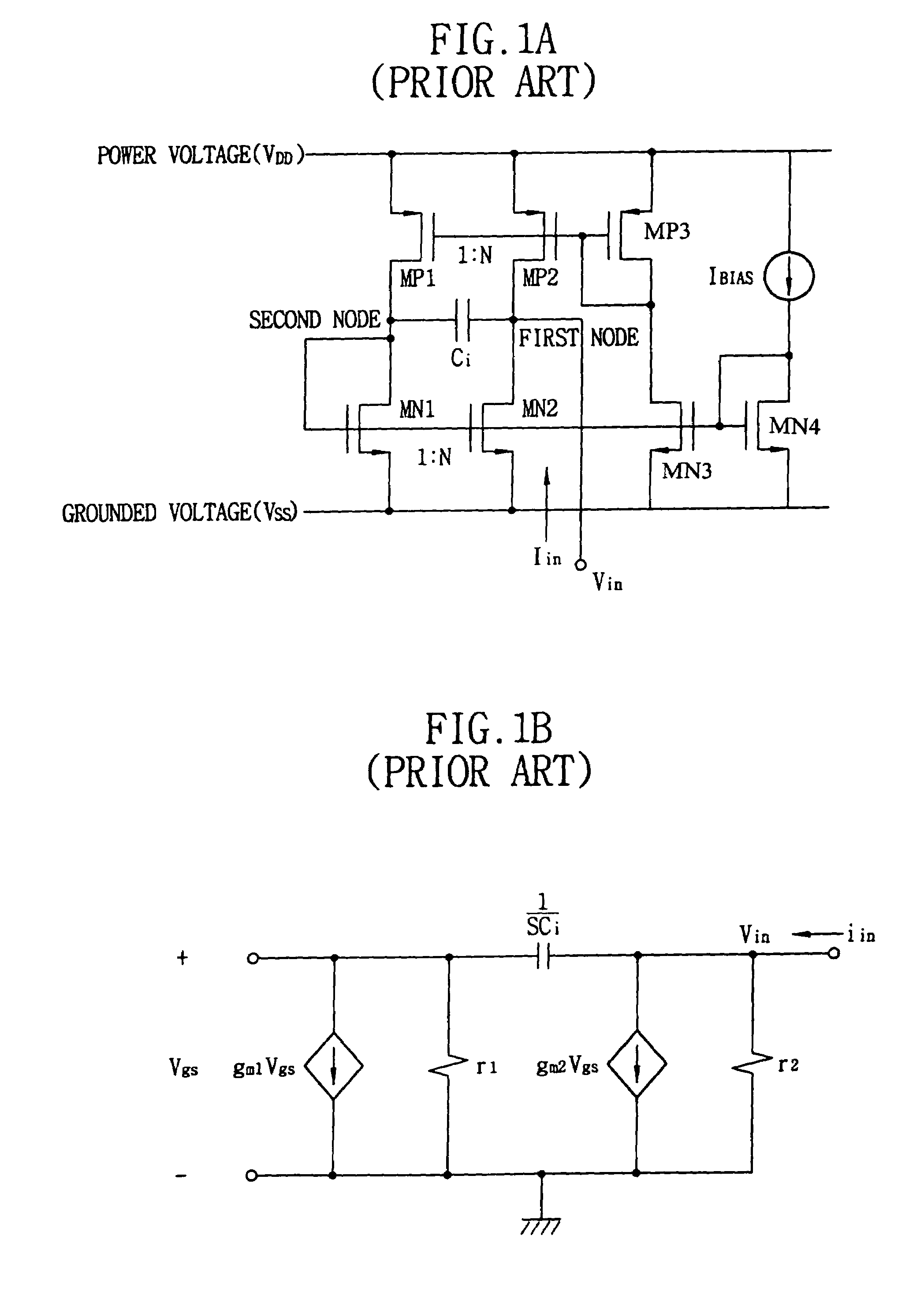

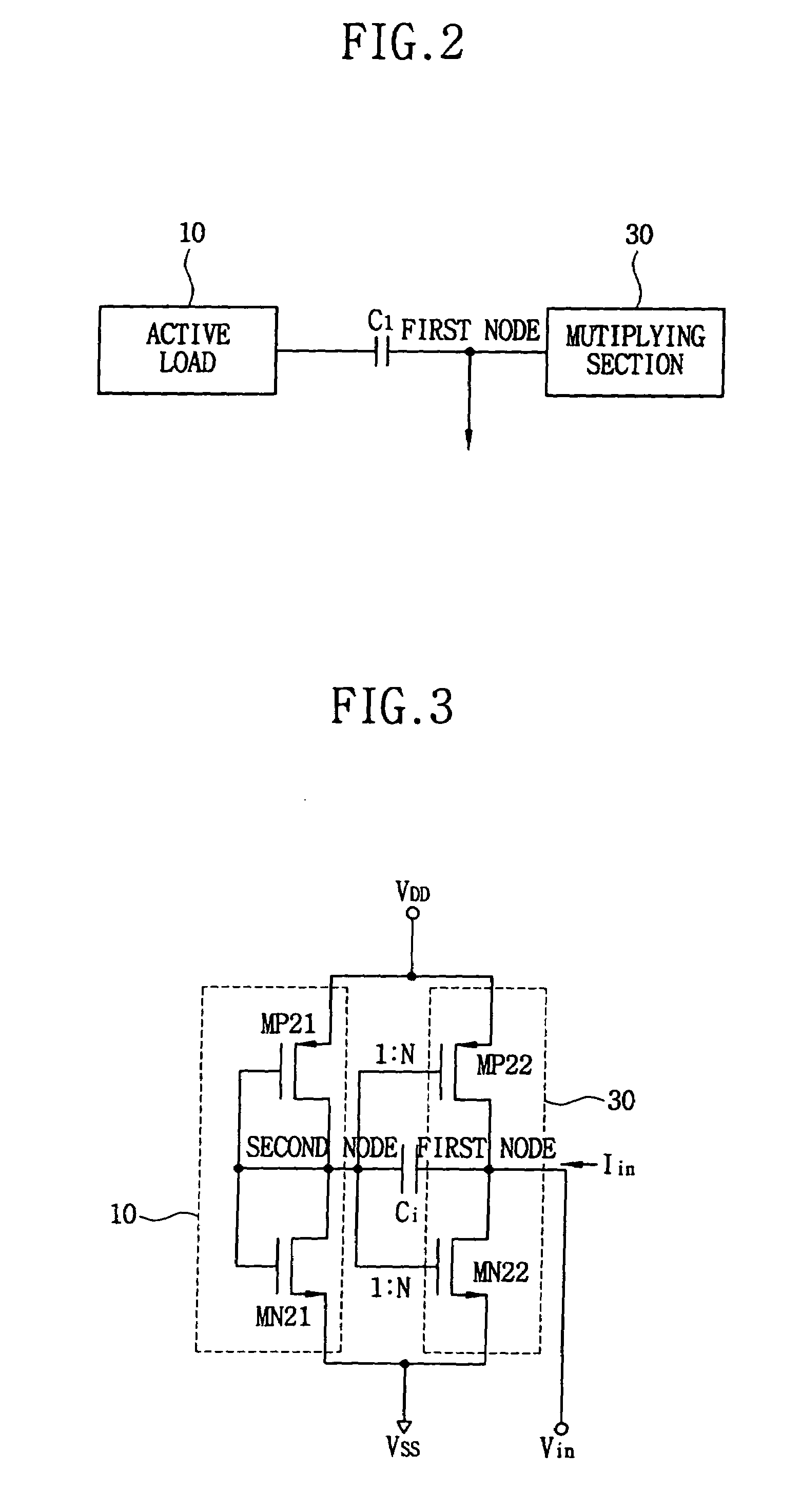

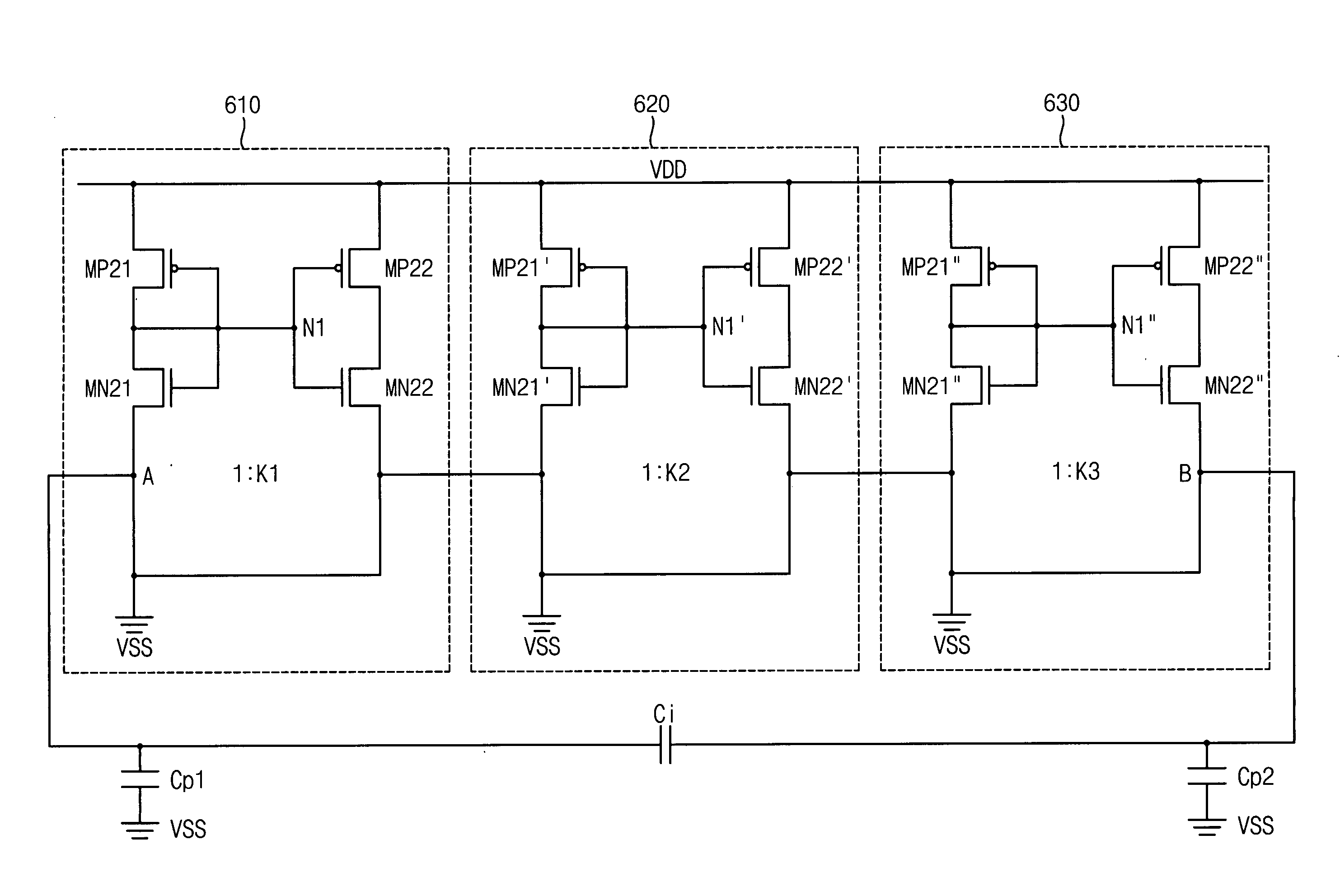

A capacitance multiplier includes a self-biasing active load for generating a stable bias voltage without a separate current bias. In addition, the capacitance multiplier includes a cascode load within a multiplying section for increasing the output resistance and in turn the charging / discharging efficiency. Furthermore, the capacitance multiplier is implemented with a plurality of multiplying paths to reduce effects of noise for more stable generation of the multiplied capacitance.

Owner:SAMSUNG ELECTRONICS CO LTD

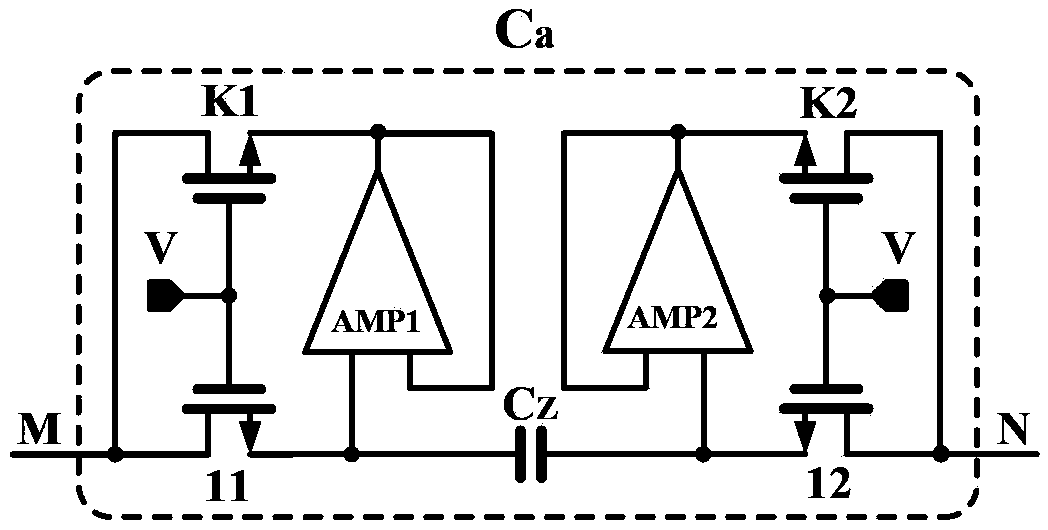

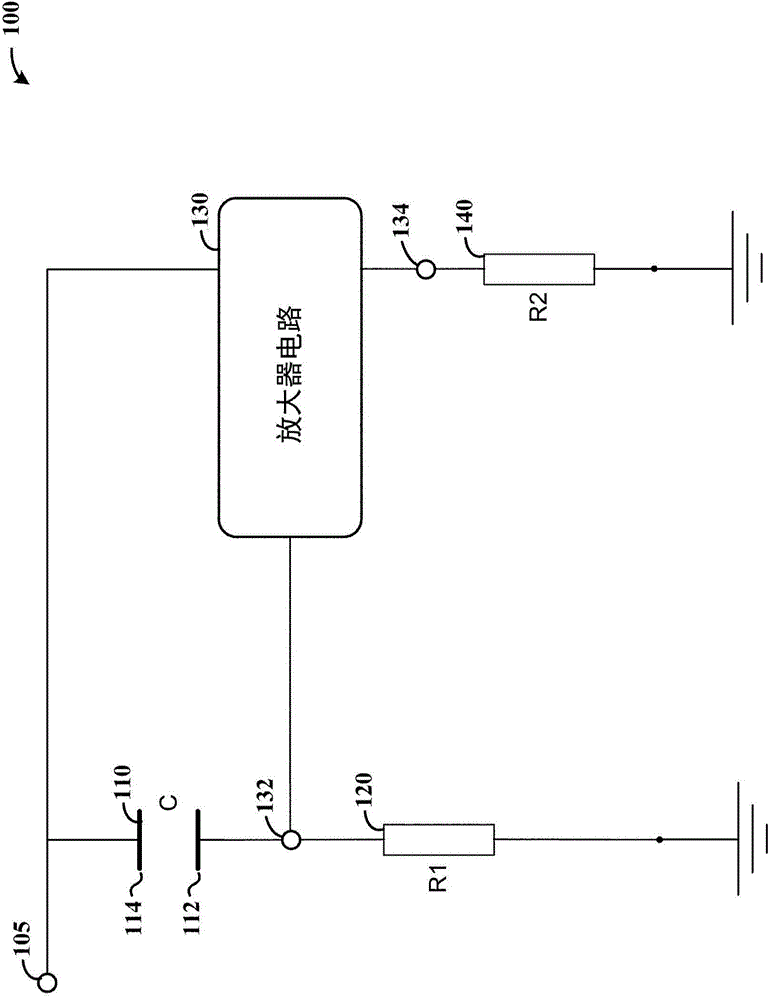

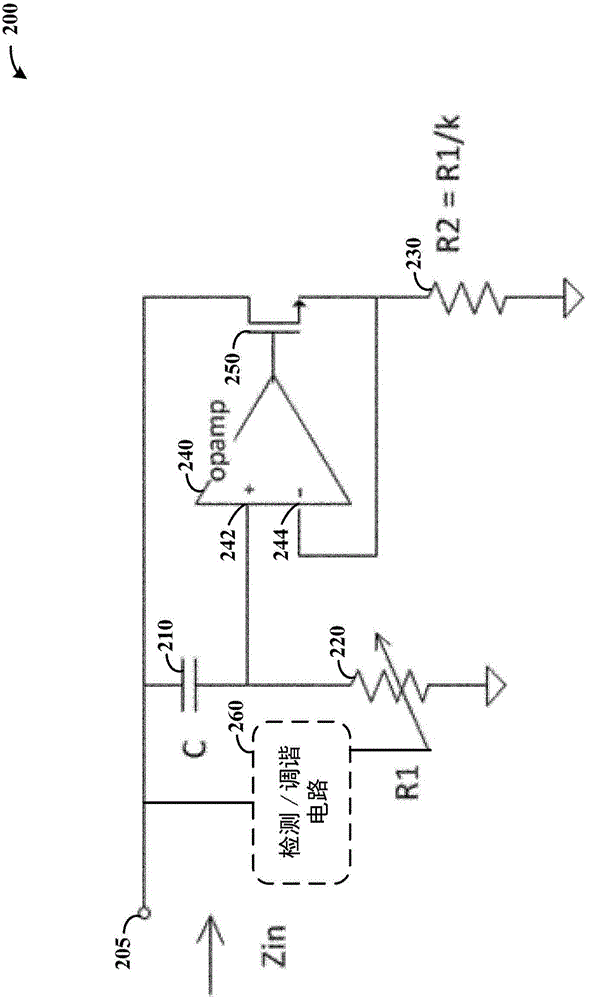

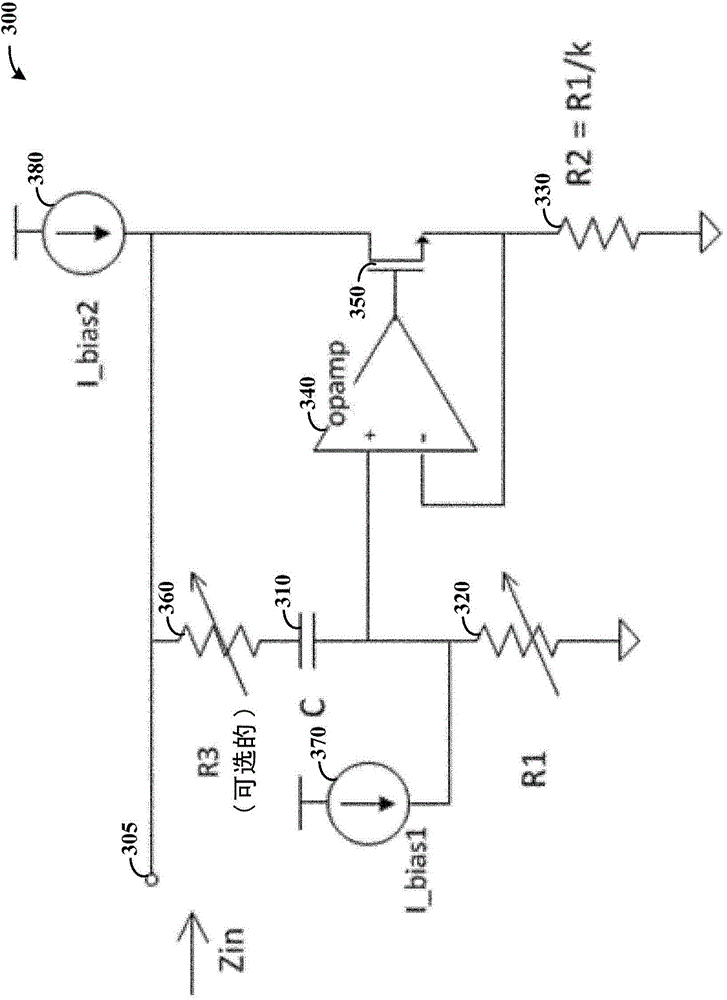

Capacitance multiplier and method

ActiveCN105048991AApparatus without intermediate ac conversionOne-port active networksCapacitanceEngineering

Capacitance multiplier circuitry provides an increased equivalent capacitance, and may be implemented using a desirably small footprint. As may be implemented in accordance with one or more embodiments, a capacitor provides a first capacitance across first and second plates, and capacitance multiplier circuitry operates with the capacitor to provide a second equivalent capacitance that is a multiple of the first capacitance. The capacitance multiplier circuitry includes a first circuit path having a first resistor between the first plate and a common terminal, and a second circuit path having a switch and a second resistor between the second plate and the common terminal. An amplifier has differential inputs respectively corresponding to the first and second circuit paths and provides the second equivalent capacitance by controlling operation of the switch based upon the differential inputs and the respective resistances provided by the resistors in the first and second circuit paths.

Owner:NXP BV

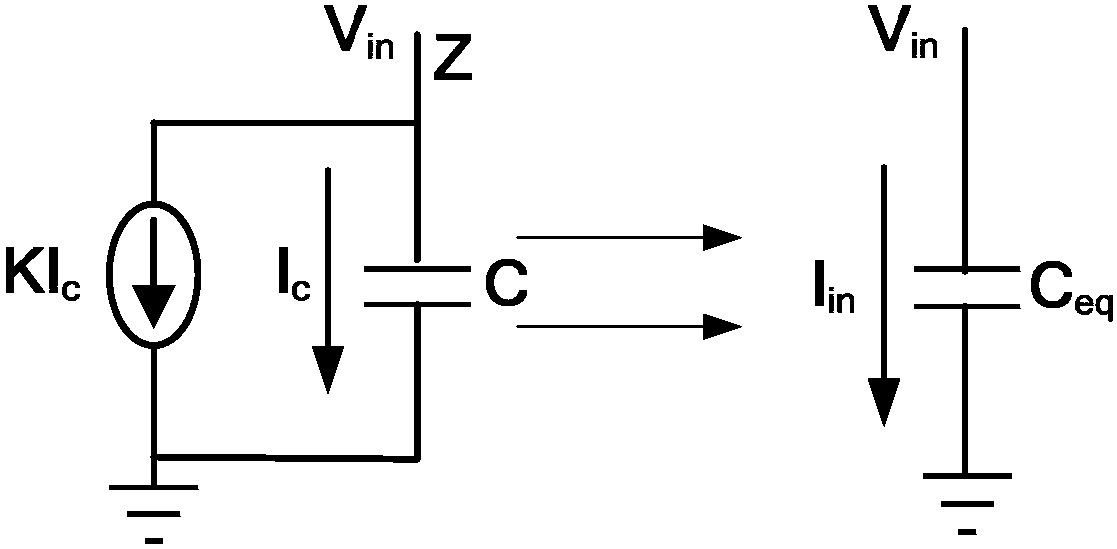

Capacitance multiplier

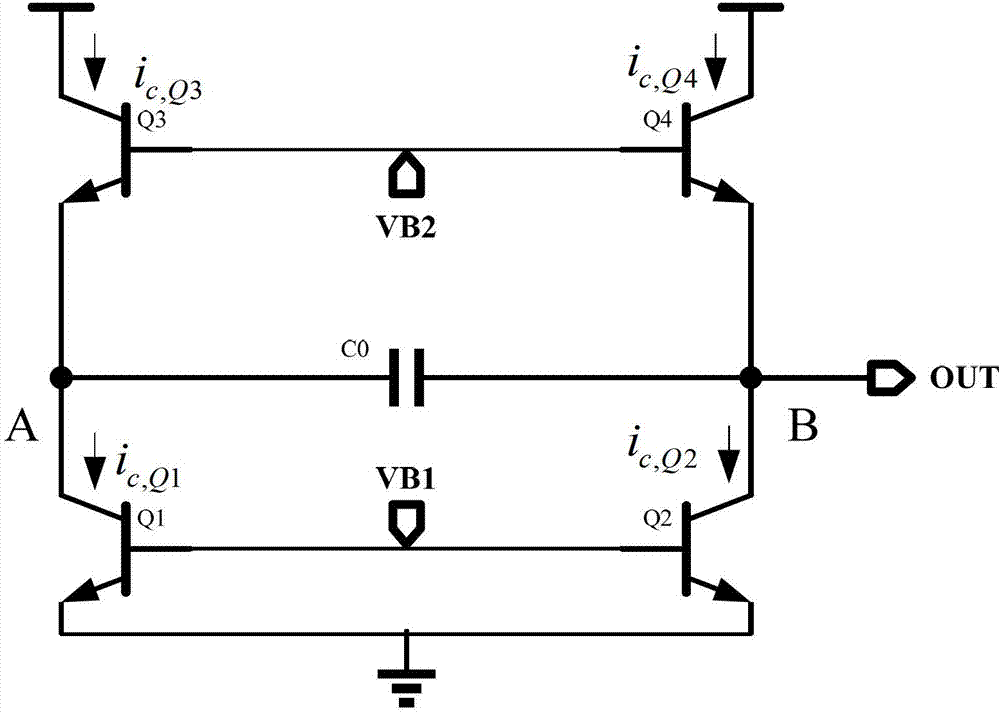

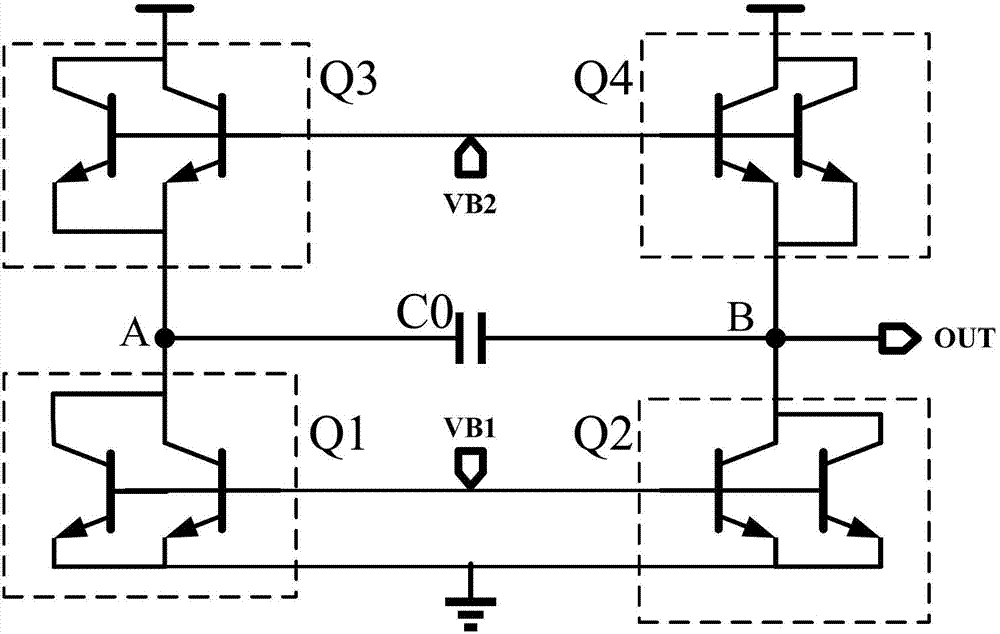

InactiveCN102832903AReduce areaSimple structureActive element networkCapacitanceCapacitance multiplier

The invention provides a capacitance multiplier which employs an active device. Since the area of the active device is intrinsically smaller than that of a passive device, and the capacitance multiplier only comprises four transistors and a capacitor and is simple in structure, the capacitance multiplier is small in area, and cost of an integral chip can be reduced. Further, noise generated by the whole capacitance multiplier is low as devices are less, so that improvement of the noise performance of a whole circuit is benefited.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

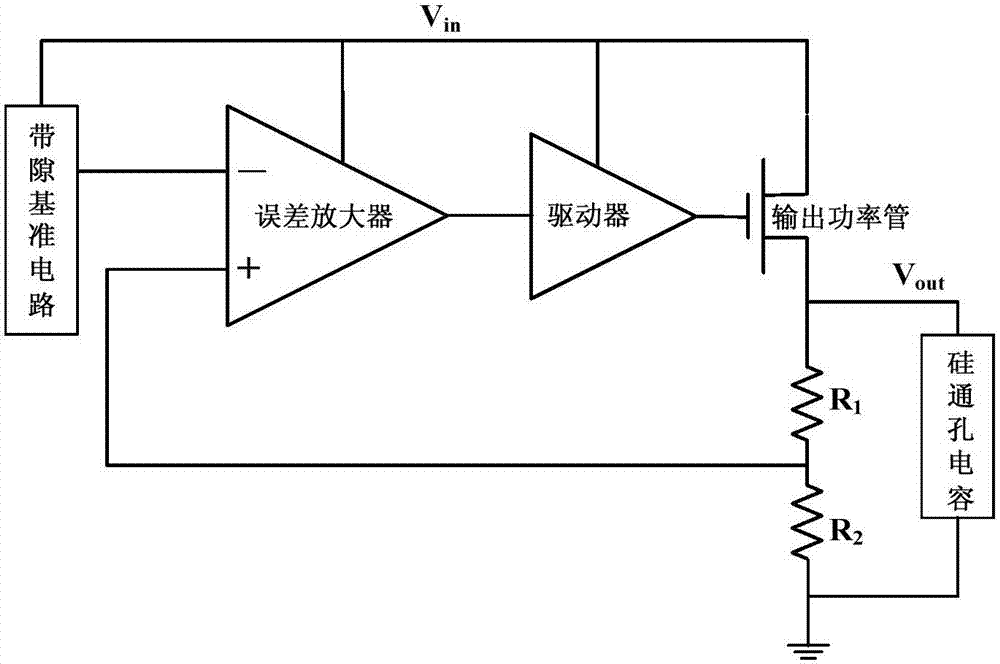

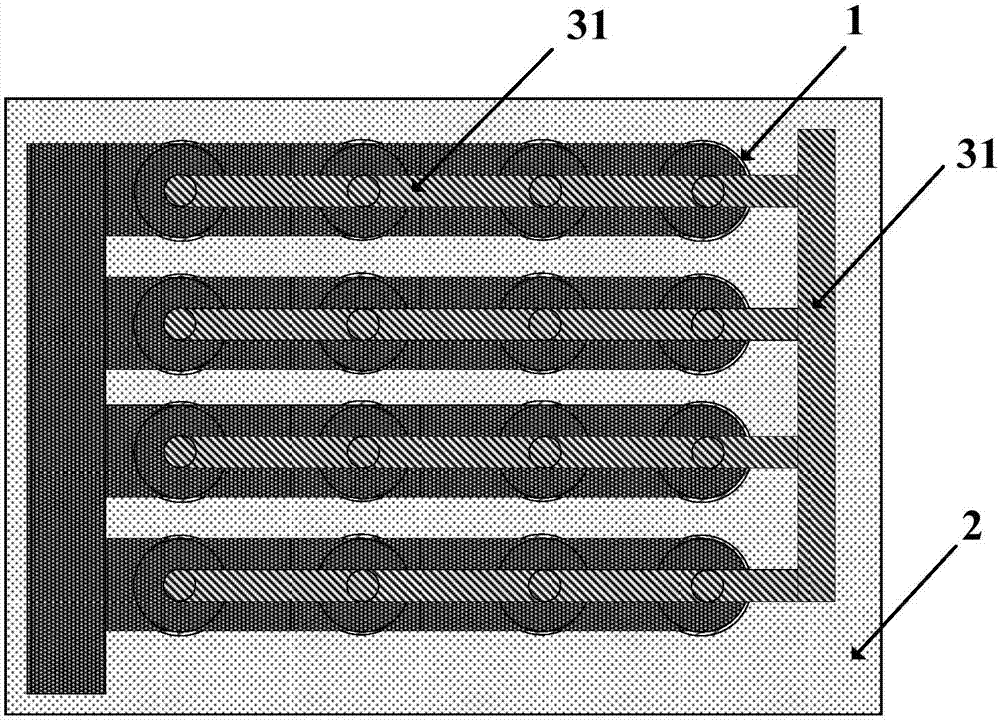

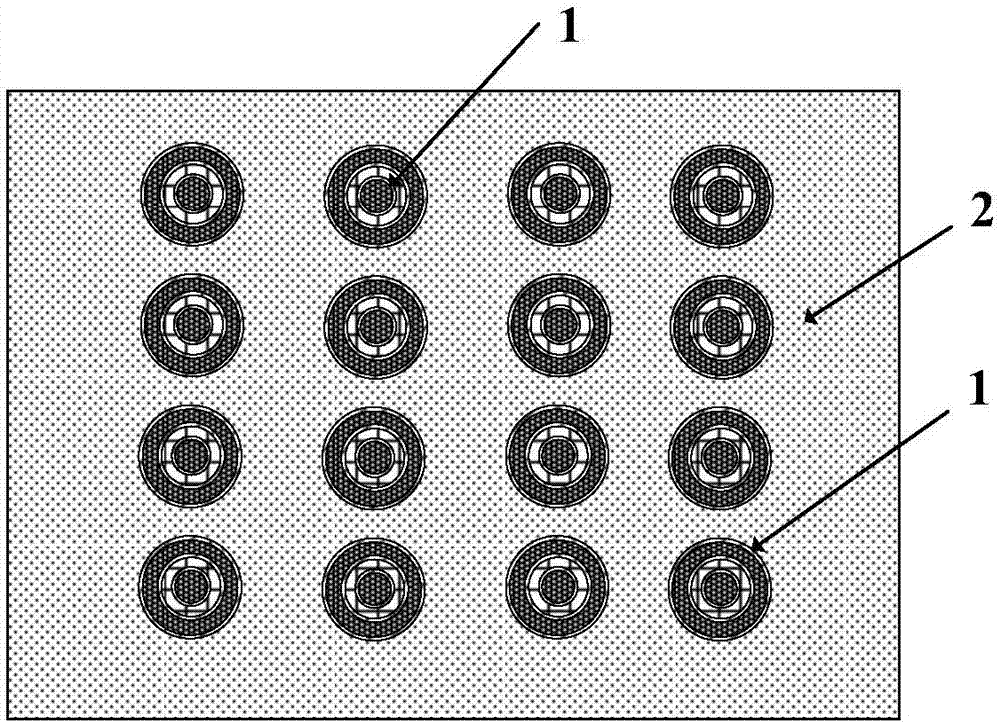

Off-chip capacitor-less LDO circuit based on through silicon via array

ActiveCN107402593AHigh rejection ratioSuppress noiseElectric variable regulationCapacitanceElectrical resistance and conductance

The invention discloses an off-chip capacitor-less LDO circuit based on a through silicon via array. The off-chip capacitor-less LDO circuit comprises a band-gap reference circuit, an error amplifier, a driver, an output power transistor, a sampling resistor network and a through silicon via capacitor. A positive input terminal of the error amplifier is connected with an output terminal of the sampling resistor network. A negative input terminal of the error amplifier is connected with an output terminal of the band-gap reference circuit. An output terminal of the error amplifier is connected with an input terminal of the driver. An output terminal of the driver drives the output power transistor. An output terminal of the output power transistor is respectively connected with one terminal of the sampling resistor network and one terminal of the through silicon via capacitor. The other terminal of the sampling resistor network and the other terminal of the through silicon via capacitor are connected and grounded. The band-gap reference circuit, the error amplifier, the driver and the output power transistor are respectively connected with an external input power supply. An additional capacitance multiplier circuit or off-chip capacitor is not required for the LDO circuit, noise of the external input power supply can be effectively rejected, and the off-chip capacitor-less LDO circuit has the advantages that the off-chip capacitor-less LDO circuit is good in technology compatibility, small in area, large in capacity and high in power supply rejection ratio.

Owner:NINGBO UNIV

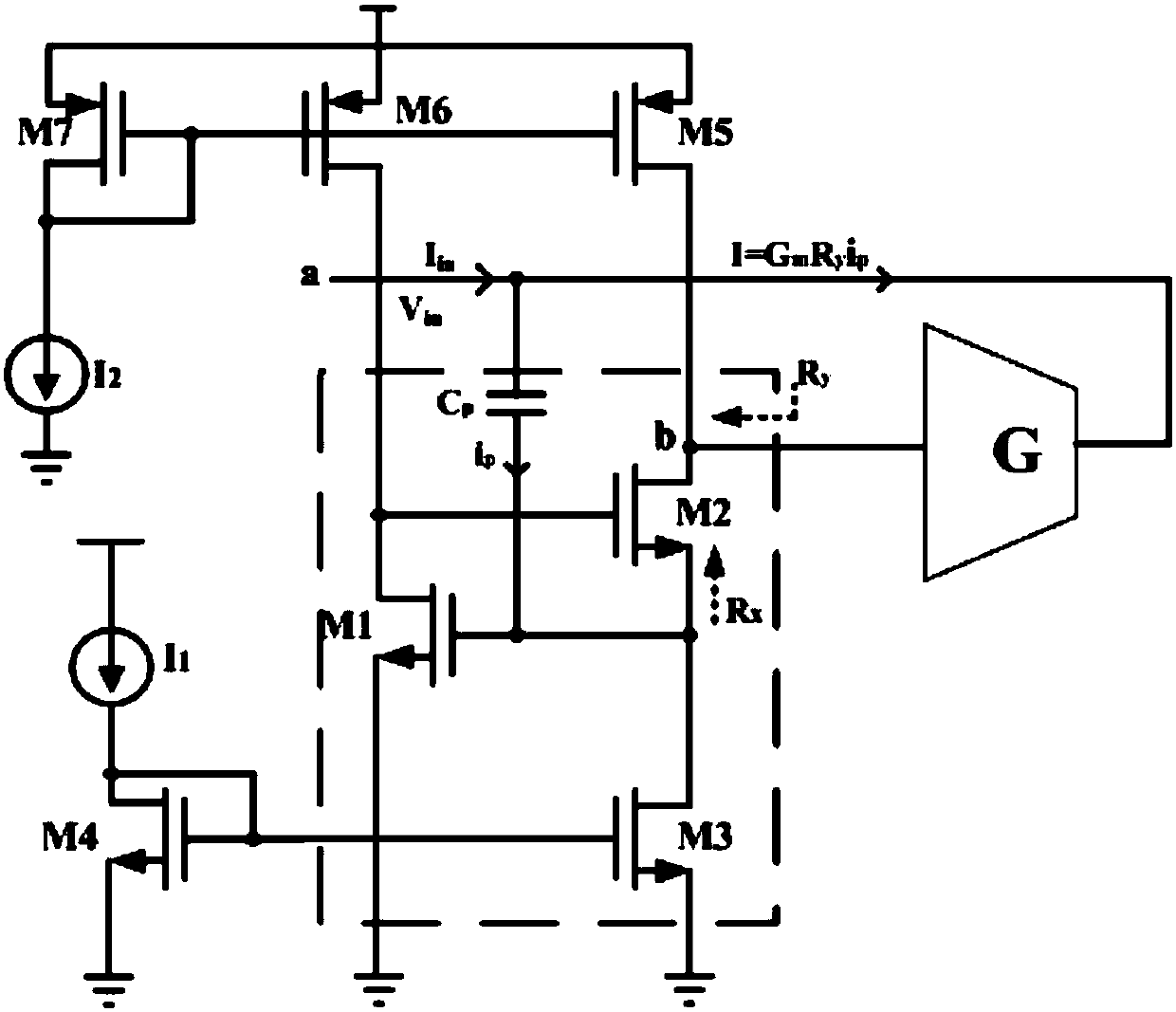

Capacitance multiplier with high multiplication constant

ActiveCN107565928AHigh multiplication factorLarge multiplication factorActive element networkCapacitanceCMOS

The invention discloses a capacitance multiplier with a high multiplication constant; the capacitance multiplier comprises a first cascode circuit module, a second cascode circuit module, a trsanscondutance amplifier circuit module, an on-chip capacitor, a first bias current source, a second bias current source and a third bias current source; the trsanscondutance amplifier circuit module is provided with a first input end and a second input end, wherein the first input end is connected with the first cascode circuit module output end, the second input end is connected with the second cascodecircuit module output end, and the trsanscondutance amplifier circuit module output end is connected with the on-chip capacitor; the high output impedance adjusting type cascode circuit structure is employed, and a current mirror structure is added on the trsanscondutance amplifier circuit module output end, thus greatly improving the capacitance multiplier multiplication constant, and forming a greater equivalent on-chip capacitor. The whole capacitance multiplier circuit structure only uses a CMOS transistor and the capacitor, is small in area, and high in multiplication constant.

Owner:NINGBO UNIV

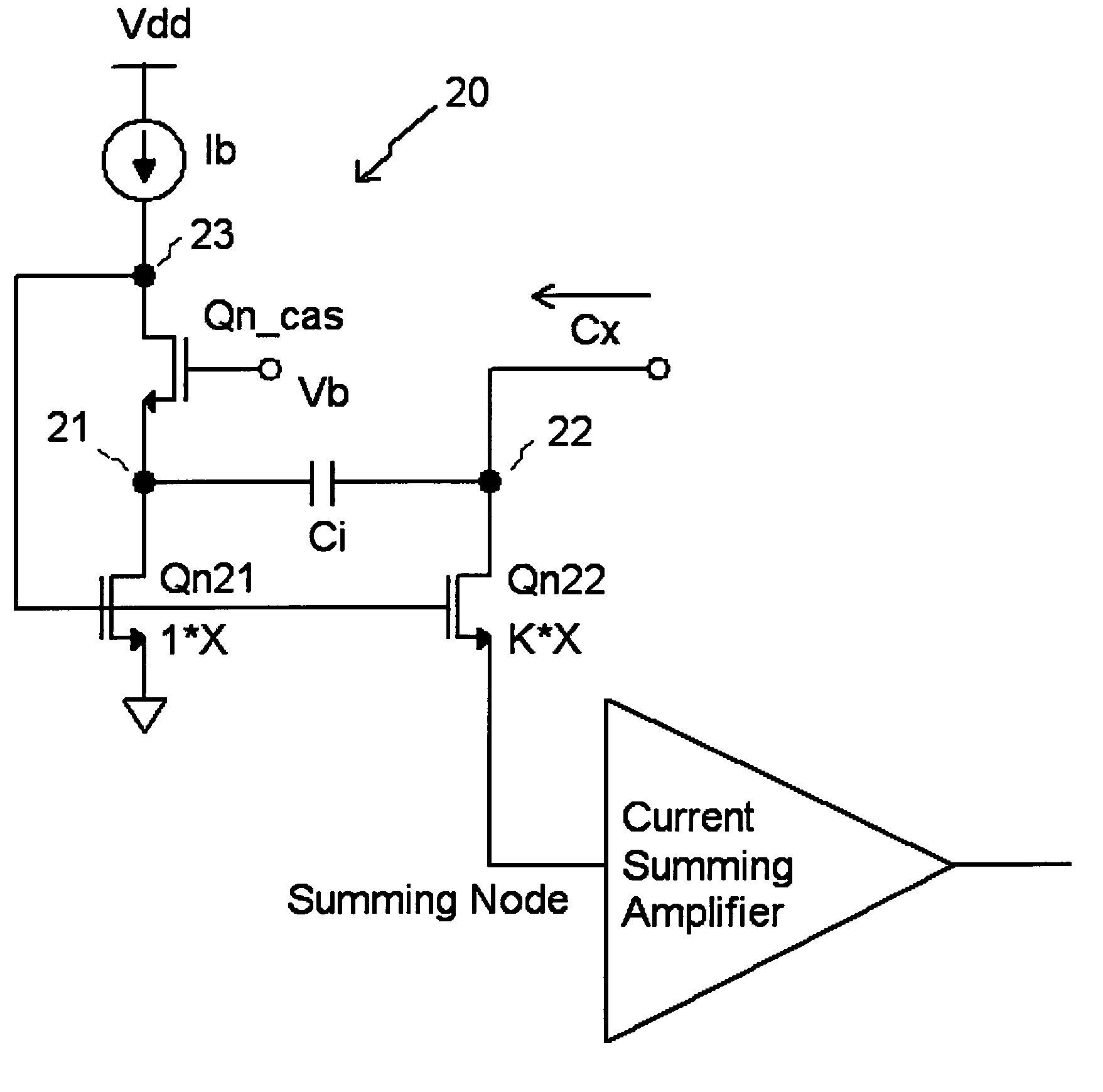

Capacitance multiplier circuit exhibiting improved bandwidth

InactiveUS20060087345A1Reduced series resistanceImprove design flexibilityNegative-feedback-circuit arrangementsLogic circuits characterised by logic functionCapacitanceFrequency compensation

A monolithic capacitance multiplication circuit serves to reduce the required die area when larger capacitance values are needed such as in filter and loop frequency compensation circuits. A current mirror / cascoding device arrangement reduces the effective series resistance of the multiplier capacitor. As a result, the multiplier topology exhibits improved bandwidth over prior art capacitance multiplier circuits.

Owner:ASAHI KASEI TOKO POWER DEVICE

Differential circuit providing a function to cancel input offset voltage

ActiveUS7782137B2Amplifier modifications to raise efficiencyDifferential amplifiersCapacitanceAudio power amplifier

A new offset canceling circuit for a differential circuit is disclosed whose input offset voltage may be cancelled independent of the variation of the input level, accordingly, enables the cut-off frequency of the canceling circuit unchanged. The offset canceller of the invention provides a buffer amplifier and a filter. The filter includes a capacitance multiplier including an operational amplifier (Op-Amp) operating in the inverting mode and a capacitor connected between the input and output of the Op-Amp. The Op-Amp operating in the inverting mode whose closed loop gain is solely determined by resistors, and the capacitance of the capacitor is multiplied by the closed loop gain of the Op-Amp by the Miller effect.

Owner:SUMITOMO ELECTRIC IND LTD

A mixed model capacitance multiplier circuit

ActiveCN104320105AReduce areaReduce power consumptionActive element networkCapacitanceAudio power amplifier

The present invention discloses a mixed model capacitance multiplier circuit, which includes a voltage mode multiplication circuit unit and a current mode multiplication circuit unit; the voltage mode multiplication circuit unit includes an operational amplifier and a source follower, an input voltage signal is input to a positive input end of the operational amplifier, an output end of the operational amplifier is added to a negative input end of the operational amplifier via the source follower, and the output end of the operational amplifier is connected with the current mode multiplication circuit unit; the current mode multiplication circuit unit includes a capacitor C, a bias circuit of a high swing cascode current mirror and the high swing cascode current mirror, the output end of the operational amplifier is connected with one end of the capacitor C, the other end of the capacitor C is connected with the input end of the current mirror, and the output end of the current mirror is connected with an input voltage; and the bias circuit of the current mirror provides bias for the current mirror. The mixed model capacitance multiplier circuit of the present invention has the characteristics such as low power consumption, small area, input impedance at high and low frequencies and wide working bandwidth.

Owner:SUN YAT SEN UNIV +1

Capacitance multiplier with enhanced gain and low power consumption

InactiveUS7215164B2High capacitance gainReduce power consumptionPulse automatic controlNetwork simulating reactancesCapacitanceCapacitance multiplier

A capacitance multiplier includes a cascade of a plurality of current amplifiers with each current amplifier having a respective current gain Ki. In addition, the capacitance multiplier includes a capacitor coupled in parallel across the cascade of current amplifiers. Such a capacitance multiplier occupies a smaller area with higher capacitance gain but with low power consumption.

Owner:SAMSUNG ELECTRONICS CO LTD

Capacitance multiplier

ActiveUS7113022B2High bandwidthReduce areaNetwork simulating reactancesAc-dc conversionCapacitanceDischarge efficiency

A capacitance multiplier includes a self-biasing active load for generating a stable bias voltage without a separate current bias. In addition, the capacitance multiplier includes a cascode load within a multiplying section for increasing the output resistance and in turn the charging / discharging efficiency. Furthermore, the capacitance multiplier is implemented with a plurality of multiplying paths to reduce effects of noise for more stable generation of the multiplied capacitance.

Owner:SAMSUNG ELECTRONICS CO LTD

Capacitance multiplier with enhanced gain and low power consumption

InactiveUS20050275438A1Increase capacitanceReduce power consumptionPulse automatic controlNetwork simulating reactancesCapacitanceCapacitance multiplier

A capacitance multiplier includes a cascade of a plurality of current amplifiers with each current amplifier having a respective current gain Ki. In addition, the capacitance multiplier includes a capacitor coupled in parallel across the cascade of current amplifiers. Such a capacitance multiplier occupies a smaller area with higher capacitance gain but with low power consumption.

Owner:SAMSUNG ELECTRONICS CO LTD

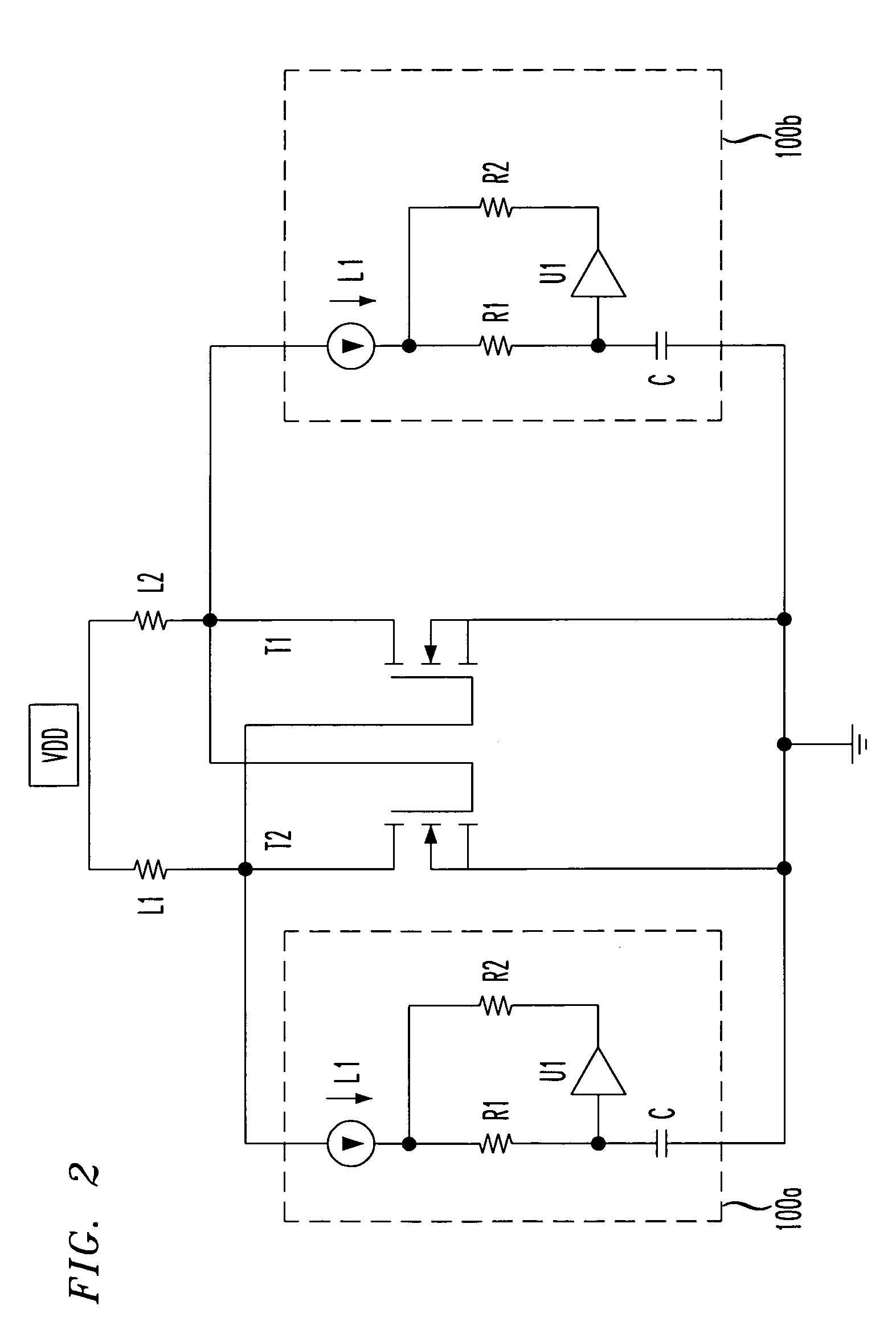

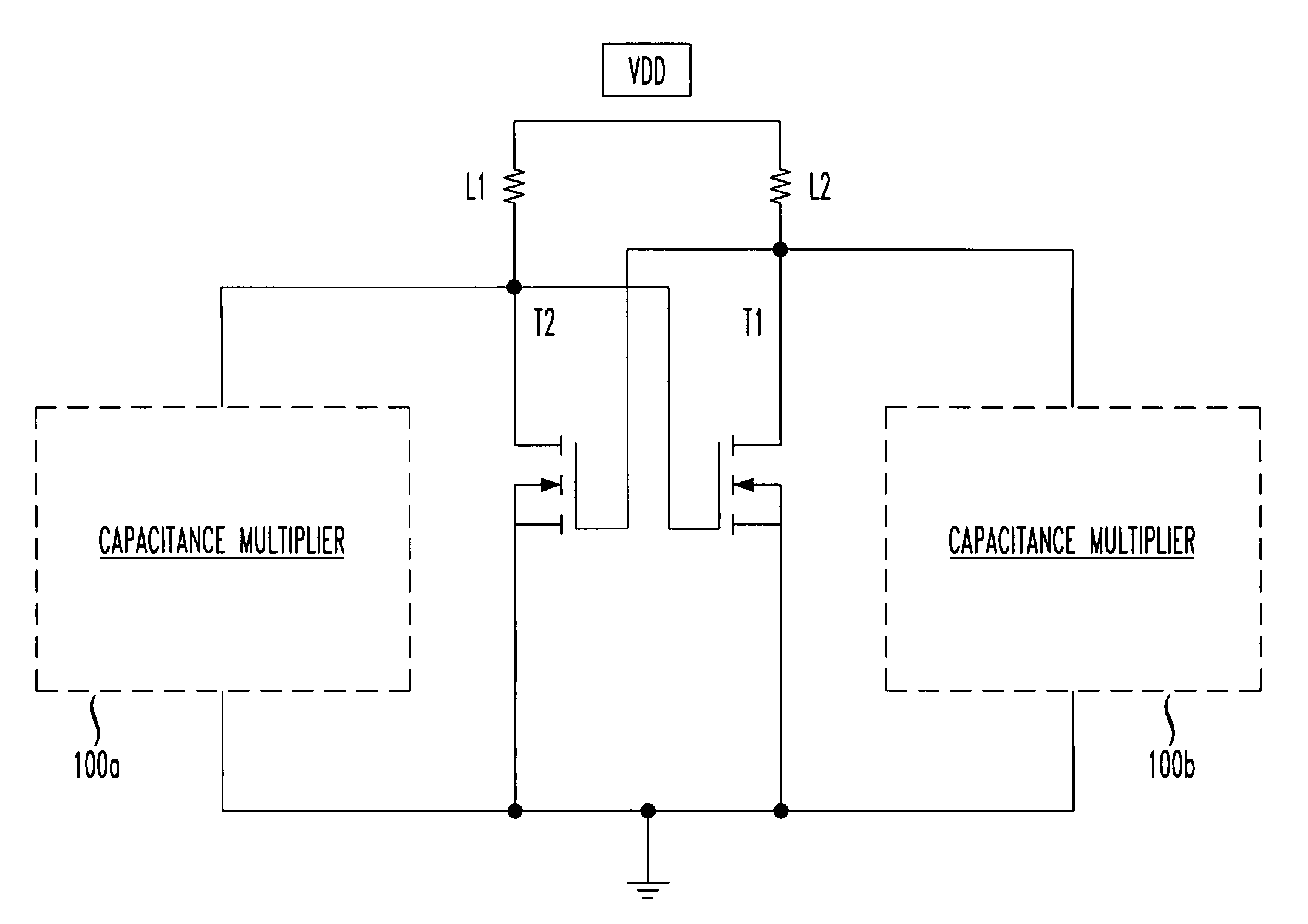

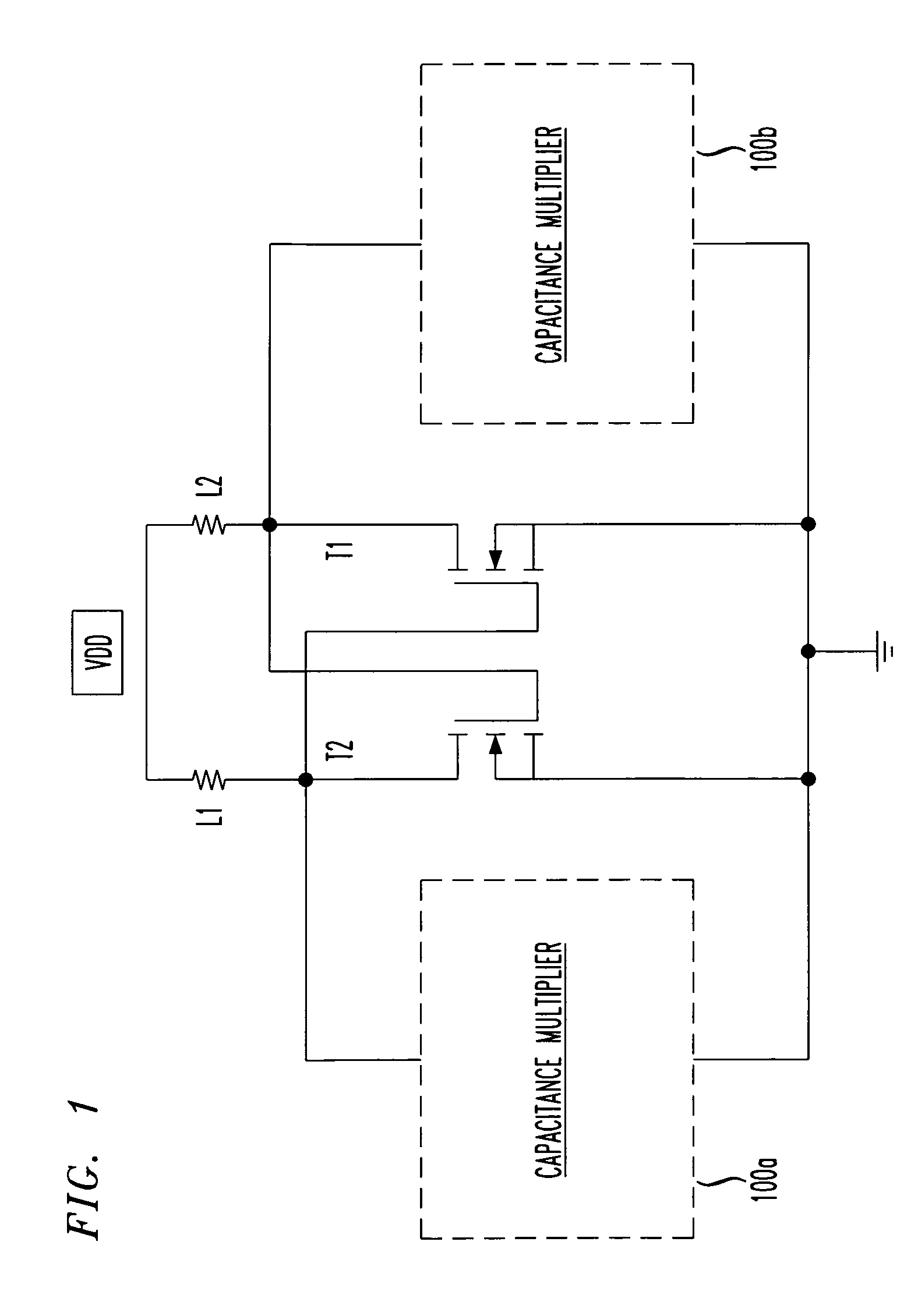

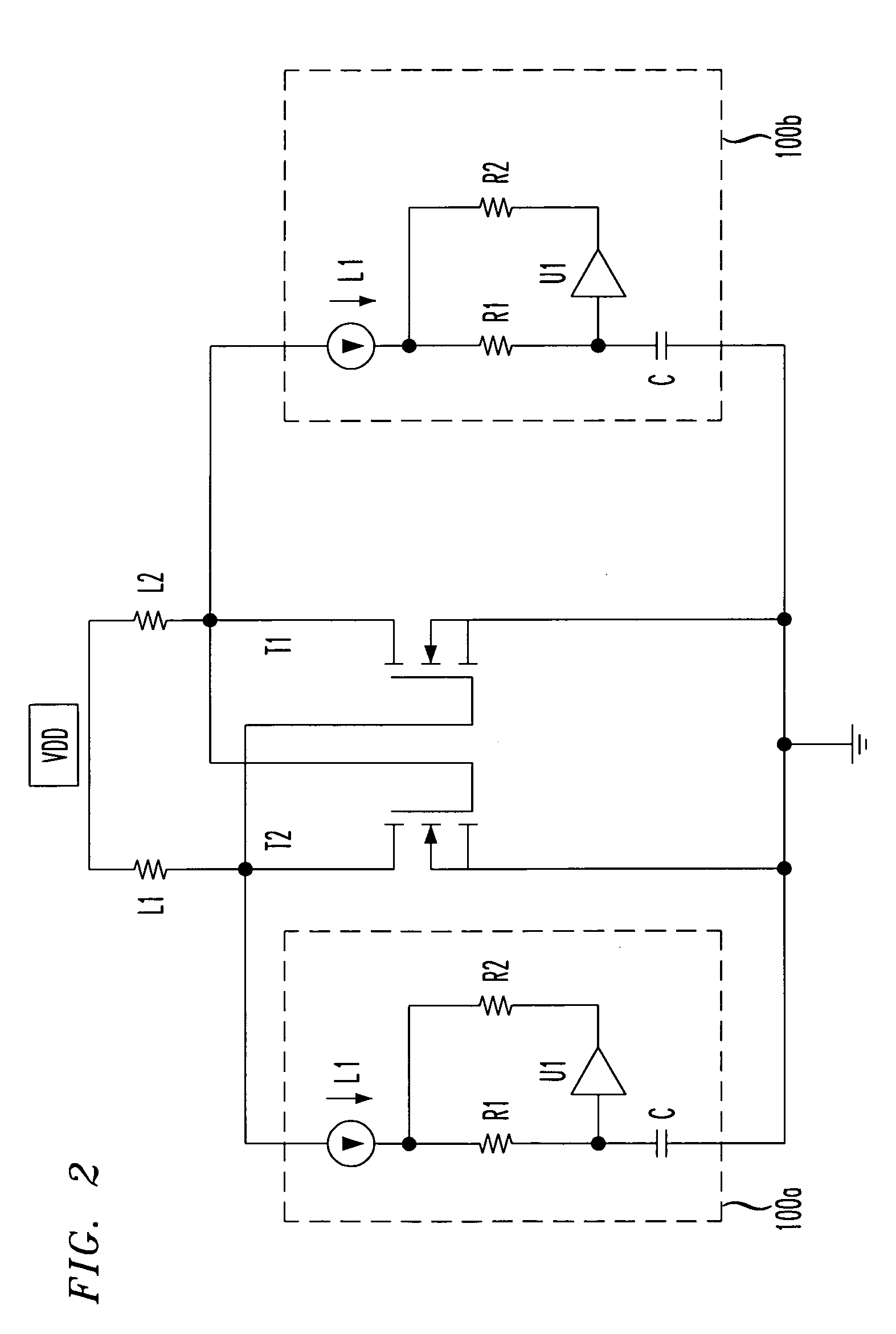

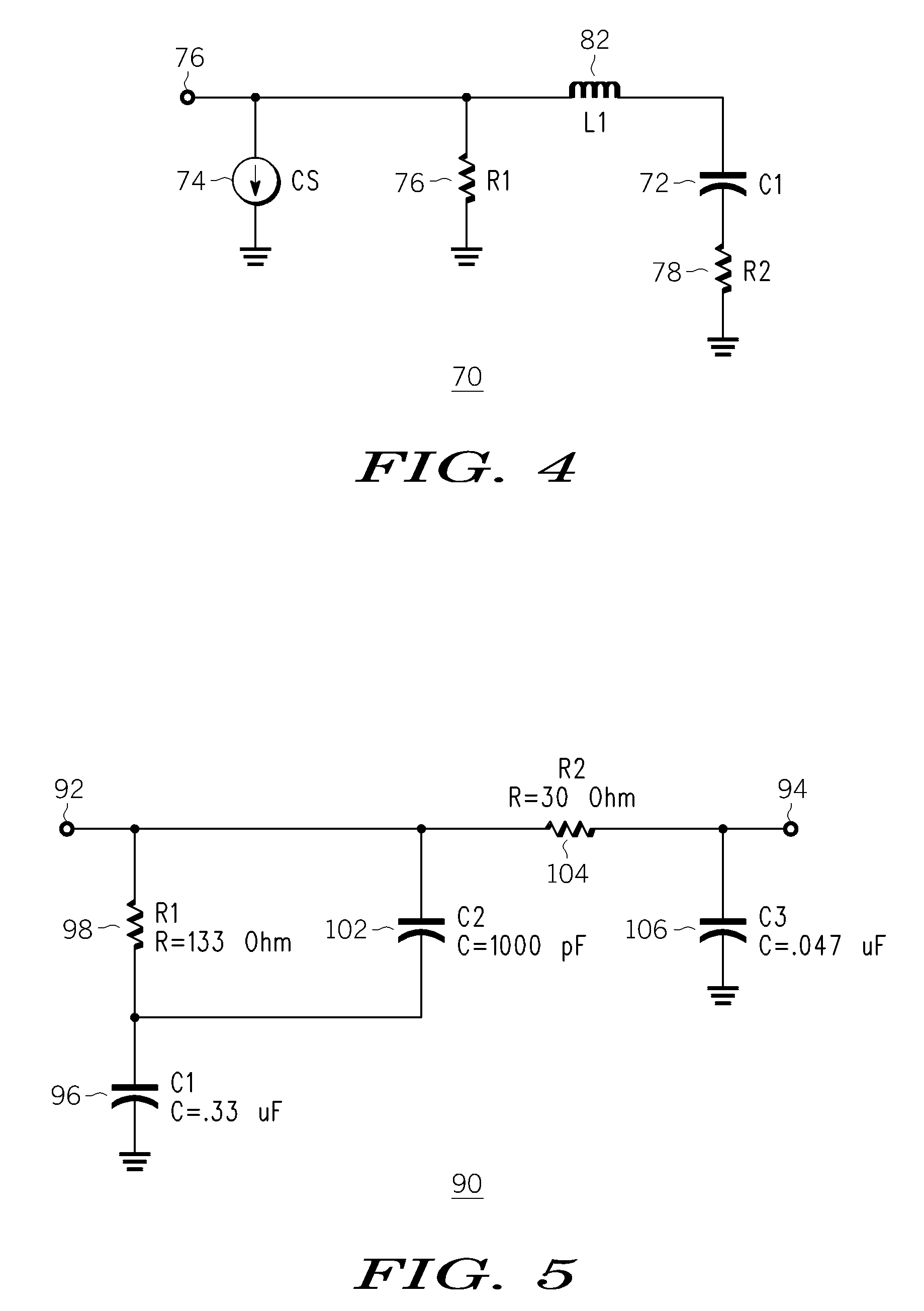

Frequency selection using capacitance multiplication

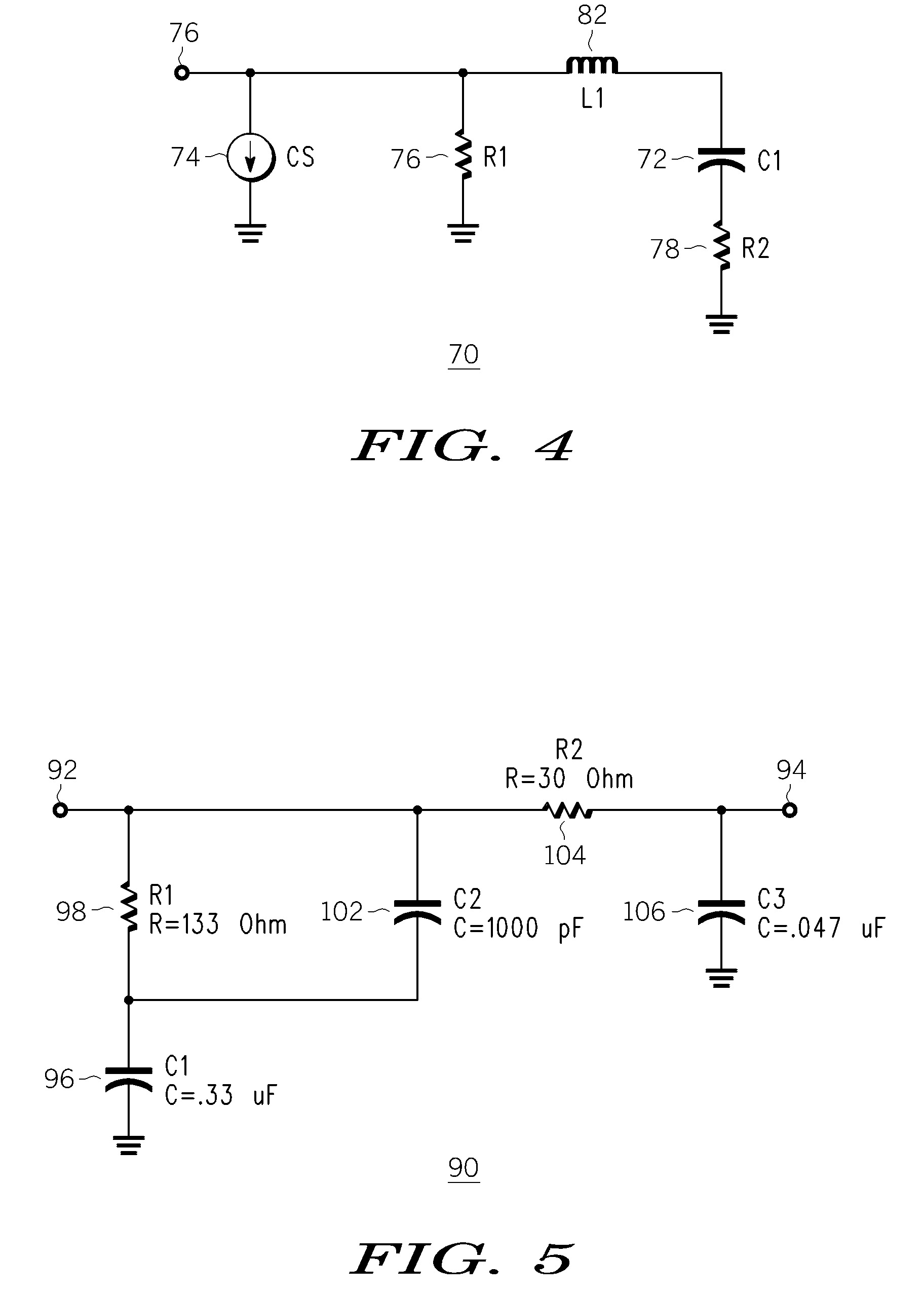

A variable capacitance circuit on an integrated circuit comprises a MOS transistor, and a capacitance multiplier connected to one end of a channel of the MOS device. A MOS device is formed in series with an inductance, and a capacitance multiplier is formed to be connected to a node between the MOS device and the inductance.

Owner:AVAGO TECH INT SALES PTE LTD

Frequency selection using capacitance multiplication

A variable capacitance circuit on an integrated circuit comprises a MOS transistor, and a capacitance multiplier connected to one end of a channel of the MOS device. A MOS device is formed in series with an inductance, and a capacitance multiplier is formed to be connected to a node between the MOS device and the inductance.

Owner:AVAGO TECH INT SALES PTE LTD

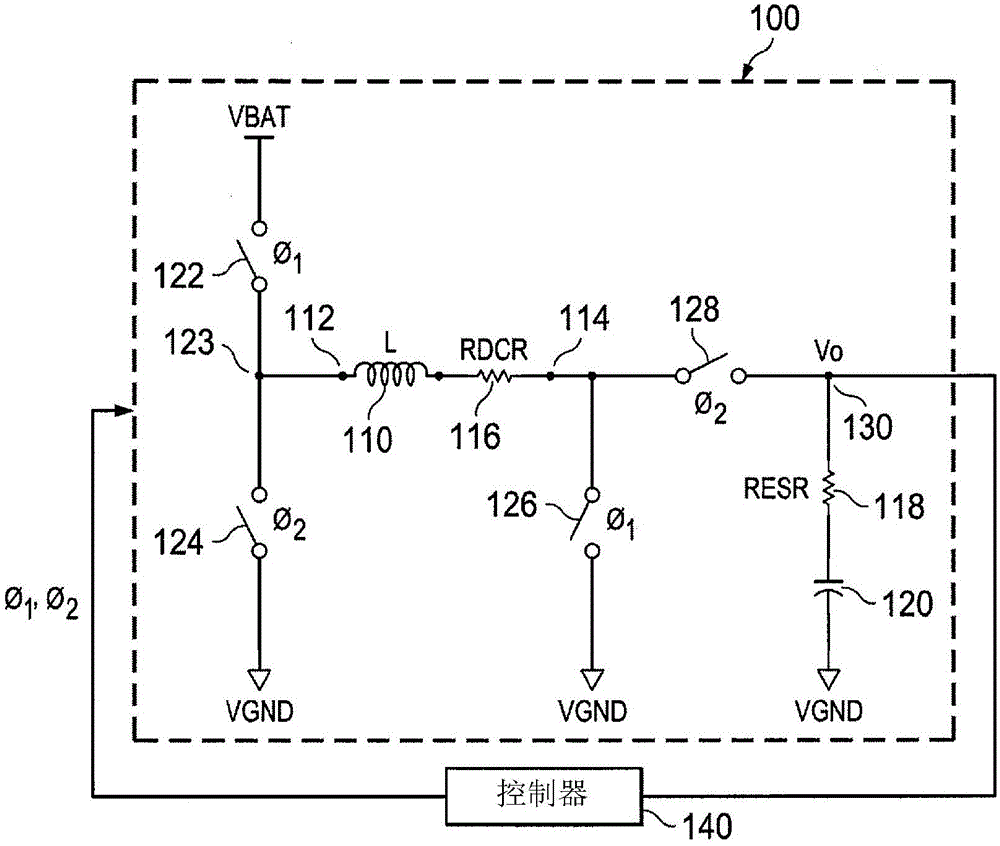

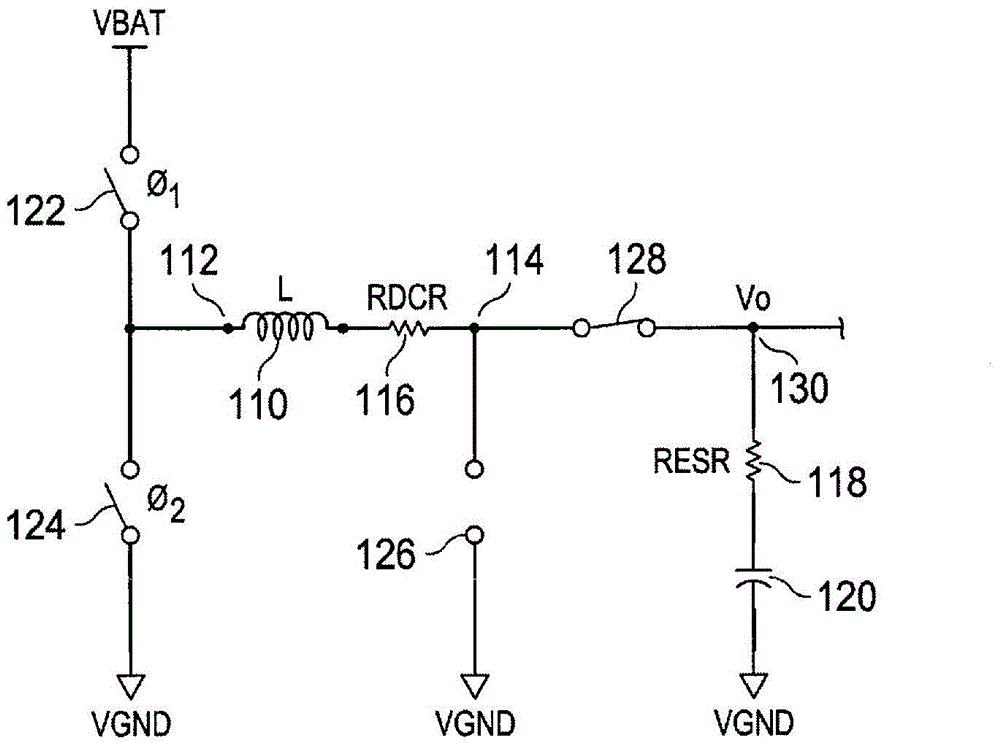

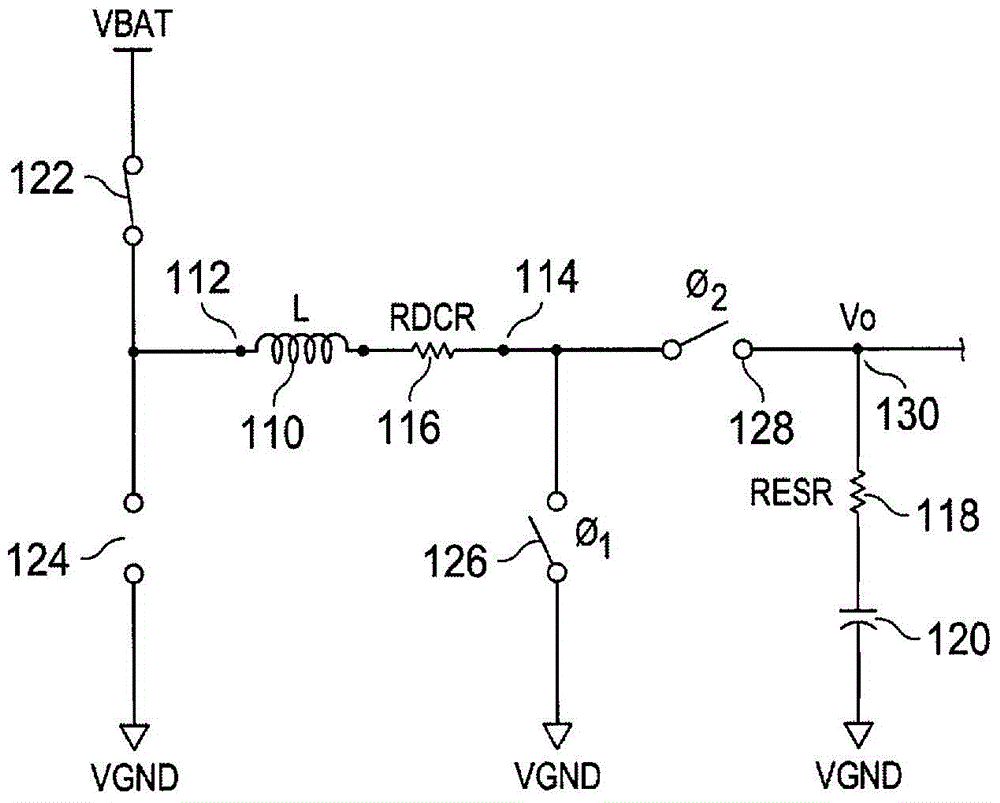

Power converters and compensation circuits thereof

In an embodiment, a circuit includes a Direct Current (DC)-DC buck-boost converter and a controller. The controller includes an error amplifier configured to receive a feedback signal responsive to an output signal of the buck-boost converter. The error amplifier is configured to compare the feedback signal and a reference signal to generate an error signal. The controller includes a modulator circuit that is configured to receive the error signal and compare the error signal with a periodic ramp signal to generate a modulated signal. The controller further includes a digital logic block to generate switching signals in response to the modulated signal that is fed to the buck-boost converter to control the output signal of the buck-boost converter. The controller includes a capacitance multiplier circuit coupled to the output of the error amplifier to configure a dominant pole so as to compensate the buck-boost converter.

Owner:TEXAS INSTR INC

Capacitance multiplier circuit

ActiveUS7598793B1Increase effective capacitanceImpedence convertorsNetwork simulating reactancesCapacitanceEngineering

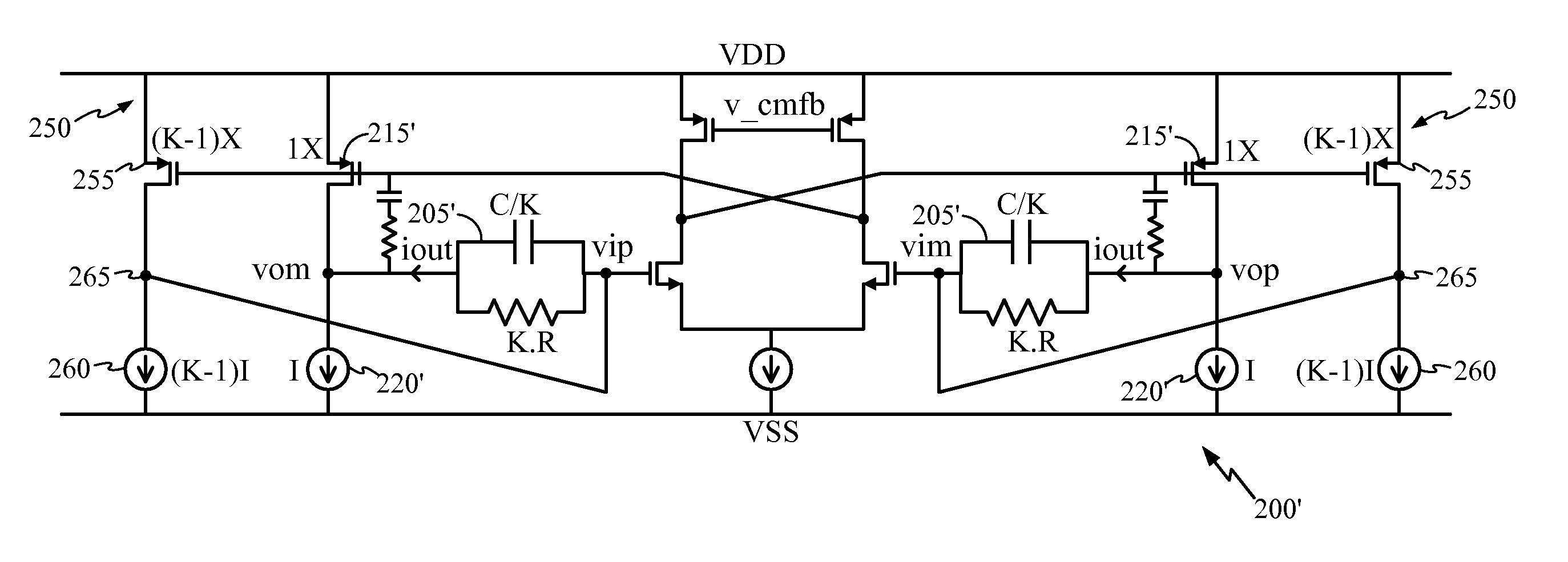

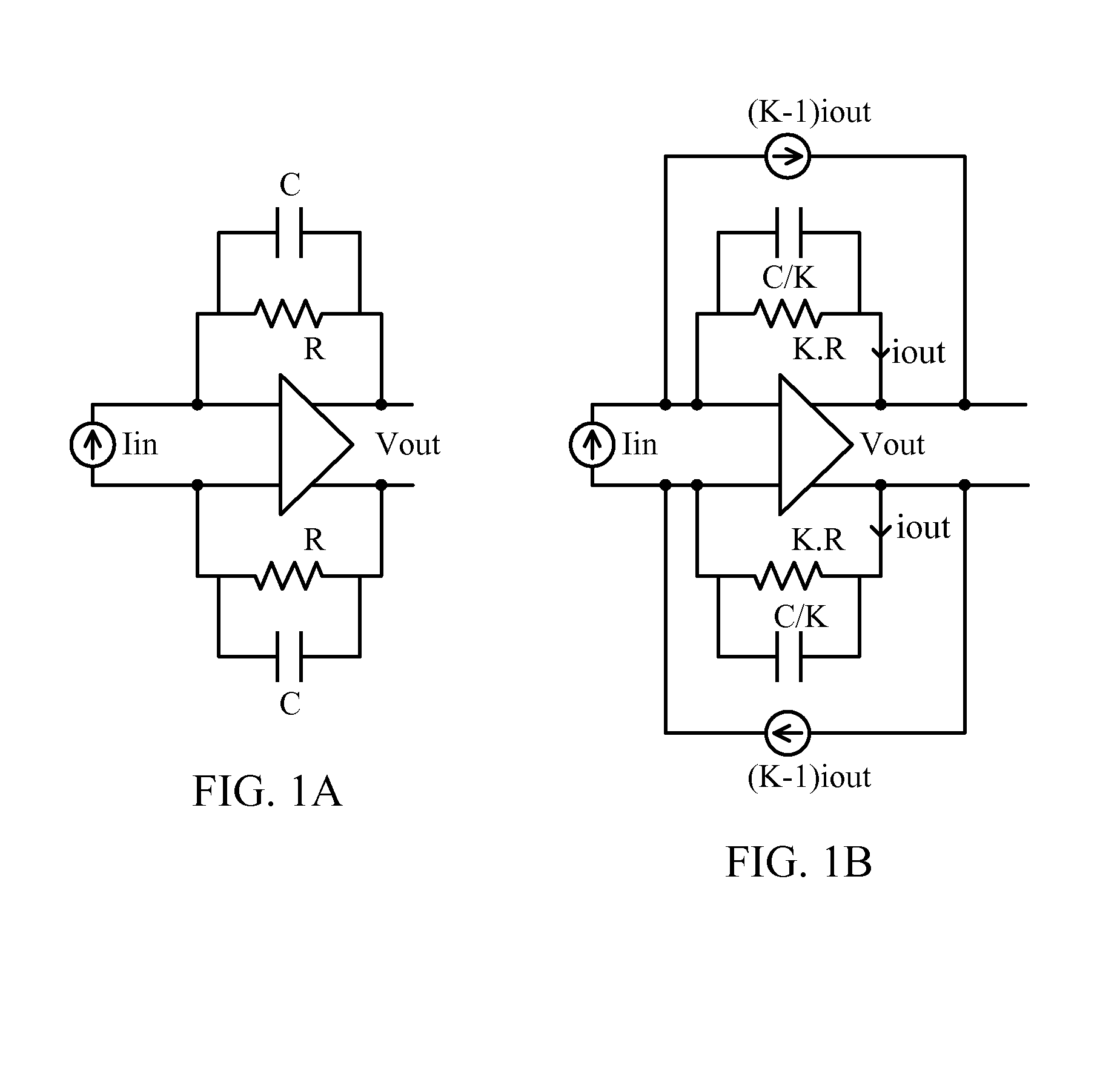

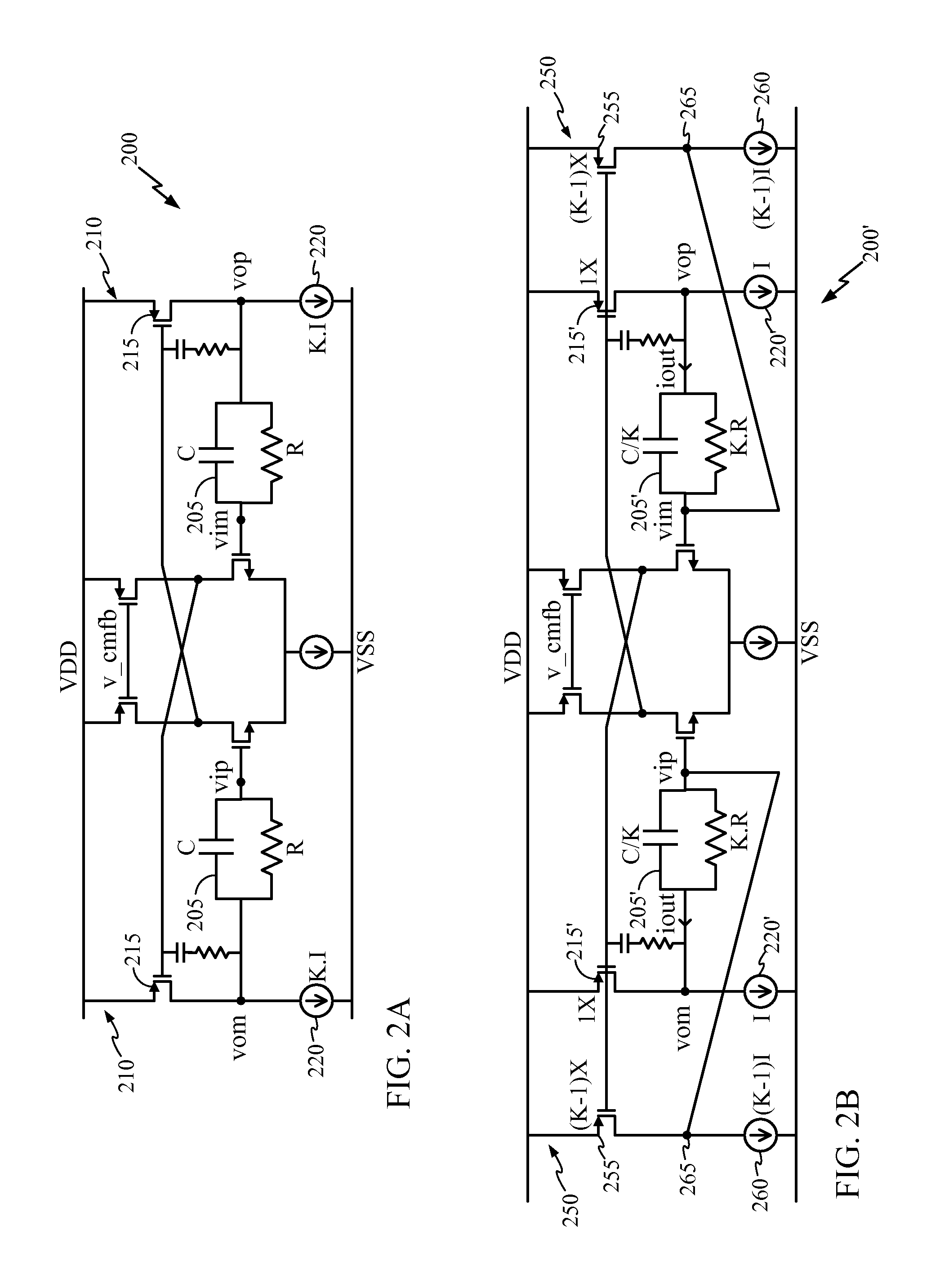

A capacitance multiplier circuit is configured to sense a current through a capacitor in an RC filter of the circuit and to multiply the current so as to achieve a capacitance multiplier effect without adding additional circuitry or requiring additional power. The circuit includes an RC filter, a first signal path connected to a filter output, and a second signal path connected to an input to the filter. A current output through the filter (iout) is split between the two paths, sensed in the first path and multiplied in the second path. The multiplied current is fed back from the second path to the filter input to raise the effective capacitance of capacitor C. The capacitance multiplier circuit, in raising the effective capacitance of the capacitor in the filter, does not affect the frequency response, linearity performance and / or stability of the overall circuit.

Owner:QUALCOMM INC

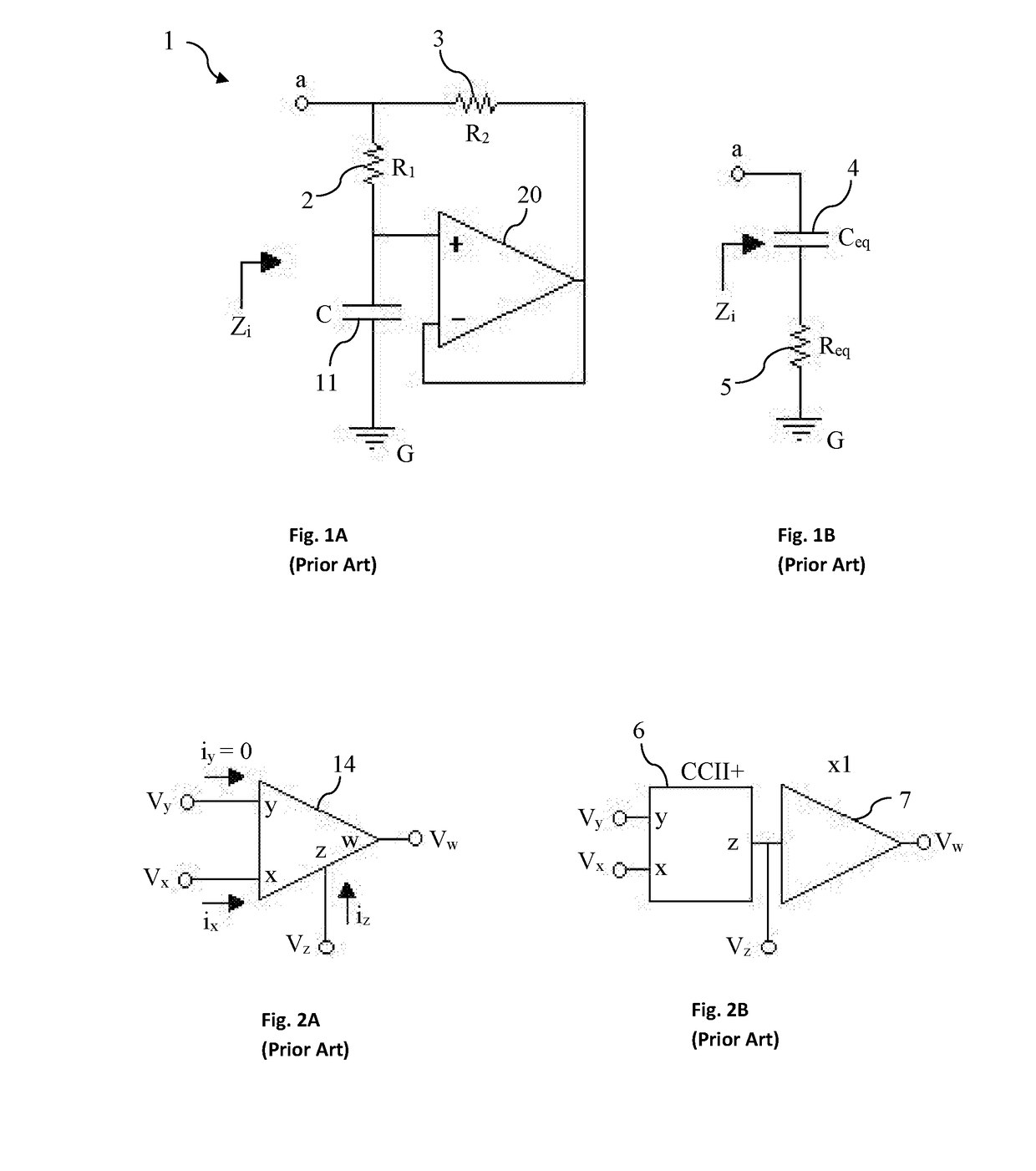

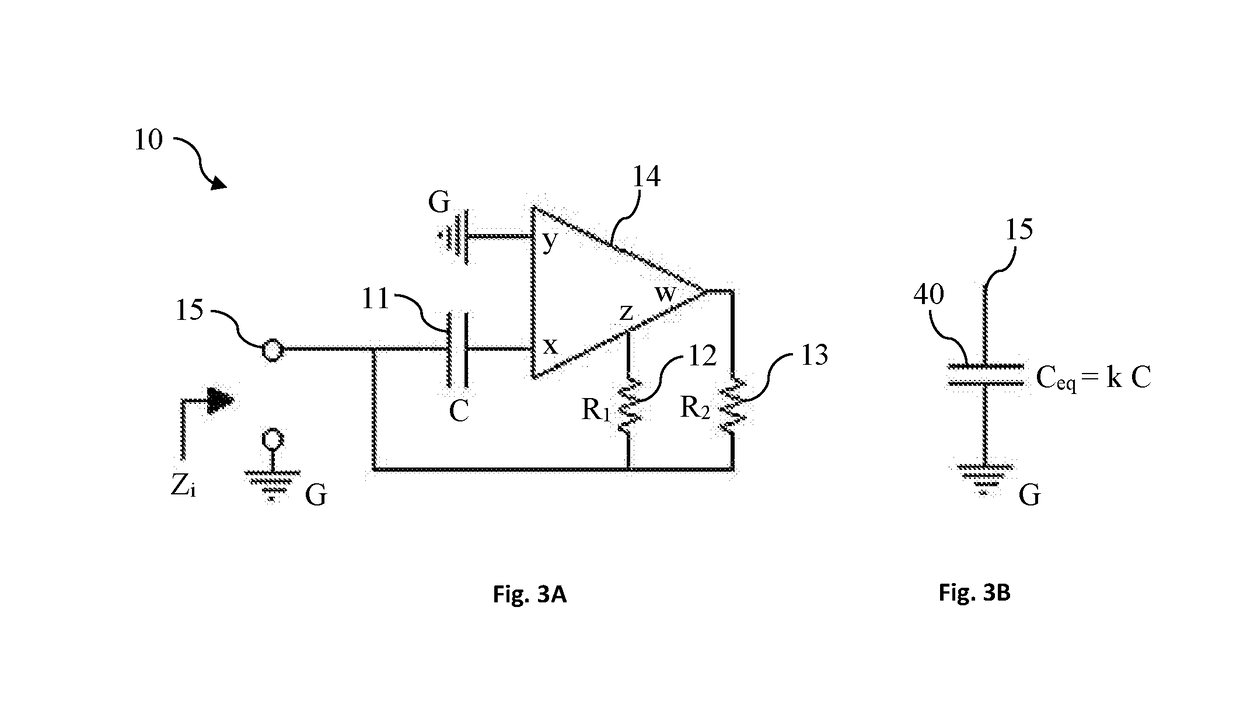

Grounded capacitance multipliers with electronic tuning possibility using single current feedback amplifier

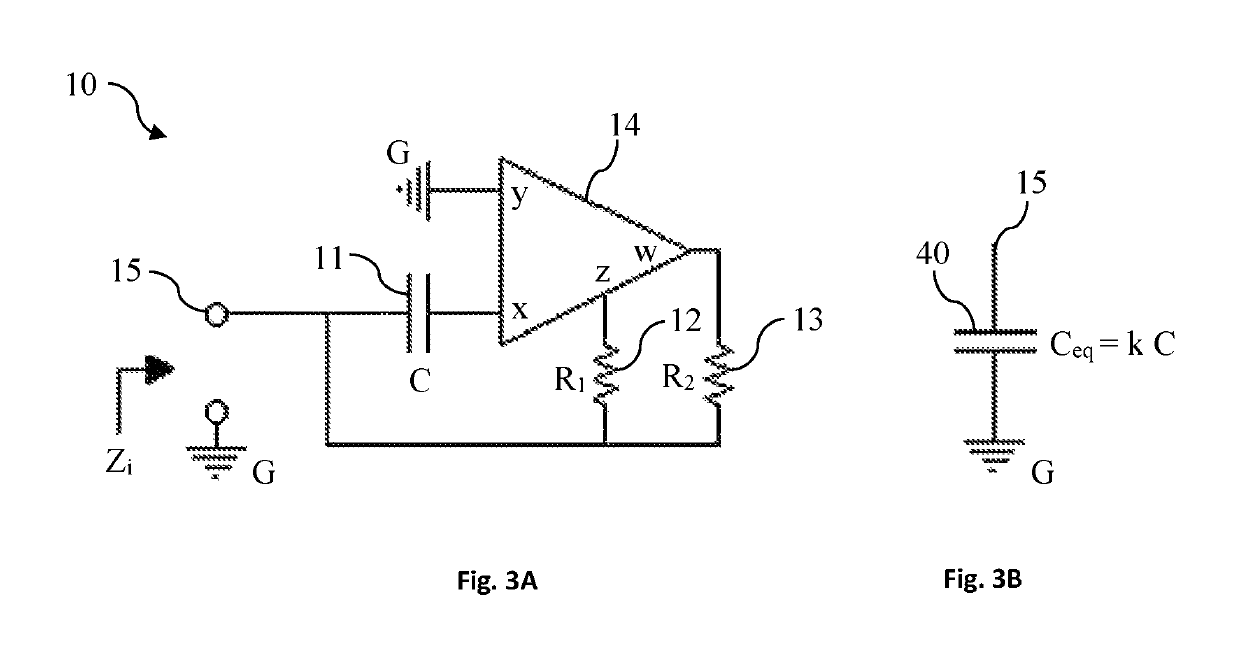

ActiveUS10382011B2Minimal numberSmall capacitanceImpedence convertorsNetwork simulating reactancesCapacitanceAudio power amplifier

The present invention relates to a capacitance multiplier topology suitable for both positive and negative capacitance multiplication having a minimum configuration consisting of a current feedback amplifier (CFOA), two resistors and a reference capacitor, with each C-multiplier having a respective capacitance amplification constant k which is externally adjustable. Such a capacitance multiplier has less parasitic components, occupies a smaller chip area with higher simulated capacitance value.

Owner:YEDITEPE UNIVSI

Capacitance multiplier circuit

An integrated circuit including a capacitance multiplier having reduced parasitics and injected noise compared to conventional multiplier methods. The integrated circuit includes a reference capacitor and a current mirror arrangement coupled to the reference capacitor. The current mirror arrangement, which includes a current gain factor N, varies the capacitance of the reference capacitor by a factor of N+1, based on the reference capacitor current. The current mirror arrangement includes an operational amplifier operating in conjunction with two mirror transistors to form a current mirror arrangement having little or no series resistance. The current mirror also can include a plurality of resistors configured to reduce the noise from the capacitance multiplier, thus making the capacitance multiplier useful for applications that may require relatively low noise.

Owner:INTEL CORP

High-gain isolated type direct current-direct current (DC-DC) convertor

ActiveCN103391009BOutput current ripple is zeroOutput Current Ripple ZeroAc-dc conversion without reversalEfficient power electronics conversionCapacitanceFuel cells

Owner:厦门市爱维达电子有限公司

Grounded capacitance multipliers with electronic tuning possibility using single current feedback amplifier

ActiveUS20180351536A1Minimal numberSmall capacitanceNetwork simulating reactancesTunable filtersCapacitancePower flow

The present invention relates to a capacitance multiplier topology suitable for both positive and negative capacitance multiplication having a minimum configuration consisting of a current feedback amplifier (CFOA), two resistors and a reference capacitor, with each C-multiplier having a respective capacitance amplification constant k which is externally adjustable. Such a capacitance multiplier has less parasitic components, occupies a smaller chip area with higher simulated capacitance value.

Owner:YEDITEPE UNIVSI

A Control Strategy of Dynamic Voltage Stabilizer for Distribution Network

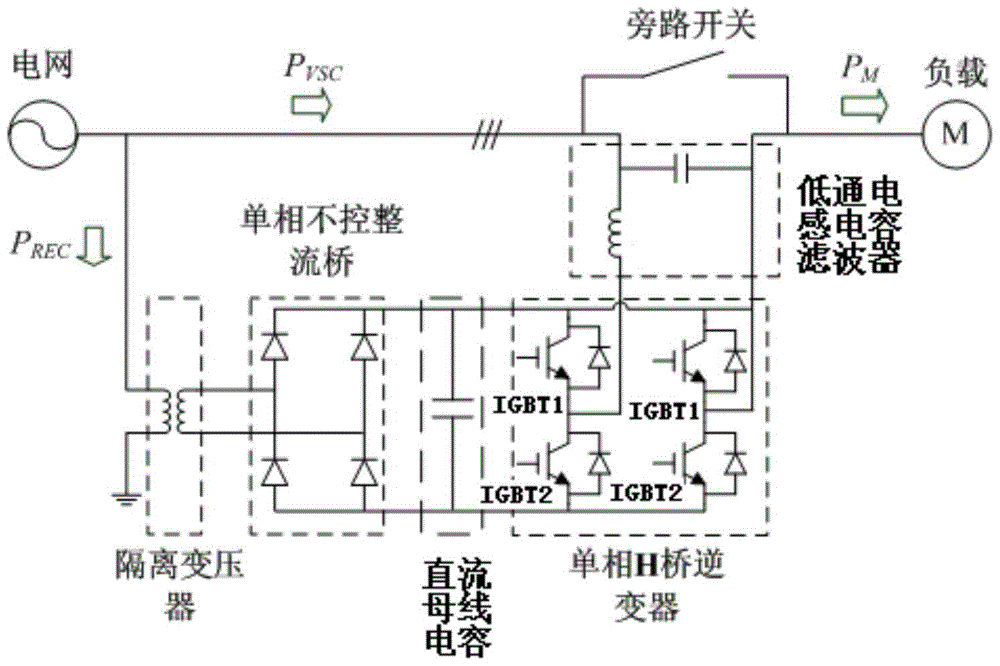

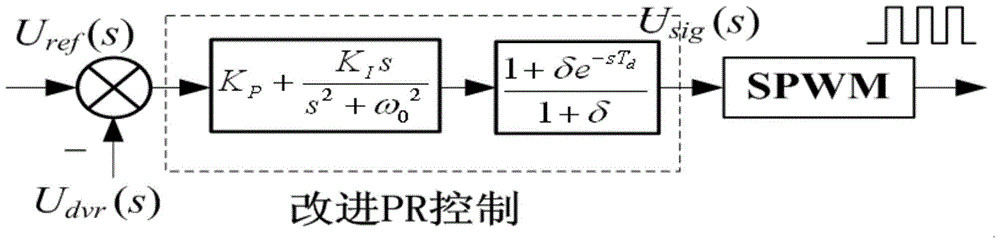

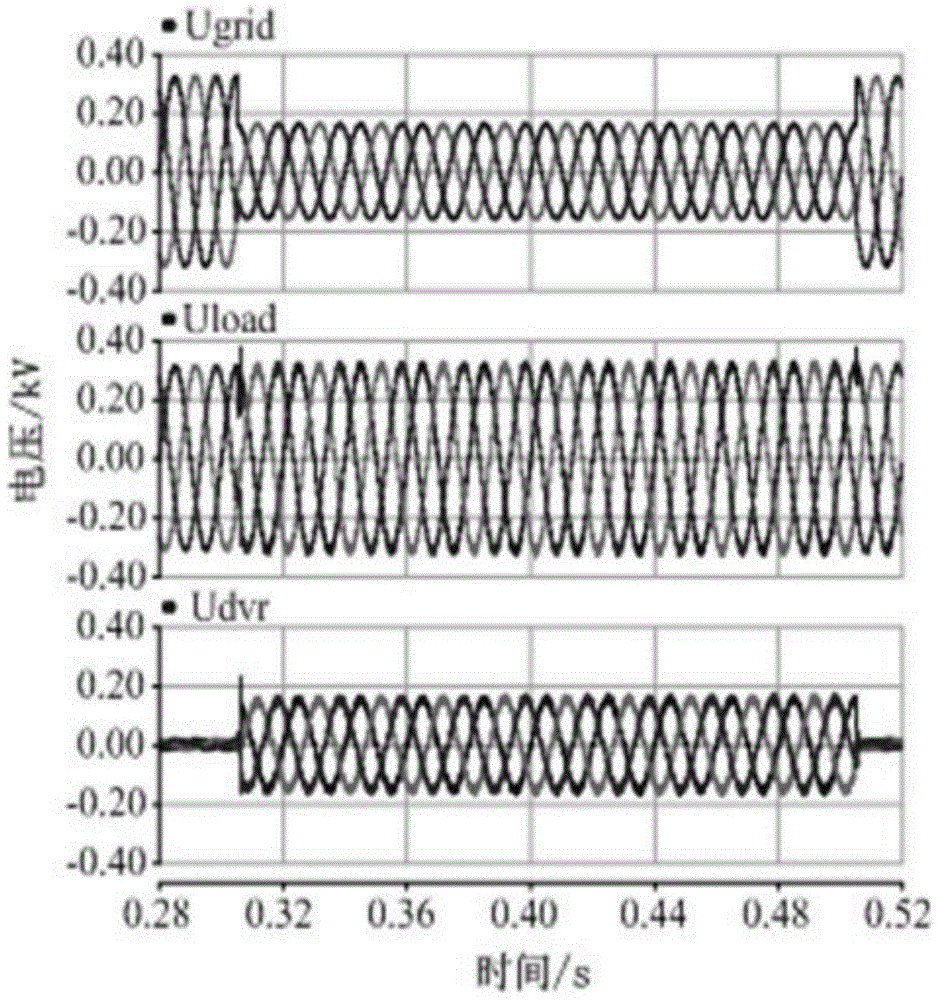

ActiveCN104578083BIncrease dampingImprove transient response characteristicsFlicker reduction in ac networkAc network voltage adjustmentCapacitanceAlternating current

The invention discloses a dynamic voltage stabilizer of a power distribution network. The dynamic voltage stabilizer comprises an isolation transformer, a single-phase uncontrolled rectifier bridge, a direct current bus capacitor, a single-phase H-bridge inverter, a low-pass inductance-capacitance filter and a by-pass switch, wherein the primary side of the isolation transformer is connected with a power grid, the secondary side of the isolation transformer is connected with the alternating current side of the single-phase uncontrolled rectifier bridge, the single-phase uncontrolled rectifier bridge, the direct current bus capacitor and the single-phase H-bridge inverter are connected in parallel, the alternating current side of the single-phase H-bridge inverter is connected with the low-pass inductance-capacitance filter, and the by-pass switch is connected with a capacitor of the low-pass inductance-capacitance filter. The invention also discloses a control strategy of the dynamic voltage stabilizer. According to the dynamic voltage stabilizer of the power distribution network, a half-cycle Posicast control method is introduced in the traditional proportional resonant control, DVR (Discharge Voltage Regulator) dampness is increased, large high-frequency gain is achieved, the sensitivity of the system to noise is reduced, the underdamping effect caused by the low-pass inductance-capacitance filter can be effectively inhibited and the transient response characteristic of the DVR is greatly improved.

Owner:STATE GRID CORP OF CHINA +2