A mixed model capacitance multiplier circuit

A multiplication circuit and capacitance multiplication technology, applied in electrical components, impedance networks, networks using active components, etc., can solve the problems affecting circuit bandwidth, circuit area and power consumption increase, and achieve small circuit area, small power consumption. The effect of small consumption and small area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] The accompanying drawings are for illustrative purposes only and cannot be construed as limiting the patent;

[0036] In order to better illustrate this embodiment, some parts in the drawings will be omitted, enlarged or reduced, and do not represent the size of the actual product;

[0037] For those skilled in the art, it is understandable that some well-known structures and descriptions thereof may be omitted in the drawings.

[0038] The technical solutions of the present invention will be further described below in conjunction with the accompanying drawings and embodiments.

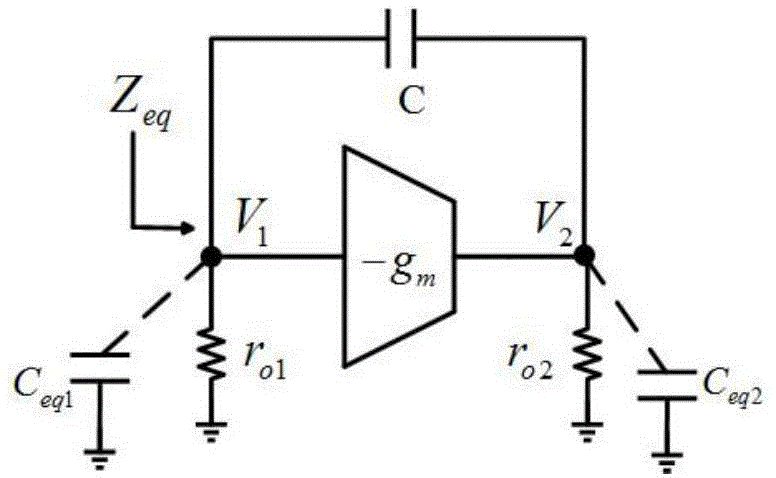

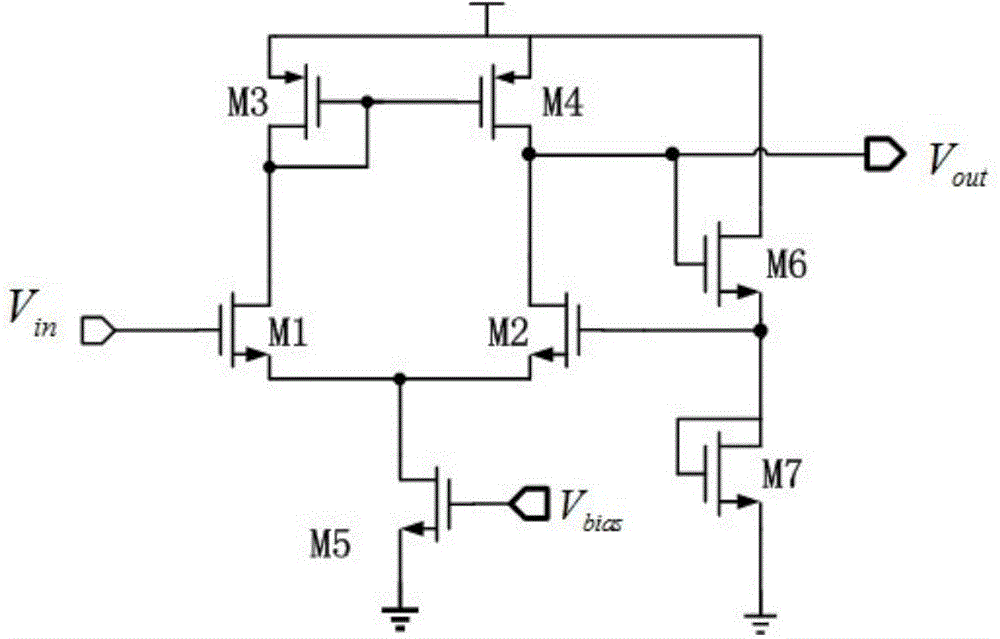

[0039] Such as image 3 , the voltage mode multiplier circuit unit is composed of CMOS tubes by M 1 , M 2 , M 3 , M 4 , M 5 , M 6 and M 7 composition. The M 1 , M 2 , M 3 , M 4 and M 5 constitutes a differential input operational amplifier loaded with a current mirror, the M 6 with M 7 Constitute a source follower structure, used as the feedback network of the amplifier. When t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More