Patents

Literature

112 results about "Cascode current mirror" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

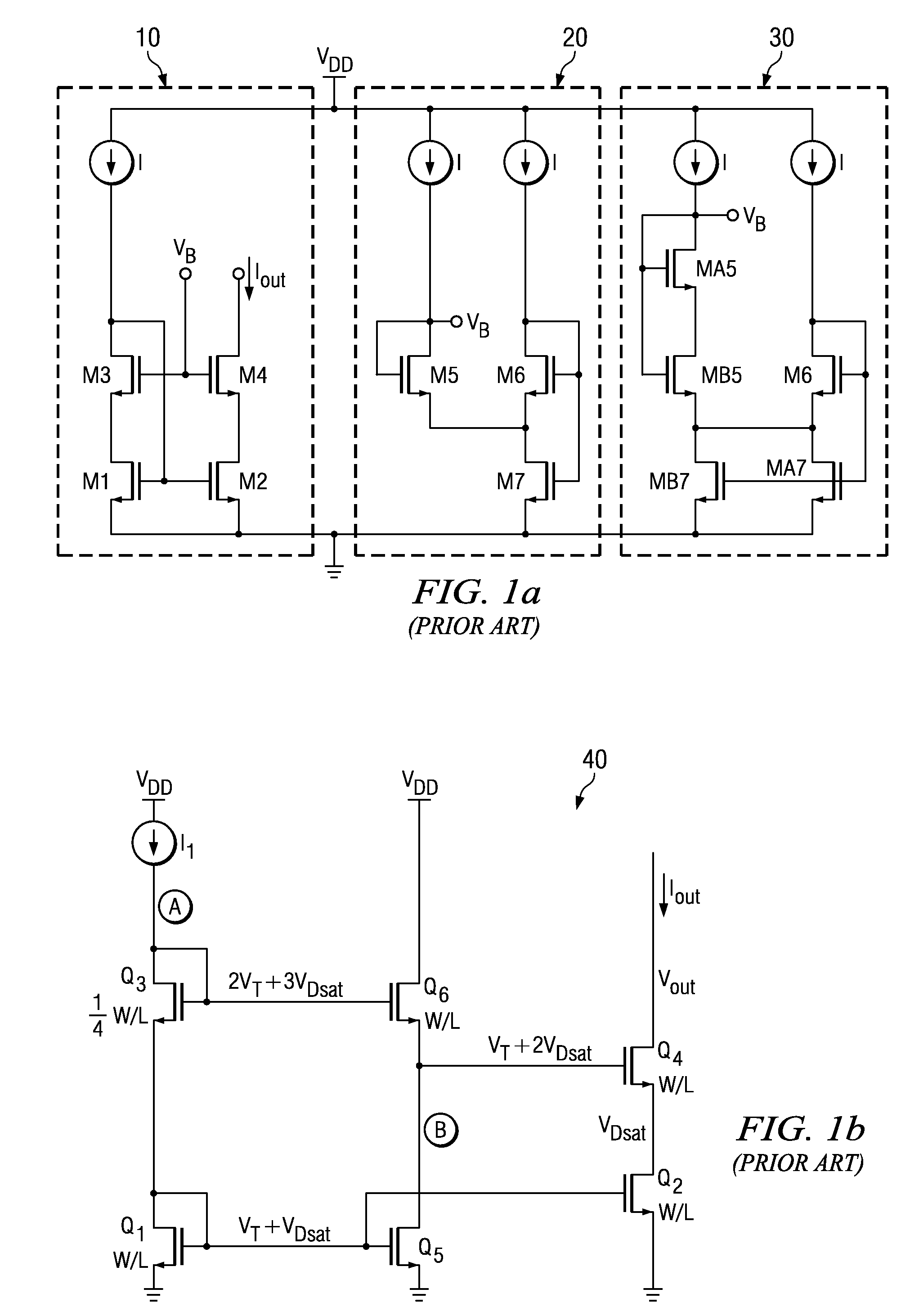

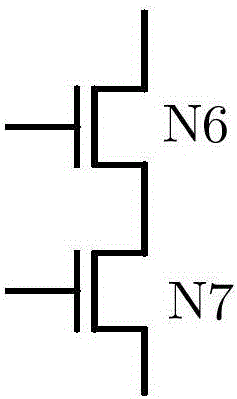

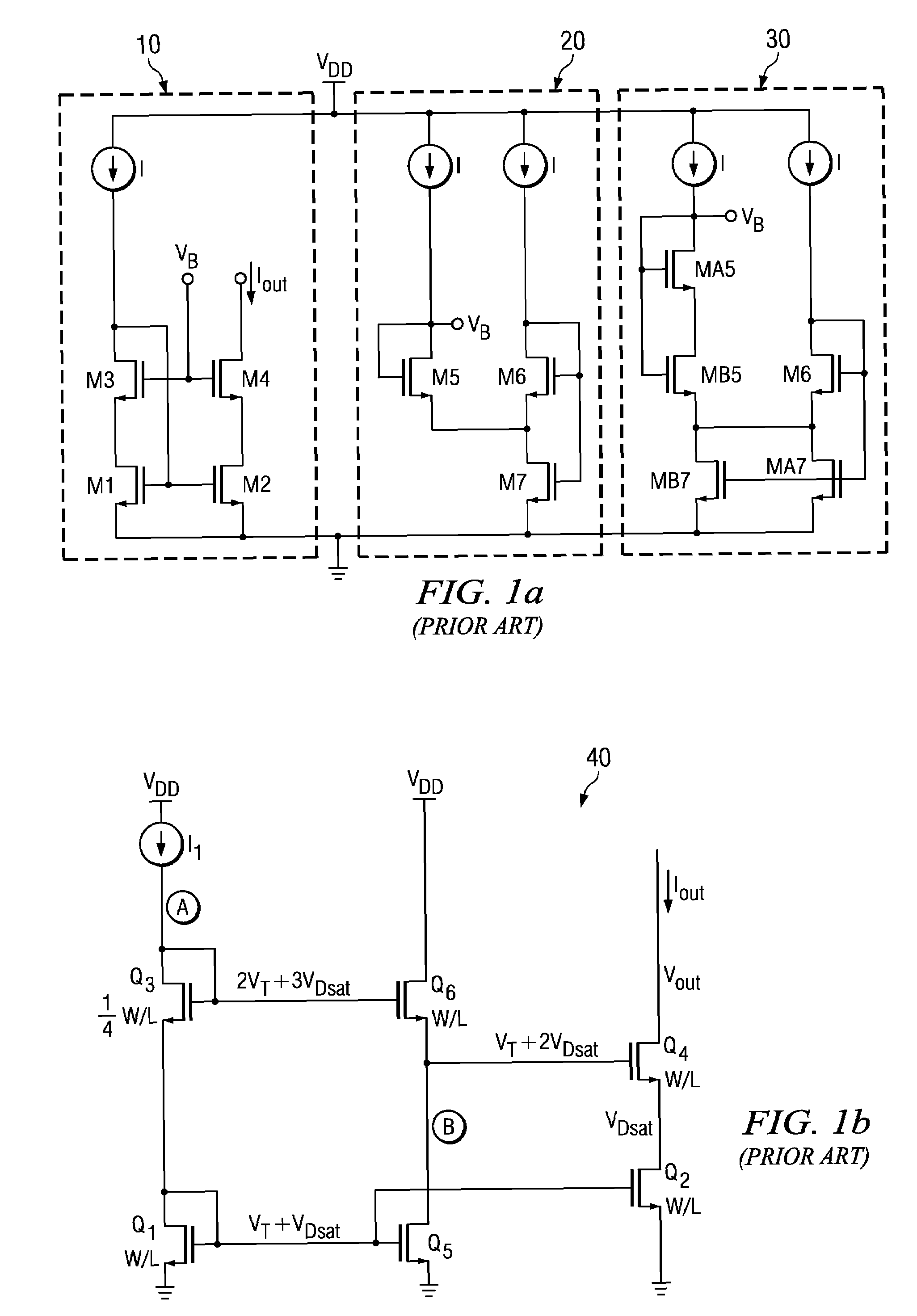

Cascoded current mirror. The cascoded current mirror resembles a stack of two simple current mirrors and it looks very much like the improved version of the Wilson current mirror (with a diode connection at Q1/M1 instead of Q2/M2). Therefore, this circuit is made up by 4 transistors.

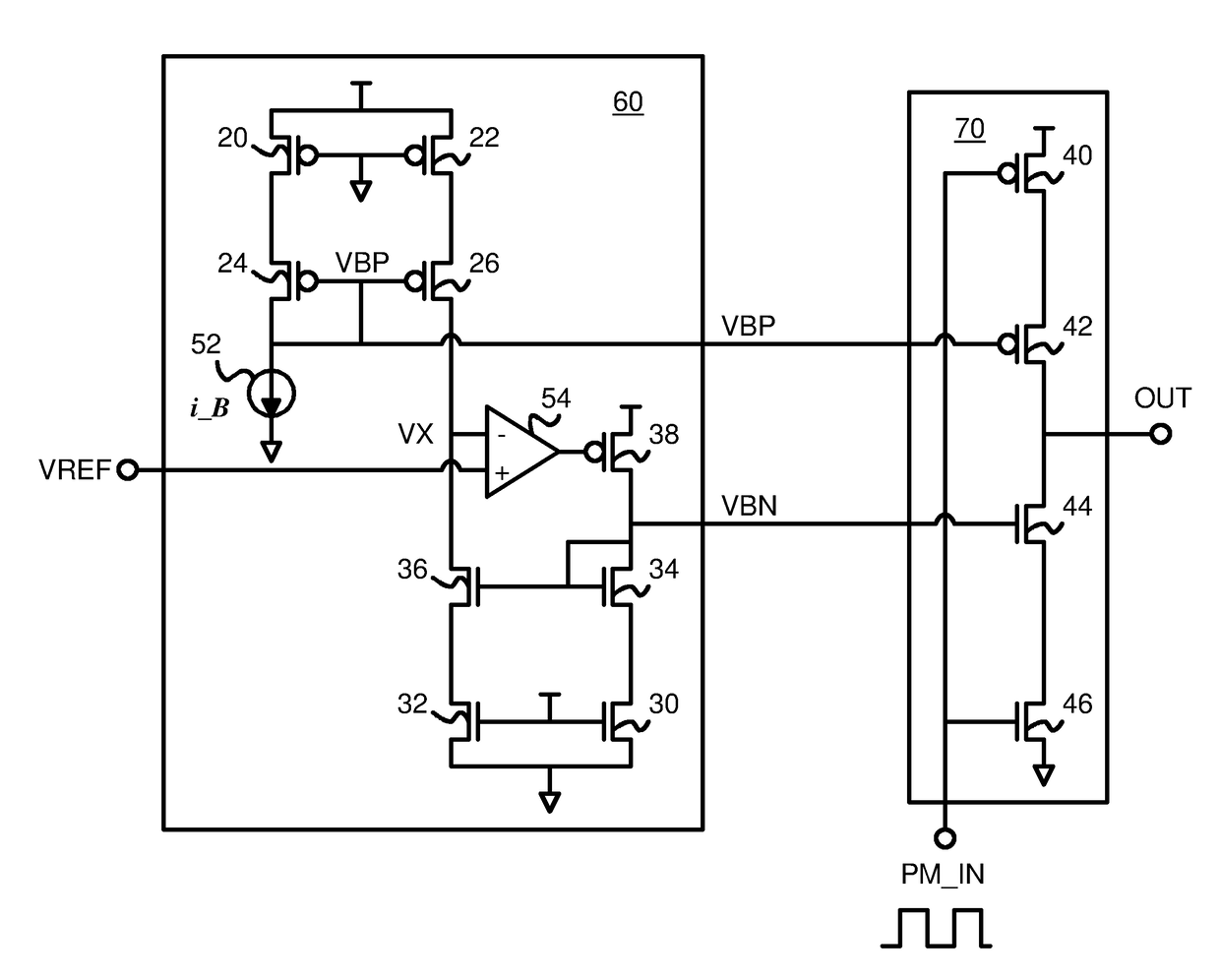

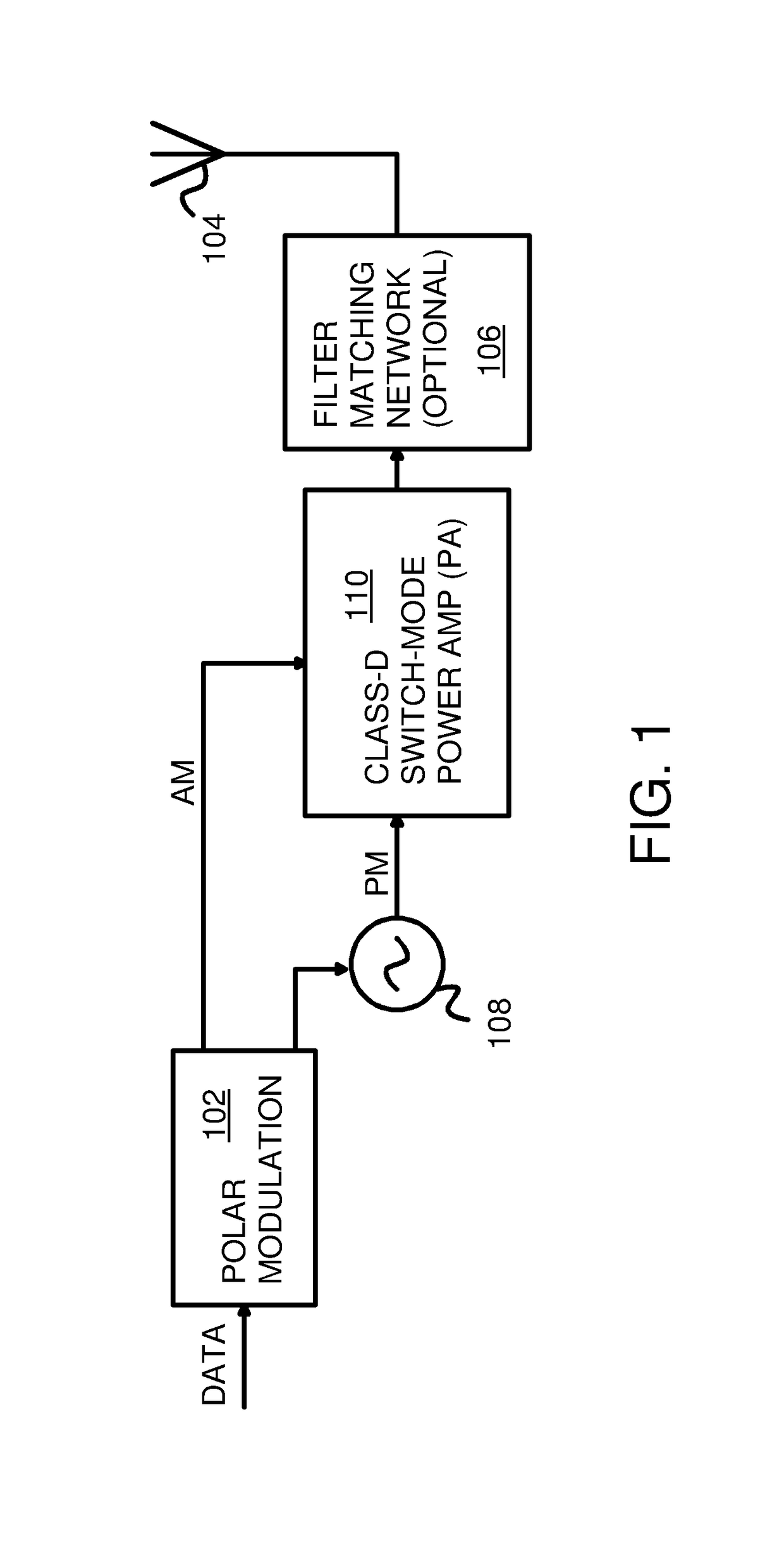

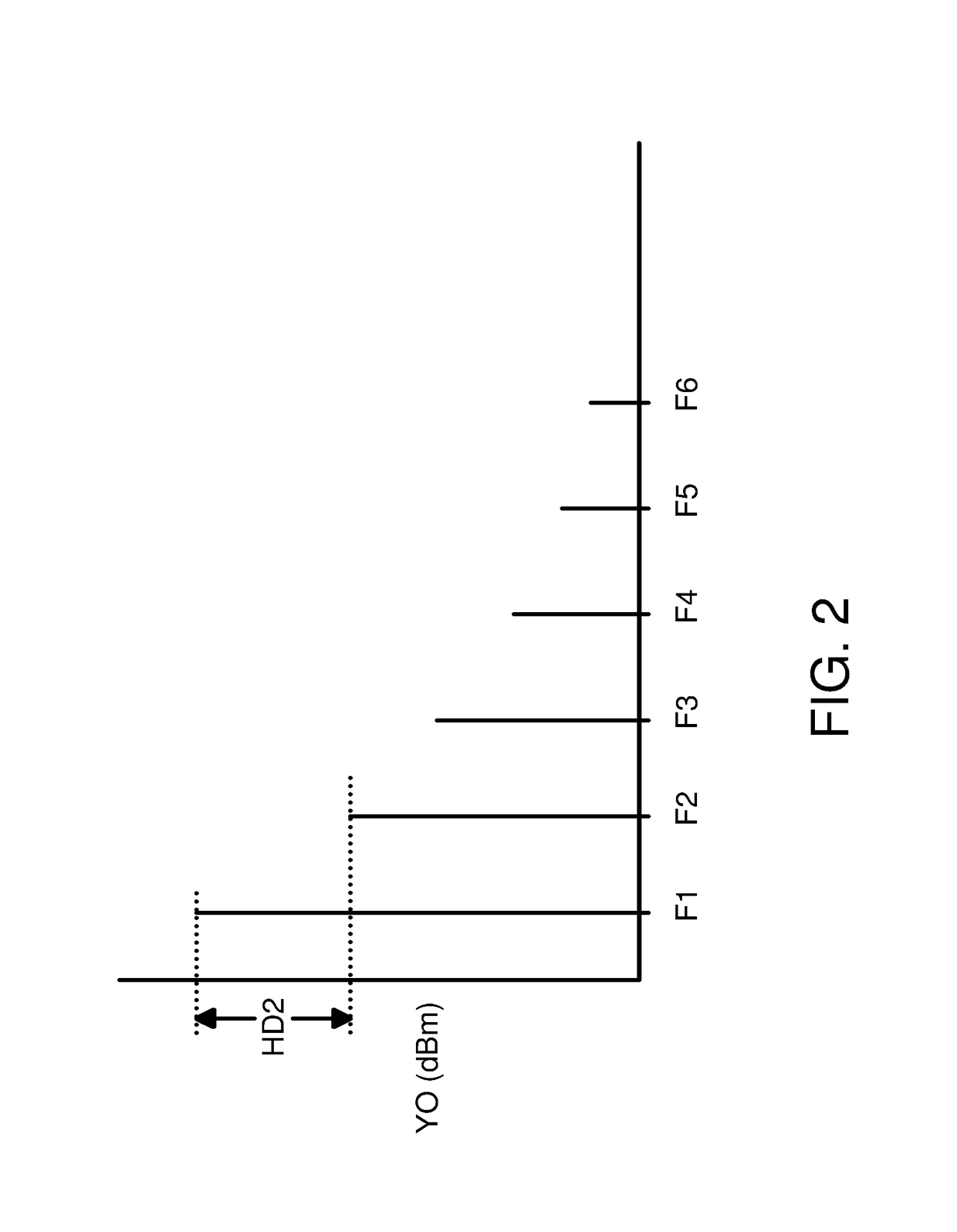

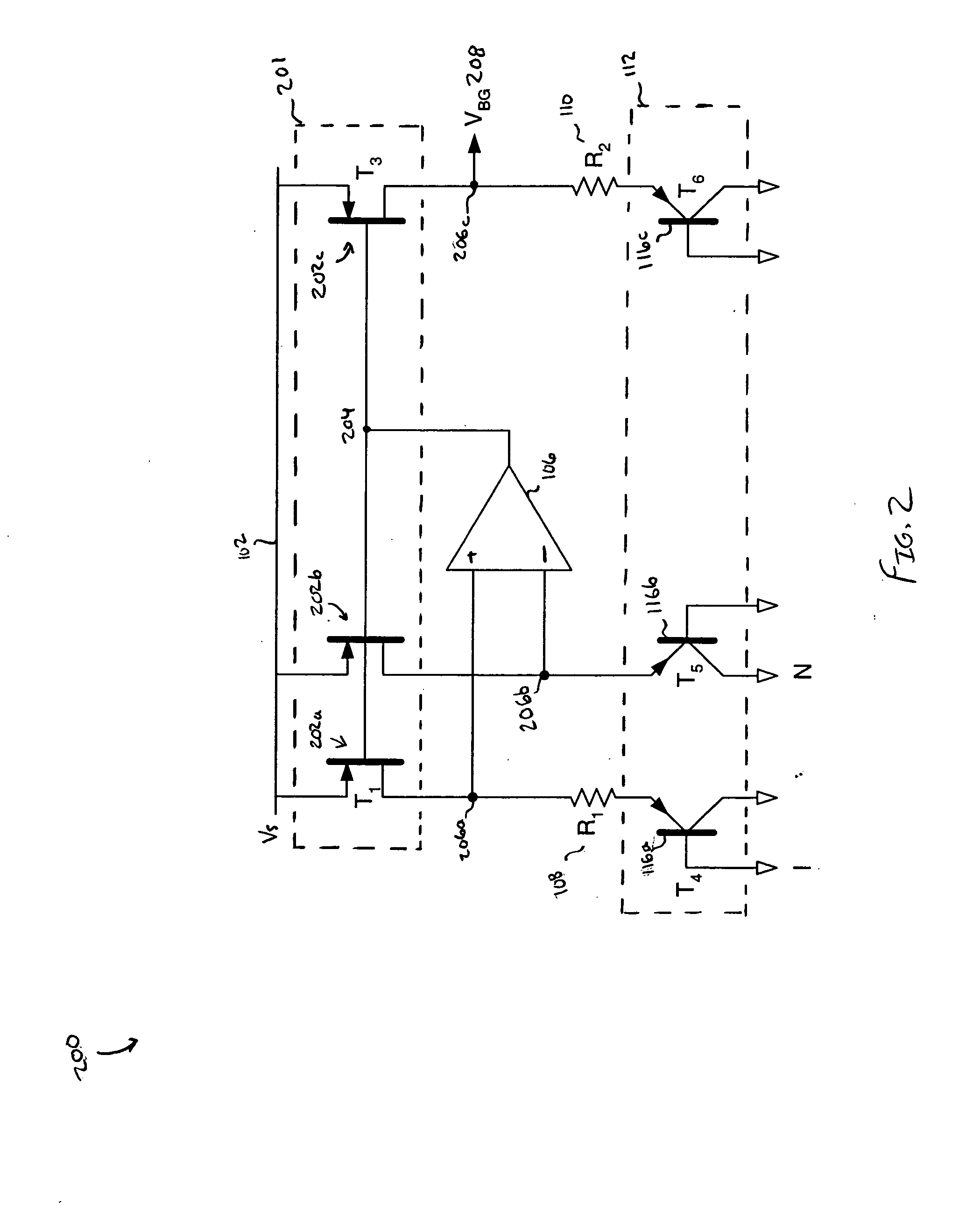

Harmonics suppression circuit for a switch-mode power amplifier

ActiveUS9641141B1Amplifier modifications to raise efficiencyAmplifier with semiconductor-devices/discharge-tubesPower flowAudio power amplifier

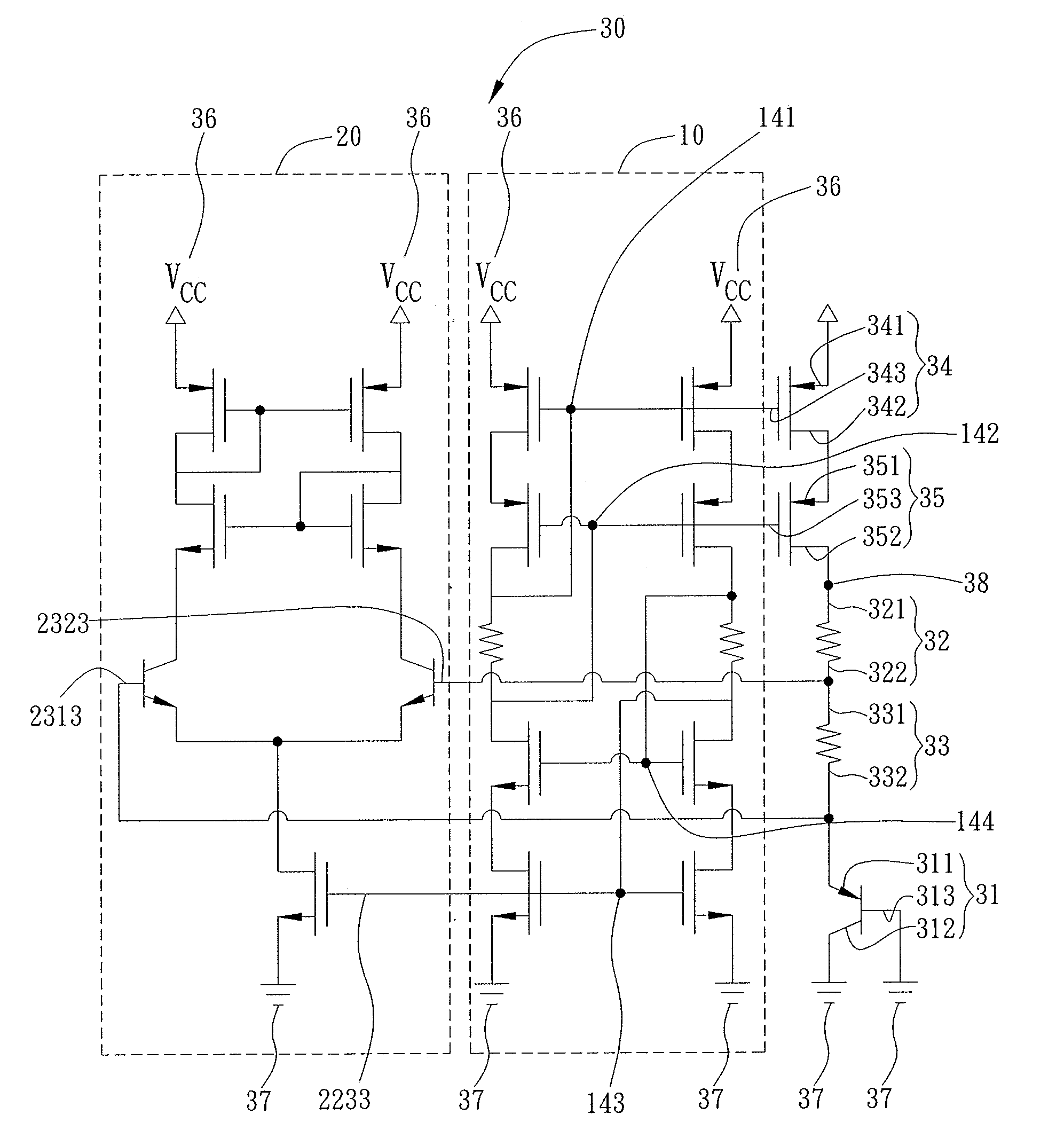

Even harmonics are suppressed by a harmonics-reducing bias generator that drives bias voltages to cascode control transistors in series with driver transistors in a power amplifier. A first bias voltage is generated by mirroring pull-up currents in the power amplifier. A p-channel source transistor and a p-channel cascode current-mirror transistor also mirror the power amplifier pull-up current to a midpoint node. An n-channel sink transistor and an n-channel cascode current-mirror transistor mirror the pull-down current in the power amplifier to the midpoint node. An op amp compares the midpoint node to VDD / 2, and drives the gate of a p-channel feedback transistor. Current from the p-channel feedback transistor flows through an n-channel cascode current-mirror transistor that generates a second bias voltage. The second bias voltage is adjusted until the midpoint node reaches VDD / 2, causing the pull-up and pull-down currents in the power amplifier to better match, reducing even harmonics.

Owner:HONG KONG APPLIED SCI & TECH RES INST

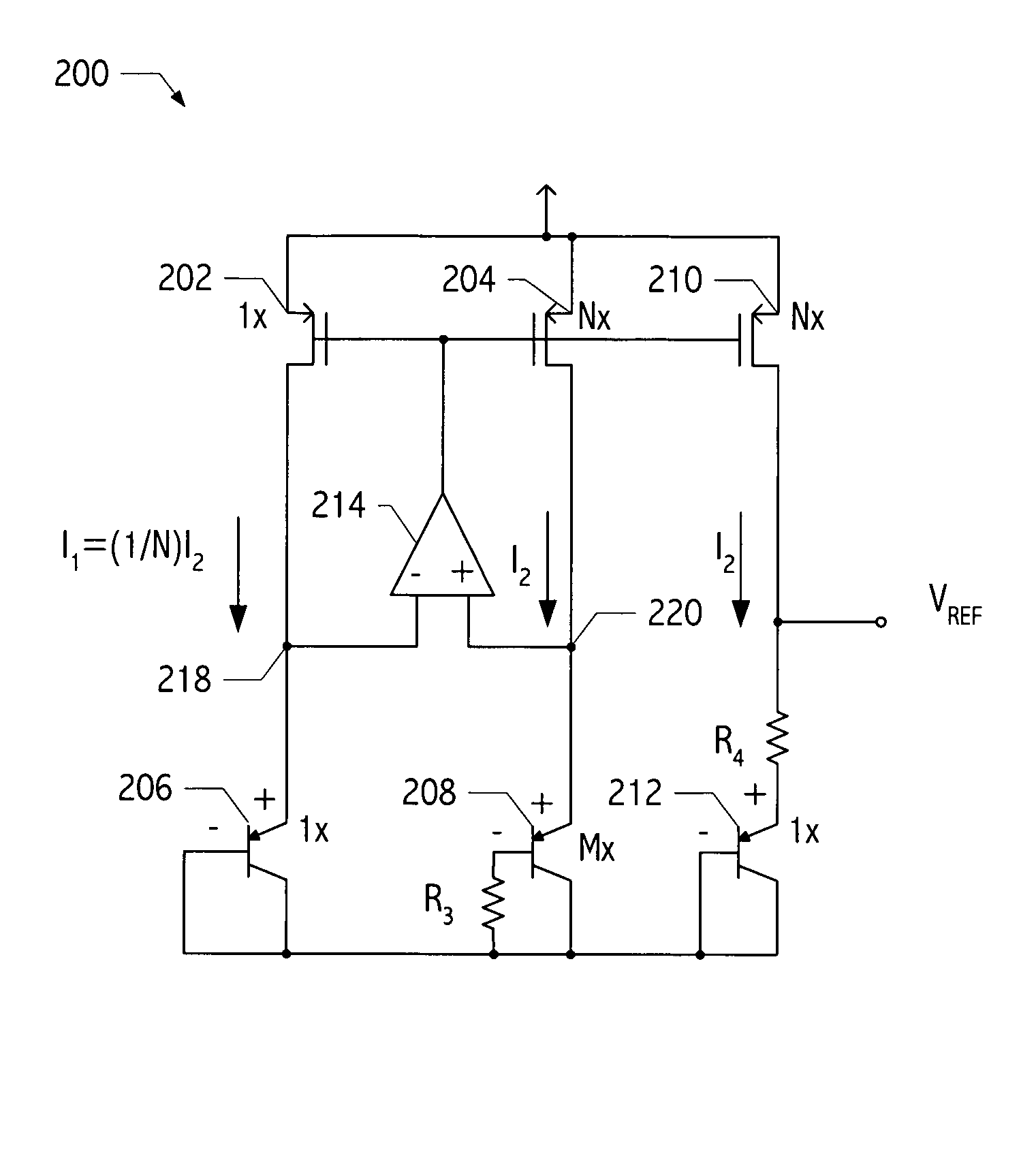

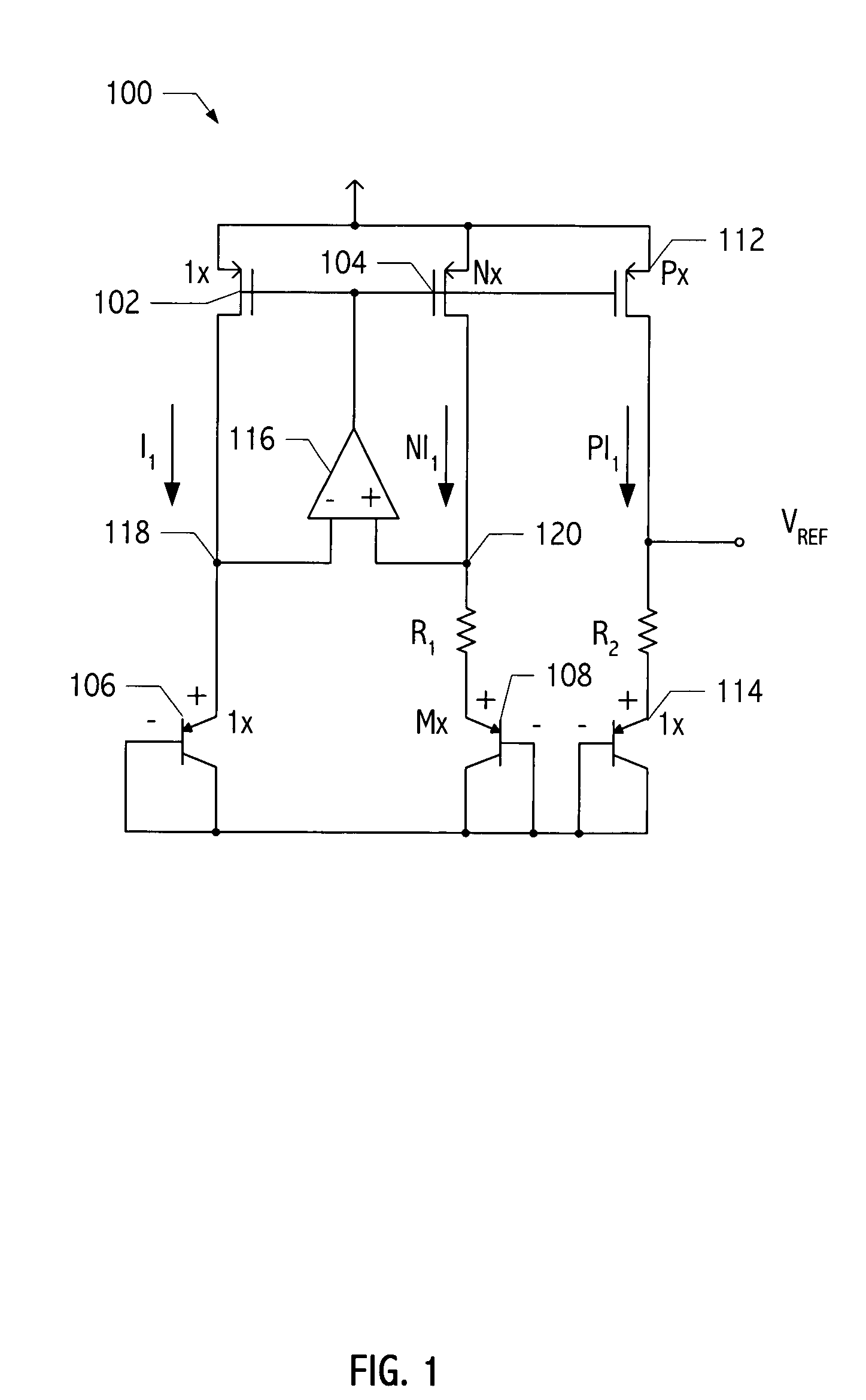

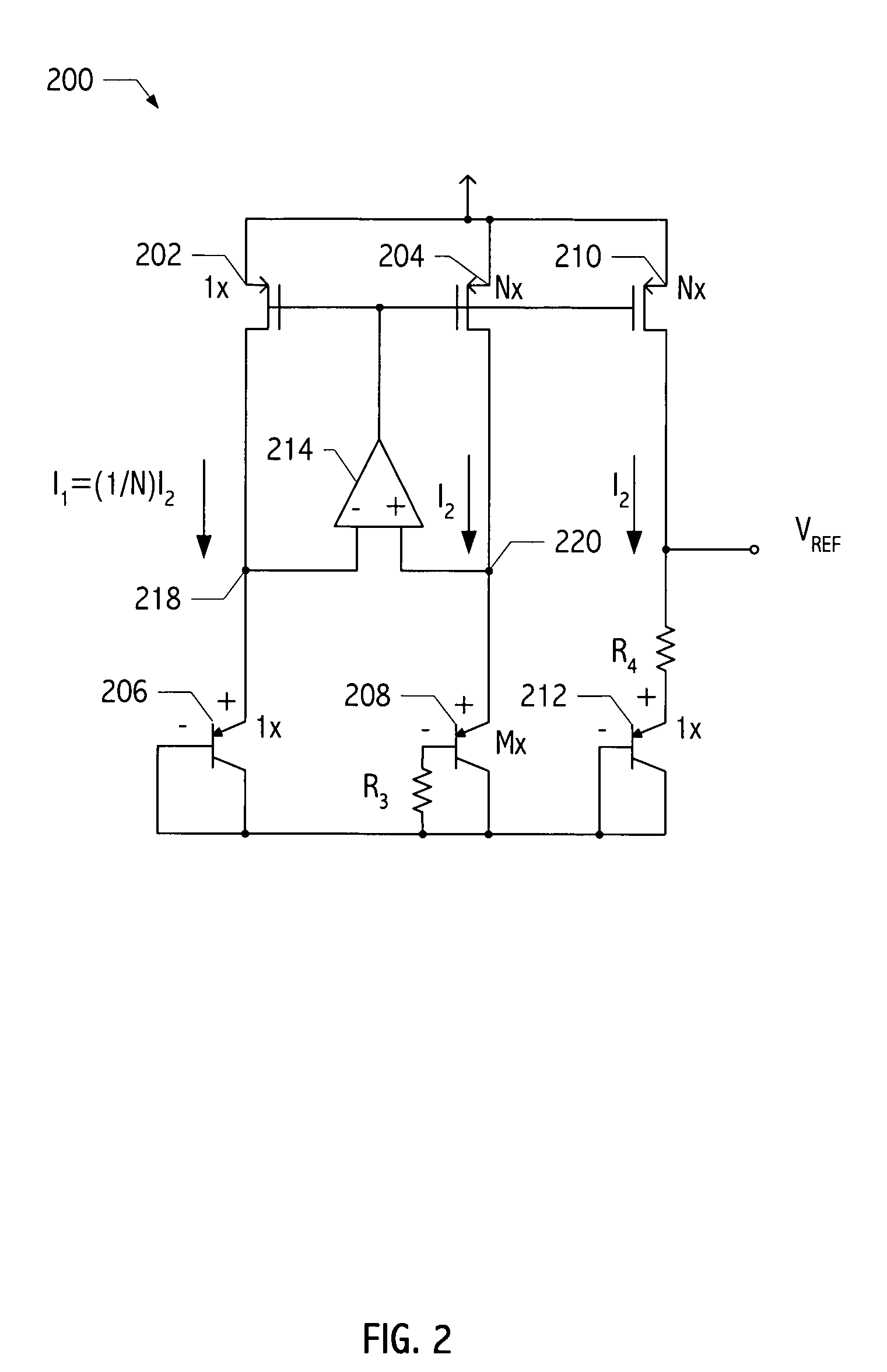

Voltage reference generator circuit using low-beta effect of a CMOS bipolar transistor

A voltage reference generator has been discovered that generates a stable reference voltage that is less than the bandgap voltage of silicon for power supply voltages less than 2V, yet provides sufficient voltage headroom to operate a cascaded current mirror. In one embodiment, the voltage reference generator has a power supply rejection ratio of at least 60 dB and has improved noise performance as compared to traditional bandgap circuits. These advantages are achieved by leveraging the low-beta effect of a CMOS bipolar transistor to generate a current proportional to an absolute temperature.

Owner:SILICON LAB INC

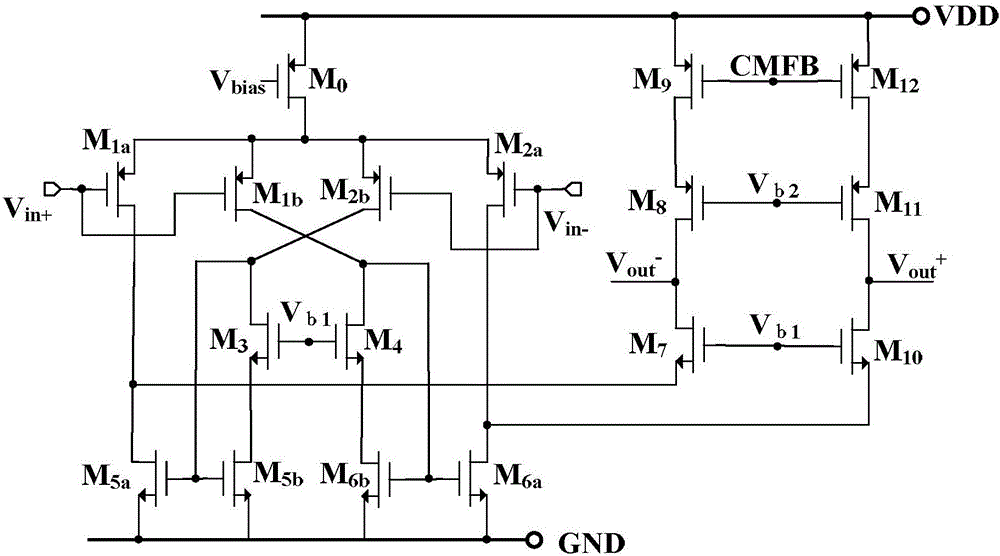

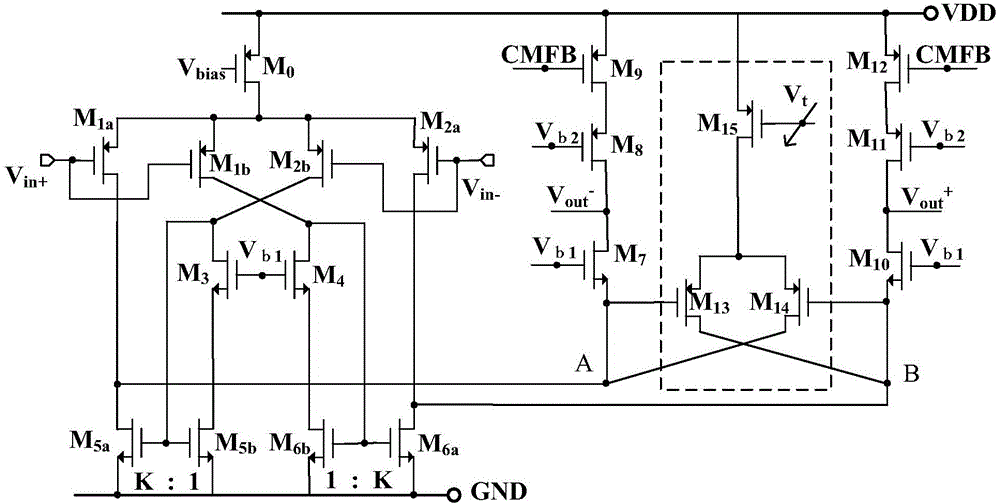

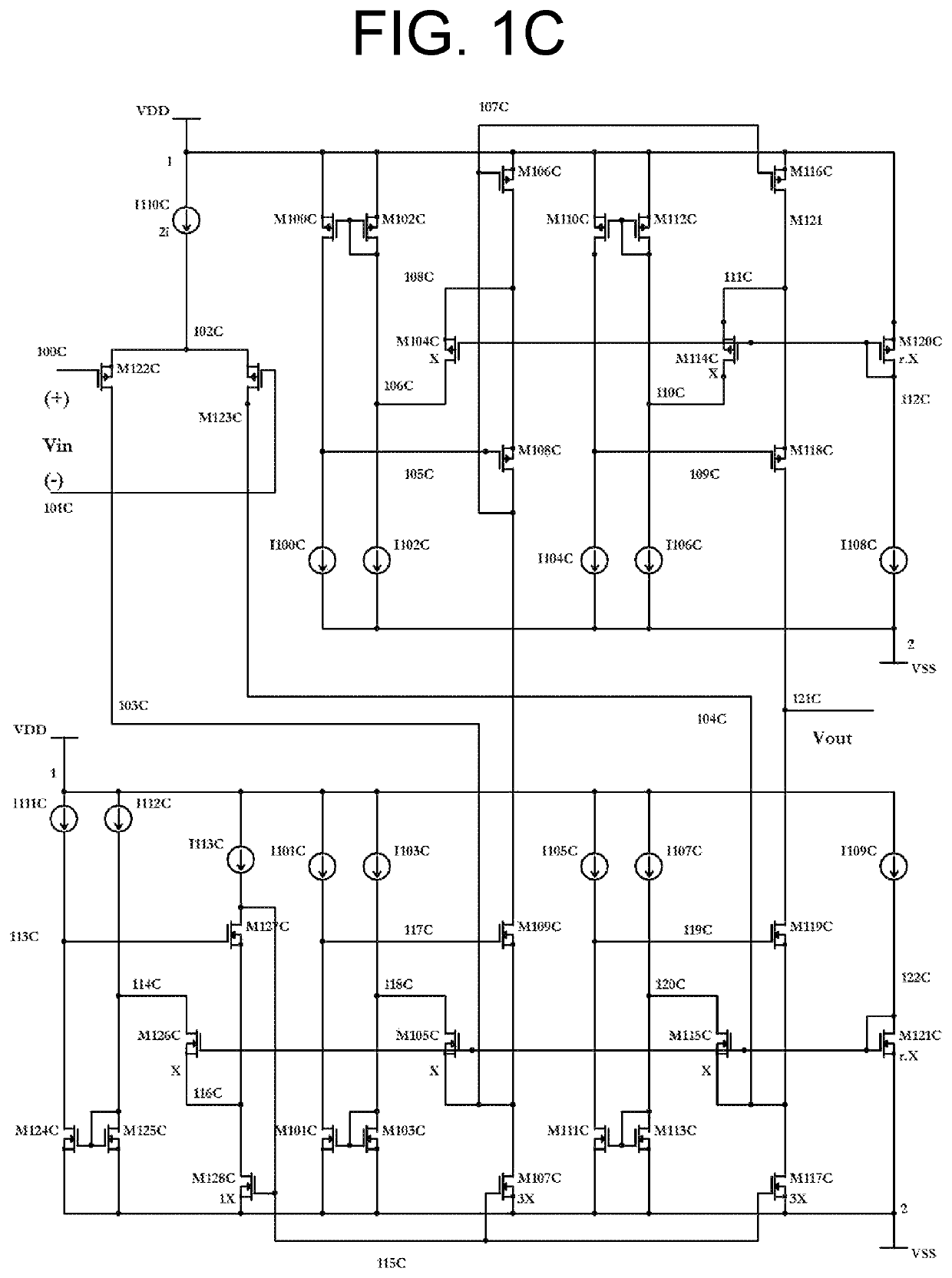

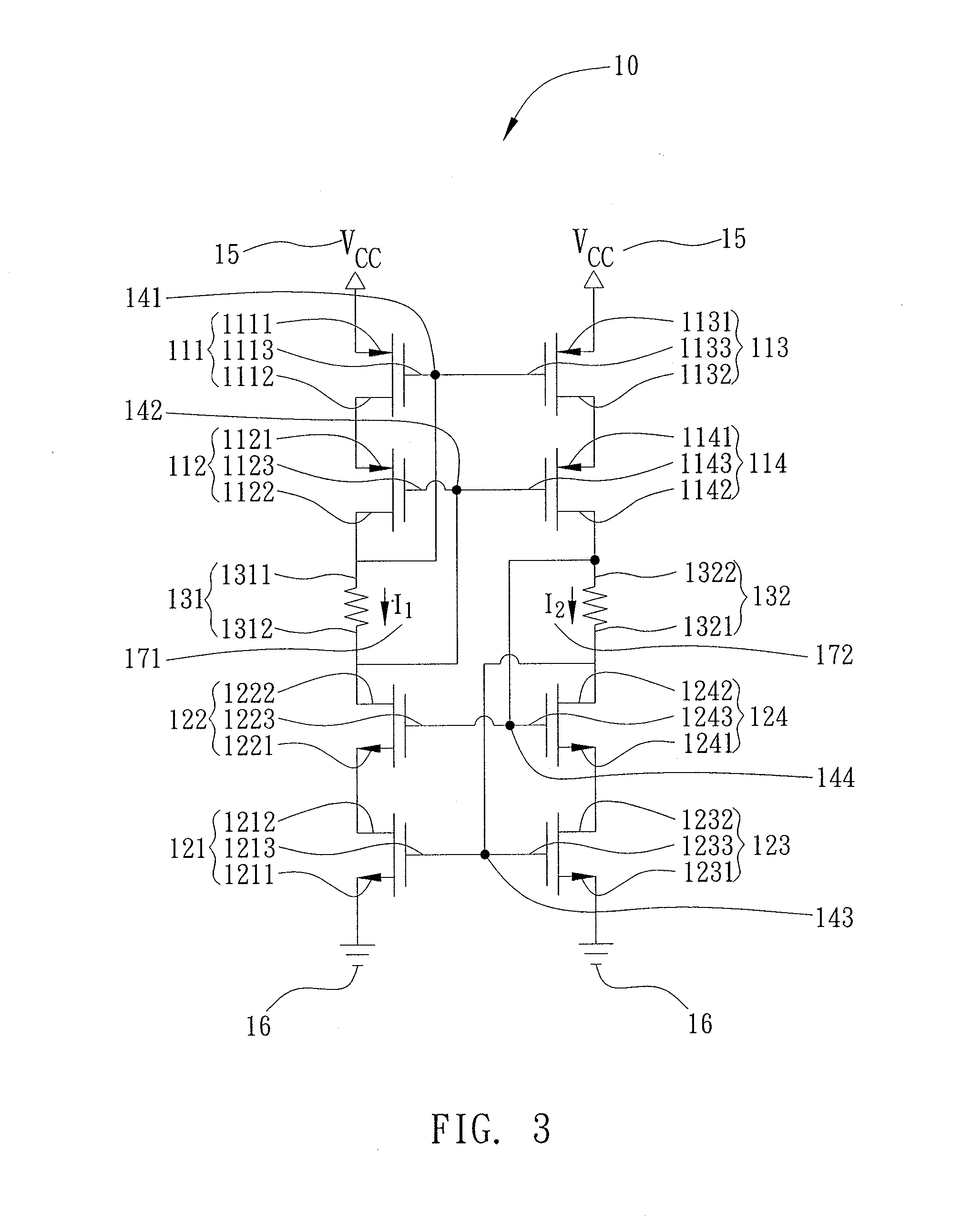

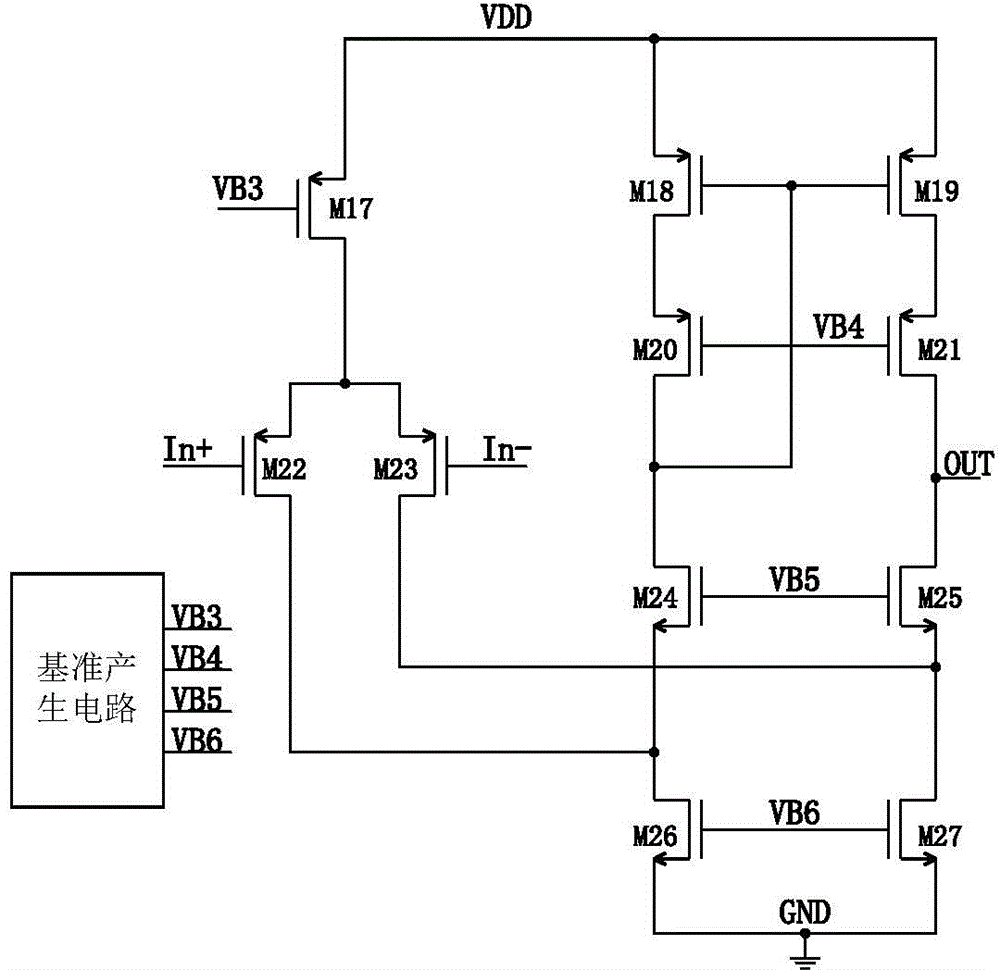

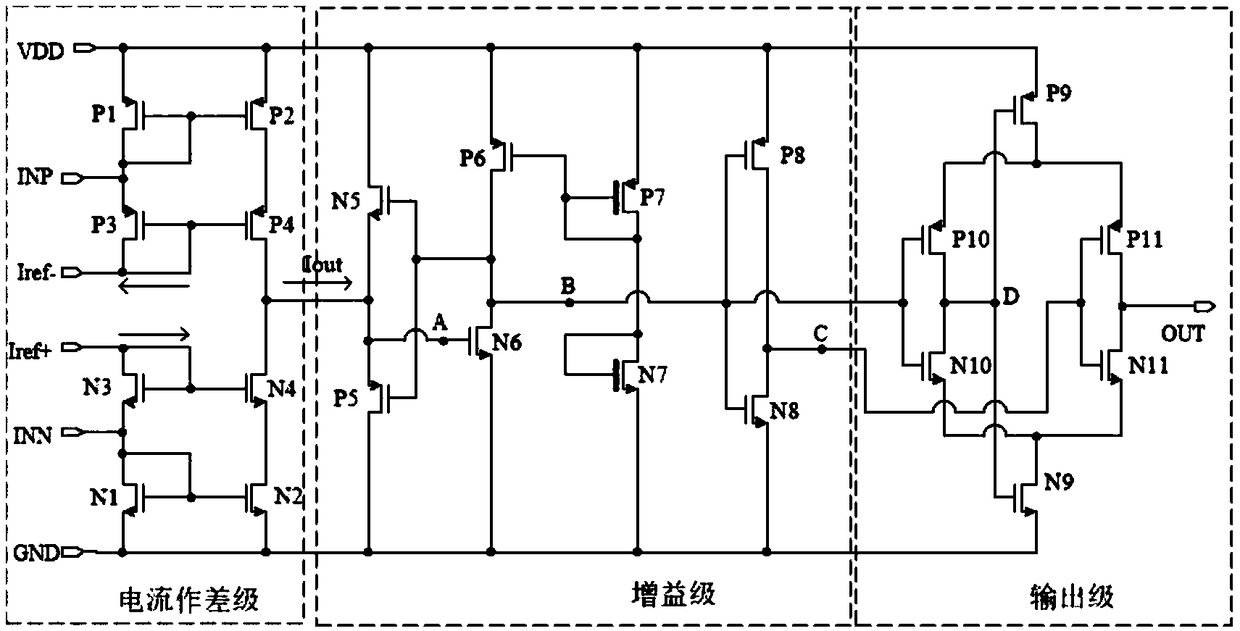

Gain increased operational transconductance amplifier

InactiveCN105141265ADoubling the transconductanceIncrease transient slew rateAmplifier modifications to reduce temperature/voltage variationDifferential amplifiersAutomatic controlPower flow

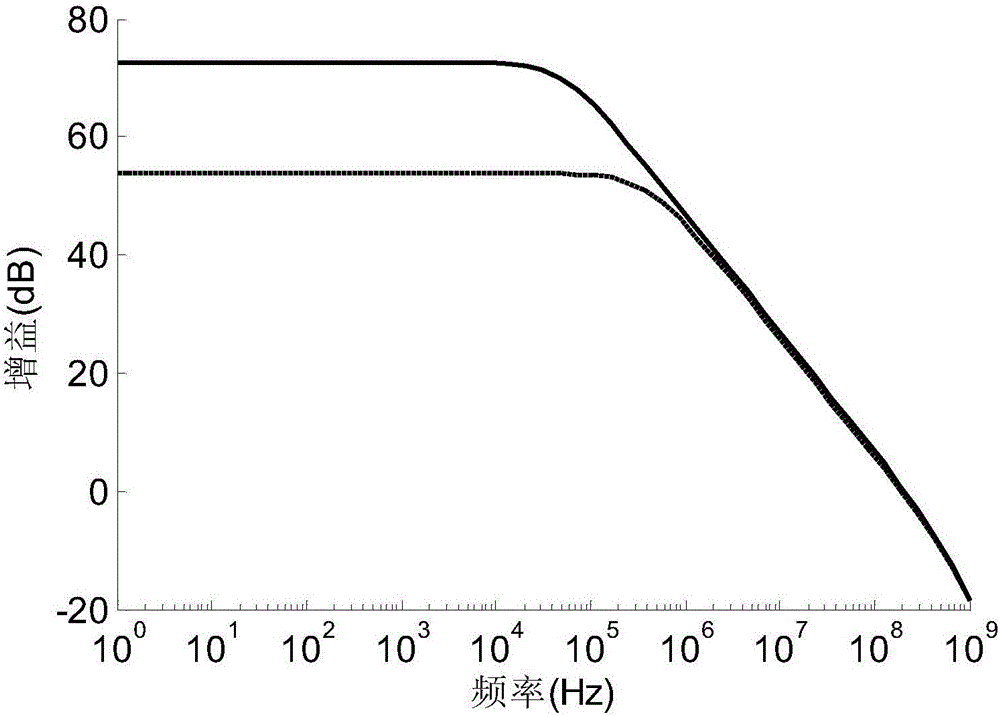

The invention discloses a gain increased operational transconductance amplifier which is formed in a manner that a bias constant current source is sequentially connected with differential input, a load current mirror, a cascode output stage and an adjustable auxiliary differential pair in sequence, wherein the differential input is composed of four PMOS pipes namely M1a, M2a, M1b and M2b; the load current mirror is composed of six NMOS pipes namely M3, M4, M5a, M6a, M5b and M6b; the cascode output stage is composed of six MOS pipes namely M7, M8, M9, M10, M11 and M12; the adjustable auxiliary differential pair is composed of M13, M14 and M15. Reutilization of current and the output stage increased adjustable auxiliary differential pair thoroughly solve the inherent contradiction among gain, bandwidth, power dissipation and the like in a circuit; the gain increased operational transconductance amplifier is slightly influenced by output voltage, an additional pole is not introduced, the simulation results show same static power dissipation, and multiplication is realized for gain and bandwidth; the gain increased operational transconductance amplifier further has the characteristics of fine tuning and high accuracy and is applicable to communication, electronic measurement and automatic control systems.

Owner:GUANGXI NORMAL UNIV

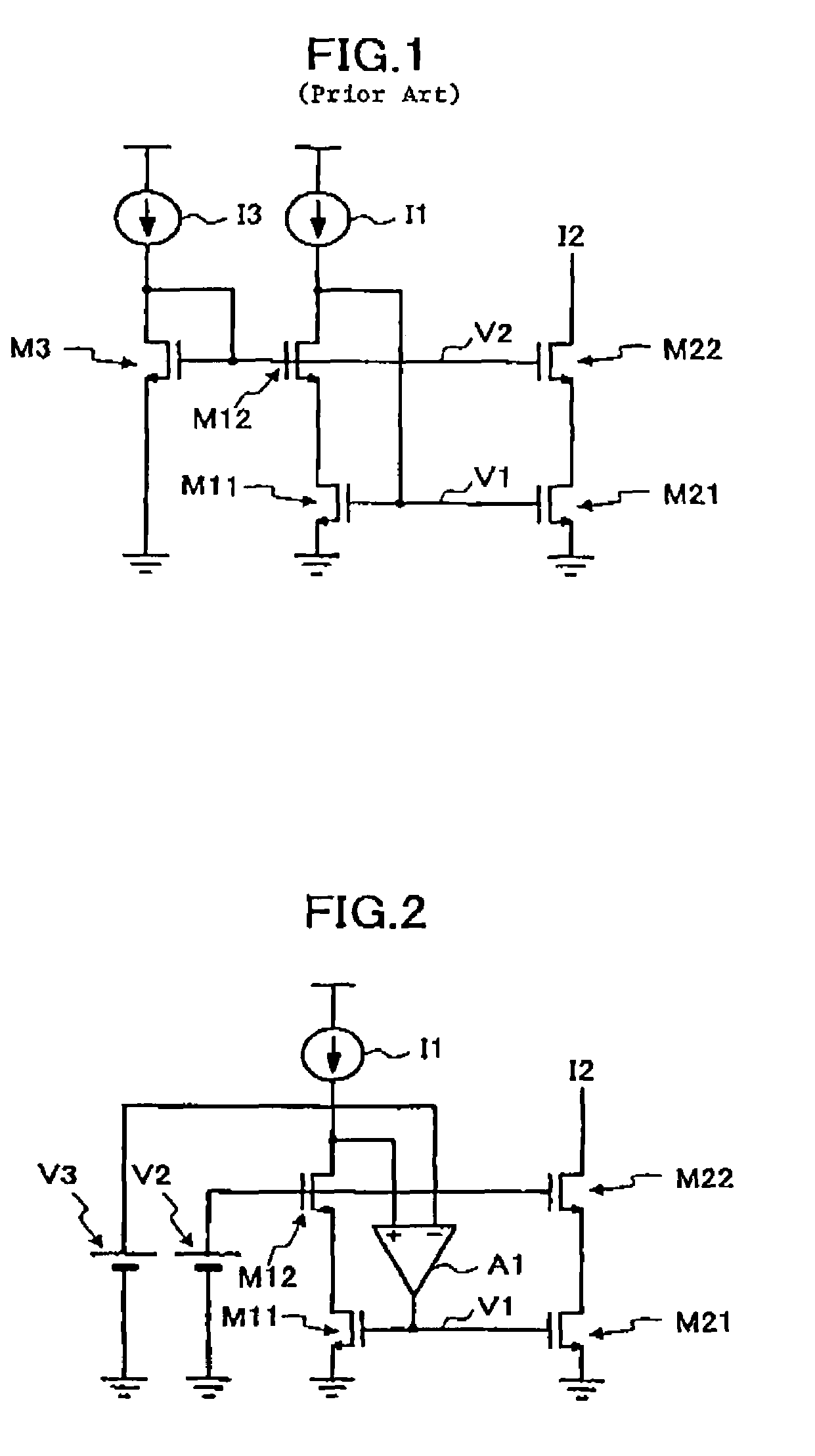

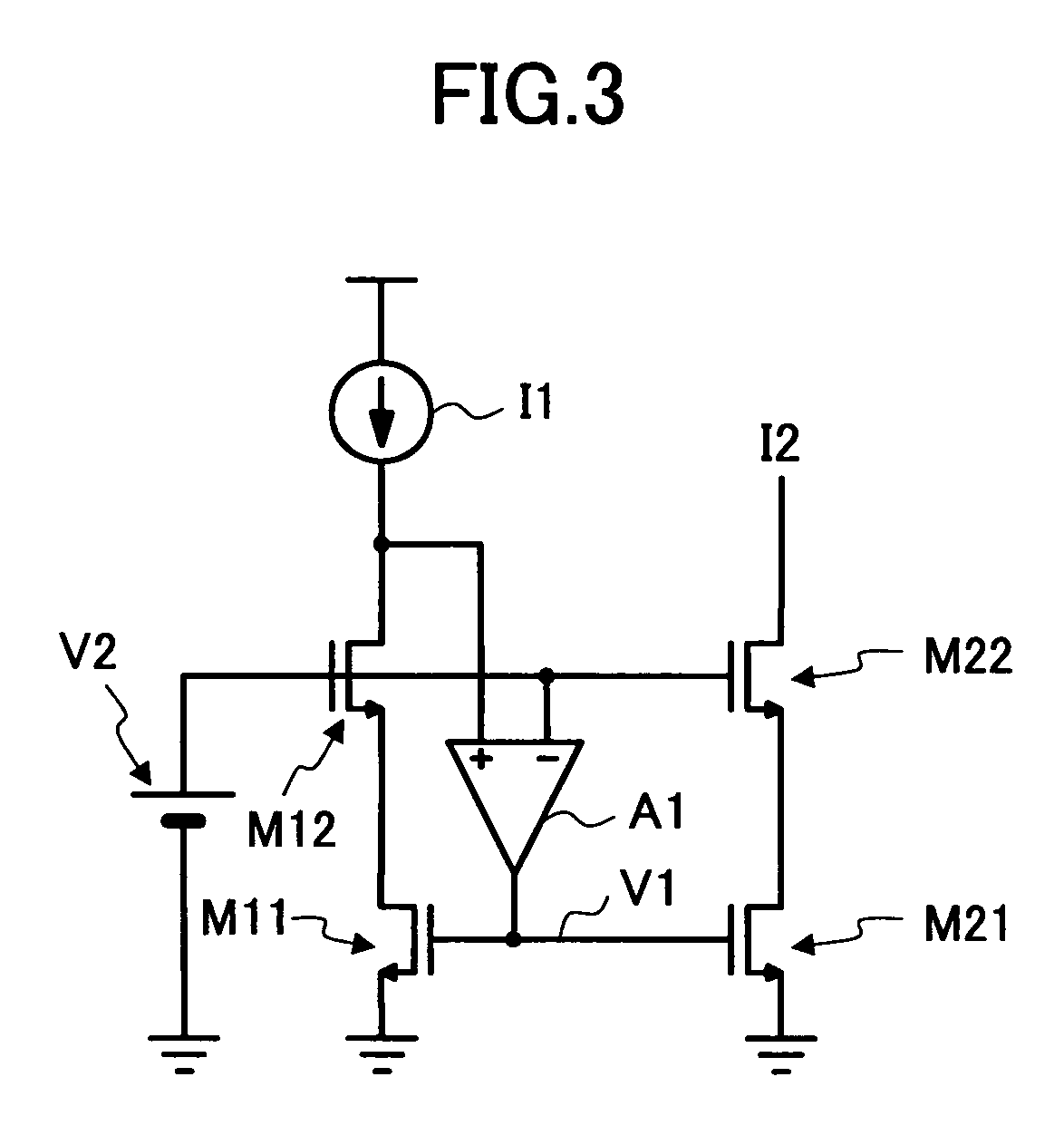

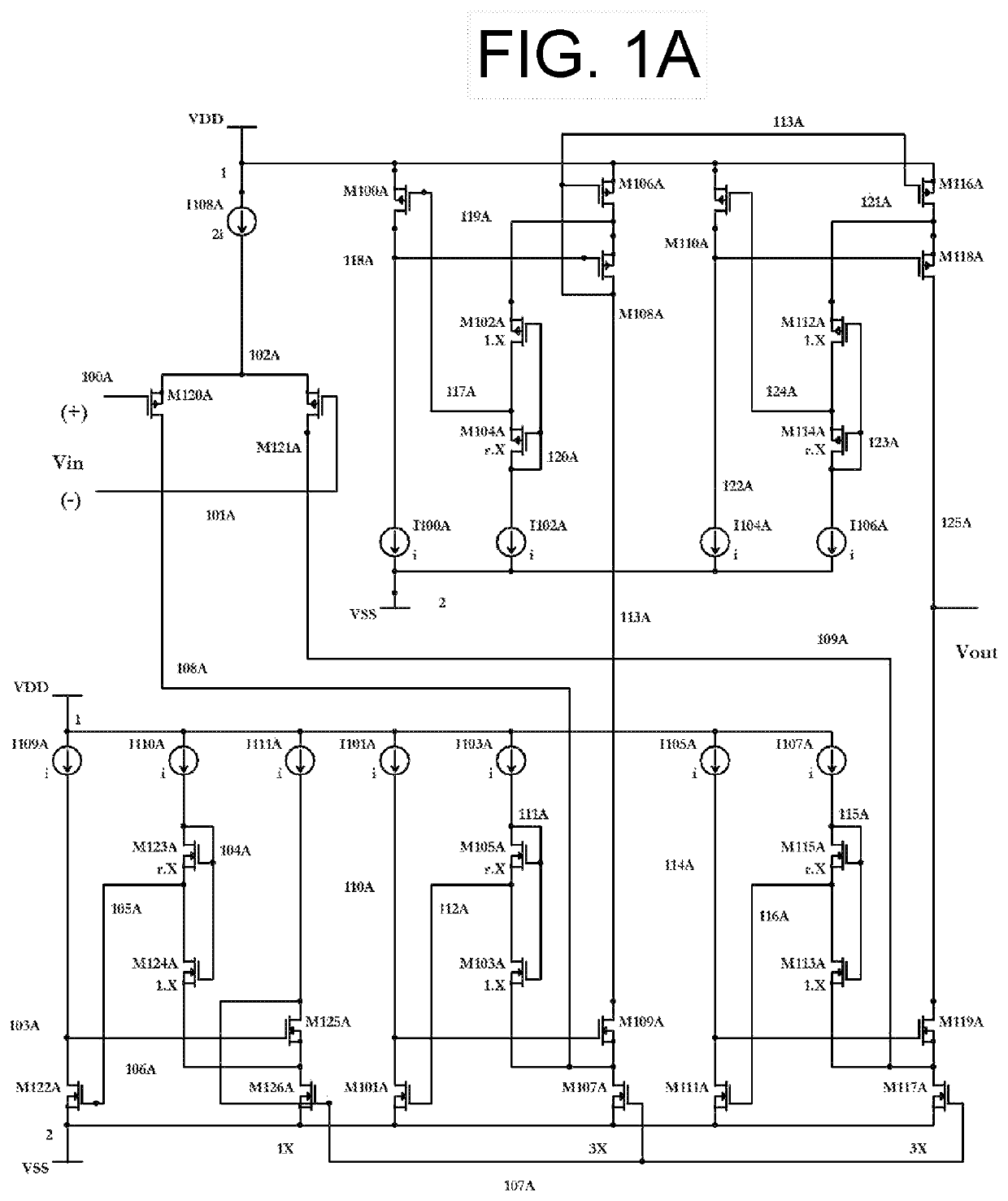

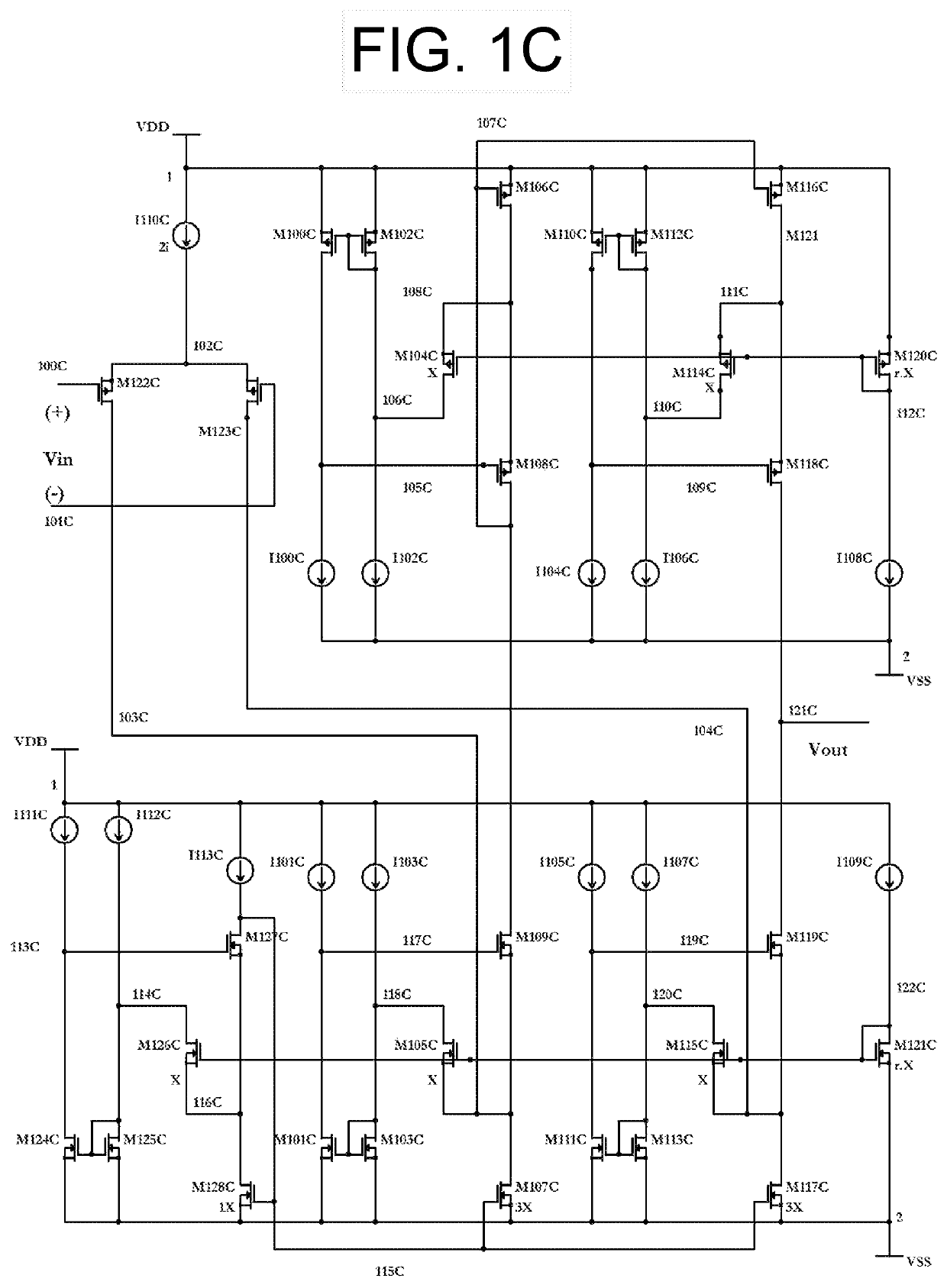

Differential amplifier, data driver and display device

ActiveUS20070159250A1Convenient ArrangementSlightly affectedDifferential amplifiersDc-amplifiers with dc-coupled stagesLoad circuitDisplay device

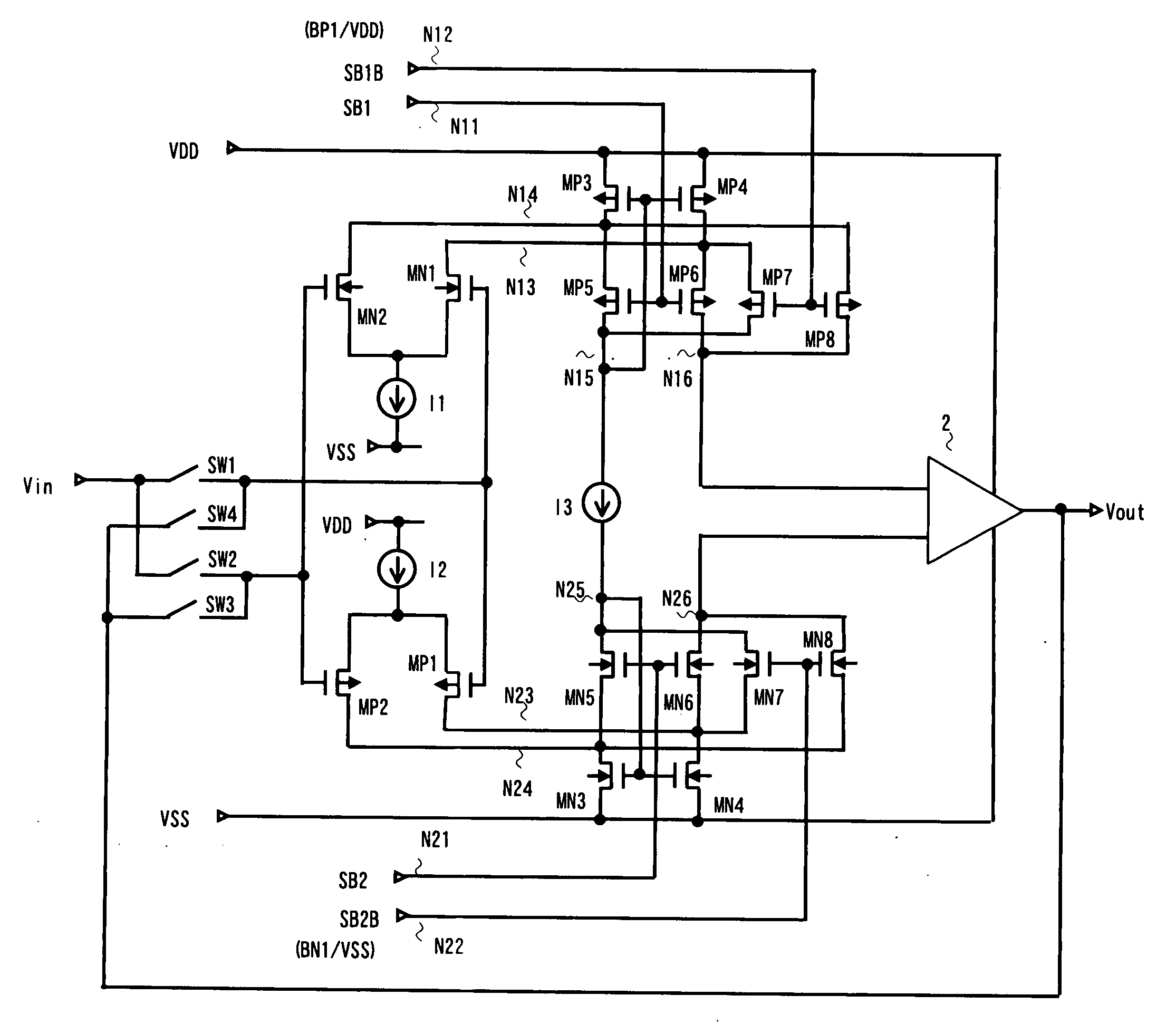

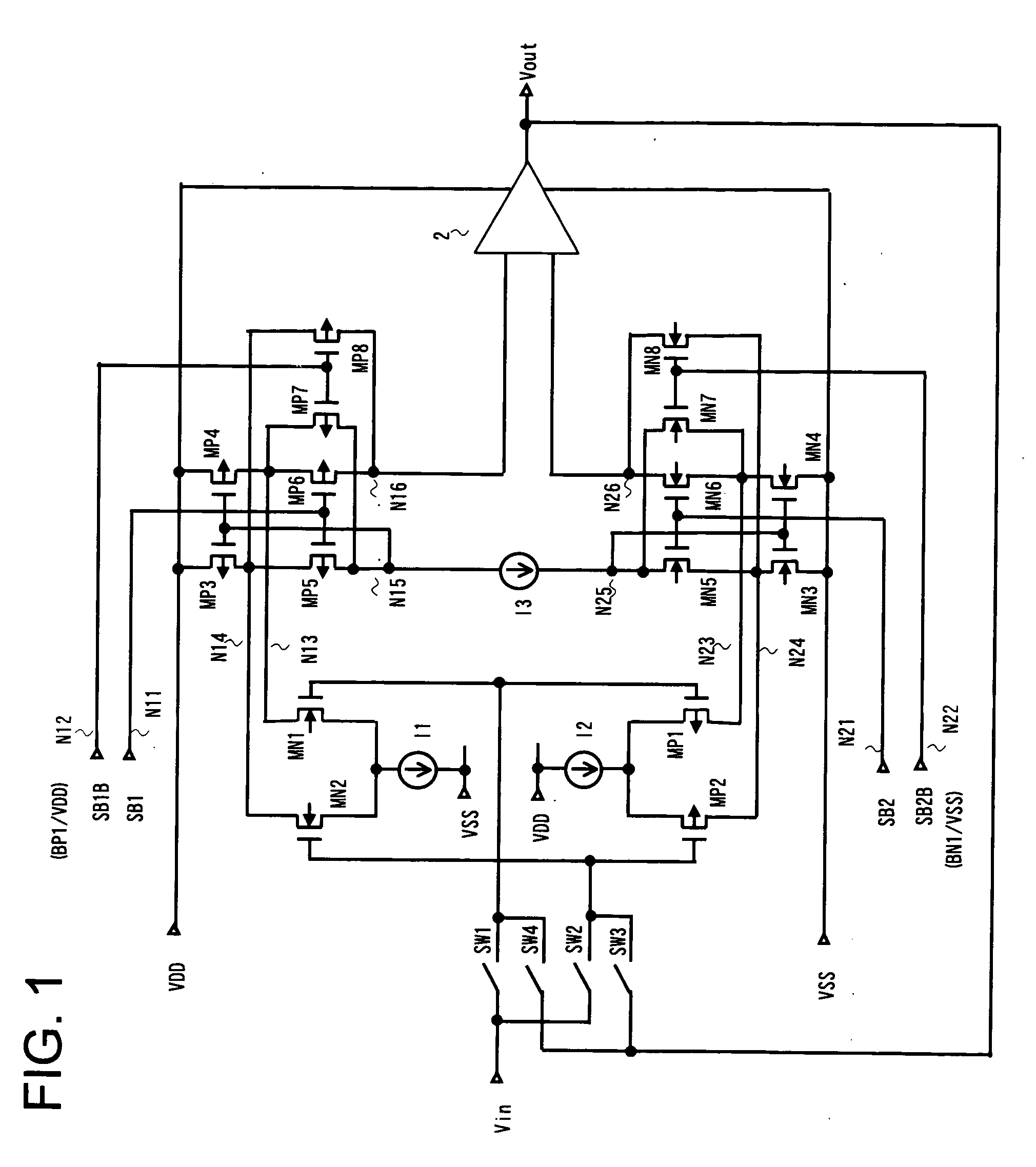

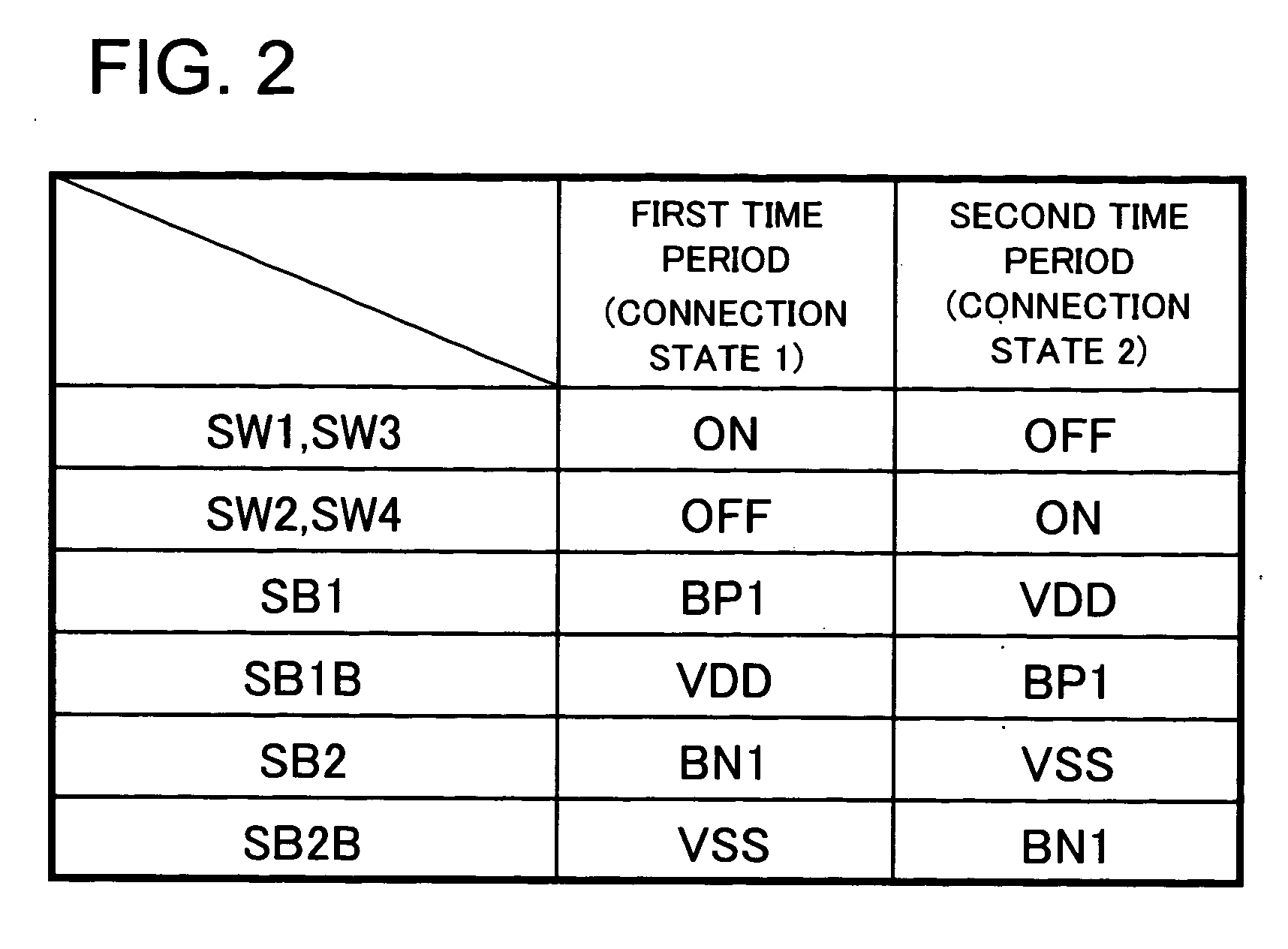

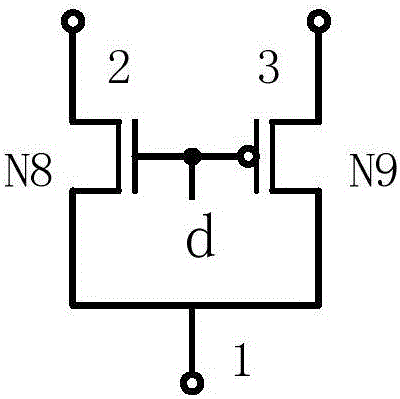

A differential amplifying circuit that includes a differential pair and a cascode current mirror circuit that forms the load circuit of this differential pair. The cascode current mirror circuit includes a control-terminal-coupled first transistor pair, and second and third transistor pairs that receive first and second bias signals at coupled control terminals, respectively. The second transistor pair is straight-connected between the first transistor pair and the input end and the output end of the cascode current mirror circuit, and the third transistor pair is cross-connected between the first transistor pair and the input end and the output end of the cascode current mirror circuit. The second and third transistor pairs are controlled so as to each be placed in active and inactive states by changing over voltage values of the first and second bias signals, with control being exercised in such a manner that when one of these transistor pairs is in an active state, the other is in an inactive state.

Owner:RENESAS ELECTRONICS CORP

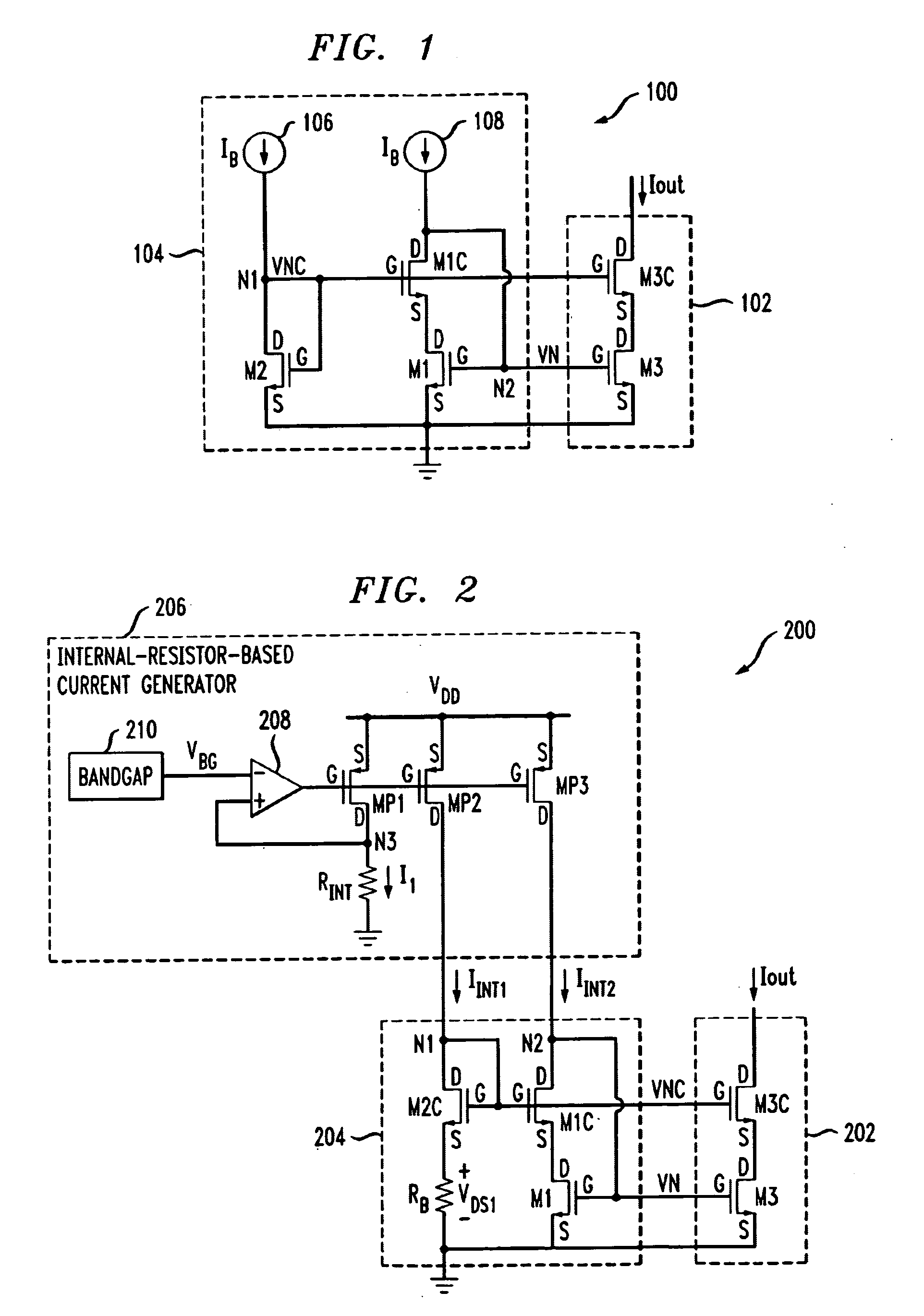

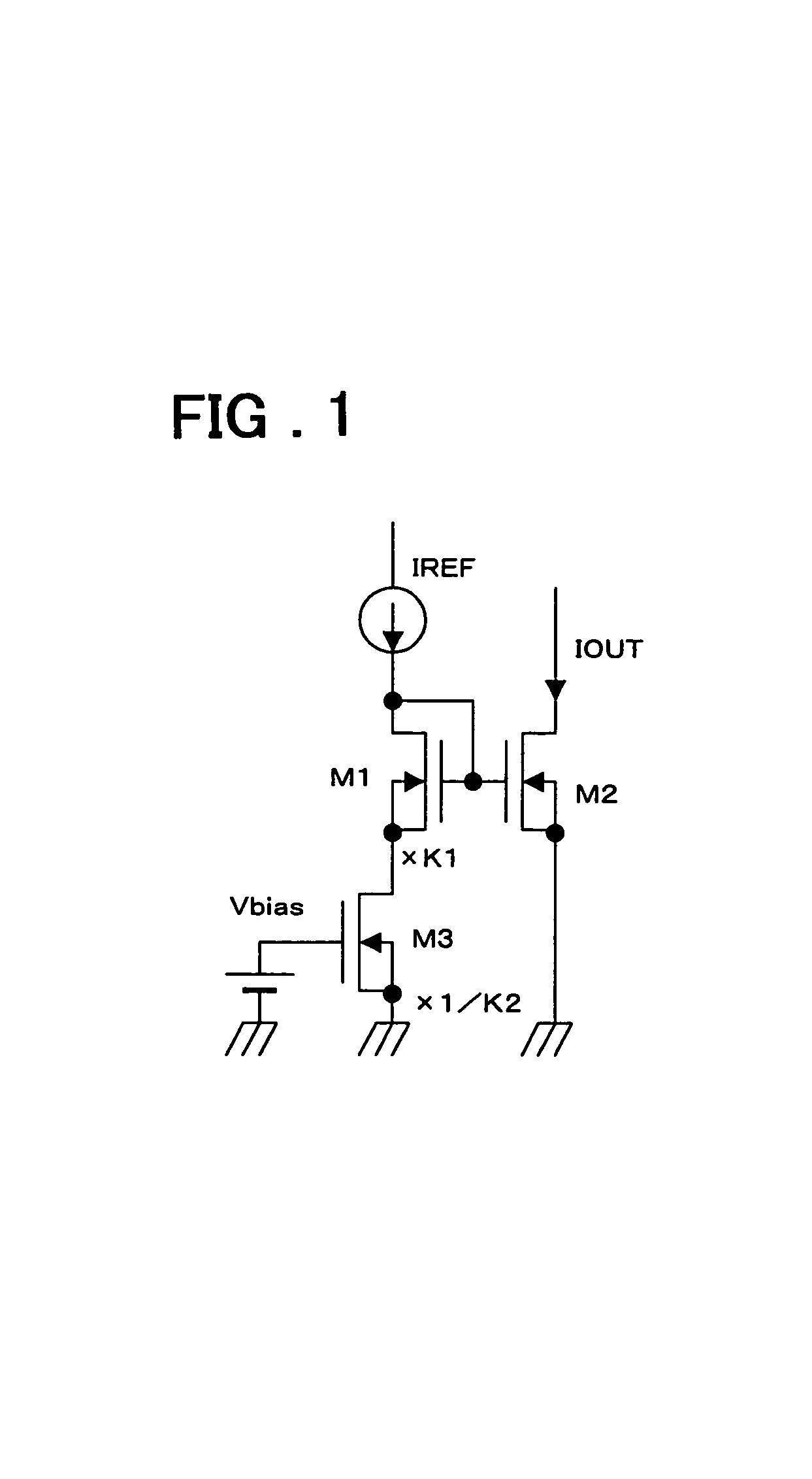

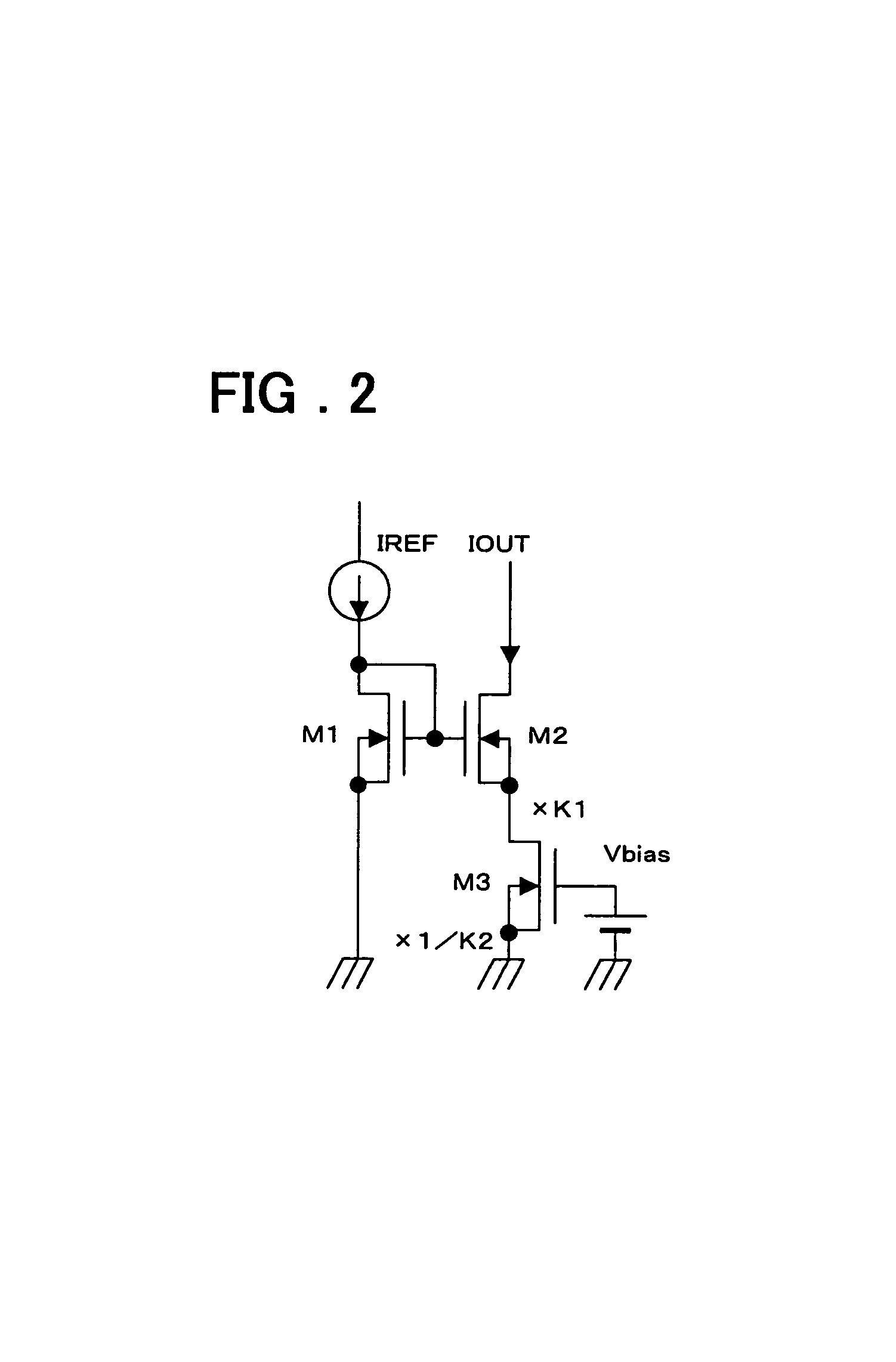

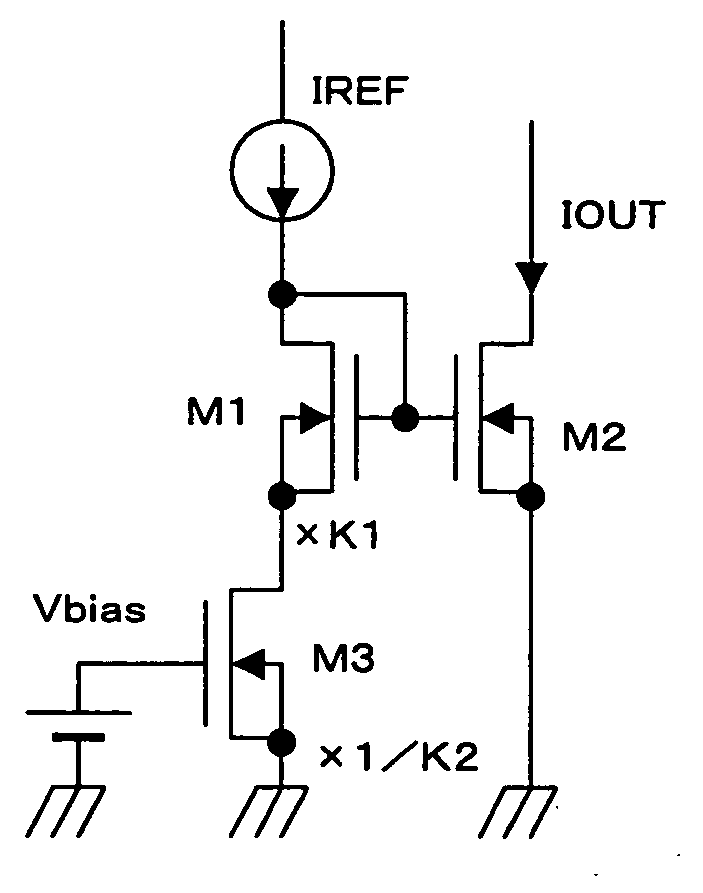

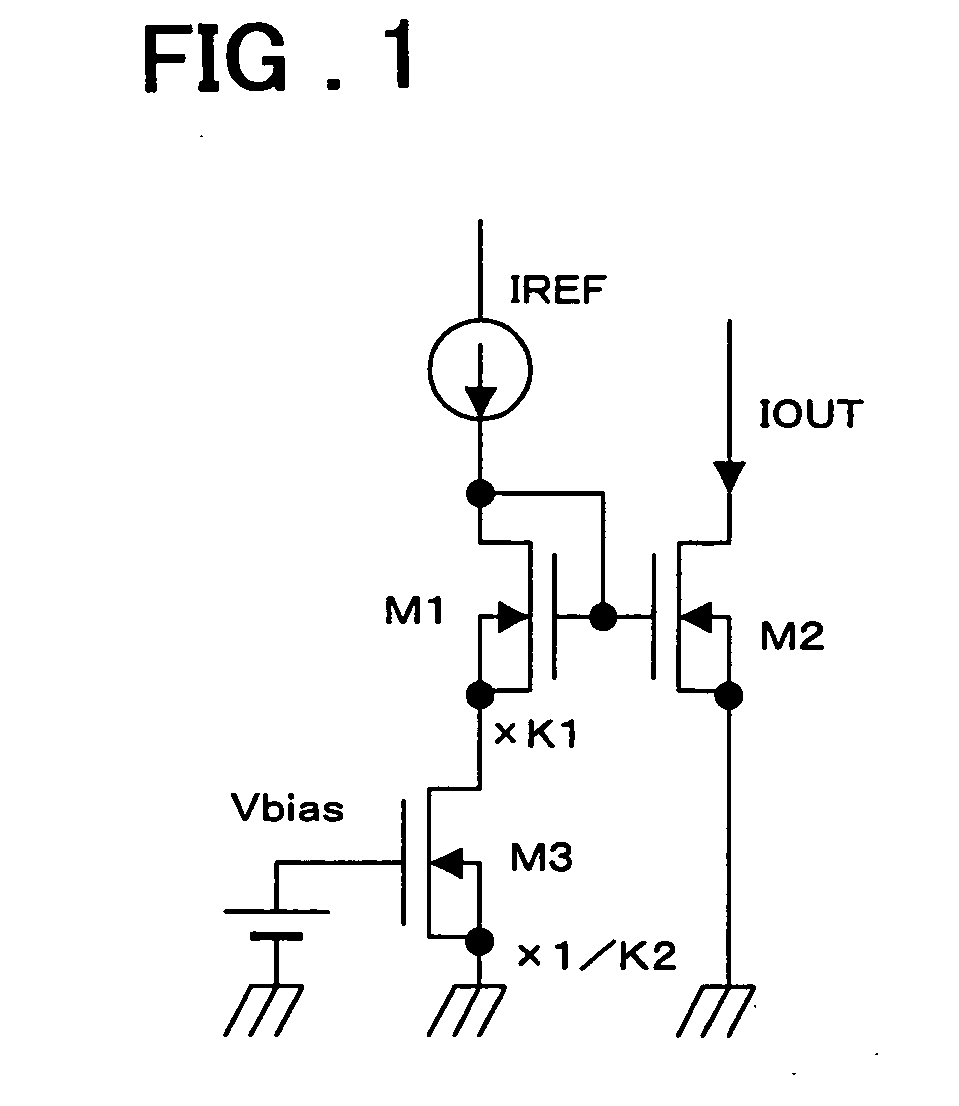

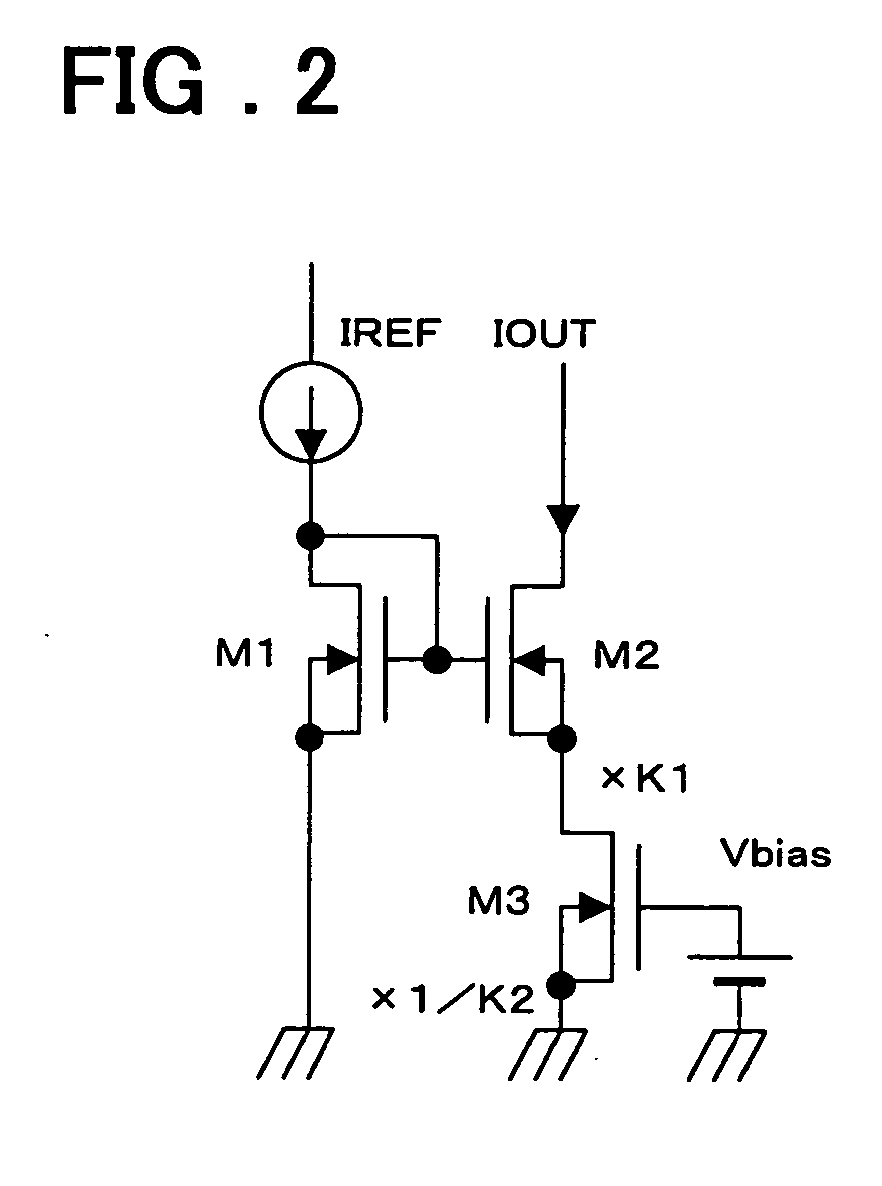

Bias circuit for high-swing cascode current mirrors

InactiveUS7208998B2Electric variable regulationAmplifiers with semiconductor devices onlyReference currentCascode current mirror

Owner:AVAGO TECH INT SALES PTE LTD

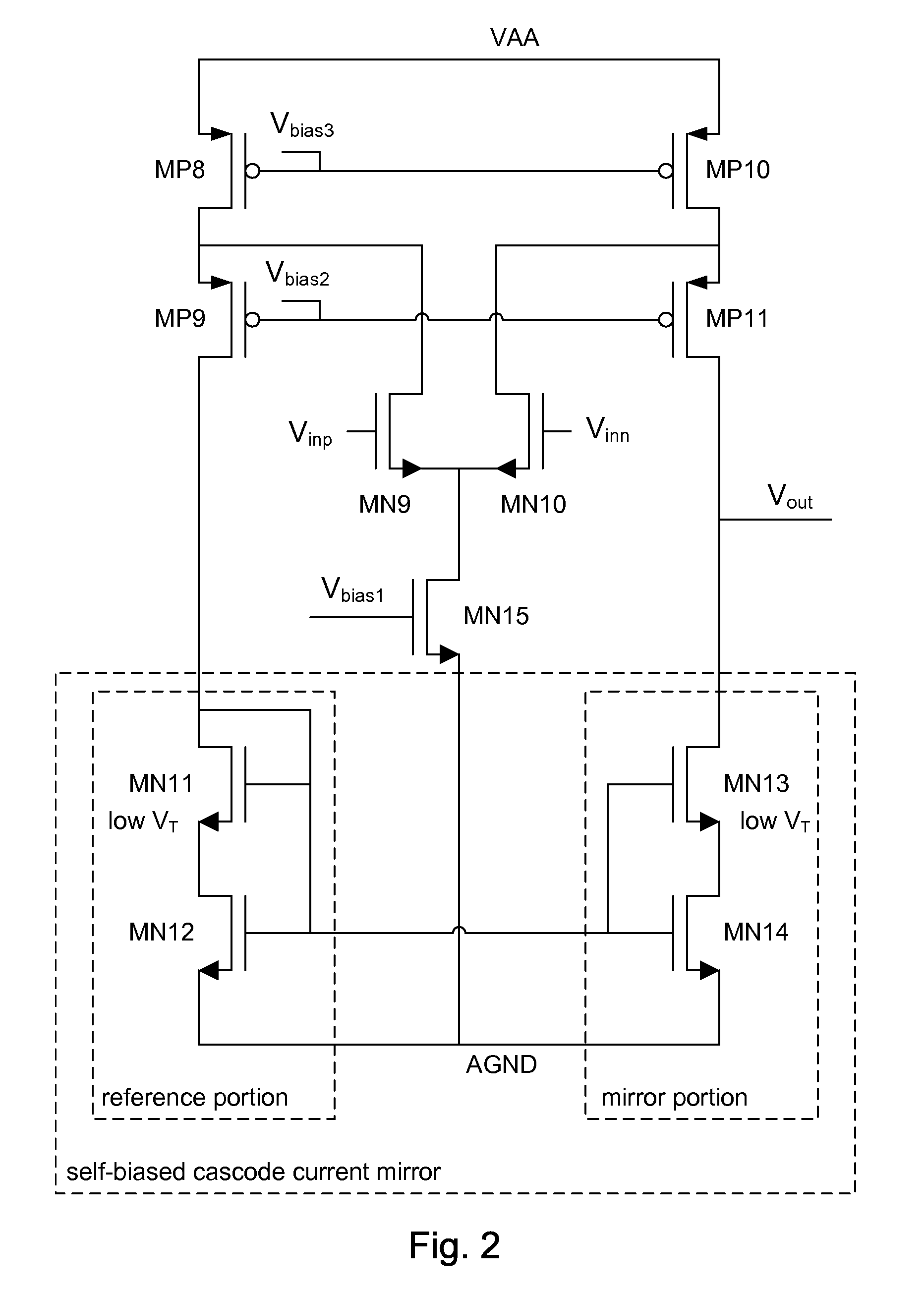

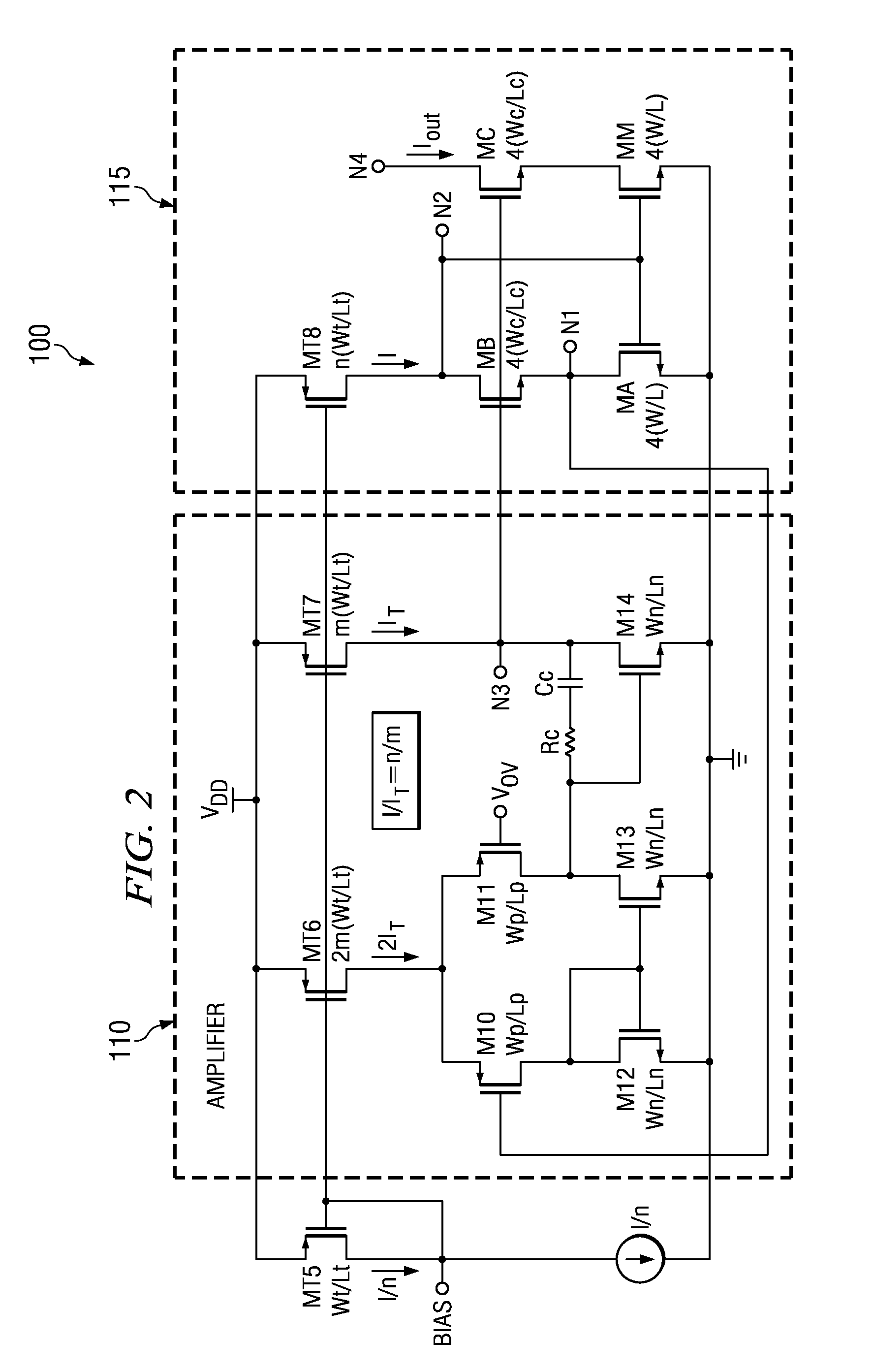

Operational transconductance amplifier (OTA)

ActiveUS20080272845A1Differential amplifiersElectric variable regulationAudio power amplifierCascode current mirror

Apparatus and methods provide an operational transconductance amplifier (OTA) with one or more self-biased cascode current mirrors. Applicable topologies include a current-mirror OTA and a folded-cascode OTA. In one embodiment, the self-biasing cascode current mirror is an optional aspect of the folded-cascode OTA. The self-biasing can advantageous reduce the number of biasing circuits used, which can save chip area and cost. One embodiment includes an input differential pair of a current-mirror OTA.

Owner:MICRON TECH INC

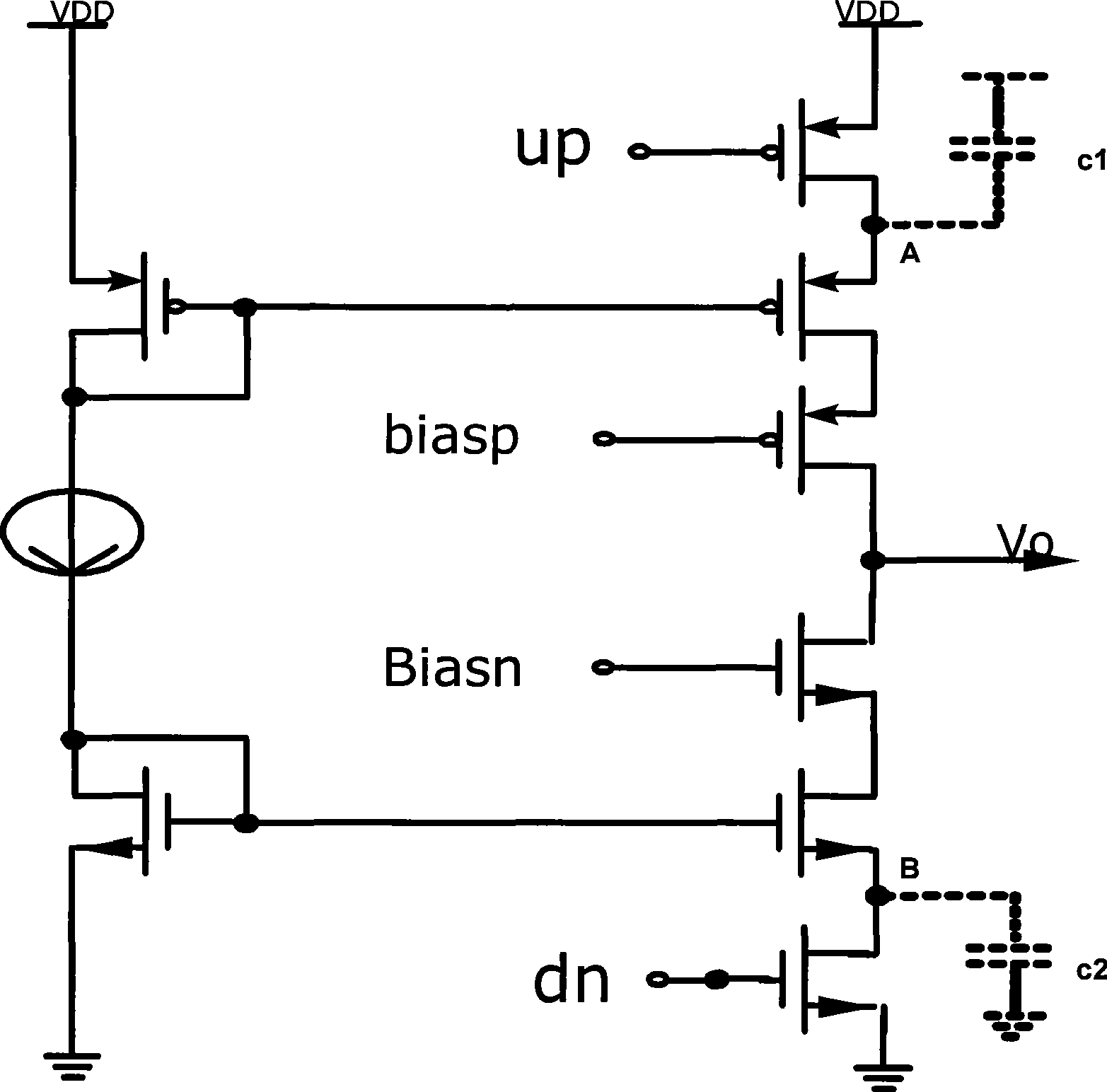

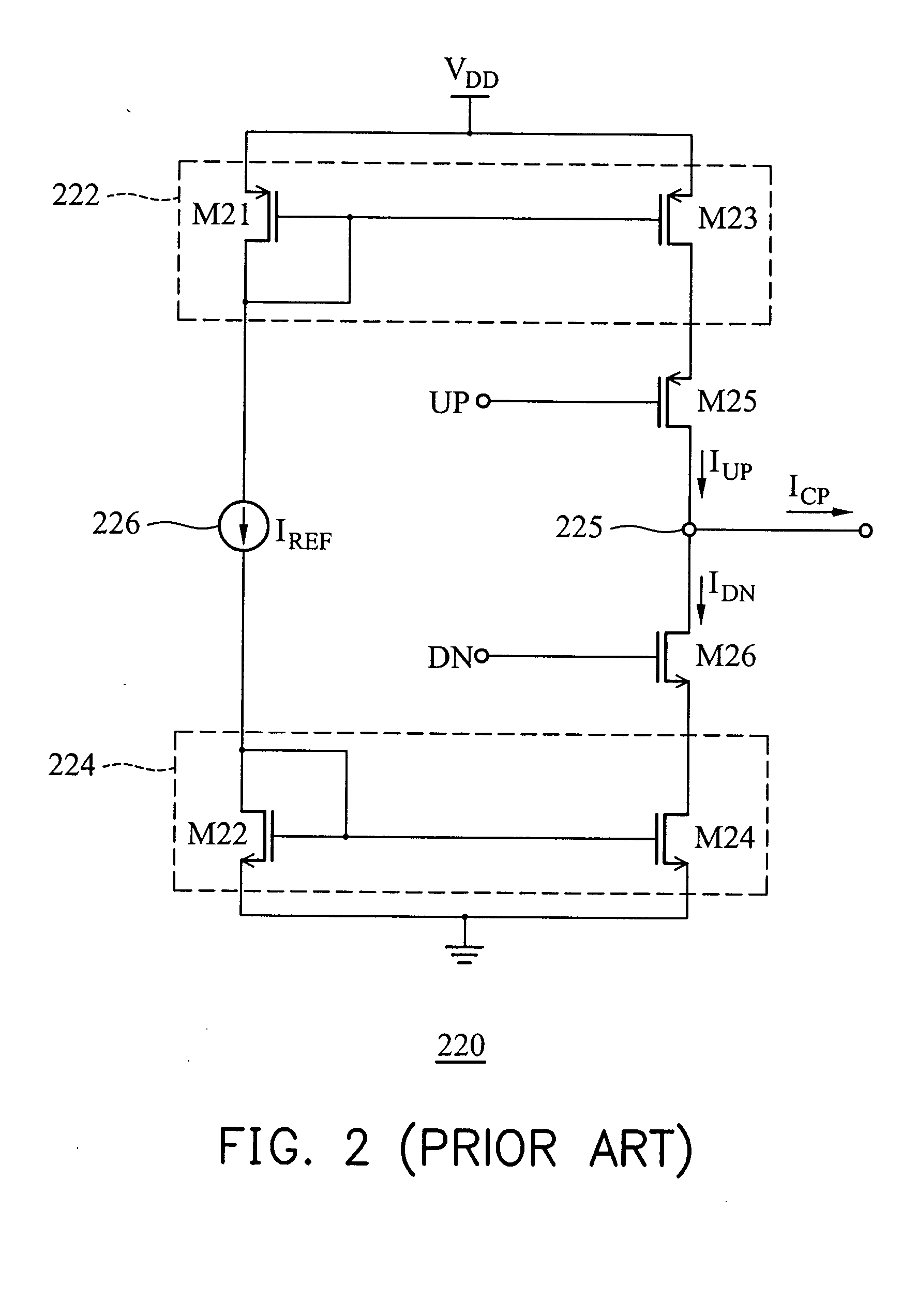

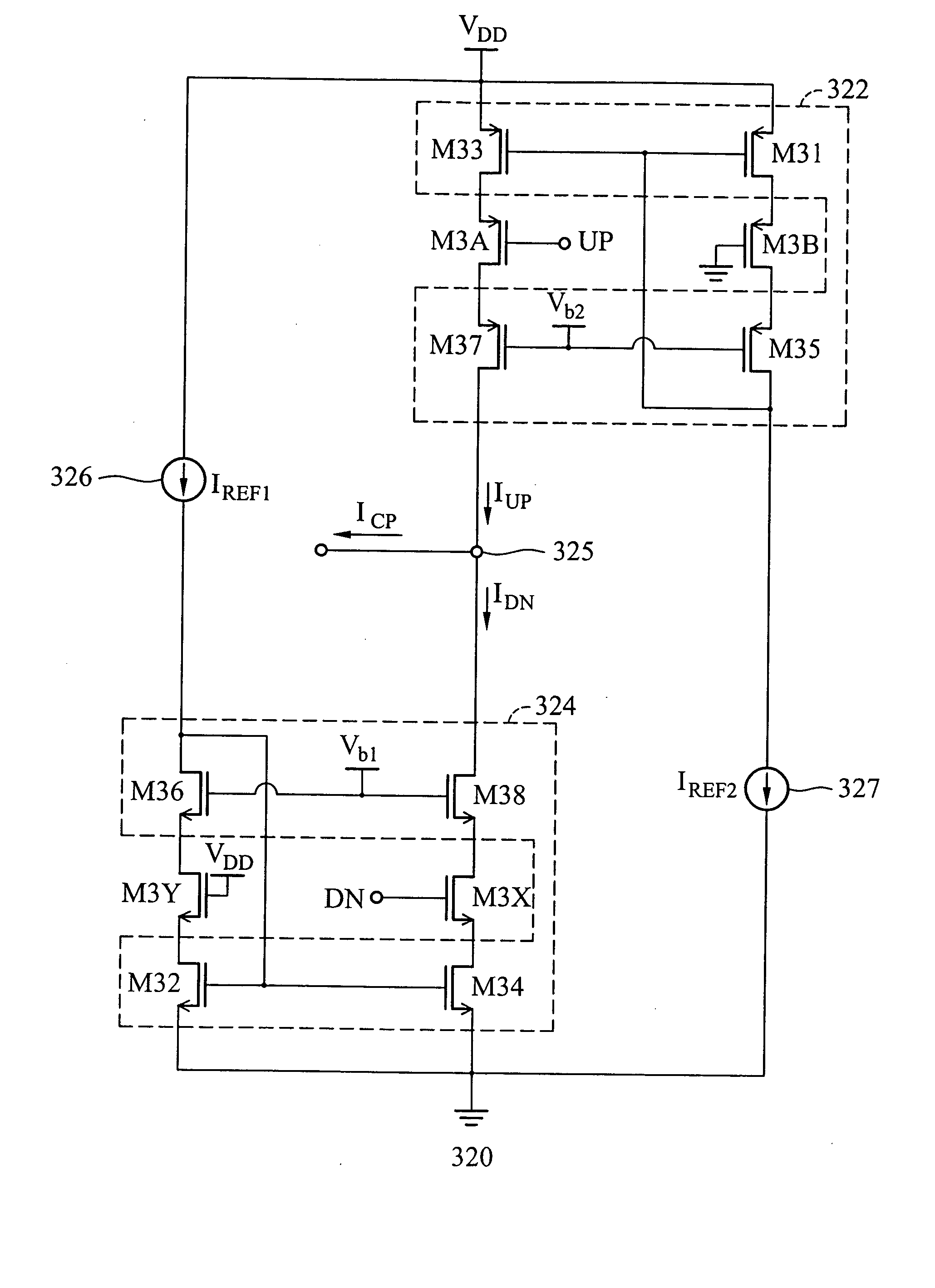

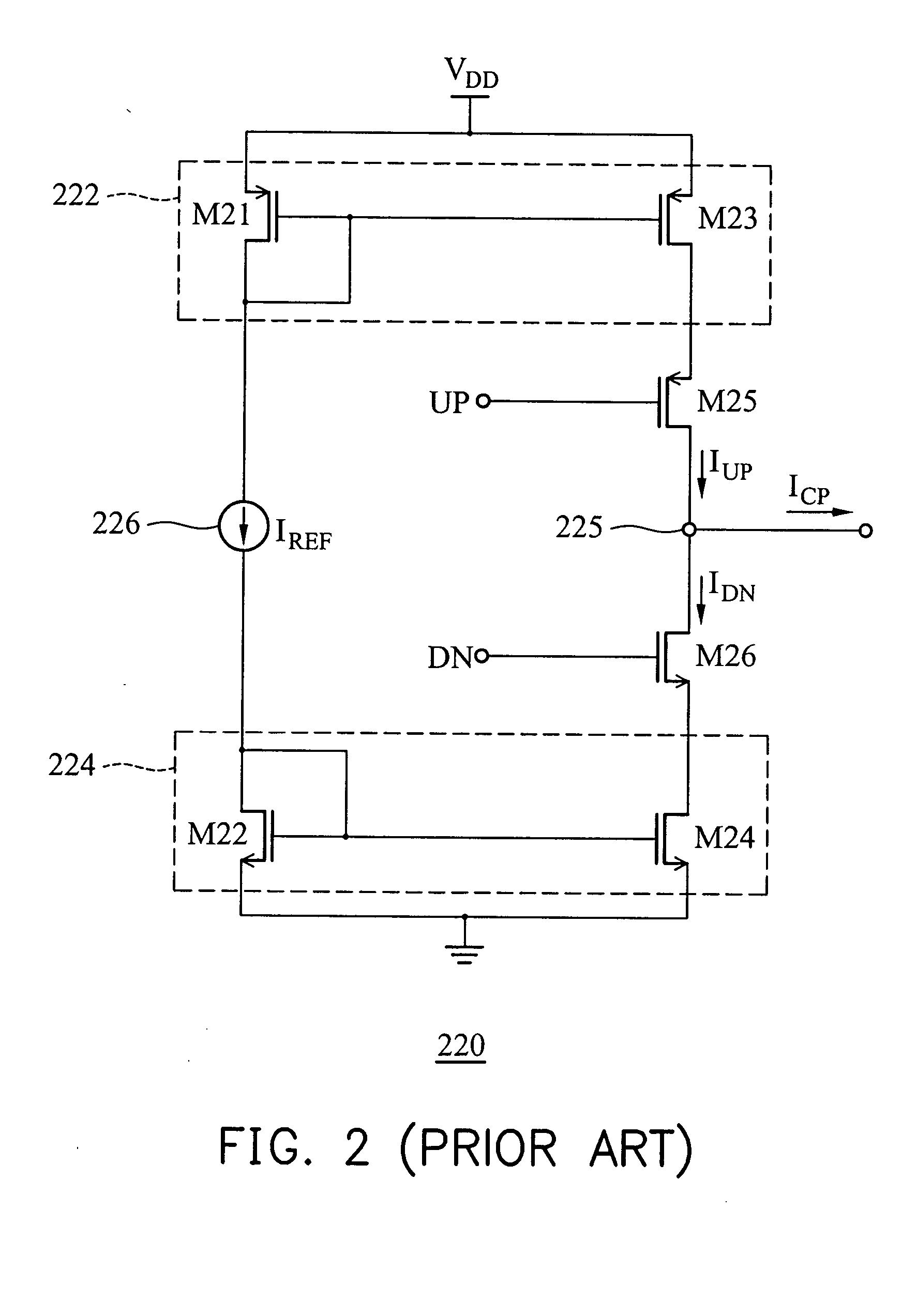

A charge pump circuit

InactiveCN101488710AIncrease resistanceInsulate the influencePulse automatic controlApparatus without intermediate ac conversionCascode current mirrorEngineering

The invention discloses a charge pump circuit which comprises an input high swing amplitude cascode current mirror, an output high swing amplitude cascode current mirror and a suppression charge shared circuit, wherein, a pull-up and a pull-down circuits are formed by a pull-up output cascode current mirror and a pull-down output cascode current mirror in the output high swing amplitude cascode current mirror as well as the suppression charge shared circuit, a pull-up switch pipe and a pull-down switch pipe. The cascode current mirror structure is adopted by output, so that the resistance of the output current mirror is increased, the influence of the change of the output voltage on the electric current is reduced, and the noise of a switching tube is avoided affecting the output voltage. Meanwhile, the sharing effect and the coupling effect of the charge can be inhibited.

Owner:CHENGDU CORPRO TECH CO LTD

High-speed low-noise charge pump

InactiveUS7005896B2Fast switching speedReduce noisePulse automatic controlElectric pulse generatorLow noiseControl signal

Owner:VIA TECH INC

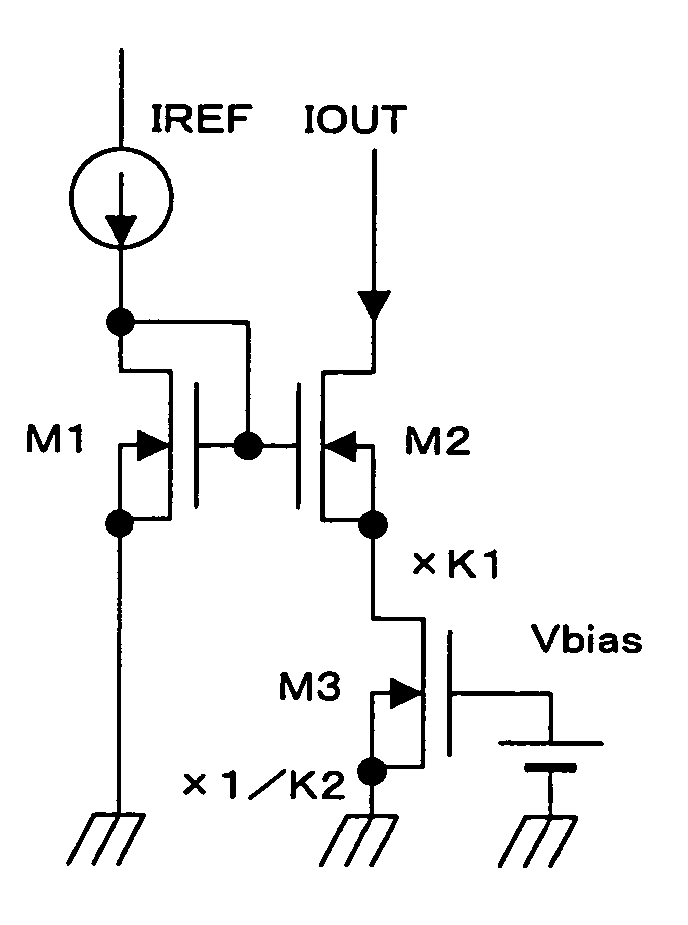

Bias circuit for high-swing cascode current mirrors

InactiveUS20060226893A1Electric variable regulationAmplifiers with semiconductor devices onlyReference currentCascode current mirror

A bias circuit for providing at least first and second bias signals for biasing a cascode current source and / or a cascode current sink includes a resistive element and first, second and third transistors, each transistor having first and second source / drain terminals and a gate terminal. The first source / drain terminal of the first transistor is coupled to the gate terminal, the first bias signal being generated at the first source / drain terminal in response to receiving a first reference current at the first source / drain terminal. A first end of the first resistive element is coupled to the second source / drain terminal of the first transistor. The gate terminal of the second transistor is coupled to the gate terminal of the first transistor, the second bias signal being generated at the first source / drain terminal of the second transistor in response to receiving a second reference current at the first source / drain terminal of the second transistor. The first source / drain terminal of the third transistor is coupled to the second source / drain terminal of the second transistor, the second source / drain terminal of the third transistor is coupled to a second end of the first resistive element, and the gate terminal of the third transistor is coupled to the first source / drain terminal of the second transistor.

Owner:AVAGO TECH INT SALES PTE LTD

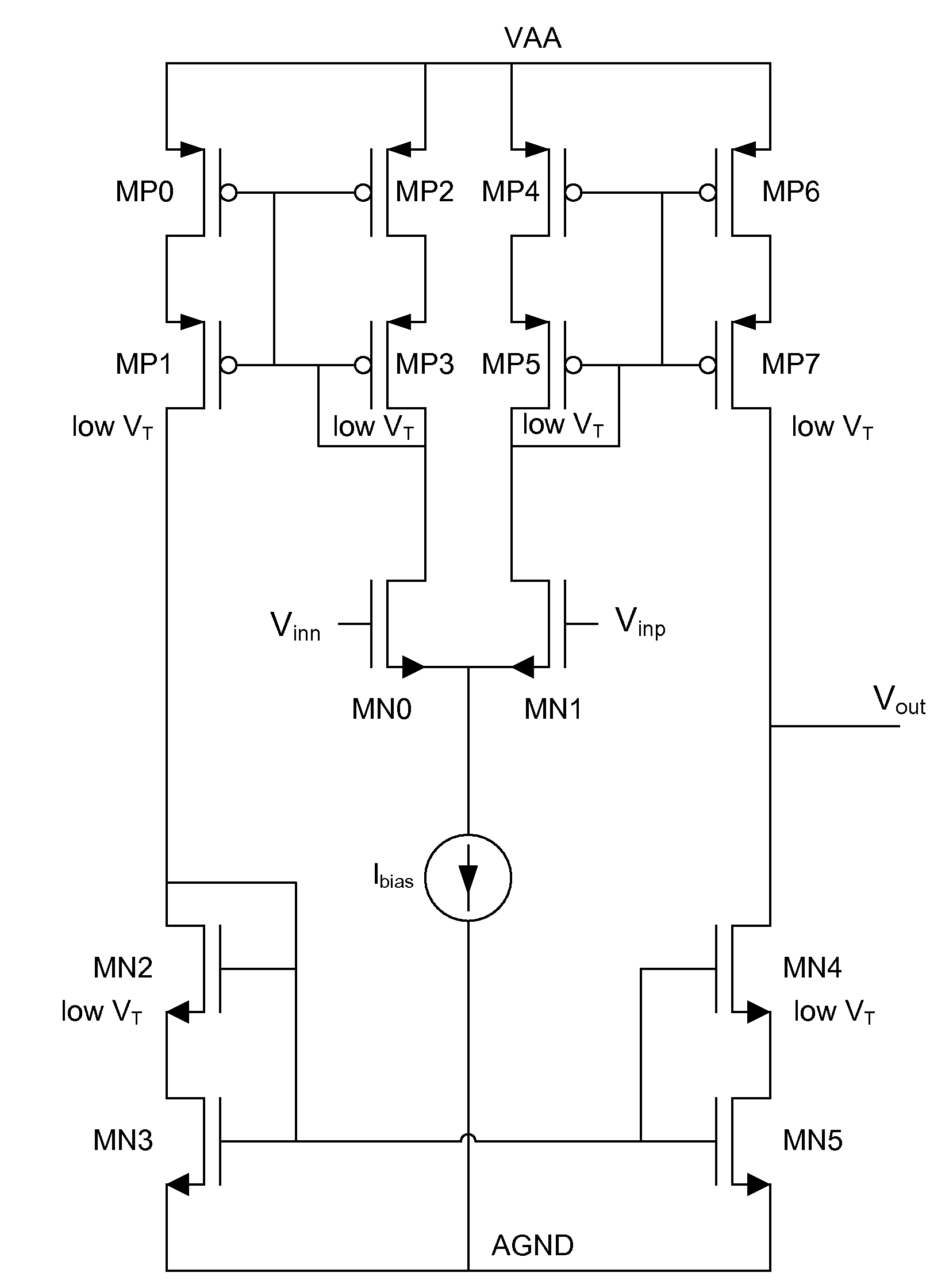

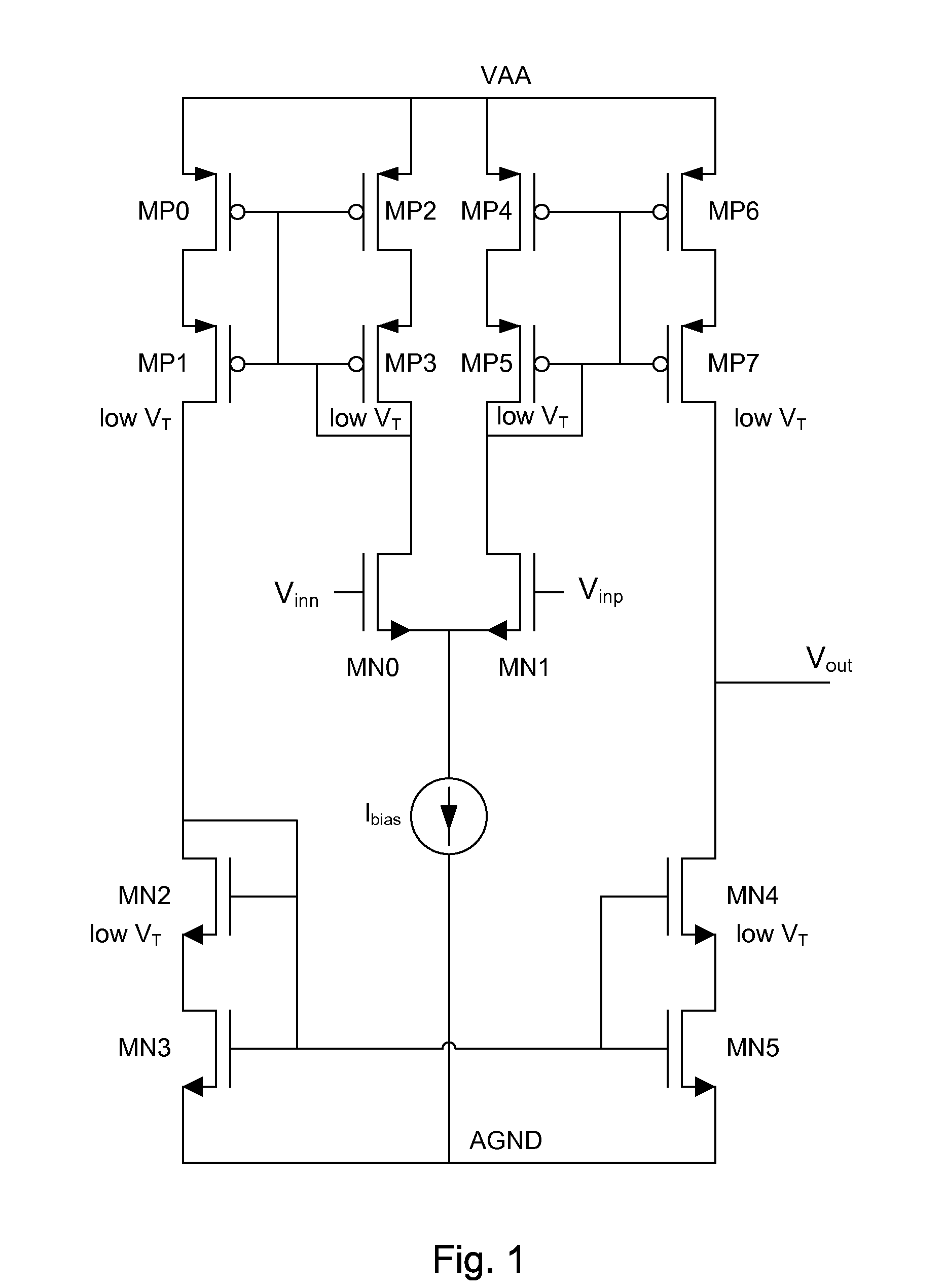

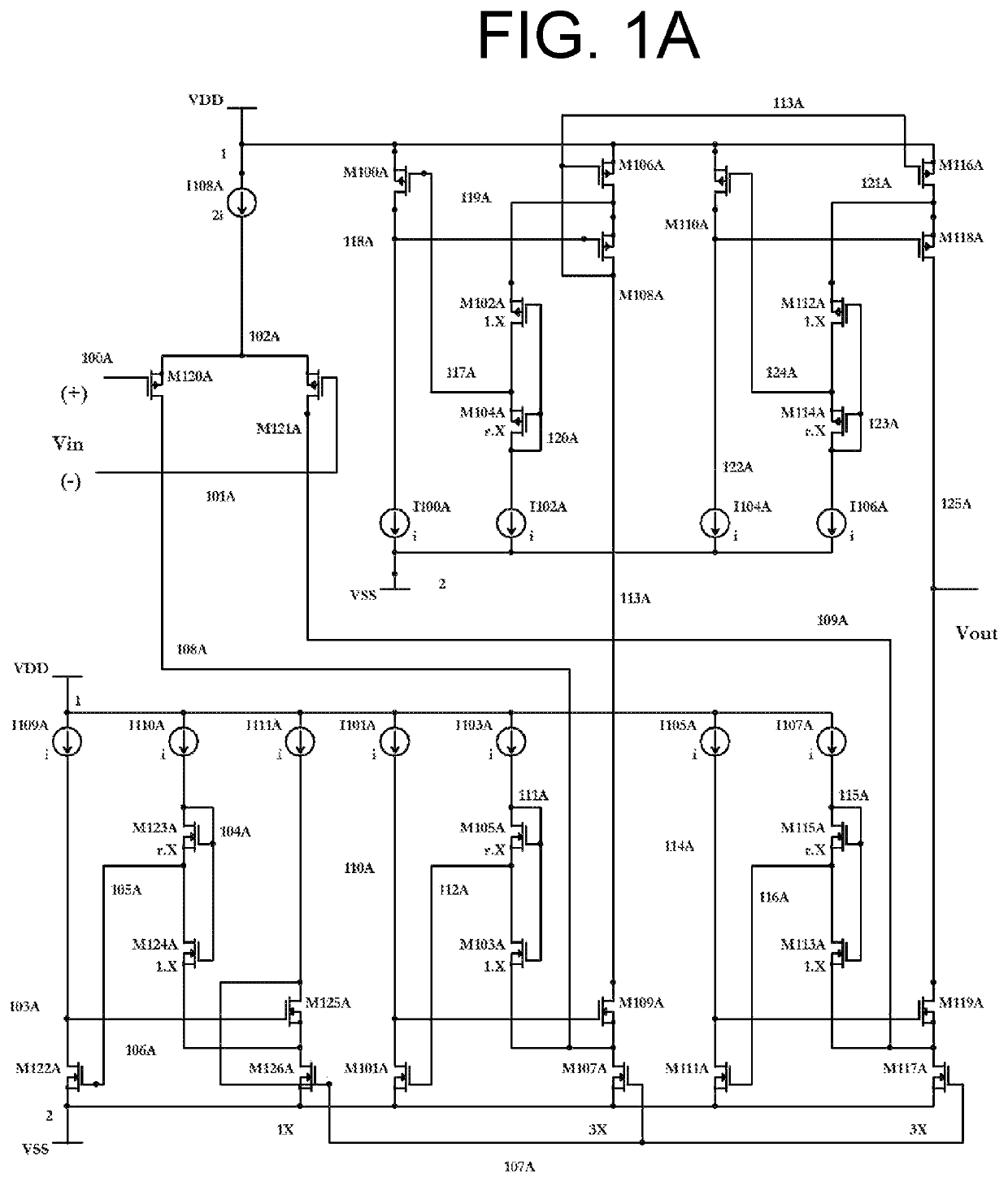

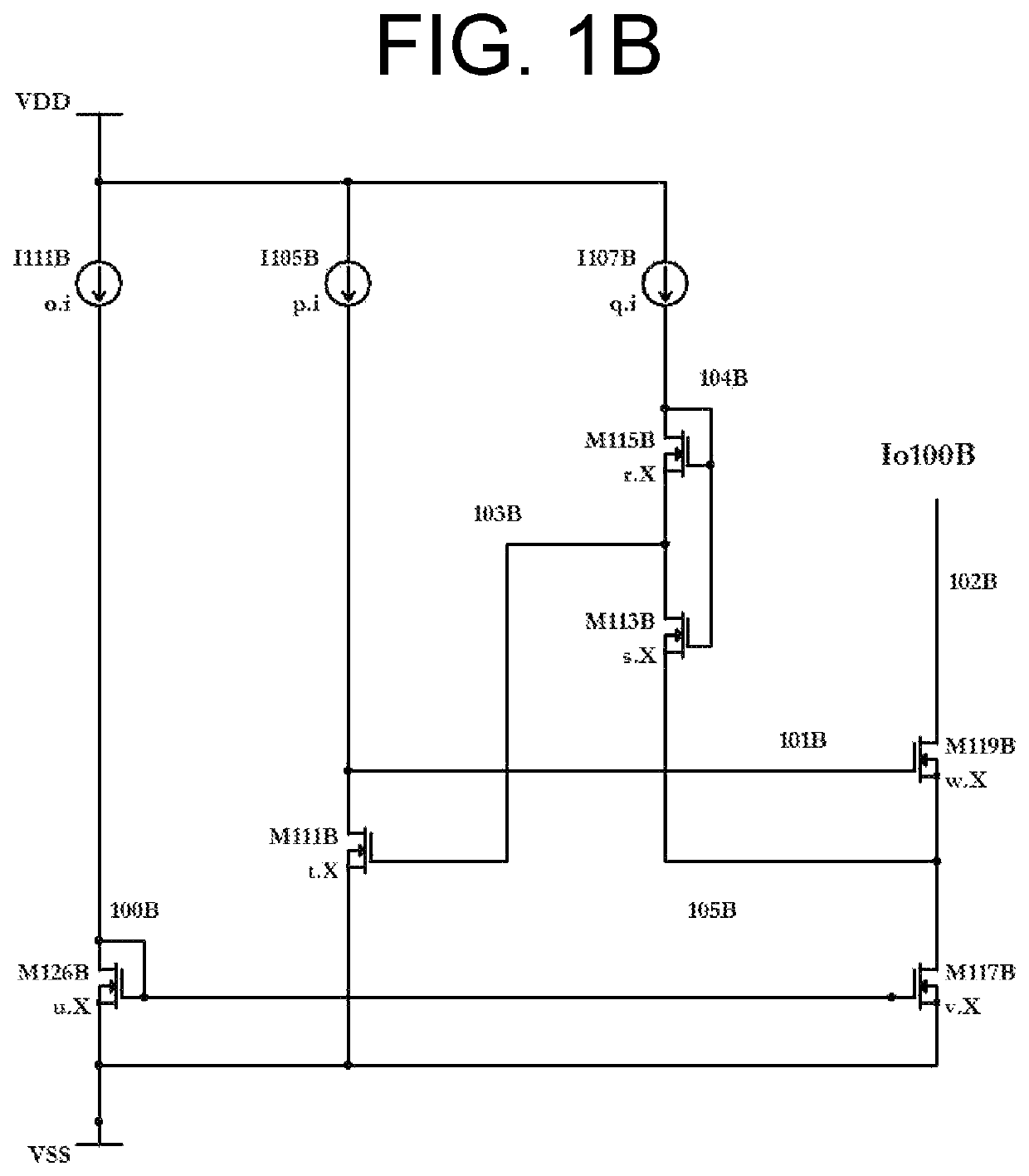

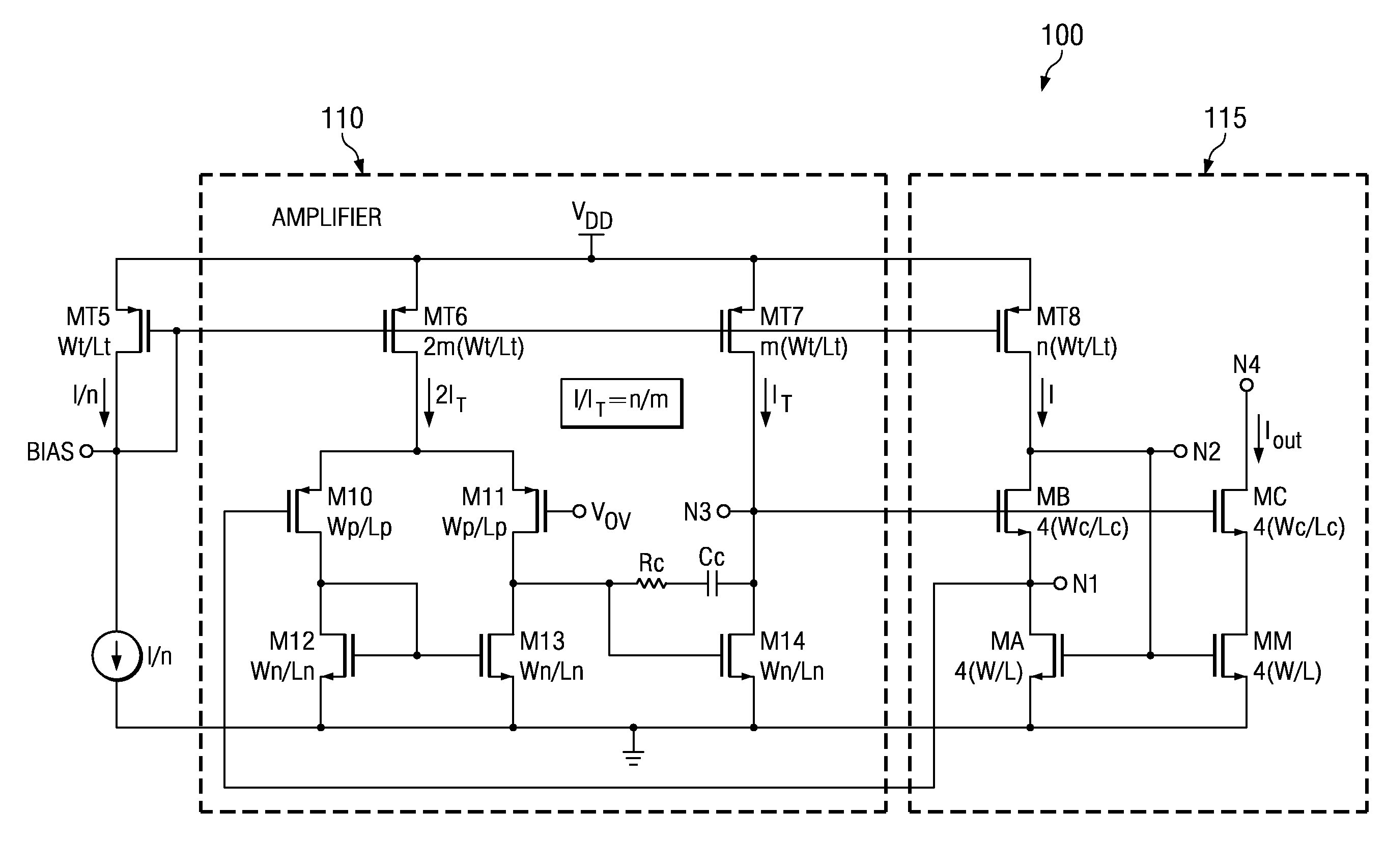

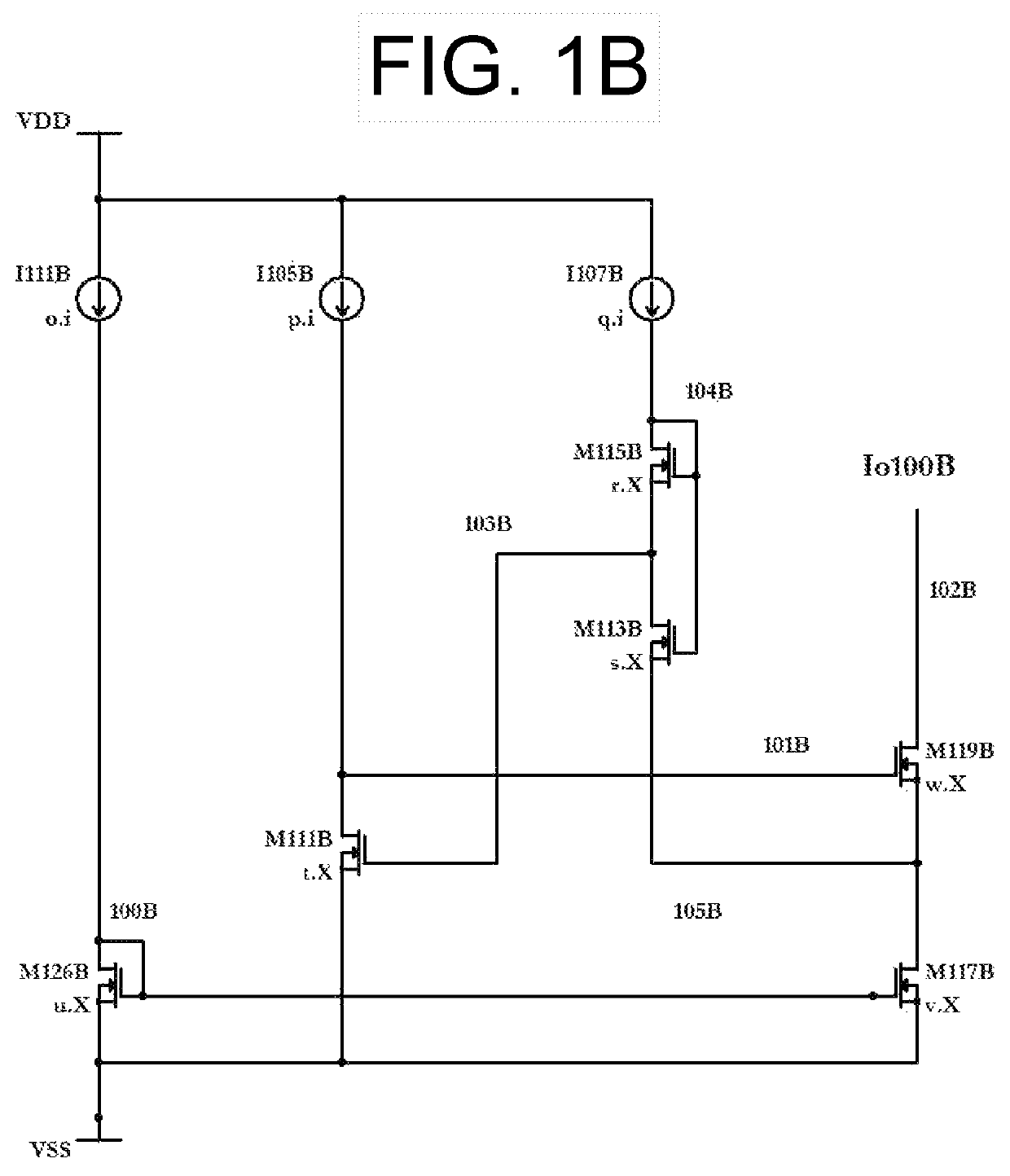

Low voltage rail to rail high speed analog buffer and method thereof

ActiveUS10536117B1Wide input-output voltage spanReduce voltagePush-pull amplifiersPhase-splittersLow noiseLow voltage

Methods, circuits, and apparatuses that provide Buffer Amplifier, containing Amplifiers and Buffer Drivers, one or more of the following: ultra low power Buffer Amplifier, capable of having high gain, low noise, high speed, near rail-to-rail input-output voltage span, high sink-source current drive capability for an external load, and able to operate at low power supply voltages. Methods, circuits, and apparatuses that provide regulated cascode (RGC) current mirrors (CM) capable of operating at low power supply and having wide input-output voltage spans.

Owner:FAR ALI TASDIGHI

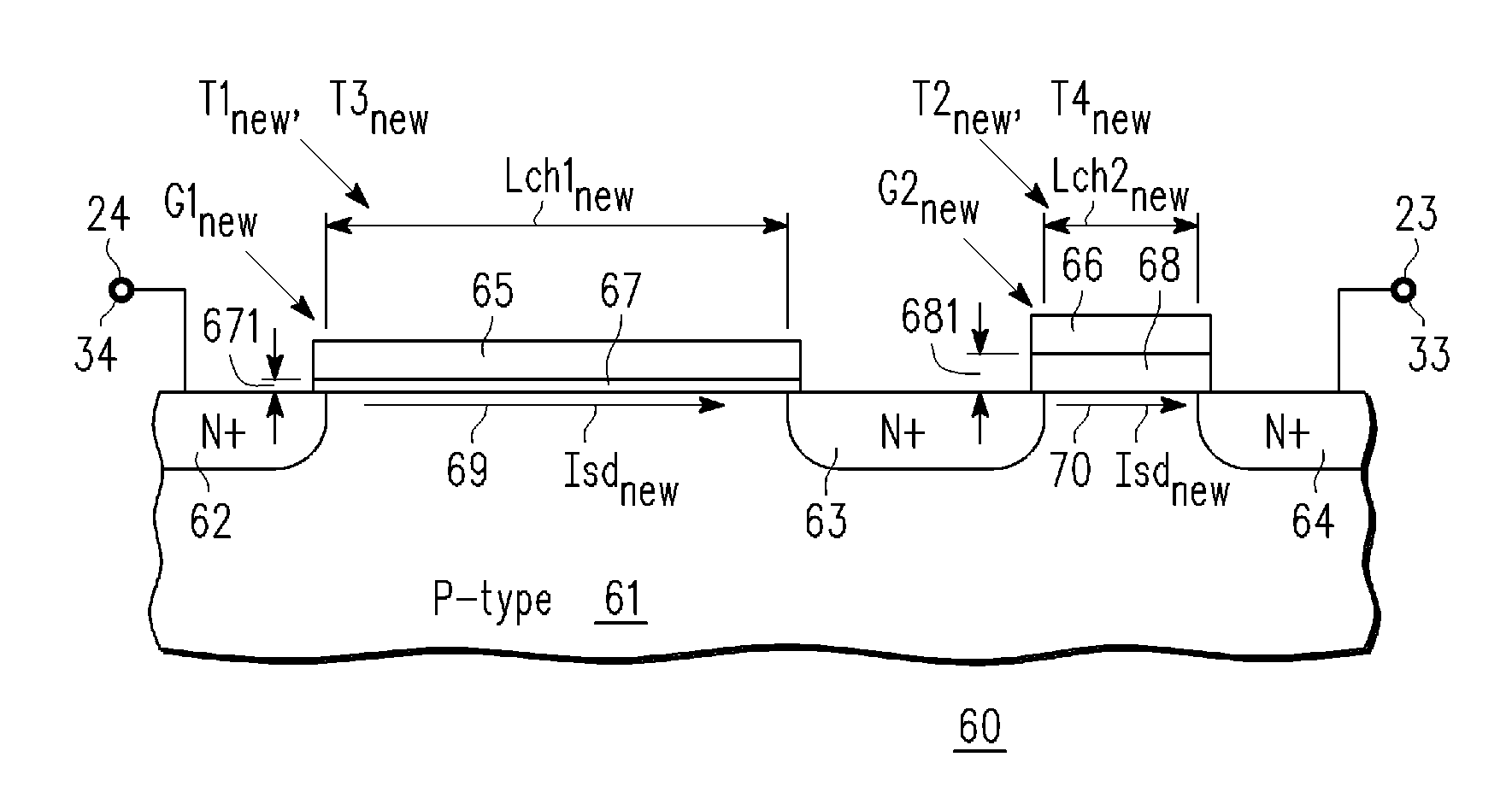

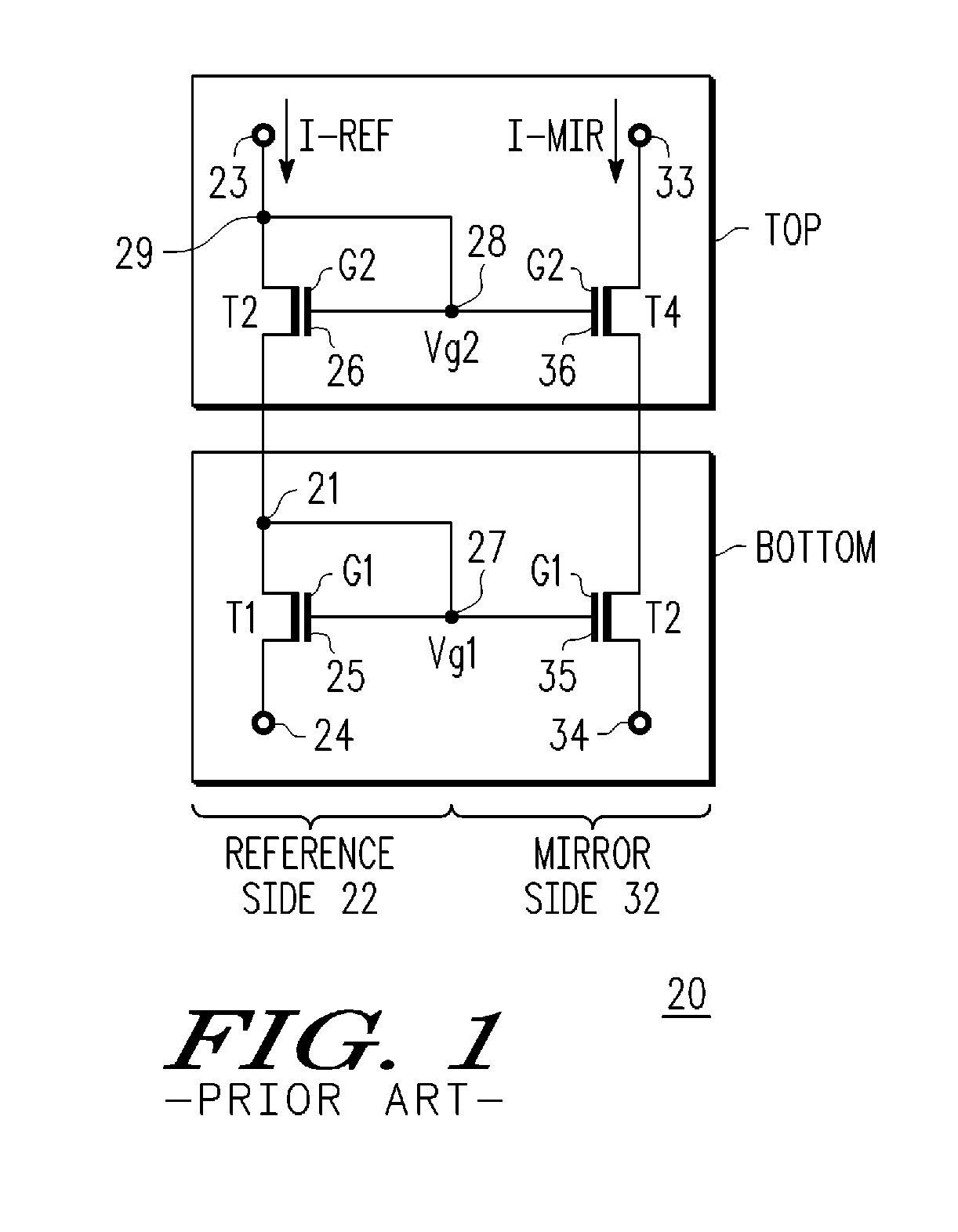

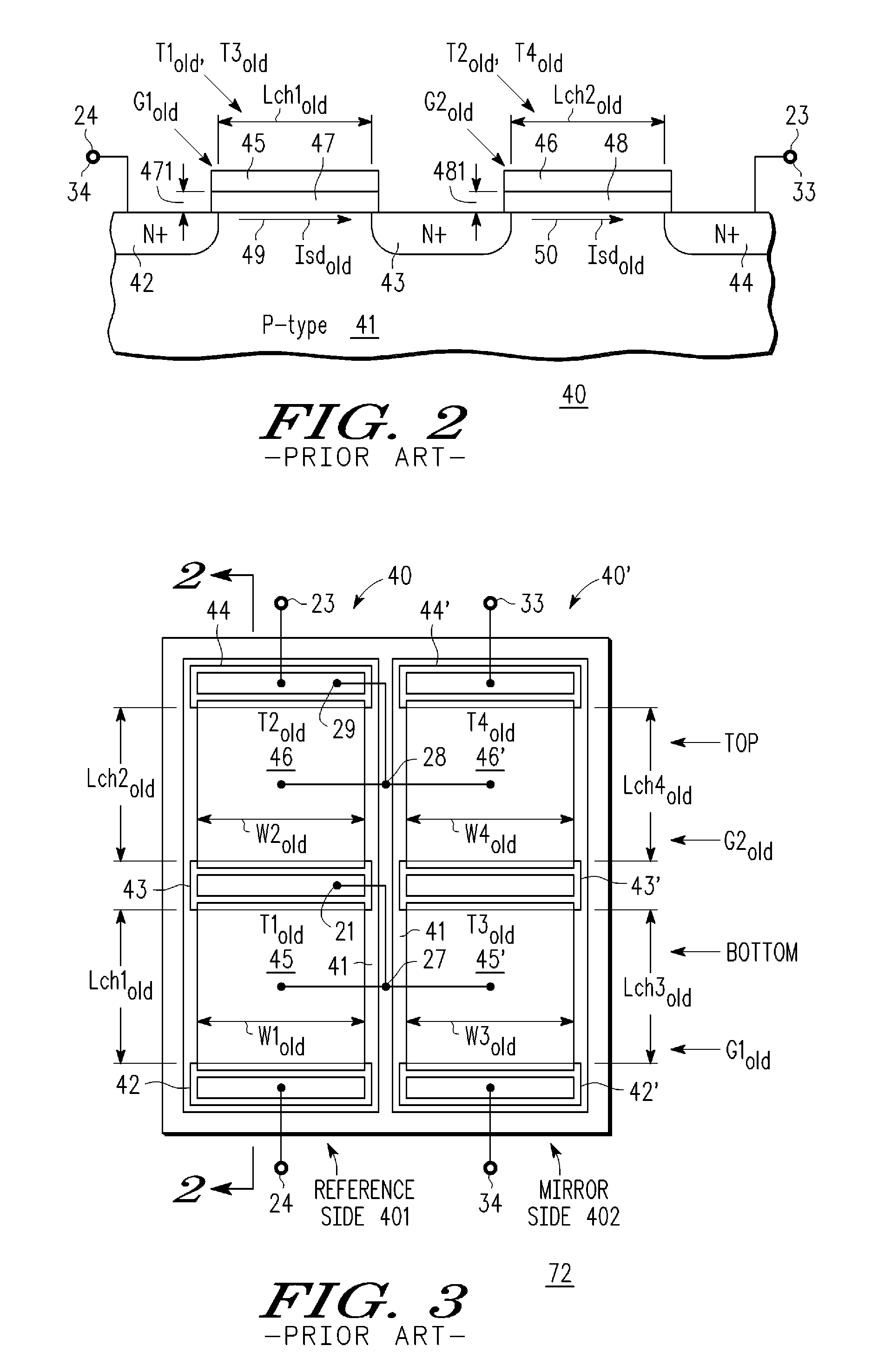

Cascode current mirror and method

ActiveUS20080224221A1TransistorSemiconductor/solid-state device manufacturingGate dielectricReference current

A cascode amplifier (CA) (60) is described having a bottom transistor (T1new) with a relatively thin gate dielectric (67) and higher ratio (RB) of channel length (Lch1new) to width (W1new) and a series coupled top transistor (T2new) with a relatively thick gate dielectric (68) and a lower ratio (RT) of channel length (Lch2new) to width (W2new). An improved cascode current mirror (CCM) (74) is formed using a coupled pair of CAs (60, 60′), one (60) forming the reference current (RC) side (601) and the other (60′) forming the mirror current side (602) of the CCM (74). The gates (65, 65′) of the bottom transistors (T1new, T3new) are tied together and to the common node (21) between the series coupled bottom (T1new) and top (T2new) transistors of the RC side (601), and the gates (66′, 66′) of the top transistors (T2new, T4new) are coupled together and to the top drain node (64) of the RC side (601). The area of the CCM (74) can be substantially shrunk without adverse affect on the matching, noise performance and maximum allowable operating voltage.

Owner:NXP USA INC

Cascode current mirror circuit, bandgap circuit, reference voltage circuit having the cascode current mirror circuit and the bandgap circuit, and voltage stabilizing/regulating circuit having the reference voltage circuit

InactiveUS20090267585A1Reduce the effect of temperatureMitigate ripple voltage perturbationAmplififers with field-effect devicesAmplifier detailsReference currentCascode current mirror

A cascode current mirror circuit and a bandgap circuit are provided. The circuits are used together and function as a reference voltage circuit. The reference voltage circuit outputs a reference current resistant to temperature variation and ripple-voltage. Accordingly, a voltage stabilizing / regulating circuit corrects error voltage precisely and promptly, and the resultant voltage is temperature insensitive and ripple-voltage-independent.

Owner:NAT TAIWAN UNIV

CMOS current mirror circuit and reference current/voltage circuit

InactiveUS7429854B2Small temperature characteristicStable voltageElectric variable regulationCMOSReference current

Disclosed is a CMOS current mirror circuit including a first MOS transistor and a second MOS transistor constituting a current mirror, in which a drain of the first MOS transistor and a gate of the second MOS transistor are connected in common, a source of the first MOS transistor is directly grounded, and a gate of the first MOS transistor is connected to the drain of the first MOS transistor through a third MOS transistor which has a source connected to the drain of the first MOS transistor, a drain connected to the gate of the first MOS transistor, and a gate being biased. The source of the second MOS transistor is directly grounded. Current is input to the drain of the third MOS transistor. The drain current of the second MOS transistor is mirrored by cascode current mirror circuits. An output current is output from the source of a MOS transistor for conversion to a voltage by a circuit that receives the current which outputs a reference voltage.

Owner:RENESAS ELECTRONICS CORP

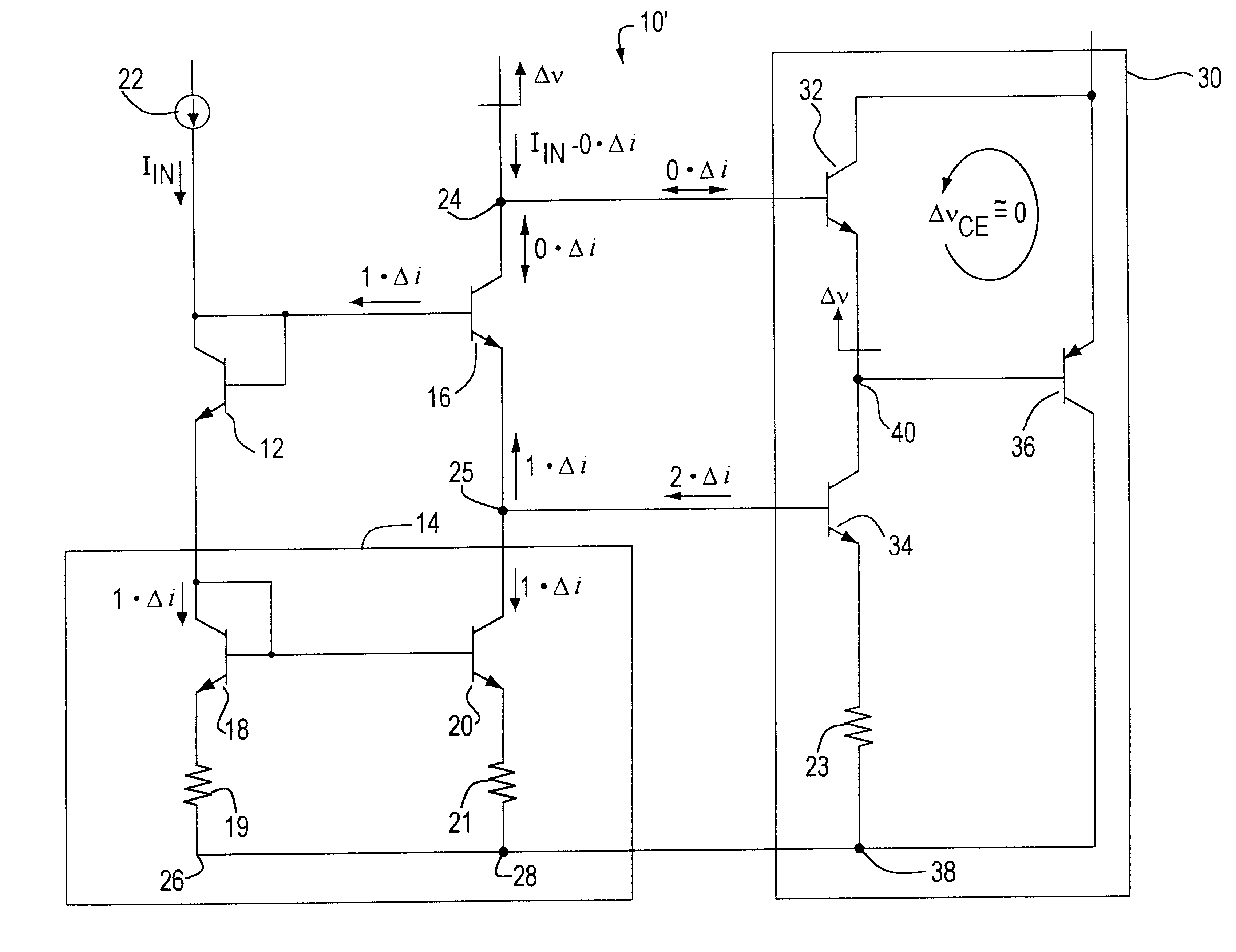

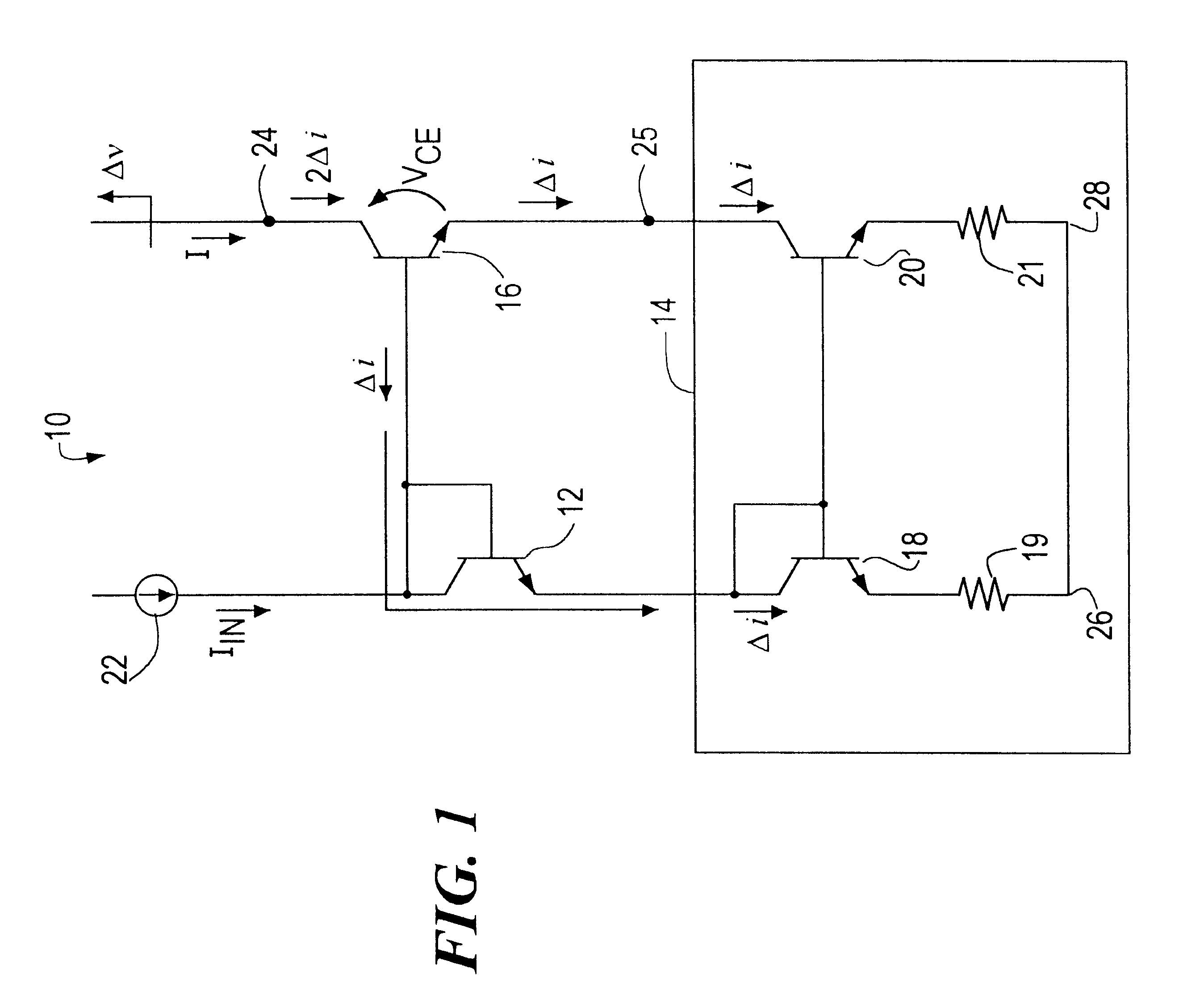

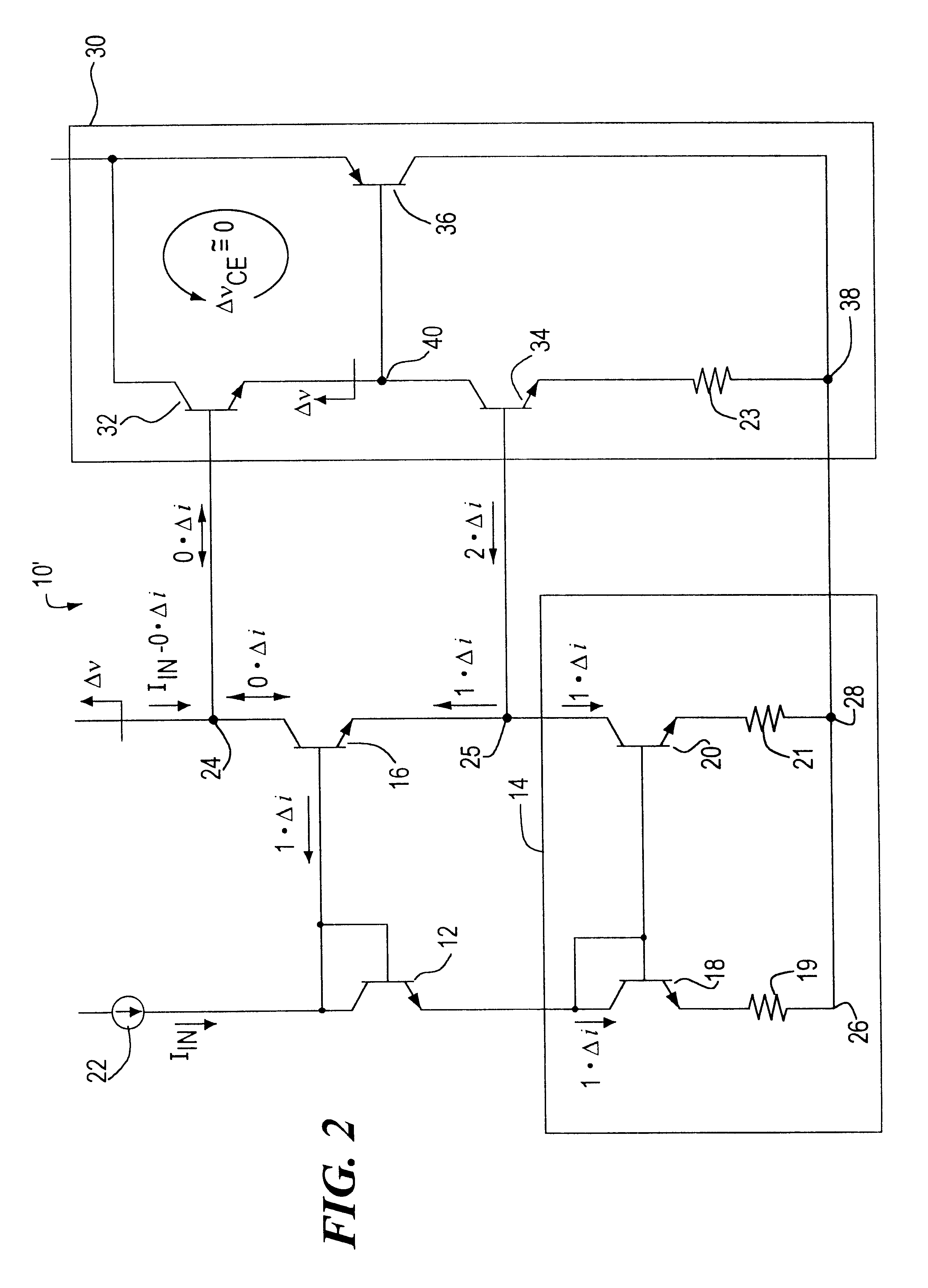

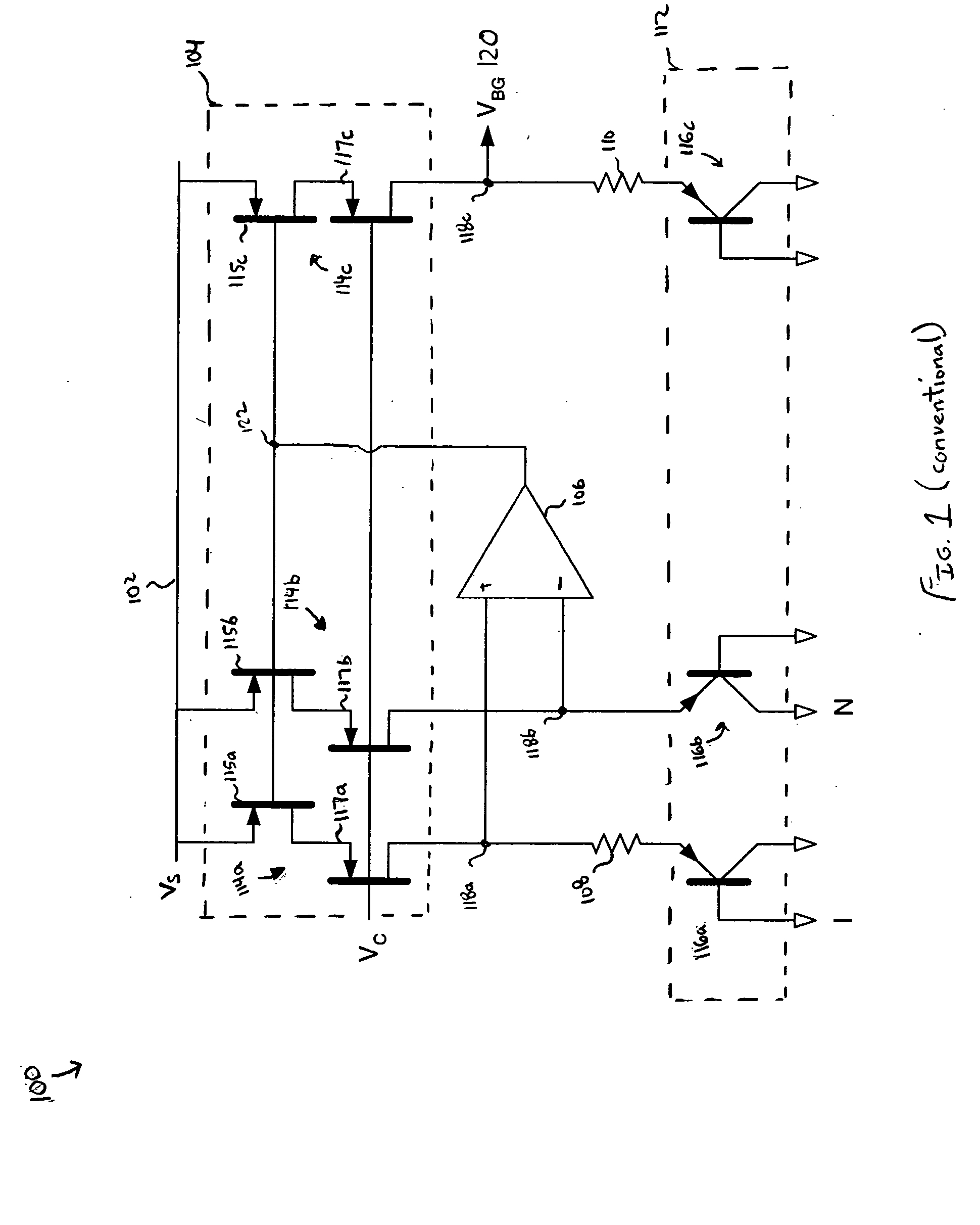

Early voltage and beta compensation circuit for a current mirror

InactiveUS6194886B1Easy to implementAvoid mistakesElectric variable regulationCascode current mirrorVoltage variation

An Early voltage and beta current compensated cascode current mirror includes a cascode current mirror having an input stage responsive to an input current, a current mirror circuit having a first stage responsive to the input stage and a second stage responsive to the first stage, and an output stage responsive to the second stage for providing an output voltage and current; and a compensation circuit, responsive to the cascode current mirror, having a first compensation stage, a second compensation stage and a bootstrapping buffer, the first compensation stage, in response to a change in the output voltage, impressing a corresponding change in voltage on the second compensation stage, the second compensation stage thereby providing a change in current to the cascode current mirror for cancelling current errors induced by base current modulation in the output stage, the bootstrapping buffer, in response to the change in voltage, impressing a corresponding change in voltage on the first compensation stage to prevent errors from base current modulation effects in the first compensation stage, the first and second compensation stages further providing a base current to the cascode current mirror for cancelling base current errors in the output current induced by the cascode current mirror.

Owner:ANALOG DEVICES INC

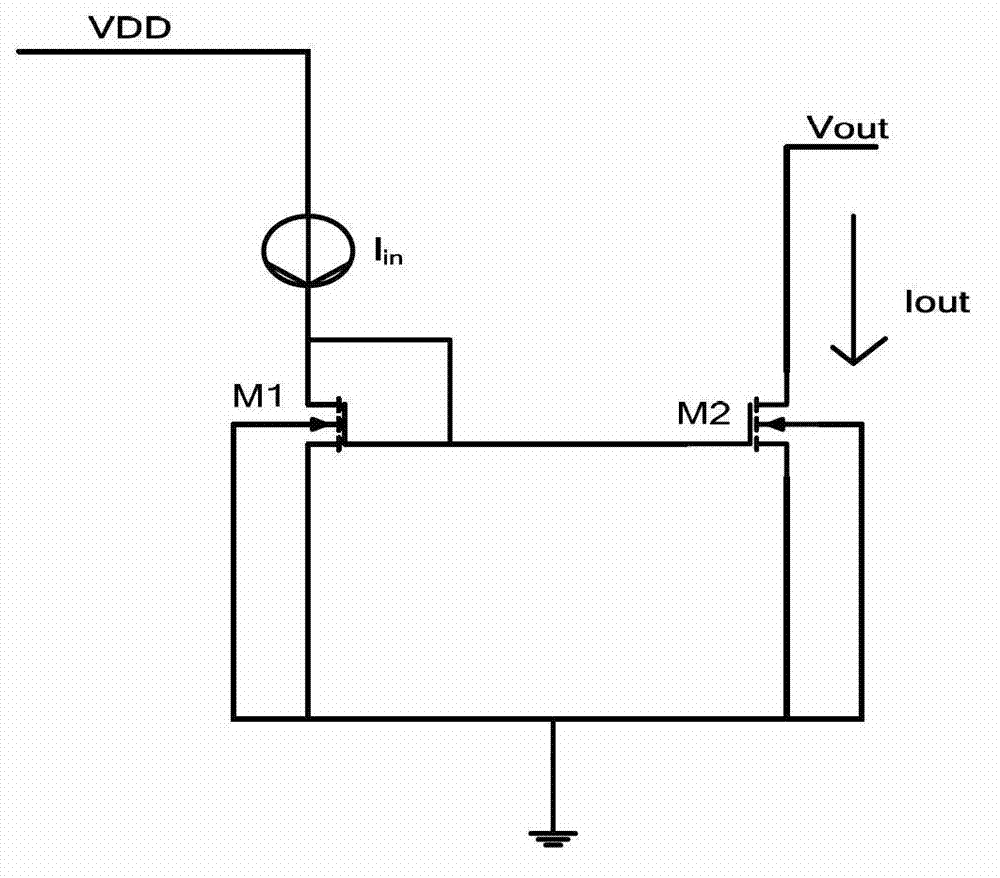

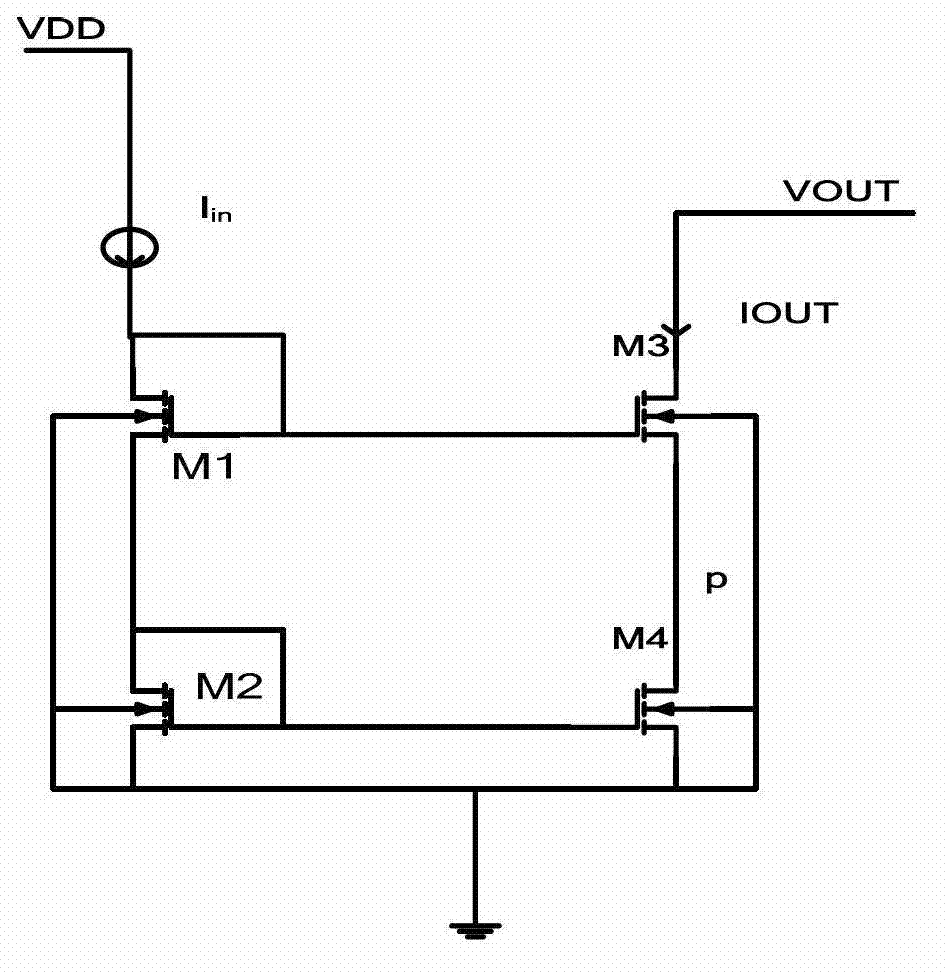

Low voltage current mirror

InactiveCN102809982AImprove mirroring accuracyLarge output resistanceElectric variable regulationLow voltageCascode current mirror

The invention discloses a low voltage current mirror, and aims to solve the problem that output voltage swing is reduced because threshold voltage is wasted by the voltage redundancy of the conventional cascode current mirror. The low voltage current mirror comprises an input current source, a first P-channel metal oxide semiconductor (PMOS) tube, a second PMOS tube, a third PMOS tube, a first N-channel metal oxide semiconductor (NMOS) tube, a second NMOS tube, a third NMOS tube, a fourth NMOS tube and a fifth NMOS tube. The low voltage current mirror has a cascode output structure, output resistance is very high, and the influence of a load on output current is relatively small, so that the mirror image precision of the current mirror is very high; and a channel length modulation effect is rationally used by the structure, so that compared with the cascode current mirror, the current mirror has the advantages that the redundancy of the threshold voltage is reduced, and the output voltage swing is increased.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

CMOS current mirror circuit and reference current/voltage circuit

InactiveUS20060091940A1Reducing temperature characteristic (dependency)Guaranteed uptimeElectric variable regulationCMOSReference current

Owner:RENESAS ELECTRONICS CORP

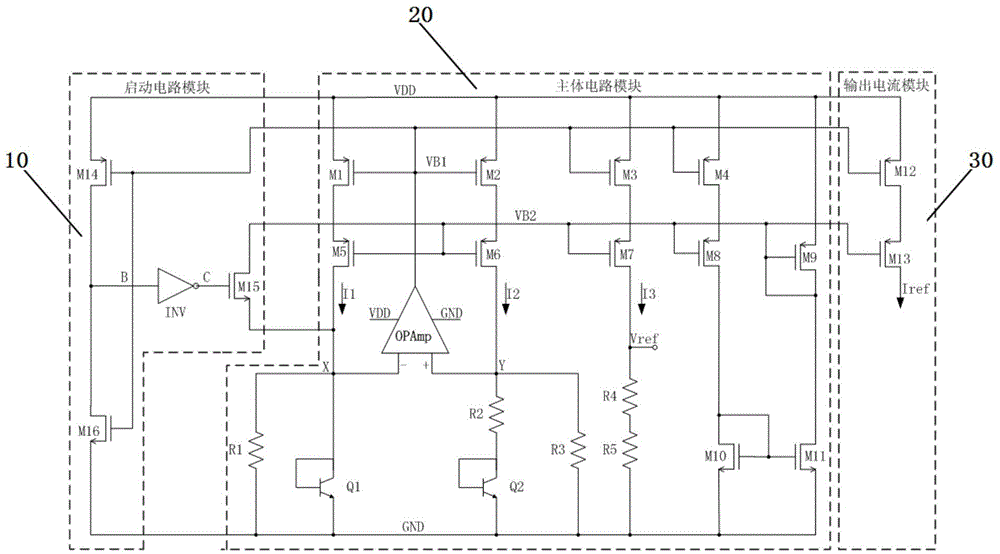

High-precision band-gap reference source

InactiveCN104793690AReduce complexityHigh precisionElectric variable regulationCircuit complexityAudio power amplifier

The invention relates to a high-precision band-gap reference source which comprises a body circuit module, an output current module and a starting circuit module. A band-gap reference source structure with the adjustable output reference voltage is adopted in the body circuit module, and the flexible reference voltage can be output. In addition, feedback precision is improved through an operational amplifier of a folded cascode structure, different temperature characteristics of different resistors are utilized, second-order compensation of the temperature characteristic of the reference voltage source is achieved in a resistor split mode, the circuit complexity is reduced, and the area is saved. In addition, a cascode current mirror is adopted in the output current module to improve the precision of the reference current, and the high-precision reference voltage and reference current are output at the same time.

Owner:XIDIAN UNIV

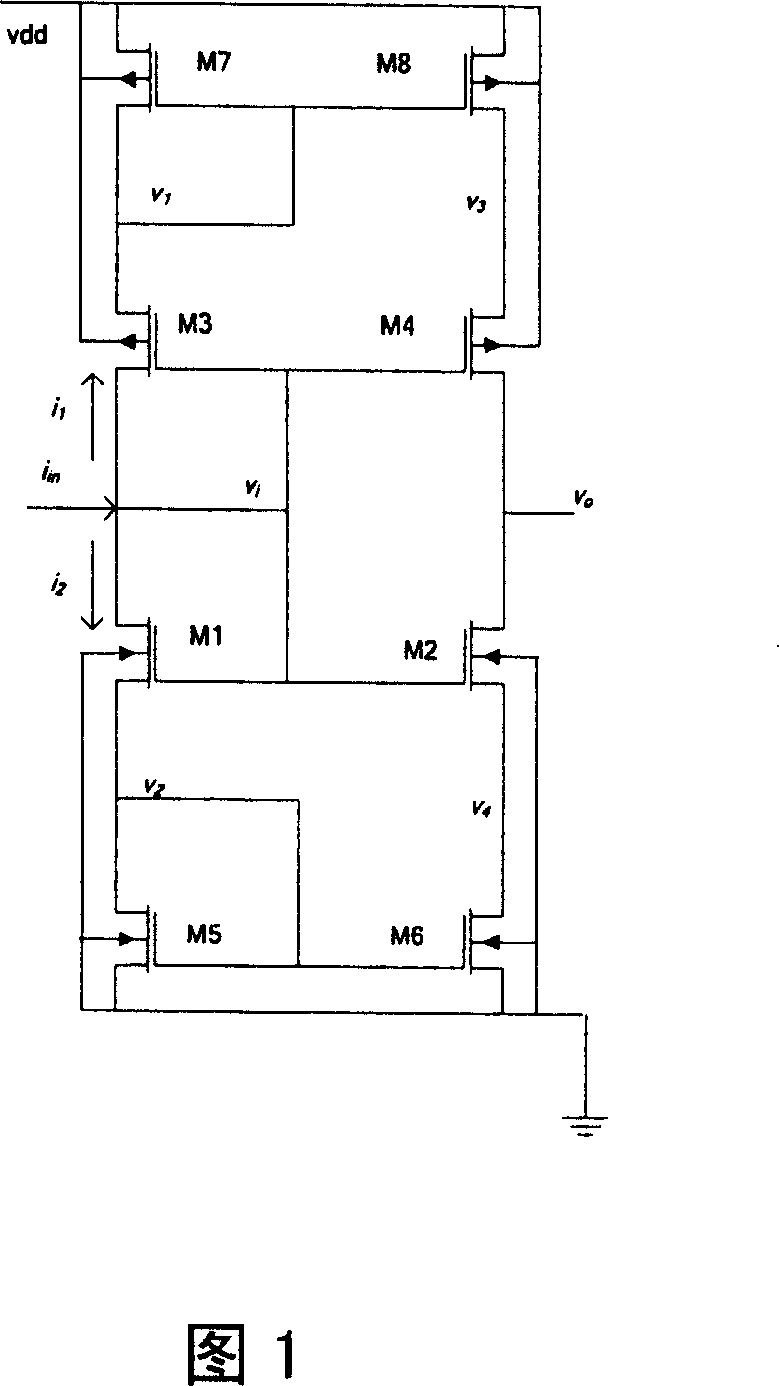

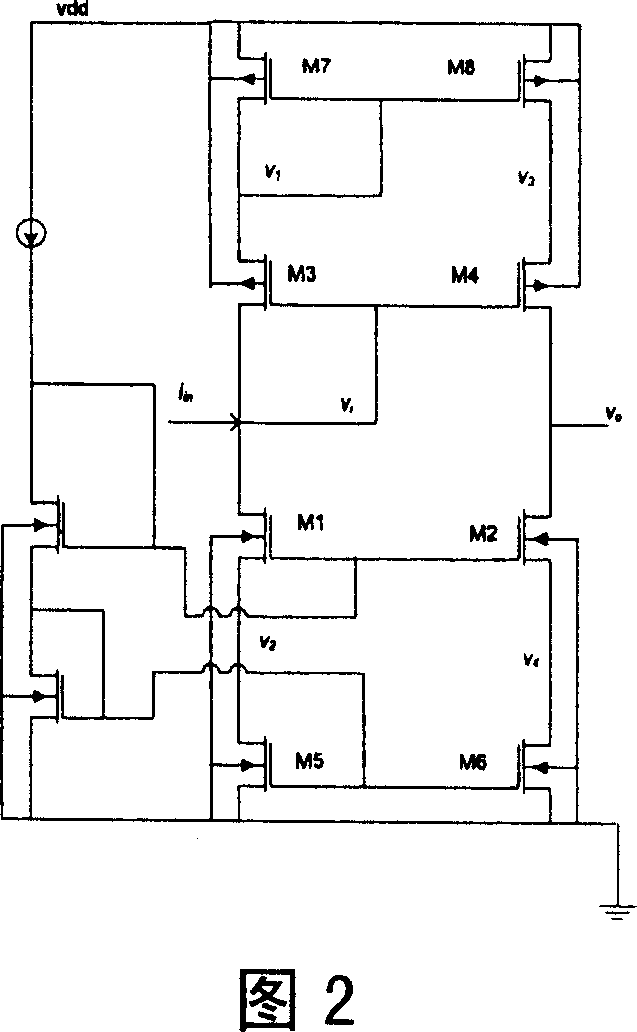

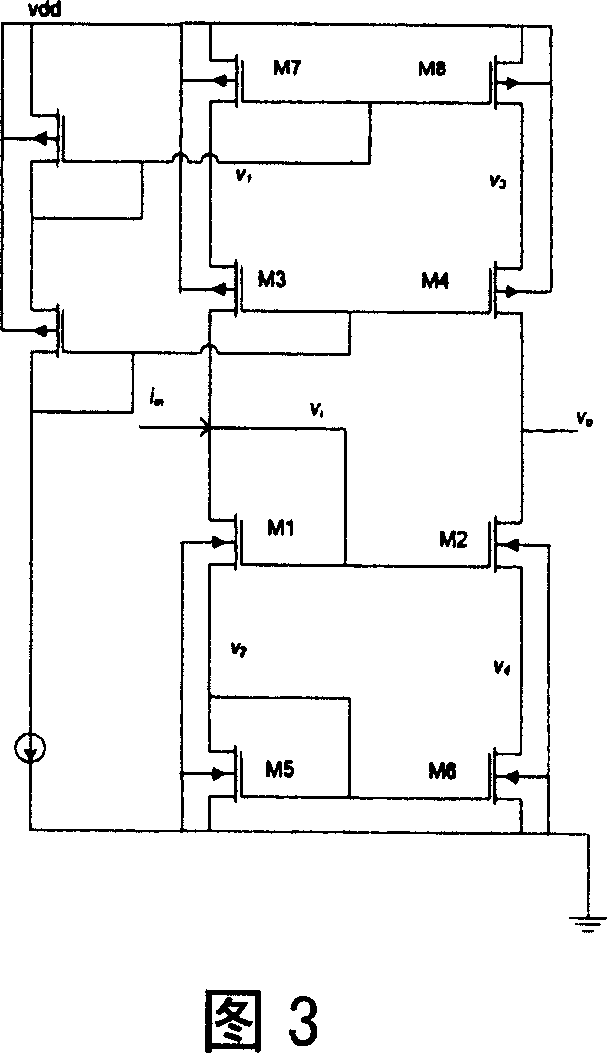

Complementary metal oxide semiconductor cascade high-gain current-to-voltage converter

ActiveCN101064497ASimple structureHigh gainLogic circuits coupling/interface using field-effect transistorsAmplifier with semiconductor-devices/discharge-tubesCascode current mirrorTransimpedance amplifier

A kind of CMOS common source common bar high plus current voltage converter, The invention relates to current voltage converting technique field, it includes common source common bar current mirror composed by transistors, the common source common bar current mirror is end-to-end joint by the common source common bar current mirror composed by four PMOS transistors and the common source common bar current mirror composed by four NMOS transistors, the alternating current signal is input from the joint position of upper and lower current mirror, and imaged by two current mirrors, the output voltage equals to the product of input current and output common source common bar structure resistance. The invention converts tiny pA class current signal to mV voltage, realizes high plus with character that the output resistance of the common source common bar current mirror is big, the structure is simple and plus is big, because there is feedback resistance, problem of stability does not be taken into account.

Owner:INST OF ELECTRONICS CHINESE ACAD OF SCI

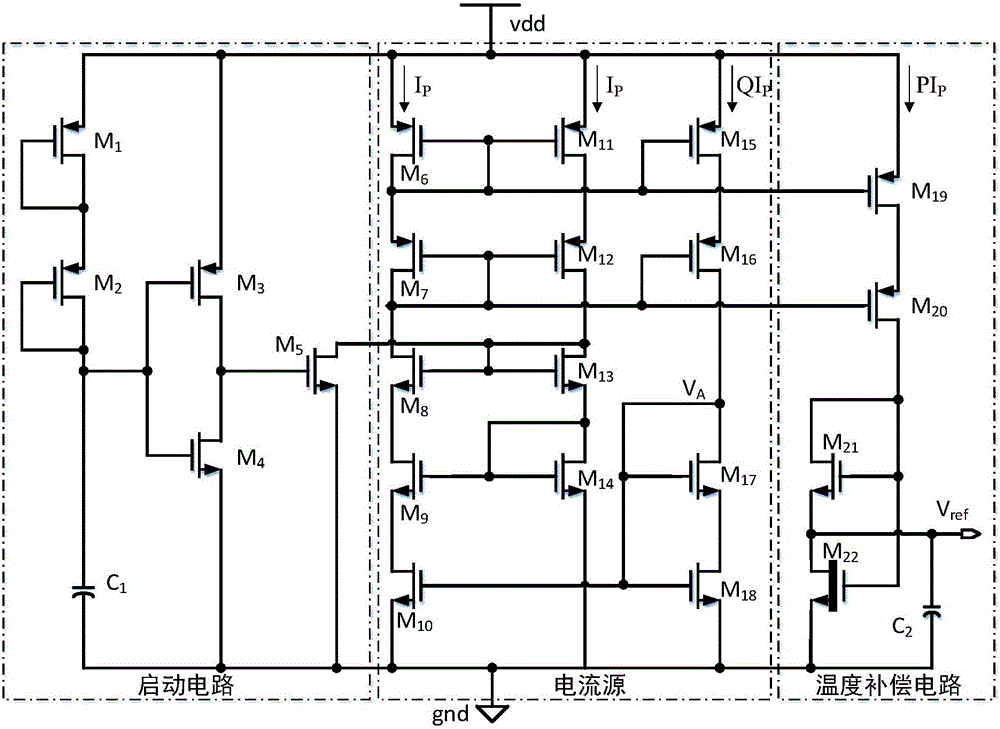

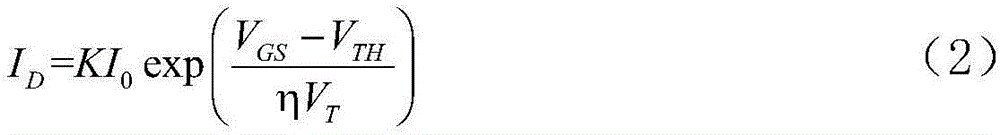

All-CMOS (Complementary Metal Oxide Semiconductor) based reference voltage source with high power supply rejection ratio

ActiveCN106843358ASuppress noiseReduce areaElectric variable regulationReference currentCascode current mirror

The invention discloses an all-CMOS (Complementary Metal Oxide Semiconductor) reference voltage source with a high power supply rejection ratio, which comprises a reference voltage source. The reference voltage source comprises a starting circuit, a current source circuit and a temperature compensating circuit, wherein an output end of the starting circuit is connected with an input end of the current source circuit; an output end of the current source circuit is connected with an input end of the temperature compensating circuit; an output end of the temperature compensating circuit forms an output end of the whole reference voltage source. The working characteristic of an MOS transistor working in a sub-threshold region is utilized by the all-CMOS reference voltage source, a nanoampere-magnitude reference current is generated; power supply noise is rejected by adopting a cascode current mirror. In addition, the all-CMOS reference voltage source not only has the advantages that the chip area is small and the power consumption is low and is only nanowatt-magnitude, but also has the advantages that the all-CMOS reference voltage source has the high power supply rejection ratio, the temperature drift coefficient is low, and the line-voltage regulation is low; moreover, a resistor, a diode and a triode are not used; the all-CMOS reference voltage source is compatible with a standard CMOS process; the layout area is effectively reduced; the production cost is decreased.

Owner:GUILIN UNIV OF ELECTRONIC TECH

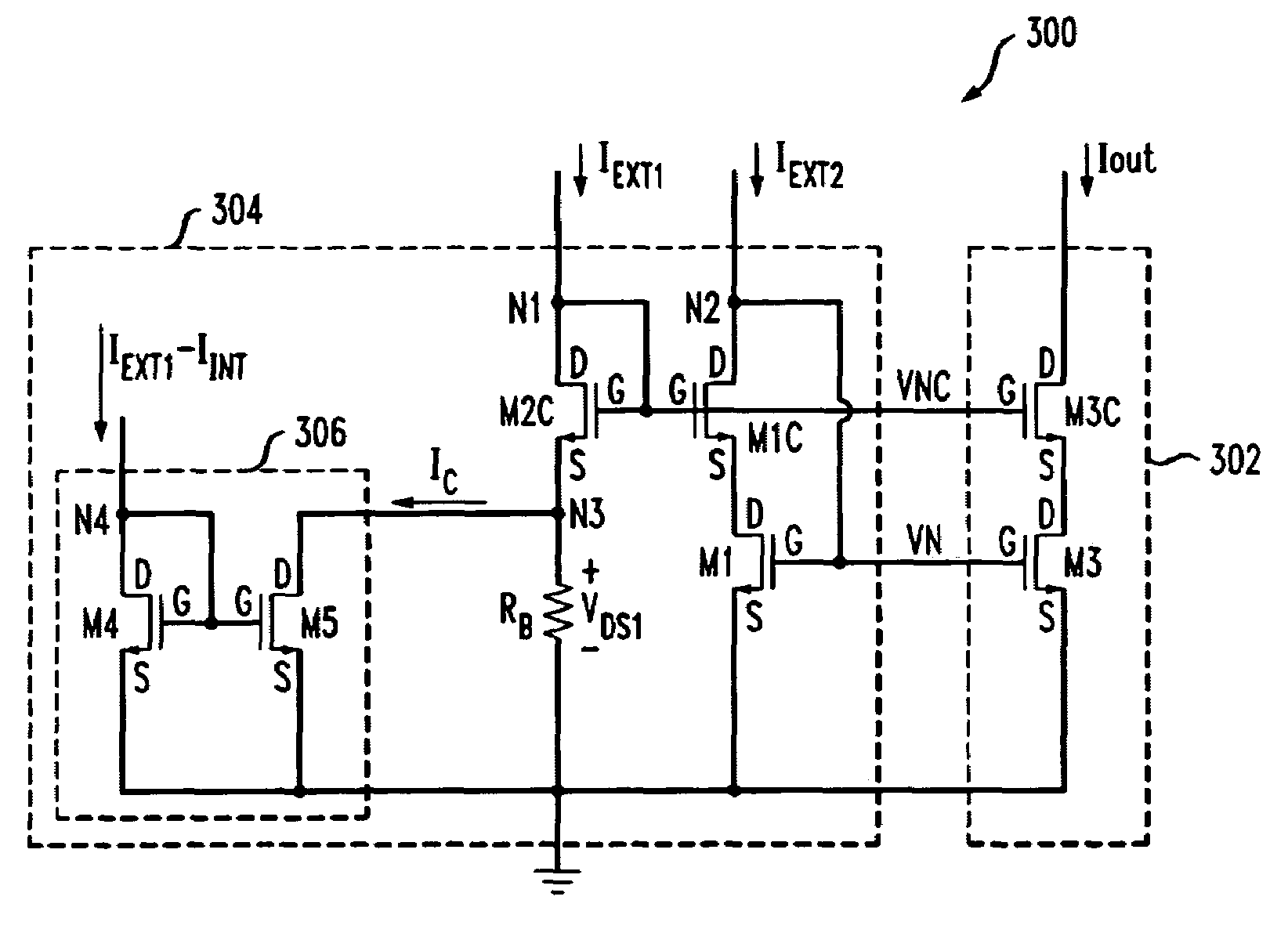

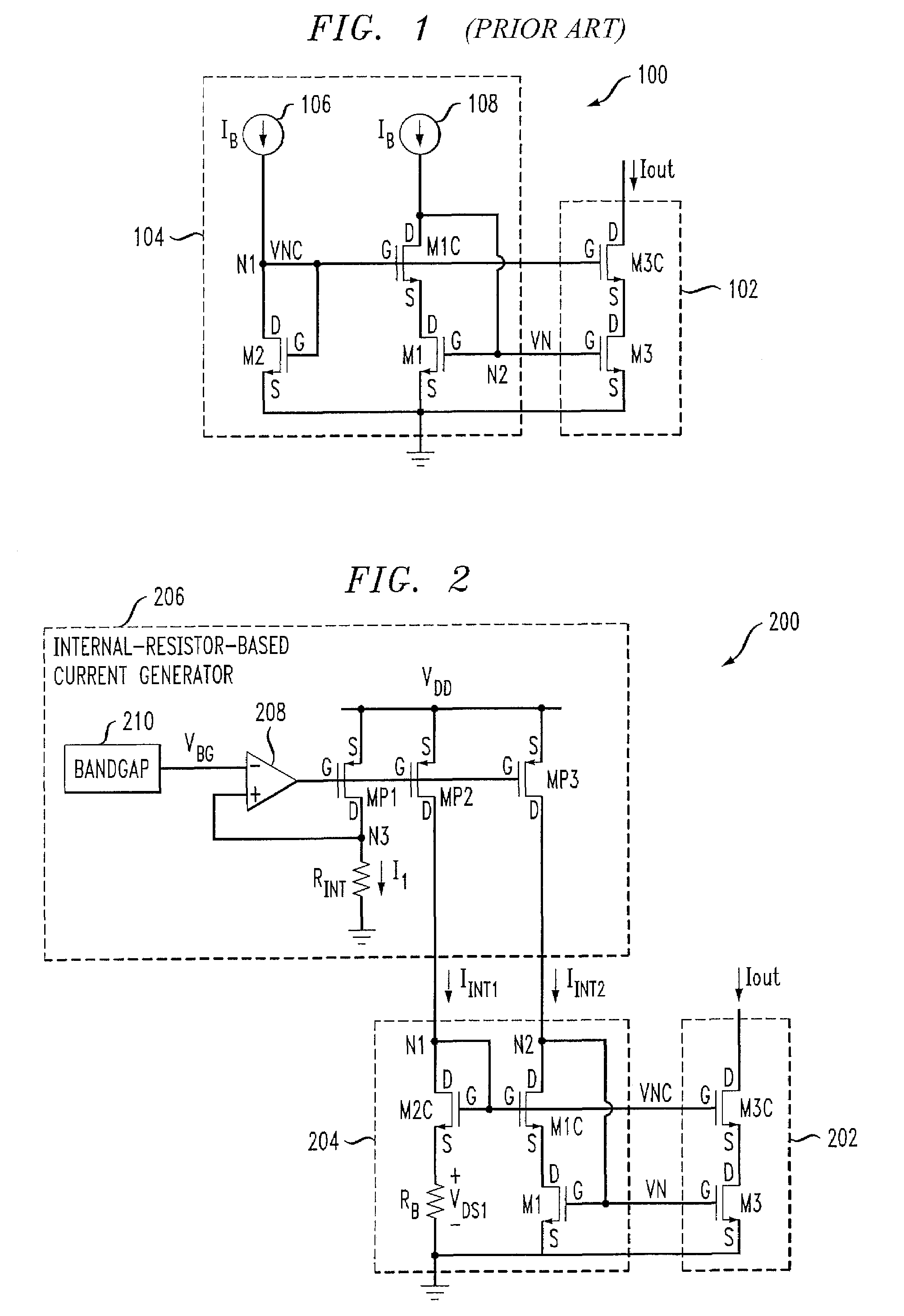

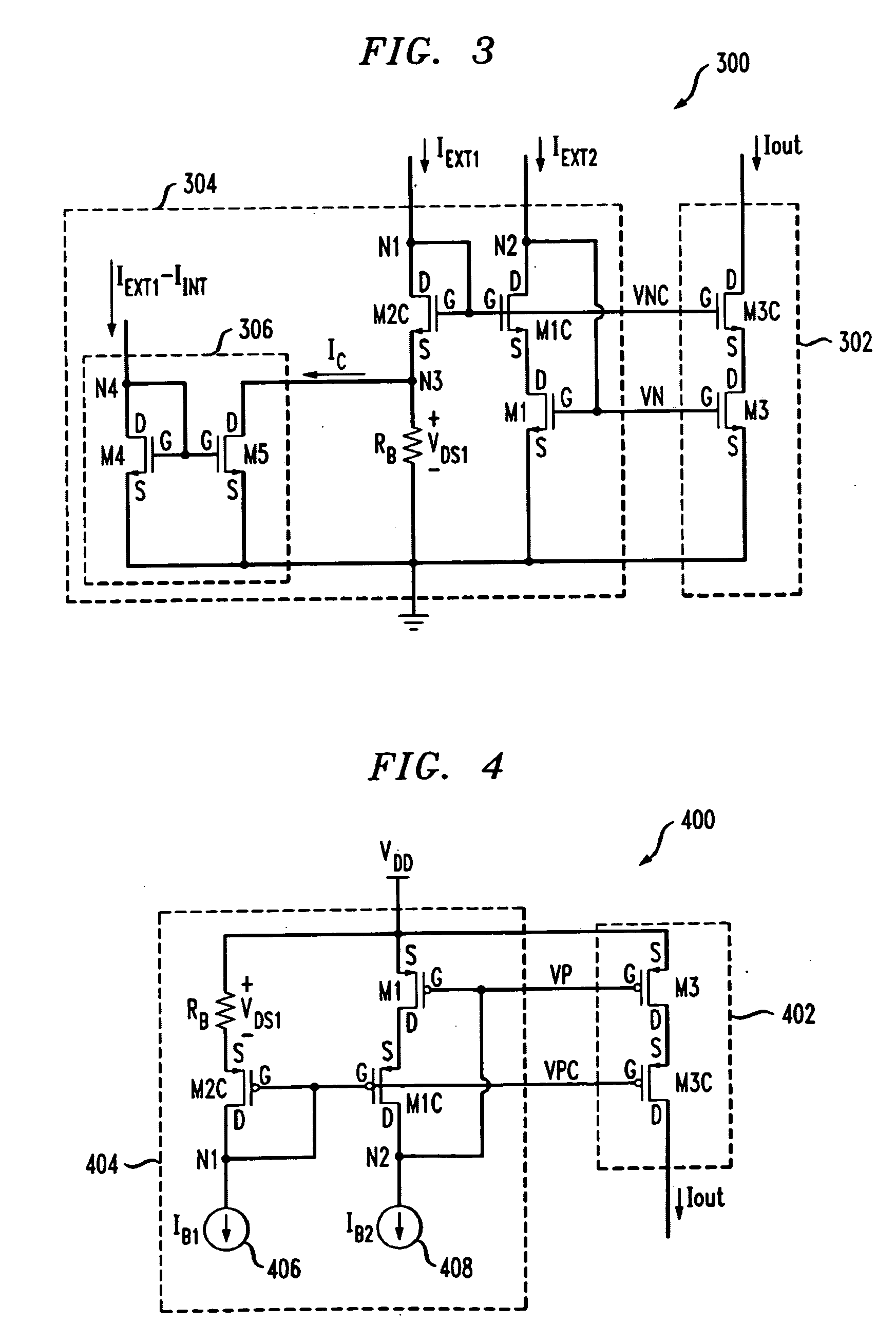

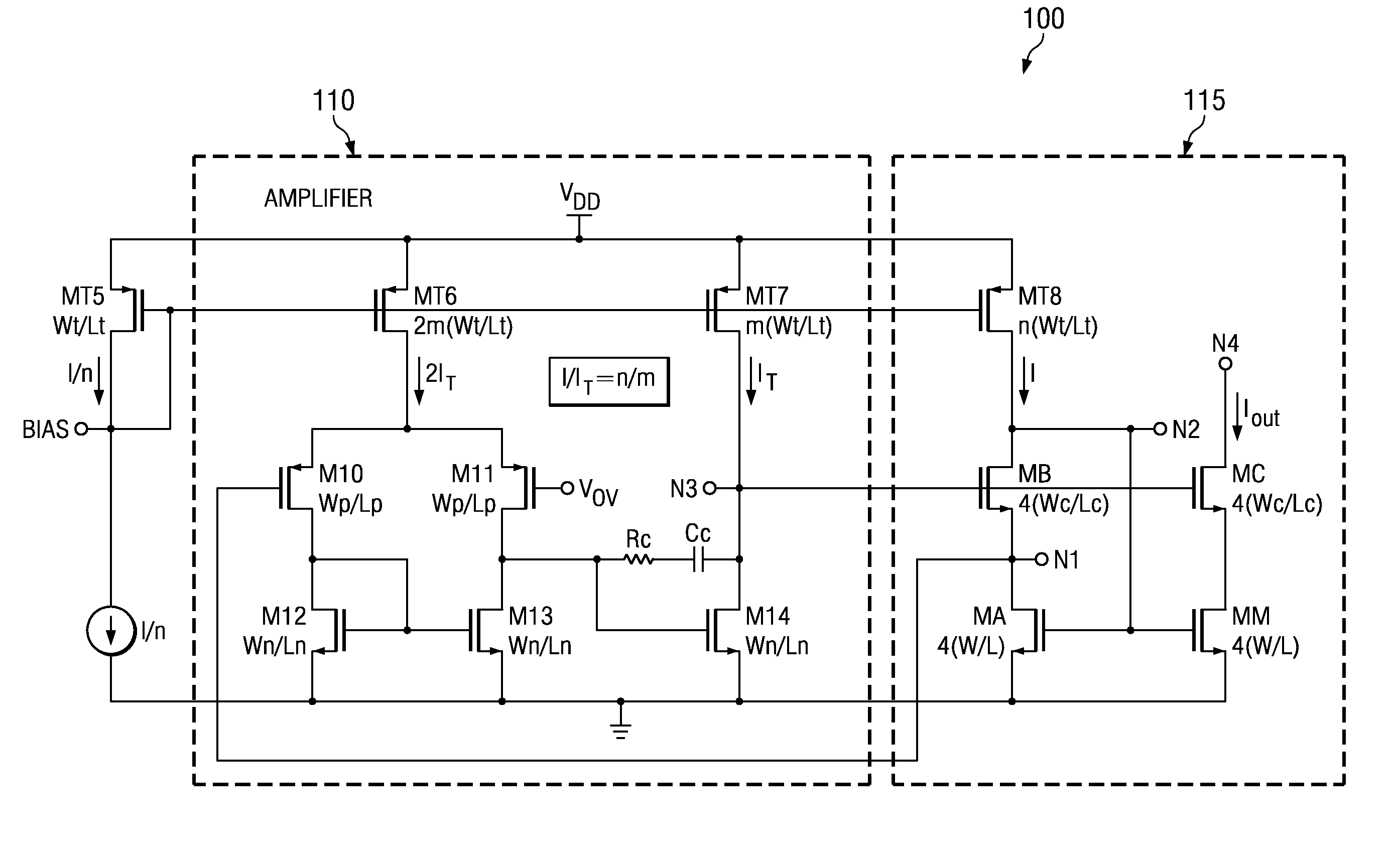

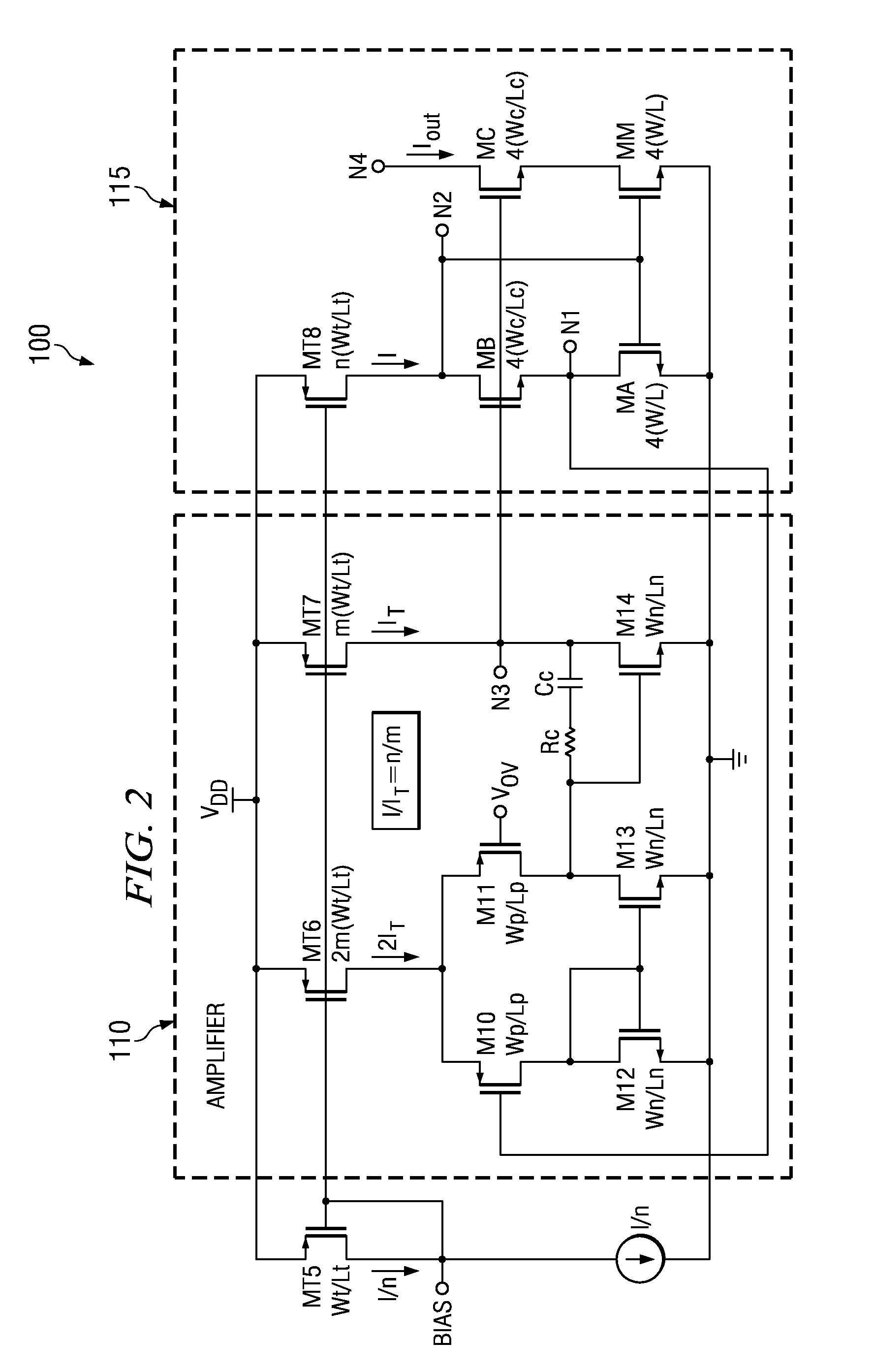

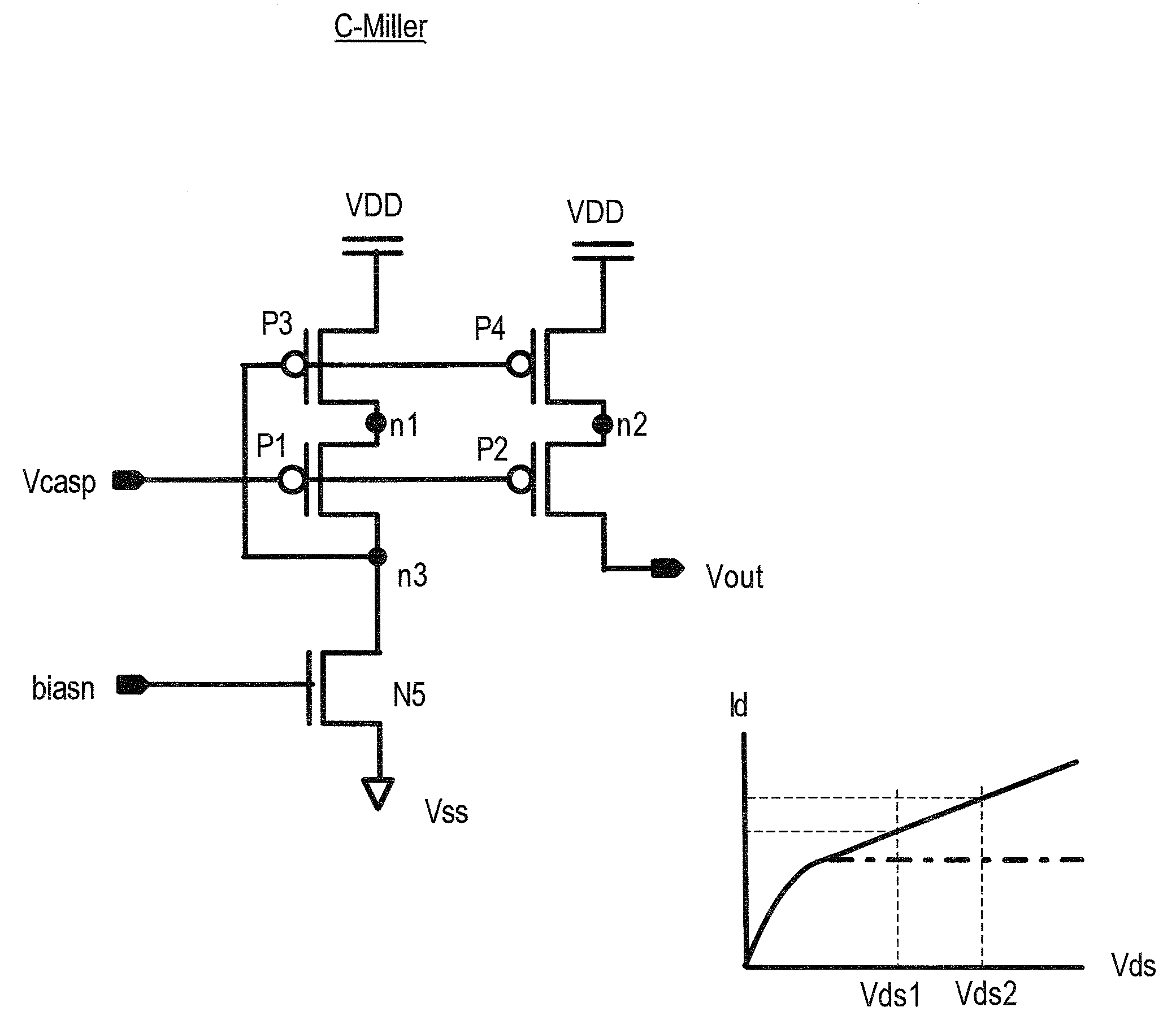

Biasing Scheme for Low-Voltage MOS Cascode Current Mirrors

ActiveUS20080186101A1Easy to trackAmplifier detailsElectric variable regulationAudio power amplifierLow voltage

A circuit and a method for biasing a compound cascode current mirror (CCCM) that enables high-voltage swing at the output and accurate current mirroring is presented. The CCCM has mirror transistors and cascode transistors which may be of a different technology kind. The drain-source voltage Vds of the mirror transistor on the input leg of the CCCM is held at a voltage Vov that is generated by the biasing circuit; Vov is the overdrive voltage of the input mirror transistor of the CCCM and the value of Vov is maintained by the bias circuit and a feed-back amplifier such that the mirror transistor remains on the edge of its active region, over manufacture deviations and tracks even over operational conditions such as temperature and supply variations. The feed-back amplifier drives the gates of the cascode transistors and uses its feedback node to hold the Vds at Vov.

Owner:TEXAS INSTR INC

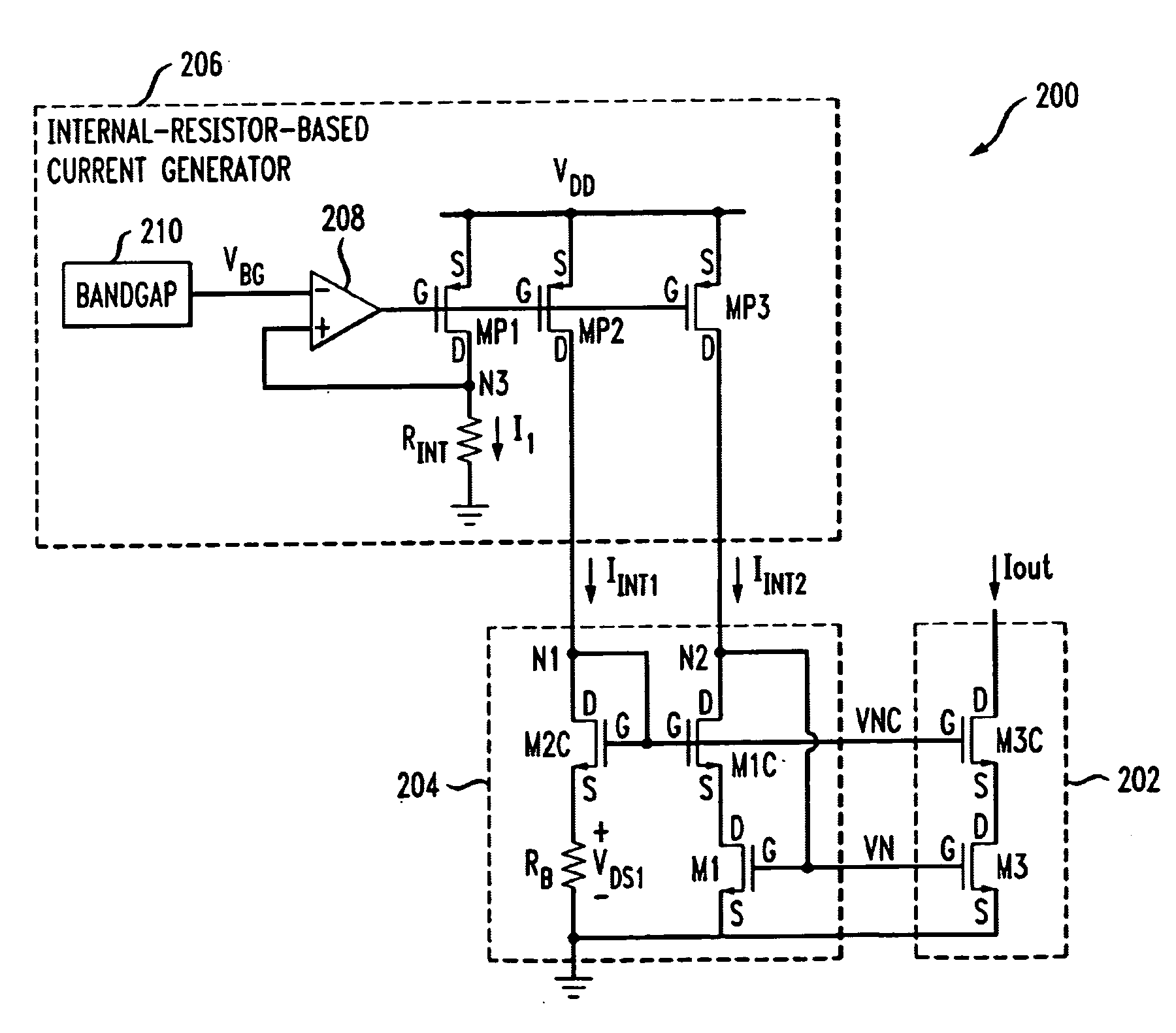

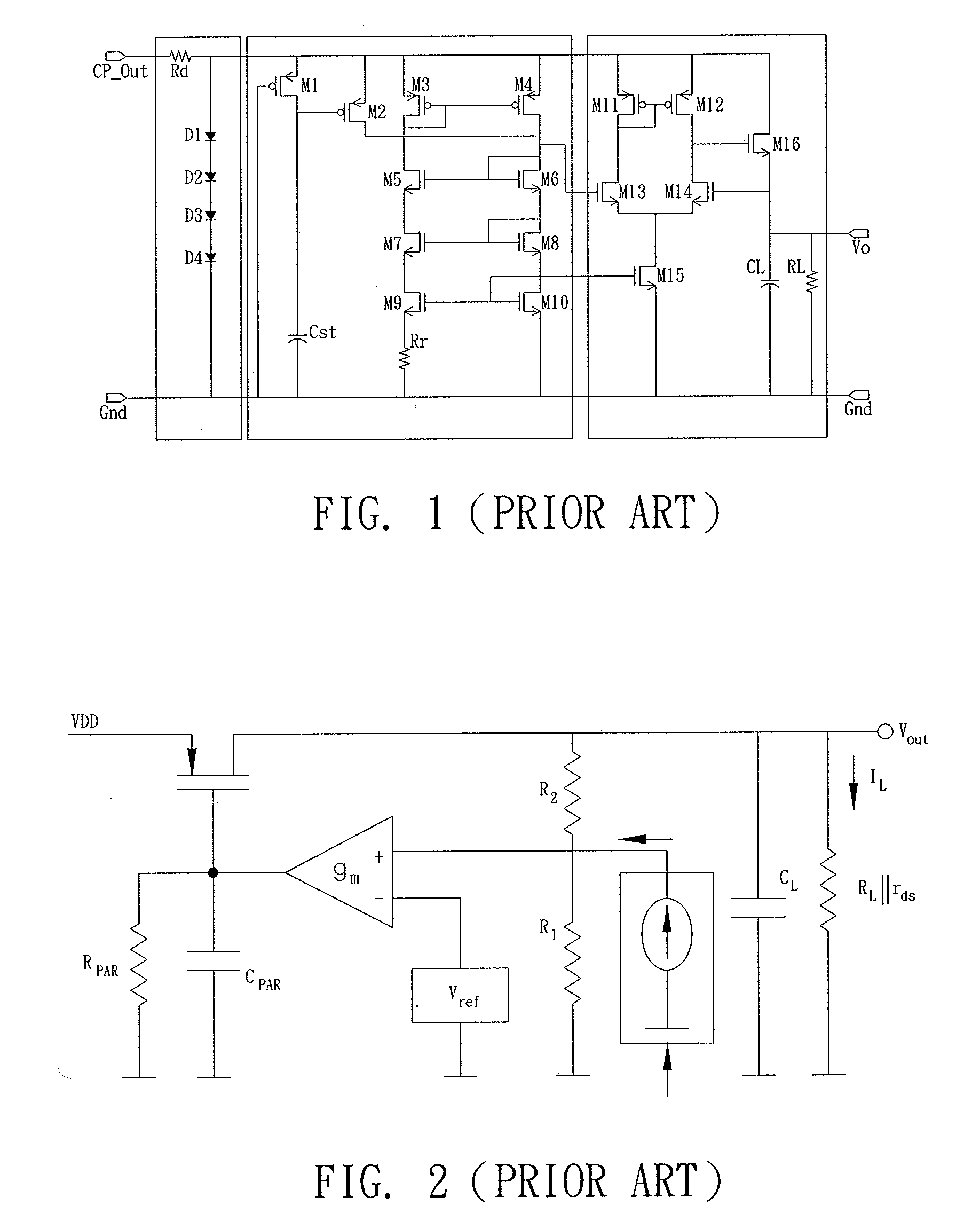

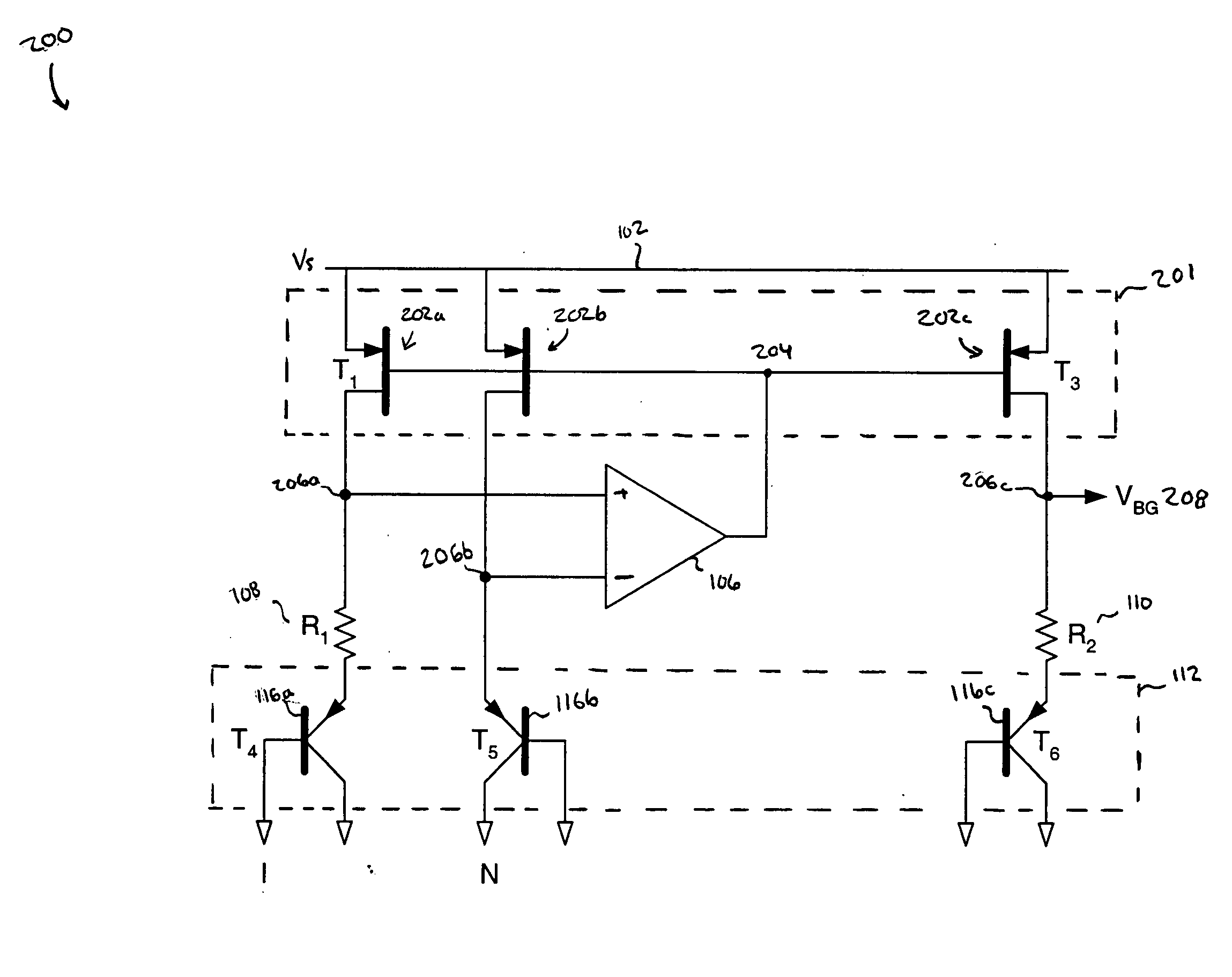

Apparatus and method for a low voltage bandgap voltage reference generator

A bandgap voltage generator generates an output reference voltage and is configured to operate from a low voltage power supply and consumes low power. The bandgap voltage generator includes a non-cascode current mirror that is directly connected to a power supply input and that produces current mirror outputs in response to the power supply input. A differential amplifier senses two of the current mirror outputs, and generates an output that controls the non-cascode current mirror so that the current mirror outputs produce substantially the same current and voltage at the sensed current mirror outputs. A bandgap core circuit includes first and second bipolar devices that receive the constant current from the two current mirror outputs. The first bipolar device is scaled in size relative to the second bipolar device so as to produce an output voltage at a third current mirror output that is multiple of the characteristic bandgap voltage of the bipolar devices. The non-cascode current mirror includes FET devices having their respective sources connected to the power supply input, and having their respective drains connected to the respective current mirror outputs. The FETs are not implemented with a cascode configuration, so that the bandgap voltage generator can operate with a low voltage power supply and also consumes low power.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

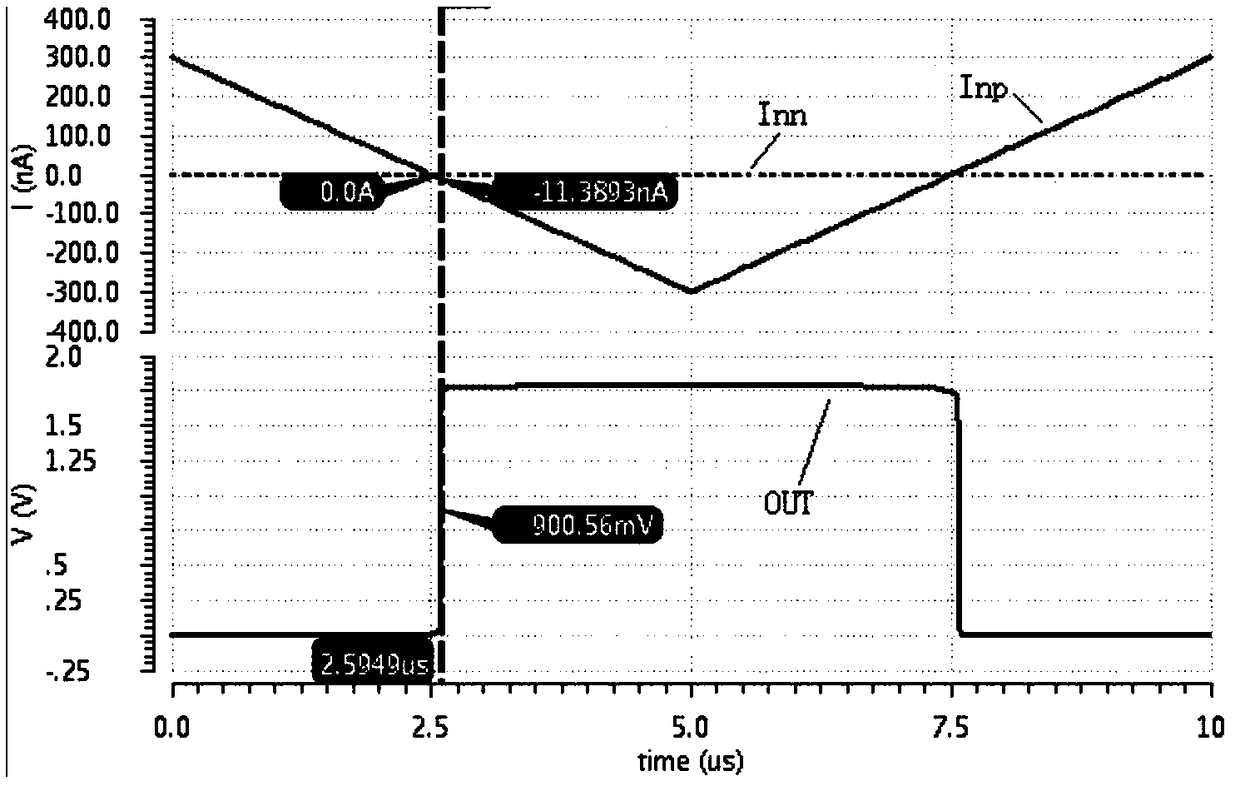

Current comparator

ActiveCN109379064AThe equivalent input impedance is smallHigh speedMultiple input and output pulse circuitsCascode current mirrorEngineering

The invention discloses a current comparator, comprising a current difference stage, a gain stage and an output stage, wherein the current difference stage is a cascode current mirror, a current inputend is connected with an MOS transistor with short circuited gate and drain, so that the equivalent input impedance of the current comparator is reduced, and the comparison speed can be improved; thegain stage introduces a common source amplifier of a current source load with feedback, a current source bias voltage is generated by a high threshold voltage tube, so that the bias tube current canbe reduced, and the power consumption is reduced; and the output stage introduces a self-biased differential amplifier, so that the driving capability of the output comparator can be obviously improved. Theoretical analysis and simulation results indicate that the current comparator disclosed by the invention has the characteristics of high precision and high driving capability.

Owner:MORNSUN GUANGZHOU SCI & TECH

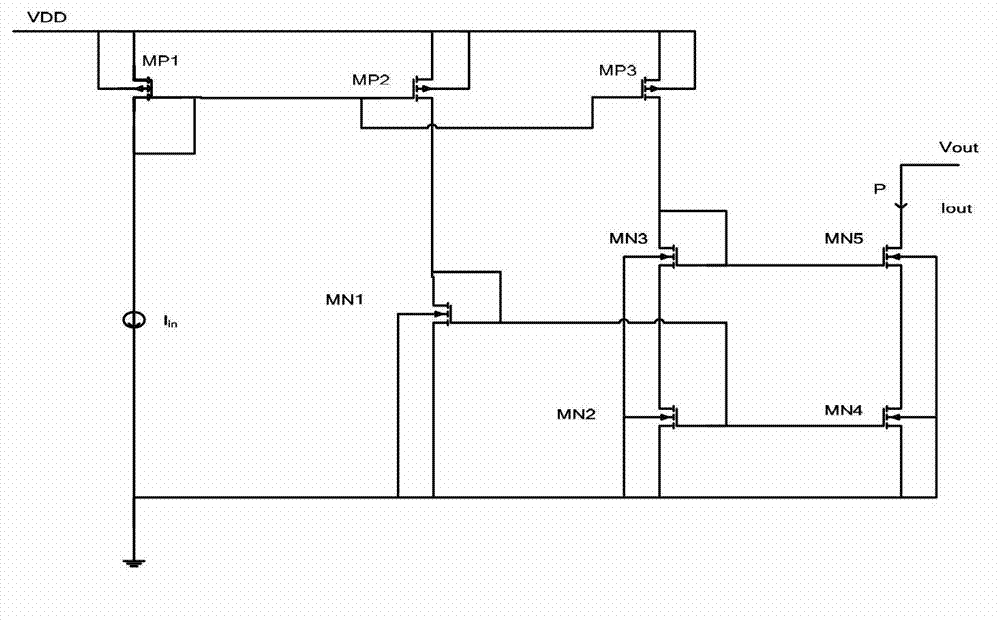

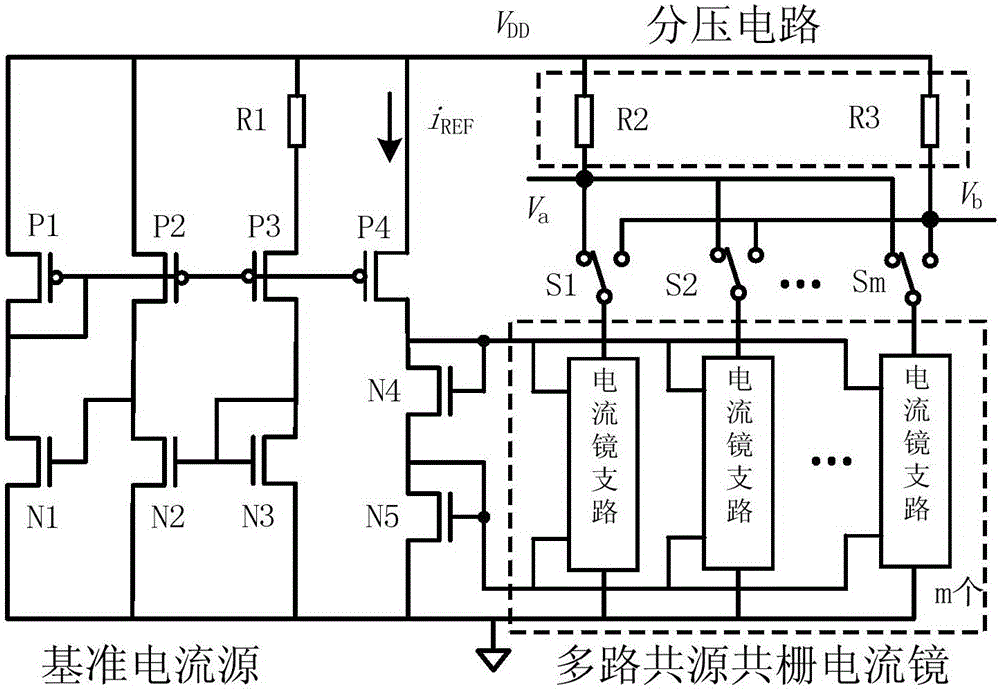

Deviation signal producing circuit and multiport configurable PUF circuit

ActiveCN105676942AImprove robustnessImprove uniquenessElectric variable regulationElectrical resistance and conductanceCascode current mirror

The invention discloses a deviation signal producing circuit and a multiport configurable PUF circuit.A standard current source is formed by a first PMOS tube, a second PMOS tube, a third PMOS tube, a fourth PMOS tube, a first NMOS tube, a second NMOS tube, a third NMOS tube, a fourth NMOS tube, a fifth NMOS tube and a first resistor, the standard current source has the property of being insensitive to mains voltage fluctuation and temperature variation, the deviation signal producing circuit copies an electric current of the standard current source to all current mirror branches of a multi-channel cascode current mirror through a cascode form, all the current mirror branches are insensitive to temperature and voltage, and therefore the whole deviation signal producing circuit has the advantage that high robustness is achieved; the deviation signal producing circuit and the multiport configurable PUF circuit have the advantages that for an output response of the PUF circuit of the deviation signal producing circuit, uniqueness, randomness and reliability are higher, it is indicated through experimental results that the PUF circuit has good uniqueness and randomness, and the reliability of working at different temperatures of -40-125 DEG C and under voltage of 1.02-1.32 V is larger than 97.4 percent.

Owner:NINGBO UNIV

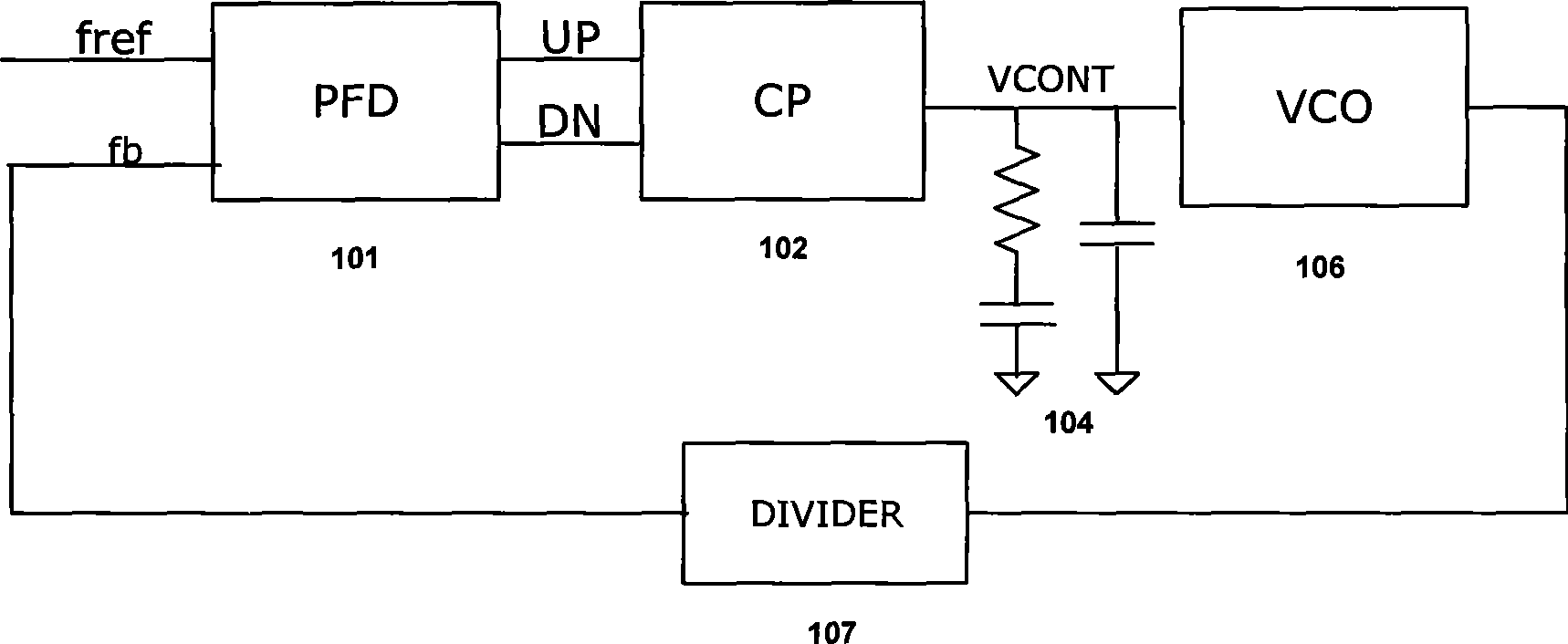

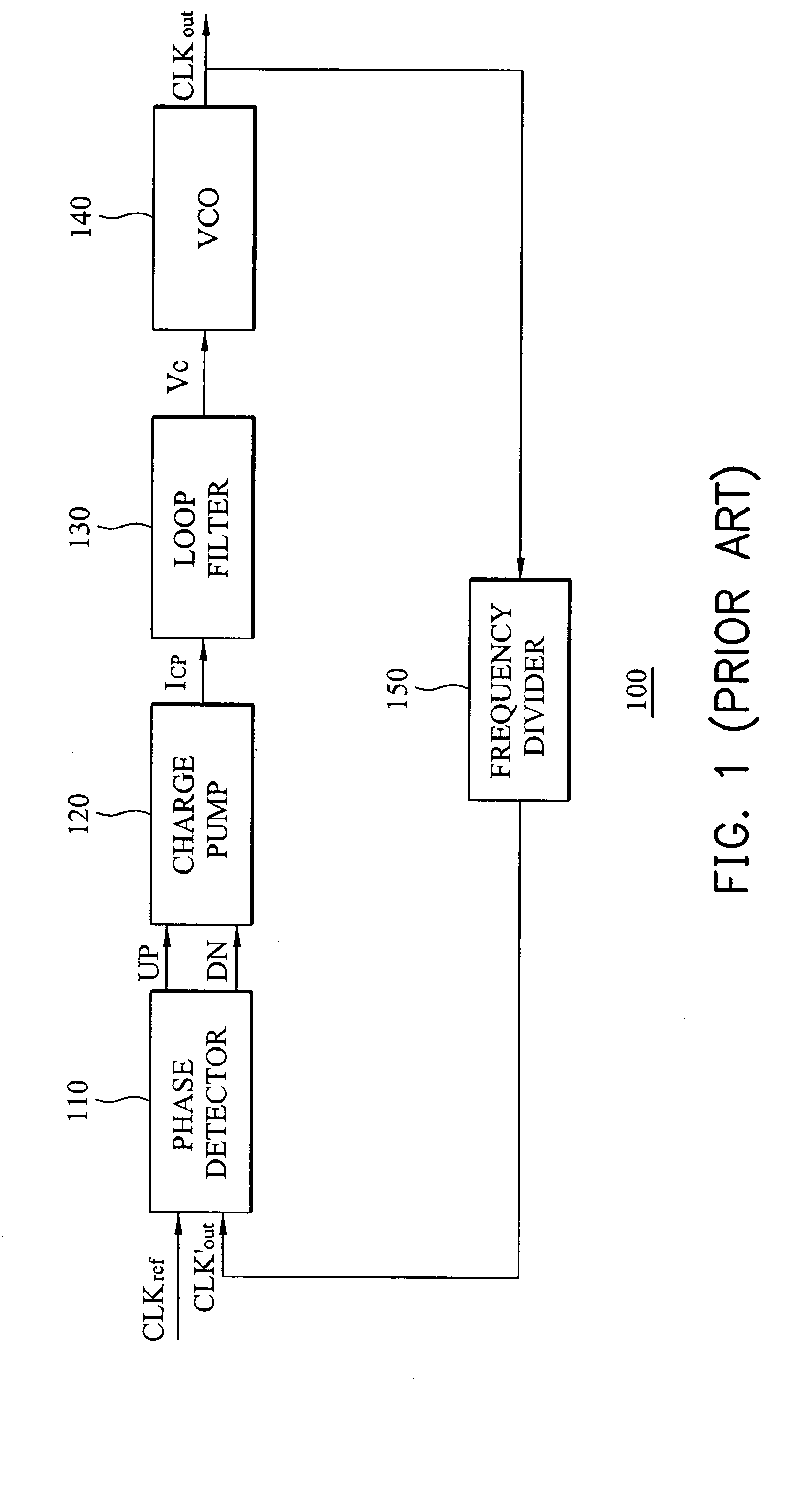

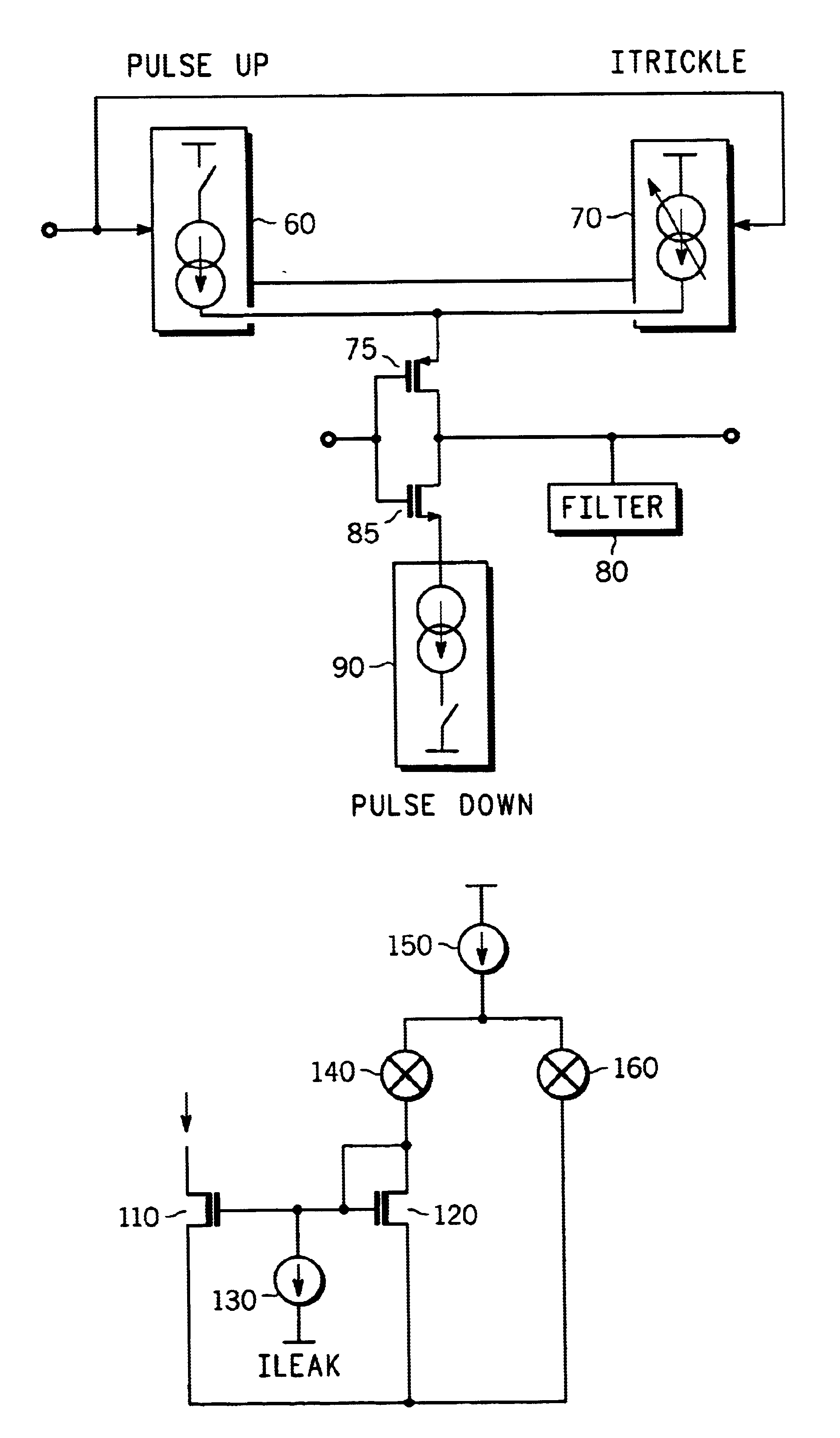

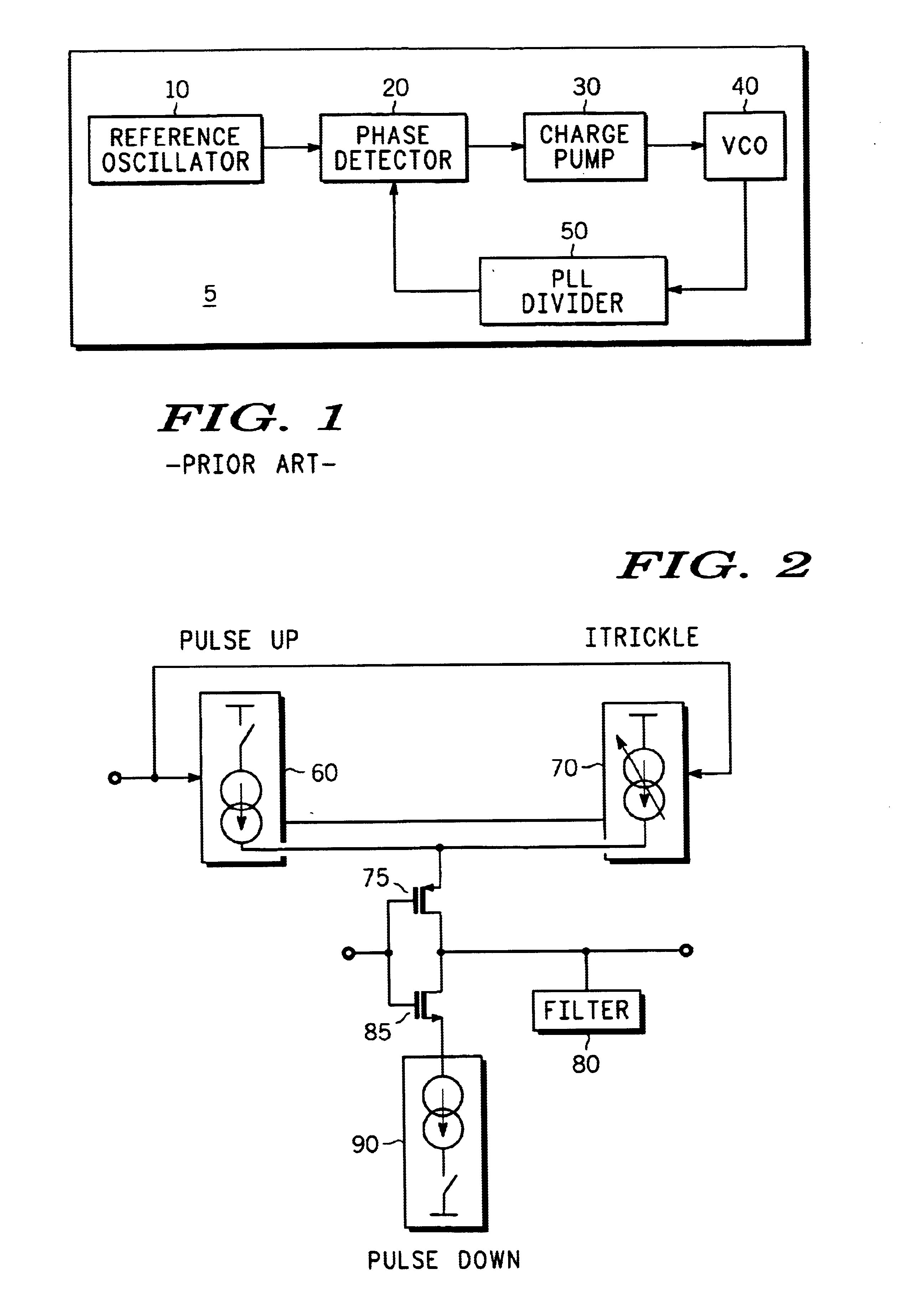

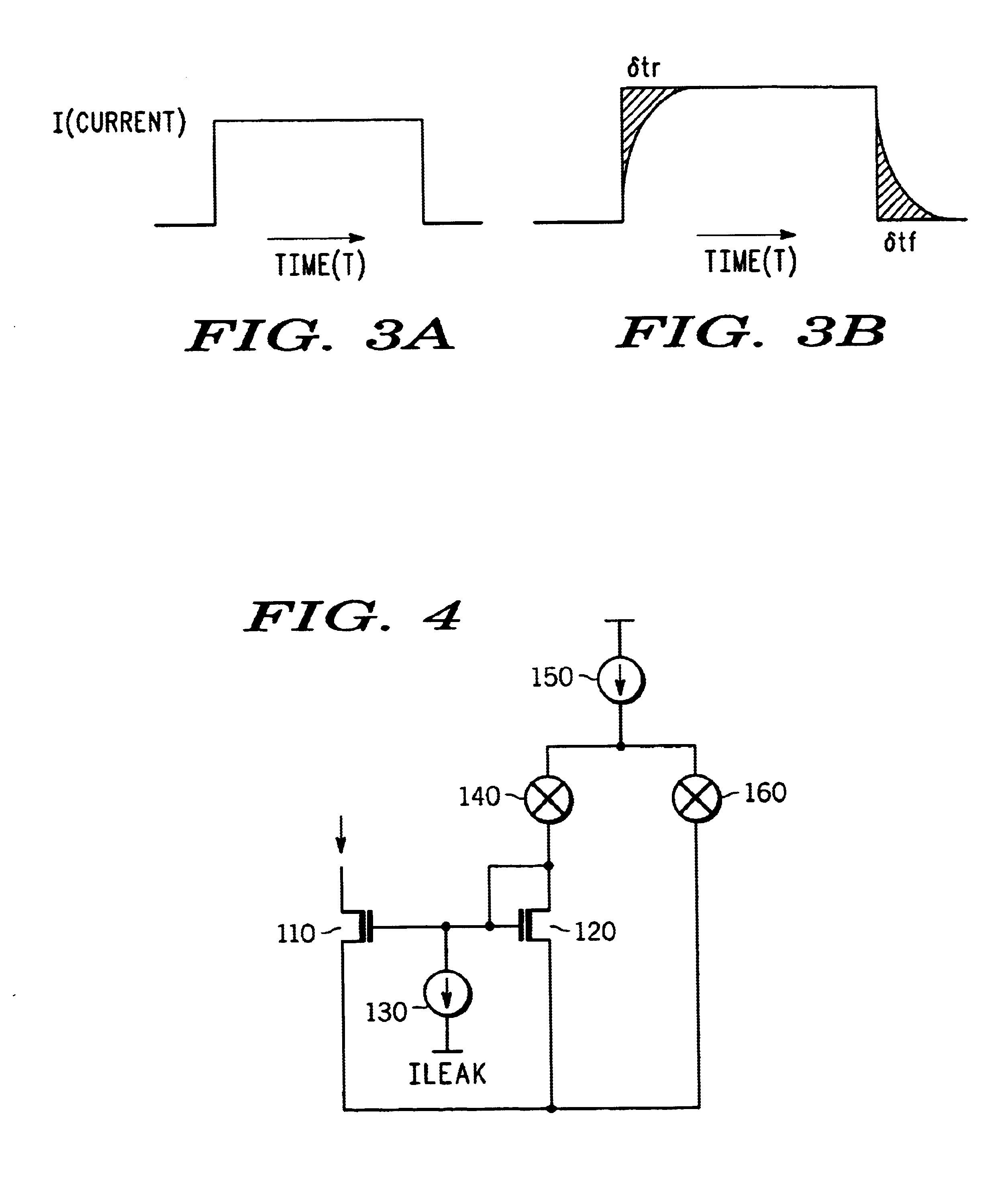

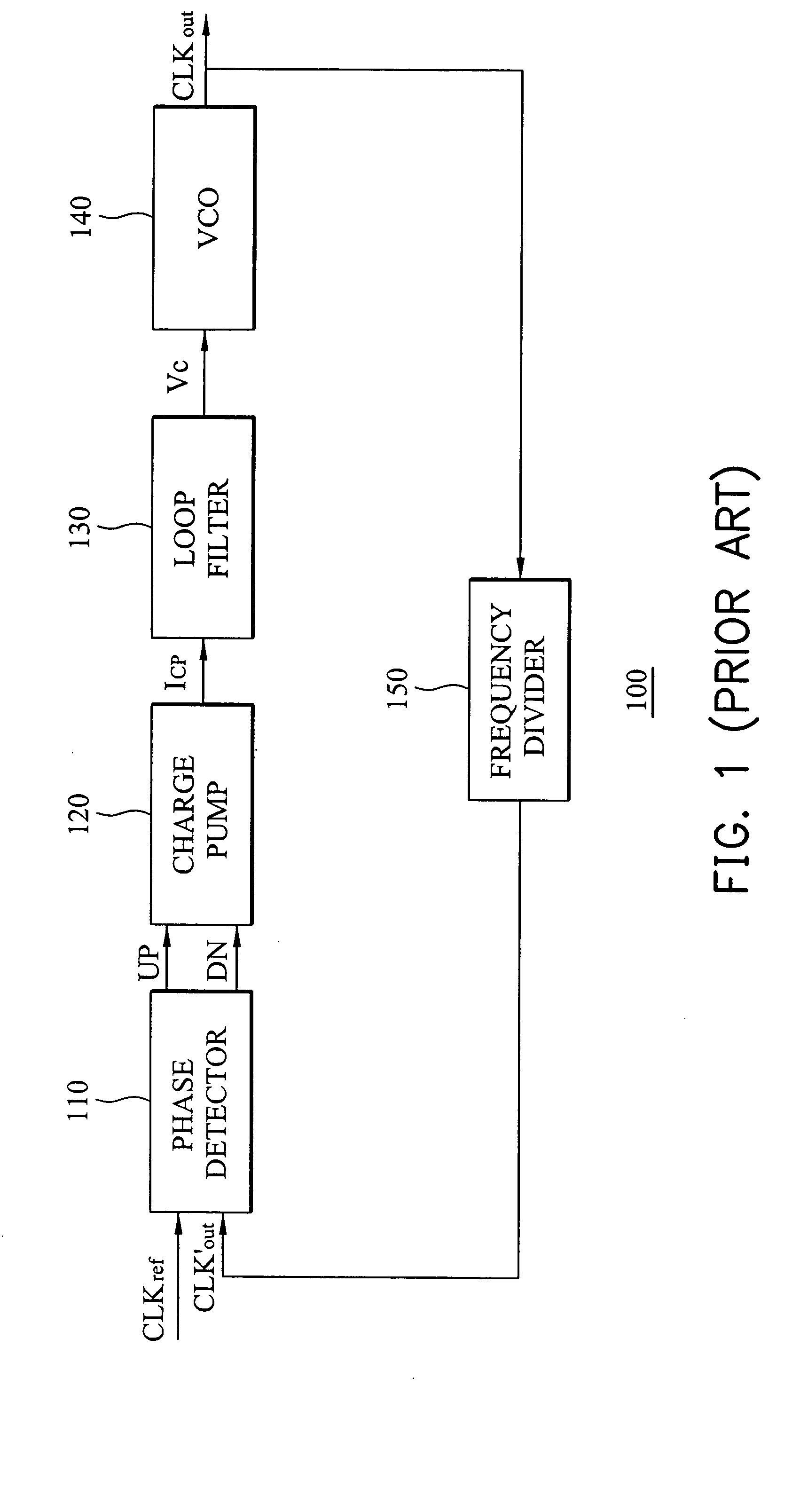

PPL arrangement, charge pump, method and mobile transceiver

A charge pump arrangement for a phase-locked-loop has a current source circuit (60) which provides charging current to the phase locked loop, and a current sink circuit (90) which depletes charging current from the phase locked loop. The current source circuit (60) and the current sink circuit (90) have slew rates which have a predetermined relationship. In this way, the charge pump causes substantially no non-linear charge injection in the phase-locked-loop. Cascoded current mirrors (75, 85) are utilised to provide a high voltage with thin gate oxide technology. The arrangement has a relatively small die size. Since bias currents of the arrangement are mirrored according to the output current required, improved transient times are produced, leading to reduced phase noise.

Owner:FREESCALE SEMICON INC

Cascode current mirror circuit operable at high speed

InactiveUS7312651B2Electric variable regulationAmplifiers with semiconductor devices onlyCascode current mirrorEngineering

A current mirror circuit includes a first transistor having a source node connected to a reference potential, a second transistor having a source node coupled to a drain node of the first transistor and a gate node connected to a first predetermined potential, an inverted amplification circuit having a non-inverted input node coupled to a drain node of the second transistor, an inverted input node coupled to a second predetermined potential, and an output node coupled to a gate node of the first transistor, a third transistor having a gate node connected to a potential substantially equal to a potential of the gate node of the first transistor, and a fourth transistor having a gate node connected to a potential substantially equal to a potential of the gate node of the second transistor.

Owner:FUJITSU LTD

Biasing scheme for low-voltage MOS cascode current mirrors

A circuit and a method for biasing a compound cascode current mirror (CCCM) that enables high-voltage swing at the output and accurate current mirroring is presented. The CCCM has mirror transistors and cascode transistors which may be of a different technology kind. The drain-source voltage Vds of the mirror transistor on the input leg of the CCCM is held at a voltage Vov that is generated by the biasing circuit; Vov is the overdrive voltage of the input mirror transistor of the CCCM and the value of Vov is maintained by the bias circuit and a feed-back amplifier such that the mirror transistor remains on the edge of its active region, over manufacture deviations and tracks even over operational conditions such as temperature and supply variations. The feed-back amplifier drives the gates of the cascode transistors and uses its feedback node to hold the Vds at Vov.

Owner:TEXAS INSTR INC

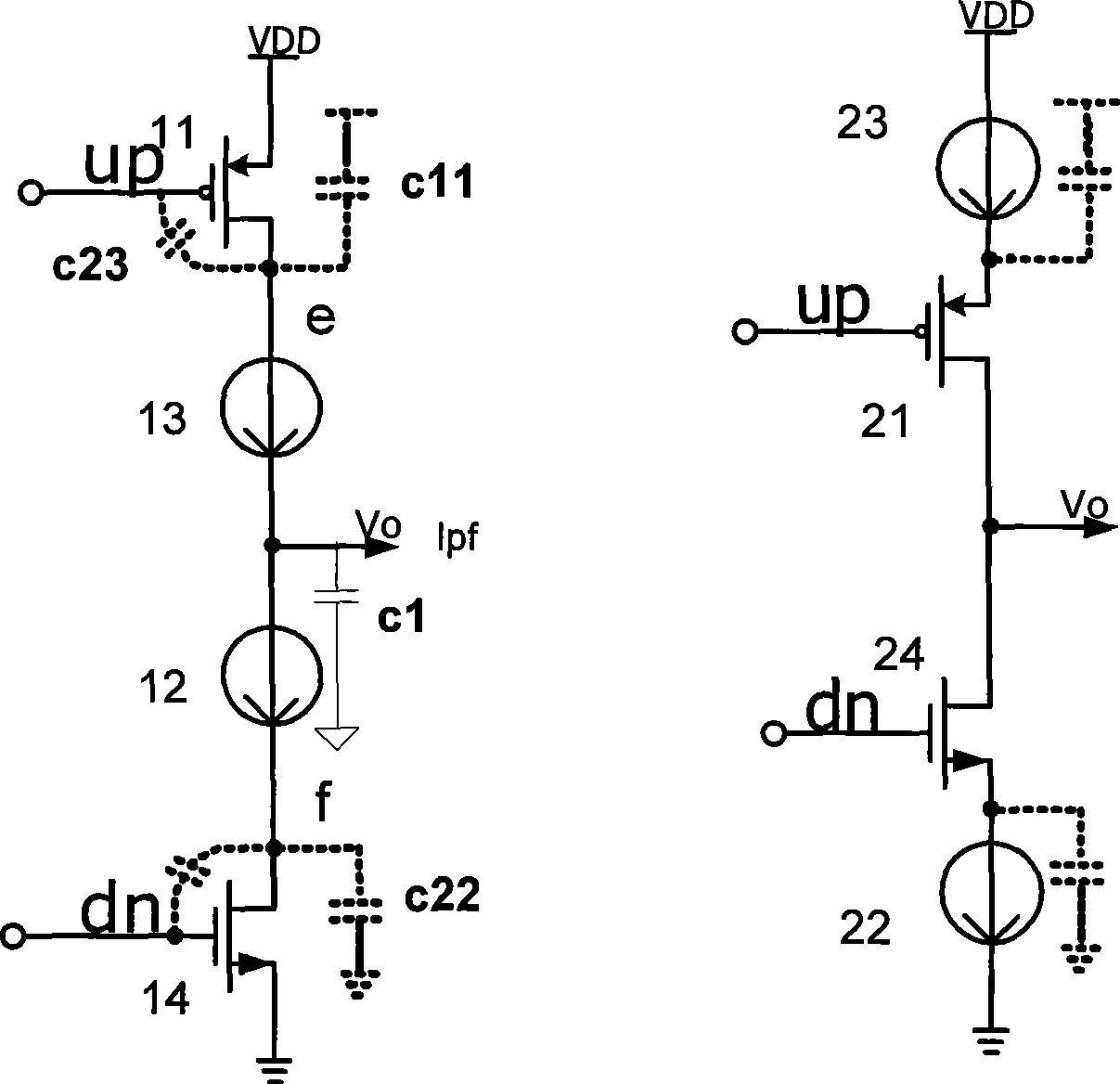

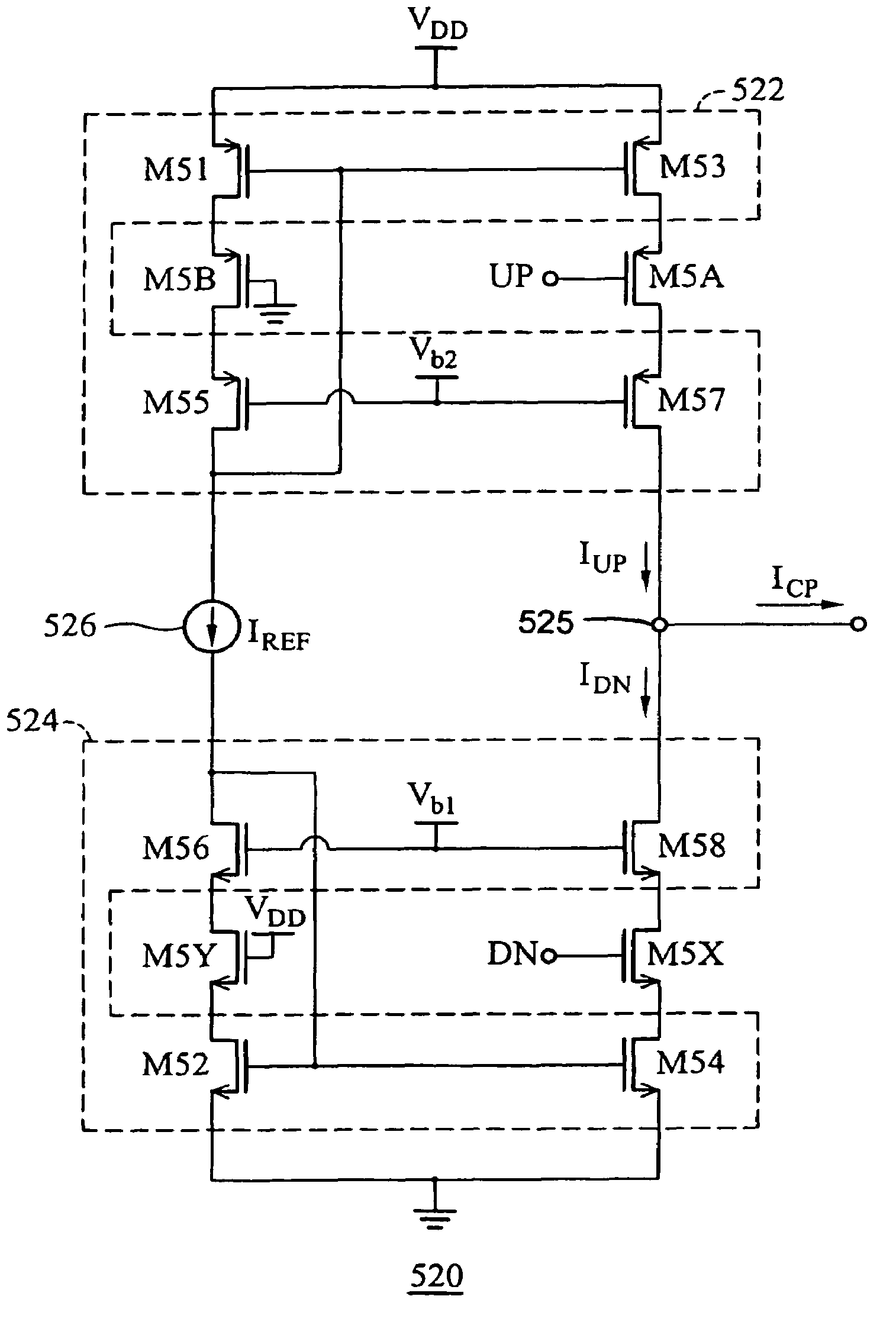

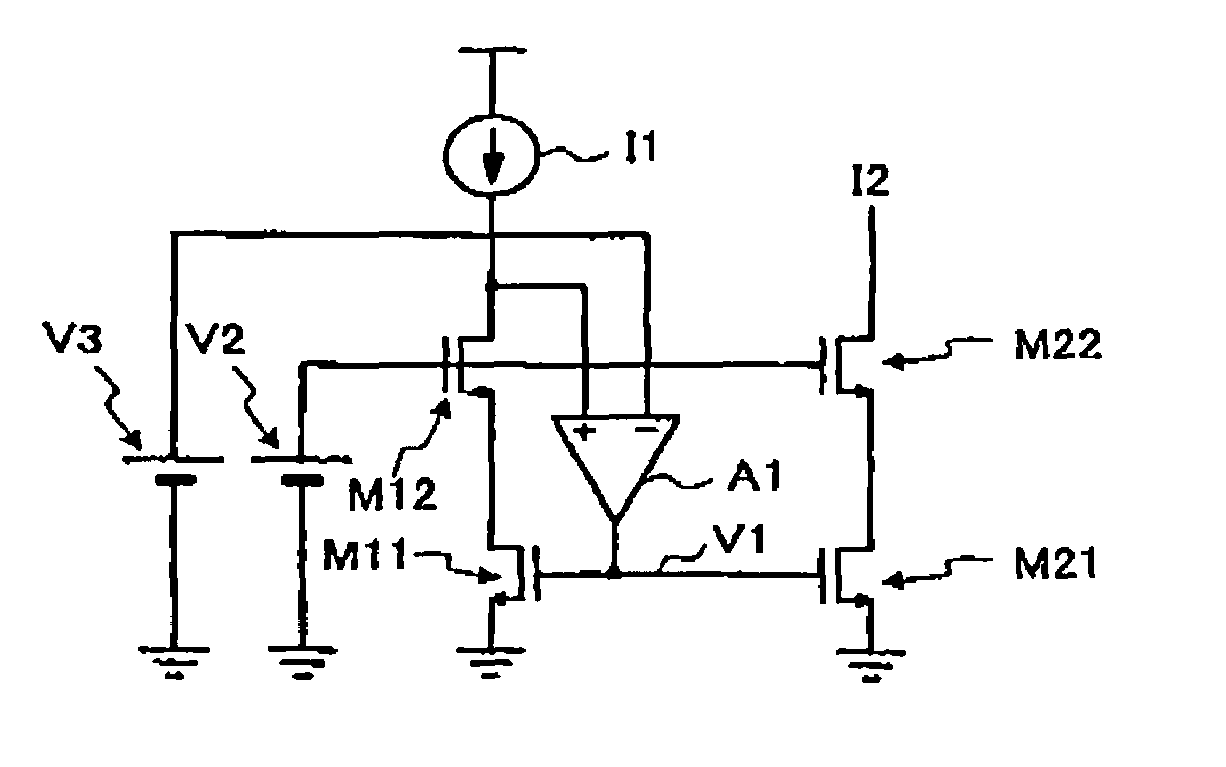

High-speed low-noise charge pump

ActiveUS20050068090A1Fast switching speedReduce noisePulse automatic controlElectric pulse generatorLow noiseControl signal

A high-speed, low-noise charge pump for use in a phase-locked loop. The charge pump is constituted by first and second cascode current mirrors, as well as first and second switching transistors. The first cascode current mirror includes a first output mirror transistor and a first output cascode transistor. The first switching transistor is interposed between the first output mirror and the first output cascode transistors. During assertion of a first control signal, the first switching transistor is turned on so a first mirror current can flow through an output node. Likewise, the second cascode current mirror includes a second output mirror transistor and a second output cascode transistor. The second switching transistor is interposed between the second output mirror and the second output cascode transistors. During assertion of a second control signal, the second switching transistor is turned on so the second mirror current can flow through the output node.

Owner:VIA TECH INC

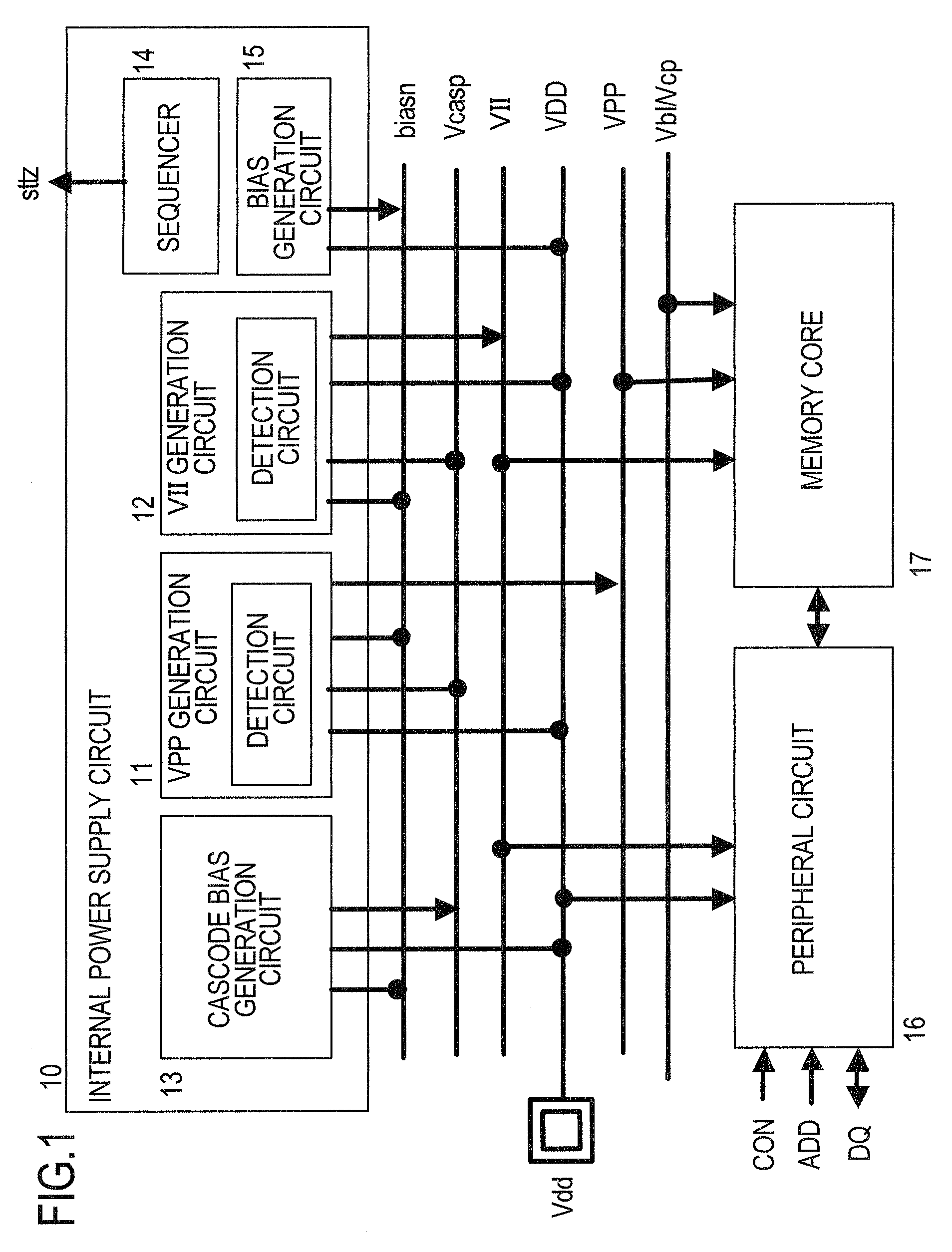

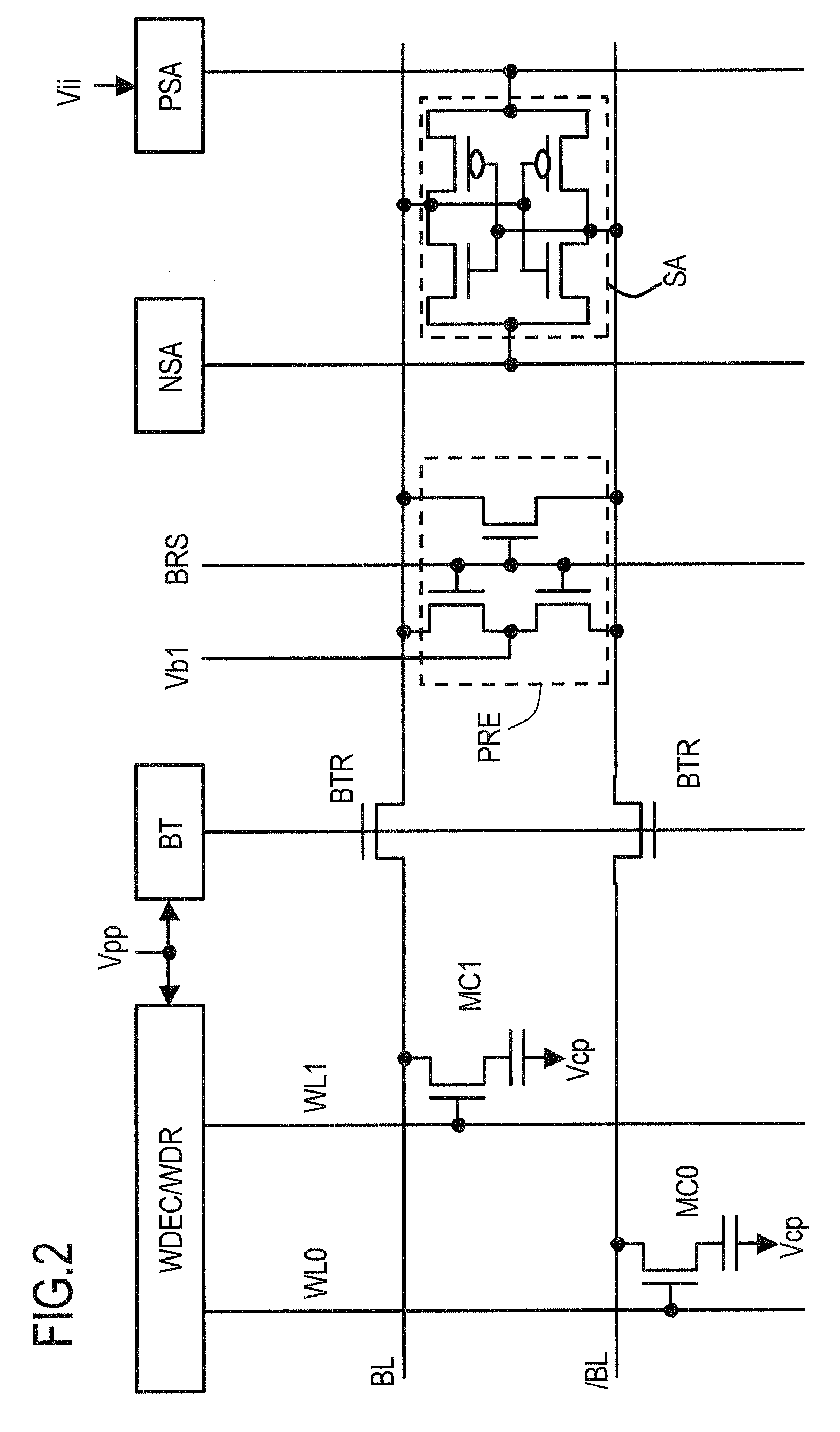

Internal Power Supply Circuit Having a Cascode Current Mirror Circuit

ActiveUS20090230770A1Erroneous operationAvoid misuseBoards/switchyards circuit arrangementsDc source parallel operationCascode current mirrorPower circuits

A current mirror circuit which is connected to first and second power supplies and generates a desired current, has a plurality of first transistors which are connected in parallel to the first power supply side and the gates of which are connected to a common node, a plurality of second transistors which are cascode-connected to the plurality of first transistors and the gates of which are supplied with a cascode bias potential and a cascode bias generation circuit which generates the cascode bias potential, wherein the cascode bias generation circuit maintains the cascode bias potential during normal operation at a first potential between the potentials of the first and second power supplies, and maintains the cascode bias potential during power-on at a second potential closer to the potential of the second power supply than the first potential.

Owner:SOCIONEXT INC

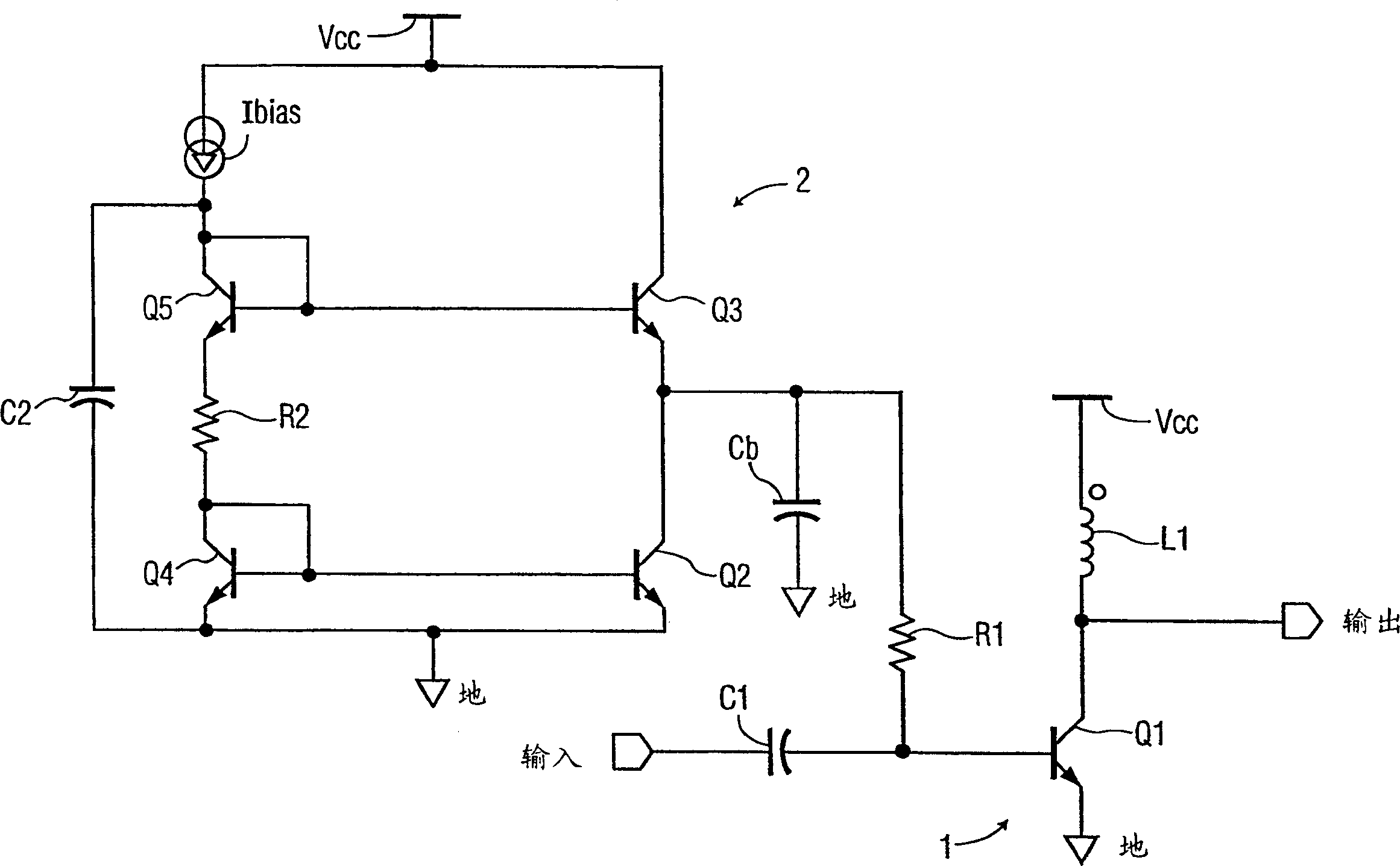

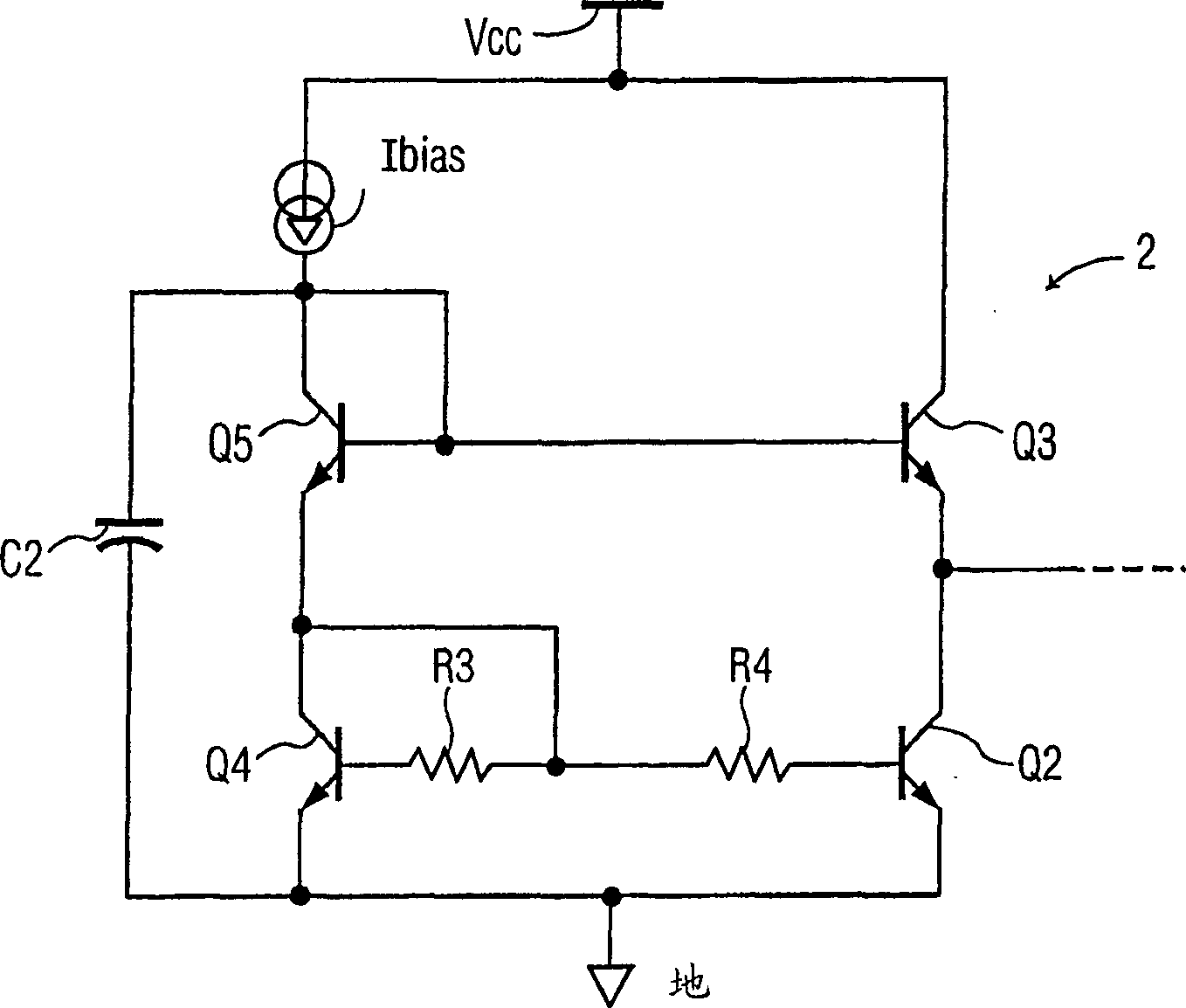

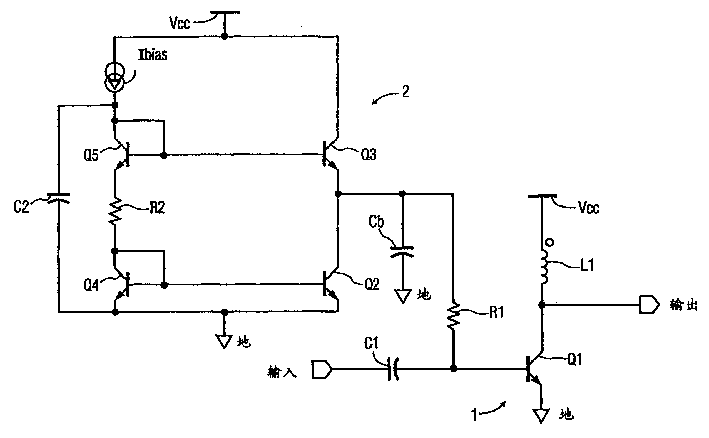

Power amplifier having a cascode current-mirror self-bias boosting circuit

InactiveCN1550063AIncrease the maximum output powerReduce noise levelAmplifier modifications to reduce temperature/voltage variationPower amplifiersAudio power amplifierCascode current mirror

A power amplifier circuit includes an amplifying transistor and a dc bias circuit for biasing the amplifier transistor to obtain a conduction angle of at least about 180 DEG . The dc bias circuit includes a self-bias boosting circuit which has a cascode current-mirror circuit having an output coupled to a control terminal of the amplifying transistor by a resistor, and a capacitor coupled from the cascode current-mirror circuit to a common terminal. The value of the capacitor can be selected to obtain the desired amount of self-bias boosting.

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV

Method of equalizing currents in transistors and floating current source

ActiveUS10560058B1Wide input-output voltage spanReduce voltagePush-pull amplifiersPhase-splittersLow noiseCascode current mirror

Methods, circuits, and apparatuses that provide Buffer Amplifier, containing Amplifiers and Buffer Drivers, one or more of the following: ultra low power Buffer Amplifier, capable of having high gain, low noise, high speed, near rail-to-rail input-output voltage span, high sink-source current drive capability for an external load, and able to operate at low power supply voltages. Methods, circuits, and apparatuses that provide regulated cascode (RGC) current mirrors (CM) capable of operating at low power supply and having wide input-output voltage spans.

Owner:FAR ALI TASDIGHI