All-CMOS (Complementary Metal Oxide Semiconductor) based reference voltage source with high power supply rejection ratio

A high power supply rejection ratio, reference voltage source technology, applied in the direction of adjusting electrical variables, control/regulation systems, instruments, etc., can solve the problems of large reference voltage source layout area, low power supply suppression, high power consumption, etc., to achieve low power consumption , low power supply voltage adjustment rate, and the effect of reducing production costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0016] Below in conjunction with accompanying drawing and embodiment, describe technical solution of the present invention in detail:

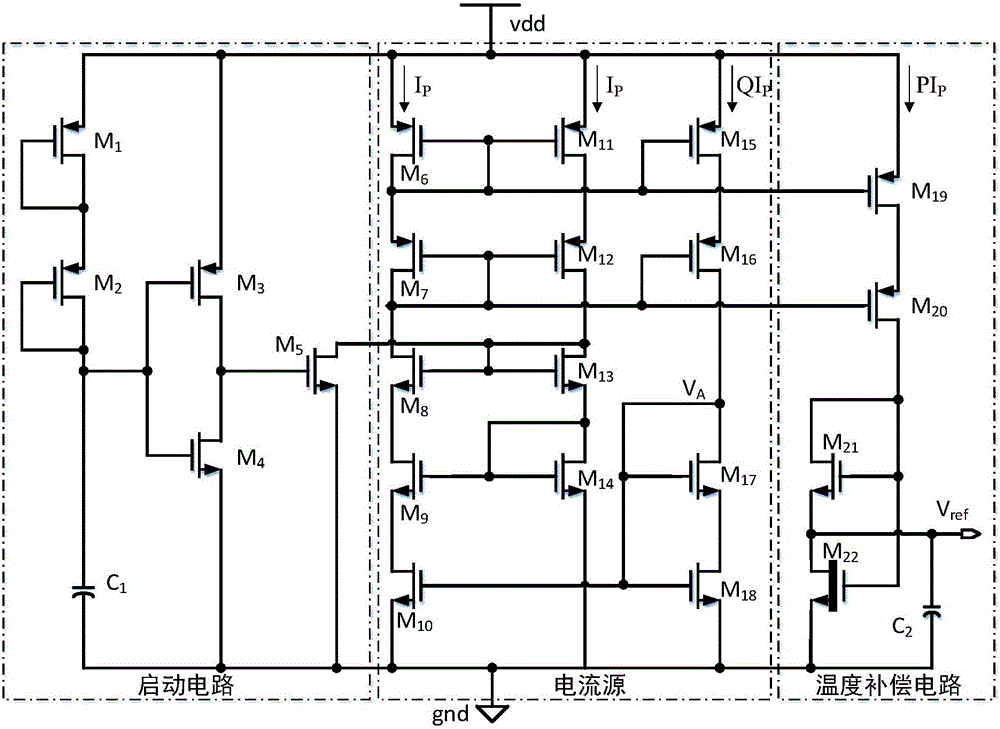

[0017] A high power supply rejection ratio full CMOS voltage reference, such as figure 1 Shown, including start-up circuit, current source and temperature compensation circuit. The output terminal of the start-up circuit is connected to the input terminal of the current source circuit, the output terminal of the current source circuit is connected to the input terminal of the temperature compensation circuit, and the output terminal of the temperature compensation circuit forms the output terminal V of the entire reference voltage source. ref .

[0018] The start-up circuit provides current when the reference voltage source is turned on, so that the reference voltage source gets rid of the degenerate bias point and enters a normal working state. In a preferred embodiment of the present invention, the above startup circuit includes a PMOS tra...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More