Capacitance multiplier with high multiplication constant

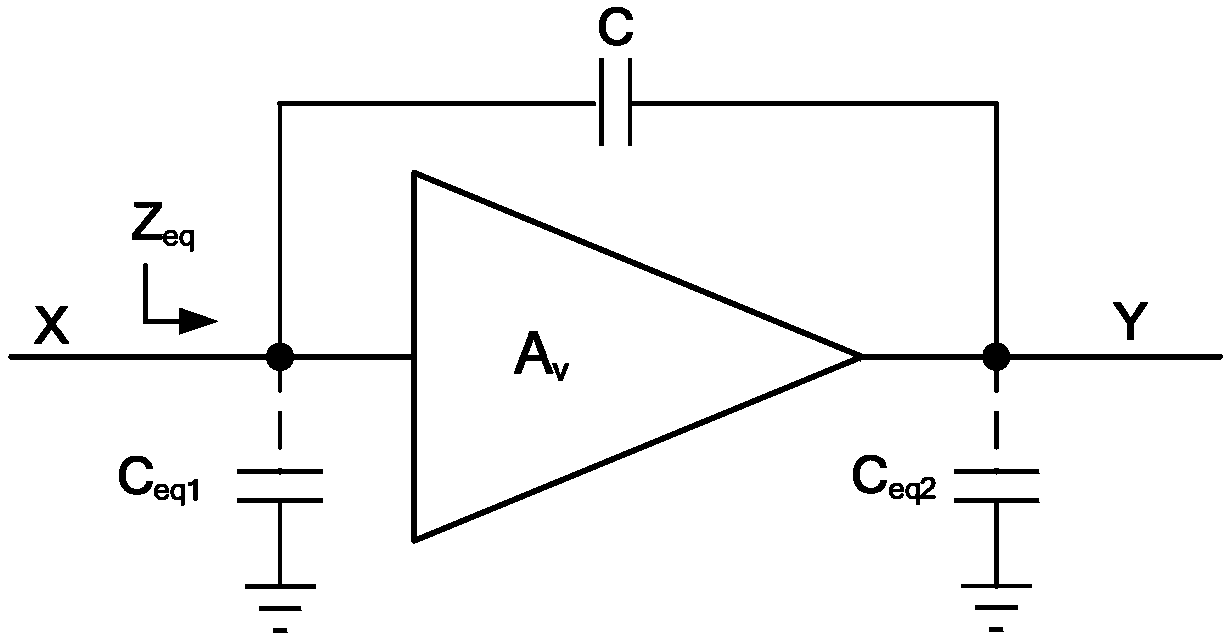

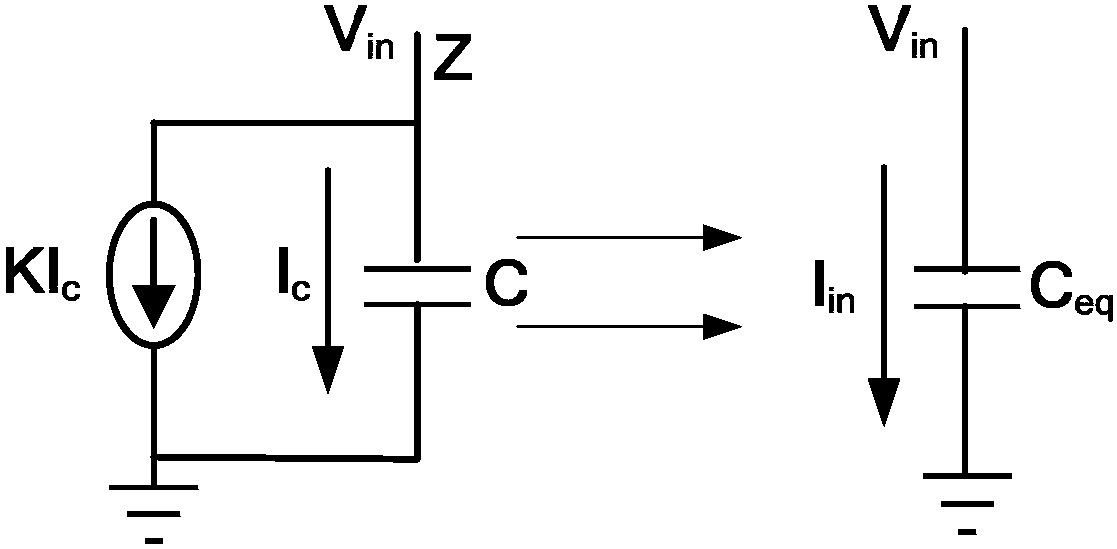

A multiplication factor and capacitance multiplication technology, applied in electrical components, networks using active components, impedance networks, etc., can solve the problems of increased circuit power consumption, inappropriate capacitance multipliers, etc., to improve the multiplication factor and high multiplication factor. , the effect of small area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

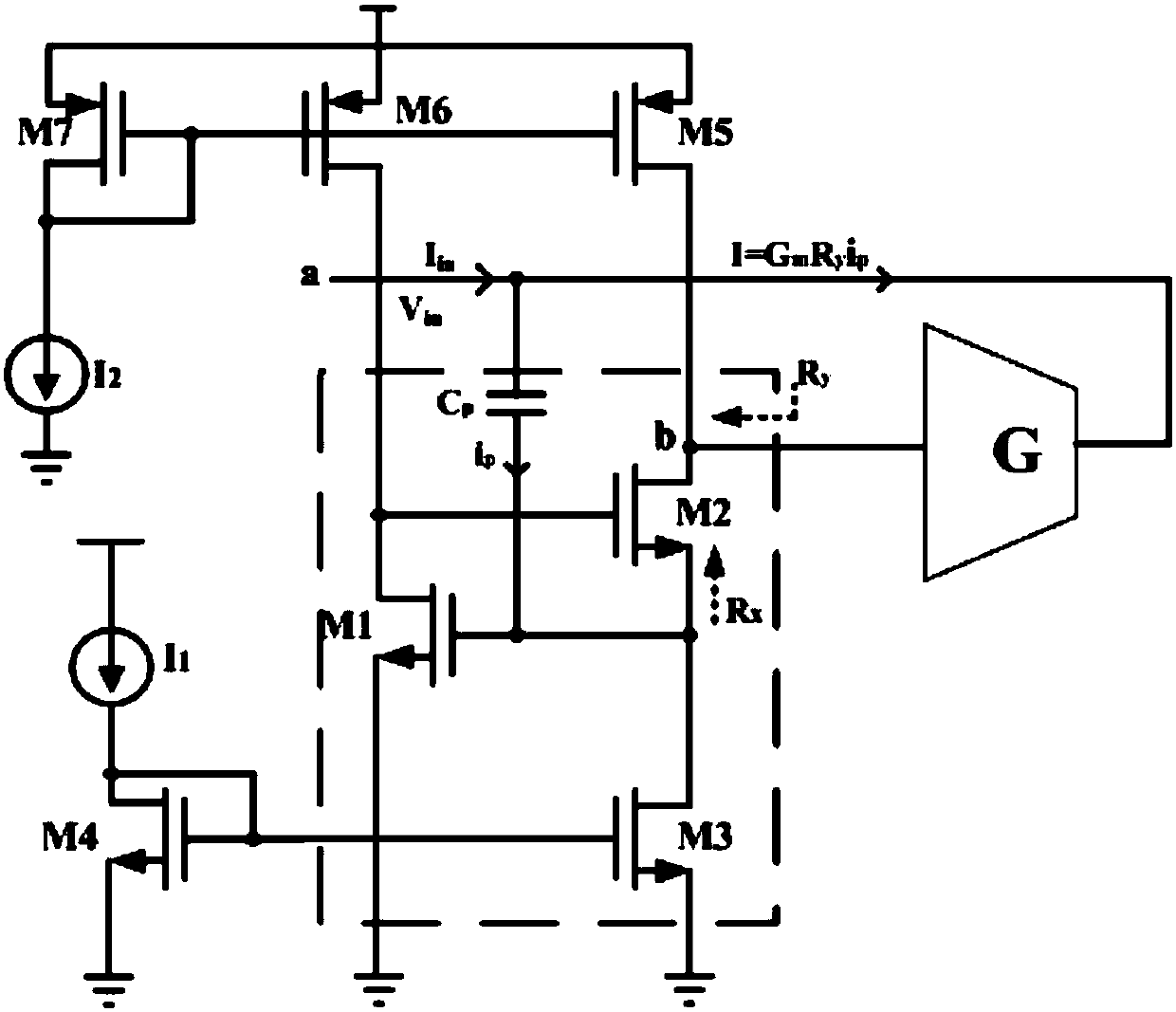

[0026] Below in conjunction with embodiment the present invention is described in further detail.

[0027] The capacitance multiplier with high multiplication factor of the embodiment, as shown in the figure, includes a first cascode circuit module, a second cascode circuit module, a transconductance amplifier circuit module G, and an on-chip capacitor C p , the first bias current source I 1 , the second bias current source I 2 and a third bias current source I 3 , the transconductance amplifier circuit module G is provided with a first input terminal and a second input terminal, the first input terminal is connected with the output terminal of the first cascode circuit module, and the second input terminal is connected with the second cascode circuit module The output terminal of the module is connected, the output terminal of the transconductance amplifier circuit module G is connected to the on-chip capacitor C p connect;

[0028] The first cascode circuit module includ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More