Patents

Literature

30results about How to "Increase effective capacitance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

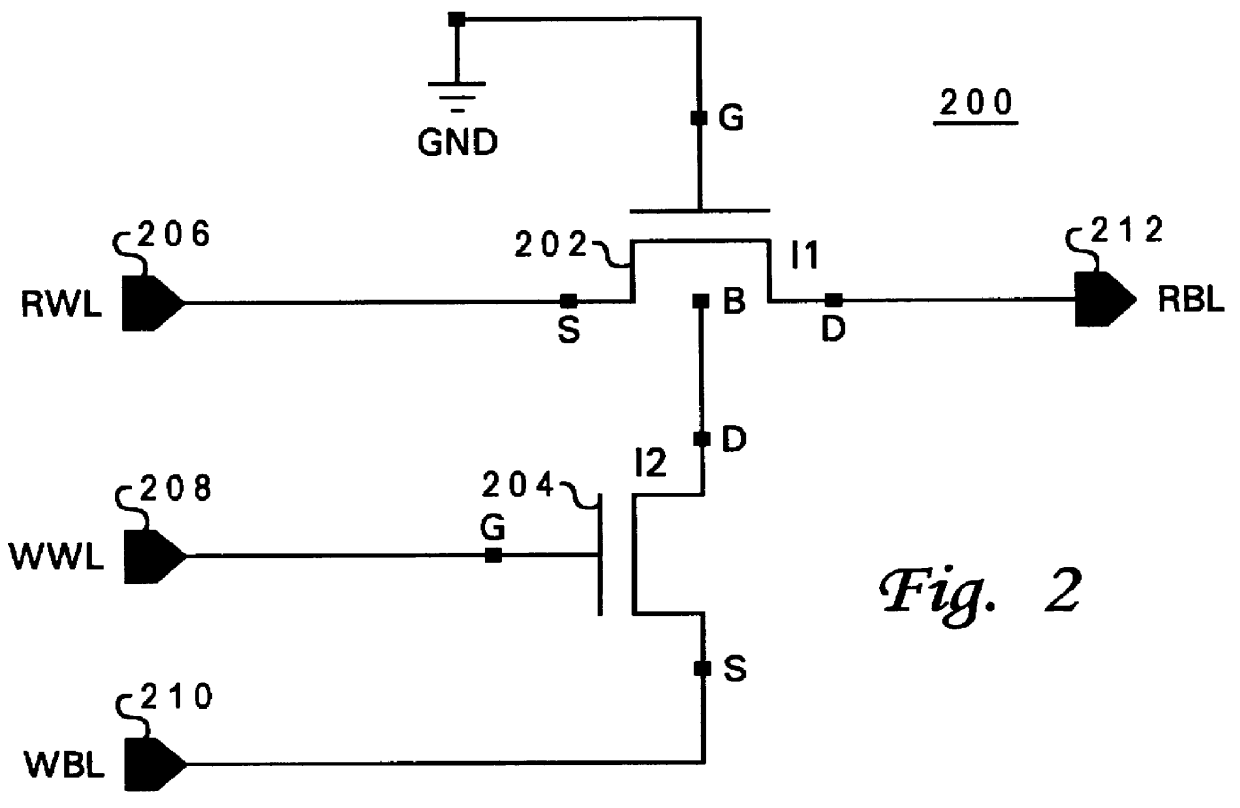

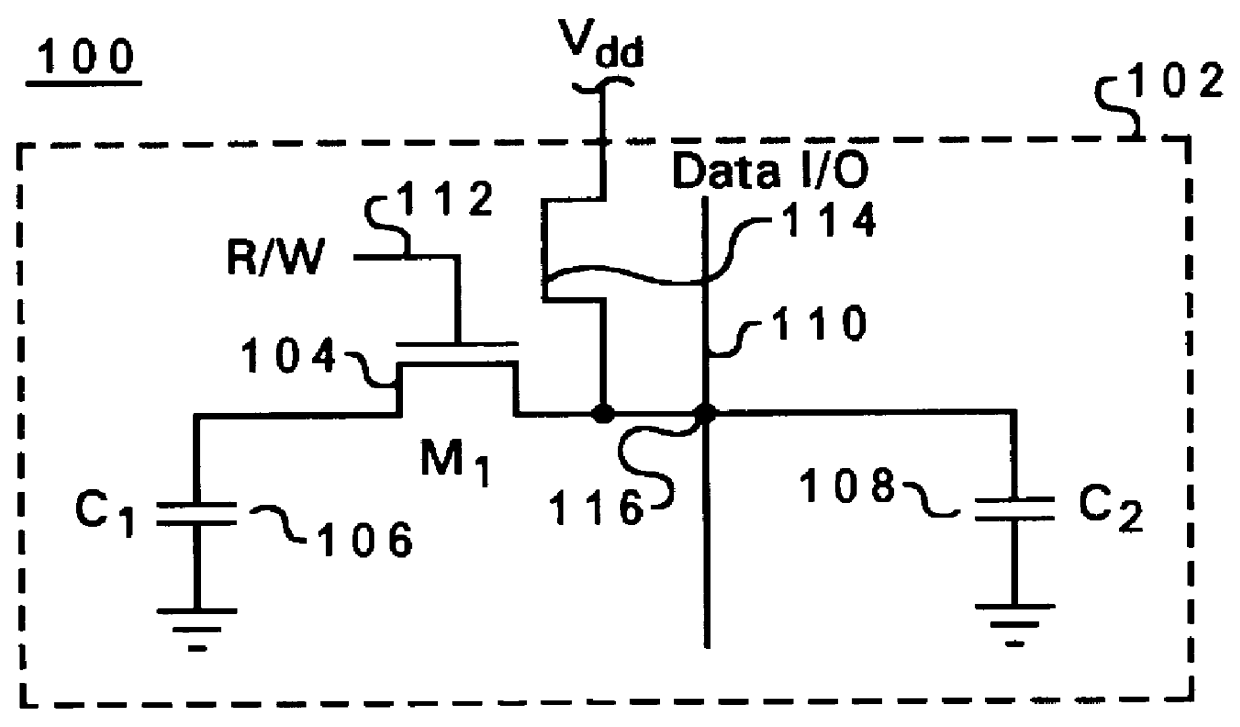

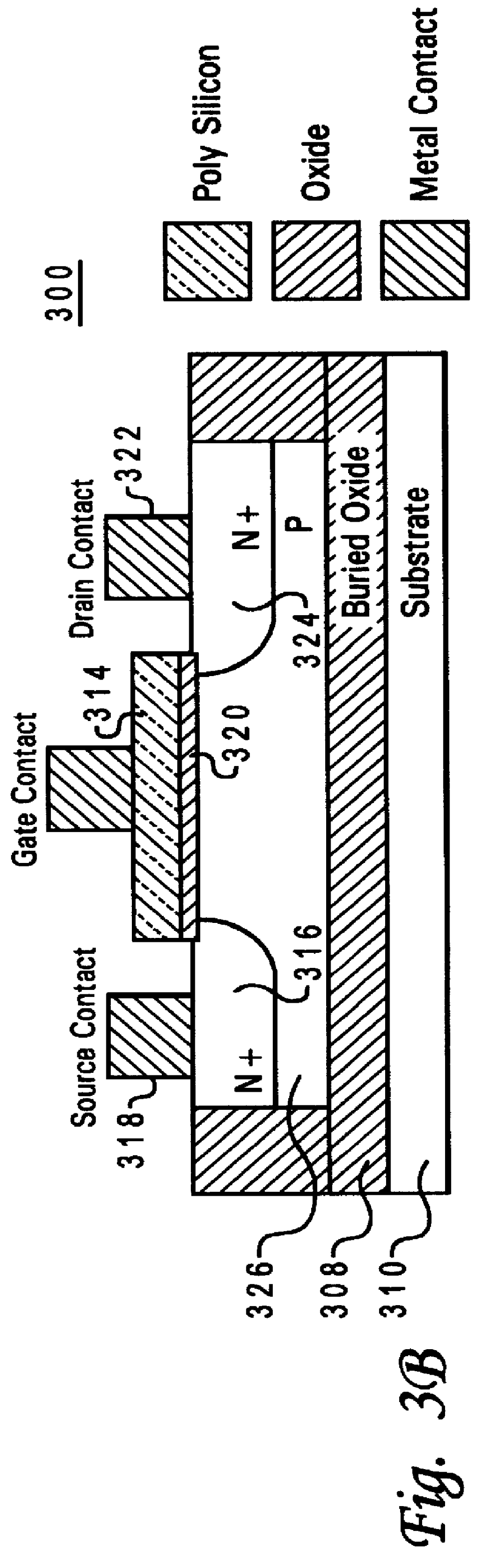

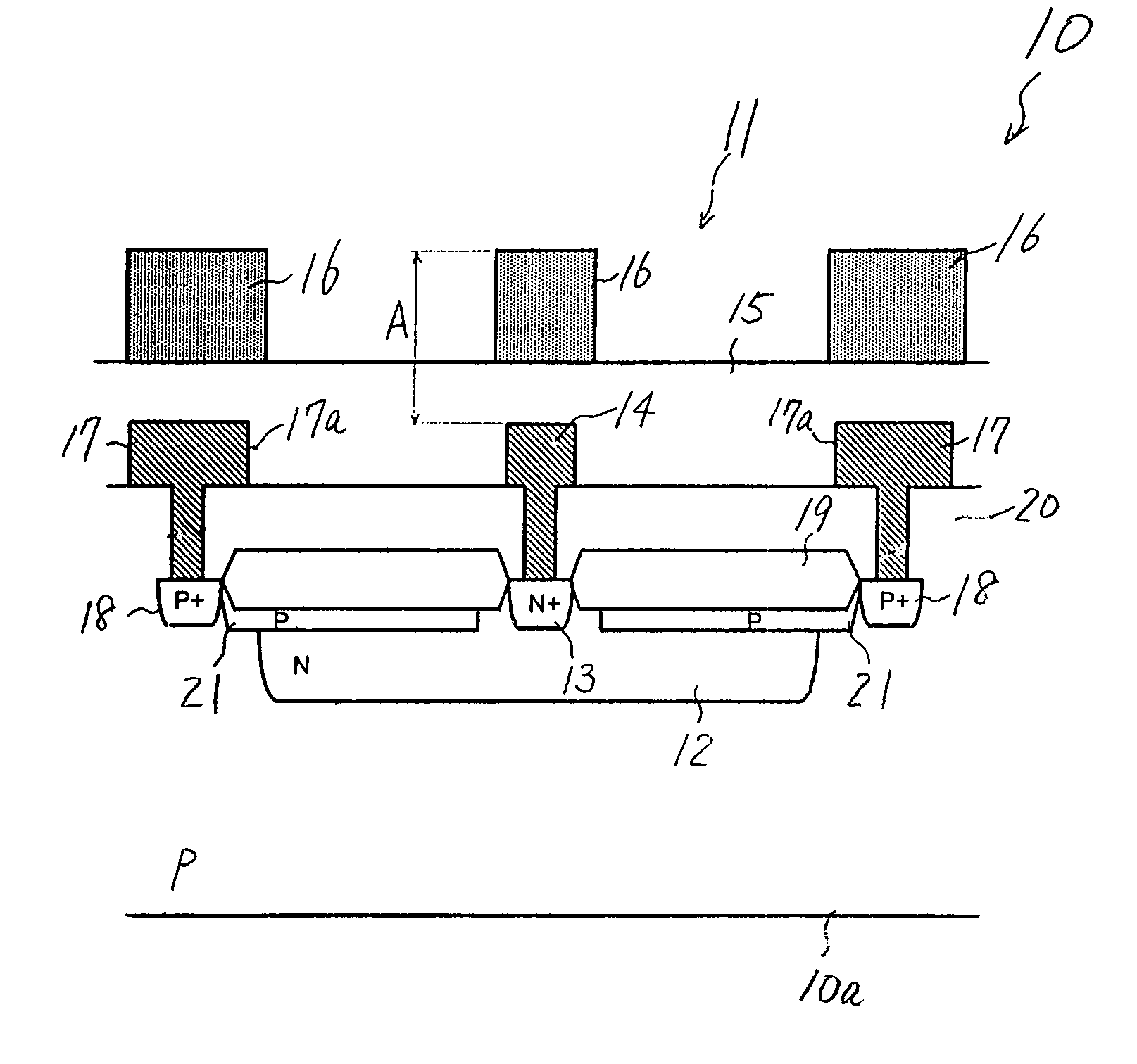

Body contacted dynamic memory

InactiveUS6111778AEfficiently store and retrieveIncreases magnitudeTransistorSolid-state devicesBody contactMemory circuits

A dynamic memory circuit in which the inherent bipolar transistor effect within a floating body transistor is utilized to store an information bit. A floating body of a storage transistor stores an information bit in the form of an electric charge. The floating body is charged and discharged via an access transistor during data write operations. The inherent bipolar transistor resident within the floating body transistor increases the effective capacitance of the floating body which acts as the storage node, and thereby enhances the magnitude of the discharge current which represents the stored information bit during read operations.

Owner:IBM CORP

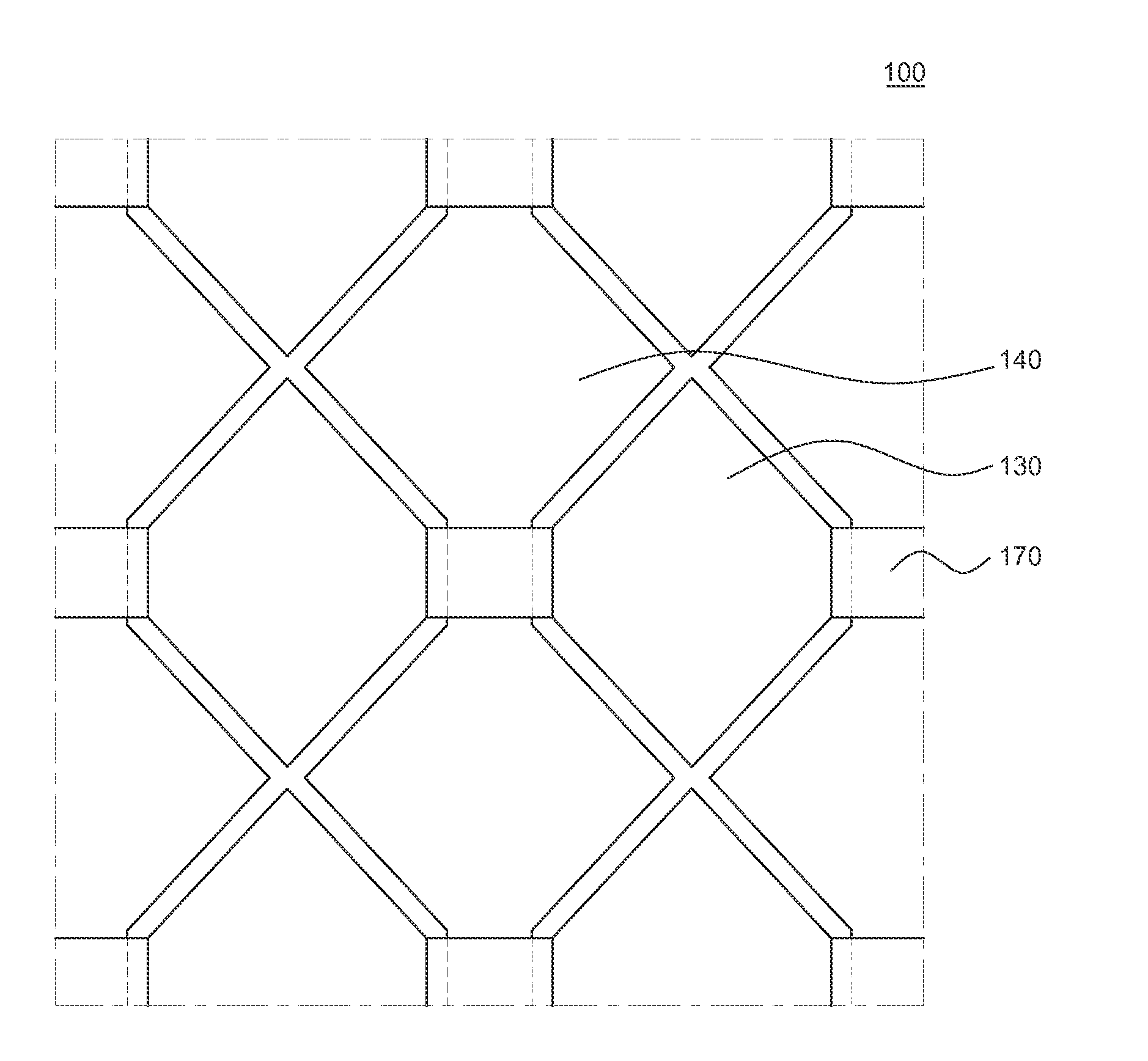

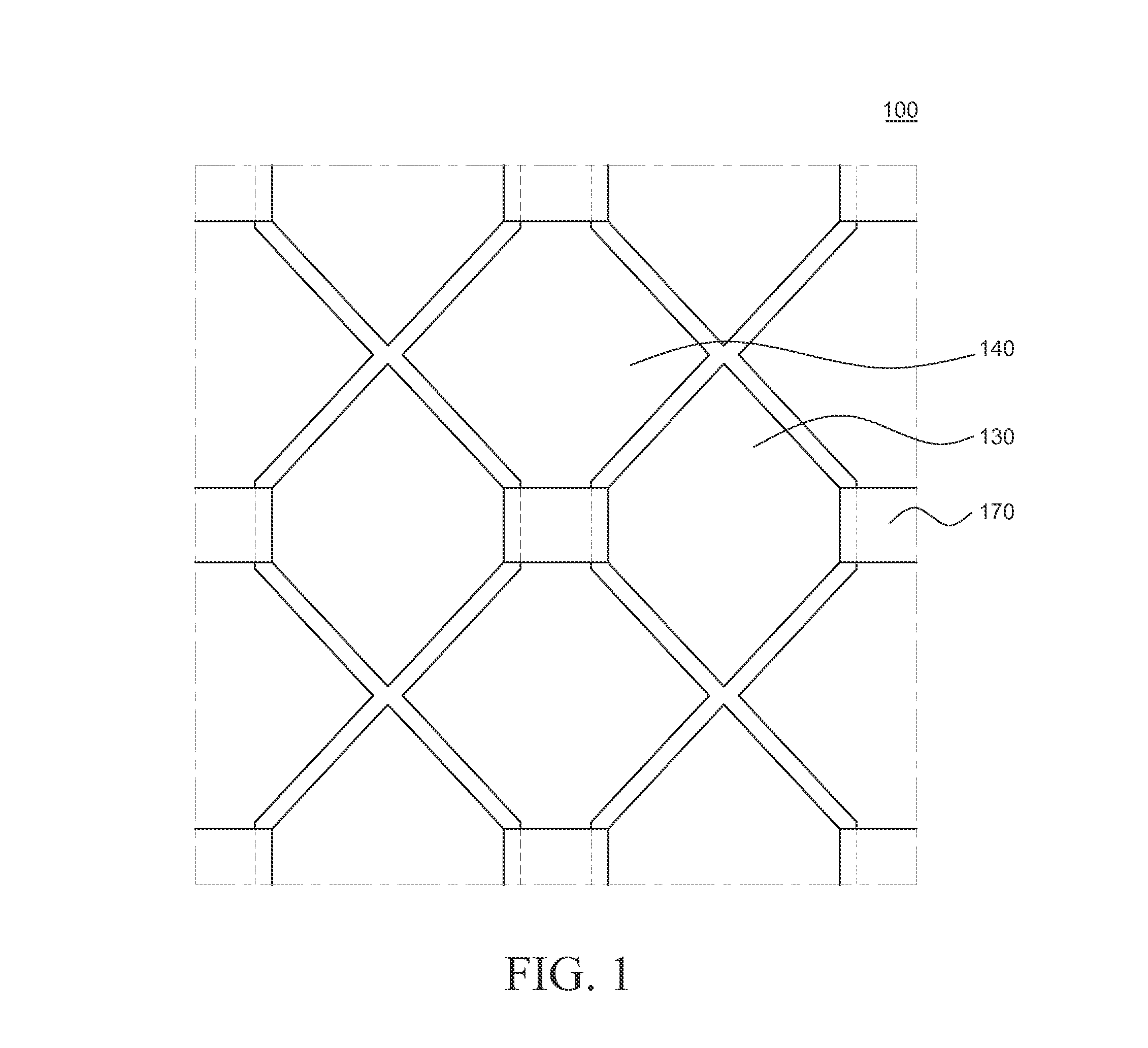

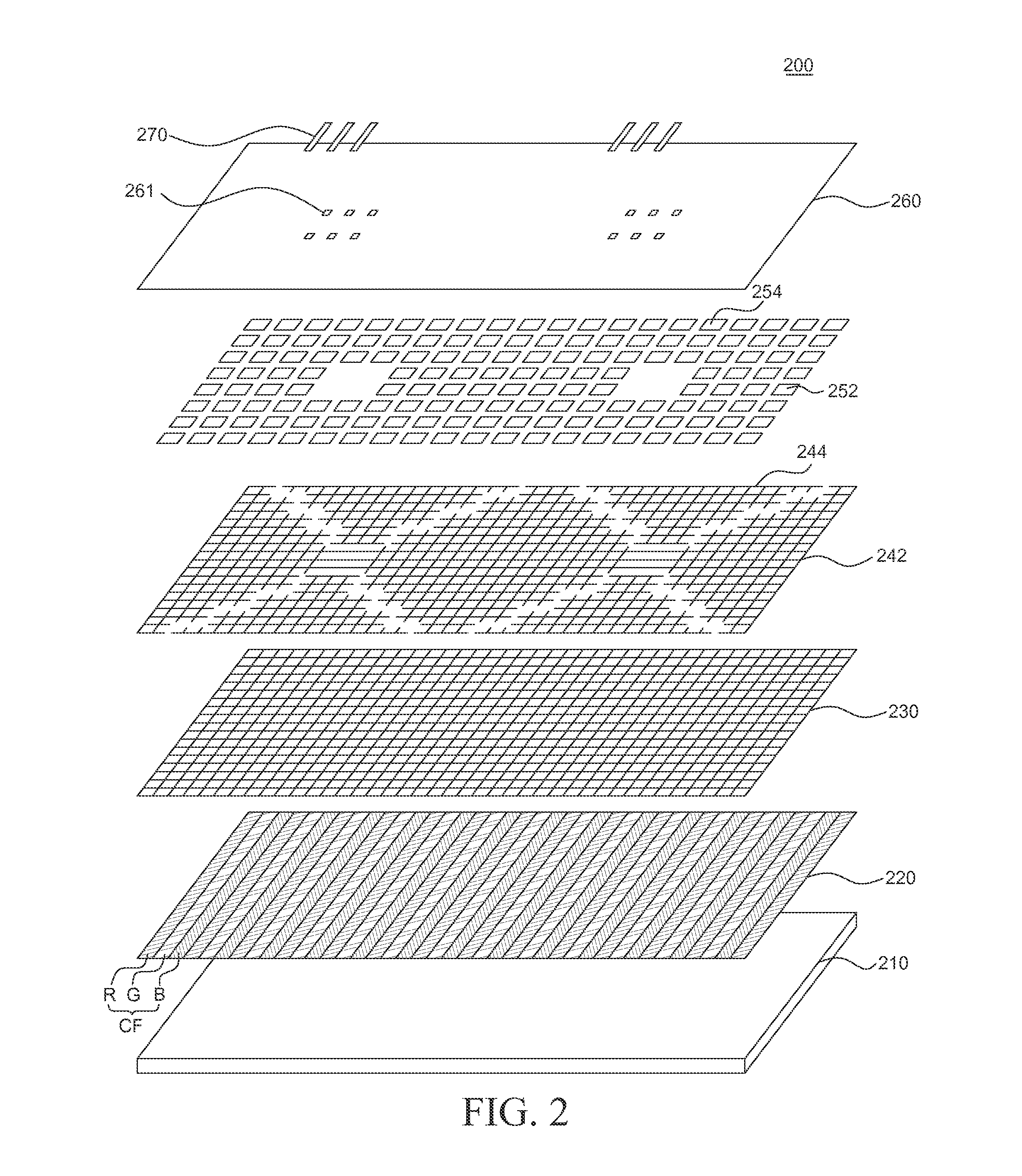

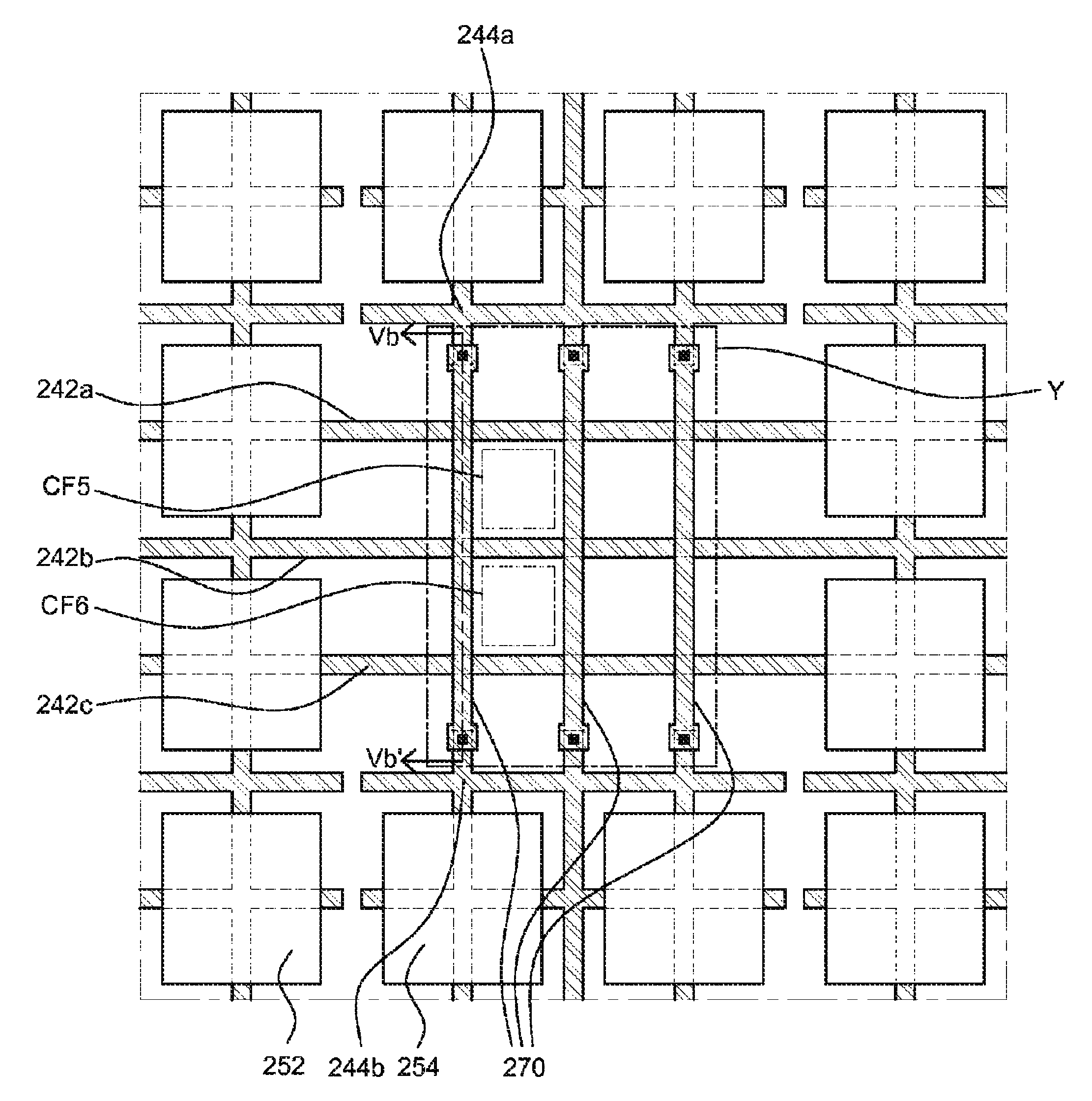

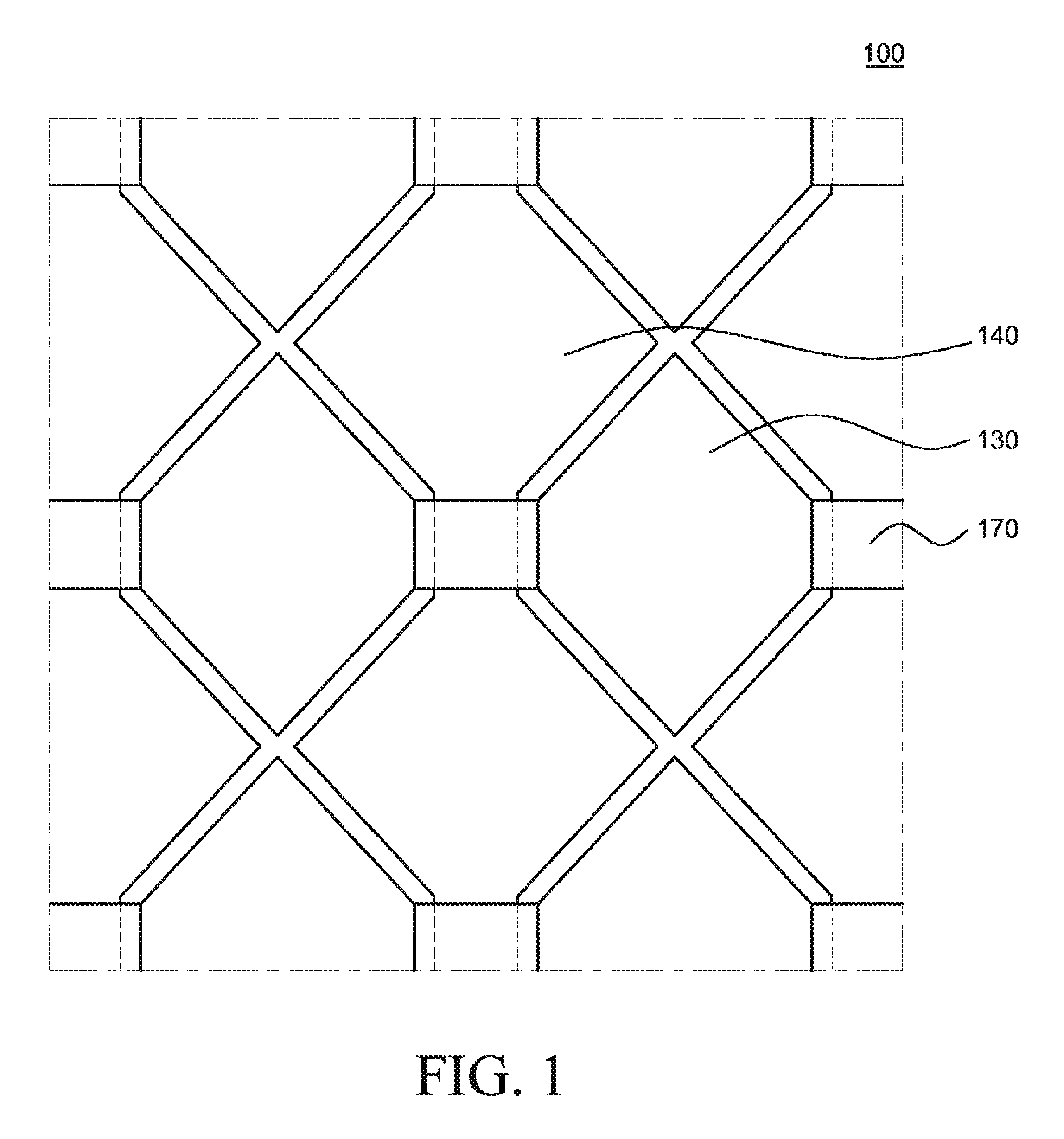

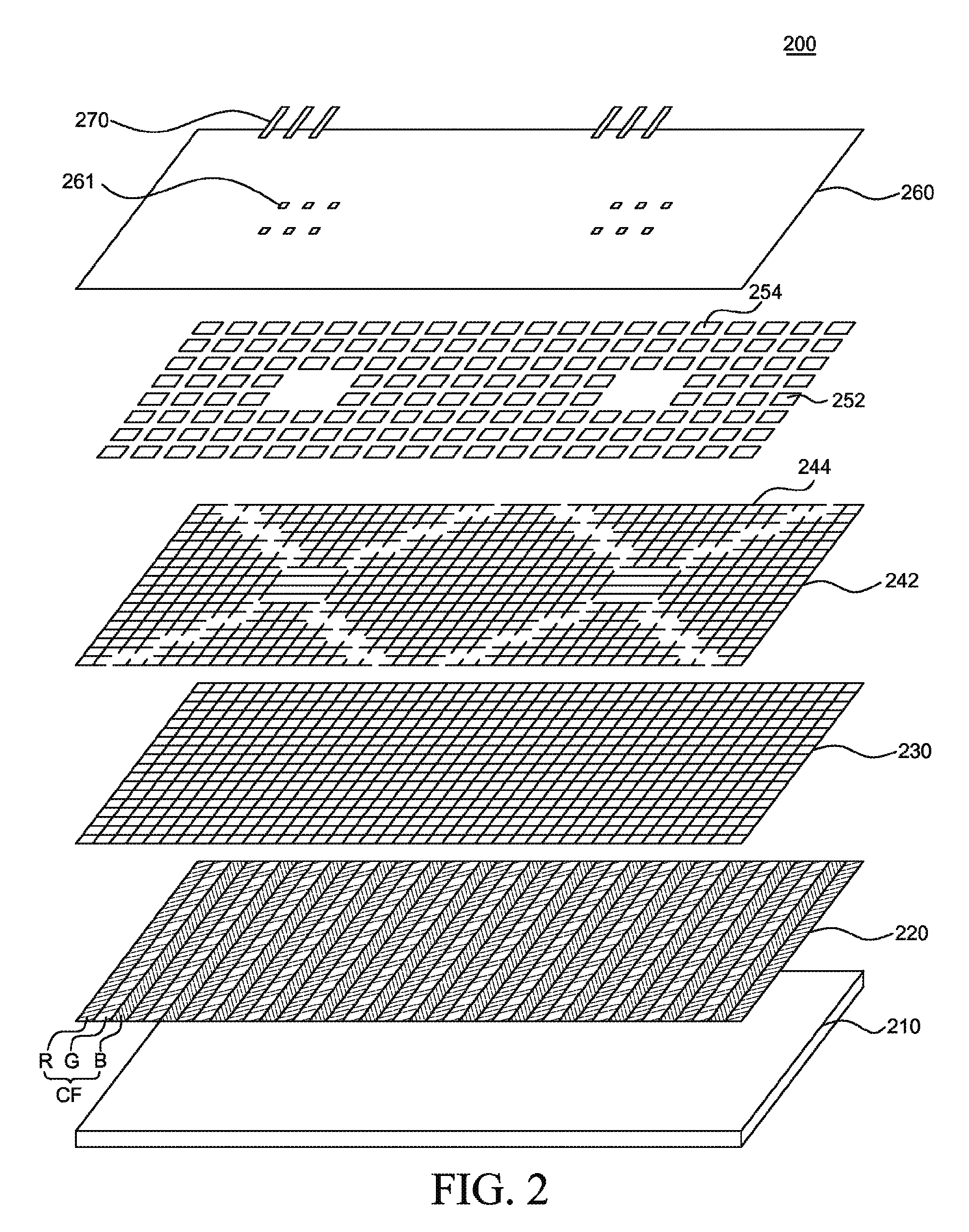

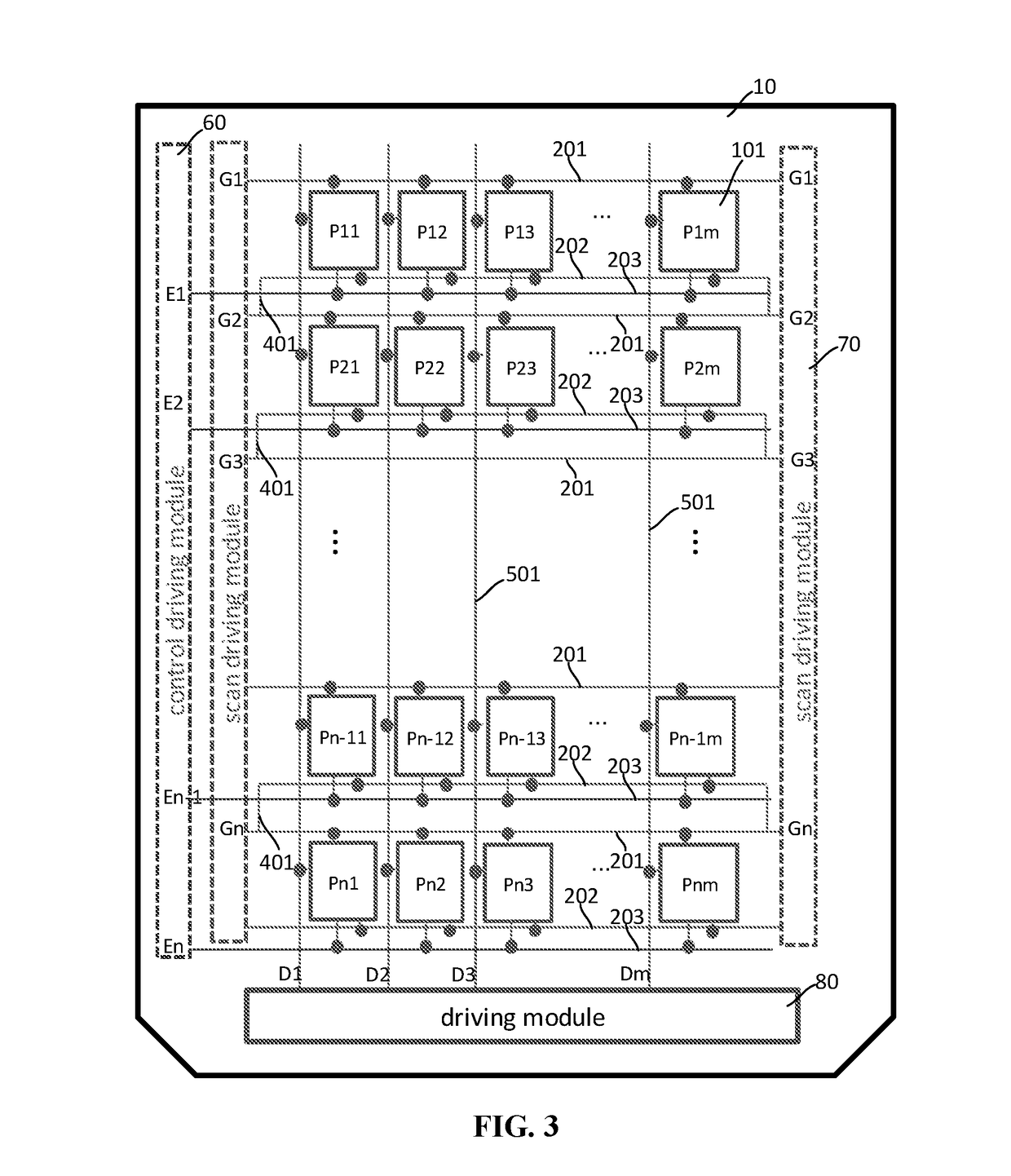

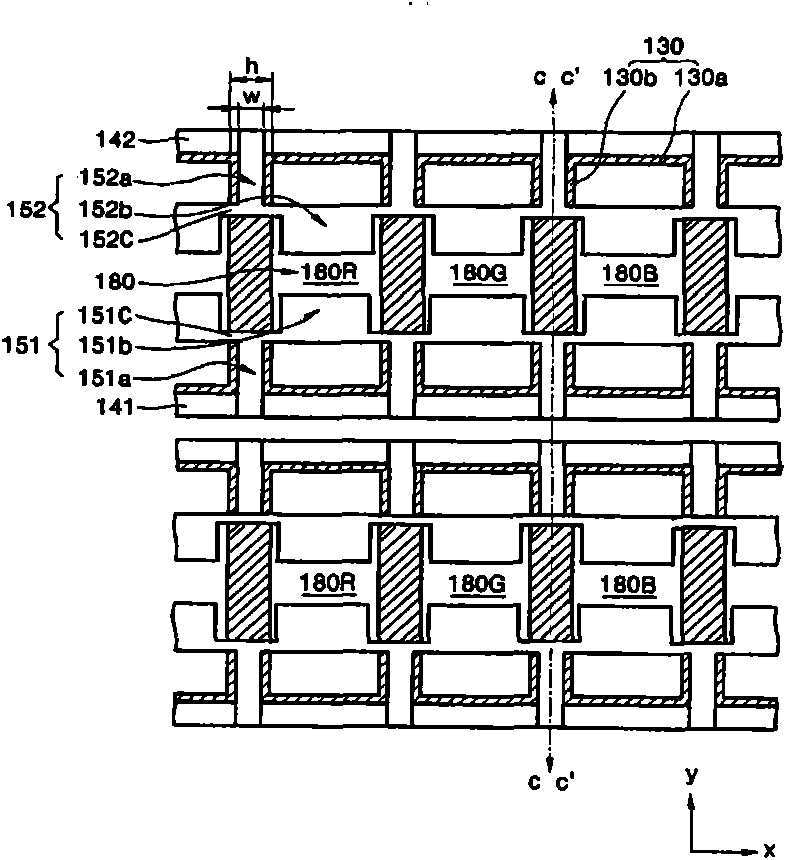

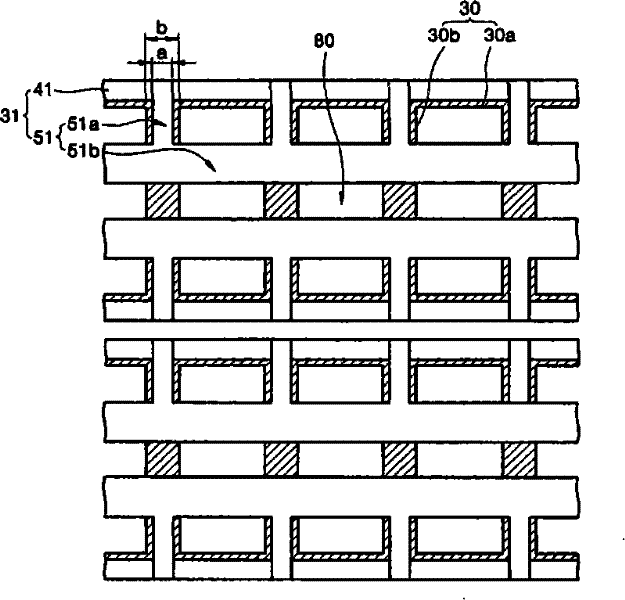

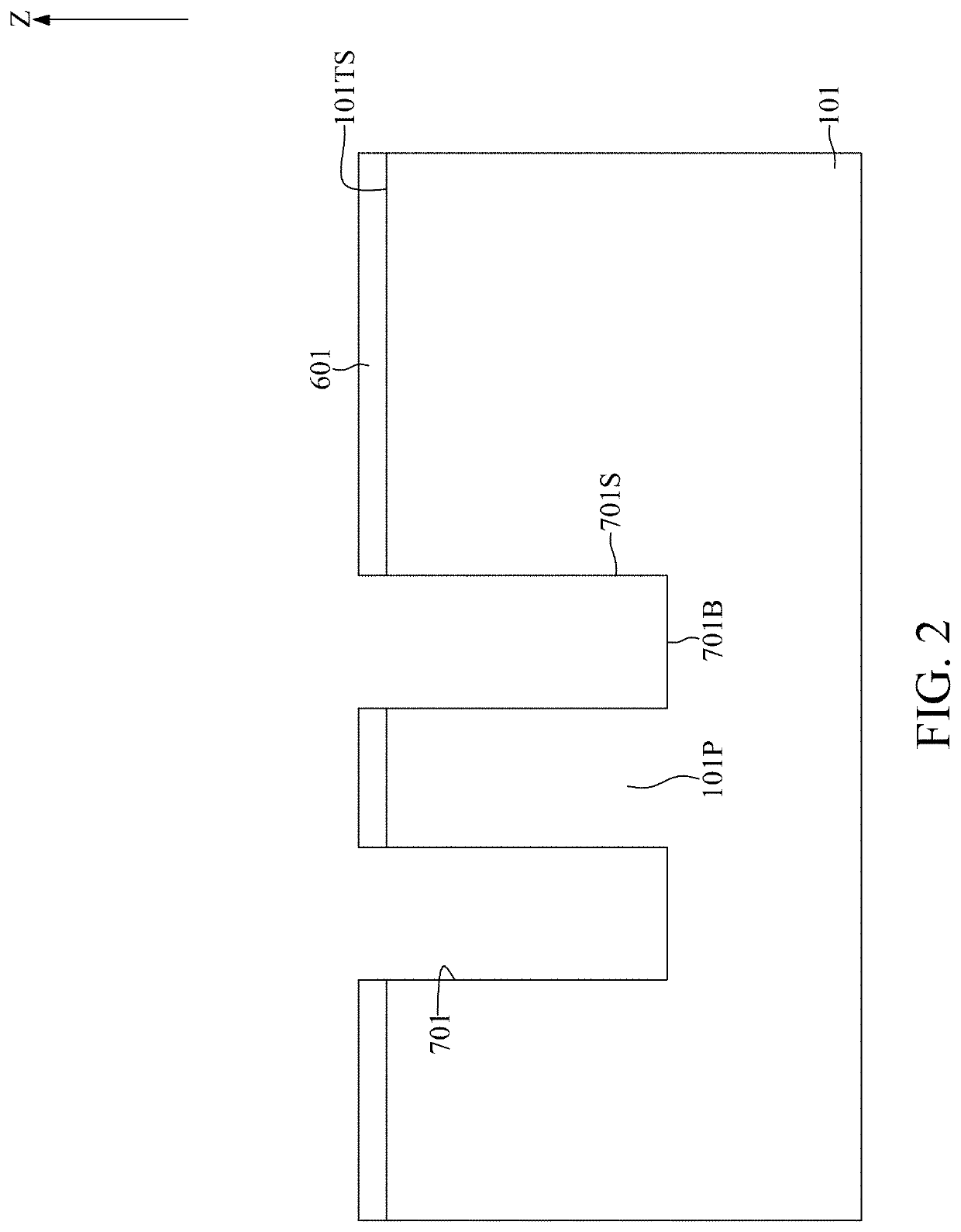

Touch screen panel and touch screen-integrated display device

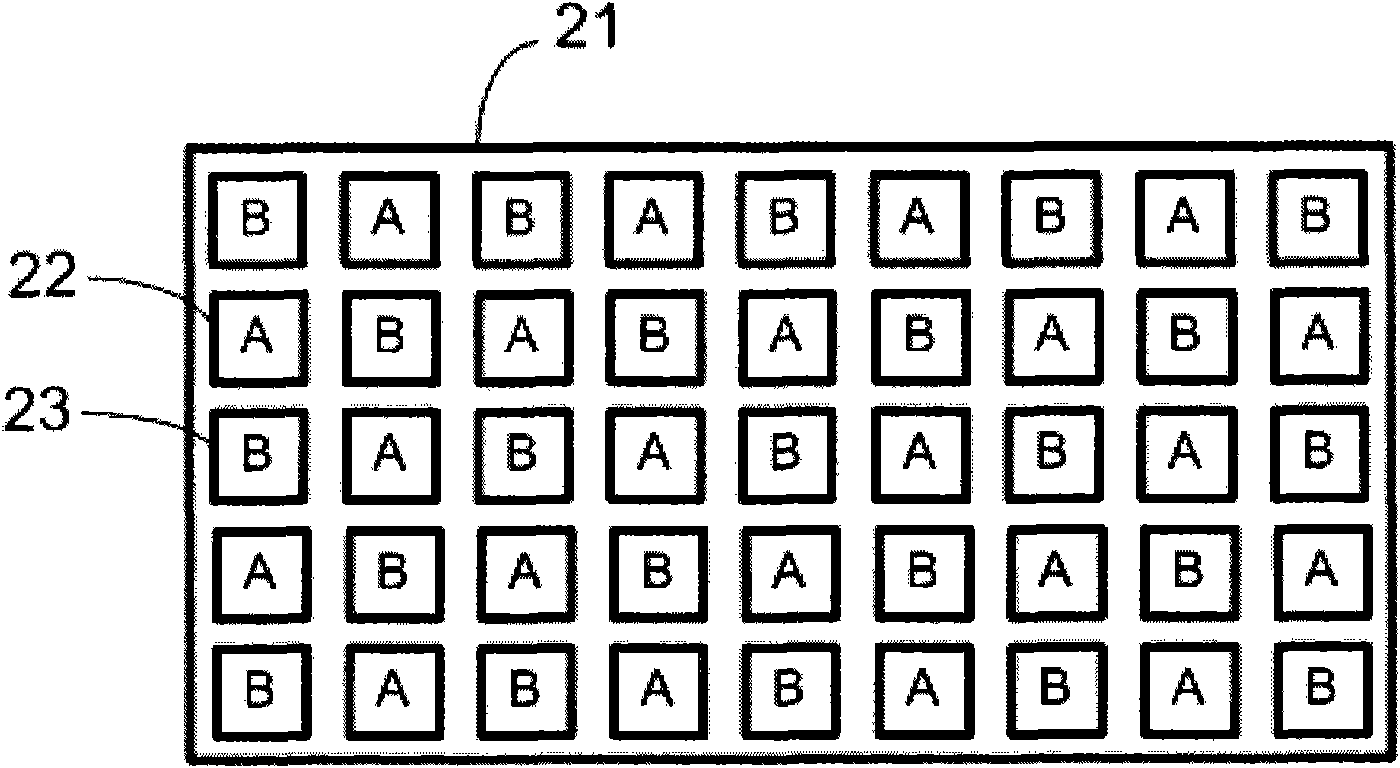

ActiveUS20160070406A1Increase flexibilitySufficient capacitance areaElectric switchesSelector switchesDisplay deviceEngineering

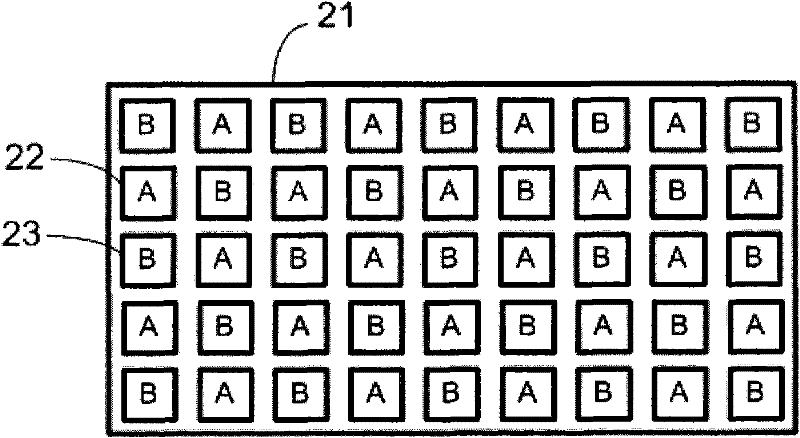

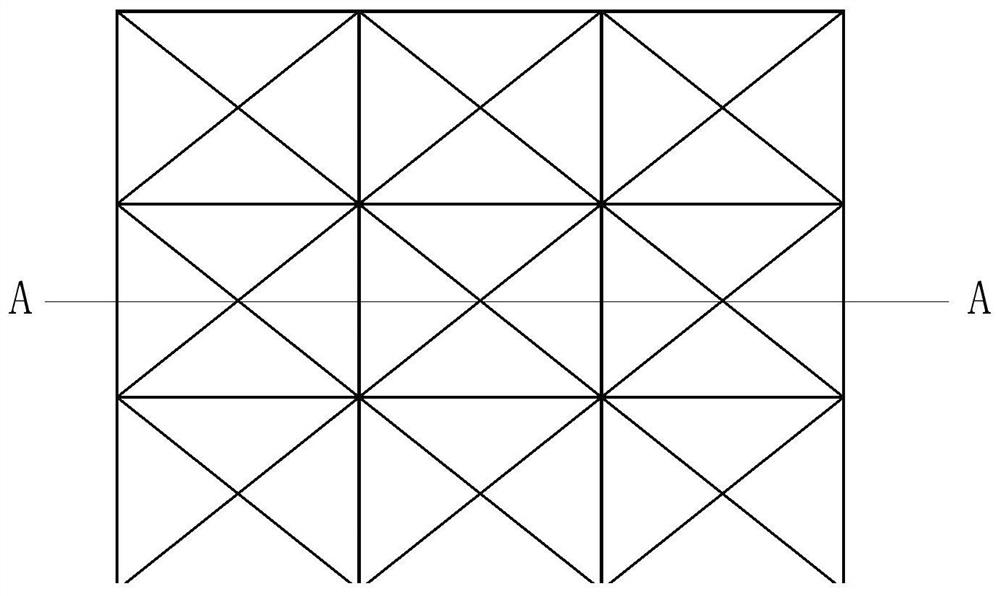

Discussed is a touch screen panel including: a substrate; a first line electrode in a mesh pattern on the substrate; a plurality of first segment electrodes disposed on the first line electrode; a second line electrode in a mesh pattern on the substrate, and disconnected in an intersection area where the second line electrode is to intersect the first line electrode; a plurality of second segment electrodes disposed on the second line electrode; and a plurality of connection electrodes that connect the disconnected second line electrode in the intersection area, wherein the first and second line electrodes reduce resistance, and the first and second segment electrodes increase effective capacitance for sensing a touch to thereby reduce an RC-delay in the touch screen panel.

Owner:LG DISPLAY CO LTD

Touch screen panel and touch screen-integrated display device

ActiveUS9459750B2Low RC-delayReduce resistanceStatic indicating devicesDigital data processing detailsDisplay deviceEngineering

Discussed is a touch screen panel including: a substrate; a first line electrode in a mesh pattern on the substrate; a plurality of first segment electrodes disposed on the first line electrode; a second line electrode in a mesh pattern on the substrate, and disconnected in an intersection area where the second line electrode is to intersect the first line electrode; a plurality of second segment electrodes disposed on the second line electrode; and a plurality of connection electrodes that connect the disconnected second line electrode in the intersection area, wherein the first and second line electrodes reduce resistance, and the first and second segment electrodes increase effective capacitance for sensing a touch to thereby reduce an RC-delay in the touch screen panel.

Owner:LG DISPLAY CO LTD

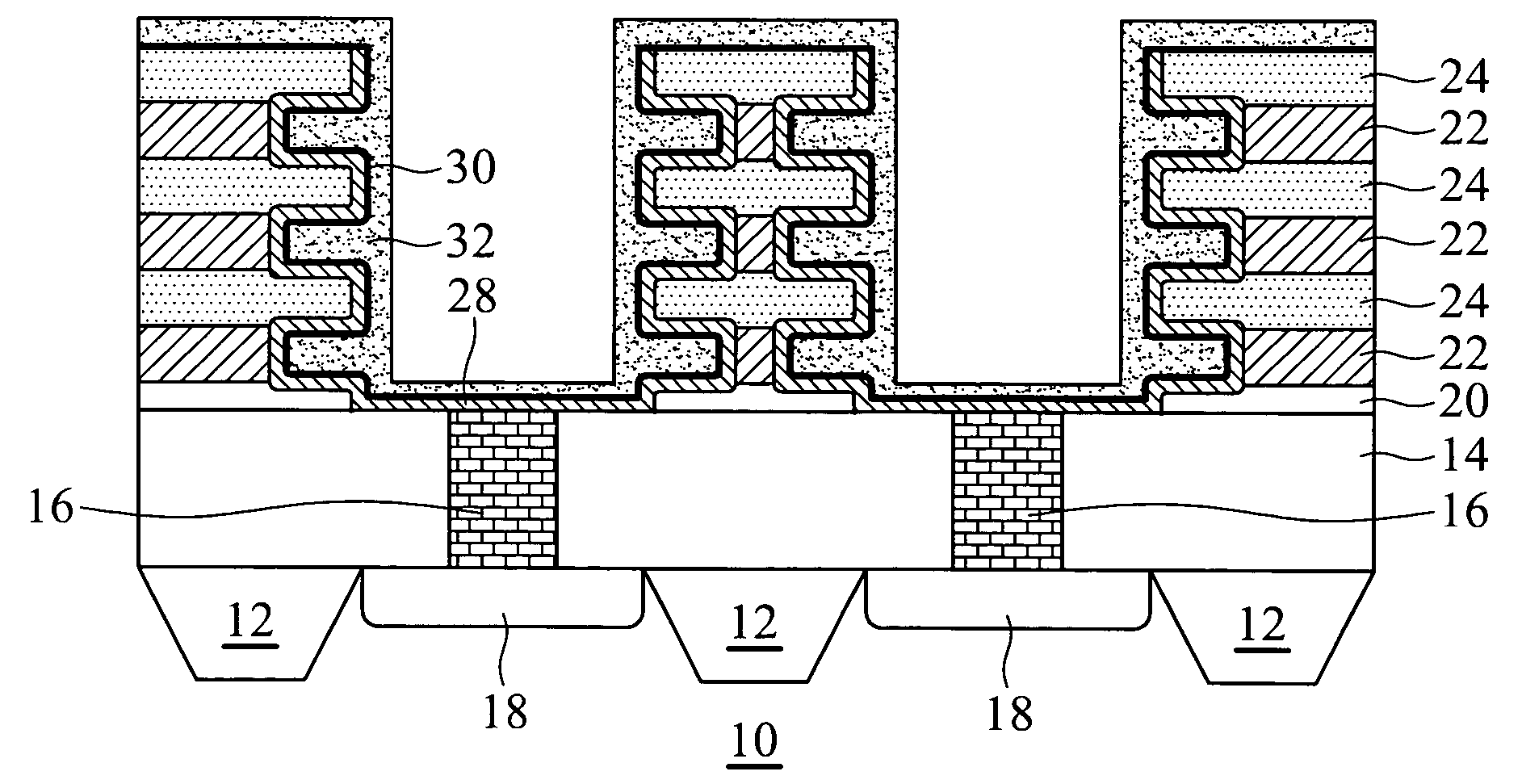

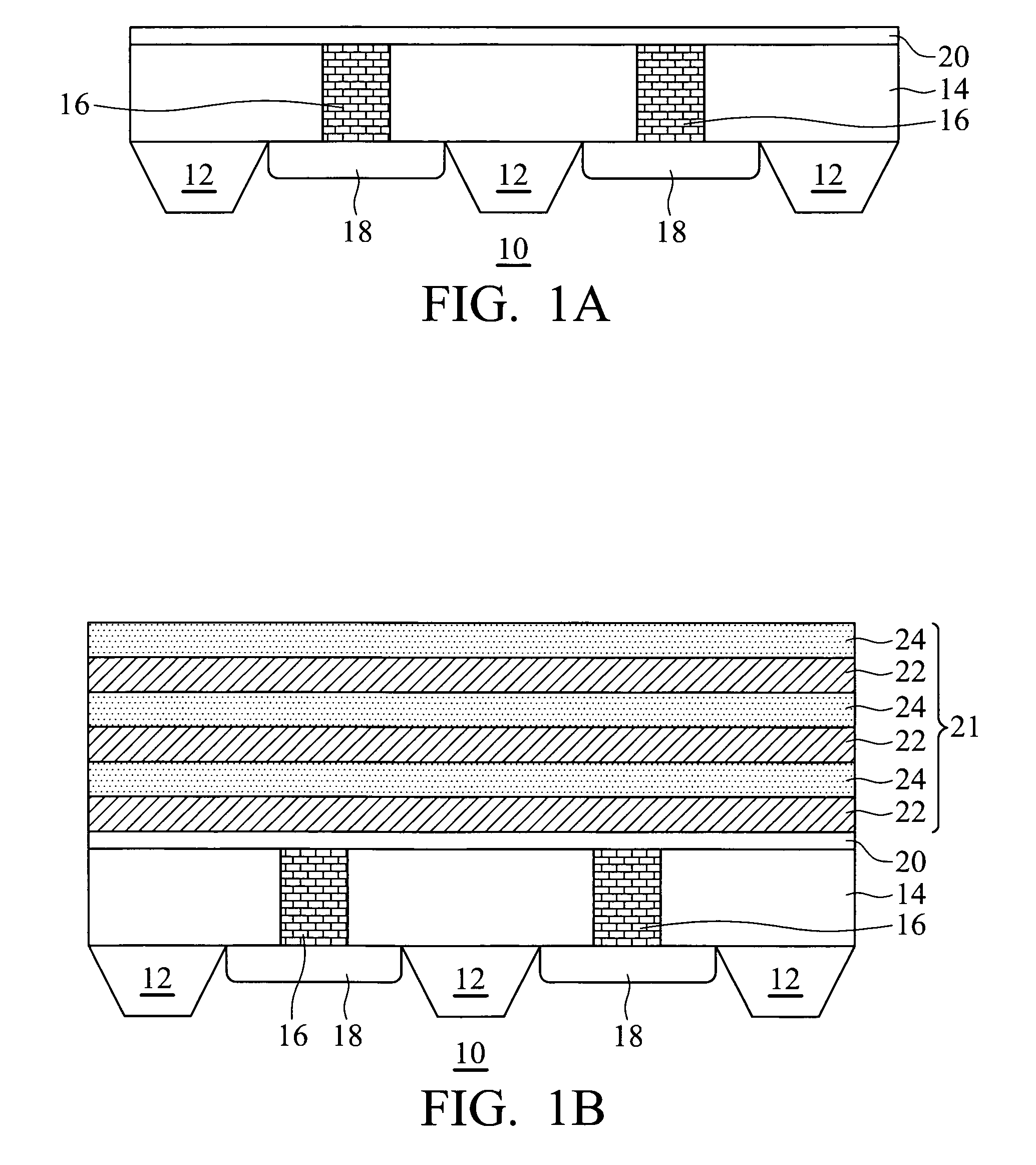

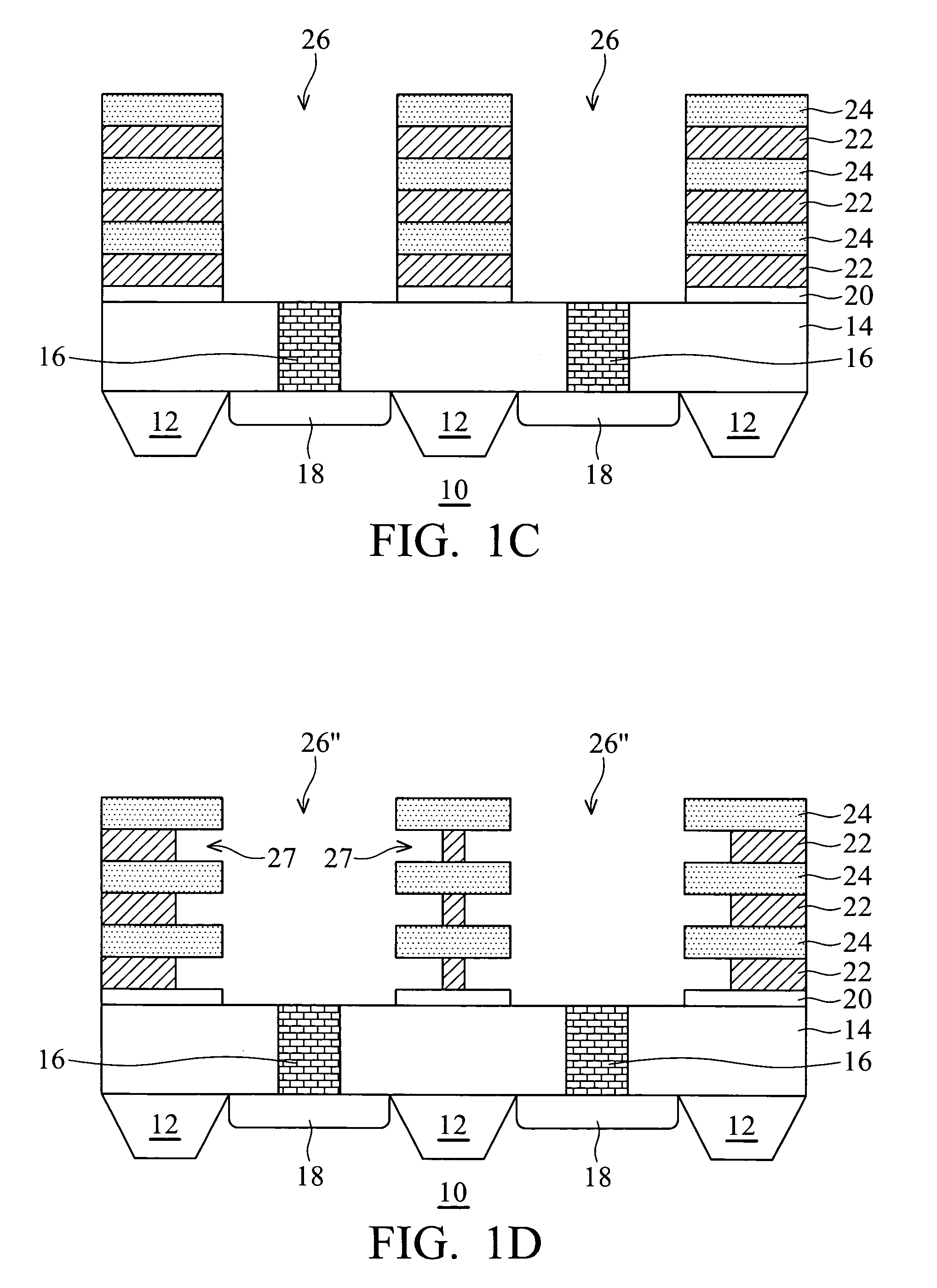

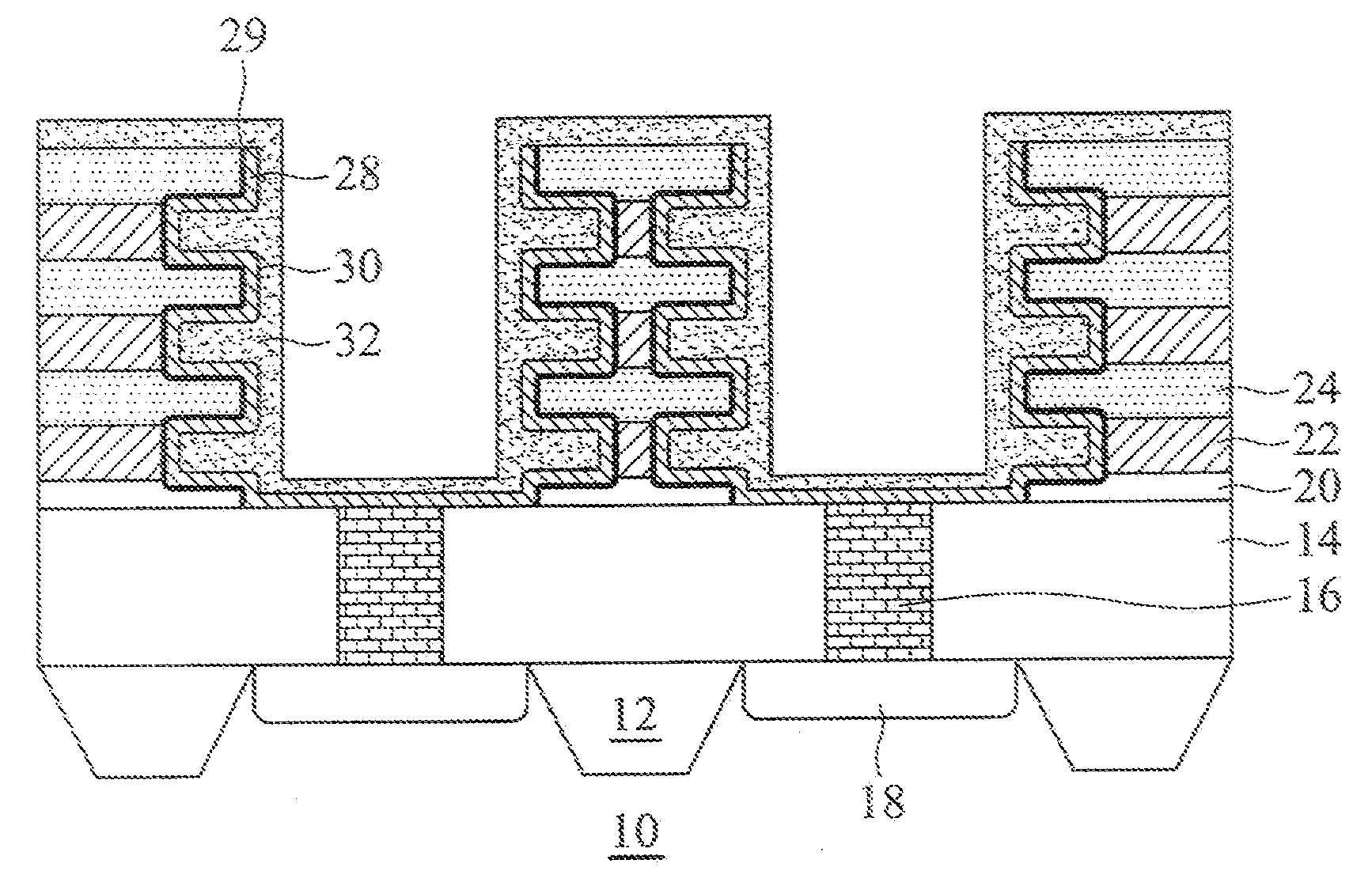

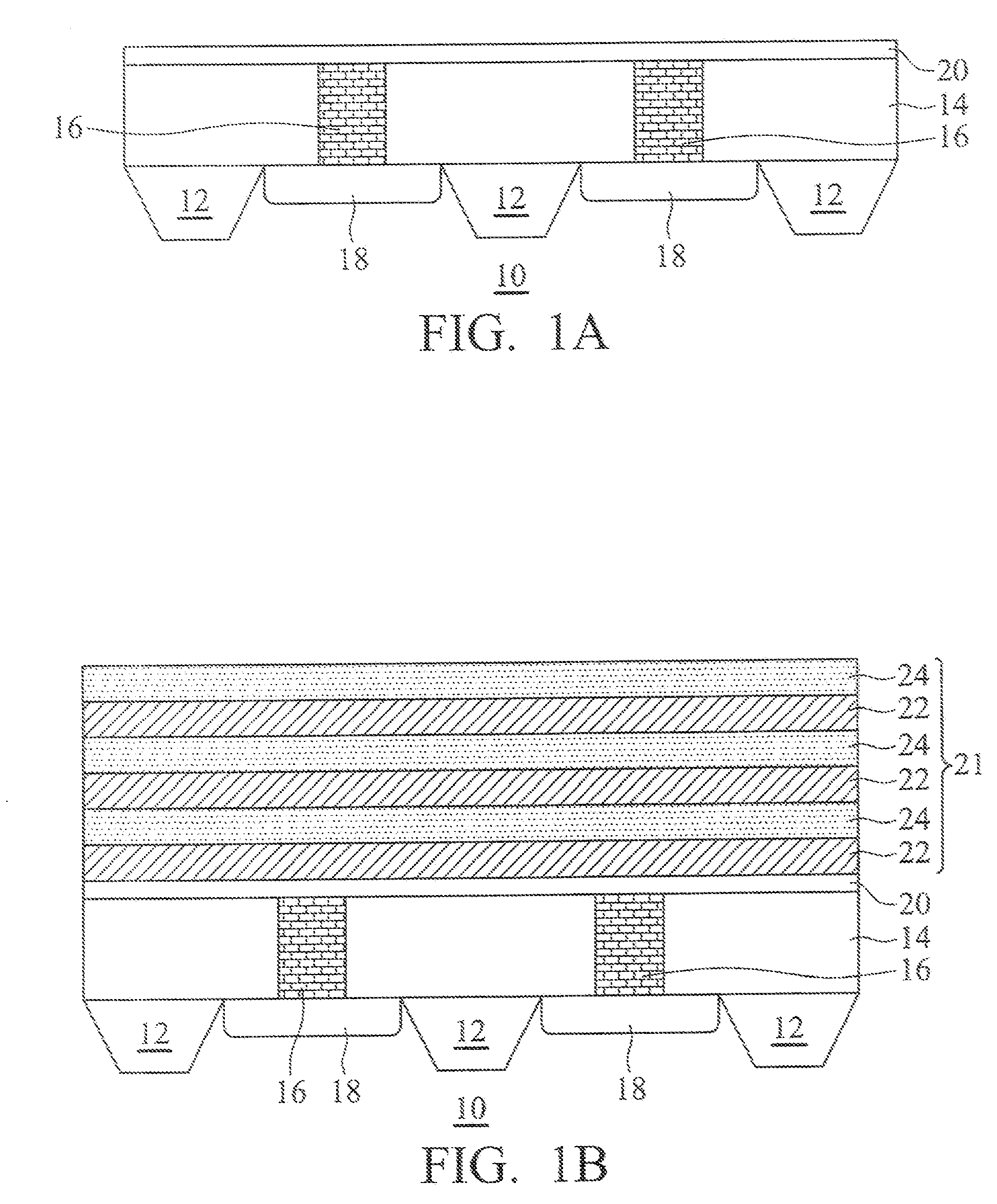

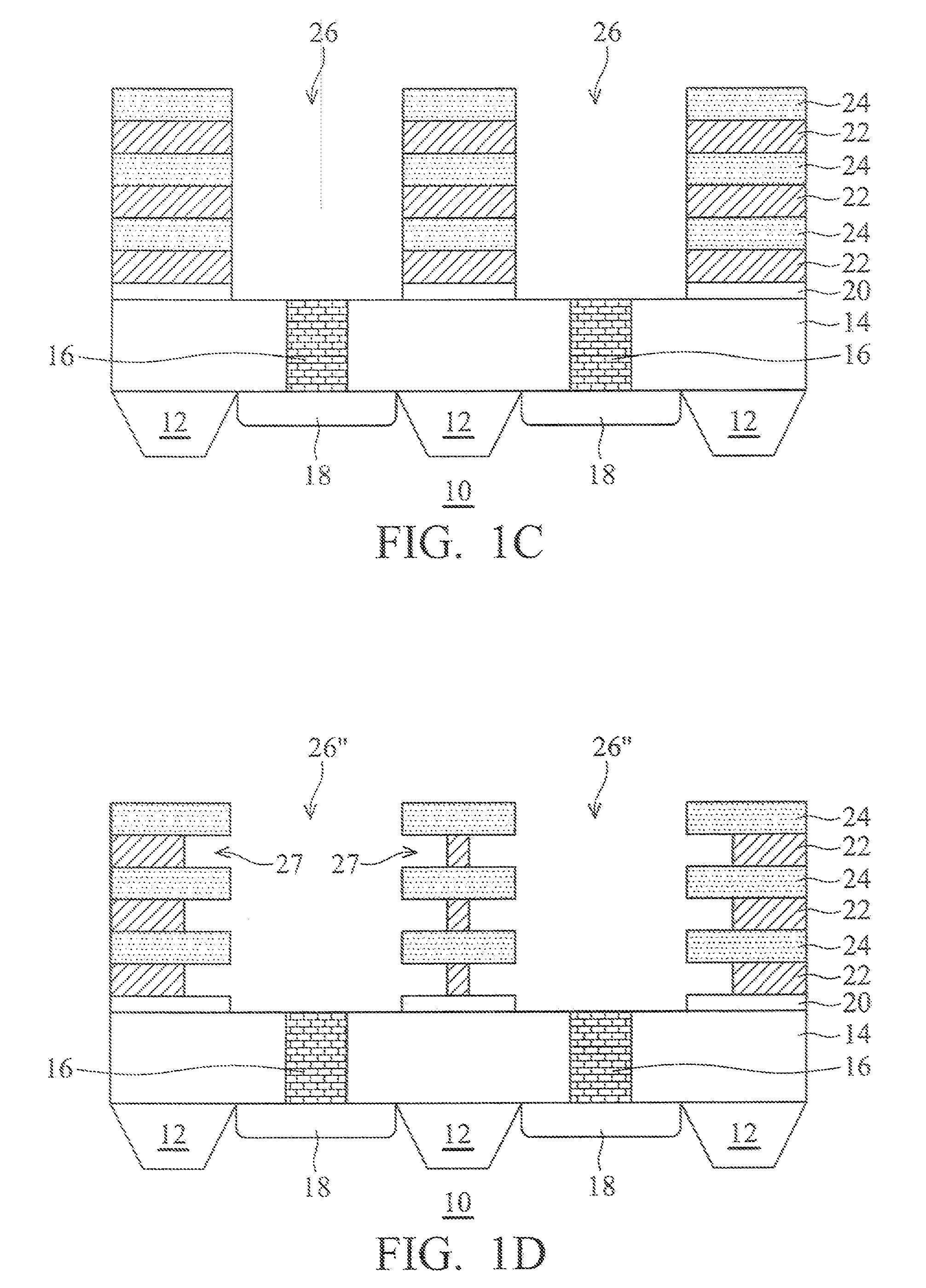

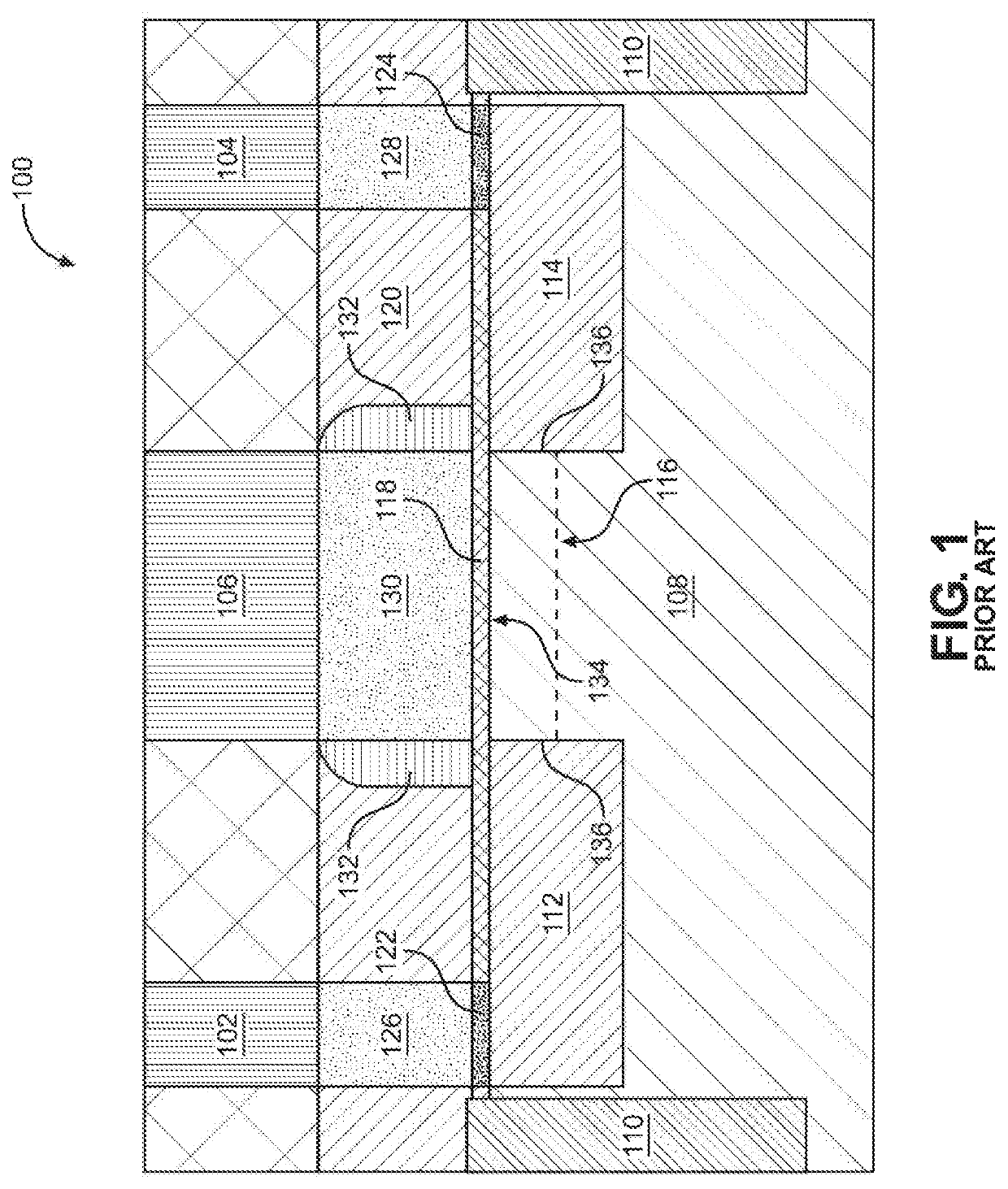

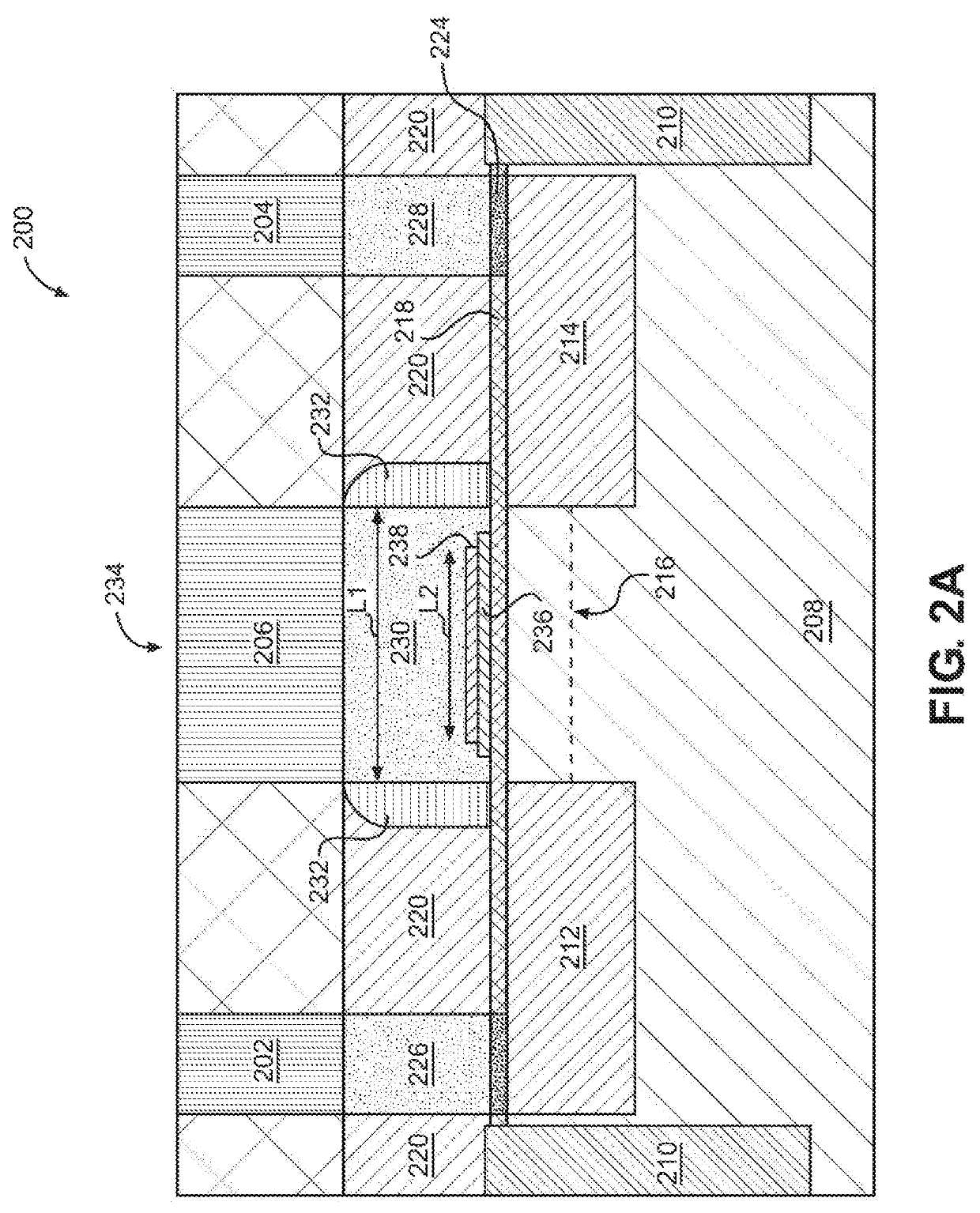

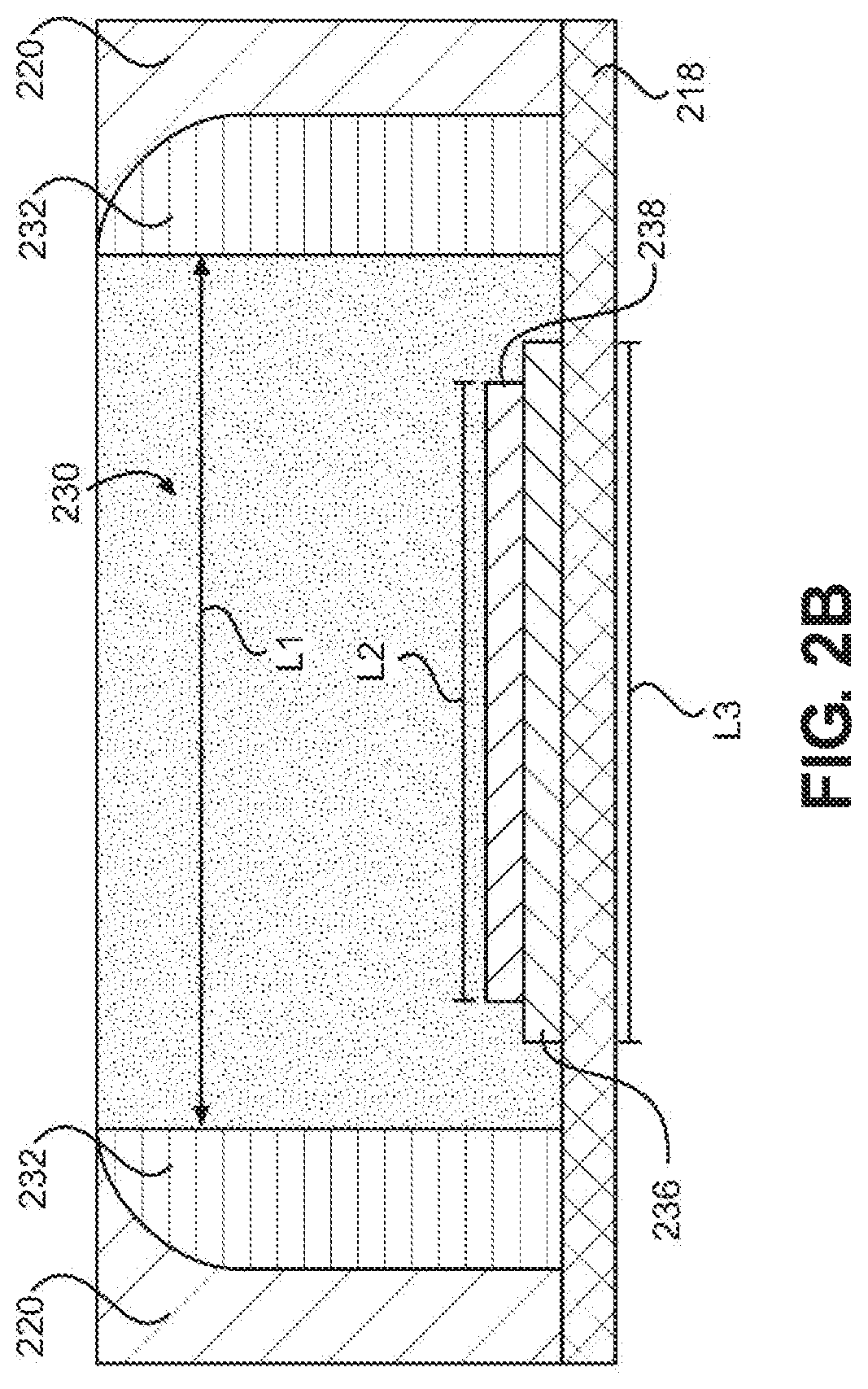

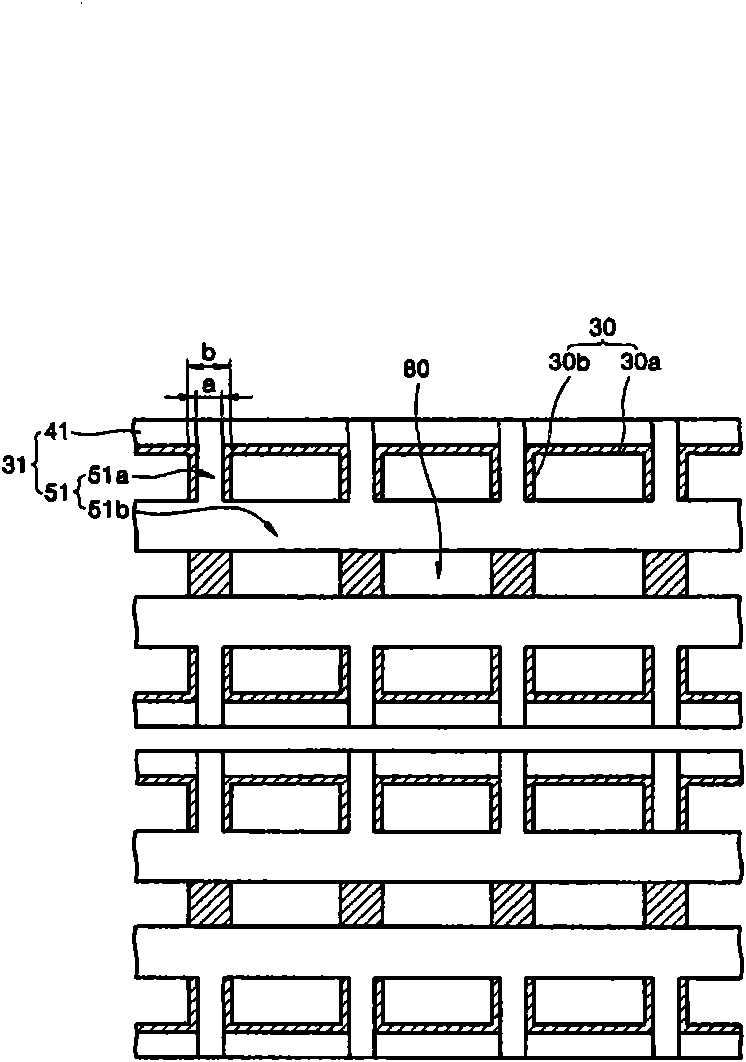

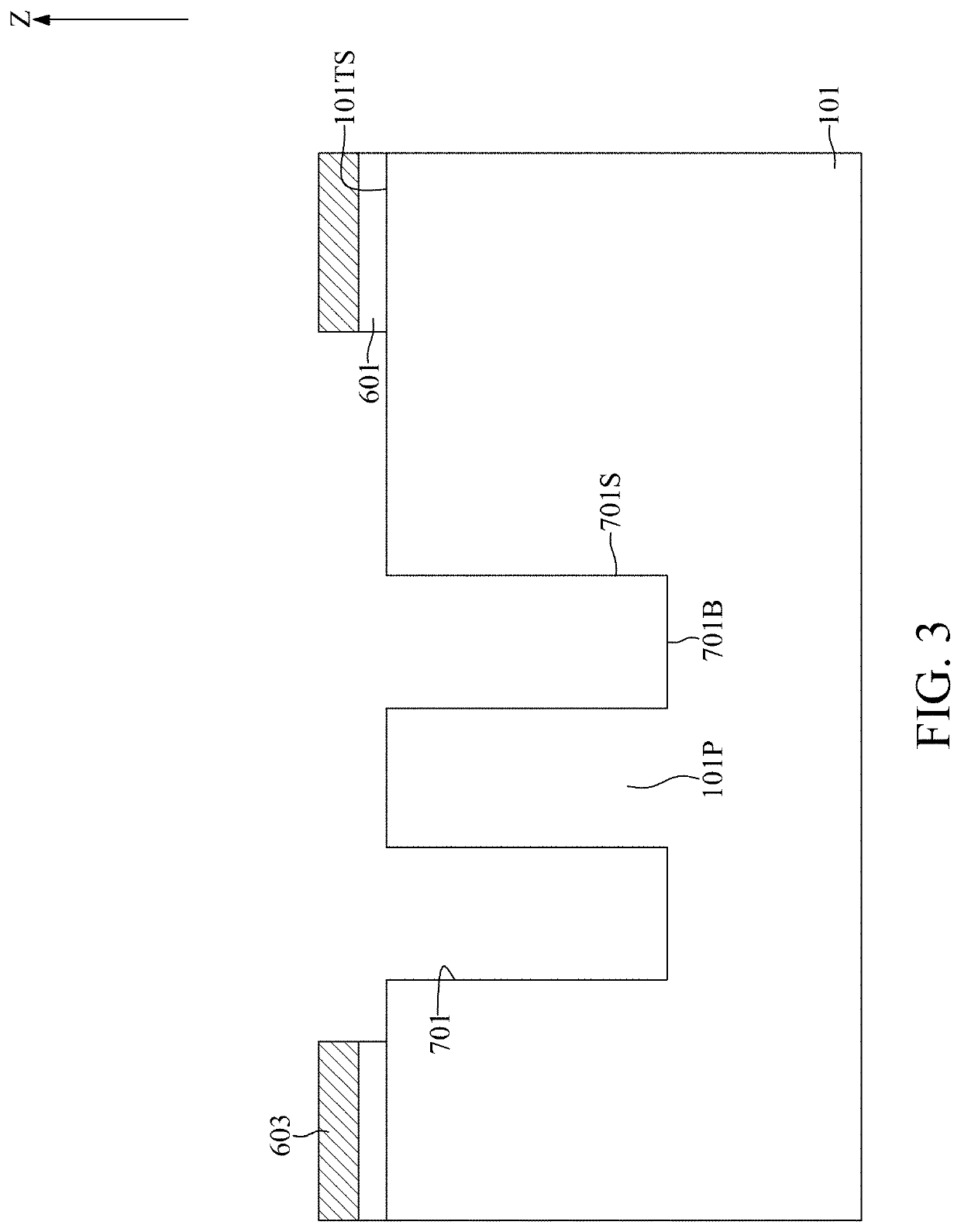

Method of forming a metal-insulator-metal capacitor

ActiveUS7666737B2Increase effective capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingLateral recessEngineering

A method of forming a metal-insulator-metal capacitor has the following steps. A stack dielectric structure is formed by alternately depositing a plurality of second dielectric layers and a plurality of third dielectric layers. A wet etch selectivity of the second dielectric layer relative to said third dielectric layer is of at least 5:1. An opening is formed in the stack dielectric structure, and then a wet etch process is employed to remove relatively-large portions of the second dielectric layers and relatively-small portions of the third dielectric layers to form a plurality of lateral recesses in the second dielectric layers along sidewalls of the opening. A bottom electrode layer is formed to extend along the serrate sidewalls, a capacitor dielectric layer is formed on the bottom electrode layer, and a top electrode layer is formed on the capacitor dielectric layer.

Owner:TAIWAN SEMICON MFG CO LTD

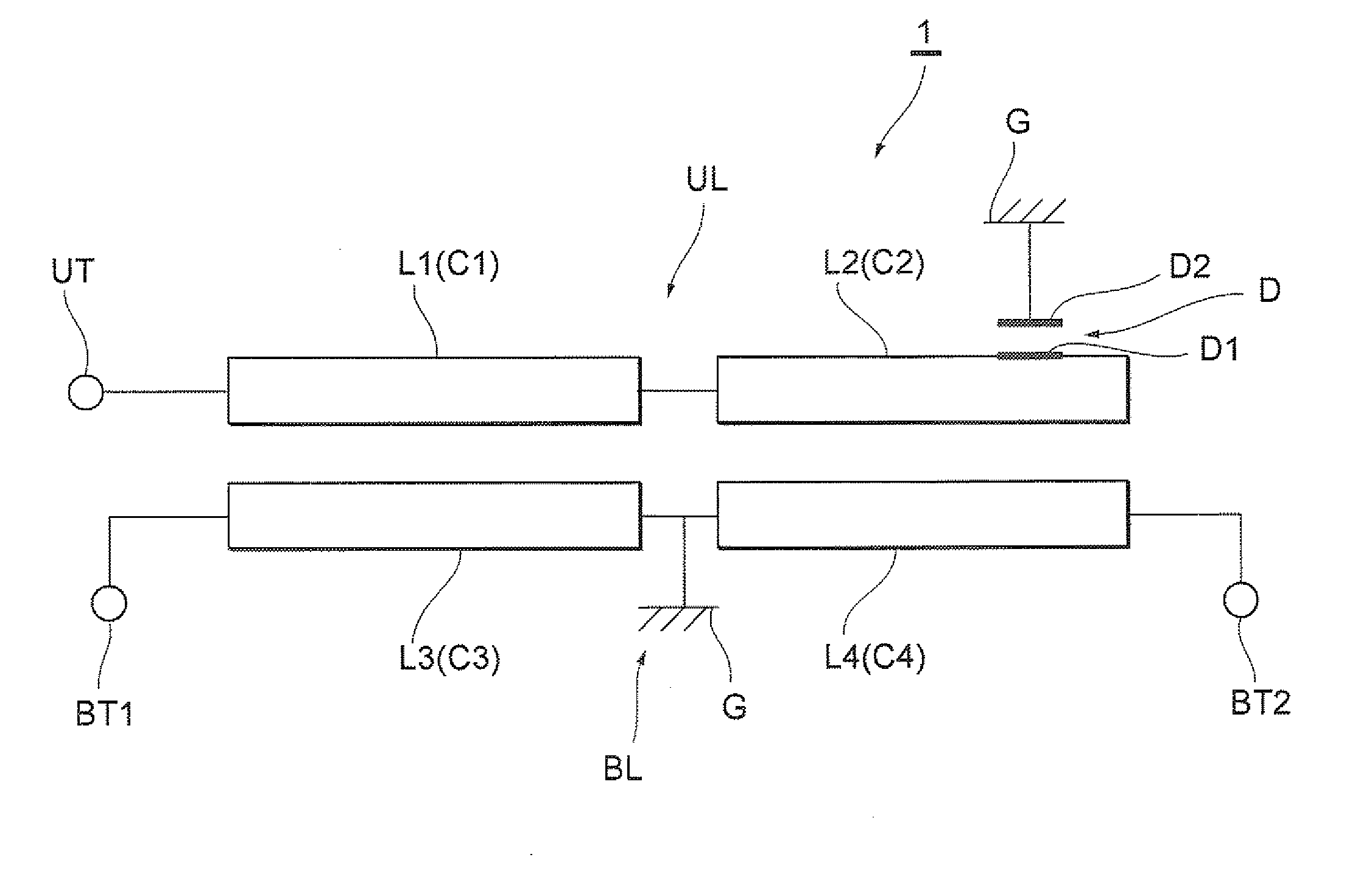

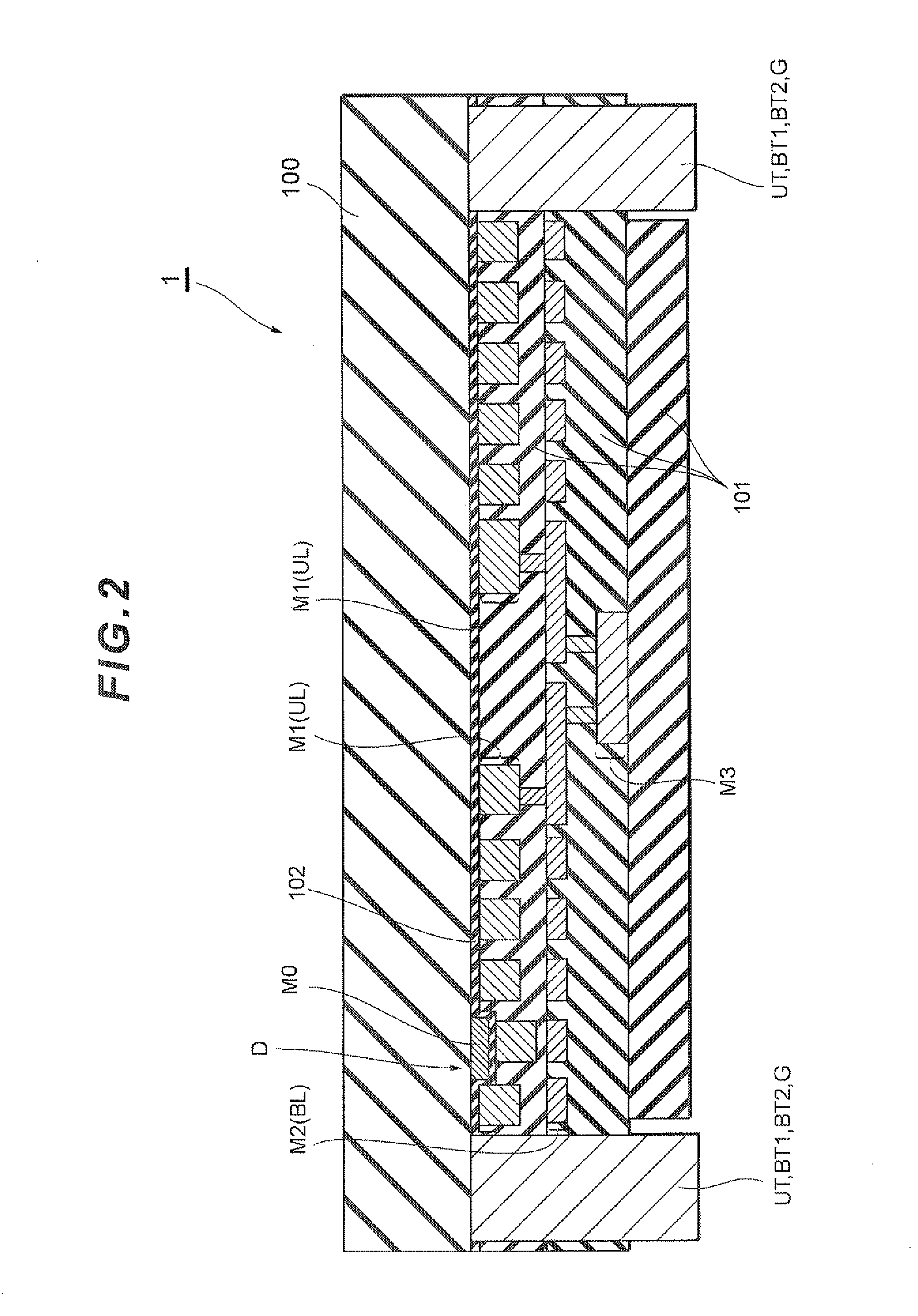

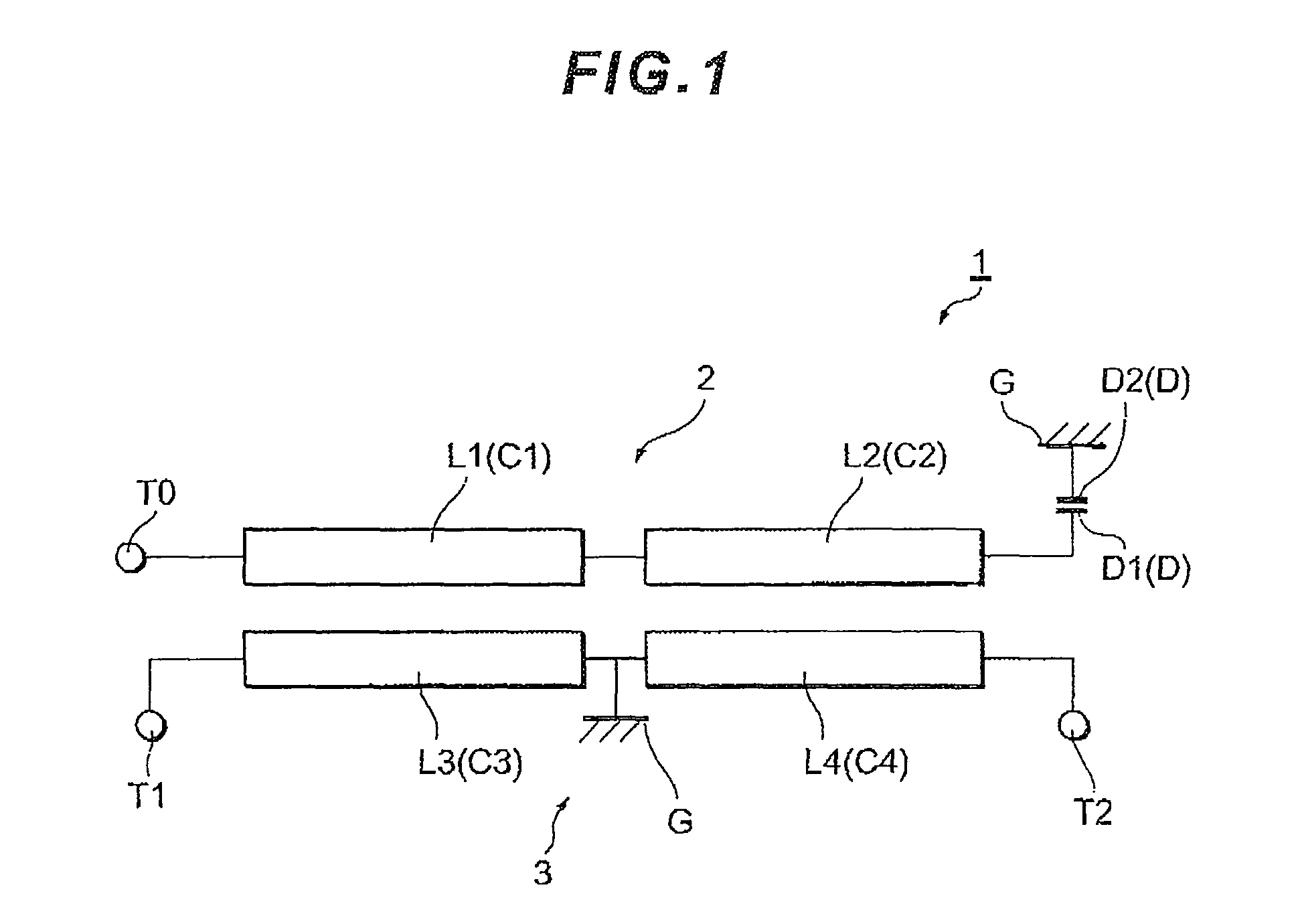

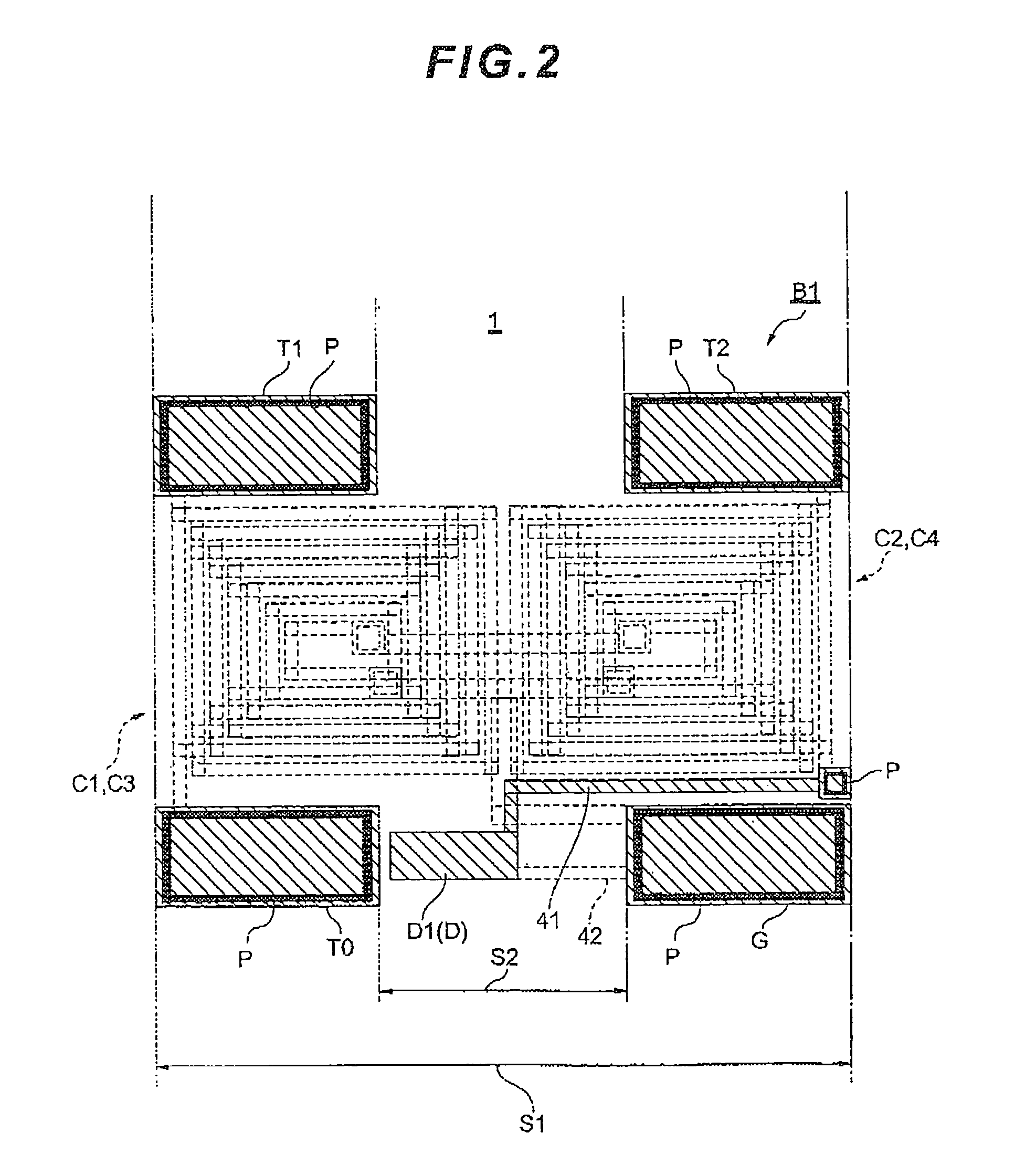

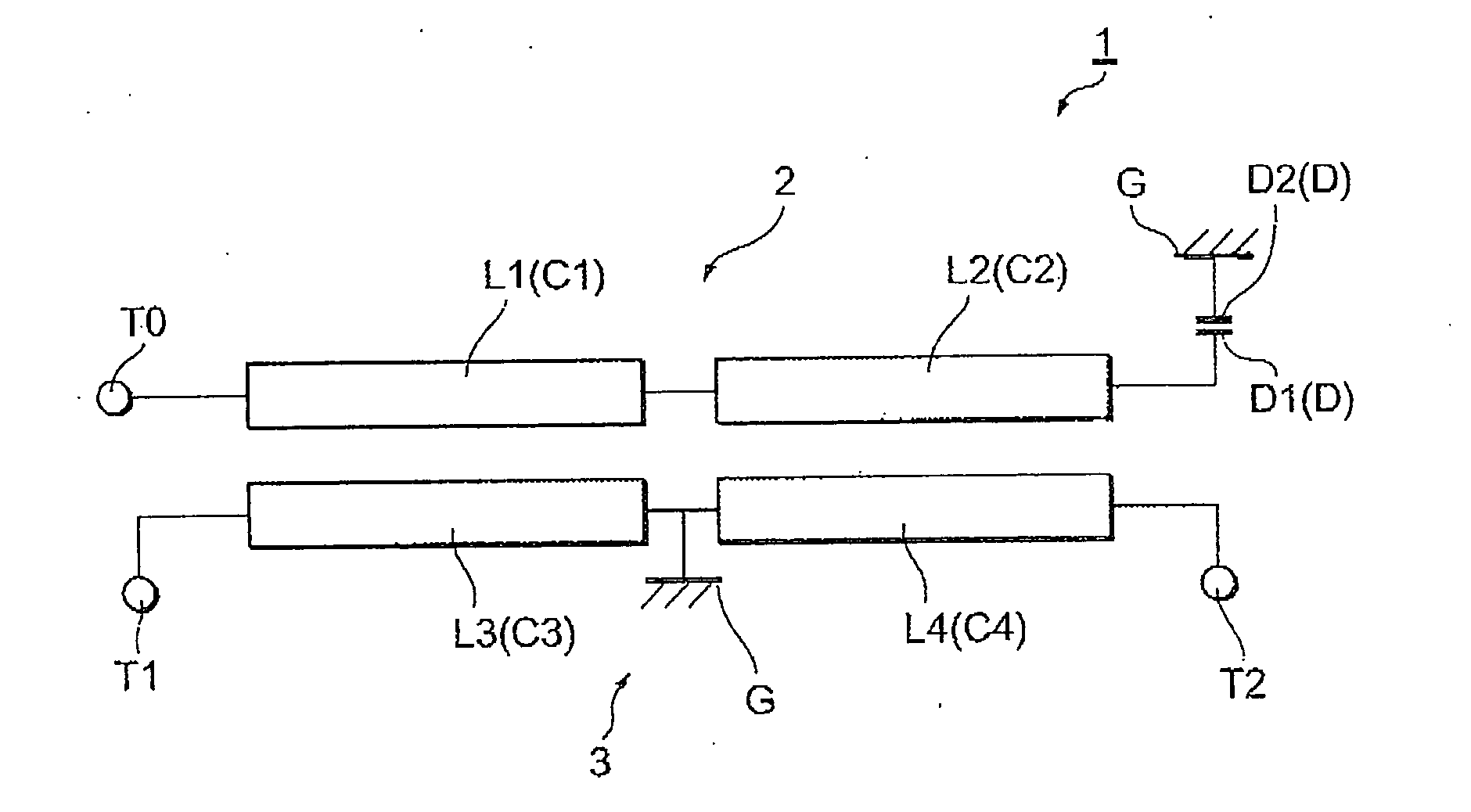

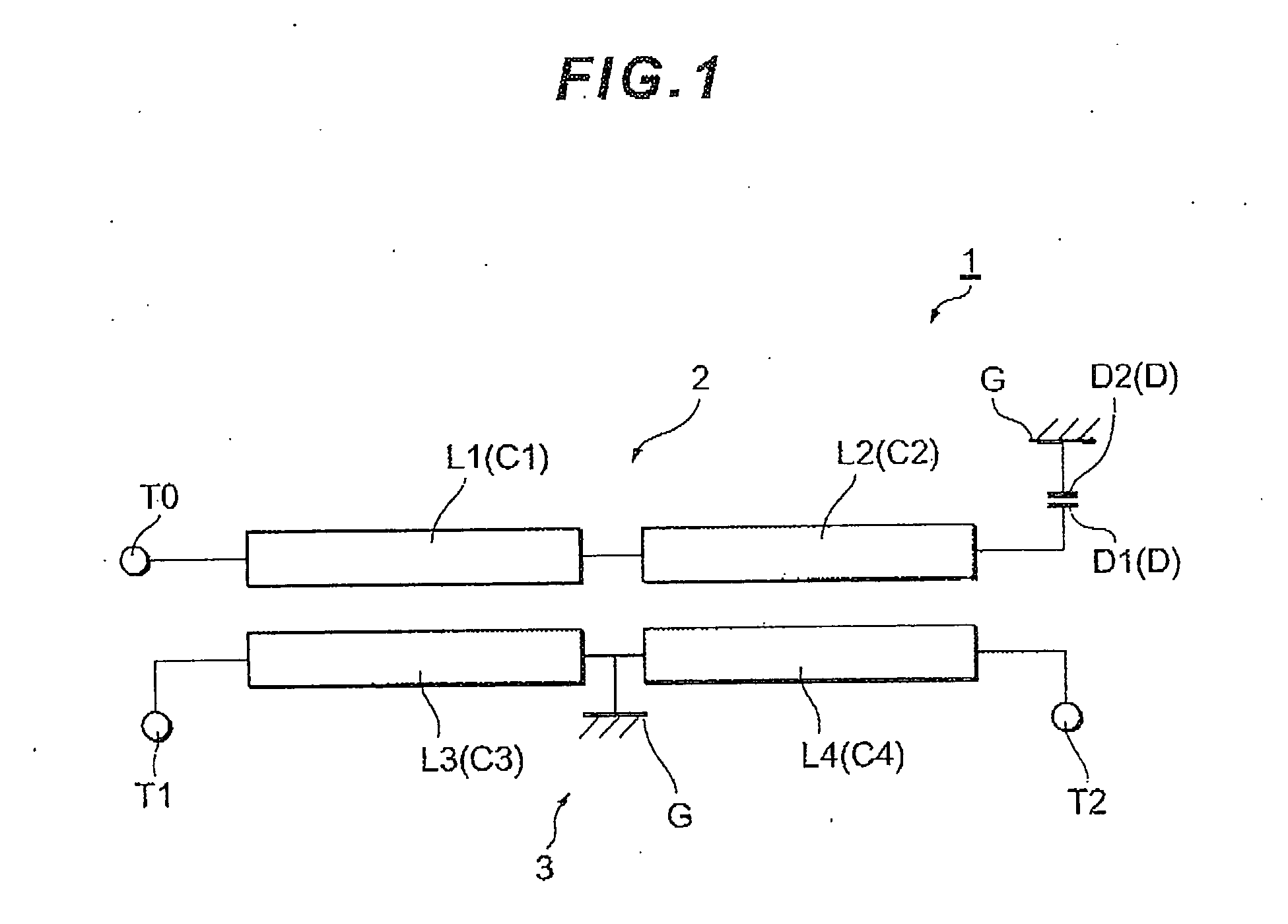

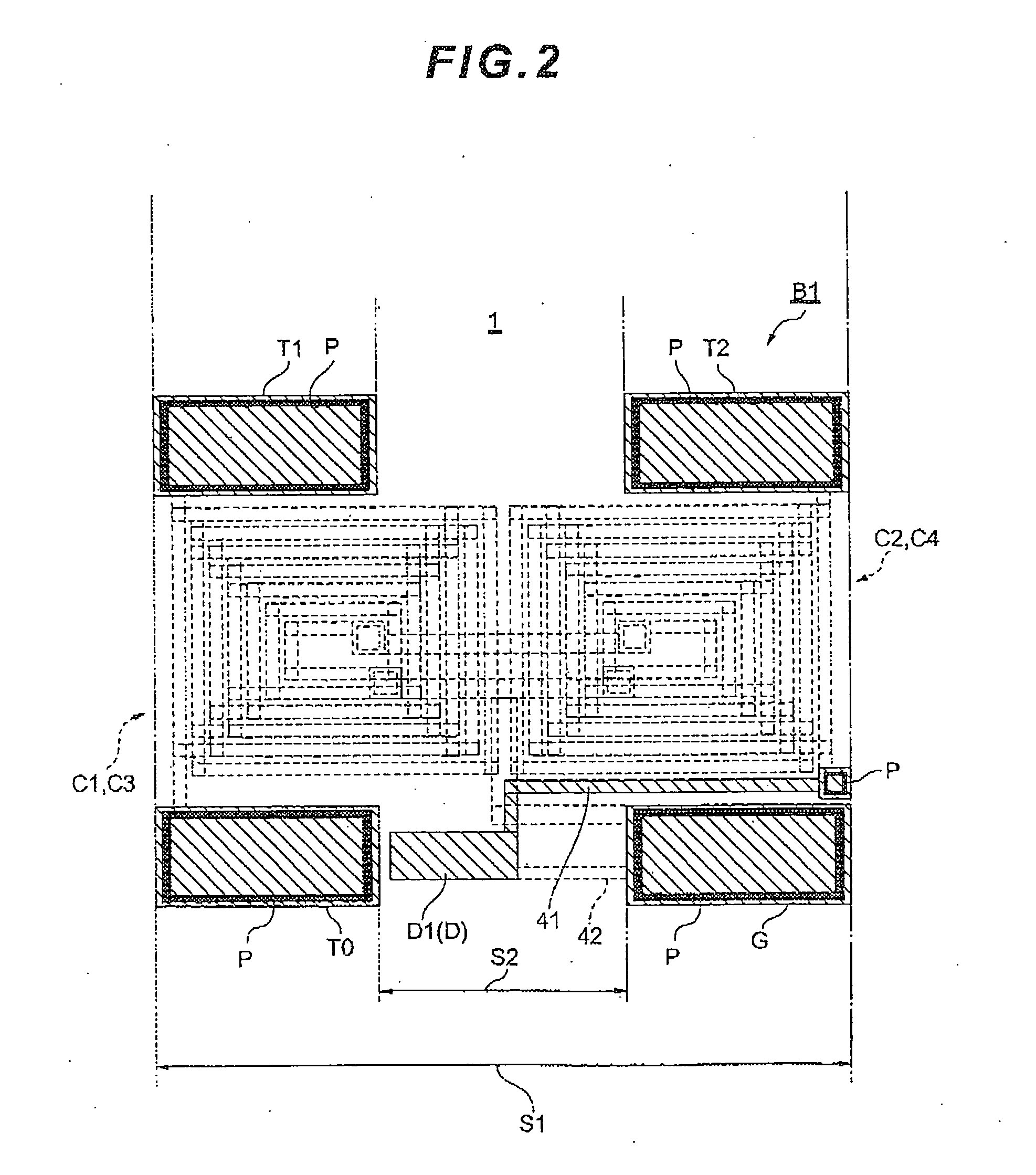

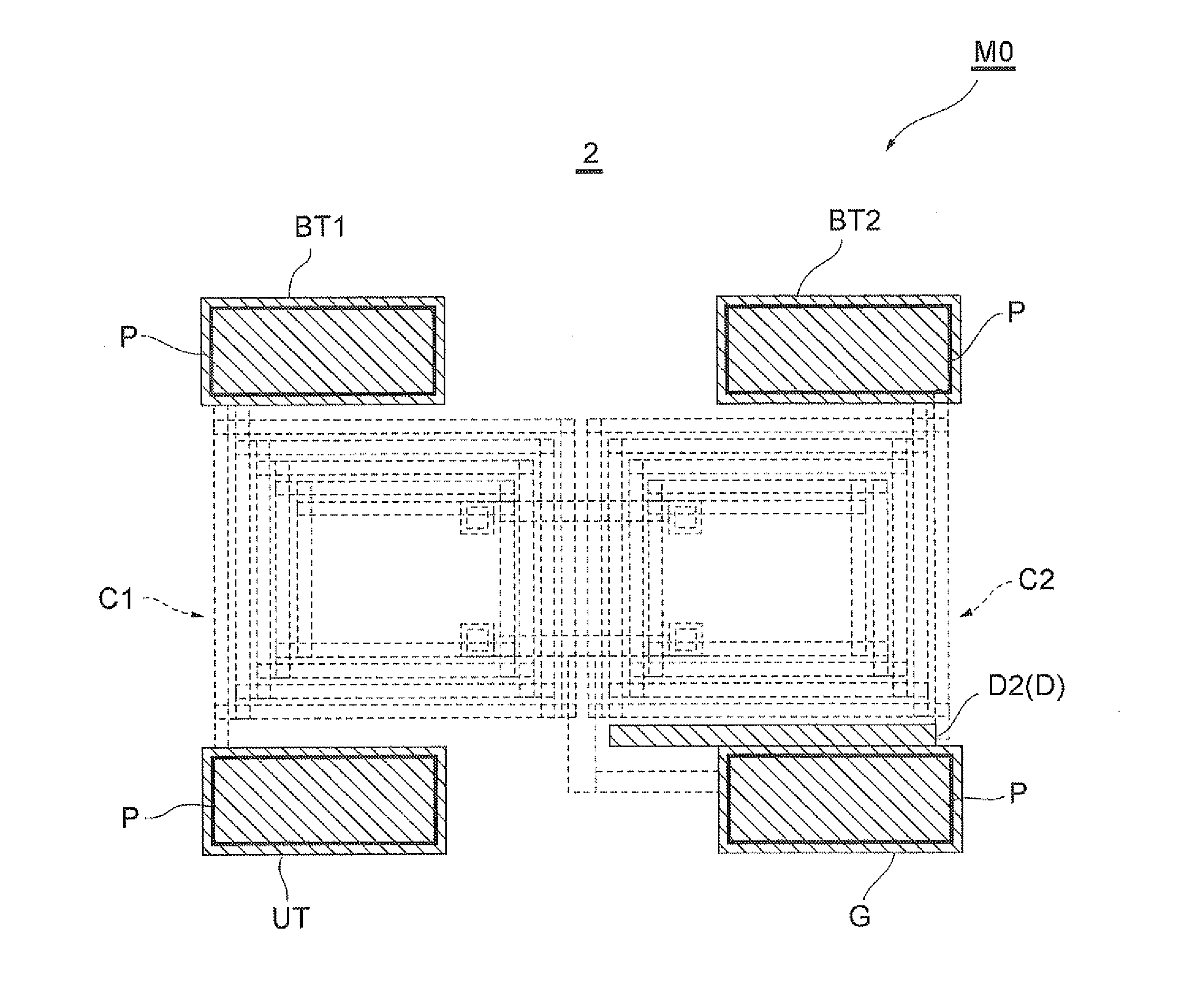

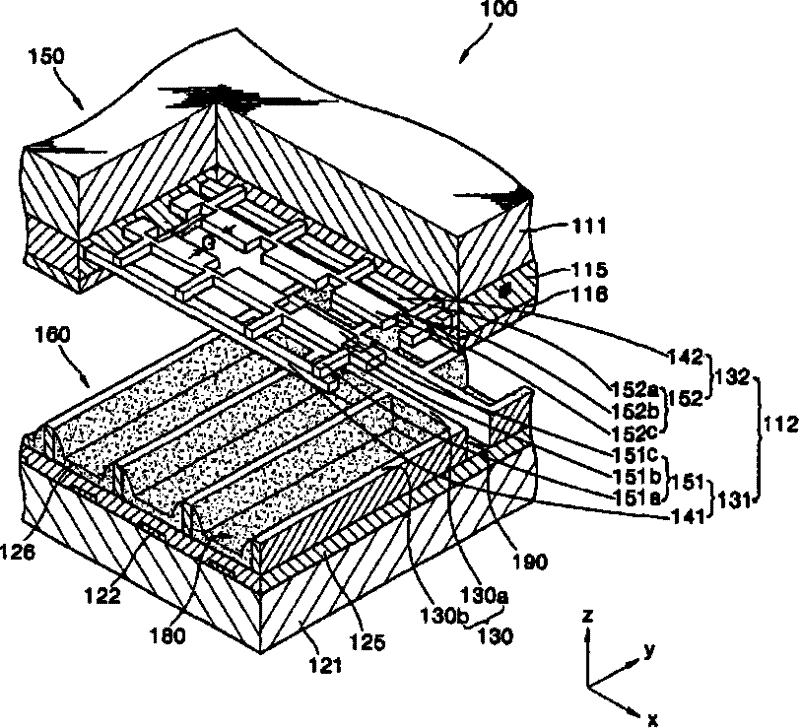

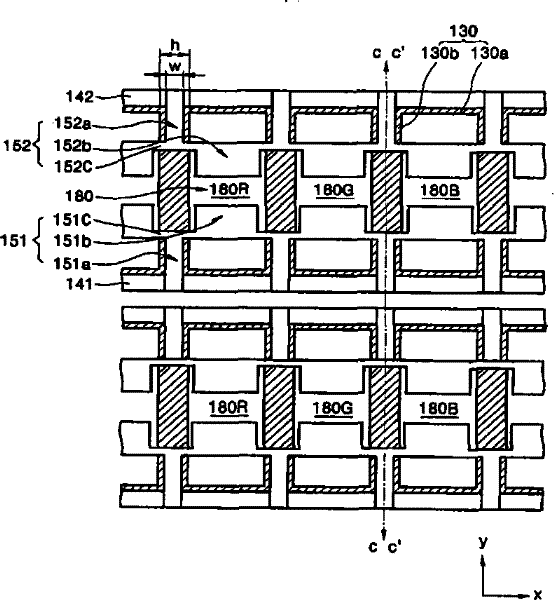

Thin film balun

ActiveUS20110012690A1Characteristic impedance can be changedExcellent passage characteristicMultiple-port networksOne-port networksEngineeringBalun

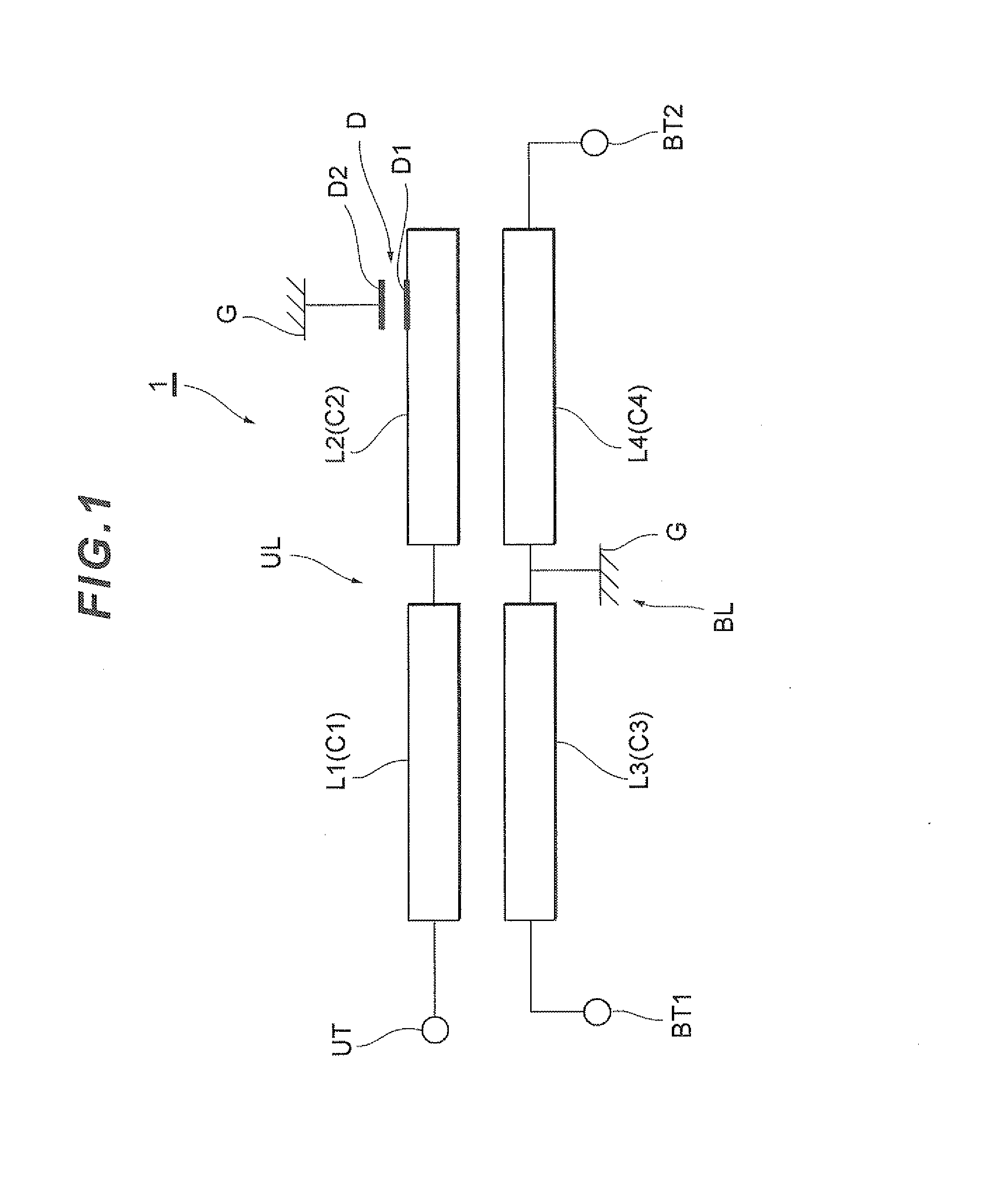

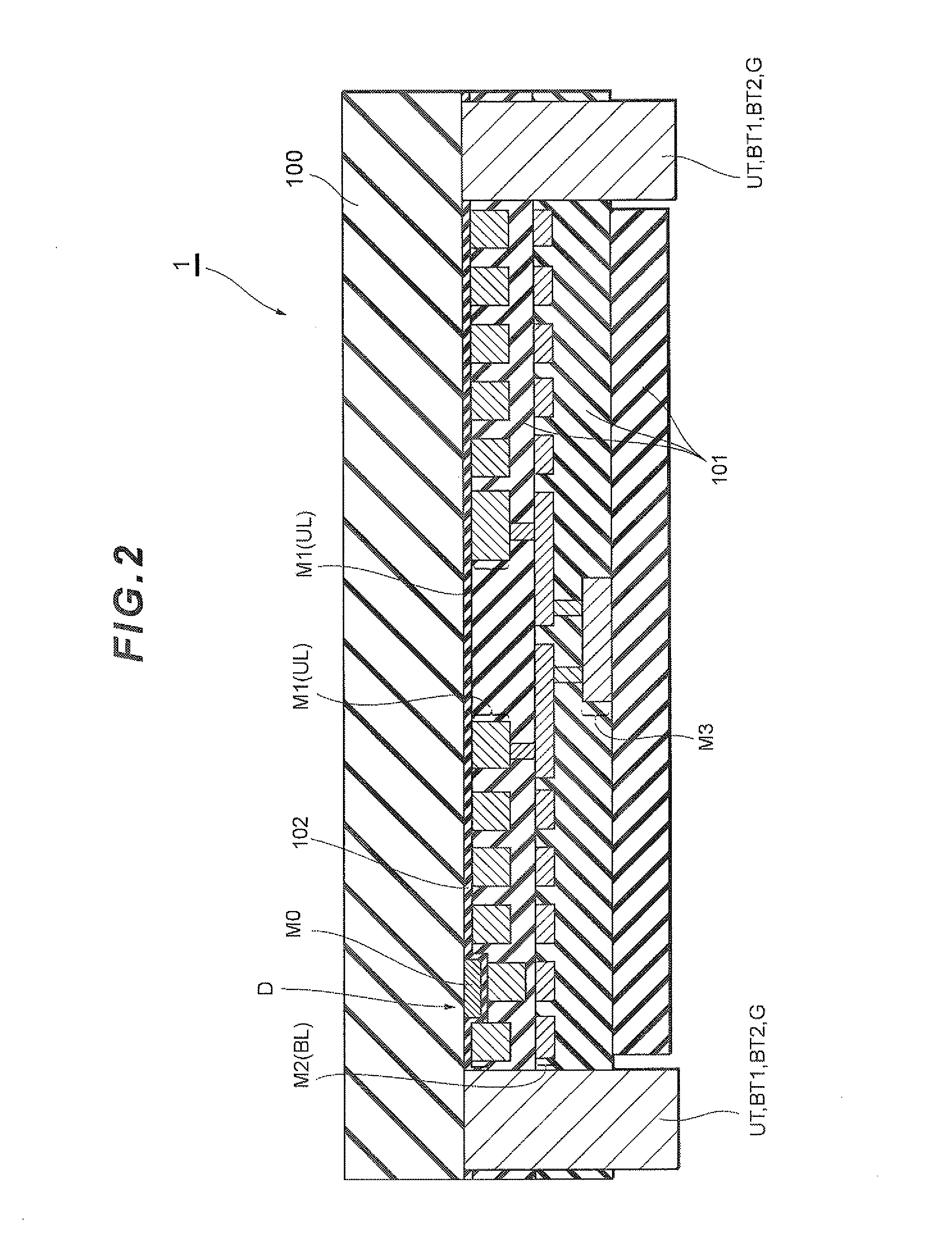

A thin film balun that can be made smaller and thinner while maintaining required balun characteristics is provided. A thin film balun 1 includes: an unbalanced transmission line UL including a first coil portion C1 and a second coil portion C2; a balanced transmission line BL including a third coil portion C3 and a fourth coil portion C4 that are positioned facing and magnetically coupled to the first coil portion C1 and the second coil portion C2 respectively; an unbalanced terminal UT connected to the first coil portion C1; a ground terminal G connected to the second coil portion C2 via a C component D; and an electrode D2 connected to the ground terminal G and facing a part of the second coil portion C2. The C component D is formed by the electrode D2 and the part D1 of the second coil portion C2.

Owner:TDK CORPARATION

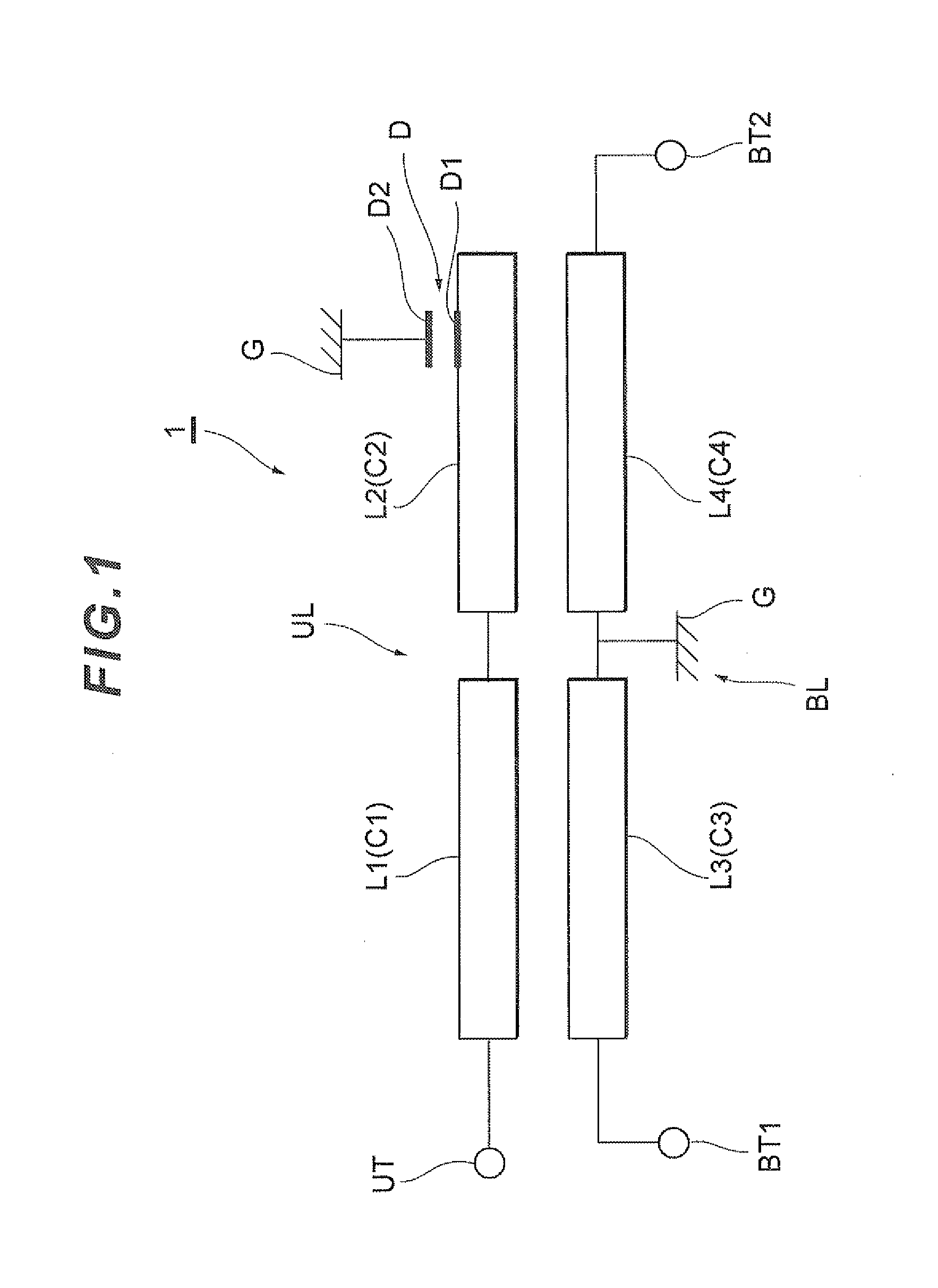

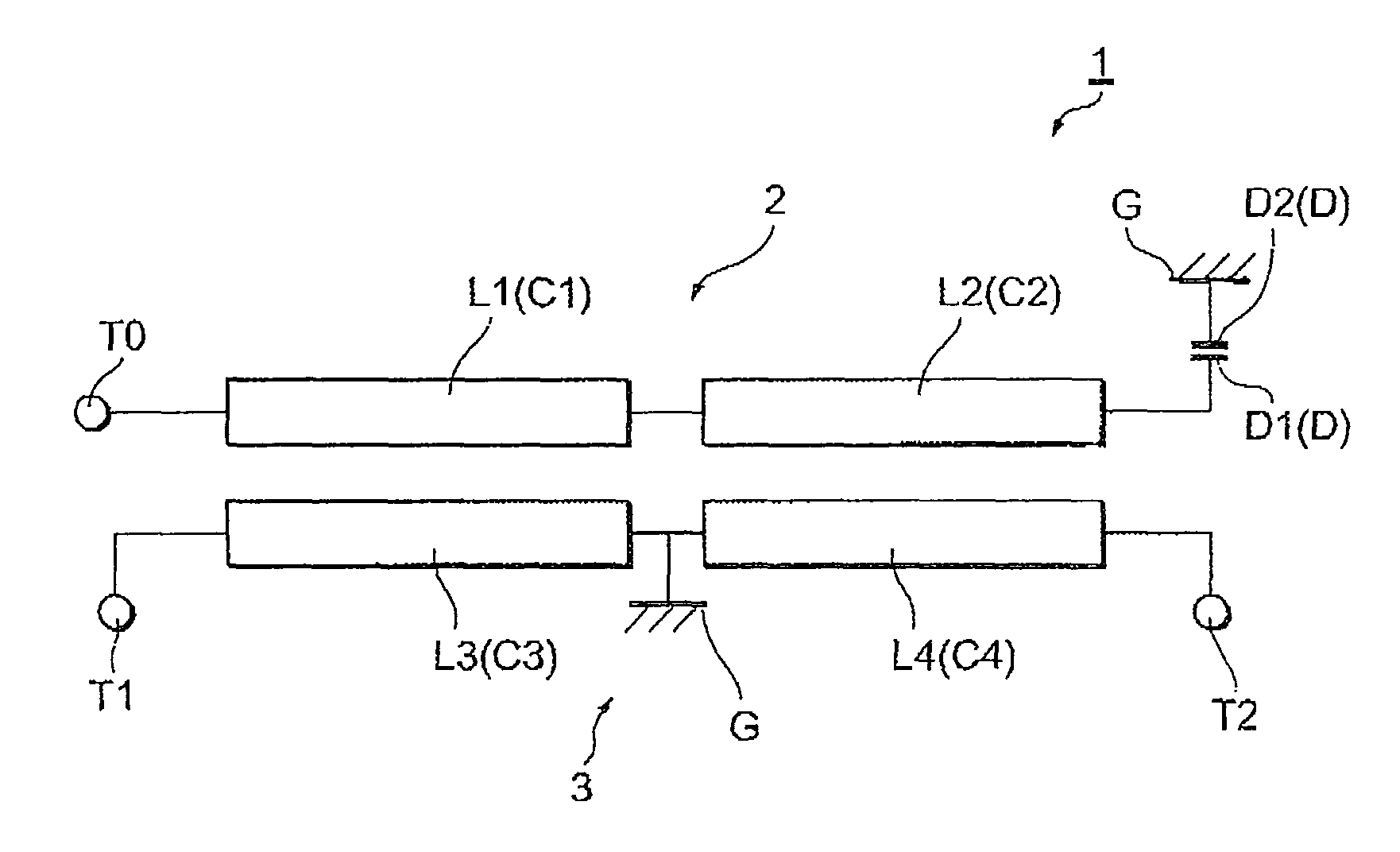

Thin film balun

ActiveUS8203396B2Avoid resonant frequencyHigh frequencyMultiple-port networksOne-port networksEngineeringCapacitor

The present invention provides a thin film balun capable of preventing a resonant frequency from being increased to a high frequency, and thus realizing a preferable passage characteristic. A thin film balun 1 includes: an unbalanced transmission line 2 having a first coil portion C1 and a second coil portion C2; and a balanced transmission line 3 having a third coil portion C3 and a fourth coil portion C4 which are magnetically coupled with the first coil portion C1 and the second coil portion C2, respectively. The first coil portion C1 is connected to an unbalanced terminal T0, and the second coil portion C2 is connected to a ground terminal G (ground potential) via a capacitor D (C component). The third coil portion C3 is connected to a balanced terminal T1 and the fourth coil portion C4 is connected to a second balanced terminal T2. The capacitor D is provided, in a plan view, in an area S1 between the outer end of the unbalanced terminal T0 and the outer end of the ground terminal G.

Owner:TDK CORPARATION

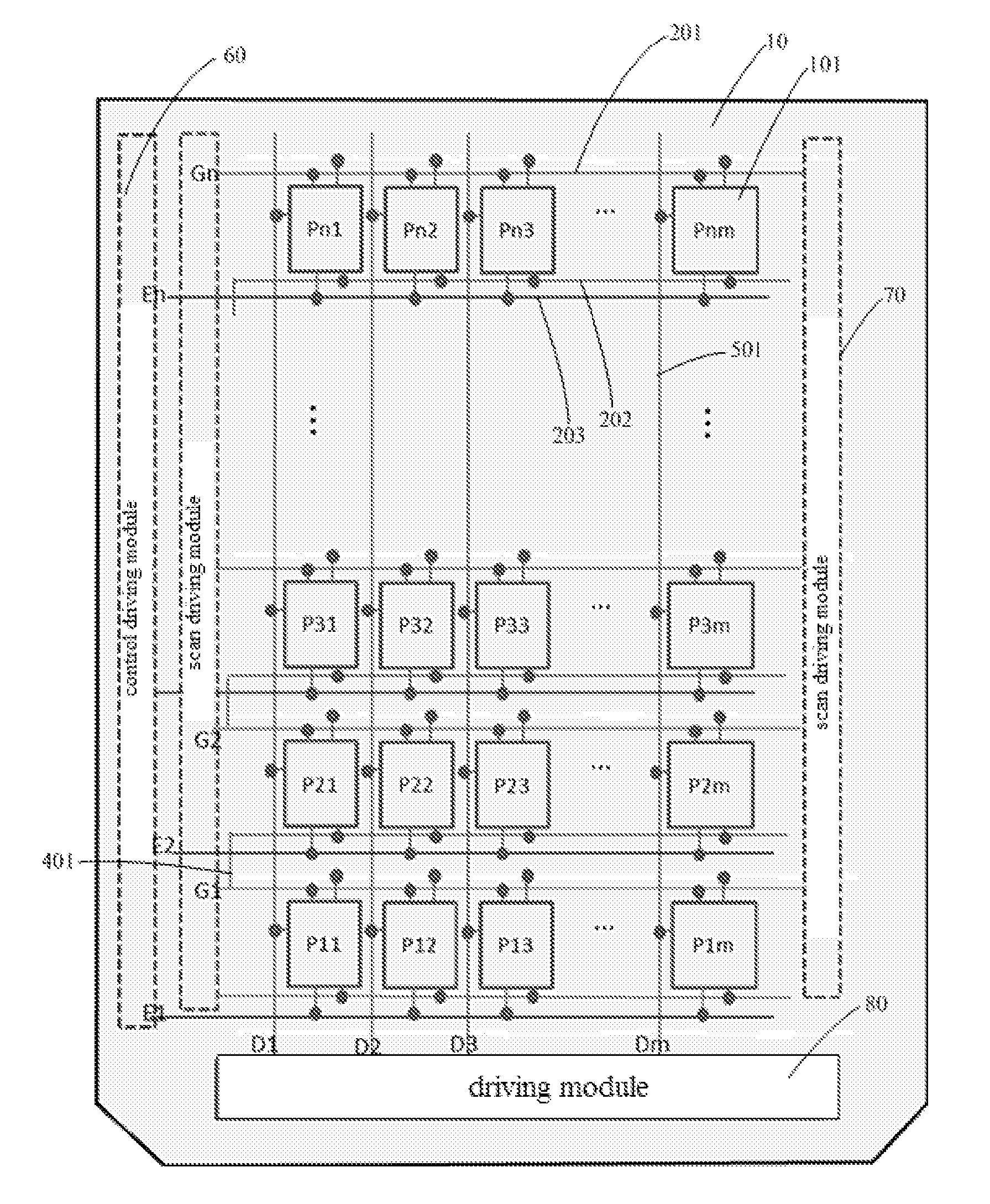

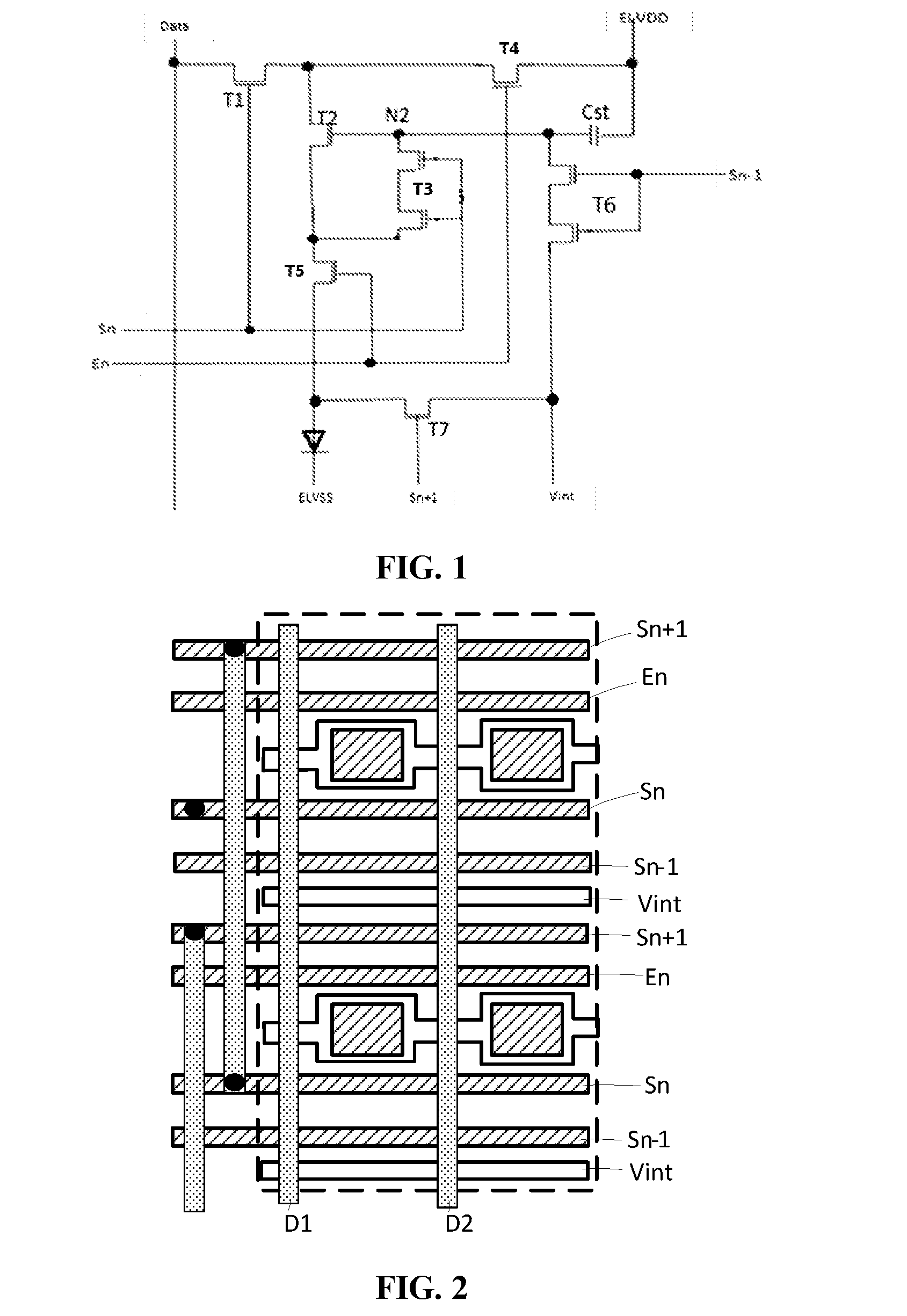

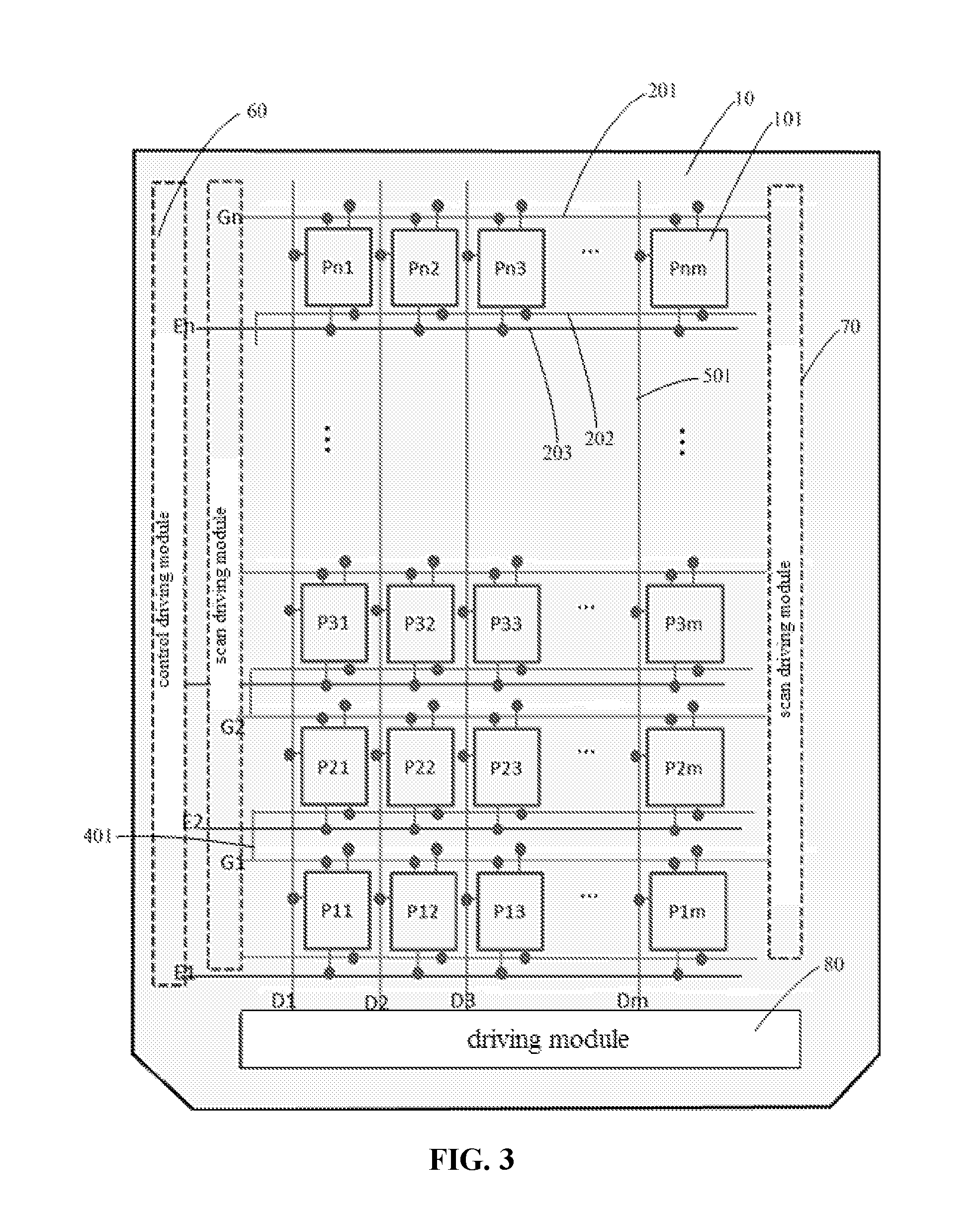

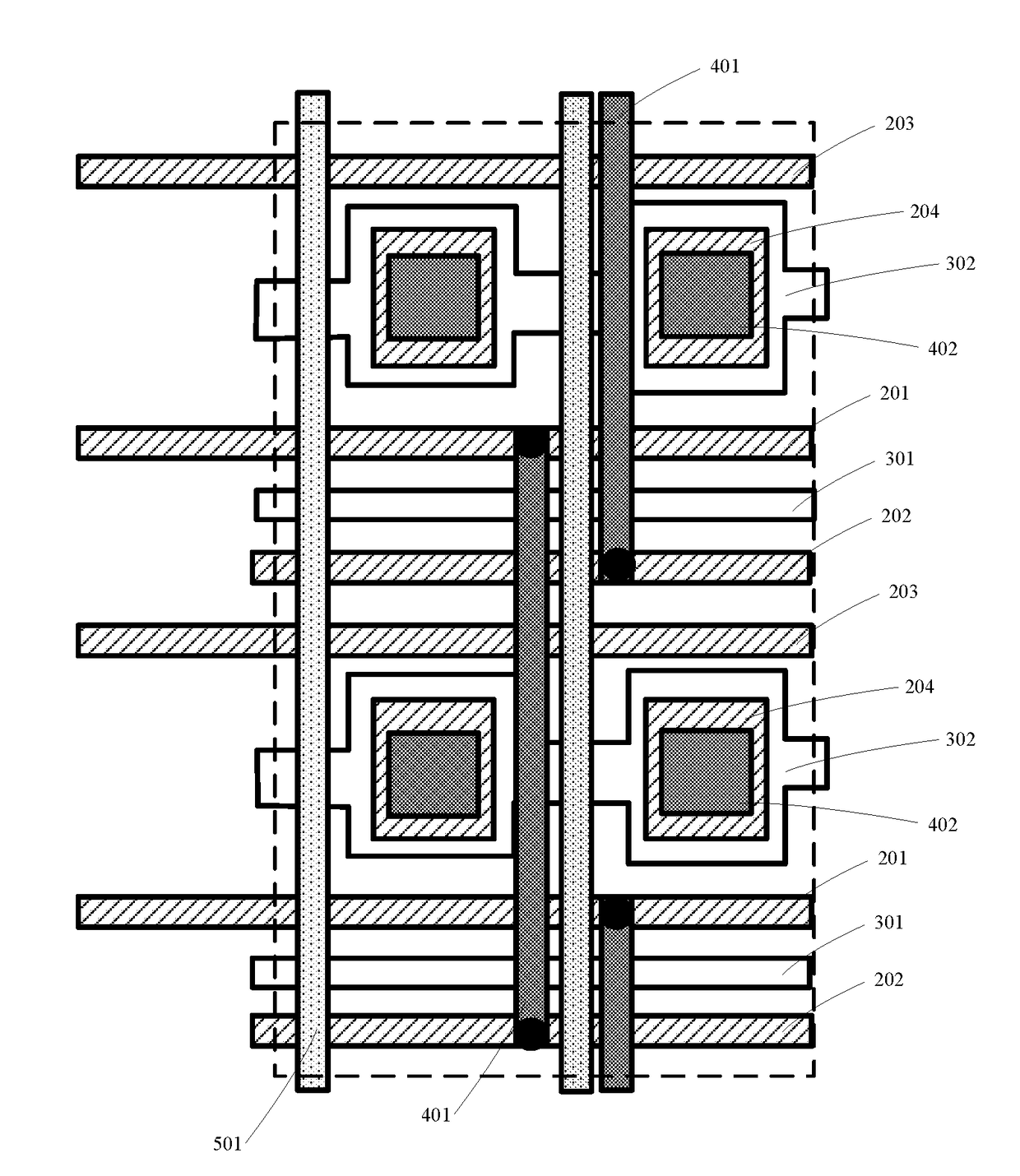

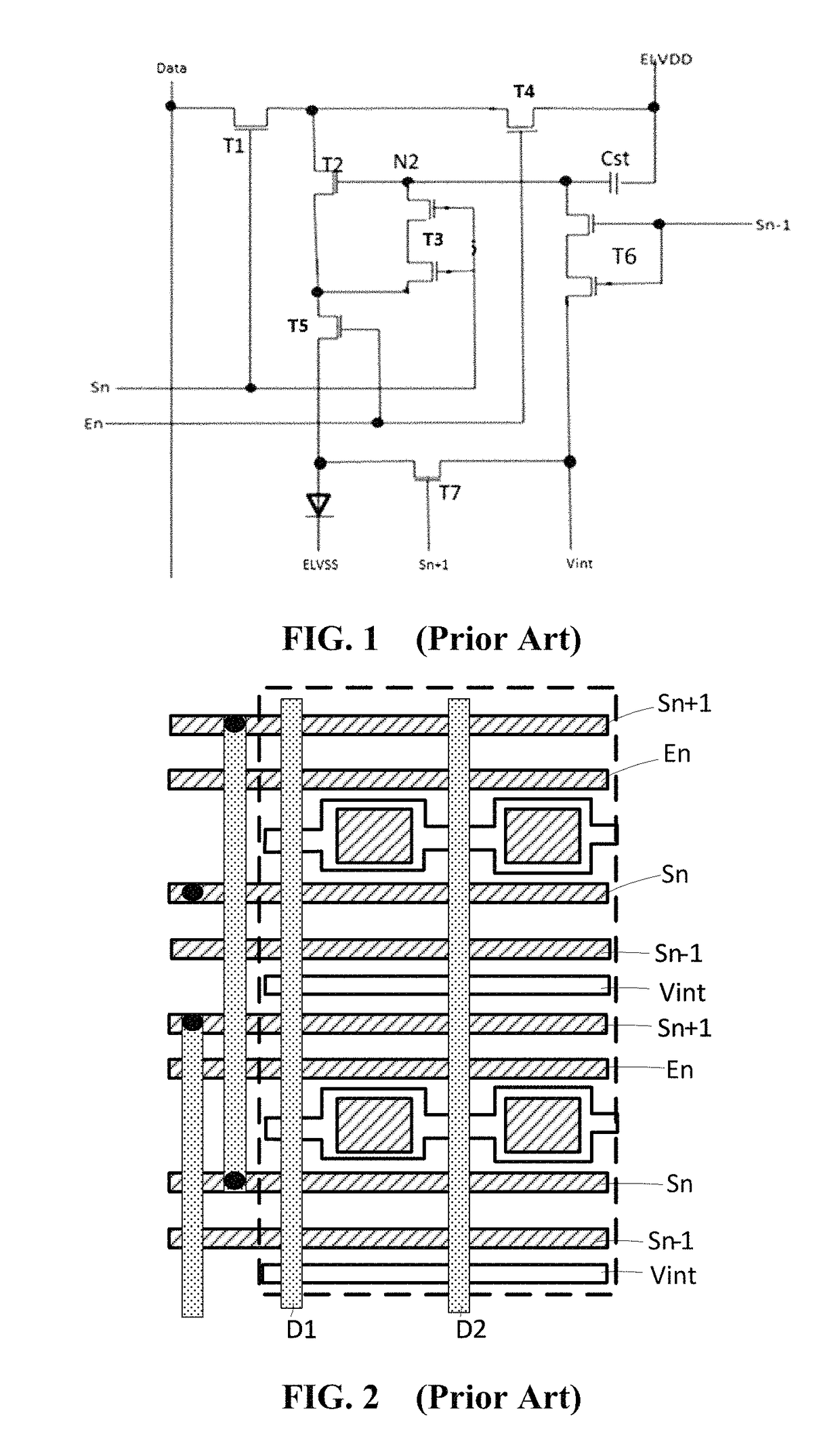

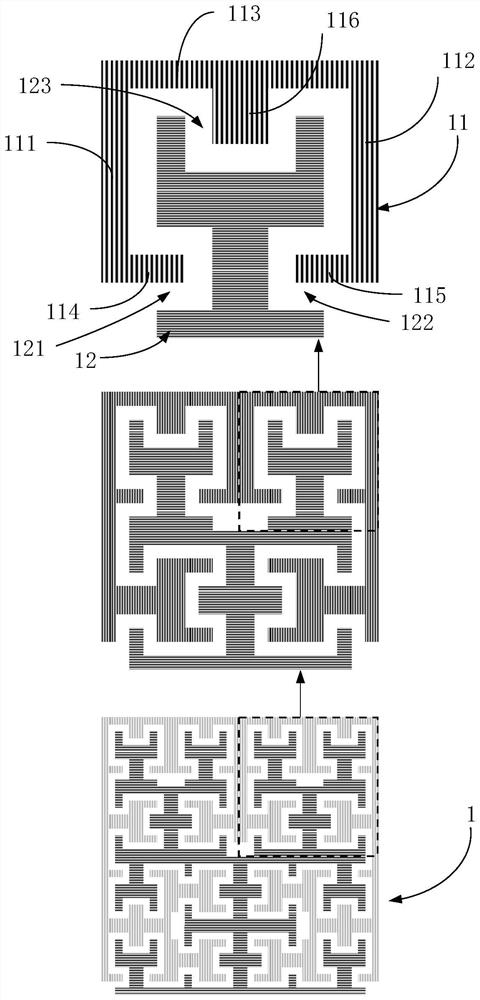

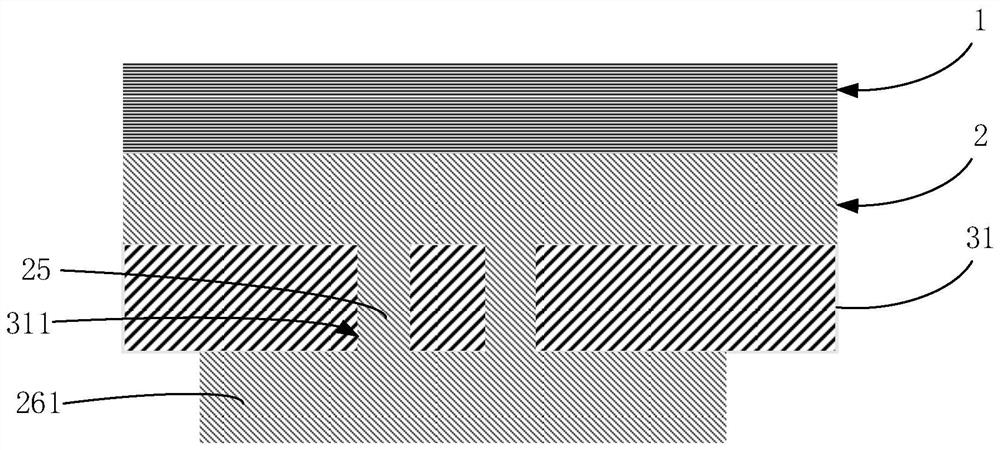

Pixel structure

A pixel structure includes a pixel unit layer and a first metal wire layer. Each of control signal line and first and second scan signal lines in the first metal wire layer is connected to each pixel unit in a corresponding row. An insulating layer is disposed between each first metal patterned section in the first metal wire layer and a corresponding row of pixel units. A second metal wire layer includes initial signal lines and second metal patterned sections. Each initial signal line is connected to each pixel unit in a corresponding row. Each second metal patterned section overlaps with one of the first metal patterned sections to form a capacitor. Each connection signal line in a third metal wire layer connects the first scan signal line of a current row of pixel units to the second scan signal line of a next row of pixel units.

Owner:EVERDISPLAY OPTRONICS (SHANGHAI) CO LTD

High-density low-parasitic capacitor

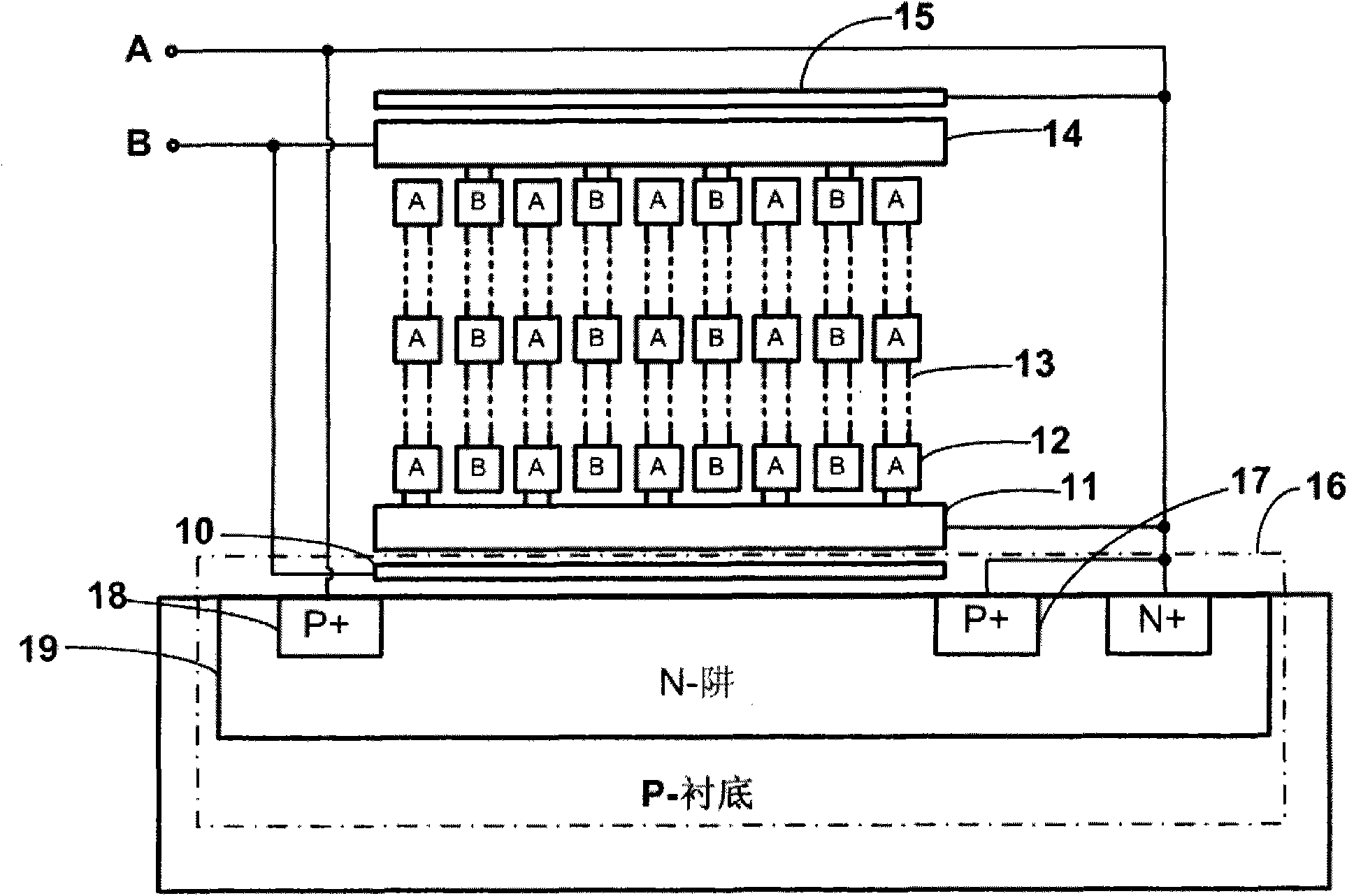

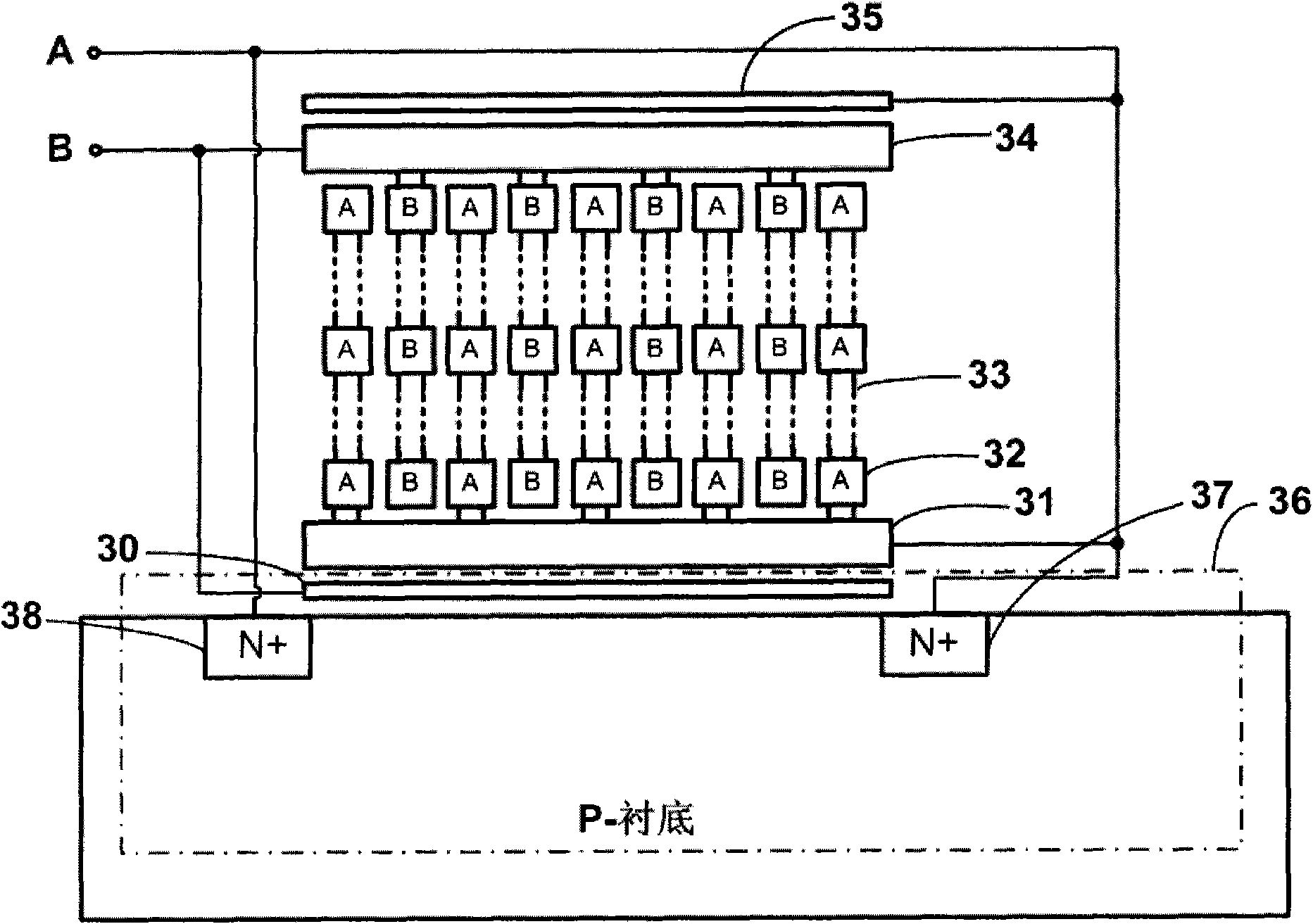

ActiveCN101789430AReduce the ratioReduce power consumptionSolid-state devicesSemiconductor devicesCapacitanceParasitic capacitor

The invention discloses a high-density low-parasitic capacitor, comprising a PMOS capacitor, a first capacitor, a second capacitor, a third capacitor and an MIM capacitor, wherein the PMOS capacitor is composed of a polysilicon gate, gate oxide, and a source electrode, a drain electrode and an N-well; the source electrode, the drain electrode and an N-well are connected together; the first capacitor is arranged between the polysilicon gate and the metal at the first layer; the second capacitor is arranged between metals at the same layer; the metal at the first layer is composed of a metal block array, and each metal block and an adjacent metal block thereof are respectively connected with the port A and port B of the second capacitor; the third capacitor is arranged between through holes, and each through hole and an adjacent through hole thereof are respectively connected with the port A and port B of the capacitor; and the MIM capacitor is provided an upper polar plate and a lower polar plate which are respectively connected to the port A and port B of the capacitor. In the invention, the capacitor between the polysilicon gate and the metal layer, the capacitor between the metals at the same layer, the capacitor between the through holes, the MIM capacitor and the like are realized on an MOS capacitor, thus reaching the maximal capacitance on a unit area.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

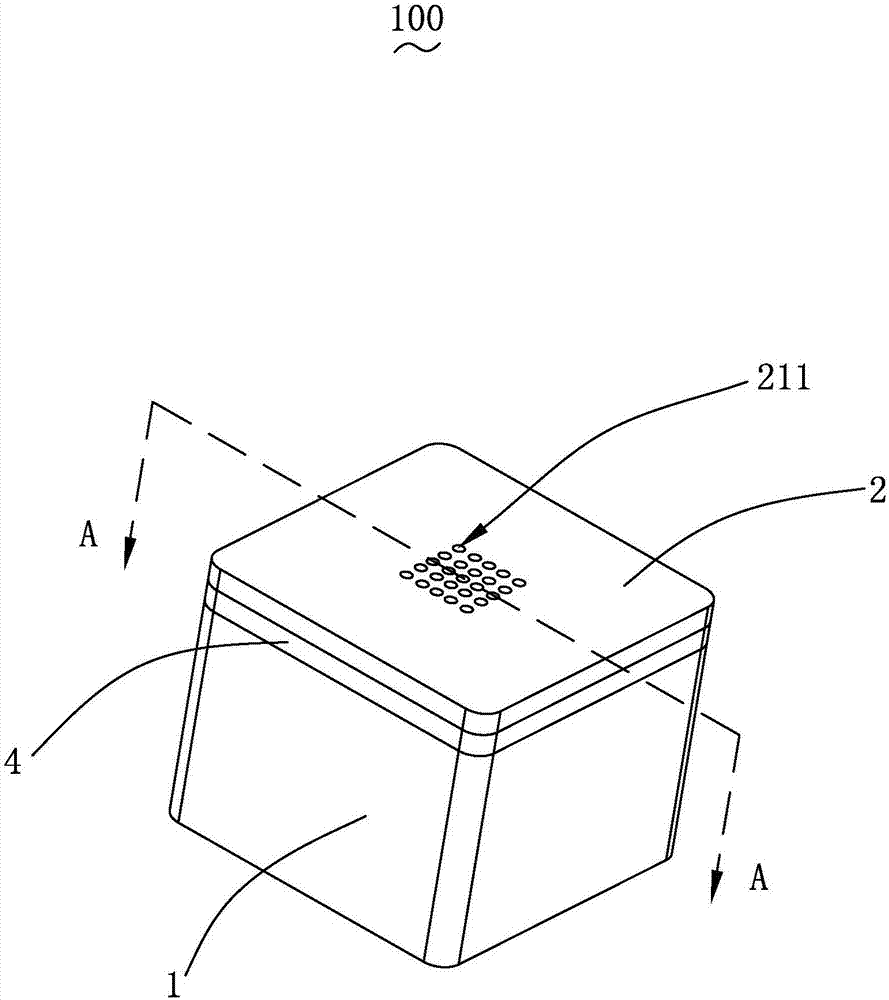

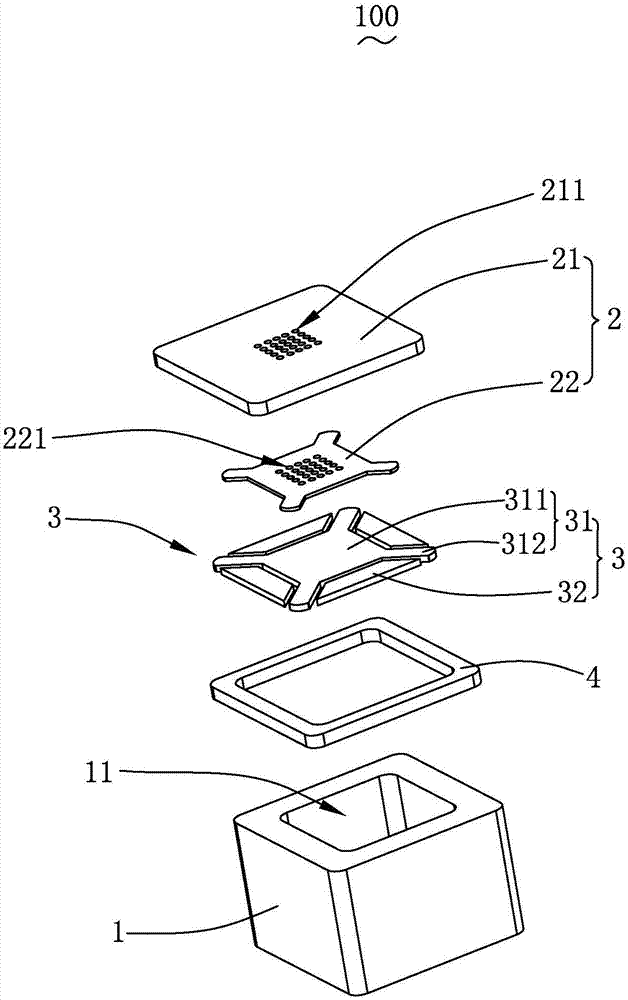

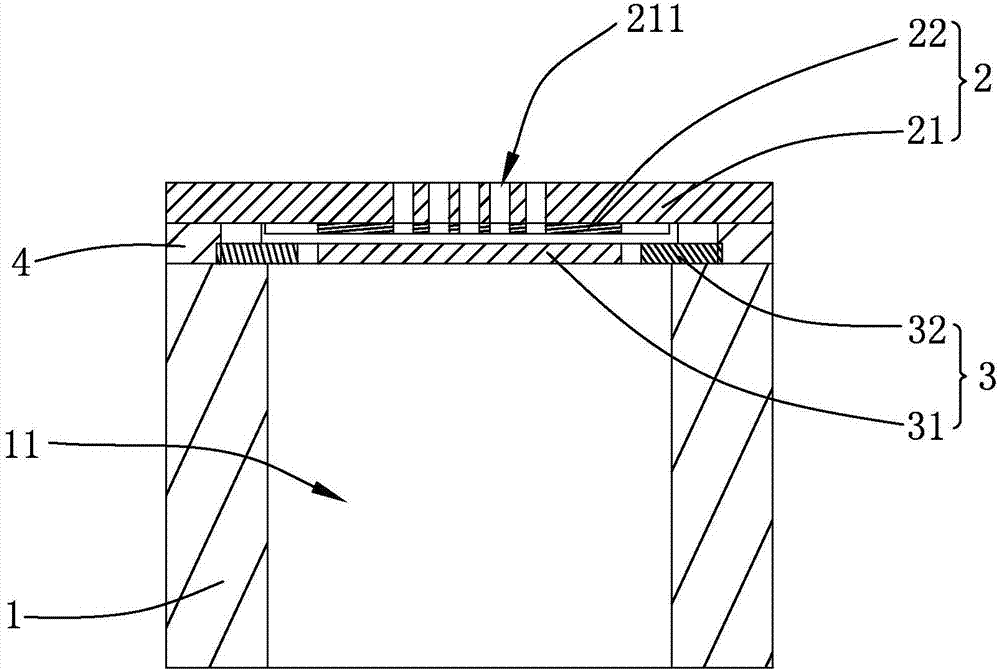

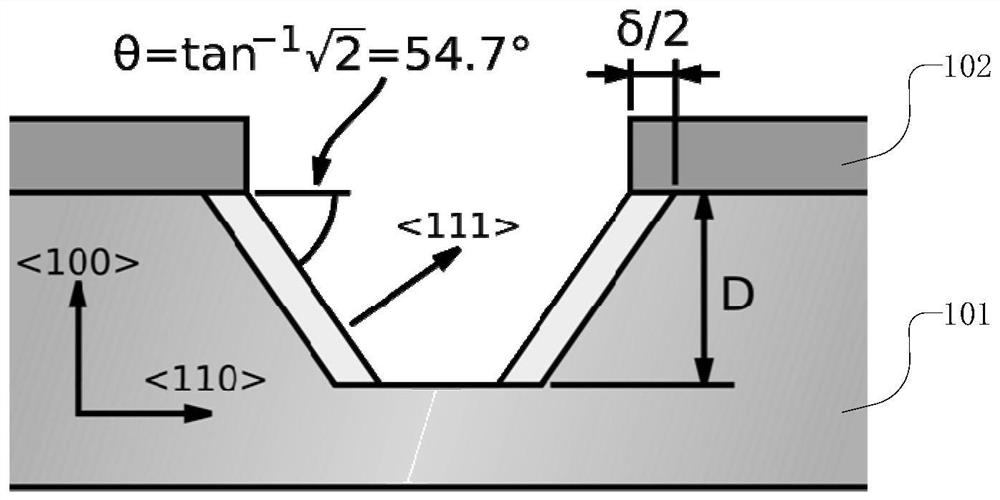

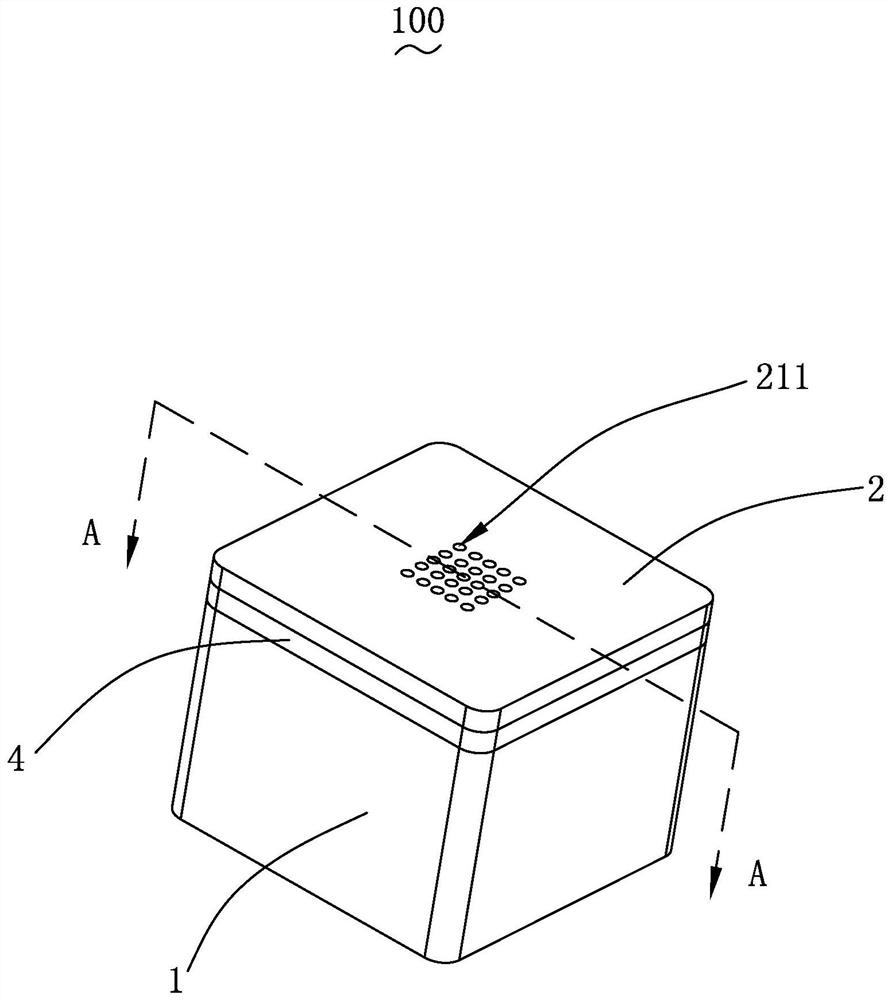

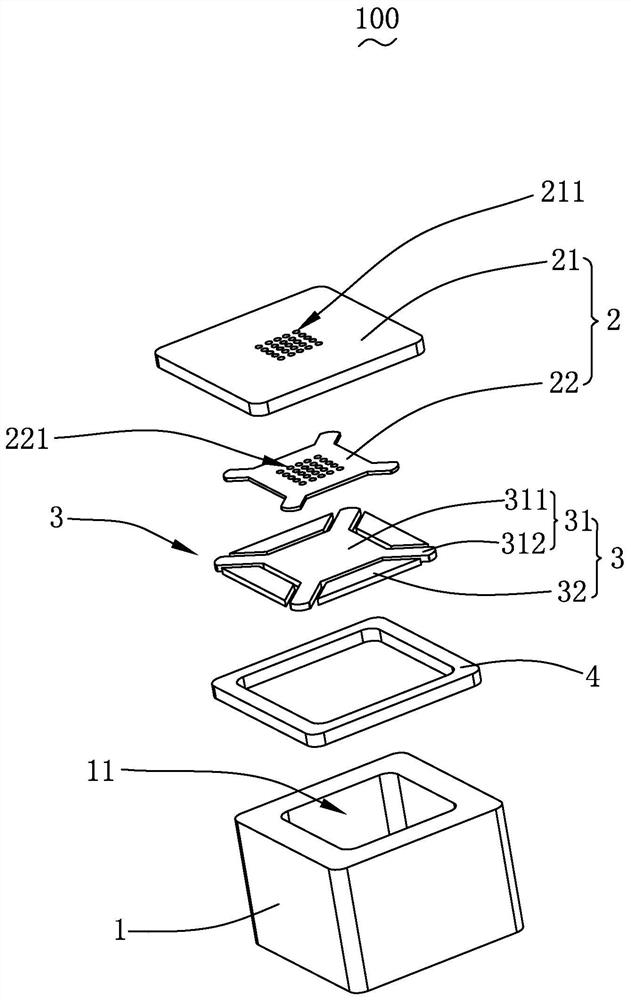

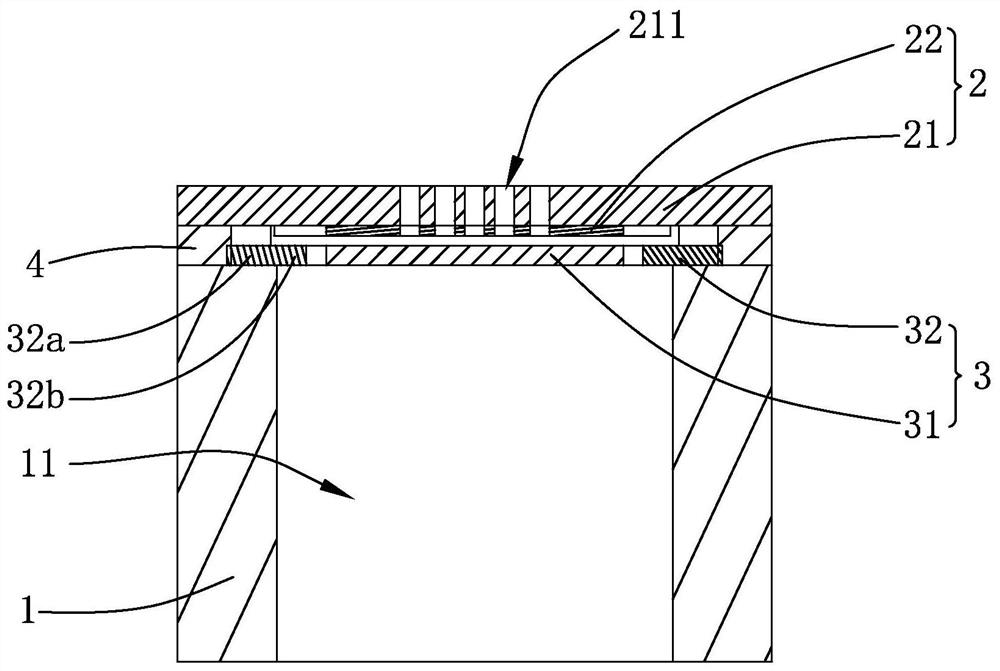

MEMS microphone

ActiveCN107484051AIncrease effective capacitanceImprove acoustic performanceMouthpiece/microphone attachmentsDiaphragm constructionCapacitanceMems microphone

The invention provides a MEMS microphone. The MEMS microphone comprises a substrate with a vocal cavity, back polar plates fixed on the substrate and vibration films which are arranged oppositely to the back polar plate alternately to form capacitive structures, wherein the back polar plate comprises a back plate and a fixed electrode; the vibration film comprises an effective vibration part and an invalid vibration part; the effective vibration part comprises a vibration body arranged oppositely to the vocal cavity and a fixed arm that is extended by the vibration body and fixed on the substrate; the parts of the vibration body and the fixed arm which are opposite to the vocal cavity form an effective vibration area; the invalid vibration part is located between two adjacent fixed arms and is arranged at intervals with the effective vibration part; the invalid vibration part is at least partially fixed on the substrate; the fixed electrode is the same as the shape of the effective vibration area. Compared with the related technology, the MEMS microphone provided by the invention has better acoustic performance.

Owner:AAC ACOUSTIC TECH (SHENZHEN) CO LTD

Thin film balun

ActiveUS20100164643A1Avoid resonant frequencyPreferable characteristicMultiple-port networksOne-port networksEngineeringCapacitor

The present invention provides a thin film balun capable of preventing a resonant frequency from being increased to a high frequency, and thus realizing a preferable passage characteristic. A thin film balun 1 includes: an unbalanced transmission line 2 having a first coil portion C1 and a second coil portion C2; and a balanced transmission line 3 having a third coil portion C3 and a fourth coil portion C4 which are magnetically coupled with the first coil portion C1 and the second coil portion C2, respectively. The first coil portion C1 is connected to an unbalanced terminal T0, and the second coil portion C2 is connected to a ground terminal G (ground potential) via a capacitor D (C component). The third coil portion C3 is connected to a balanced terminal T1 and the fourth coil portion C4 is connected to a second balanced terminal T2. The capacitor D is provided, in a plan view, in an area S1 between the outer end of the unbalanced terminal T0 and the outer end of the ground terminal G.

Owner:TDK CORPARATION

Pixel structure

ActiveUS10026361B2Reduce in quantitySave spaceSolid-state devicesCathode-ray tube indicatorsControl signalCapacitor

A pixel structure includes a pixel unit layer and a first metal wire layer. Each of control signal line and first and second scan signal lines in the first metal wire layer is connected to each pixel unit in a corresponding row. An insulating layer is disposed between each first metal patterned section in the first metal wire layer and a corresponding row of pixel units. A second metal wire layer includes initial signal lines and second metal patterned sections. Each initial signal line is connected to each pixel unit in a corresponding row. Each second metal patterned section overlaps with one of the first metal patterned sections to form a capacitor. Each connection signal line in a third metal wire layer connects the first scan signal line of a current row of pixel units to the second scan signal line of a next row of pixel units.

Owner:EVERDISPLAY OPTRONICS (SHANGHAI) CO LTD

Method of forming a metal-insulator-metal capacitor

ActiveUS20100109124A1Increase effective capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingLateral recessEngineering

Owner:TAIWAN SEMICON MFG CO LTD

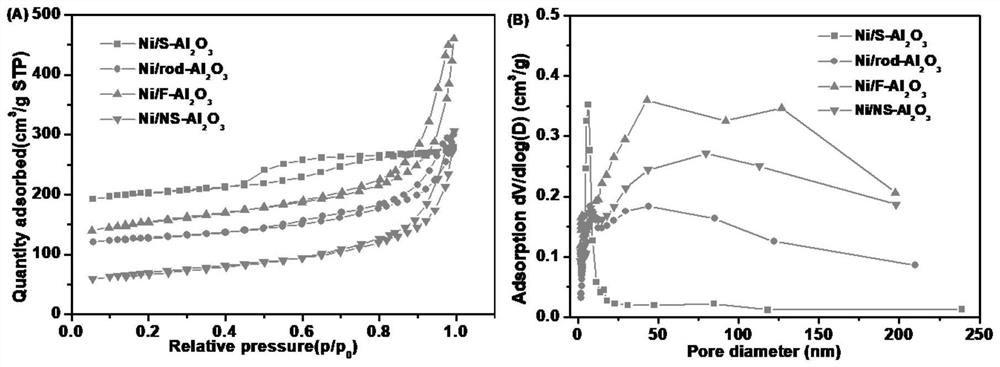

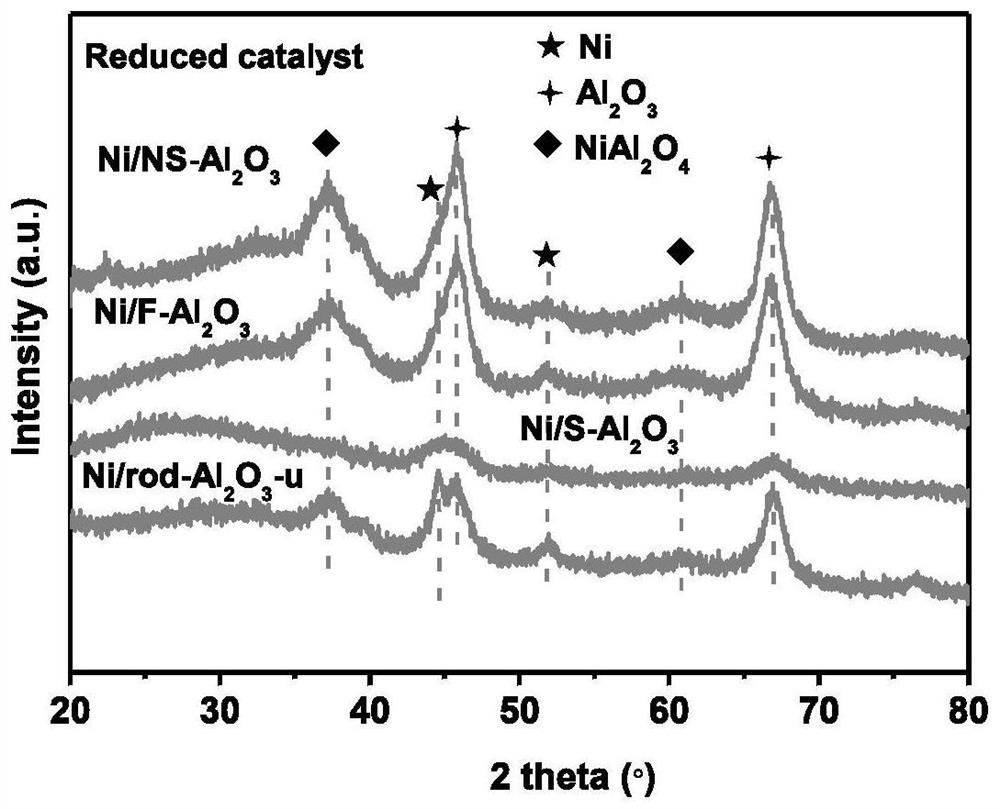

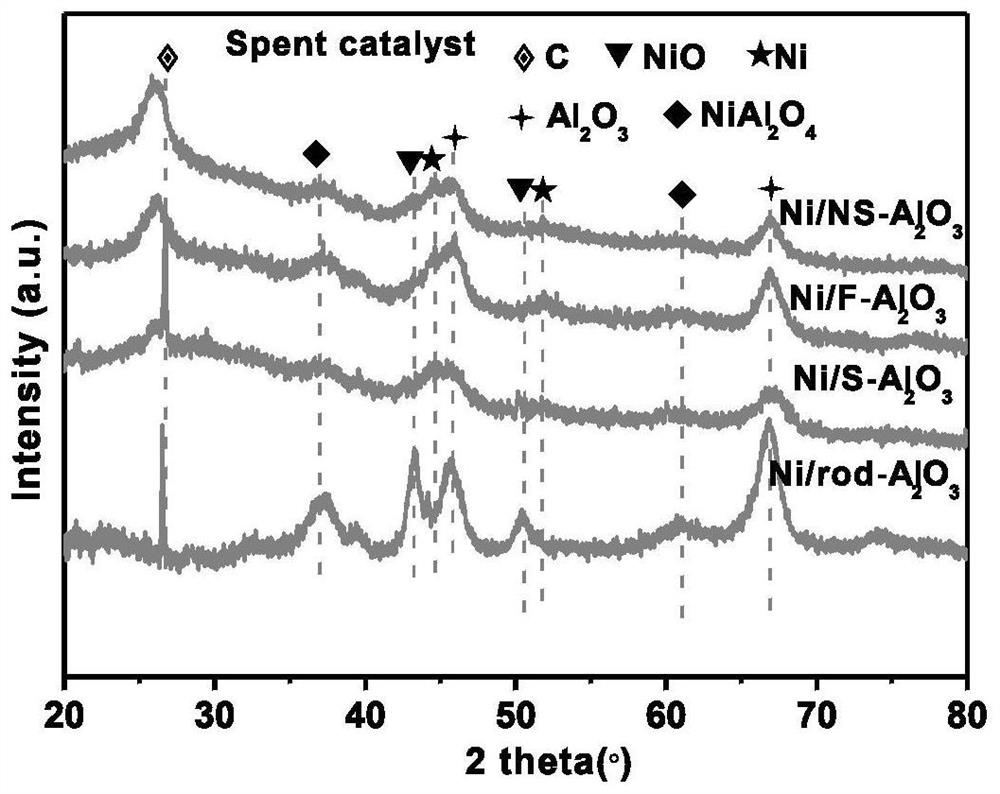

Application of alumina-loaded Ni catalyst with specific microstructure in preparation of synthesis gas by plasma catalytic methane dry reforming

ActiveCN114249300AImprove anti-sintering performanceLarge specific surface areaHydrogenHydrogen/synthetic gas productionPtru catalystPhysical chemistry

The invention provides a method for improving reaction performance and energy efficiency of synthesis gas prepared by low-temperature methane dry reforming through coupling of plasma and a specific microstructure catalyst, and the method comprises the following steps: taking methane and carbon dioxide as raw materials, taking Ni / Al2O3 as a catalyst, carrying out reaction in a plasma reactor, and preparing the synthesis gas under mild conditions; and the Al2O3 is one or a mixture of more of nano sheet-shaped Al2O3, feather-shaped Al2O3, ball-flower-shaped Al2O3 and rod-shaped Al2O3 with different microstructures. The carriers with different structures directly influence dispersion, stability and discharge capacitance of Ni particles, so that the catalytic performance of Ni / Al2O3 under mild conditions is influenced. According to the method, the dispersity of metal Ni is remarkably improved, meanwhile, the energy efficiency of the catalyst and the discharge stability of the catalyst under the plasma discharge condition are improved, and efficient conversion of CH4 and CO2 under the mild condition is achieved.

Owner:DALIAN UNIV OF TECH

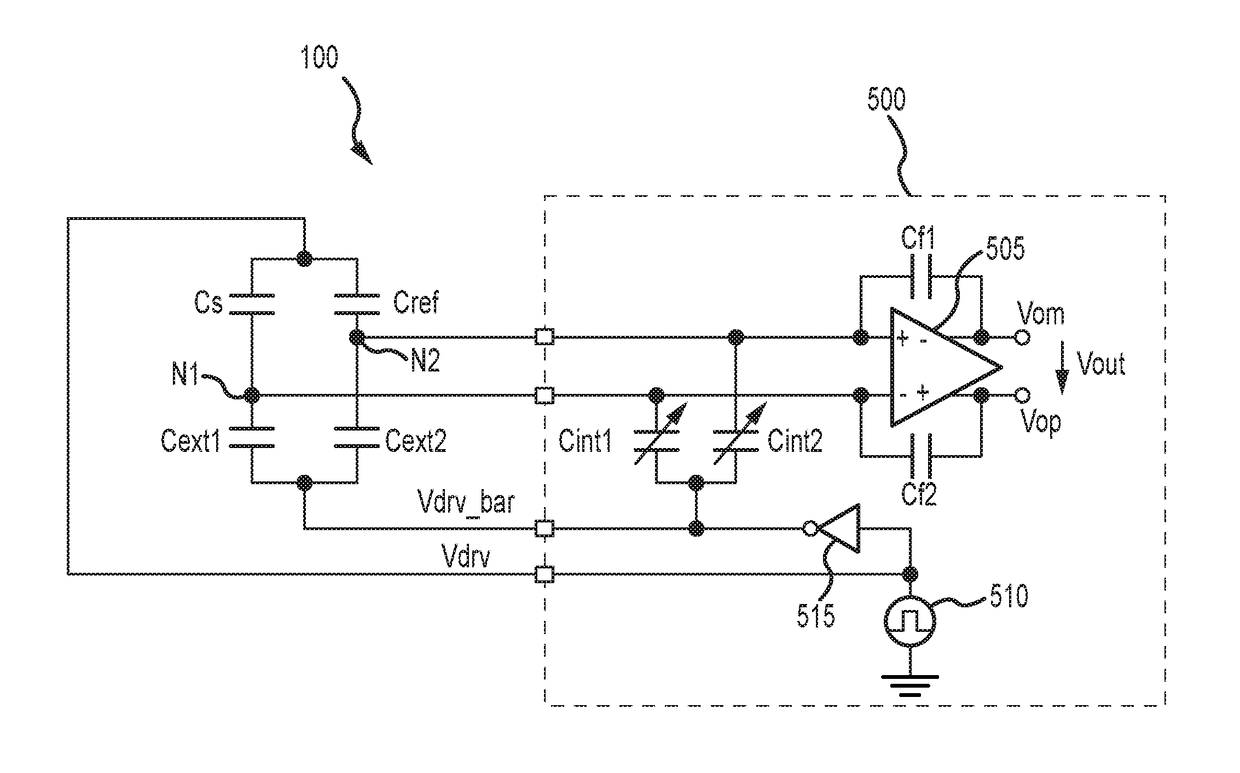

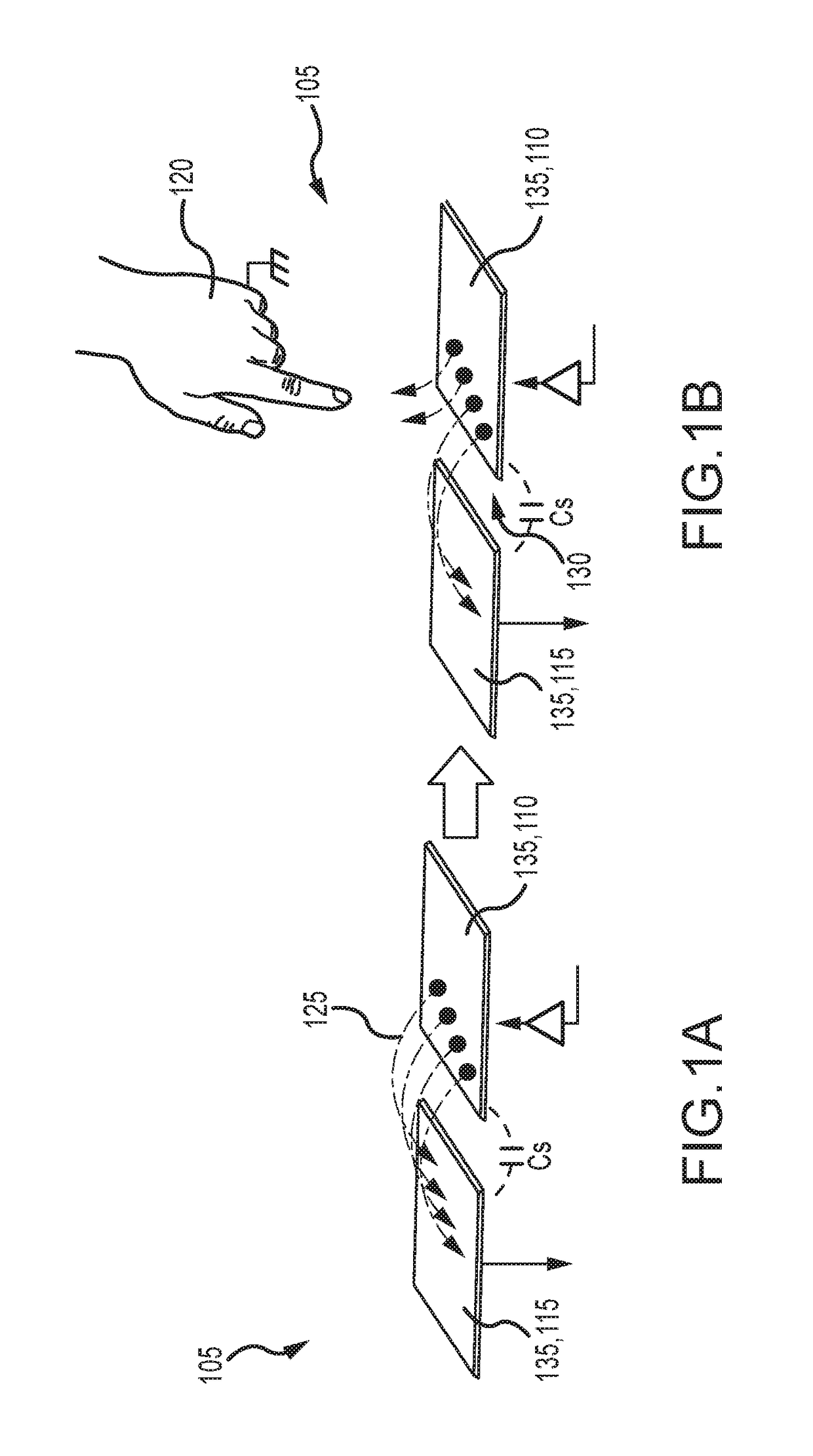

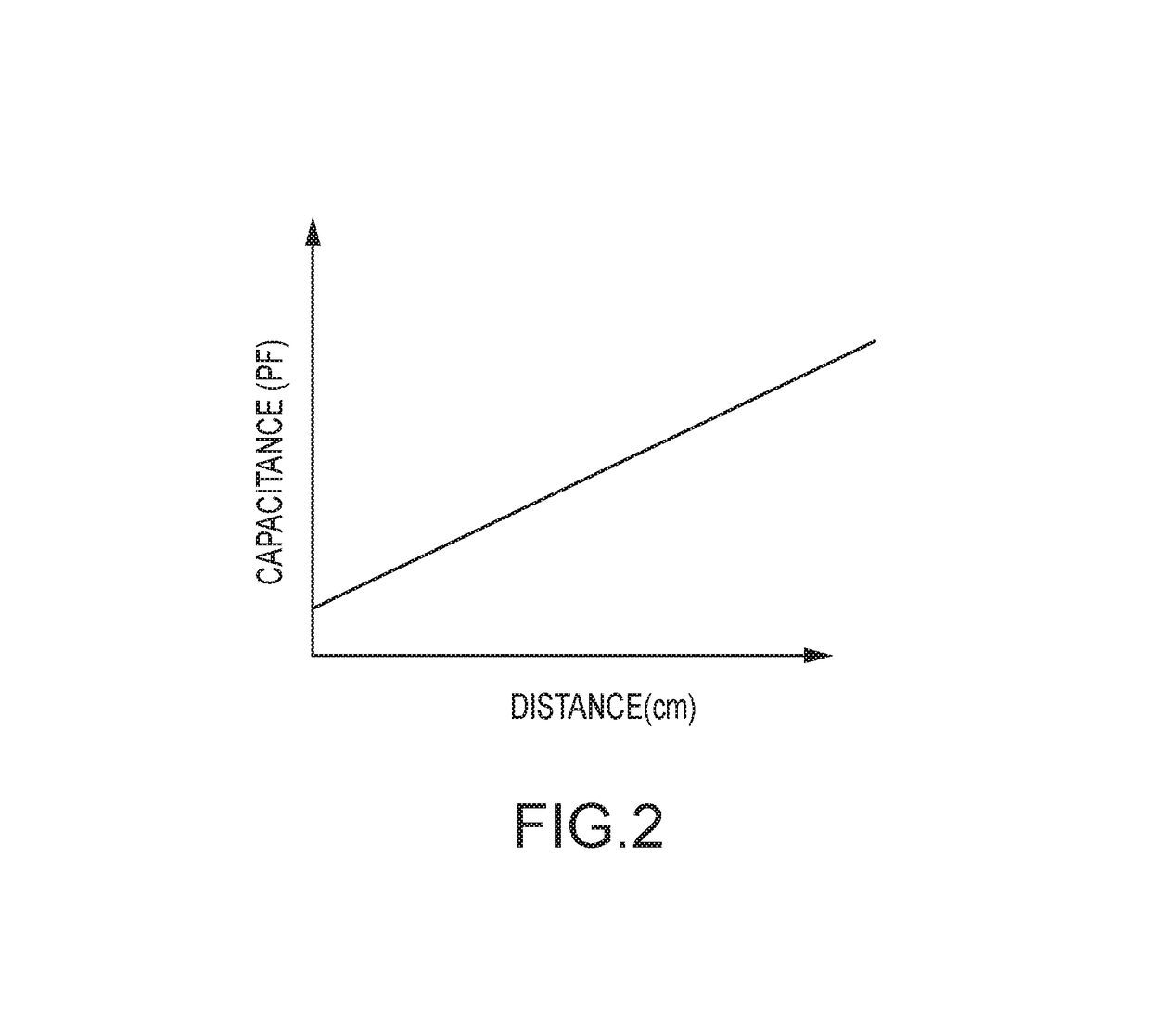

Methods and apparatus for a capacitive sensor

ActiveUS10073574B2High sensitivityIncrease effective capacitanceInput/output processes for data processingProximity sensorInternal variable

Various embodiments of the present technology may comprise methods and apparatus for increased sensitivity of a capacitive proximity sensor. The method and apparatus may comprise additional external capacitors coupled in parallel with internal variable capacitors to increase the effective capacitance of a detection circuit allowing for a larger sensing element, and therefore a stronger sensing field, without increasing the applied voltage or the internal capacitance of the proximity sensor. In alternative embodiments, the methods and apparatus may be configured to operate as one of a transmission electrode and a reception electrode to increase the strength of the sensing field.

Owner:SEMICON COMPONENTS IND LLC

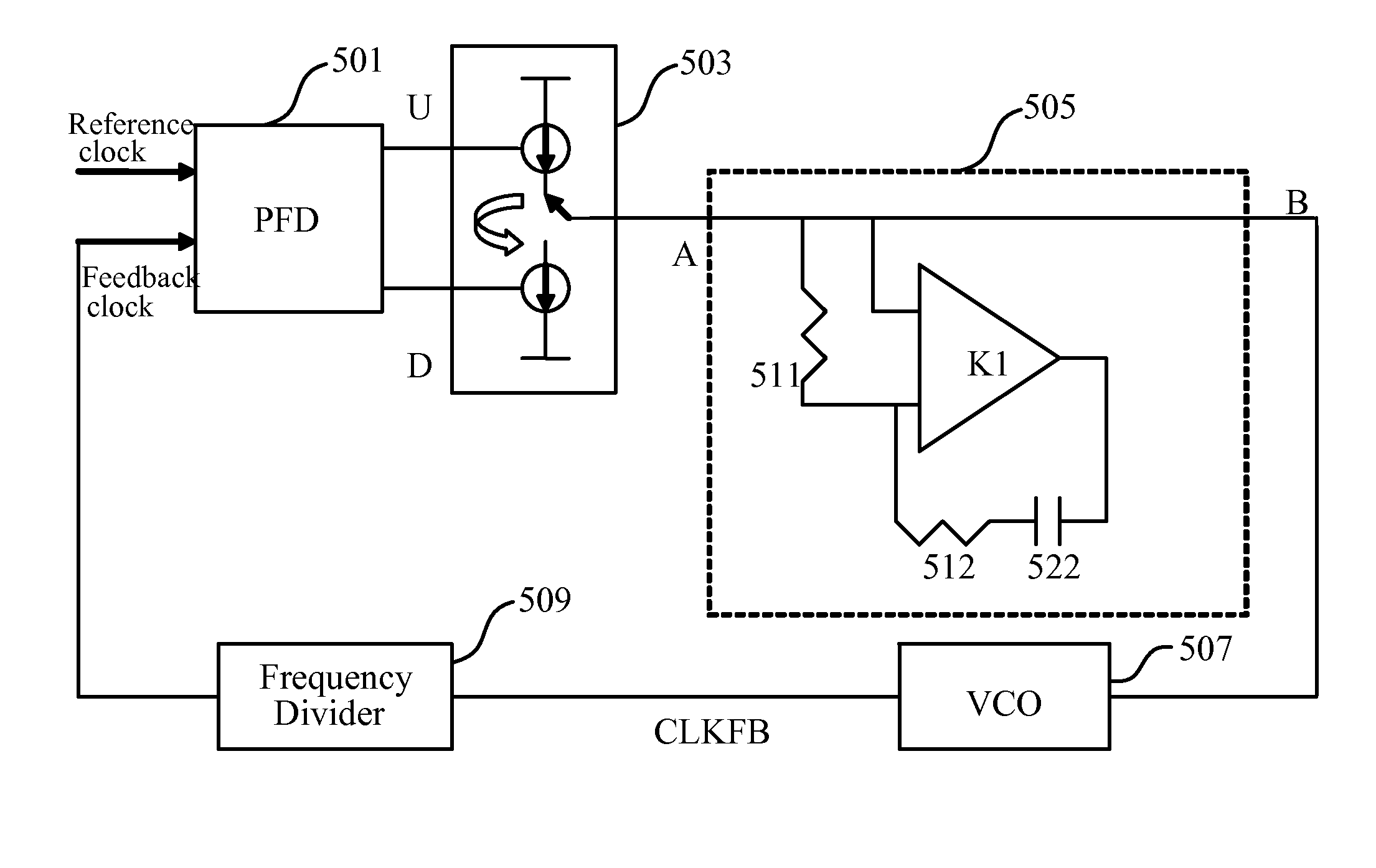

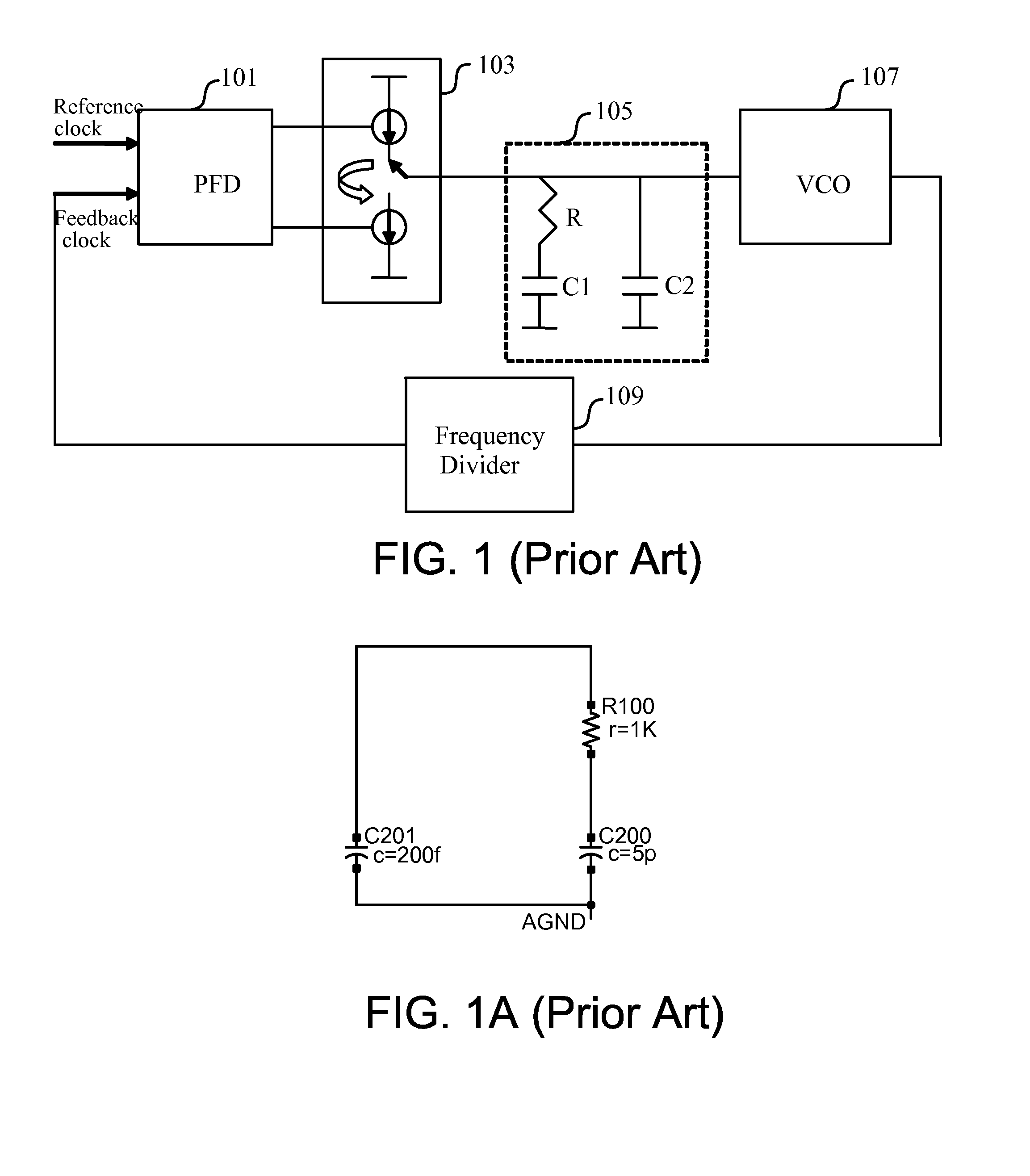

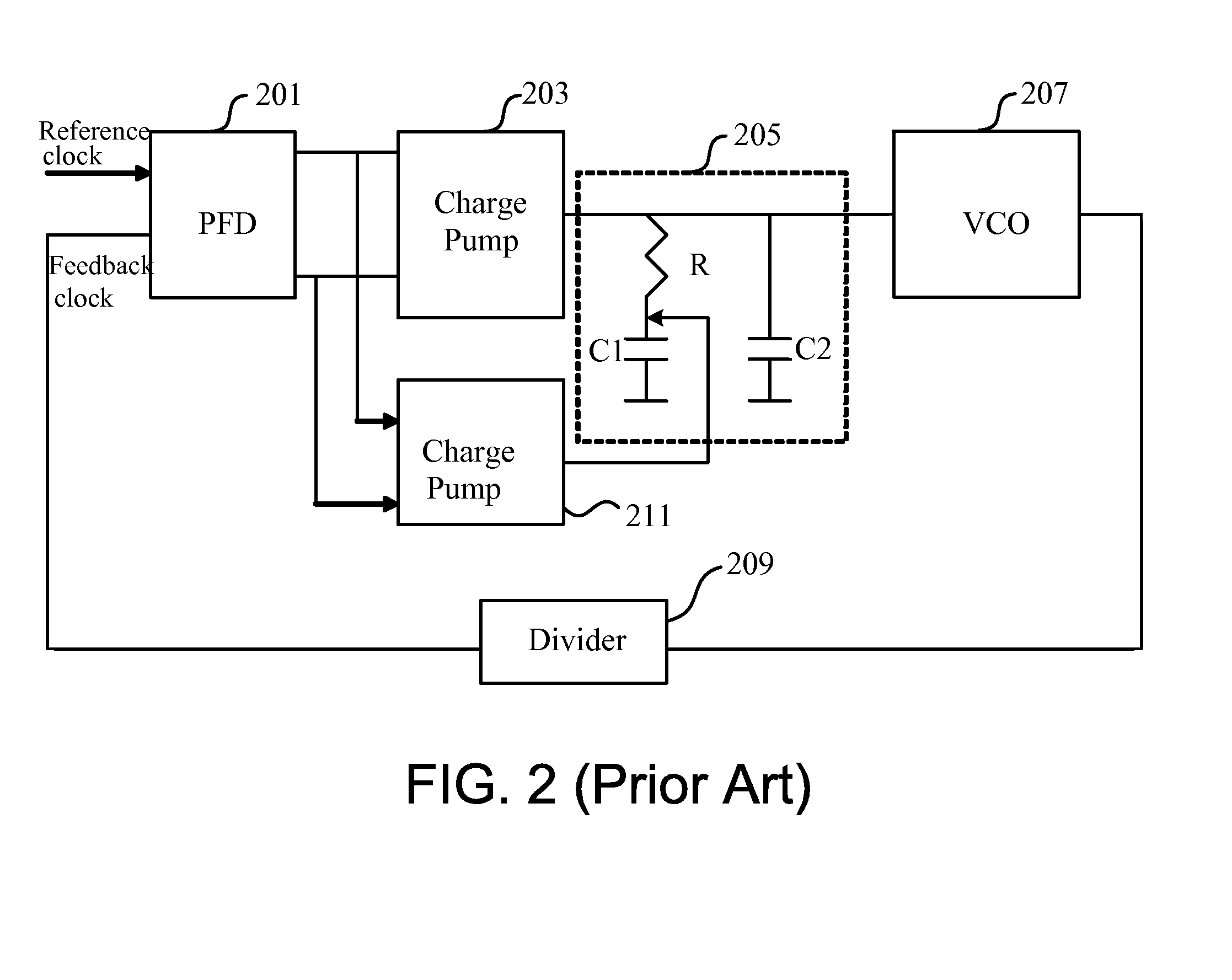

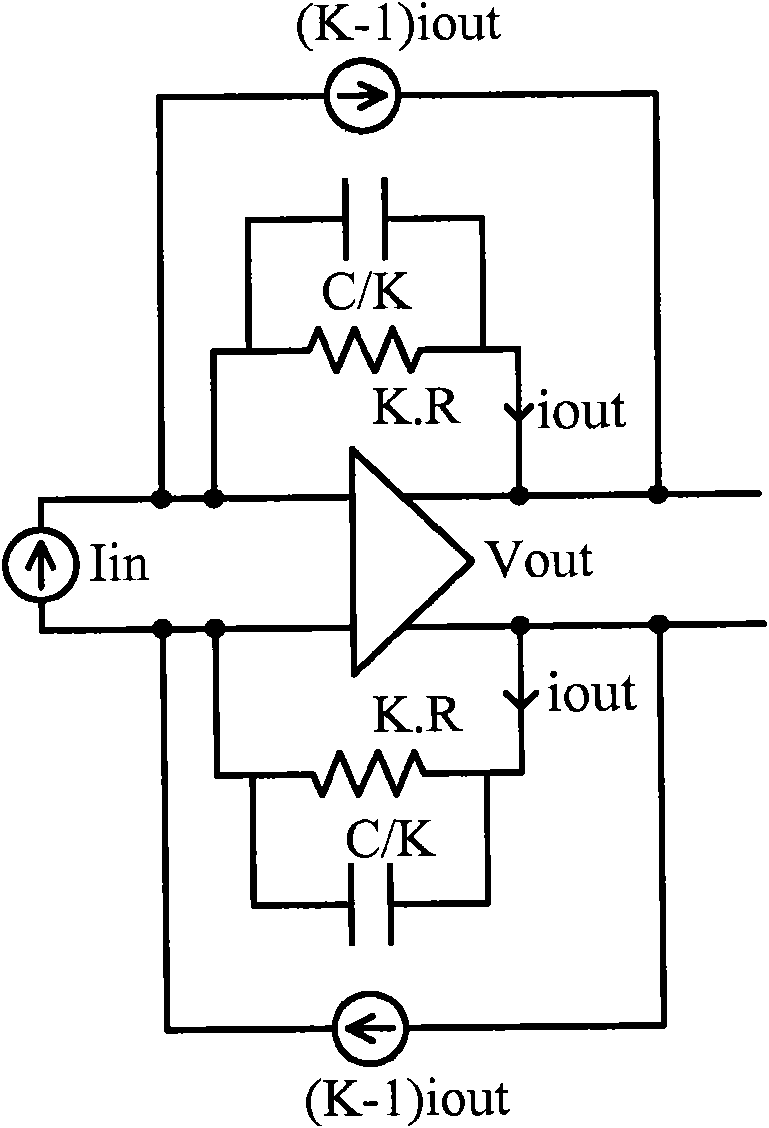

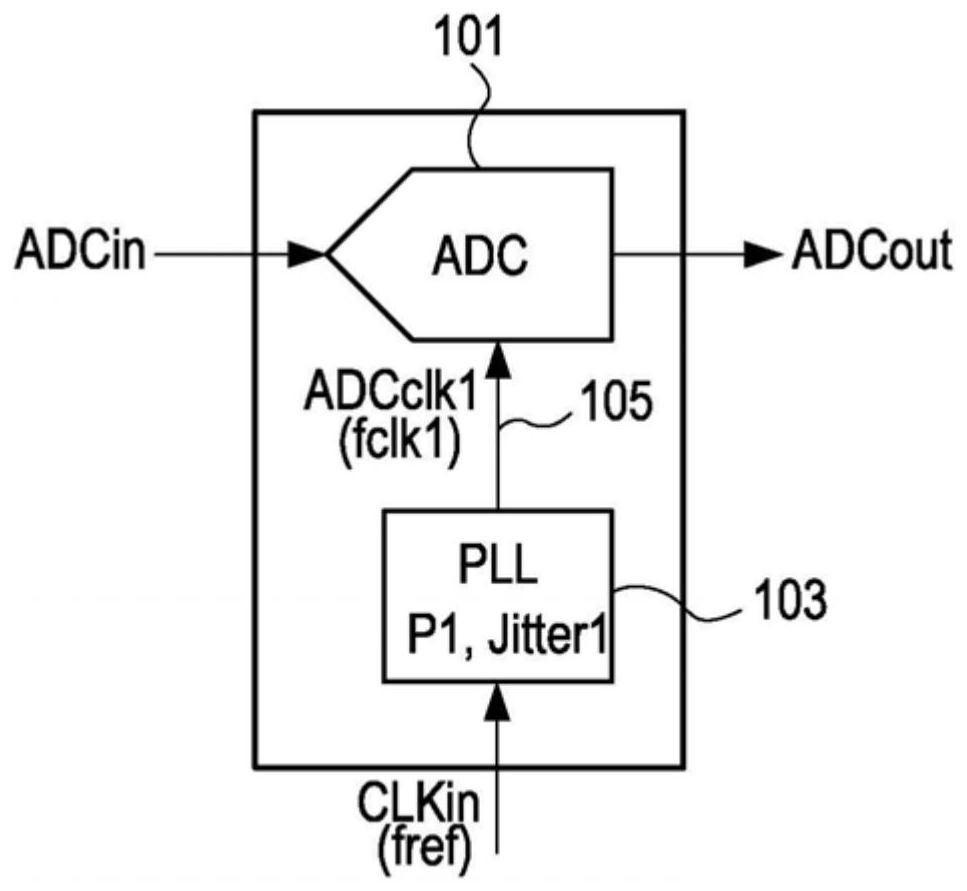

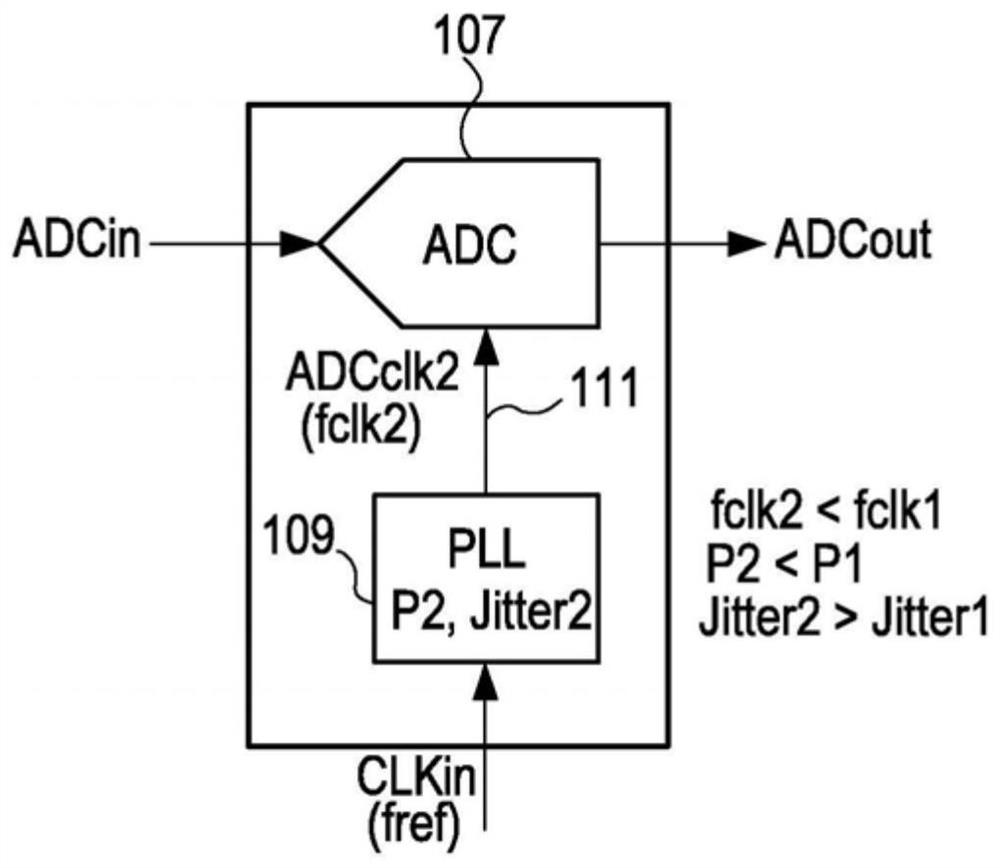

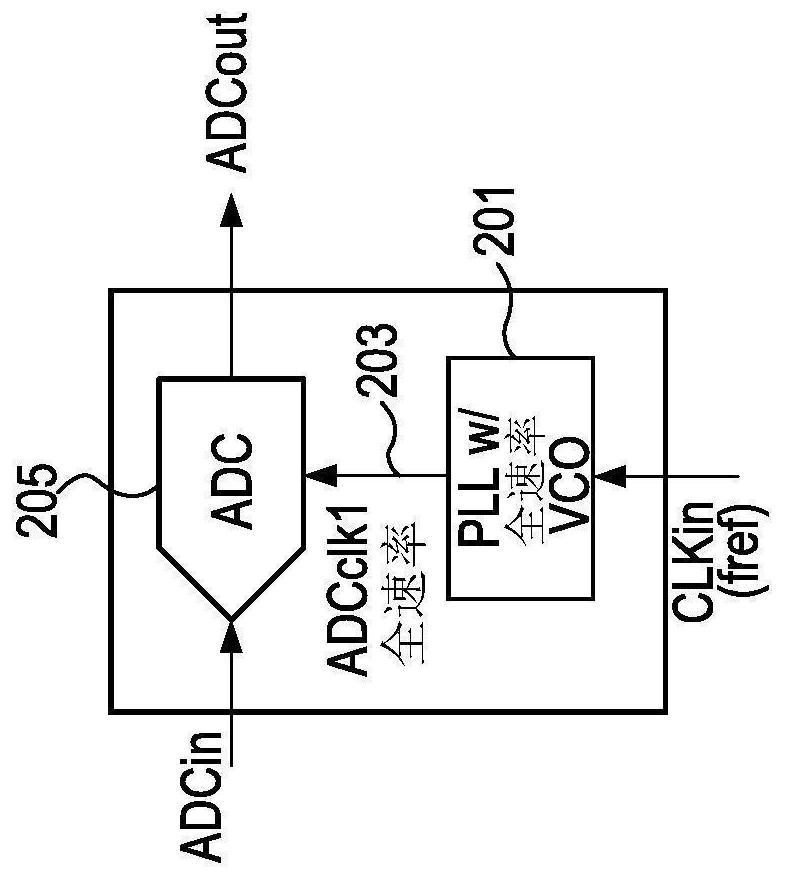

Adjustable pole and zero location for a second order low pass path filter used in a phase lock loop circuit

InactiveUS20140184287A1Reduce areaIncrease effective capacitancePulse automatic controlOscillations generatorsCapacitanceLoop filter

This invention provides a loop filter device and a method for IC designers to adjust the pole or zero location of a phase lock loop (PLL) circuit. The pole and zero location are controlled by an amplifier and some on-chip resistor and capacitor components. The effective capacitance is magnified by the gain of the amplifier. The advantage of the loop filter device and the method according to embodiments of the present invention provides a feasible way to achieve a very low bandwidth in the PLL circuit without a huge external surface-mount capacitor.

Owner:DANG YEN

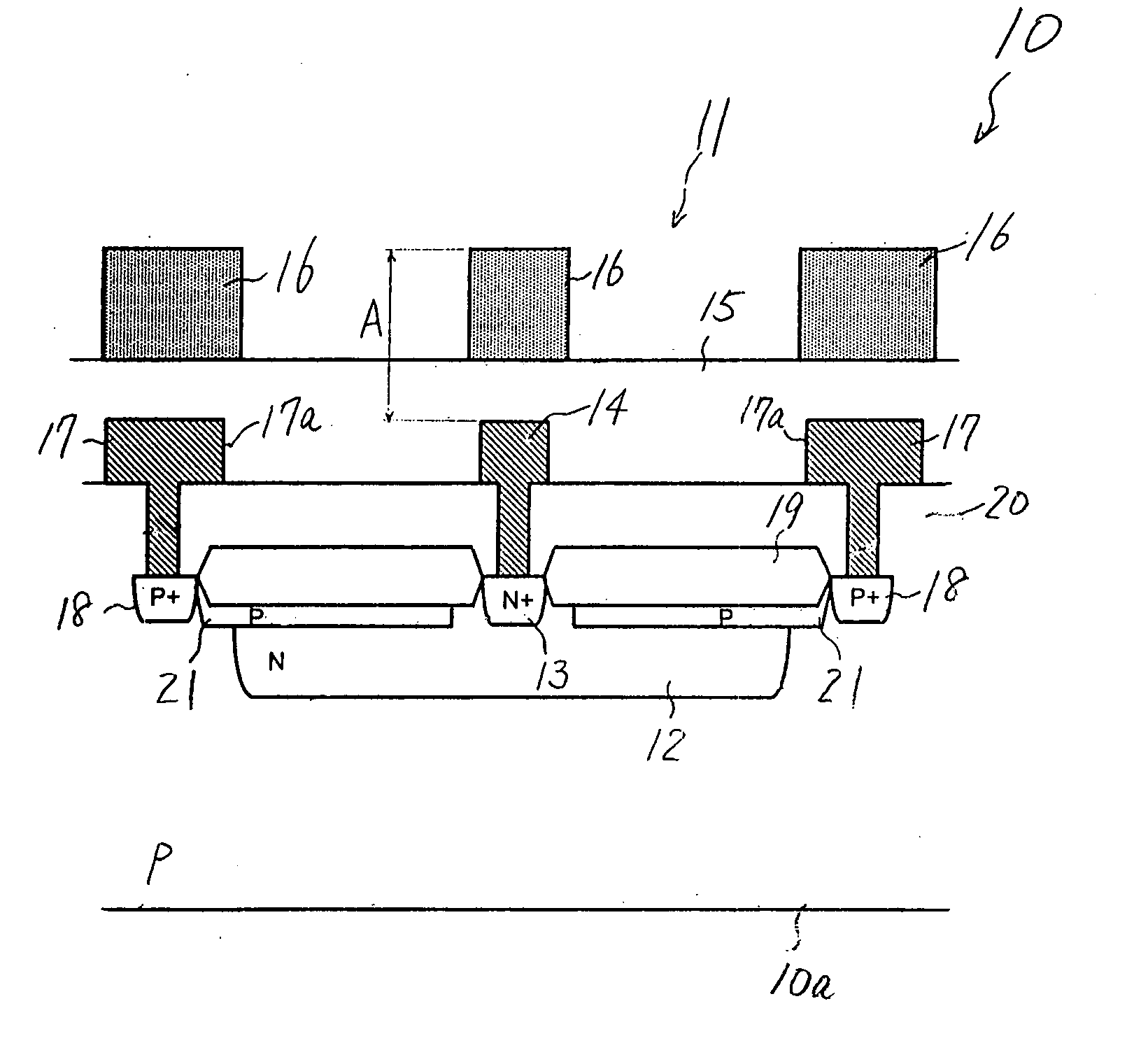

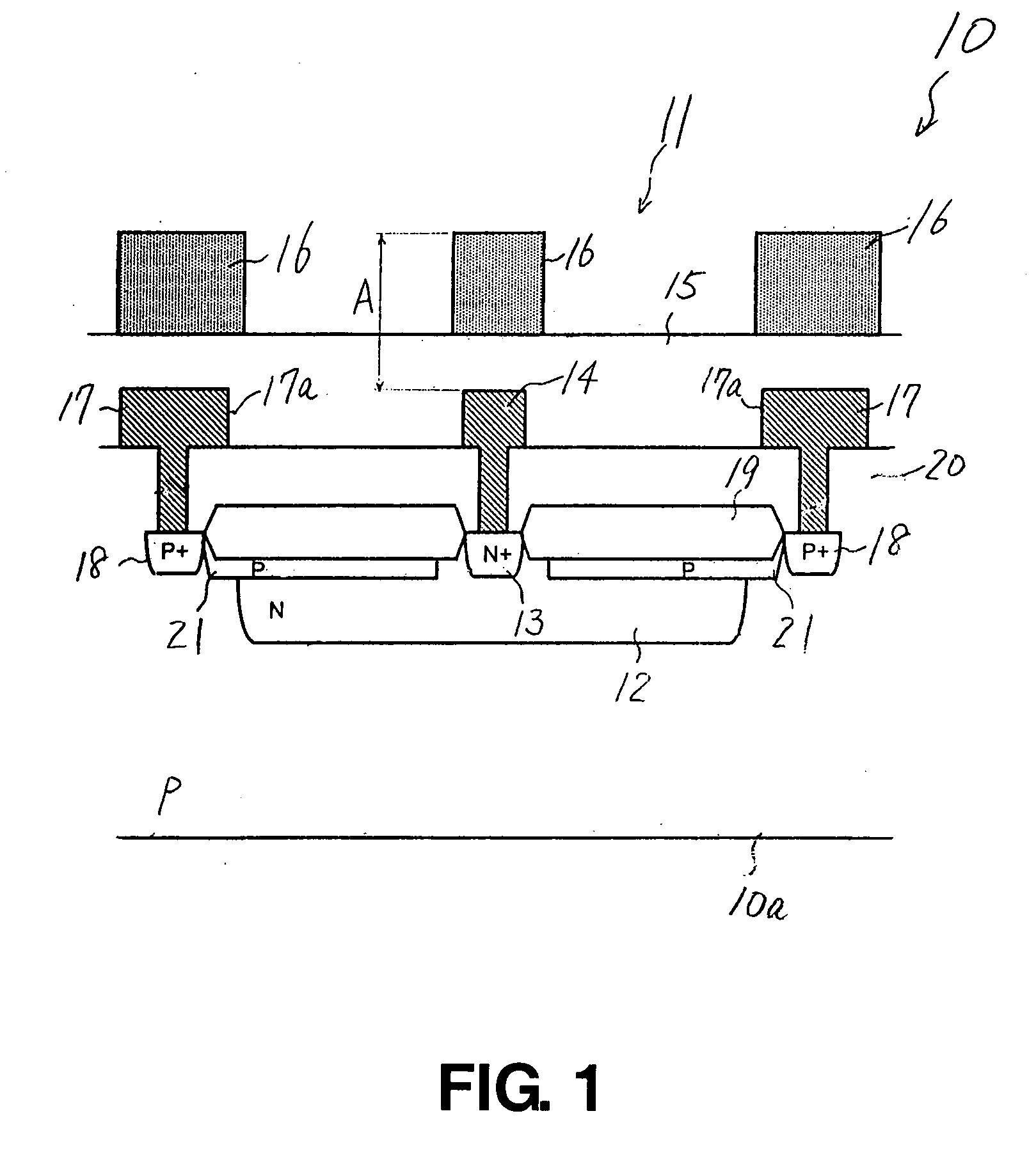

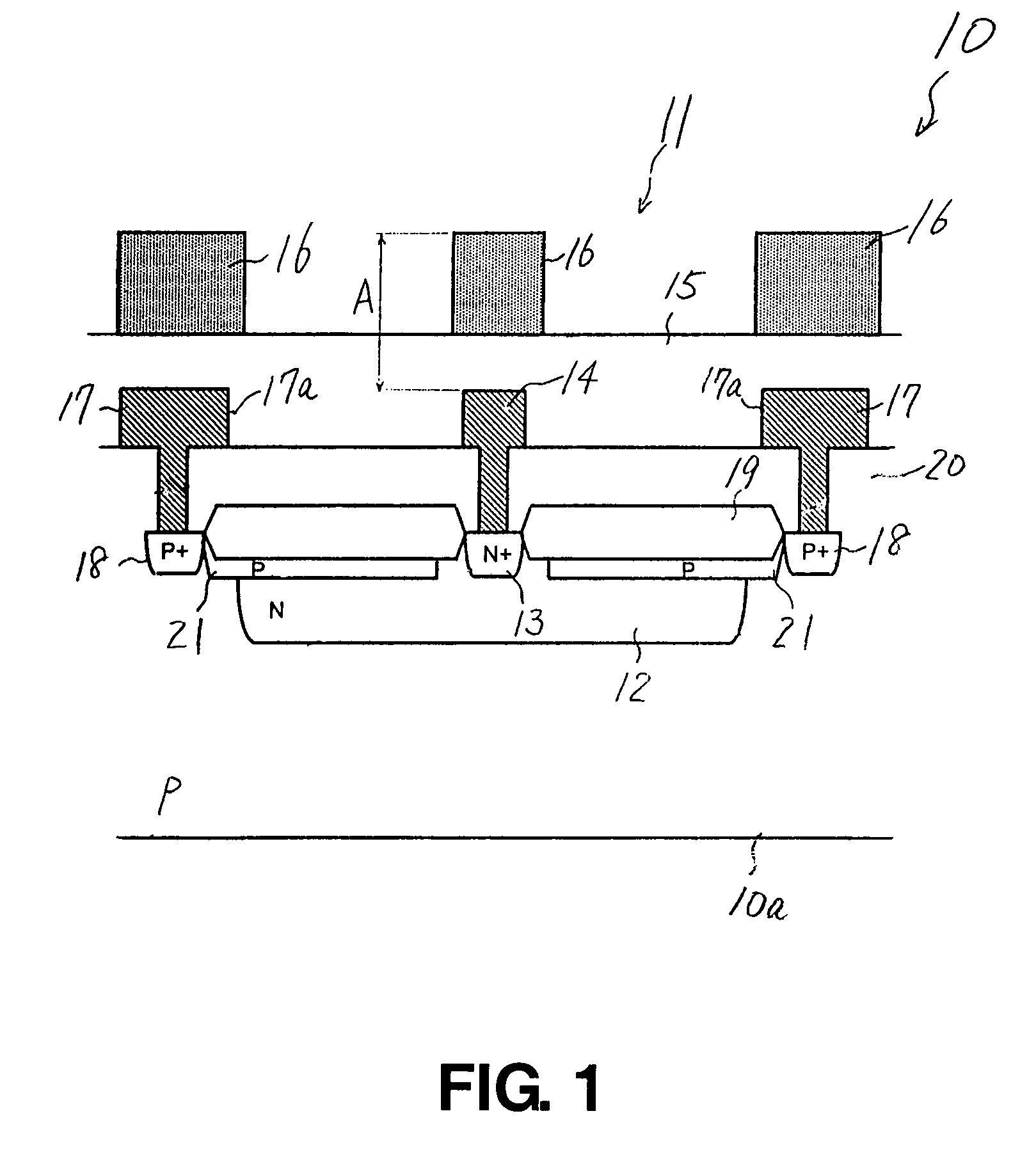

Photoelectric conversion device and image sensor

InactiveUS20070210396A1Reduce capacitanceAvoid desensitizationSolid-state devicesSemiconductor devicesFiberOrganic film

A photoelectric conversion device (10) includes a first conductivity type first semiconductor region (10a) located in a pixel region (11), a second conductivity type second semiconductor region (12) provided in the first semiconductor region (10a), for storing a signal charge, interconnecting portions (13 and 14) for connecting the second semiconductor region (12) with a circuit element provided outside the pixel region (11), and an organic film (16) which is provided above a portion located in the pixel region (11) in the interconnecting portions (13 and 14) through an insulating protective film (15) and held at a predetermined potential. The organic film (16) is made of a thermoplastic polyimide resin containing one of a conductive particle and a conductive fiber.

Owner:ABLIC INC

Thin film balun

ActiveUS20140022028A1Increase effective capacitanceImprove balanceMultiple-port networksOne-port networksEngineeringElectrode

A thin film balun that can be made smaller and thinner while maintaining required balun characteristics is provided. A thin film balun 1 includes: an unbalanced transmission line UL including a first coil portion C1 and a second coil portion C2; a balanced transmission line BL including a third coil portion C3 and a fourth coil portion C4 that are positioned facing and magnetically coupled to the first coil portion C1 and the second coil portion C2 respectively; an unbalanced terminal UT connected to the first coil portion C1; a ground terminal G connected to the second coil portion C2 via a C component D; and an electrode D2 connected to the ground terminal G and facing a part of the second coil portion C2. The C component D is formed by the electrode D2 and the part D1 of the second coil portion C2.

Owner:TDK CORPARATION

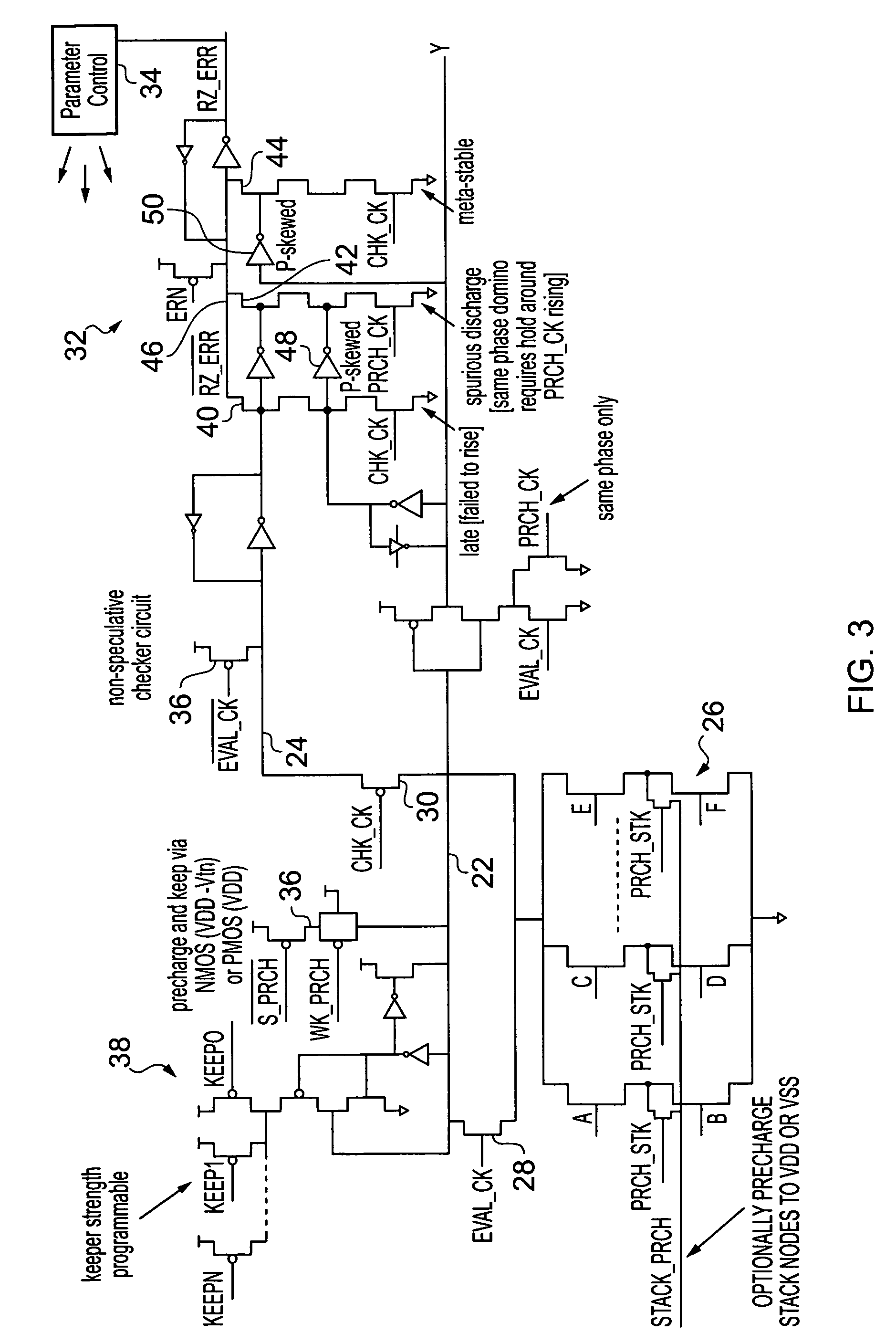

Error detection in precharged logic

ActiveUS8006147B2Increases magnitudeHigh voltageElectronic circuit testingStatic storageDomino logicControl circuit

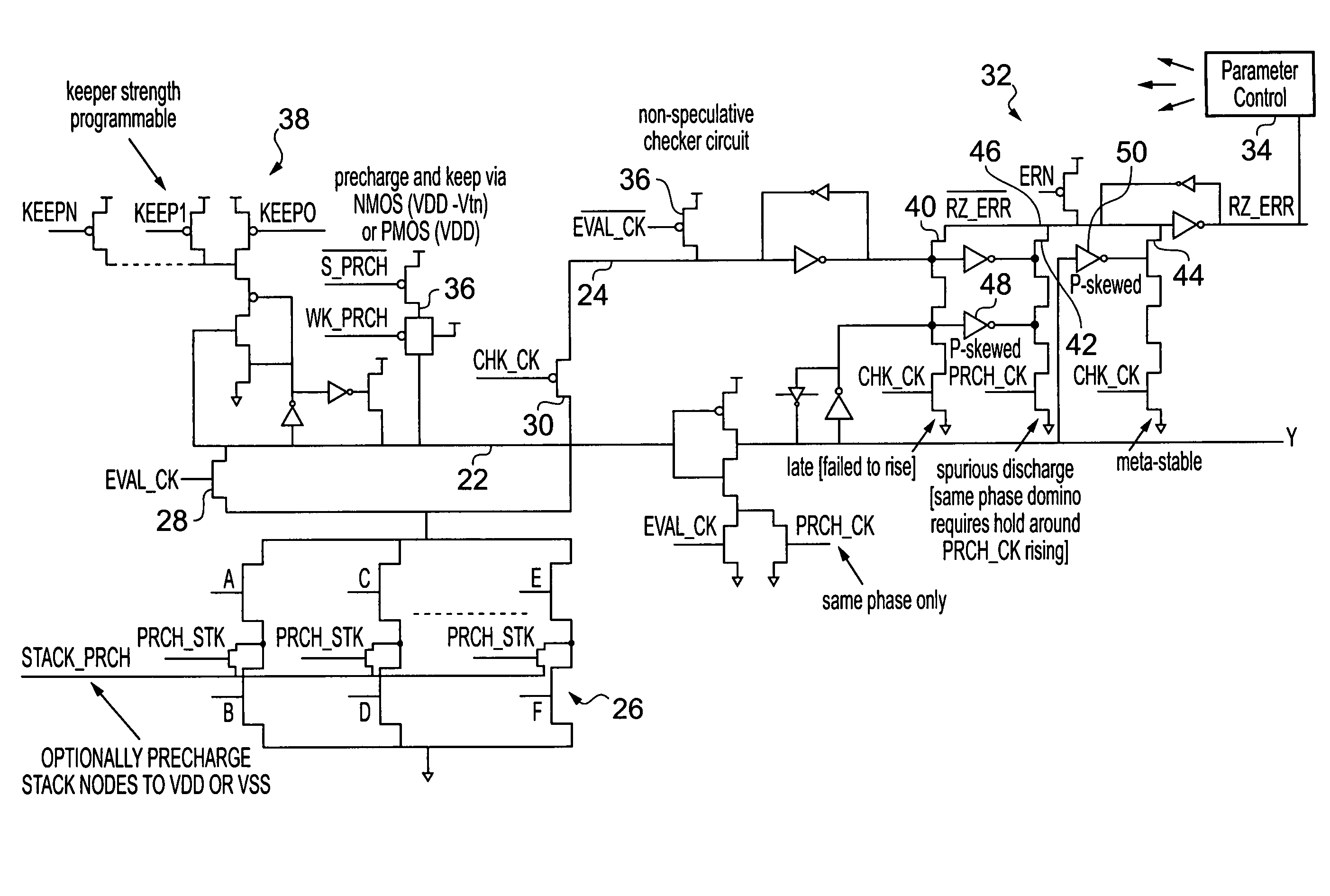

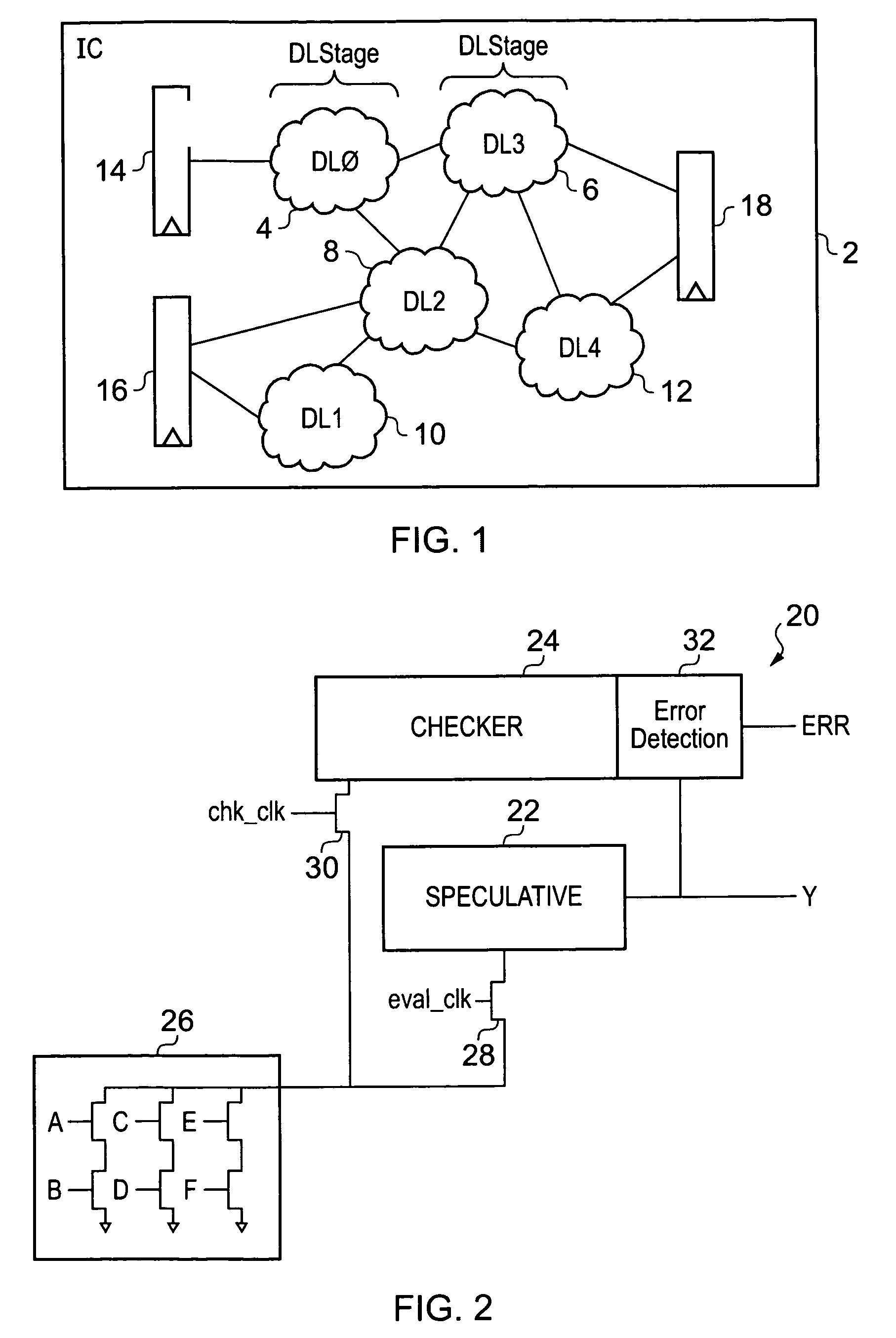

An integrated circuit is provided with domino logic including a speculative node and a checker node. Precharged circuitry precharges both the speculative node and the checker node. Logic circuitry provides a discharge path for the speculative node and the checker node in dependence upon input signal values. Evaluation control circuitry first couples the speculative node to the logic circuitry and then subsequently couples the checker node to the logic circuitry such that these can be discharged if the input signals to the logic circuitry have appropriate values. Error detection circuitry detects an error when the speculative node and the checker node are not one of both discharged or both undischarged.

Owner:RGT UNIV OF MICHIGAN +1

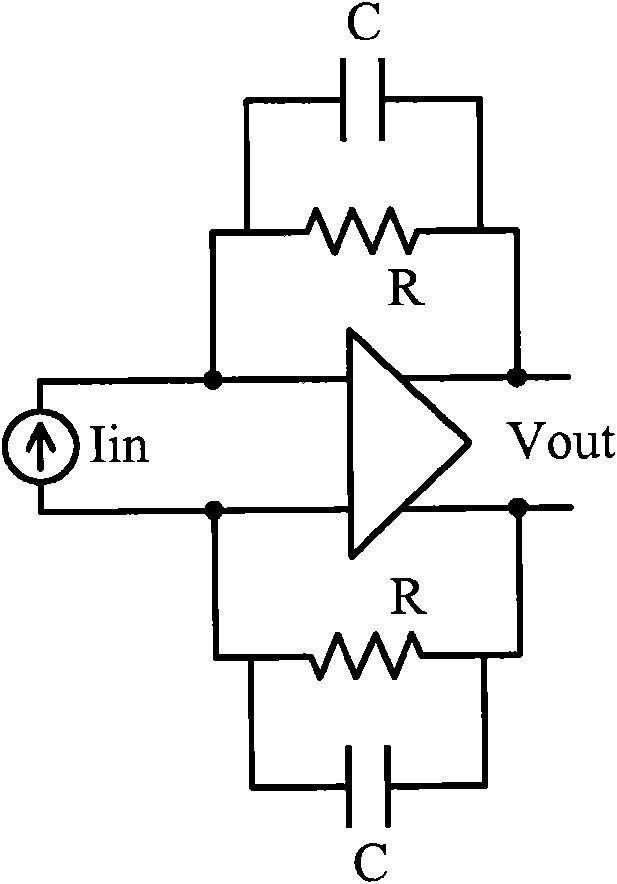

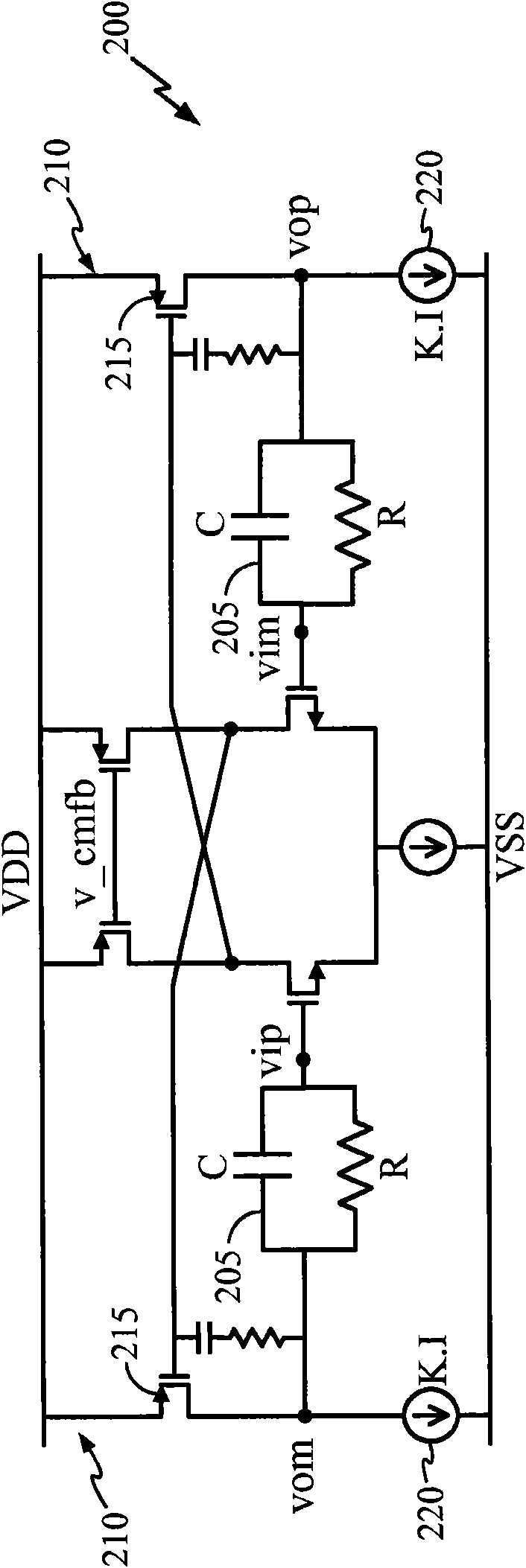

Capacitance multiplier circuit

ActiveCN101978600AIncrease effective capacitanceImpedence convertorsNetwork simulating reactancesCapacitancePower flow

A capacitance multiplier circuit is configured to sense a current through a capacitor in an RC filter of the circuit and to multiply the current so as to achieve a capacitance multiplier effect without adding additional circuitry or requiring additional power. The circuit includes an RC filter, a first signal path connected to a filter output, and a second signal path connected to an input to the filter. A current output through the filter (iout) is split between the two paths, sensed in the first path and multiplied in the second path. The multiplied current is fed back from the second path to the filter input to raise the effective capacitance of capacitor C. The capacitance multiplier circuit, in raising the effective capacitance of the capacitor in the filter, does not affect the frequency response, linearity performance and / or stability of the overall circuit.

Owner:QUALCOMM INC

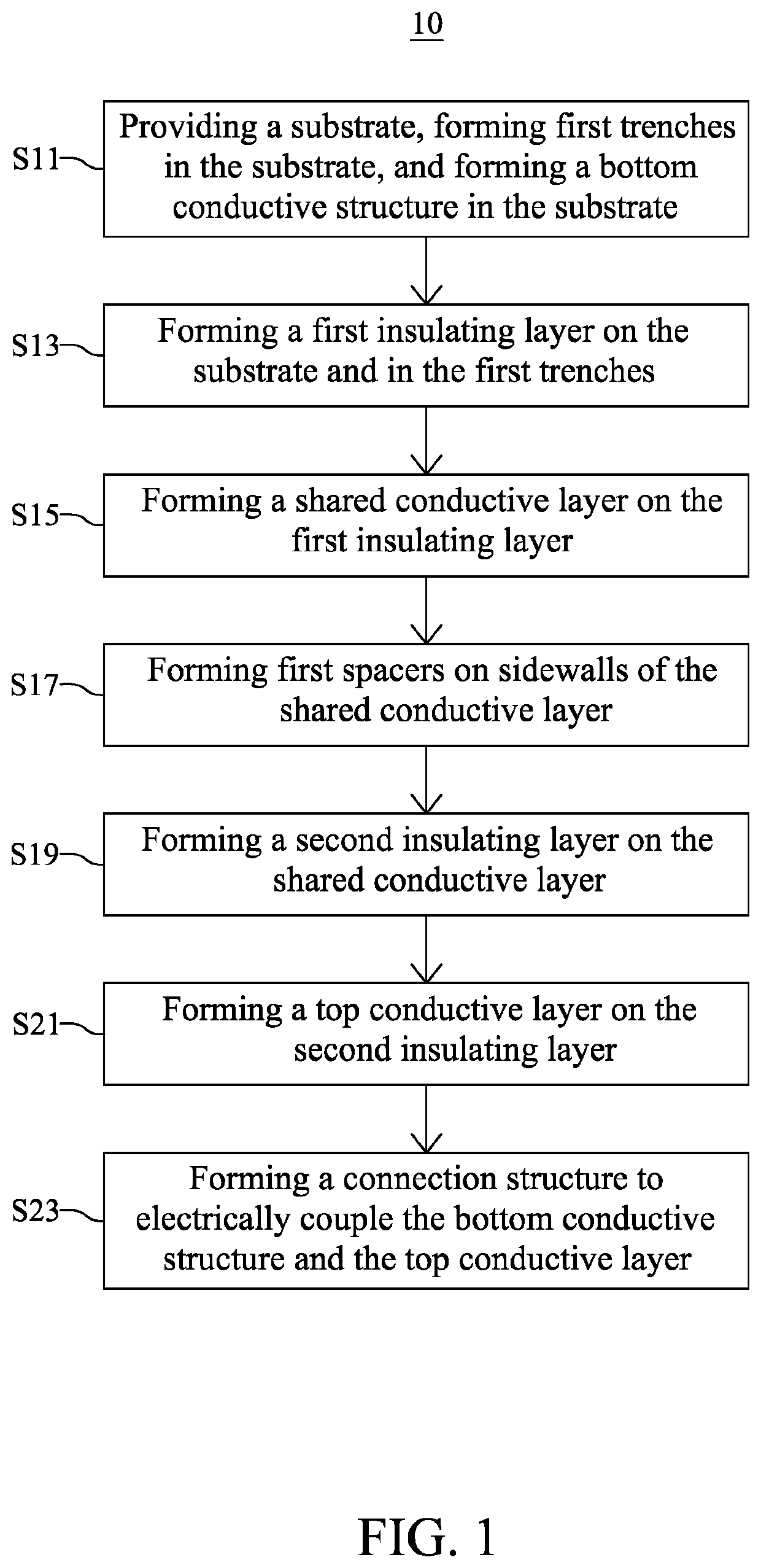

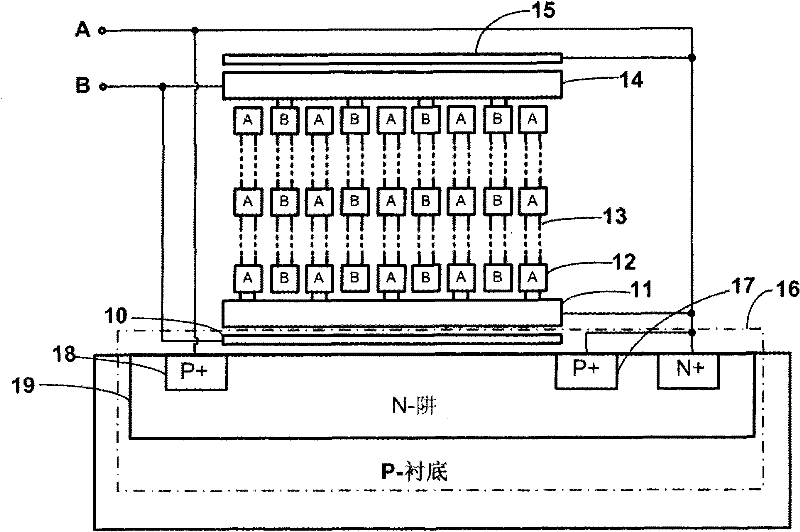

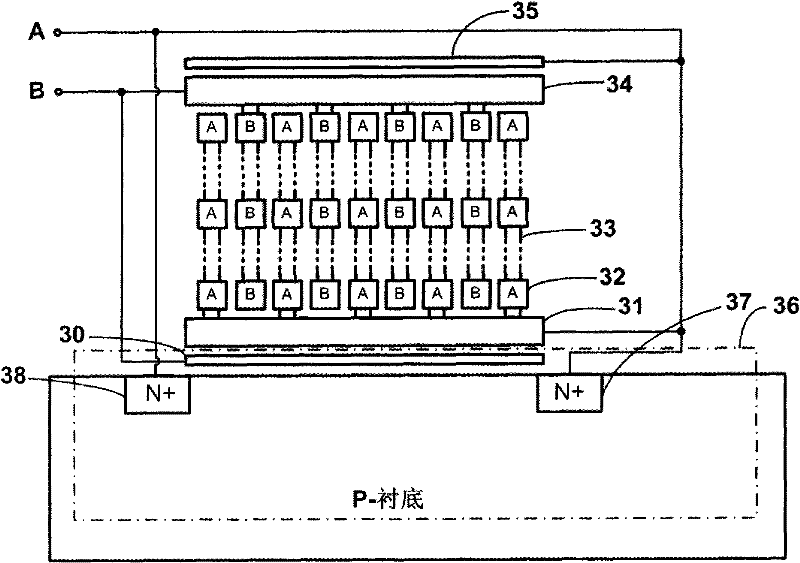

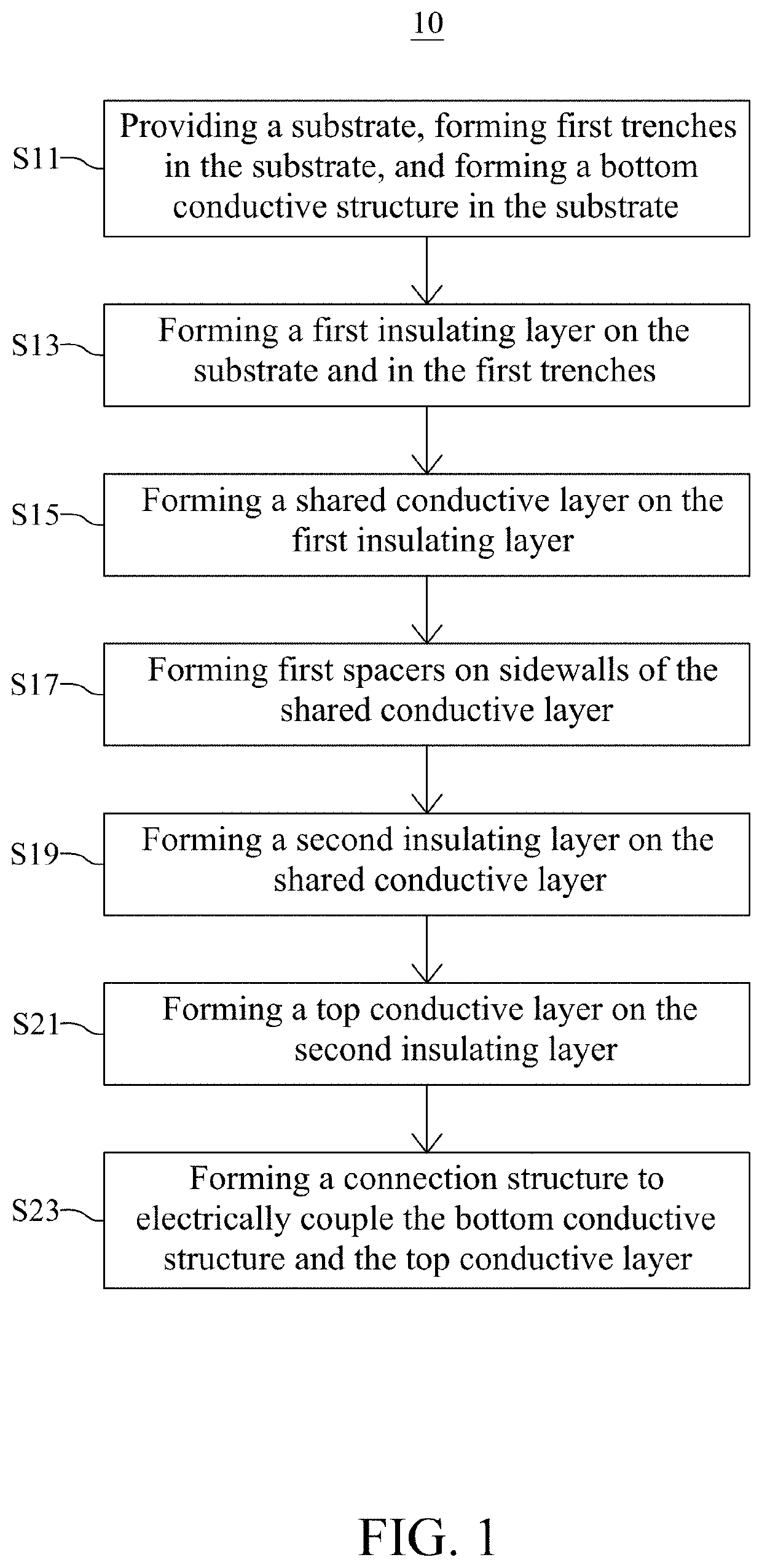

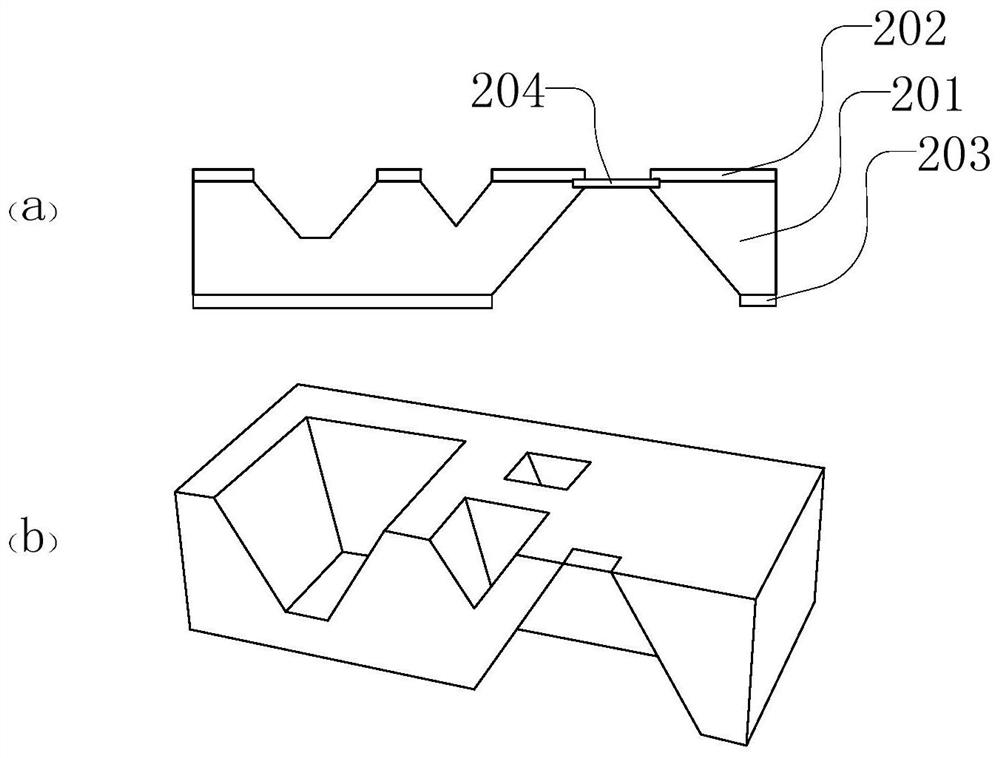

Method for fabricating semiconductor device with capacitors having shared electrode

ActiveUS20220262894A1Increase capacitance densityIncrease effective capacitanceFixed capacitor electrodesSemiconductor/solid-state device detailsCapacitanceDevice material

The present application discloses a method for fabricating a semiconductor device with capacitors having a shared electrode. The method includes providing a substrate, forming a first trench in the substrate, doping sidewalls and a bottom surface of the first trench to form a bottom conductive structure, forming a first insulating layer on the bottom conductive structure and in the first trench, forming a shared conductive layer on the first insulating layer, forming a second insulating layer on the shared conductive layer, forming a top conductive layer on the second insulating layer, and forming a connection structure electrically connecting the bottom conductive structure and the top conductive layer. The bottom conductive structure, the first insulating layer, and the shared conductive layer together configure a first capacitor unit. The shared conductive layer, the second insulating layer, and the top conductive layer together configure a second capacitor unit.

Owner:NAN YA TECH

Controlling dimensions of a negative capacitance layer of a gate stack of a field-effect transistor (FET) to increase power density

ActiveUS10714582B2Reduce chargeReduce the differenceSemiconductor/solid-state device manufacturingDigital storageCapacitanceEngineering

A Field-Effect Transistor (FET) with a negative capacitance layer to increase power density provides a negative capacitor connected in series with a conventional positive capacitor. The dimensions of the negative capacitor are controlled to allow the difference in capacitances between the negative capacitor and the positive capacitor to approach zero, which in turn provides a large total capacitance. The large total capacitance provides for increased power density.

Owner:QUALCOMM INC

Photoelectric conversion device and image sensor

InactiveUS7705414B2Avoid desensitizationReduce manufacturing costSolid-state devicesSemiconductor devicesOrganic filmFiber

Owner:ABLIC INC

Charge pump and active loop filter with shared unity gain buffer

PendingCN111756369AReduce mismatchIncrease effective capacitancePulse automatic controlApparatus without intermediate ac conversionLoop filterCapacitance

Owner:SILICON LAB INC

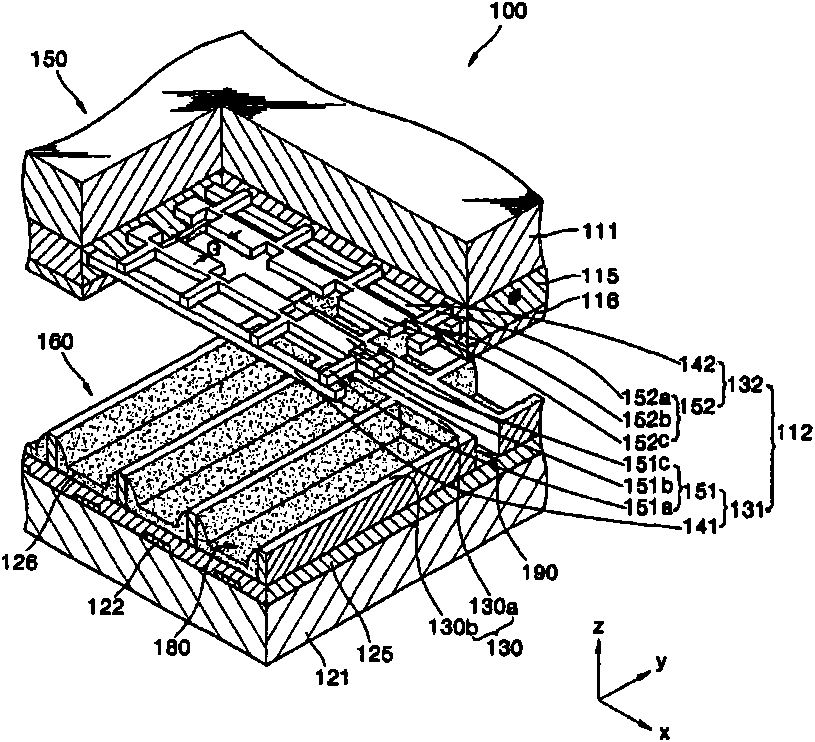

Plasma display panel and front substrate thereof

InactiveCN101599405AIncrease effective capacitanceReduce capacitanceSolid cathode detailsCold-cathode tubesEngineeringMedia layer

The invention discloses a plasma display panel and a front substrate thereof. The front substrate comprises a plurality of pairs of maintaining electrodes distributed on the lower surface of the front substrate, front medium layers covered on the maintaining electrodes and the lower surface of the front substrate, and protective layers covered on the lower surfaces of the front medium layers; each pair of the plurality of pairs of maintaining electrodes comprise public electrodes and scanning electrodes, the public electrode and the scanning electrodes all comprise bus electrodes and transparent electrodes, wherein each transparent electrode comprises a discharge transparent electrode, an extending transparent electrode which extends from the top of one of a plurality of first retaining walls on a rear substrate of the plasma display panel and is connected with each bus electrode, and a connecting transparent electrode connected with the discharge transparent electrode and the extending transparent electrode; and the bus electrodes are arranged on one of a plurality of second retaining walls on the rear substrate of the plasma display panel and a place corresponding to one of the second retaining walls.

Owner:SICHUAN COC DISPLAY DEVICES

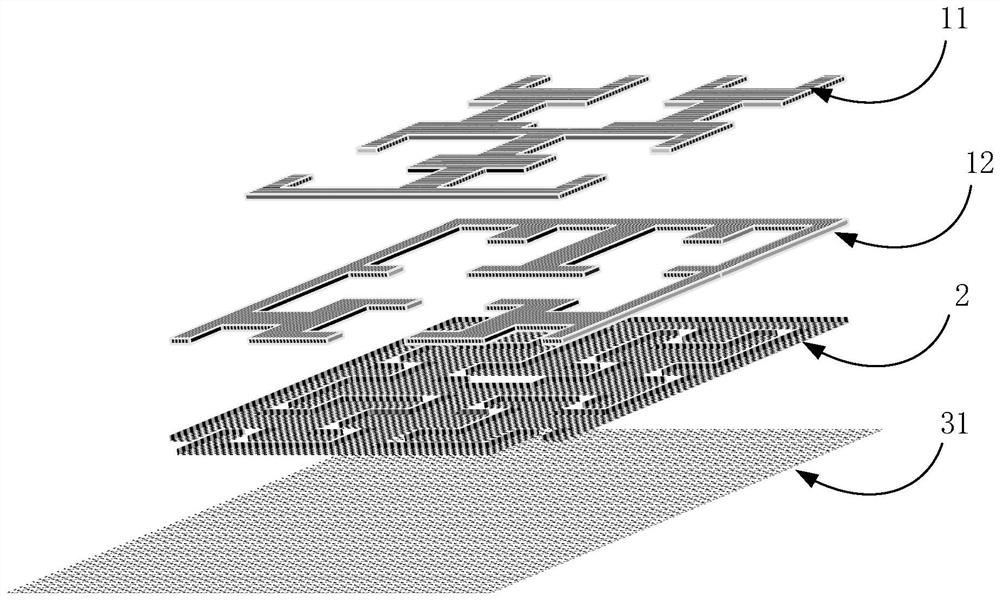

Tailorable battery cell, battery and manufacturing method thereof

PendingCN114824424AImprove area utilizationIncrease effective capacitancePrimary cellsSecondary cells manufactureInternal resistanceElectrical connection

The invention discloses a cuttable battery cell, a battery and a manufacturing method of the cuttable battery cell, and relates to the technical field of battery structures. The cuttable battery cell comprises at least two electrode units, each electrode unit comprises an electrode layer and a current collection layer which are arranged in a stacked mode, each electrode layer comprises a first electrode body and a second electrode body, and an electrode arm of each first electrode body is meshed with an electrode arm of each second electrode body; the adjacent electrode units are connected through an electric connection structure, and the electric connection structure is used for cutting to split the adjacent electrode units; the adjacent electrode units are connected through an electric connection structure for cutting. The pole arm of the first electrode body is meshed with the pole arm of the second electrode body, so that the area utilization rate is improved, the ion transmission distance is shortened, the internal resistance of the battery is reduced, and the effective capacitance can be improved. In addition, through connection of the electric connection structure for tailoring, the tailorable battery cell can be conveniently disassembled, customized tailoring is facilitated, and the battery with the required capacity can be rapidly assembled.

Owner:ZINERGY SHENZHEN LTD

Plasma display panel and front substrate thereof

InactiveCN101599405BIncrease effective capacitanceReduce capacitanceSolid cathode detailsCold-cathode tubesEngineeringMedia layer

Owner:SICHUAN COC DISPLAY DEVICES

High-density low-parasitic capacitor

ActiveCN101789430BReduce the ratioReduce power consumptionSolid-state devicesSemiconductor devicesCapacitanceParasitic capacitor

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

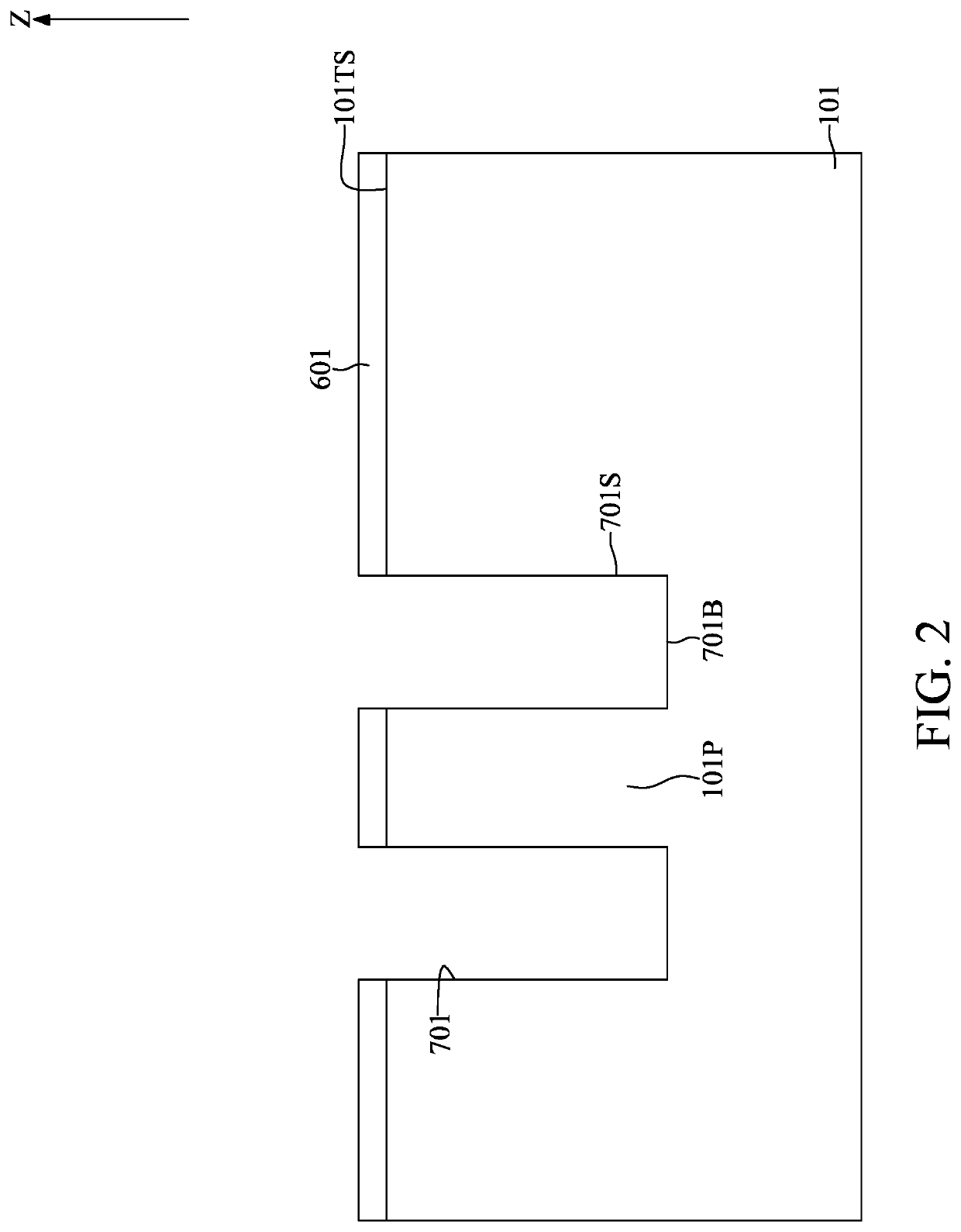

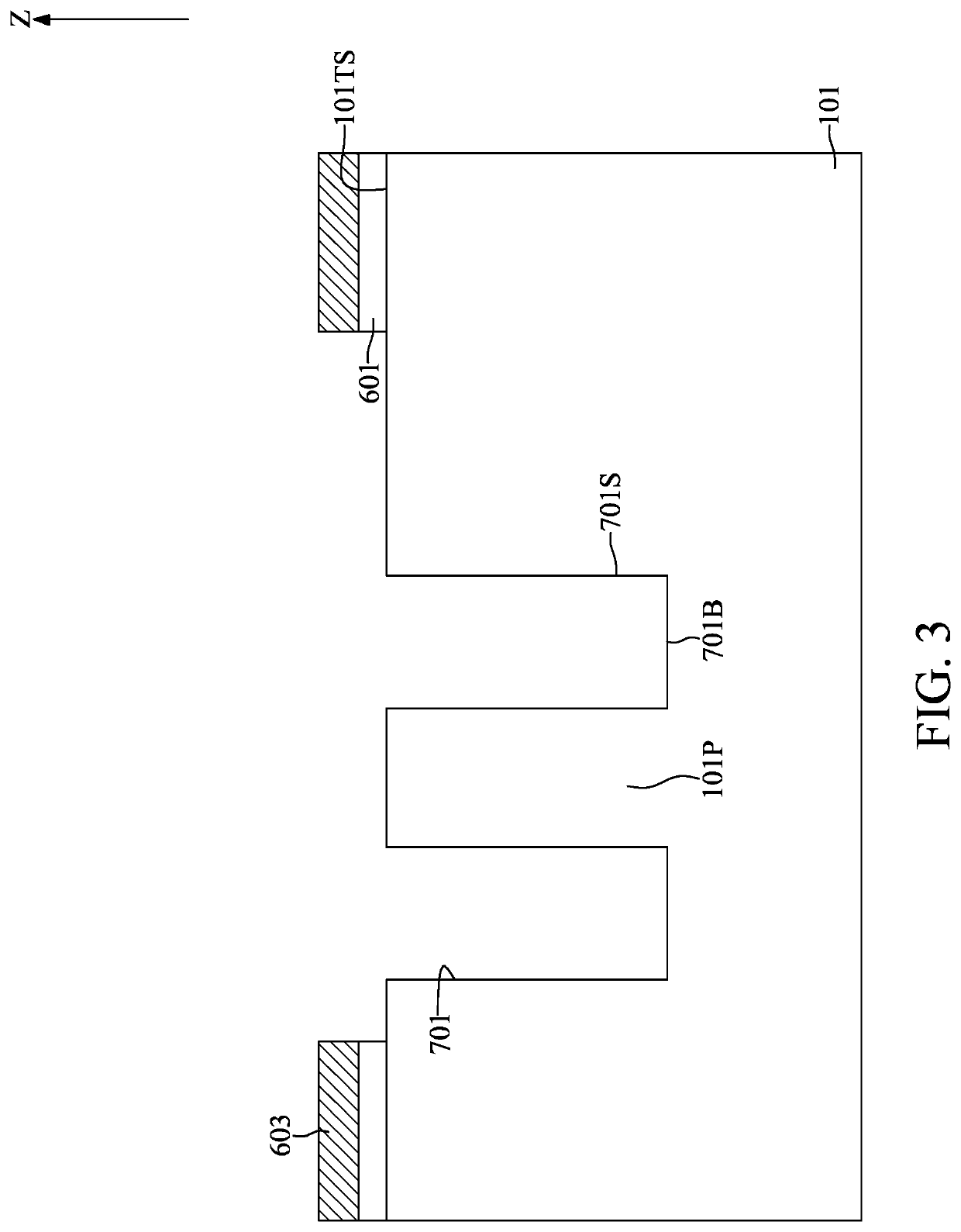

Semiconductor device with capacitors having shared electrode and method for fabricating the same

ActiveUS20220190102A1Increase capacitance densityIncrease effective capacitanceFixed capacitor electrodesSemiconductor/solid-state device detailsCapacitanceDevice material

The present application discloses a semiconductor device with capacitors having a shared electrode and a method for fabricating the semiconductor device. The semiconductor device includes a substrate, a first capacitor unit, a second capacitor unit, and a connection structure. The first capacitor unit includes a bottom conductive structure inwardly positioned in the substrate, and a shared conductive layer positioned above the bottom conductive structure with a first insulating layer interposed therebetween. The second capacitor unit includes the shared conductive layer, a top conductive layer positioned above the shared conductive layer with a second insulating layer interposed therebetween. The connection structure electrically connects the bottom conductive structure and the top conductive layer such that the first capacitor unit and the second capacitor unit are in parallel.

Owner:NAN YA TECH

Quantum dot array capacitor and preparation method thereof

ActiveCN111863778AIncrease capacitance densityIncrease effective capacitanceSemiconductor/solid-state device detailsSolid-state devicesCapacitanceEngineering

The invention provides a quantum dot array capacitor and a preparation method thereof. The capacitor comprises a semiconductor substrate, a first conductive layer located on the semiconductor substrate, a first dielectric layer located on the first conductive layer, a second conductive layer located on the first dielectric layer and a second dielectric layer located on the second conductive layer.Conductive layers and dielectric layers are and alternately formed to obtain a multi-layer capacitor structure. The capacitor is formed into a multi-layer pyramid-shaped array. Due to the fact that the pyramid array structure is adopted in the array capacitor, larger capacitance is generated on the same wafer area; and the conductive layers and the dielectric layers can be repeatedly formed, so that the capacitance density per unit area can be further improved.

Owner:SIEN QINGDAO INTEGRATED CIRCUITS CO LTD

mems microphone

ActiveCN107484051BIncrease effective capacitanceImprove acoustic performanceMouthpiece/microphone attachmentsDiaphragm constructionVibrating membraneCapacitance

Owner:AAC ACOUSTIC TECH (SHENZHEN) CO LTD