Patents

Literature

32results about How to "Improve lithography precision" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

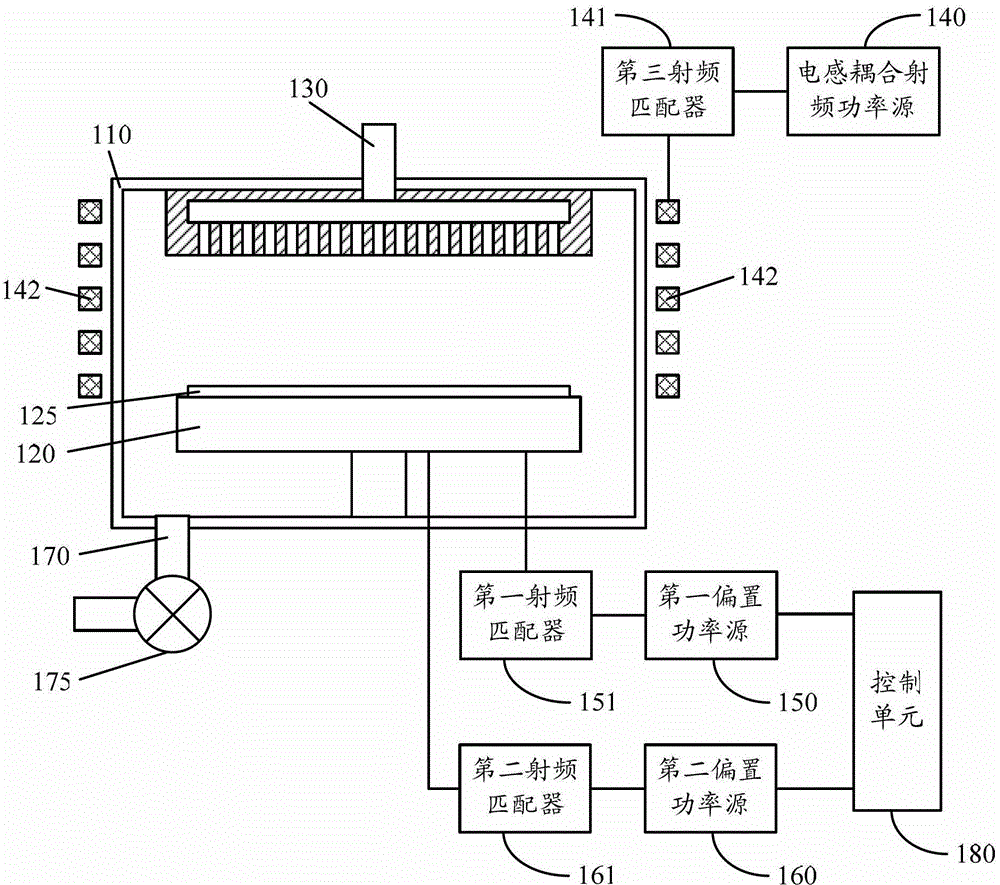

Semiconductor etching device and etching method of semiconductor structure

ActiveCN103021912AAvoid contaminationAvoid pollutionElectric discharge tubesSemiconductor/solid-state device manufacturingSemiconductor structureEngineering

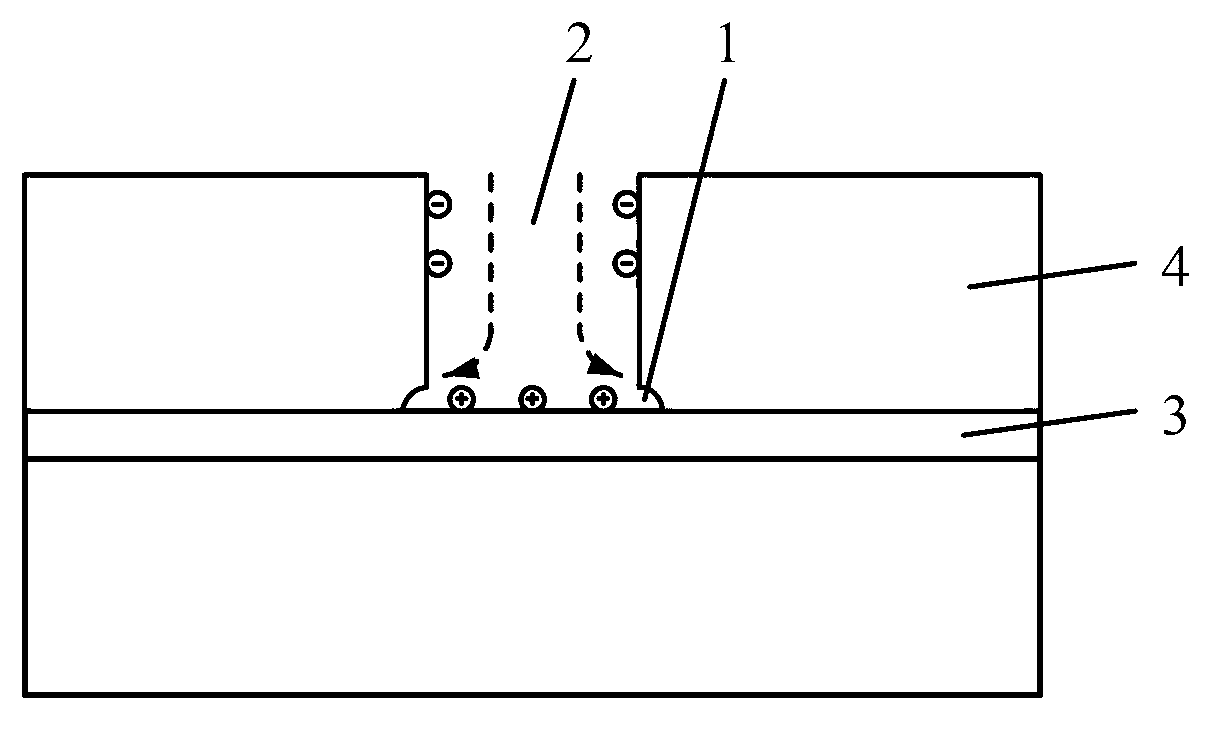

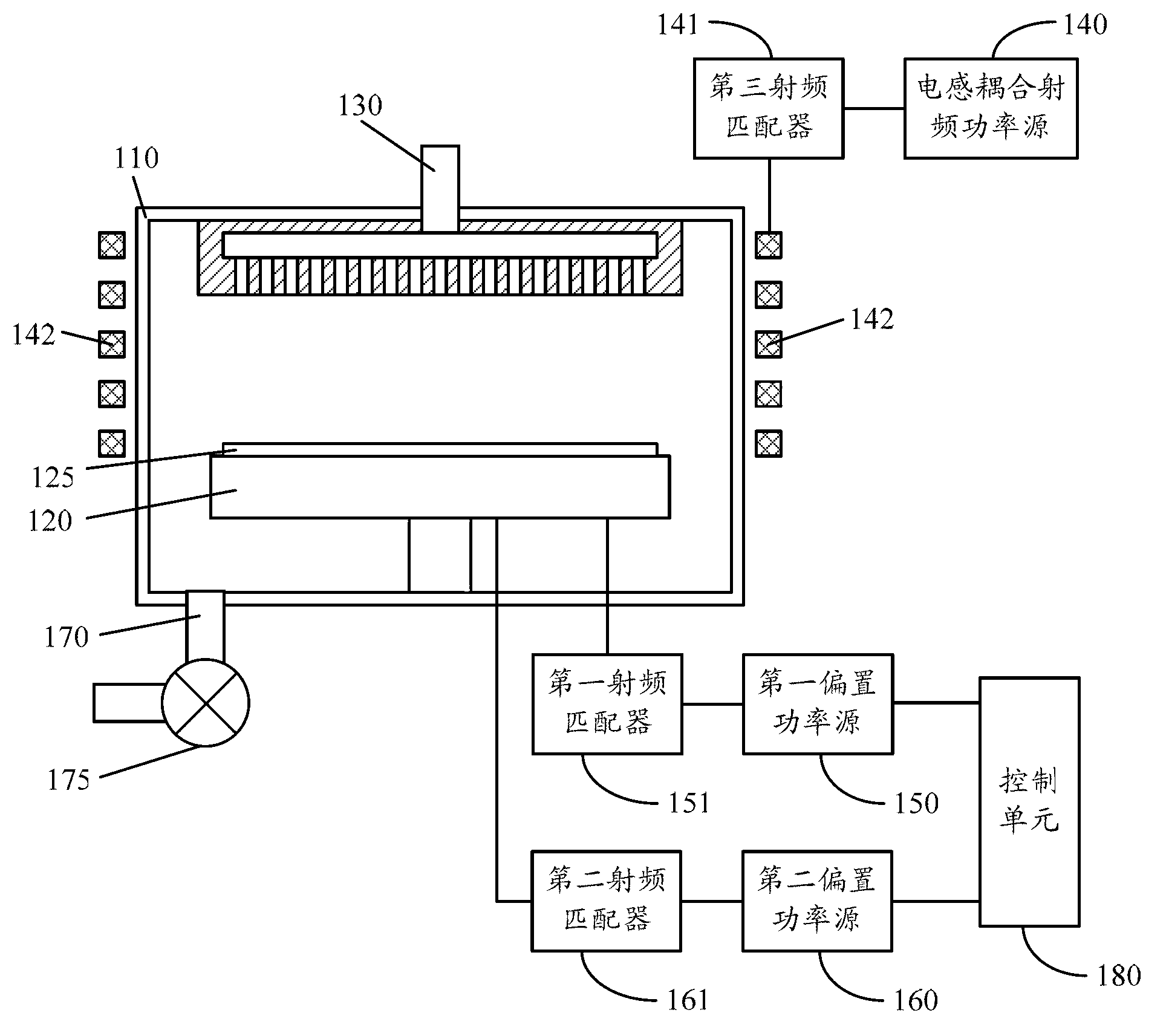

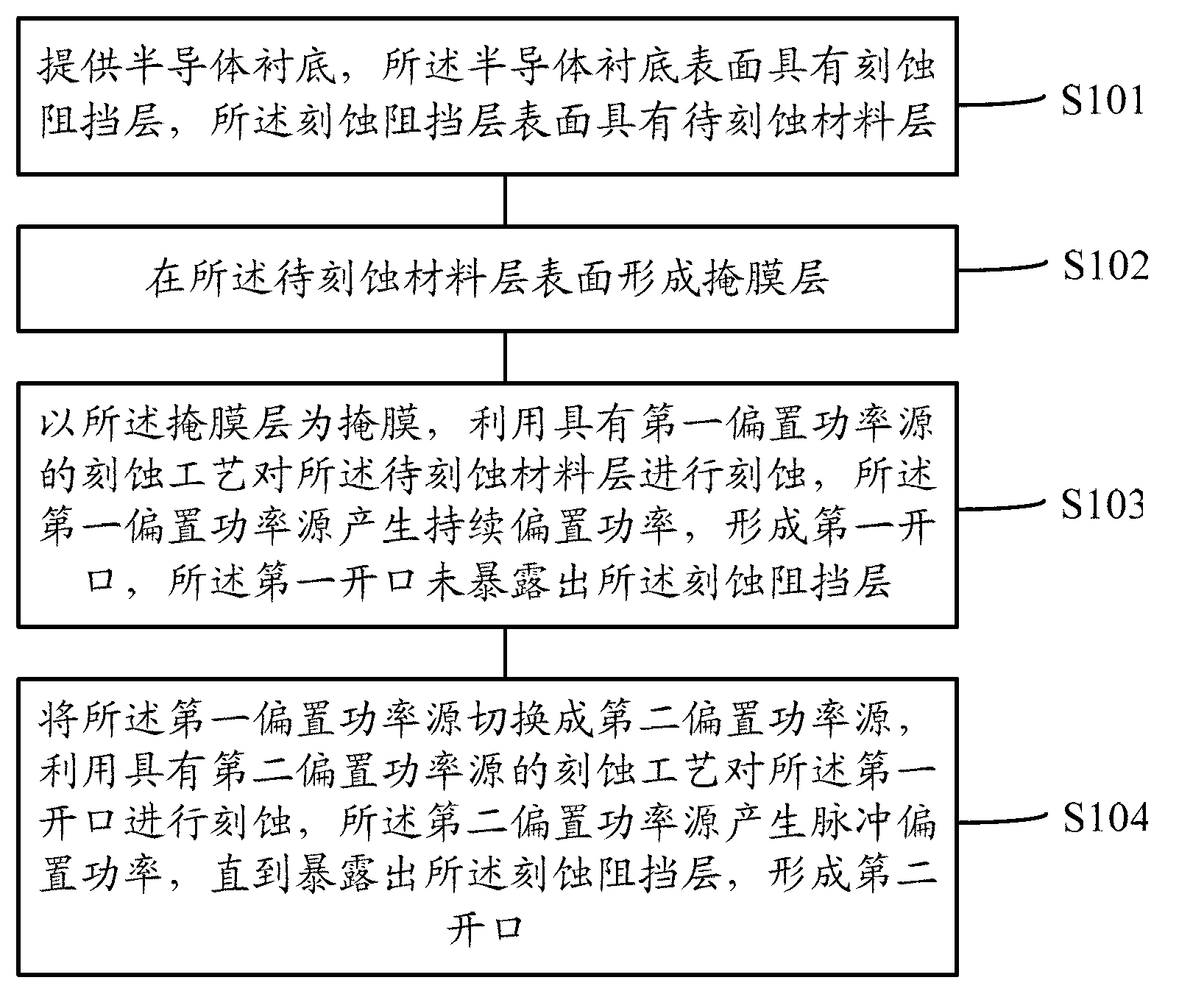

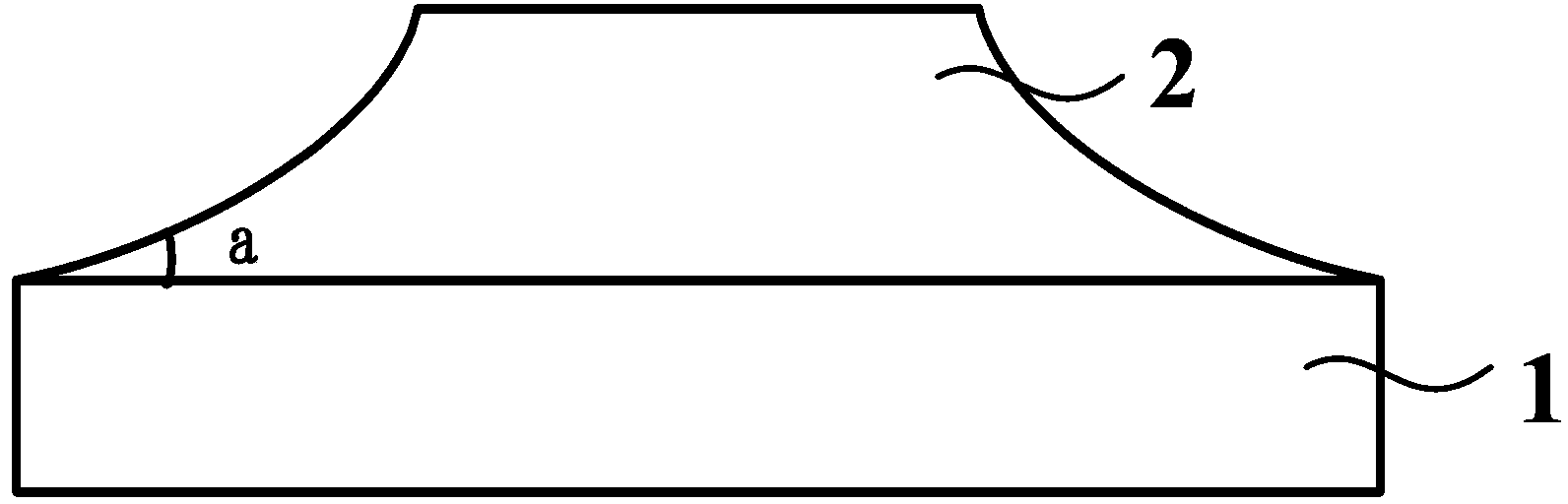

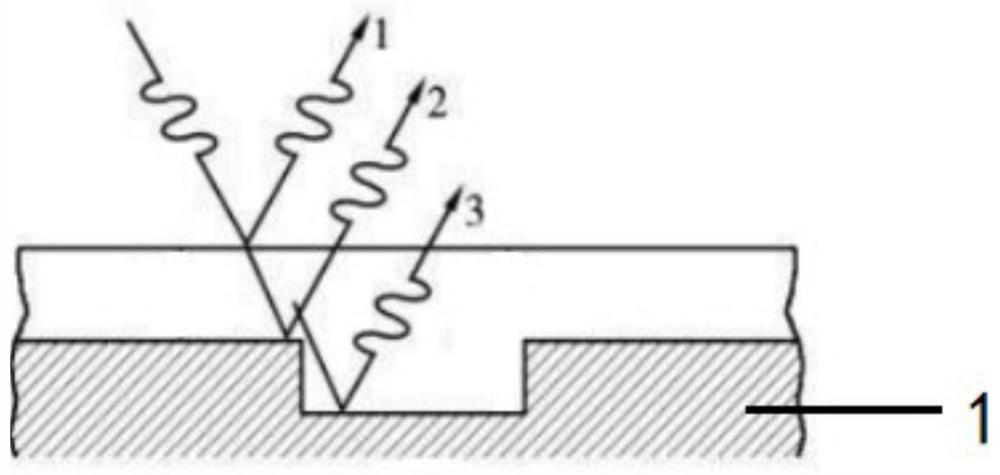

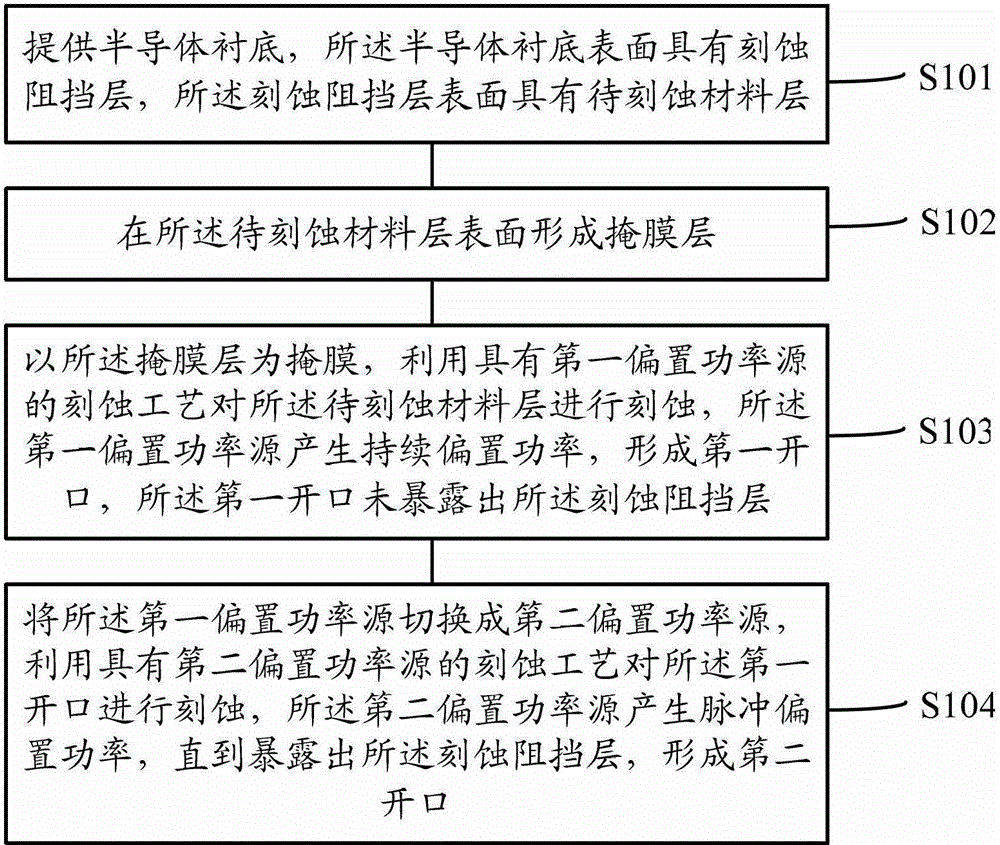

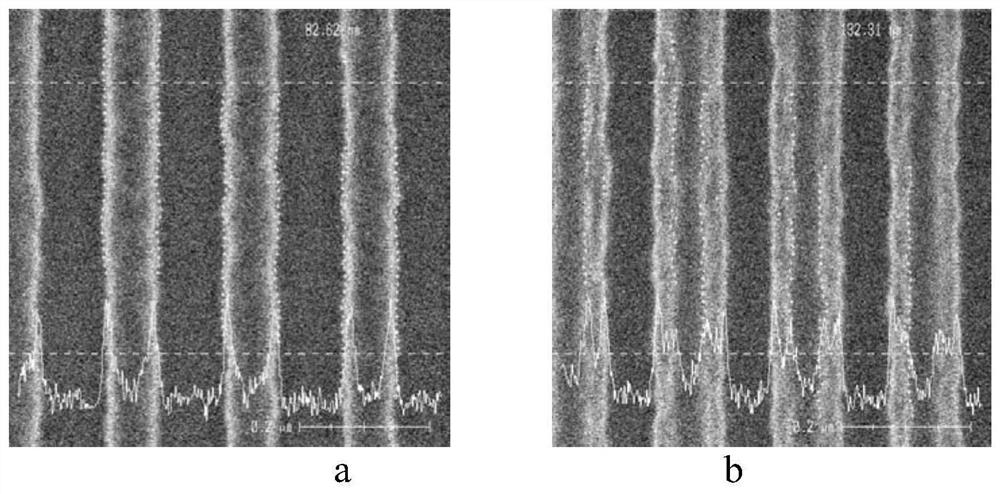

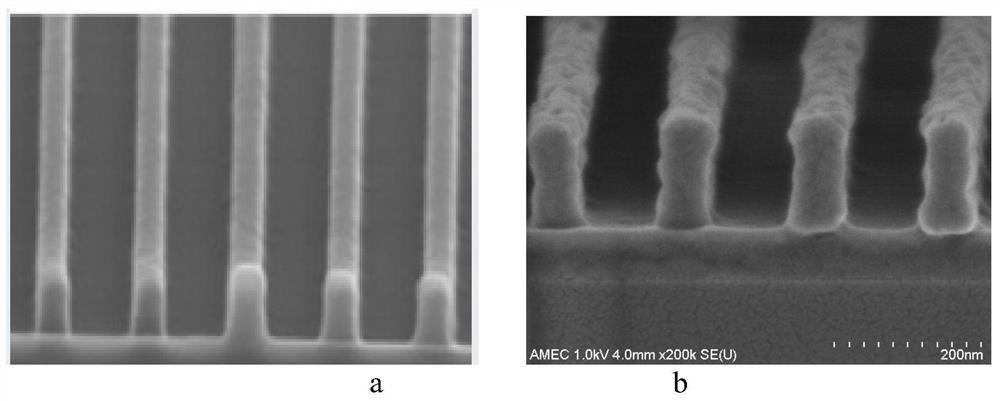

Disclosed are a semiconductor etching device and an etching method of a semiconductor structure. The etching method includes: a etching process with a first bias power source is utilized to etch a to-be-etched material layer, and the first bias power source generates continuous bias power to form a first opening which does not expose a etching blocking layer; and then a etching process with a second bias power source is utilized to etch the first opening, and the second bias power source generates pulse bias power until the etching blocking layer is exposed to form a second opening. Due to the fact that the continuous bias power is utilized to form bias voltage for etching firstly, side wall appearance is good, and etching selection ratio to a photo layer is high. The continuous bias power is switched into pulse bias power to form bias voltage for etching in prior to exposure of the etching blocking layer, so that cuts are avoided from being formed at the side wall bottom, close to the etching blocking layer, of the to-be-etched material layer.

Owner:ADVANCED MICRO FAB EQUIP INC CHINA

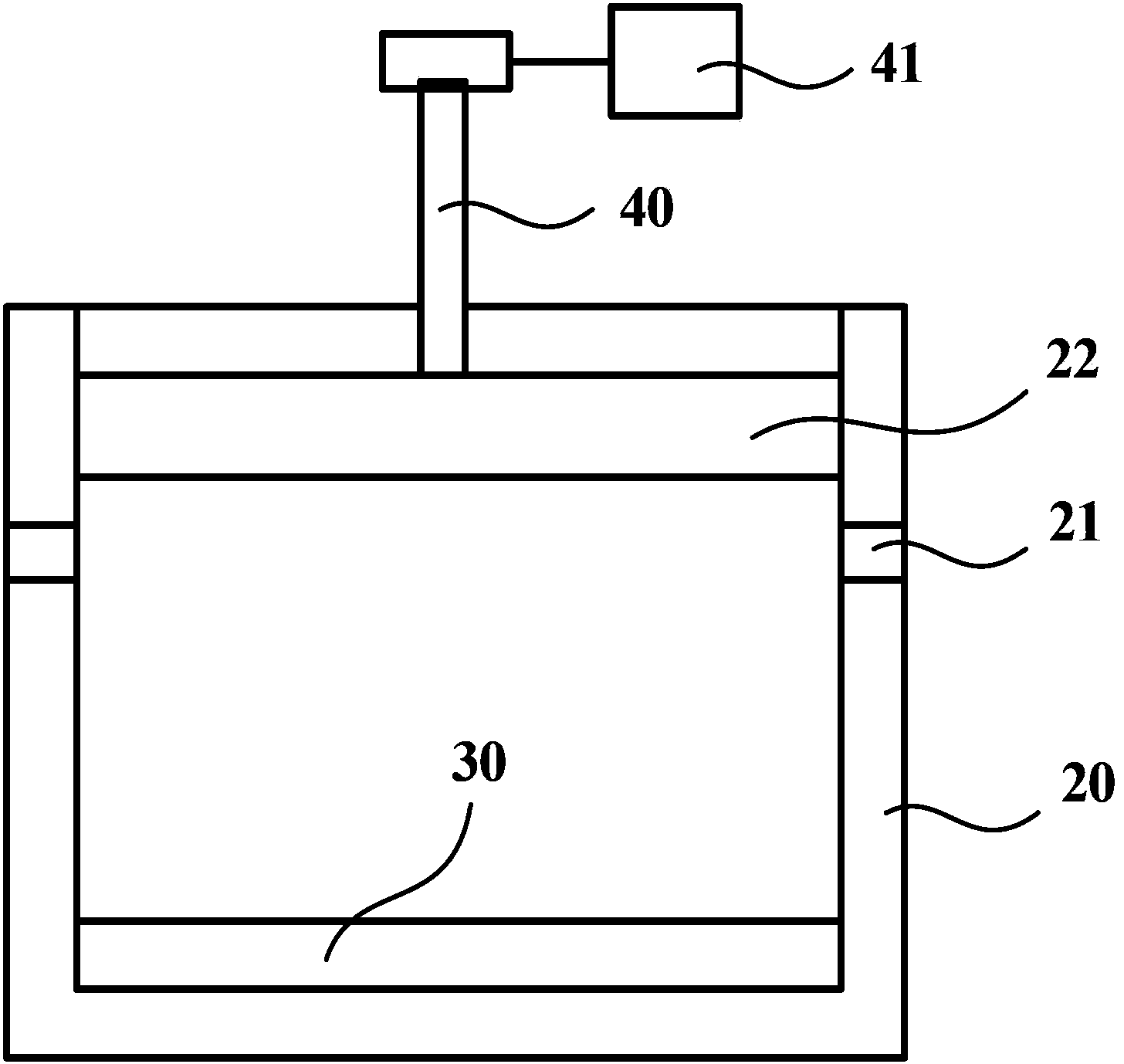

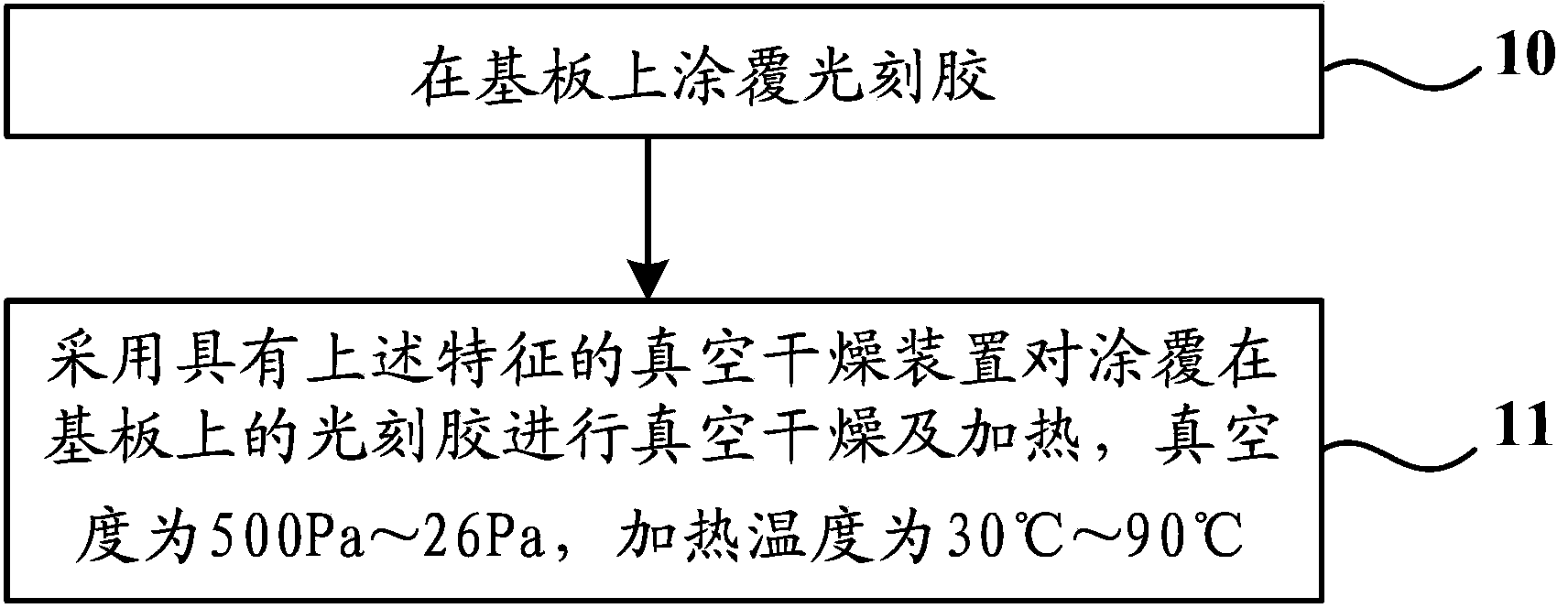

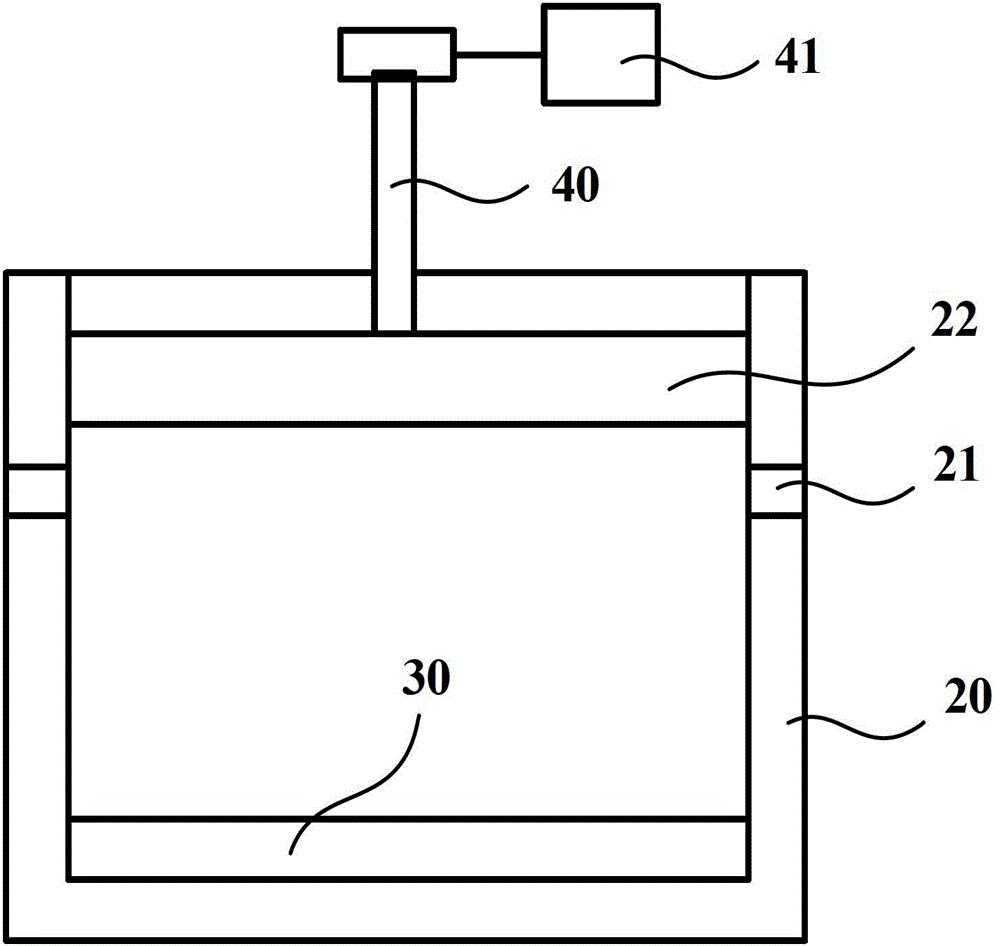

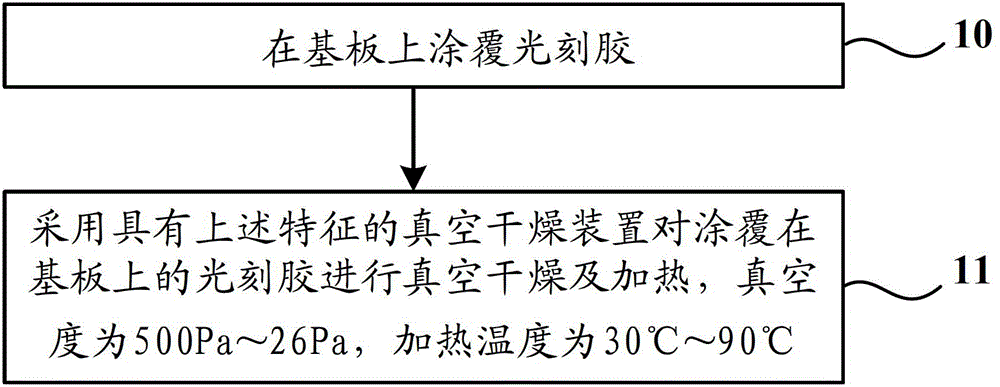

Vacuum drying device and photolithographic process

InactiveCN103353209AIncrease bank angleImprove adhesionDrying using combination processesDrying solid materials without heatVacuum pumpingPulp and paper industry

The invention relates to the technical field of substrate manufacture, in particular to a vacuum drying device and a photolithographic process which are used for improving the photolithographic accuracy. The disclosed vacuum drying device comprises a vacuum chamber provided with exhaust vents and a chamber door, a vacuum pumping device communicated with the exhaust vents, as well as a heating assembly arranged in the vacuum chamber. When the vacuum drying device is adopted for performing vacuum drying on a substrate coated with photoresist, heating and vacuum drying simultaneously act on the photoresist, so that less hardening film is produced, the residual quantity of a solvent in the photoresist is reduced, and the photolithographic accuracy is improved. The invention further discloses a photolithographic process which comprises steps as follows: the substrate is coated with the photoresist; and the vacuum drying device with the characteristics is adopted for performing vacuum drying and heating on the photoresist coating the substrate at the vacuum degree ranging from 26 Pa to 500 Pa at the heating temperature ranging from 30 DEG C-90 DEG C.

Owner:BOE TECH GRP CO LTD +1

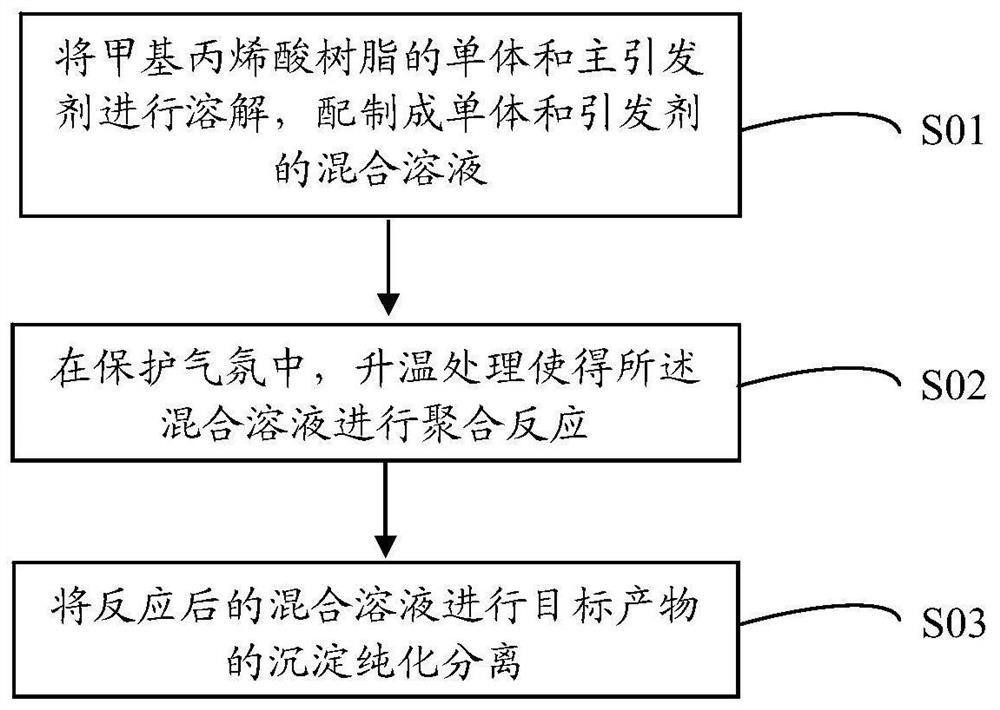

Methacrylic resin and preparation method and application thereof

InactiveCN111718439APromote aggregationIncreased confusionPhotomechanical apparatusPolymer sciencePolymer chemistry

The invention provides a preparation method of methacrylic resin. The preparation method of the methacrylic resin comprises the following steps: dissolving a monomer and a main initiator of the methacrylic resin to prepare a mixed solution of the monomer and the initiator; and in a protective atmosphere, carrying out heating treatment to enable the mixed solution to be subjected to polymerizationreaction. According to the preparation method of the methacrylic resin, the main initiator and the auxiliary initiator have a synergistic effect, and the preparation method can rapidly initiate monomer polymerization to generate a polymer with a specific chain length so that the molecular weight of the prepared resin meets the use requirements of ArF photoresist.

Owner:NINGBO NATA OPTO ELECTRONICS MATERIAL CO LTD

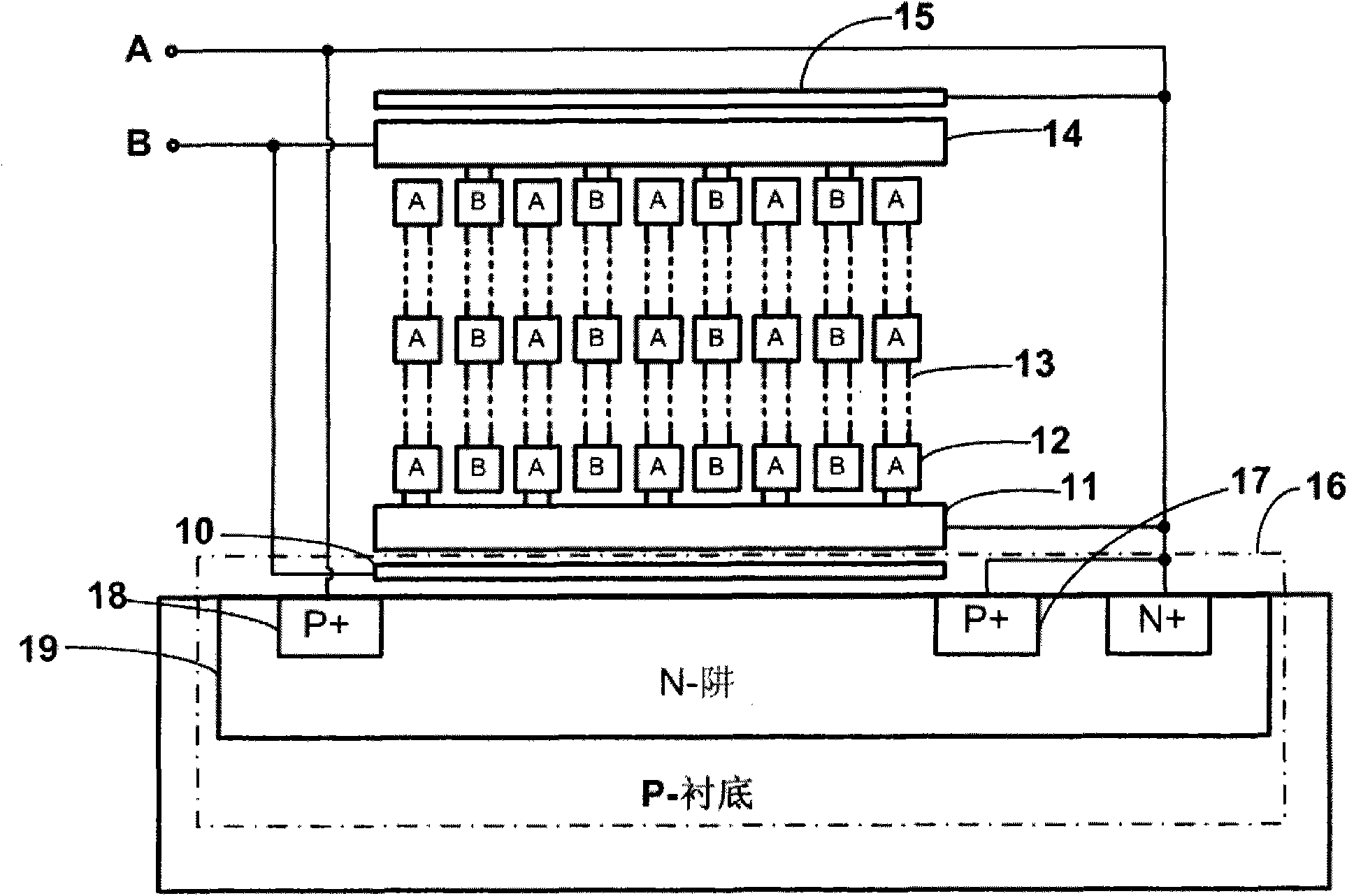

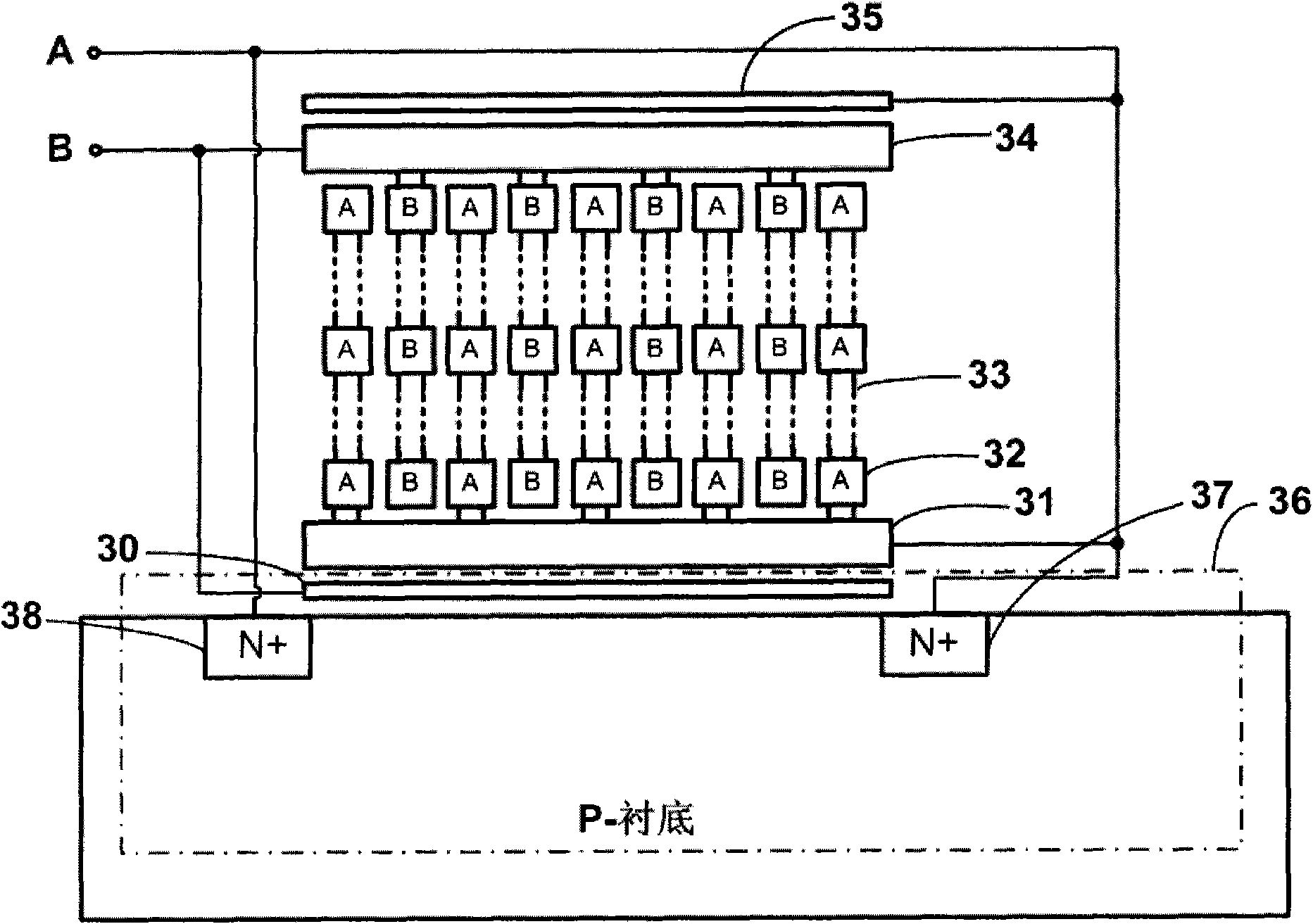

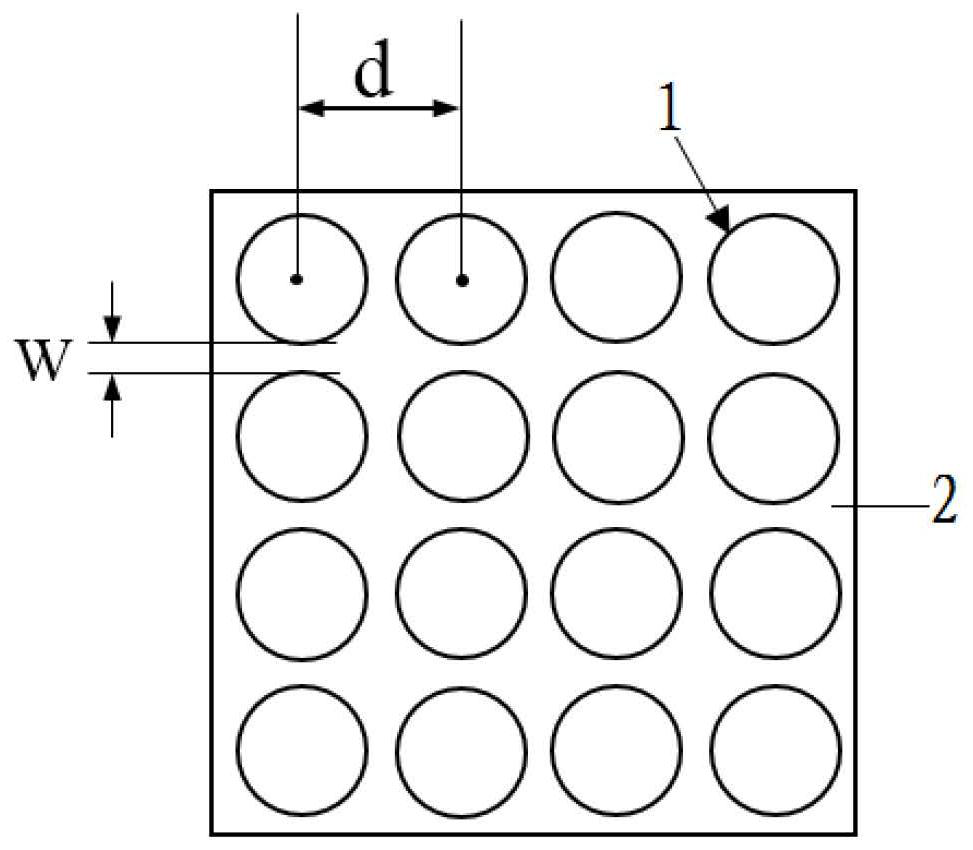

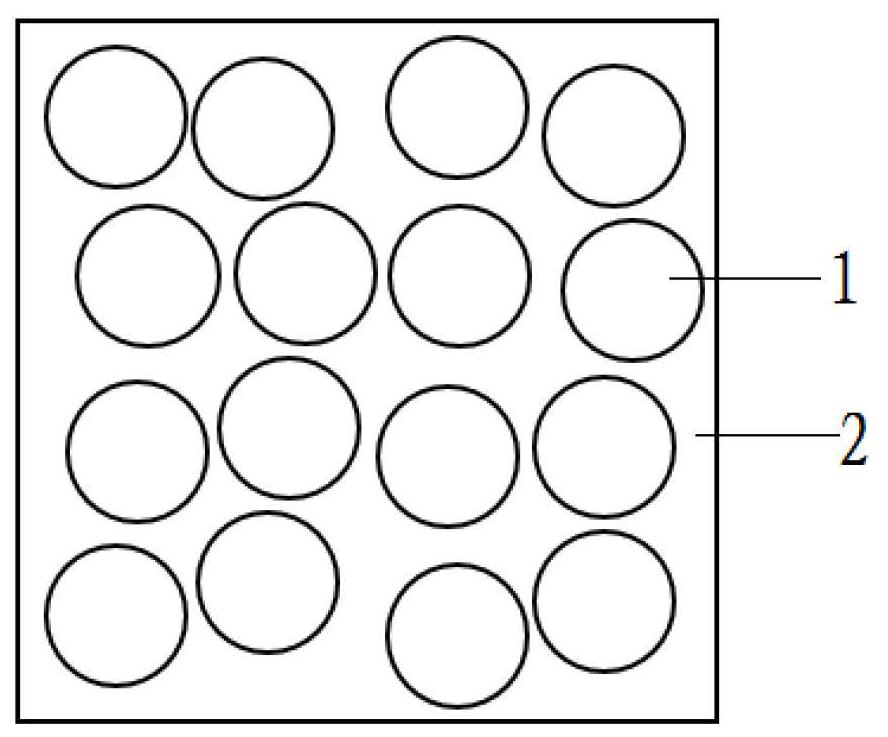

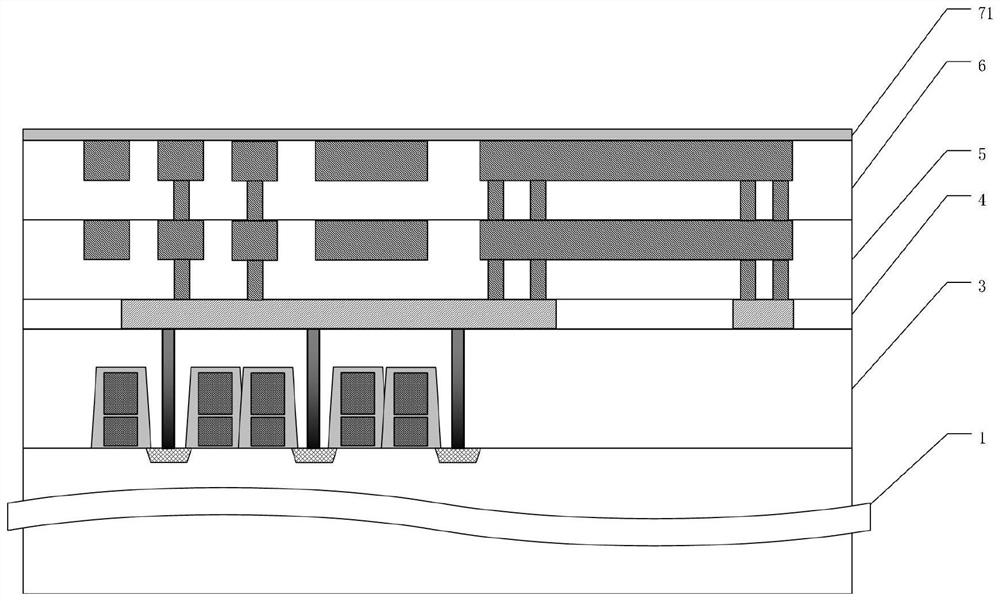

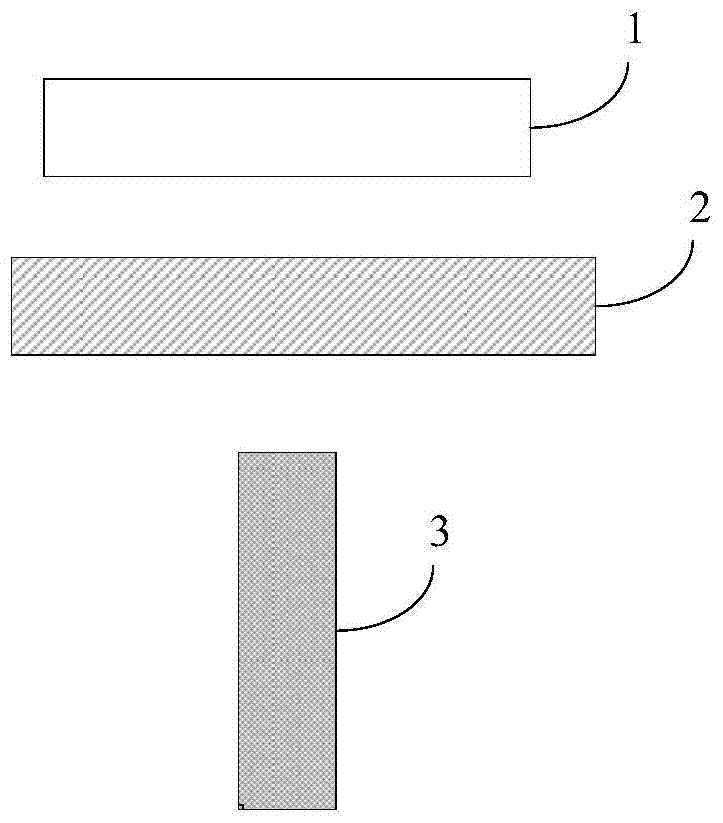

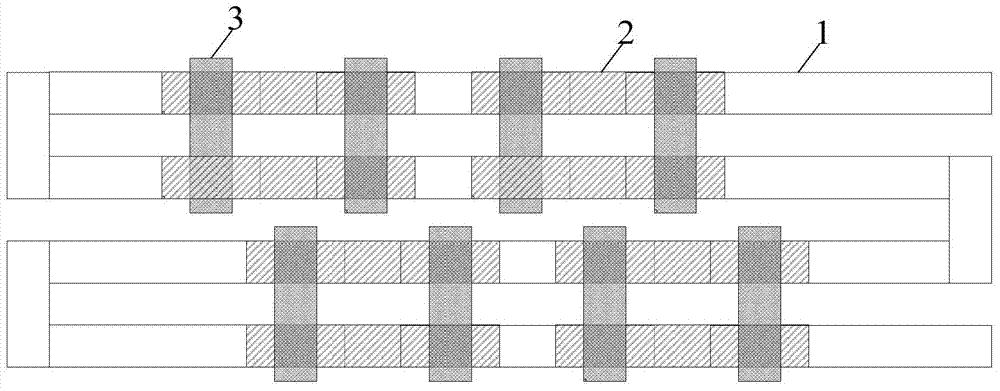

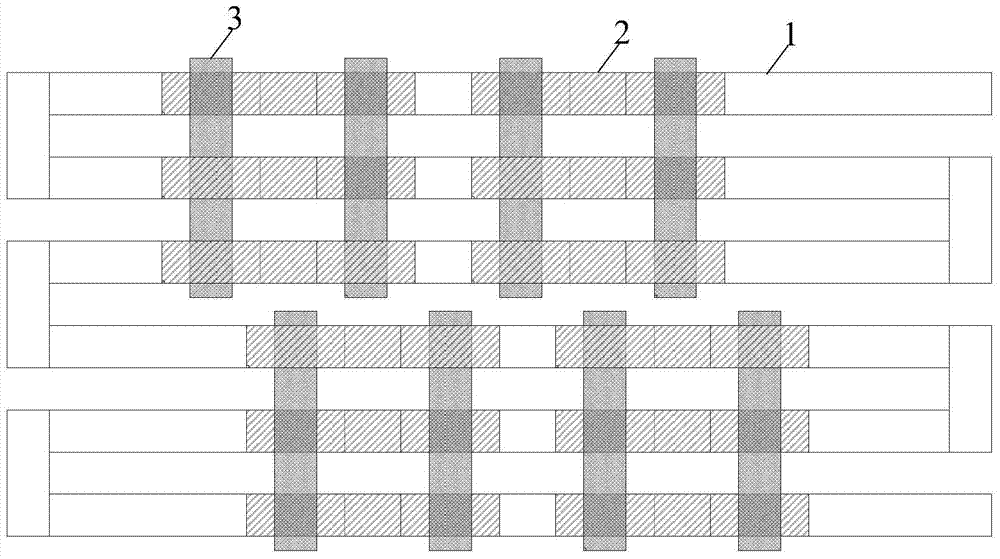

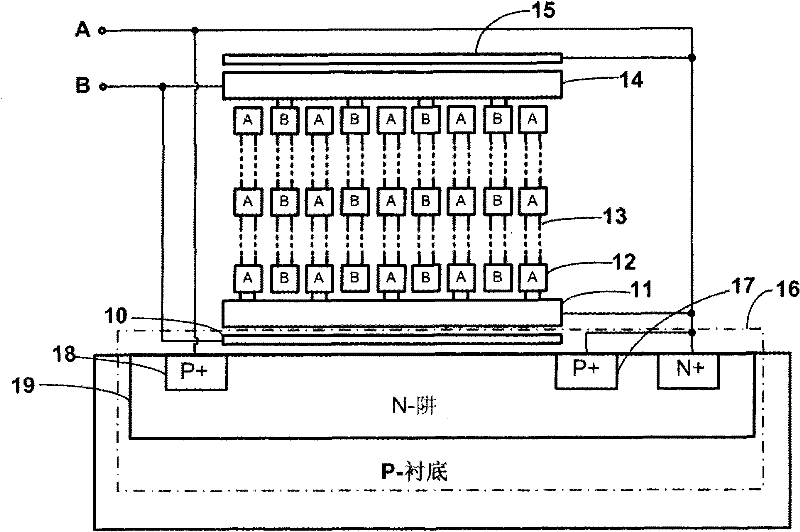

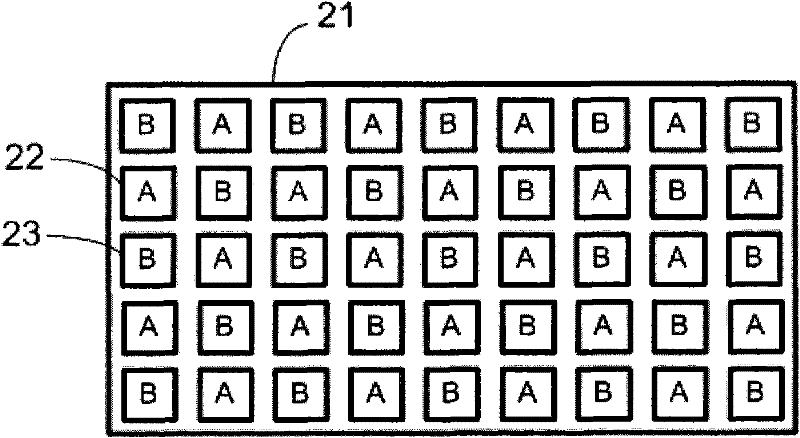

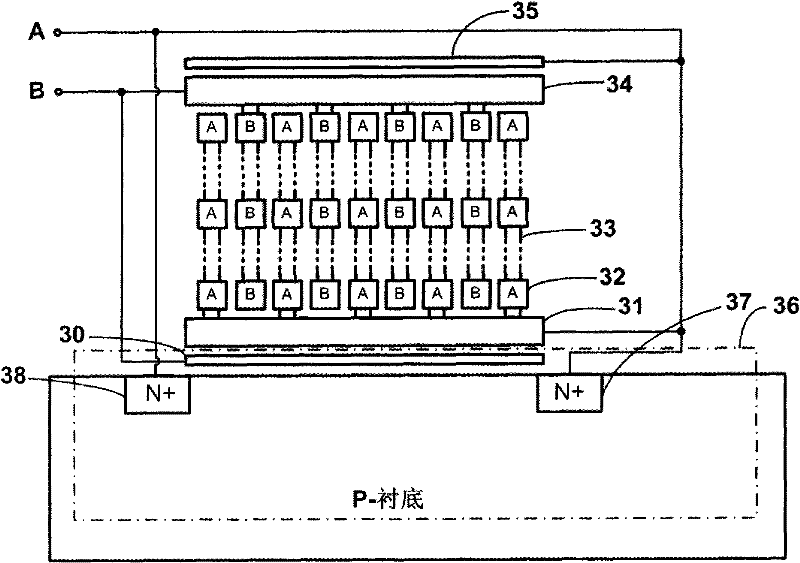

High-density low-parasitic capacitor

ActiveCN101789430AReduce the ratioReduce power consumptionSolid-state devicesSemiconductor devicesCapacitanceParasitic capacitor

The invention discloses a high-density low-parasitic capacitor, comprising a PMOS capacitor, a first capacitor, a second capacitor, a third capacitor and an MIM capacitor, wherein the PMOS capacitor is composed of a polysilicon gate, gate oxide, and a source electrode, a drain electrode and an N-well; the source electrode, the drain electrode and an N-well are connected together; the first capacitor is arranged between the polysilicon gate and the metal at the first layer; the second capacitor is arranged between metals at the same layer; the metal at the first layer is composed of a metal block array, and each metal block and an adjacent metal block thereof are respectively connected with the port A and port B of the second capacitor; the third capacitor is arranged between through holes, and each through hole and an adjacent through hole thereof are respectively connected with the port A and port B of the capacitor; and the MIM capacitor is provided an upper polar plate and a lower polar plate which are respectively connected to the port A and port B of the capacitor. In the invention, the capacitor between the polysilicon gate and the metal layer, the capacitor between the metals at the same layer, the capacitor between the through holes, the MIM capacitor and the like are realized on an MOS capacitor, thus reaching the maximal capacitance on a unit area.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

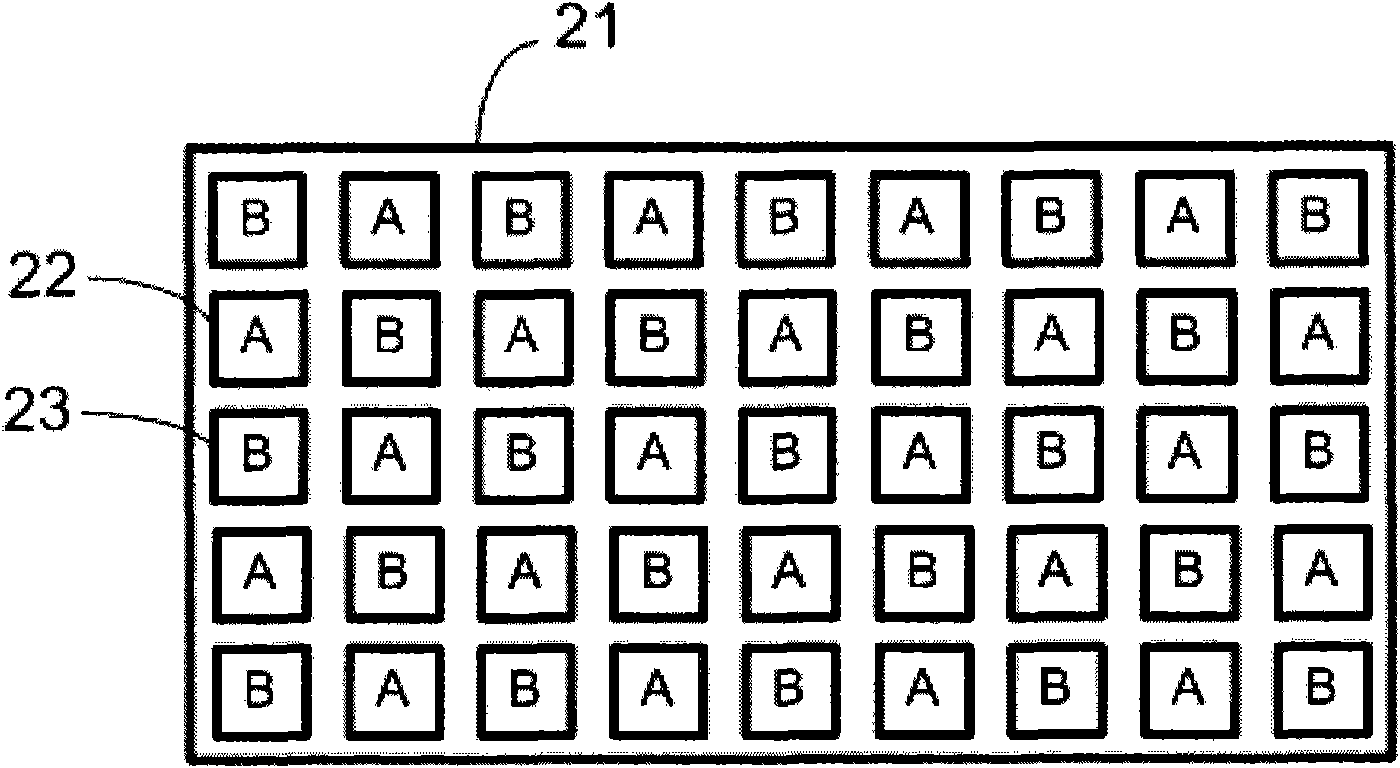

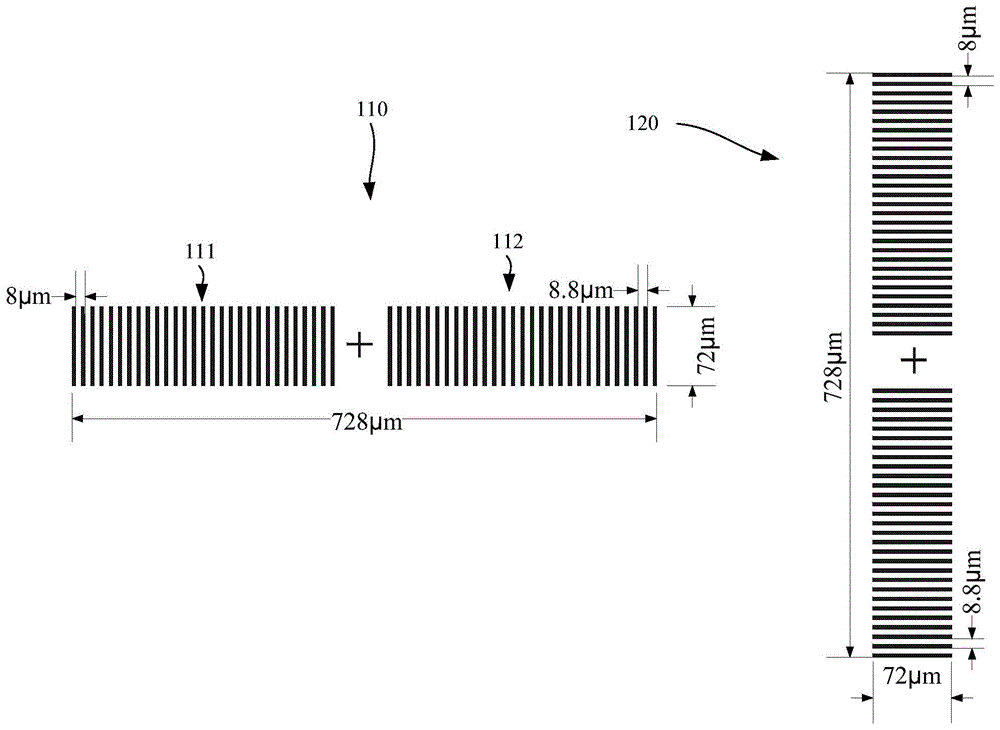

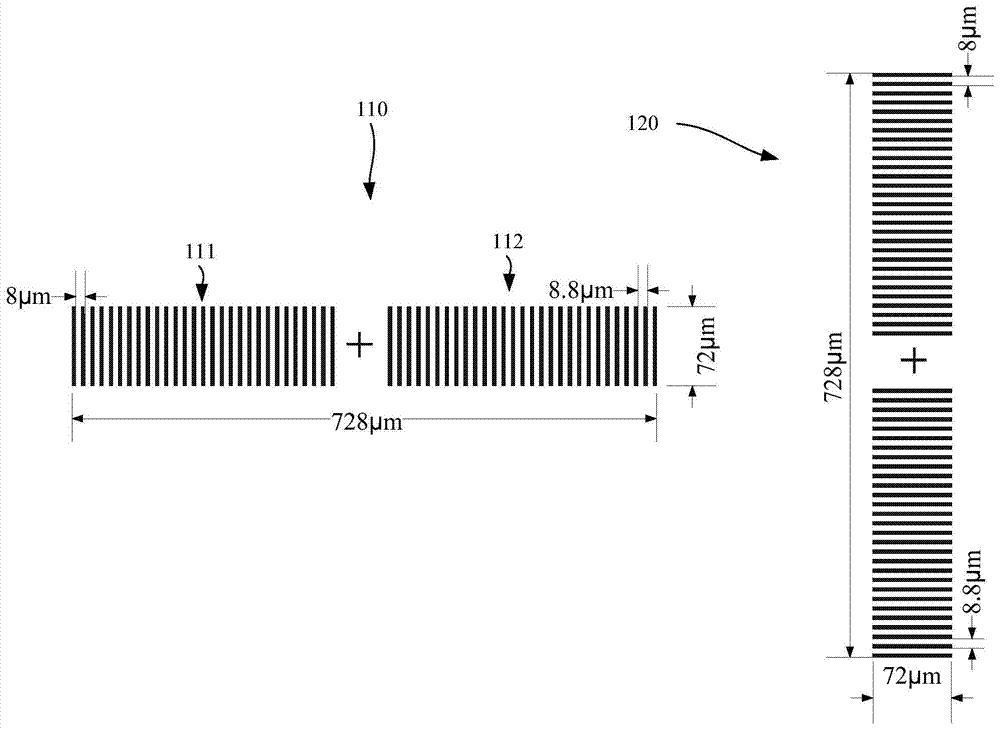

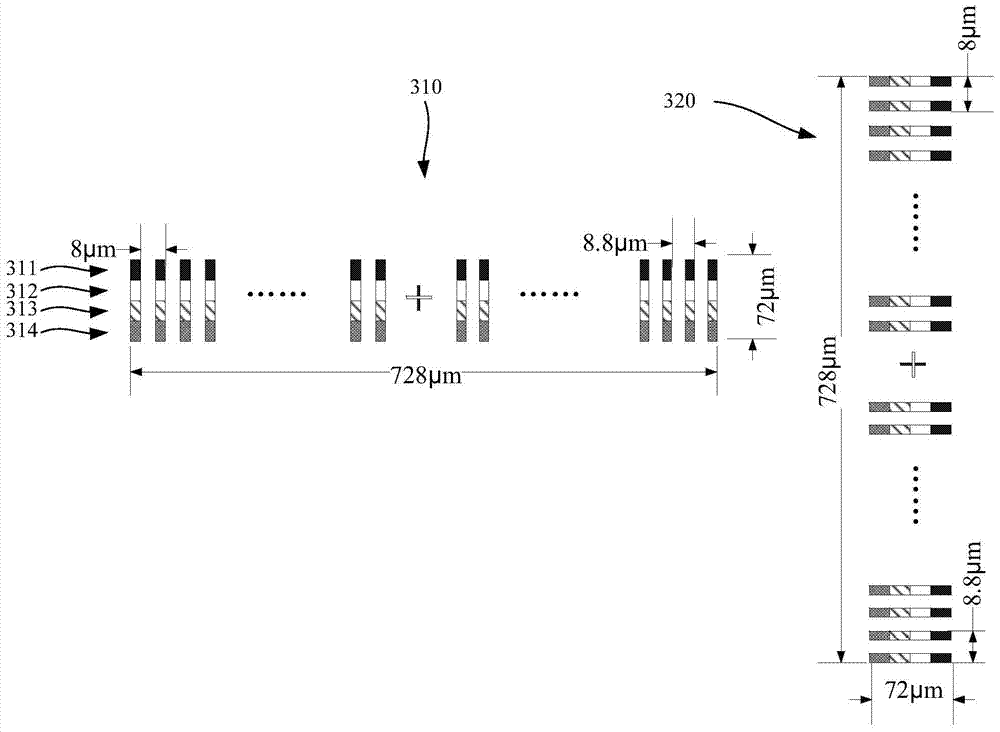

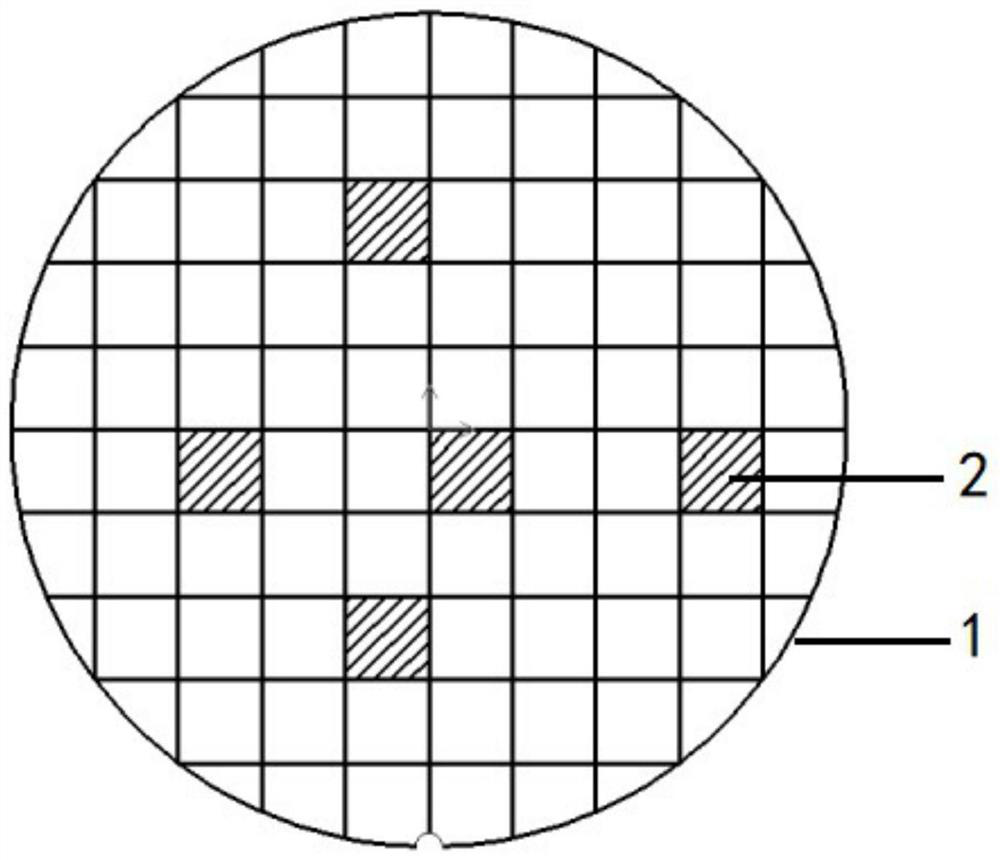

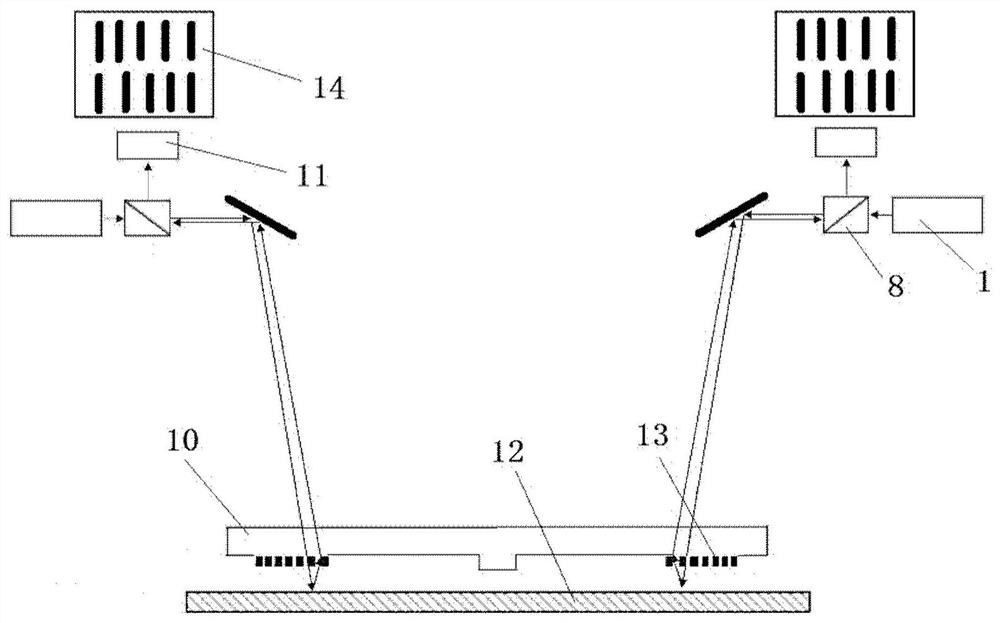

Alignment marker and alignment method thereof

ActiveCN104952851AImprove yieldImprove lithography precisionSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsGratingLithographic artist

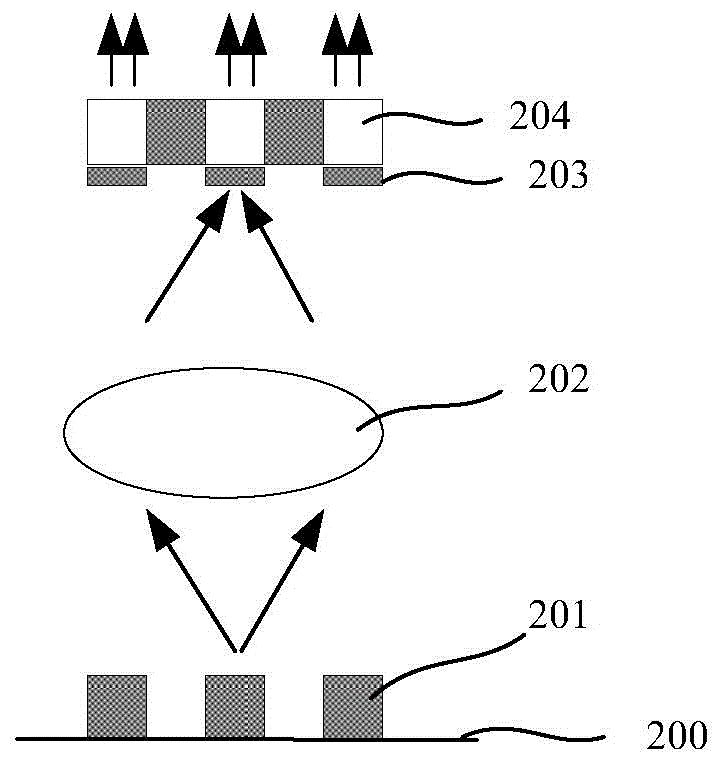

The present invention discloses an alignment marker and alignment method thereof. The alignment marker comprises a group of main markers formed on a semiconductor substrate. Each of the main markers is formed by N groups of sub markers which are formed in the N layers of films on the substrate, and N is the number of layers which are needed to be aligned in lithographic process. Each group of the sub markers comprises a first sub marker of a horizontal direction and a second sub marker of a vertical direction. The first sub marker is two groups of gratings in a horizontal direction, and the second sub marker is two groups of gratings in a vertical direction. Multiple layers can be aligned in alignment, and lithography precision and device yield can be improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Photoetching method and processing chamber

InactiveCN105093821AHigh precisionNot easy to existPhotomechanical apparatusSemiconductor/solid-state device manufacturingEngineeringAtmospheric pressure

The invention provides a photoetching method and a processing chamber. The photoetching method comprises the following steps: putting a wafer into a coating chamber, setting the air pressure in the coating chamber to be first air pressure, carrying out first spinning on the wafer surface, and covering the wafer surface with a photoetching material layer; after carrying out first spinning, carrying out first depressurization step, and lowering the air pressure in the coating chamber into the second air pressure from the first air pressure; carrying out second spinning on the wafer surface; carrying out solidification treatment on the photoetching material layer; and photoetching the wafer covered with the photoetching material layer. The first depressurization step is carried out after first spinning is carried out on the wafer surface, so that bubbles in the photoetching material layer are extruded or broken off along with air pressure drop; the bubbles do not easily exist in the photoetching material layer which is subjected to second spinning and solidification treatment. Therefore, the photoetching accuracy can be effectively improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

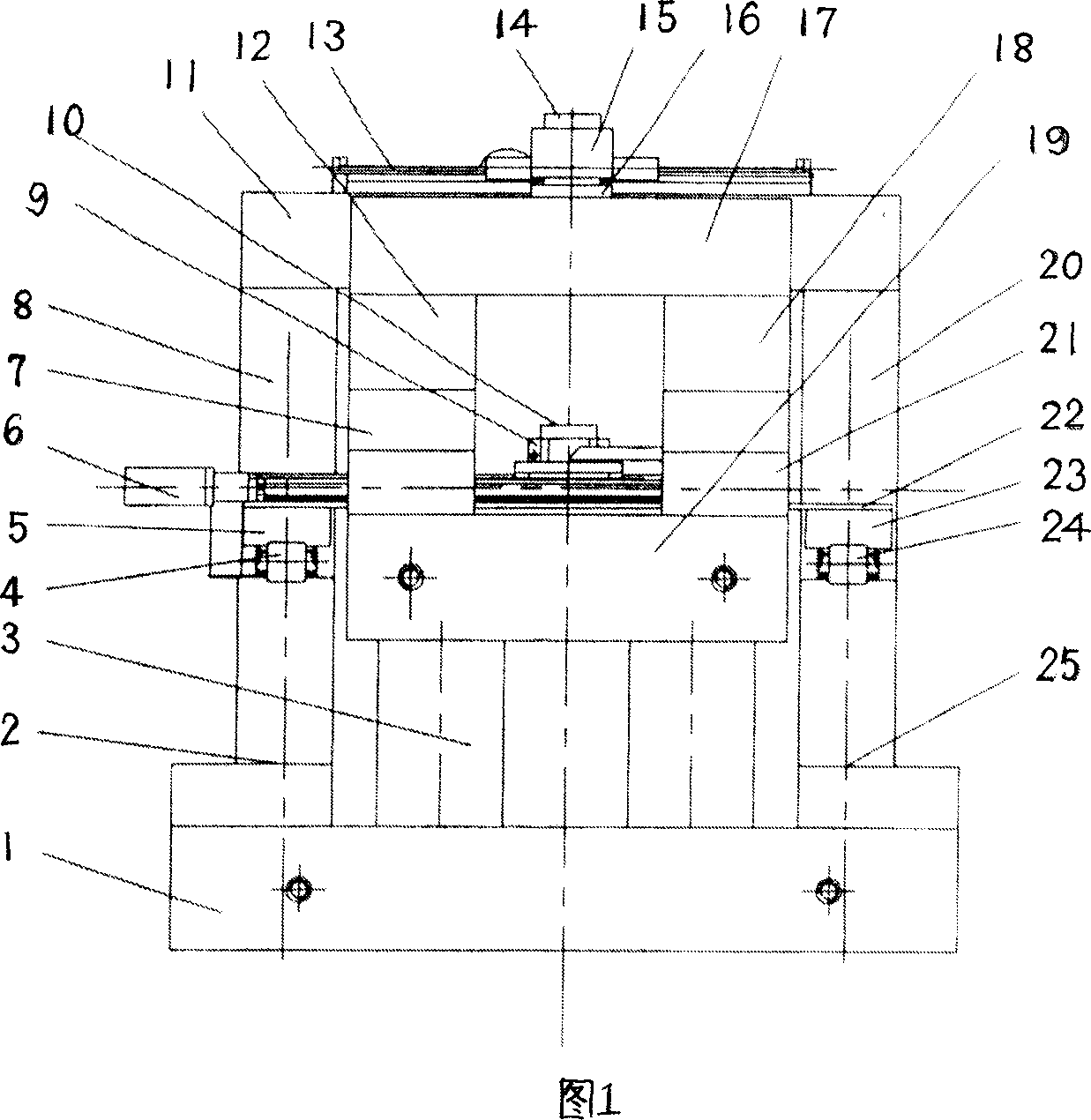

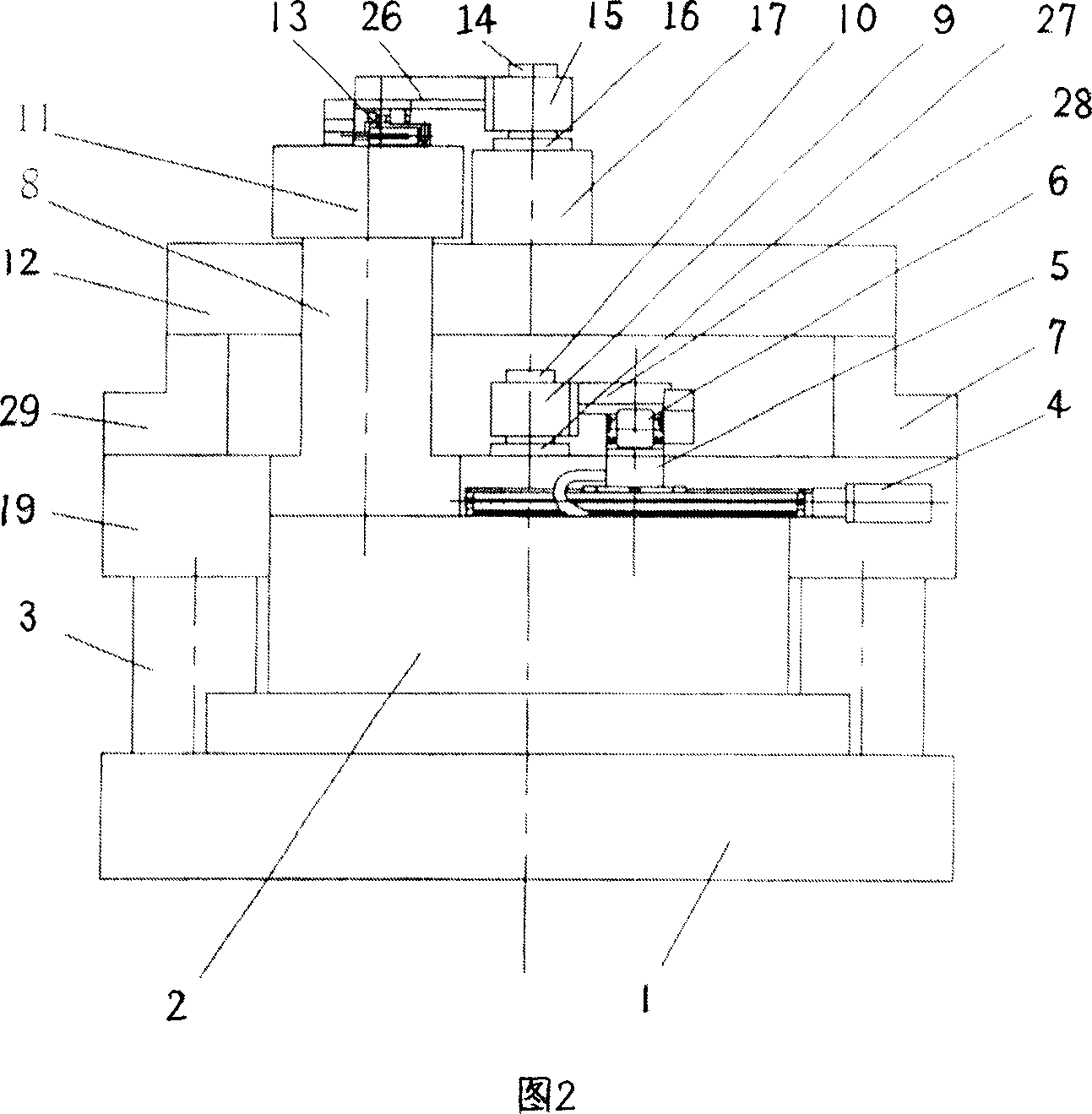

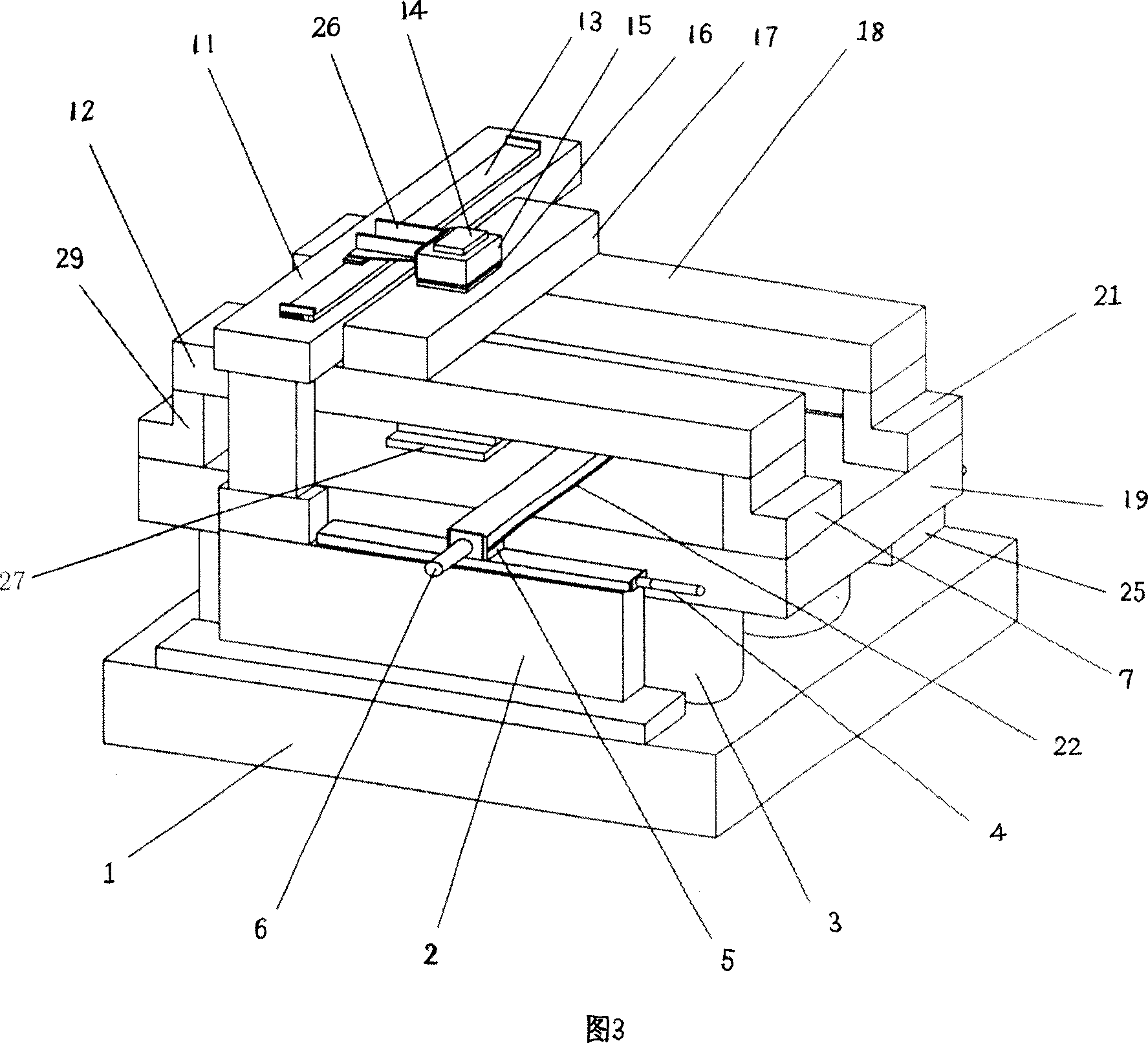

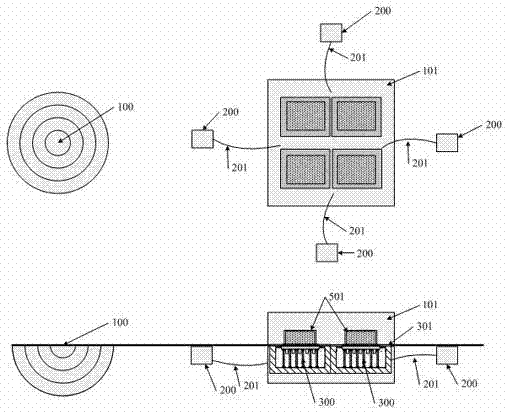

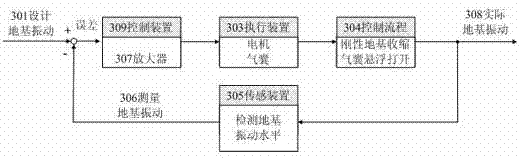

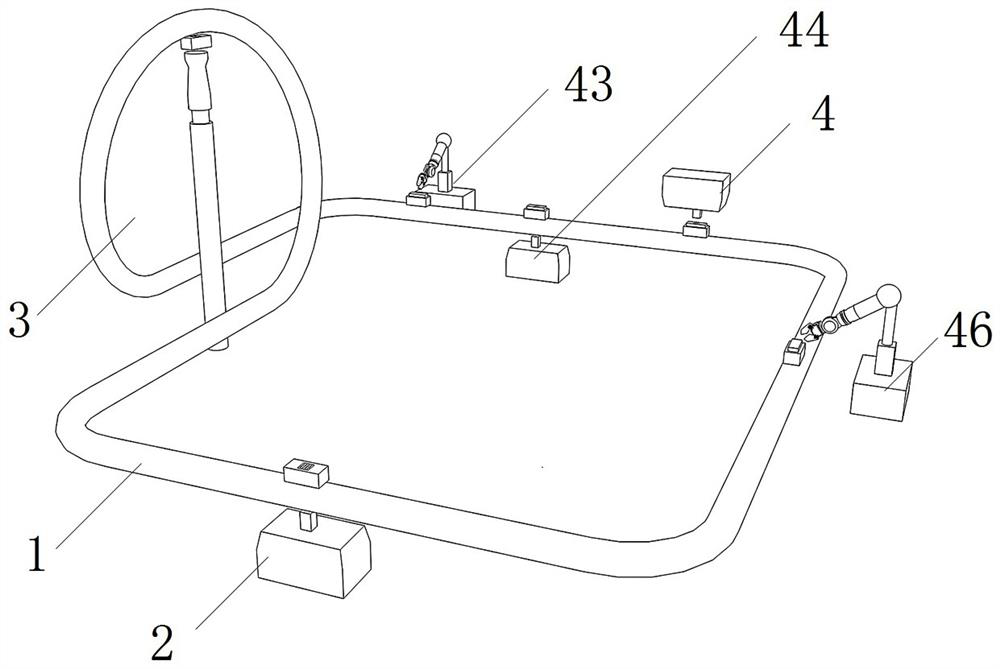

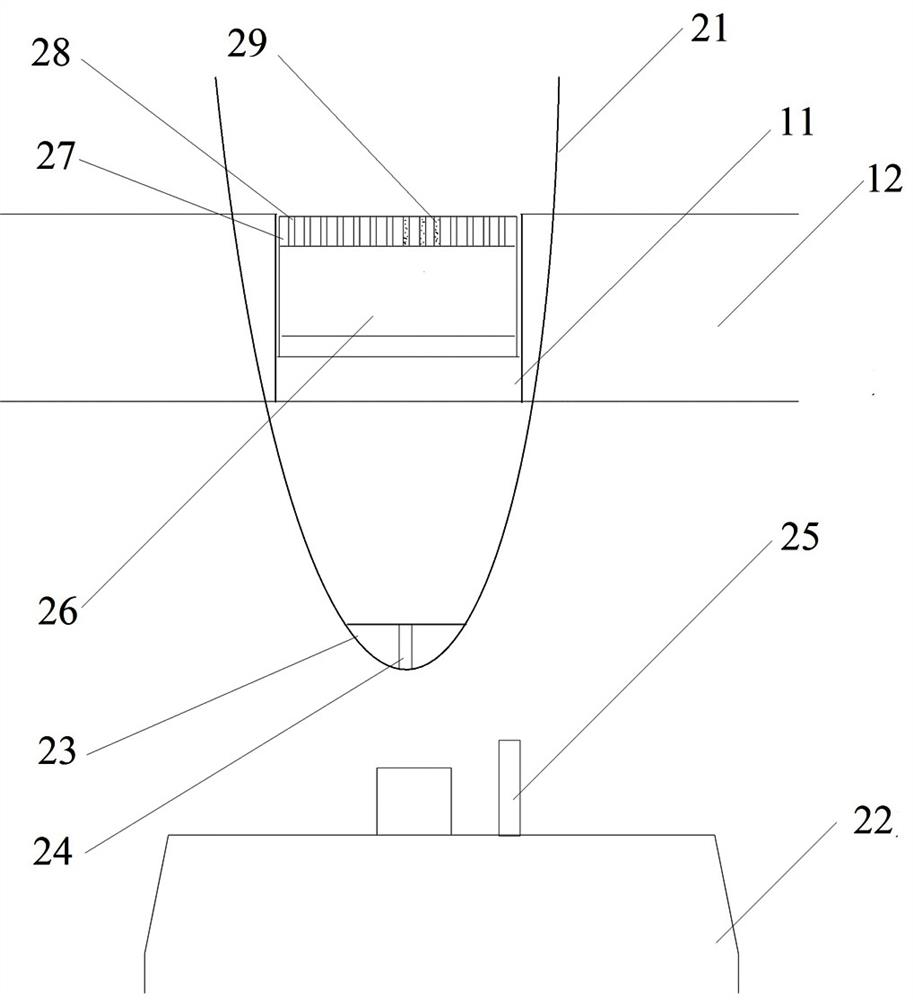

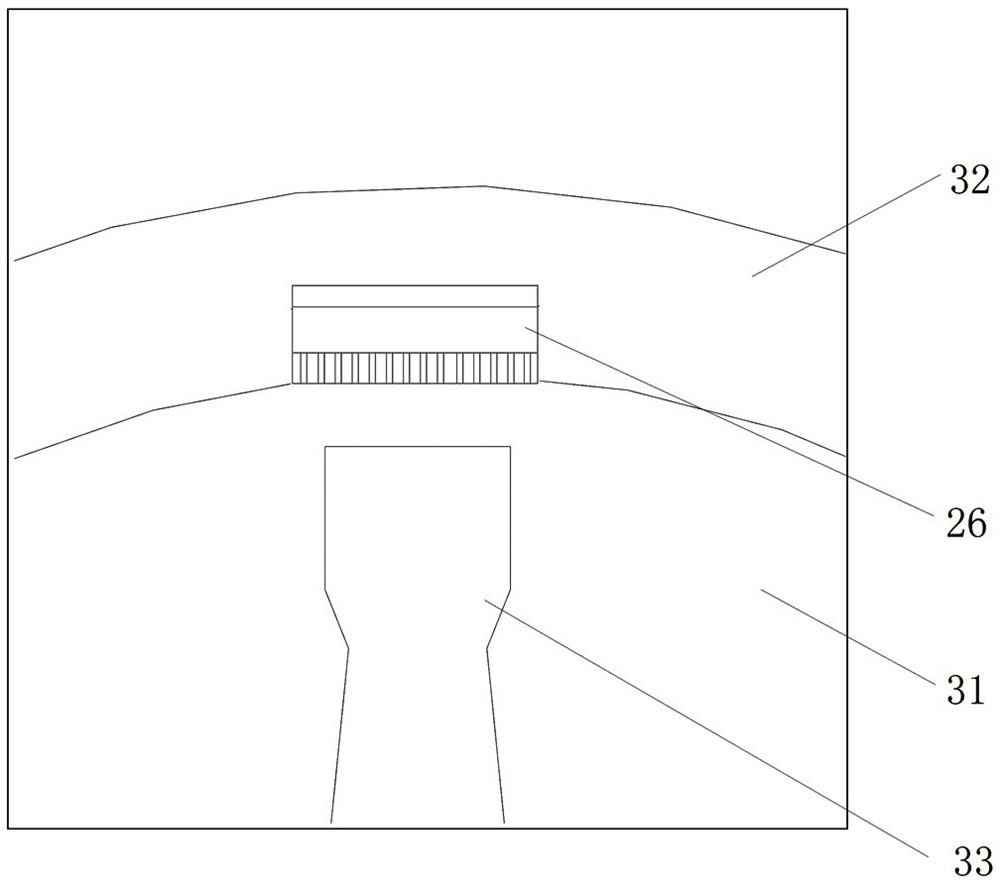

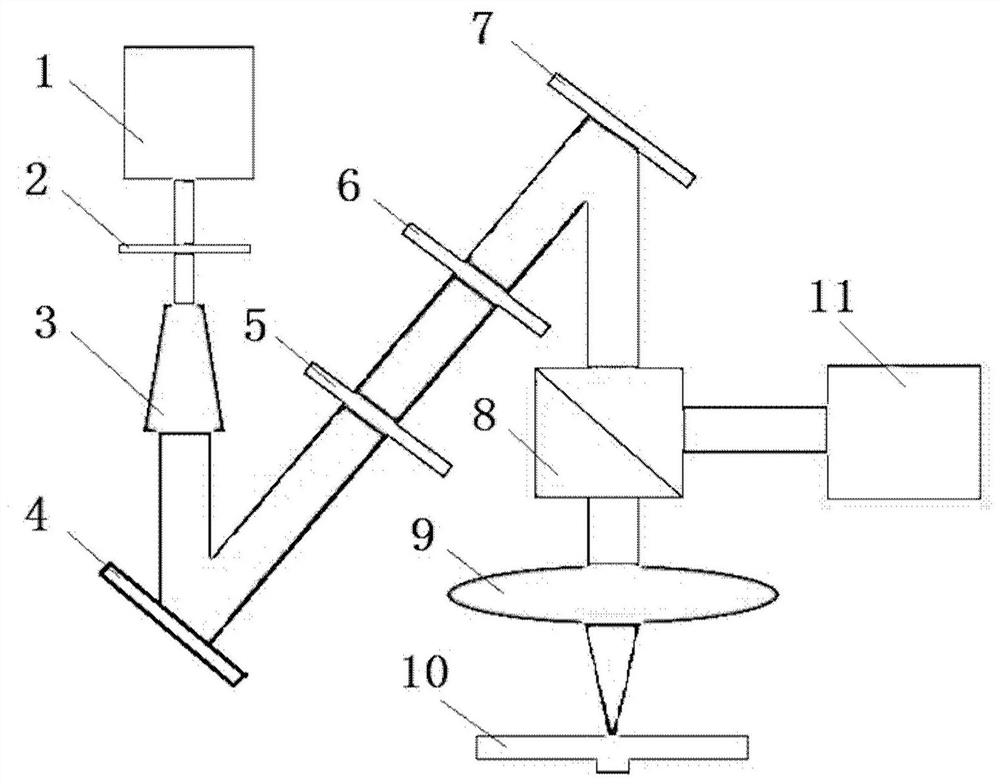

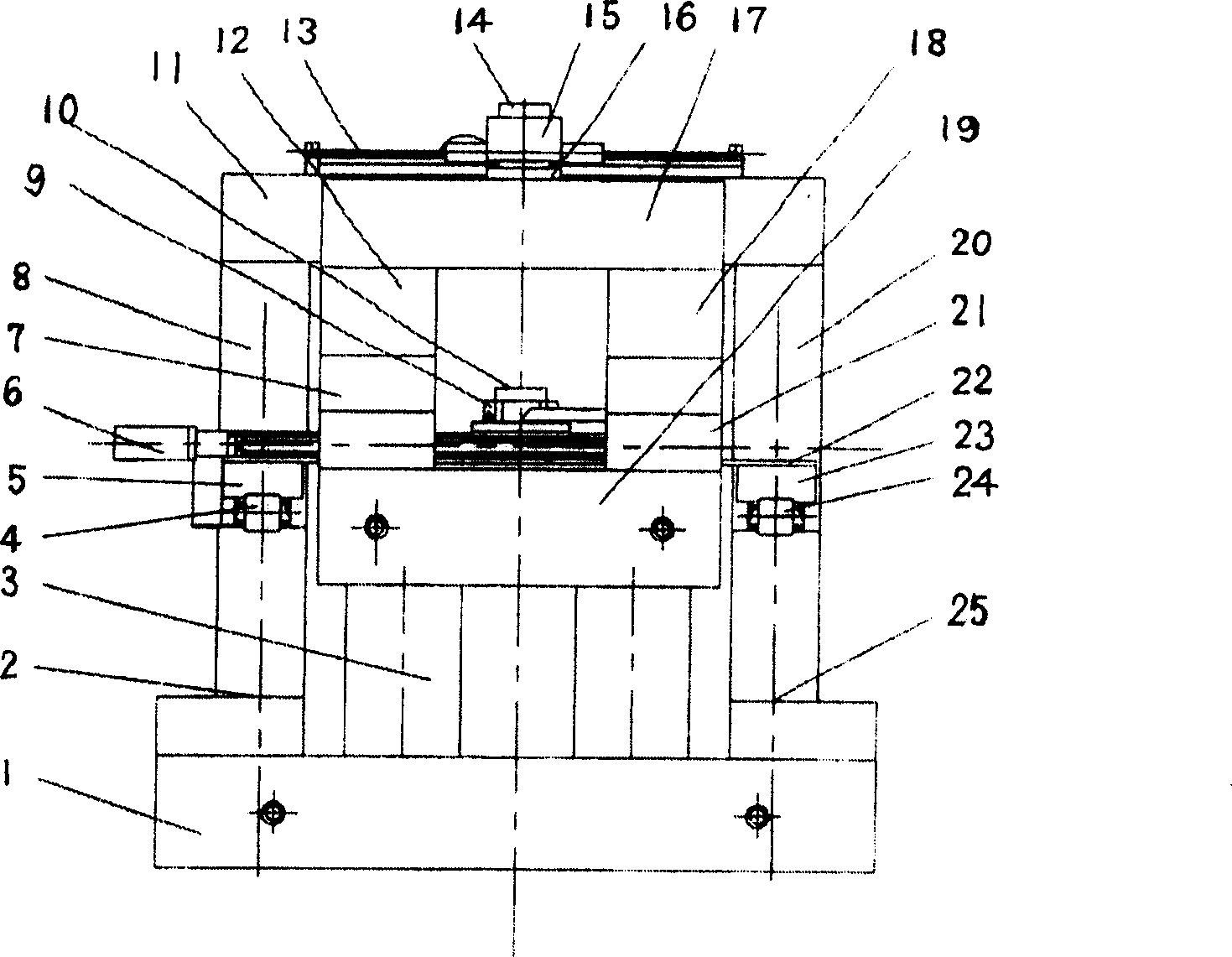

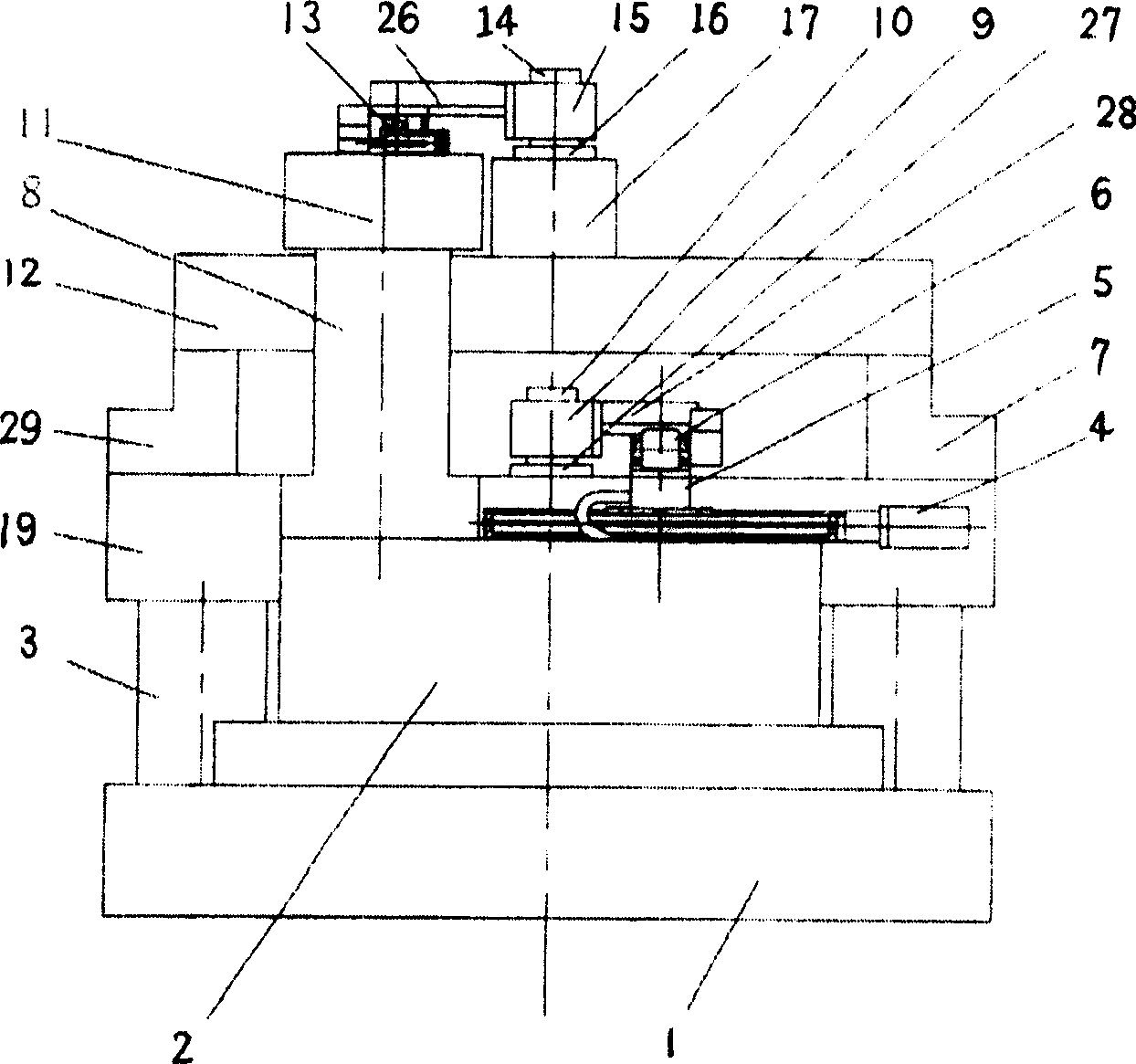

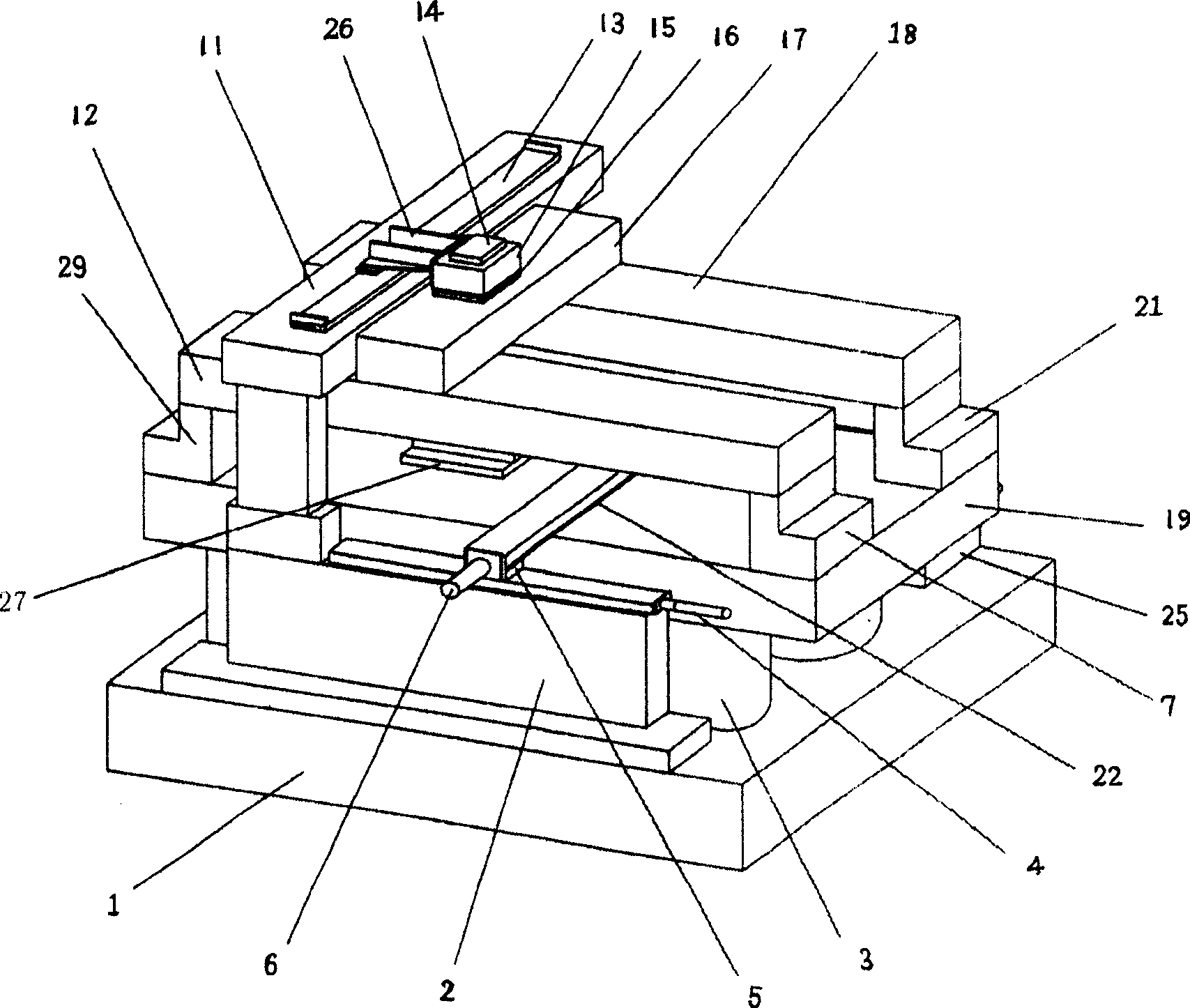

Stepped scanning photoetching machine vibration isolation system analoy experimental apparatus

InactiveCN1932647AImprove lithography precisionPrecise positioningSemiconductor/solid-state device manufacturingPhotomechanical exposure apparatusMachining vibrationsVibration control

The invention discloses a step-and-scan photoetching machine's isolation system simulation test device; it divides the whole test device into the internal world and the outside world. The outside world mostly complete the simulation of the photoetching machine's precision scanning movements, it lets the workpiece platform and the mask plate have the curve movement according to the schedule speed and acceleration, it completely reappears the true photoetching machine's step-and-scan movement, the internal world is mainly to install the optics system and the workpiece platform and the mask plate, and finishes the last photoetching service. Internal world and the outside world can be joined by the six degrees of freedom precision initiative vibration damper, it depresses the vibration of that the outside world passes to the internal world and this can ensure the internal world's quiet. The invention can let the core part-installation source system's work platform is in the range that the design allows. It improves the silicon's photoetching precision, at the same time; it has precise positioning and synchronous control of step-and-scan photoetching machine's isolation system simulation test device.

Owner:SHANGHAI MICRO ELECTRONICS EQUIP (GRP) CO LTD +1

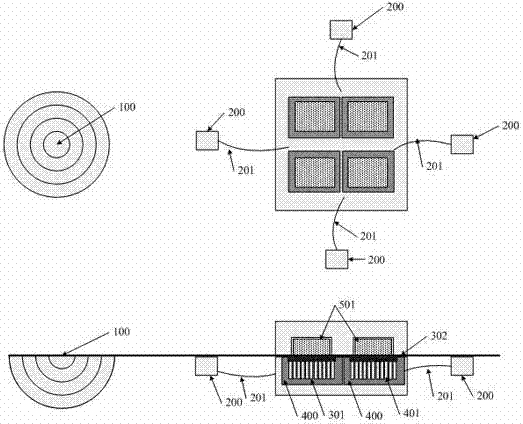

Suspension shakeproof equipment and method

ActiveCN104746527AImprove the vibration isolation effectImprove stabilityProtective foundationEngineering

Owner:SHANGHAI MICRO ELECTRONICS EQUIP (GRP) CO LTD

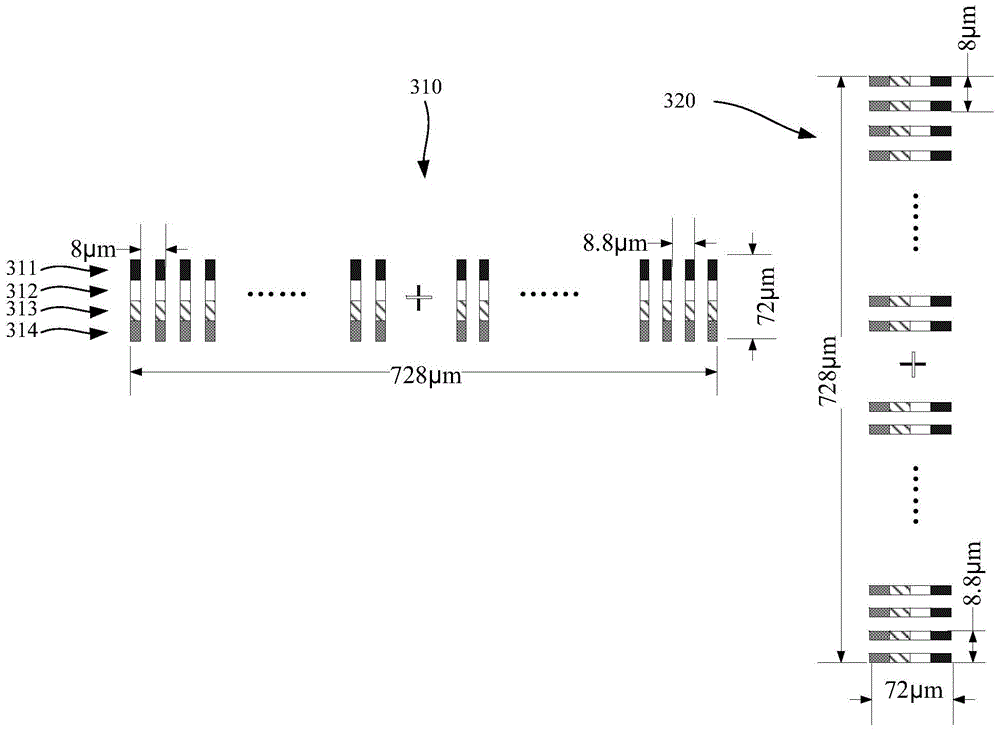

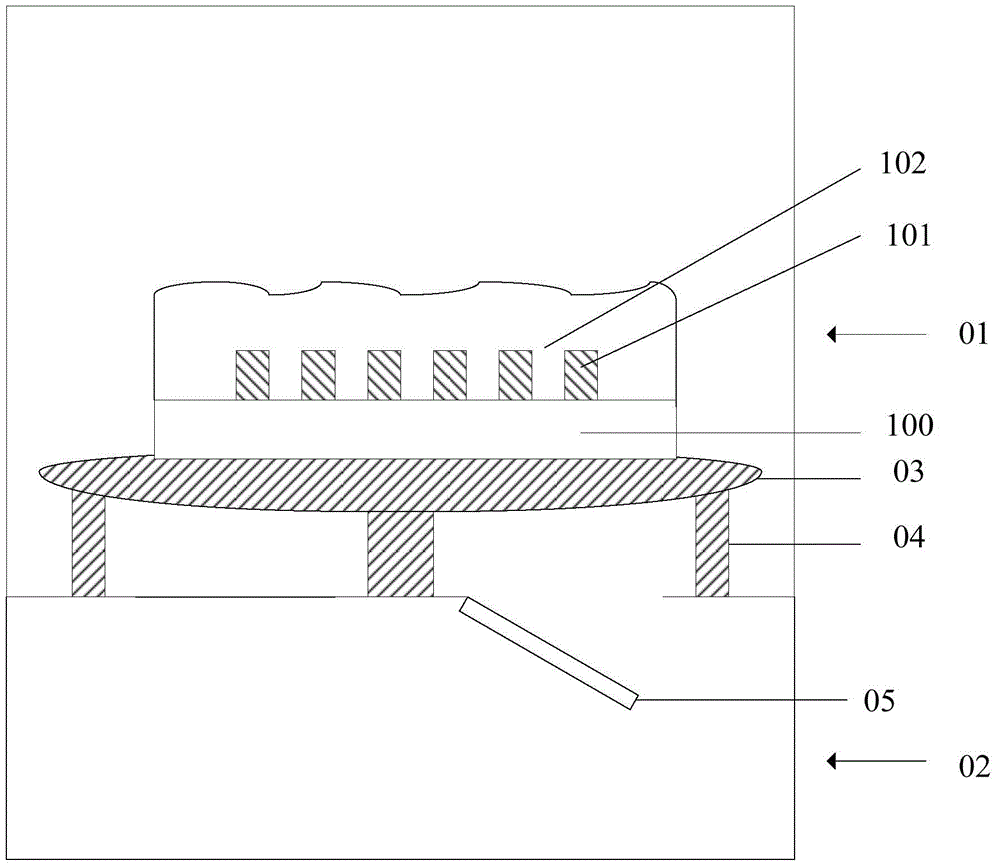

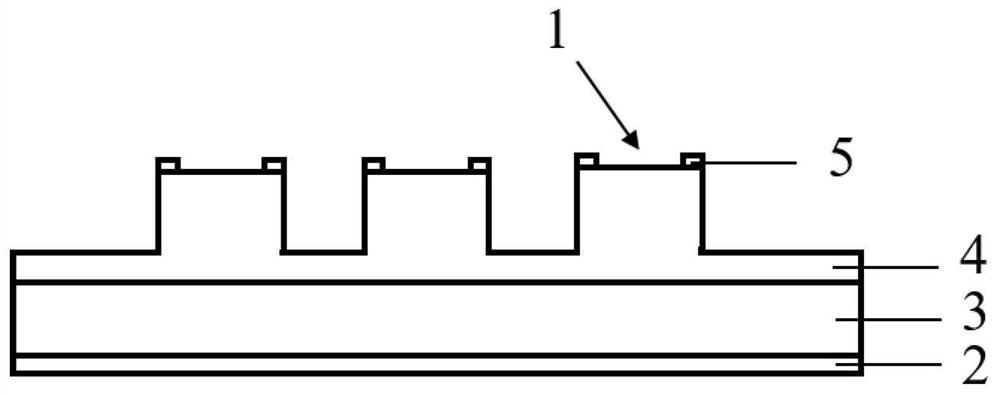

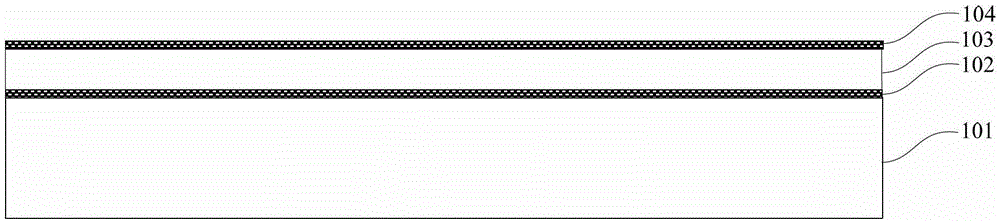

Small-spacing close-packed vertical cavity surface emitting laser and preparation method thereof

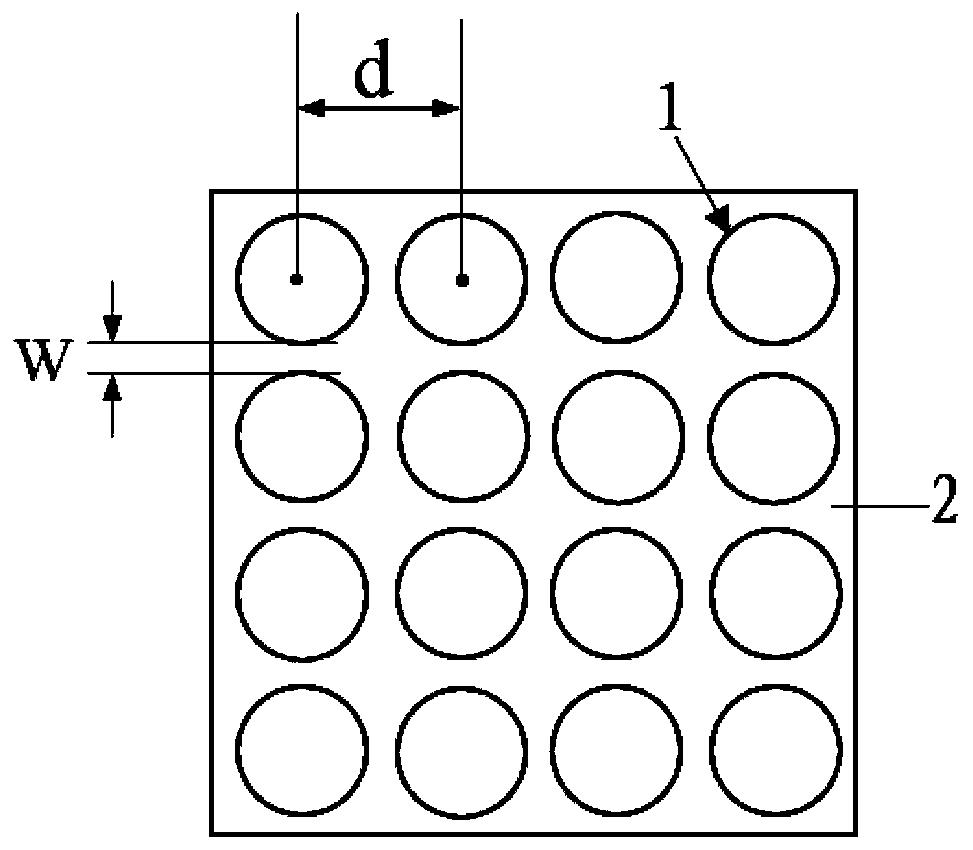

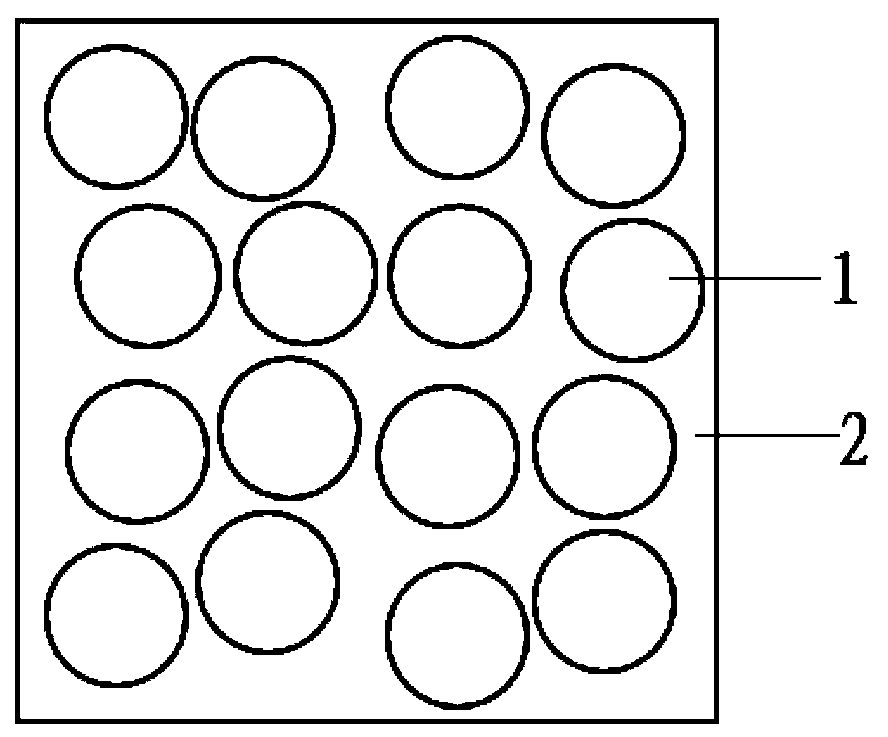

ActiveCN110137802AReduce warpageImprove lithography precisionLaser detailsSemiconductor lasersVertical-cavity surface-emitting laserLithographic artist

The invention provides a small-spacing close-packed vertical cavity surface emitting laser and a preparation method thereof. The laser includes a substrate, an epitaxial layer, mesas prepared on the epitaxial layer, upper electrodes and a lower electrode. The multiple mesas are arranged on the surface of one side of the epitaxial layer. Any mesa forms a light emitting point of the epitaxial layer.Any mesa is provided with upper electrodes thereon. The lower electrode is arranged on the surface of one side of the substrate. The center spacing between adjacent mesas is 8-20 microns, and the edge spacing between adjacent mesas is 0.5-5 microns. A layer of silicon oxide, silicon nitride or other dielectric material is deposited on the back of the epitaxial wafer. By adjusting the thickness and stress level of the material, the warpage of the epitaxial wafer is reduced. Therefore, the lithography precision in the manufacture of the small-spacing close-packed vertical cavity surface emitting laser is improved, and the preparation of a small-spacing close-packed vertical cavity surface emitting laser is realized.

Owner:EVERBRIGHT INST OF SEMICON PHOTONICS CO LTD

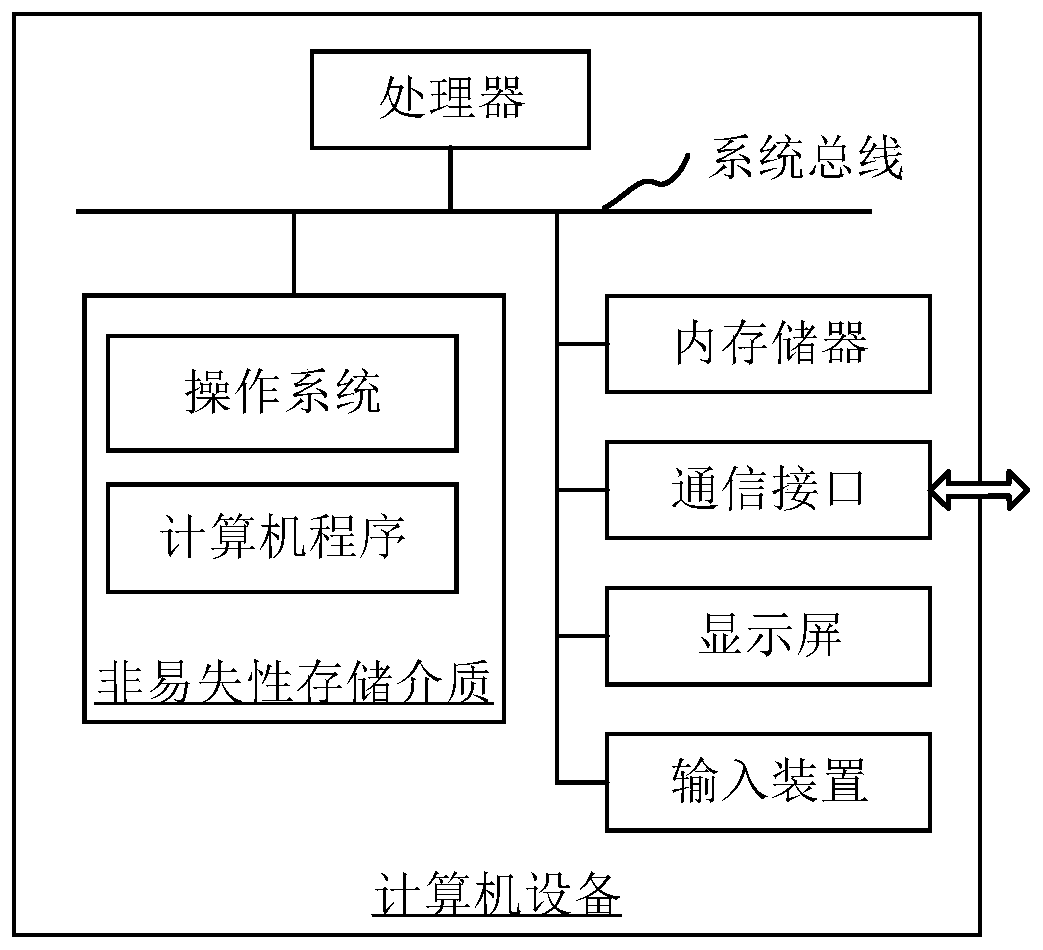

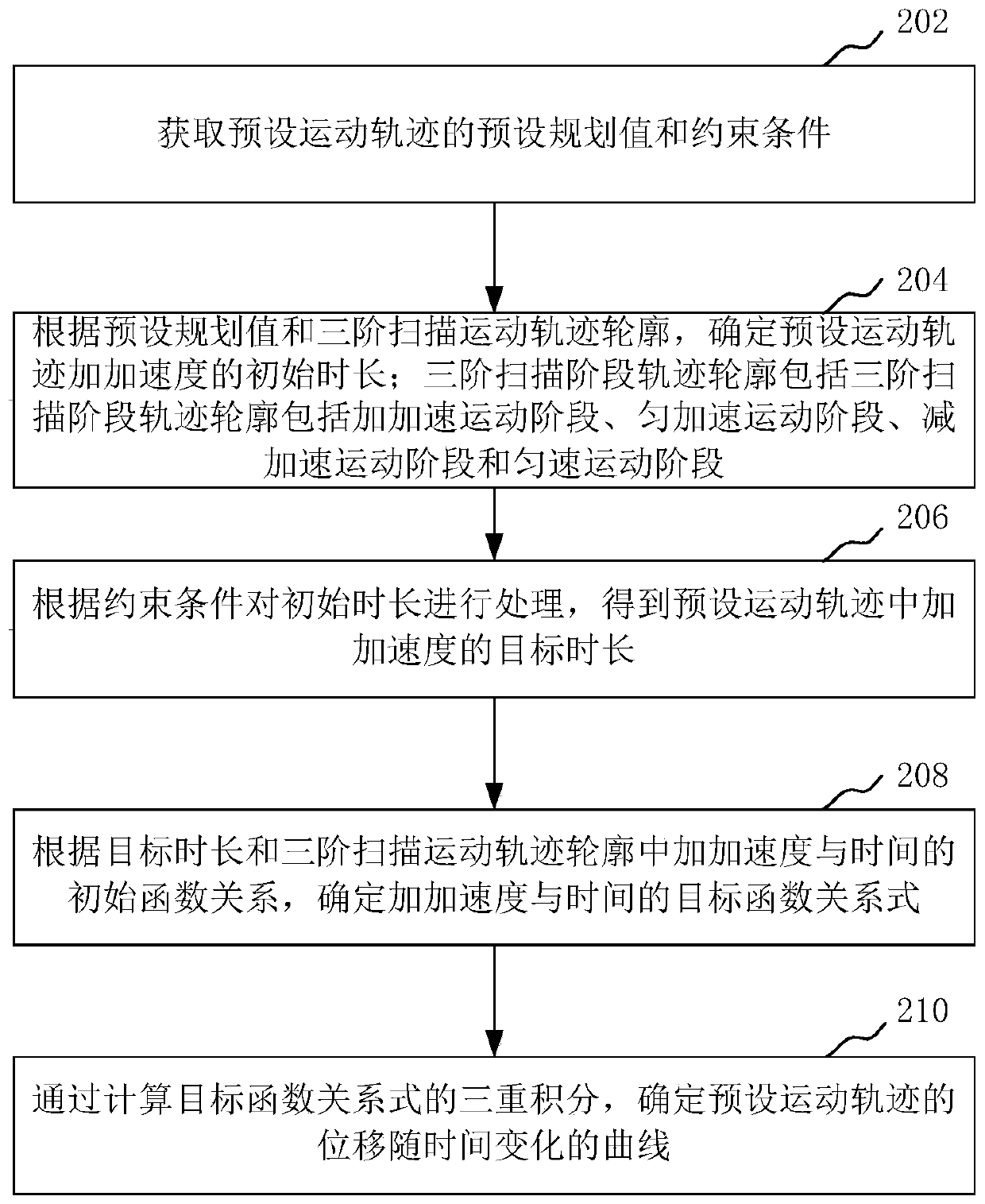

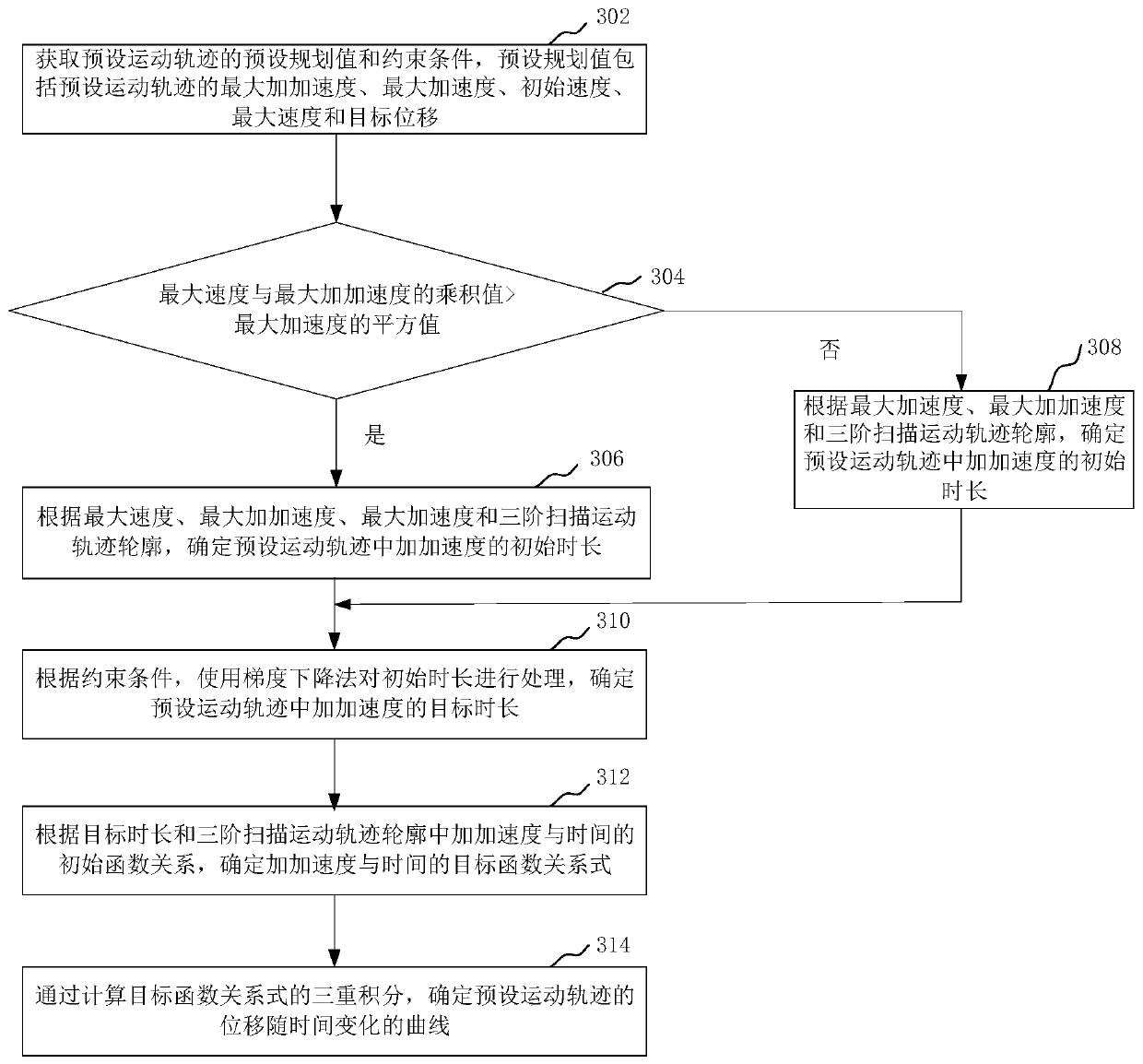

Photoetching machine motion track planning method and device, computer equipment and storage medium

PendingCN111474825AHigh movement precisionImprove lithography precisionPhotomechanical exposure apparatusMicrolithography exposure apparatusComputer equipmentClassical mechanics

The invention relates to a photoetching machine motion trail planning method and device, computer equipment and a storage medium. The method comprises the steps: acquiring a preset planning value anda constraint condition of a preset motion trail; determining the initial duration of jerk in the preset motion trail according to the preset planning value and a third-order scanning motion trail contour, wherein the third-order scanning stage track contour comprises a jerk motion stage, a uniform acceleration motion stage, a reduced acceleration motion stage and a uniform motion stage; processingthe initial duration according to the constraint condition to obtain a target duration of jerk in the preset motion trail; determining a target function relational expression of jerk and time according to the target duration and the initial function relation of the jerk and the time in the third-order scanning motion track contour; and determining a time-varying curve of the displacement of the preset motion trail by calculating triple integrals of the objective function relational expression. By adopting the method, the motion precision and photoetching precision of the photoetching machinecan be improved.

Owner:GOOGOL TECH SHENZHEN LTD GUANGDONG

Preparation method of high-precision photoresist

InactiveCN108803239AHigh water affinityImprove curing efficiencyPhotosensitive materials for photomechanical apparatusDecompositionAluminium hydroxide

The invention discloses a preparation method of high-precision photoresist and belongs to the technical field of photoetching. When carbon dioxide is used for carrying out carbonation decomposition ona sodium aluminate solution to prepare aluminum hydroxide powder, the causticity ratio of the sodium aluminate solution is reduced and the decomposition of an aluminum hydroxide crystal seed is inhibited; the granularity of aluminum hydroxide formed at the periphery becomes thin, so that the shrinkage rate is reduced when the photoresist is cured; in a curing process of the photoresist, part of aluminum hydroxide grains in a dispersed glue solution react with sodium silicate to generate nano silicon dioxide; surfaces of resin grains are covered with the nano silicon dioxide grains; modified epoxy acrylic resin utilizes a low-shrinkage additive which takes polystyrene with a similar curing shrinkage rate as a main material; the low-shrinkage additive is a core-shell-structure material andan inner core of the low-shrinkage additive is styrene; in a curing and shrinkage process, the steric hindrance is increased; the wavelength received by epoxy acrylate covered with the aluminum hydroxide grains is shorter, so that the photoetching precision of the photoresist is higher and the photoresist has a wide application prospect.

Owner:FOSHAN GAOMING DISTRICT ZHUAHE NEW MATERIAL TECH CO LTD

Alignment mark and its alignment method

ActiveCN104952851BImprove yieldImprove lithography precisionSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsLithographic artistProcess alignment

The invention discloses an alignment mark and its alignment method. The alignment mark includes a set of main marks formed on a semiconductor substrate, the main mark is composed of N groups of sub-marks, and the N groups of sub-marks Formed in N layers of film layers on the substrate, N is the number of layers that need to be aligned in this photolithography process; each group of sub-marks includes the first sub-mark in the horizontal direction and the second sub-mark in the vertical direction; the The first sub-marks are two groups of gratings in the horizontal direction, and the second sub-marks are two groups of gratings in the vertical direction. In this way, it can be aligned with multiple layers during alignment, thereby improving photolithographic precision and device yield.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

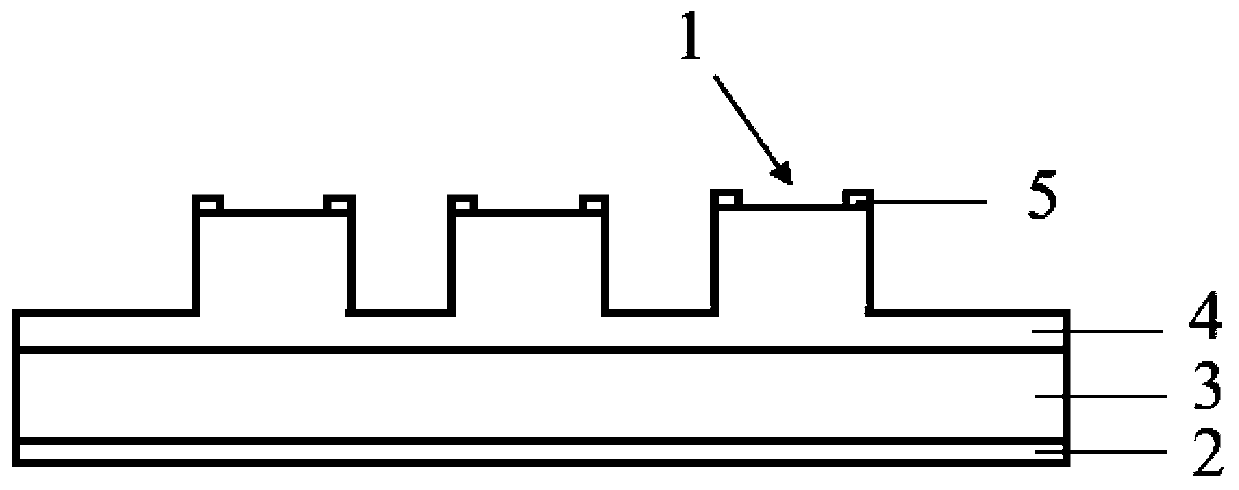

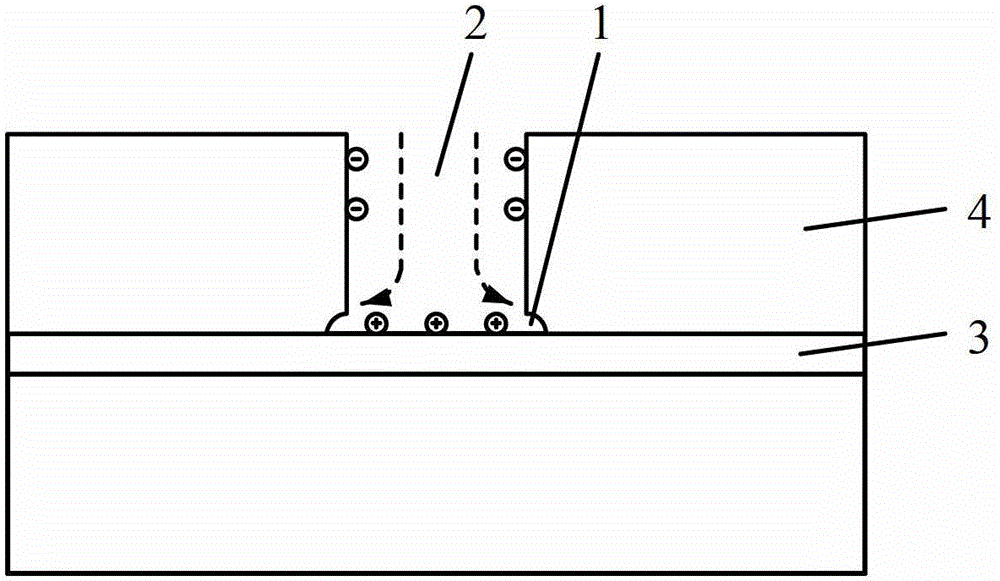

Double-hinge type electrostatic suspension probe structure

InactiveCN110515276AMake up deflection angleMake up requestPhotomechanical exposure apparatusMicrolithography exposure apparatusControl systemEngineering

Aiming at probe suspension of a certain photoetching machine, the present invention provides a double-hinge type electrostatic suspension probe structure, so that electrostatic suspension of a probe of a certain photoetching machine and a silicon wafer at the bottom of a photoetching machine is achieved under the assistance of a double-elastic hinge layer. The double-hinge type electrostatic suspension probe structure comprises a photoetching probe, an upper electrode layer, a lower electrode layer, a middle double-hinge layer and a suspension control system, the upper electrode layer and thelower electrode layer are identical in structure and comprise common electrodes and control electrodes, electrostatic force is applied through the upper electrode layer and the lower electrode layer,under the assistance of the middle double-hinge layer, the four movement freedom degrees of x, y, [theta] and [phi] of the probe are restrained, the suspension position can be adjusted in the z direction, and electrostatic suspension of the probe is achieved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Vacuum drying device and photolithographic process

InactiveCN103353209BIncrease bank angleImprove adhesionDrying using combination processesDrying solid materials without heatVacuum pumpingLithography process

A vacuum drying apparatus comprises a vacuum chamber provided with an exhaust vent and a chamber door, a vacuum pumping apparatus in communication with the exhaust vent, and a heating assembly disposed in the vacuum chamber. A vacuum drying method by using the vacuum drying apparatus comprises: when vacuum drying is performed on a substrate coated with a photoresist, simultaneously performing the heating and vacuum drying on the photoresist, the vacuum degree preferably ranging from 26Pa to 500Pa during the drying, and the heating temperature preferably ranging from 30 to 90 degrees centigrade, so as to produce less hardening films, thereby reducing the residual amount of a solvent in the photoresist, and improving the photolithographic accuracy.

Owner:BOE TECH GRP CO LTD +1

Wafer exposure method

PendingCN113721431APrecise positioningImprove lithography precisionPhotomechanical exposure apparatusMicrolithography exposure apparatusWaferExposure

The invention provides a wafer exposure method. When the wafer is exposed, firstly, the alignment mark area on the glued wafer is exposed through the first mask plate, and the development operation is carried out on the alignment mark area, so that when the secondary exposure is carried out, the alignment mark in the alignment mark area on the wafer can be clearly exposed, and exposure operation is carried out at the moment, so that the wafer can be accurately positioned, and the photoetching precision is effectively improved.

Owner:安徽光智科技有限公司

Photoetching machine system and photoetching method

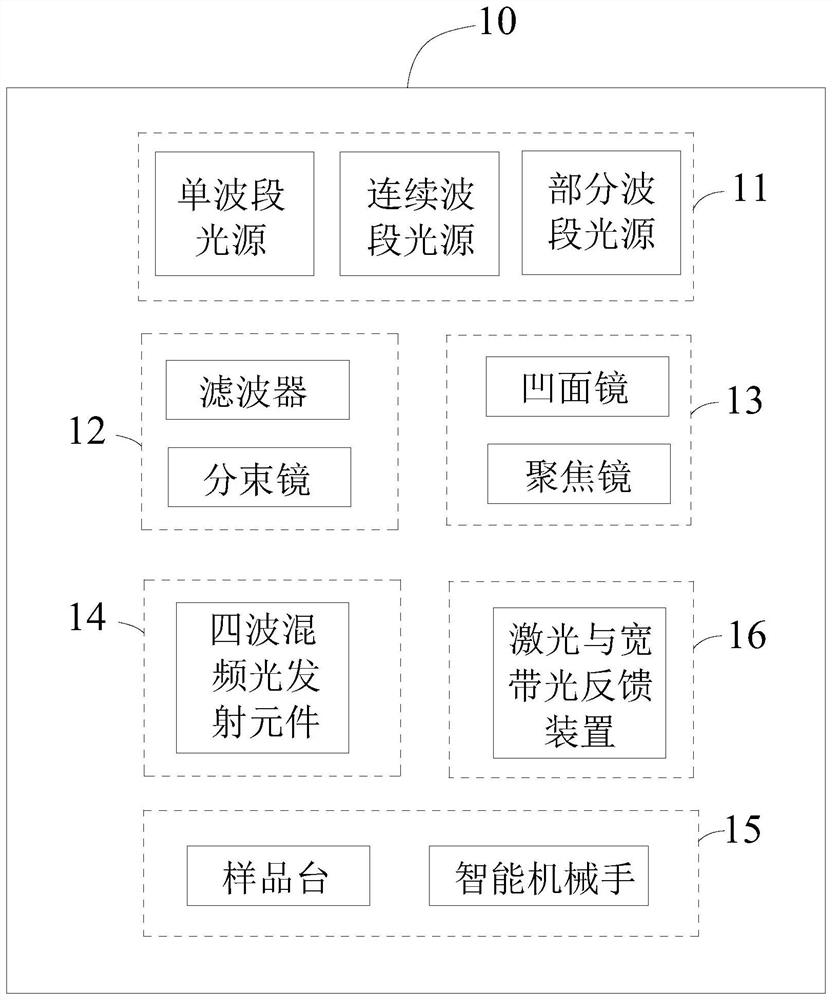

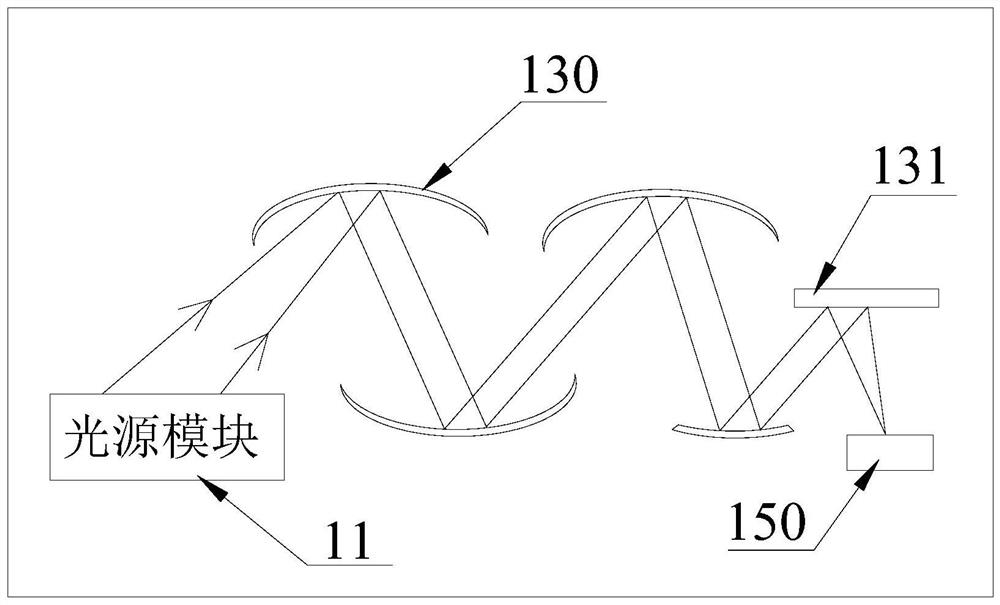

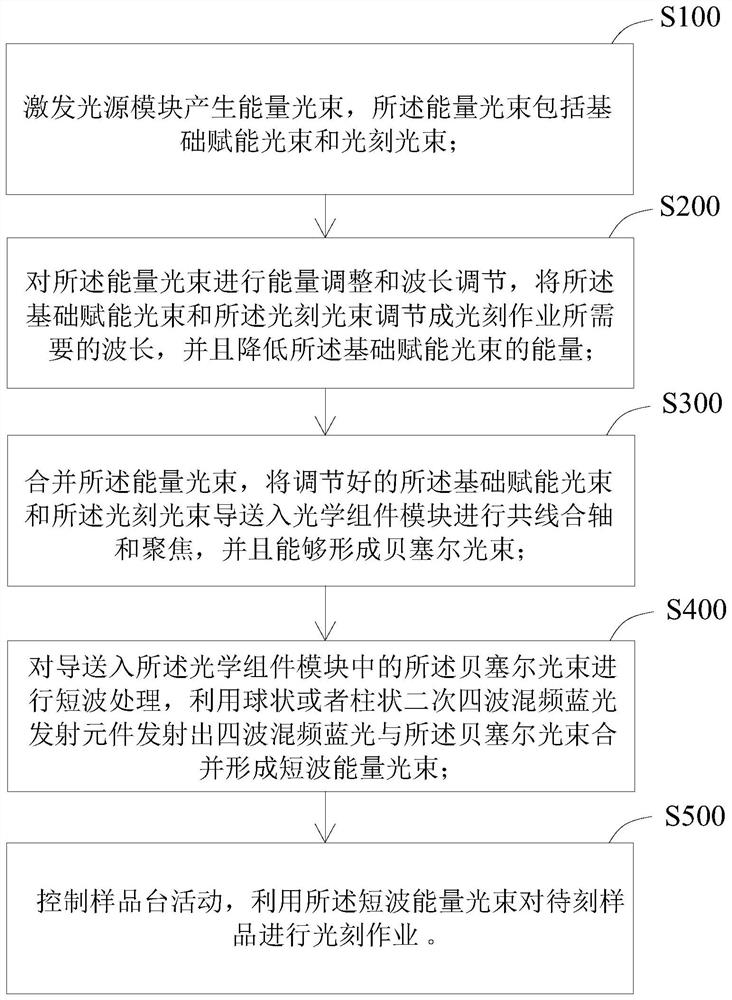

PendingCN114114856ARealize photolithography actionReduce line widthPhotomechanical exposure apparatusMicrolithography exposure apparatusBeam energyLine width

The invention relates to the technical field of photoetching machines, in particular to a photoetching machine system and a photoetching method. The photoetching machine system comprises a light source module, wherein the light source module can emit at least two energy light beams; the energy beam adjusting module is used for adjusting the wavelength and energy of the energy beam; the optical assembly module is used for carrying out collinear axis combination and focusing on the energy light beams to form Bessel light beams; the four-wave mixing light emitting module is used for providing four-wave mixing blue light, and the four-wave mixing blue light and the Bessel beam are subjected to collinear axis combination and focusing to form a short-wave energy beam; the movement assembly module comprises a sample table and an intelligent manipulator, the sample table is set to be in a position moving state, the intelligent manipulator is used for adjusting the position of a sample to be etched on the sample table, the line width of a photoetching light beam can be reduced infinitely through the system, the light beam can be reduced to 5nm, 3nm, 2nm or even lower, and the accuracy of photoetching is improved. And the power consumption is reduced while the photoetching precision is improved.

Owner:深圳市笨辉光电科技有限公司

EUV radiation source generating device for photoetching machine

PendingCN114397799AIncrease transmission speedIncrease tin loadingPhotomechanical exposure apparatusX-ray tube with very high currentExtreme ultravioletErbium lasers

The invention discloses an EUV radiation source generating device for a photoetching machine. The EUV radiation source generating device comprises a conveying belt, the device is characterized by further comprising an EUV radiation source generation unit, a cleaning unit, a fuel injection unit and a vacuum control unit, the EUV radiation source generation unit comprises a reflection cup and a laser; a light through hole is formed in a belt body of the conveying belt, a laser crystal is arranged in the light through hole, a coating is arranged on the upper portion of the laser crystal, a plurality of micron holes are formed in the coating, and fuel capable of generating extreme ultraviolet light is arranged in the micron holes. The cleaning unit comprises a fragment cleaning cavity and a steam jet; the fuel injection unit comprises a fuel injection cavity and a high-pressure nozzle; a first mechanical arm and an auxiliary light source are arranged on the front portion of the fuel injection cavity, and a second mechanical arm is arranged on the rear portion of the fuel injection cavity. The continuous operation of the device is effectively realized, the reliability of fuel filling is ensured, the production efficiency of the device is improved, and meanwhile, the aim of improving the photoetching precision is fulfilled.

Owner:张玥

A small-pitch close-packed vertical-cavity surface-emitting laser and its preparation method

ActiveCN110137802BReduce warpageImprove lithography precisionLaser detailsSemiconductor lasersVertical-cavity surface-emitting laserSilicon oxide

The invention provides a small-spacing close-packed vertical cavity surface emitting laser and a preparation method thereof. The laser includes a substrate, an epitaxial layer, mesas prepared on the epitaxial layer, upper electrodes and a lower electrode. The multiple mesas are arranged on the surface of one side of the epitaxial layer. Any mesa forms a light emitting point of the epitaxial layer.Any mesa is provided with upper electrodes thereon. The lower electrode is arranged on the surface of one side of the substrate. The center spacing between adjacent mesas is 8-20 microns, and the edge spacing between adjacent mesas is 0.5-5 microns. A layer of silicon oxide, silicon nitride or other dielectric material is deposited on the back of the epitaxial wafer. By adjusting the thickness and stress level of the material, the warpage of the epitaxial wafer is reduced. Therefore, the lithography precision in the manufacture of the small-spacing close-packed vertical cavity surface emitting laser is improved, and the preparation of a small-spacing close-packed vertical cavity surface emitting laser is realized.

Owner:EVERBRIGHT INST OF SEMICON PHOTONICS CO LTD

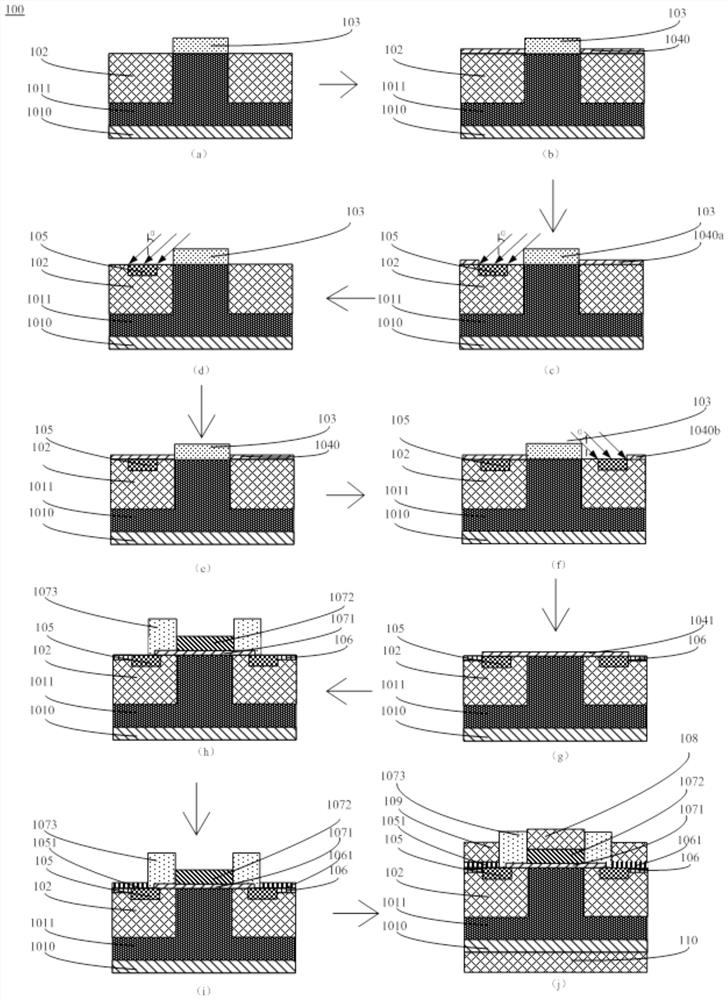

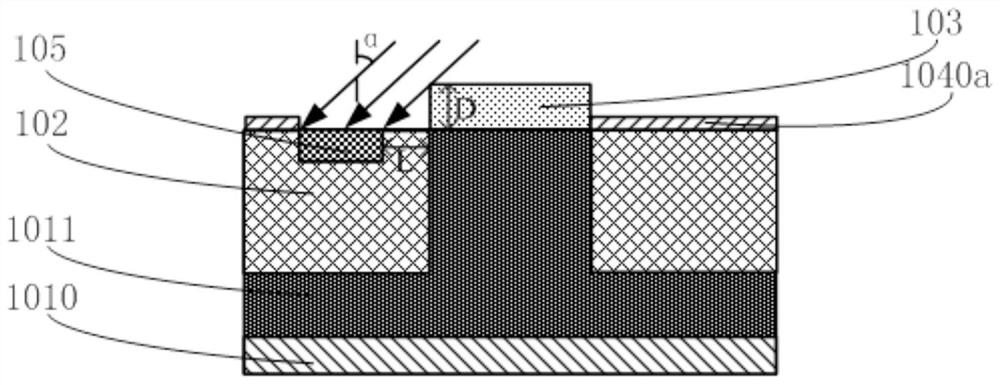

Preparation method of silicon carbide semiconductor device, silicon carbide semiconductor device and application of silicon carbide semiconductor device

PendingCN114156184AImprove controllabilityImprove stabilitySemiconductor/solid-state device manufacturingSemiconductor devicesCarbide siliconDevice material

The invention discloses a silicon carbide semiconductor device preparation method, a silicon carbide semiconductor device and application thereof, a first mask layer is formed on one side of a silicon carbide substrate layer, first injection is performed to form a well region, the silicon carbide substrate layer is of a first conductive type, and the well region is of a second conductive type; the first conductive type is opposite to the second conductive type, and the thickness of the first mask layer is 0.1-10 [mu] m; the first conduction type material is injected into the well region for the second time, a first source region is formed, and the angle between the first source region and the normal is 10-70 degrees during injection. According to the preparation method of the silicon carbide semiconductor device, the short channel with the required width is formed by adjusting the thickness and the injection angle of the mask layer, and the thickness and the injection angle of the mask layer can be accurately controlled through process parameters of equipment, namely, the required channel length can be controlled by adjusting the process parameters; and the controllability and the stability of preparing the silicon carbide semiconductor device with the required channel can be improved.

Owner:GTA SEMICON CO LTD

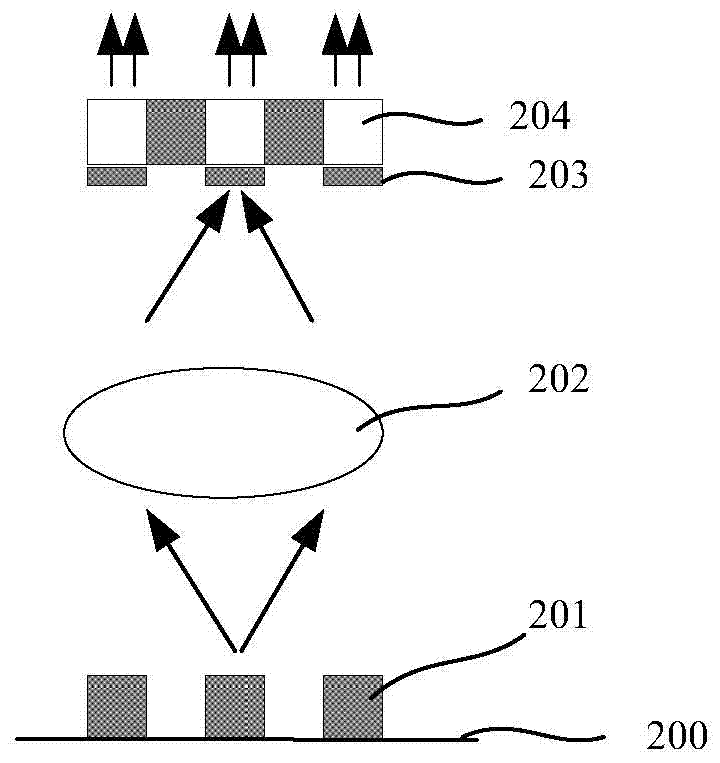

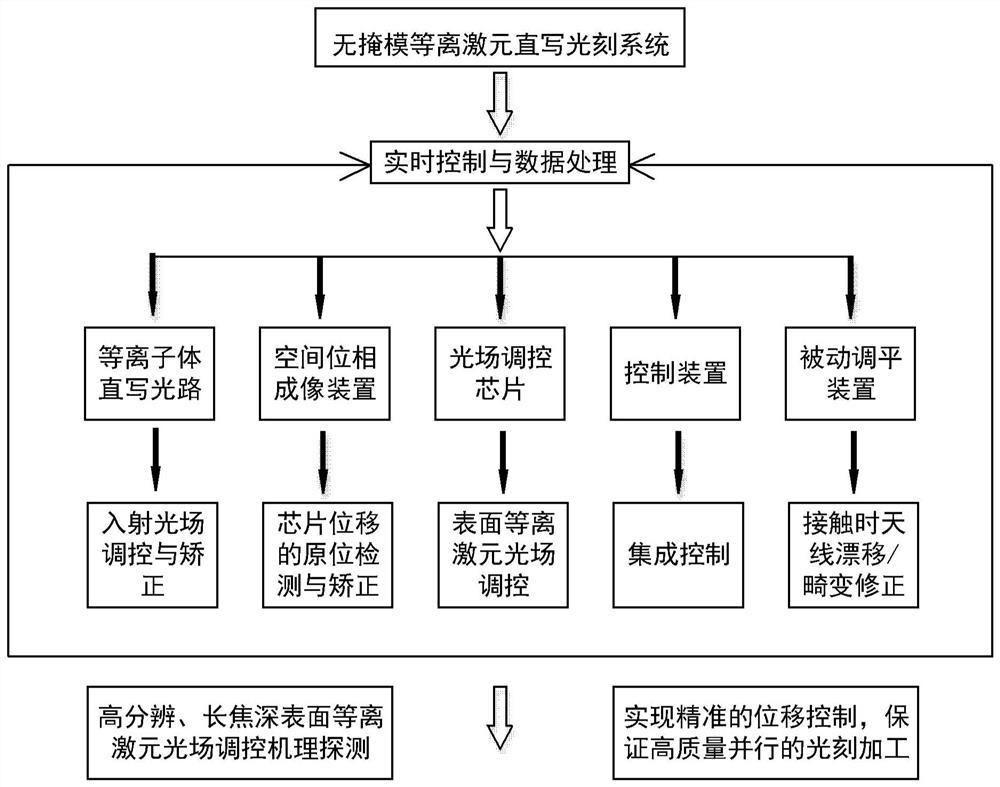

Maskless plasmon direct-writing photoetching system

InactiveCN112558429ALow cost of preparationImprove lithography precisionPhotomechanical exposure apparatusMicrolithography exposure apparatusOptical pathSurface plasmon polariton

The invention discloses a maskless plasmon direct-writing photoetching system which comprises a light field regulation and control chip used for exciting to generate surface plasmon as an exposure light field of direct-writing photoetching, a plasma direct writing light path used for providing incident light for a light field regulation and control chip, a spatial phase imaging device, a passive leveling device and an adjusting device, wherein the spatial phase imaging device includes a detector and a frequency conversion grating, the frequency conversion grating receives reflected light of asample and generates interference fringes, and the detector receives the interference fringes and judges the distance between the light field regulation and control chip and the sample; the passive leveling device is used for passively adjusting the parallelism of the chip and the surface of the sample during high-precision contact exposure; and the adjusting device is used for adjusting the relative position of the light field regulation and control chip and the sample, the distance between the light field regulation and control chip and the sample can be accurately adjusted through the spatial phase imaging device, a complex and high-precision system design is not needed, the preparation cost is low, higher photoetching precision can be achieved, and the precision can reach 20-500 nm.

Owner:UNIV OF SCI & TECH OF CHINA

Semiconductor etching device and etching method for semiconductor structure

ActiveCN103021912BAvoid contaminationAvoid pollutionElectric discharge tubesSemiconductor/solid-state device manufacturingSemiconductor structureBlocking layer

Disclosed are a semiconductor etching device and an etching method of a semiconductor structure. The etching method includes: a etching process with a first bias power source is utilized to etch a to-be-etched material layer, and the first bias power source generates continuous bias power to form a first opening which does not expose a etching blocking layer; and then a etching process with a second bias power source is utilized to etch the first opening, and the second bias power source generates pulse bias power until the etching blocking layer is exposed to form a second opening. Due to the fact that the continuous bias power is utilized to form bias voltage for etching firstly, side wall appearance is good, and etching selection ratio to a photo layer is high. The continuous bias power is switched into pulse bias power to form bias voltage for etching in prior to exposure of the etching blocking layer, so that cuts are avoided from being formed at the side wall bottom, close to the etching blocking layer, of the to-be-etched material layer.

Owner:ADVANCED MICRO FAB EQUIP INC CHINA

Intelligent reversible photosensitive femtosecond laser photoresist and photoetching processing method

PendingCN113253572AEnhanced inhibitory effectImprove lithography precisionPhotomechanical apparatusFemto second laserNonlinear absorption

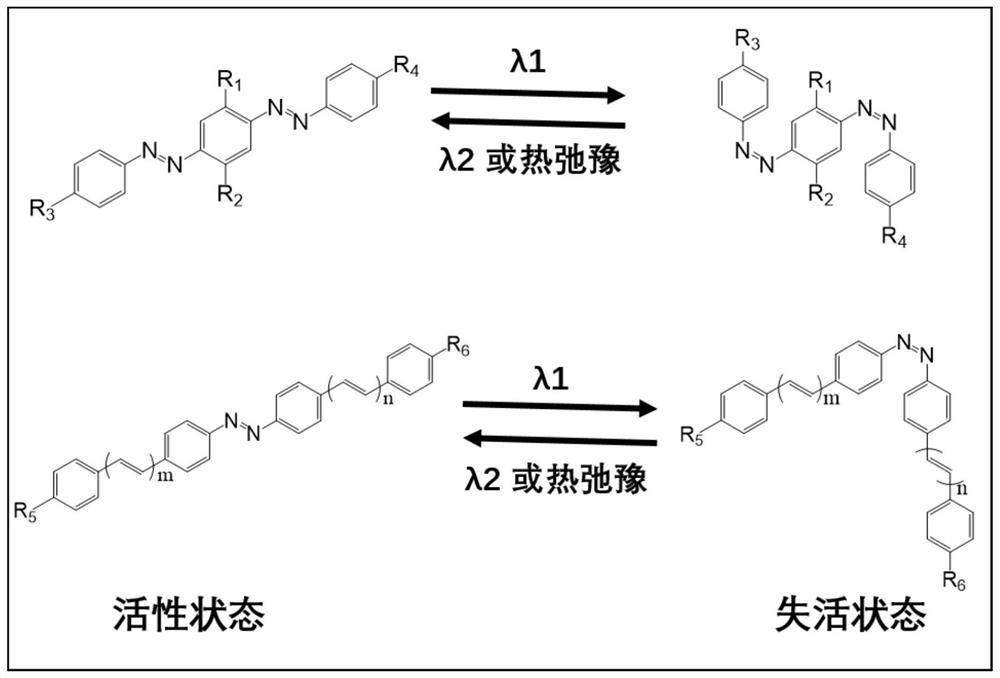

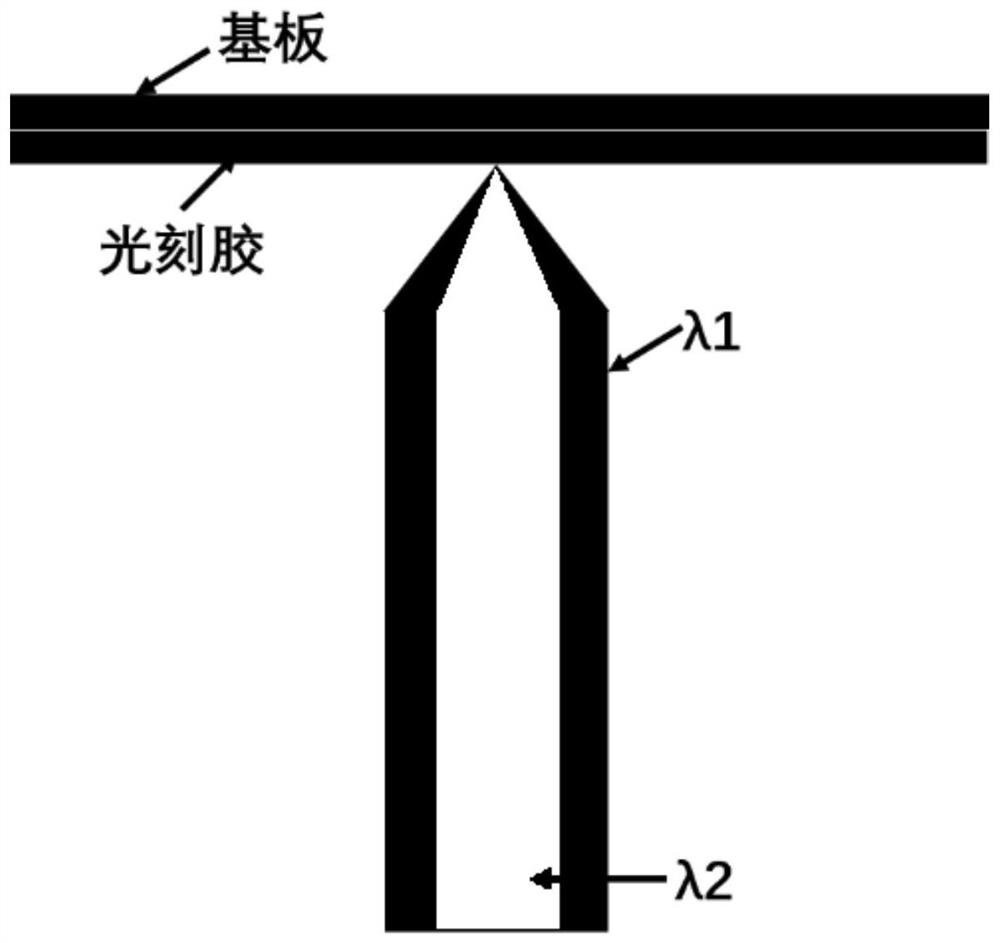

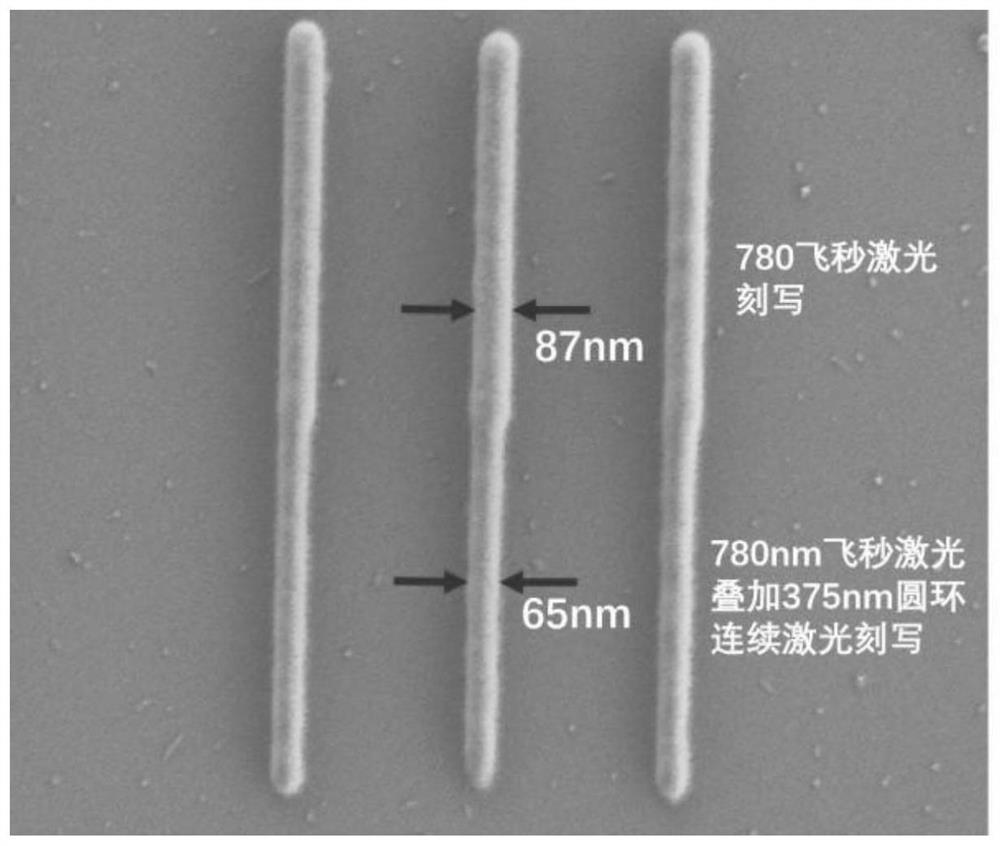

The invention discloses an intelligent reversible photosensitive femtosecond laser photoresist and a photoetching processing method. The intelligent reversible photosensitive femtosecond laser photoresist is characterized in that the intelligent reversible photosensitive femtosecond laser photoresist comprises a reversible photoinitiator which has reversible photosensitivity, and under the stimulation of a light source with the wavelength of 350-550 nm, the reversible photoinitiator can be subjected to structural conformation transformation, loses the nonlinear absorption capacity for femtosecond laser with the wavelength of 700-1000 nm and becomes inactive, so that the photochemical reaction of the photoresist is controlled, and higher photoetching precision is obtained; and the intelligent reversible photosensitive femtosecond laser photoresist is prepared from 0.1-6 wt% of a reversible photoinitiator A and 94-99.9 wt% of resin B.

Owner:ZHEJIANG LAB +1

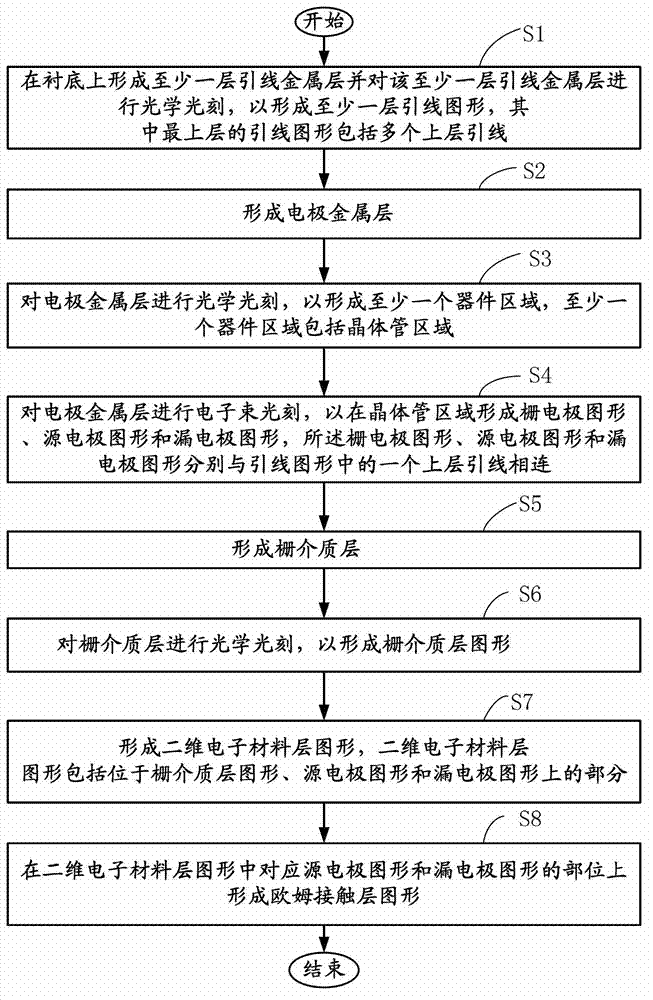

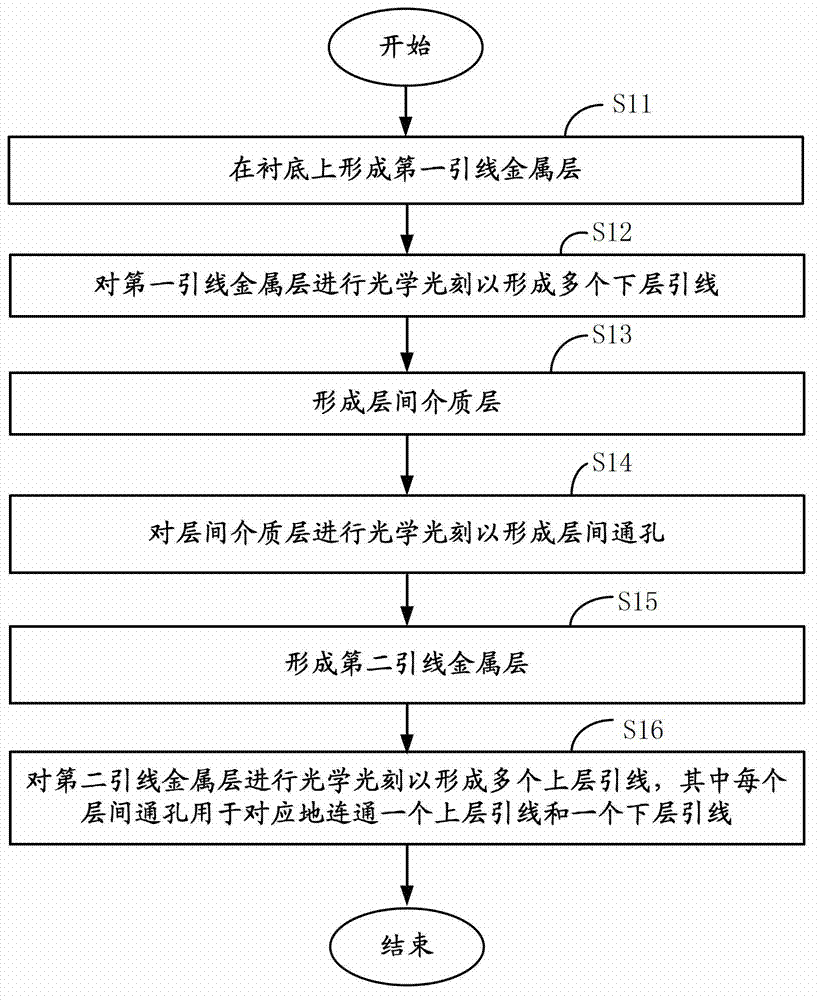

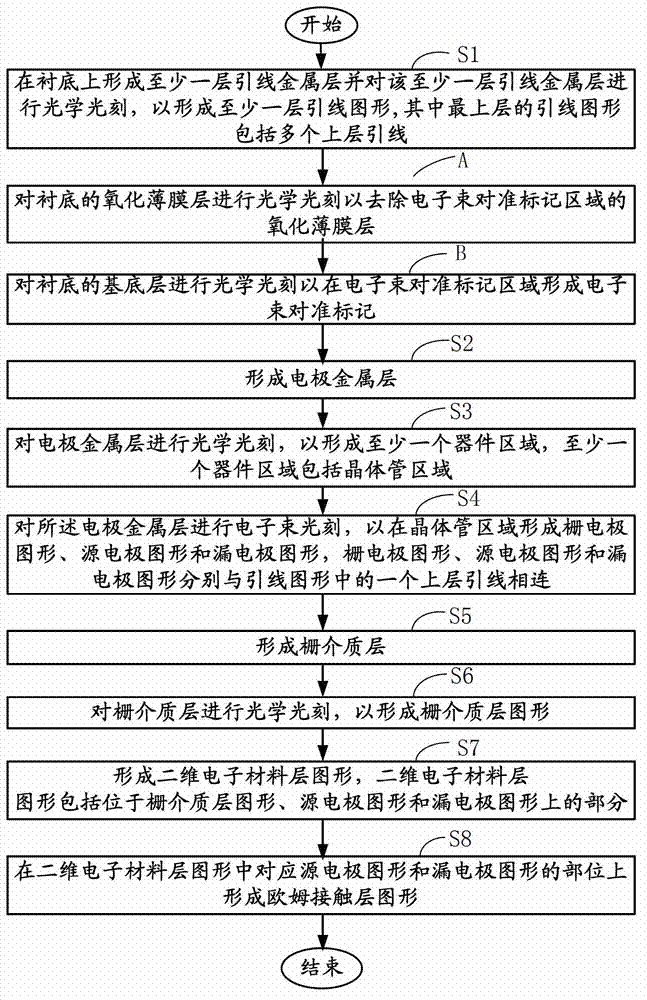

Two-dimensional electronic material device and mixed photoetching method thereof

ActiveCN102945794BSimple processReduce the number of photolithographySemiconductor/solid-state device detailsSolid-state devicesOhmic contactLead Metal

The invention relates to a two-dimensional electronic material device and a mixed photoetching method thereof, wherein the method comprises the following steps: forming at least one lead metal layer on a substrate, and performing optical photoetching on the at least one lead metal layer so as to form at least one layer of lead figures, wherein an uppermost layer comprises a plurality of upper layer leads, and a grid electrode, a source electrode and a drain electrode are respectively connected with one upper layer lead; forming an electrode metal layer; performing the optical photoetching on the electrode metal layer so as to form a transistor region; performing electron-beam photoetching on the electrode metal layer so as to form the figures of the grid electrode, the source electrode and the drain electrode; forming a grid dielectric layer; performing the optical photoetching on the grid dielectric layer so as to form the figure of the grid dielectric layer; forming the figure of a two-dimensional electronic material layer; and forming the figure of an ohmic contact layer. The device is capable of eliminating or decreasing the destruction of intrinsic properties of the two-dimensional electronic material, capable of greatly improving the photoetching precision of small-size devices based on guaranteeing the process cost and improving the performance of the devices, and capable of saving the processing time based on guaranteeing the processing precision.

Owner:TSINGHUA UNIV

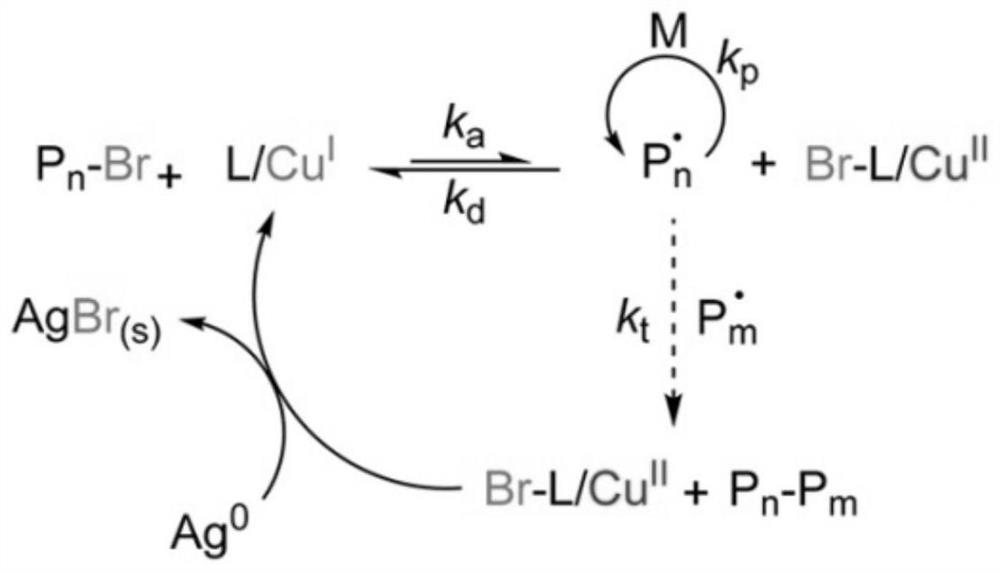

Acrylic resin and preparation method and application thereof

ActiveCN112175133ALow number average molecular weight distributionReduce concentrationPhotosensitive materials for photomechanical apparatusBulk chemical productionPolymer scienceCu2 ions

The invention provides acrylic resin as well as a preparation method and application thereof. The preparation method of the acrylic resin comprises the steps of mixing an acrylic monomer, cuprous bromide, a ligand, an initiator and a reducing agent in a reaction solvent, and then carrying out polymerization reaction, wherein the reducing agent is elemental silver, and the quantity of the reducingagent is sufficient. According to the preparation method of the acrylic resin, zero-valent elemental silver is used as a mild reducing agent, monovalent copper ions in the polymerization process can be kept constant, the active polymerization reaction process is controllable, and the acrylic resin generated through polymerization has lower number-average molecular weight distribution, for example,the number-average molecular weight distribution of the acrylic resin is less than 1.2.

Owner:NINGBO NATA OPTO ELECTRONICS MATERIAL CO LTD

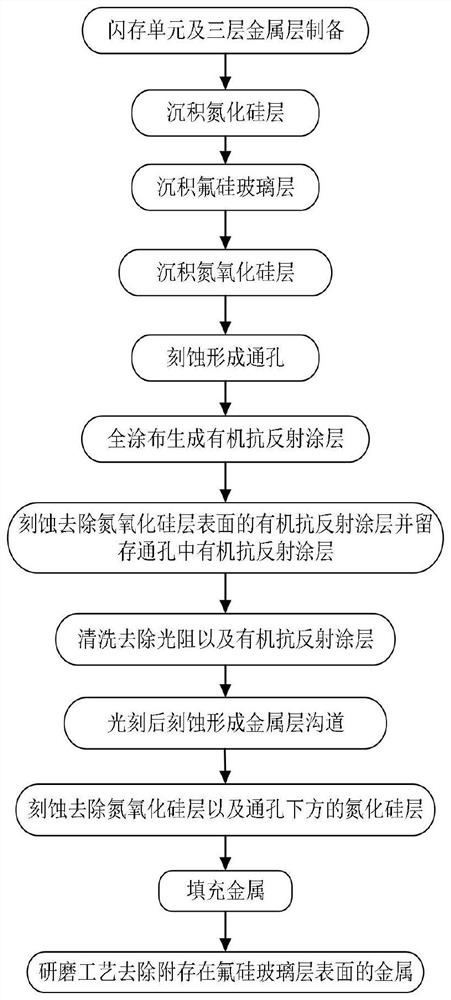

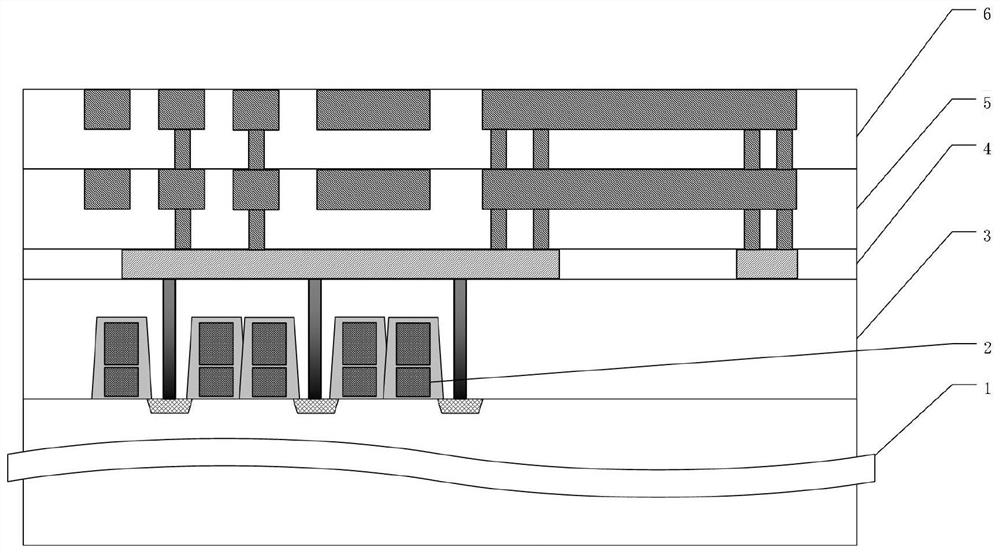

NOR flash memory manufacturing method, circuit and application thereof

PendingCN113809005AImprove electrical performanceImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesWaferHemt circuits

The invention relates to the technical field of semiconductor manufacturing, and discloses a NOR flash memory manufacturing method, circuit and application thereof. The method comprises the steps that on the basis of a wafer of a NOR flash memory circuit with a flash memory unit and three metal layers, a third metal layer is covered with a fourth metal layer communicated with the third metal layer. The method disclosed in the invention is compatible with the existing process. The metal wiring requirement of the Nor flash memory chip with more complex functions can be met, feasible preconditions are provided for arranging more aluminum pads to meet the requirement of advanced packaging pressure welding, and the practical value in practical significance is achieved.

Owner:HEFEI HENGSHUO SEMICON CO LTD

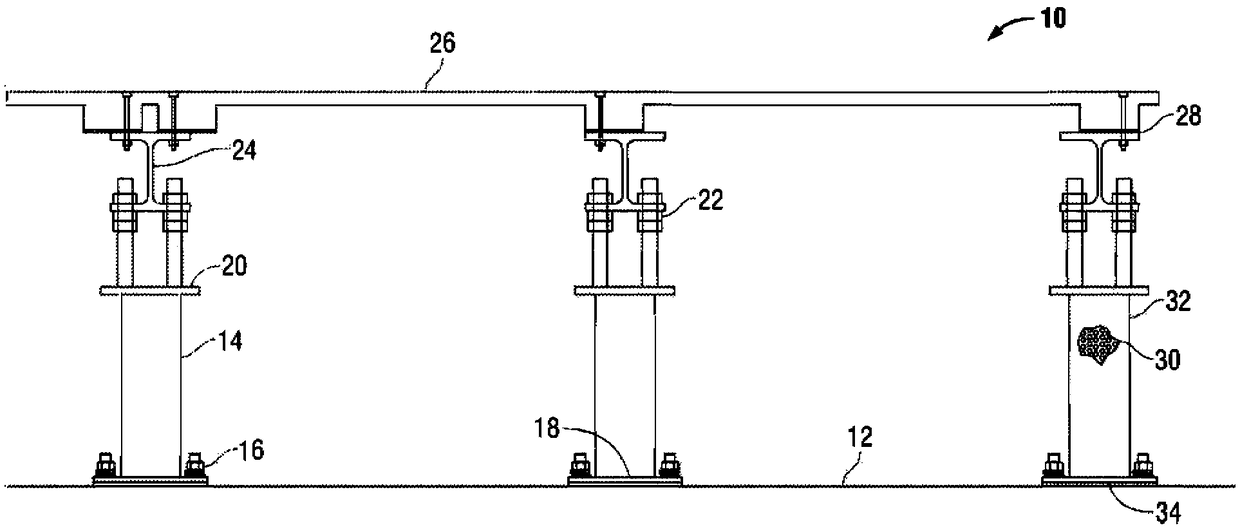

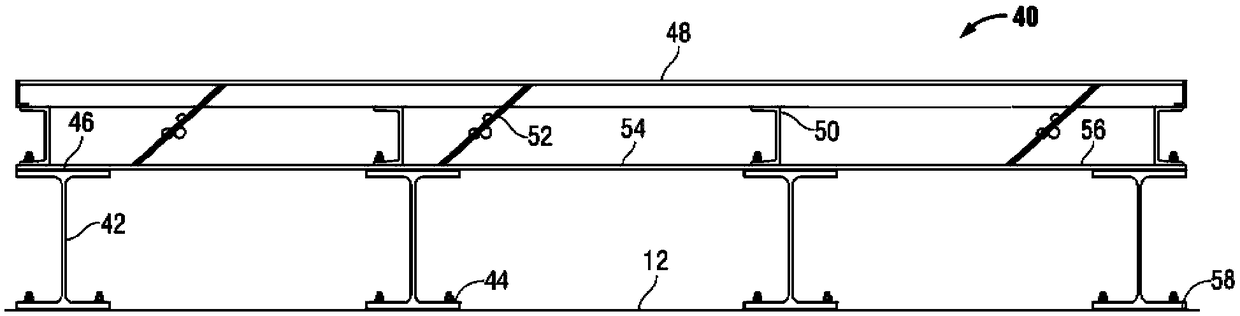

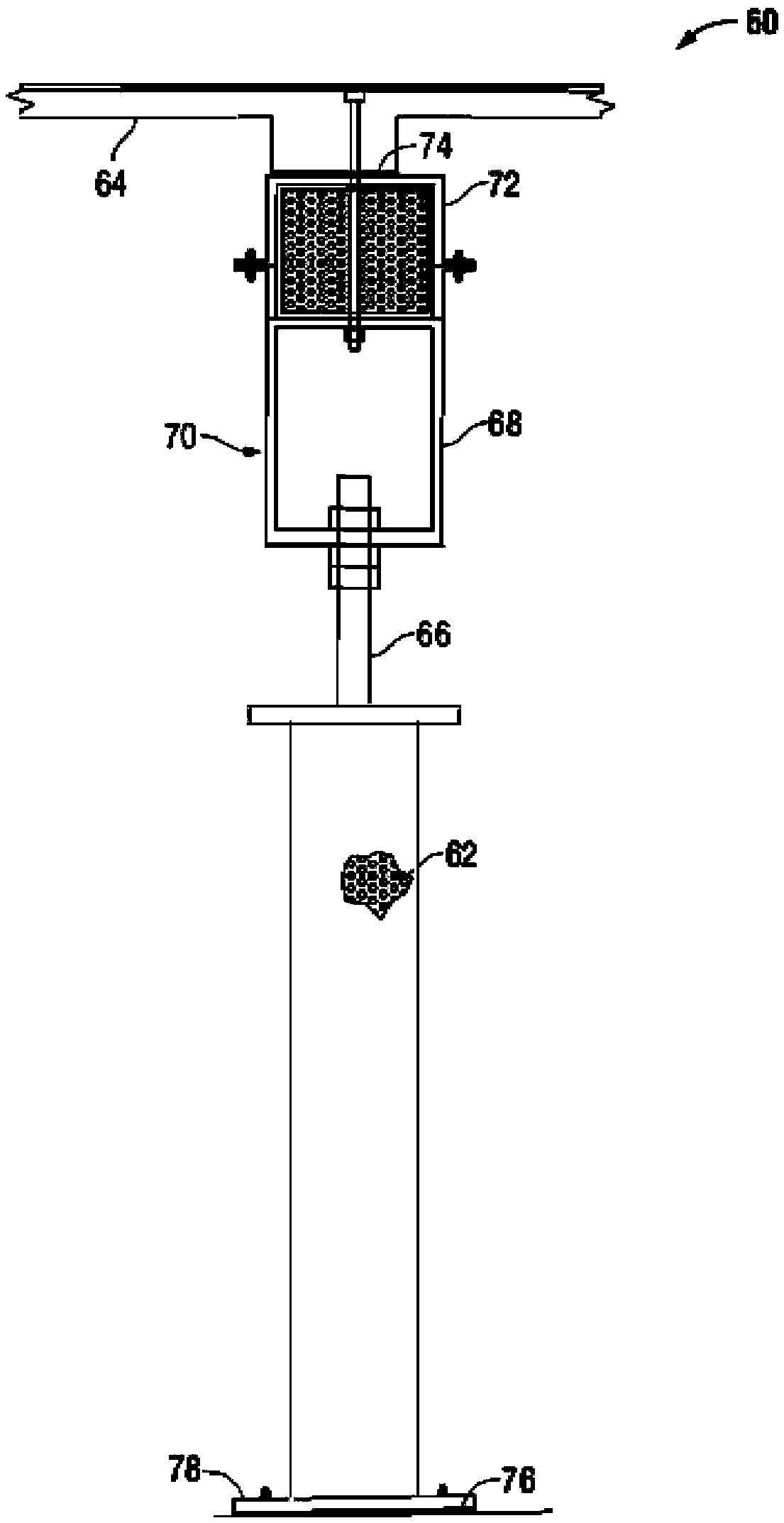

Method for improved semiconductor processing equipment tool pedestal/pad vibration isolation and reduction

InactiveCN109496255AEliminate vibration frequencyVibration is eliminated or greatly reducedMachine framesStrutsSemiconductor chipEngineering physics

A method to improve vibration isolation in semiconductor process level inhibits vibration frequencies transmitted through building structure from production tools, pumps, compressors, chillers, AHUs (Air Handling Units), and footfalls traffic on raised floor system on to tool pedestals and pads from affecting semiconductor fabrication processes. Rapid advancement and technological evolution in semiconductor industry foresee the imminent requirements for decrease in semiconductor chip node sizes to single digit nanometer. Dealing with such advancements, the tool pedestal systems are also requiring tighter specifications for stiffness and vibration isolation / reduction. Some key tools used in the semiconductor fabrication process require improved barrier from electromagnetic interference (EMI), as the disturbance from EMI degrade the performance of semiconductor processing tools that are key to the fabrication process and production yield rate.

Owner:에스케이커머셜컨스트럭션인크

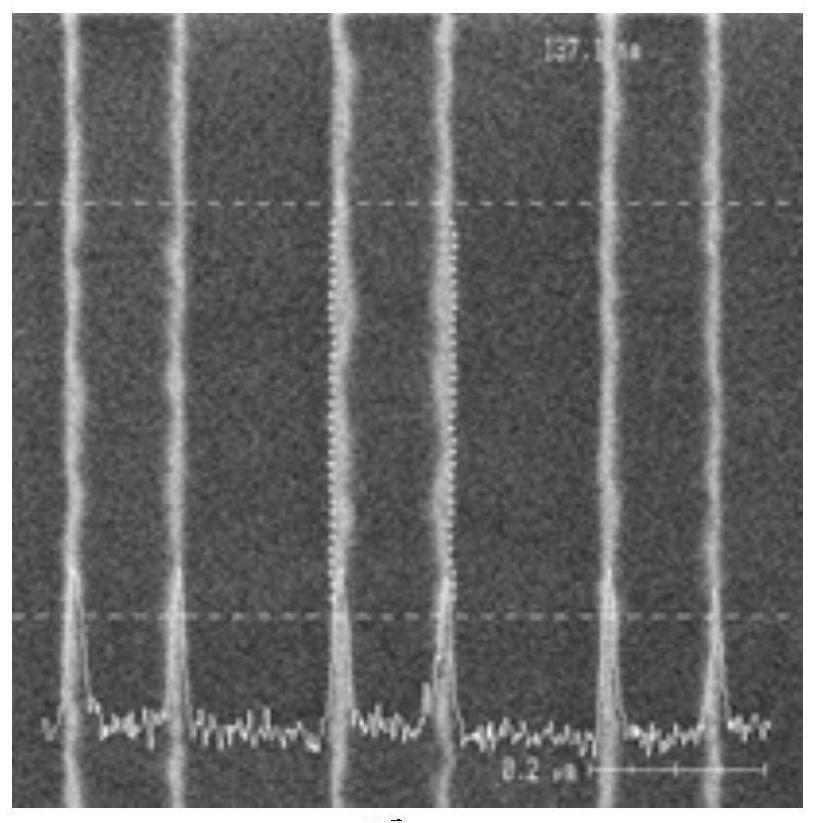

Method of making electrical test structure for detecting vias

ActiveCN104465446BReduce etch rateReduce spacingSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsResistGraph size

The invention provides a manufacturing method of an electric testing structure for detecting through holes. When a layout is designed, a through hole graph is connected with the overlapping area of a plurality of adjacent metal graphs in an intersection mode, the through hole graph size is larger than the target through hole size, a through hole pattern subsequently formed in optical resist is enabled to be larger than a target through hole graph in size, and therefore a photo-etched technical window is widened, and the photoetching resolution and the photoetching precision are improved; besides, a hard mask layer serves as a mask, and an upper layer metal pattern in the hard mask layer is etched into an etched barrier layer and an upper dielectric layer so that a target through hole pattern can be formed; the target through hole size is determined by the size of the upper metal pattern in the hard mask layer and the through hole size jointly and not determined by the size of the through hole graph in the optical resist, and therefore target through holes with smaller intervals can be obtained without splitting the through hole graph, the technical window is widened, and the photoetching resolution ratio is increased.

Owner:SHANGHAI INTEGRATED CIRCUIT RES & DEV CENT

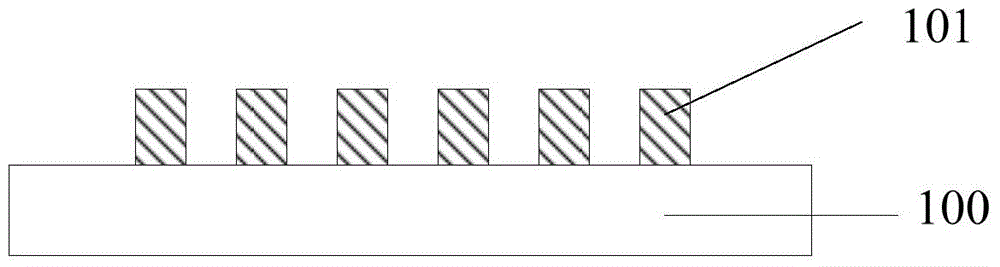

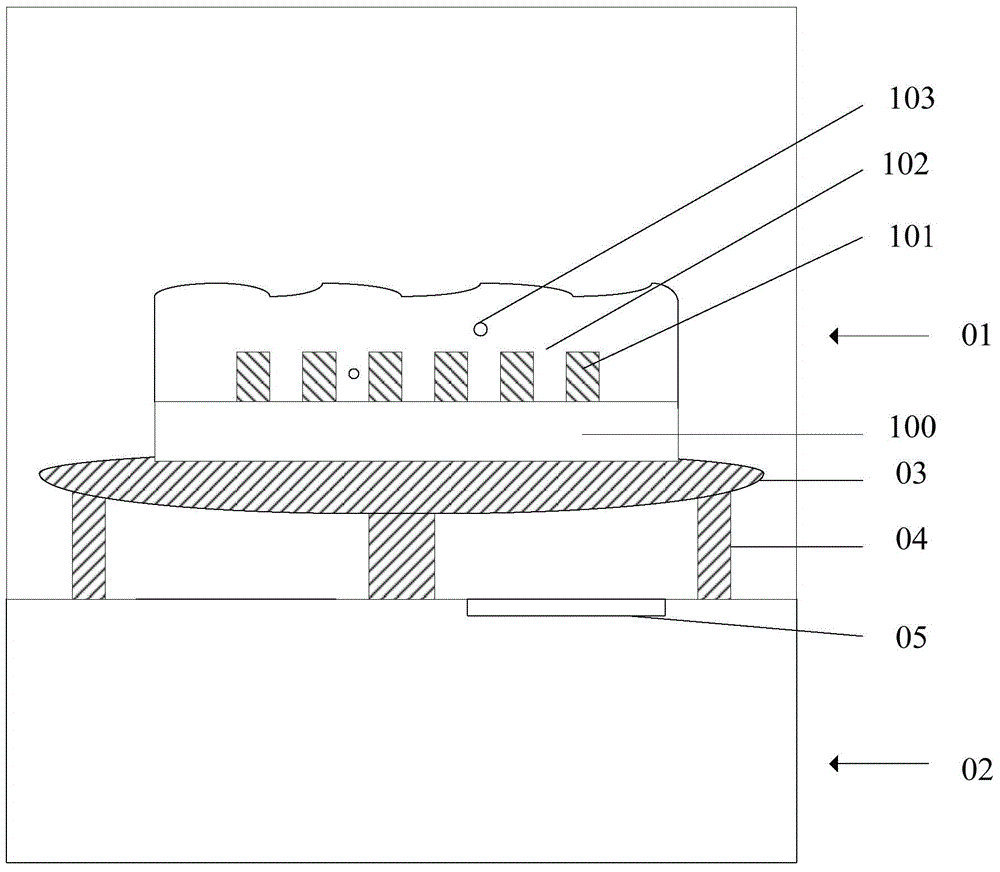

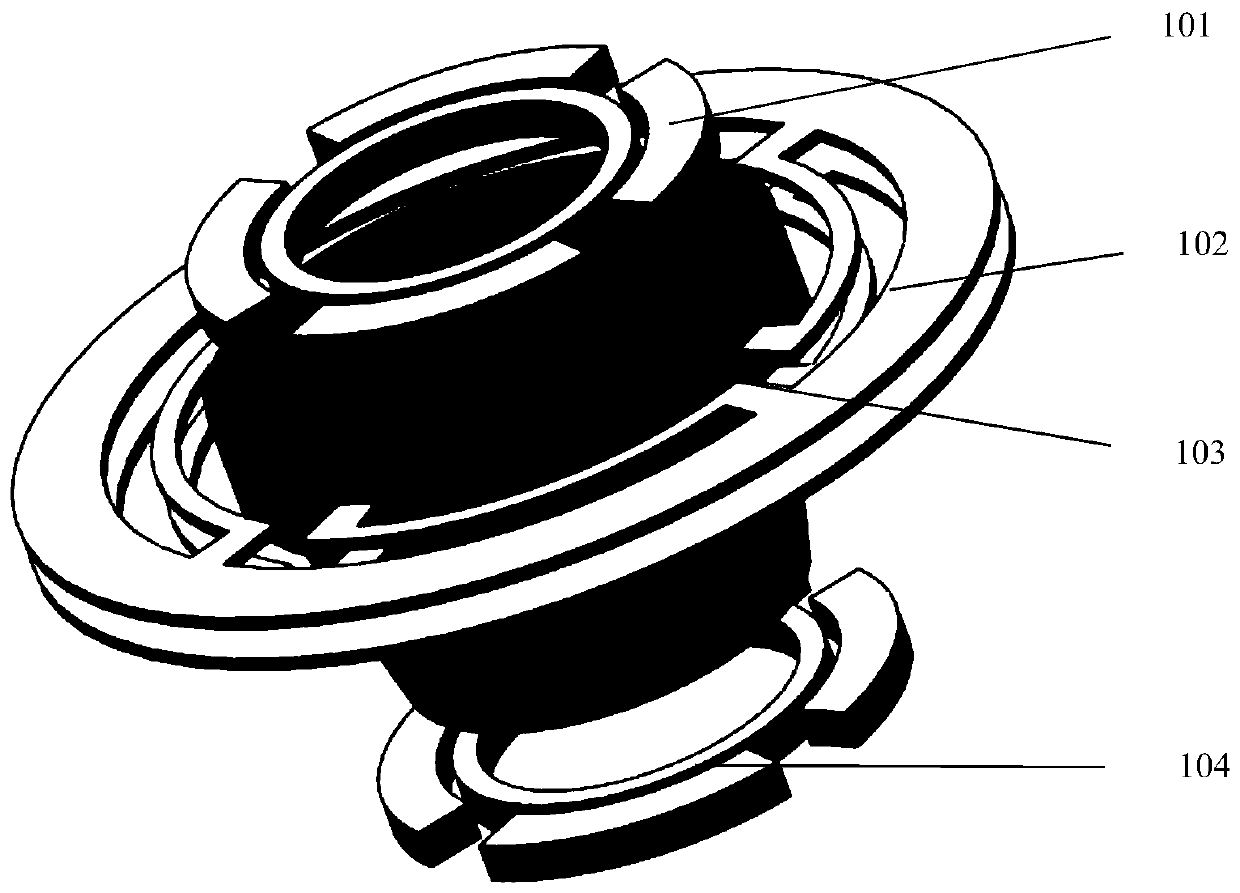

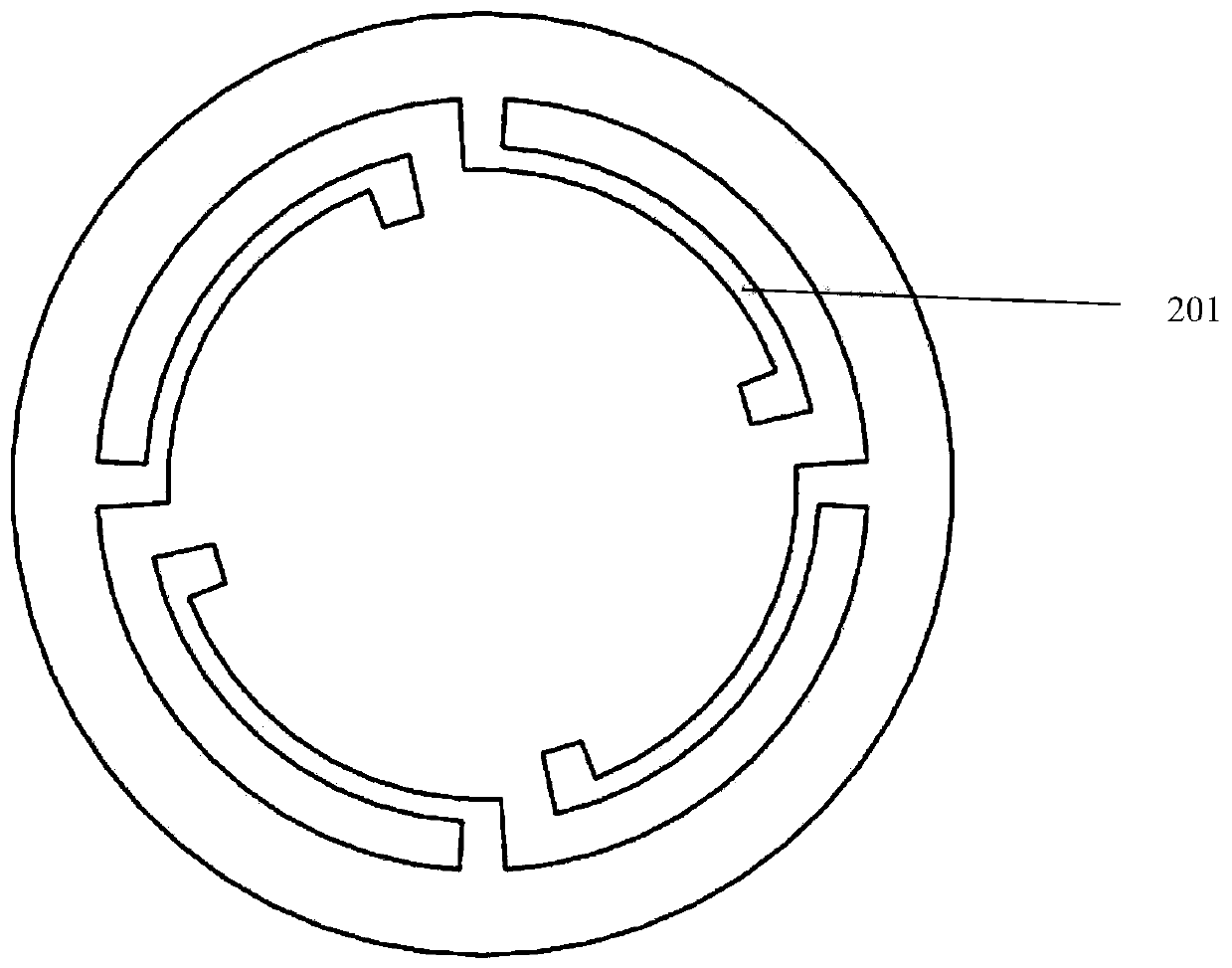

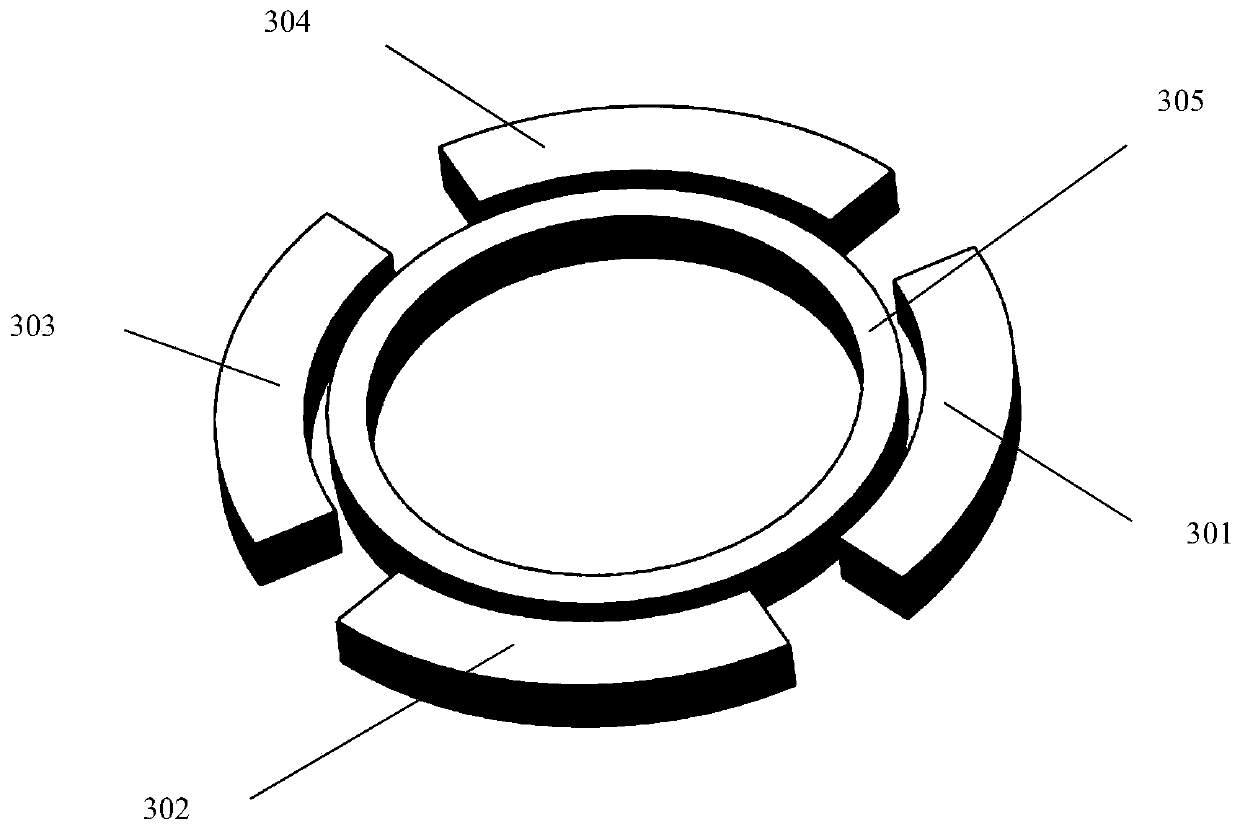

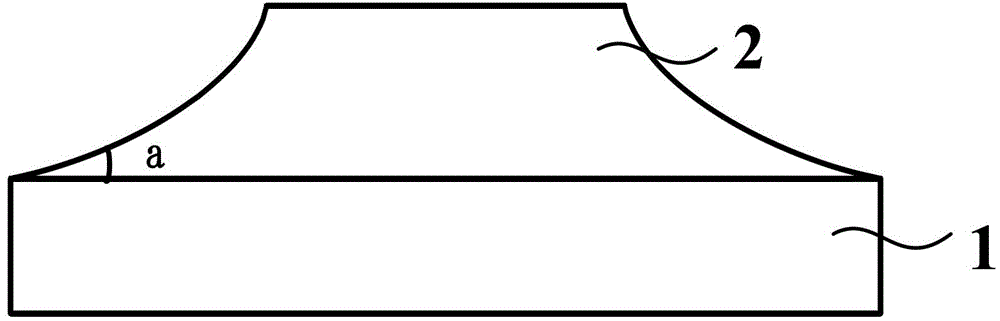

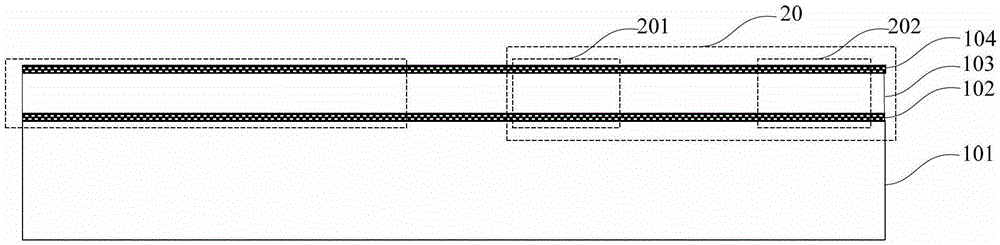

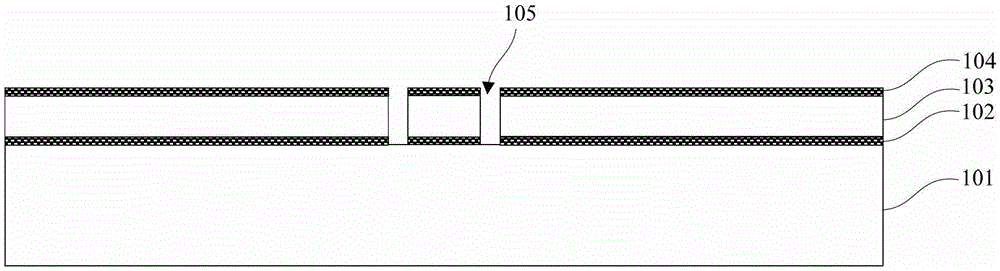

Micromechanical chip test probe card and manufacturing method thereof

ActiveCN103675365BEnsure coplanarityImprove structural strengthSemiconductor/solid-state device testing/measurementElectrical measurement instrument detailsProbe cardEngineering

Provided are a micromechanical chip test probe card and a method of fabricating same. A cantilever beam pattern (20) is defined in an SOI substrate. A blind hole (105) whose inner wall is insulated is fabricated on a floating end (201) of a cantilever beam. A probe (107) is fabricated in the blind hole (105). A metal lead (108) is fabricated on the surface of the cantilever beam. A solder ball (112) is fabricated on the fixed end (202) of the cantilever beam. SOI is etched on the front surface to form a cantilever beam structure. The solder ball (112) is inversely installed in a ceramic substrate (114). A silicon substrate (101) is etched from the bottom surface to release the cantilever beam and complete the preparation. The advantages of the micromechanical chip test probe card and the method of fabricating same are as follows: the processing precision is high; the processing technique is simple; the mechanical strength of the fabricated test probe card is high; probes can be arranged based on the pin position distribution of a chip to be tested. The fabricating technique is compatible with a conventional CMOS technique and a micromachining technique and is suitable for industrial production.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

High-density low-parasitic capacitor

ActiveCN101789430BReduce the ratioReduce power consumptionSolid-state devicesSemiconductor devicesCapacitanceParasitic capacitor

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

Stepped scanning photoetching machine vibration isolation system analoy experimental apparatus

InactiveCN100465794CMeet the needs of installing various componentsImprove lithography precisionSemiconductor/solid-state device manufacturingPhotomechanical exposure apparatusMachining vibrationsVibration control

The invention discloses a step-and-scan photoetching machine's isolation system simulation test device; it divides the whole test device into the internal world and the outside world. The outside world mostly complete the simulation of the photoetching machine's precision scanning movements, it lets the workpiece platform and the mask plate have the curve movement according to the schedule speed and acceleration, it completely reappears the true photoetching machine's step-and-scan movement, the internal world is mainly to install the optics system and the workpiece platform and the mask plate, and finishes the last photoetching service. Internal world and the outside world can be joined by the six degrees of freedom precision initiative vibration damper, it depresses the vibration of that the outside world passes to the internal world and this can ensure the internal world's quiet. The invention can let the core part-installation source system's work platform is in the range that the design allows. It improves the silicon's photoetching precision, at the same time; it has precise positioning and synchronous control of step-and-scan photoetching machine's isolation system simulation test device.

Owner:SHANGHAI MICRO ELECTRONICS EQUIP (GRP) CO LTD +1