Patents

Literature

31results about How to "Good sidewall morphology" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

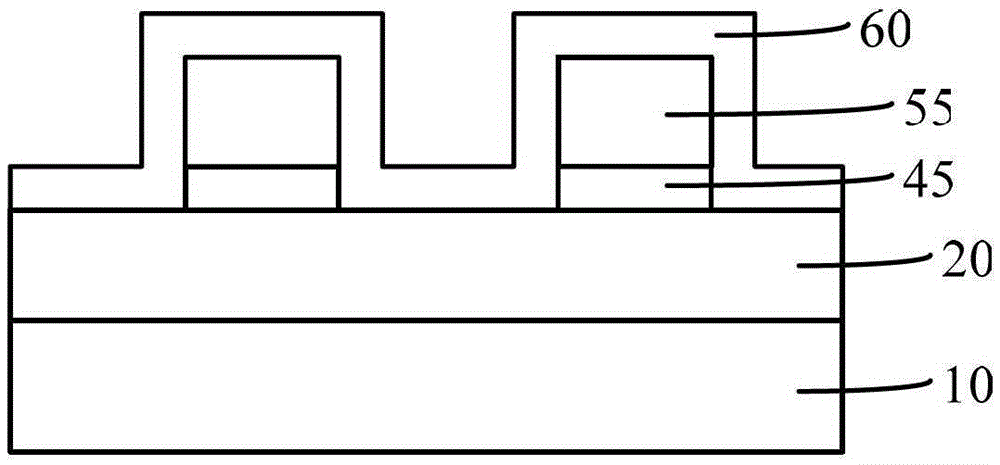

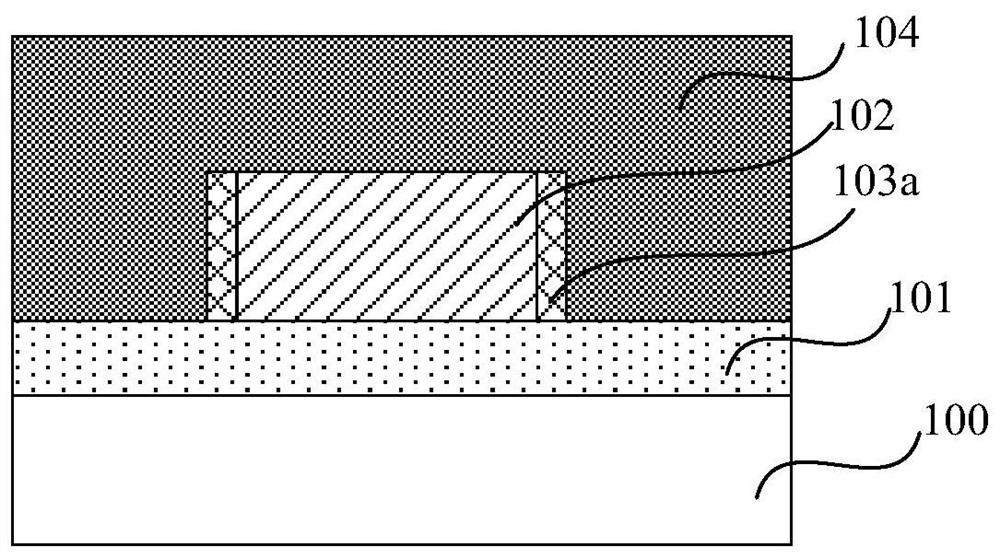

Self-aligned double patterning formation method

InactiveCN103632928AGood sidewall morphologySave one step etching processSemiconductor/solid-state device manufacturingResistEngineering

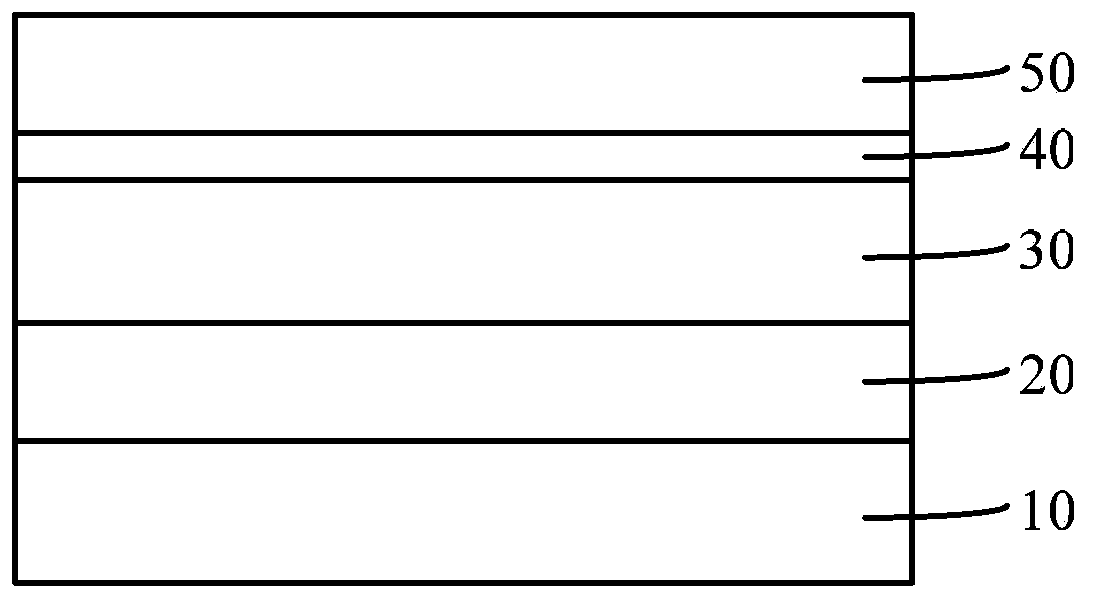

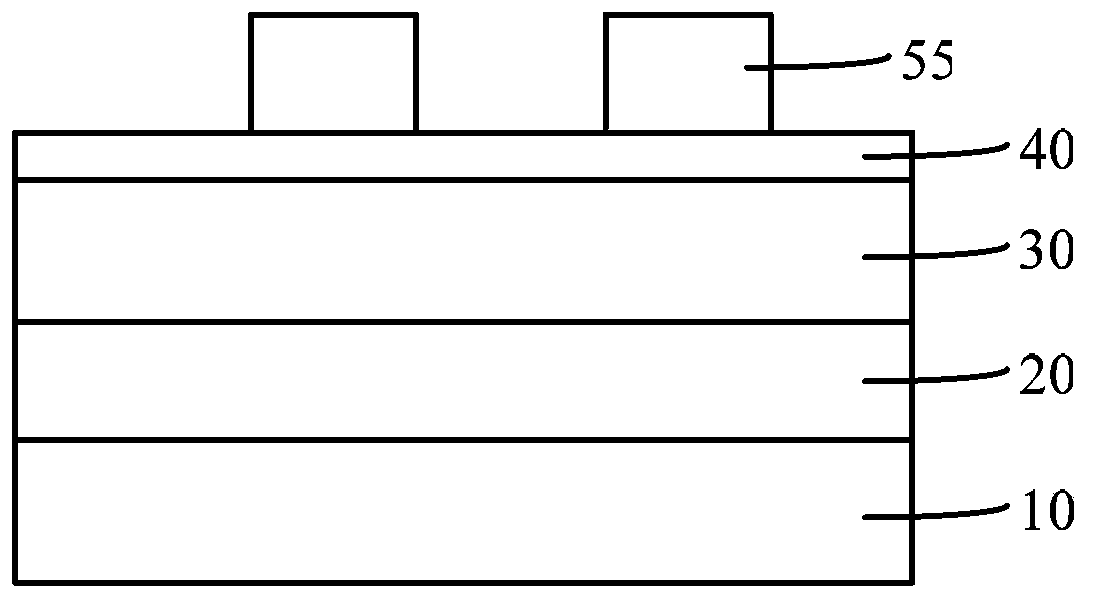

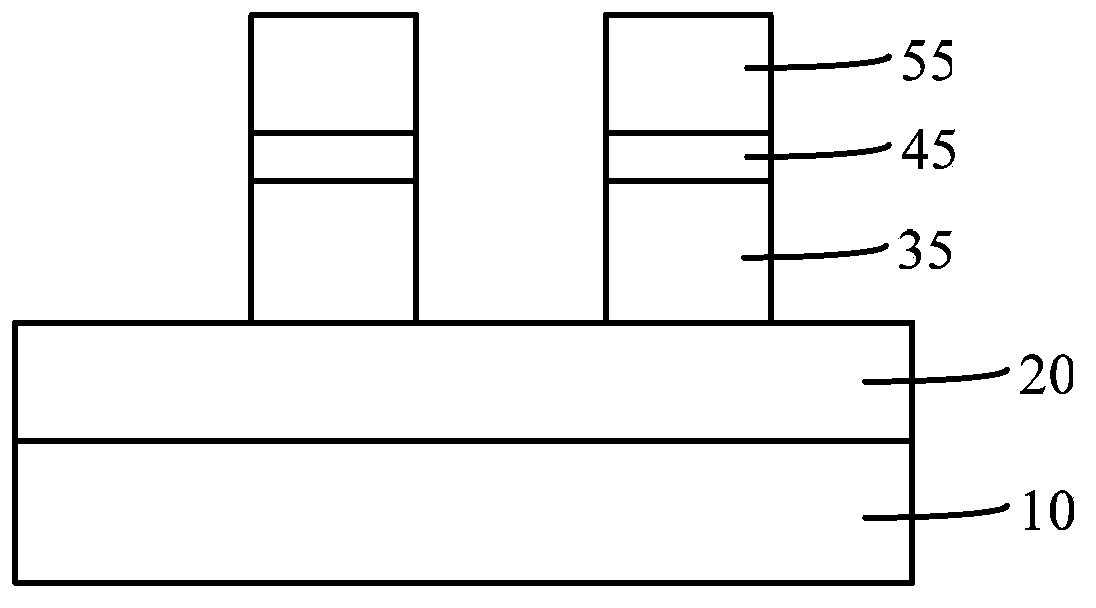

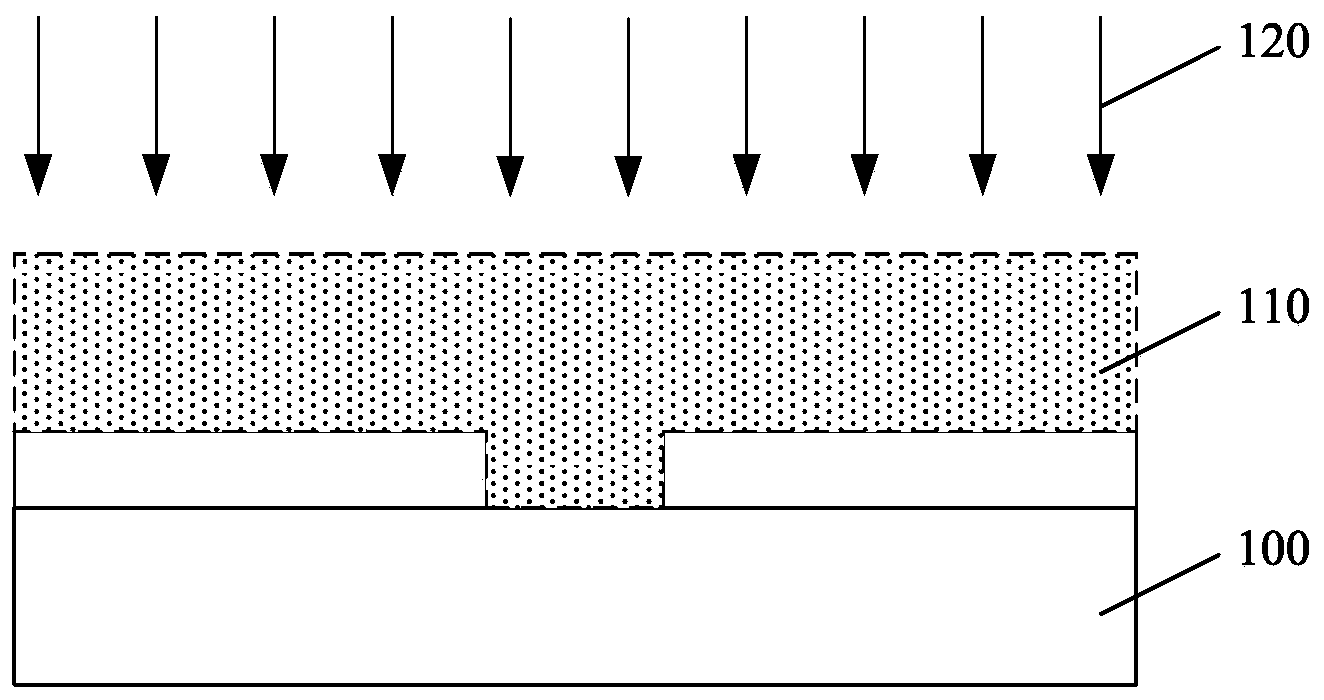

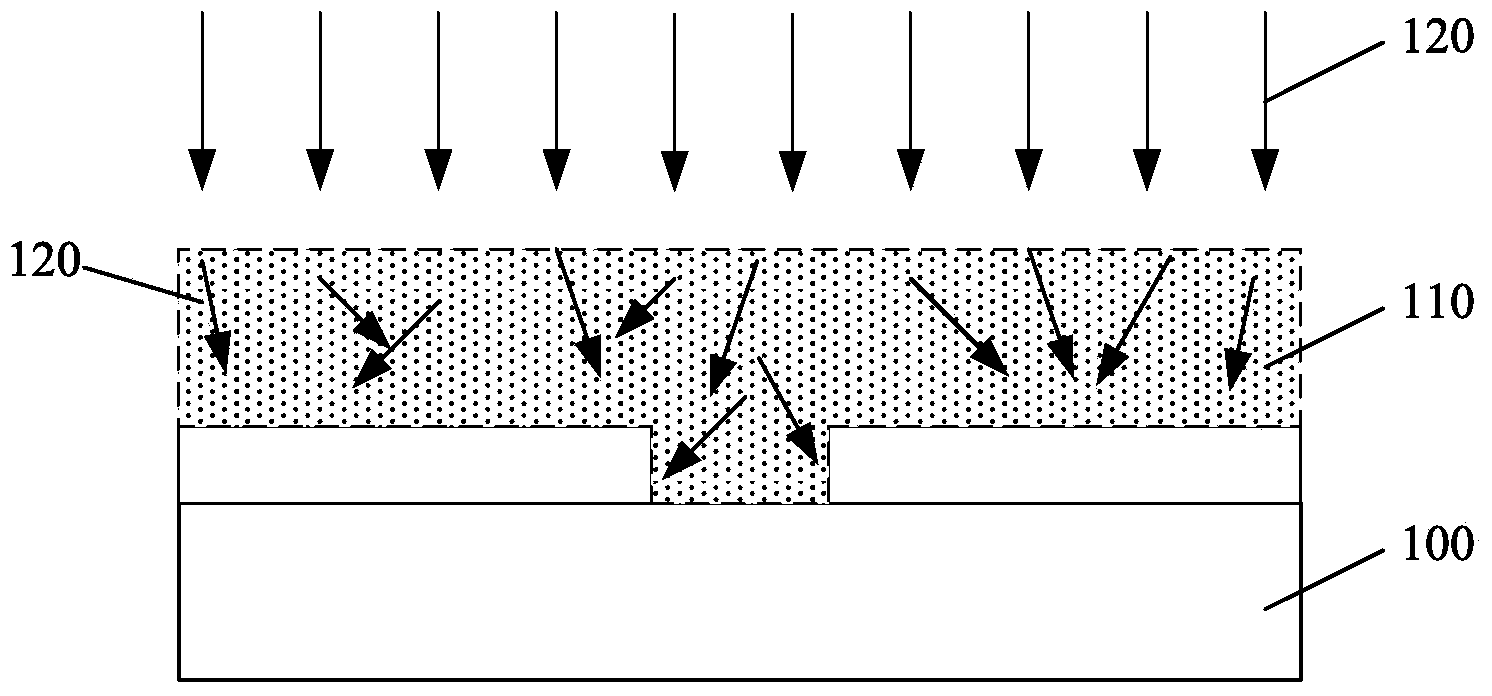

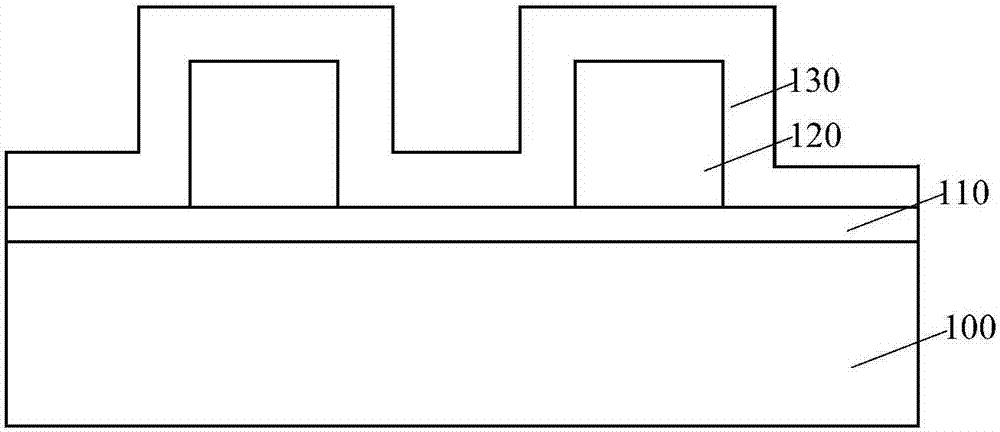

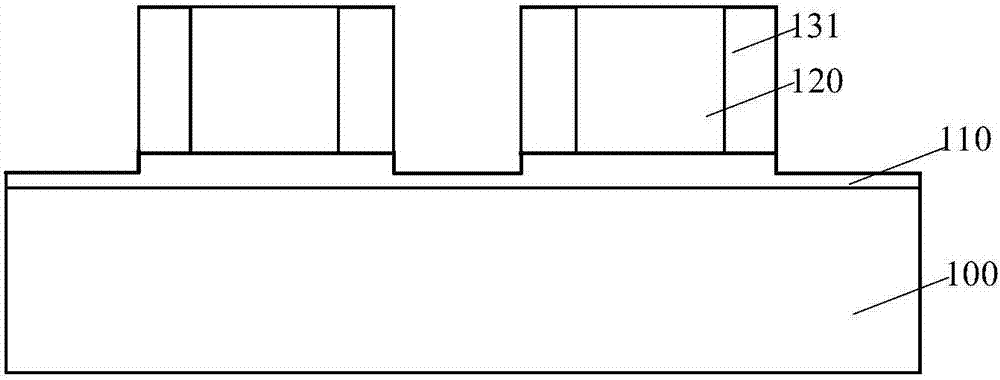

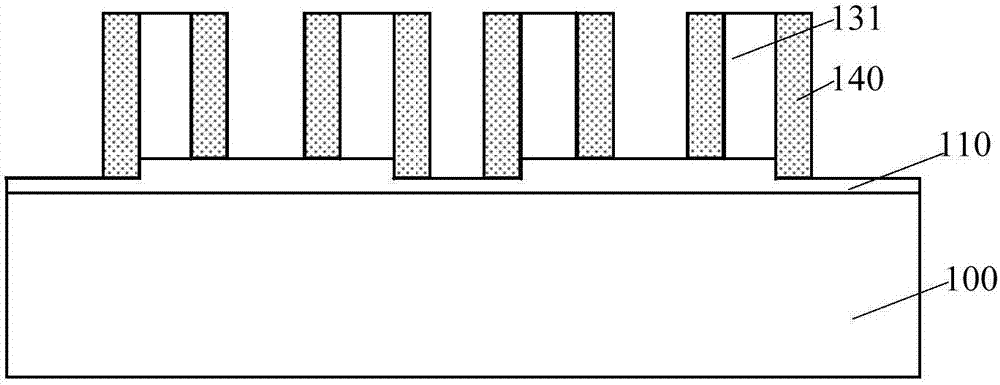

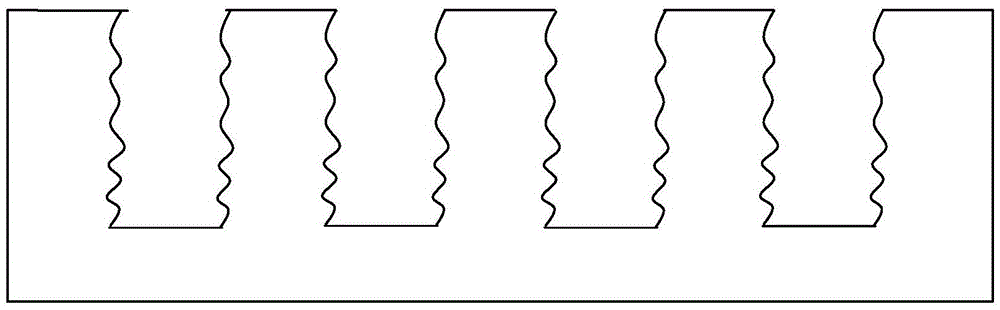

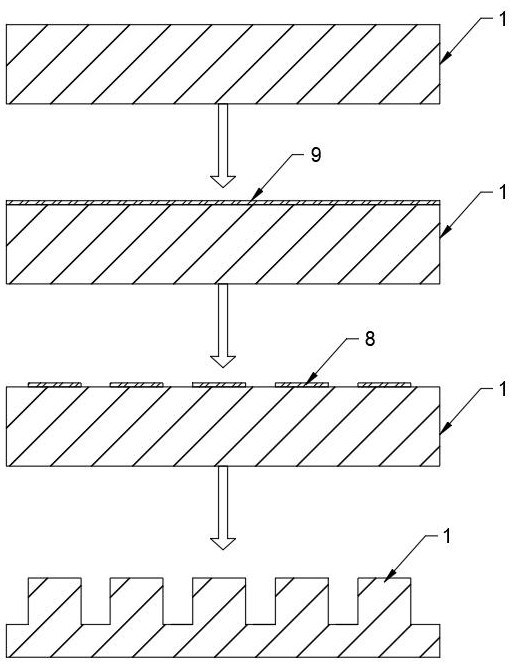

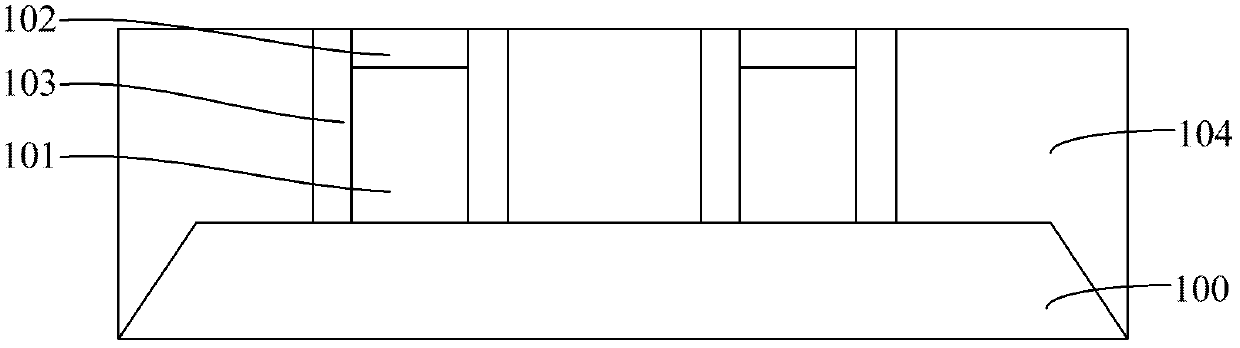

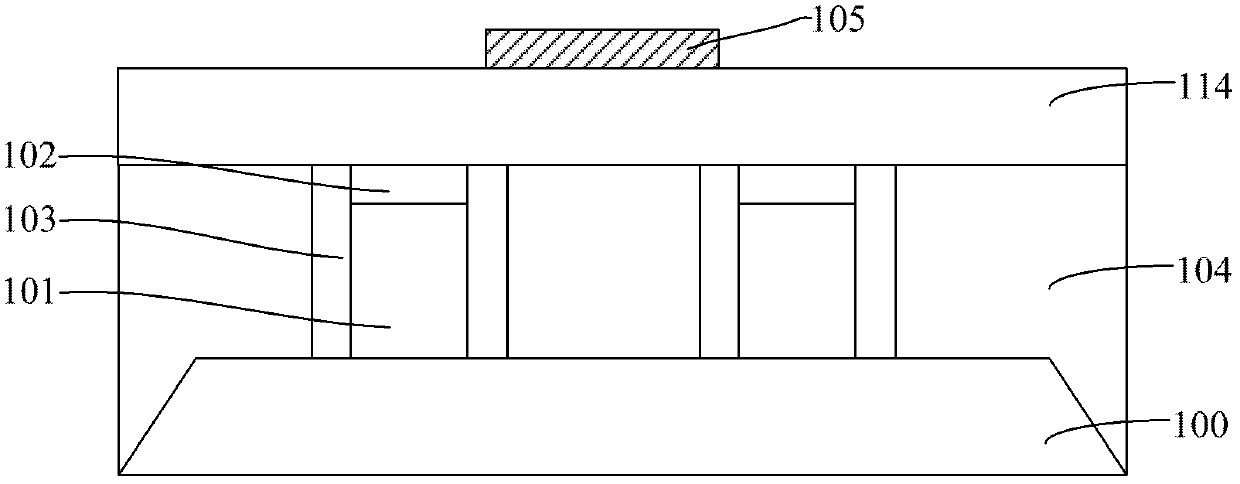

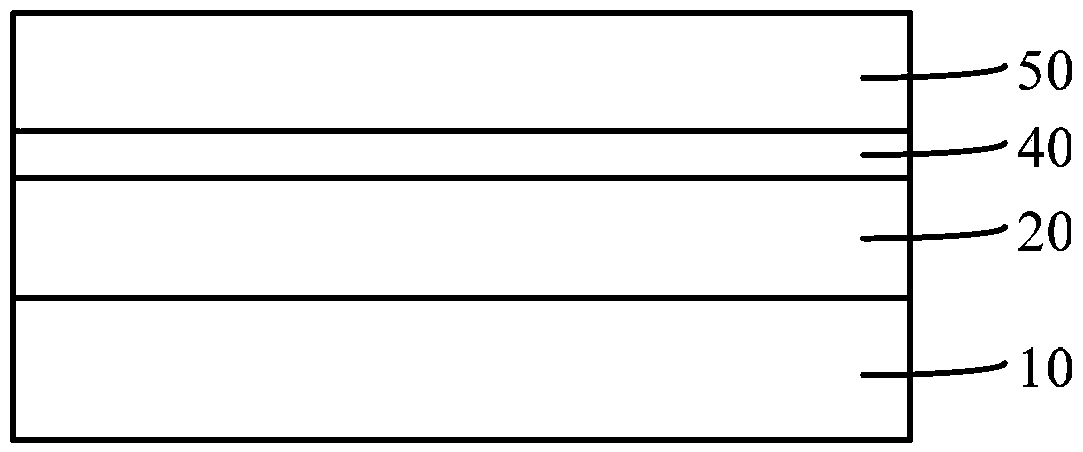

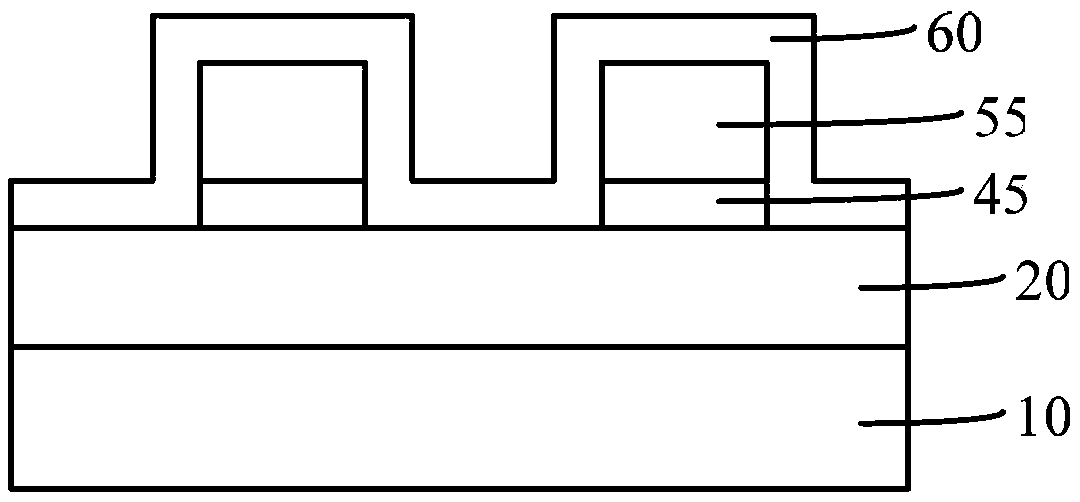

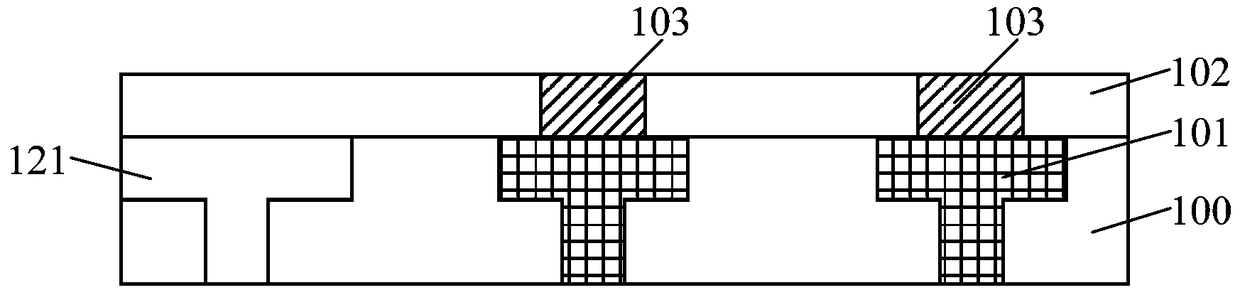

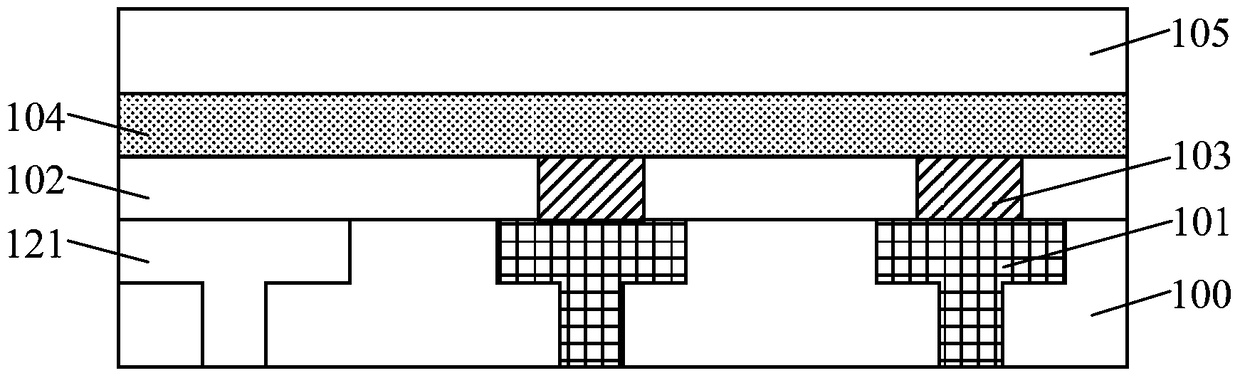

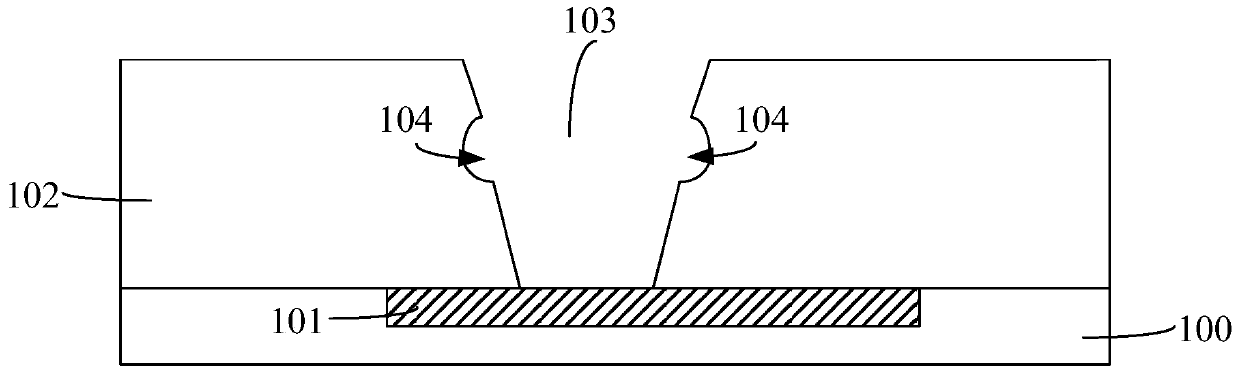

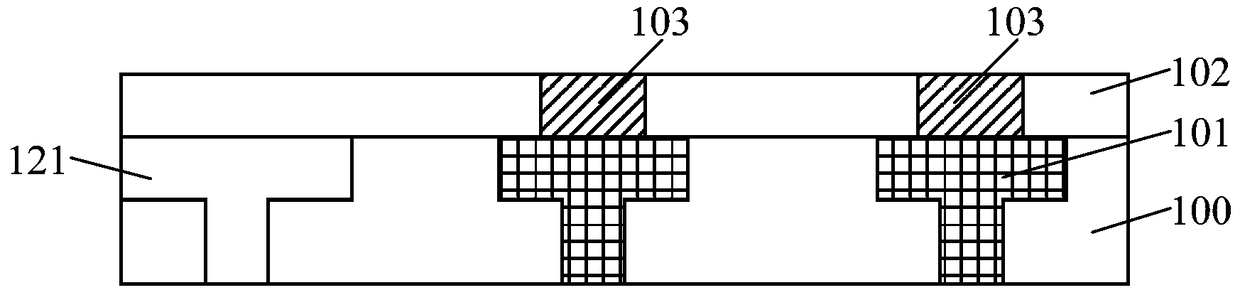

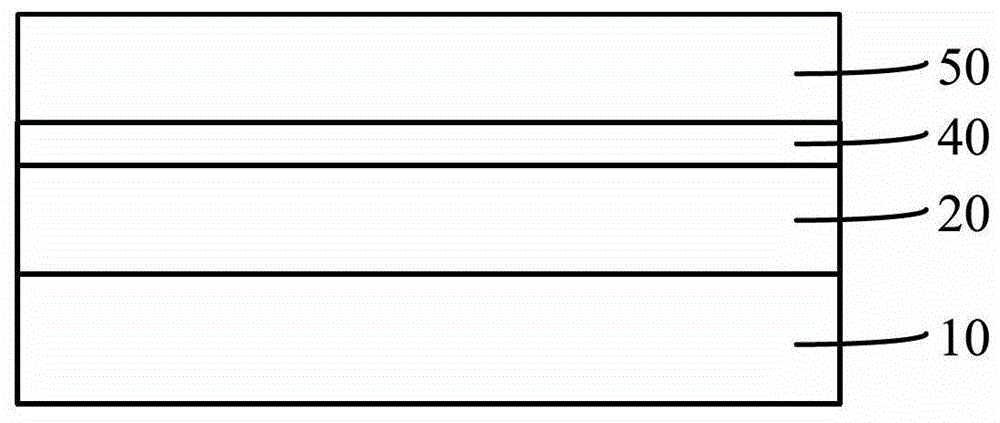

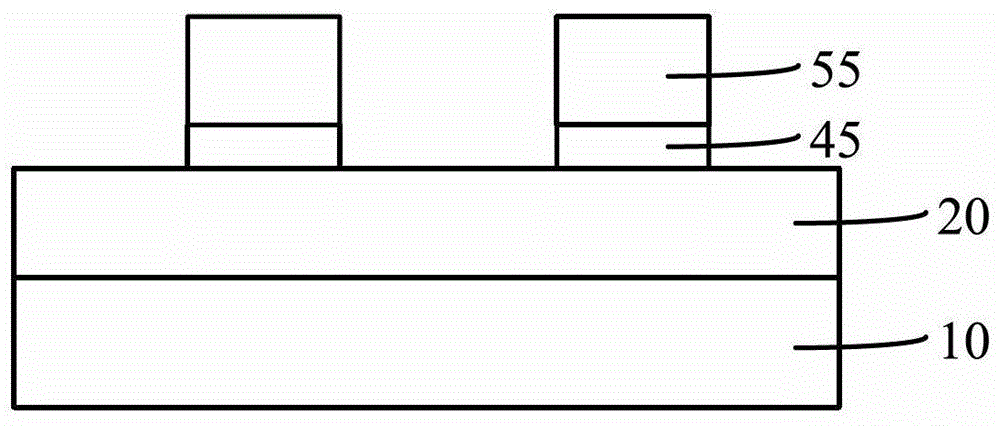

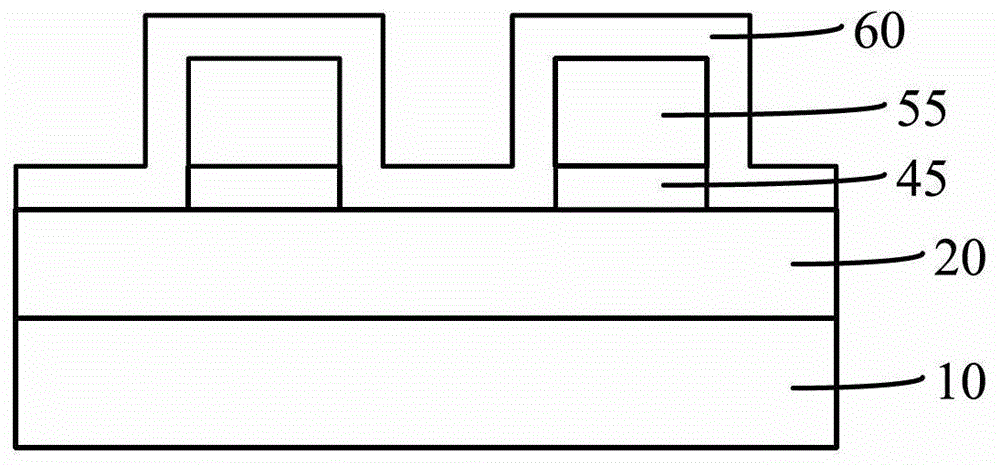

Provided is a self-aligned double patterning formation method. The method comprises the following steps: a material layer to be etched is provided; a bottom part antireflective layer and a photo-resist layer which are soluble in a developing solvent are formed on the surface of the material layer to be etched; exposure and developing are synchronously performed on the bottom part antireflective layer and the photo-resist layer so that a patterned sacrificial bottom part antireflective layer and a sacrificial photo-resist layer are formed; first covering film material layers are formed on the surface of the material layer to be etched, the side wall surfaces of the sacrificial bottom part antireflective layer and the sacrificial photo-resist layer and the surface of the sacrificial photo-resist layer; the first covering film material layers are back-etched so that first covering film patterns are formed; and the sacrificial bottom part antireflective layer and the sacrificial photo-resist layer are removed. The bottom part antireflective layer and the photo-resist layer after exposure are synchronously soluble in the developing solvent so that the sacrificial photo-resist layer does not need to be utilized as a covering film to etch the bottom part antireflective layer, and one step in etching technology is saved. Besides, side wall appearance of a first covering film pattern is great so that the side wall appearance of the finally formed etching pattern is great.

Owner:SEMICON MFG INT (SHANGHAI) CORP

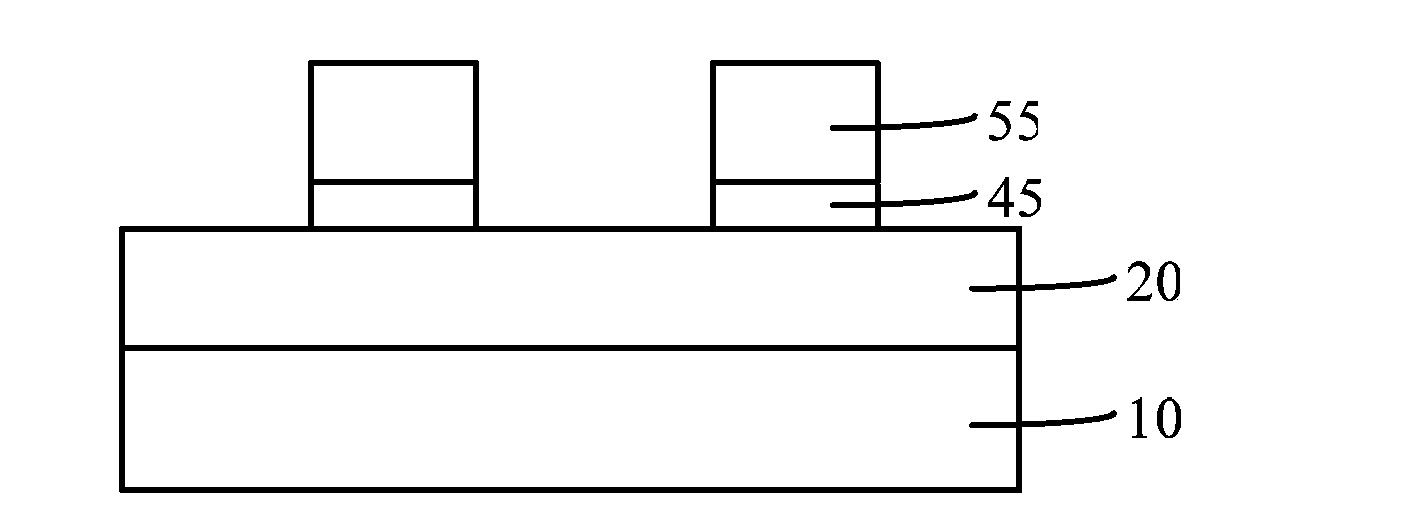

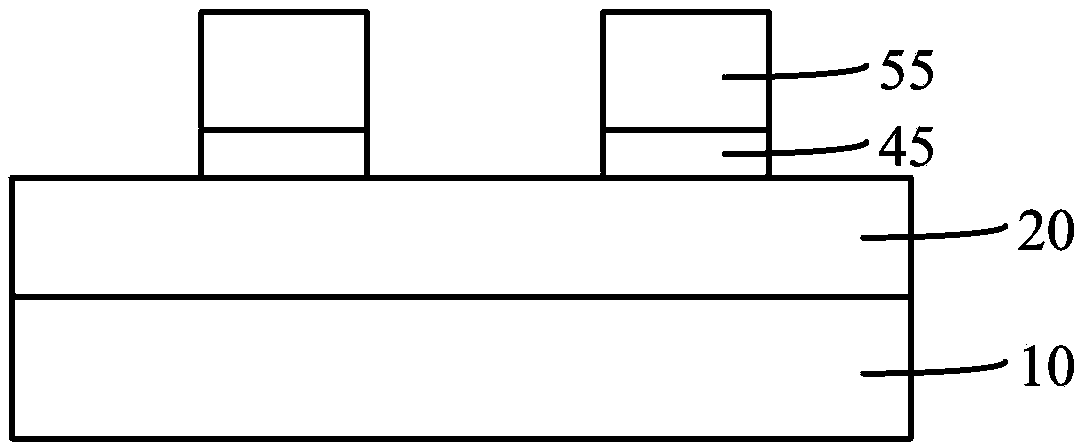

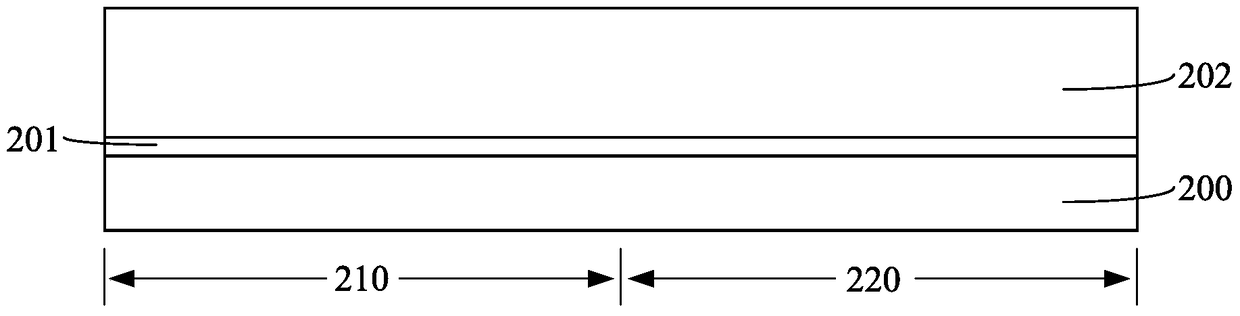

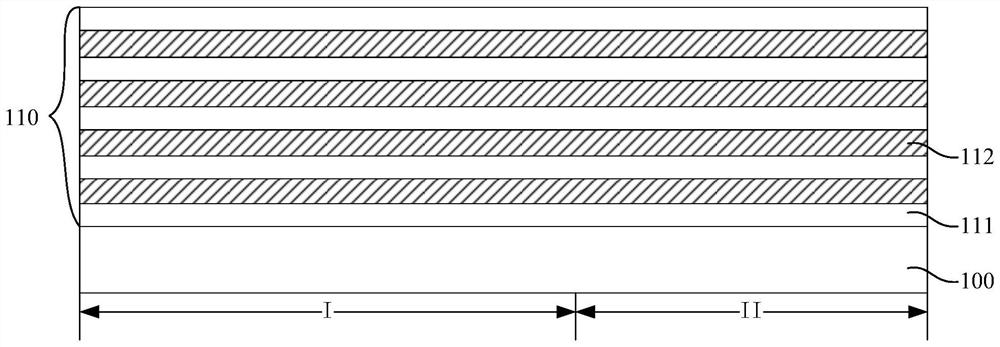

Method for forming self-alignment duplex pattern

ActiveCN103681234AHigh hardnessWill not deformSemiconductor/solid-state device manufacturingPhotoresistMaterials science

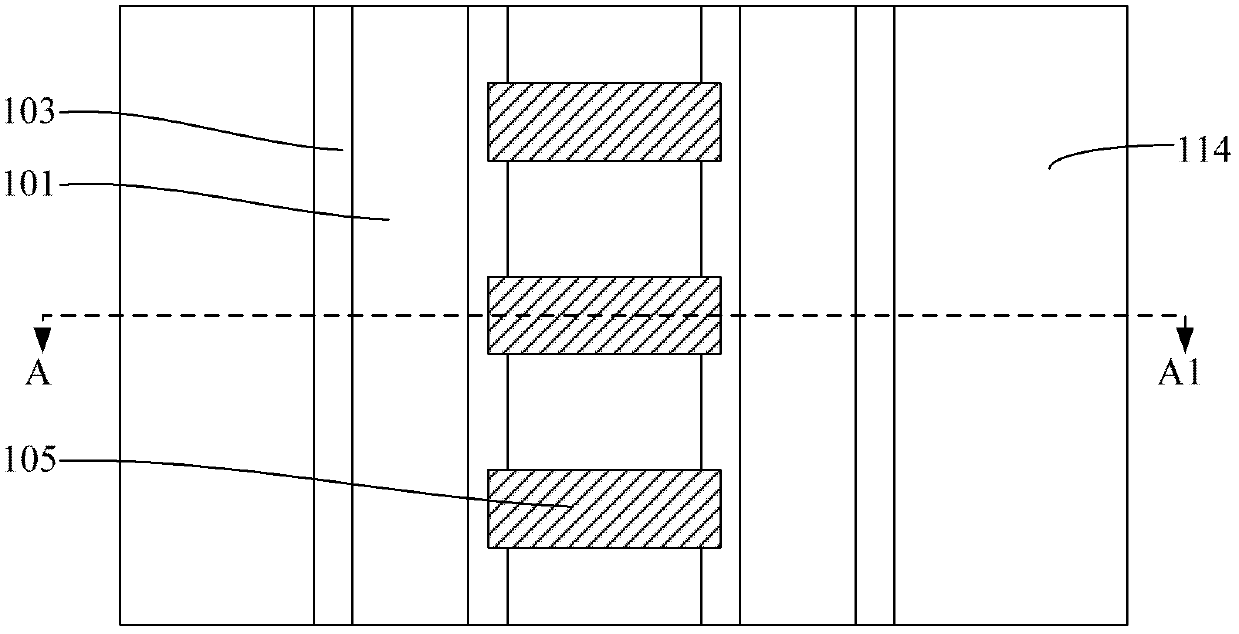

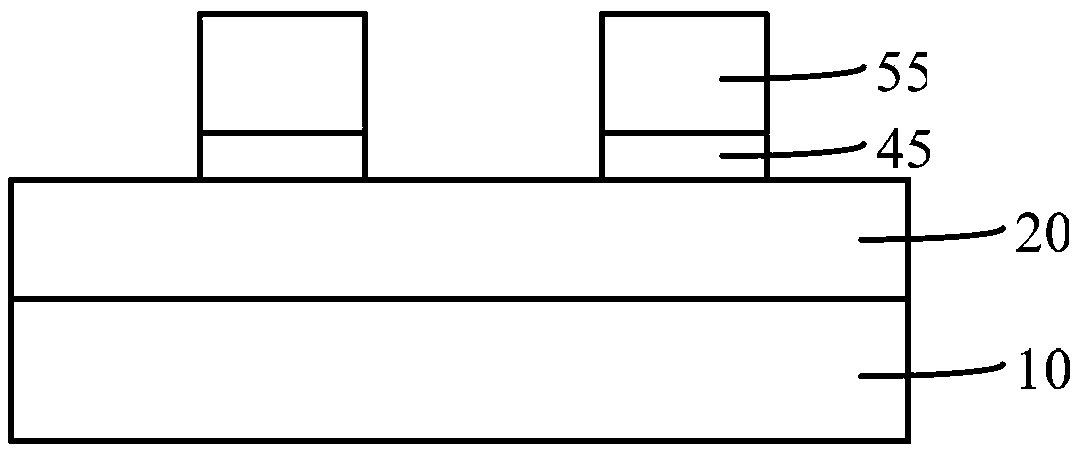

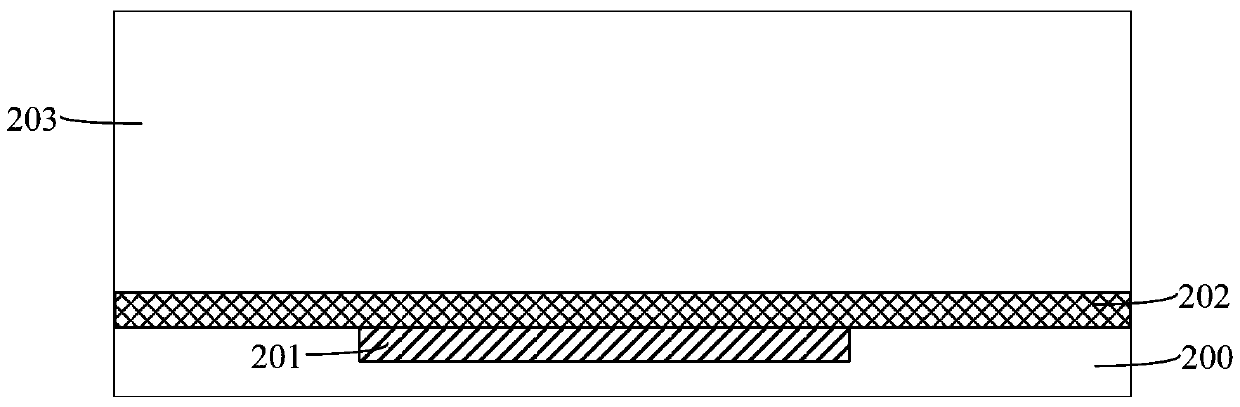

The invention provides a method for forming self-alignment duplex pattern. The method comprises the following steps: providing a material layer to be etched, forming a sacrificial photoresist layer on the material layer to be etched, curing the sacrificial photoresist layer, forming a first mask pattern on the side wall surface of the sacrificial photoresist layer, and removing the sacrificial photoresist layer. As the sacrificial photoresist layer is cured, the hardness of the sacrificial photoresist layer is increased, and during the process of forming the first mask pattern, the sacrificial photoresist layer does not deform under the stress generated by the first mask material layer, so that the side wall of the sacrificial photoresist layer is still perpendicular to the surface of the material layer to be etched, and finally, the side wall of the etched pattern which is formed by etching the material layer to be etched has a better profile.

Owner:SEMICON MFG INT (SHANGHAI) CORP

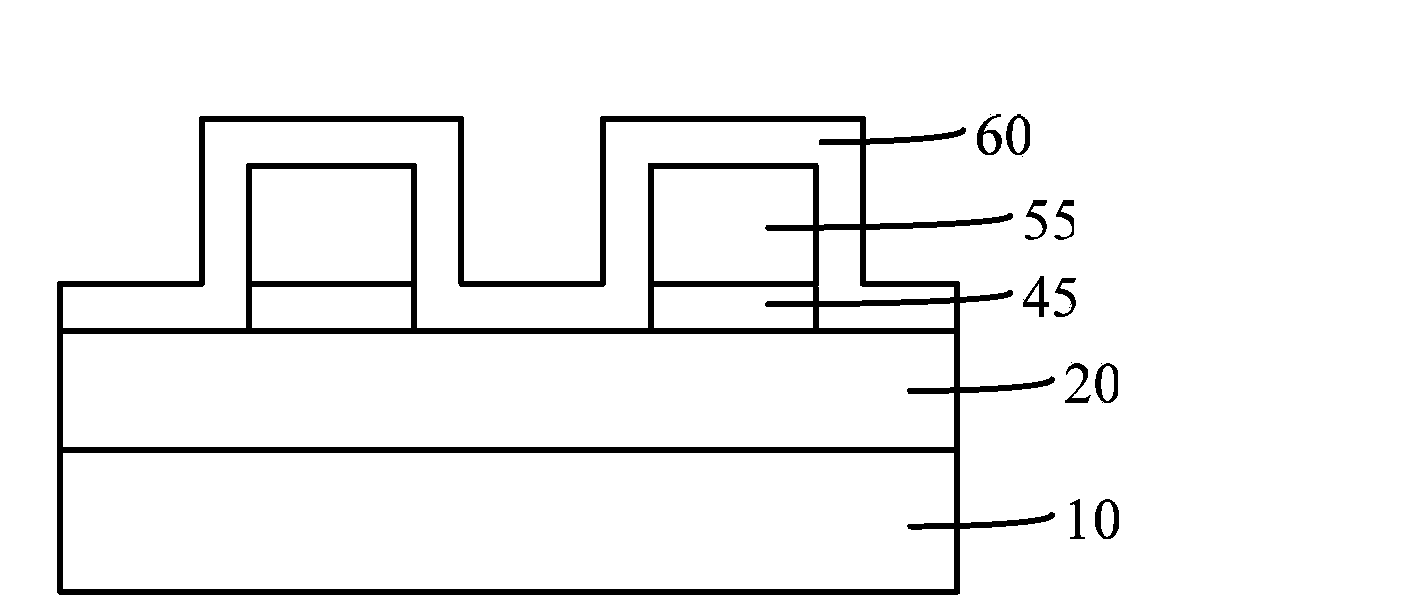

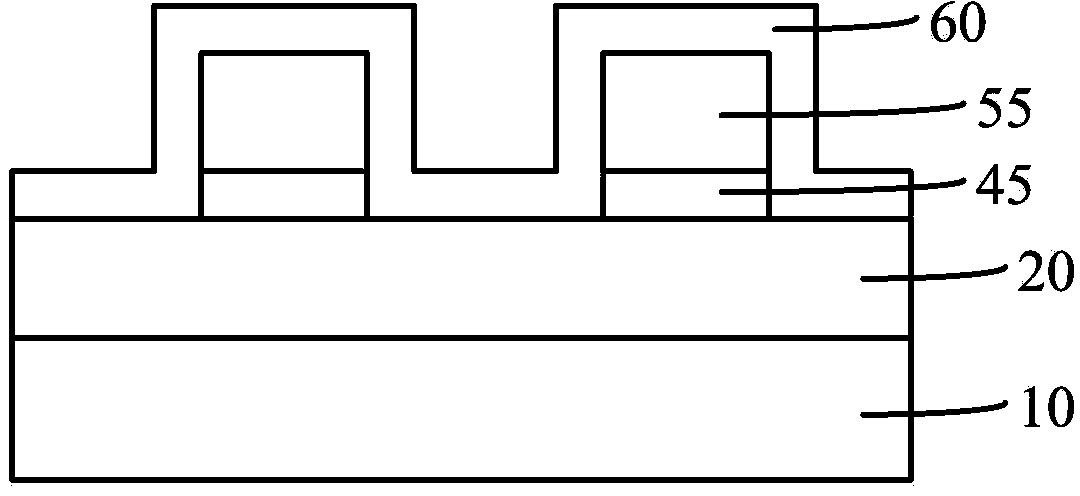

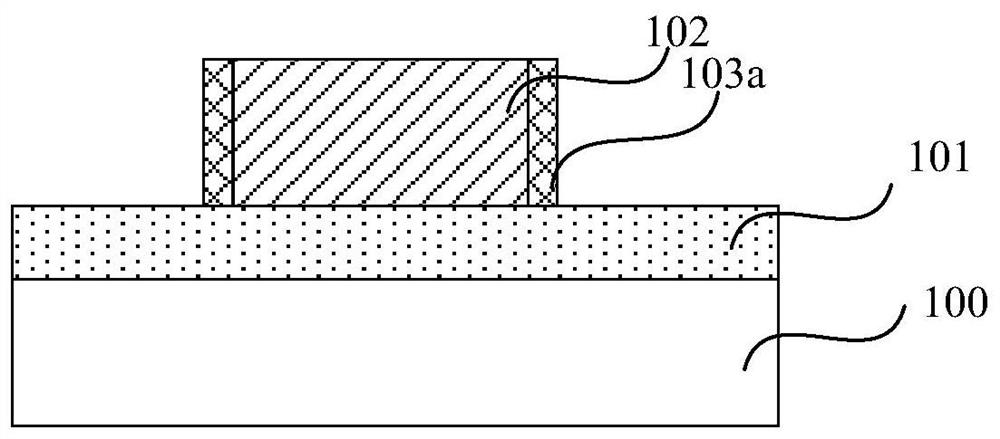

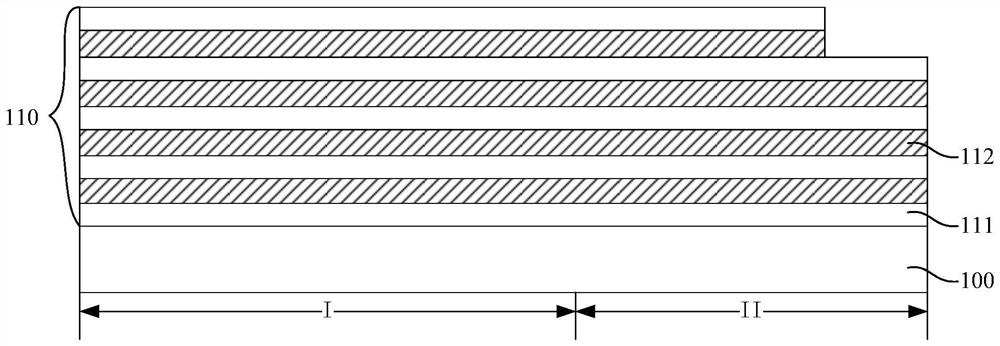

Self-alignment duplex patterning method

ActiveCN103681293AMorphological influenceGood sidewall morphologySemiconductor/solid-state device manufacturingPhotoresistMaterials science

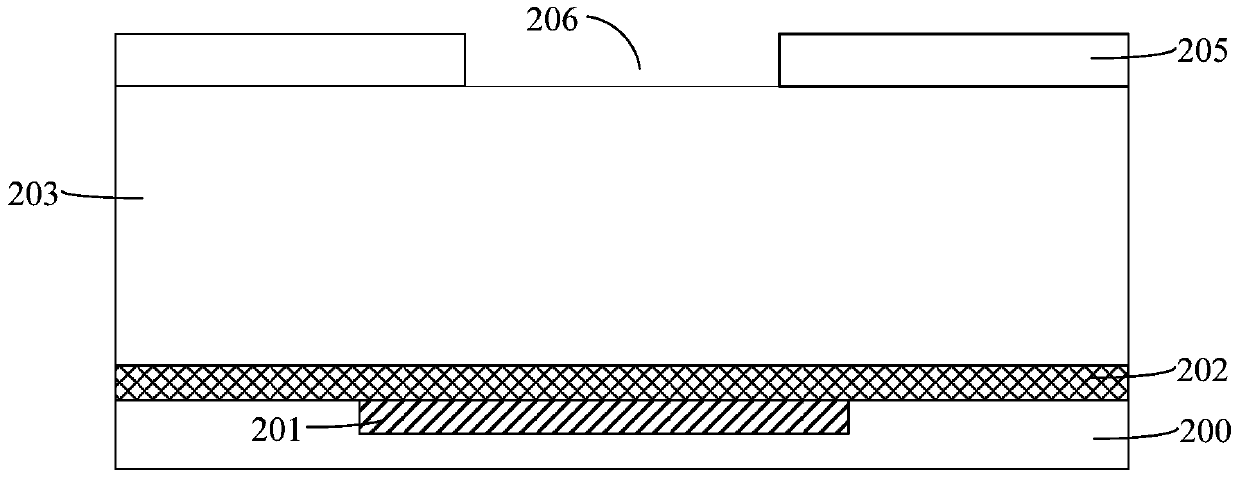

The invention provides a self-alignment duplex patterning method. The method comprises the following steps: providing a material layer to be etched, forming a sacrificial photoresist layer on the material layer to be etched, curing photoresist at the top and side wall of the sacrificial photoresist layer to form a cured photoresist casing, performing back-etching on the cured photoresist casing at the top of the sacrificial photoresist layer until an uncured inner sacrificial photoresist layer is exposed, forming a first mask pattern on the cured photoresist casing on the side wall of the inner sacrificial photoresist layer, and removing the uncured inner sacrificial photoresist layer. As a hard mask layer is not required to form, the process procedures are reduced, and the impact of the stress generated by the hard mask layer on the profile of the sacrificial photoresist layer is eliminated. Besides, the first mask pattern is formed by removing the top of the cured photoresist casing, the side wall of the sacrificial photoresist layer formed by the photolithographic process is smooth and perpendicular to the surface of the material layer to be etched, and the side wall of the finally-formed etched pattern has a better profile.

Owner:SEMICON MFG INT (SHANGHAI) CORP

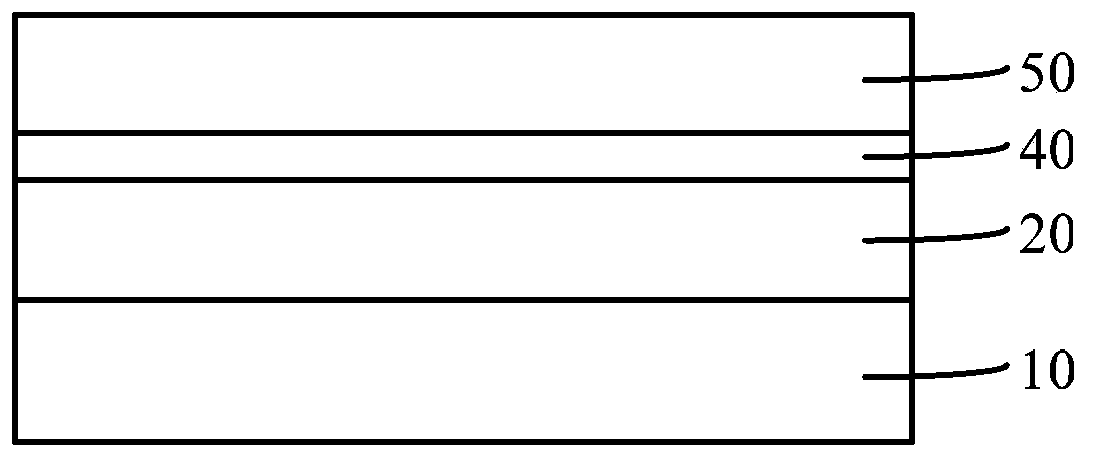

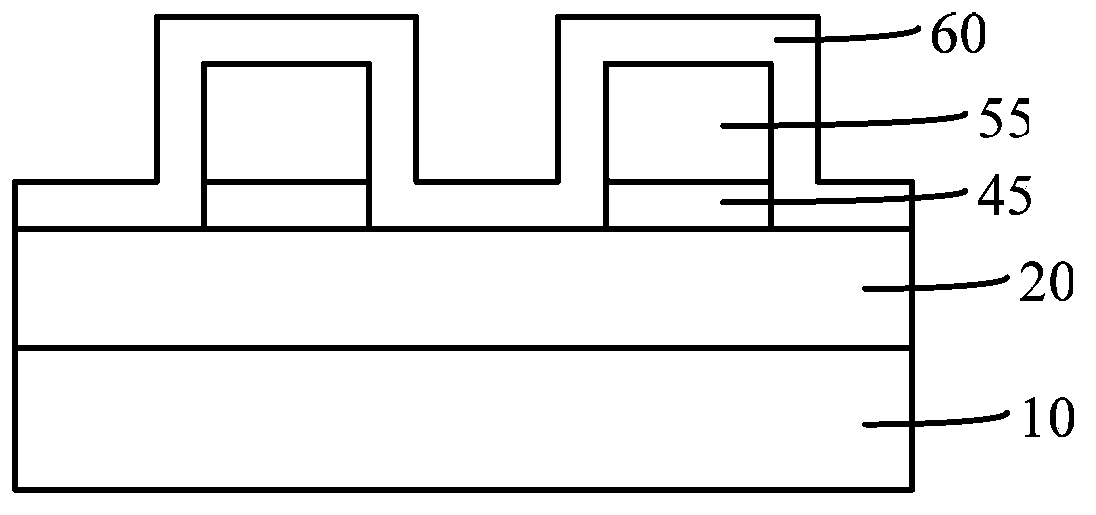

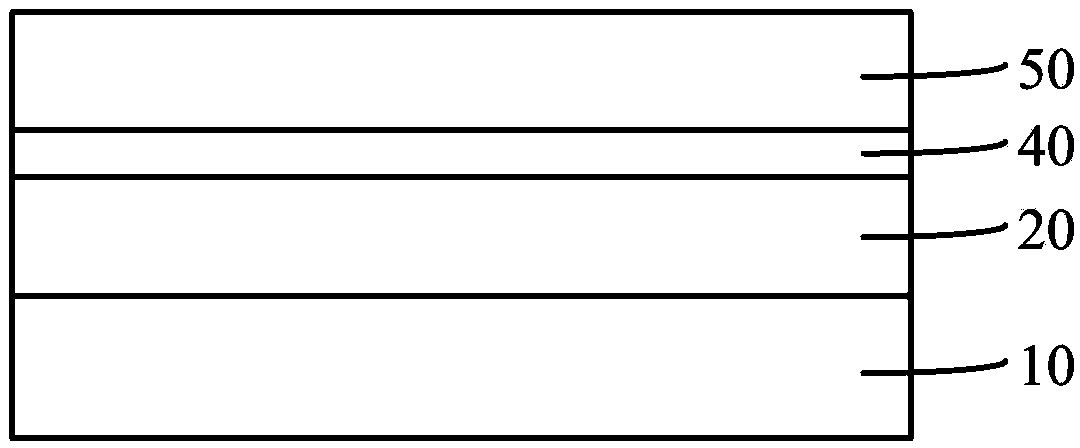

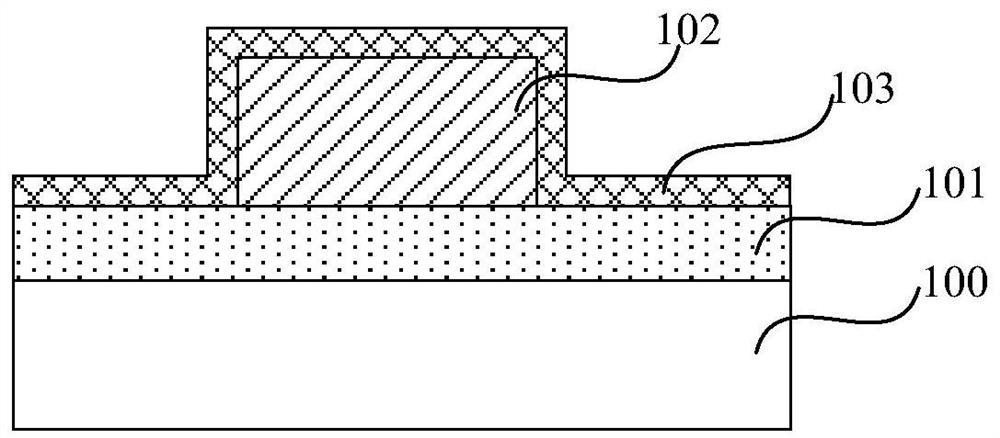

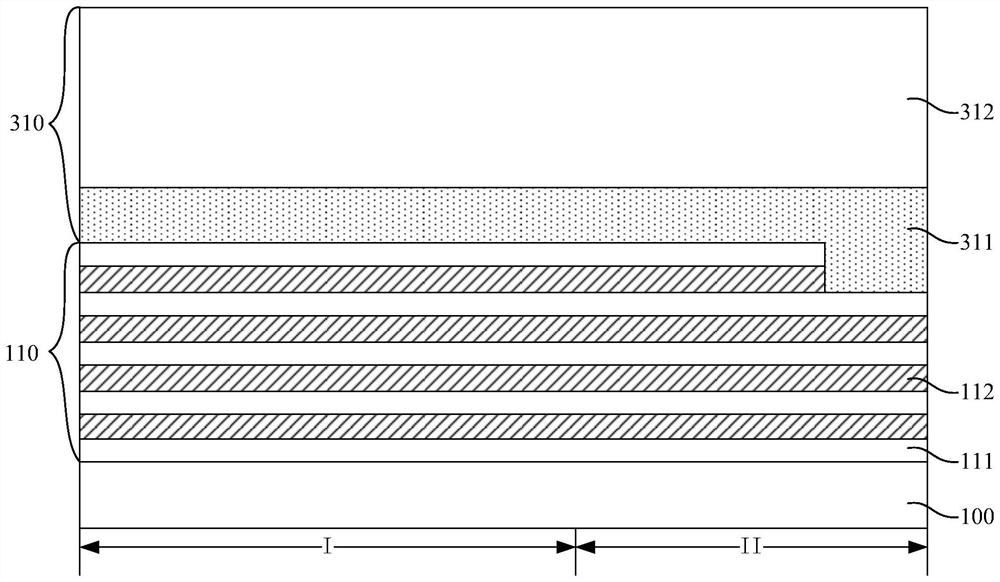

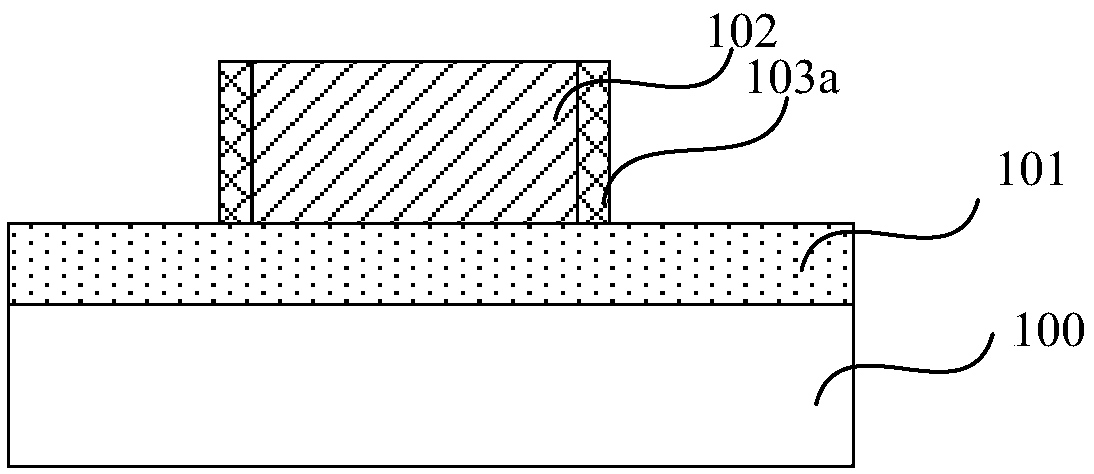

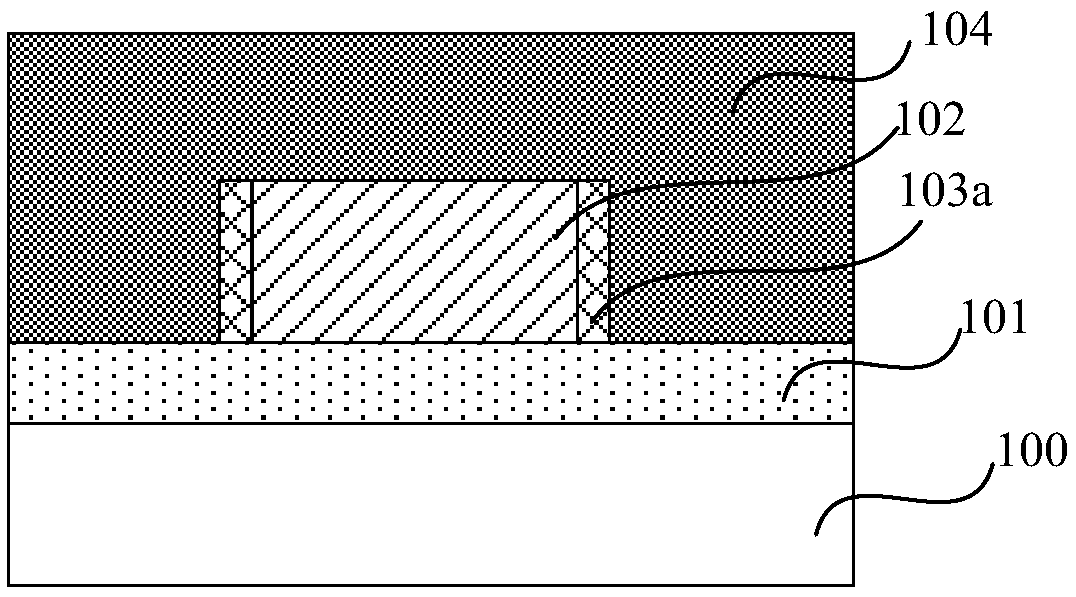

Self-aligned double patterning formation method

ActiveCN103839783AHigh hardnessGood sidewall morphologySemiconductor/solid-state device manufacturingHardnessDeposition process

A self-aligned double patterning formation method comprises the steps of providing a material layer to be etched, forming a sacrificial photoresist layer on the material layer to be etched, forming a polymer layer on the surfaces of the top and the side walls of the sacrificial photoresist layer, forming a first mask material layer on the surface of the polymer layer, and back-etching the first mask material layer to enable the first mask material layer on the two sides of the sacrificial photoresist layer to form a first mask pattern. As the polymer layer is formed on the surfaces of the top and the side walls of the sacrificial photoresist layer, and the hardness of the polymer layer is far higher than that of the sacrificial photoresist layer, the shape of the sacrificial photoresist layer does not deform due to stress generated by the first mask material layer. Moreover, the rotation angle of the polymer layer formed by the use of a deposition process and an etching process is a right angle, which enables the sidewall morphology of the final etched pattern to be good.

Owner:SEMICON MFG INT (SHANGHAI) CORP

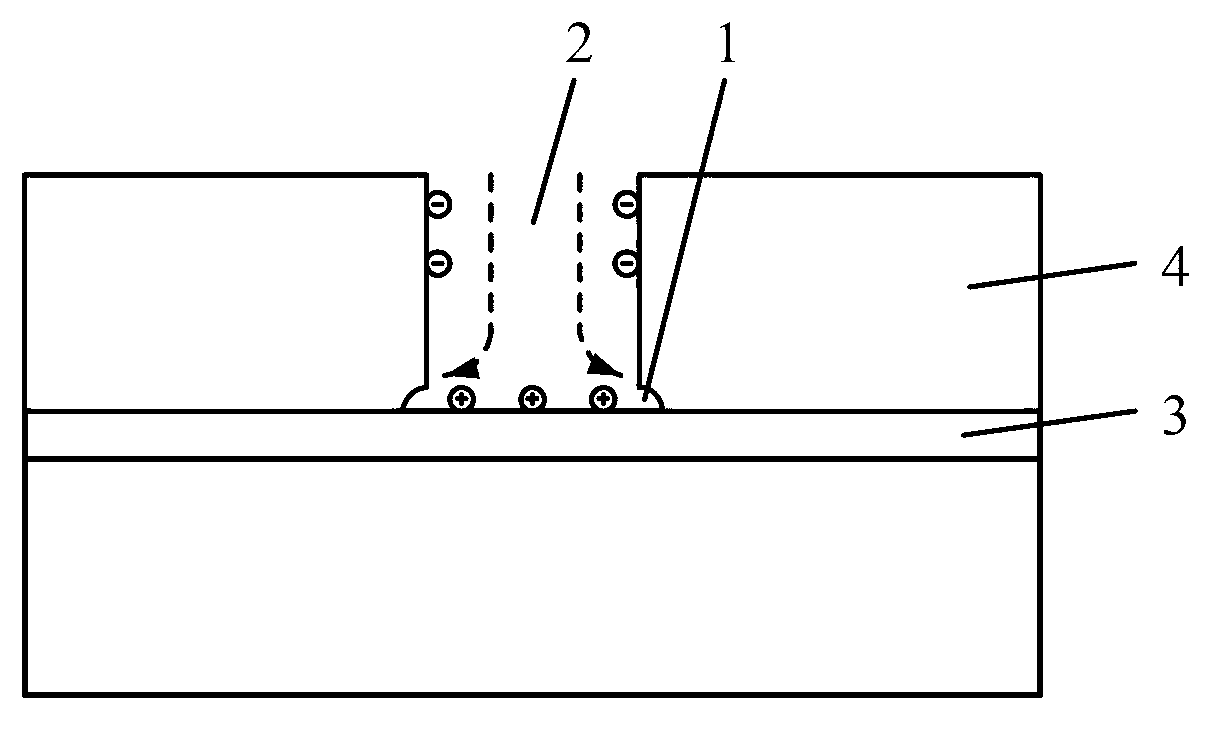

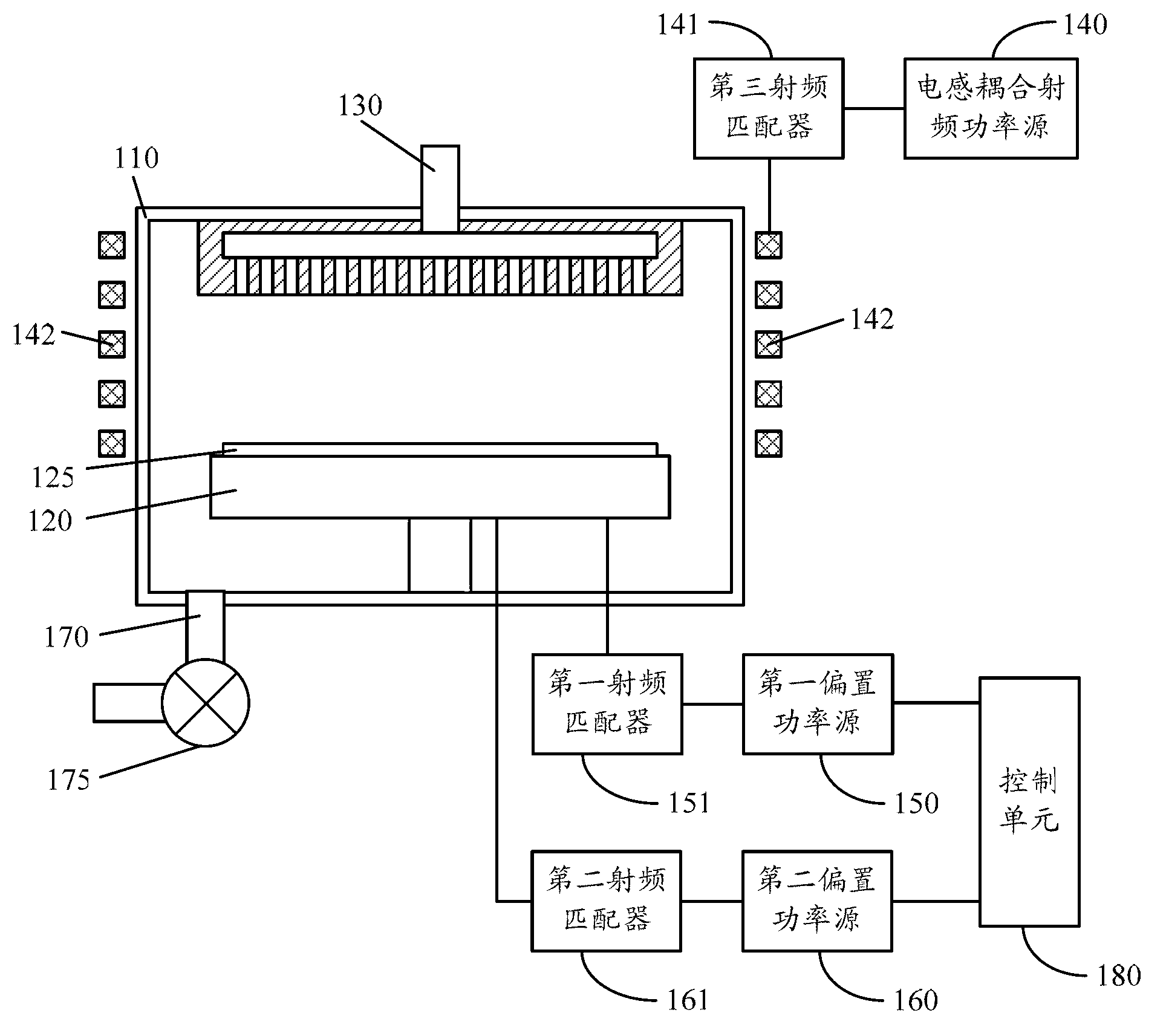

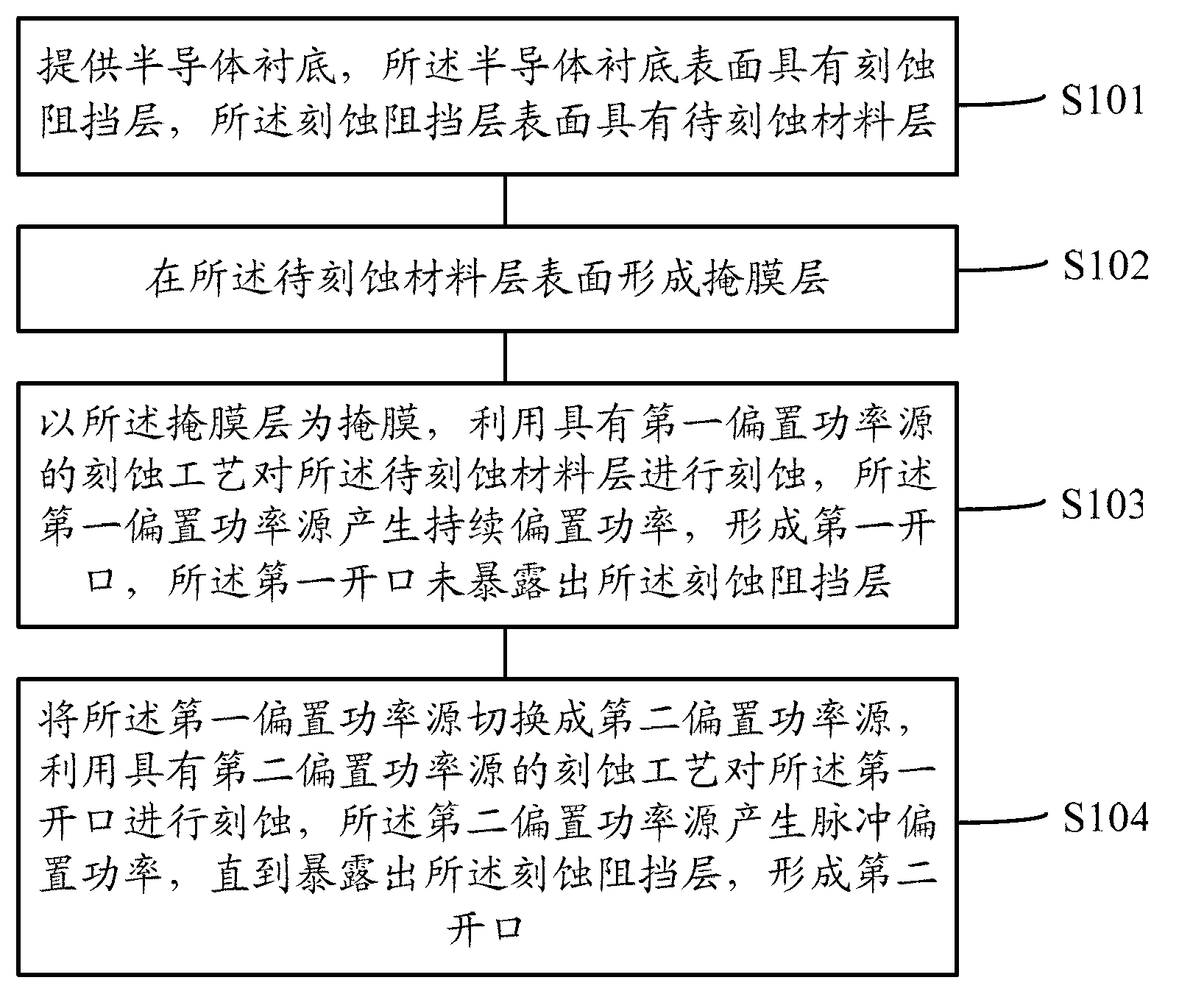

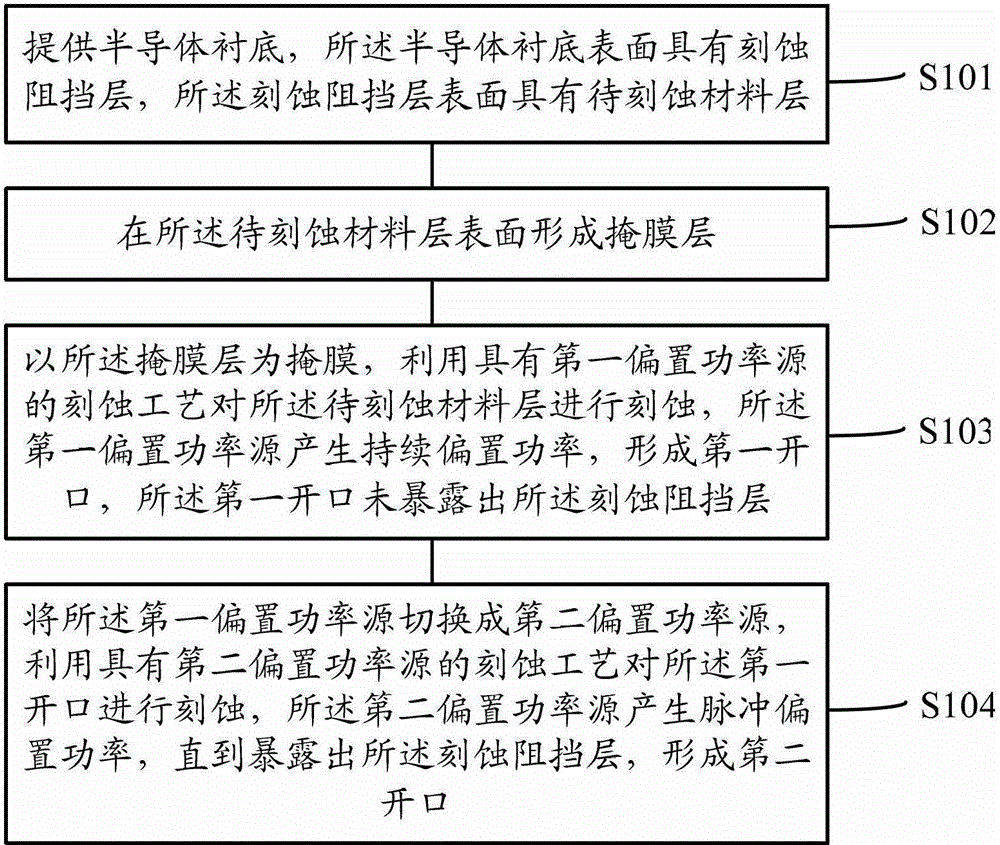

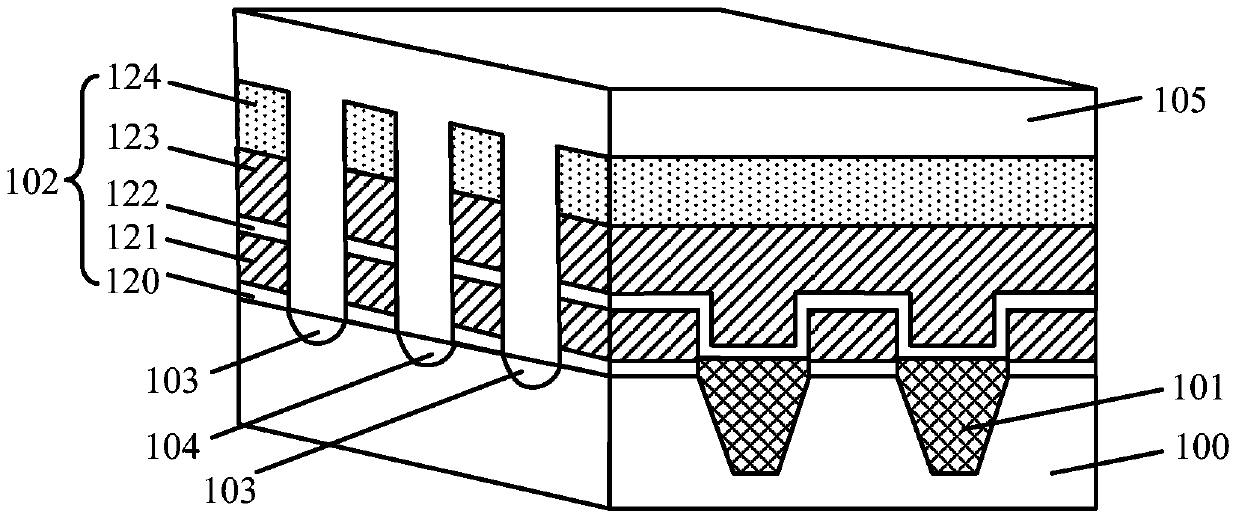

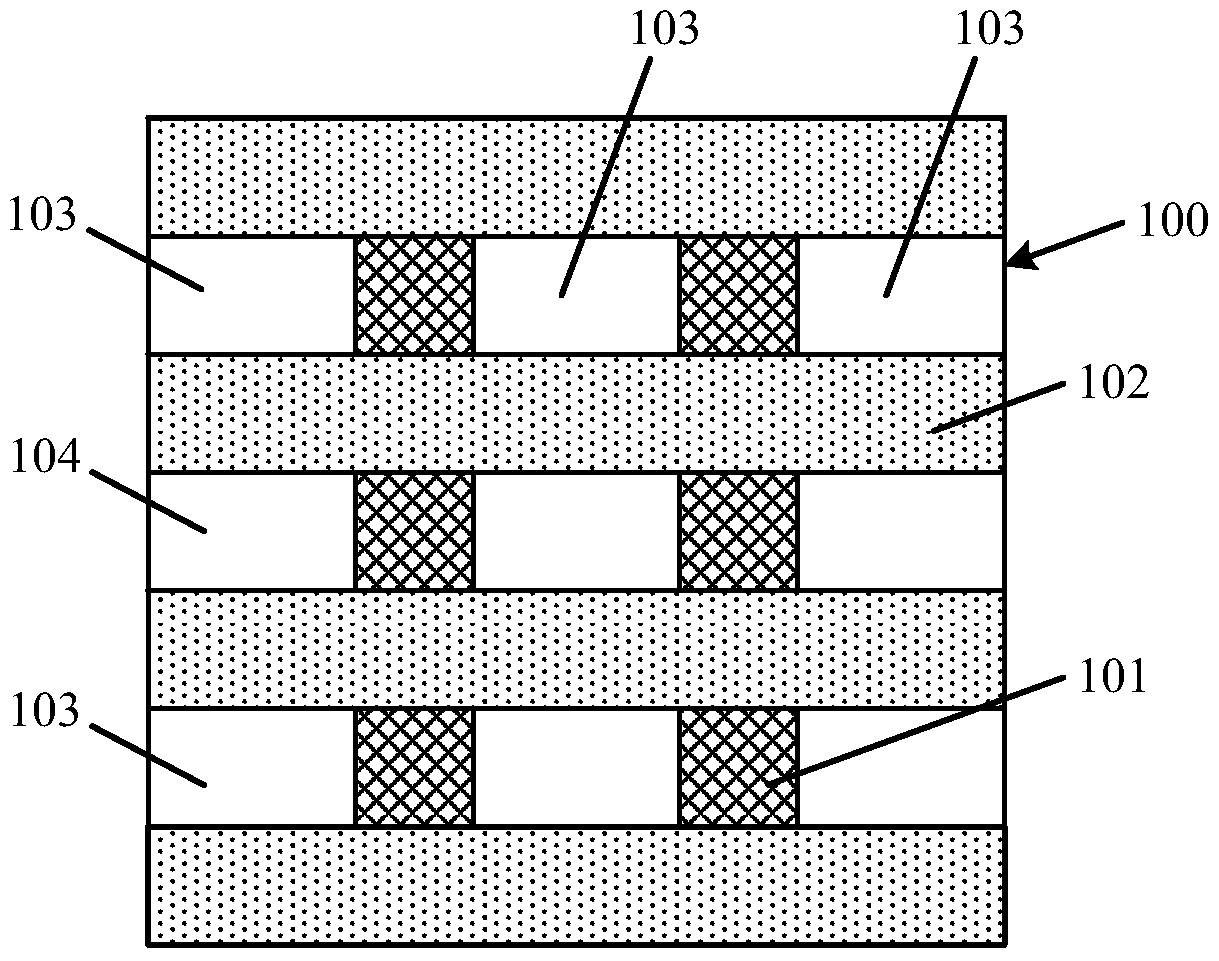

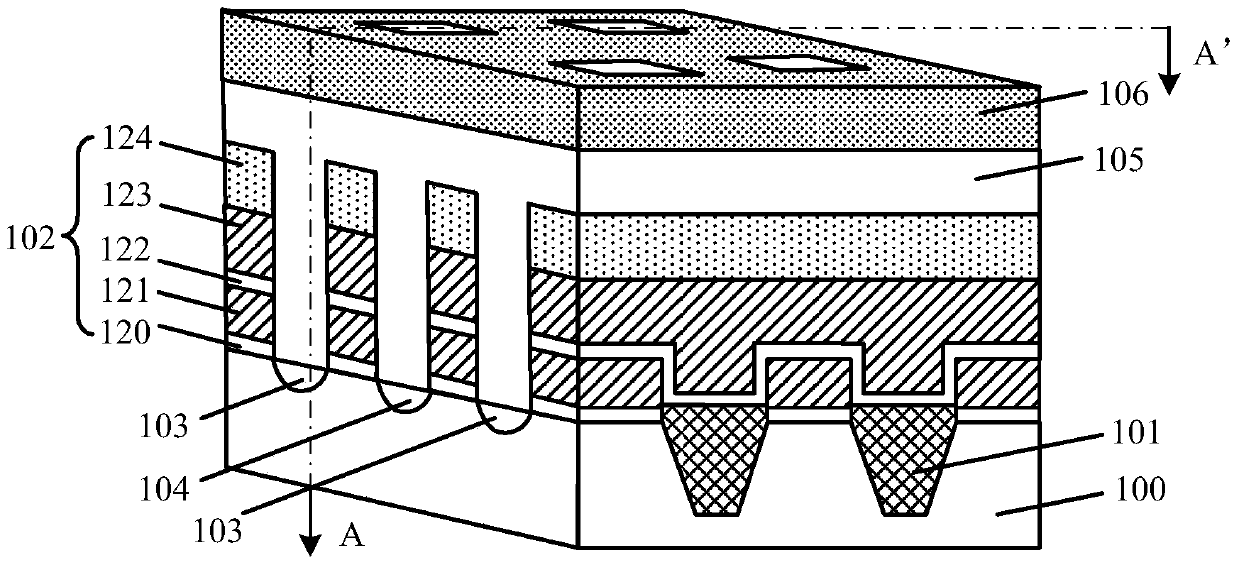

Semiconductor etching device and etching method of semiconductor structure

ActiveCN103021912AAvoid contaminationAvoid pollutionElectric discharge tubesSemiconductor/solid-state device manufacturingSemiconductor structureEngineering

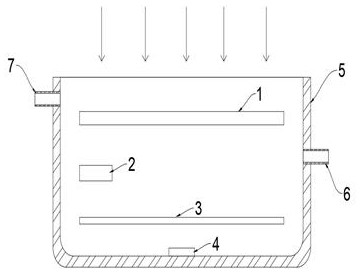

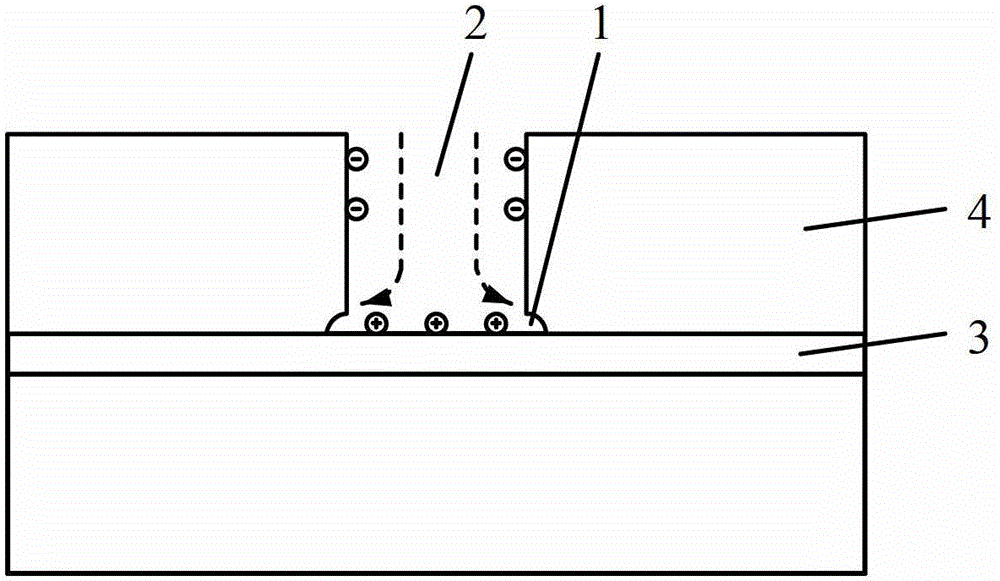

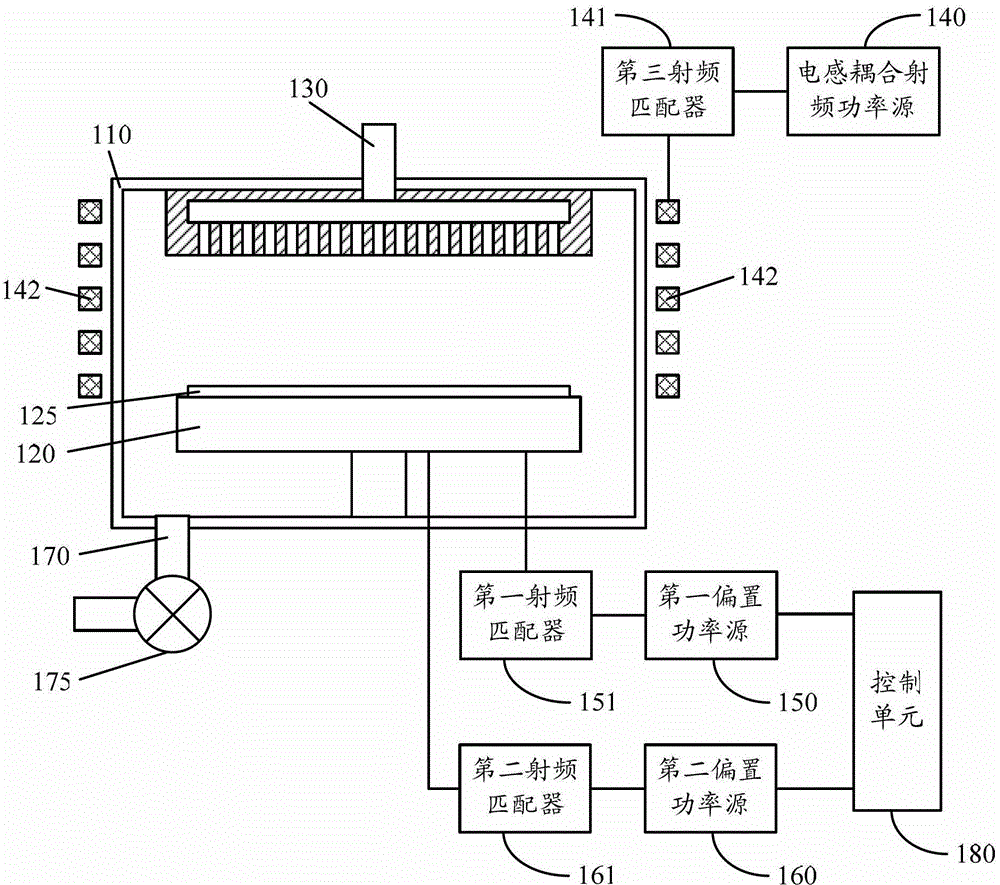

Disclosed are a semiconductor etching device and an etching method of a semiconductor structure. The etching method includes: a etching process with a first bias power source is utilized to etch a to-be-etched material layer, and the first bias power source generates continuous bias power to form a first opening which does not expose a etching blocking layer; and then a etching process with a second bias power source is utilized to etch the first opening, and the second bias power source generates pulse bias power until the etching blocking layer is exposed to form a second opening. Due to the fact that the continuous bias power is utilized to form bias voltage for etching firstly, side wall appearance is good, and etching selection ratio to a photo layer is high. The continuous bias power is switched into pulse bias power to form bias voltage for etching in prior to exposure of the etching blocking layer, so that cuts are avoided from being formed at the side wall bottom, close to the etching blocking layer, of the to-be-etched material layer.

Owner:ADVANCED MICRO FAB EQUIP INC CHINA

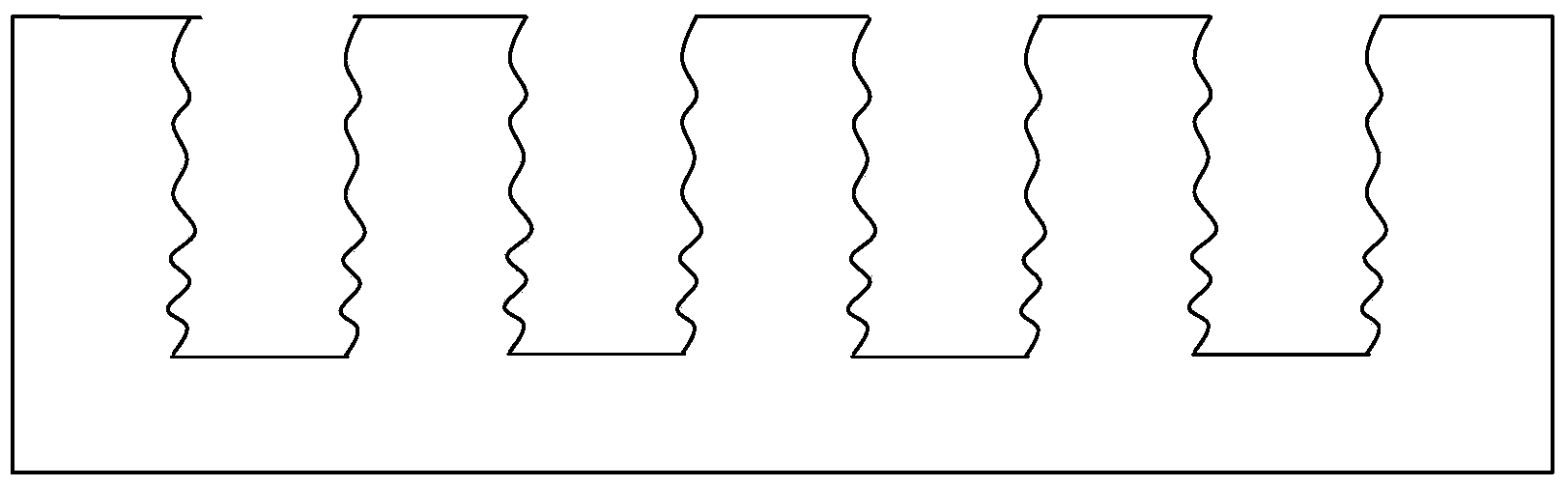

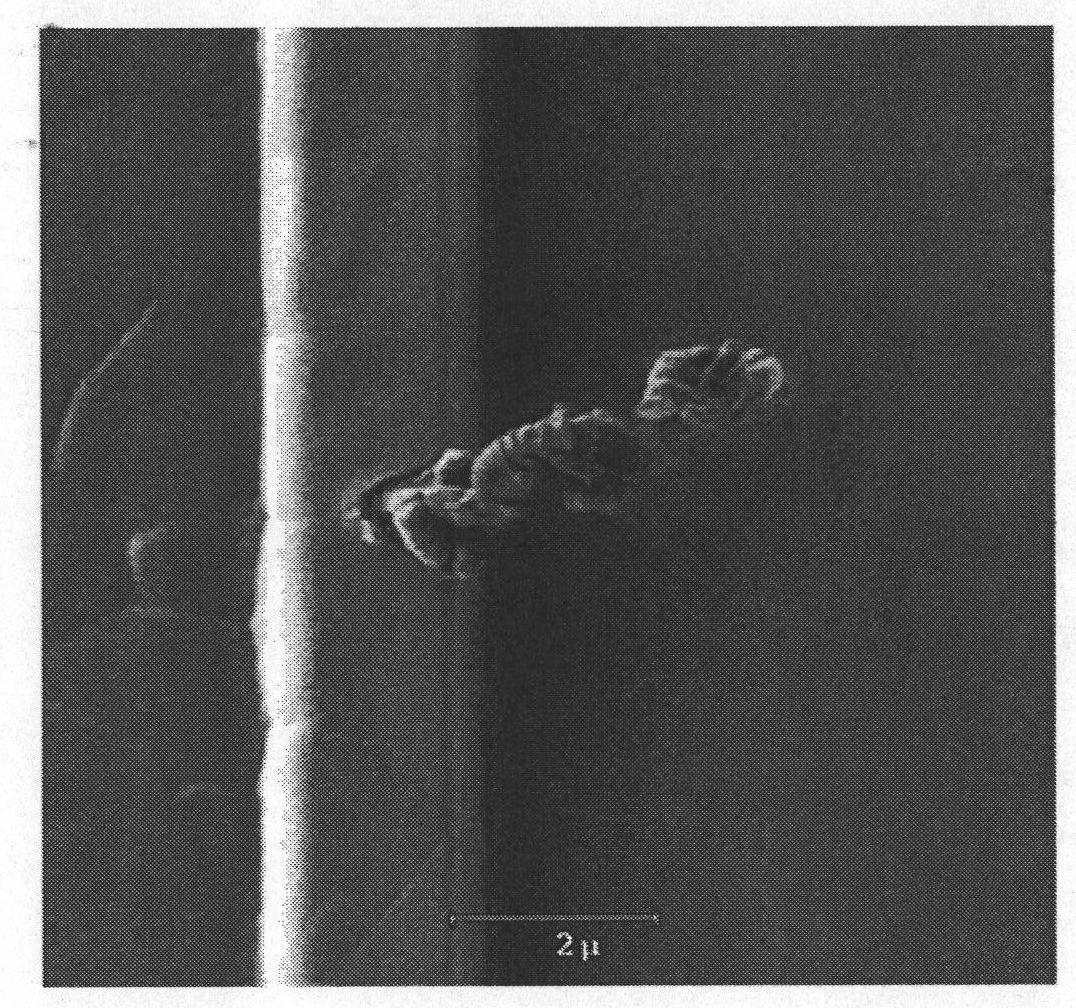

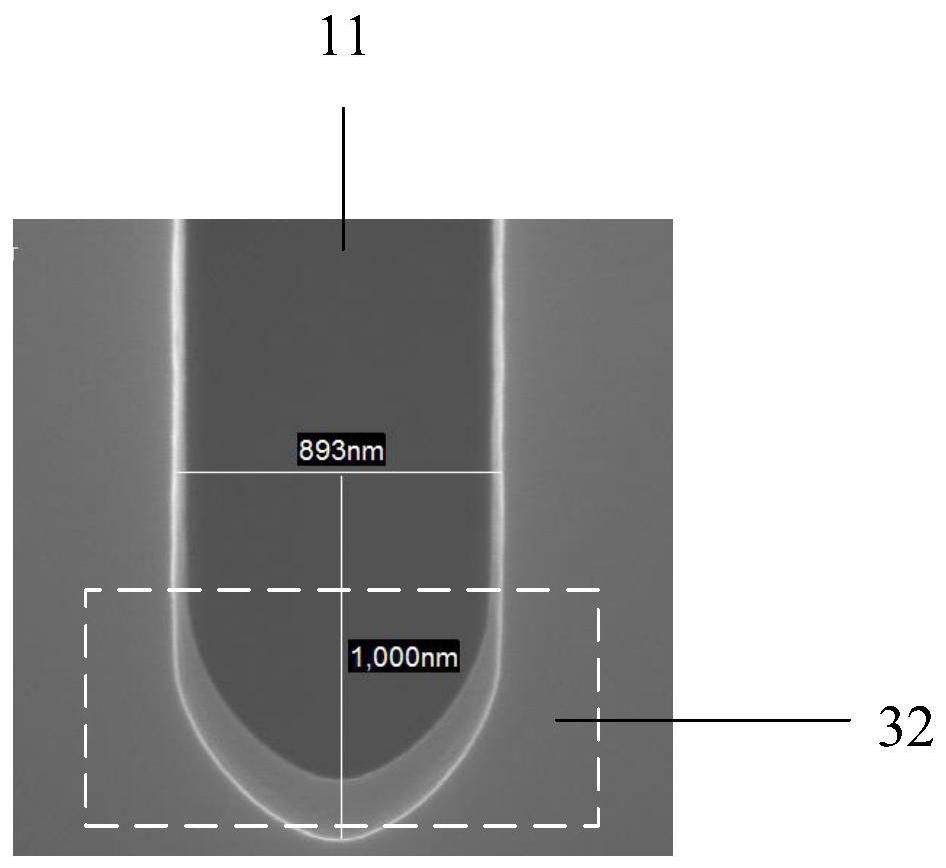

A method for forming a through silicon via

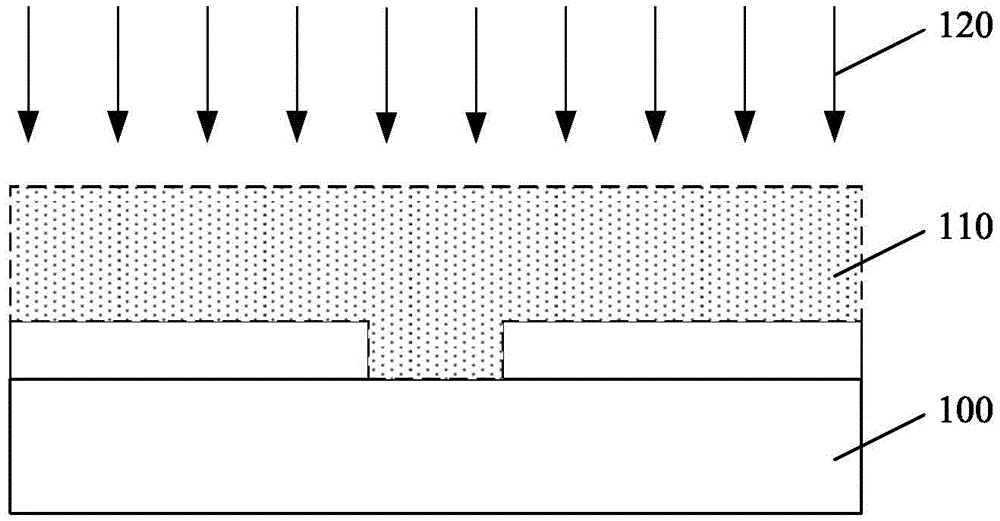

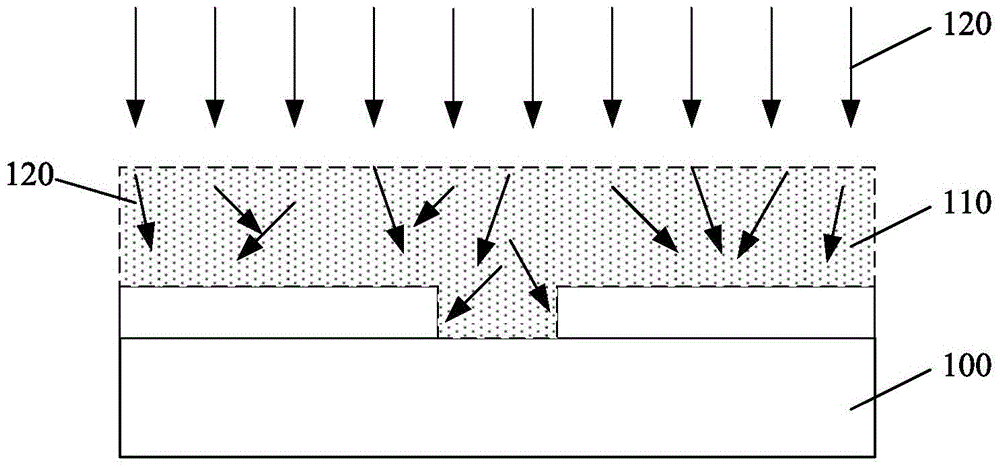

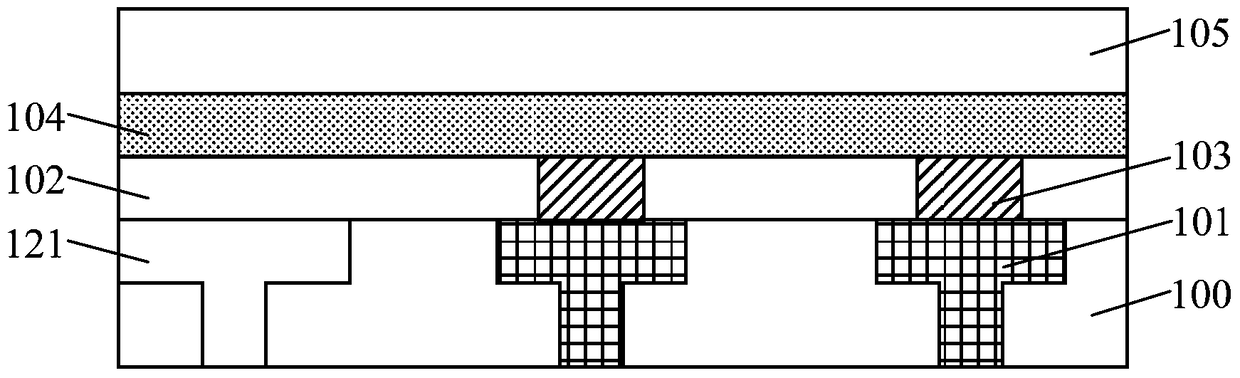

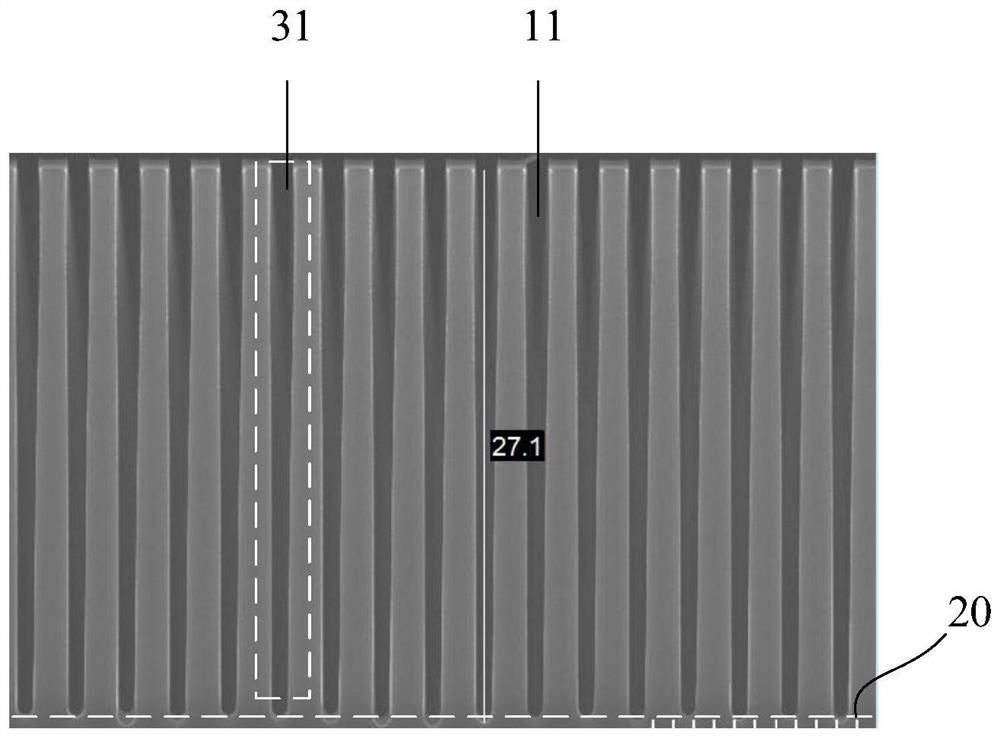

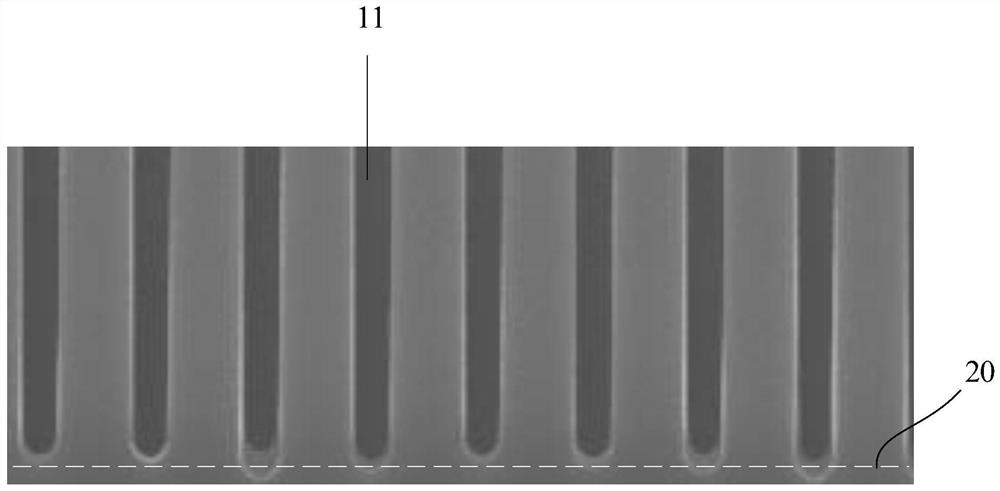

ActiveCN103646917AReduce reflectionReduce refractionSemiconductor/solid-state device manufacturingEtchingProtection layer

Provided is a method for forming a through silicon via. The method comprises: obtaining a first etching stage and a second etching stage according to a through silicon via to be formed; etching a silicon substrate with a first Bosch process in the first etching stage at a first etching temperature in order to form a first via; and etching the silicon substrate with a second Bosch process along the first via in the second etching stage at a second etching temperature until a through silicon via is formed, wherein the second Bosch process comprises: etching the silicon substrate with the first etching in order to form an opening; forming a protection layer on the sidewall and the bottom of the opening with passivation deposition; and successively and circularly using the first etching and the passivation deposition until the through silicon via is formed, wherein the second etching temperature is below the first etching temperature or over the first etching temperature. The through silicon via formed by using the method for forming a through silicon via has high quality.

Owner:ADVANCED MICRO FAB EQUIP INC CHINA

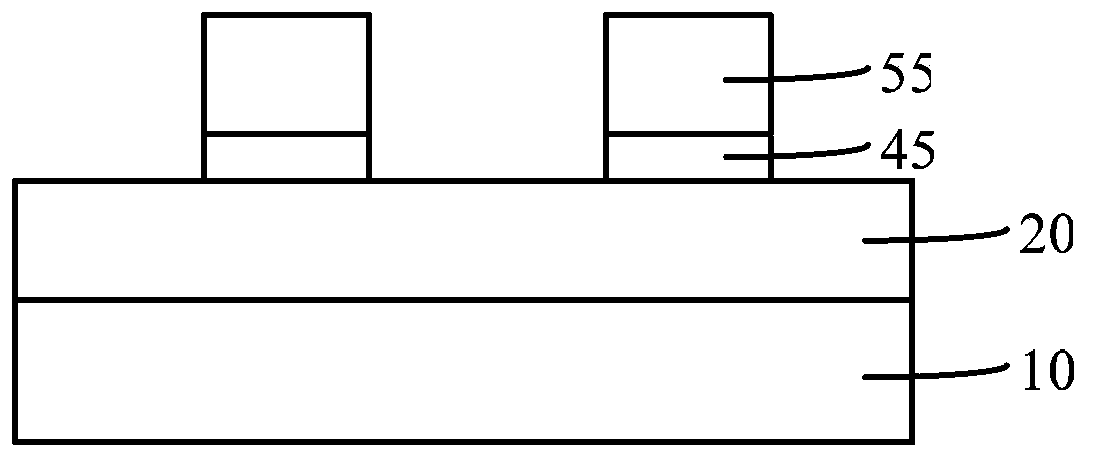

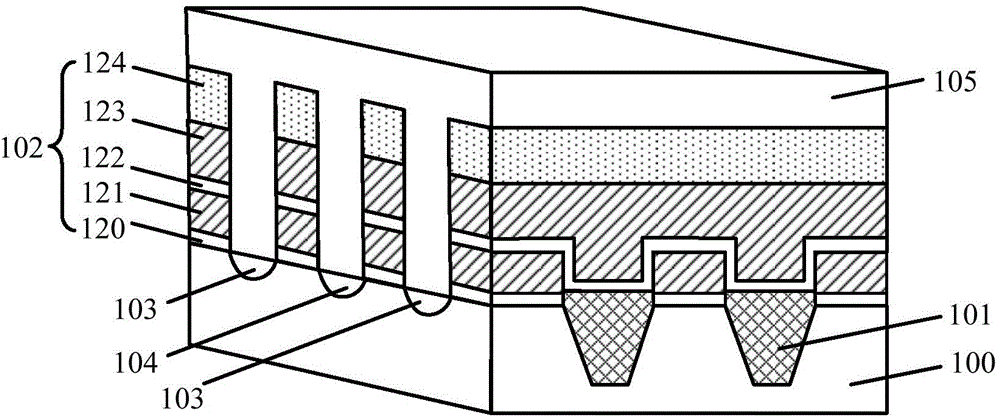

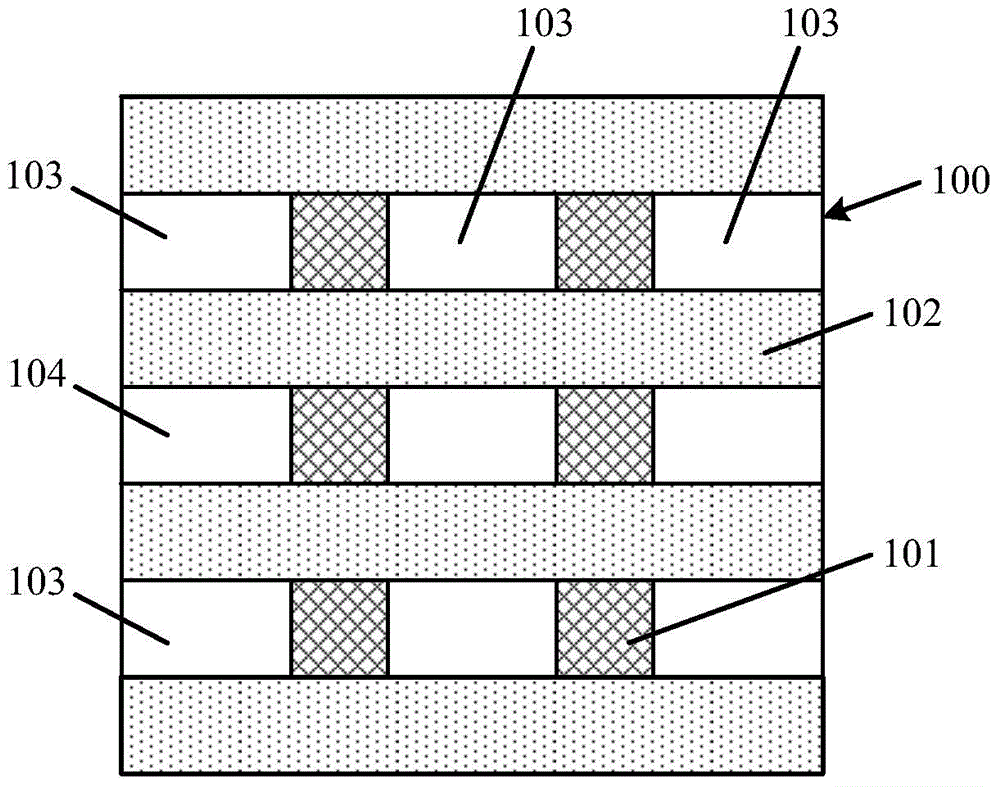

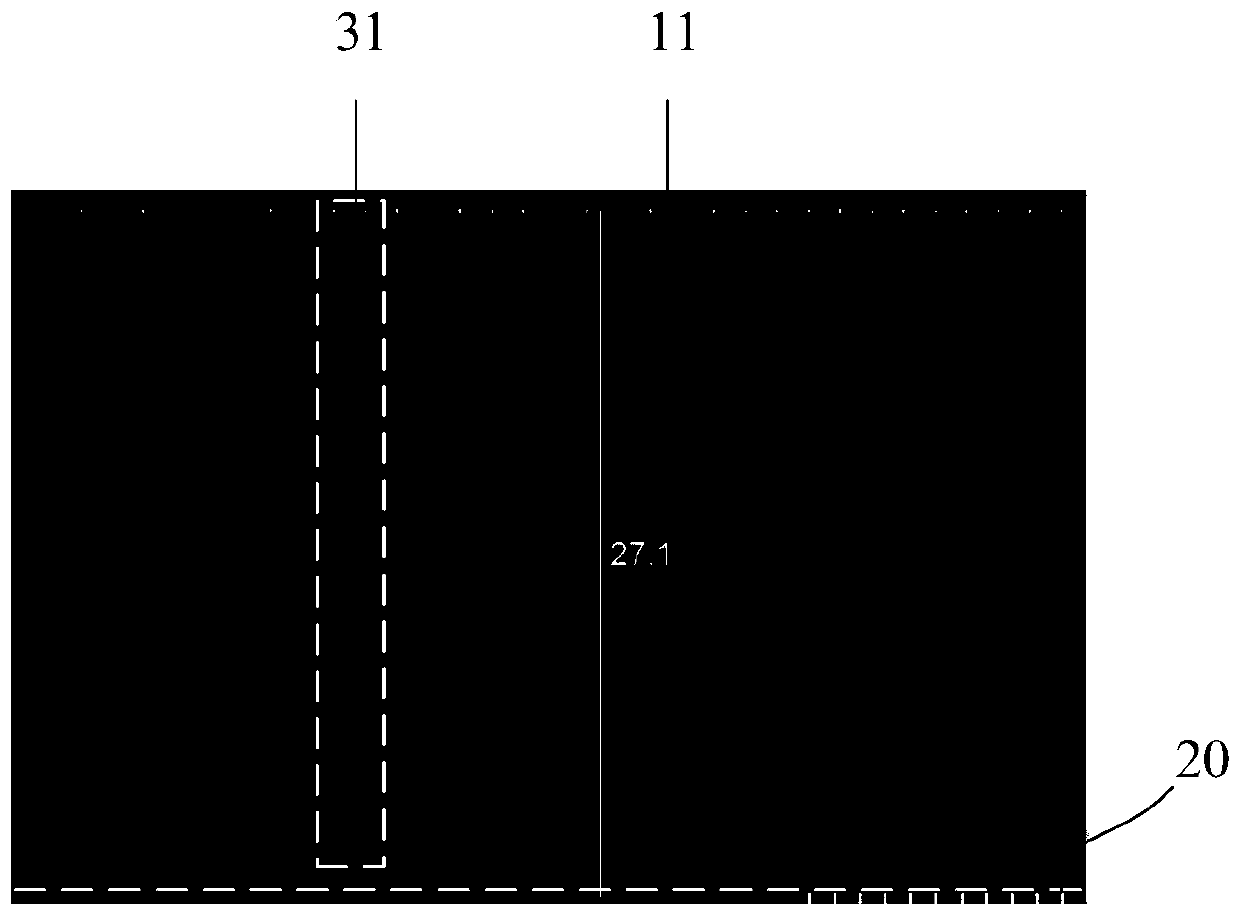

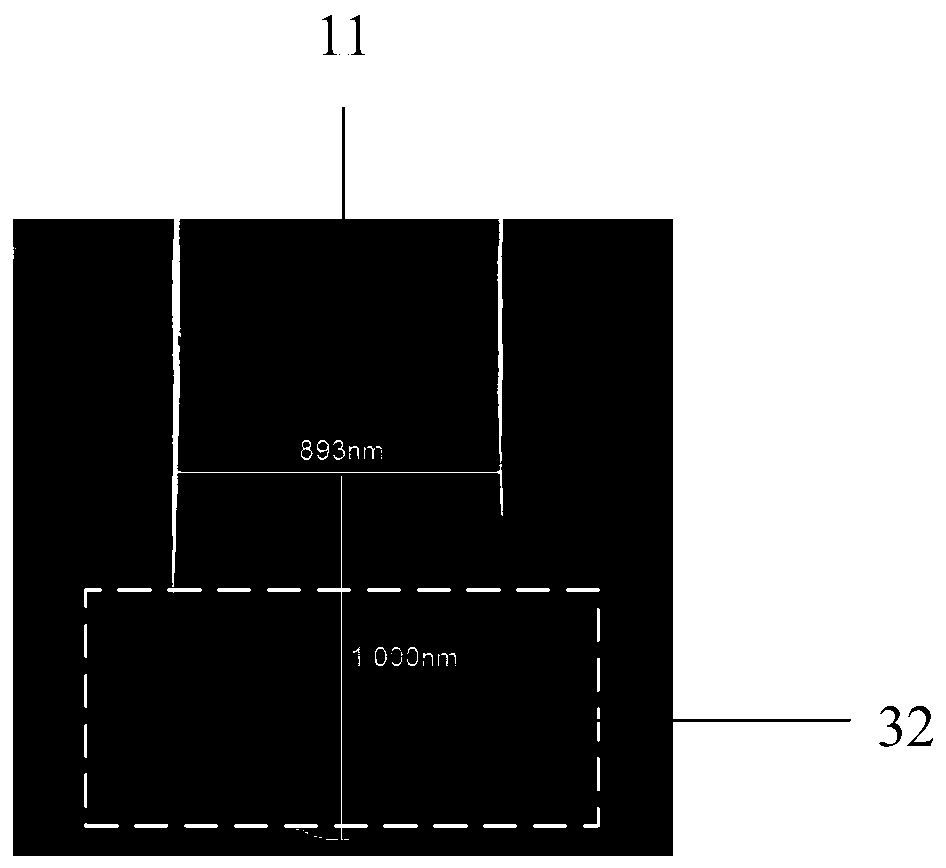

Method of forming semiconductor device

ActiveCN107579001ALess etching lossReduce height differenceSemiconductor/solid-state device manufacturingSemiconductorMaterials science

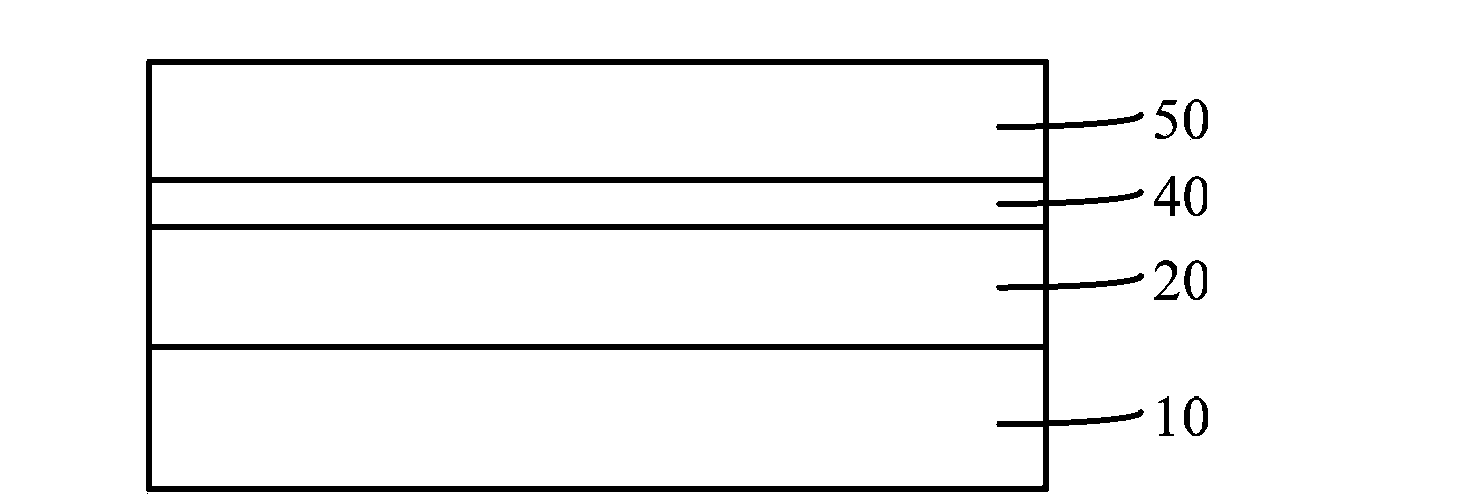

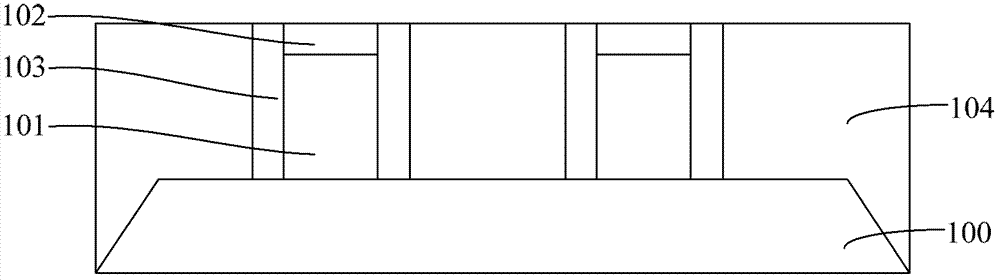

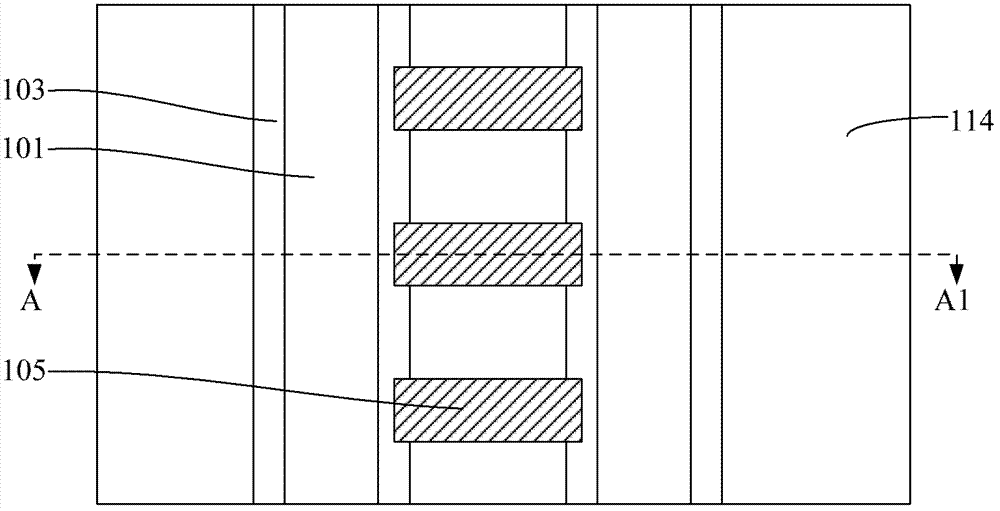

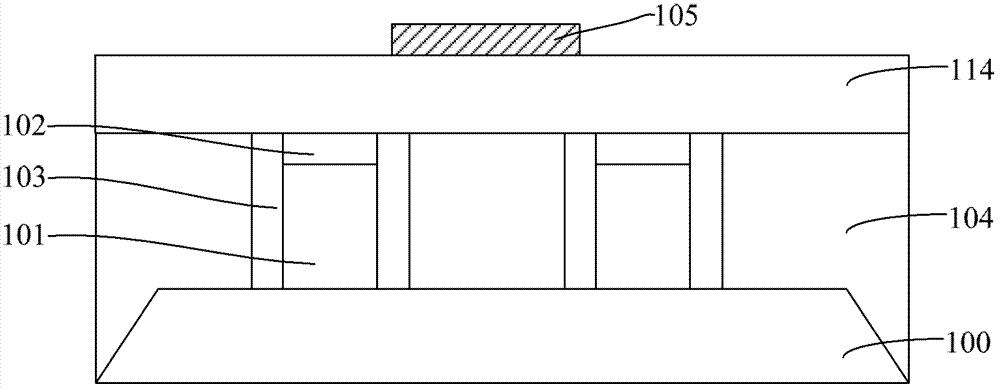

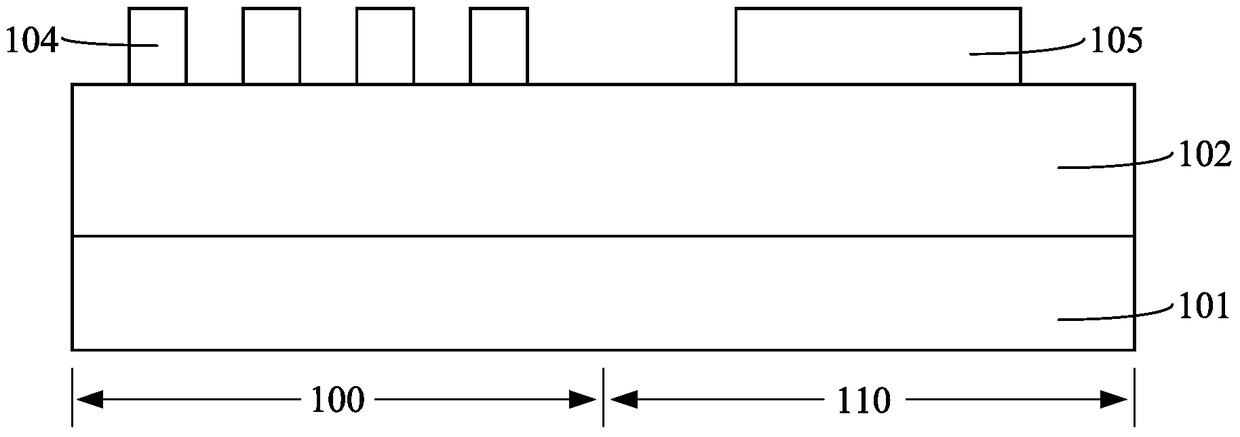

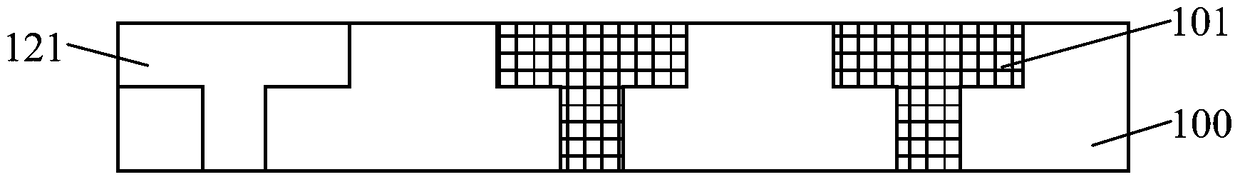

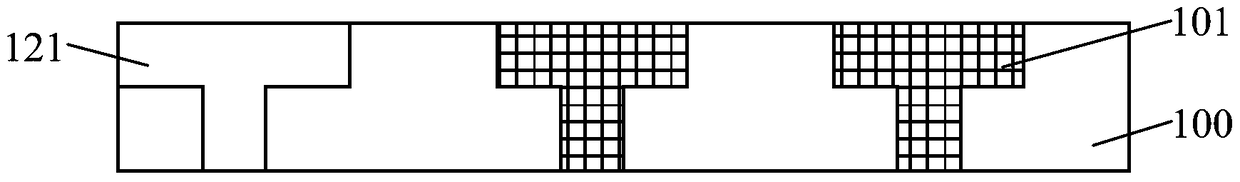

A method for forming a semiconductor device includes the steps of providing a material layer to be etched, wherein material layer to be etched has a barrier layer; forming a plurality of discrete sacrificial layers on the surface of the barrier layer; forming a first sidewall material layer on the top surfaces and the sidewall surfaces of the sacrificial layers, and the surface of the barrier layer; etching the first sidewall material layer until exposing the surface of the barrier layer and top surfaces of the sacrificial layers, forming a first side wall on the sidewalls of the sacrificial layers, with an etching selection ratio of the first sidewall material layer to the barrier layer being greater than or equal to 10; and after removing the sacrificial layers, etching the barrier layerand the material to be etched by using the first sidewall as a mask. The method of forming the semiconductor device improves the performance of the patterns in the semiconductor device.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

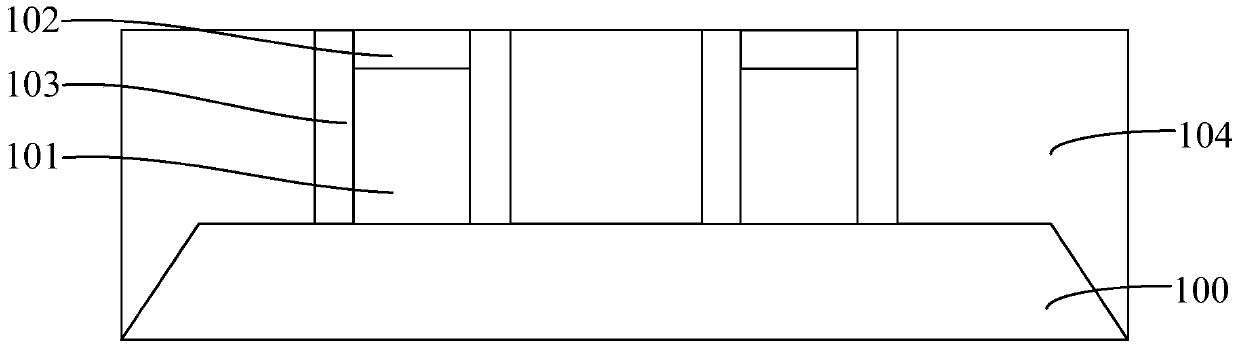

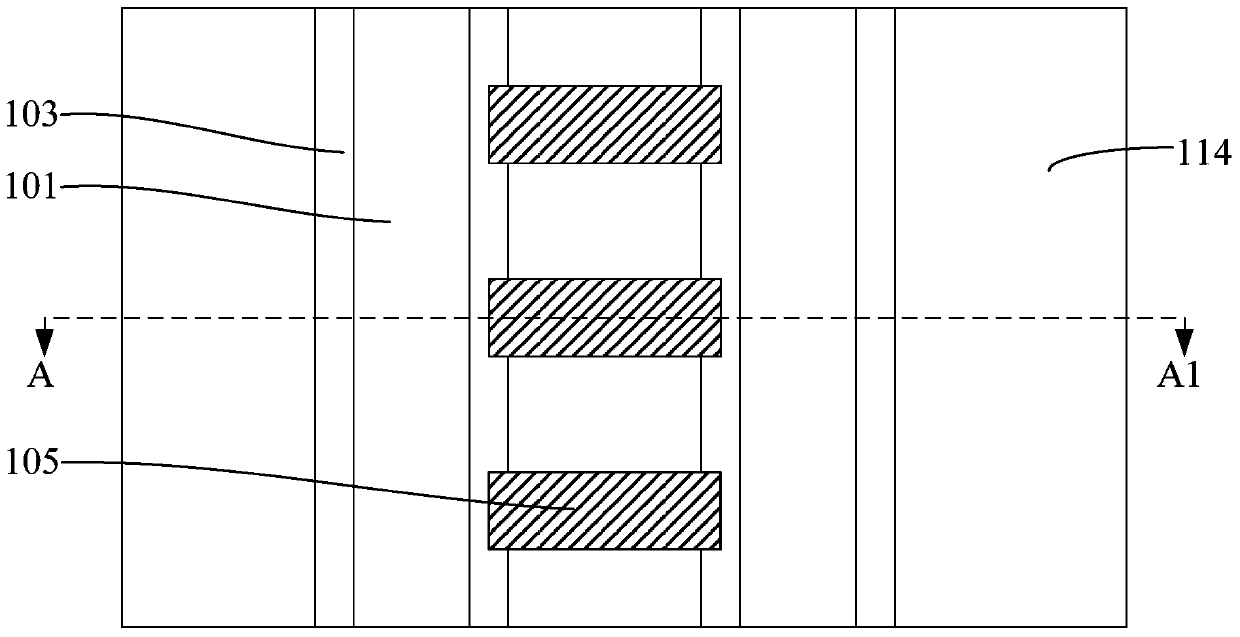

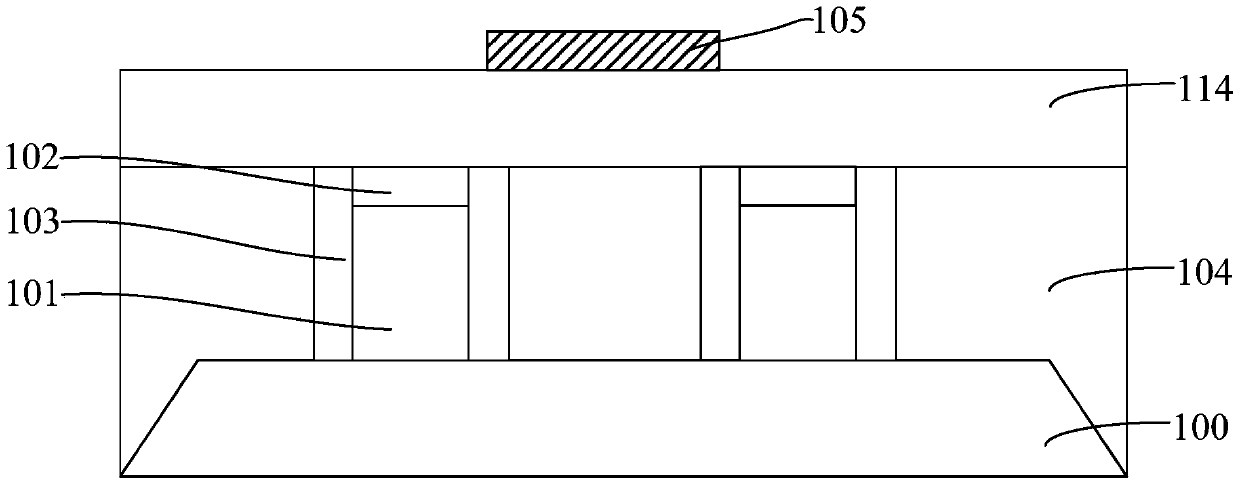

Formation method of semiconductor structure

ActiveCN107039334AAvoid exposureAvoid etch damageSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor structureDielectric layer

The invention provides a formation method of a semiconductor structure. The formation method comprises the steps that a first opening is formed in a dielectric layer, and the first opening crosses adjacent gate structures; a first mask layer is formed on the surface of the sidewall of the first opening, and the first mask layer crosses the adjacent gate structures; a sacrificial layer fully filling in the first opening is formed on the surface of first mask layer, and the material etching resistance of the first mask layer is greater than that of the sacrificial layer; a second mask layer having a second opening is formed on the surface of the dielectric layer, the surface of the sacrificial layer and the surface of the first mask layer, and the second opening crosses the sacrificial layer and the first mask layer; the dielectric layer exposed out of the sacrificial layer and the first mask layer is etched along the second opening with the second mask layer acting as the mask, and discrete contact holes are formed in the dielectric layer arranged between the adjacent gate structures; and conductive plugs fully filling in the contact holes are formed. The sidewall position accuracy and the shape accuracy of the formed contact holes can be enhanced so as to improve the performance of the formed semiconductor structure.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Formation method of semiconductor structure

ActiveCN105762114AGood lookingUniform pore sizeSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor structureEngineering

The invention provides a formation method of a semiconductor structure. The method includes the following steps that: a substrate is provided, a plurality of active regions are arranged in the substrate, and isolation structures are arranged between adjacent active regions, the substrate surfaces of a part of the active regions are provided with gate structures, two sides of each gate structure are respectively provided with a source region and a drain region; a first dielectric layer is formed on the surfaces of the active regions, the isolation structures and the gate structures; the first dielectric layer on the isolation structures is removed, initial through holes are formed in the first dielectric layer; a protective layer is formed on the surfaces of the side walls of the initial through holes; after the first dielectric layer at the bottoms of the initial through holes is removed, first through holes are formed in the first dielectric layer; a second dielectric layer is formed in the first through holes; after the first dielectric layer is removed, a second through hole and a source line trench are formed at two sides of each gate structure respectively; and drain conductive structures are formed in the second through holes, and source line conductive structures are formed in the source line trenches. The semiconductor structure formed by adopting the method has a beautiful appearance and stable performance.

Owner:SEMICON MFG INT (SHANGHAI) CORP

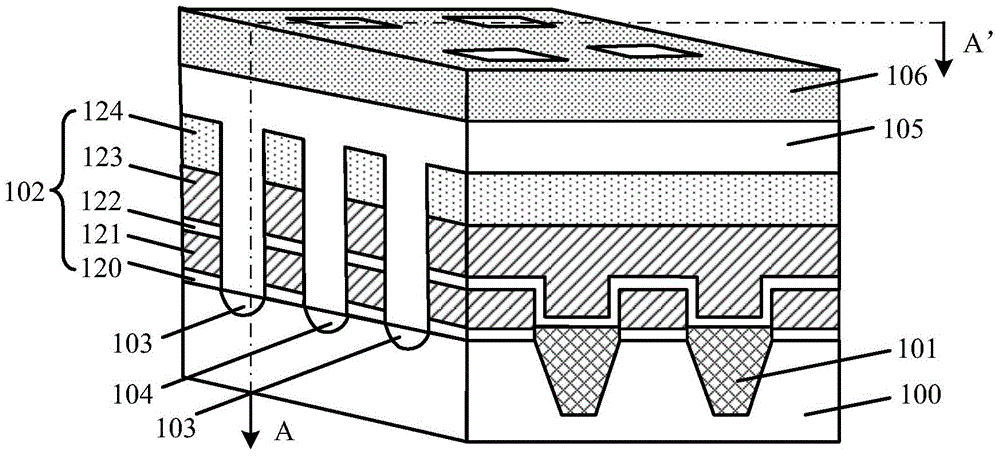

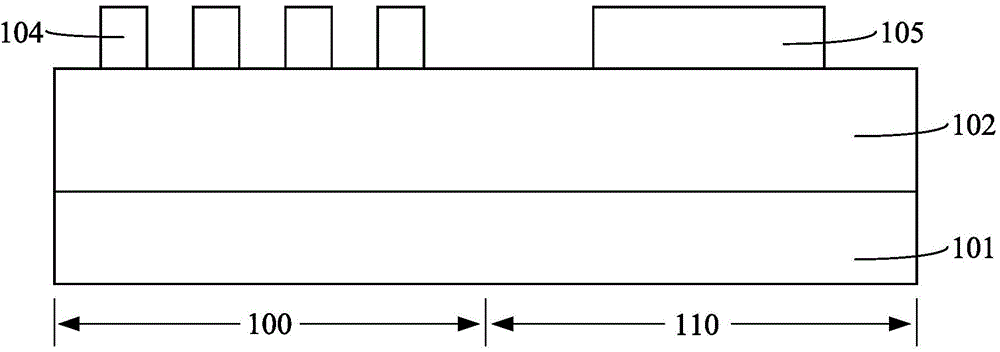

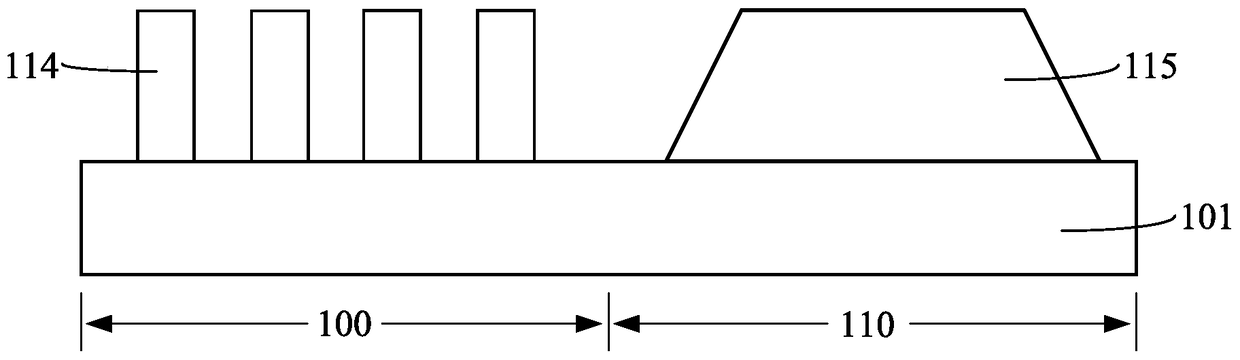

Formation method of semiconductor device

ActiveCN104952782AEasy to shapeGood lookingSemiconductor/solid-state device manufacturingComputational physicsSemiconductor

A formation method of a semiconductor device includes providing a substrate having a to-be-etched layer including a graph dense zone and a graph sparse zone; forming a first mask layer having sparse images on the surface of the graph sparse zone of the to-be-etched layer; forming a photo-etching layer covering the surface of the to-be-etched layer and the surface of the first mask layer; performing exposure development on the photo-etching layer and forming a second mask layer having dense images on the image dense zone of the to-be-etched layer and the surface of the first mask layer; etching the graph dense zone of to-be-etched layer by taking the second mask layer as a mask and etching the graph sparse zone of the to-be-etched layer by taking the second mask layer and the first mask layer as the mask until the surface of the substrate is exposed. By adopting the invention, problems caused by load effect during an etching process can be solved, so that the etching layer formed after the etching process of the graph sparse zone has a good appearance.

Owner:SEMICON MFG INT (SHANGHAI) CORP

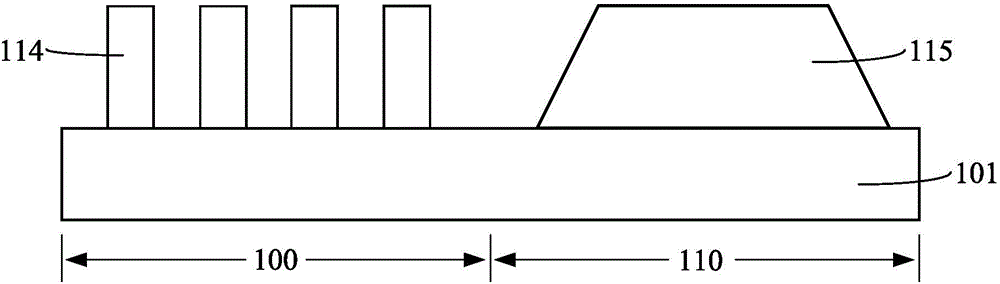

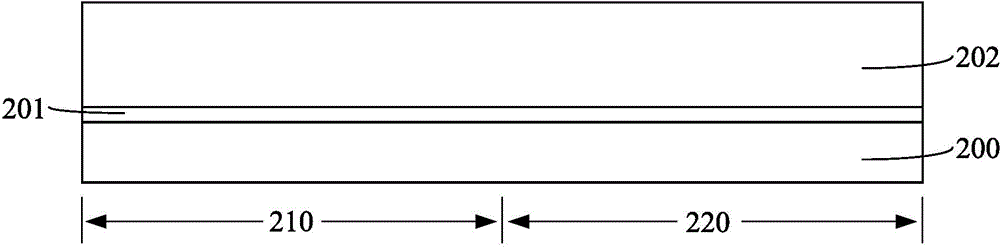

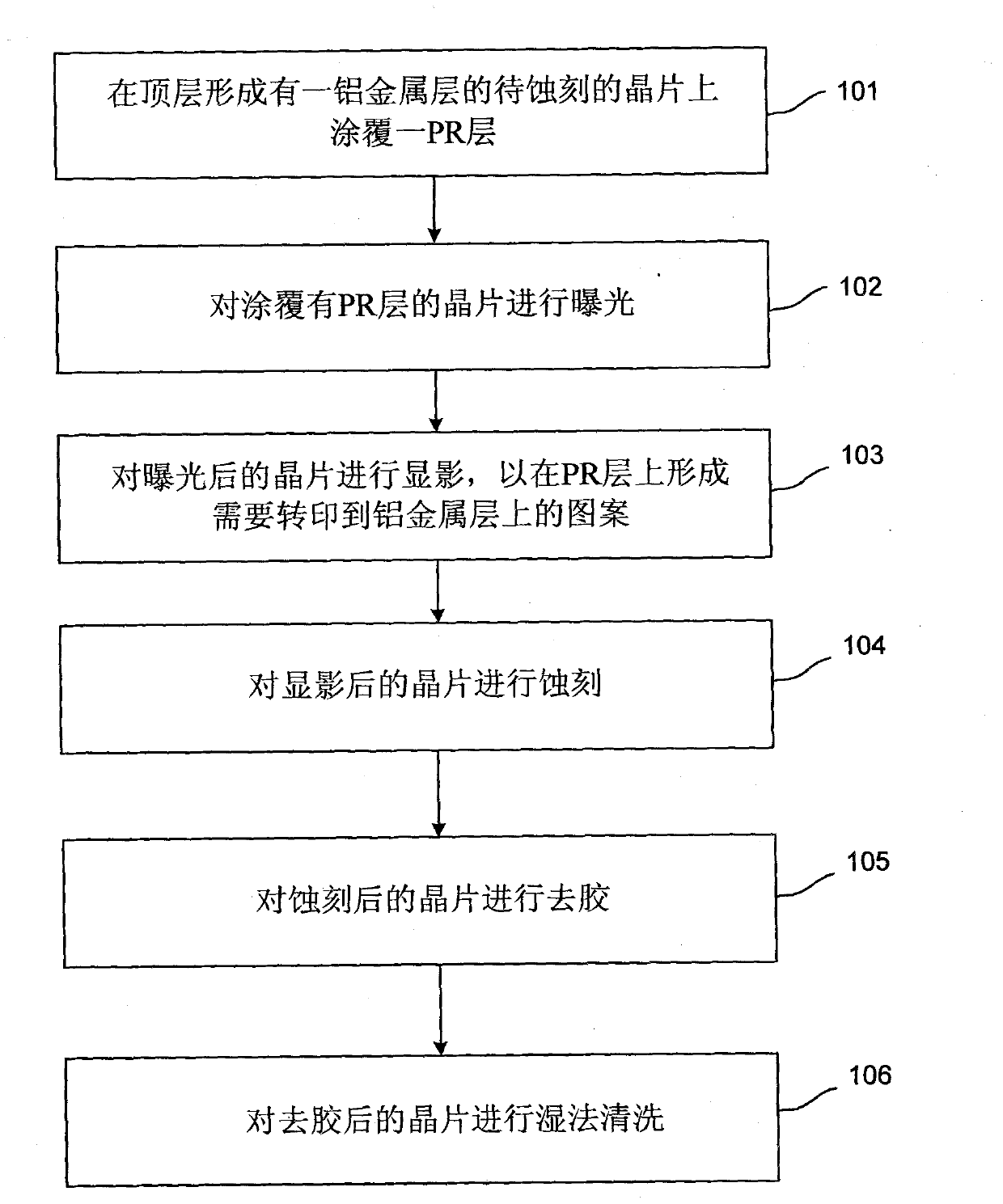

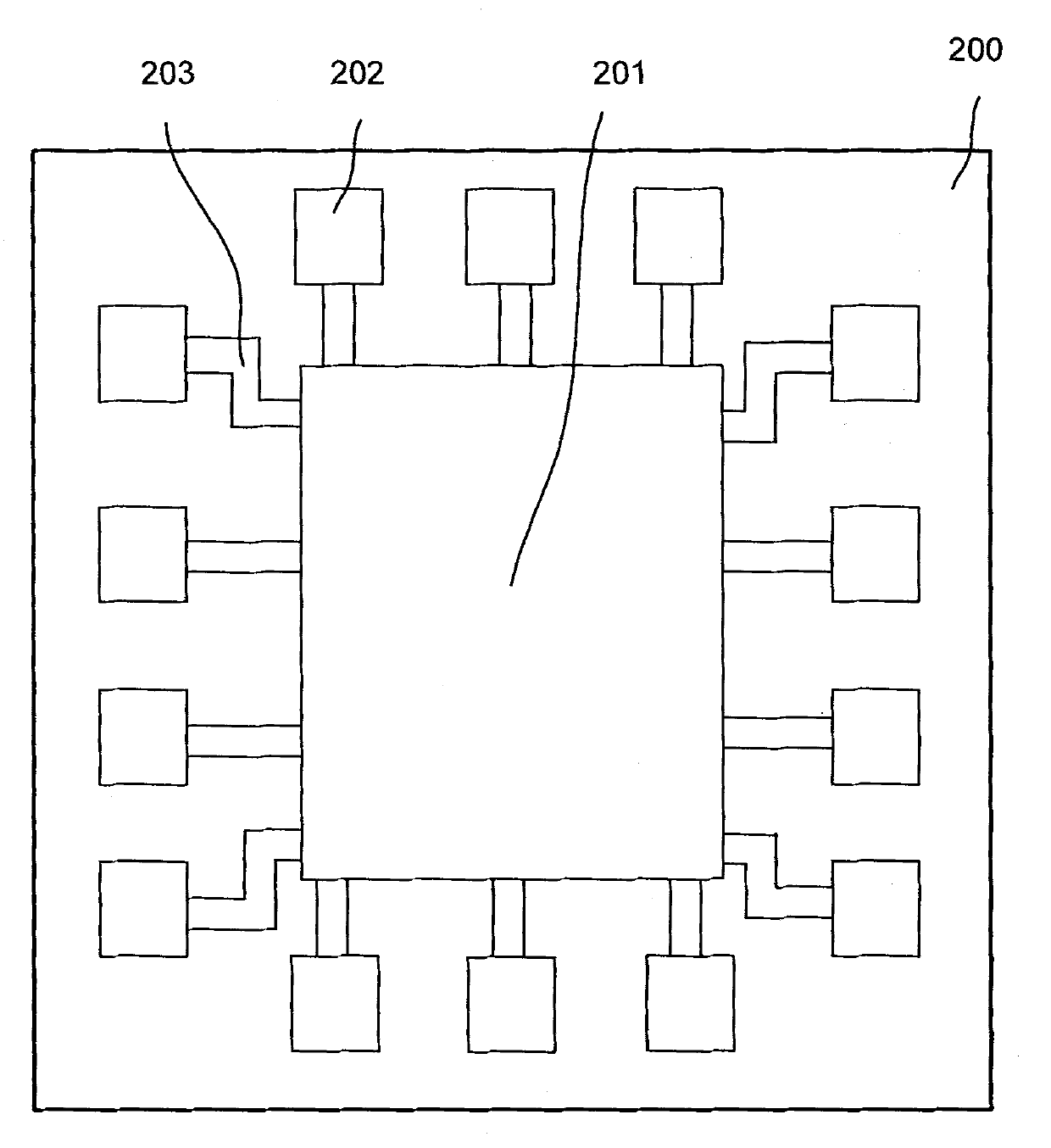

Manufacture method for semiconductor device

InactiveCN102201350AAvoid bombardment damageIncreased anisotropySolid-state devicesSemiconductor/solid-state device manufacturingResistSingle exposure

The invention provides a manufacture method for a semiconductor device. The method comprises the following steps: providing a wafer to be etched, wherein a metal layer is formed on the top of the wafer; adding a first photoresist layer on the wafer; carrying out first exposure and development treatments on the wafer to form a first pattern; carrying out a first etch treatment on the wafer to remove a first portion of the metal layer; removing the first photoresist layer; carrying out a wet cleaning on the wafer; adding a second photoresist layer on the wafer; carrying out second exposure and development treatments on the wafer to form a second pattern; carrying out a second etch treatment on the wafer to remove a second portion of the metal layer; removing the second photoresist layer; and carrying out a wet cleaning on the wafer. According to the method provided in the invention, more photoresist can be provided on the whole wafer to prevent the damage of plasma bombardment, more polymer protection is provided for aluminium wire sidewall to raise the anisotropy of etching, thus the manufacture of semiconductor device with good sidewall morphology and without corrosion defect is realized.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

TSV Formation Method

ActiveCN103646917BReduce reflectionReduce refractionSemiconductor/solid-state device manufacturingEtchingProtection layer

Provided is a method for forming a through silicon via. The method comprises: obtaining a first etching stage and a second etching stage according to a through silicon via to be formed; etching a silicon substrate with a first Bosch process in the first etching stage at a first etching temperature in order to form a first via; and etching the silicon substrate with a second Bosch process along the first via in the second etching stage at a second etching temperature until a through silicon via is formed, wherein the second Bosch process comprises: etching the silicon substrate with the first etching in order to form an opening; forming a protection layer on the sidewall and the bottom of the opening with passivation deposition; and successively and circularly using the first etching and the passivation deposition until the through silicon via is formed, wherein the second etching temperature is below the first etching temperature or over the first etching temperature. The through silicon via formed by using the method for forming a through silicon via has high quality.

Owner:ADVANCED MICRO FAB EQUIP INC CHINA

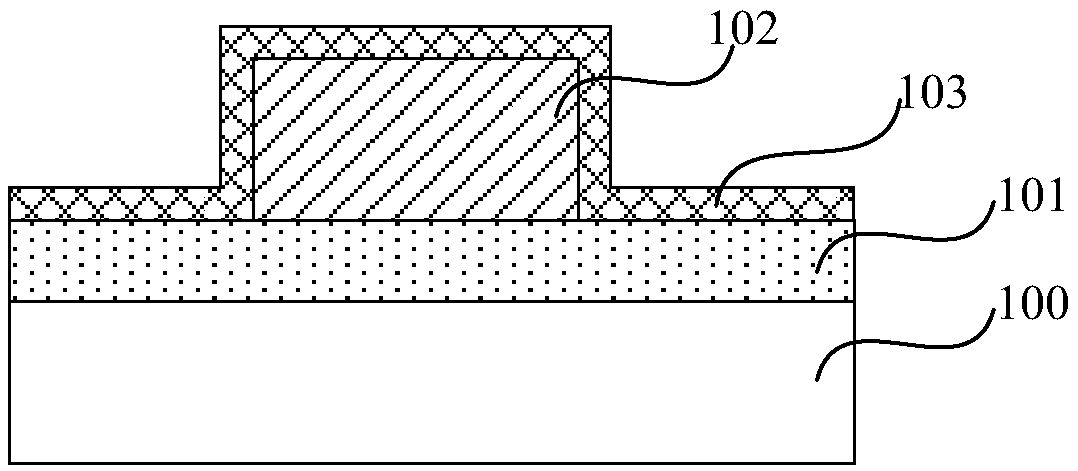

Forming method of resistive random-access memory

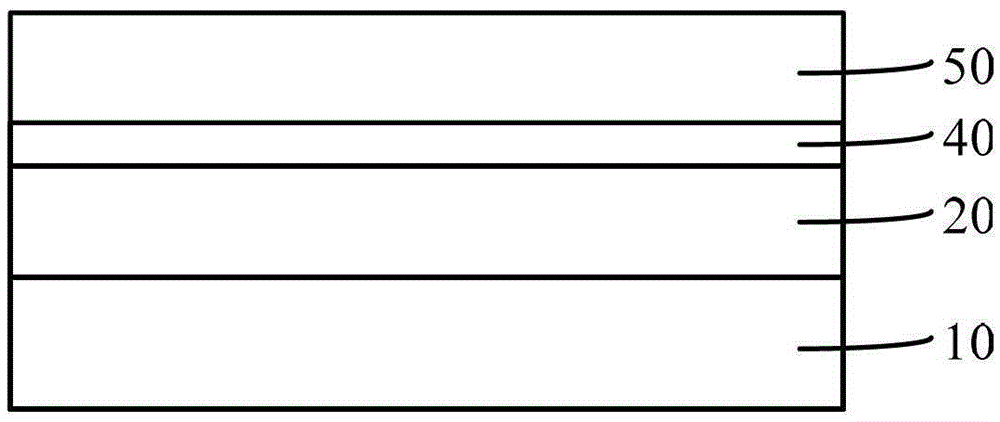

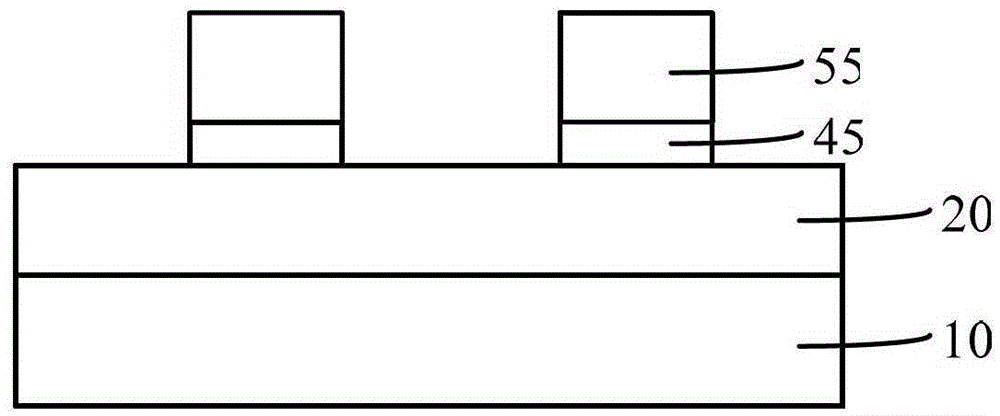

ActiveCN105679932AHigh etch selectivityQuality improvementElectrical apparatusOptoelectronicsDry etching

The invention provides a forming method of a resistive random-access memory. The method comprises the steps as follows: a substrate is provided; a lower electrode layer is arranged in the substrate; the top part of the lower electrode layer is flush with the surface of the substrate; a dielectric material layer is formed on the surface of the substrate; an upper electrode layer is formed on the surface of the dielectric material layer; a hard mask layer is formed on the surface of the upper electrode layer; the hard mask layer is patterned; an opening for exposing the upper electrode layer is formed in the hard mark layer; with the hard mask layer with the opening as a mask, the upper electrode layer and the dielectric material layer are sequentially etched by a dry etching process until the surface of the substrate is exposed; an etching gas for the dry etching process is H2; the hard mask layer with the opening is removed. The etching pollution to the upper electrode layer and the dielectric material layer caused by the etching process is avoided; and the side wall of the etched upper electrode layer and the side wall of the dielectric material layer are clean, so that the electrical properties of the formed resistive random-access memory are improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

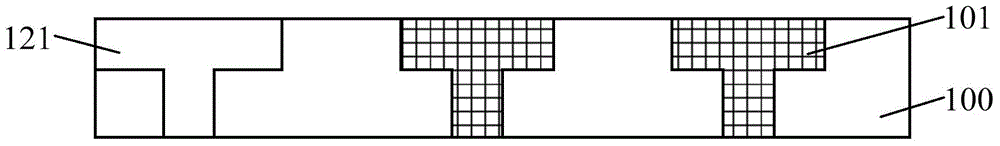

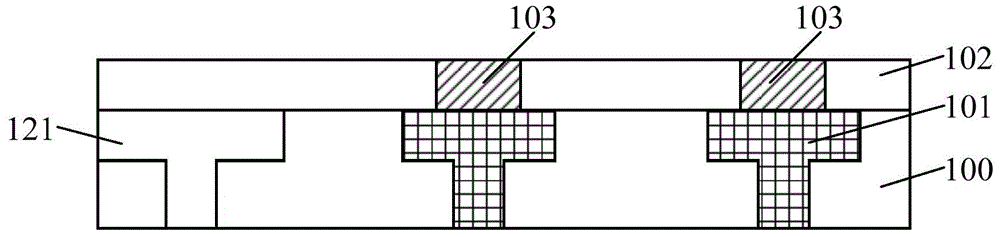

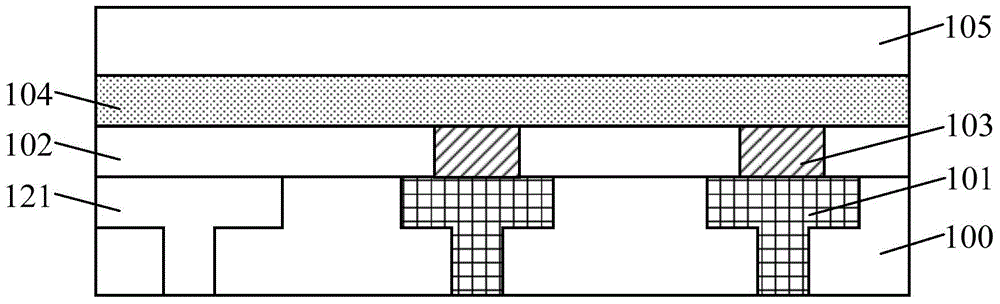

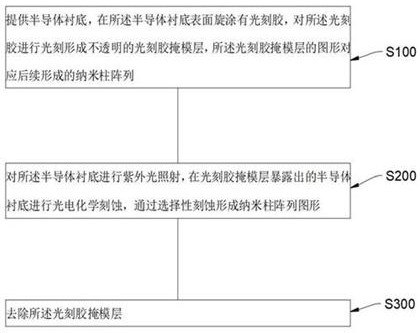

Preparation method of nano-pillar array

PendingCN114496768AGood sidewall morphologyImprove efficiencySemiconductor/solid-state device manufacturingNanotechnologyNanopillarPhotoelectrochemical etching

The invention relates to the field of process processing, in particular to a method for forming a nanopillar array on a semiconductor substrate, which comprises the following steps of: providing the semiconductor substrate, coating photoresist on the semiconductor substrate, and photoetching on the photoresist to form a pattern; a mask layer is formed on the prepared pattern, and light propagation is stopped through the mask layer; according to the method, a semiconductor substrate containing a mask layer is subjected to electrochemical etching, patterns with different heights are obtained by controlling etching conditions, then the mask layer is removed, the semiconductor substrate comprises a silicon carbide substrate slice or a gallium nitride substrate slice, the length and width of the semiconductor substrate are 2-8 inches, the thickness of the semiconductor substrate is 200-500 micrometers, and the thickness of the semiconductor substrate is 1-10 micrometers. An electron beam direct writing technology is adopted in the photoetching mode, and the pattern is in a nanopillar array shape. By adopting the photoelectrochemical etching method, the large-scale preparation of the nano-pillar array with controllable diameter size and height can be realized on the surface of the wafer-level wide bandgap semiconductor substrate slice, the process is simple, and the yield is high.

Owner:ZHEJIANG UNIV HANGZHOU GLOBAL SCI & TECH INNOVATION CENT

Formation method of self-aligned double pattern

ActiveCN103681234BHigh hardnessWill not deformSemiconductor/solid-state device manufacturingHardnessPhotoresist

The invention provides a method for forming self-alignment duplex pattern. The method comprises the following steps: providing a material layer to be etched, forming a sacrificial photoresist layer on the material layer to be etched, curing the sacrificial photoresist layer, forming a first mask pattern on the side wall surface of the sacrificial photoresist layer, and removing the sacrificial photoresist layer. As the sacrificial photoresist layer is cured, the hardness of the sacrificial photoresist layer is increased, and during the process of forming the first mask pattern, the sacrificial photoresist layer does not deform under the stress generated by the first mask material layer, so that the side wall of the sacrificial photoresist layer is still perpendicular to the surface of the material layer to be etched, and finally, the side wall of the etched pattern which is formed by etching the material layer to be etched has a better profile.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Super junction and manufacturing method thereof, and deep trench manufacturing method of super function

ActiveCN109767980AGood feature sizeGood feature size uniformitySemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringPolymer

The invention provides a super junction and a manufacturing method thereof, and a deep trench manufacturing method of the super function. In the deep trench manufacturing method of the super function,a mask layer formed on a substrate or formed on an epitaxial layer of the substrate is subjected to etching through high-molecular polymer gas to form a hard mask plate, the substrate or the epitaxial layer formed on the substrate is etched step by step through the hard mask plate under stepped increasing gas pressure, and thus, a deep trench is formed on the substrate or the epitaxial formed onthe substrate. By the deep trench manufacturing method provided by the invention, the deep trench with relatively good characteristic size uniformity, depth uniformity and angle uniformity can be formed.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Formation method of semiconductor structure

ActiveCN107039334BGood sidewall morphologyExcellent etch resistanceSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor structureDielectric layer

A method for forming a semiconductor structure, comprising: forming a first opening in a dielectric layer, the first opening spanning an adjacent gate structure; forming a first mask layer on the sidewall surface of the first opening, and the first mask layer The film layer spans the adjacent gate structure; a sacrificial layer filling the first opening is formed on the surface of the first mask layer, and the material etch resistance of the first mask layer is greater than the material etch resistance of the sacrificial layer; A second mask layer with a second opening is formed on the surface of the dielectric layer, the surface of the sacrificial layer and the surface of the first mask layer, and the second opening spans the sacrificial layer and the first mask layer; as a mask, etch the dielectric layer exposed by the sacrificial layer and the first mask layer along the second opening, and form discrete contact holes in the dielectric layer between adjacent gate structures; plug. The invention improves the position accuracy and shape accuracy of the side wall of the formed contact hole, thereby improving the performance of the formed semiconductor structure.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Method for forming semiconductor device

ActiveCN104952782BEasy to shapeGood lookingSemiconductor/solid-state device manufacturingComputational physicsSemiconductor

A formation method of a semiconductor device includes providing a substrate having a to-be-etched layer including a graph dense zone and a graph sparse zone; forming a first mask layer having sparse images on the surface of the graph sparse zone of the to-be-etched layer; forming a photo-etching layer covering the surface of the to-be-etched layer and the surface of the first mask layer; performing exposure development on the photo-etching layer and forming a second mask layer having dense images on the image dense zone of the to-be-etched layer and the surface of the first mask layer; etching the graph dense zone of to-be-etched layer by taking the second mask layer as a mask and etching the graph sparse zone of the to-be-etched layer by taking the second mask layer and the first mask layer as the mask until the surface of the substrate is exposed. By adopting the invention, problems caused by load effect during an etching process can be solved, so that the etching layer formed after the etching process of the graph sparse zone has a good appearance.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Manufacturing method of metal nanowire and semiconductor device and manufacturing method thereof

ActiveCN110571186BGood lookingImprove performanceSemiconductor/solid-state device detailsSolid-state devicesDevice materialMetal nanowires

The invention provides a method for manufacturing a metal nanowire, a semiconductor device and a method for manufacturing the same. After covering a patterned core layer and a surface of a semiconductor substrate with a metal layer, first form a side wall on the side wall of the metal layer, and then Under the protection of the sidewall, the metal layer on the top surface of the patterned core layer and the surface of the semiconductor substrate outside the sidewall is removed, thereby forming an L-shaped structure sandwiched between the patterned core layer and the sidewall. The metal nanowires have better sidewall morphology and higher thickness uniformity, thereby improving device performance and product yield.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Formation method of three-dimensional memory step structure

ActiveCN109411474BGood sidewall morphologyImproved sidewall morphologySolid-state devicesSemiconductor/solid-state device manufacturingOrageneOrganic polymer

The present invention relates to a method for forming a stepped structure of a three-dimensional memory, comprising: providing a substrate on which a stacked structure is formed, the stacked structure including a stepped area; forming a mask layer on the surface of the stepped area, and The mask layer includes at least a first sub-mask layer whose hardness is greater than that of the organic polymer layer; using the mask layer as a mask, step etching is performed on the step region of the stacked structure to form a step structure. The above method can improve the sidewall morphology of the formed step structure.

Owner:YANGTZE MEMORY TECH CO LTD

Self-Aligned Dual Patterning Method

ActiveCN103681293BMorphological influenceGood sidewall morphologySemiconductor/solid-state device manufacturingPhotoresistMaterials science

The invention provides a self-alignment duplex patterning method. The method comprises the following steps: providing a material layer to be etched, forming a sacrificial photoresist layer on the material layer to be etched, curing photoresist at the top and side wall of the sacrificial photoresist layer to form a cured photoresist casing, performing back-etching on the cured photoresist casing at the top of the sacrificial photoresist layer until an uncured inner sacrificial photoresist layer is exposed, forming a first mask pattern on the cured photoresist casing on the side wall of the inner sacrificial photoresist layer, and removing the uncured inner sacrificial photoresist layer. As a hard mask layer is not required to form, the process procedures are reduced, and the impact of the stress generated by the hard mask layer on the profile of the sacrificial photoresist layer is eliminated. Besides, the first mask pattern is formed by removing the top of the cured photoresist casing, the side wall of the sacrificial photoresist layer formed by the photolithographic process is smooth and perpendicular to the surface of the material layer to be etched, and the side wall of the finally-formed etched pattern has a better profile.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Formation method of resistive random access memory

ActiveCN106159082BPrevent adhesionAvoid etch contaminationElectrical apparatusStatic random-access memoryRandom access memory

The invention discloses a forming method of a resistance-type random access memory. The forming method comprises the following steps: using a hard mask layer with an opening as a mask, etching a top electrode layer with a first dry method etching technology until the surface of a dielectric material layer is exposed, wherein etching gas of the first dry method etching technology is CH4; continuously using the hard mask layer with the opening as the mask, etching the dielectric material layer with a second dry method etching technology until the surface of a bottom electrode layer is exposed, wherein etching gas of the second dry method etching technology is H2. According to the forming method, the etching technologies are prevented from causing etching pollution on the top electrode layer and the dielectric material layer, so that the side wall of the top electrode layer and the side wall of the dielectric material layer after etching are clean, and then the electrical property of the formed resistance-type random access memory is improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Semiconductor etching device and etching method for semiconductor structure

ActiveCN103021912BAvoid contaminationAvoid pollutionElectric discharge tubesSemiconductor/solid-state device manufacturingSemiconductor structureBlocking layer

Disclosed are a semiconductor etching device and an etching method of a semiconductor structure. The etching method includes: a etching process with a first bias power source is utilized to etch a to-be-etched material layer, and the first bias power source generates continuous bias power to form a first opening which does not expose a etching blocking layer; and then a etching process with a second bias power source is utilized to etch the first opening, and the second bias power source generates pulse bias power until the etching blocking layer is exposed to form a second opening. Due to the fact that the continuous bias power is utilized to form bias voltage for etching firstly, side wall appearance is good, and etching selection ratio to a photo layer is high. The continuous bias power is switched into pulse bias power to form bias voltage for etching in prior to exposure of the etching blocking layer, so that cuts are avoided from being formed at the side wall bottom, close to the etching blocking layer, of the to-be-etched material layer.

Owner:ADVANCED MICRO FAB EQUIP INC CHINA

Formation method of semiconductor structure

ActiveCN105762114BGood lookingUniform pore sizeSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor structureEngineering

Owner:SEMICON MFG INT (SHANGHAI) CORP

Formation method of semiconductor structure

ActiveCN106356330BShorten the timeAvoid secondary pollutionSemiconductor/solid-state device manufacturingSemiconductor structureDielectric layer

A forming method of a semiconductor structure comprises: providing a substrate, wherein a dielectric layer is formed at the surface of the substrate; etching to remove the dielectric layer of first thickness by means of first etching process, and forming a pre-opening in the dielectric layer; depositing a silicon layer at the bottom and sidewall surface of the pre-opening by means of depositing process; etching to remove the silicon layer at the bottom surface of the pre-opening by means of second etching process, and etching to remove the dielectric layer of second thickness below the pre-opening; repeating the depositing process and the second etching process until an opening running through the dielectric layer is formed, and exposing the bottom of the opening to the surface of the substrate; forming a conductive layer filling the opening. The shape of the sidewall of the formed opening is improved, breakthrough voltage of the semiconductor structure that is formed is improved, and the breakthrough problem of time related media is improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Formation method of resistive random access memory

ActiveCN105679932BPrevent adhesionAvoid etch contaminationElectrical apparatusStatic random-access memoryRandom access memory

The invention provides a forming method of a resistive random-access memory. The method comprises the steps as follows: a substrate is provided; a lower electrode layer is arranged in the substrate; the top part of the lower electrode layer is flush with the surface of the substrate; a dielectric material layer is formed on the surface of the substrate; an upper electrode layer is formed on the surface of the dielectric material layer; a hard mask layer is formed on the surface of the upper electrode layer; the hard mask layer is patterned; an opening for exposing the upper electrode layer is formed in the hard mark layer; with the hard mask layer with the opening as a mask, the upper electrode layer and the dielectric material layer are sequentially etched by a dry etching process until the surface of the substrate is exposed; an etching gas for the dry etching process is H2; the hard mask layer with the opening is removed. The etching pollution to the upper electrode layer and the dielectric material layer caused by the etching process is avoided; and the side wall of the etched upper electrode layer and the side wall of the dielectric material layer are clean, so that the electrical properties of the formed resistive random-access memory are improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Super junction and manufacturing method thereof, deep trench manufacturing method of super junction

ActiveCN109767980BGood feature sizeGood feature size uniformitySemiconductor/solid-state device manufacturingSemiconductor devicesOptoelectronicsHard mask

The invention provides a super junction and its manufacturing method, and a method for manufacturing a deep trench of a super junction. The method of manufacturing a deep trench of a super junction is formed on a substrate or formed on a substrate by a polymer gas pair. The mask layer on the epitaxial layer is etched to form a hard mask, and the substrate or the epitaxial layer formed on the substrate is etched step by step through the hard mask with stepwise increasing gas pressure, so that A deep trench is formed on the substrate or an epitaxial layer formed on the substrate. The invention can form deep grooves with better feature size uniformity, better depth uniformity and better angle uniformity.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Formation method of semiconductor structure

ActiveCN107039335BImprove electrical performanceImprove yieldSemiconductor/solid-state device manufacturingSemiconductor structureElectrical performance

The invention provides a formation method of a semiconductor structure. The formation method comprises the steps that a first mask layer crossing a dielectric layer between the adjacent gate structures is formed on the surface of the dielectric layer; a side wall layer is formed on the surface of the sidewall of the first mask layer on the surface of the dielectric layer between the adjacent gate structures; a second mask layer having an opening is formed on the surface of the first mask layer and the surface of the dielectric layer, and the opening crosses the first mask layer and the side wall layer; the dielectric layer exposed out of the side wall layer and the first mask layer is etched along the opening with the second mask layer acting as the mask until the surface of a substrate is exposed, and discrete contact holes are formed in the dielectric layer between the adjacent gate structures; the second mask layer and the first mask layer are removed; and conductive plugs fully filling in the contact holes are formed. The sidewall position accuracy and the shape accuracy of the formed contact holes are improved so as to enhance the electrical performance and the yield rate of the formed semiconductor structure.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Formation method of self-aligned double pattern

ActiveCN103839783BHigh hardnessGood sidewall morphologySemiconductor/solid-state device manufacturingHardnessDeposition process

Owner:SEMICON MFG INT (SHANGHAI) CORP

Method for manufacturing metal nanowire, semiconductor device, and method for manufacturing same

ActiveCN110571186AGood lookingImprove performanceSemiconductor/solid-state device detailsSolid-state devicesSemiconductorSemiconductor device

The invention provides a method for manufacturing a metal nanowire, a semiconductor device, and a method for manufacturing the same. After a patterned core layer and the surface of a semiconductor substrate are covered with a metal layer, a spacer is formed on the sidewall of the metal layer. Then, under the protection of the spacer, the metal layer on the top surface of the patterned core layer and the surface of the semiconductor substrate outside the spacer is removed, thereby forming an L-shaped metal nanowire sandwiched between the patterned core layer and the spacer. The metal nanowire has a good sidewall shape and high thickness uniformity, which can improve device performance and a product yield.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1