TSV Formation Method

A technology of through-silicon vias and morphology, which is applied in the direction of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems of easy leakage, poor interconnection structure quality of through-silicon vias, etc., and achieve the effect of slowing down the offset phenomenon

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

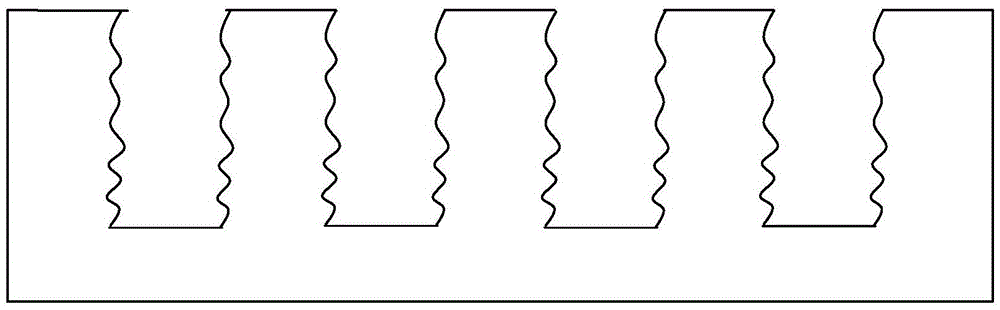

[0022] Research has been carried out on TSV products with serious leakage phenomena. After analyzing the cross-section of the TSV formed by the prior art with a scanning electron microscope, it is found that the morphology of the TSV formed by the existing process is as follows: figure 1 Shown is scalloped, serrated or corrugated to a greater degree, with higher roughness. Form an insulating layer on the surface of a shell-shaped, jagged or corrugated through-hole with high roughness, and then fill it with a conductive substance. The uniformity of the insulating layer is difficult to control, so that the conductive substance along the thinner position of the insulating layer Diffusion into the wafer, resulting in serious leakage of TSV products.

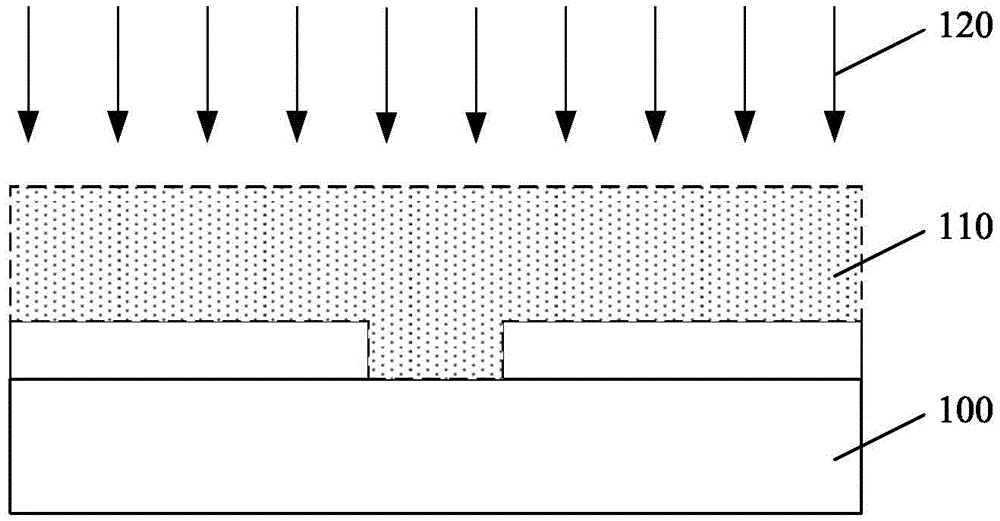

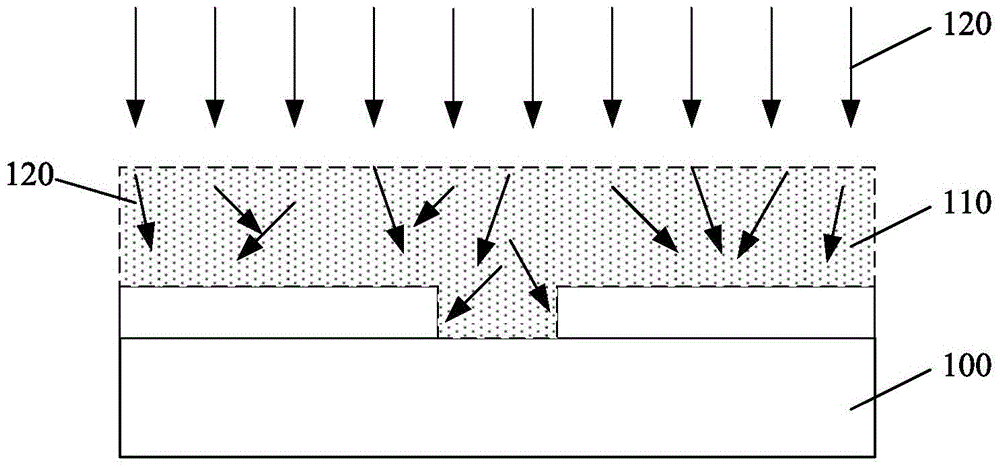

[0023] After further research on the process of forming the through-silicon vias, it was found that the reason for the formation of the surface of the above-mentioned corrugated through-holes is that in the formation process of the t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More