Formation method of semiconductor structure

A technology of semiconductor and gate structure, applied in the field of semiconductor structure formation, can solve the problems of deviation of design value, influence of conductive plug connection performance, influence of semiconductor structure performance, etc., to prevent the distance from being too close, good sidewall position accuracy accuracy and topographical accuracy, avoiding electrical connection problems

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] It can be seen from the background art that the performance of the semiconductor structure formed in the prior art needs to be improved.

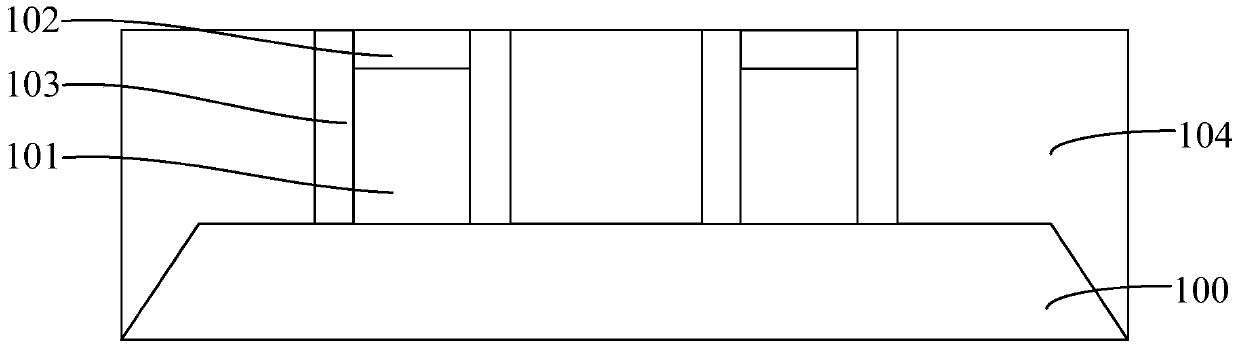

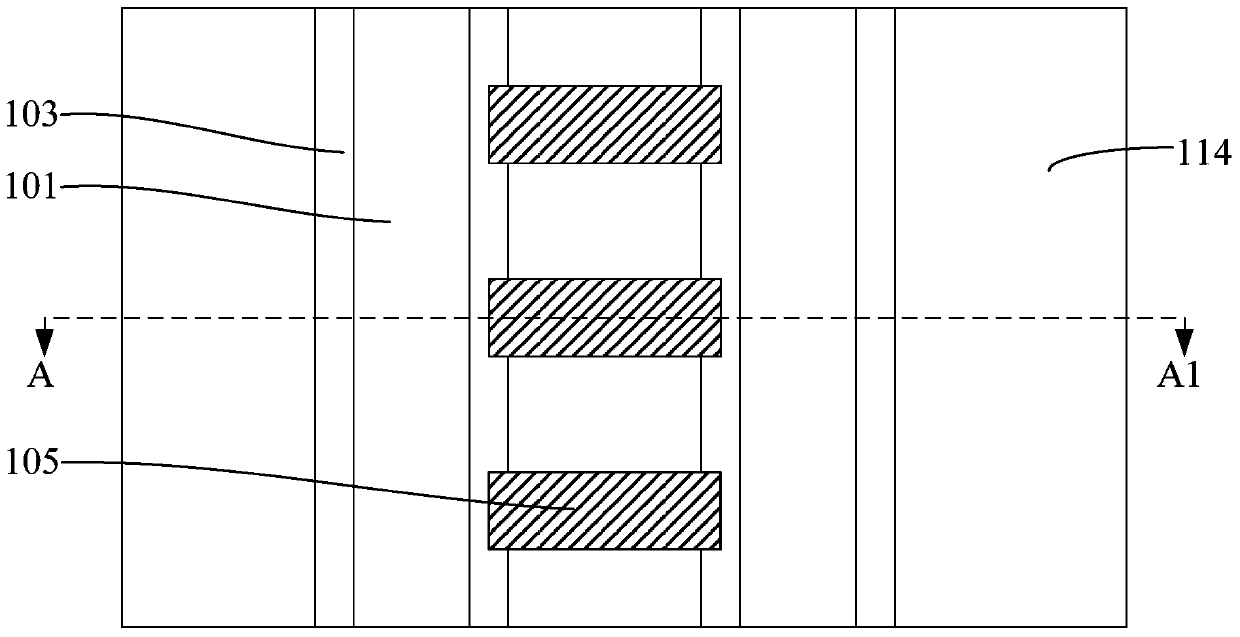

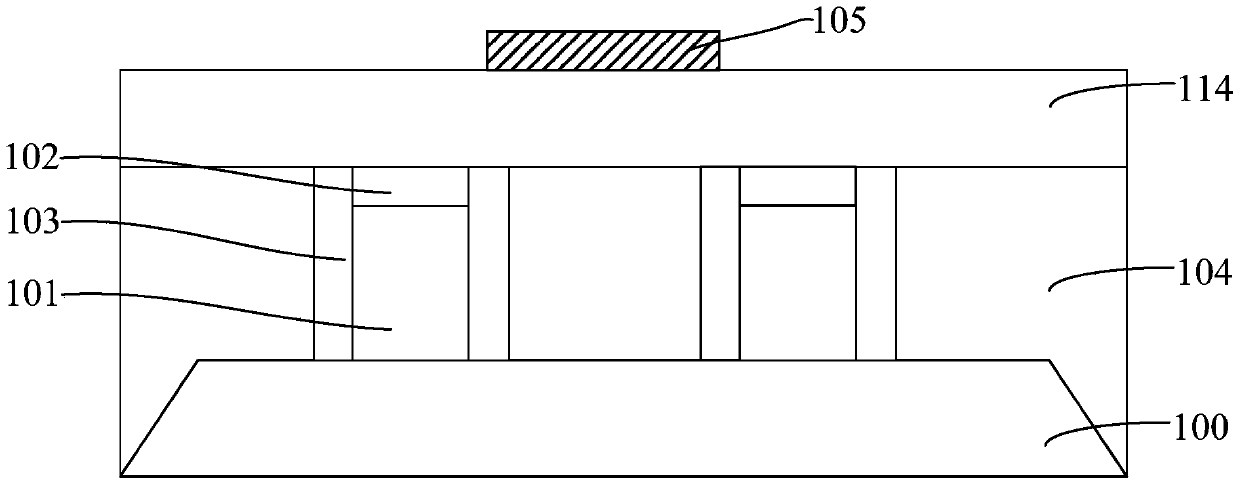

[0033] Figure 1 to Figure 7 It is a structural schematic diagram of a process of forming a semiconductor structure provided by an embodiment.

[0034] refer to figure 1 , provide a substrate 100, the surface of the substrate 100 forms a number of discrete gate structures, the gate structure includes: a gate 101, a hard mask layer 102 located on the surface of the gate 101, the gate structure also includes a cover gate The sidewall surface of the pole 101 and the sidewall 103 on the sidewall surface of the hard mask layer 102 . The surface of the substrate 100 is further formed with a first dielectric layer 104 covering the sidewall surface of the gate structure, and the top of the first dielectric layer 104 is flush with the top of the gate structure.

[0035] Wherein, the gate 101 includes a gate dielectric layer and a gate elec...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More