Patents

Literature

36 results about "Photoelectrochemical etching" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

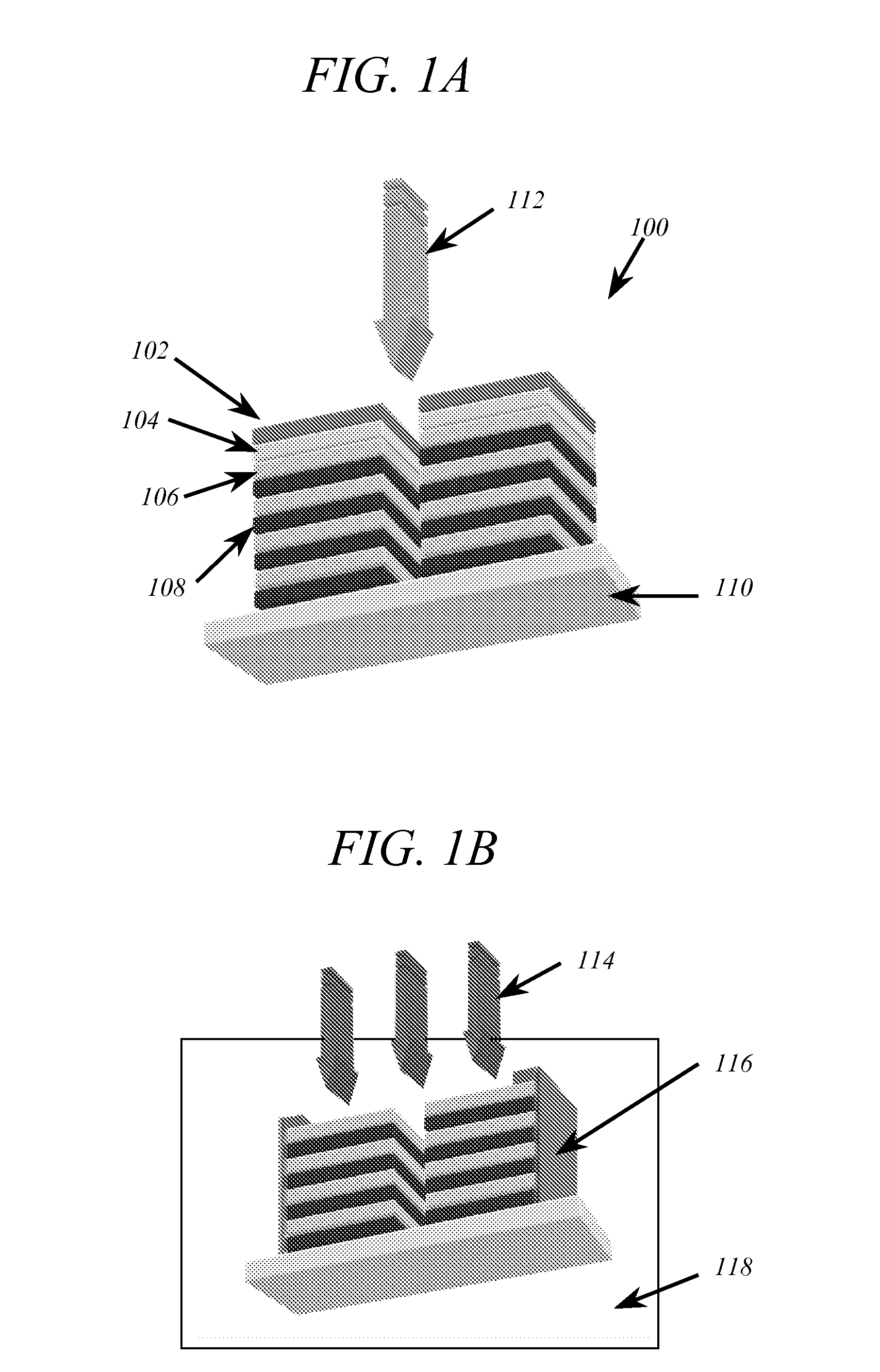

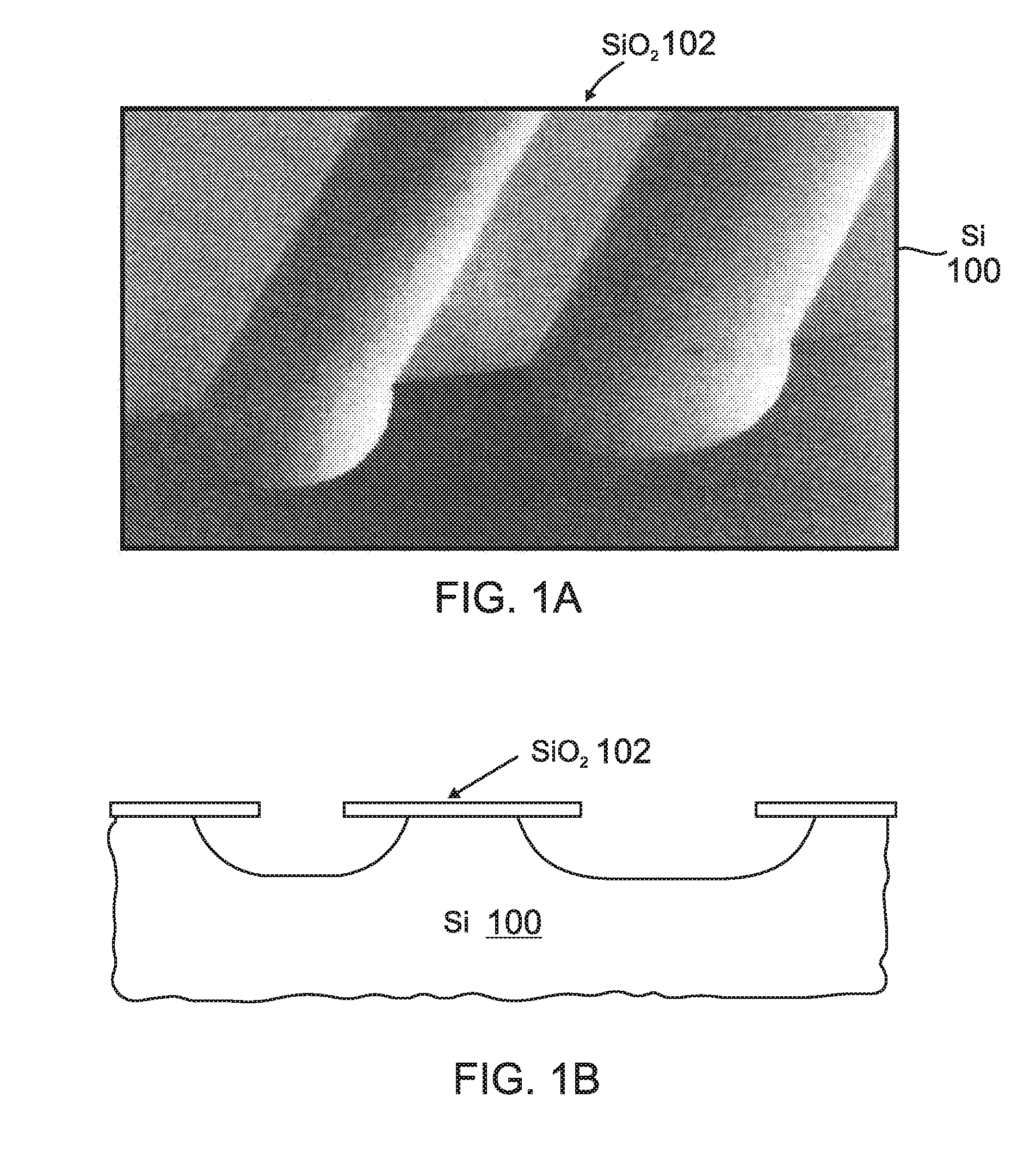

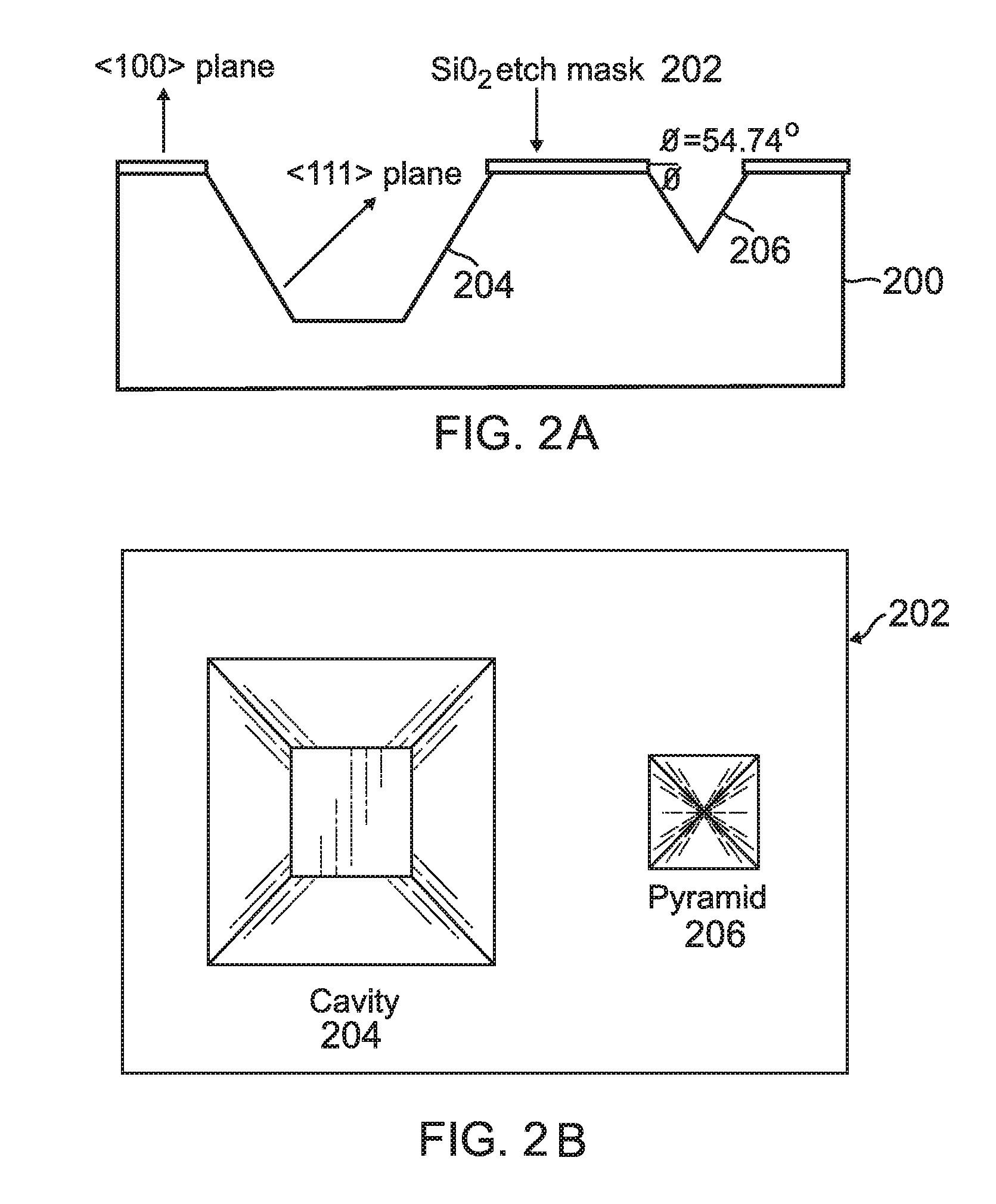

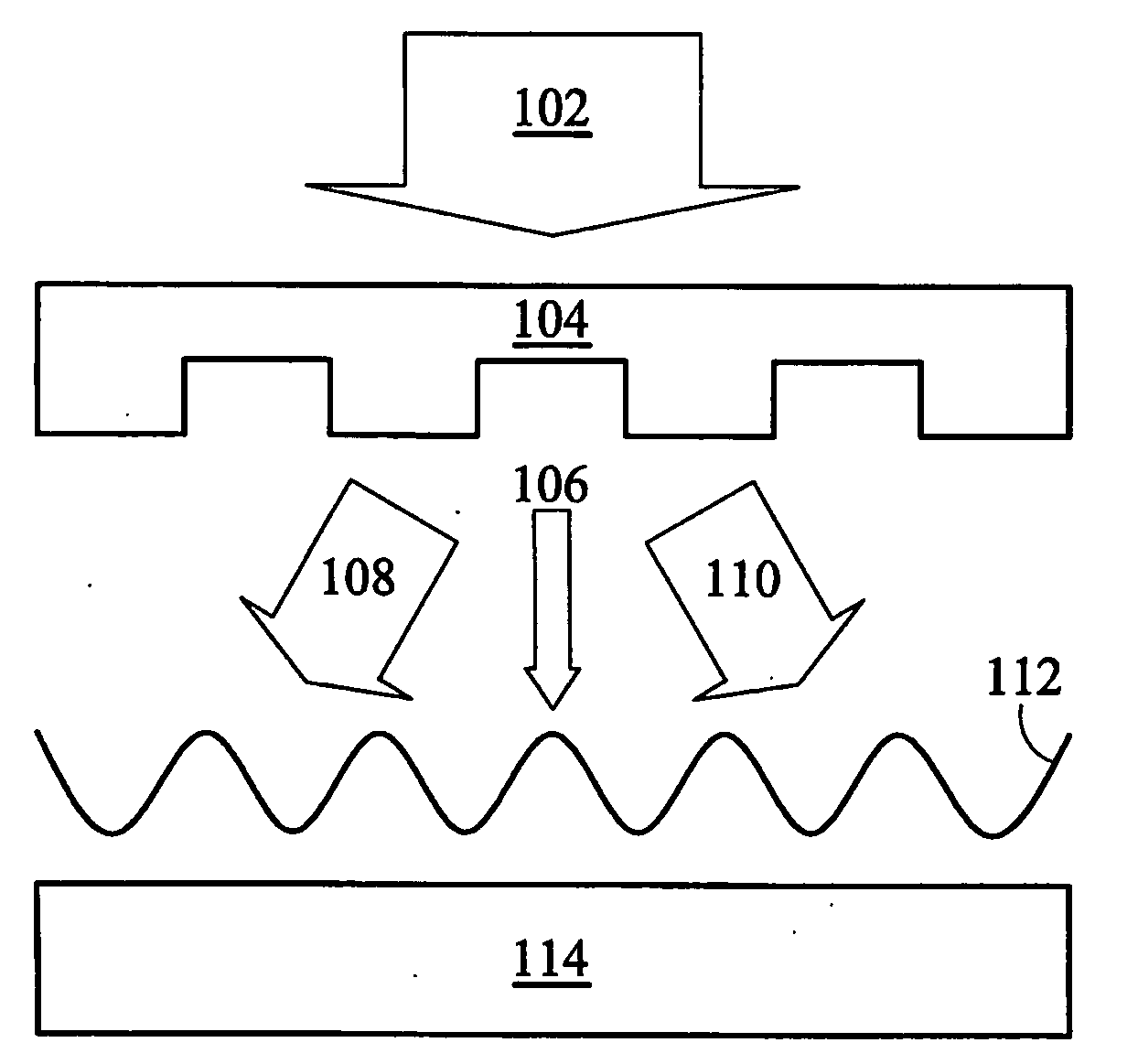

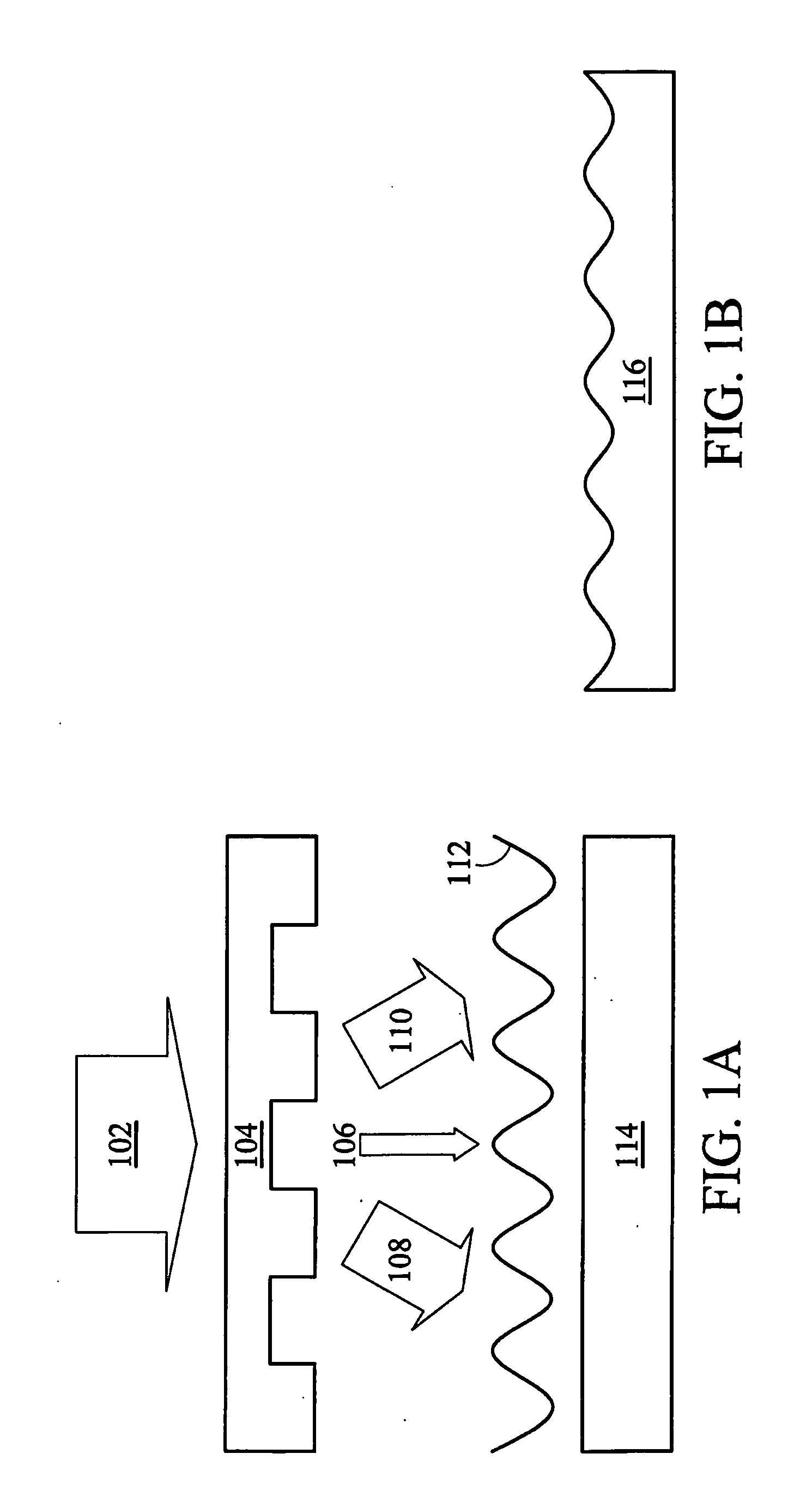

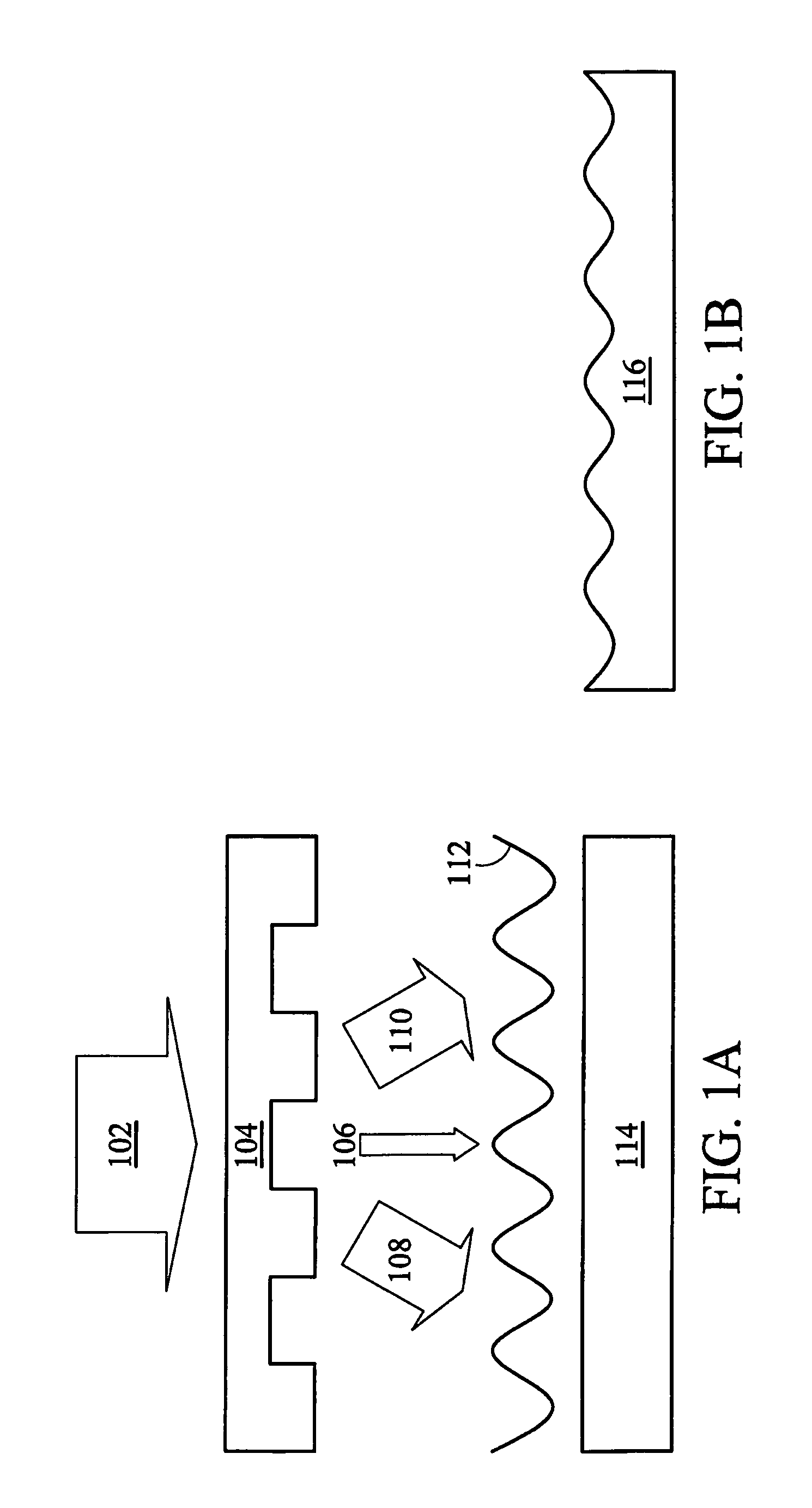

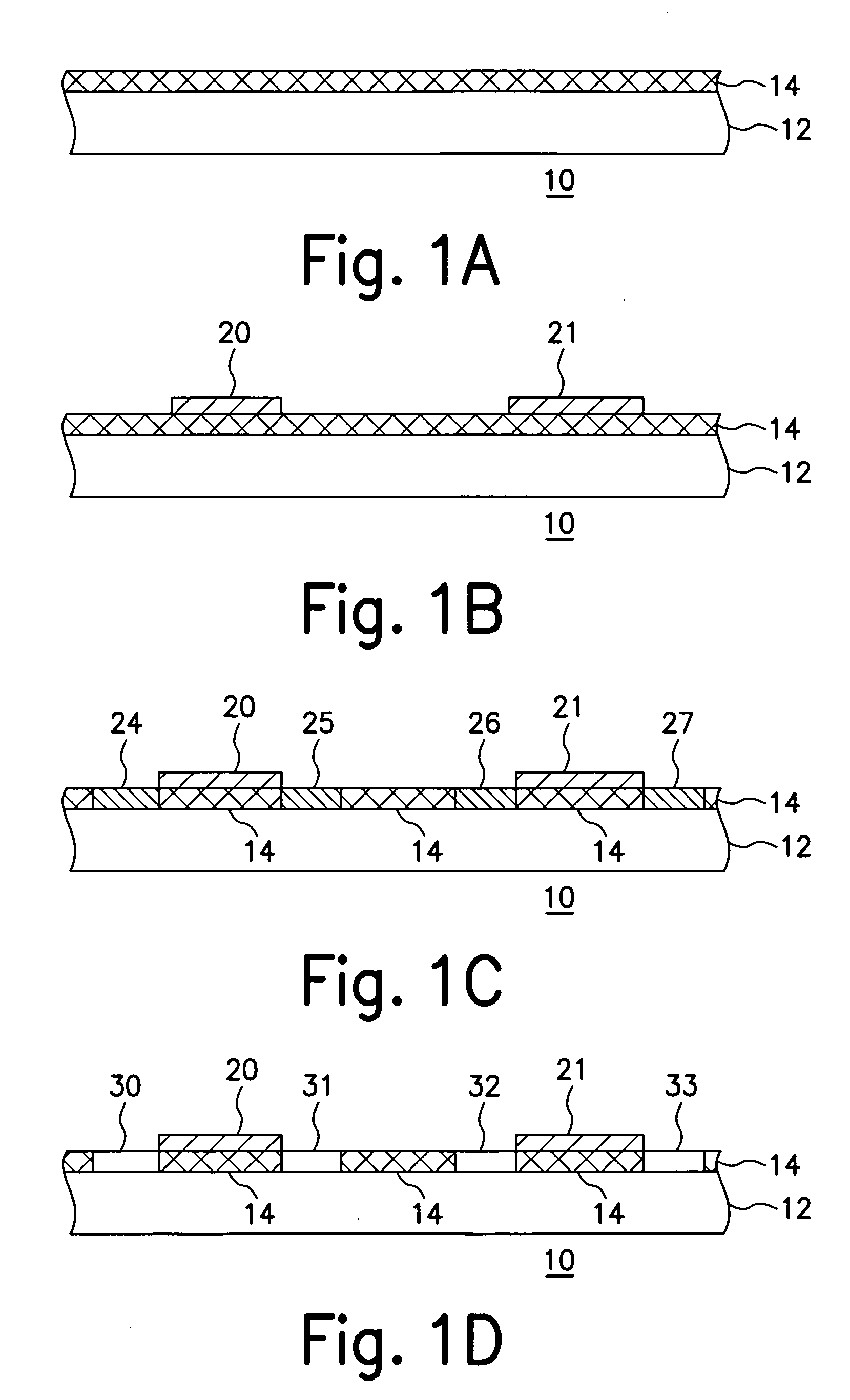

Direct patterning of silicon by photoelectrochemical etching

ActiveUS20050009374A1High resolutionComplex detailDecorative surface effectsAnalogue computers for chemical processesPhotoelectrochemical etchingSoft lithography

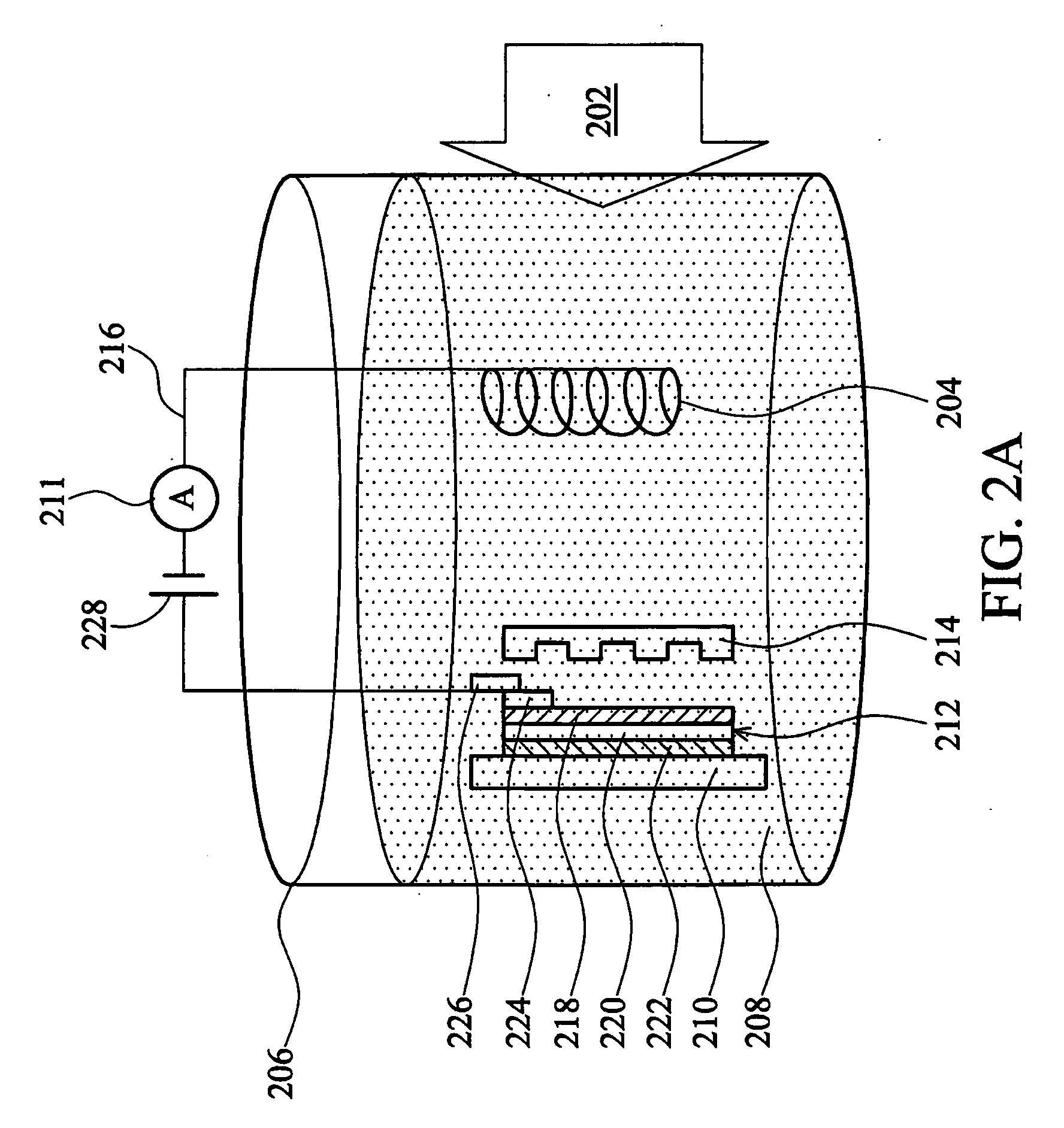

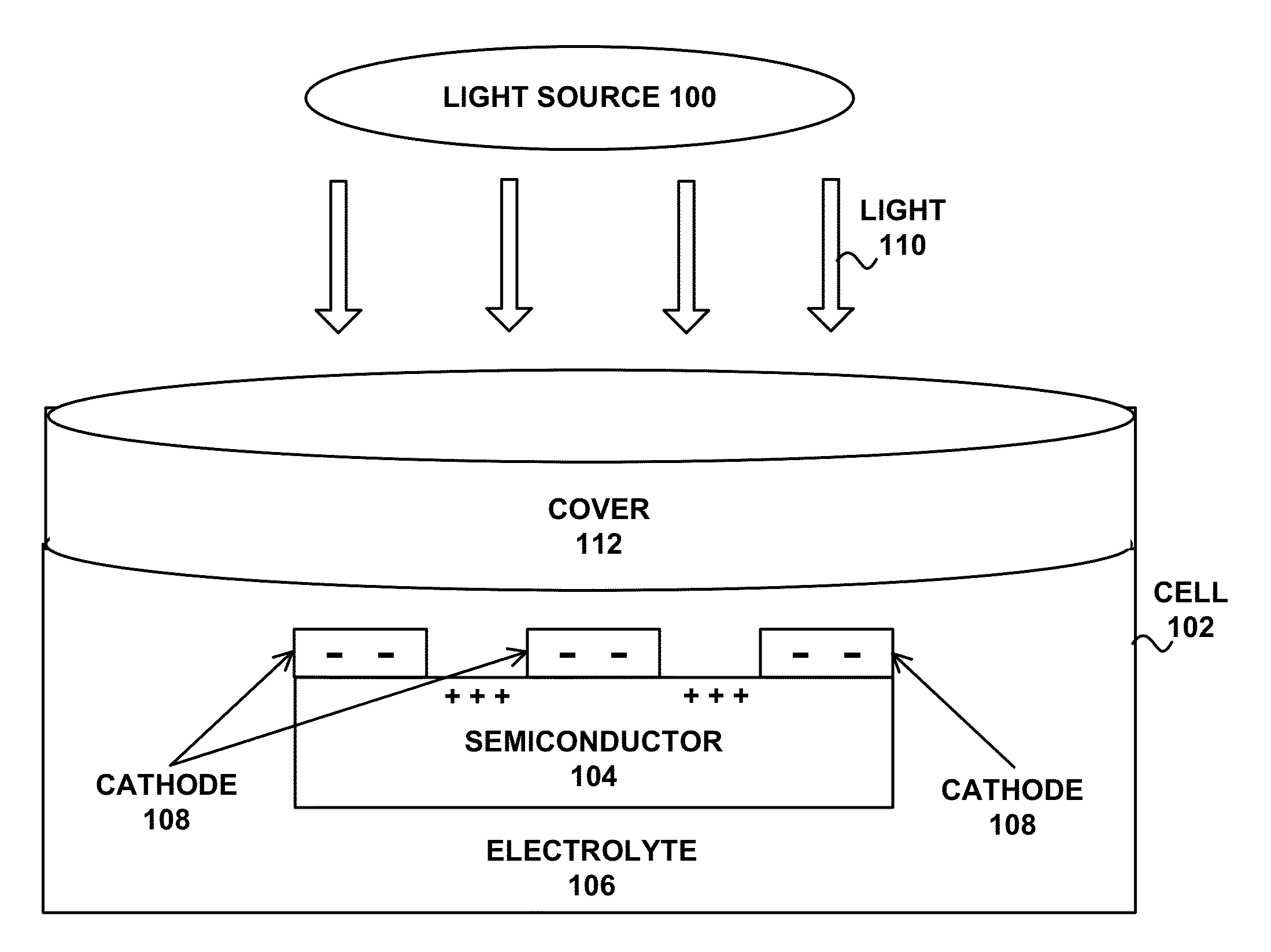

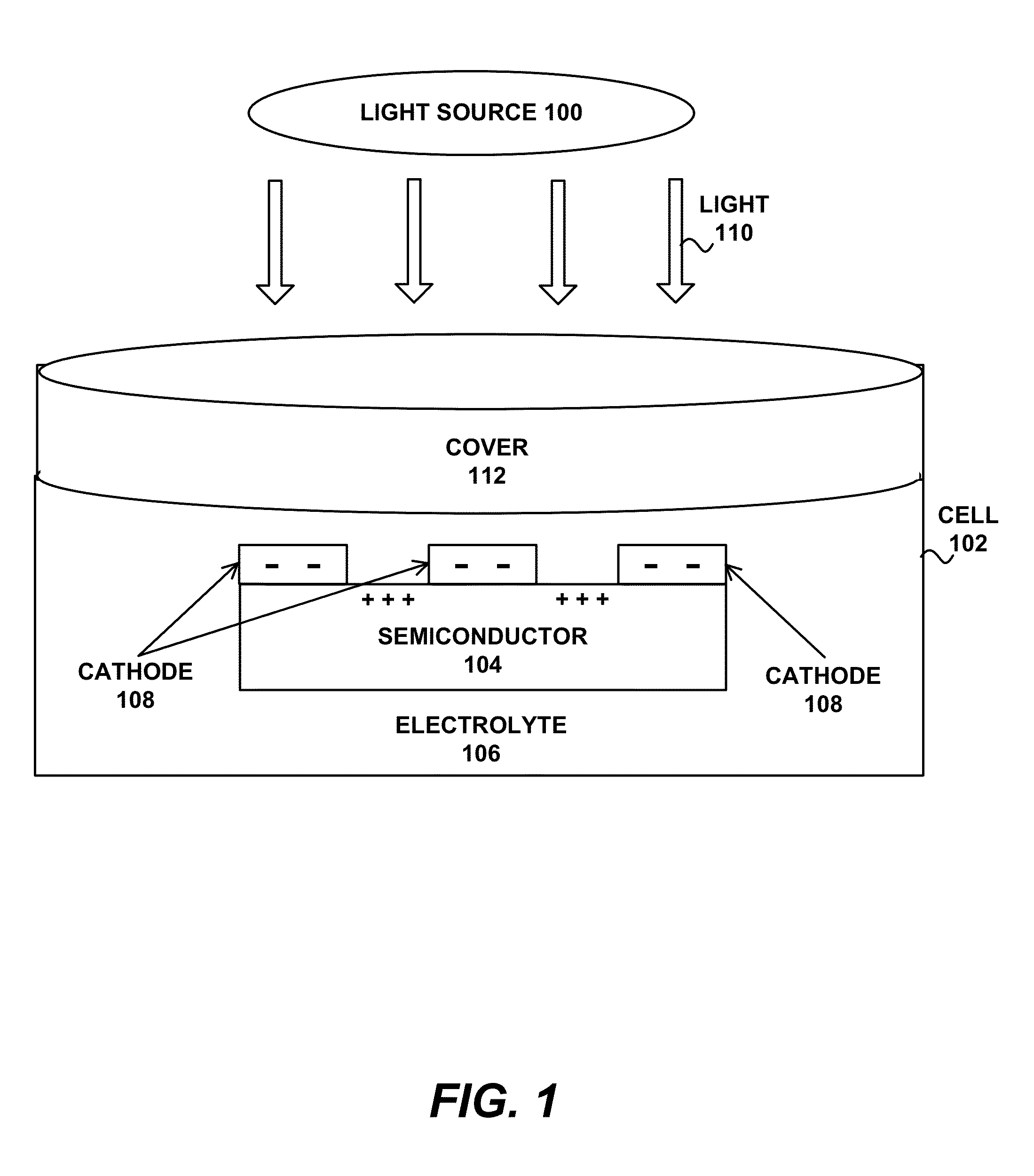

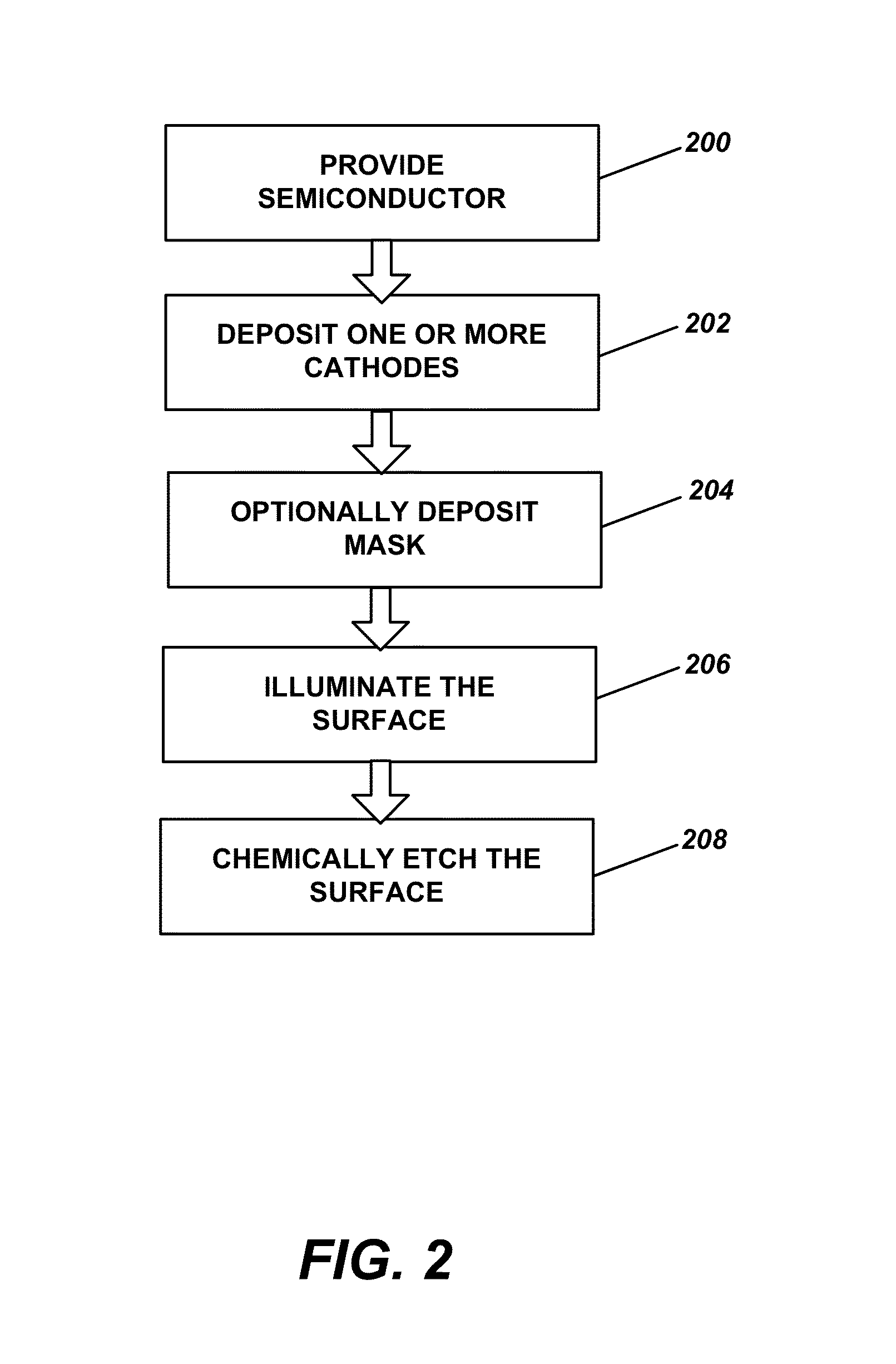

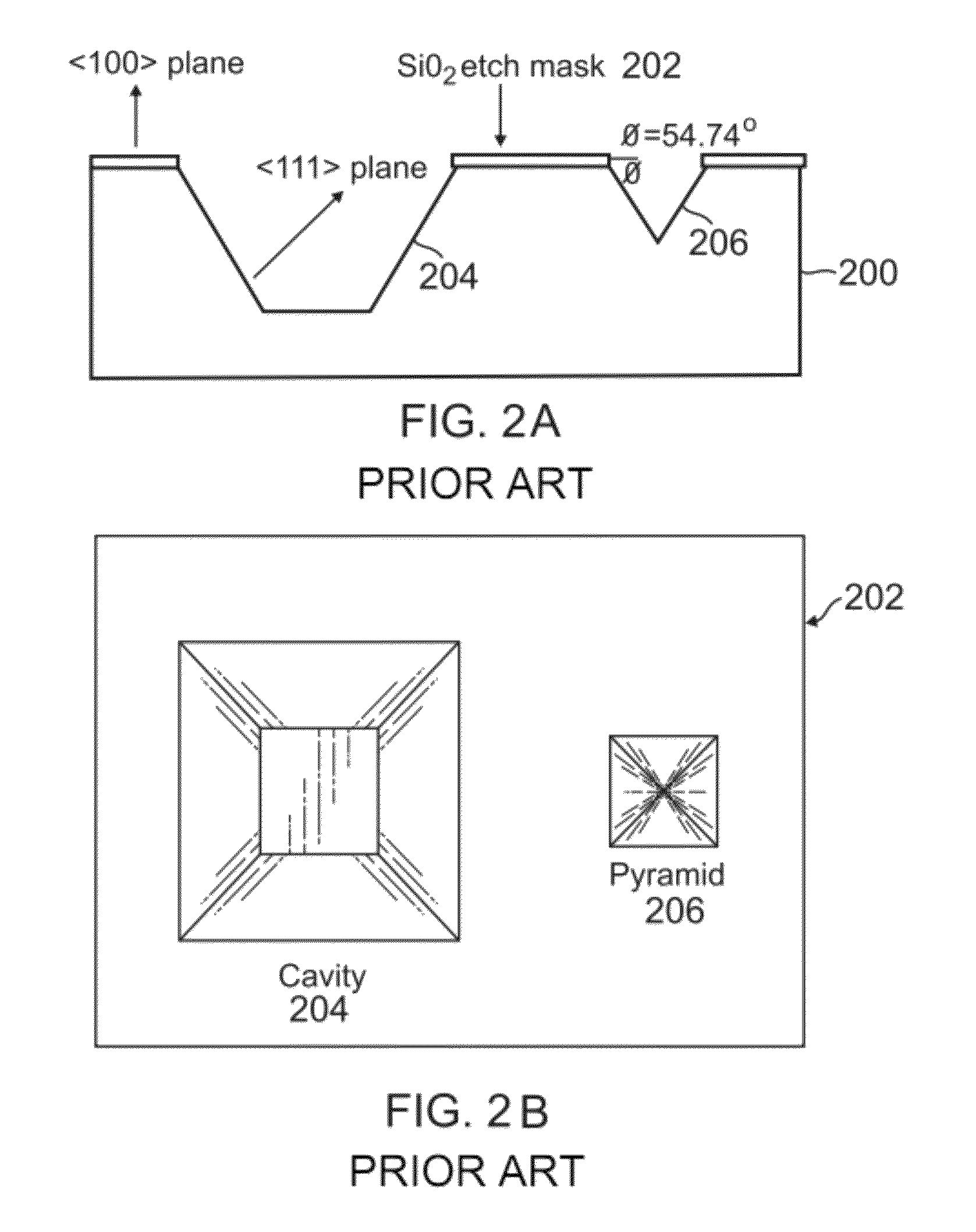

The invention is directed to methods for direct patterning of silicon. The invention provides the ability to fabricate complex surfaces in silicon with three dimensional features of high resolution and complex detail. The invention is suitable, for example, for use in soft lithography as embodiments of the invention can quickly create a master for use in soft lithography. In an embodiment of the invention, electrochemical etching of silicon, such as a silicon wafer, for example, is conducted while at least a portion of the silicon surface is exposed to an optical pattern. The etching creates porous silicon in the substrate, and removal of the porous silicon layer leaves a three-dimensional structure correlating to the optical pattern.

Owner:RGT UNIV OF CALIFORNIA

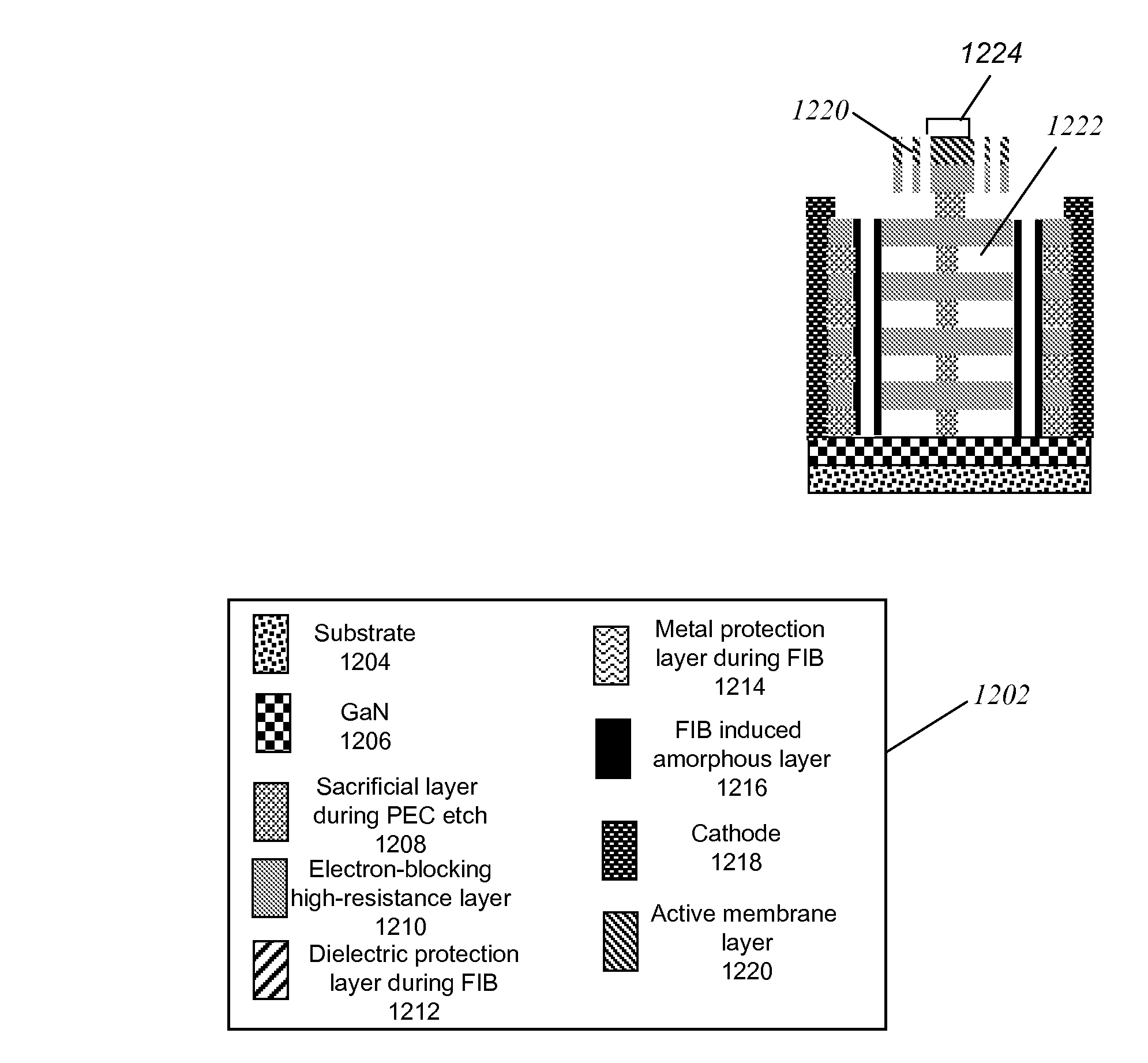

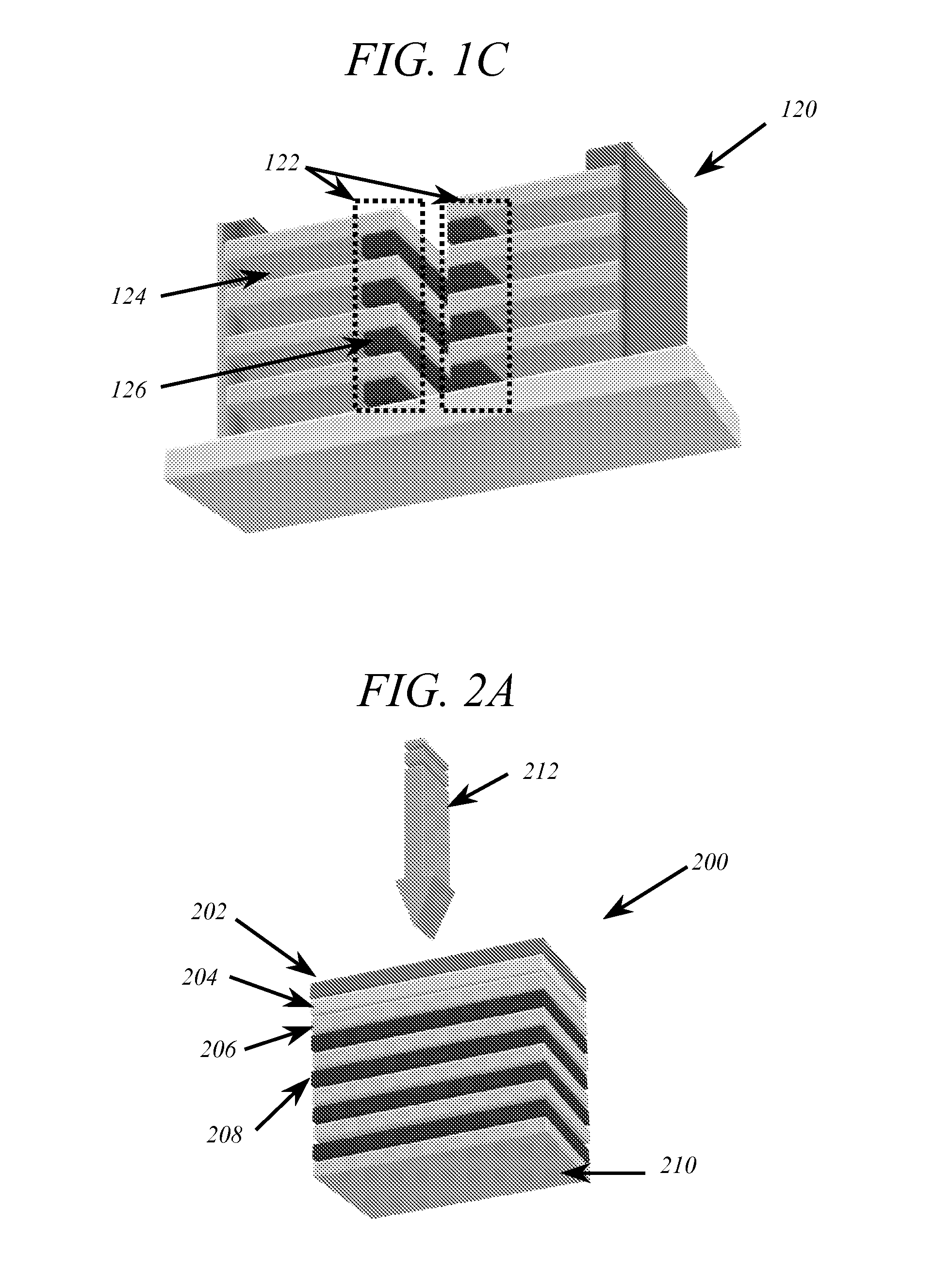

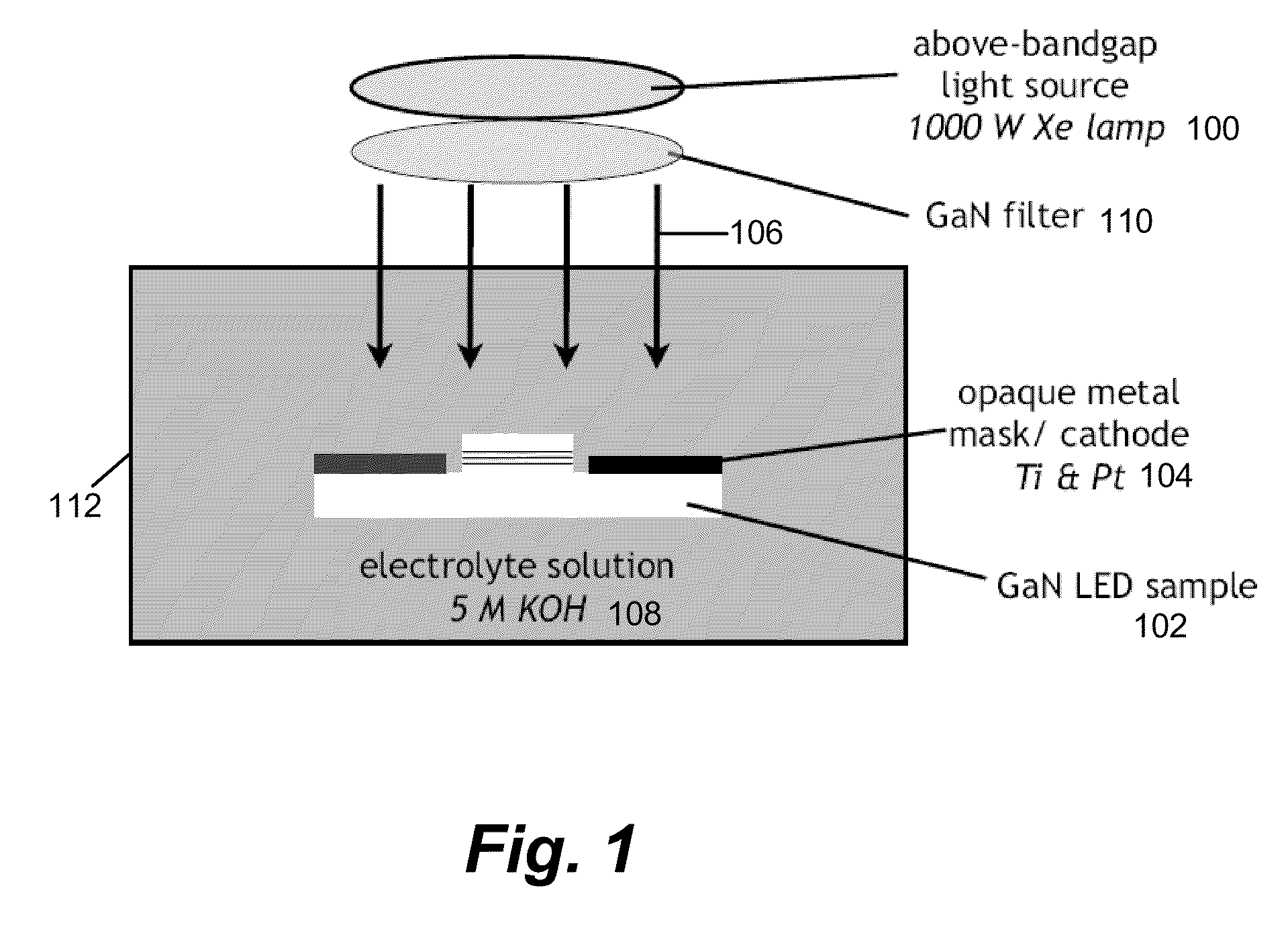

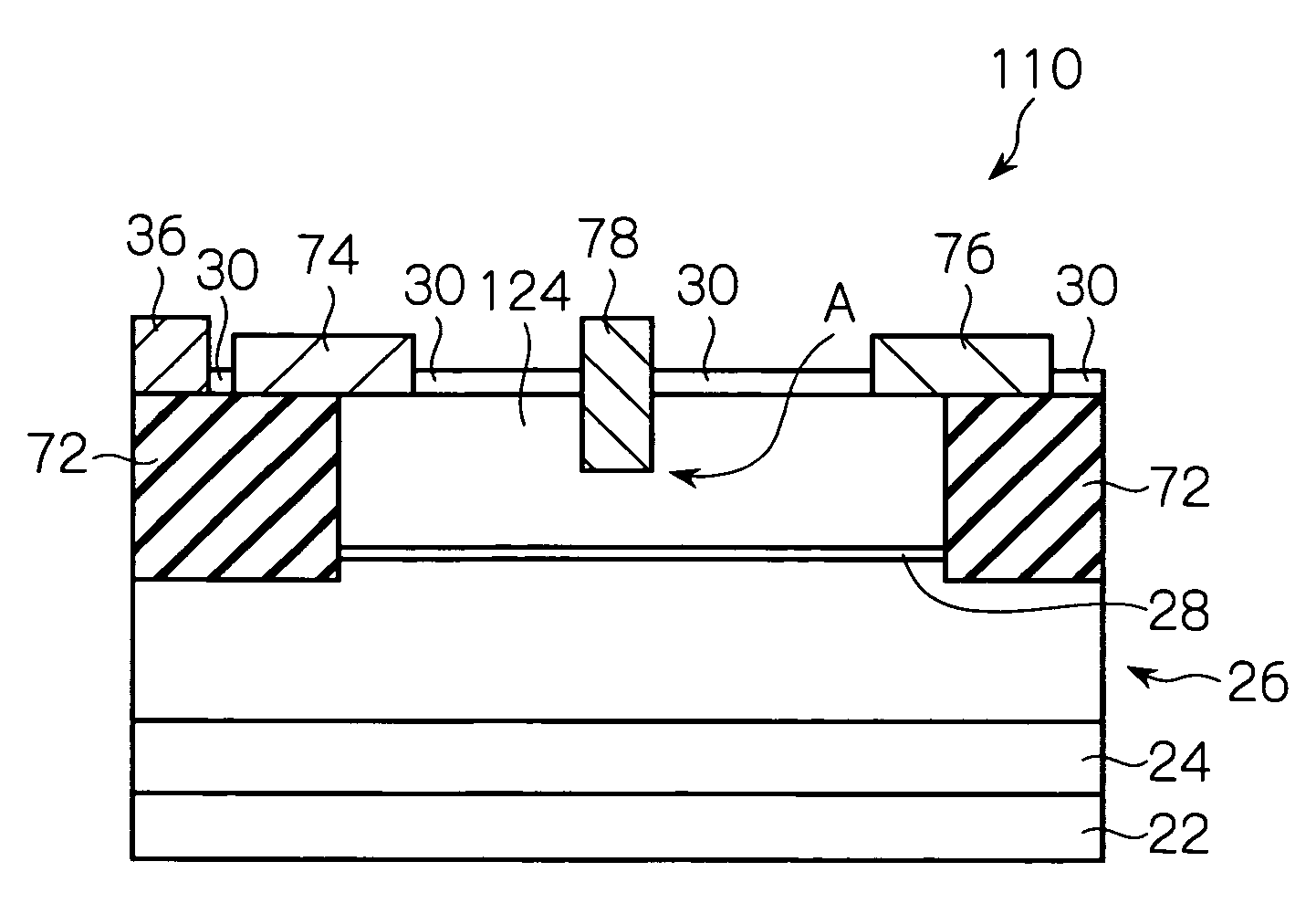

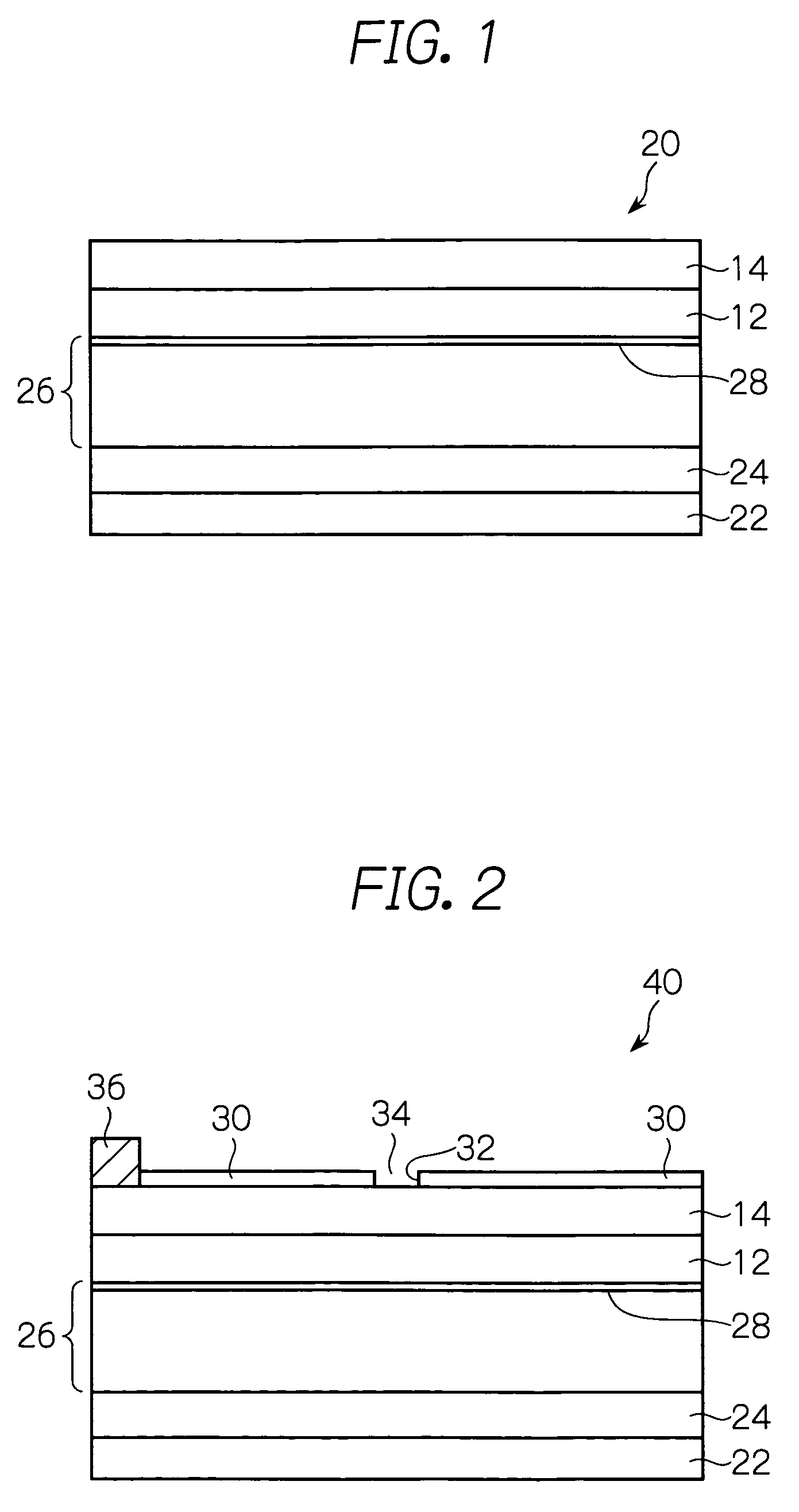

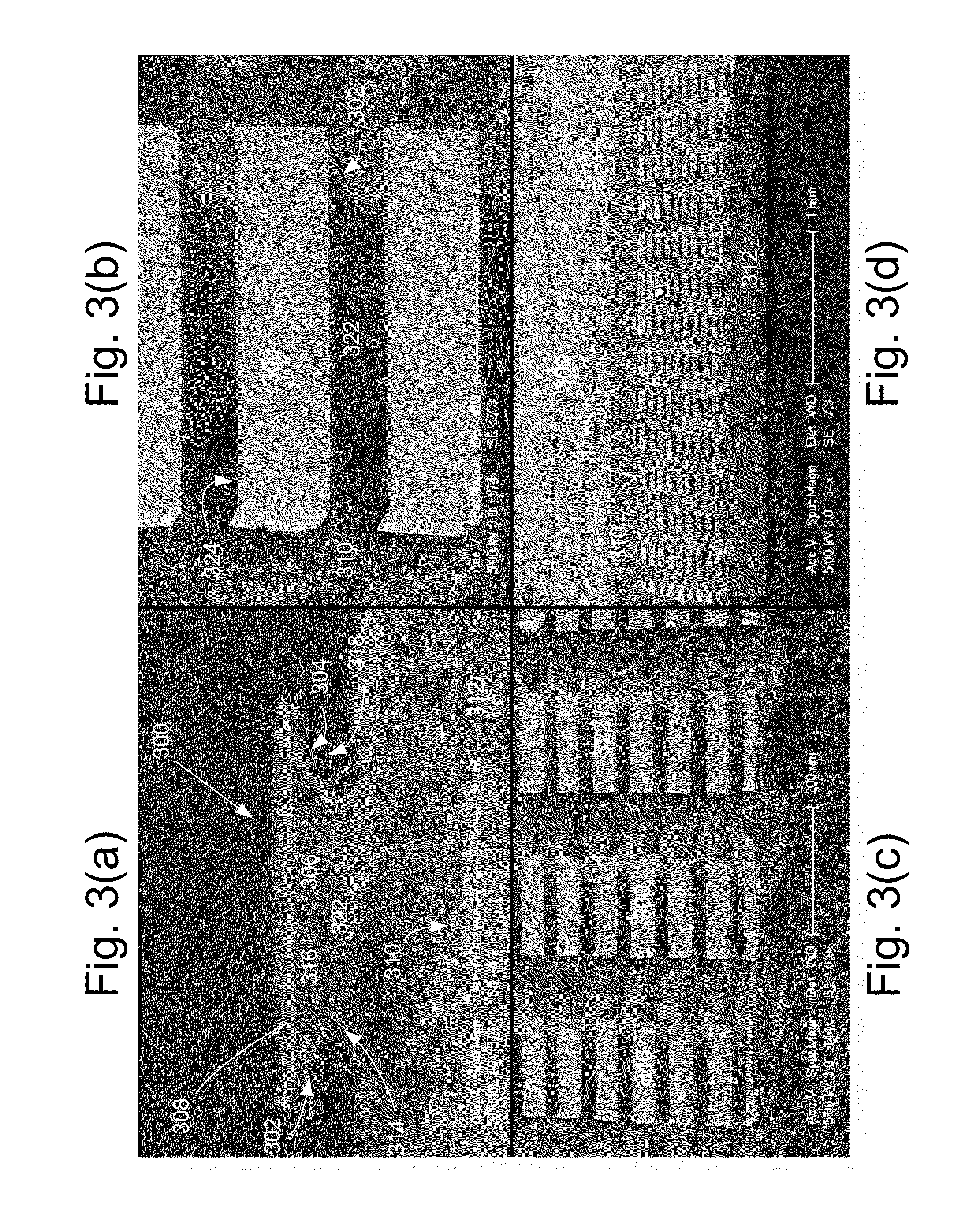

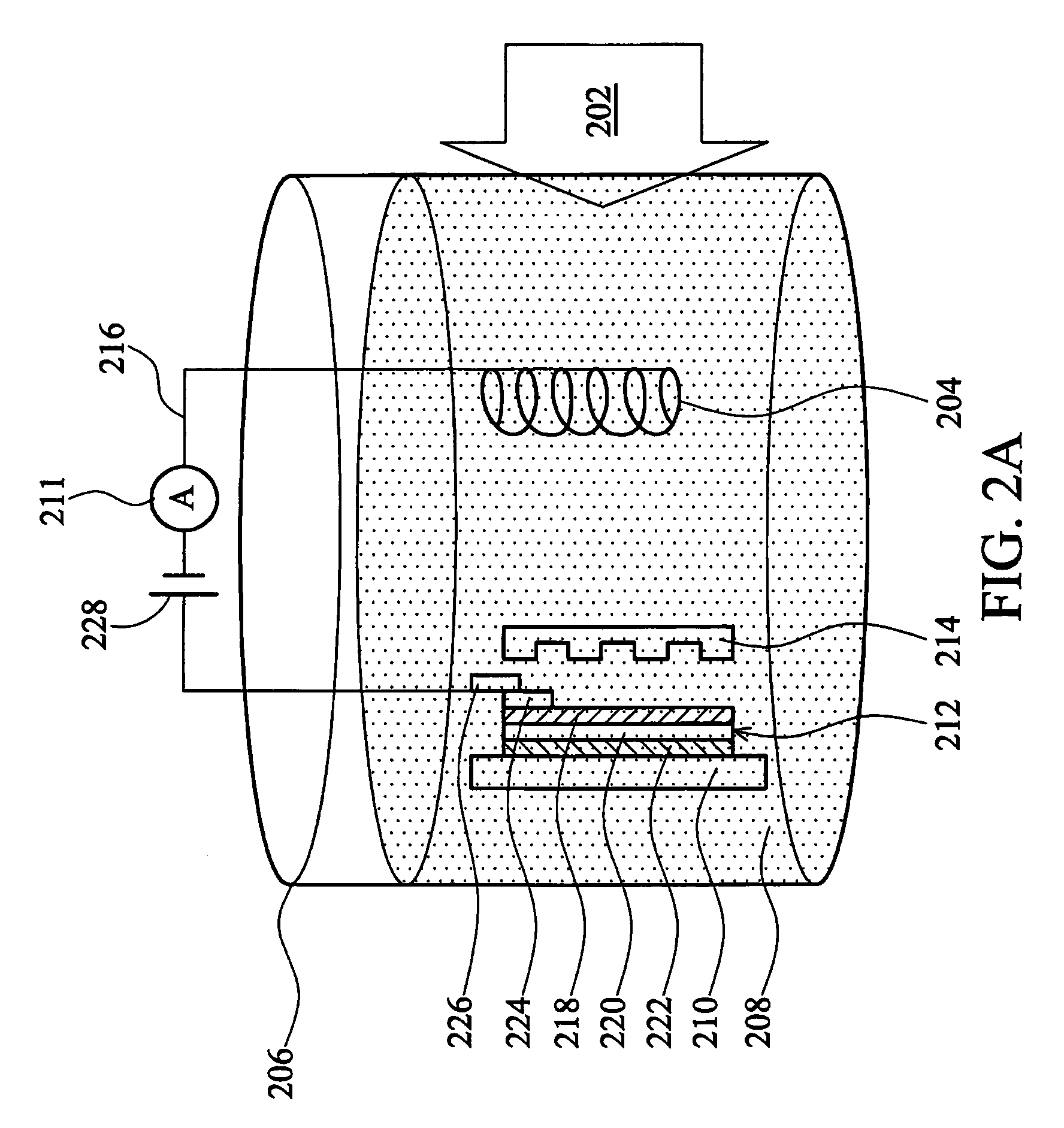

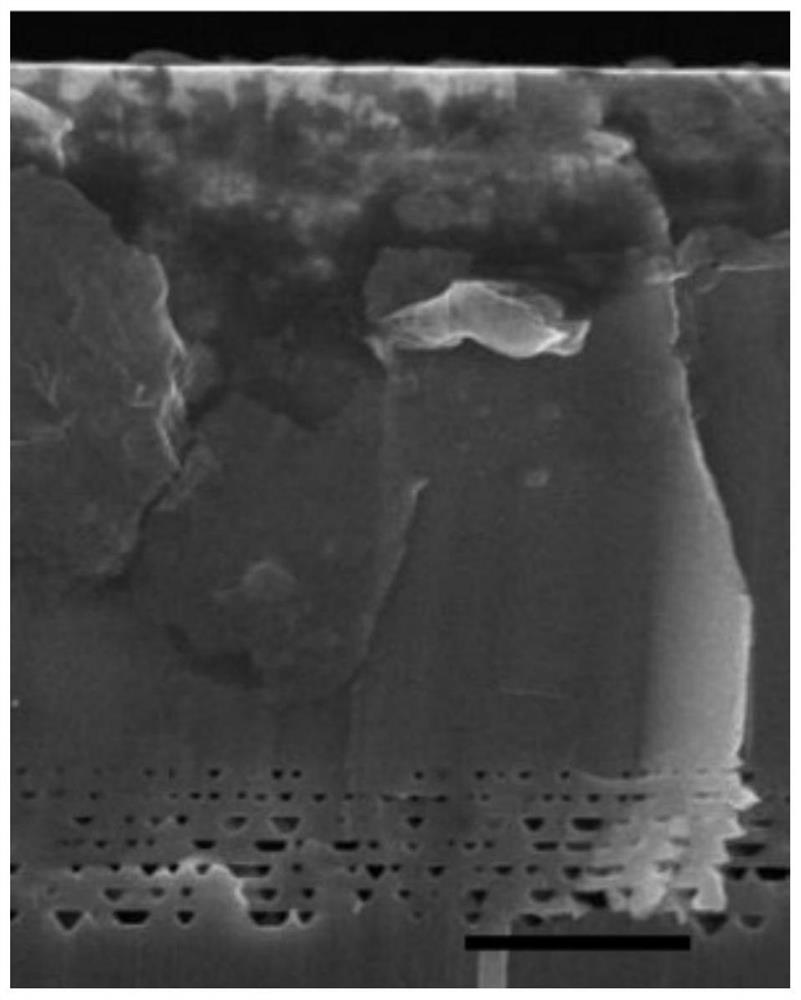

Ion beam treatment for the structural integrity of air-gap iii-nitride devices produced by the photoelectrochemical (PEC) etching

InactiveUS20080182420A1Avoid damageSemiconductor/solid-state device manufacturingSemiconductor devicesPhotoelectrochemical etchingPhotonics

A method for ensuring the structural integrity of III-nitride opto-electronic or opto-mechanical air-gap nano-structured devices, comprising (a) performing ion beam implantation in a region of the III-nitride opto-electronic and opto-mechanical air-gap nano-structured device, wherein the milling significantly locally modifies a material property in the region to provide the structural integrity; and (b) performing a band-gap selective photo-electro-chemical (PEC) etch on the III-nitride opto-electronic and opto-mechanical air-gap nano-structured device. The method can be used to fabricate distributed Bragg reflectors or photonic crystals, for example. The method also comprises the suitable design of distributed Bragg reflector (DBR) structures for the PEC etching and the ion-beam treatment, the suitable design of photonic crystal distributed Bragg reflector (PCDBR) structures for PEC etching and the ion-beam treatment, the suitable placement of protection layers to prevent the ion-beam damage to optical activity and PEC etch selectivity, and a suitable annealing treatment for curing the material quality after the ion-beam treatment.

Owner:RGT UNIV OF CALIFORNIA

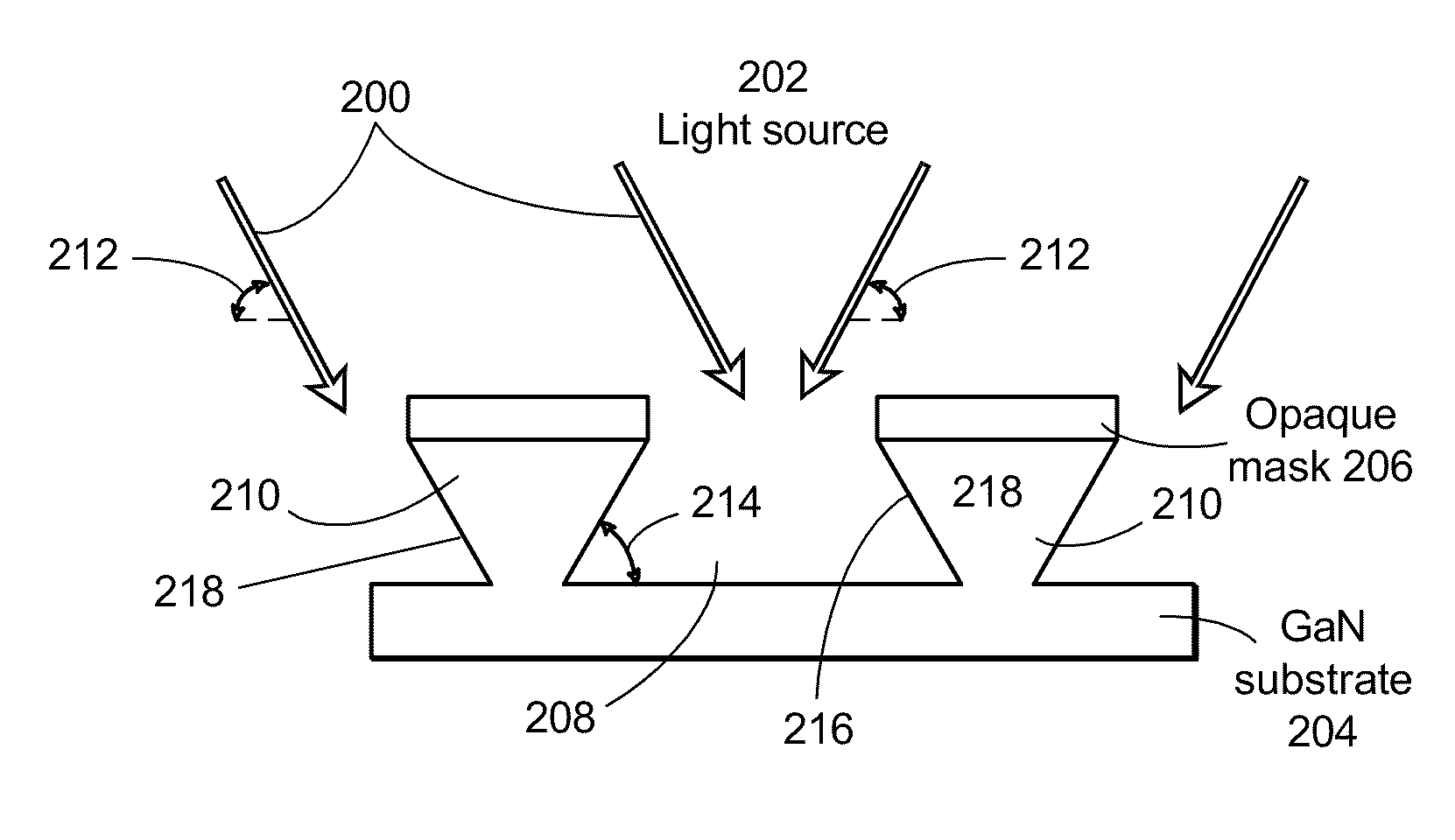

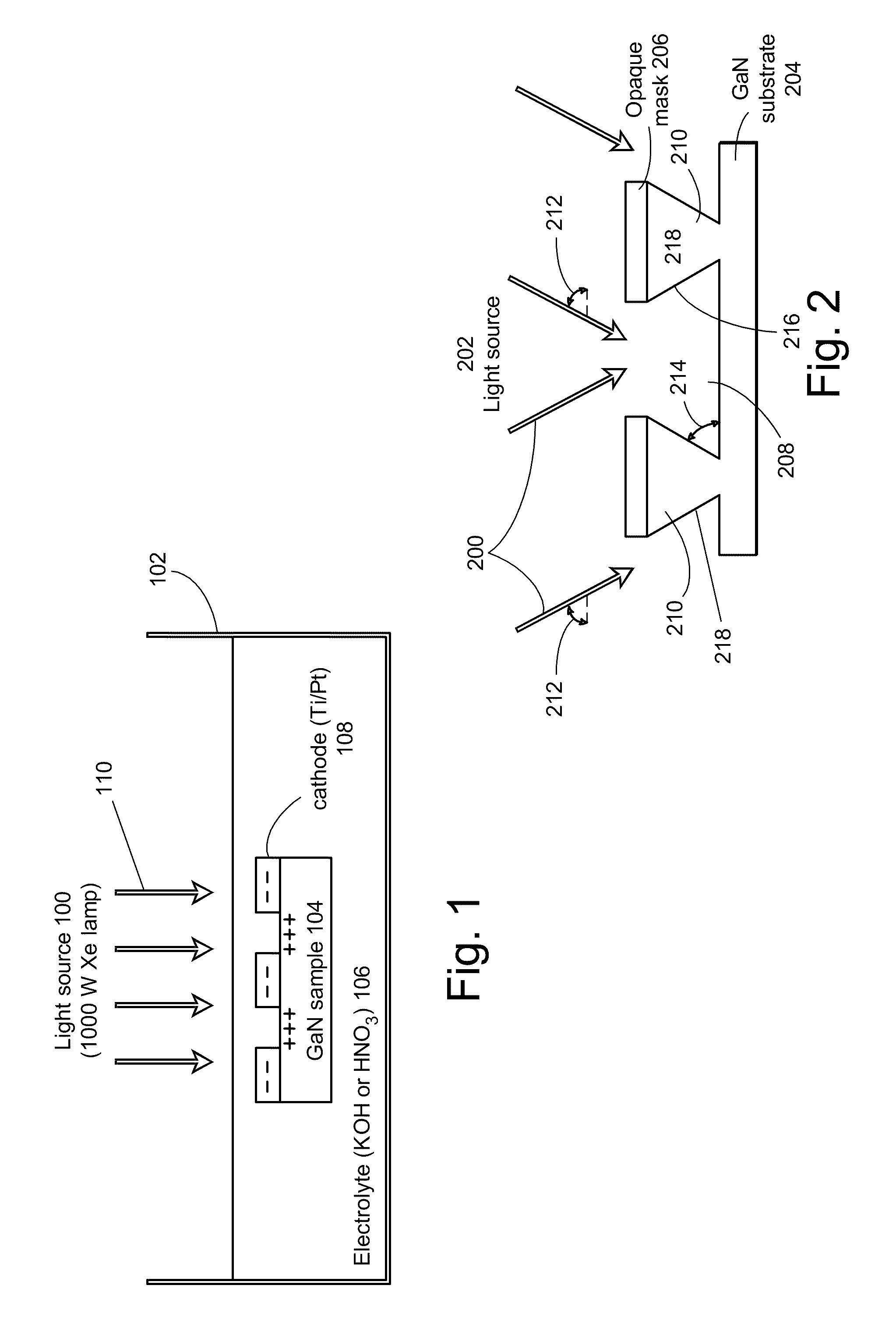

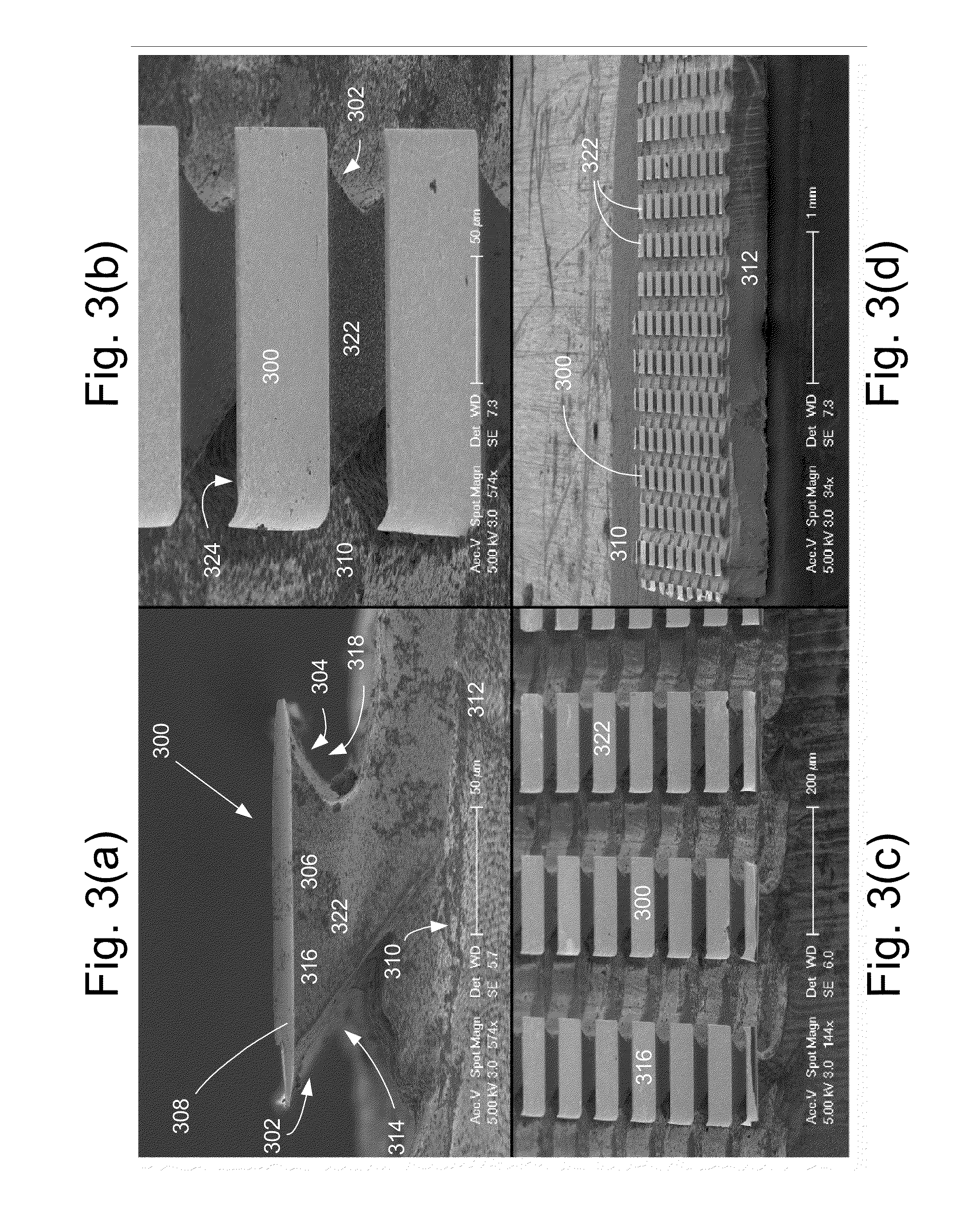

Photoelectrochemical etching for chip shaping of light emitting diodes

InactiveUS20100090240A1Speed up the extraction processControl roughnessSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor materialsPhotoelectrochemical etching

A photoelectrochemical (PEC) etch is performed for chip shaping of a device comprised of a III-V semiconductor material, in order to extract light emitted into guided modes trapped in the III-V semiconductor material. The chip shaping involves varying an angle of incident light during the PEC etch to control an angle of the resulting sidewalls of the III-V semiconductor material. The sidewalls may be sloped as well as vertical, in order to scatter the guided modes out of the III-V semiconductor material rather than reflecting the guided modes back into the III-V semiconductor material. In addition to shaping the chip in order to extract light emitted into guided modes, the chip may be shaped to act as a lens, to focus its output light, or to direct its output light in a particular way.

Owner:RGT UNIV OF CALIFORNIA

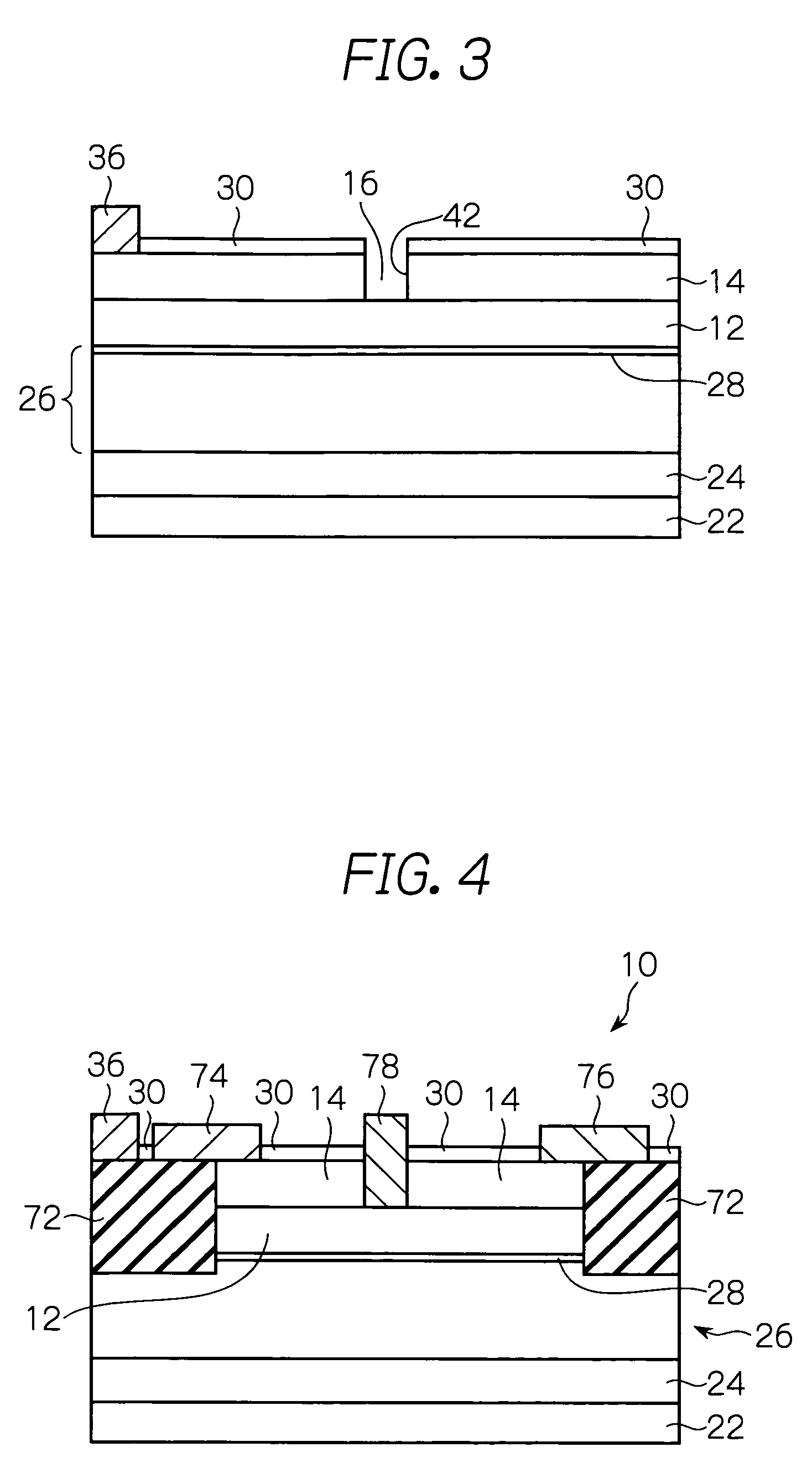

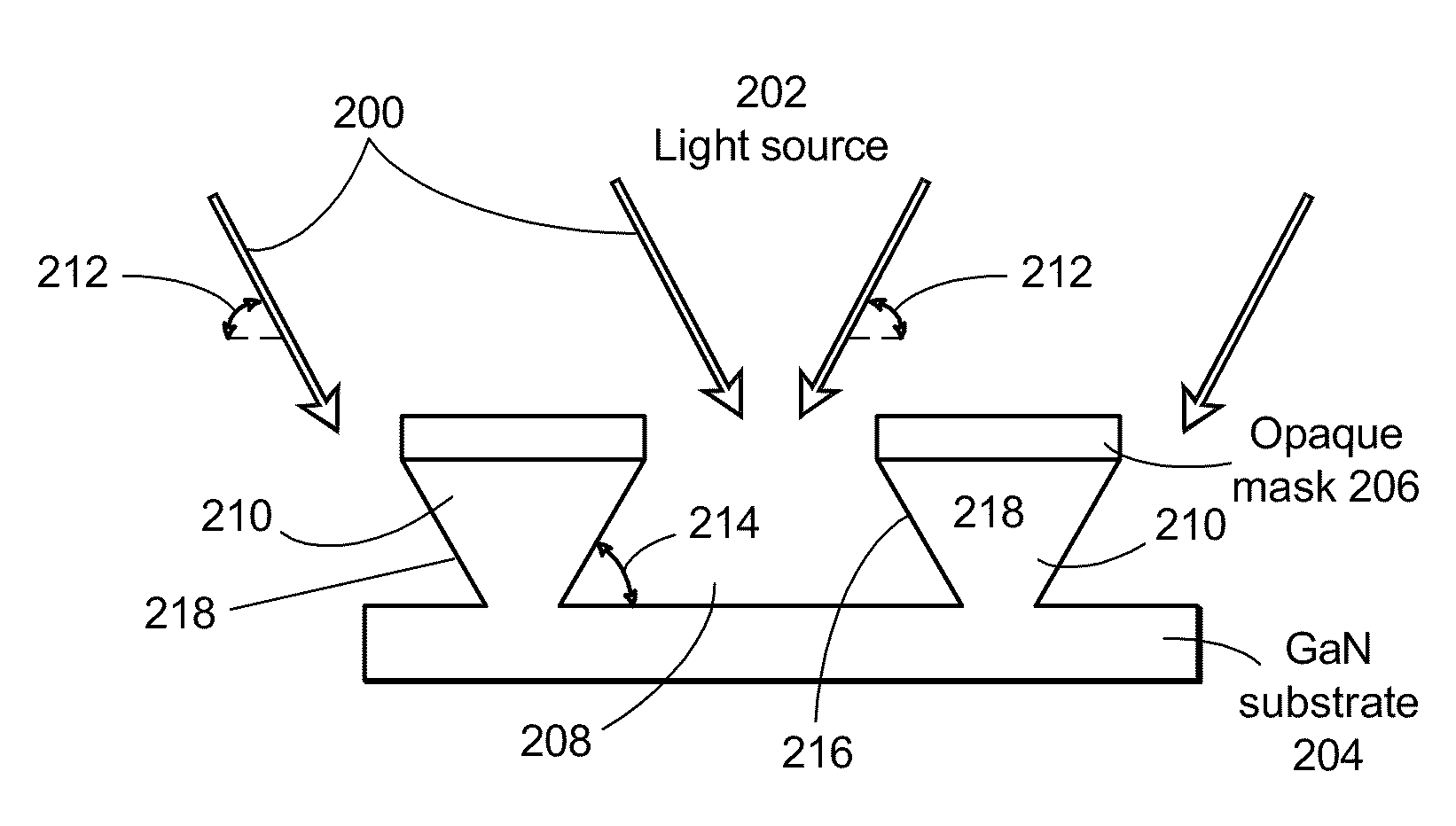

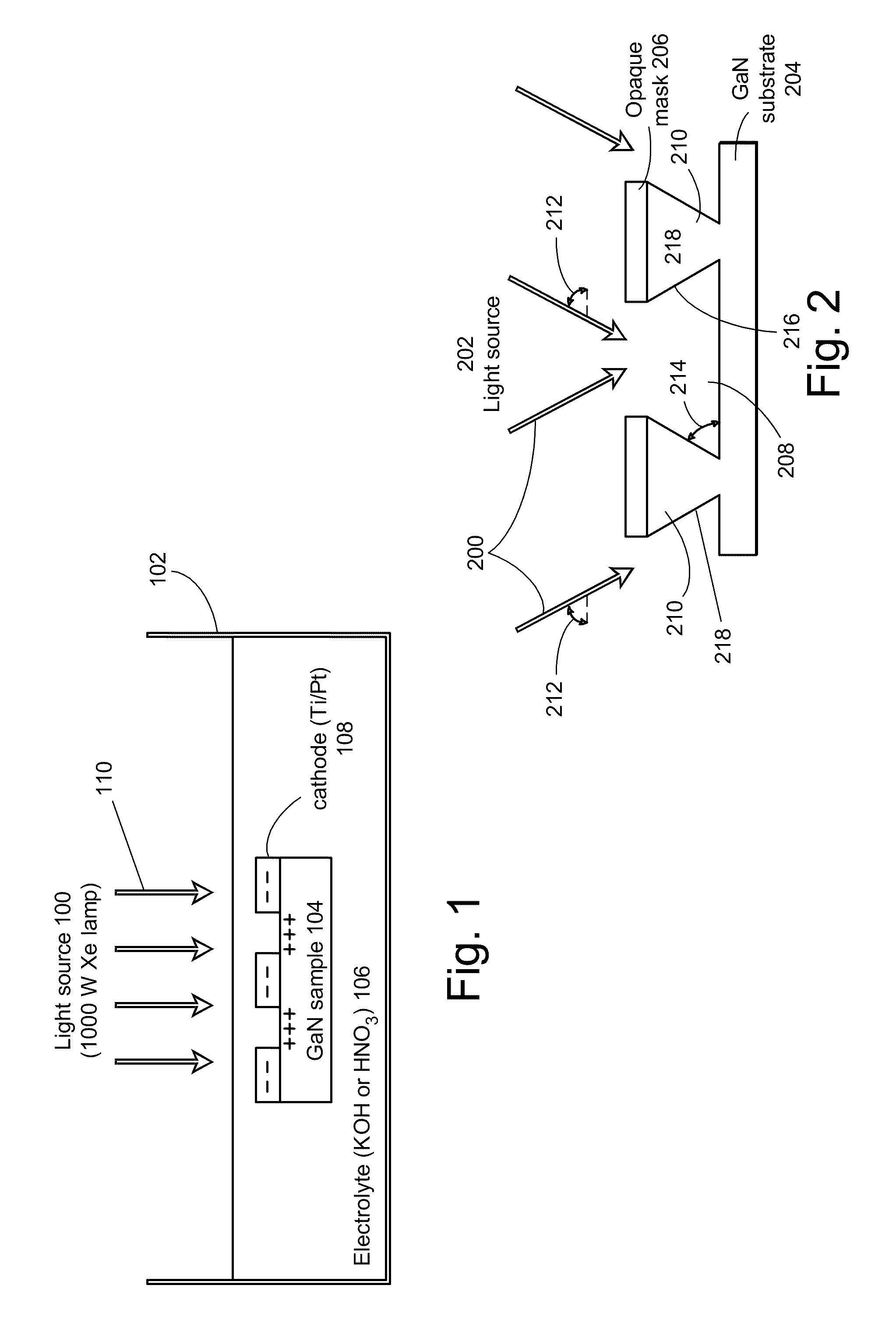

Photoelectrochemical undercut etching of semiconductor material

InactiveUS6884740B2Strong undercutKeep energy smallDecorative surface effectsSemiconductor/solid-state device manufacturingPreferential etchingSemiconductor materials

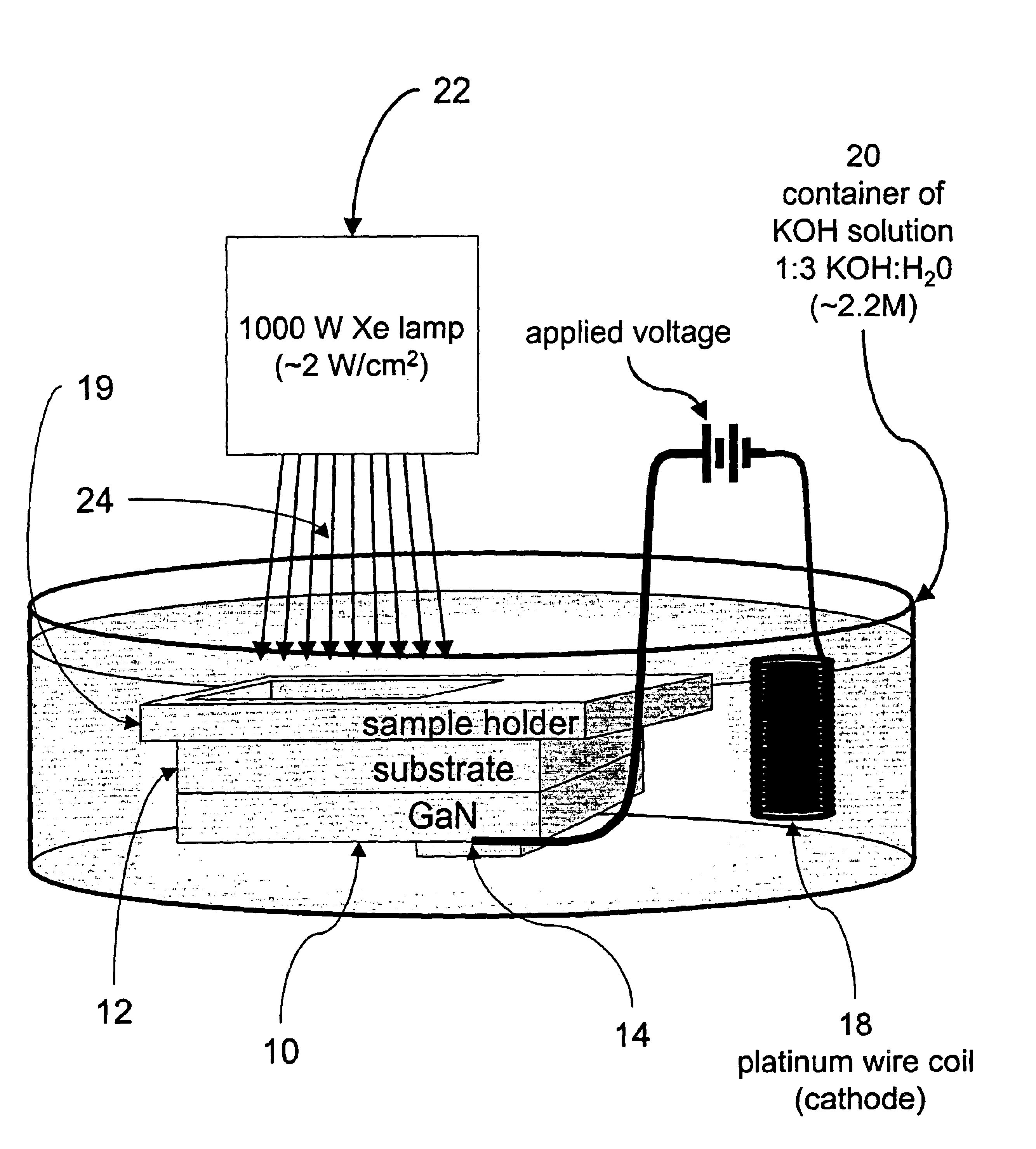

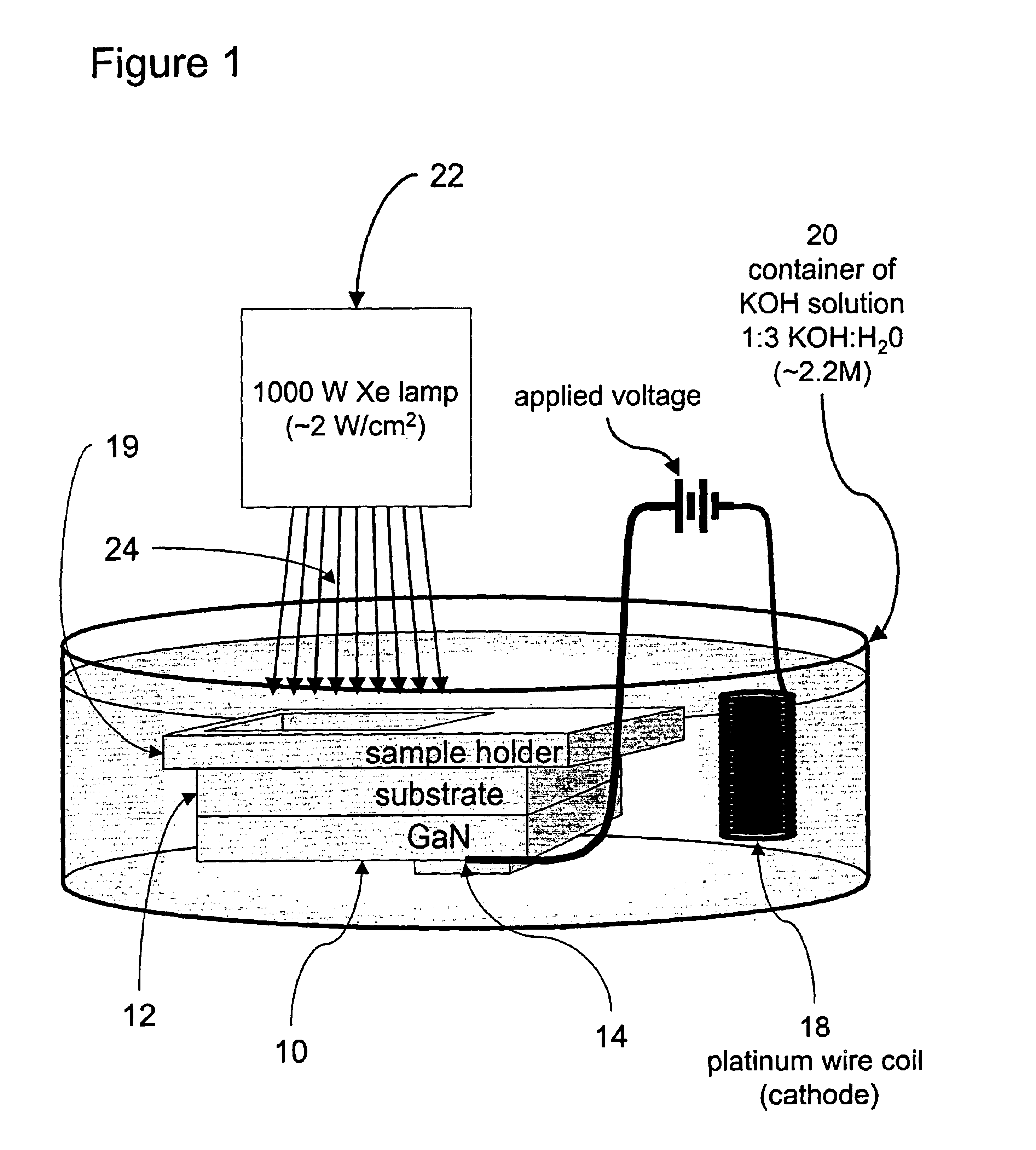

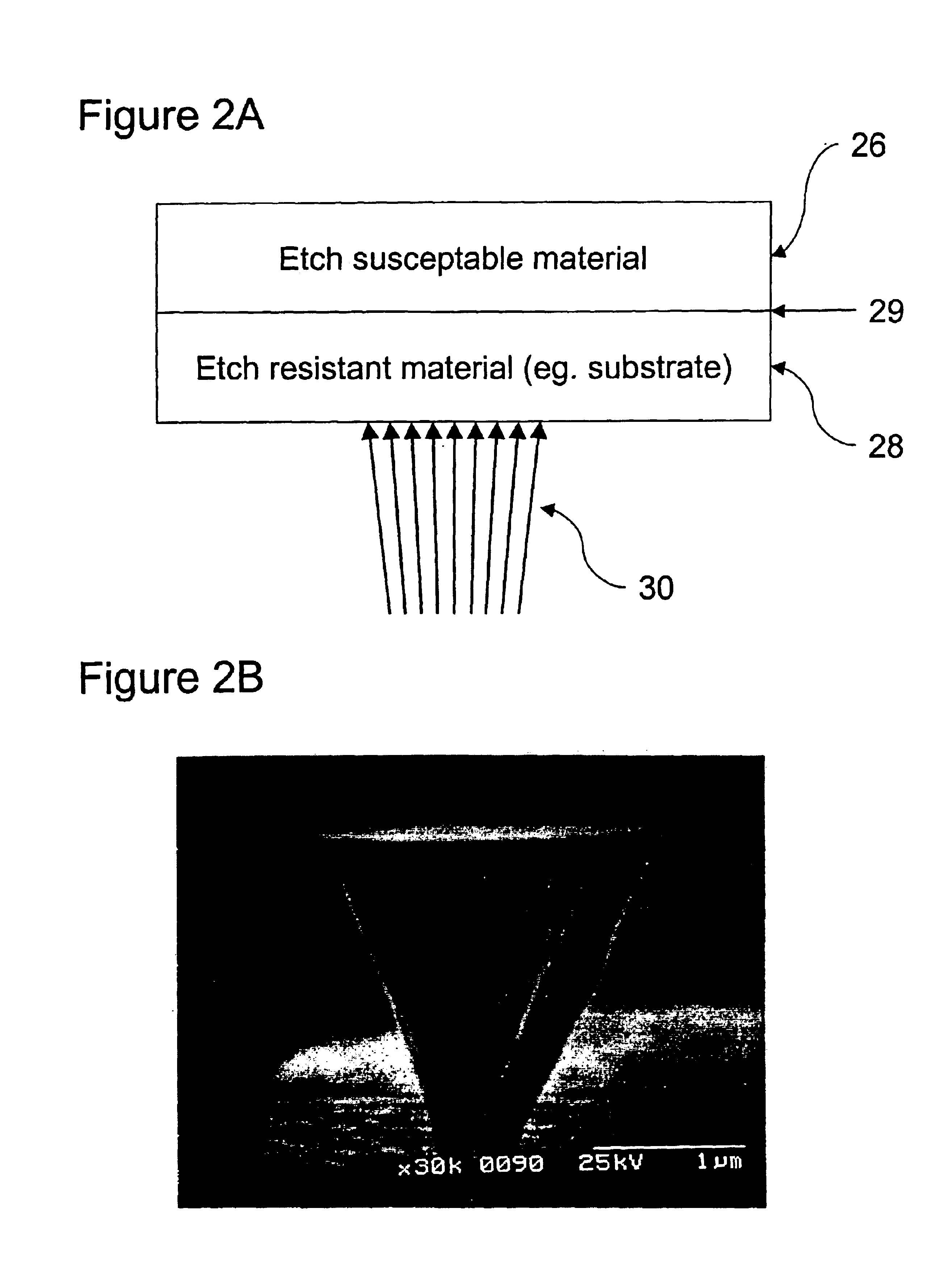

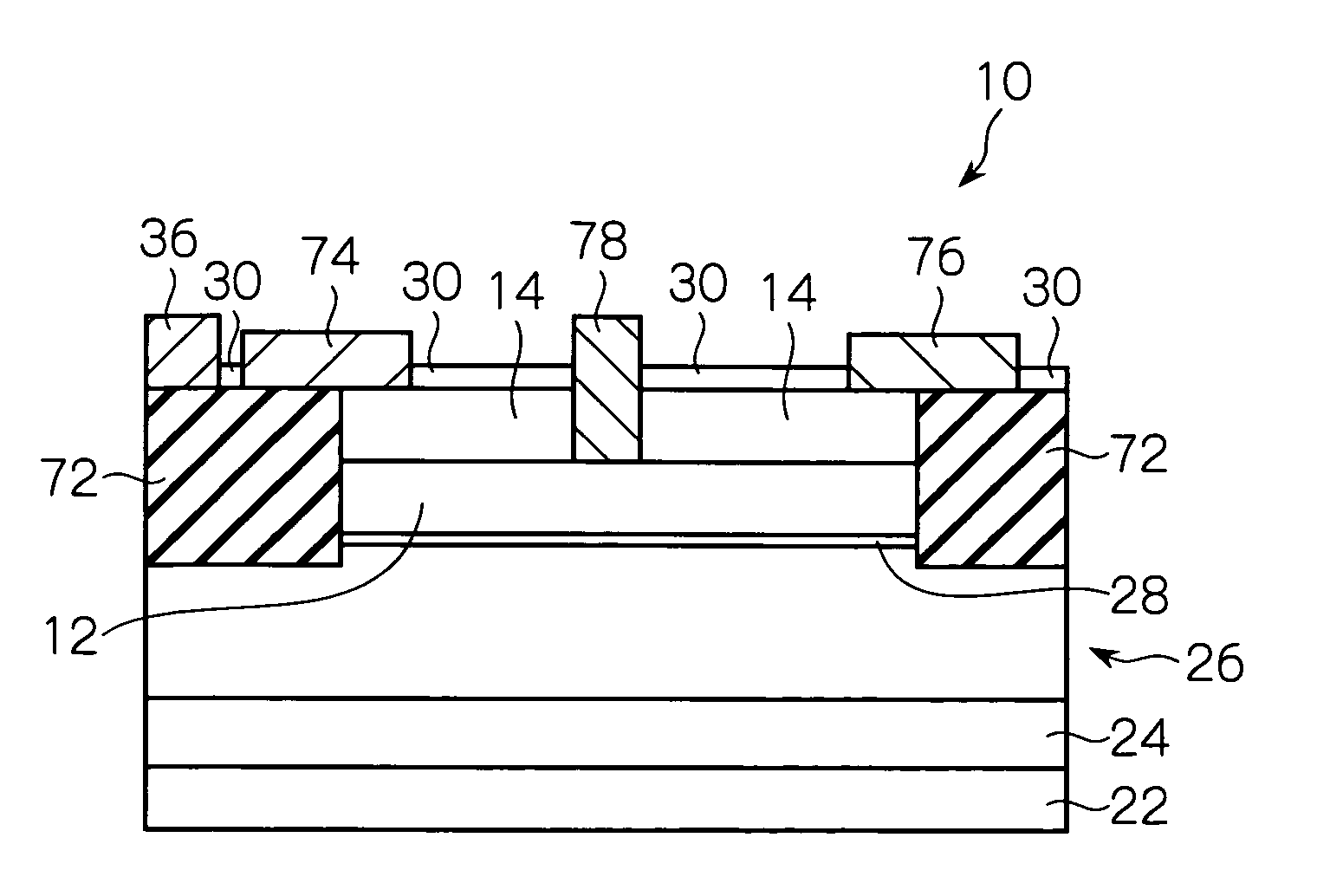

Photoelectrochemical (PEC) etching is restricted to a group III nitride semiconductor-barrier interface to laterally etch or undercut the target group III nitride. The barrier interface is provided by the transparent sapphire substrate on which the target group III nitride is epitaxially grown or by a layer of material in intimate contact with the target group III nitride material and having a bandgap sufficiently high to make it resistant to PEC etching. Due to the first orientation in which this effect was first observed, it has been named backside-Illuminated photoelectrochemical (BIPEC) etching. It refers to a preferential etching at the semiconductor-barrier layer interface. The assembly can be exposed to light from any direction to effectuate bandgap-selective PEC etching. An opaque mask can be applied to limit the lateral extent of the photoelectrochemical etching.

Owner:RGT UNIV OF CALIFORNIA

AlGaN/GaN hemt with normally-off threshold minimized and method of manufacturing the same

InactiveUS20110073912A1Suppression problemMinimizing and variation in threshold voltageSemiconductor/solid-state device manufacturingSemiconductor devicesPhotoelectrochemical etchingUltraviolet lights

In a method of forming a gate recess, on a surface of an epitaxial wafer including an epitaxial substrate, having a semiconductor layer having the band gap energy varying therein in the depth-wise direction, and a SiN surface protective layer, having a sidewall forming a gate opening and coating the surface of the epitaxial substrate, ultraviolet light having its energy equivalent to the band gap energy of the specific semiconductor layer is irradiated, while the specific semiconductor layer is photoelectrochemically etched from the gate opening with the SiN surface protective layer used as a mask. The gate recess free from plasma ion-induced damage is thus obtained.

Owner:OKI ELECTRIC IND CO LTD

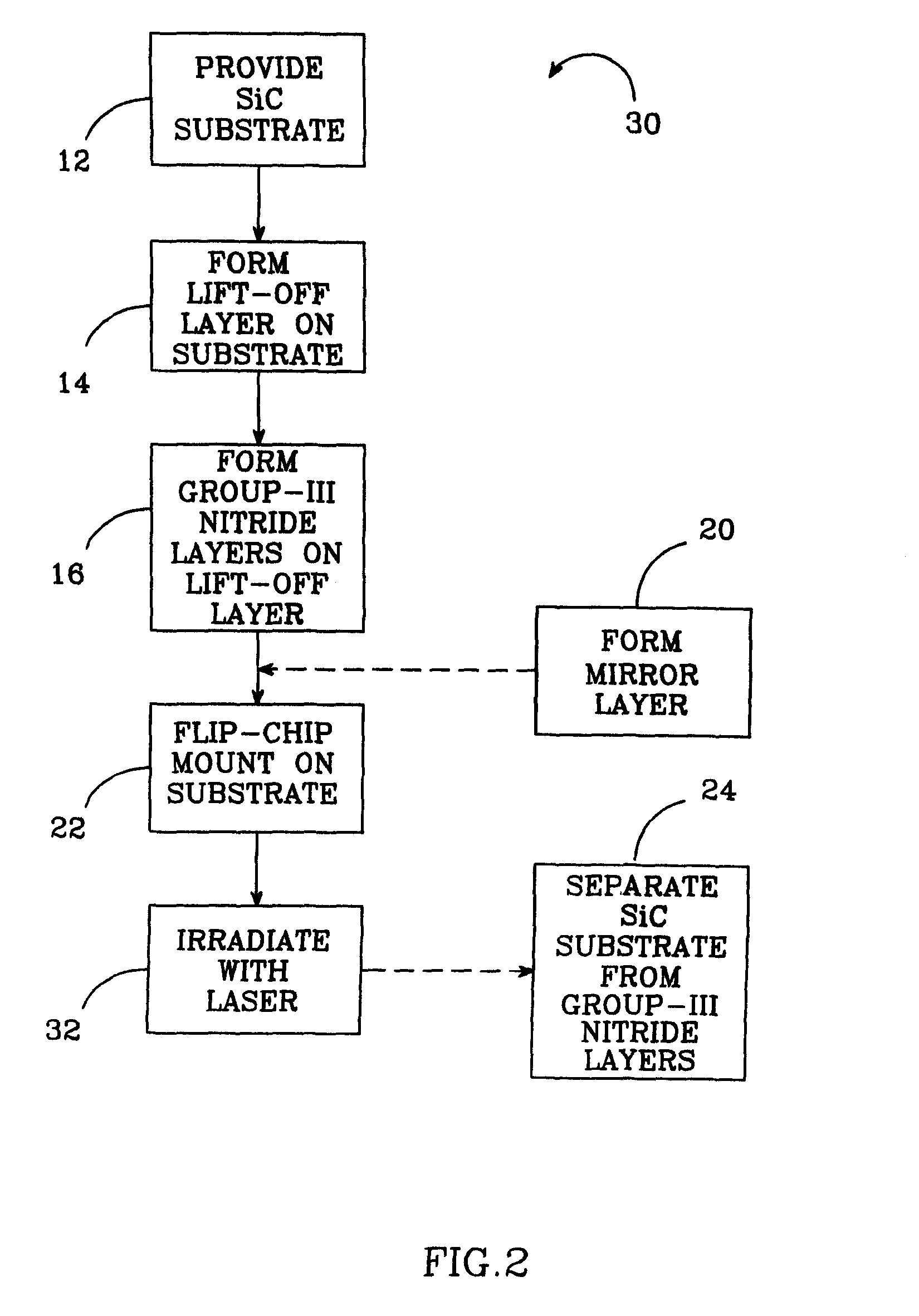

Lift-off process for GaN films formed on SiC substrates and devices fabricated using the method

ActiveUS7825006B2Semiconductor/solid-state device manufacturingSemiconductor devicesPhotoelectrochemical etchingSemiconductor structure

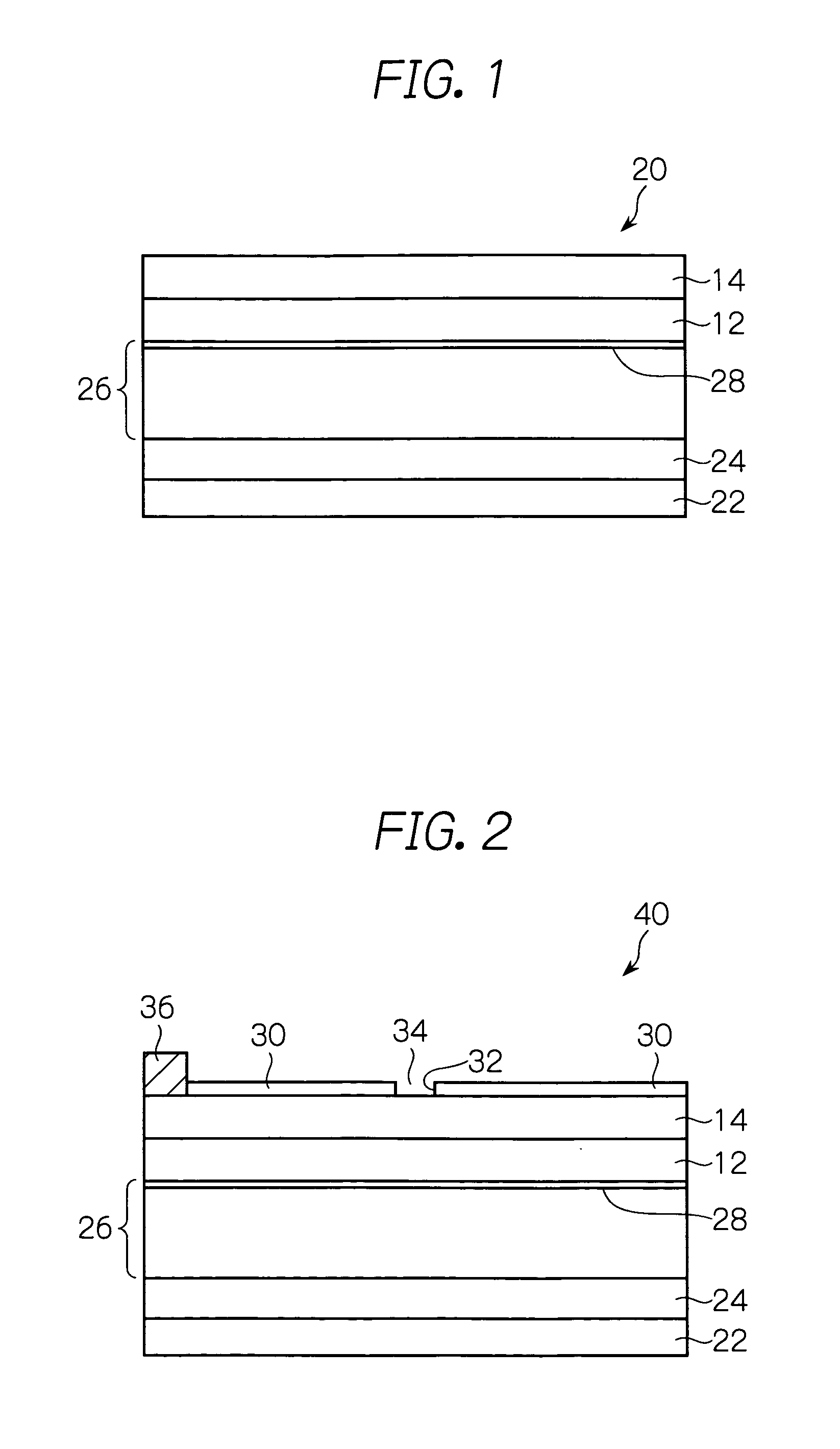

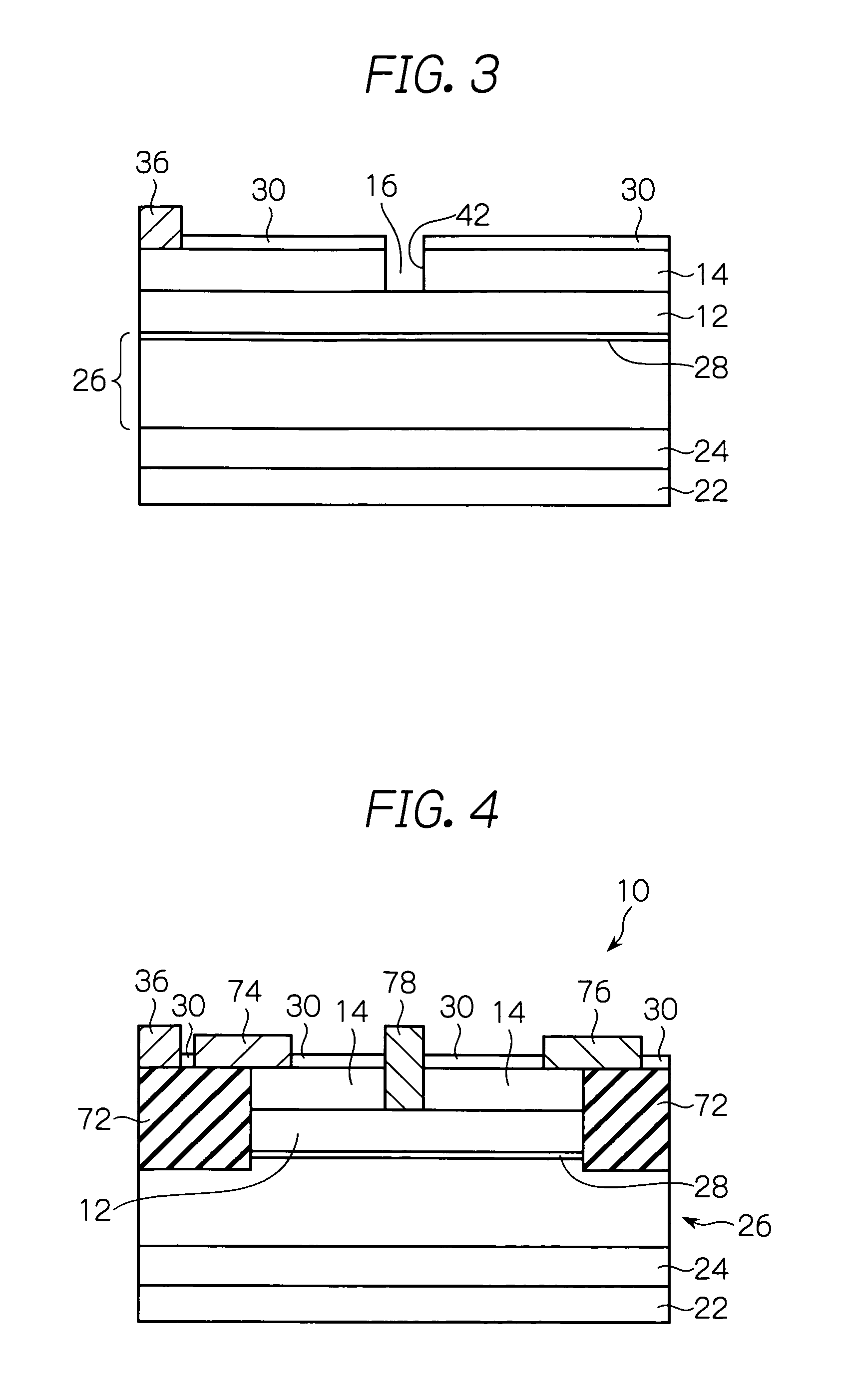

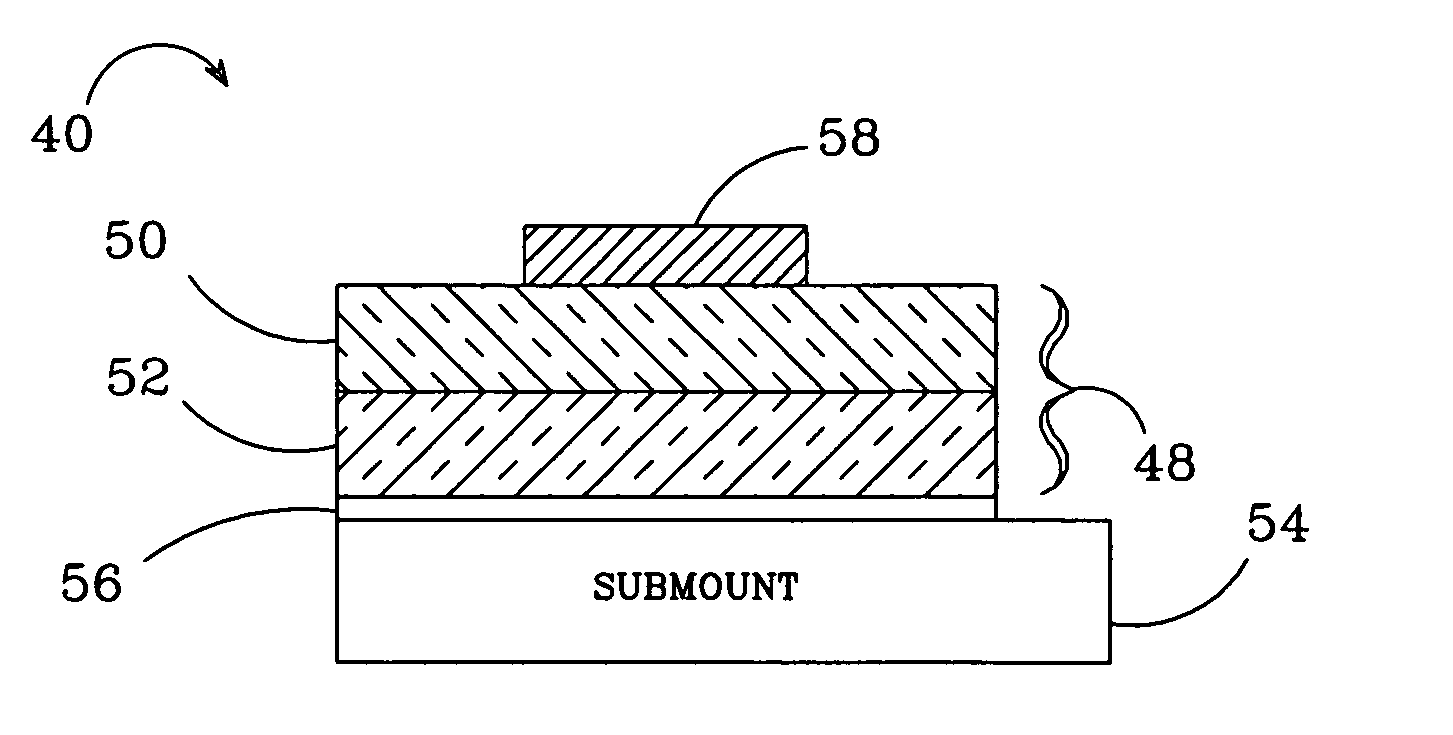

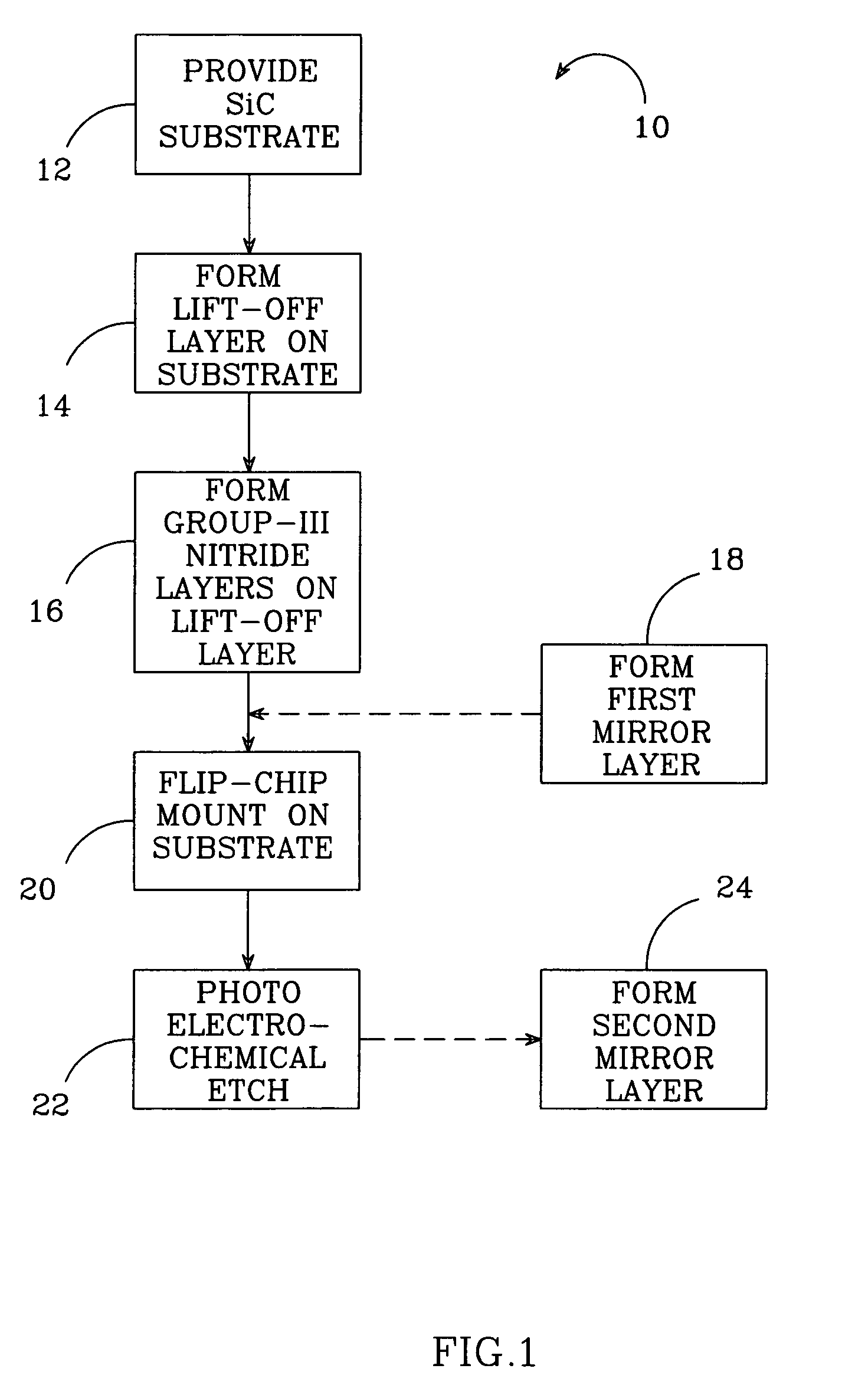

One embodiment of a method according to the present invention for fabricating a high light extraction photonic device comprises growing a lift-off layer on a substrate and growing an epitaxial semiconductor device structure on the lift-off layer such that the lift-off layer is sandwiched between said device structure and substrate. The epitaxial semiconductor structure comprises an emitter adapted to emit light in response to a bias. The device structure, lift-off layer and substrate is flip-chip mounted on a submount such that the epitaxial semiconductor device structure is sandwiched between the submount and lift-off layer. The lift-off layer is removed to separate the substrate from the device structure. Different removal methods can be used such as removal by a photo electrochemical etch or by illuminating the lift-off layer with laser light.

Owner:CREELED INC

Direct patterning of silicon by photoelectrochemical etching

ActiveUS7433811B2High resolutionComplex detailDecorative surface effectsSemiconductor/solid-state device manufacturingPhotoelectrochemical etchingSoft lithography

The invention is directed to methods for direct patterning of silicon. The invention provides the ability to fabricate complex surfaces in silicon with three dimensional features of high resolution and complex detail. The invention is suitable, for example, for use in soft lithography as embodiments of the invention can quickly create a master for use in soft lithography. In an embodiment of the invention, electrochemical etching of silicon, such as a silicon wafer, for example, is conducted while at least a portion of the silicon surface is exposed to an optical pattern. The etching creates porous silicon in the substrate, and removal of the porous silicon layer leaves a three-dimensional structure correlating to the optical pattern.

Owner:RGT UNIV OF CALIFORNIA

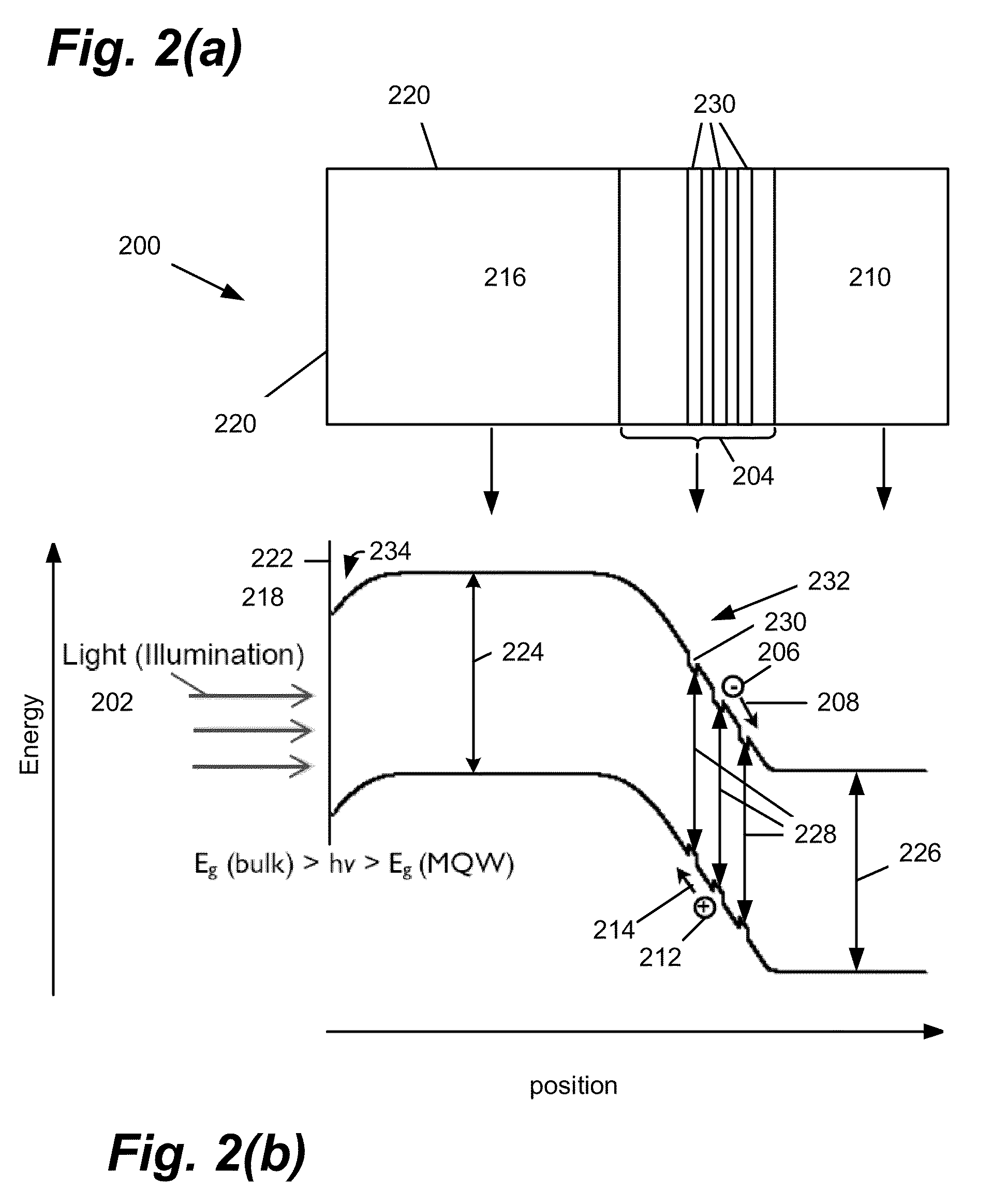

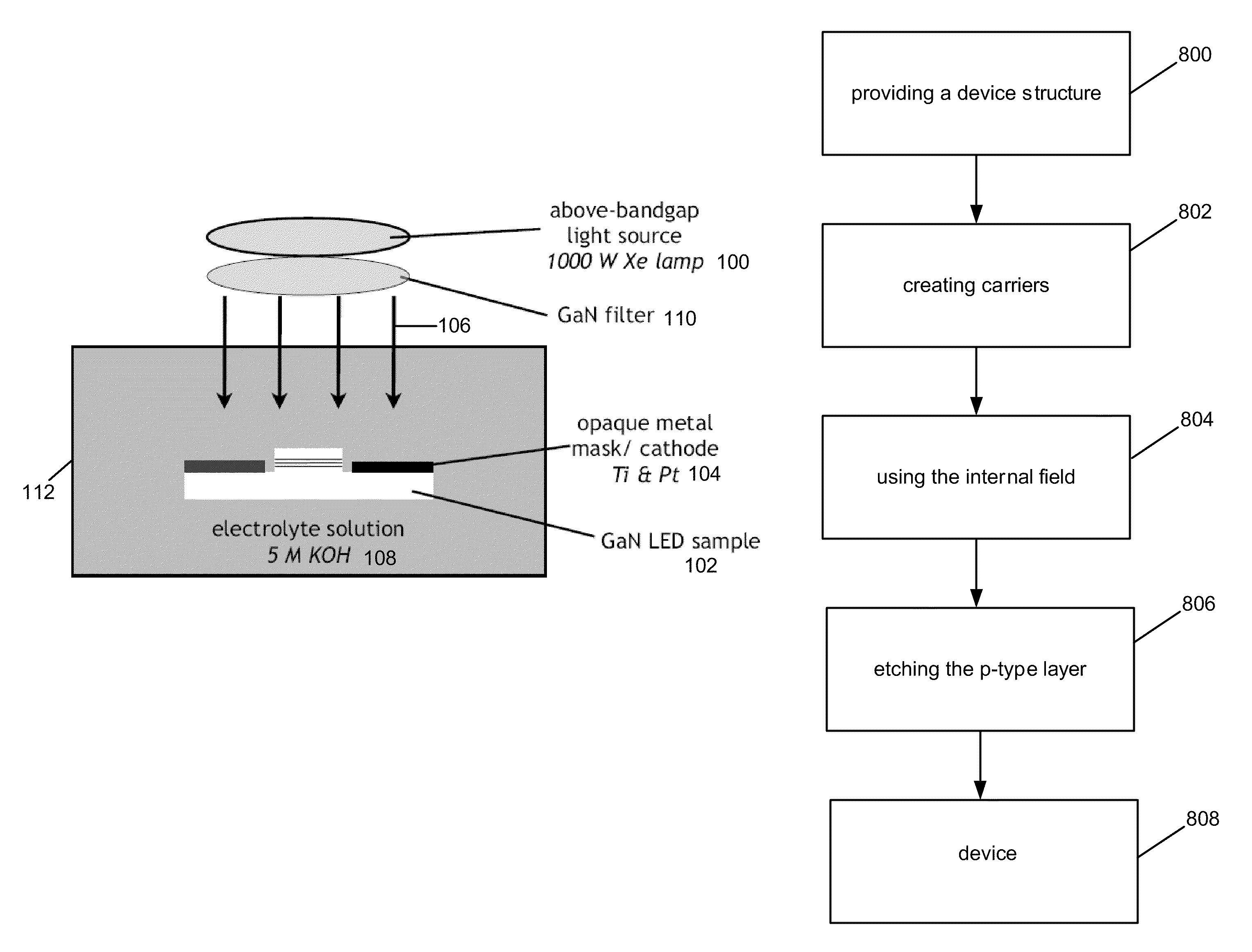

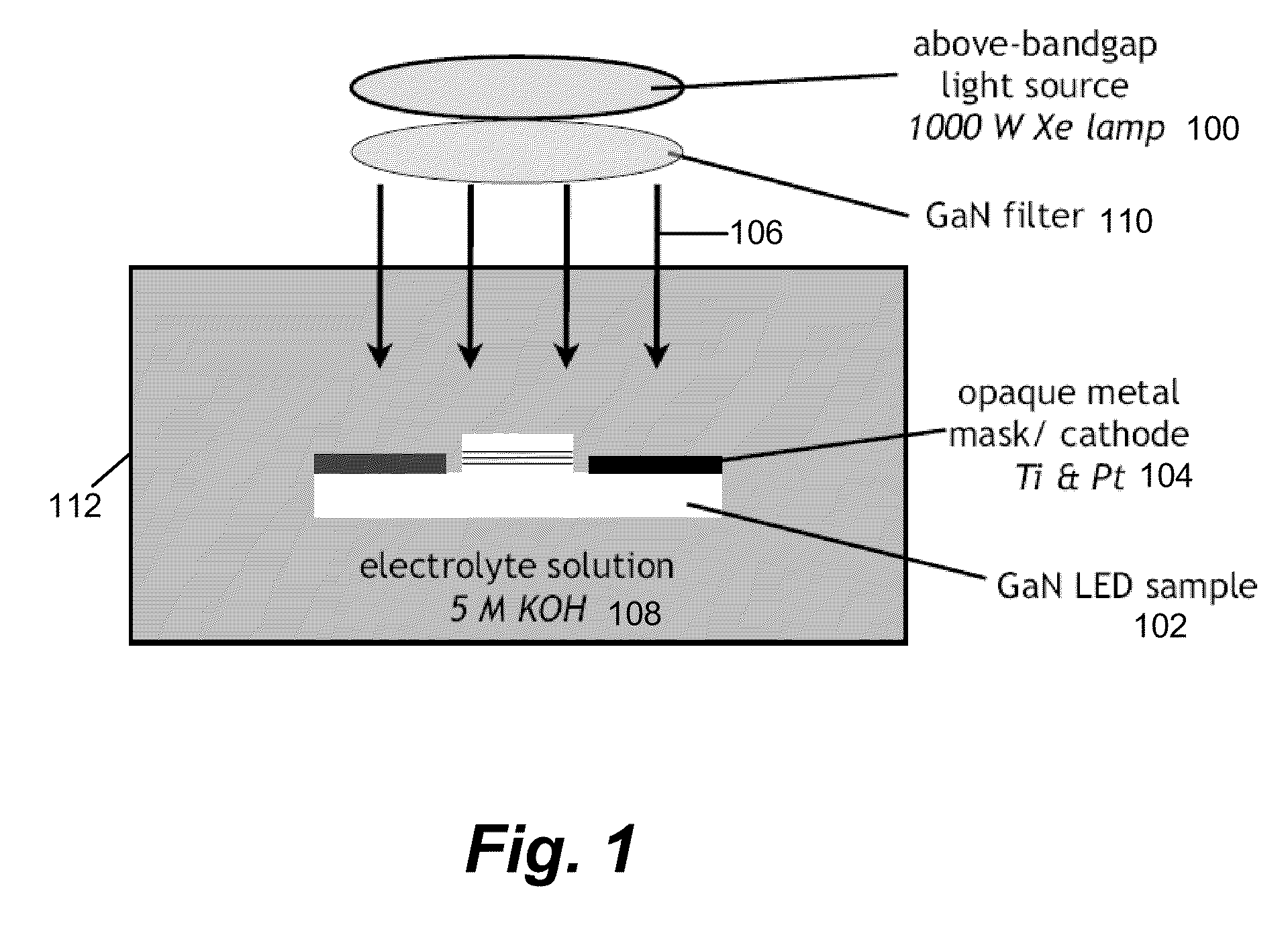

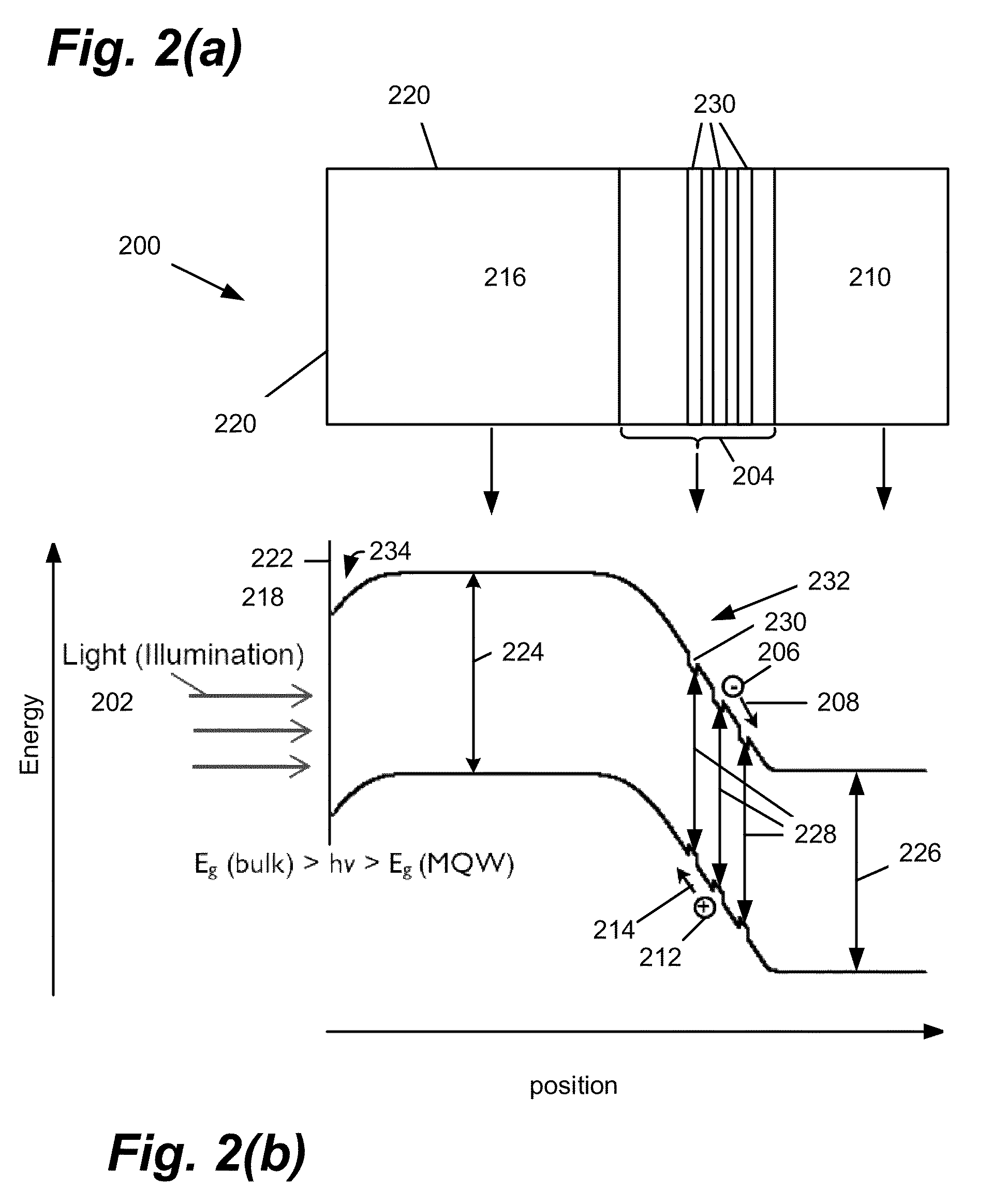

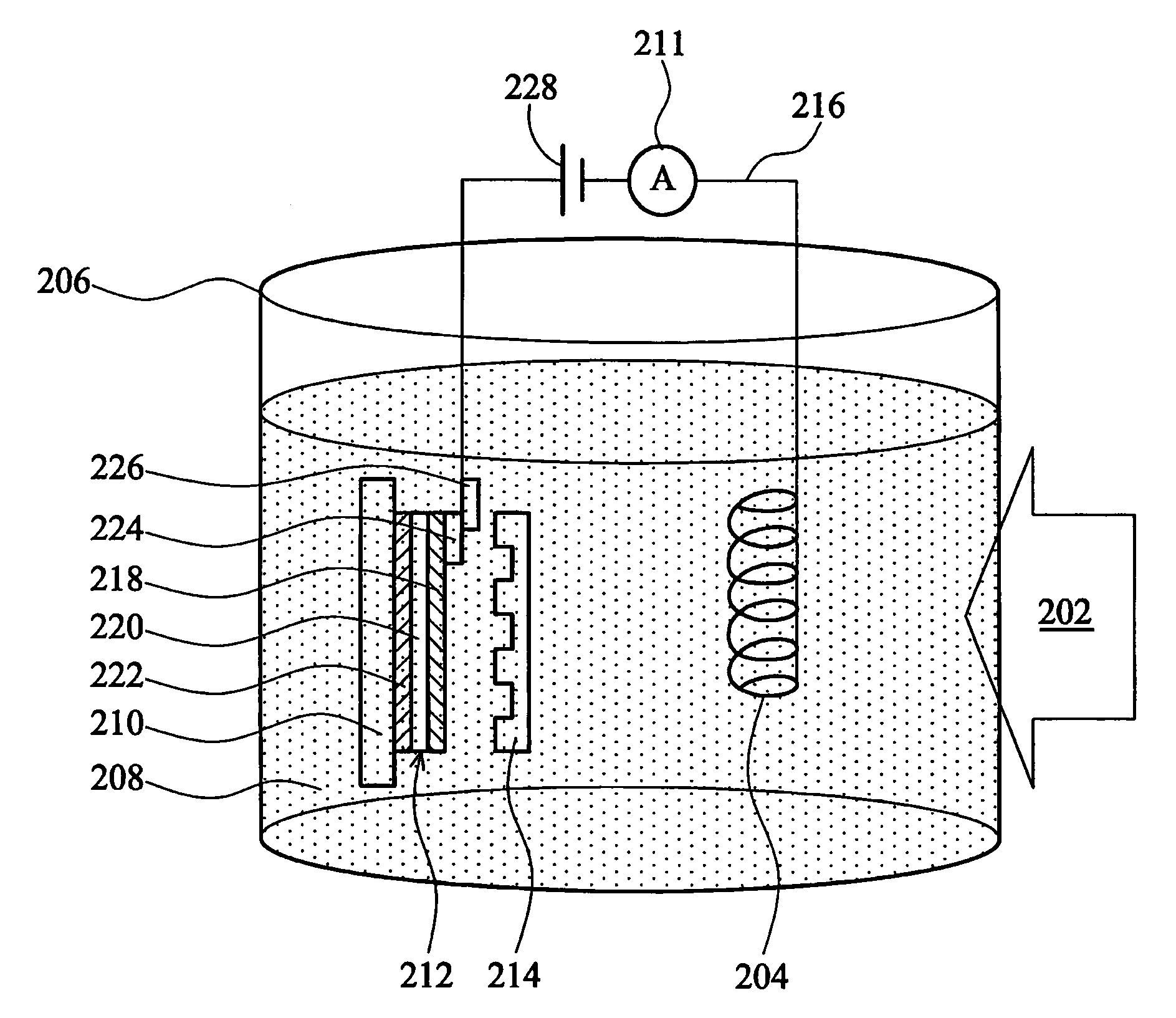

Photoelectrochemical etching of p-type semiconductor heterostructures

ActiveUS20090283800A1Reduce harmImprove smoothnessSemiconductor/solid-state device manufacturingSemiconductor devicesElectron holePhotoelectrochemical etching

A method for photoelectrochemical (PEC) etching of a p-type semiconductor layer simply and efficiently, by providing a driving force for holes to move towards a surface of a p-type cap layer to be etched, wherein the p-type cap layer is on a heterostructure and the heterostructure provides the driving force from an internal bias generated internally in the heterostructure; generating electron-hole pairs in a separate area of the heterostructure than the surface to be etched; and using an etchant solution to etch the surface of the p-type layer.

Owner:RGT UNIV OF CALIFORNIA

AlGaN/GaN HEMT with normally-off threshold minimized and method of manufacturing the same

InactiveUS8114726B2Minimize changesFree from damageSemiconductor/solid-state device manufacturingSemiconductor devicesPhotoelectrochemical etchingUltraviolet lights

In a method of forming a gate recess, on a surface of an epitaxial wafer including an epitaxial substrate, having a semiconductor layer having the band gap energy varying therein in the depth-wise direction, and a SiN surface protective layer, having a sidewall forming a gate opening and coating the surface of the epitaxial substrate, ultraviolet light having its energy equivalent to the band gap energy of the specific semiconductor layer is irradiated, while the specific semiconductor layer is photoelectrochemically etched from the gate opening with the SiN surface protective layer used as a mask. The gate recess free from plasma ion-induced damage is thus obtained.

Owner:OKI ELECTRIC IND CO LTD

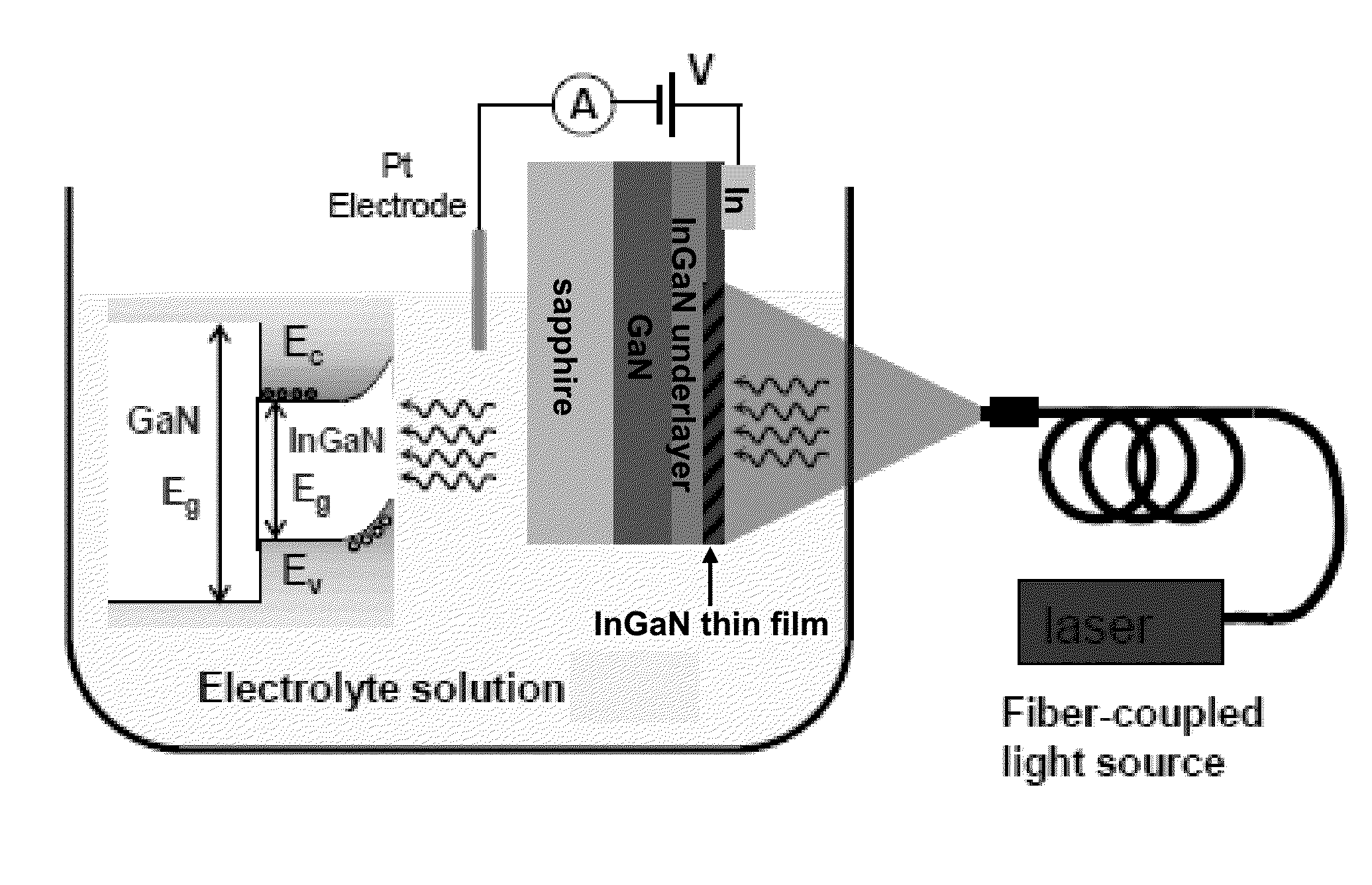

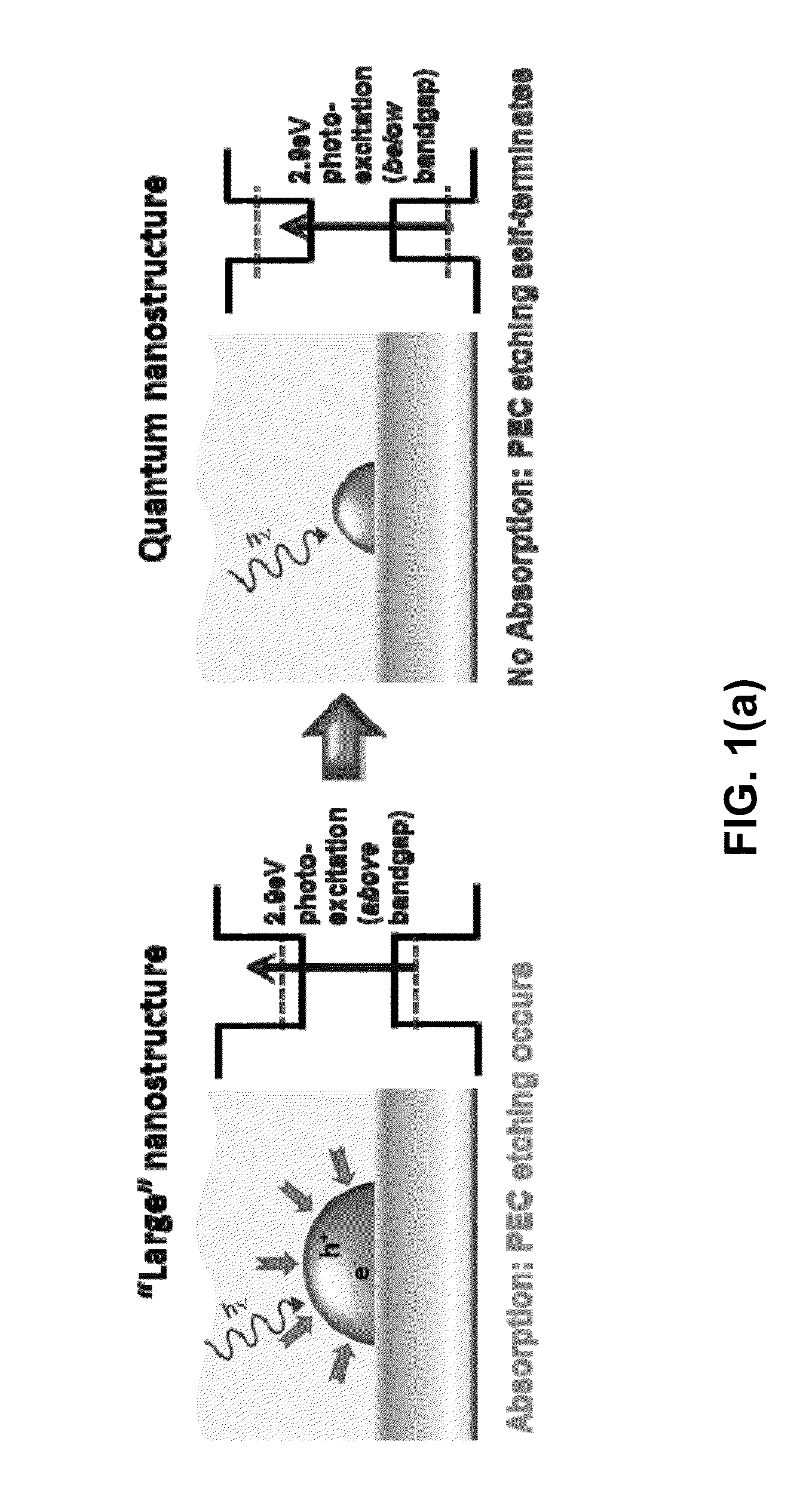

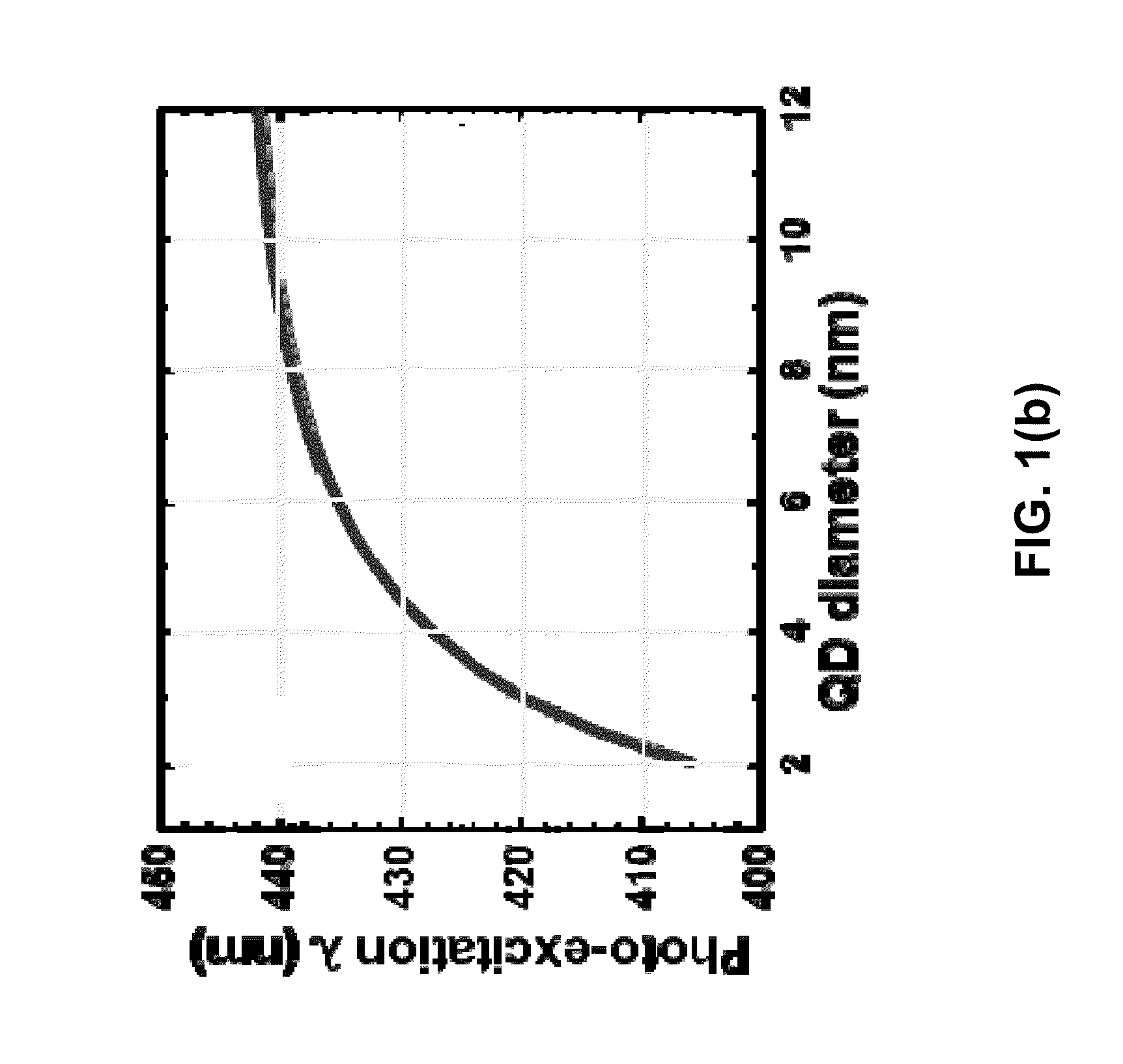

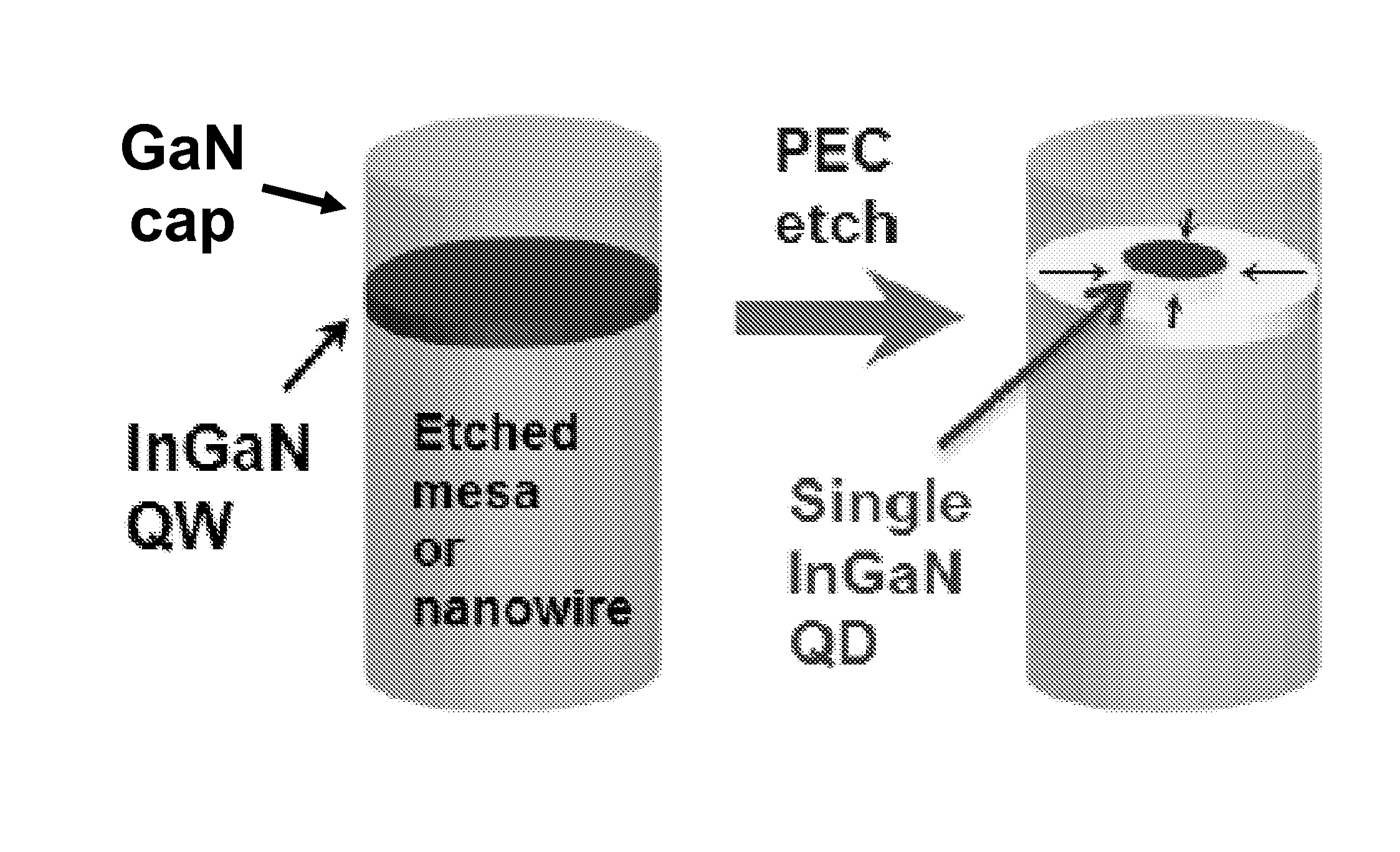

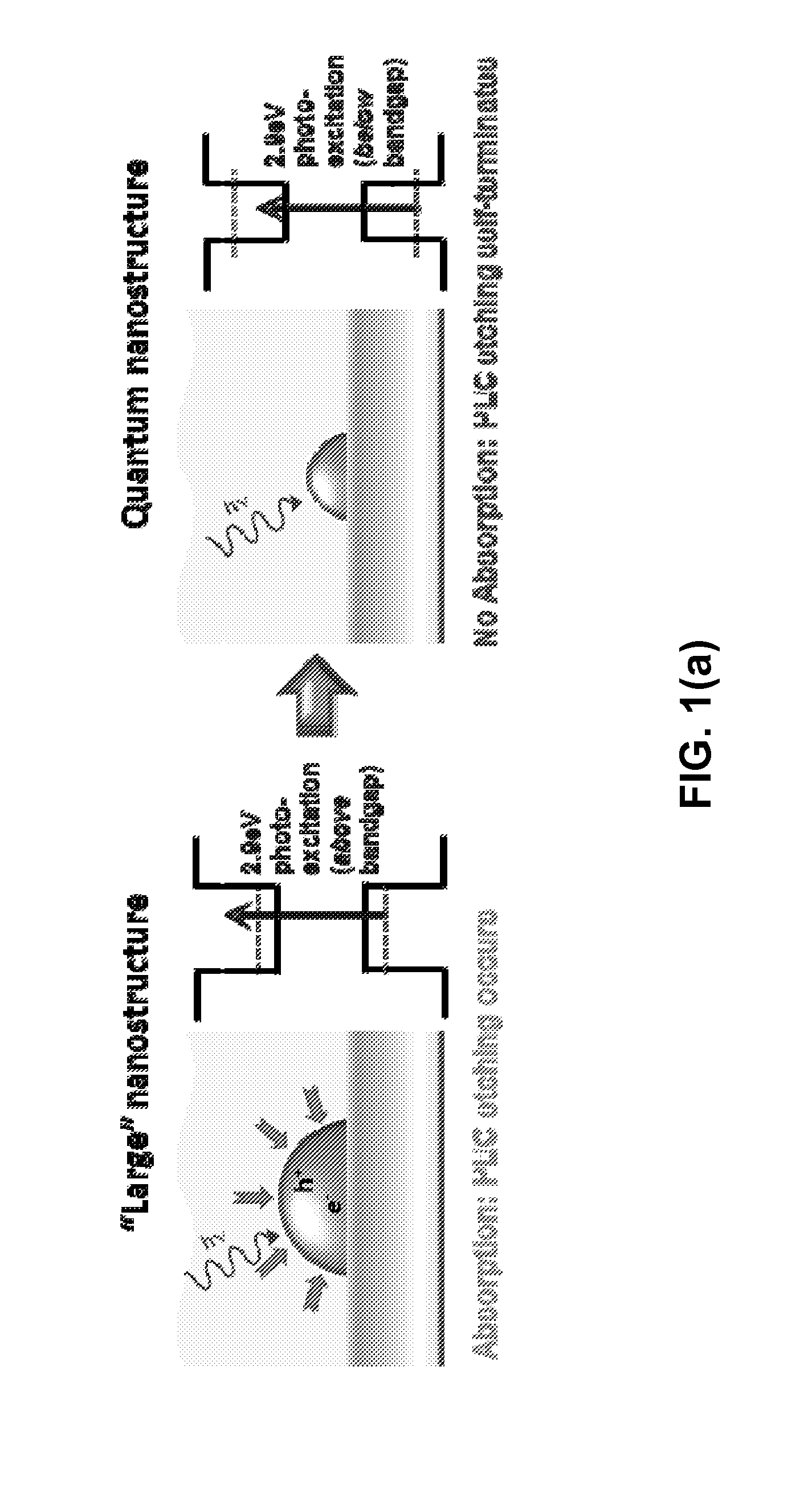

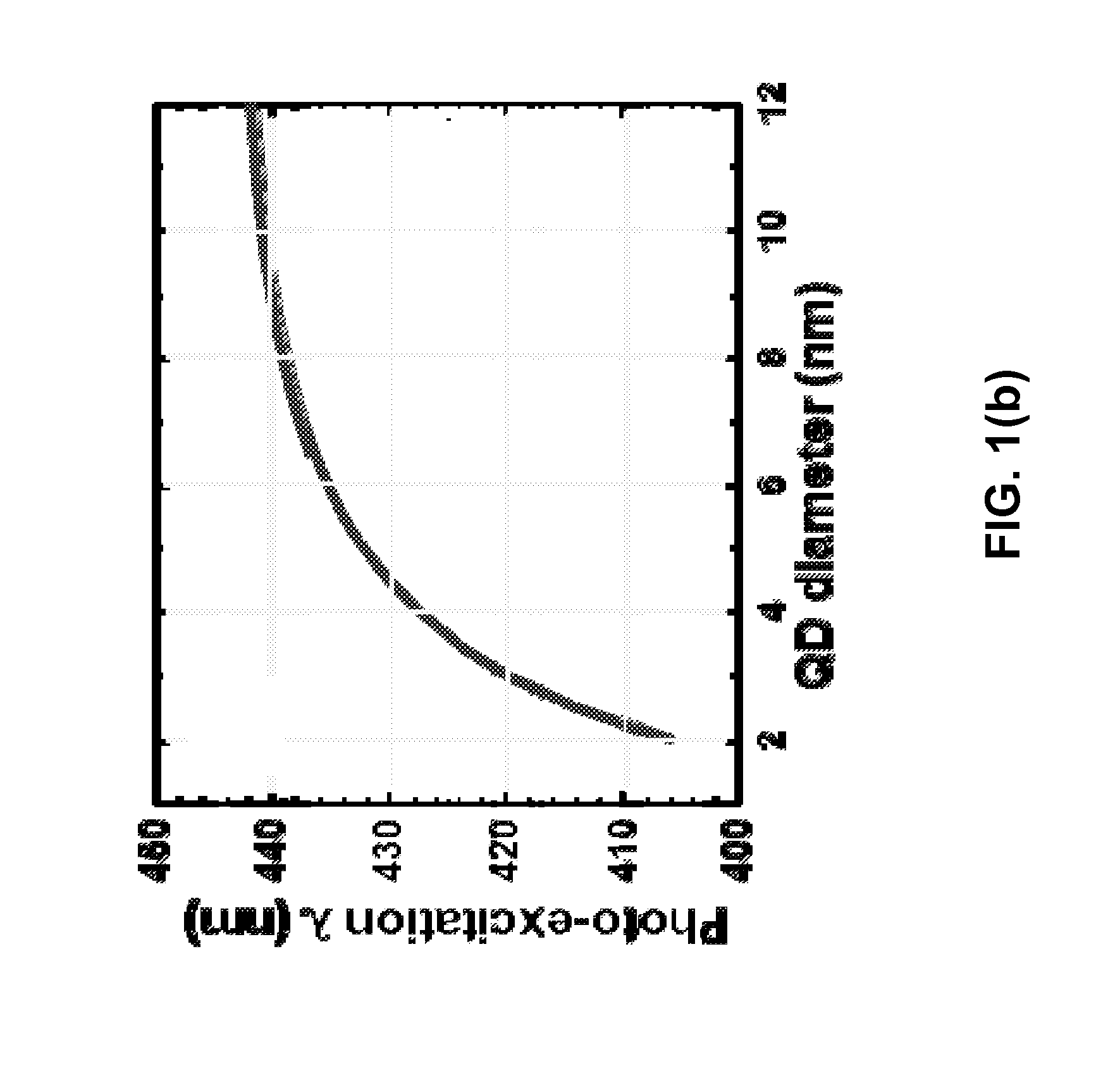

Quantum-size-controlled photoelectrochemical etching of semiconductor nanostructures

ActiveUS9276382B2Increase etch rateIncrease of bandgapsLaser detailsIndividual molecule manipulationPhotoelectrochemical etchingPhotoluminescence

Quantum-size-controlled photoelectrochemical (QSC-PEC) etching provides a new route to the precision fabrication of epitaxial semiconductor nanostructures in the sub-10-nm size regime. For example, quantum dots (QDs) can be QSC-PEC-etched from epitaxial InGaN thin films using narrowband laser photoexcitation, and the QD sizes (and hence bandgaps and photoluminescence wavelengths) are determined by the photoexcitation wavelength.

Owner:NAT TECH & ENG SOLUTIONS OF SANDIA LLC

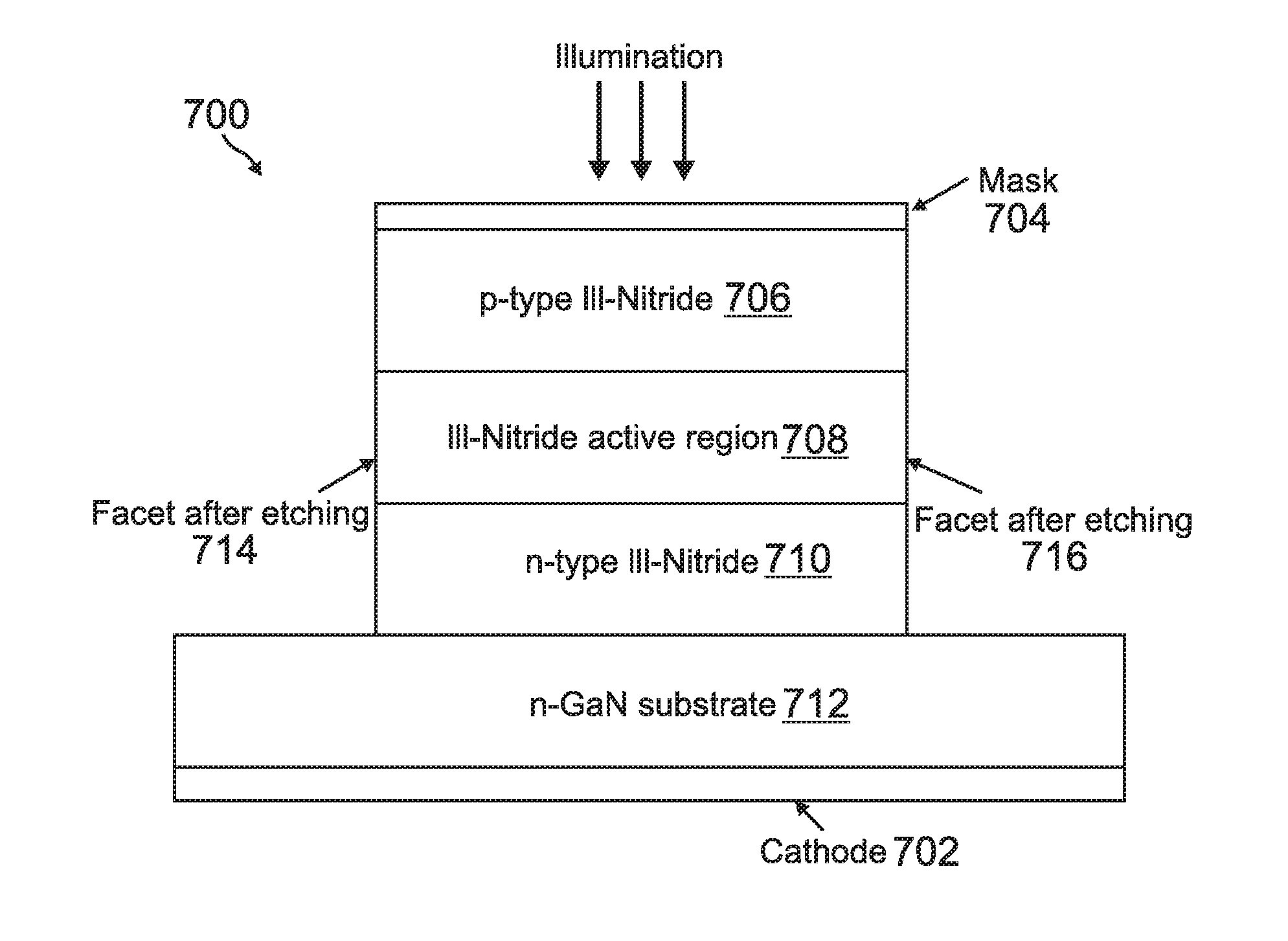

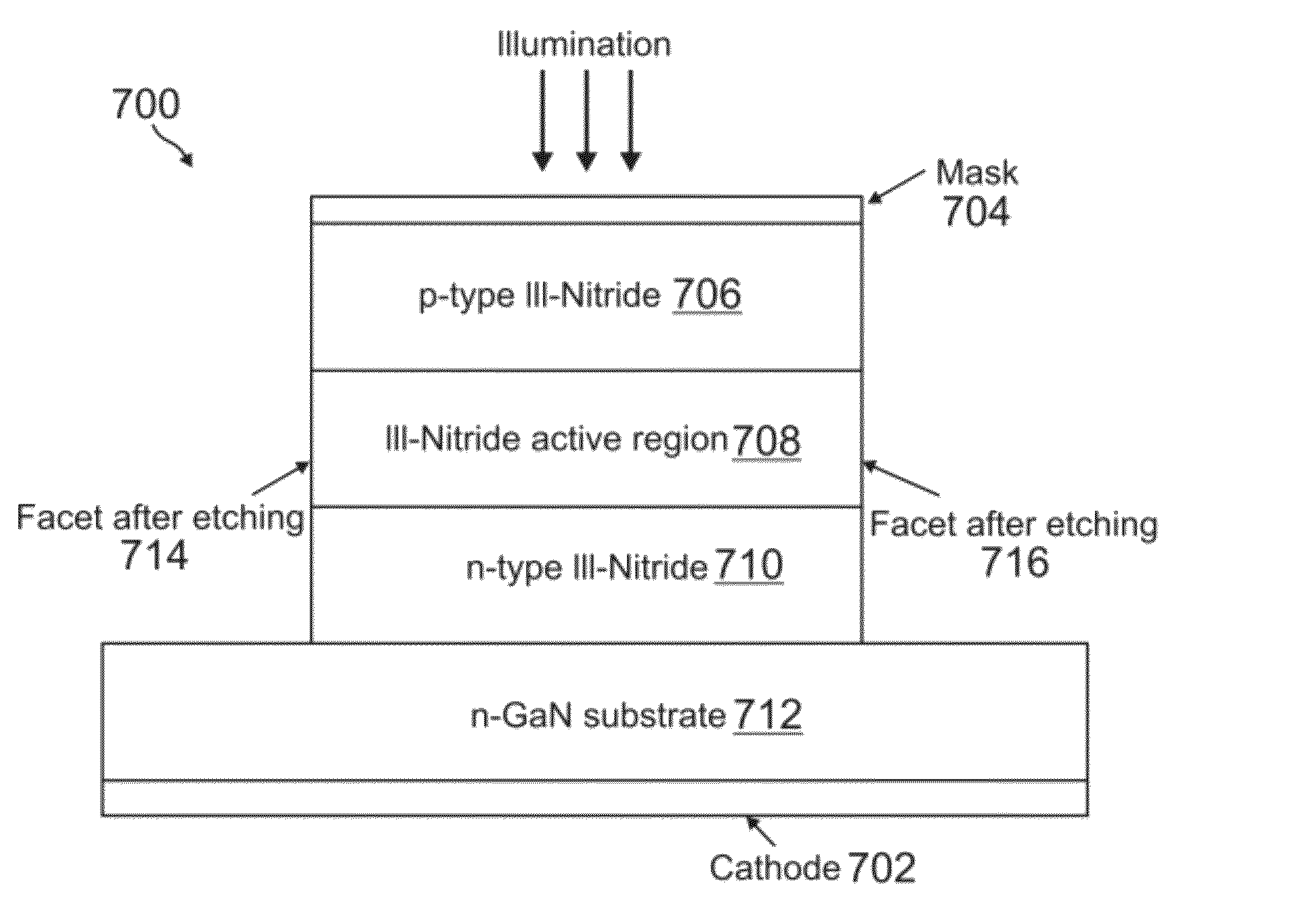

Photoelectrochemical etching for laser facets

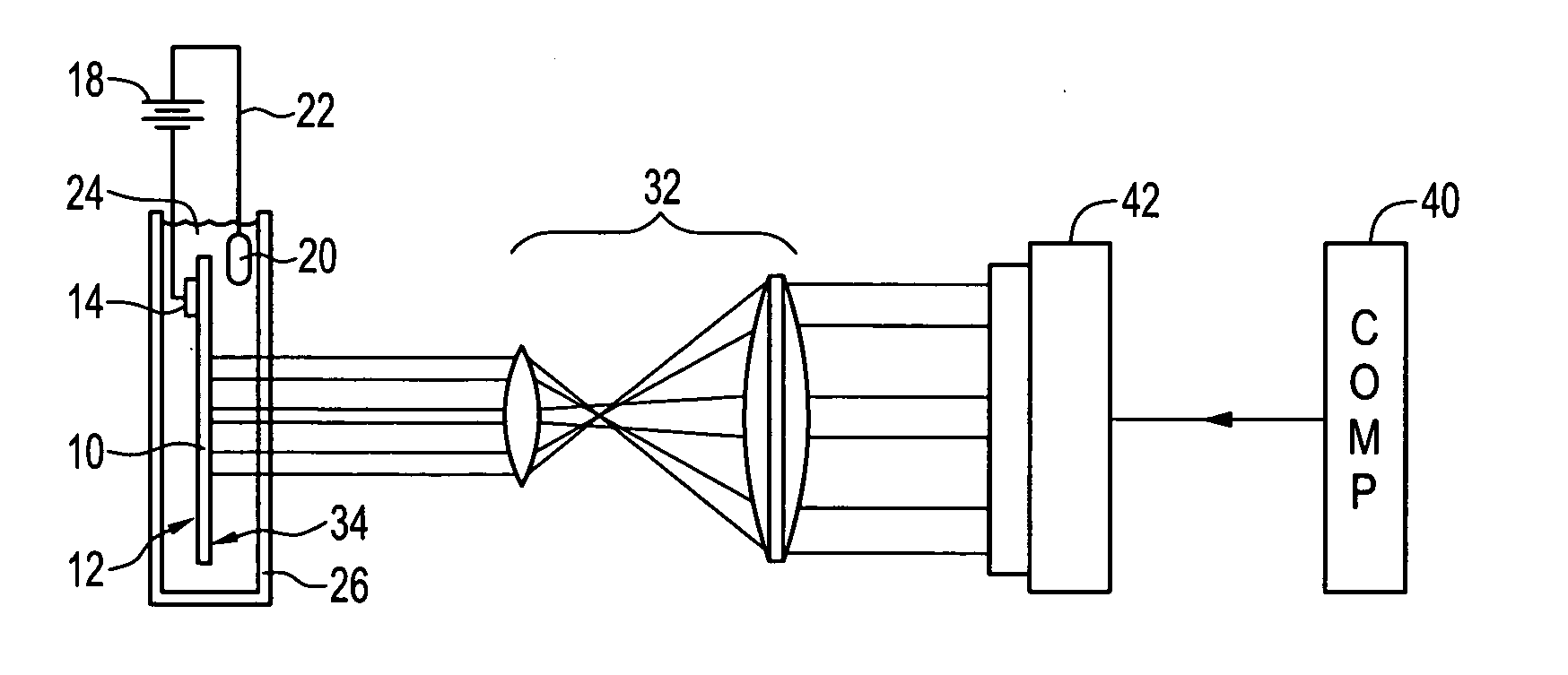

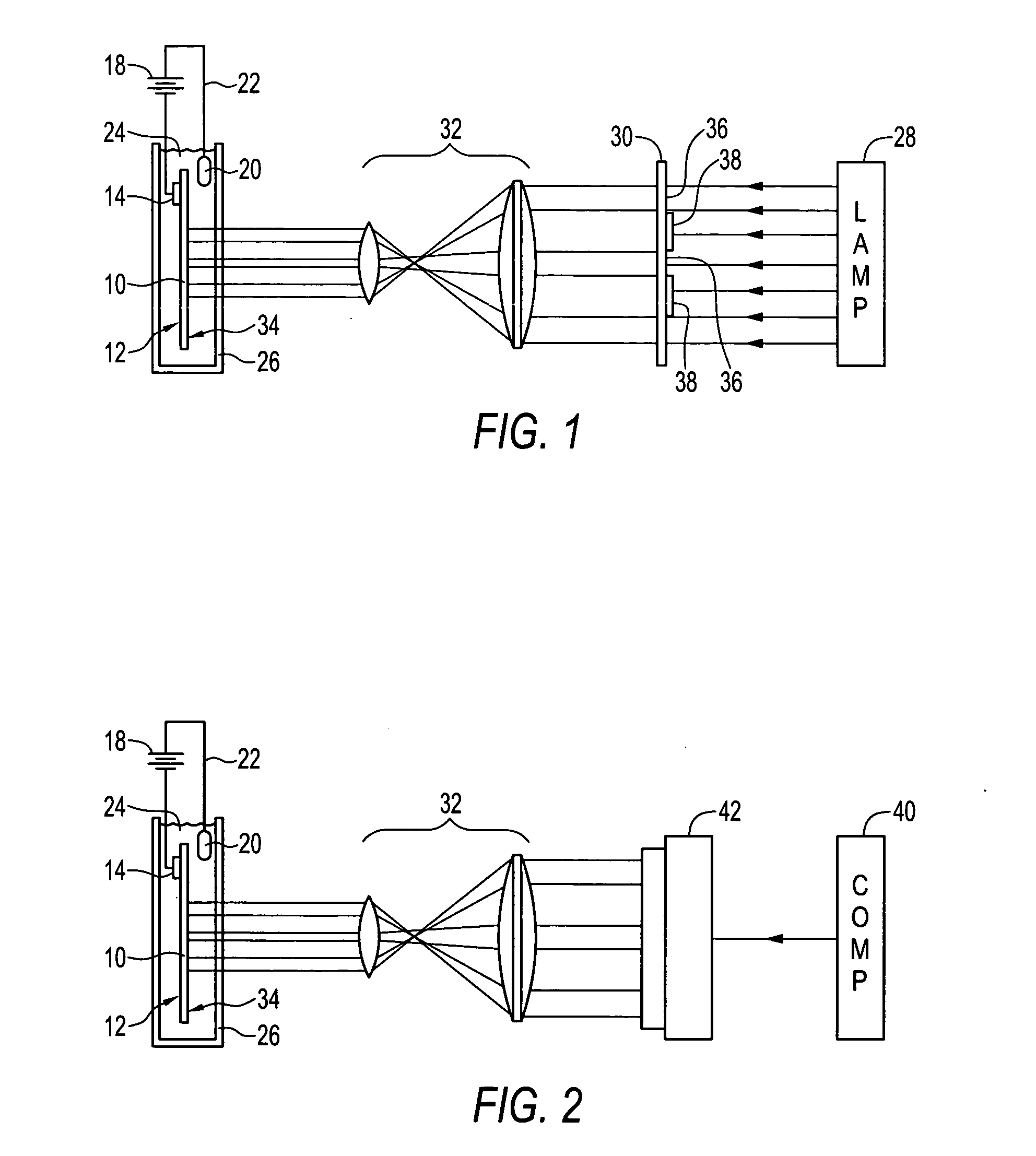

InactiveUS20100195684A1Limit angleLaser detailsSemiconductor/solid-state device testing/measurementPhotoelectrochemical etchingFaceting

A method for fabricating a semiconductor laser device, by etching facets using a photoelectrochemical (PEC) etch, so that the facets are sufficiently smooth to support optical modes within a cavity bounded by the facets.

Owner:RGT UNIV OF CALIFORNIA

Quantum-Size-Controlled Photoelectrochemical Etching of Semiconductor Nanostructures

ActiveUS20150270136A1Increase etch rateLower the volumeLaser detailsIndividual molecule manipulationPhotoelectrochemical etchingPhotoluminescence

Quantum-size-controlled photoelectrochemical (QSC-PEC) etching provides a new route to the precision fabrication of epitaxial semiconductor nanostructures in the sub-10-nm size regime. For example, quantum dots (QDs) can be QSC-PEC-etched from epitaxial InGaN thin films using narrowband laser photoexcitation, and the QD sizes (and hence bandgaps and photoluminescence wavelengths) are determined by the photoexcitation wavelength.

Owner:NAT TECH & ENG SOLUTIONS OF SANDIA LLC

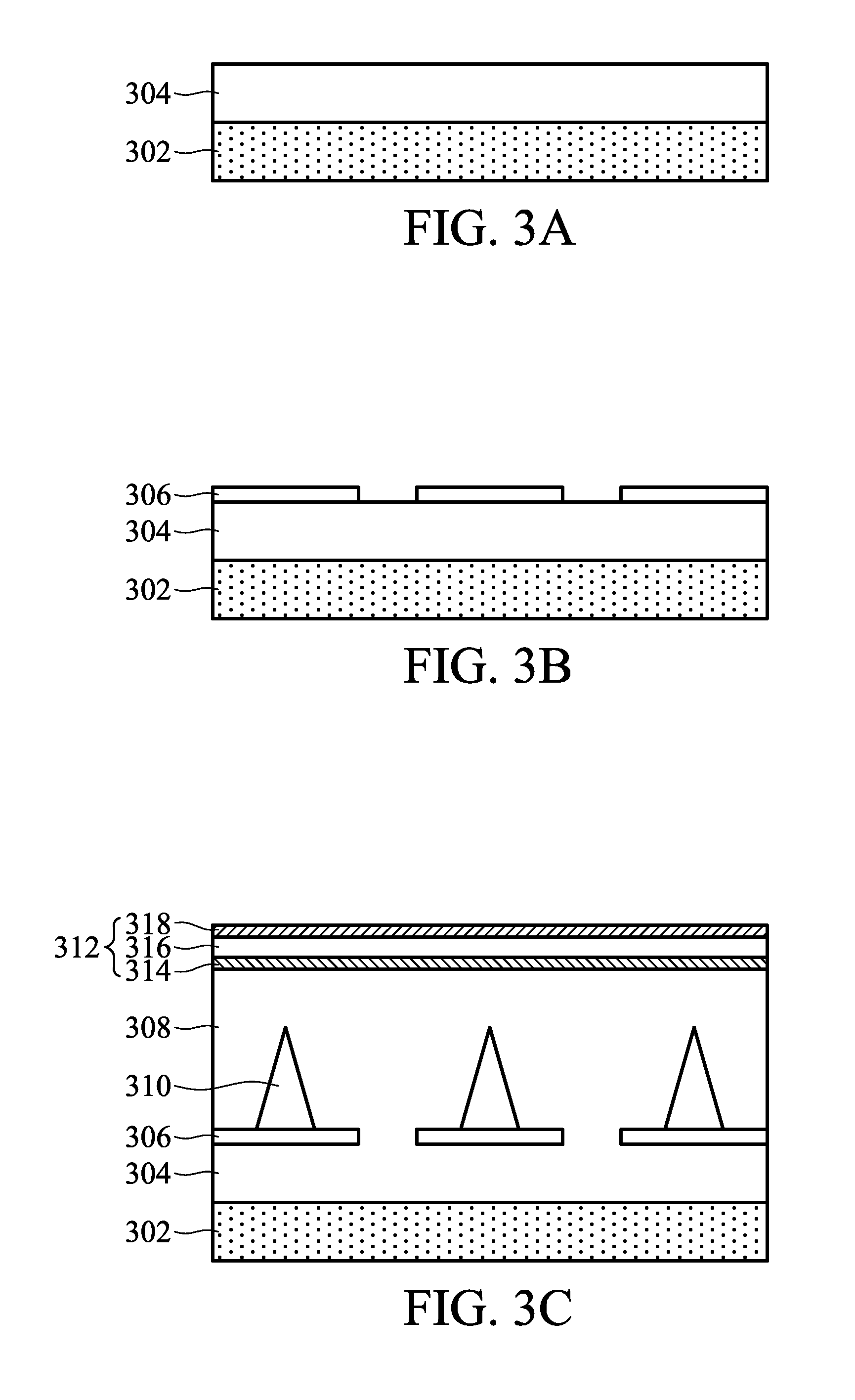

Method for forming light emitting device

ActiveUS20120070922A1Semiconductor/solid-state device manufacturingNanotechnologyPhotoelectrochemical etchingLateral overgrowth

The invention provides a method for forming a light emitting device. A first substrate is provided. A plurality of patterned masks is formed on the first substrate, or on a semiconductor epitaxial layer grown on the first substrate, or the first substrate is etched to form a plurality of trenches, followed by performing an epitaxial lateral overgrowth process to grow an epitaxy layer over the first substrate. A light emitting structure is formed on the epitaxy layer. A first electrode layer is formed on the light emitting structure. The light emitting structure is wafer bonded to a second substrate. A photoelectrochemical etching process is performed to lift off the first substrate from the epitaxy layer.

Owner:NAT TAIWAN UNIV

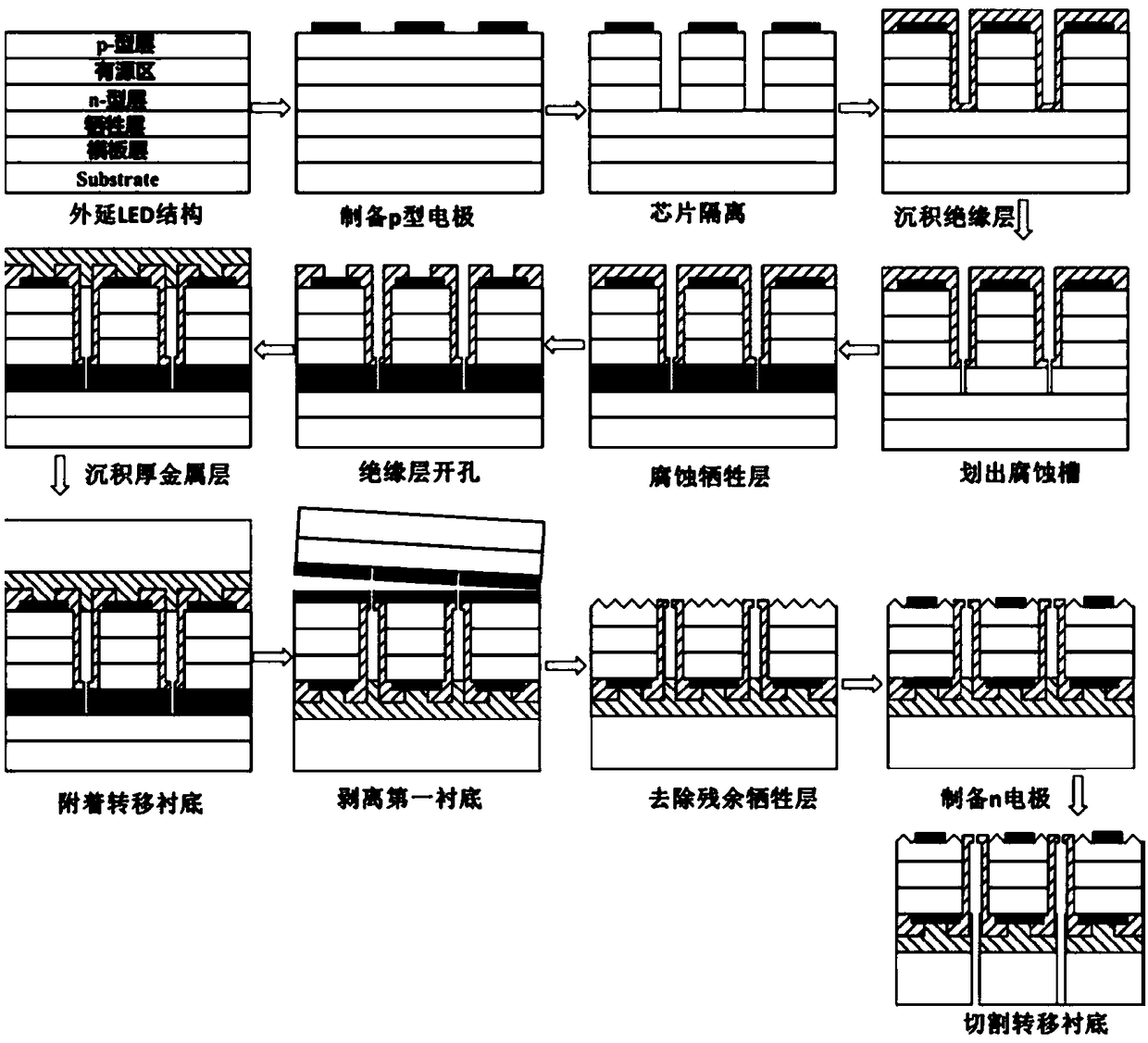

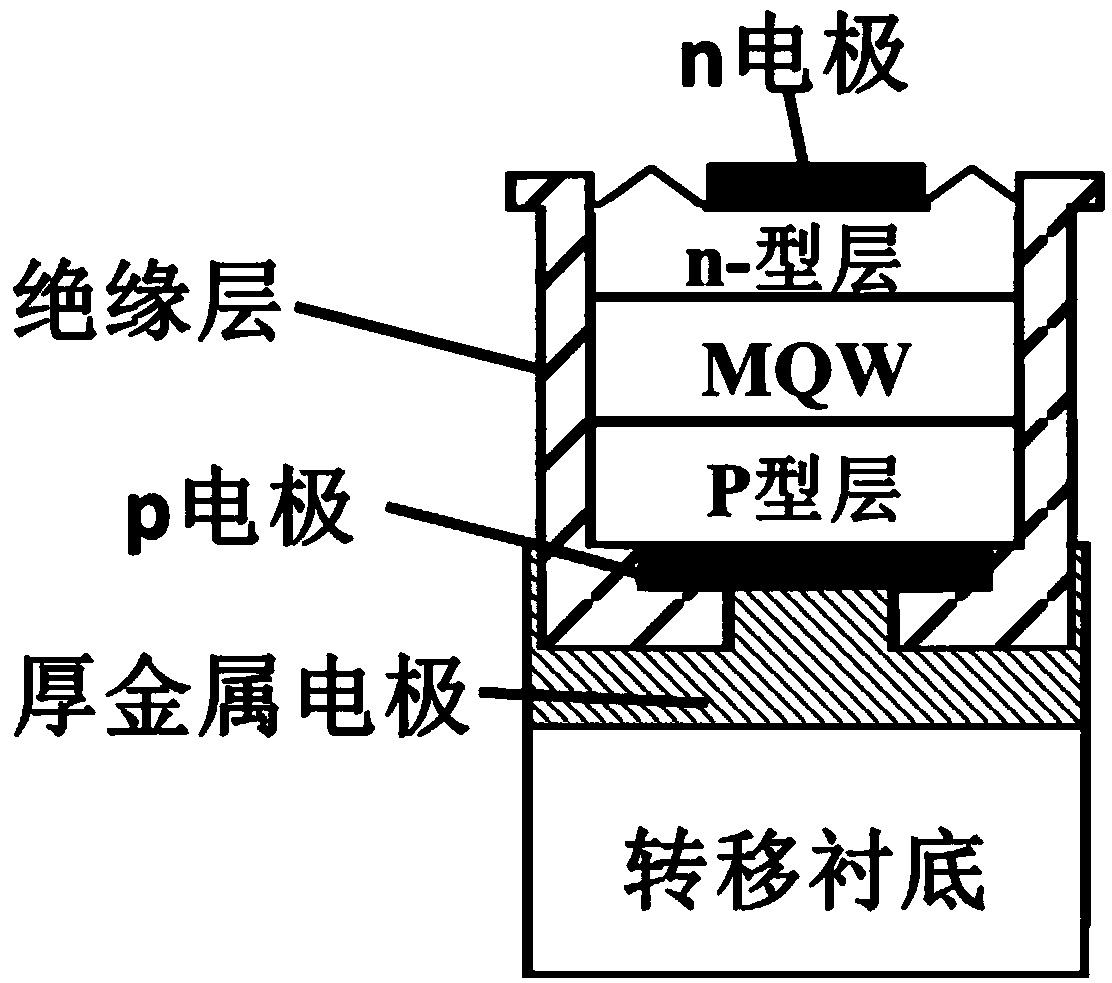

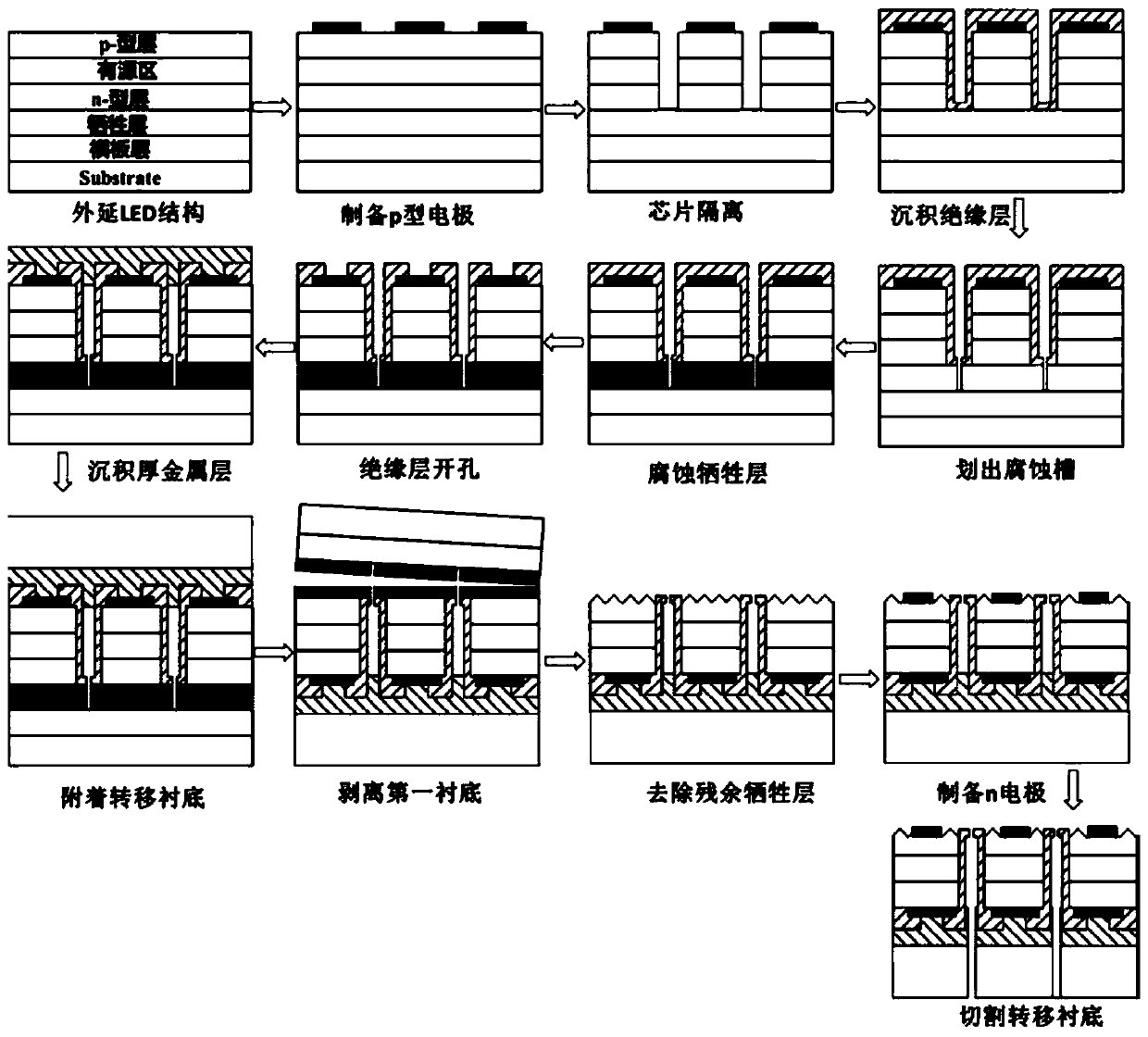

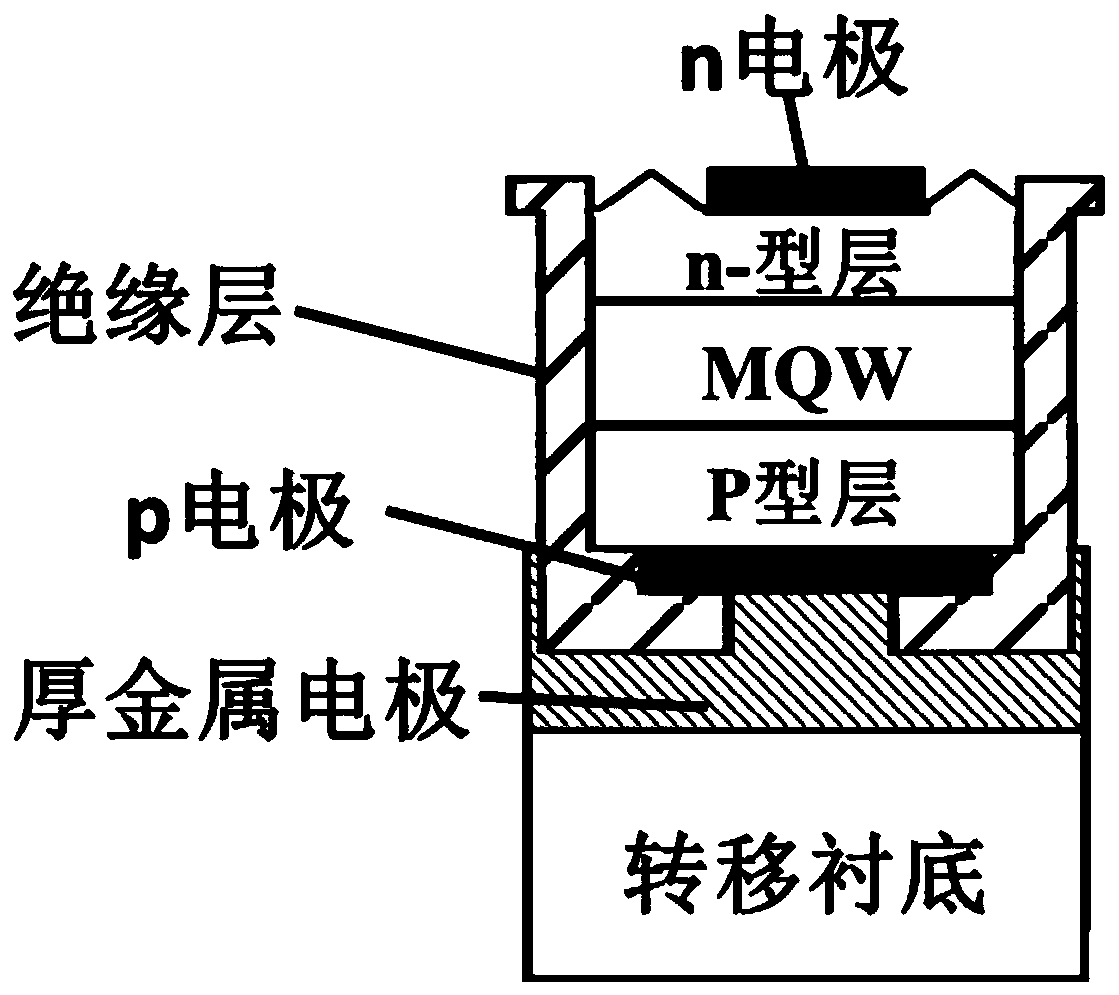

Manufacturing method of vertical structure light emitting diode chip

ActiveCN108878604AHigh thermal conductivityWon't hurtSemiconductor devicesPhoto assistedPhotoelectrochemical etching

The invention provides a preparing method of a vertical structure light-emitting diode (LED) chip. The preparing method corrodes a sacrificial layer in an epitaxial layer of an LED into a porous structure mainly through an electrochemical or photoelectrochemical etching or photo-assisted electrochemical etching method. The bonding strength between the upper and lower epitaxial layers of the sacrificial layer becomes quite weak, and the upper and lower epitaxial layers of the sacrificial layer can be easily peeled off. Compared with a vertical structure LED prepared by a laser lift-off method,the preparing method can solve the problem that the quality of an epitaxial layer material becomes poor due to laser ablation, and the yield is low.

Owner:山西中科潞安紫外光电科技有限公司

Photoelectrochemical etching for chip shaping of light emitting diodes

InactiveUS8569085B2Control roughnessControl smoothnessSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor materialsPhotoelectrochemical etching

A photoelectrochemical (PEC) etch is performed for chip shaping of a device comprised of a III-V semiconductor material, in order to extract light emitted into guided modes trapped in the III-V semiconductor material. The chip shaping involves varying an angle of incident light during the PEC etch to control an angle of the resulting sidewalls of the III-V semiconductor material. The sidewalls may be sloped as well as vertical, in order to scatter the guided modes out of the III-V semiconductor material rather than reflecting the guided modes back into the III-V semiconductor material. In addition to shaping the chip in order to extract light emitted into guided modes, the chip may be shaped to act as a lens, to focus its output light, or to direct its output light in a particular way.

Owner:RGT UNIV OF CALIFORNIA

Method for forming periodic structure

ActiveUS20090227109A1Decorative surface effectsSemiconductor/solid-state device manufacturingPhotoelectrochemical etchingOptoelectronics

A method for forming a periodic structure is disclosed. A structural layer and an optical modulation element are provided. A light is emitted to pass through the optical modulation element to irradiate interference strips on the structural layer. A photoelectrochemical etching (PEC) is performed to form the periodic structure according the interference strips irradiated on the structural layer.

Owner:NAT TAIWAN UNIV

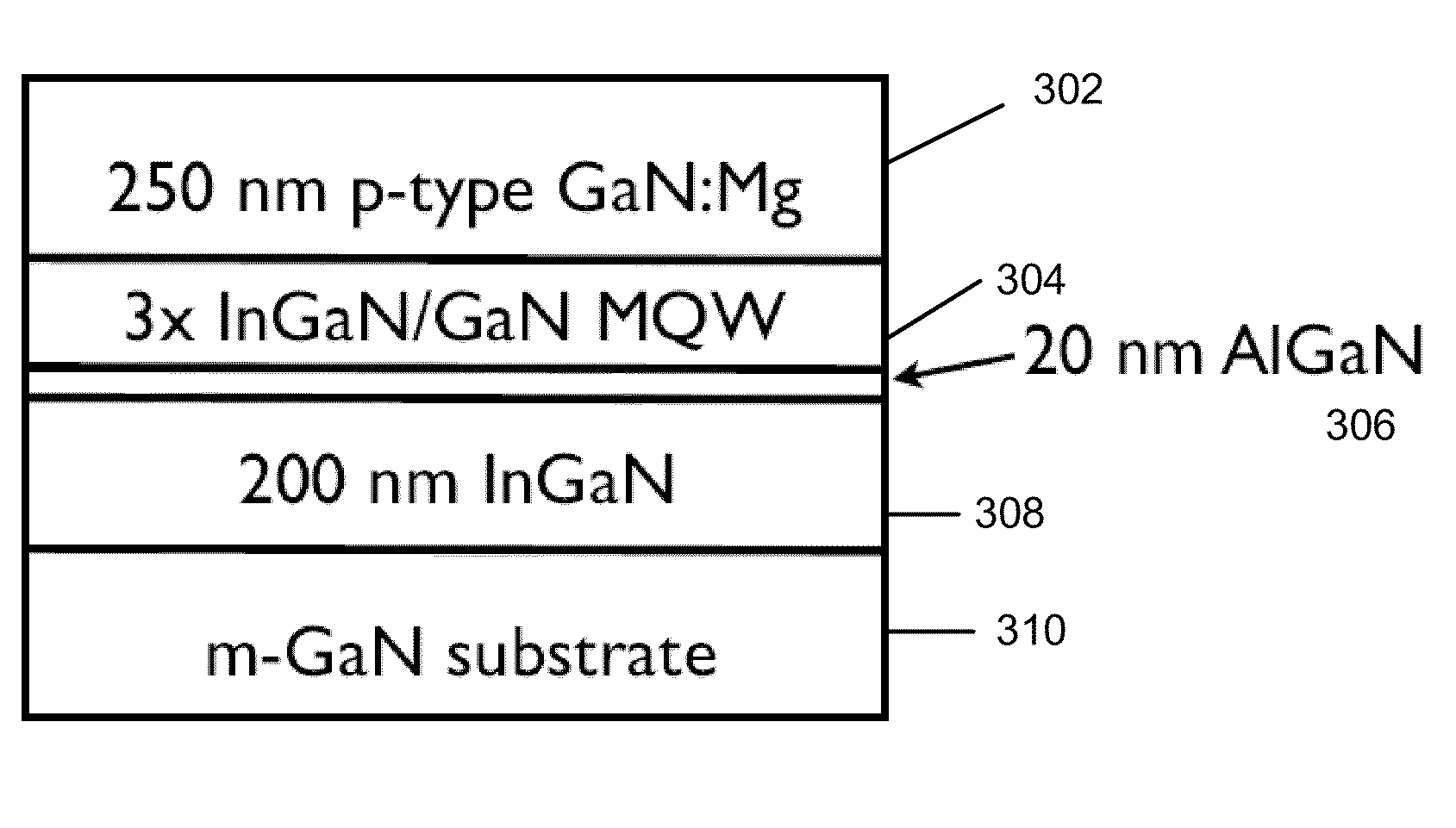

Pec etching of (20-2-1) semipolar gallium nitride for external efficiency enhancement in light emitting diode applications

InactiveUS20140167059A1Improve light extractionIncrease external efficiencySemiconductor/solid-state device manufacturingSemiconductor devicesPhotoelectrochemical etchingPhysical chemistry

A method of performing a photoelectrochemical (PEC) etch on an exposed surface of a semipolar {20-2-1} III-nitride semiconductor, for improving light extraction from and for enhancing external efficiency of one or more active layers formed on or above the semipolar {20-2-1} III-nitride semiconductor.

Owner:RGT UNIV OF CALIFORNIA

Photoelectrochemical etching of P-type semiconductor heterostructures

ActiveUS8053264B2Bringing holes to a surface of the p-type semiconductor layer fasterReduce harmSemiconductor/solid-state device manufacturingSemiconductor devicesElectron holePhotoelectrochemical etching

A method for photoelectrochemical (PEC) etching of a p-type semiconductor layer simply and efficiently, by providing a driving force for holes to move towards a surface of a p-type cap layer to be etched, wherein the p-type cap layer is on a heterostructure and the heterostructure provides the driving force from an internal bias generated internally in the heterostructure; generating electron-hole pairs in a separate area of the heterostructure than the surface to be etched; and using an etchant solution to etch the surface of the p-type layer.

Owner:RGT UNIV OF CALIFORNIA

Method for forming periodic structure

InactiveUS8052883B2Decorative surface effectsOptical articlesPhotoelectrochemical etchingOptoelectronics

Owner:NAT TAIWAN UNIV

Photoelectrochemical etching for laser facets

InactiveUS8263500B2Decorative surface effectsSemiconductor/solid-state device manufacturingPhotoelectrochemical etchingFaceting

A method for fabricating a semiconductor laser device, by etching facets using a photoelectrochemical (PEC) etch, so that the facets are sufficiently smooth to support optical modes within a cavity bounded by the facets.

Owner:RGT UNIV OF CALIFORNIA

Single-flow micro-pore heat exchanger

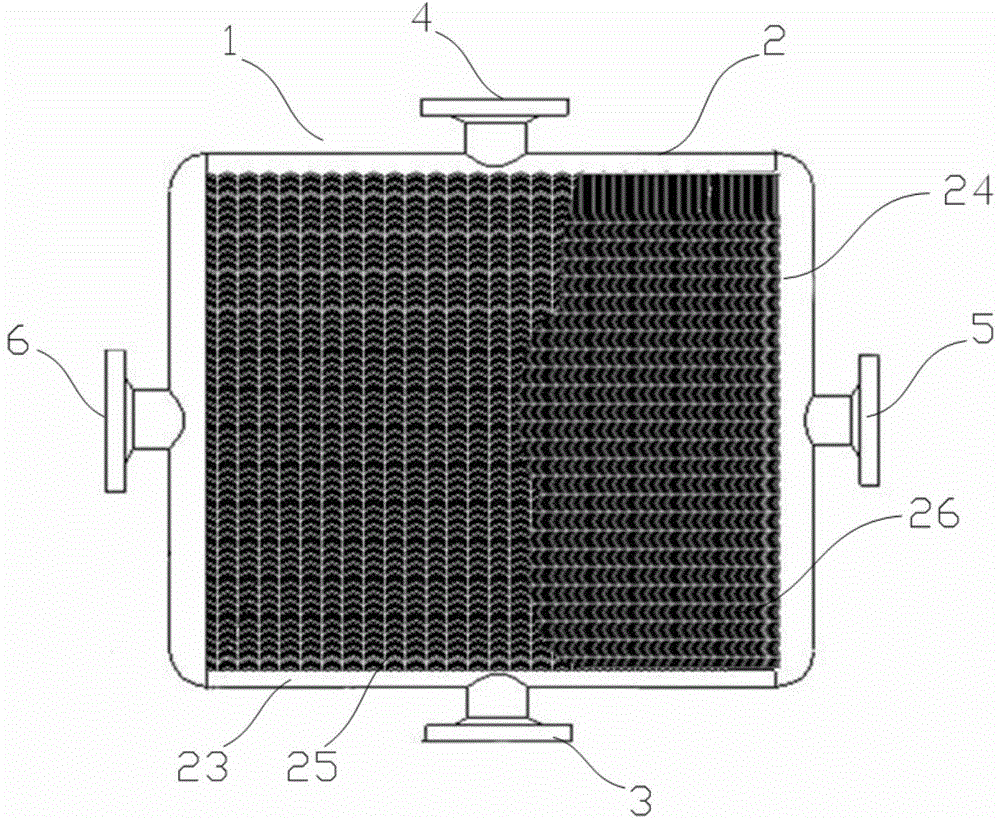

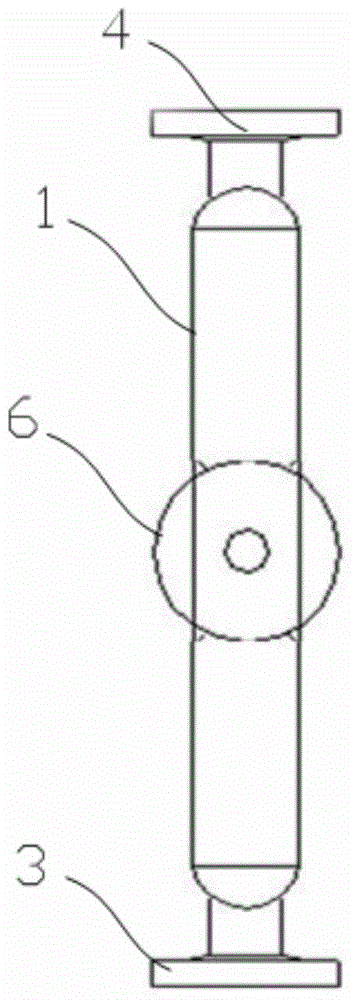

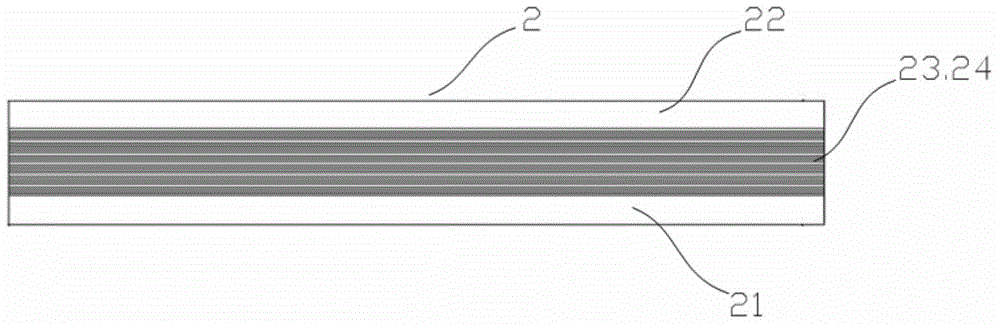

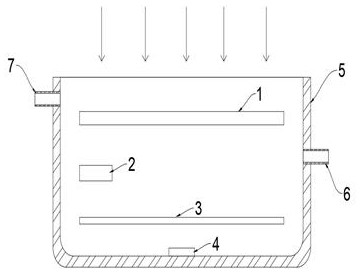

InactiveCN104896979AHigh heat transfer area densityReduce leakageStationary plate conduit assembliesPhotoelectrochemical etchingEngineering

The invention provides a single-flow micro-pore heat exchanger. A heat exchange core comprises a bottom plate, a top plate and at least one layer of cold medium sheet and at least one layer of thermal medium sheet which are clamped between the bottom plate and the top plate. The cold medium sheets and the thermal medium sheets are overlapped alternatively. A plurality of parallel cold medium flow channels are etched in the cold medium sheets, a plurality of parallel thermal medium flow channels are etched in the thermal medium sheets, and the flow directions of the thermal medium flow channel and the flow directions of the cold medium flow channels are vertical. By means of the heat exchanger, the heat transfer area density is high, a photoelectrochemical etching and atomic diffusion bonding technology is used, and accordingly, channel structures of various shapes can be formed, and leakage and vibration losses can be reduced effectively; the heat exchanger is stable in structure, good in safety, small in size, low in weight, convenient to mount and maintenance-free.

Owner:上海数映科技有限公司

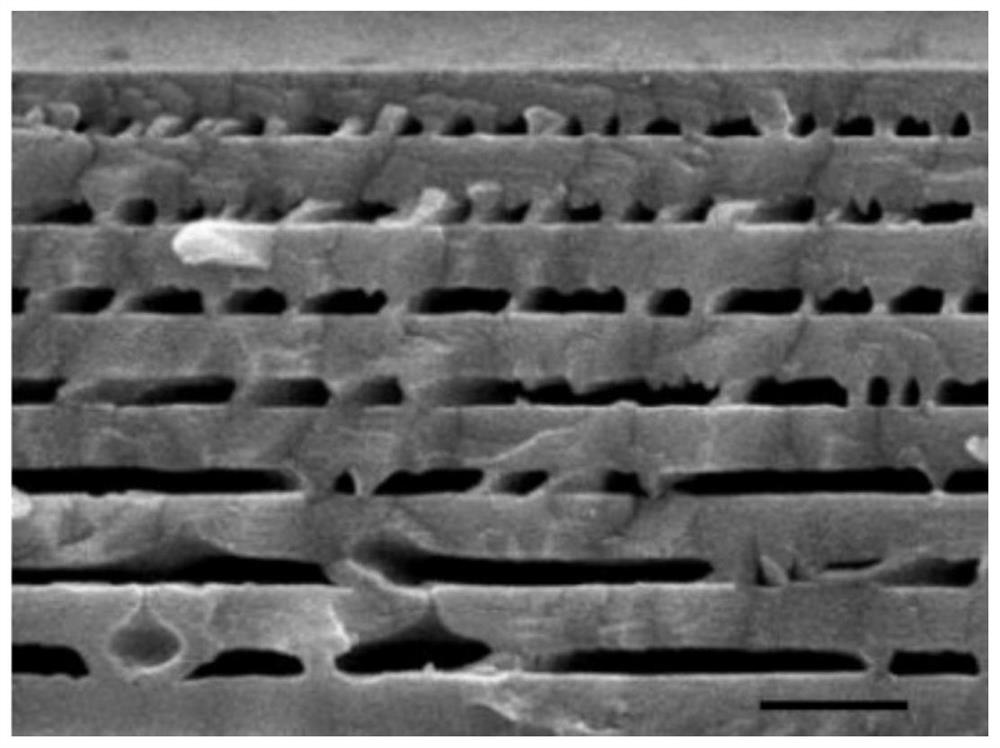

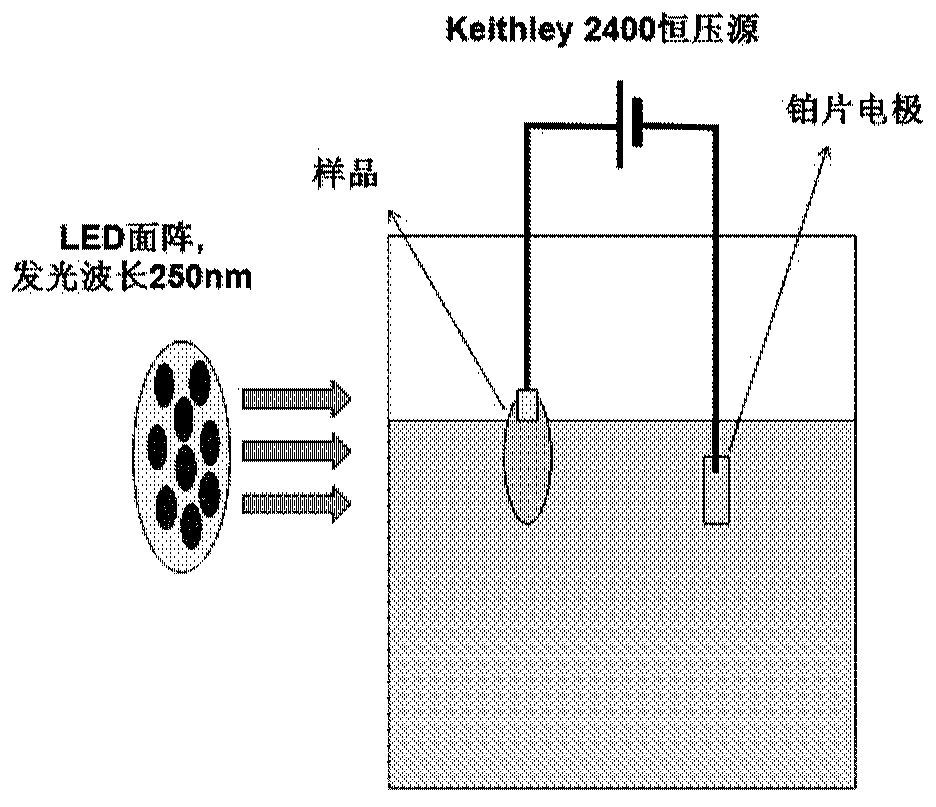

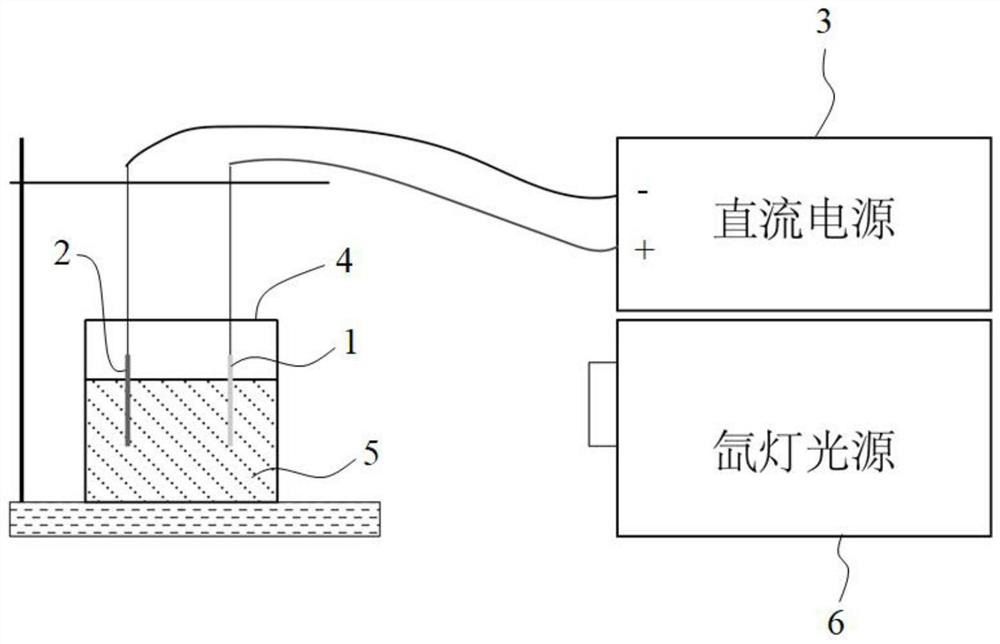

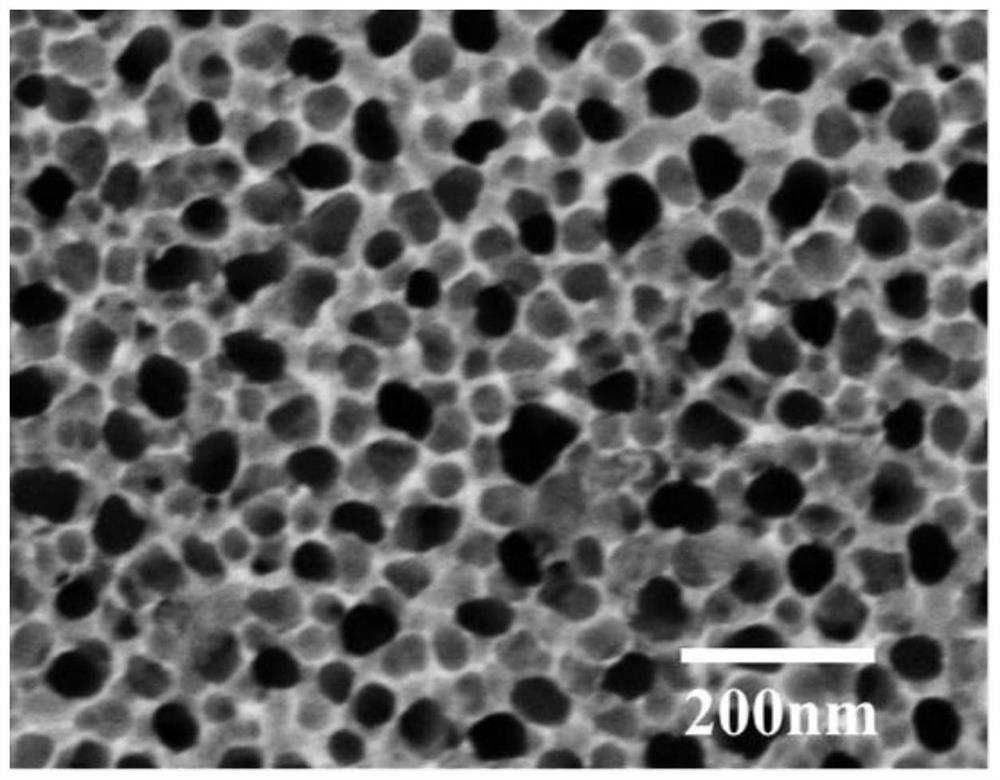

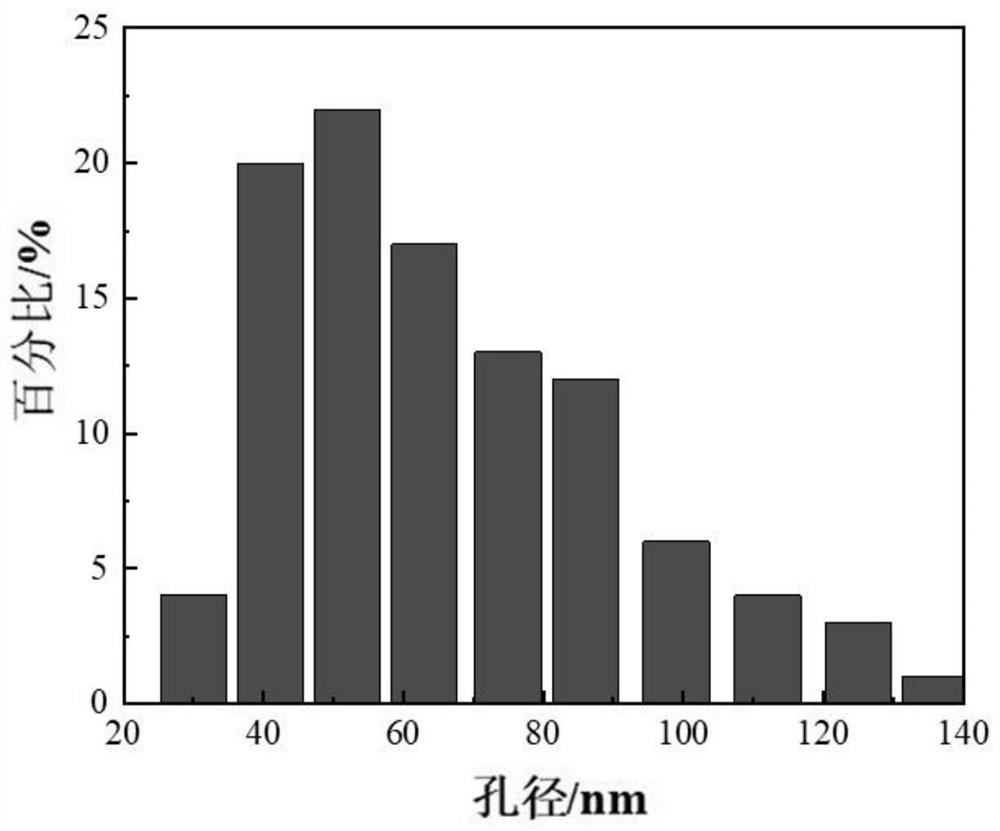

Preparation method of novel InGaN-based photo-anode

ActiveCN112095117ASpecular reflection effectReduce defect densityVacuum evaporation coatingEnergy inputPhotoelectrochemical etchingOhmic contact

The invention discloses a preparation method of a novel InGaN-based photo-anode, which is specifically implemented according to the following steps of: 1, carrying out constant-voltage etching on a GaN multi-layer structure by adopting a photoelectrochemical etching technology in an acid solution to prepare a mesoporous GaN mirror; and 2, by taking a mesoporous GaN mirror as a substrate, firstly,epitaxially growing an InGaN / GaN layer by adopting an MOCVD technology, modulating an In component through energy band engineering, modulating a band gap of the In component, and then, evaporating anohmic contact electrode by adopting an electron beam evaporation technology to prepare an InGaN-based photo-anode. and the method provided by the invention can be used for preparing the photo-anode electrode with low starting voltage, high efficiency and strong stability.

Owner:XI'AN POLYTECHNIC UNIVERSITY

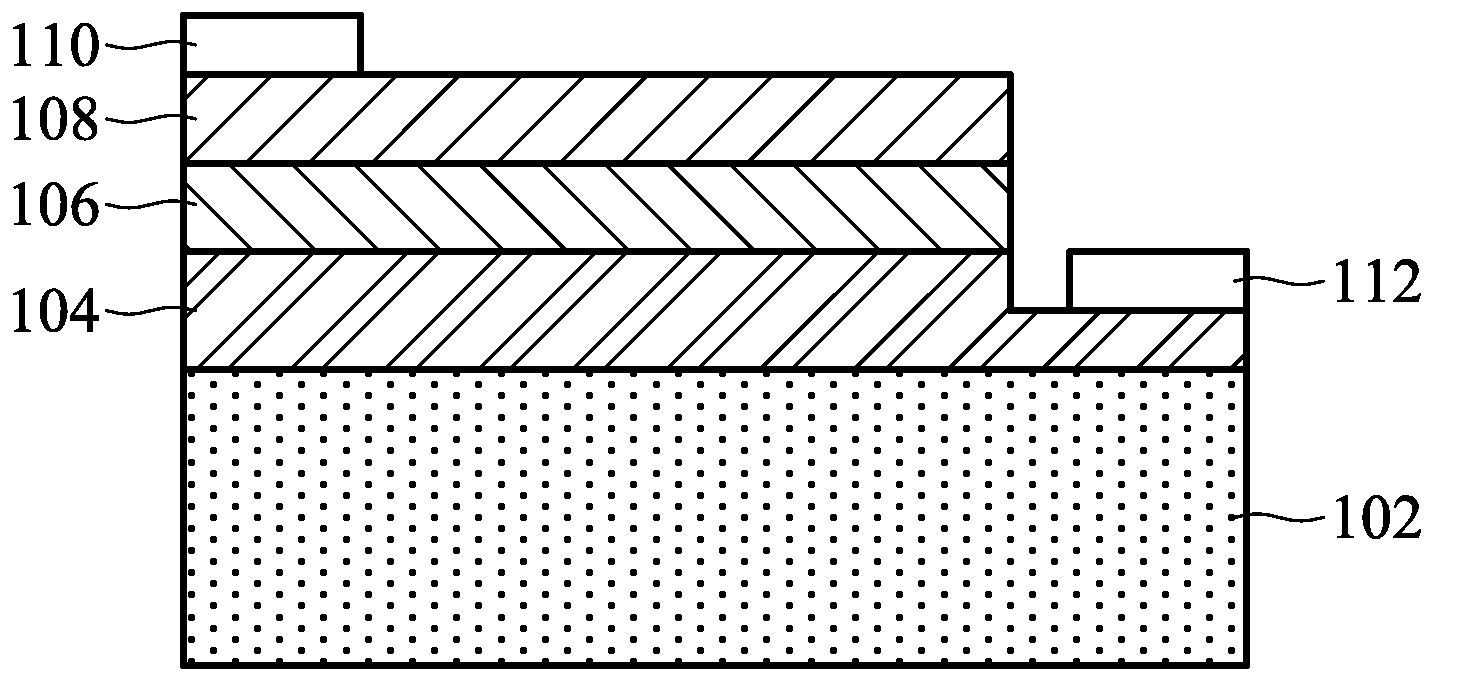

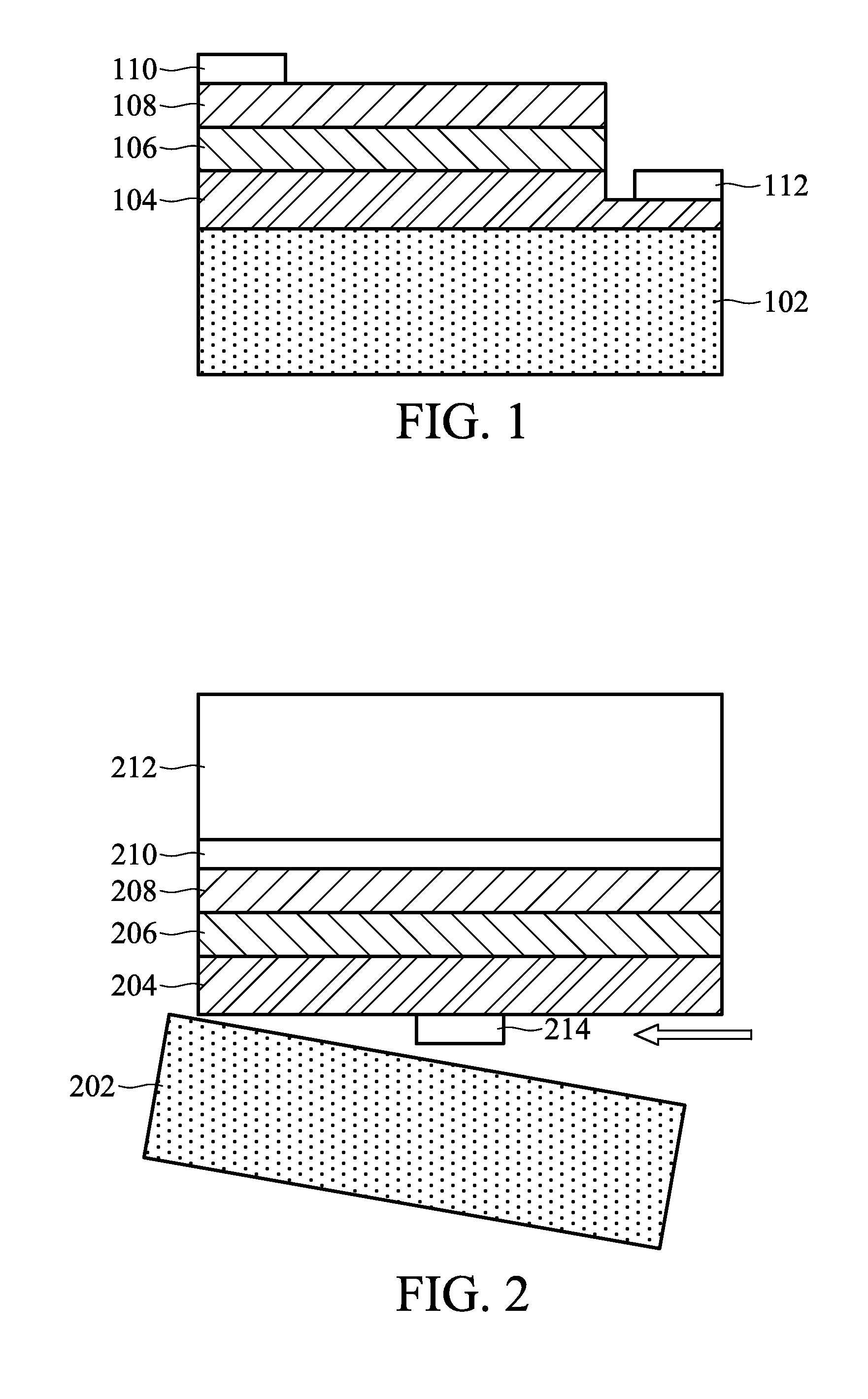

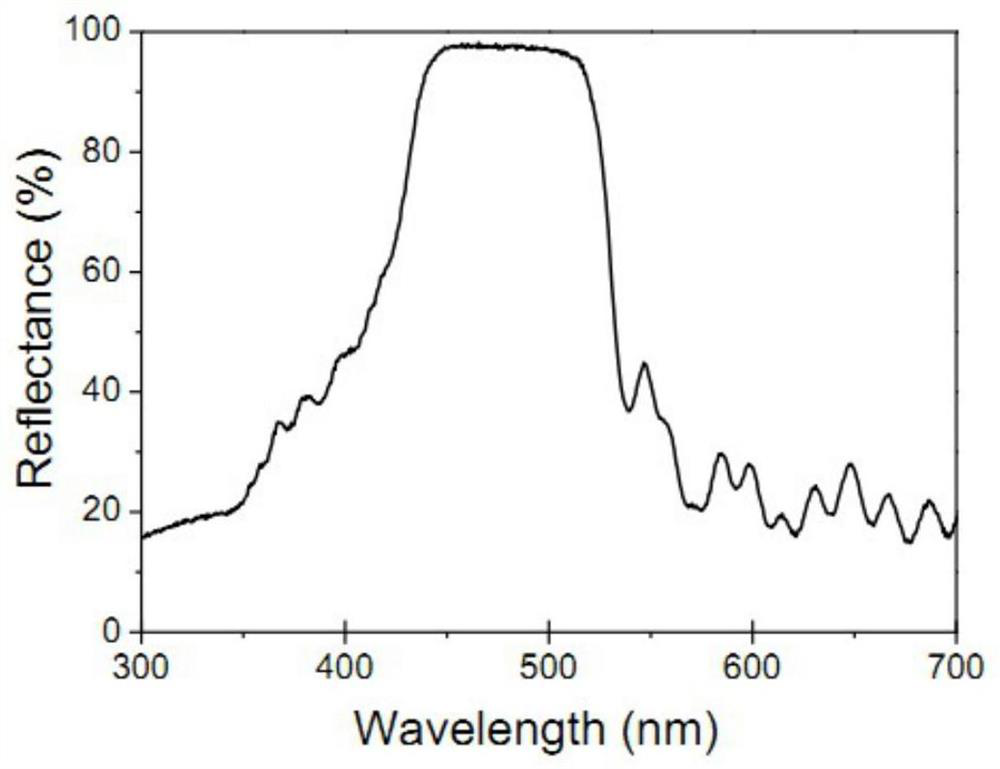

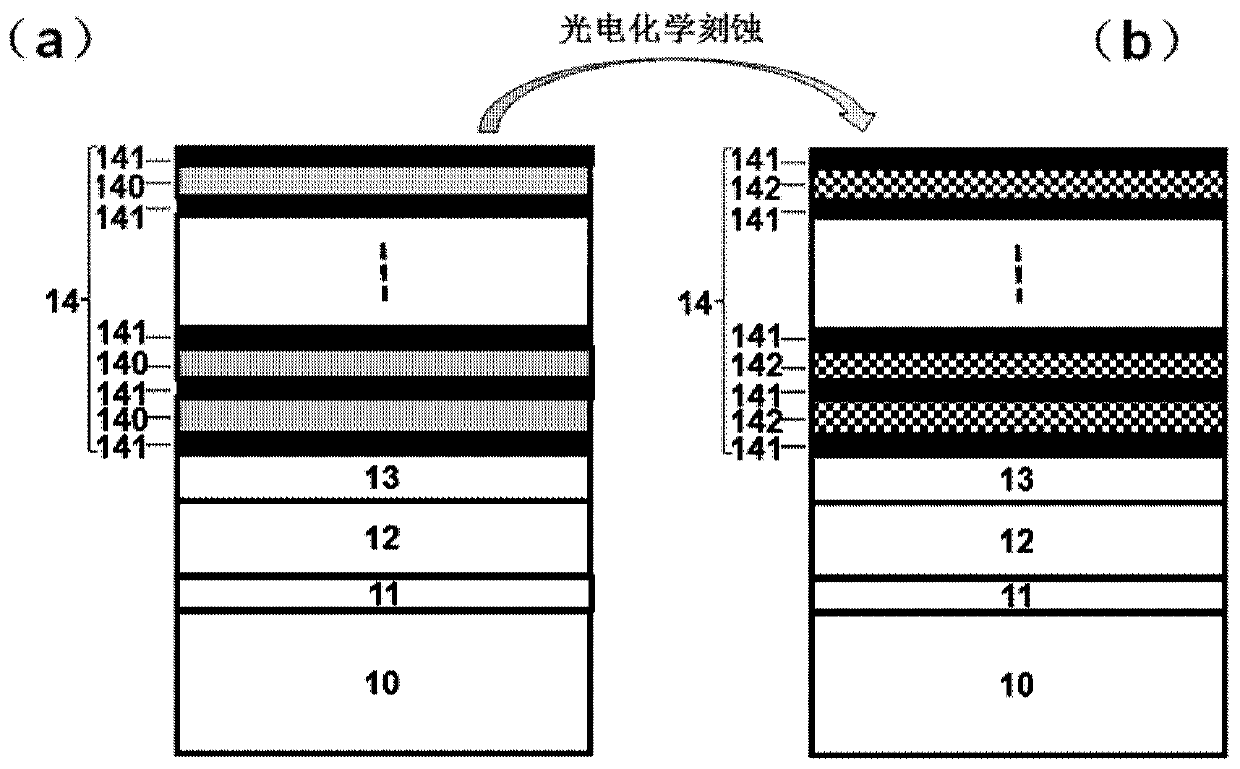

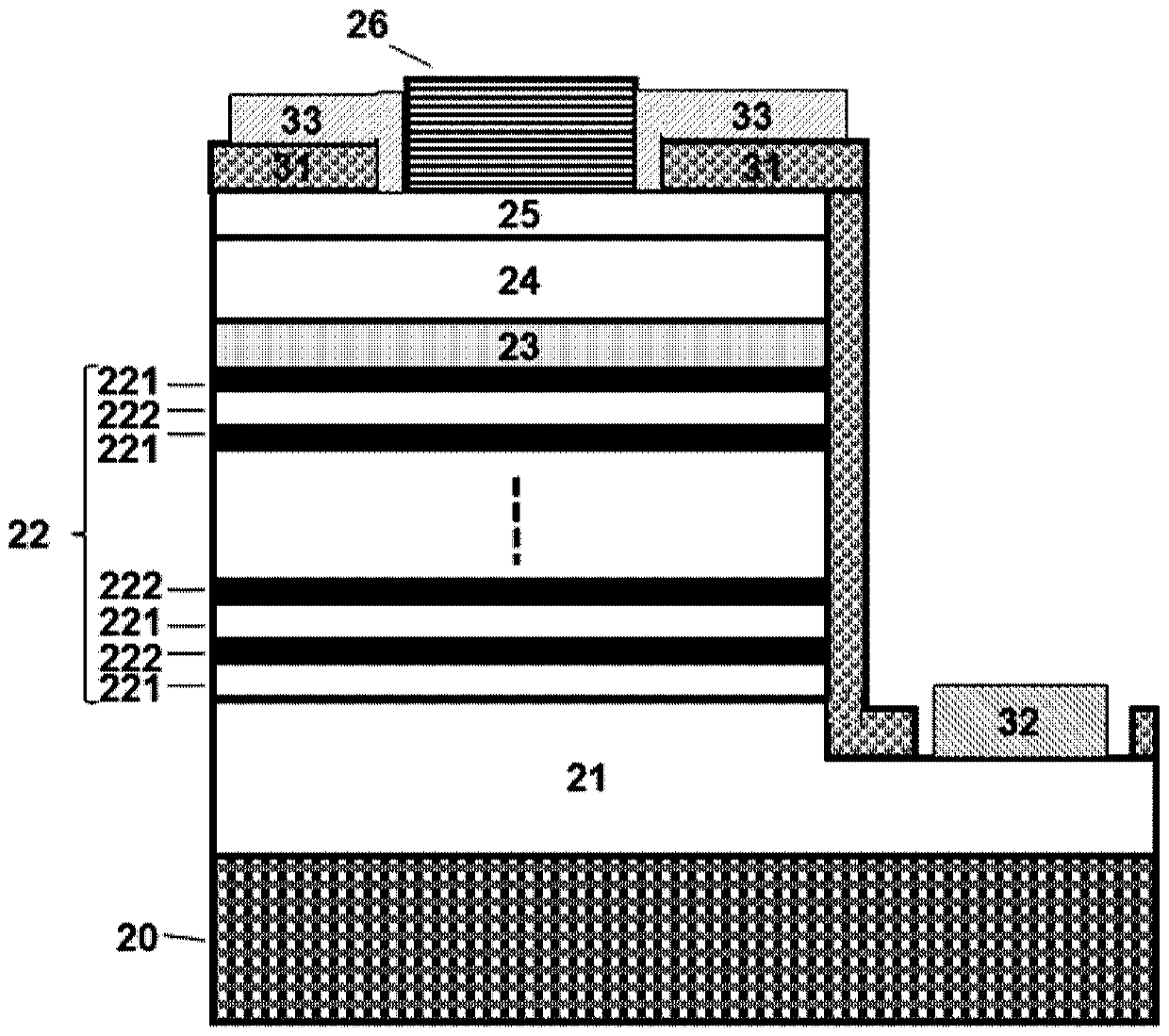

Ultraviolet distributed Bragg mirror based on porous AlGaN and preparation method thereof

ActiveCN110190511AImprove reflectivityWide cut-off bandwidthLaser detailsSemiconductor lasersChemical reactionPhotoelectrochemical etching

The invention relates to an ultraviolet distributed Bragg mirror based on porous AlGaN and a preparation method thereof. The ultraviolet distributed Bragg mirror based on porous AlGaN includes a substrate, a nucleation layer, a buffer layer, a stress regulation layer, and Alx(Ga1-x)N layers and porous Aly(Ga1-y)N layers which are in a multi-cycle alternately stacking mode. The invention further provides the preparation method of the ultraviolet distributed Bragg mirror based on the porous AlGaN, the nucleation layer, the buffer layer, the stress regulation layer, and the Alx(Ga1-x)N layers andthe porous Aly(Ga1-y)N layers in a multi-cycle alternately stacking mode are stacked on the substrate, photoelectrochemical etching is then performed, the AlGaN layer is made porous by band gap selectivity of photoelectrochemical reaction, and the ultraviolet distributed Bragg mirror based on the porous AlGaN is formed.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

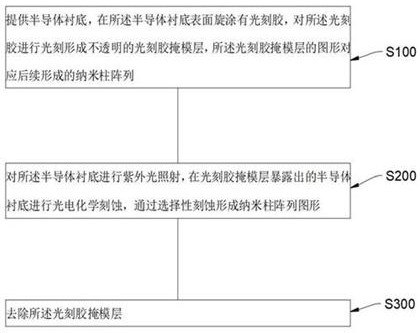

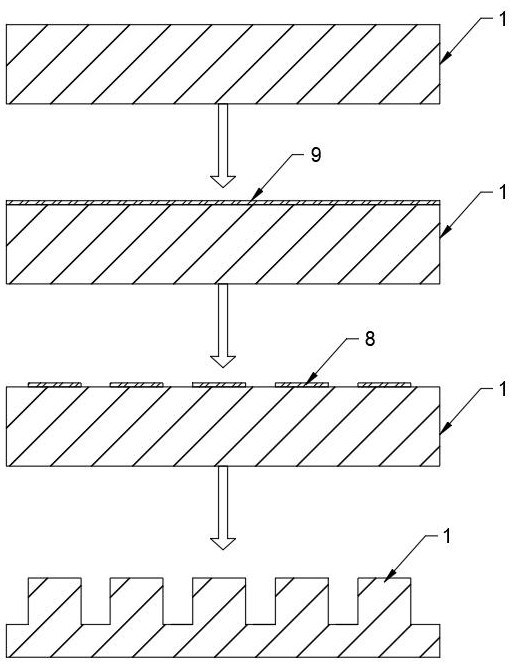

Preparation method of nano-pillar array

PendingCN114496768AGood sidewall morphologyImprove efficiencySemiconductor/solid-state device manufacturingNanotechnologyNanopillarPhotoelectrochemical etching

The invention relates to the field of process processing, in particular to a method for forming a nanopillar array on a semiconductor substrate, which comprises the following steps of: providing the semiconductor substrate, coating photoresist on the semiconductor substrate, and photoetching on the photoresist to form a pattern; a mask layer is formed on the prepared pattern, and light propagation is stopped through the mask layer; according to the method, a semiconductor substrate containing a mask layer is subjected to electrochemical etching, patterns with different heights are obtained by controlling etching conditions, then the mask layer is removed, the semiconductor substrate comprises a silicon carbide substrate slice or a gallium nitride substrate slice, the length and width of the semiconductor substrate are 2-8 inches, the thickness of the semiconductor substrate is 200-500 micrometers, and the thickness of the semiconductor substrate is 1-10 micrometers. An electron beam direct writing technology is adopted in the photoetching mode, and the pattern is in a nanopillar array shape. By adopting the photoelectrochemical etching method, the large-scale preparation of the nano-pillar array with controllable diameter size and height can be realized on the surface of the wafer-level wide bandgap semiconductor substrate slice, the process is simple, and the yield is high.

Owner:ZHEJIANG UNIV HANGZHOU GLOBAL SCI & TECH INNOVATION CENT

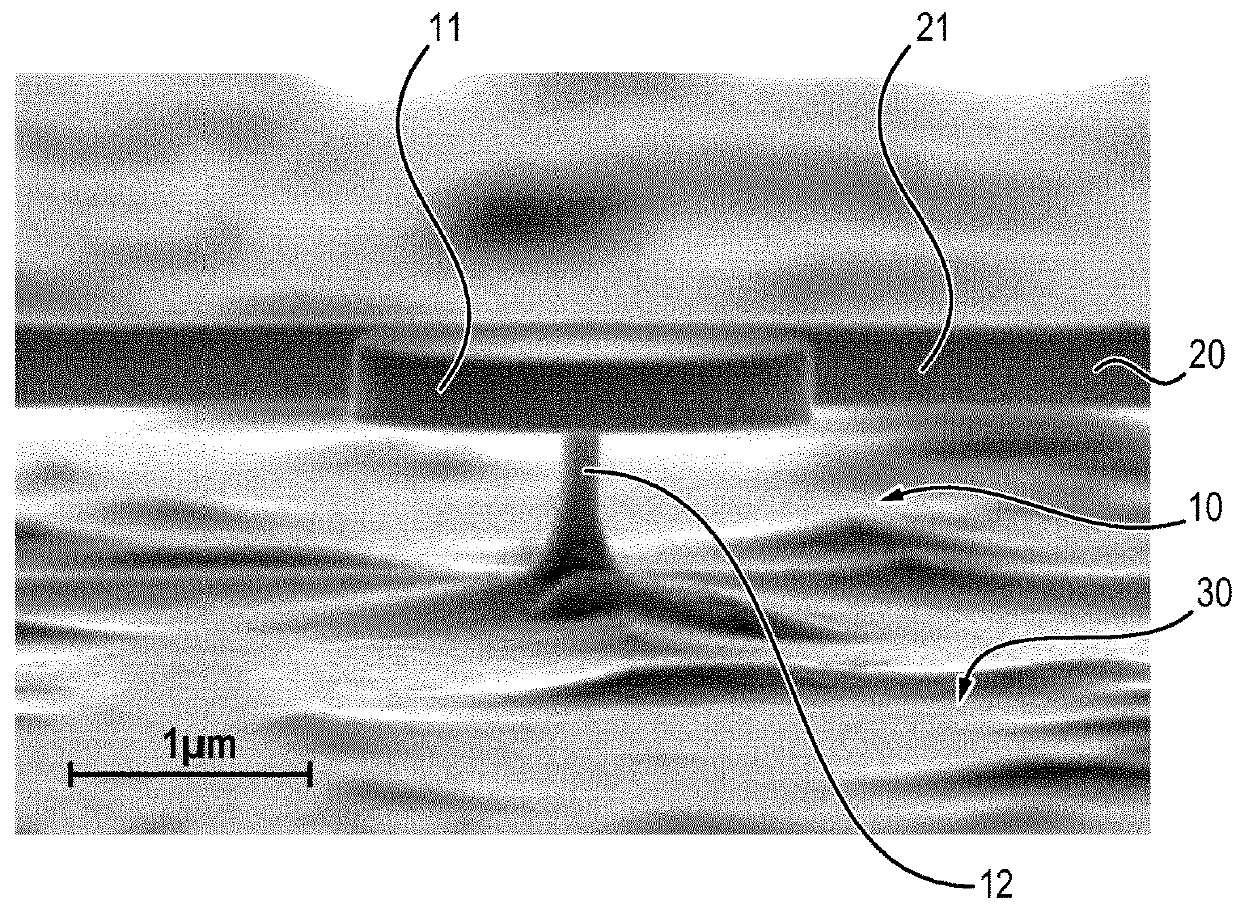

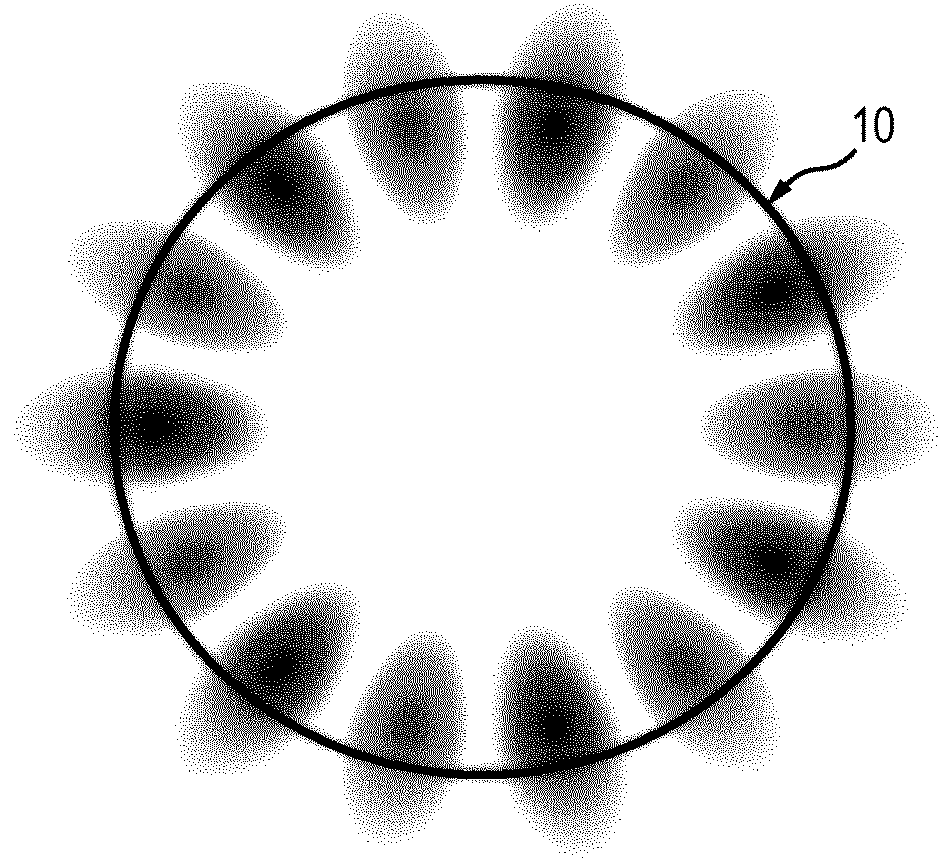

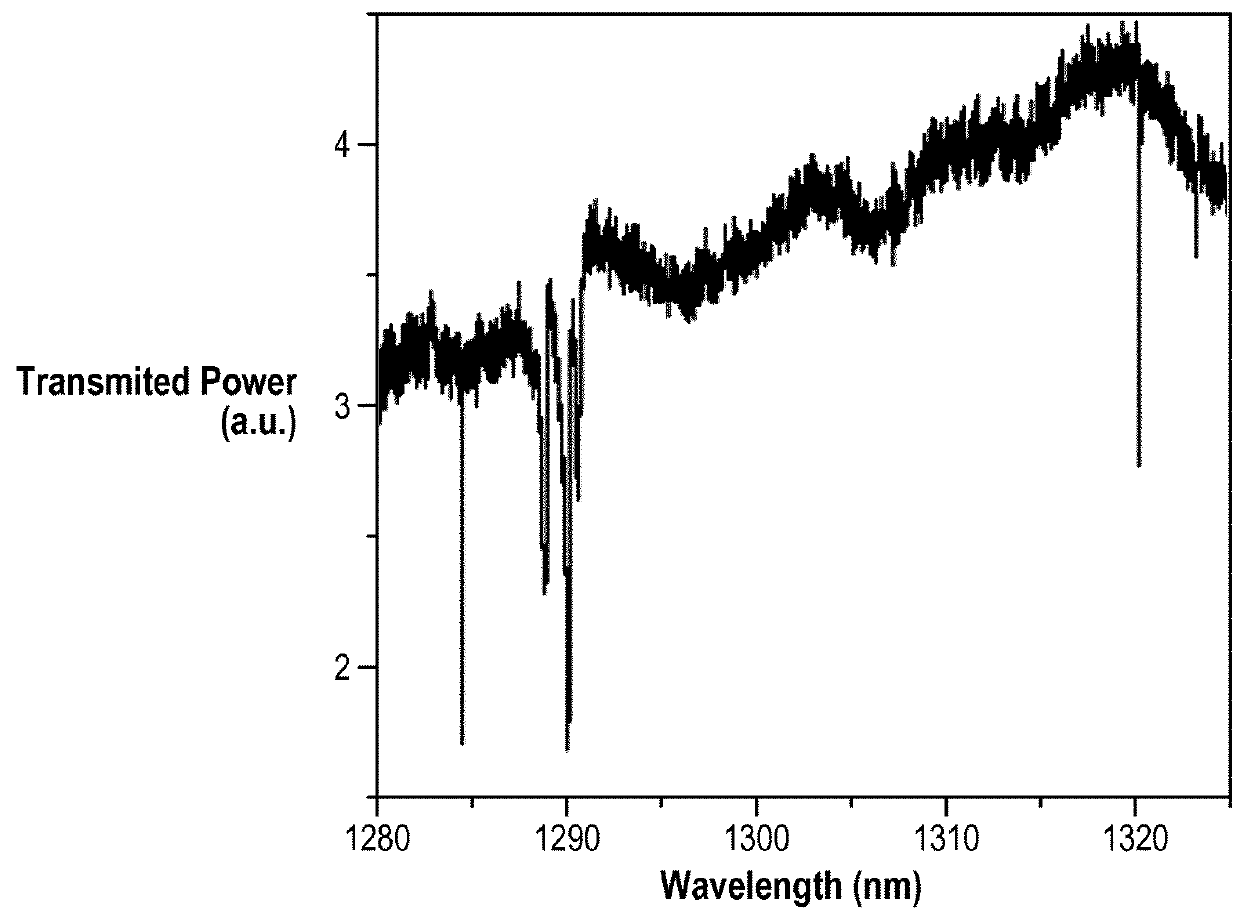

Method for tuning one or more resonator(s)

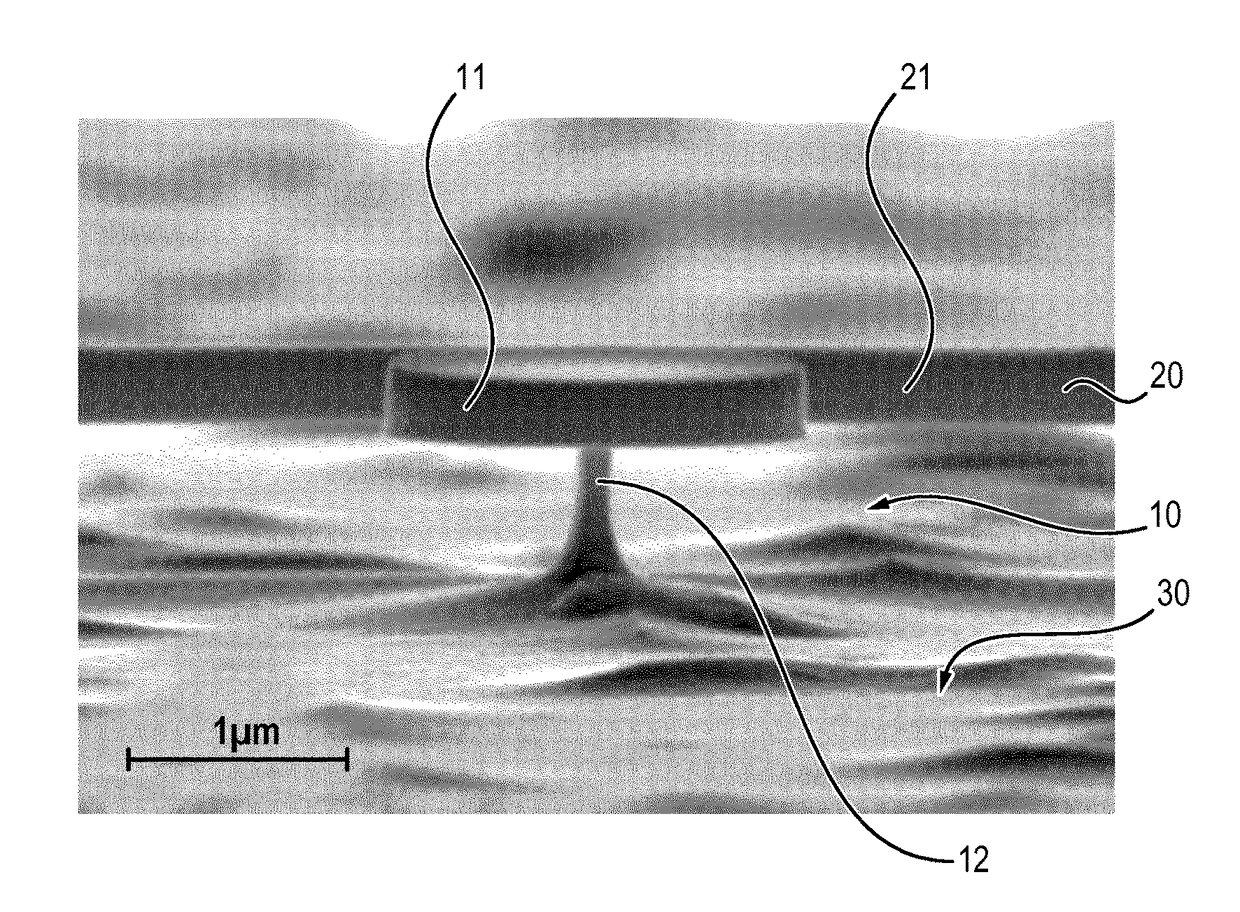

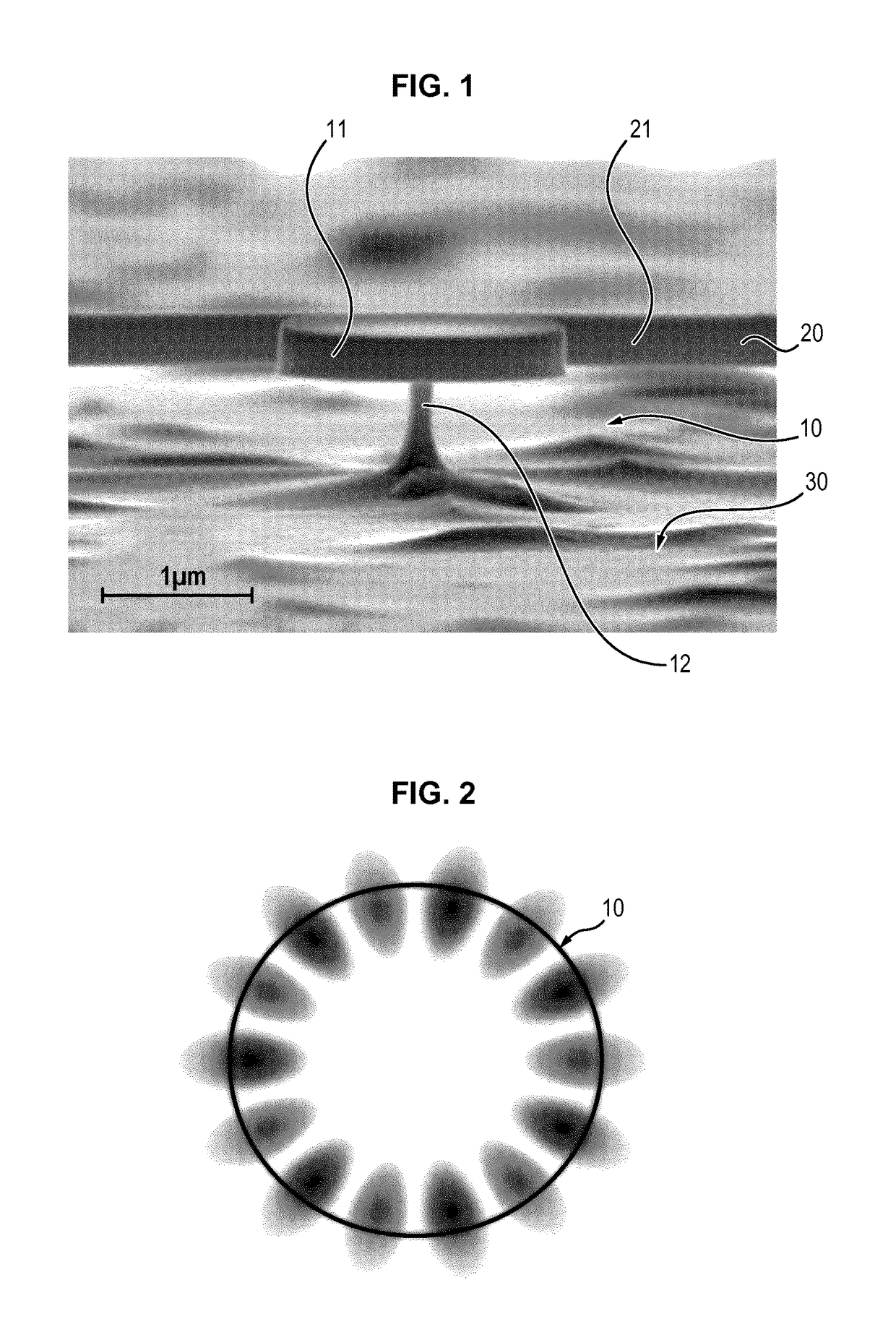

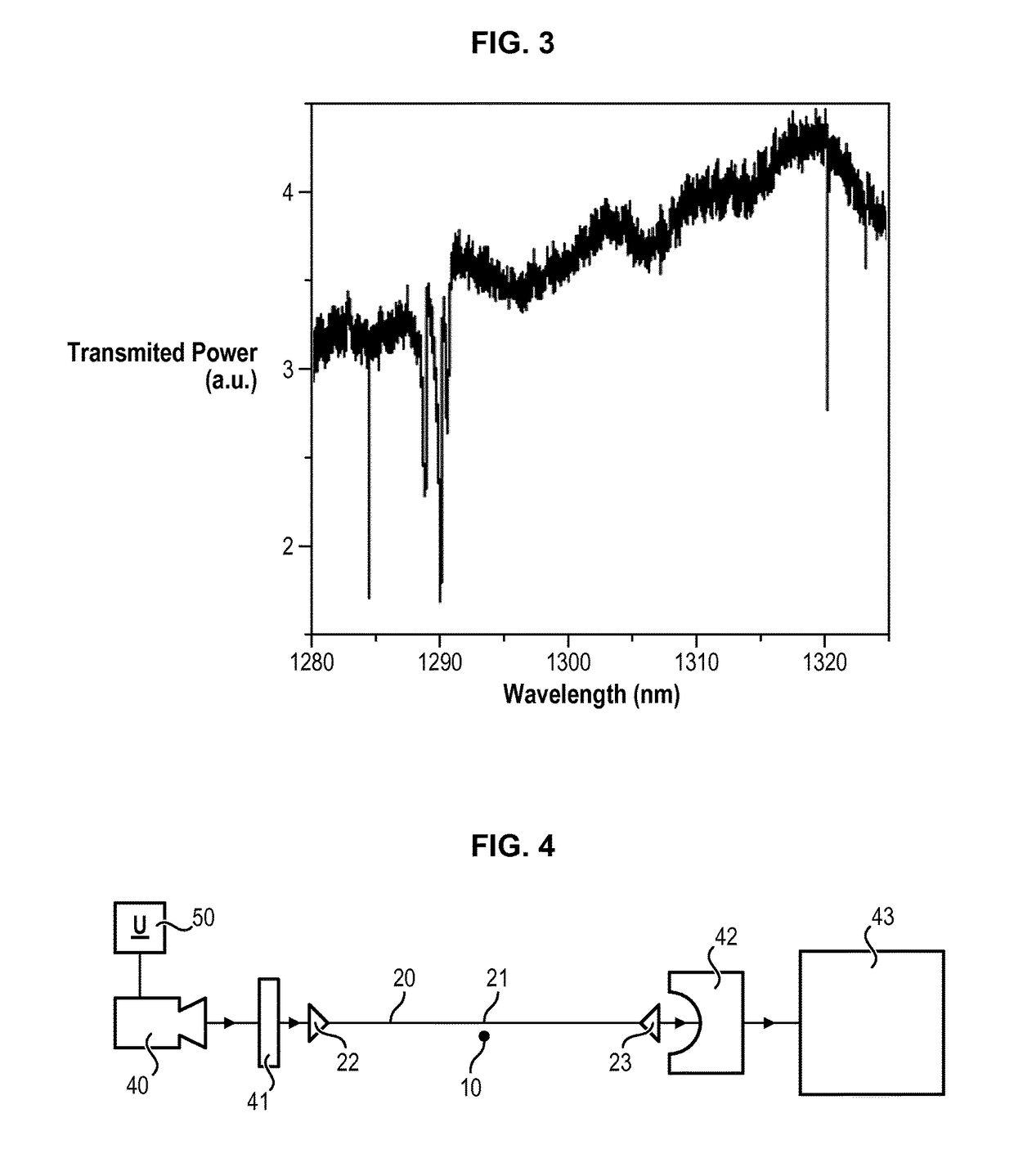

ActiveUS20180059412A1Wide rangeEasy to disassembleDiffraction gratingsOptical waveguide light guidePhotoelectrochemical etchingResonance wavelength

The invention concerns a method for tuning at a targeted resonance wavelength at least one micro and / or nanophotonic resonator, the resonator having dimensions defining resonance wavelength of said resonator, the resonator being immersed in a fluid containing ions so that the resonator is surrounded by said fluid, wherein the method comprises a step of injecting light, having a light wavelength equal to the resonance wavelength, into the resonator, so that the injected light resonates within the resonator and triggers a photo-electrochemical etching process enabled by the surrounding fluid containing ions, said etching process being enhanced by the optical resonance which amplifies light intensity in the photonic resonator, the etching decreasing dimensions of the photonic resonator, hereby lowering and tuning the resonance wavelength of the photonic resonator.

Owner:CENT NAT DE LA RECHERCHE SCI +1

Method for tuning one or more resonator(s)

ActiveUS9995929B2Made preciselyMaximum precisionDiffraction gratingsOptical waveguide light guidePhotoelectrochemical etchingResonance wavelength

The invention concerns a method for tuning at a targeted resonance wavelength at least one micro and / or nanophotonic resonator, the resonator having dimensions defining resonance wavelength of said resonator, the resonator being immersed in a fluid containing ions so that the resonator is surrounded by said fluid, wherein the method comprises a step of injecting light, having a light wavelength equal to the resonance wavelength, into the resonator, so that the injected light resonates within the resonator and triggers a photo-electrochemical etching process enabled by the surrounding fluid containing ions, said etching process being enhanced by the optical resonance which amplifies light intensity in the photonic resonator, the etching decreasing dimensions of the photonic resonator, hereby lowering and tuning the resonance wavelength of the photonic resonator.

Owner:CENT NAT DE LA RECHERCHE SCI +1

Etching solution for photoelectrochemical etching of gallium nitride

ActiveCN112779013BEtching is effectiveAvoid damageFinal product manufactureSemiconductor/solid-state device manufacturingPhotoelectrochemical etchingPhotoelectrochemistry

The invention discloses an etchant for photoelectrochemically etching gallium nitride. The etchant is composed of amino acid or its derivatives dissolved in a solvent. The invention uses amino acid or its derivatives as an etchant to photoelectrochemically etch gallium nitride, which can effectively etch gallium nitride, and the etching process has low equipment requirements, convenient operation, simple process and environmental protection, which is beneficial to The damage to the surface of the material is small.

Owner:SUZHOU INST OF NANO TECH & NANO BIONICS CHINESE ACEDEMY OF SCI

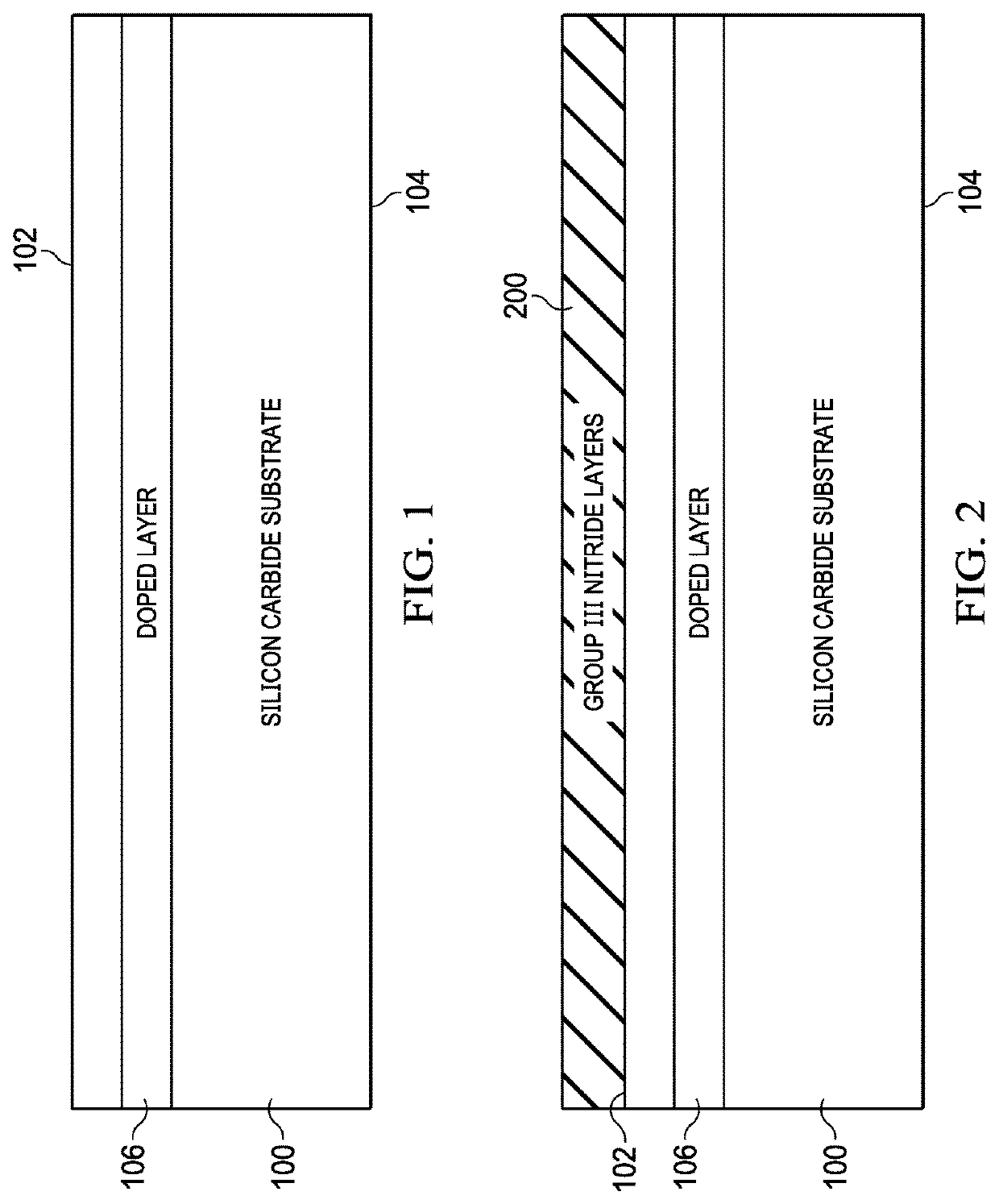

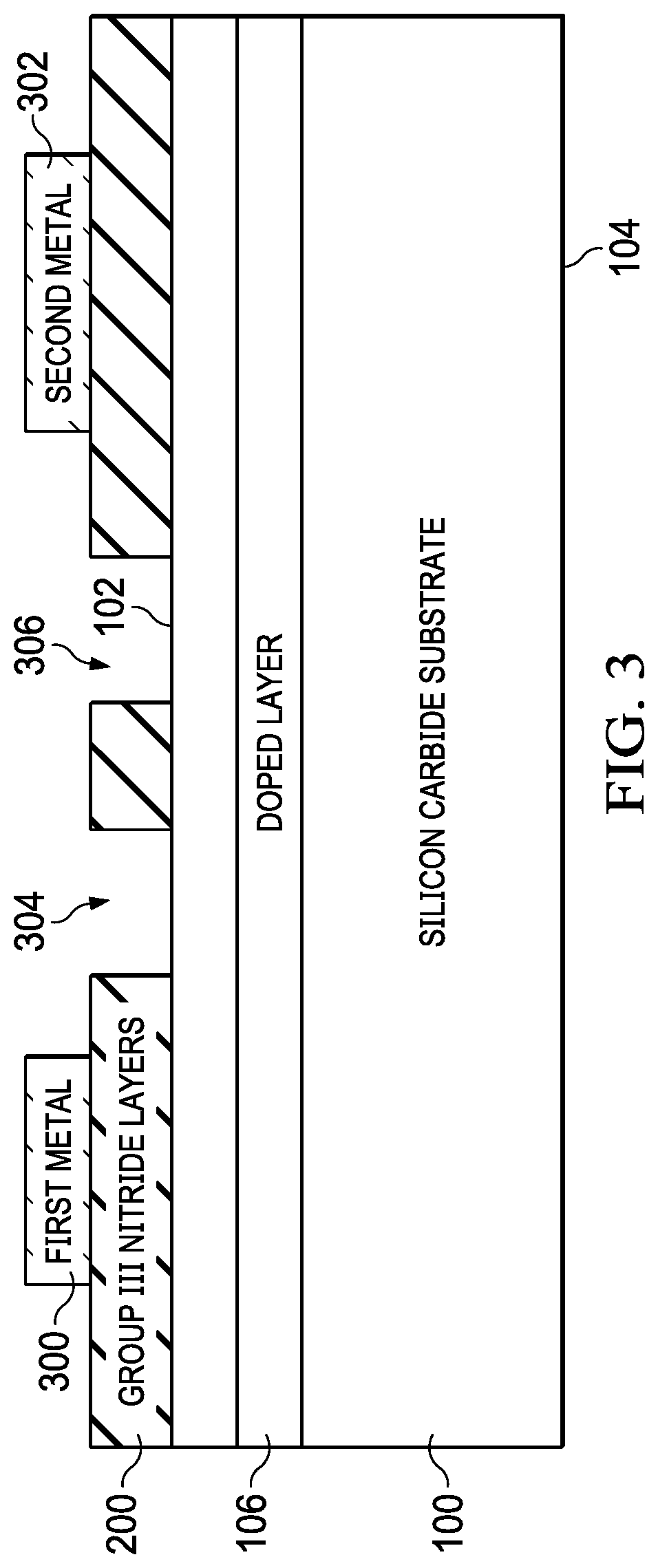

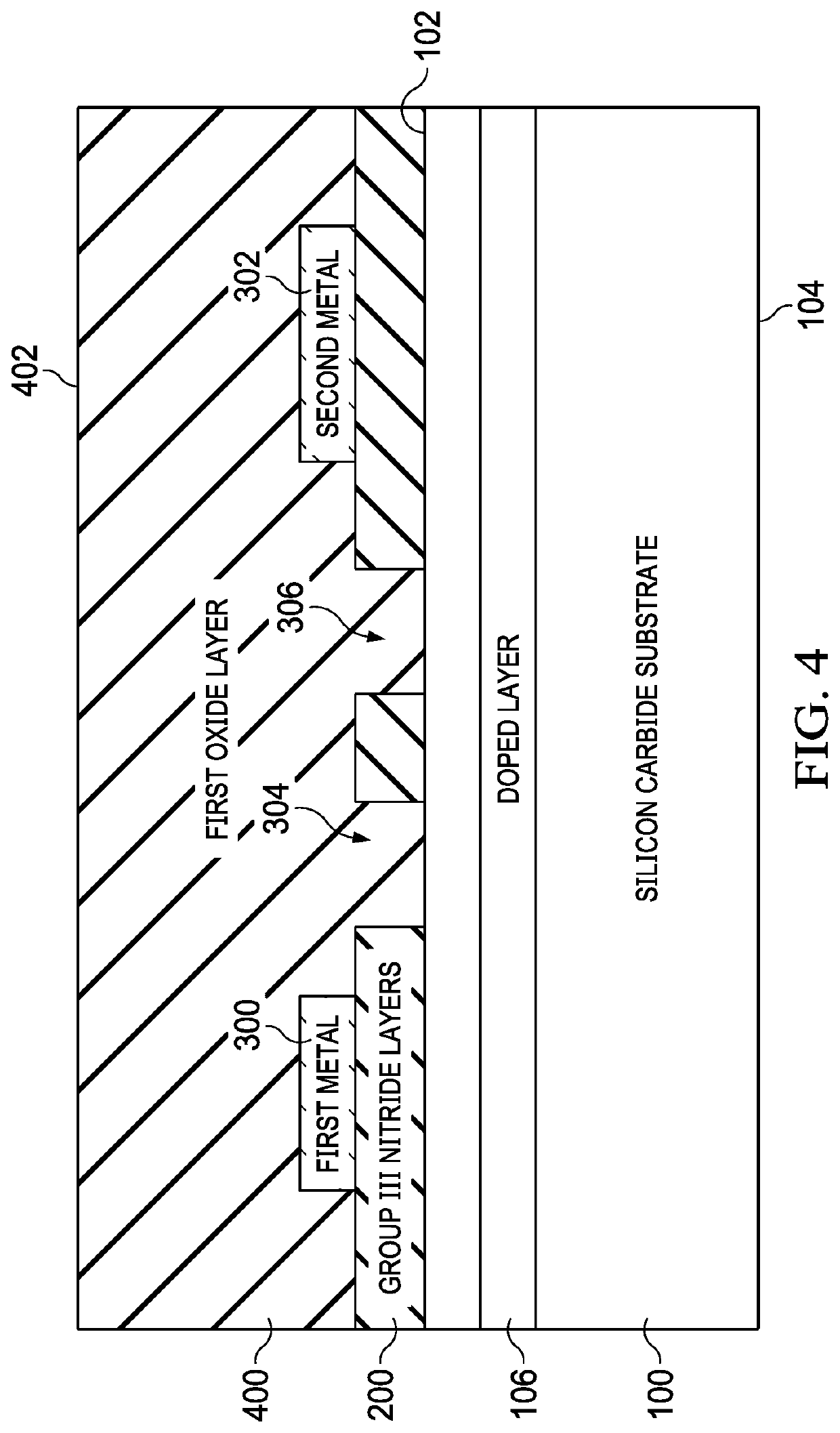

Fabricating a silicon carbide and nitride structures on a carrier substrate

ActiveUS11361964B2Semiconductor/solid-state device manufacturingNon-linear opticsCarbide siliconPhotoelectrochemical etching

A method, apparatus, and system for forming a semiconductor structure. A first oxide layer located on a set of group III nitride layers formed on a silicon carbide substrate is bonded to a second oxide layer located on a carrier substrate to form an oxide layer located between the carrier substrate and the set of group III nitride layers. The silicon carbide substrate has a doped layer. The silicon carbide substrate having the doped layer is etched using a photo-electrochemical etching process, wherein a doping level of the doped layer is such that the doped layer is removed and a silicon carbide layer in the silicon carbide substrate remains unetched. The semiconductor structure is formed using the silicon carbide layer and the set of group III nitride layers.

Owner:THE BOEING CO

A method of manufacturing a vertical light-emitting diode chip

ActiveCN108878604BHigh thermal conductivityWon't hurtSemiconductor devicesPhotoelectrochemical etchingLaser cautery

The invention provides a preparing method of a vertical structure light-emitting diode (LED) chip. The preparing method corrodes a sacrificial layer in an epitaxial layer of an LED into a porous structure mainly through an electrochemical or photoelectrochemical etching or photo-assisted electrochemical etching method. The bonding strength between the upper and lower epitaxial layers of the sacrificial layer becomes quite weak, and the upper and lower epitaxial layers of the sacrificial layer can be easily peeled off. Compared with a vertical structure LED prepared by a laser lift-off method,the preparing method can solve the problem that the quality of an epitaxial layer material becomes poor due to laser ablation, and the yield is low.

Owner:山西中科潞安紫外光电科技有限公司

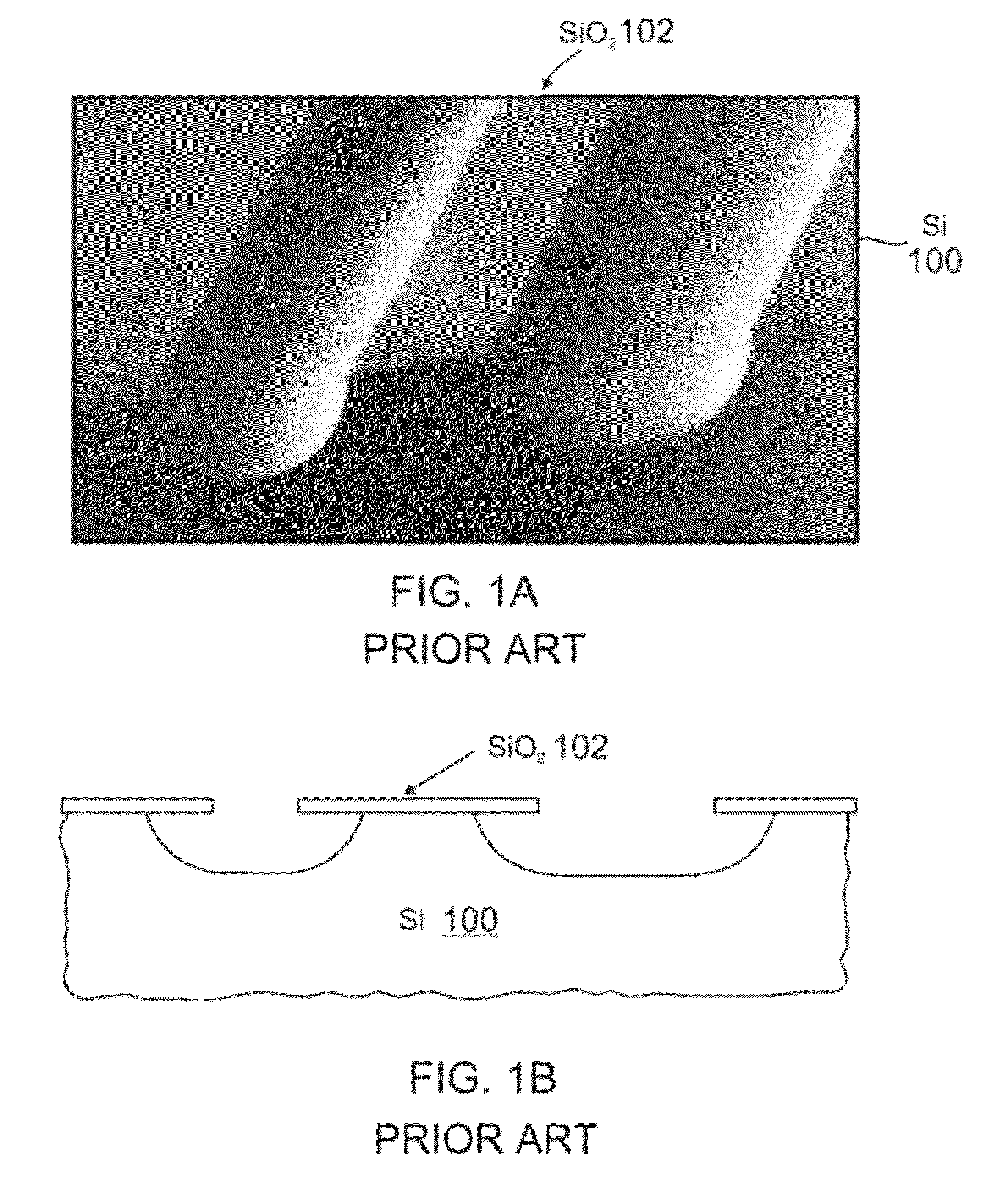

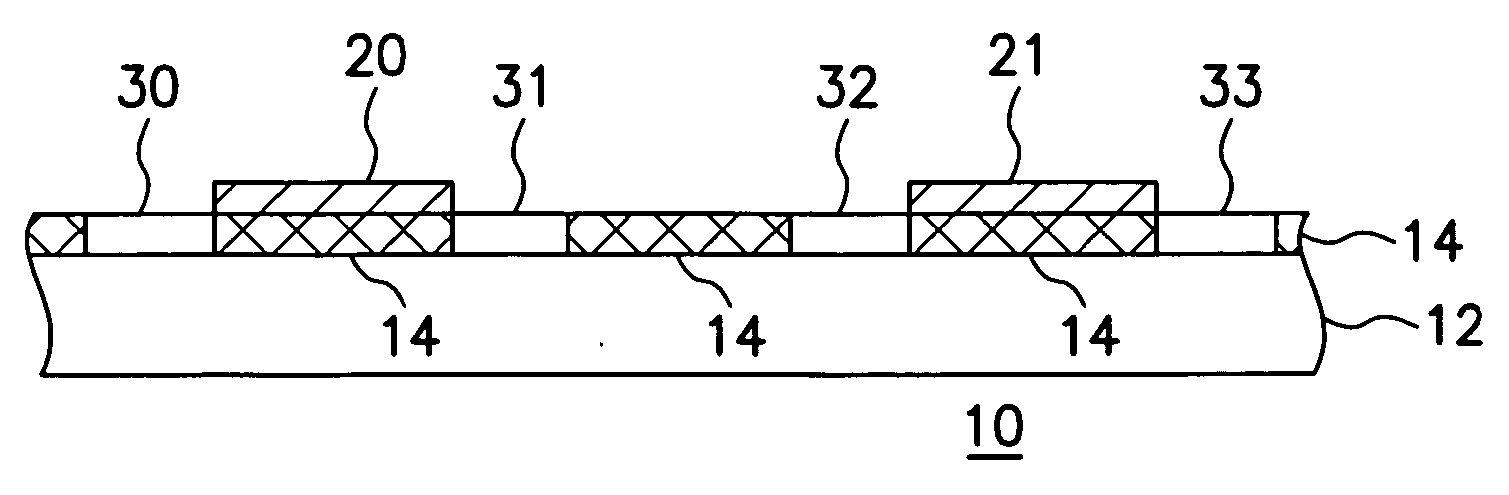

Structure and method for III-nitride device isolation

InactiveUS20060223275A1Reduce harmReducing and preventing effectSemiconductor/solid-state device manufacturingSemiconductor devicesDopantSemiconductor materials

Isolation of III-nitride devices may be performed with a dopant selective etch that provides a smooth profile with little crystal damage in comparison to previously used isolation techniques. The dopant selective etch may be an electro-chemical or photo-electro-chemical etch. The desired isolation area may be identified by changing the conductivity type of the semiconductor material to be etched. The etch process can remove a conductive layer to isolate a device atop the conductive layer. The etch process can be self stopping, where the process automatically terminates when the selectively doped semiconductor material is removed.

Owner:INFINEON TECH AMERICAS CORP