Method of making electrical test structure for detecting vias

A technology for detecting through-holes and test structures, which is applied in semiconductor/solid-state device testing/measurement, circuits, electrical components, etc., and can solve the problem of increasing process complexity and process cost, increasing requirements, and small photolithography process window, etc. problems, to achieve the effect of improving lithography resolution and lithography precision, improving lithography resolution, and expanding the process window

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

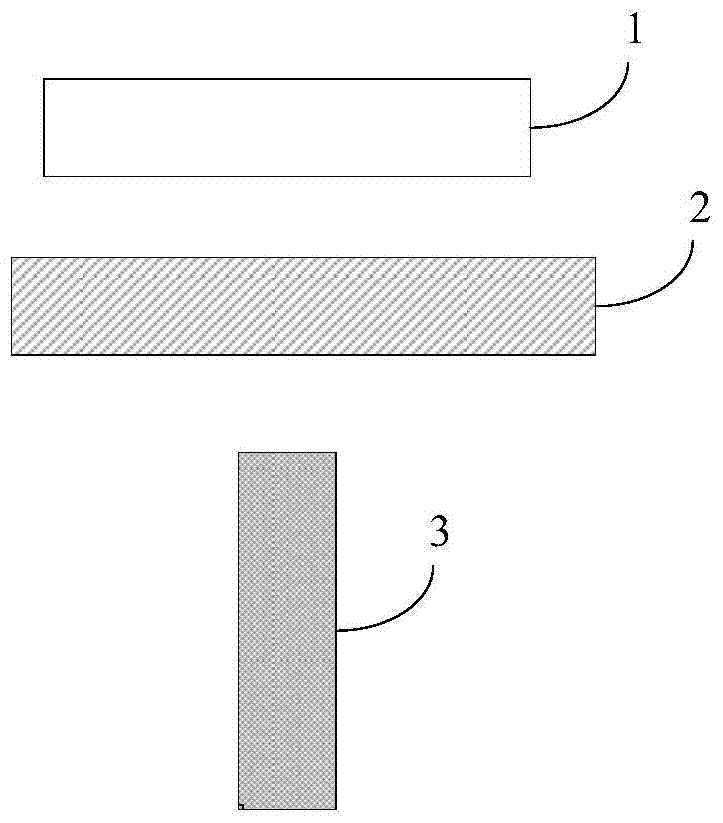

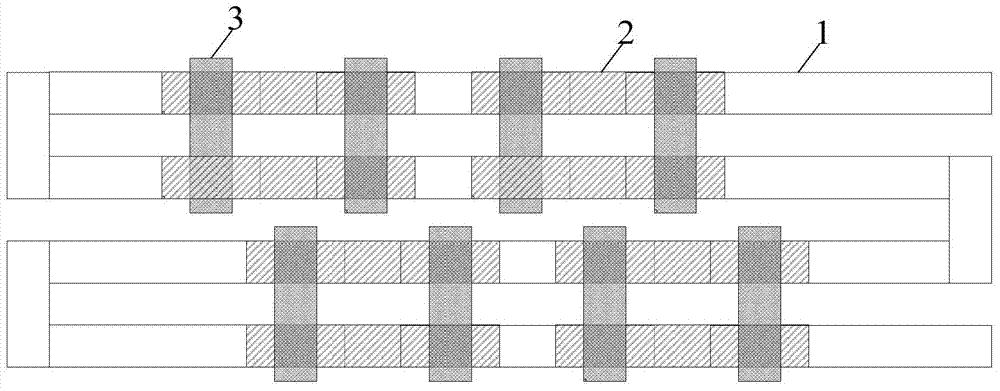

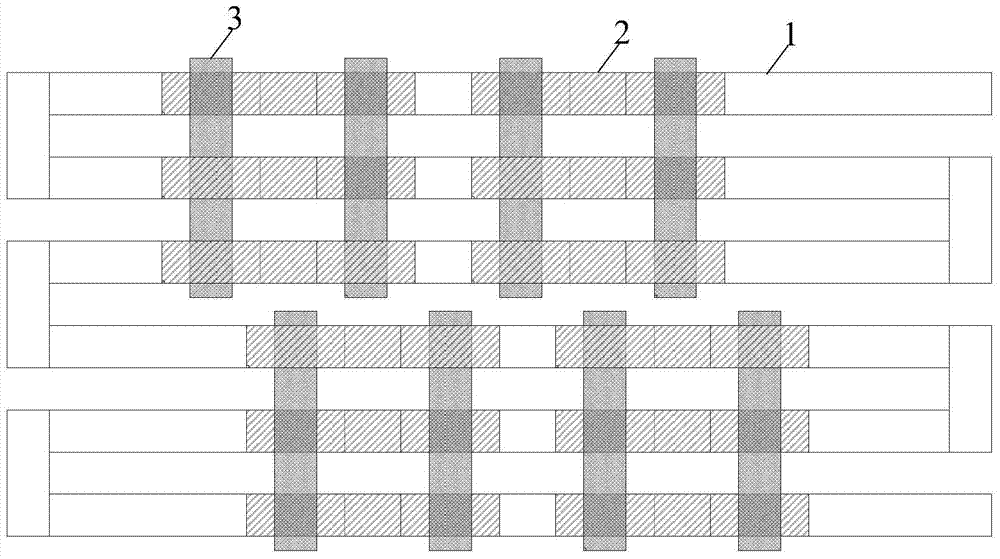

[0037] The layout adopted in the preparation process of the test structure of the present invention includes: a plurality of metal patterns arranged at a certain distance and a through-hole pattern cross-connected with a plurality of adjacent metal patterns; wherein, each metal pattern consists of an upper metal pattern and the lower metal pattern; the end of the upper metal pattern overlaps with the end of the adjacent lower metal pattern to form an overlapping area; the through hole pattern is connected to the overlapping area on a plurality of adjacent metal patterns, and through The size of the hole pattern is larger than the size of the top of the target via.

[0038] For each structure in the layout of the test structure in an embodiment of the present invention, please refer to figure 1 , the upper metal pattern, the lower metal pattern and the through-hole pattern are all strips; the size of the through-hole pattern is larger than the size of the target through-hole, s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More