Capacitance multiplier

A capacitance multiplication and capacitance technology, which is applied to electrical components, networks using active components, impedance networks, etc., can solve problems affecting circuit noise performance, large area of capacitance multiplier, and large ratio of chip area, etc., to improve noise Performance, fewer components, and less noise

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] In order to make the above objects, features and advantages of the present invention more comprehensible, specific implementations of the present invention will be described in detail below in conjunction with the accompanying drawings.

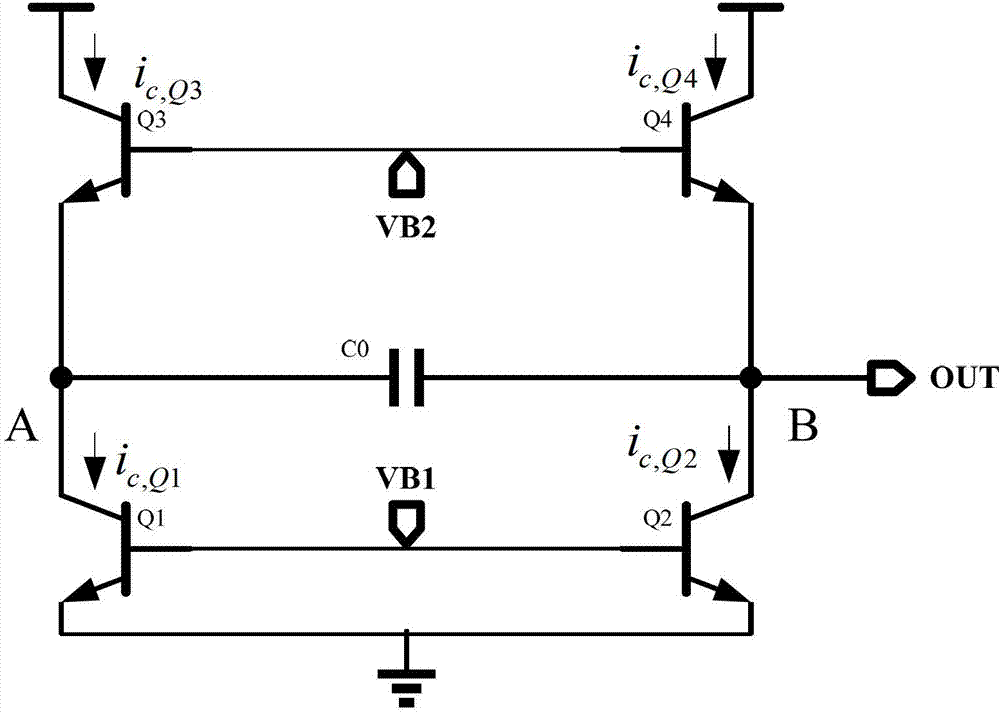

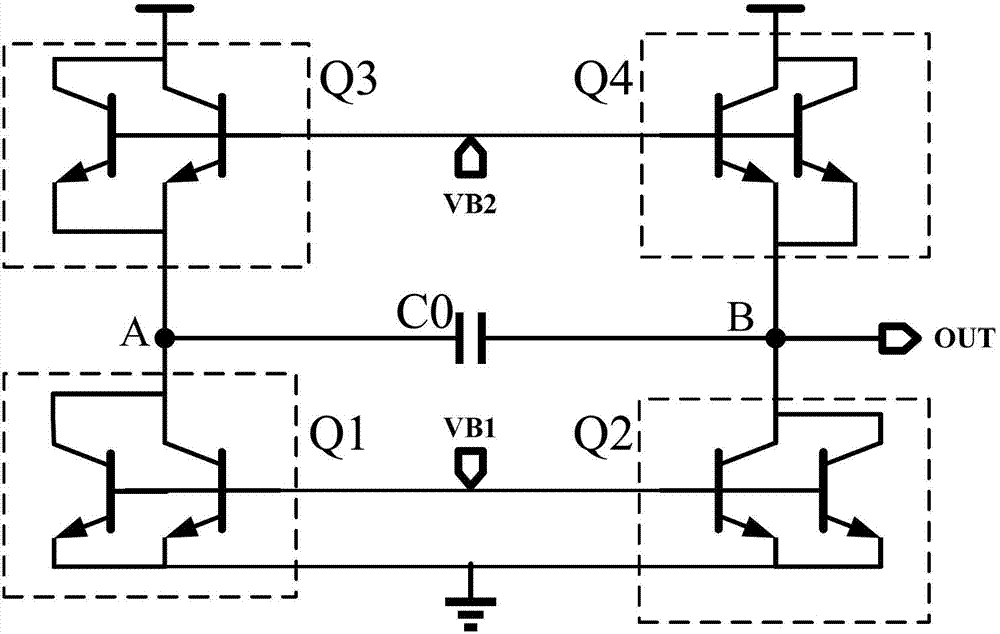

[0021] see figure 1 , which is a circuit diagram of Embodiment 1 of the capacitance multiplier provided by the embodiment of the present invention.

[0022] The capacitance multiplier provided in this embodiment includes: a first transistor Q1, a second transistor Q2, a third transistor Q3, a fourth transistor Q4, and a first capacitor C0;

[0023] The collector of the first transistor Q1 is connected to the first node A, the emitter is grounded, and the base is connected to the first bias voltage VB1;

[0024] The collector of the second transistor Q2 is connected to the second node B, the emitter is grounded, and the base is connected to the first bias voltage VB1;

[0025] The collector of the third transistor Q3 is connected to a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More