Optimization design method based on FPGA finite field multipier

An optimized design and finite field technology, applied in the direction of instruments, calculations, special data processing applications, etc., can solve problems such as ineffective use of FPGA chip resources

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

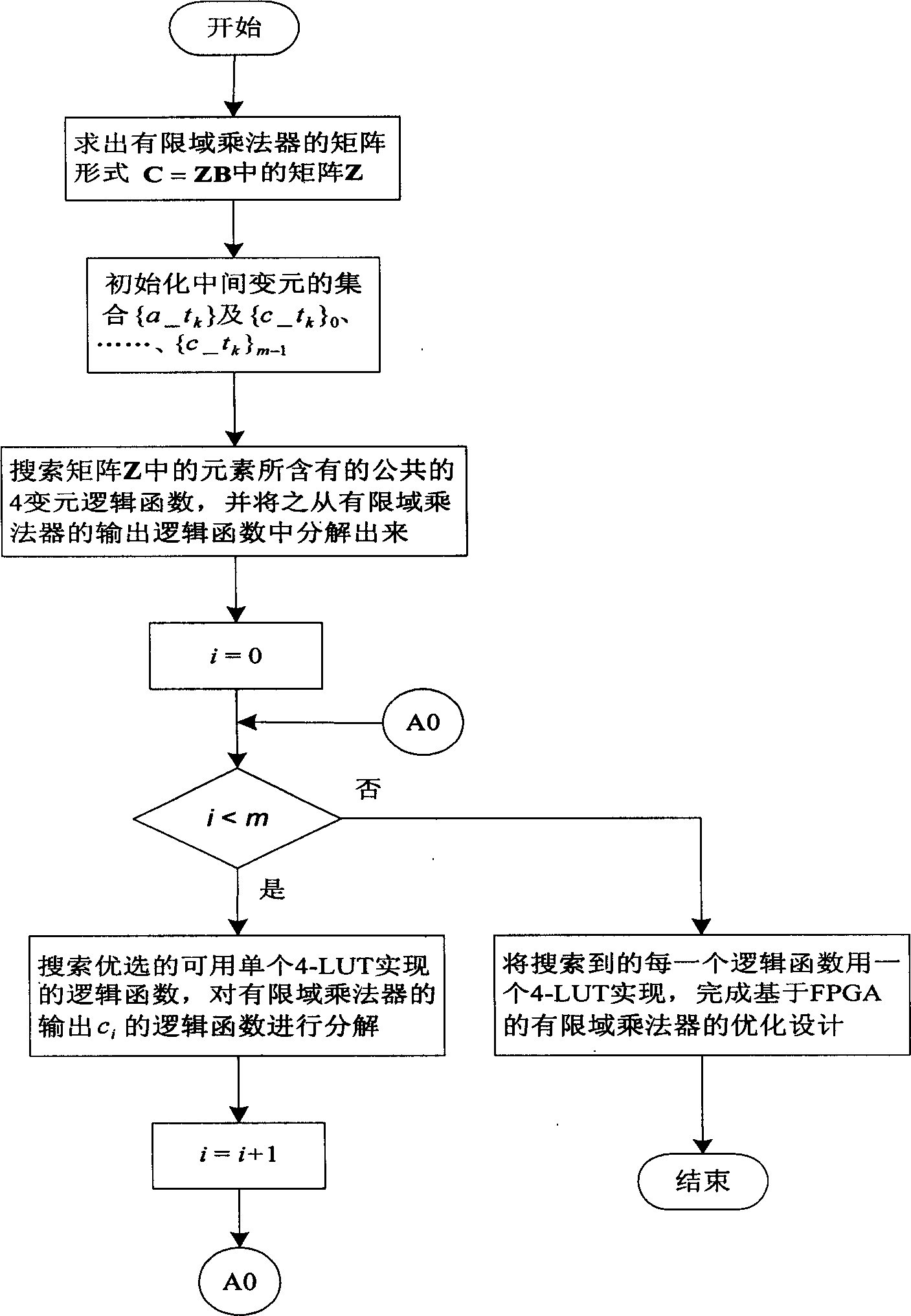

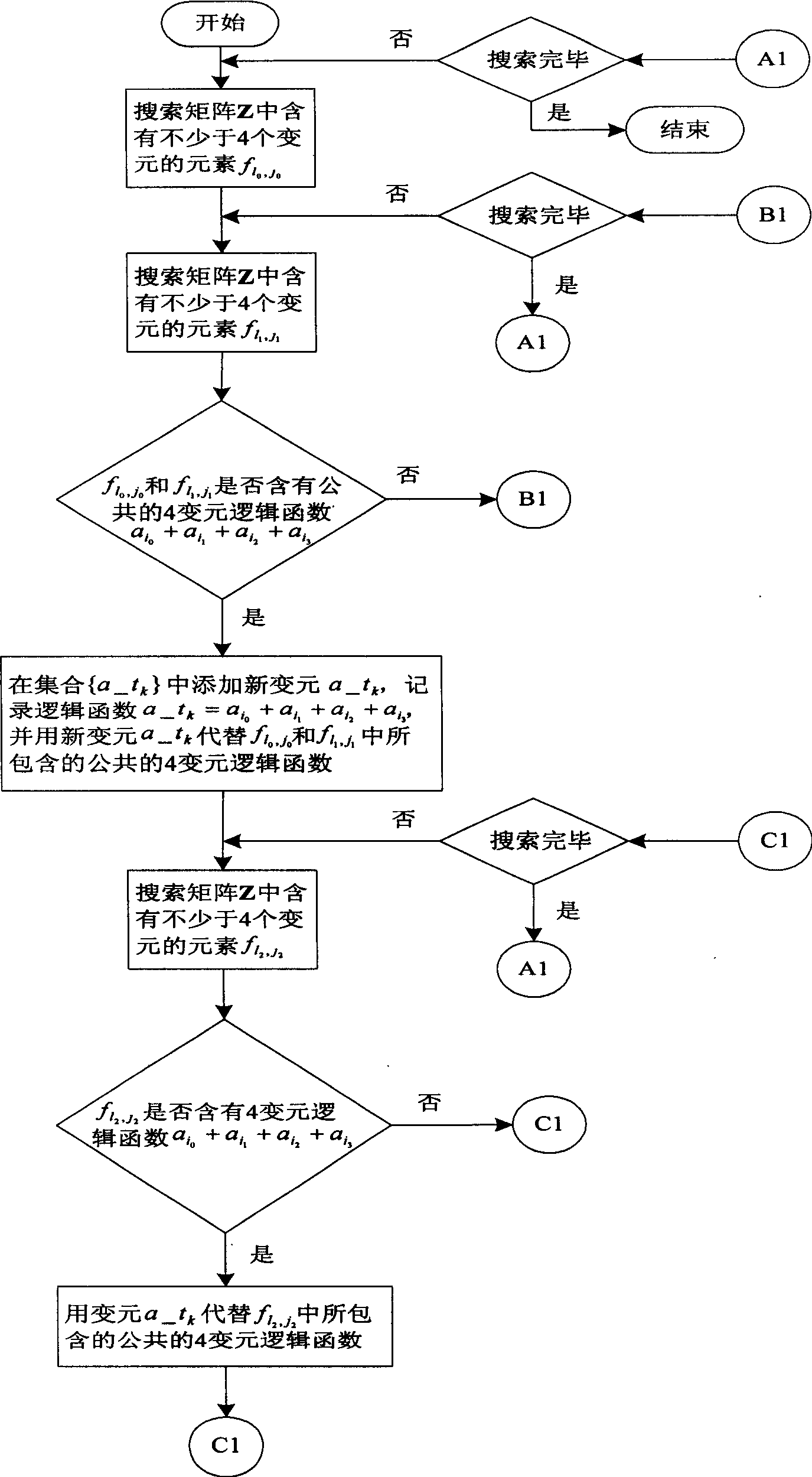

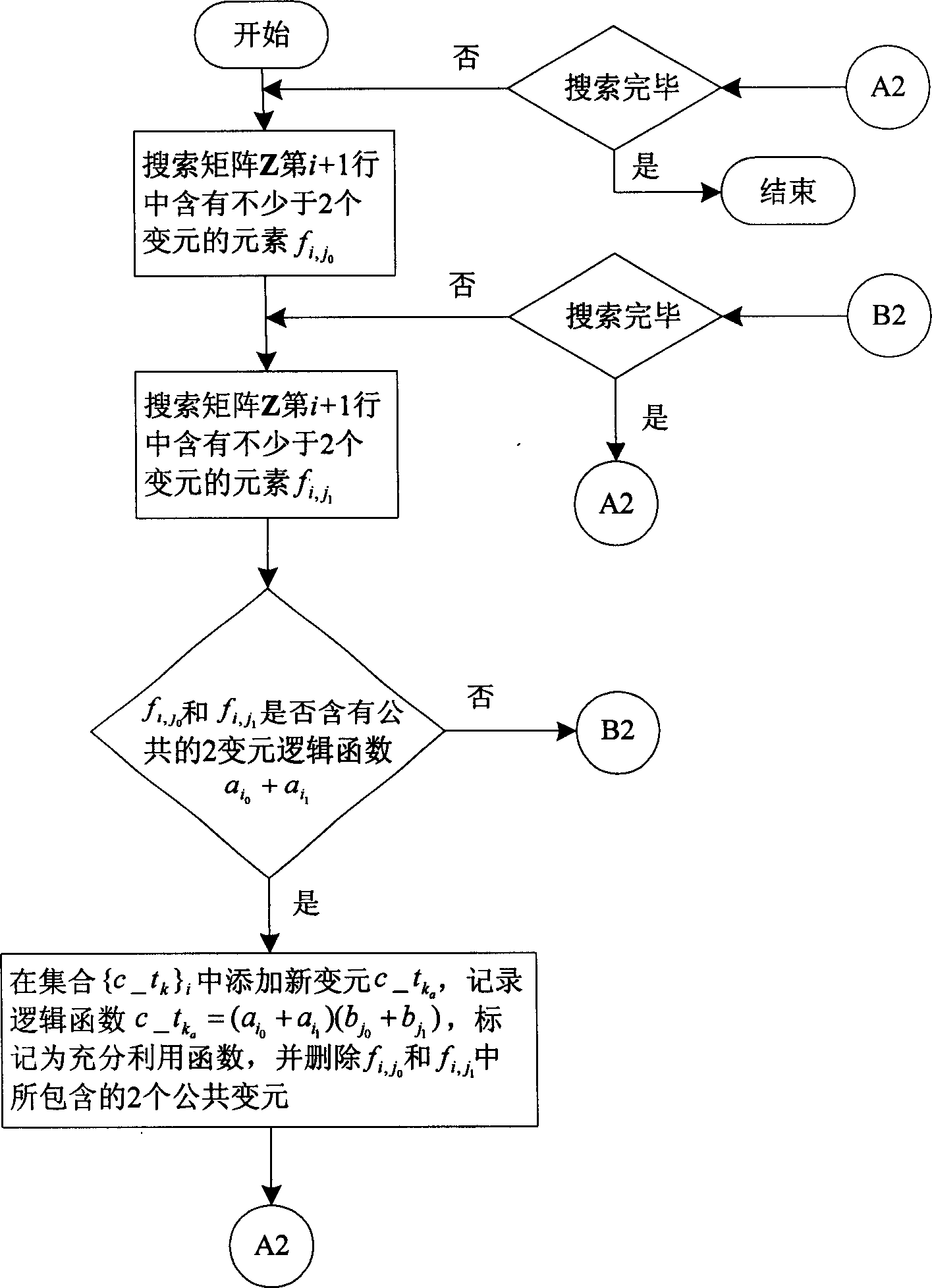

Method used

Image

Examples

Embodiment 1

[0121] Finite field GF(2 5 ), the generator polynomial is p(x)=x 5 +x 2 +1.

[0122] First, find the matrix form of the finite field multiplier:

[0123] c 0 c 1 c 2 c 3 c 4 = a 0 a 4 a 3 a ...

Embodiment 2

[0146] Finite field GF(2 8 ), the domain generator polynomial is p(x)=x 8 +x 4 +x 3 +x 2 +1.

[0147] The first step is to find the matrix form of the finite field multiplier:

[0148] c 0 c 1 c 2 c 3 c 4 c 5 c 6 c 7 = ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More