Divider and division operation method

An operation method and a technology of instruments, which are applied in the field of digital signal processing circuits, can solve problems such as the inability to achieve hardware area and operation speed, shorten the calculation time of division, and consume a lot of time.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

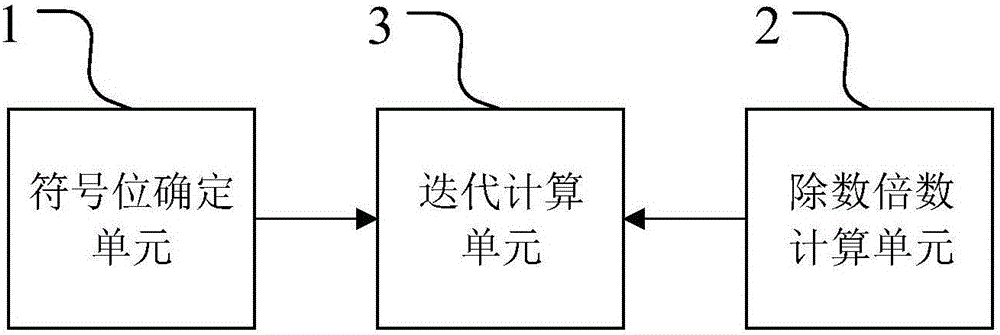

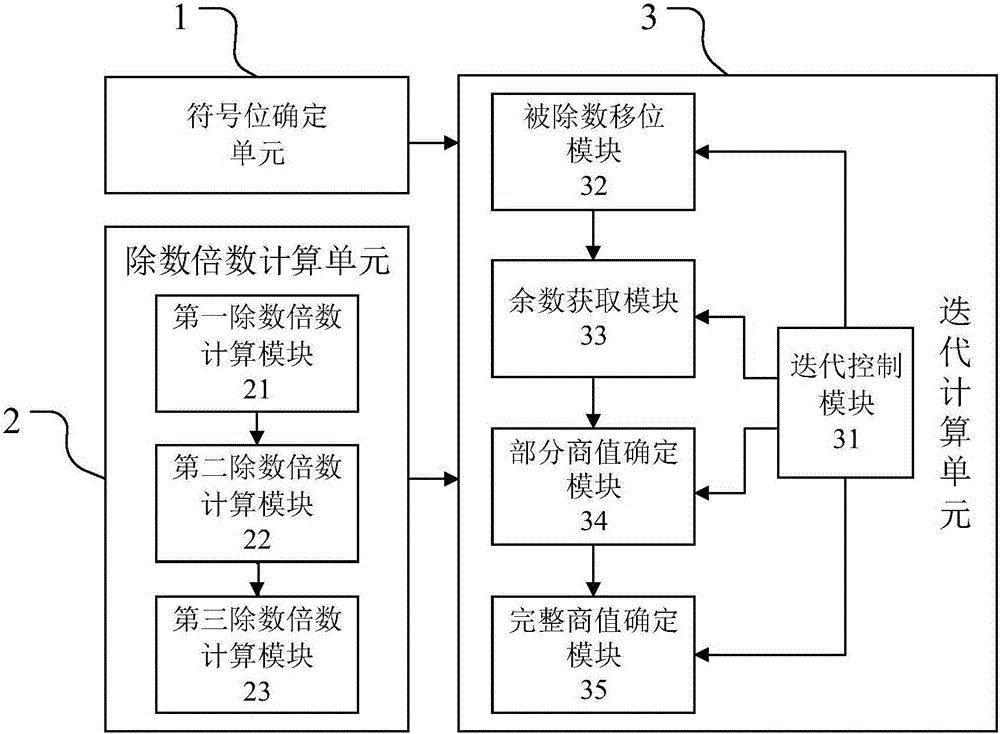

[0051] Please refer to figure 1 , the embodiment of the present invention provides a divider, the divider adopts the radix-N algorithm, wherein, N is 2 i And i is a positive integer greater than or equal to 3, and the quotient of the initial dividend and the initial divisor is greater than or equal to -N and less than or equal to N; the divider includes:

[0052] Sign bit determining unit 1, for reading in the sign bit of the initial dividend and the sign bit of the initial divisor, respectively judging whether the initial dividend and the initial divisor are positive or negative, obtaining a judgment result, and based on the judgment result determining the sign bit of the quotient result of the initial dividend and the initial divisor;

[0053] Specifically, the sign bit determination unit 1 reads the highest bit of the initial dividend and the highest bit of the initial divisor, and judges that the highest bit of the initial dividend and the highest bit of the initial divis...

Embodiment 2

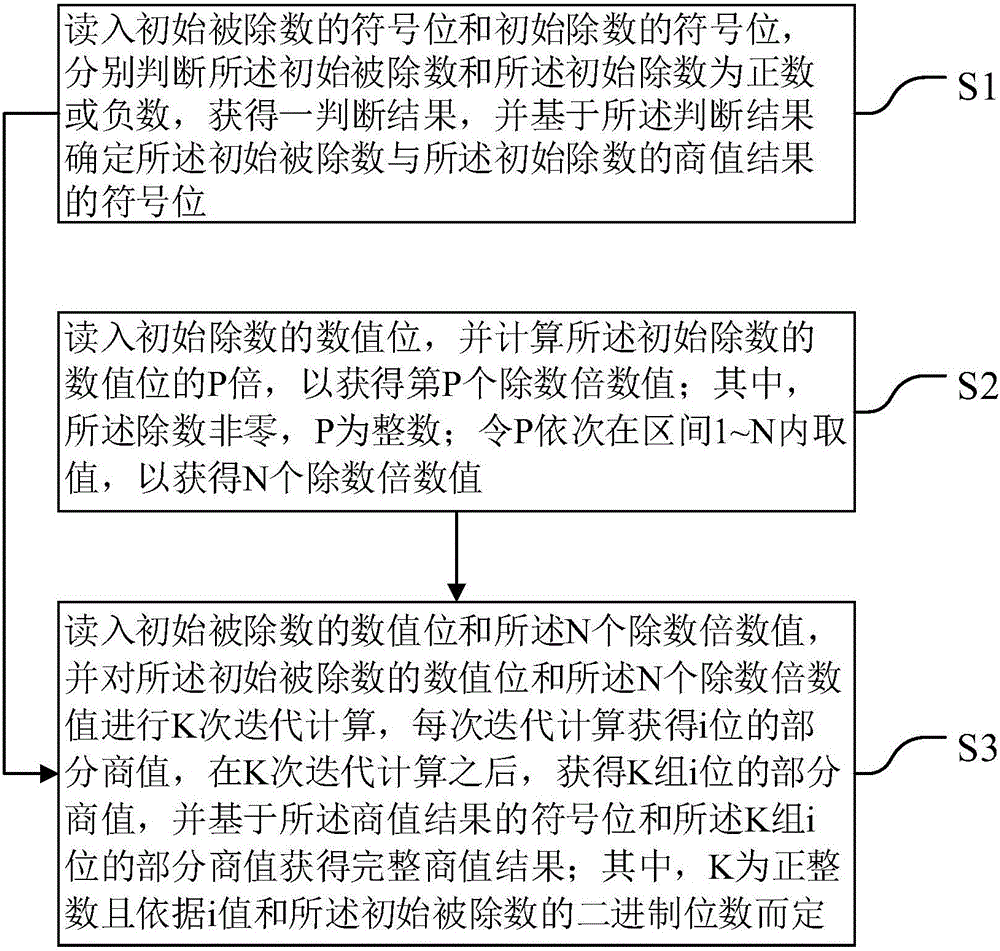

[0088] Based on the same inventive concept, please refer to image 3 , the embodiment of the present invention also provides a division operation method, which is applied in a divider, and the divider adopts a base N algorithm, wherein N is 2 i And i is a positive integer greater than or equal to 3, and the quotient of the initial dividend and the initial divisor is greater than or equal to -N and less than or equal to N; the method comprises the following steps:

[0089] S1. Read in the sign bit of the initial dividend and the sign bit of the initial divisor, respectively judge whether the initial dividend and the initial divisor are positive or negative, obtain a judgment result, and determine the initial dividend and the initial divisor based on the judgment result the sign bit of the quotient result of the initial divisor;

[0090] S2. Read in the numerical digits of the initial divisor, and calculate the P times of the numerical digits of the initial divisor to obtain th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More