Patents

Literature

43results about How to "Minimizing leakage current" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

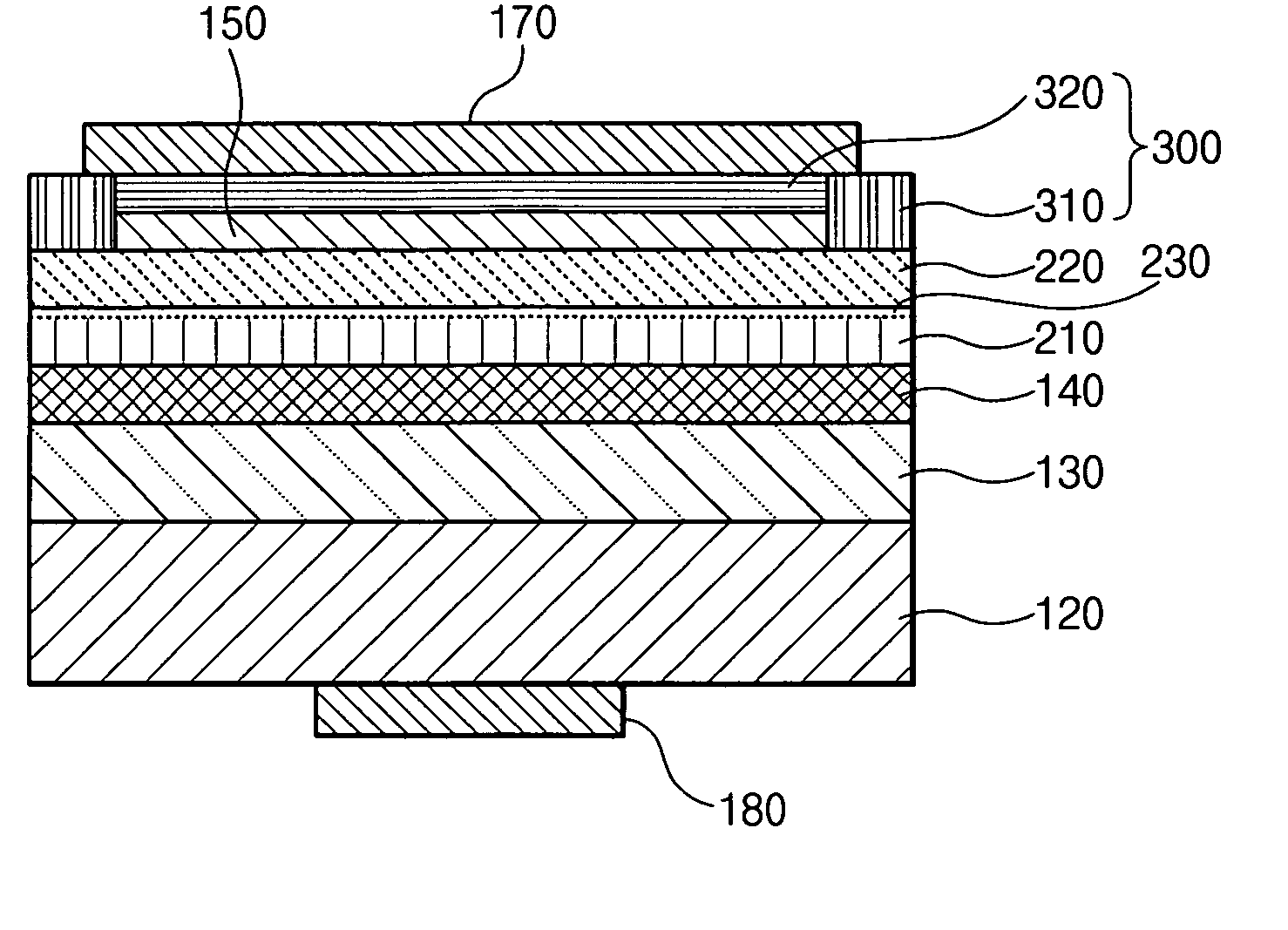

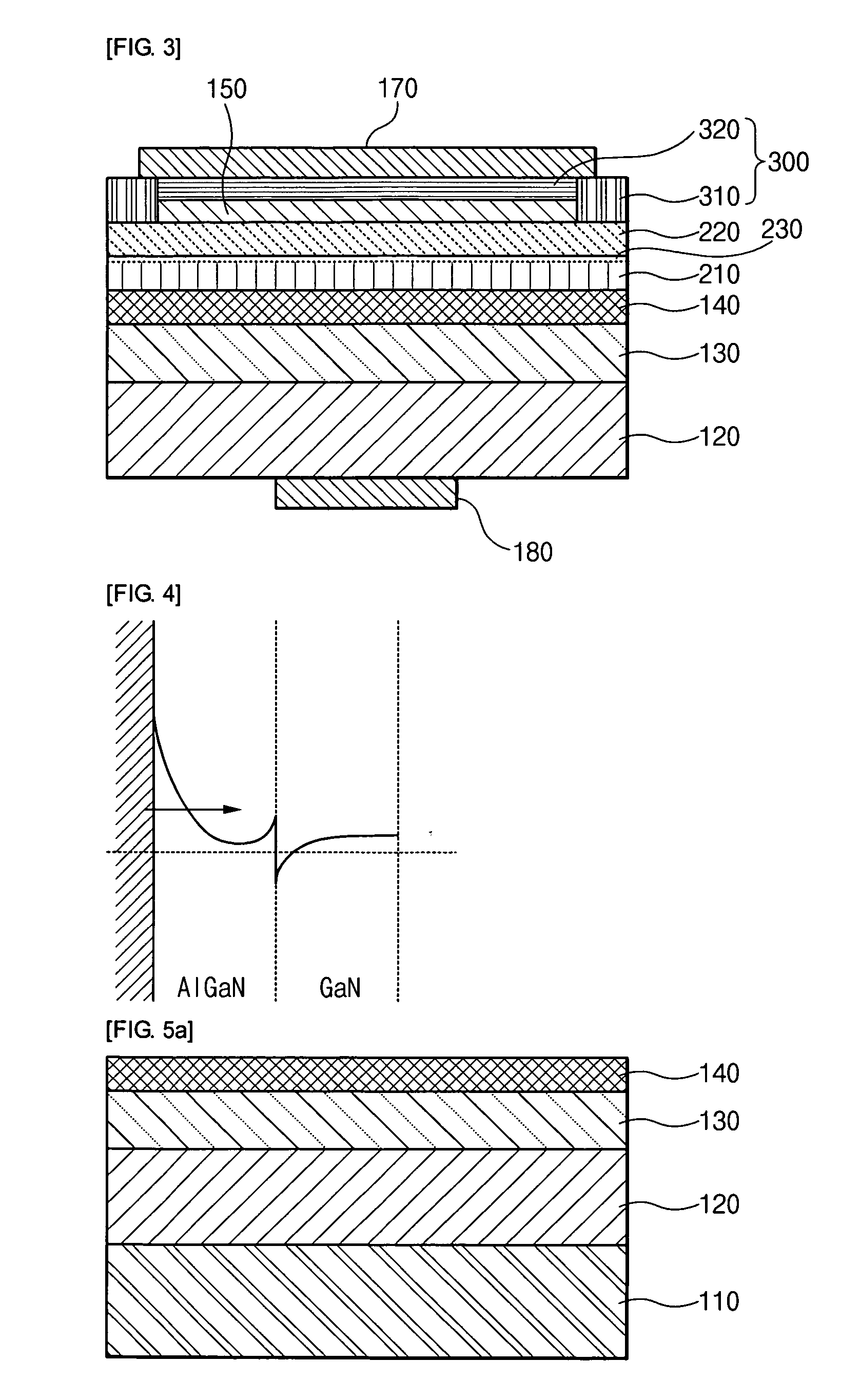

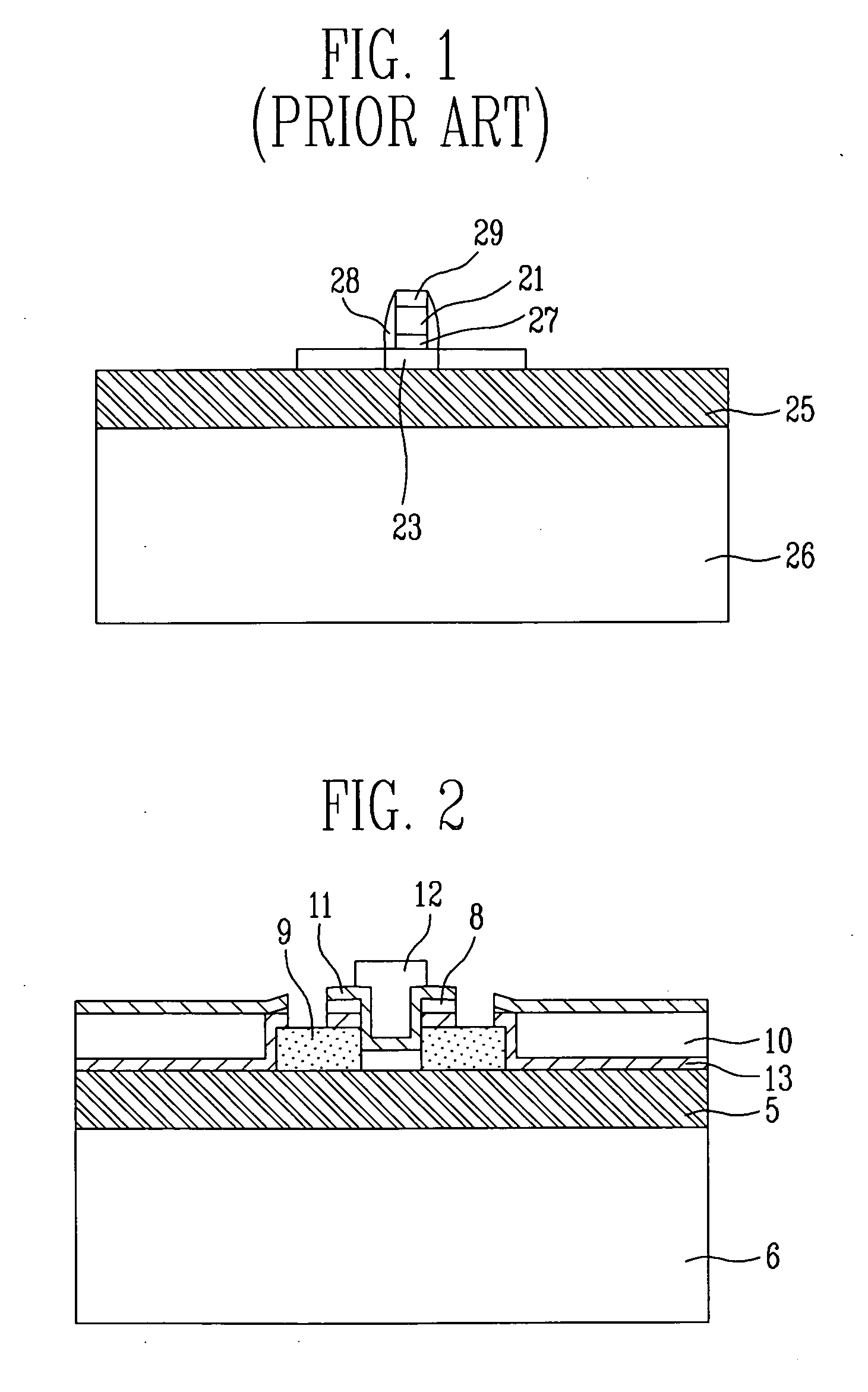

Nitride semiconductor light emitting device and method of manufacturing the same

InactiveUS20060249736A1Low working voltageGood effectSolid-state devicesMetal working apparatusReflective layerActive layer

The present invention relates to a nitride semiconductor light emitting device. The nitride semiconductor light emitting device includes an n-type electrode; an n-type nitride semiconductor layer that is formed to come in contact with the n-type electrode; an active layer that is formed on the n-type nitride semiconductor layer; a p-type nitride semiconductor layer that is formed on the active layer; an undoped GaN layer that is formed on the p-type nitride semiconductor layer; an AlGaN layer that is formed on the undoped GaN layer so as to provide a two-dimensional electron gas layer to the interface with the undoped GaN layer; a reflecting layer that is formed on the AlGaN layer; a barrier that is formed so as to surround the reflecting layer; and a p-type electrode that is formed on the barrier.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

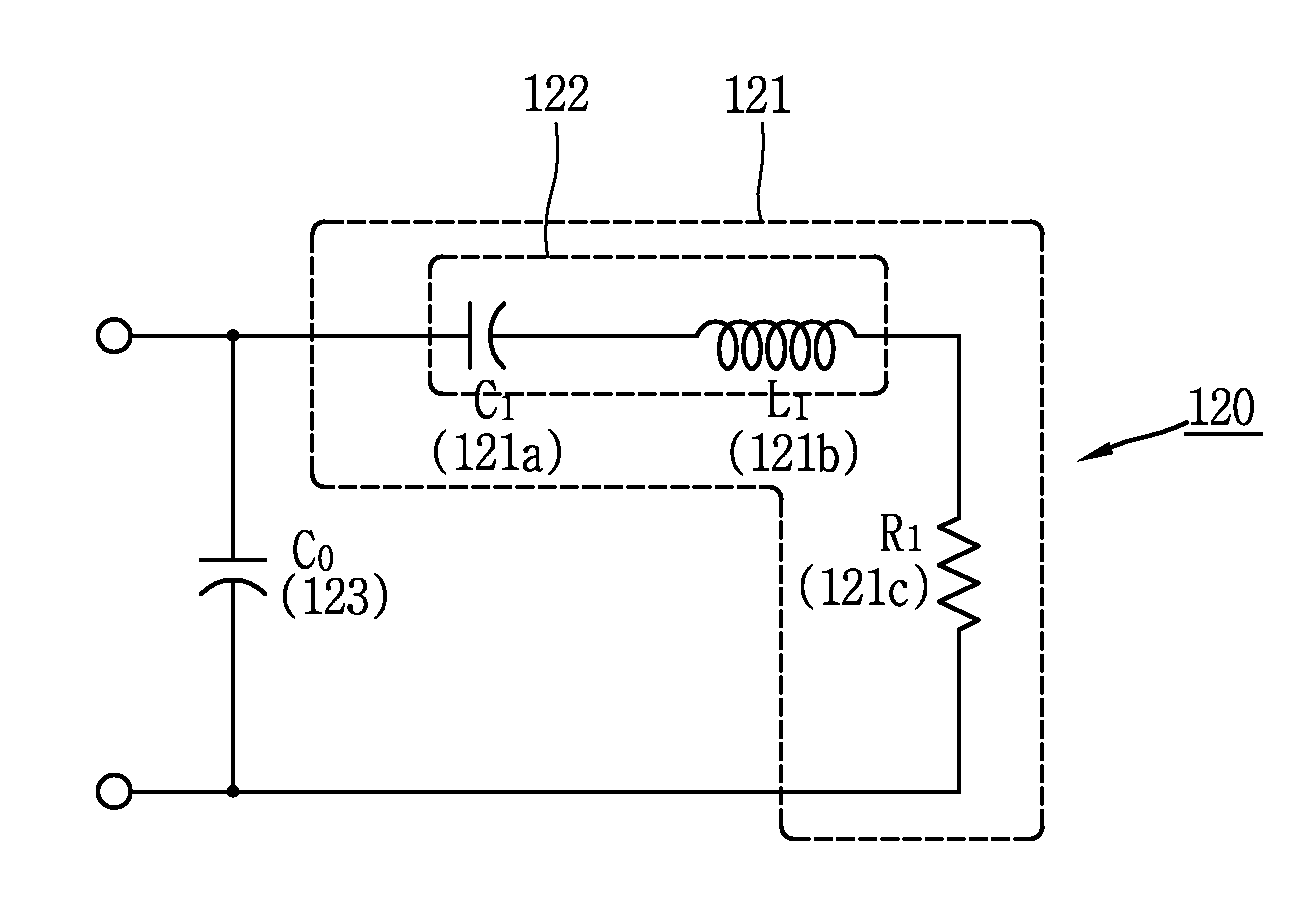

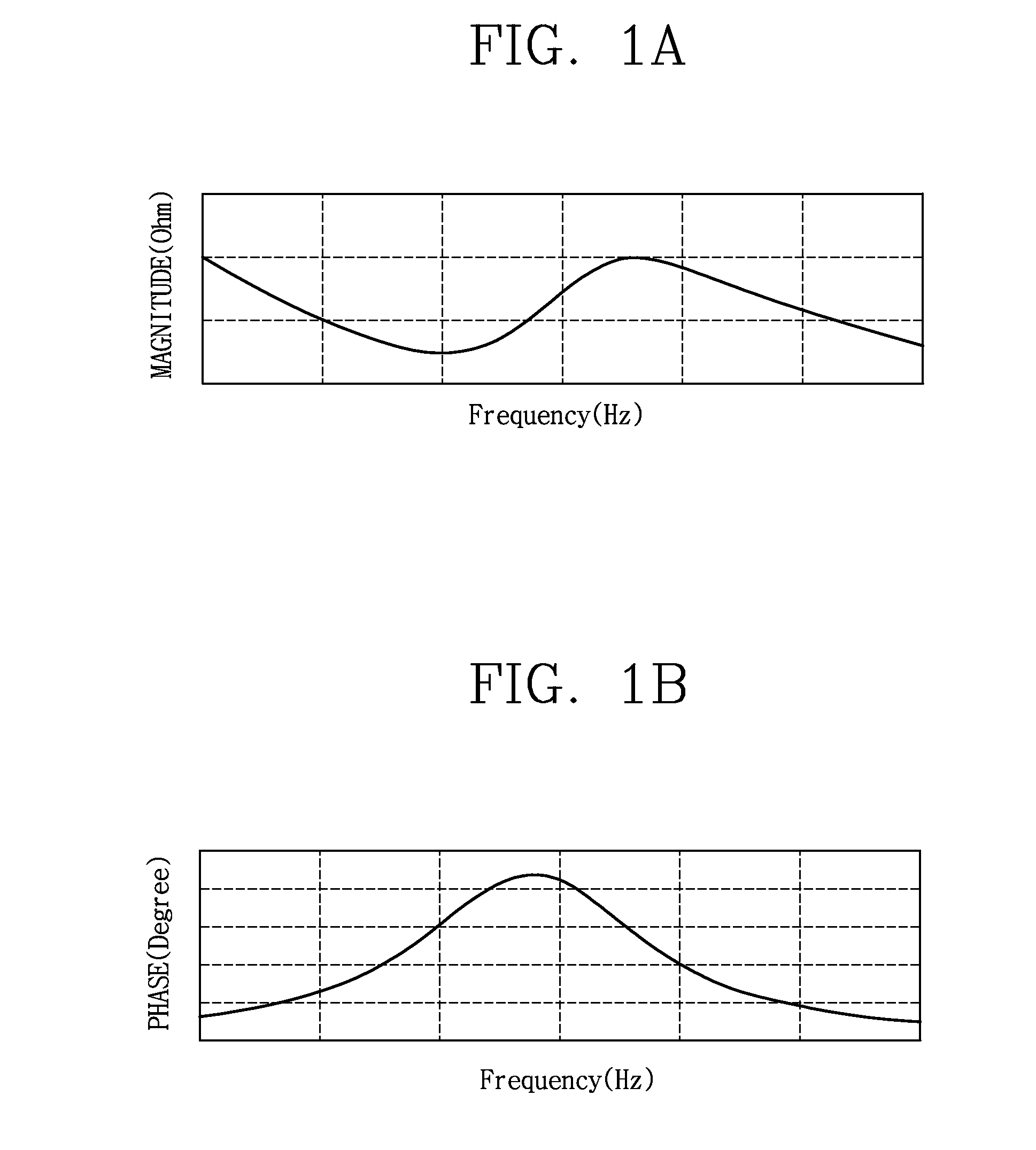

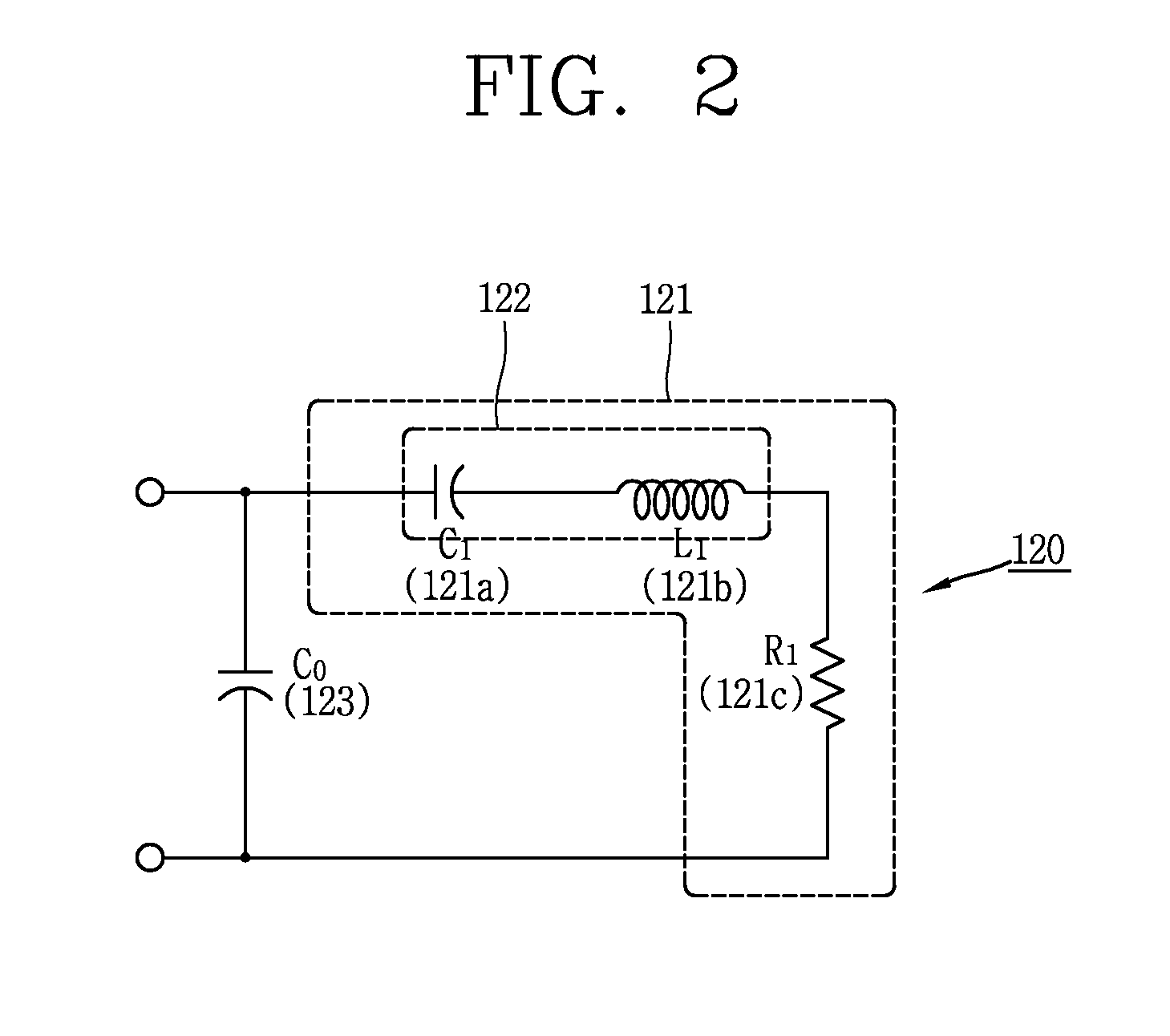

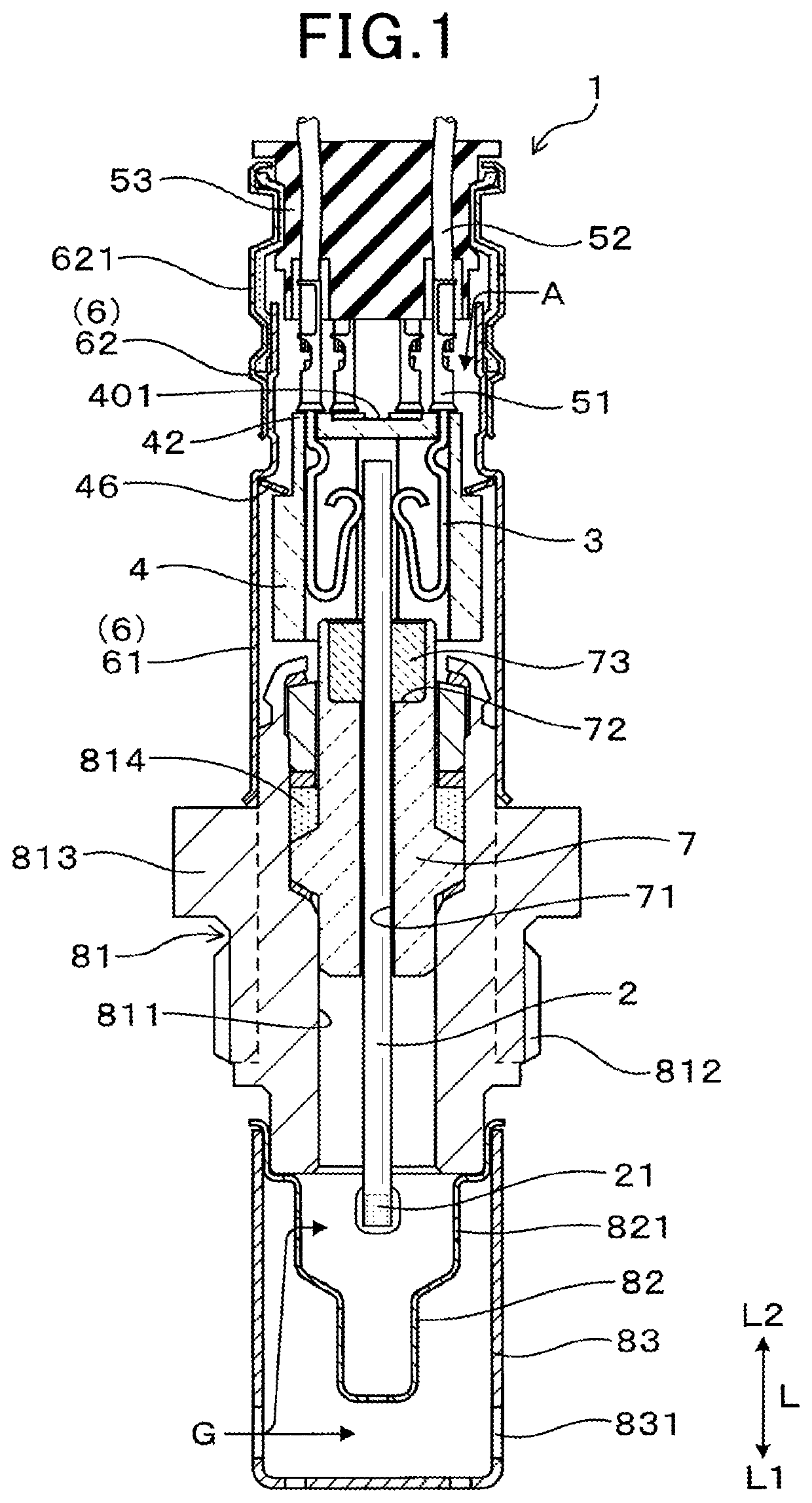

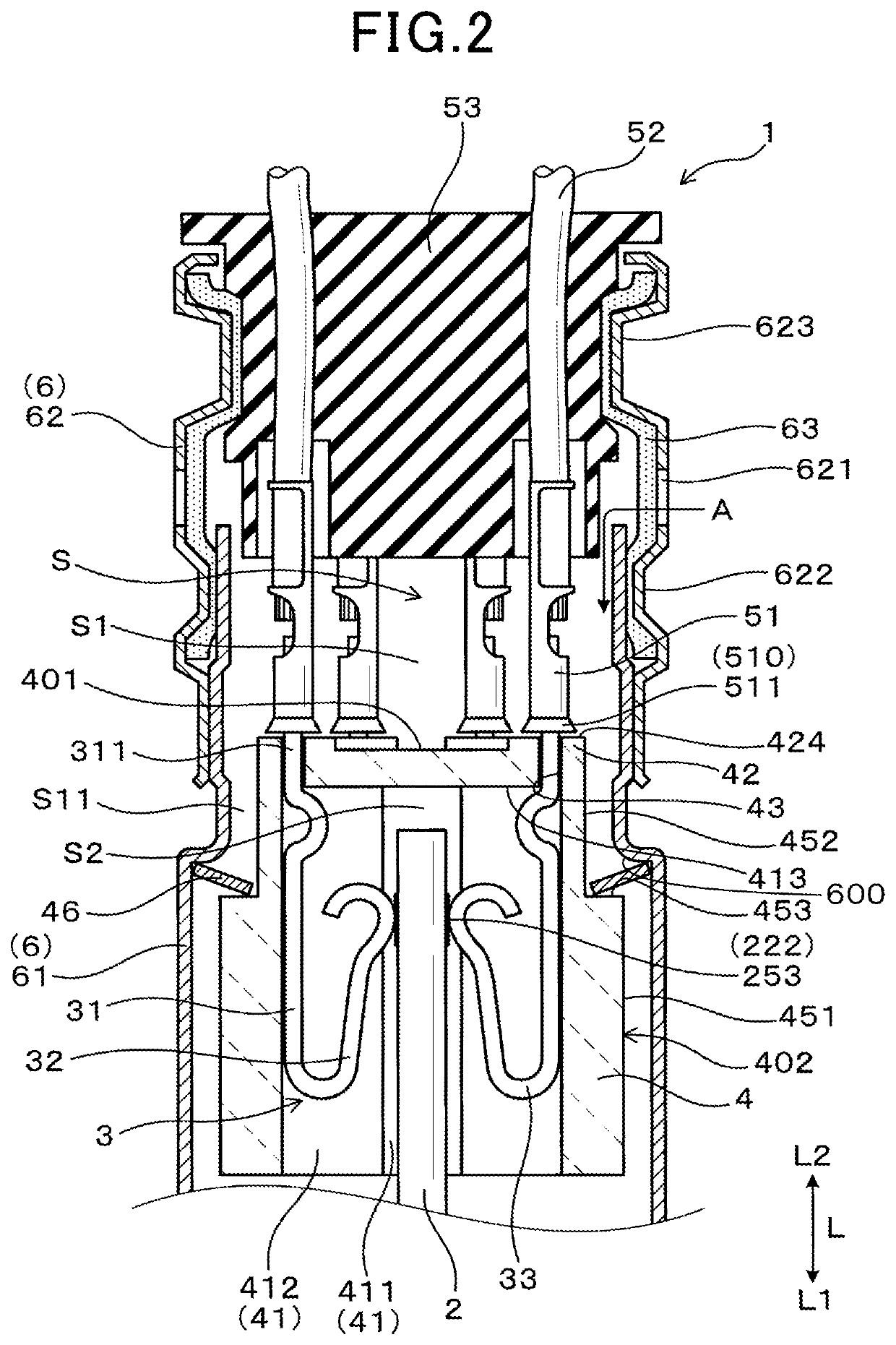

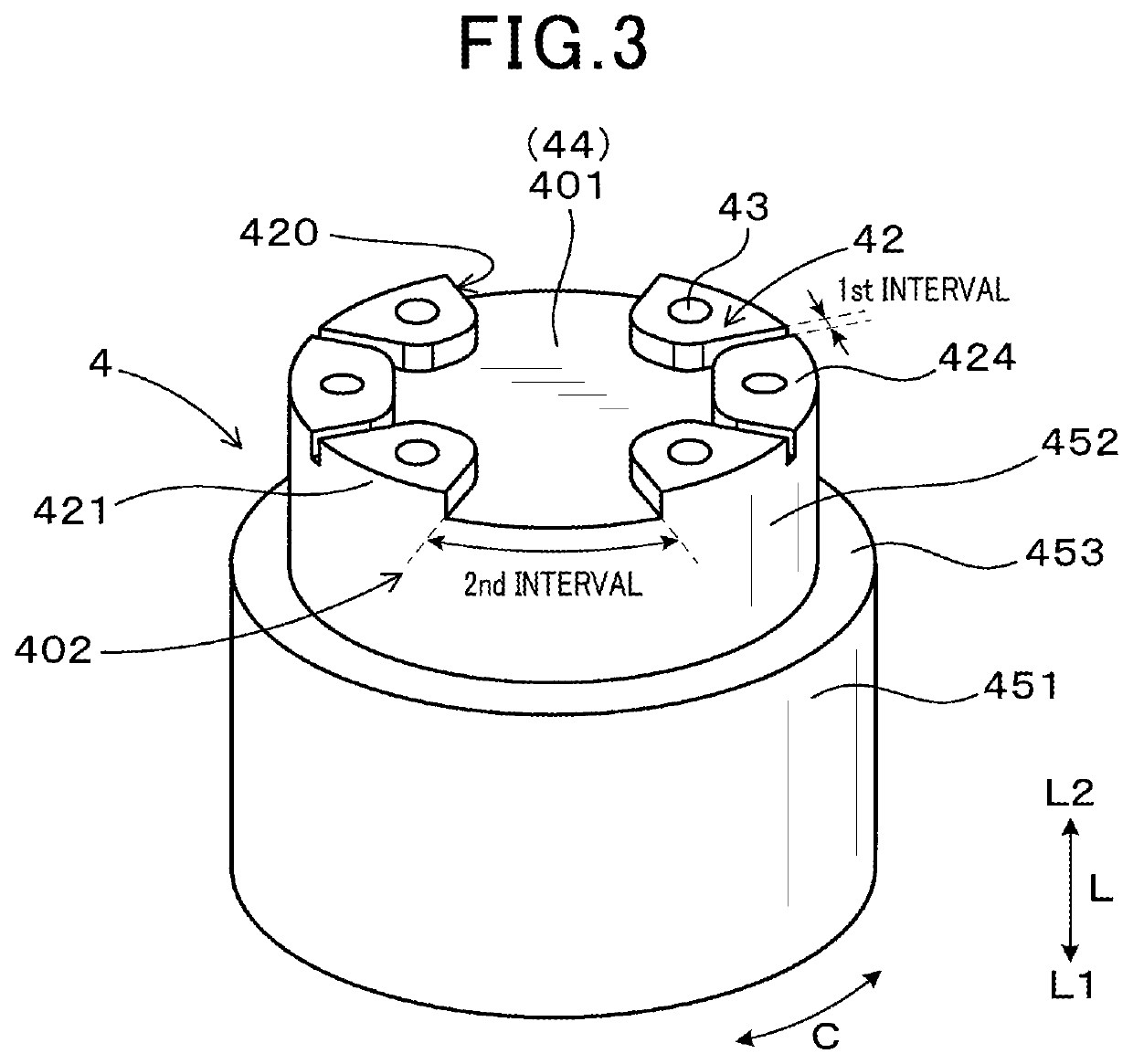

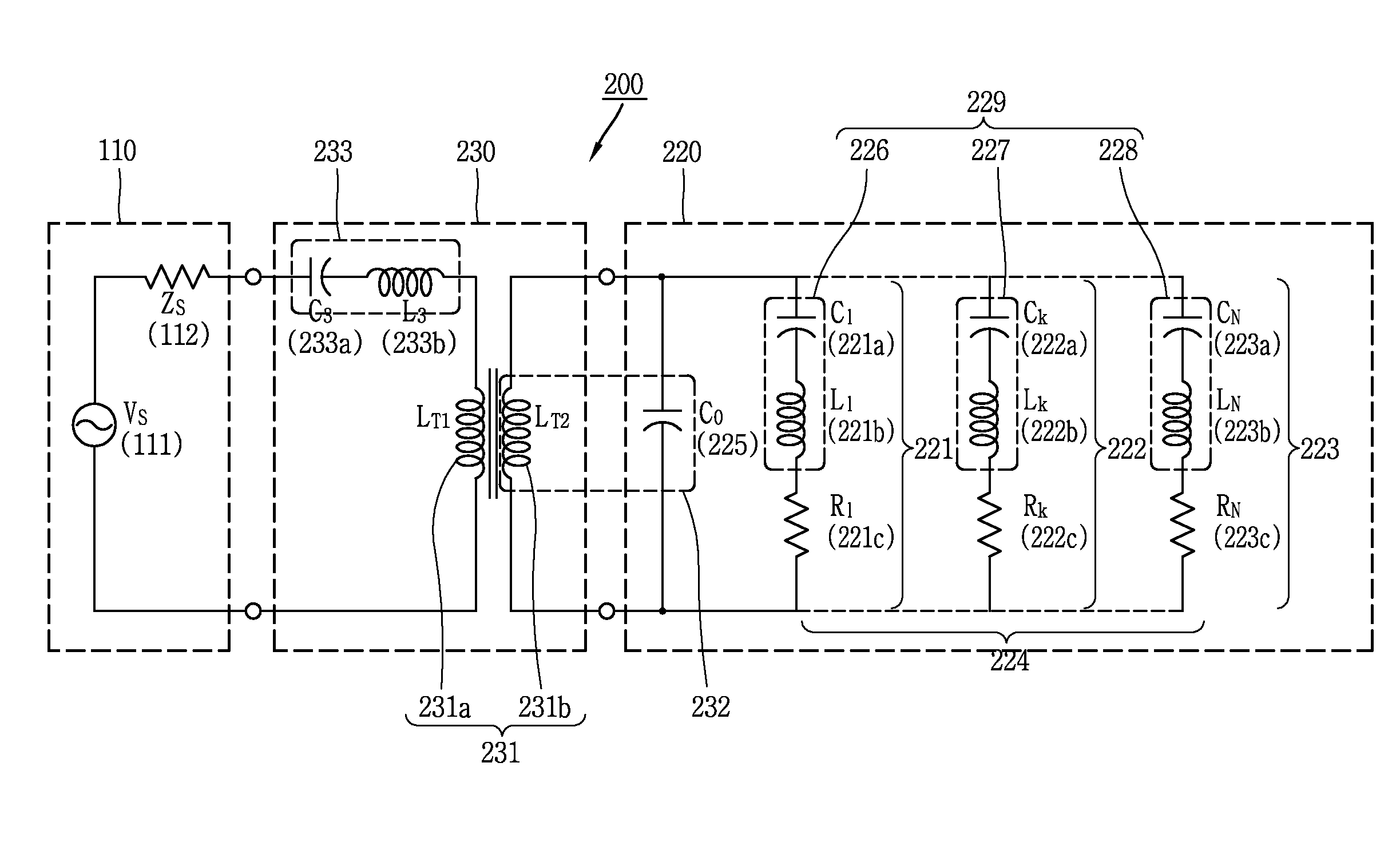

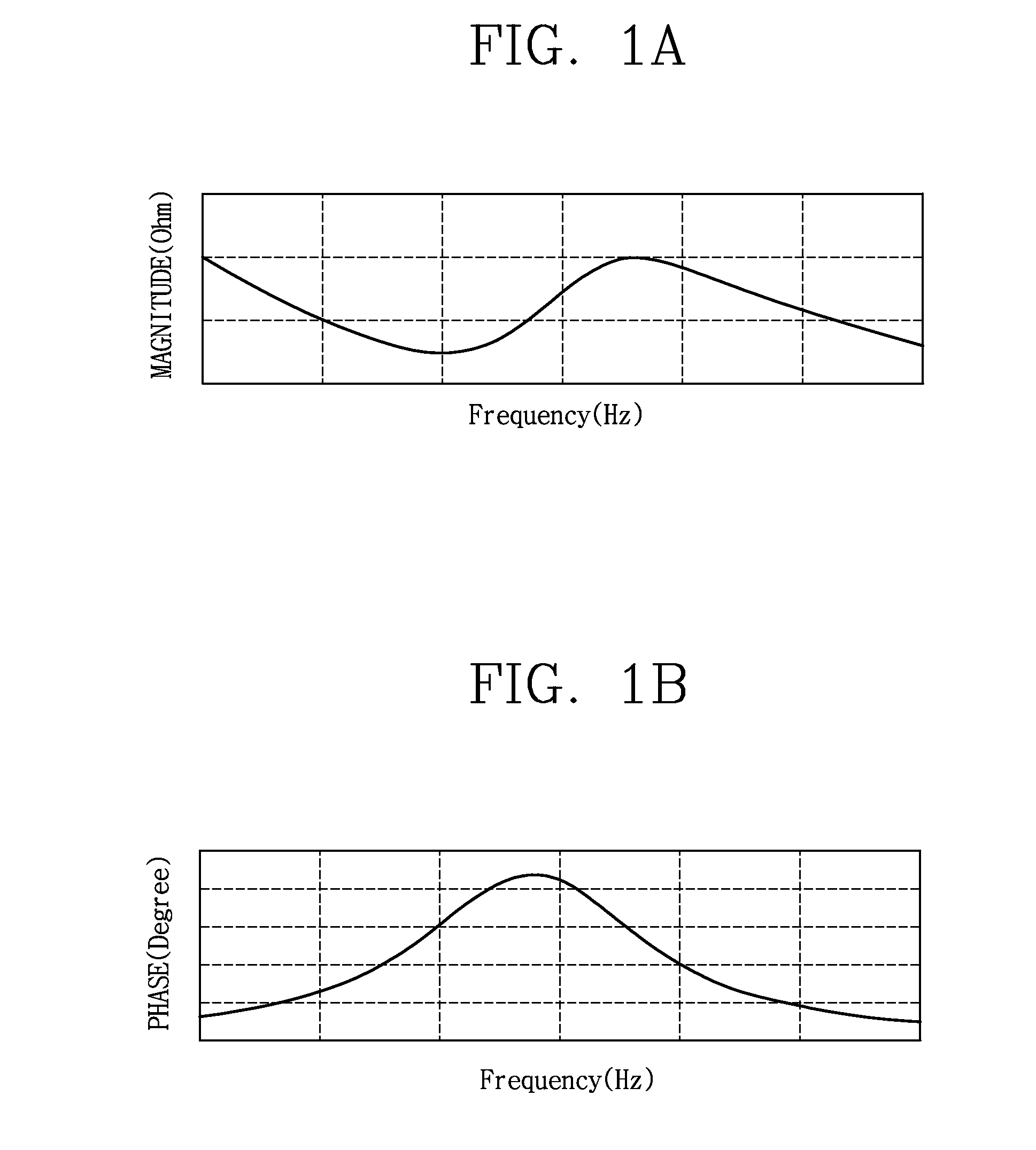

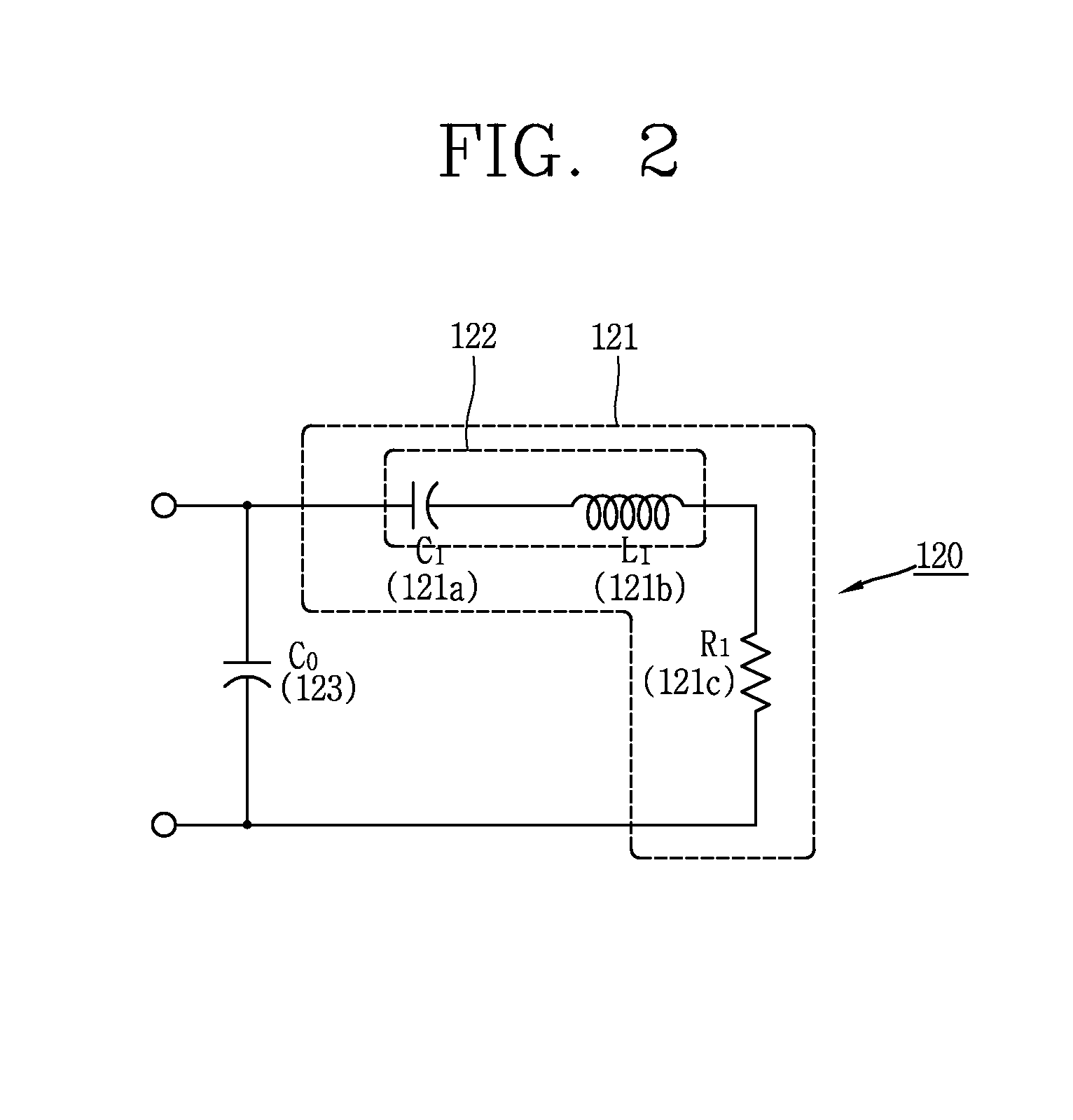

Sonar system and impedance matching method thereof

ActiveUS20140160892A1Improve power factorMinimizes physical sizeSeismic energy generationMechanical vibrations separationPower factorTransducer

This specification relates to an active SONAR system comprising a transmitter, a transducer and an impedance matching circuit for expanding bandwidth and increasing a power factor value in sound and ultrasonic wave bands by mutually matching resonant frequencies of the transducer and the impedance matching circuit or a resonant frequency between the transducer and the impedance matching circuit using an electrical equivalent model corresponding to actual impedance data of the transducer and controlling the positions and the intervals of the frequencies at which reactance components of the transducer including the impedance matching circuit become zero, and an impedance matching method thereof. This allows for efficient driving in a broadband between the transmitter and the transducer in the active SONAR system, contributing to output power performance and detection performance of the active SONAR system.

Owner:AGENCY FOR DEFENSE DEV

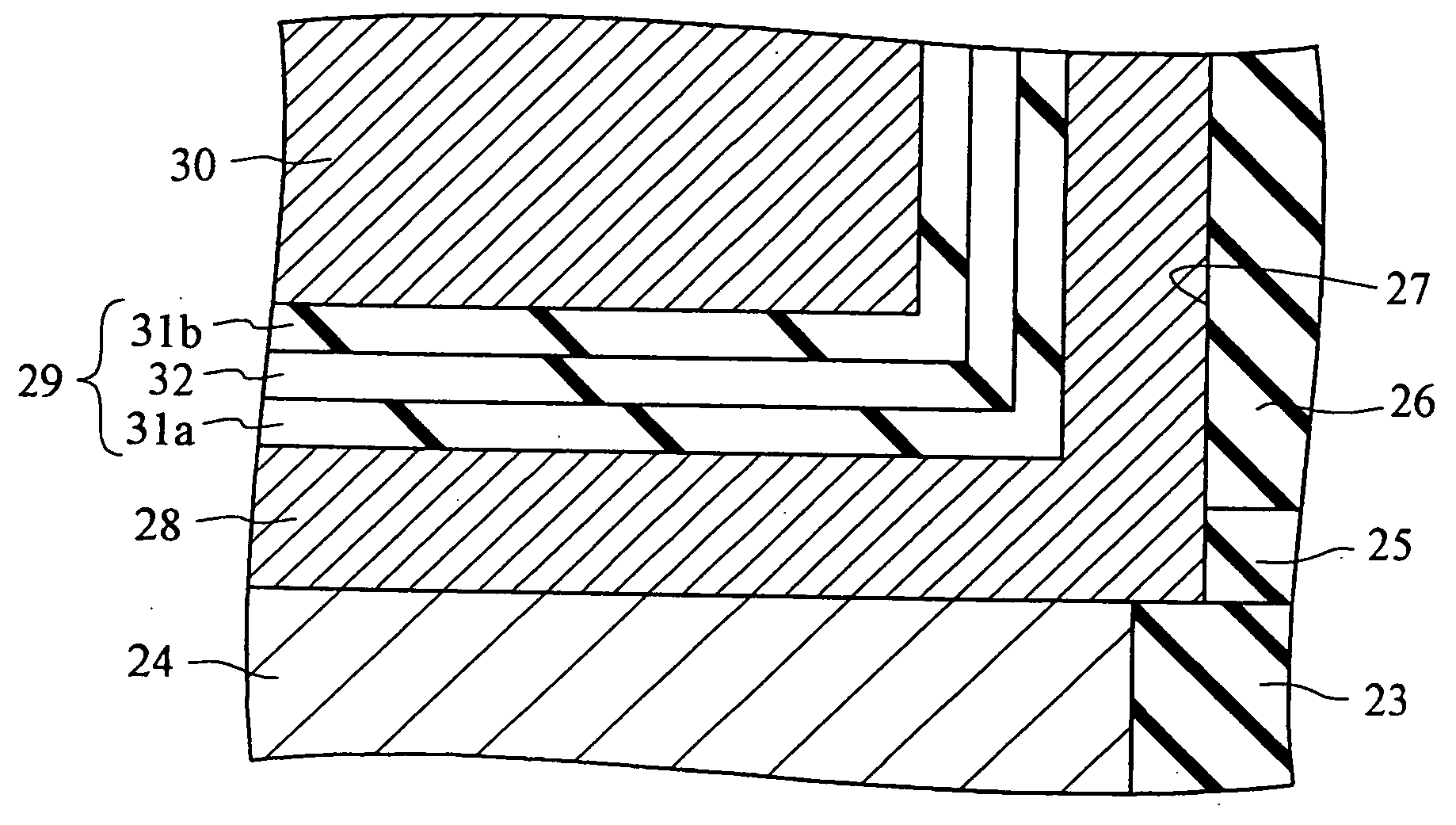

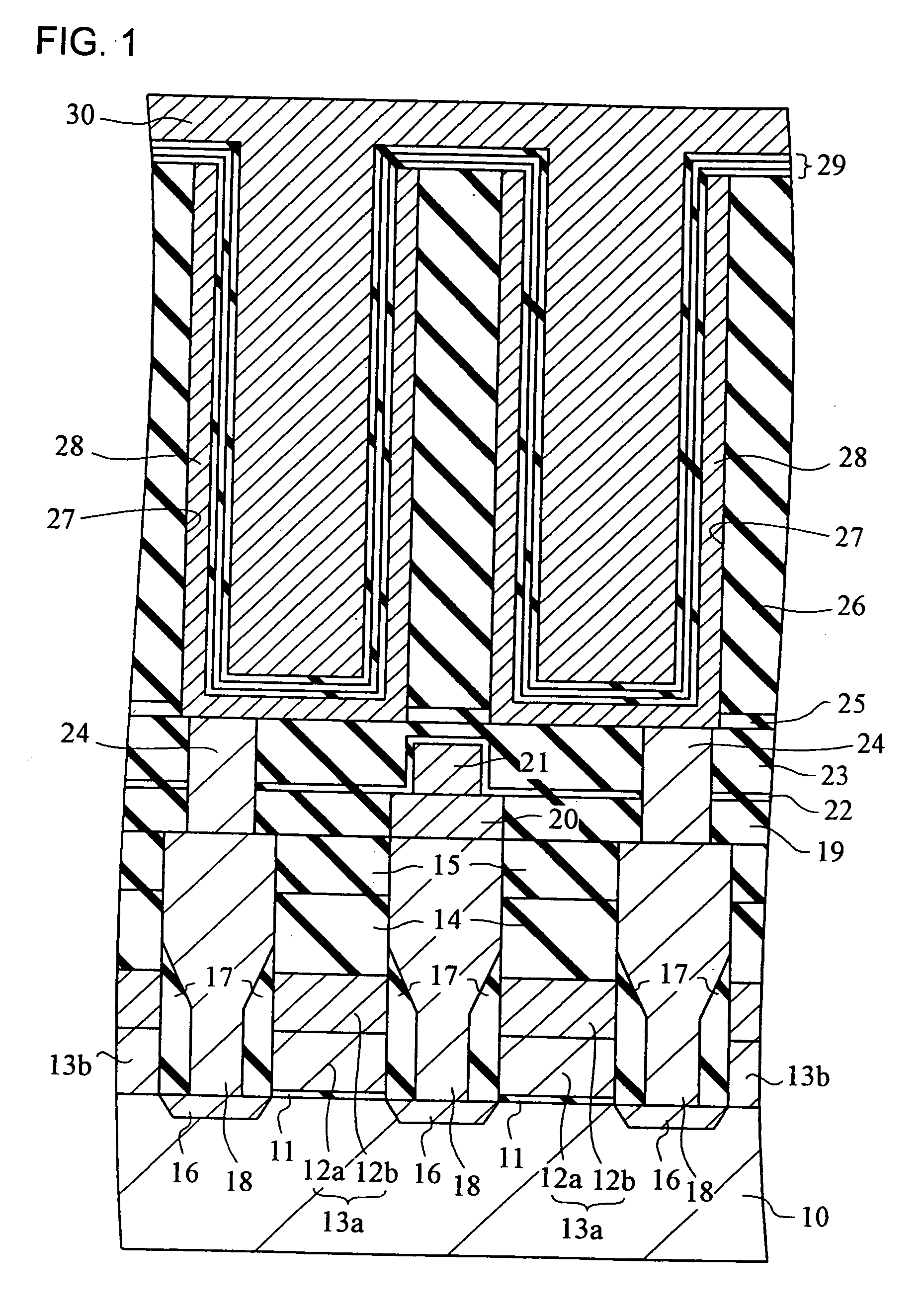

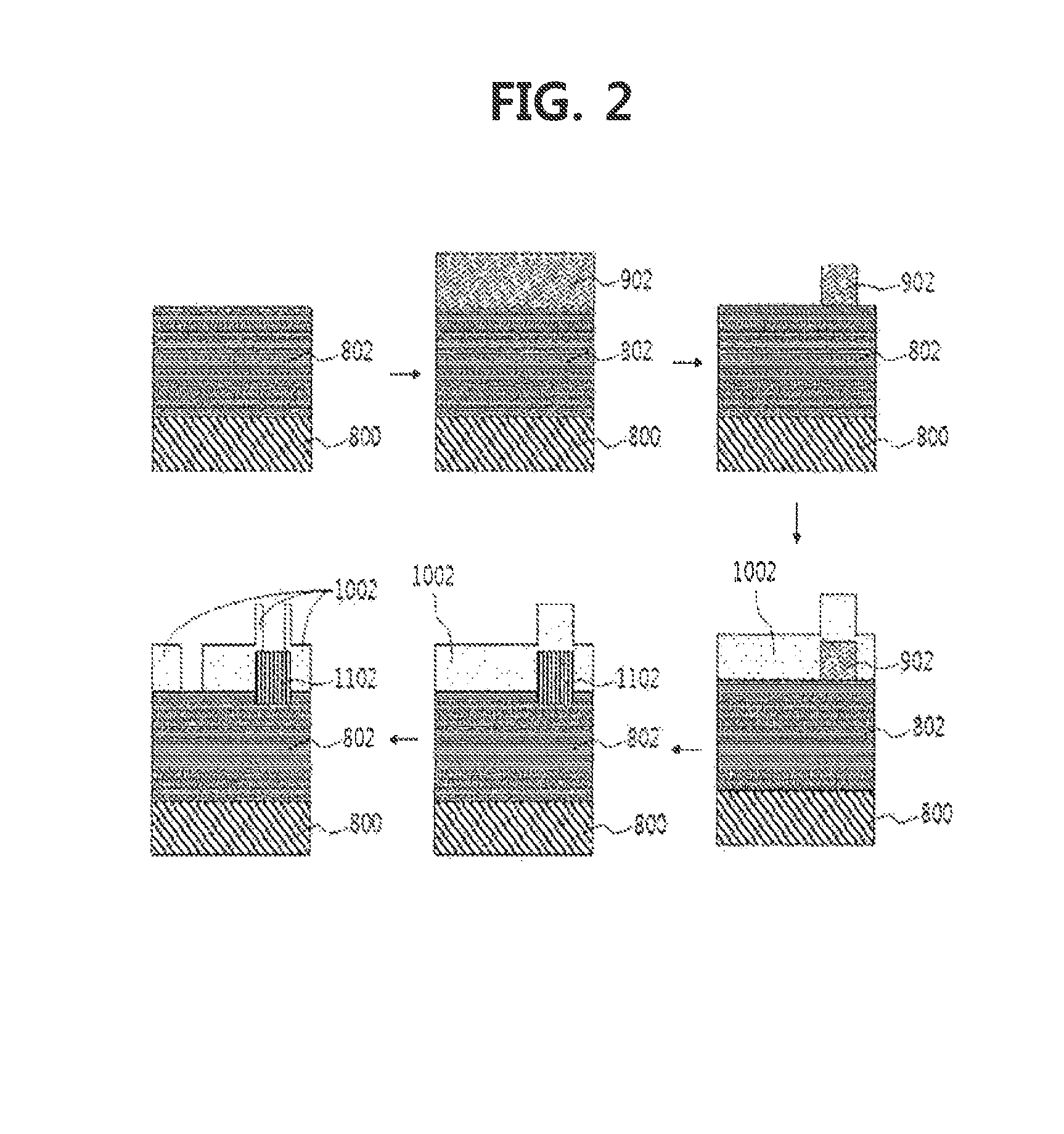

Semiconductor device and method of manufacturing the same

ActiveUS20080224263A1Minimize leakage currentSufficient capacitanceTransistorSolid-state devicesSemiconductorMetal

A semiconductor device including a capacitor which includes a first electrode, a second electrode, and a dielectric layer disposed between the first electrode and the second electrode, the dielectric layer including: a first paraelectric film formed of a material containing a first metal element and at least one kind of second metal element; a second paraelectric film disposed between the first electrode and the first paraelectric film; and a third paraelectric film disposed between the second electrode and the first paraelectric film, wherein the second paraelectric film is formed of a material containing the first metal element but substantially not containing the second metal element, and the third paraelectric film is formed of a material containing the first metal element but substantially not containing the second metal element.

Owner:MICRON TECH INC

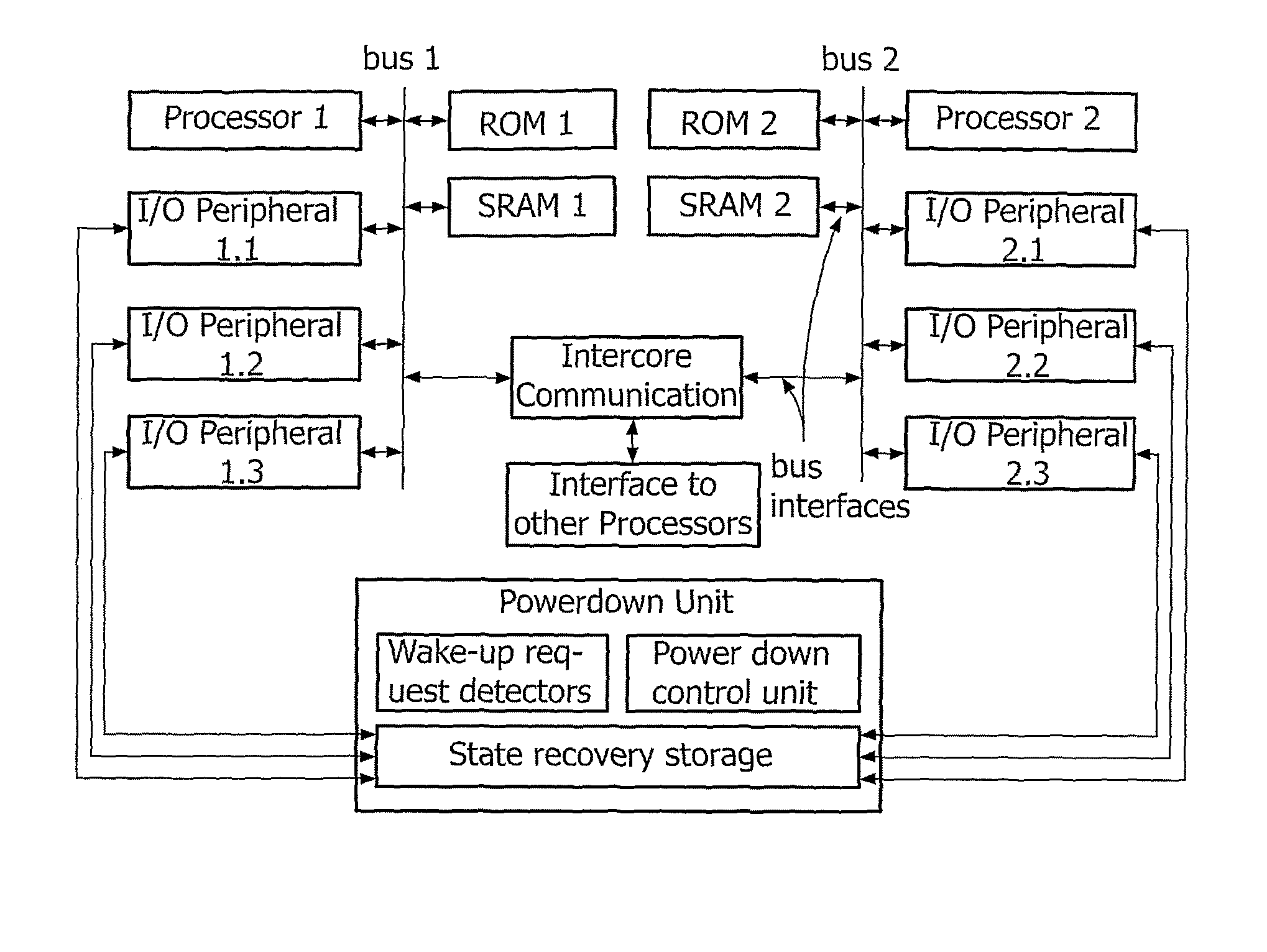

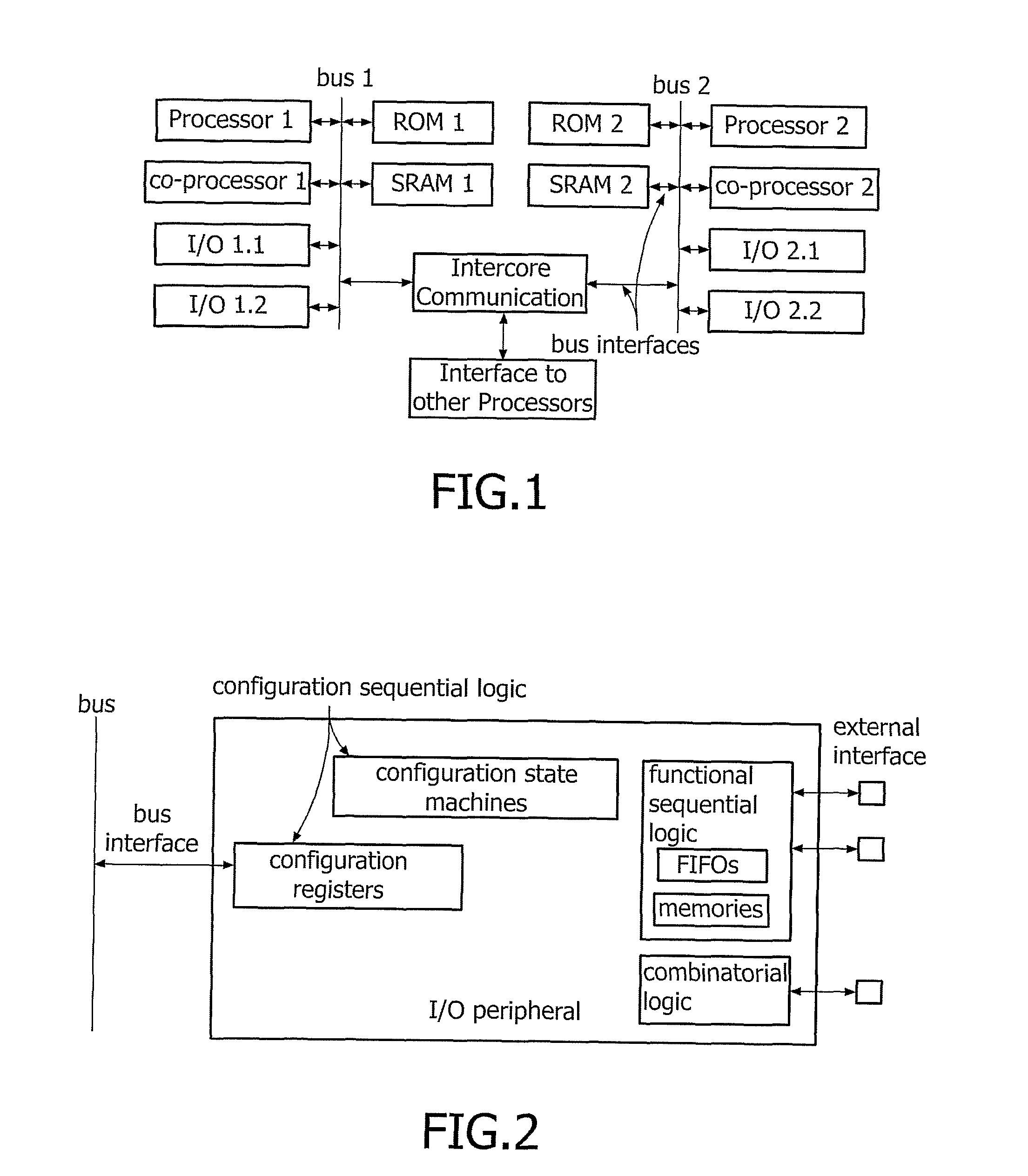

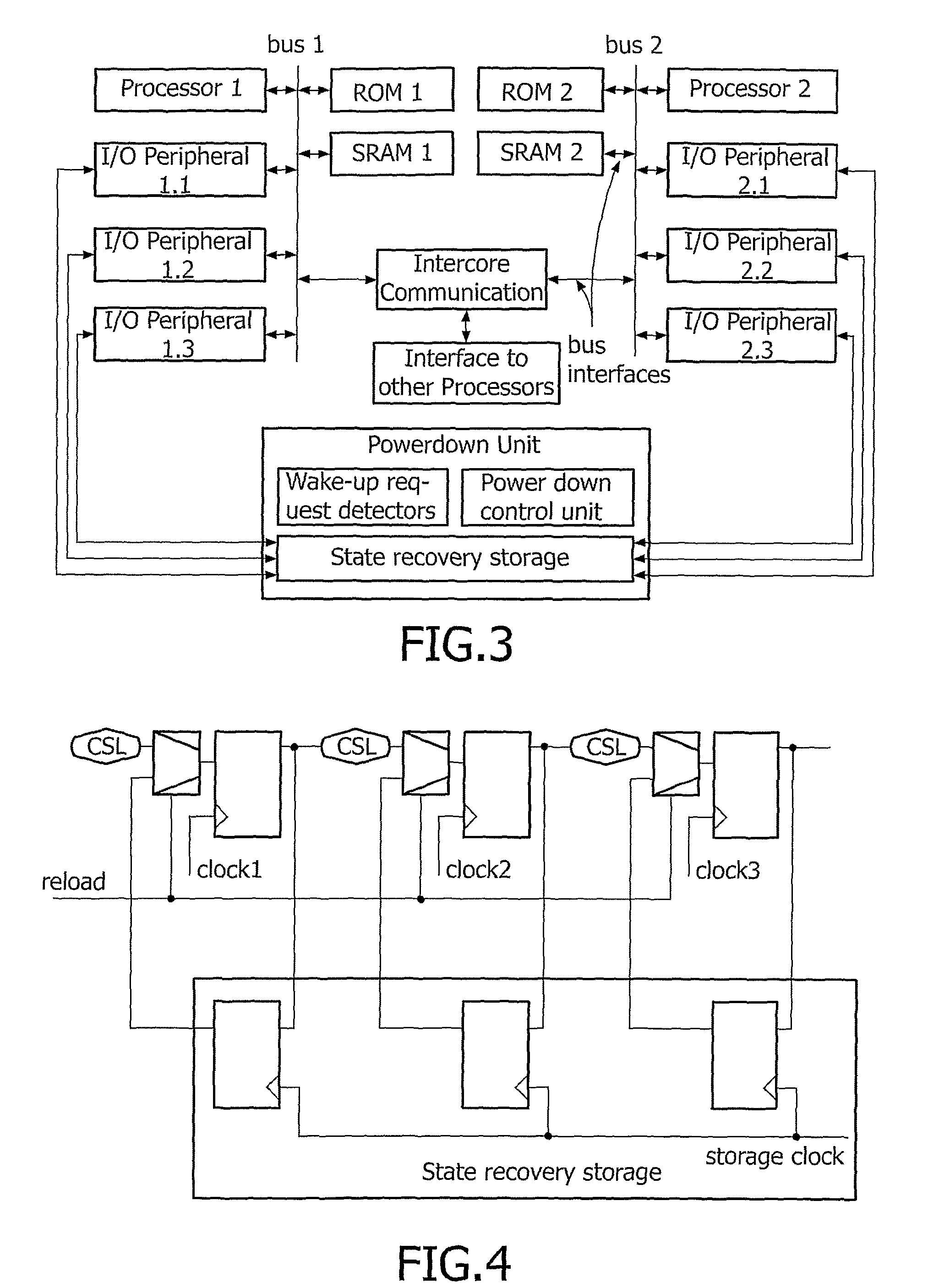

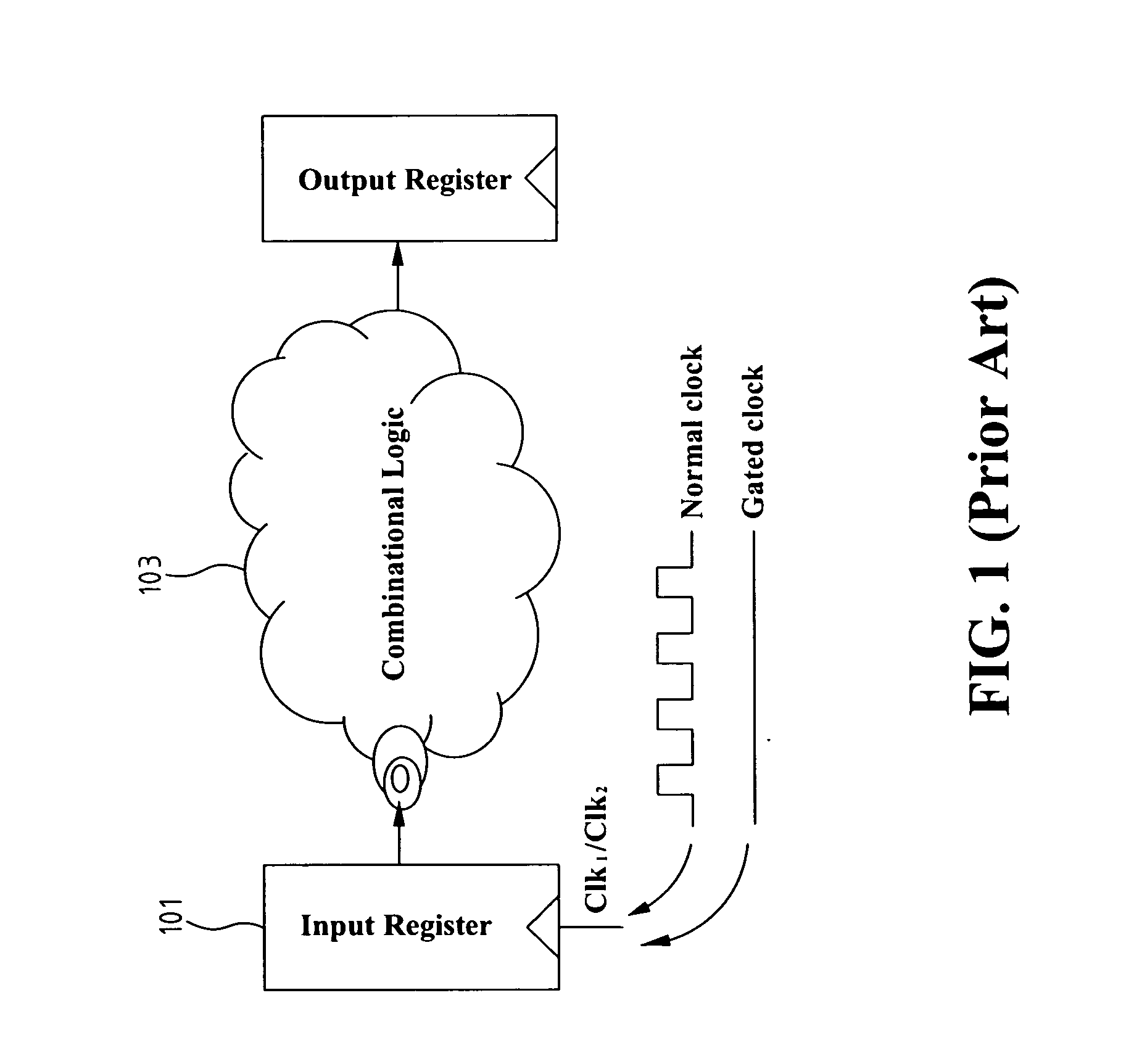

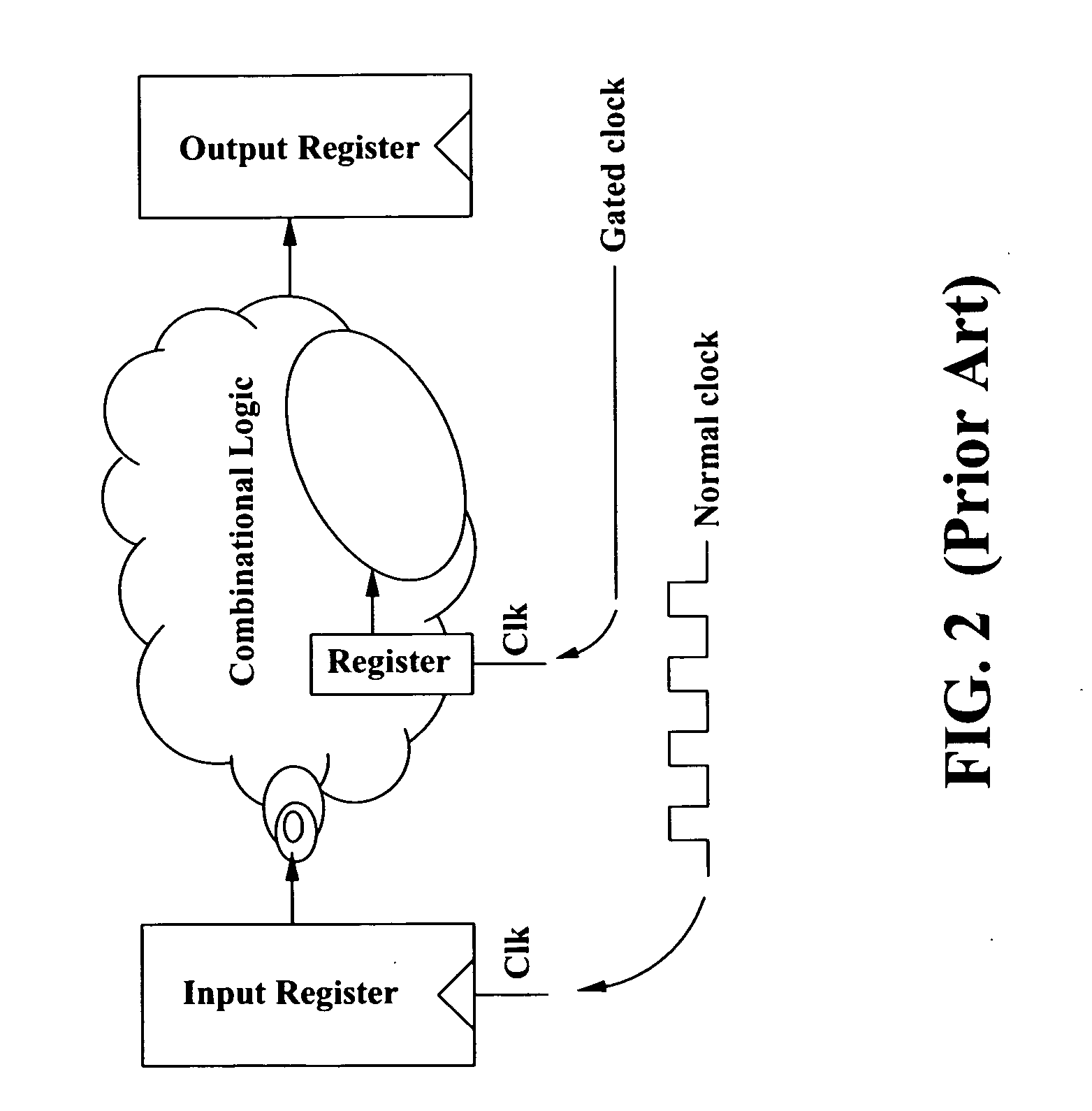

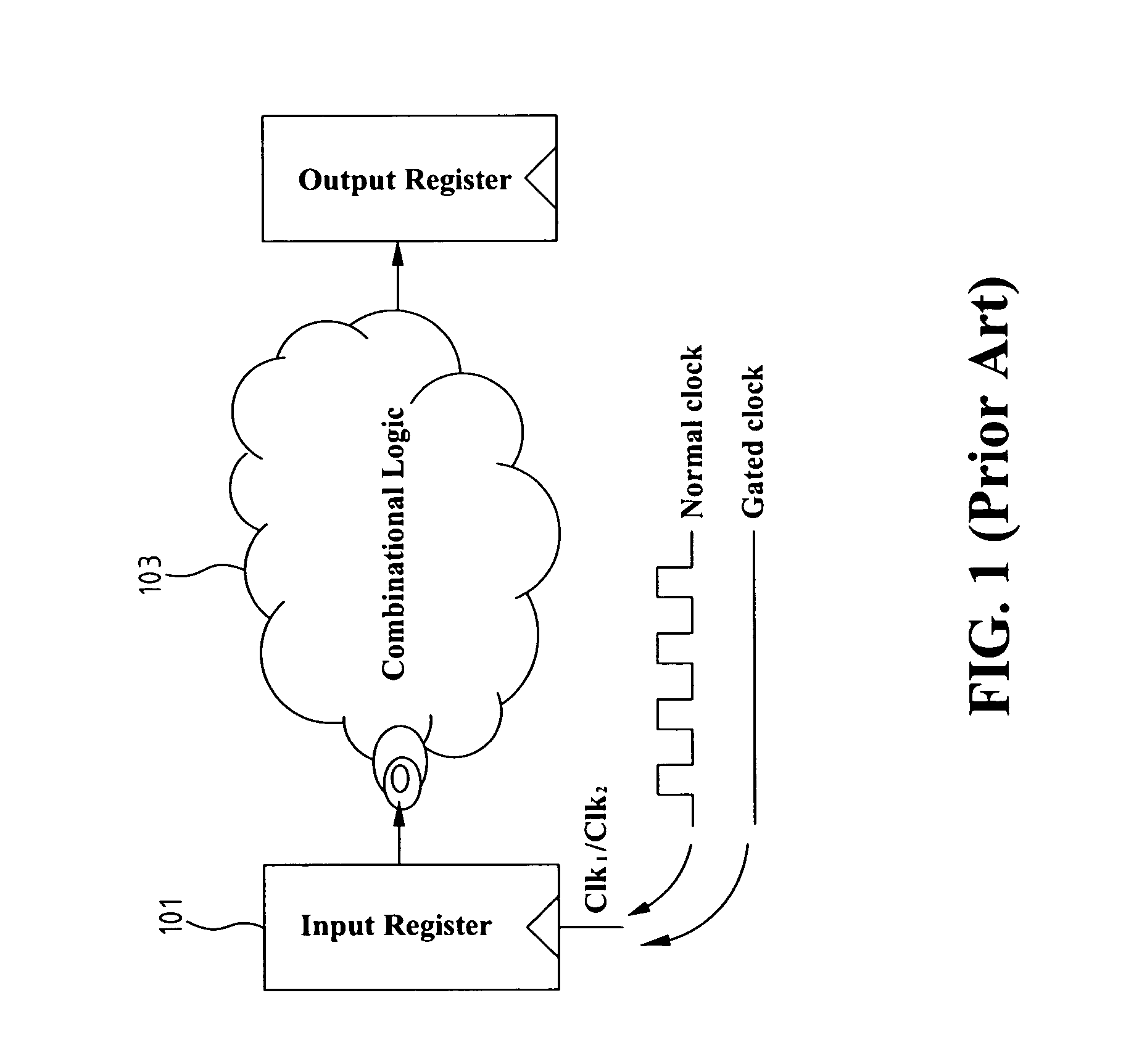

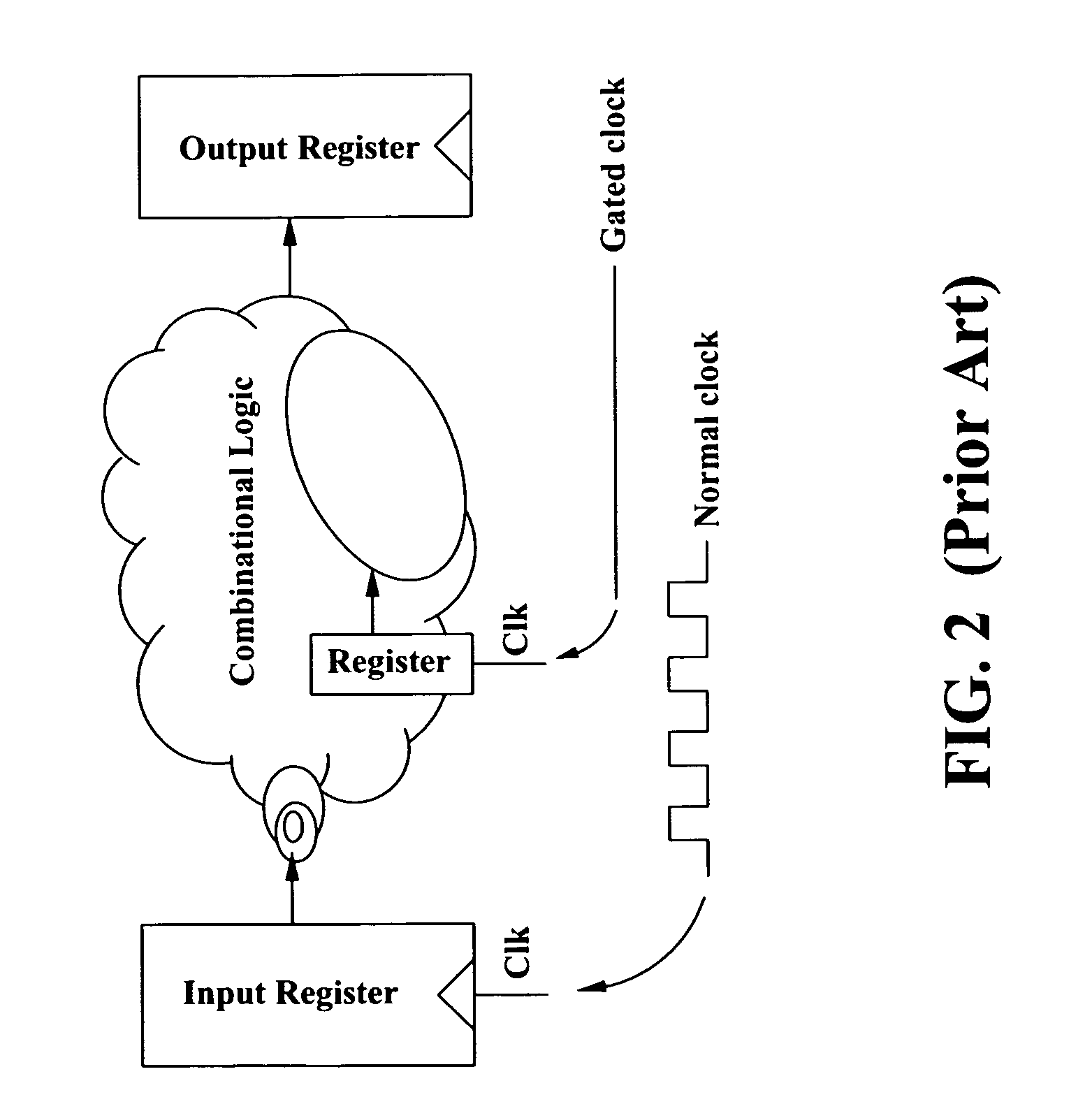

Method apparatus comprising integrated circuit and method of powering down such circuit

ActiveUS7848718B2Total current dropMinimizing leakage currentAnalogue computers for vehiclesResonant long antennasLow leakageEngineering

The present invention relates to a mobile apparatus comprising an integrated circuit to operate predefined functions, which integrated circuit is susceptible to be set in a standby operating mode wherein which said circuit can resume operation within a predefined delay. The circuit comprises configuration sequential logic having defined states that need to be stored before the circuit enters in standby mode. The mobile apparatus further comprises a power down unit for storing the states of the configuration sequential logic into a low leakage storage area during standby mode that reduces standby current considerably.

Owner:SNAPTRACK

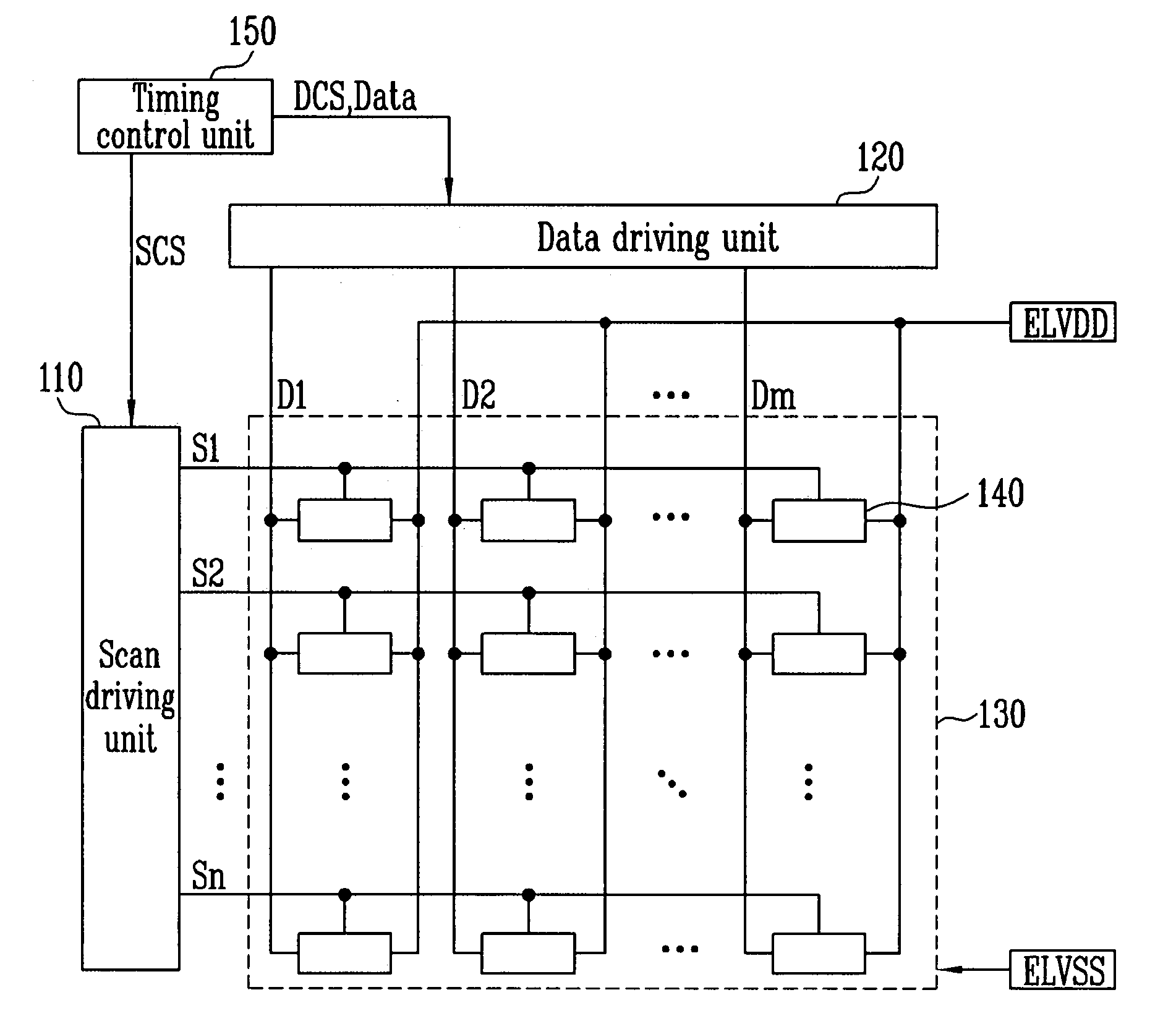

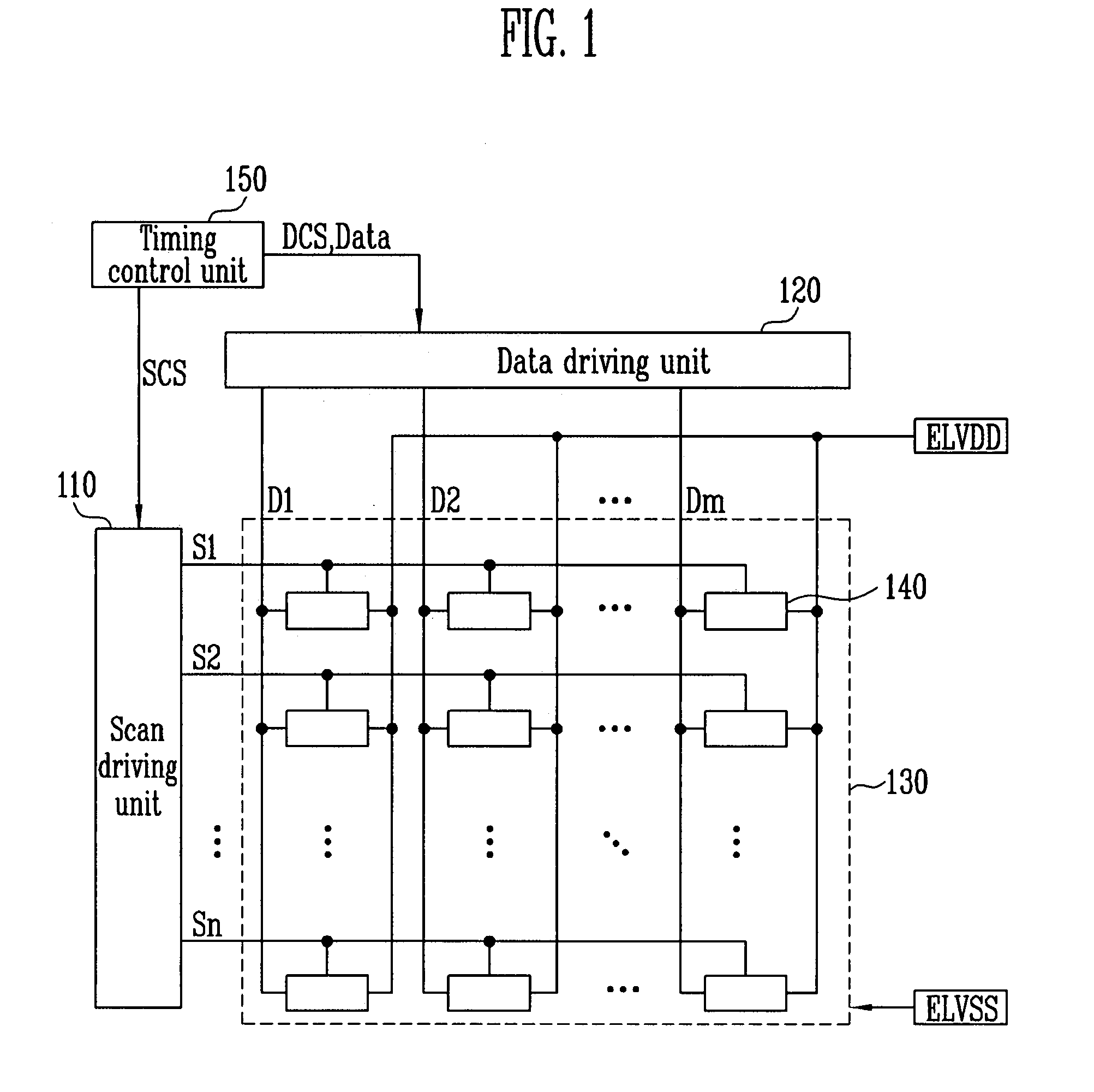

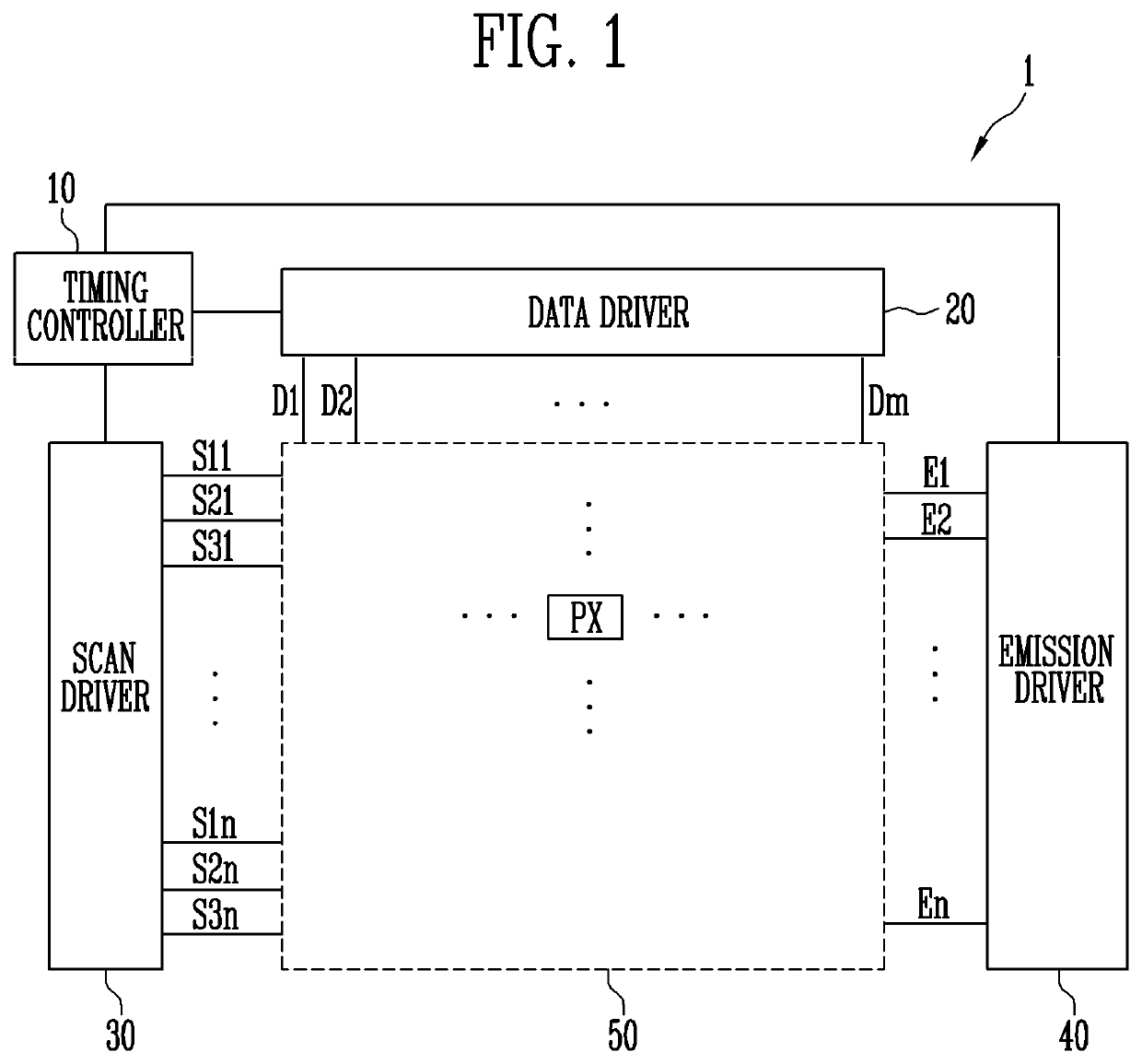

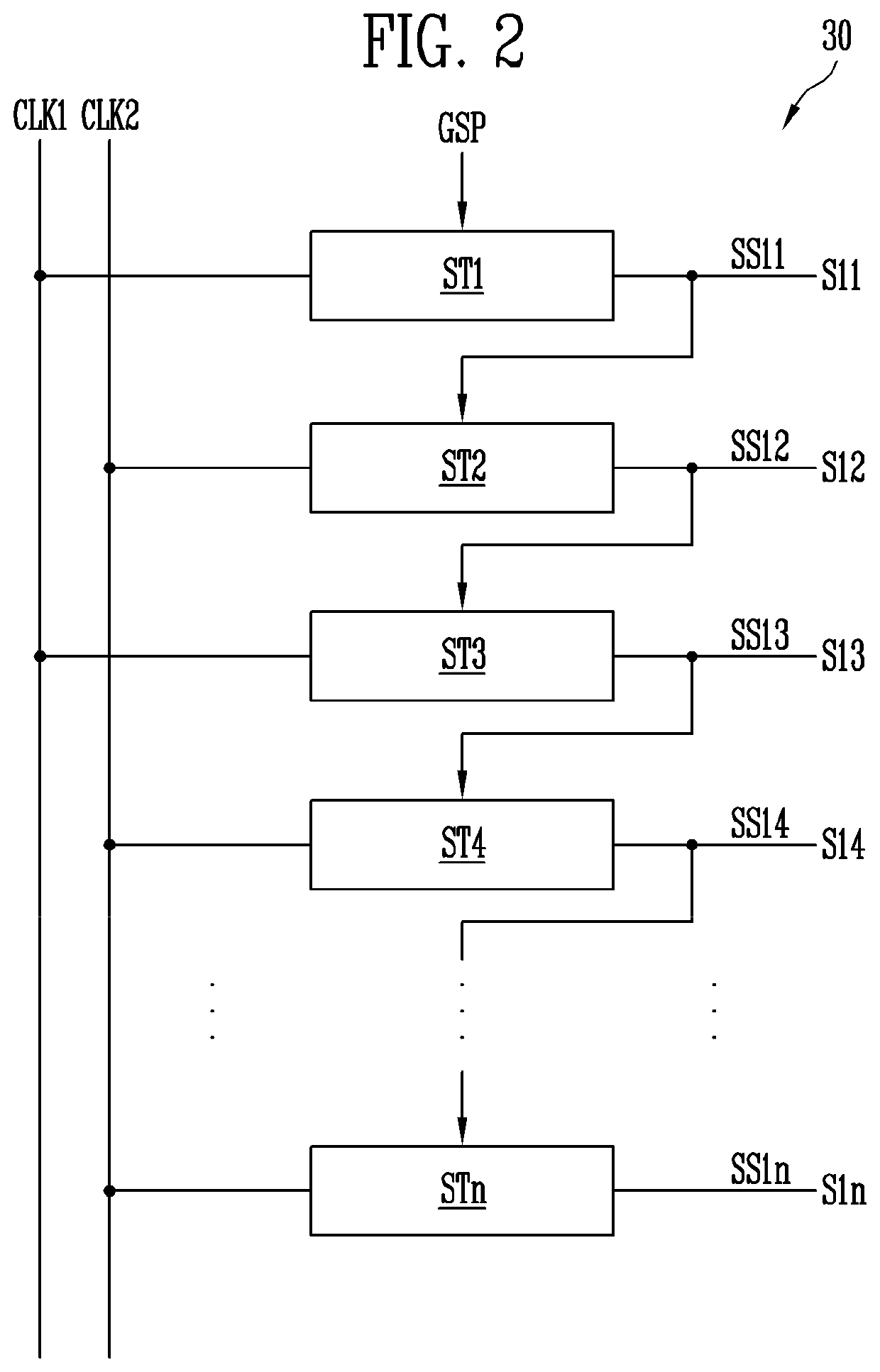

Shift register and organic light emitting display device using the same

InactiveUS20100171689A1Minimizing leakage currentSimple configurationStatic indicating devicesSolid-state devicesShift registerDisplay device

A shift register has a plurality of stages driven by first, second, and third clock signals. Each stage includes a first transistor coupled between a first power source and an output node, and having a gate electrode coupled to a first node, a second transistor coupled between the output node and the third input line, and having a gate electrode coupled to a second node, a third transistor coupled between the first power source and the first node, and having a gate electrode coupled to an input terminal receiving the start pulse or an output signal of a previous stage, a fourth transistor coupled between the first node and a second power source, and having a gate electrode coupled to the first input line, and a fifth transistor coupled between the input terminal and the second node, and having a gate electrode coupled to the second input line.

Owner:SAMSUNG DISPLAY CO LTD

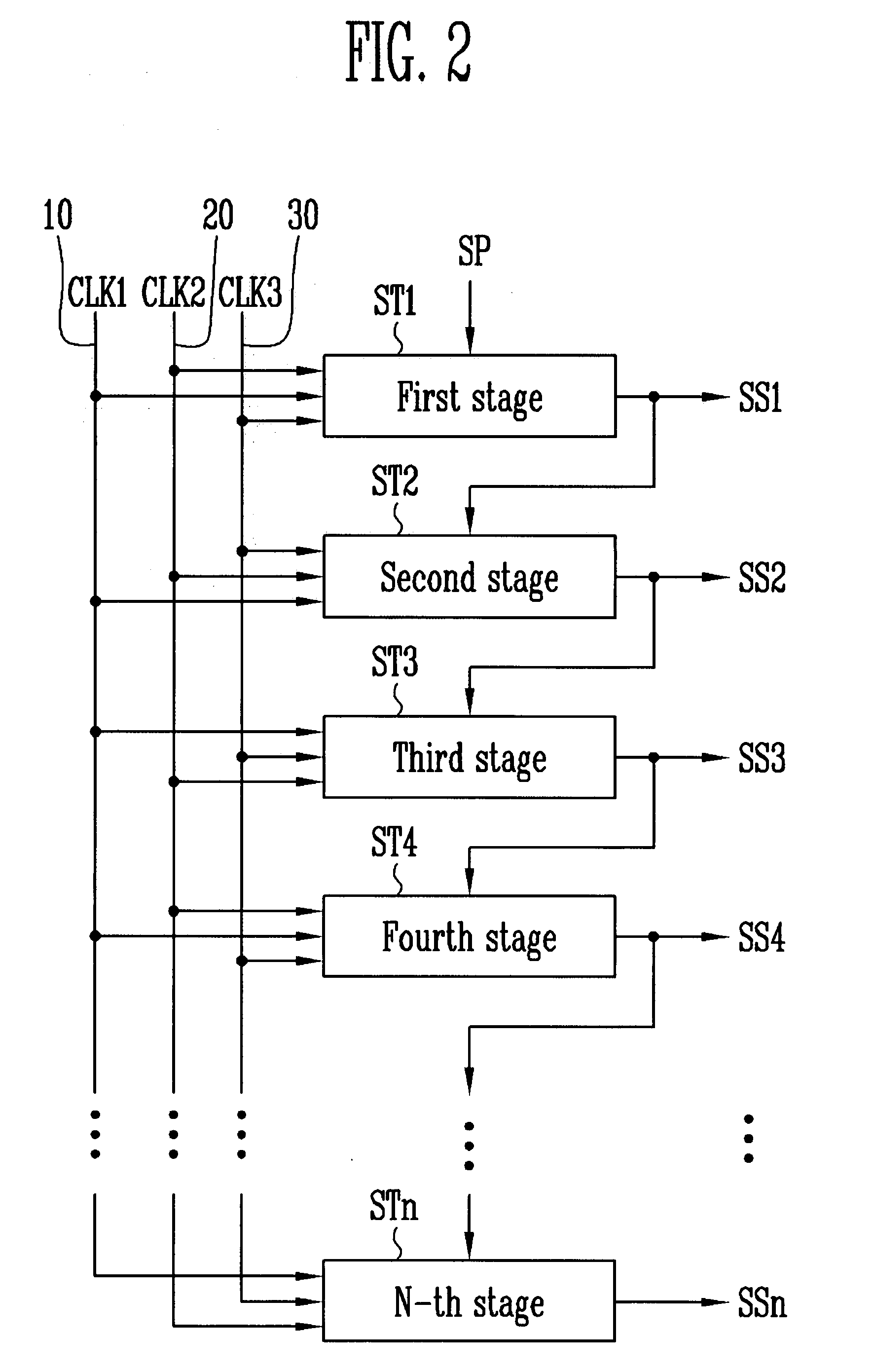

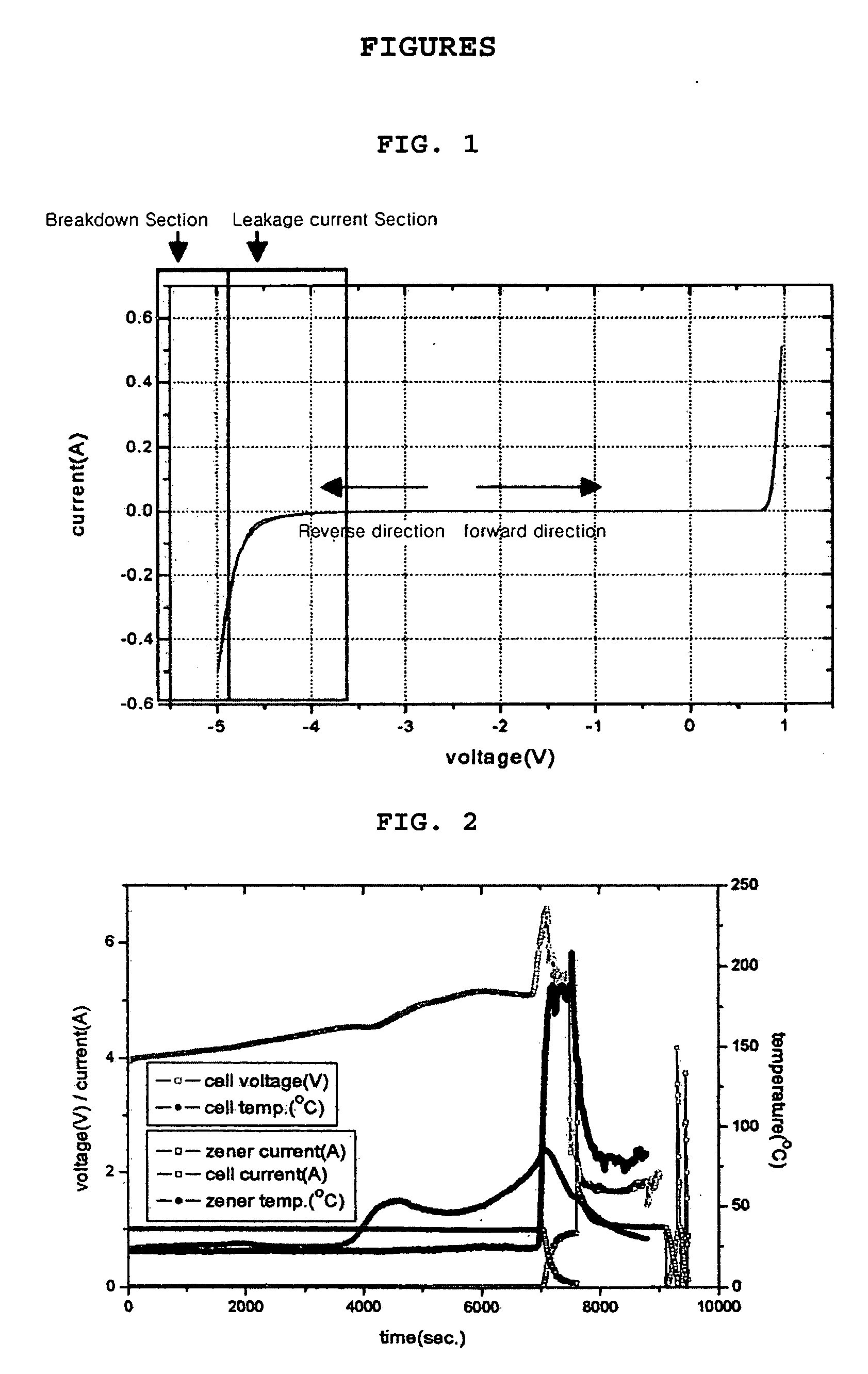

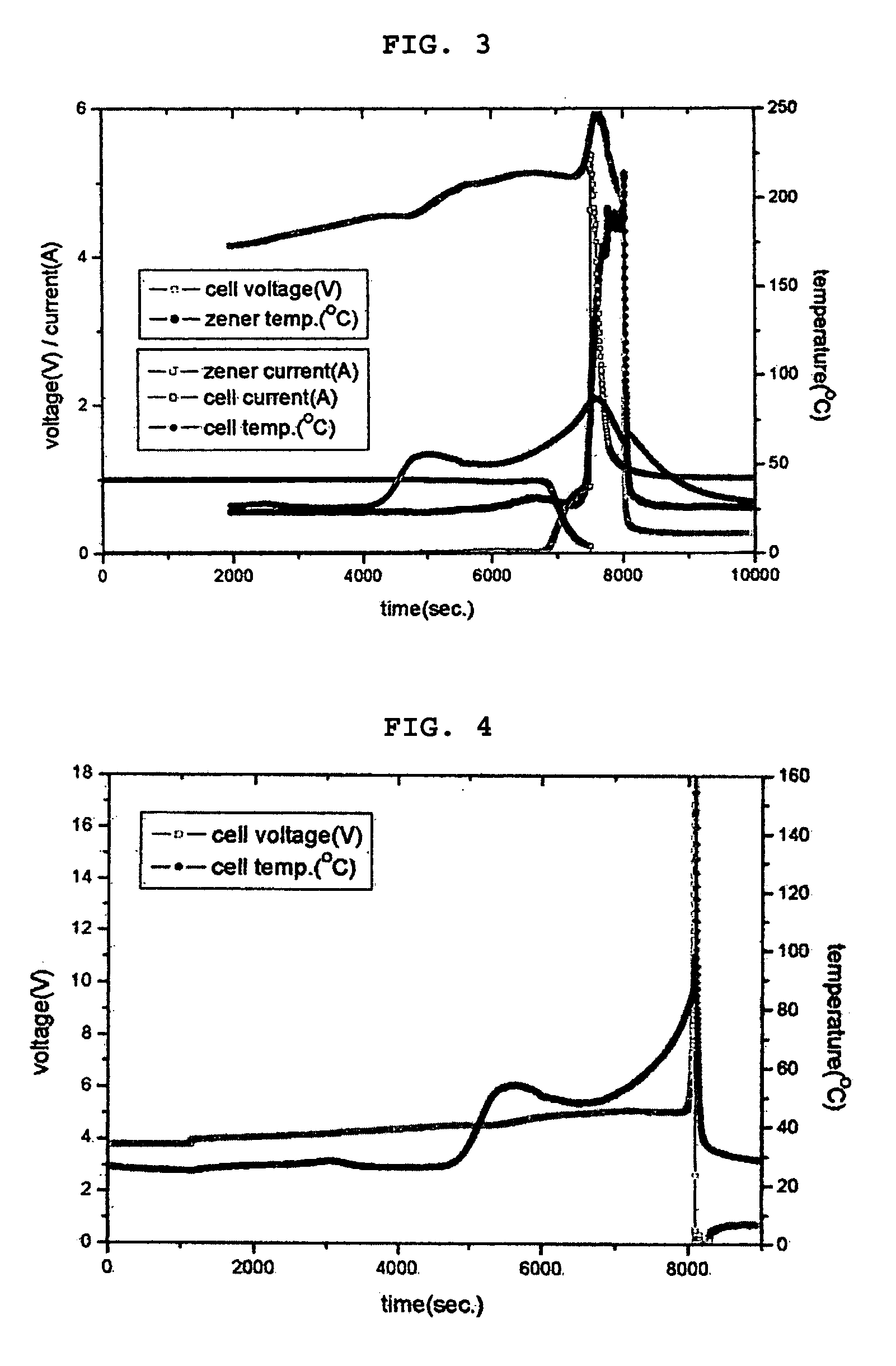

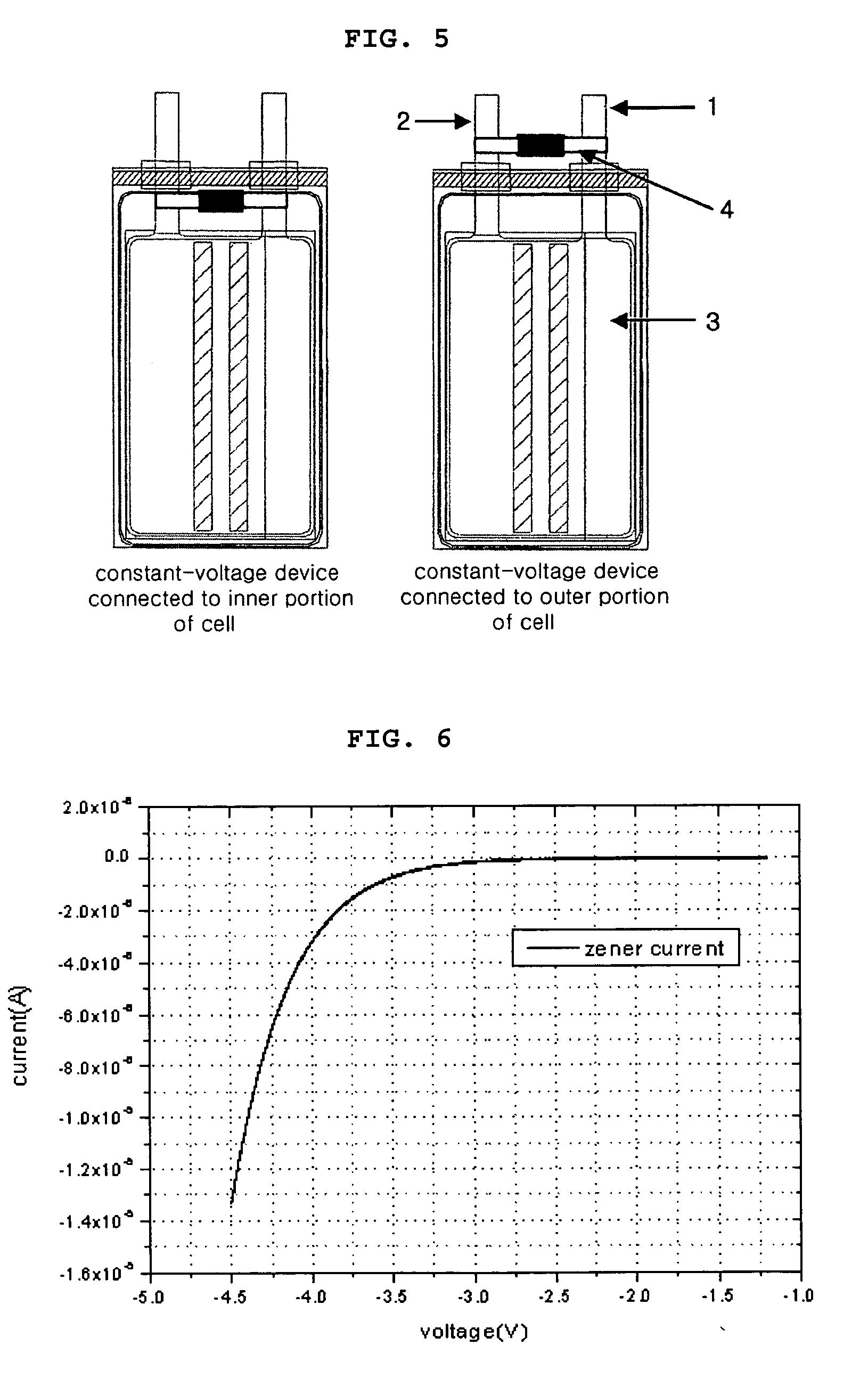

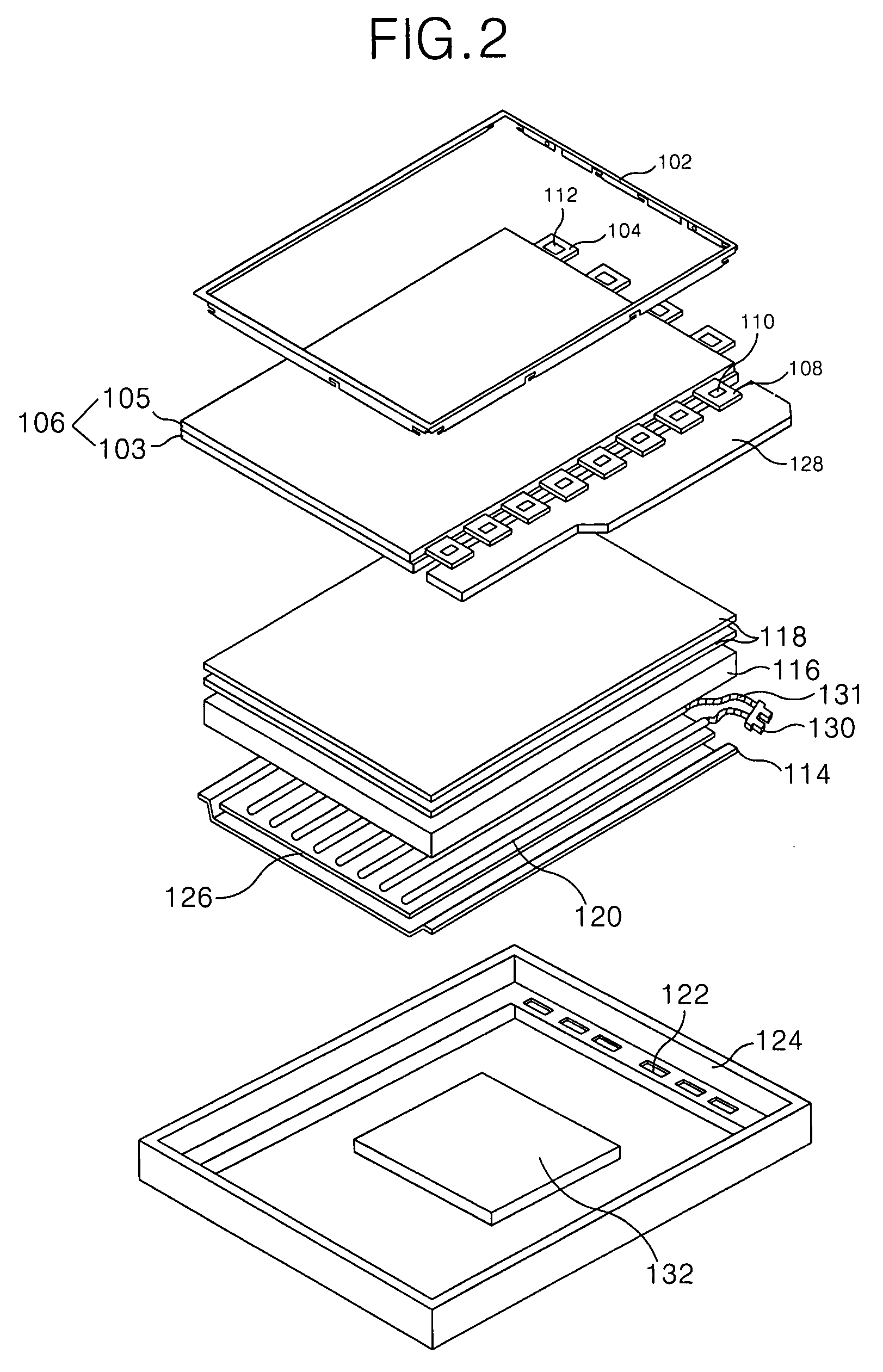

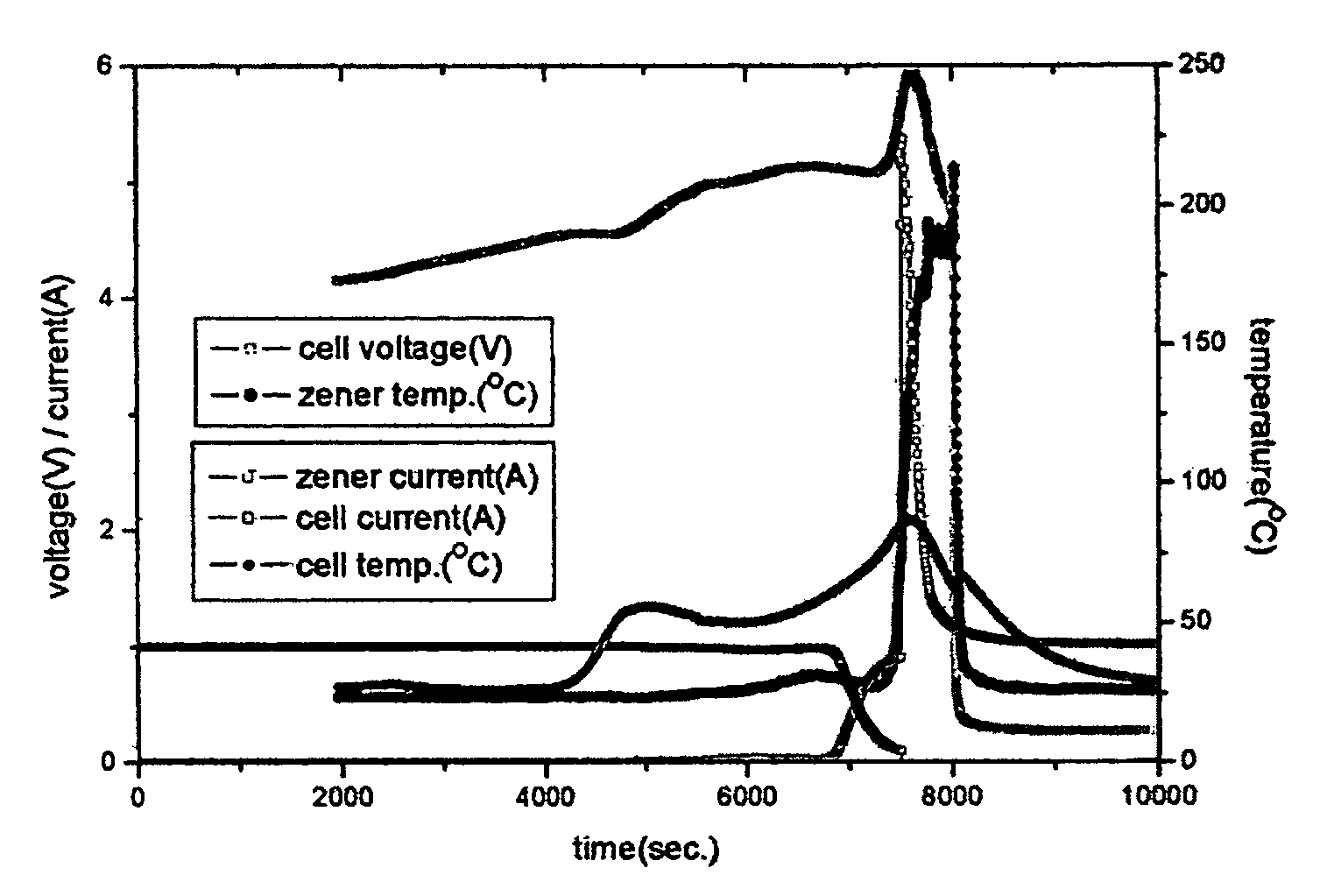

Secondary battery having constant-voltage device

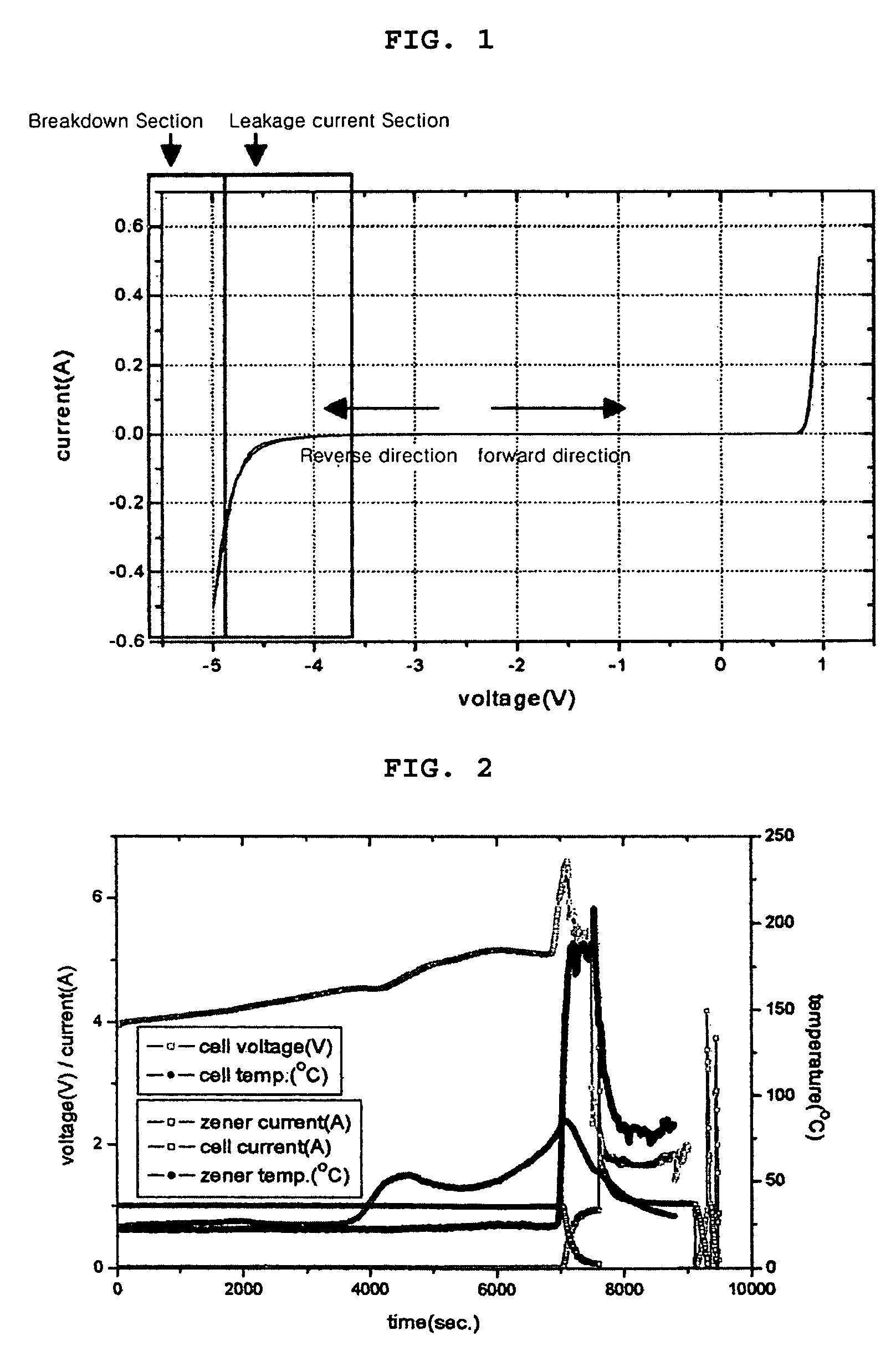

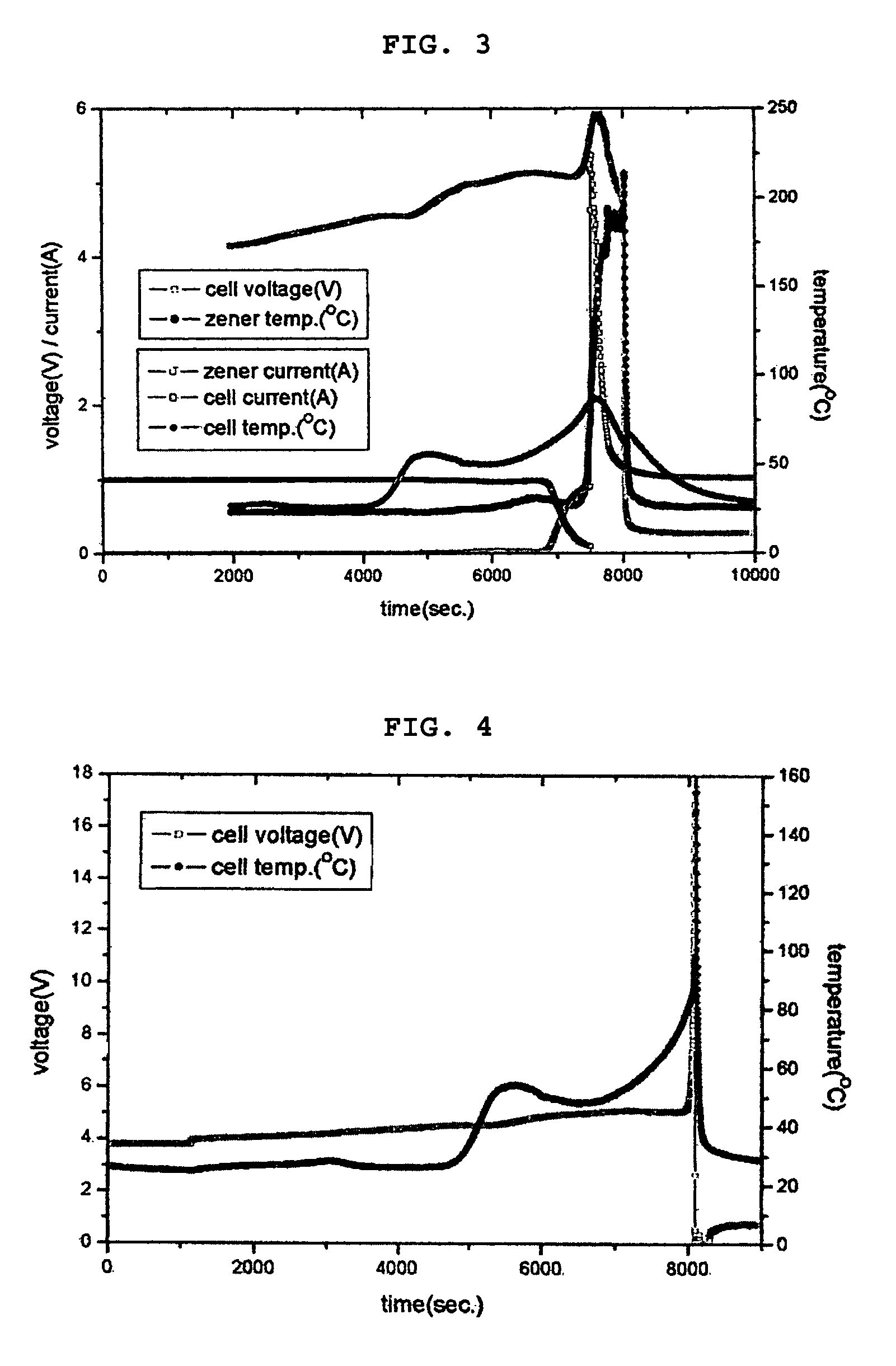

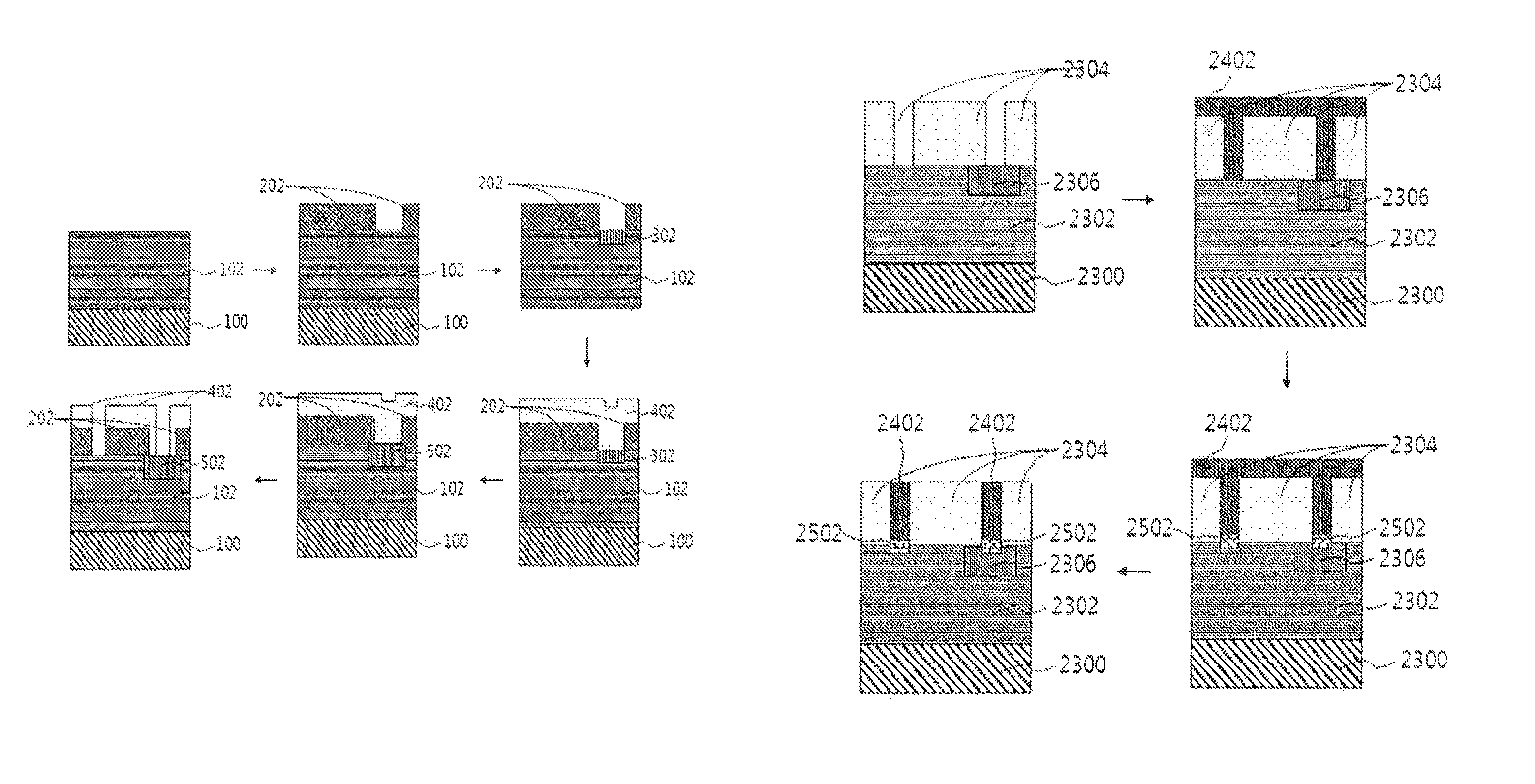

ActiveUS20060038534A1Avoid explosionAvoid ignitionBatteries circuit arrangementsElectric powerCapacity valueEngineering

Disclosed is a secondary battery having a constant-voltage device for preventing the secondary battery from being excessively overcharged. The breakdown voltage of the constant-voltage device is lower than the explosion or ignition voltage of the secondary battery, so the discharge operation may occur before the secondary battery is exploded or ignited even if the voltage of the secondary battery rises above the overcharge voltage, thereby protecting the secondary battery from explosion or ignition. The leakage current value of the constant-voltage device is less than 0.05% of the capacity value of the secondary battery under the maximum charge voltage of the secondary battery, or the breakdown voltage of the constant-voltage device is higher than the maximum charge voltage of the secondary battery. Thus, the constant-voltage device rarely generates the leakage current even if the secondary battery has been charged with the maximum charge voltage.

Owner:LG ENERGY SOLUTION LTD

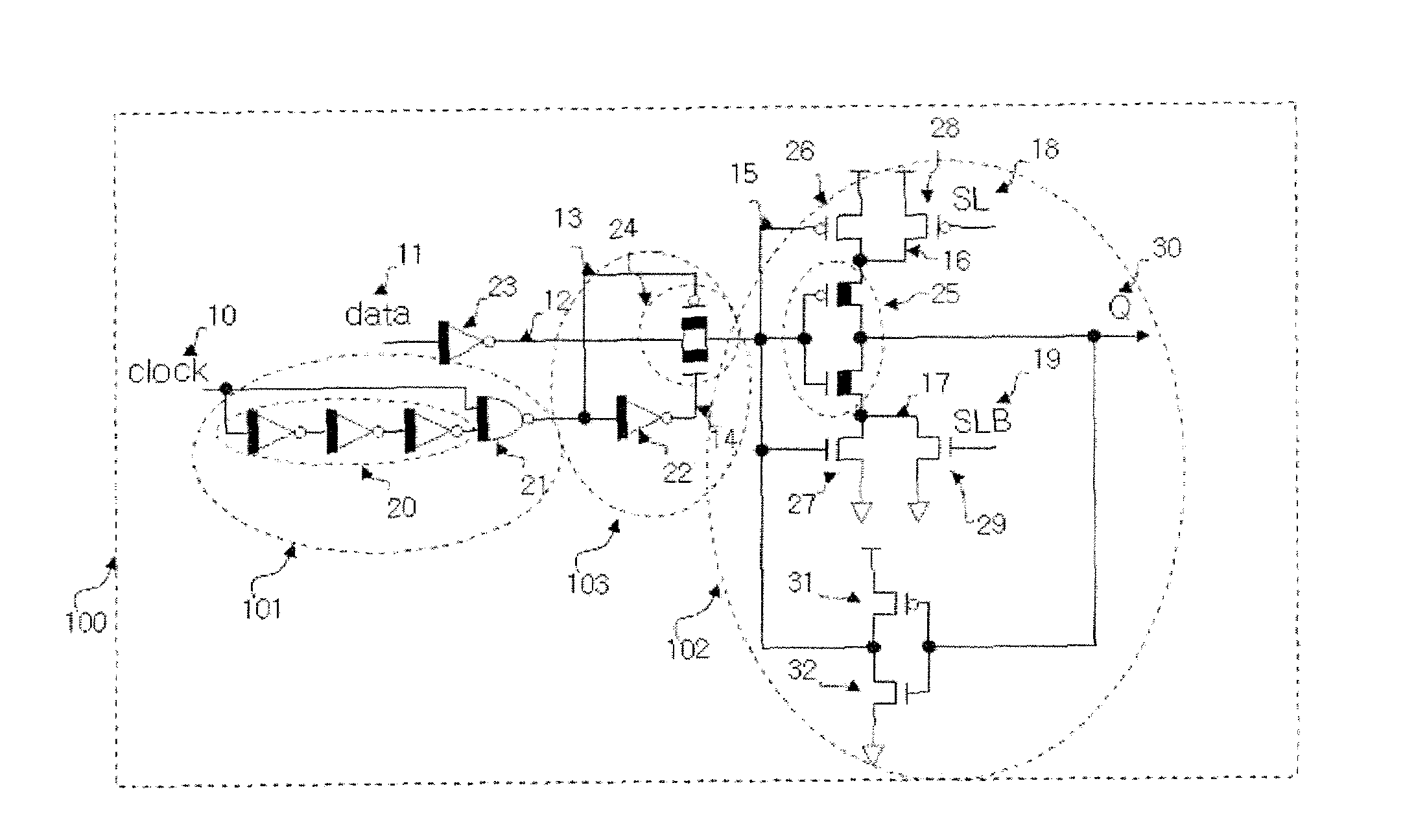

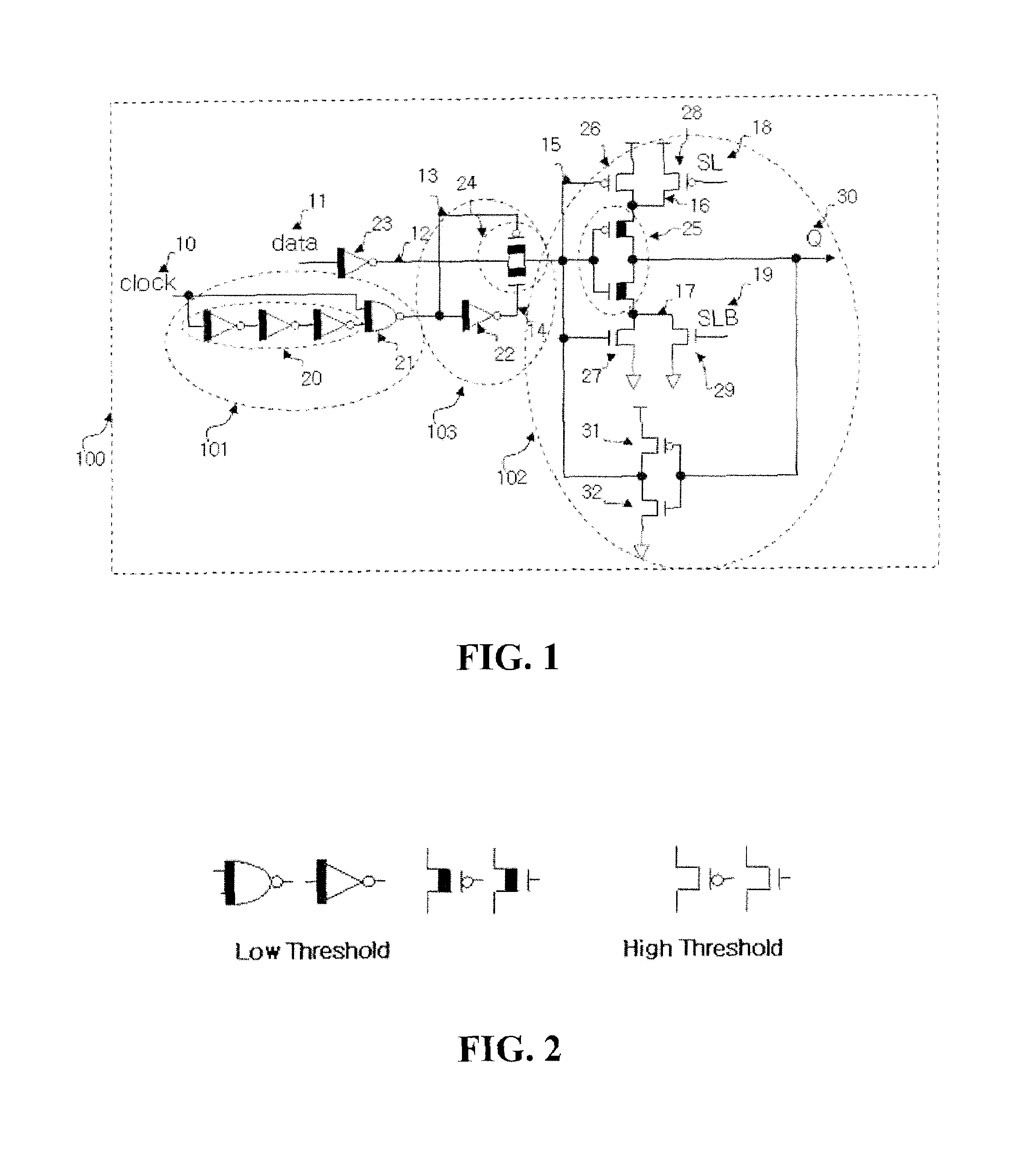

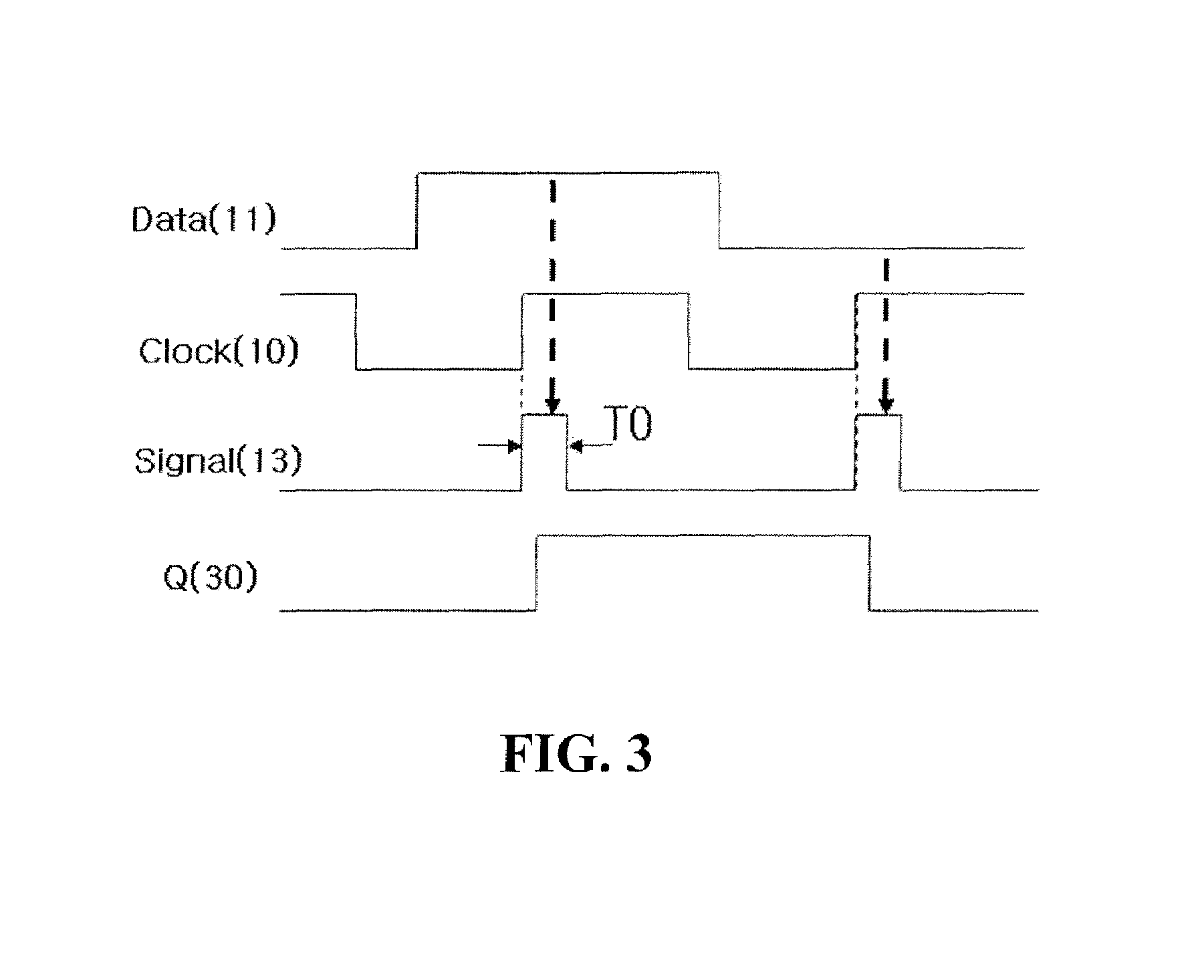

MTCMOS Flip-Flop Circuit

InactiveUS20080157842A1Minimizing leakage currentSimple interfaceDigital storageElectric pulse generatorData signalLogic gate

Disclosed is a multi-threshold CMOS (MTCMOS) flip-flop circuit. The MTCMOS flip-flop circuit includes a data input unit including an inverter for receiving an input data signal, inverting the input data signal and then outputting an inverted data signal; a clock signal generator including an inverter for receiving an input clock signal and a logic gate for generating a pulsed clock for latching the inverted data signal at a rising time of the input clock signal; a data transmitting unit including a switch for receiving the data signal output from the data input unit to selectively output the inverted data signal and controlling transmission of data based on the pulsed clock; and a data latch and output unit including a feedback inverter having a feedback path used for data latch so as to receive the inverted data signal and generate an output Q.

Owner:DONGBU HITEK CO LTD

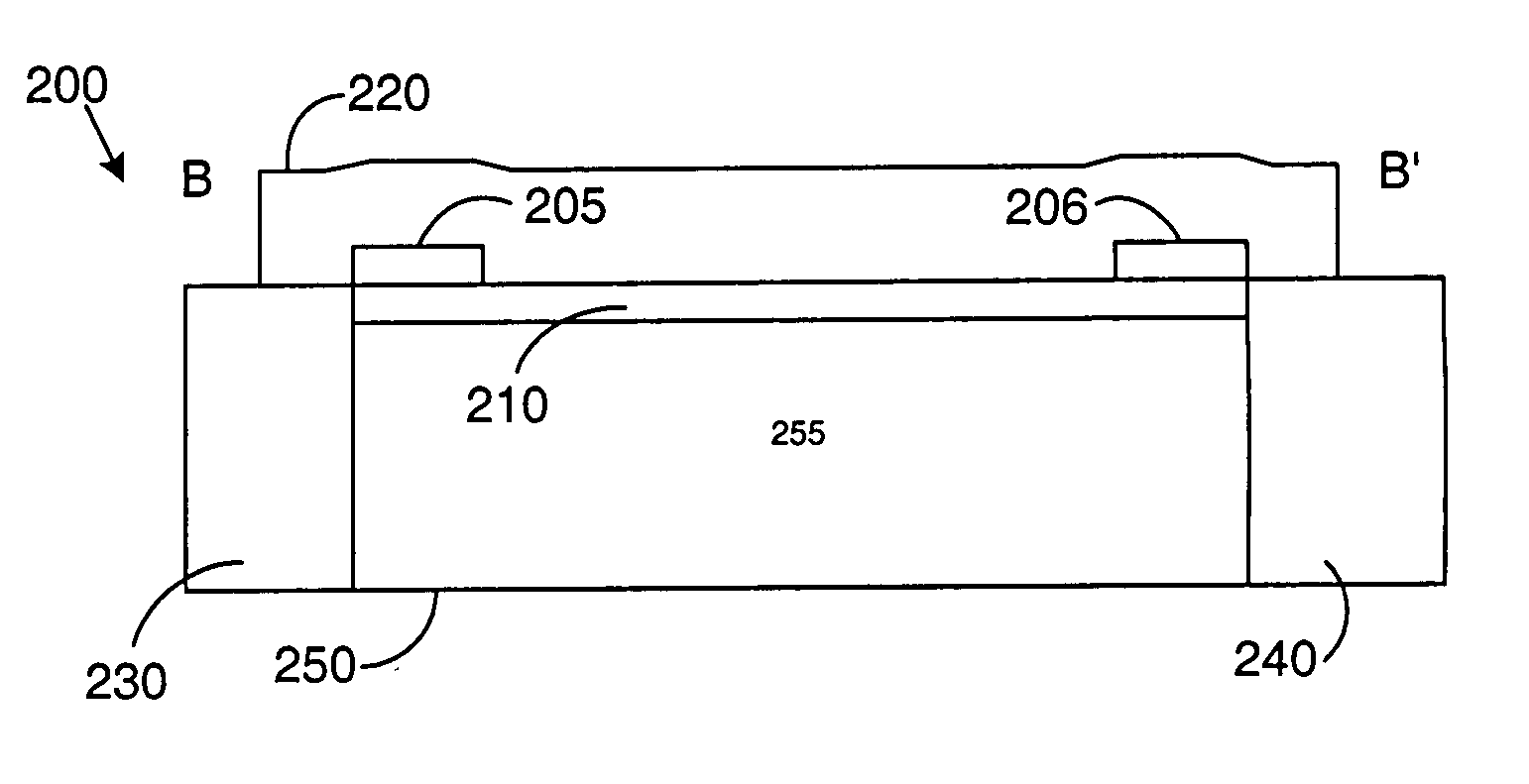

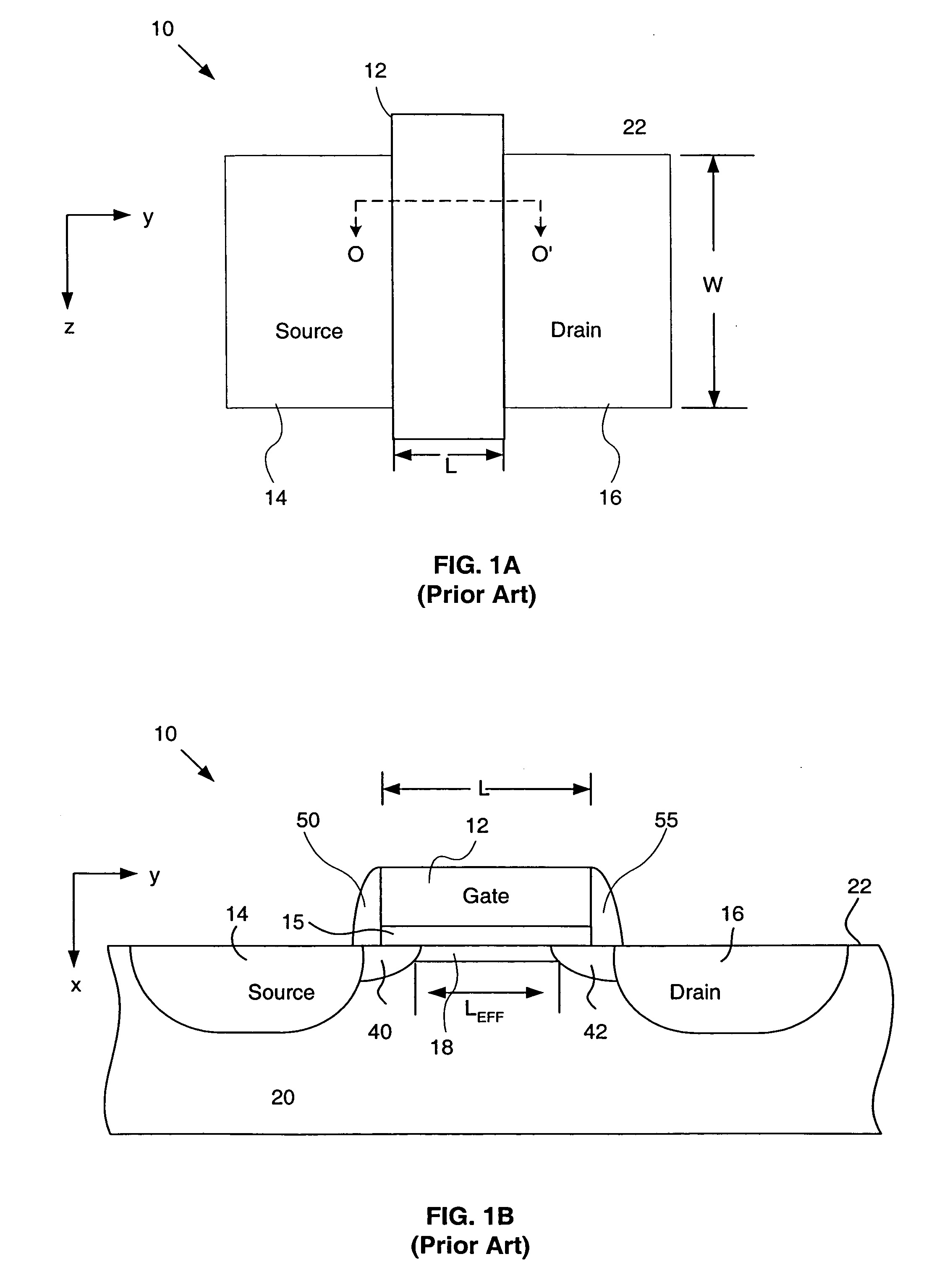

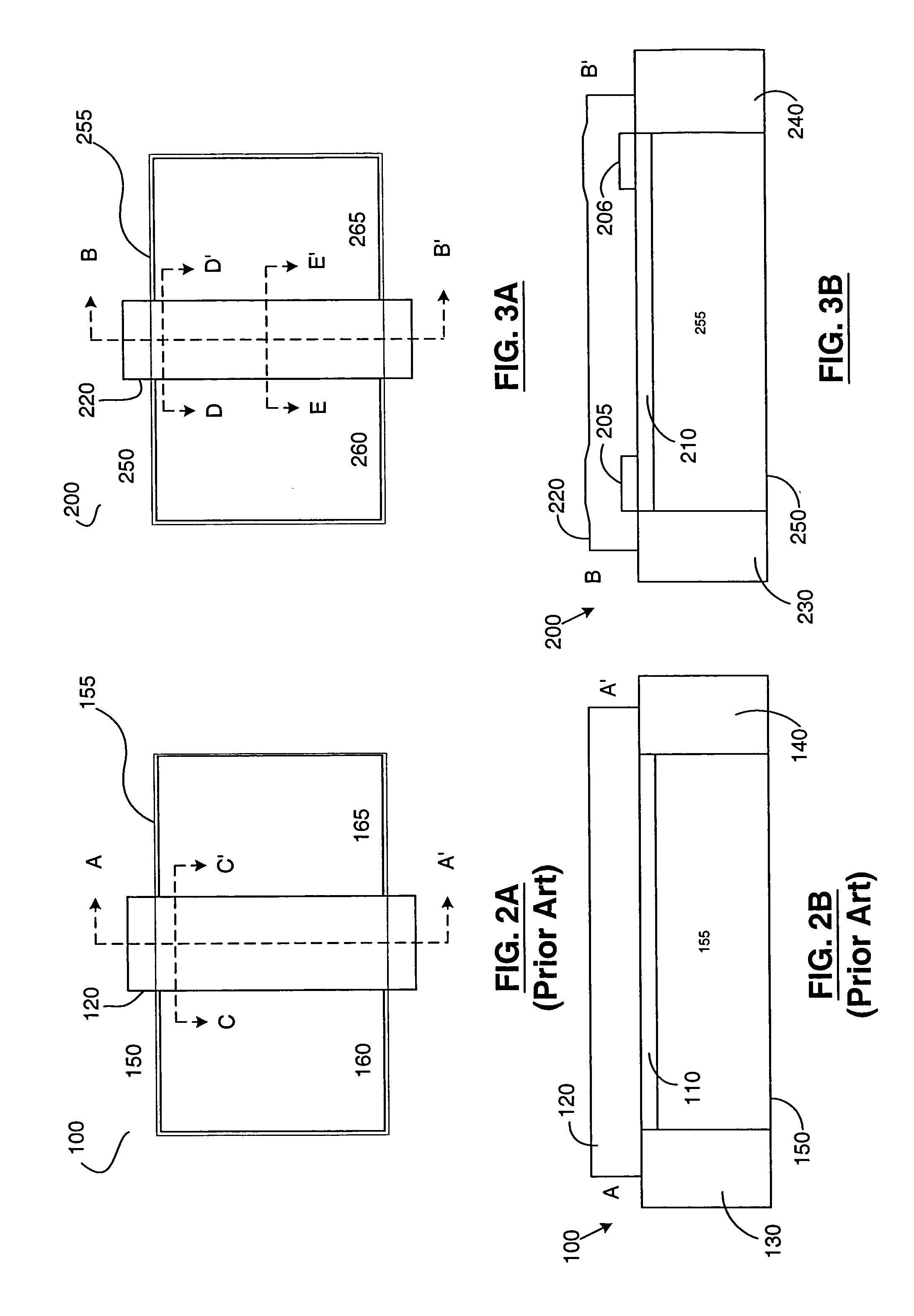

Dual-oxide transistors for the improvement of reliability and off-state leakage

InactiveUS6951792B1Minimizing leakage currentReduce leakage currentTransistorSemiconductor/solid-state device manufacturingLow leakageGate oxide

The invention provides a transistor having low leakage currents and methods of fabricating the transistor on a semiconductor substrate. The transistor has a gate and a nonuniform gate oxide under the gate.

Owner:ALTERA CORP

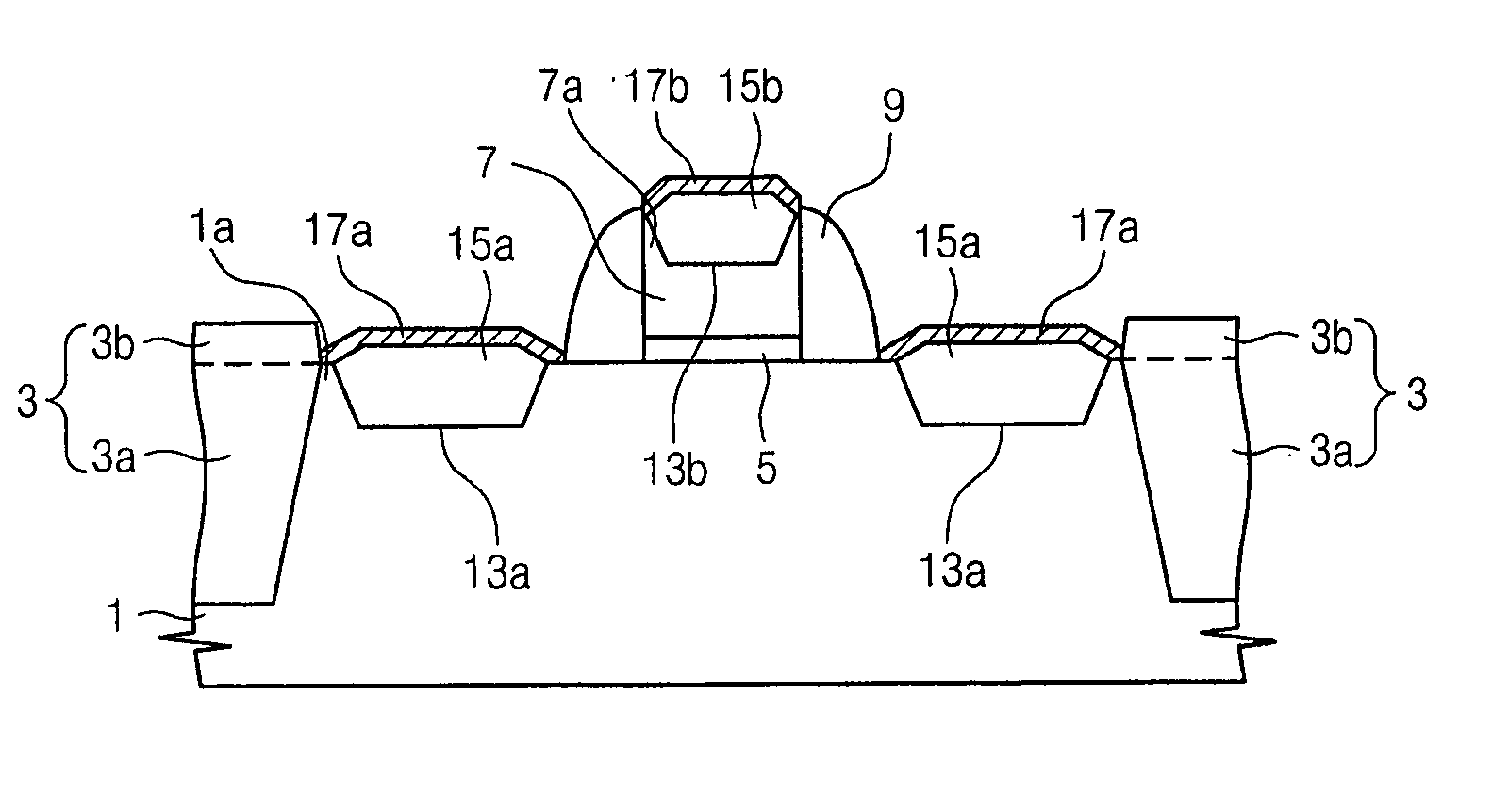

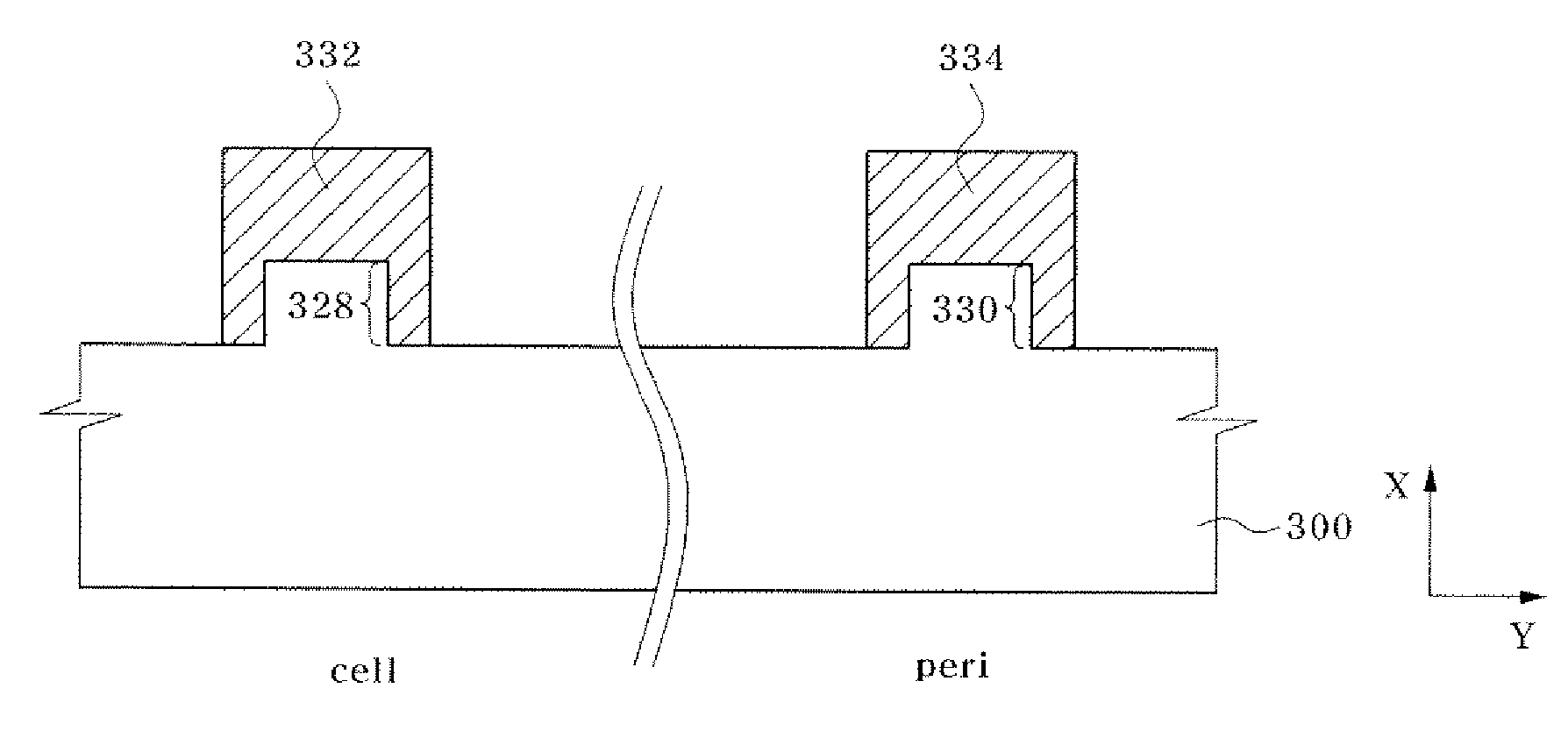

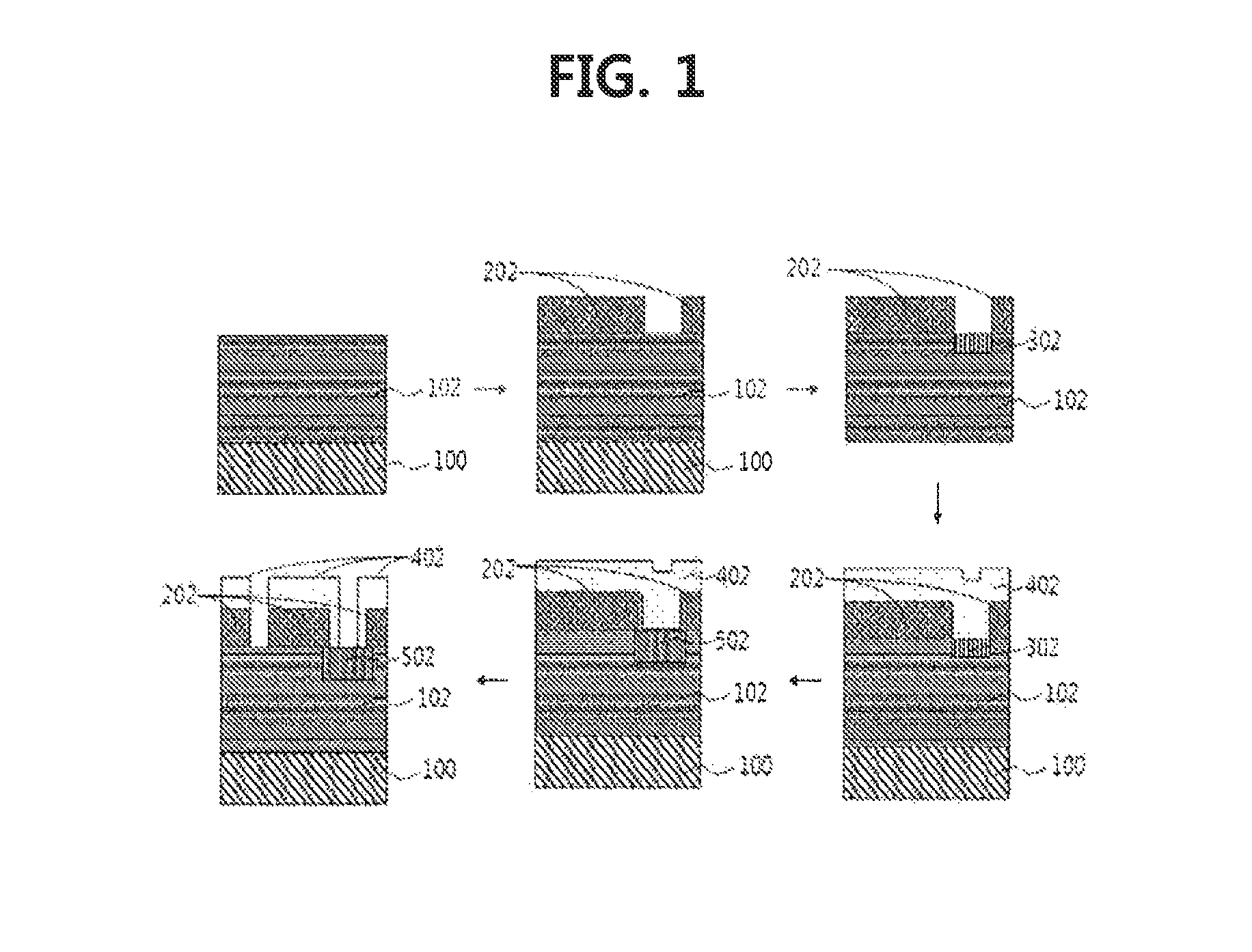

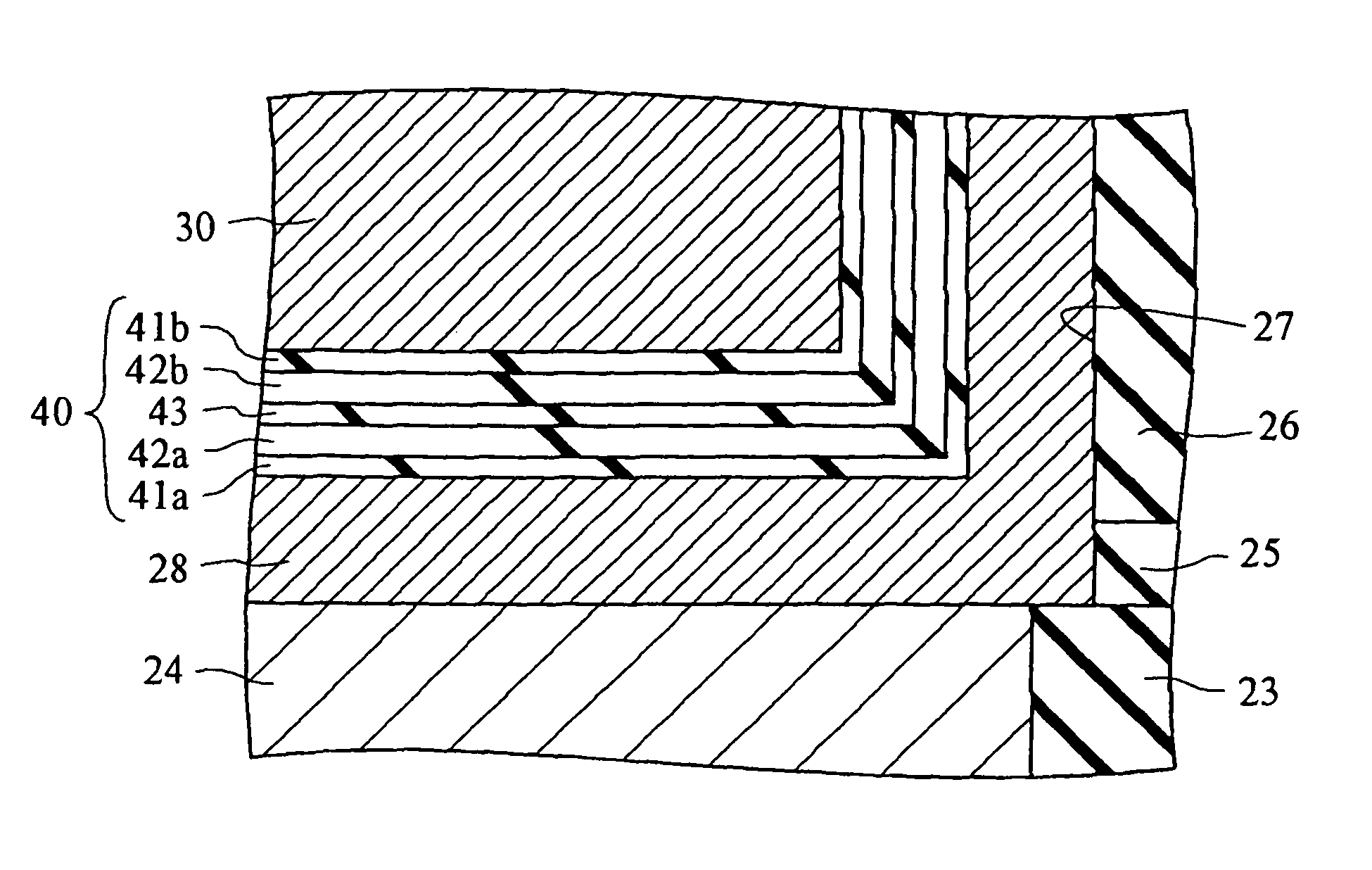

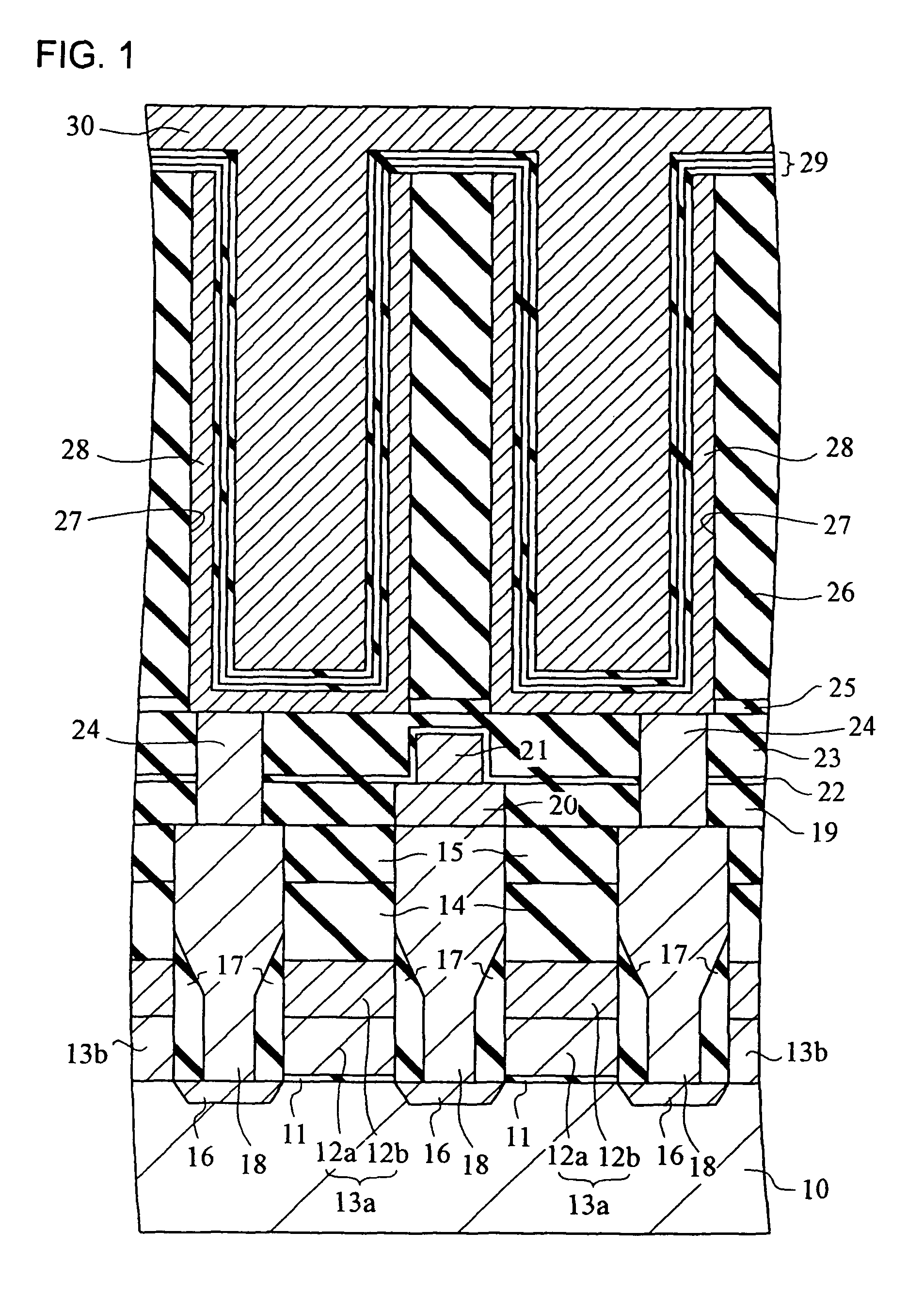

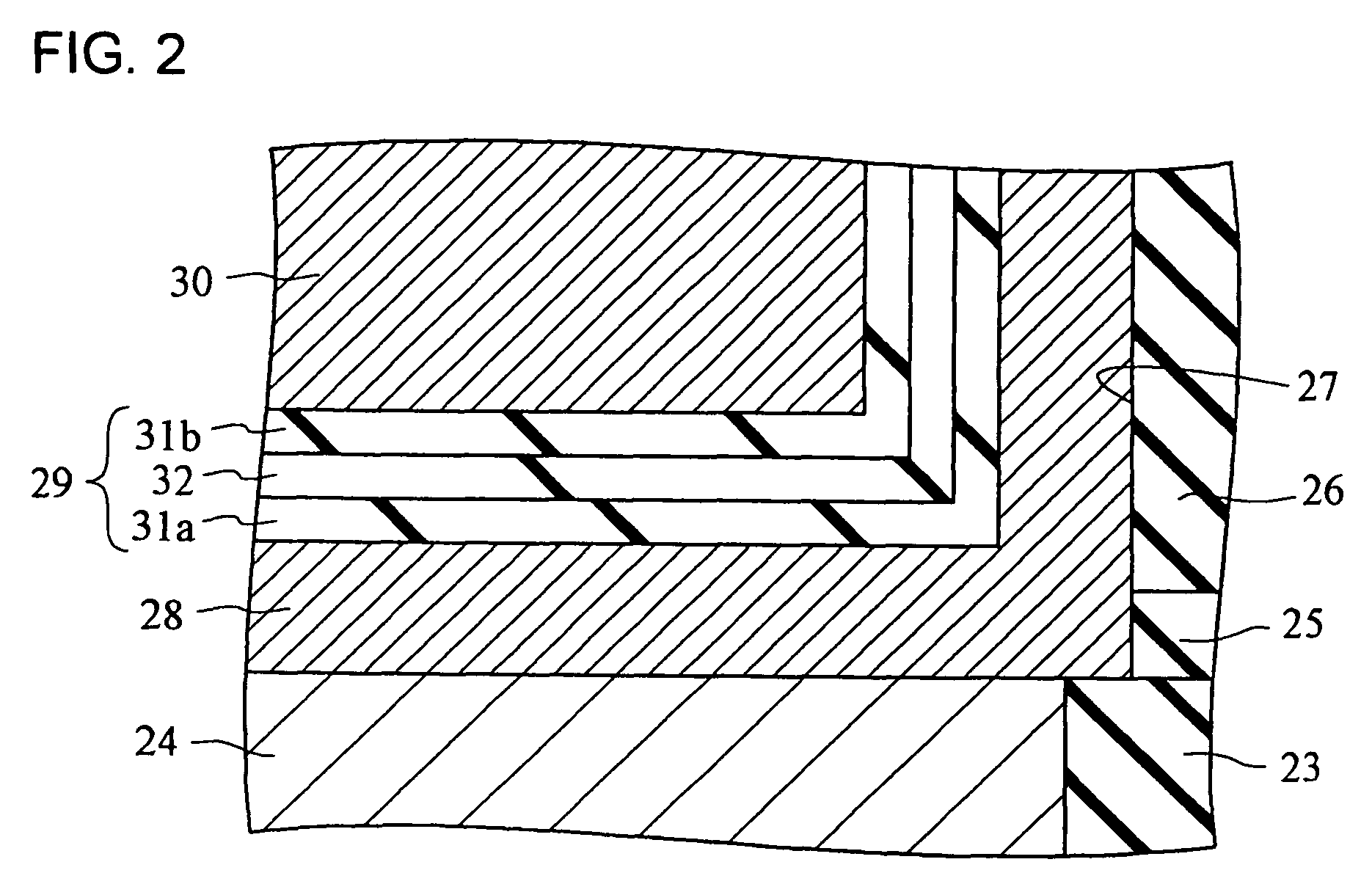

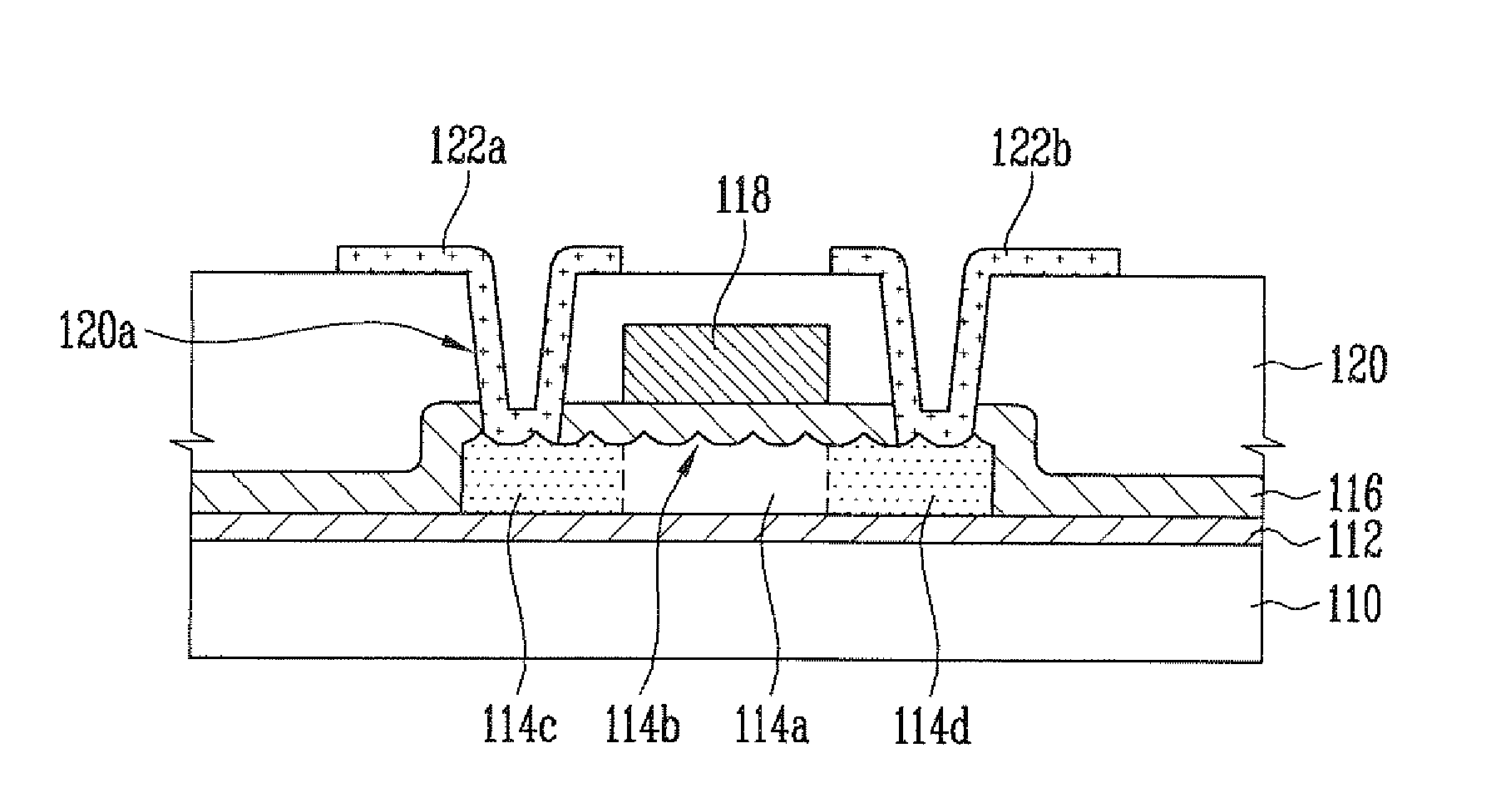

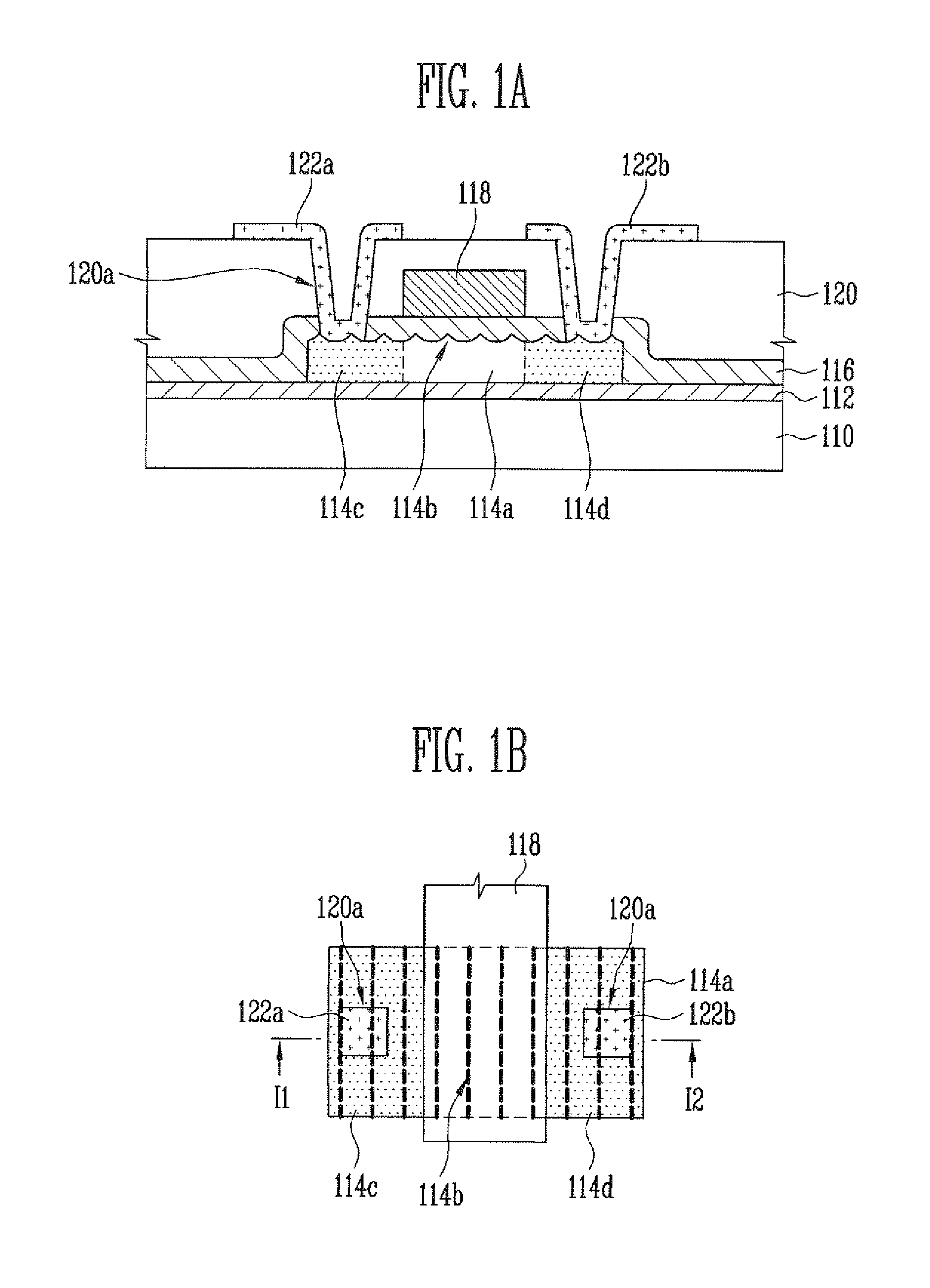

Semiconductor devices and methods of forming the same

InactiveUS20070264810A1Minimized junction leakage currentMinimizingSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialSemiconductor

A semiconductor device and a method of manufacturing the same, including obtaining a semiconductor substrate, forming a device isolating layer having a depression part and a protrusion part in the semiconductor substrate, forming a gate insulating layer and a gate electrode on the semiconductor substrate, forming a spacer in communication with the gate electrode, removing a portion of the semiconductor substrate to form at least one substrate recess region in an upper surface of the semiconductor substrate and at least one substrate remaining portion extending to a same height as the semiconductor substrate, so that the substrate remaining portion forms a sidewall of the substrate recess region and is in communication with the device isolating layer, and forming a substrate epitaxial layer in the substrate recess region.

Owner:SAMSUNG ELECTRONICS CO LTD

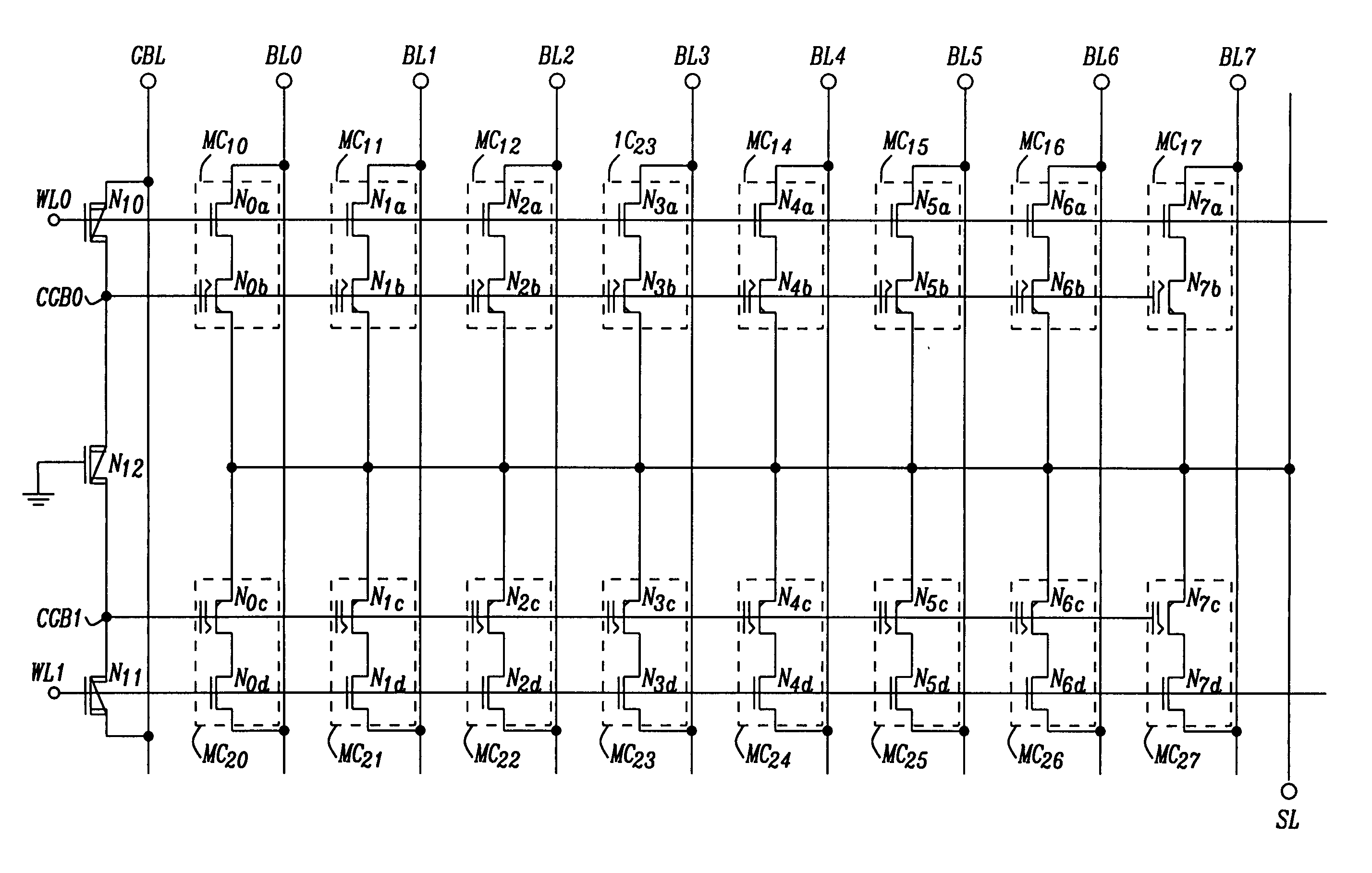

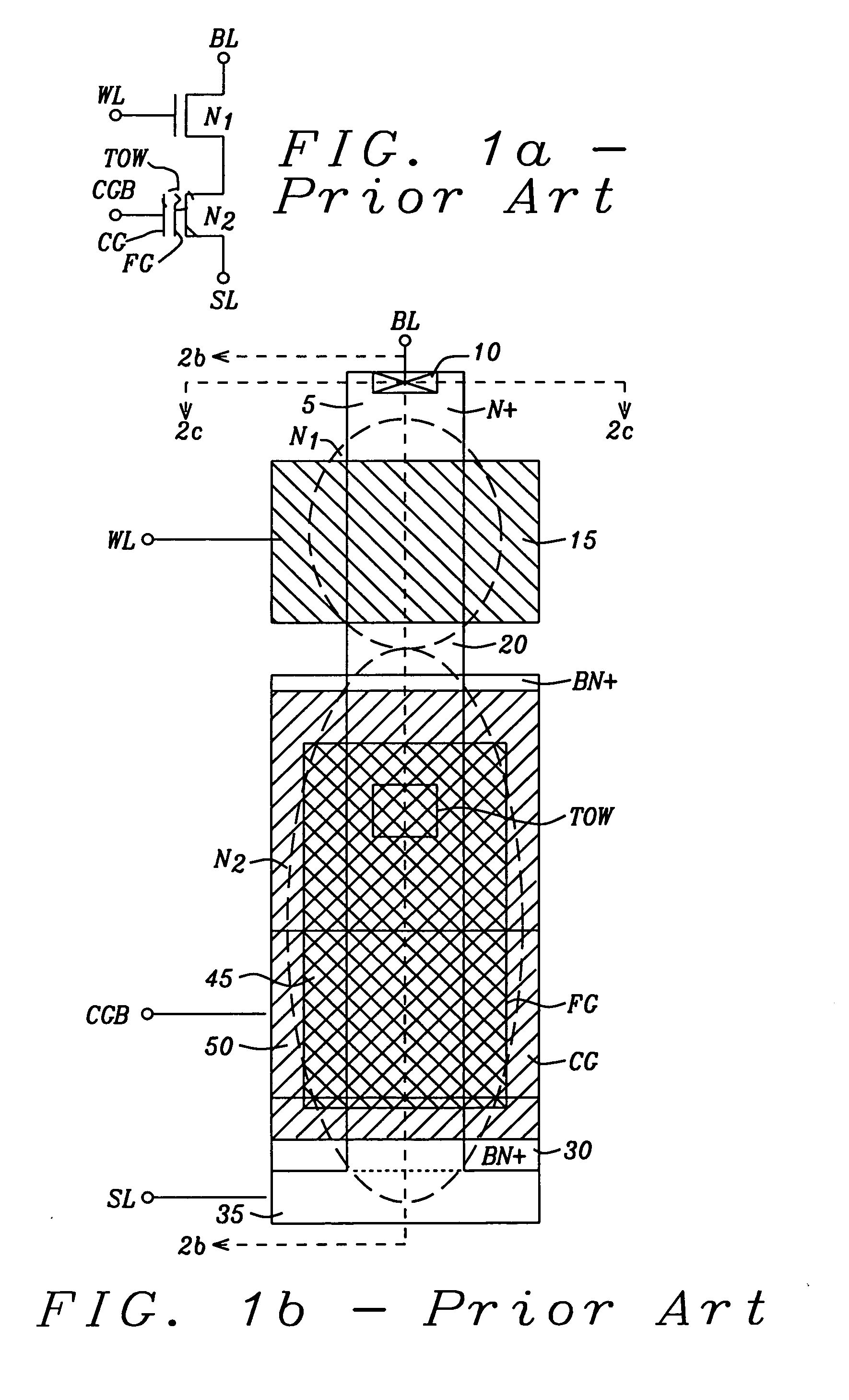

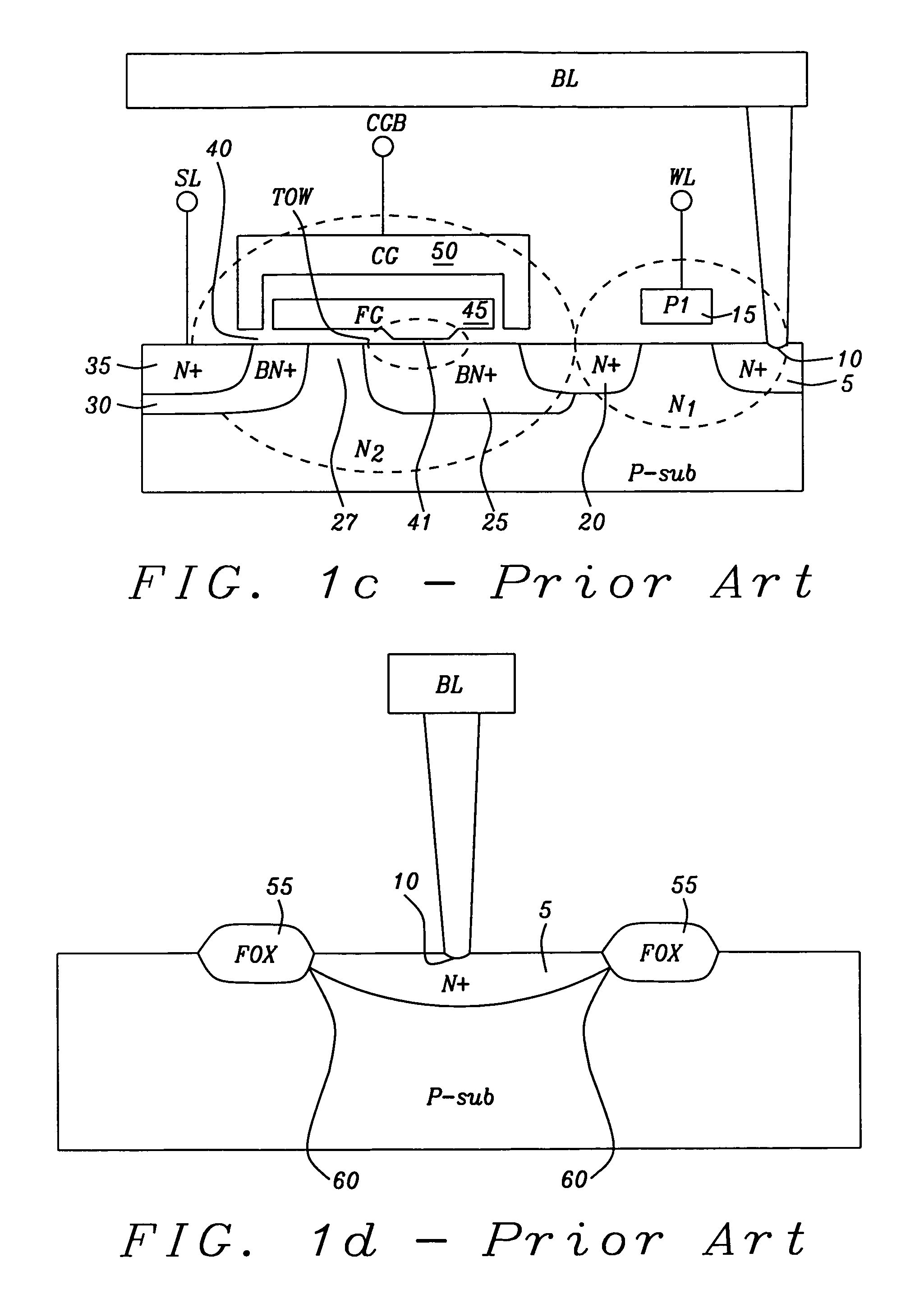

Novel high-temperature non-volatile memory design

InactiveUS20120020157A1Minimizing leakage currentSolid-state devicesRead-only memoriesDriver circuitJunction leakage

A method for fabricating a high temperature integrated circuit includes forming a drain / source diffusion and forming a buried diffusion implant containing the drain / source diffusion in a substrate to separate the drain / source diffusion from the substrate and an edge of a field isolation layer to decreases leakage current occurring with high voltage and high temperature. A nonvolatile memory array driver circuit with multiple driver transistors separated by anti-leakage transistors connected to prevent excess junction leakage current at elevated temperatures. Another nonvolatile memory array driver circuit has a high voltage blocking transistor connected to two anti-leakage transistors connected such that a source of the first anti-leakage transistor is connected to a drain of the high voltage blocking transistor and a drain of the second anti-leakage transistor is connected to prevent excess junction leakage current at elevated temperatures.

Owner:APLUS FLASH TECH

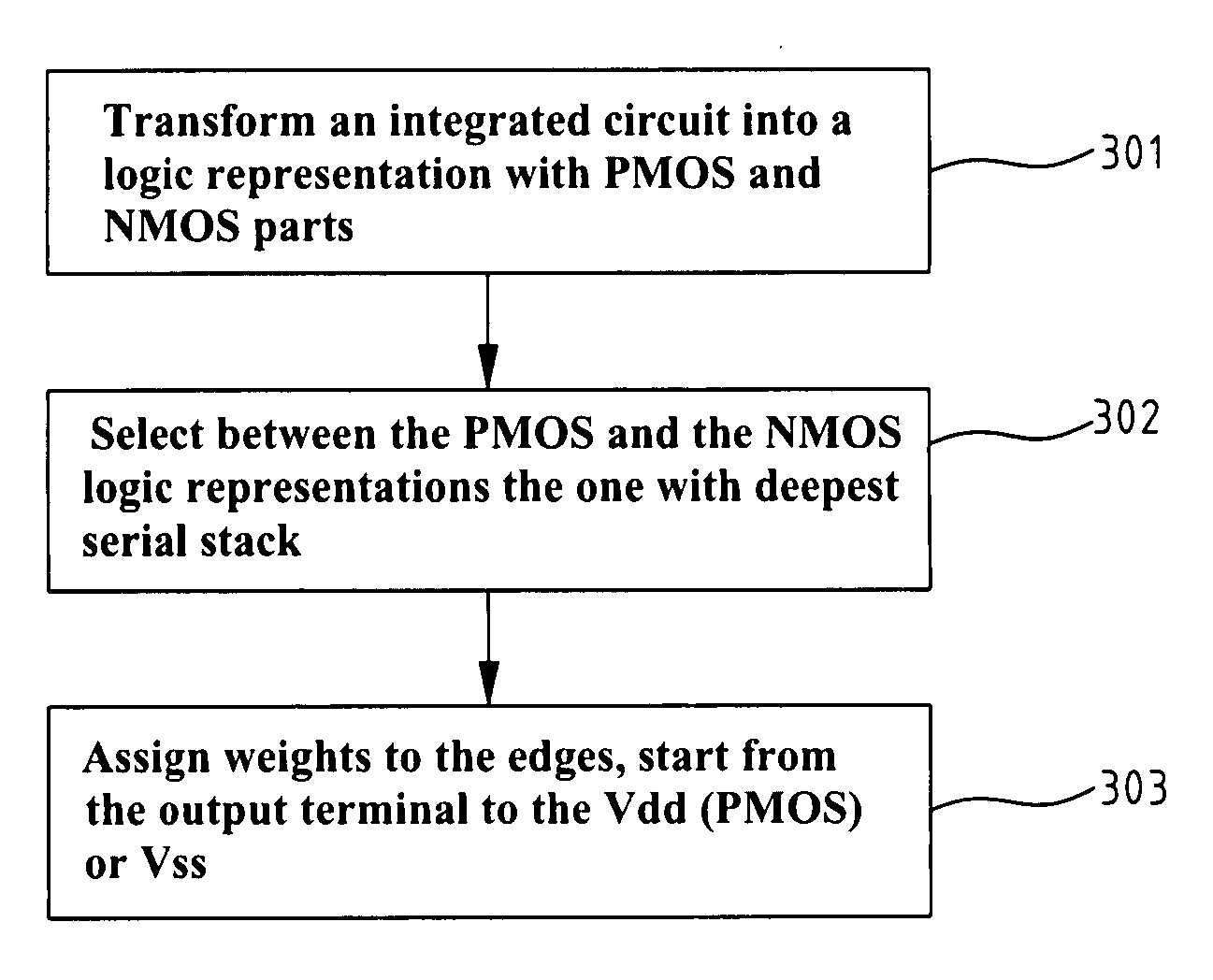

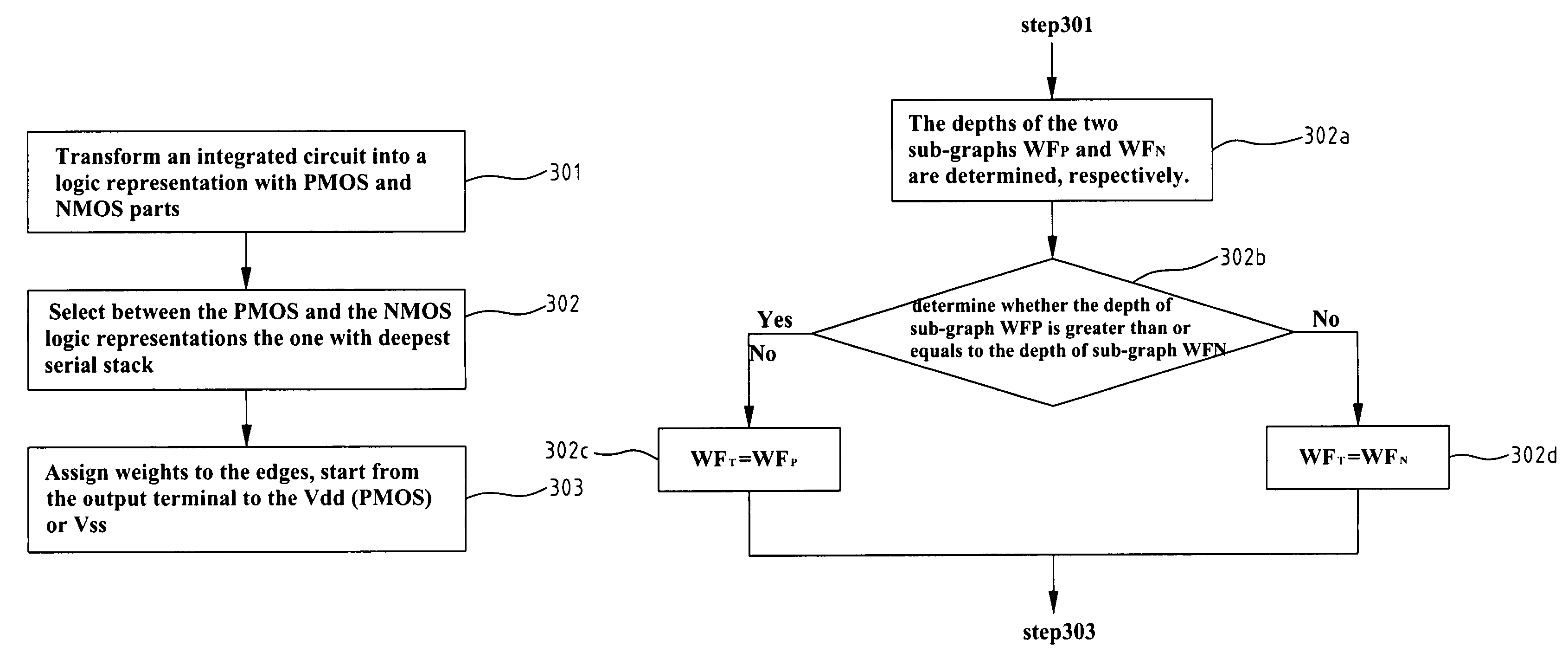

Method for generating minimal leakage current input vector using heuristics

ActiveUS20070150843A1Minimize leakage currentOvercomes drawbackComputer aided designSoftware simulation/interpretation/emulationTheoretical computer scienceNMOS logic

A method for generating an input vector to reduce the leakage current in an integrated circuit by using heuristics includes transforming the integrated circuit to a logic representation with PMOS and NMOS parts and P and N devices of the integrated circuit into edges, selecting between PMOS and NMOS logic representations the one with deepest serial stack; and for the selected PMOS or NMOS logic representation, assigning weights to the edges, thereby generating a weighted graph. The assignment includes starting from the output terminal to the Power Vdd (for PMOS) or Ground Vss (for NMOS), and labeling edge weights in a descending order. The resulted cost function from the method of the present invention can be applied as heuristics in different algorithms, such as branch-and-bound, simulated annealing, or genetic algorithm.

Owner:IND TECH RES INST

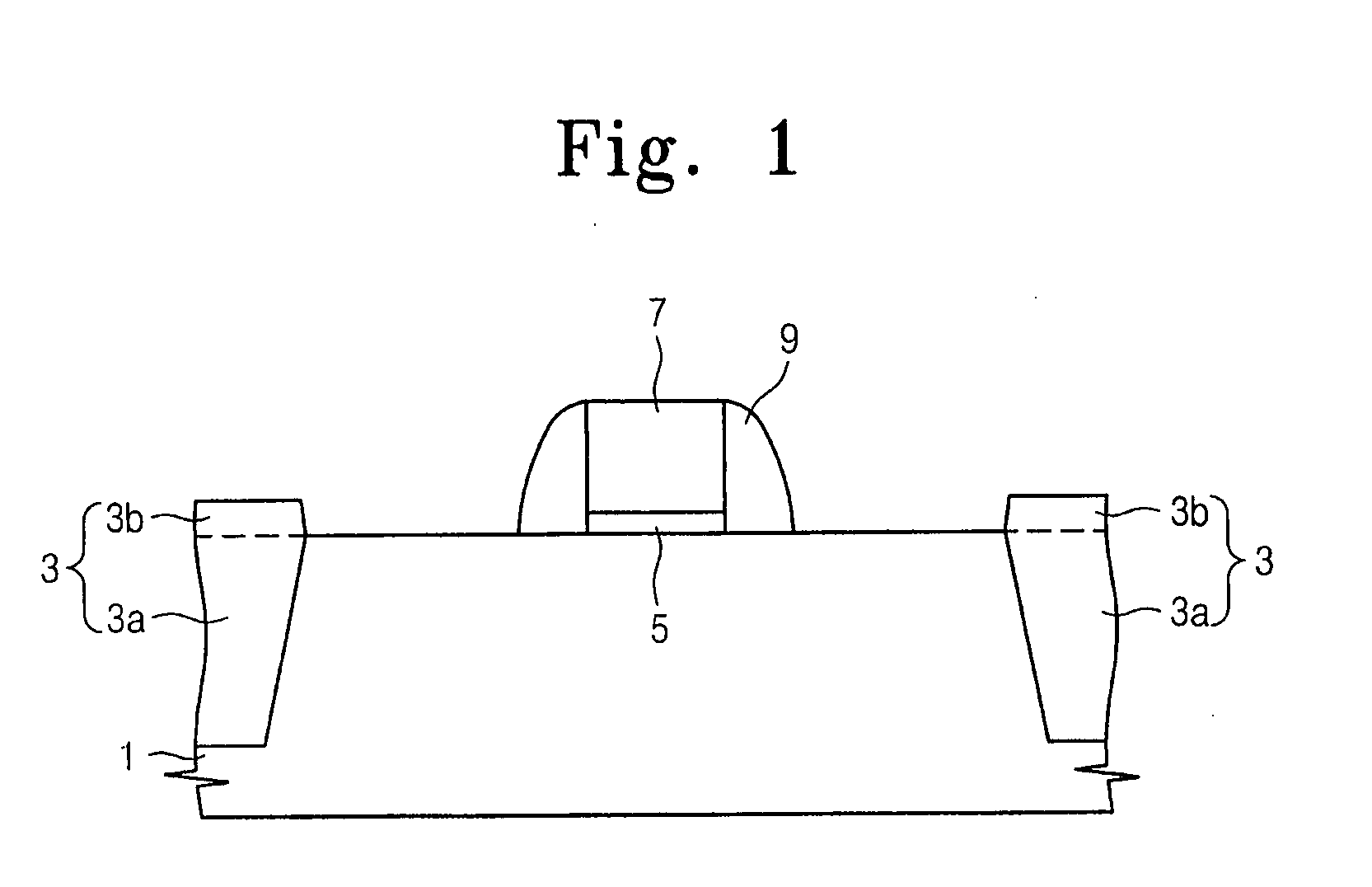

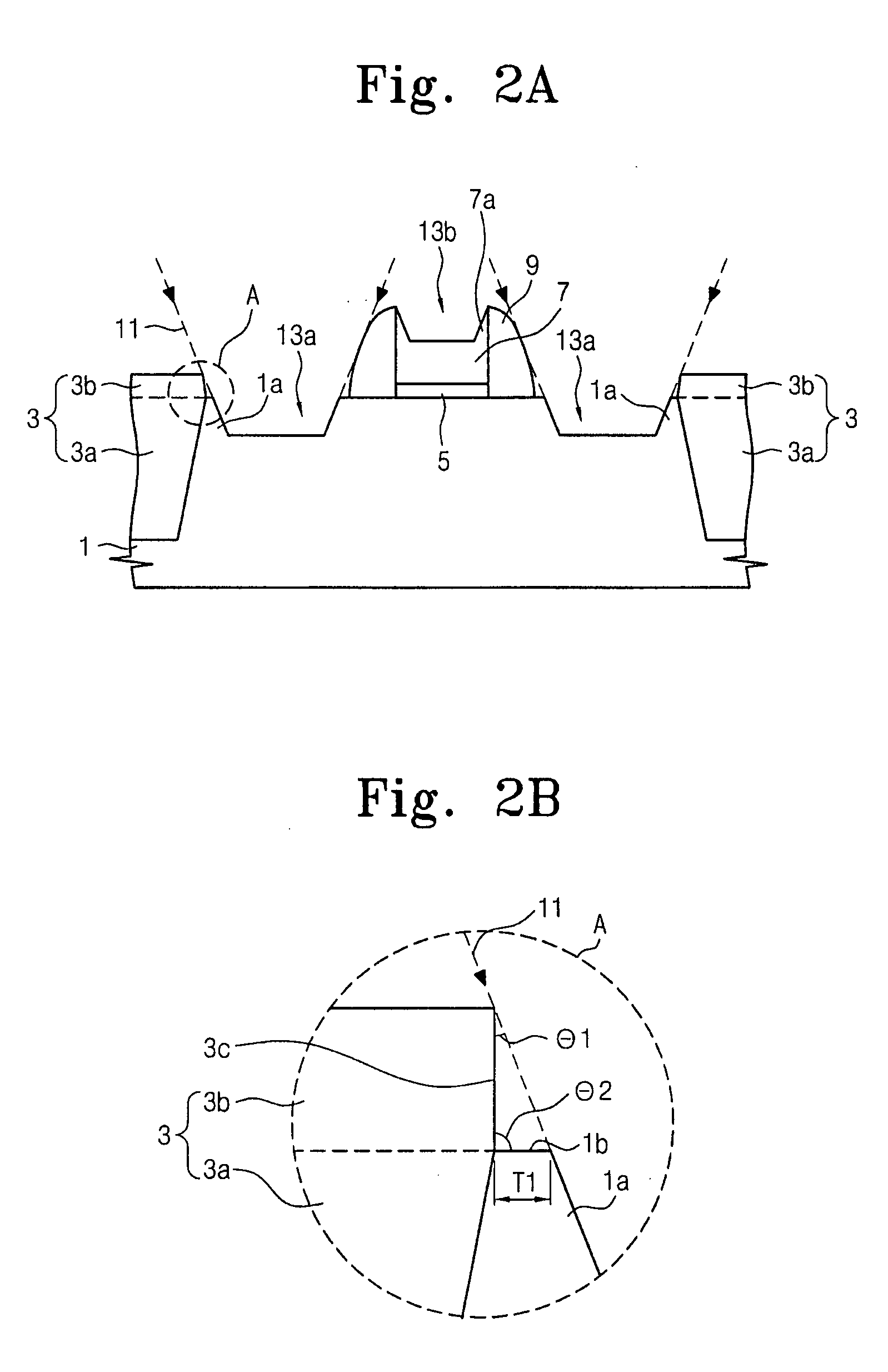

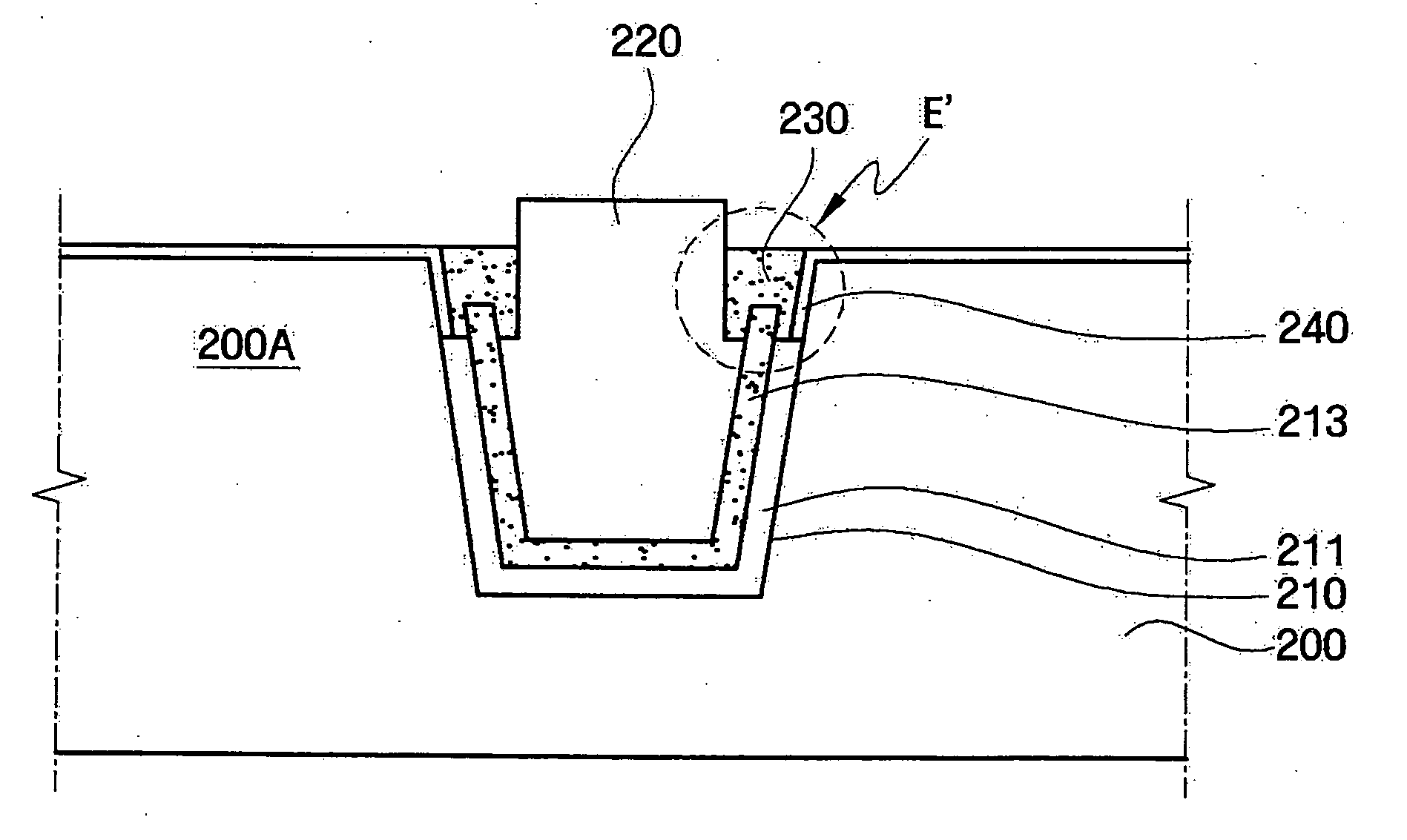

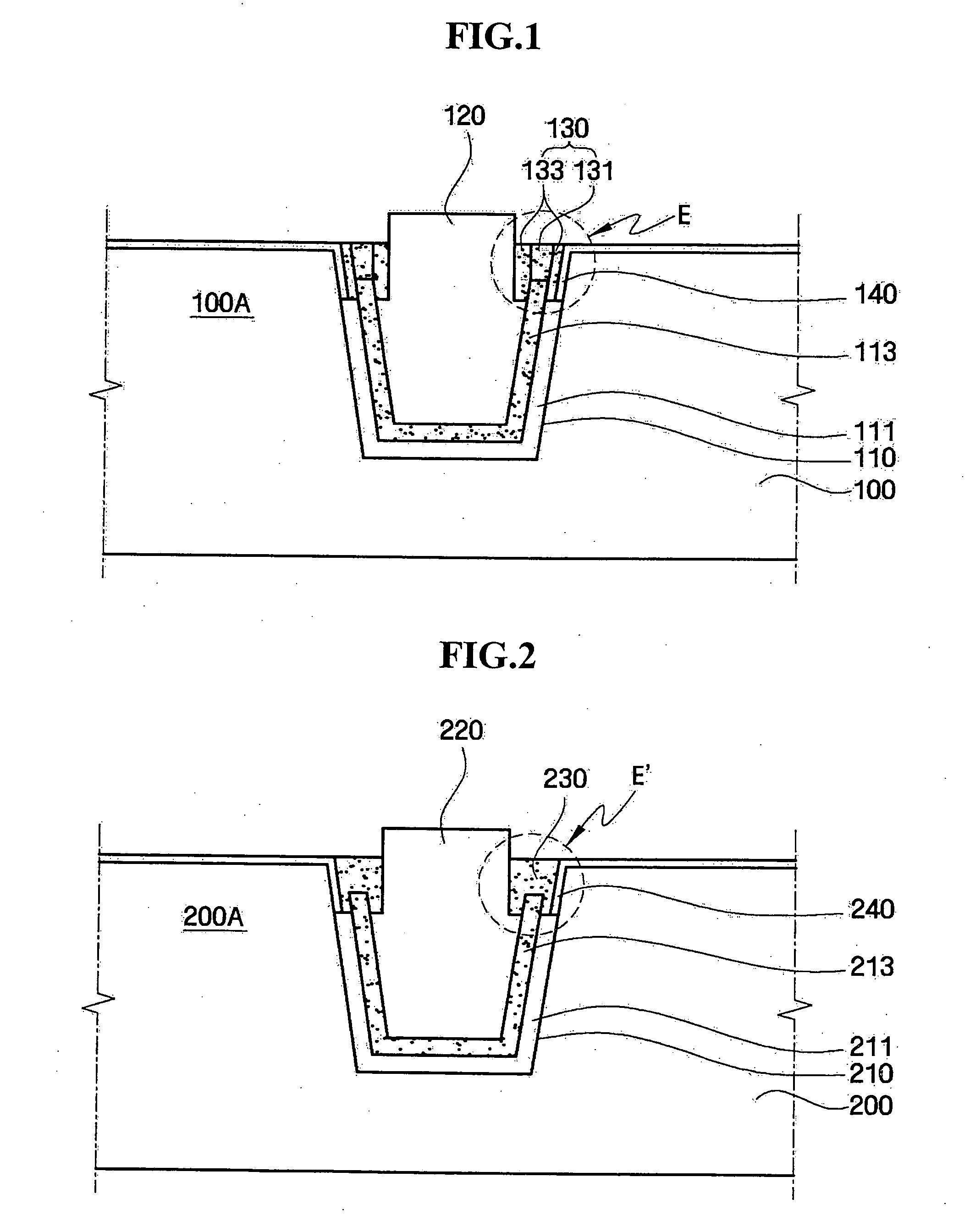

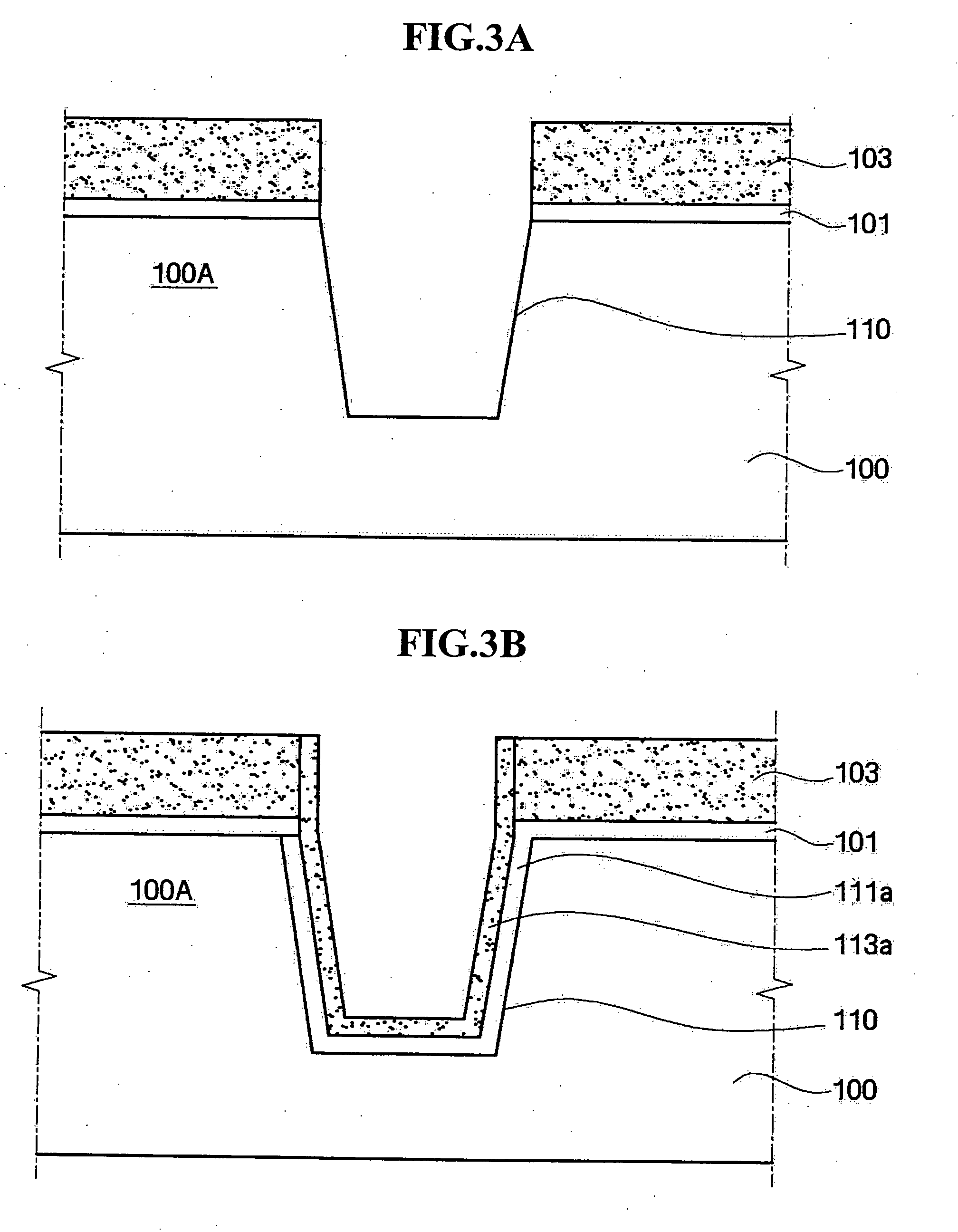

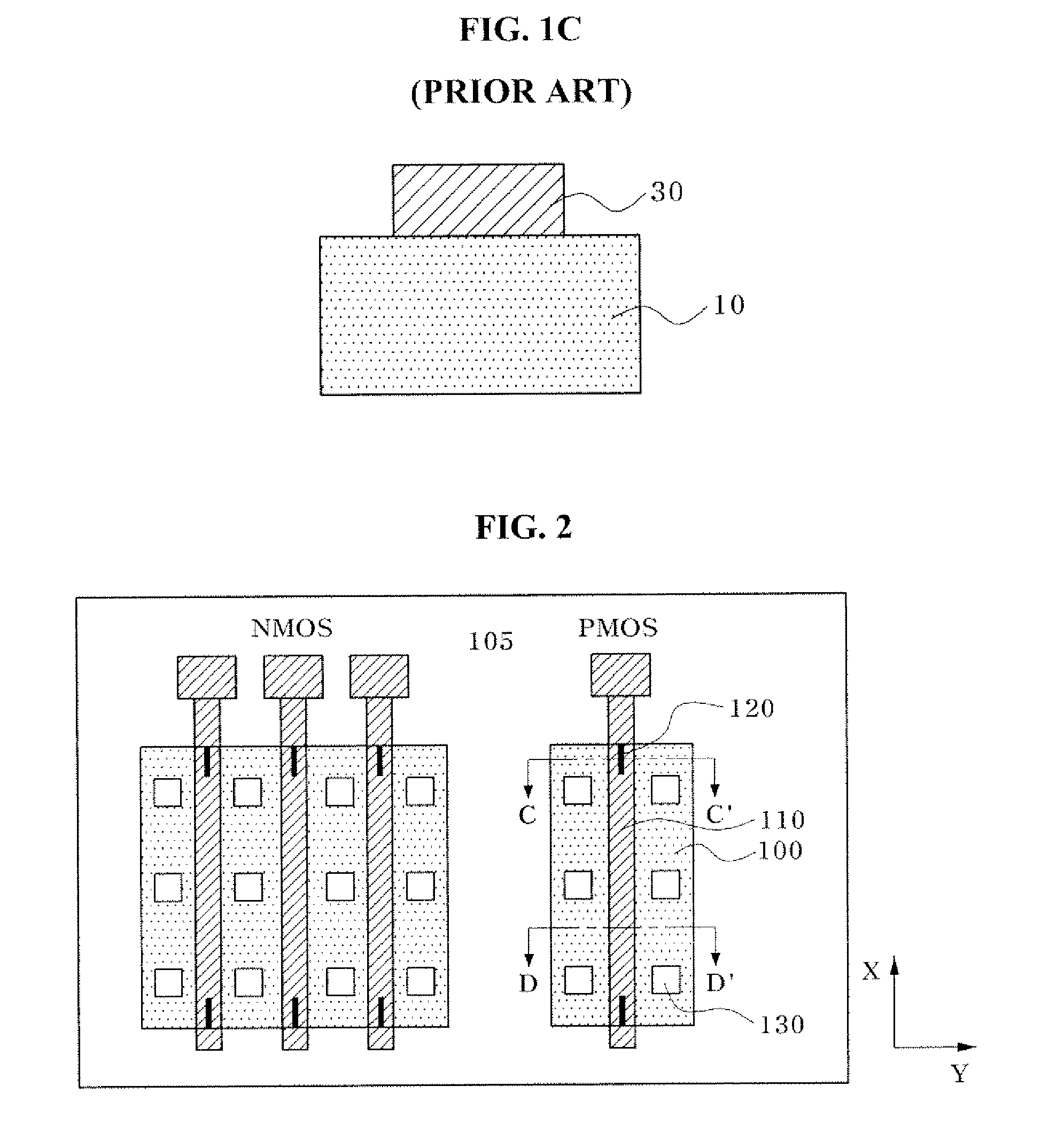

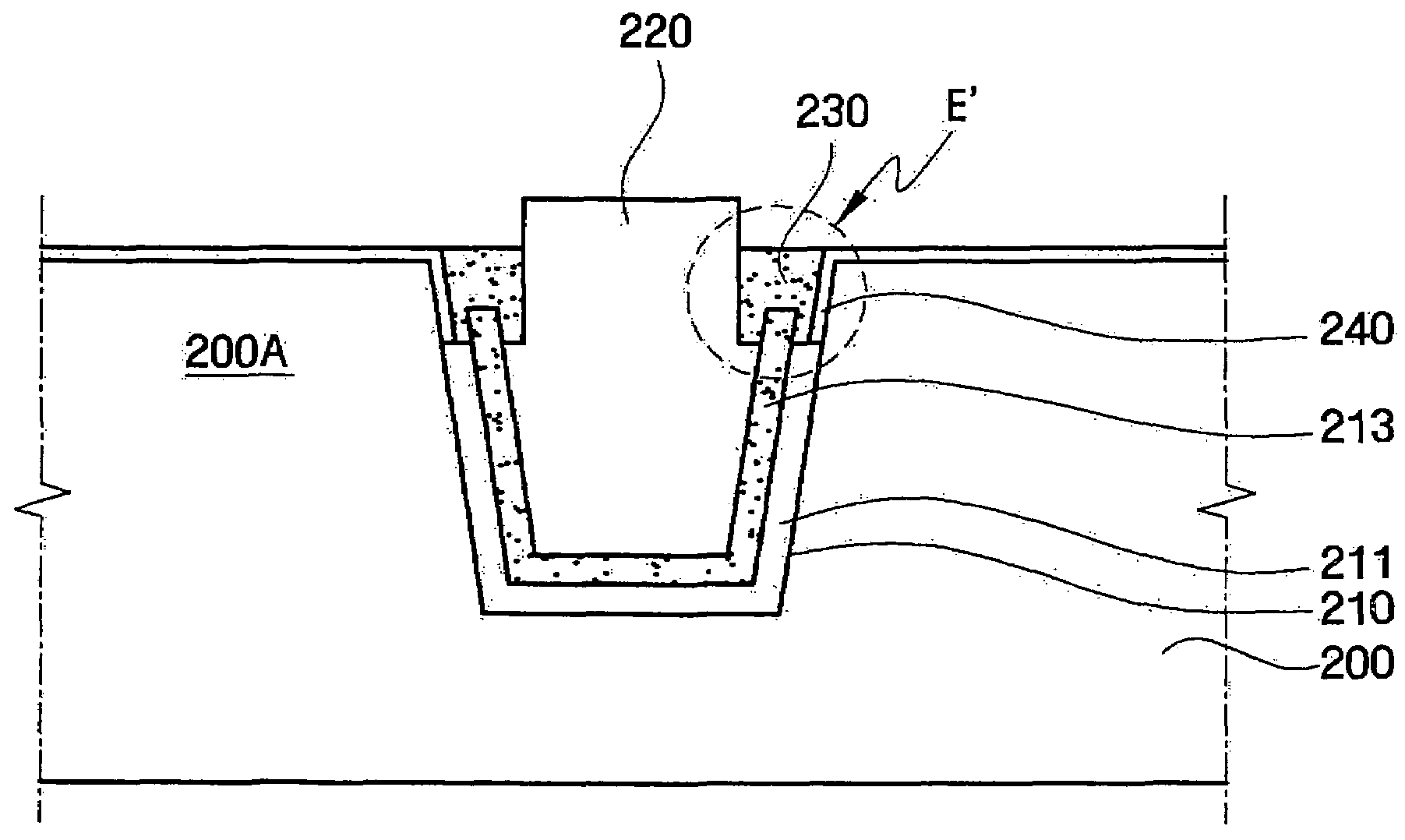

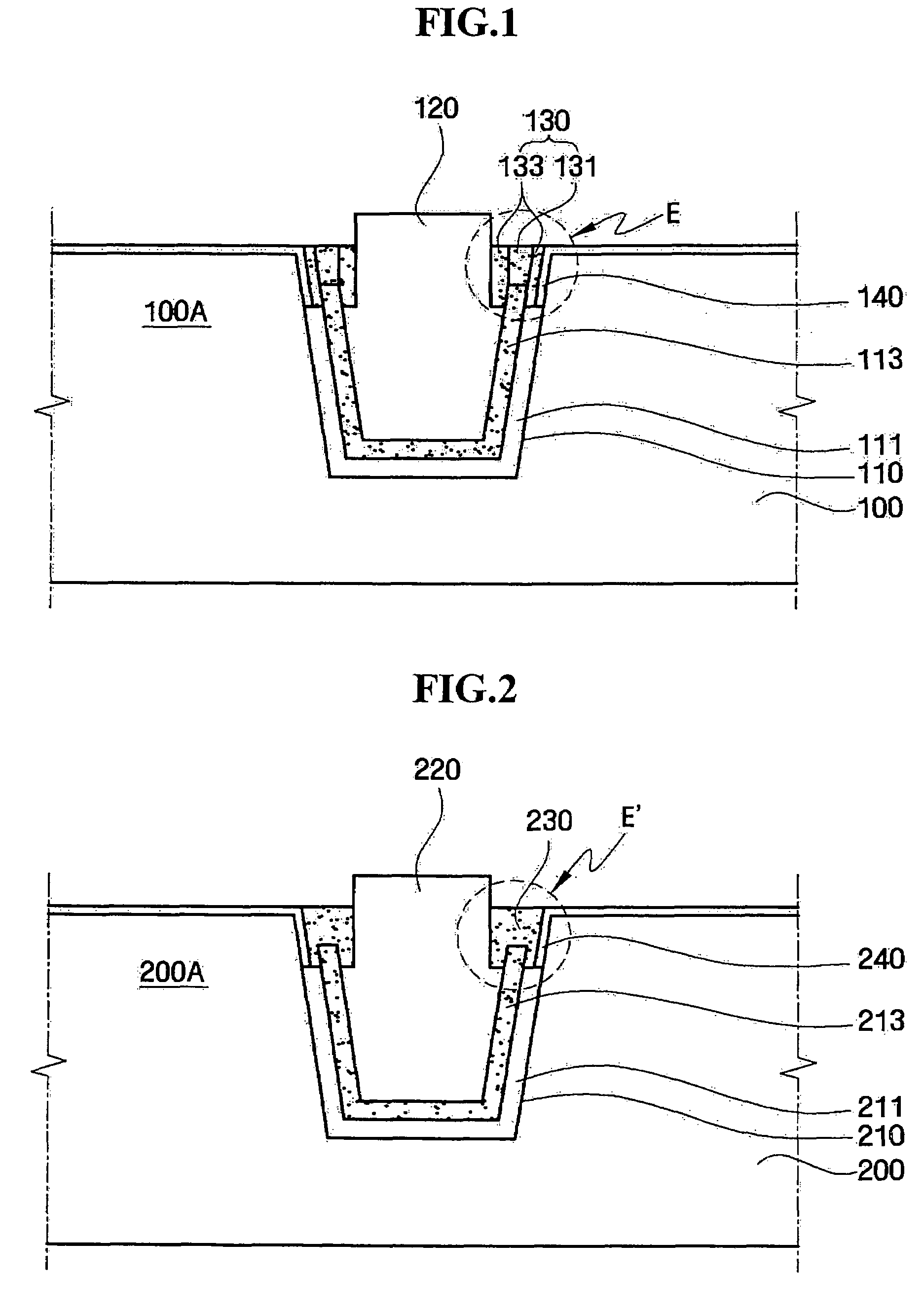

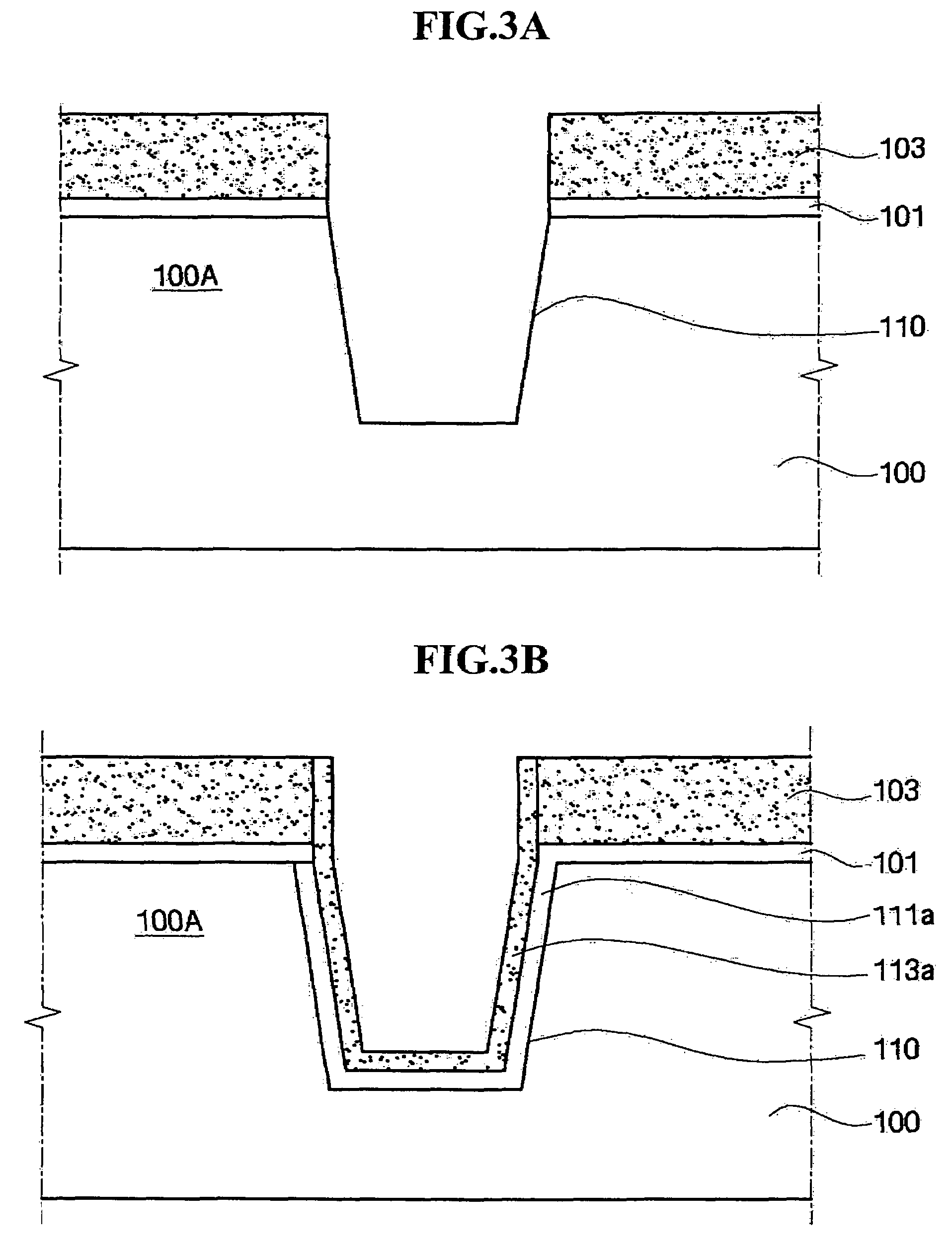

Trench isolation type semiconductor device and related method of manufacture

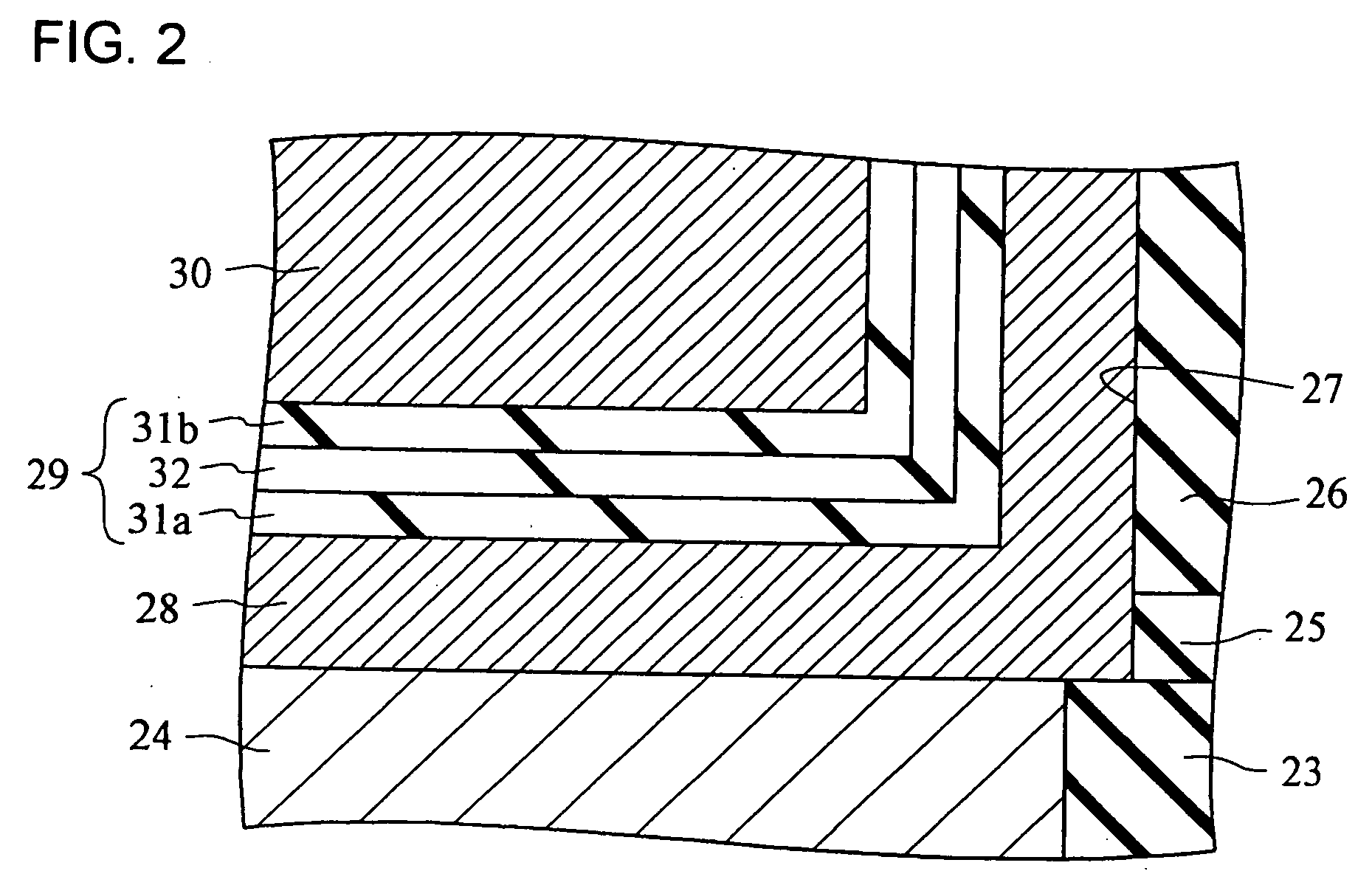

ActiveUS20070164391A1MinimizingMinimizing leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringNitride

A semiconductor device and related method of manufacture are disclosed. The device comprises; a trench having a corner portion formed in the semiconductor substrate, a first oxide film formed on an inner wall of the trench and having an upper end portion exposing the corner portion of the semiconductor substrate, a nitride liner formed on the first oxide film, a second oxide film formed in contact with the upper end of the first oxide film and on the exposed corner portion and an upper surface of the semiconductor substrate, a field insulating film formed on the nitride liner to substantially fill the trench, and a field protecting film formed in contact with the second oxide film and filling a trench edge recess formed between the field insulating film and the second oxide film.

Owner:SAMSUNG ELECTRONICS CO LTD

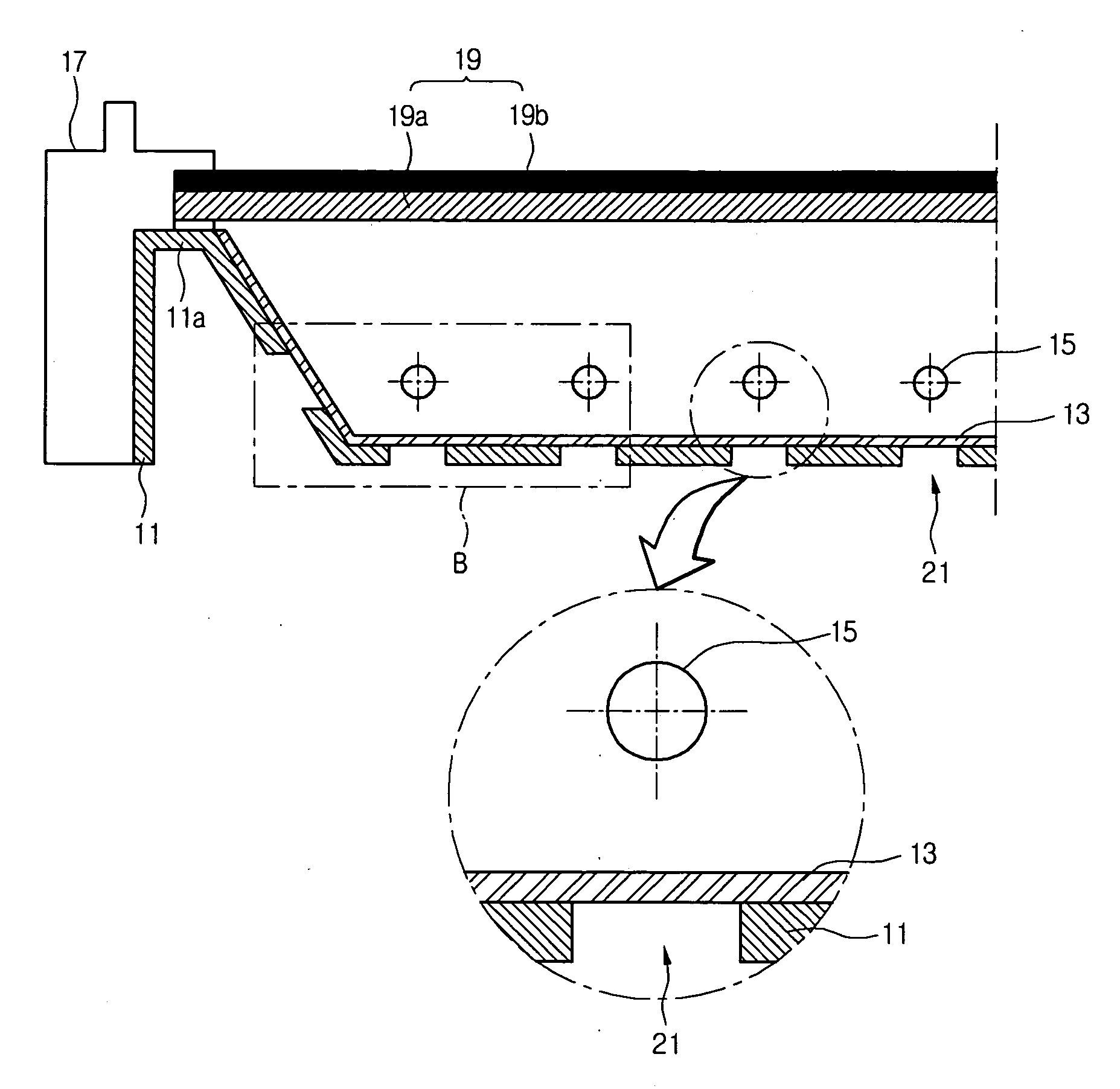

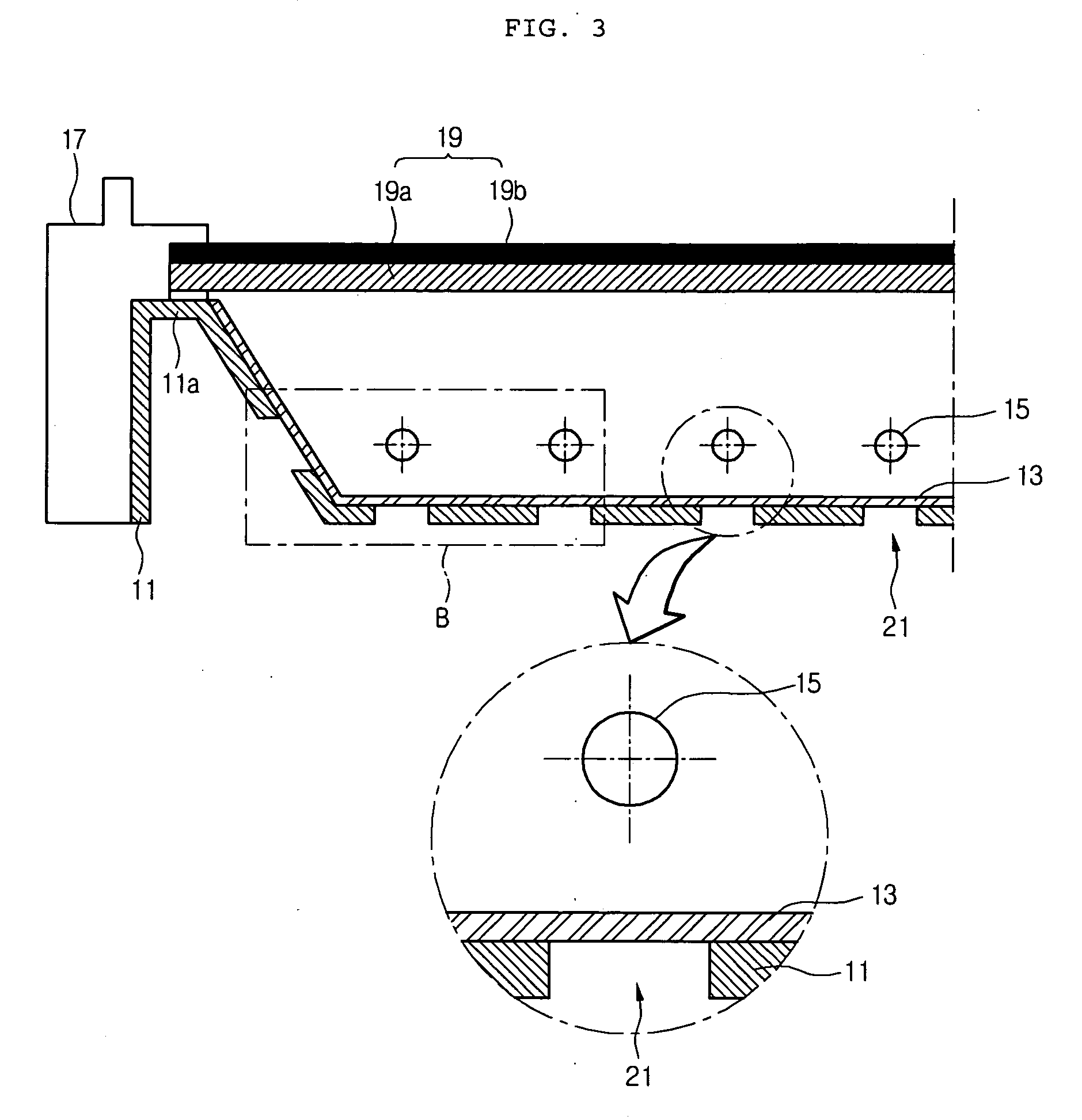

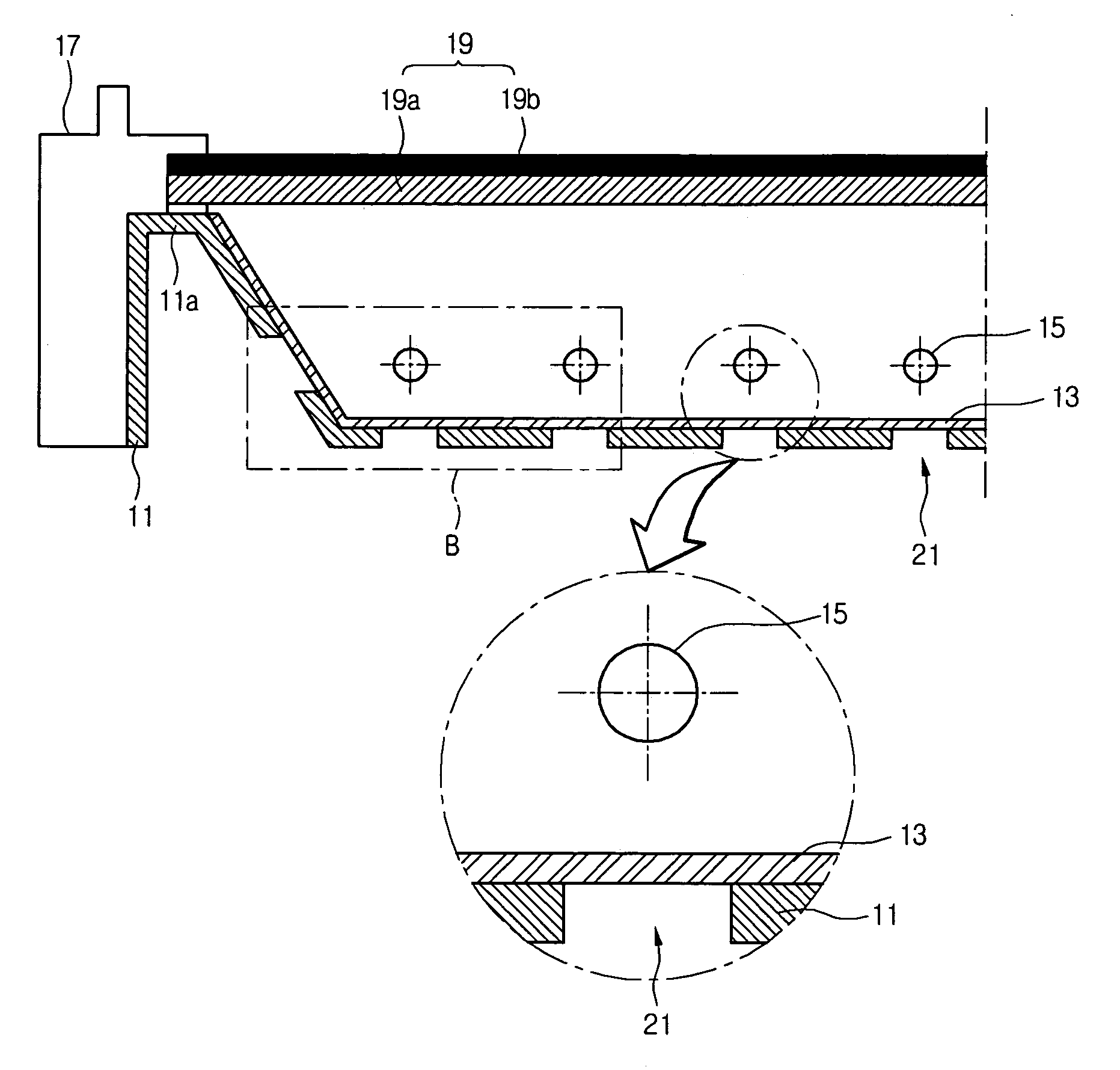

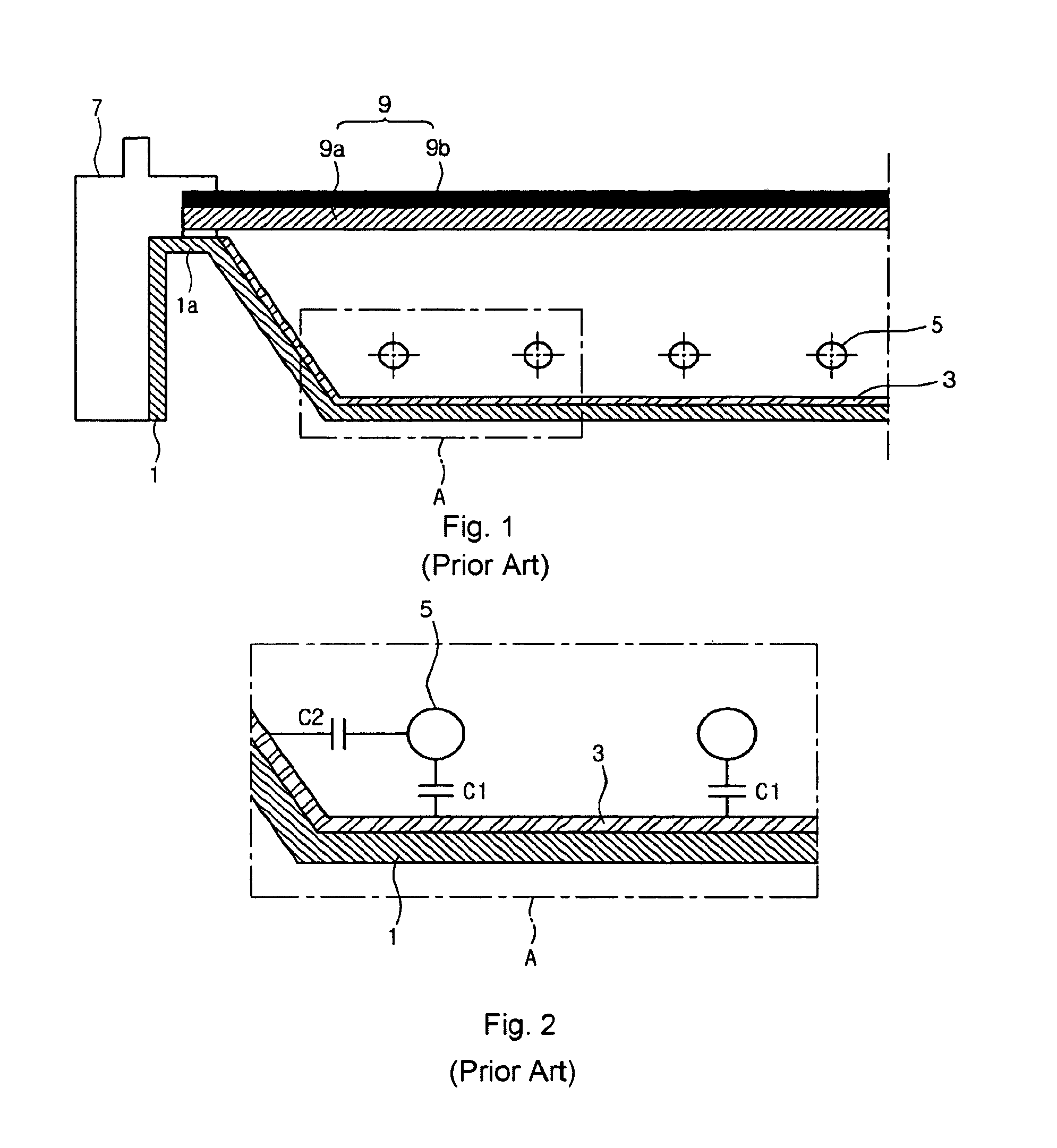

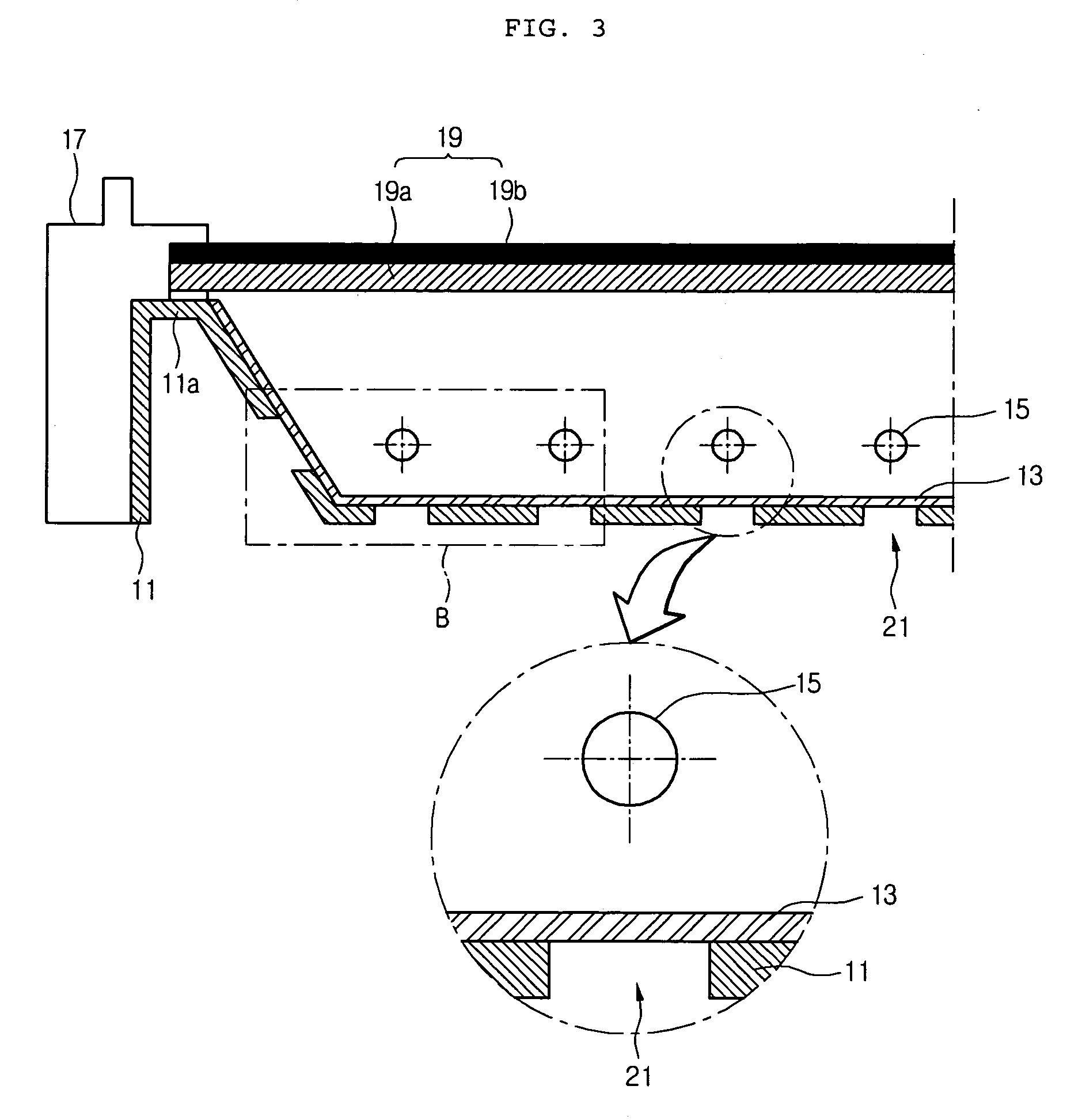

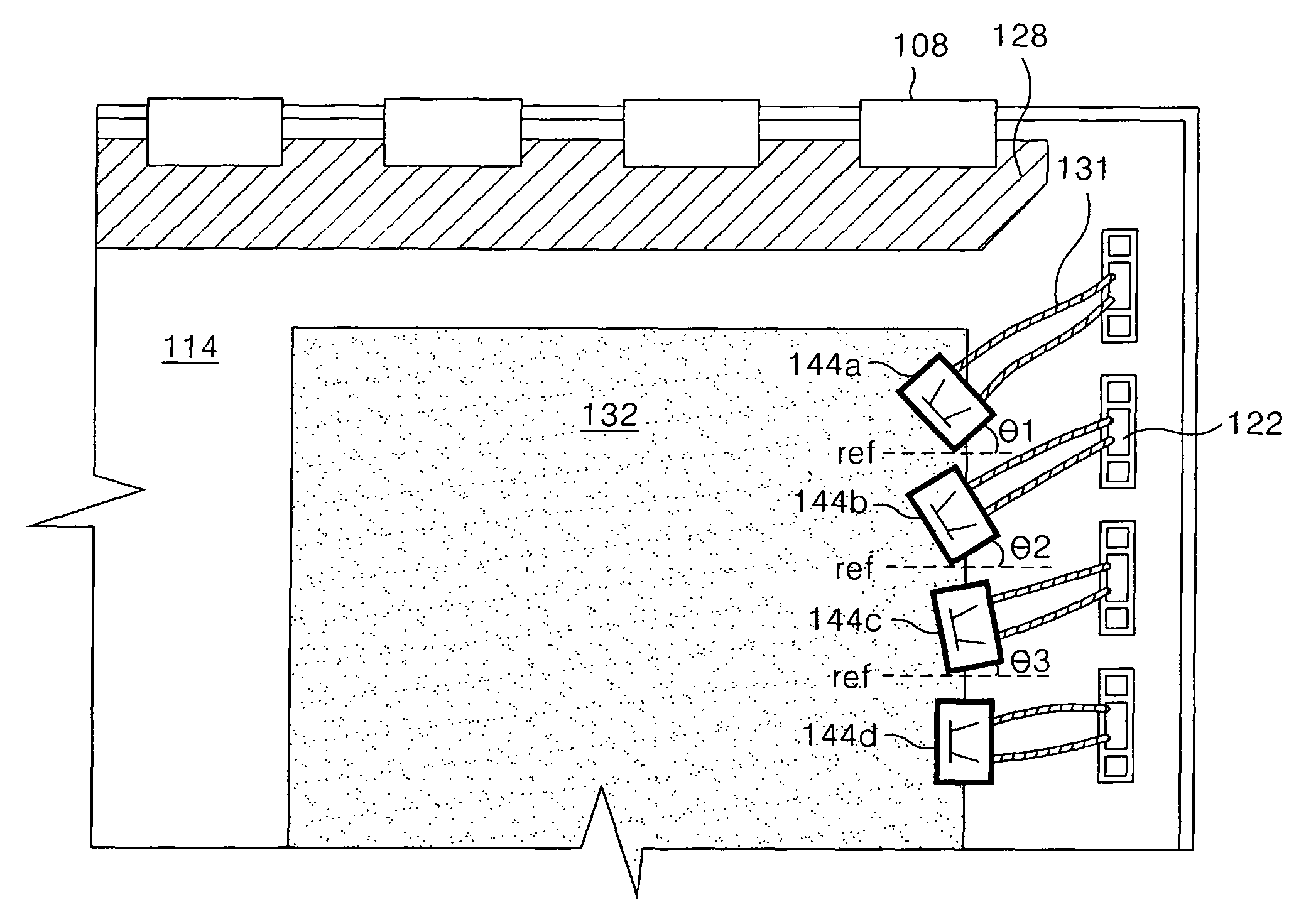

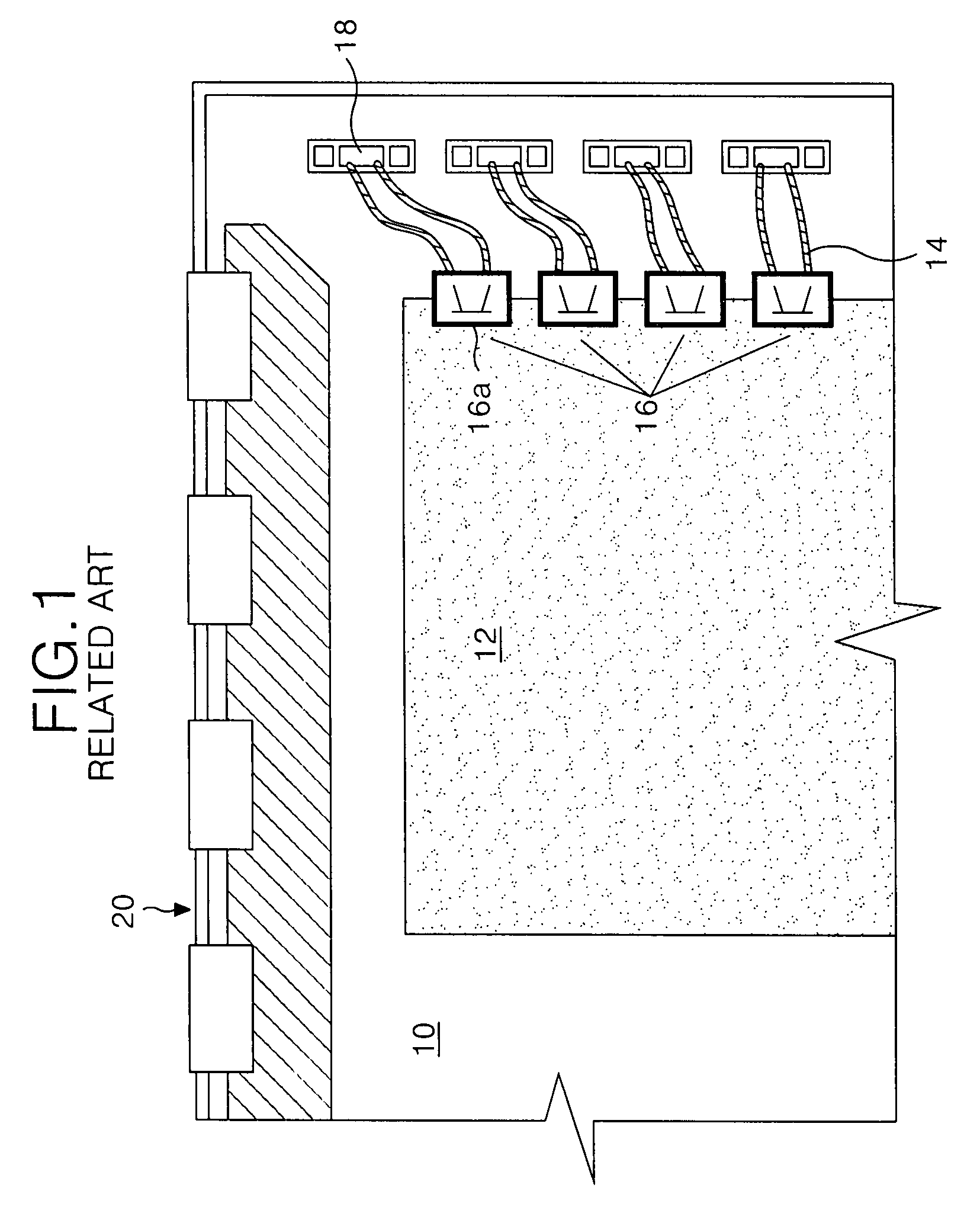

Backlight assembly

InactiveUS20070139962A1Improve luminous efficiencyMinimizing leakage currentLighting heating/cooling arrangementsIlluminated signsEngineering

Owner:LG DISPLAY CO LTD

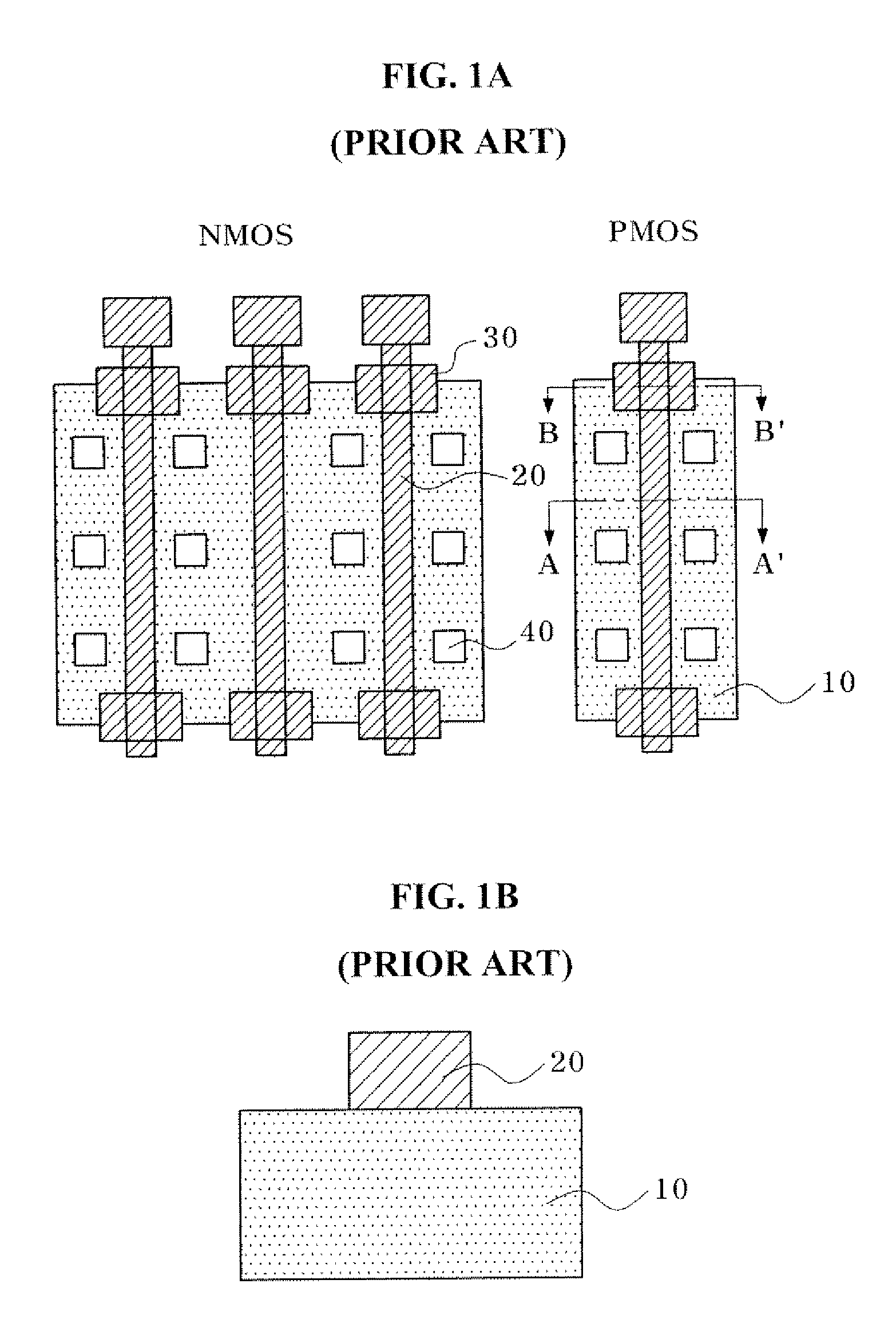

Transistor And Method For Manufacturing The Same

InactiveUS20080079040A1Minimizing leakage currentIncrease channel lengthSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringSemiconductor

A transistor includes a semiconductor substrate including an active region defined by a device isolation layer, gate lines disposed at specified intervals on the active region of the semiconductor substrate, and trenches of a valley structure etched to a specified depth in the semiconductor substrate in contact with end portions of the gate lines.

Owner:SK HYNIX INC

Trench isolation type semiconductor device and related method of manufacture

ActiveUS7557415B2Minimizing leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialEngineering

A semiconductor device and related method of manufacture are disclosed. The device comprises; a trench having a corner portion formed in the semiconductor substrate, a first oxide film formed on an inner wall of the trench and having an upper end portion exposing the corner portion of the semiconductor substrate, a nitride liner formed on the first oxide film, a second oxide film formed in contact with the upper end of the first oxide film and on the exposed corner portion and an upper surface of the semiconductor substrate, a field insulating film formed on the nitride liner to substantially fill the trench, and a field protecting film formed in contact with the second oxide film and filling a trench edge recess formed between the field insulating film and the second oxide film.

Owner:SAMSUNG ELECTRONICS CO LTD

Backlight assembly

InactiveUS7621666B2Improve luminous efficiencyMinimizing leakage currentLighting heating/cooling arrangementsIlluminated signsEngineeringLight source

Owner:LG DISPLAY CO LTD

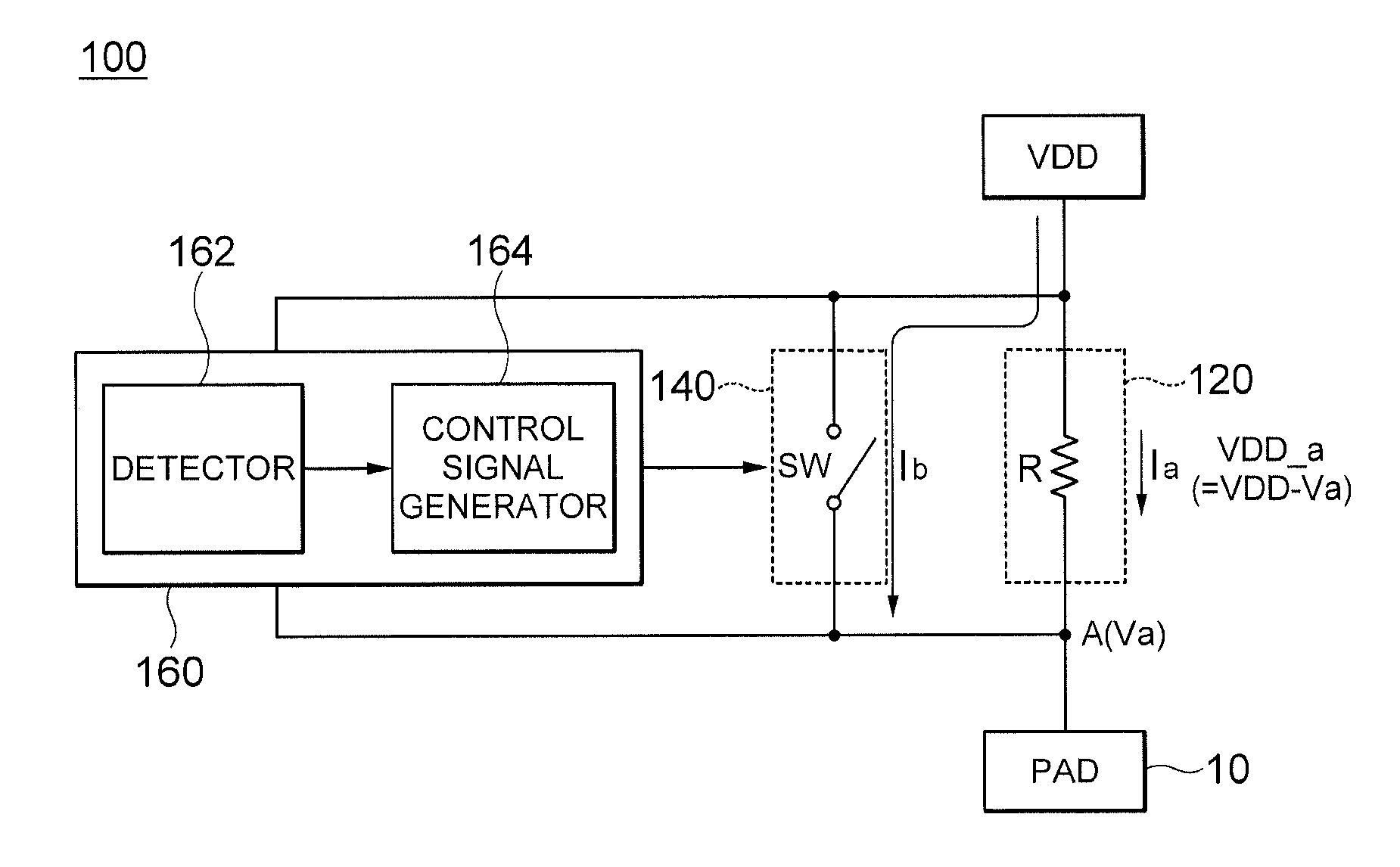

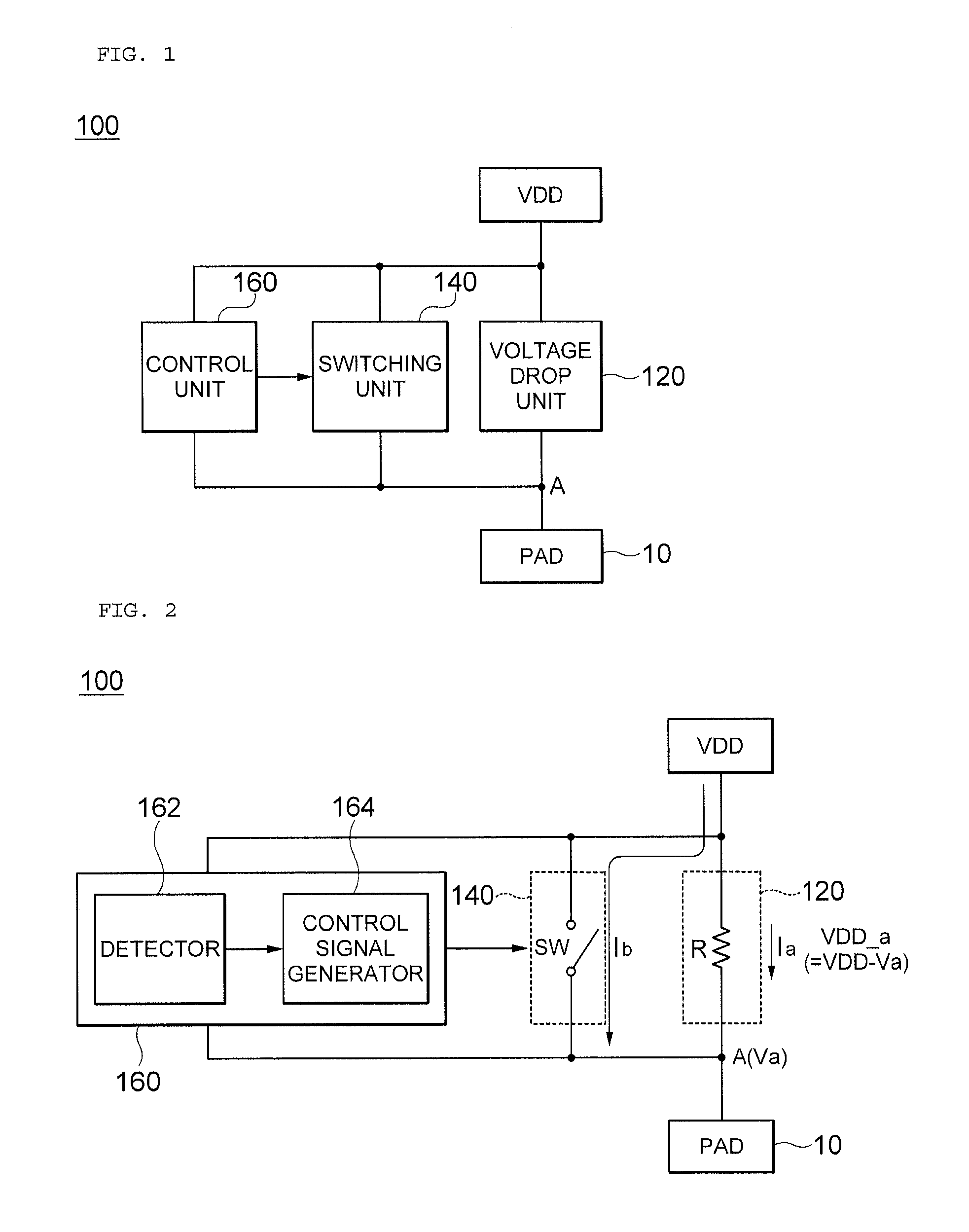

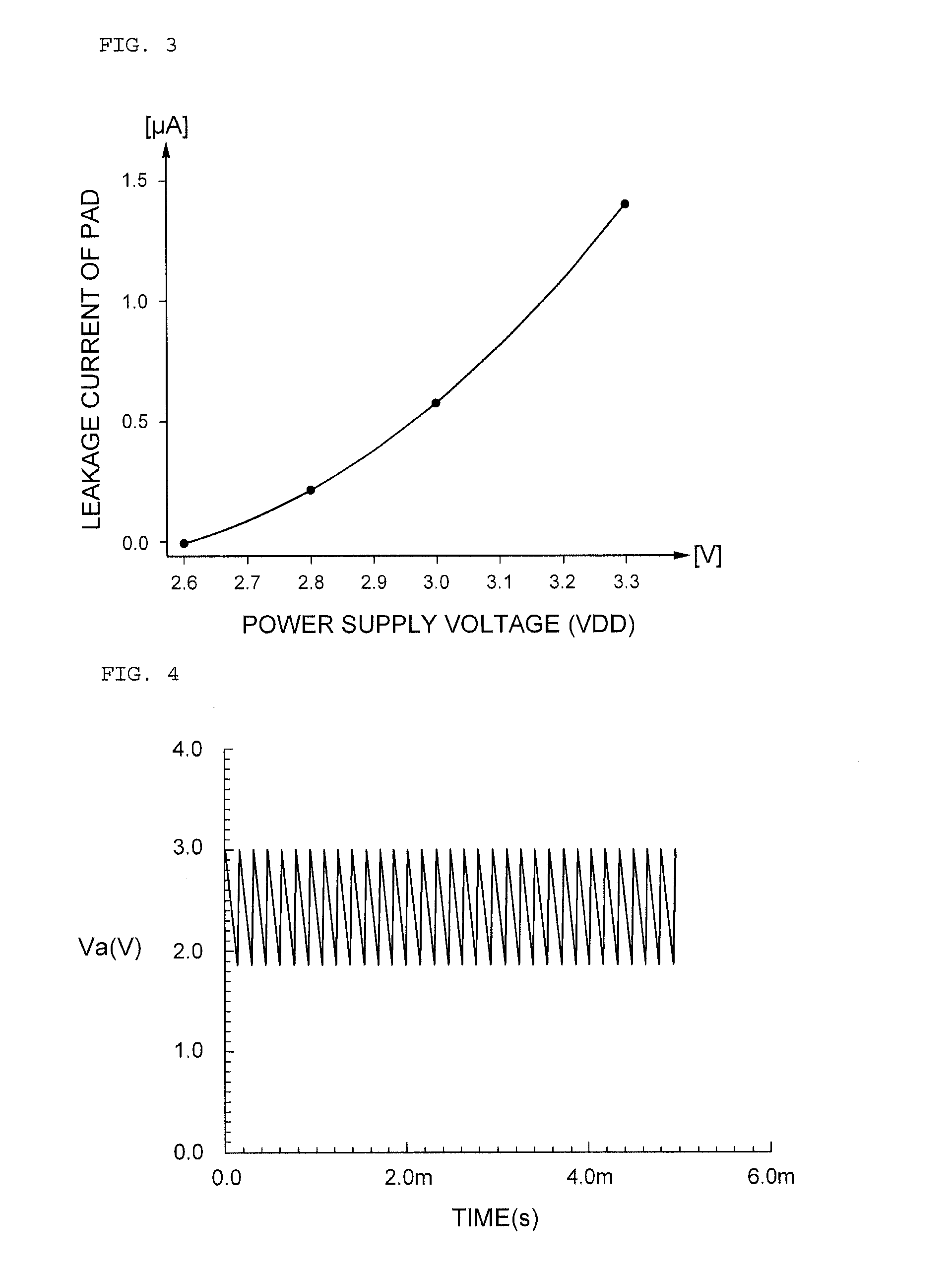

Pad controlling apparatus

InactiveUS8564360B2Minimizing leakage currentPower supply for data processingEmergency protective arrangements for limiting excess voltage/currentPower flowVoltage drop

Disclosed herein is a pad controlling apparatus controlling current and voltage applied to a pad, the pad controlling apparatus including: a voltage drop unit dropping the voltage applied to the pad; a switching unit connected in parallel with the voltage drop unit; and a control unit comparing a level of the dropped voltage and first reference voltage with each other and turning on the switching unit on when the level of the dropped voltage is larger than the first reference voltage. According to the present invention, even though interrupt occurs from the outside, a chip may be normally operated.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

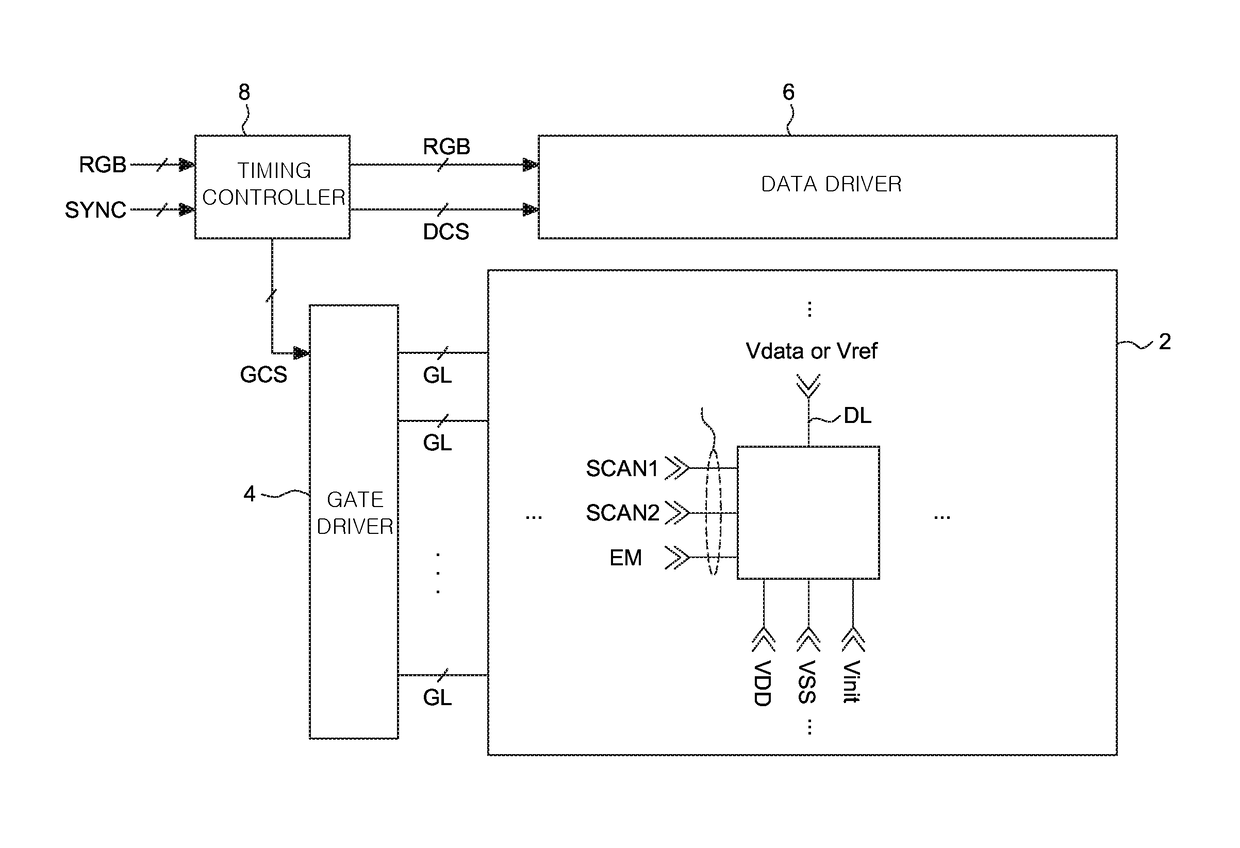

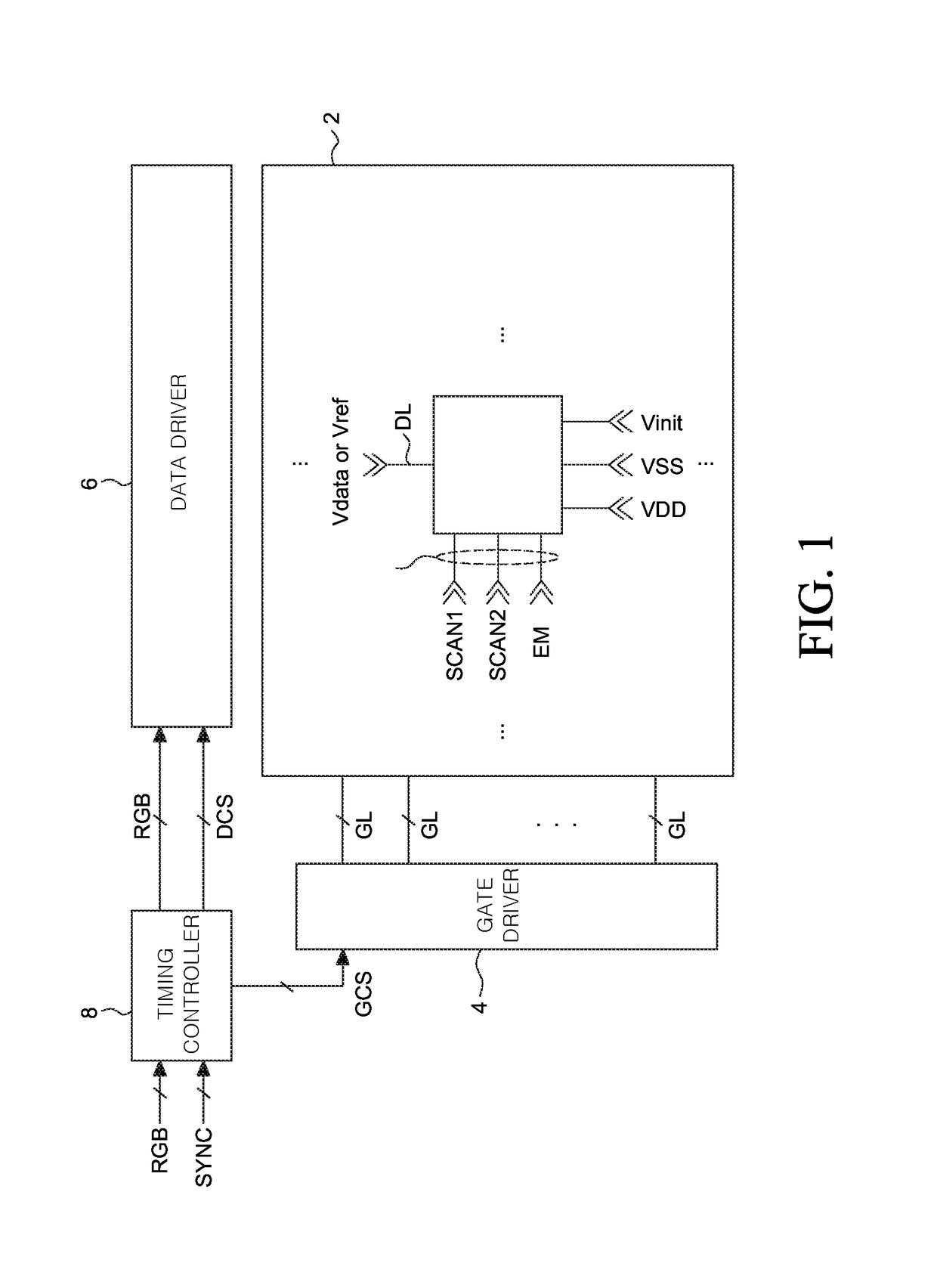

Organic light emitting diode display device including pixel driving circuit

ActiveUS9953583B2Suppress brightness dropMinimizing leakage currentStatic indicating devicesDisplay deviceEngineering

An apparatus comprising a circuit configured to control anode voltages of one or more adjacent pixel rows, which are adjacent to an Nth pixel row, to achieve minimal voltage differences between said Nth pixel row and said adjacent pixel rows to suppress luminance drops in an OLED display by minimizing leakage currents being introduced from adjacent pixel rows.

Owner:LG DISPLAY CO LTD

Schotiky barrier tunnel transistor and method of manufacturing the same

ActiveUS20070034951A1Minimizing leakage currentPromote formationSolid-state devicesSemiconductor/solid-state device manufacturingDielectricSchottky barrier

Provided are a Schottky barrier tunnel transistor and a method of manufacturing the same that are capable of minimizing leakage current caused by damage to a gate sidewall of the Schottky barrier tunnel transistor using a Schottky tunnel barrier naturally formed at a semiconductor-metal junction as a tunnel barrier. The method includes the steps of: forming a semiconductor channel layer on an insulating substrate; forming a dummy gate on the semiconductor channel layer; forming a source and a drain at both sides of the dummy gate on the insulating substrate; removing the dummy gate; forming an insulating layer on a sidewall from which the dummy gate is removed; and forming an actual gate in a space from which the dummy gate is removed. In manufacturing the Schottky barrier tunnel transistor using the dummy gate, it is possible to form a high-k dielectric gate insulating layer and a metal gate, and stable characteristics in silicidation of the metal layer having very strong reactivity can be obtained.

Owner:ELECTRONICS & TELECOMM RES INST

Method for generating minimal leakage current input vector using heuristics

ActiveUS7516425B2Minimize leakage currentOvercomes drawbackComputer aided designSoftware simulation/interpretation/emulationHeuristicGenetic algorithm

A method for generating an input vector to reduce the leakage current in an integrated circuit by using heuristics includes transforming the integrated circuit to a logic representation with PMOS and NMOS parts and P and N devices of the integrated circuit into edges, selecting between PMOS and NMOS logic representations the one with deepest serial stack; and for the selected PMOS or NMOS logic representation, assigning weights to the edges, thereby generating a weighted graph. The assignment includes starting from the output terminal to the Power Vdd (for PMOS) or Ground Vss (for NMOS), and labeling edge weights in a descending order. The resulted cost function from the method of the present invention can be applied as heuristics in different algorithms, such as branch-and-bound, simulated annealing, or genetic algorithm.

Owner:IND TECH RES INST

Gas sensor

ActiveUS10514356B2Minimizing leakage currentImprove accuracyCoupling device detailsMaterial electrochemical variablesEngineeringElectrical and Electronics engineering

Owner:DENSO CORP

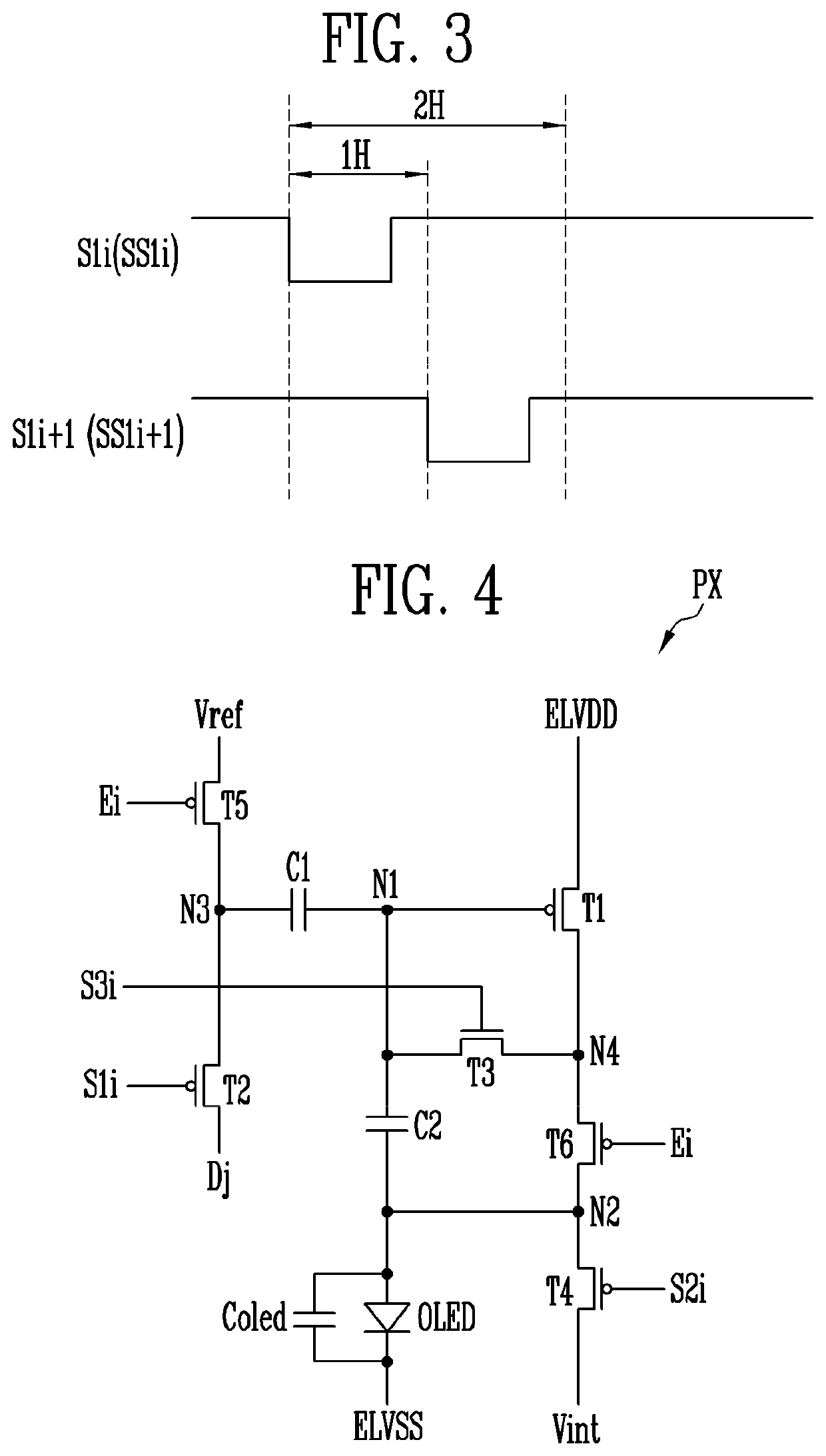

Pixels, display device comprising pixels, and driving method therefor

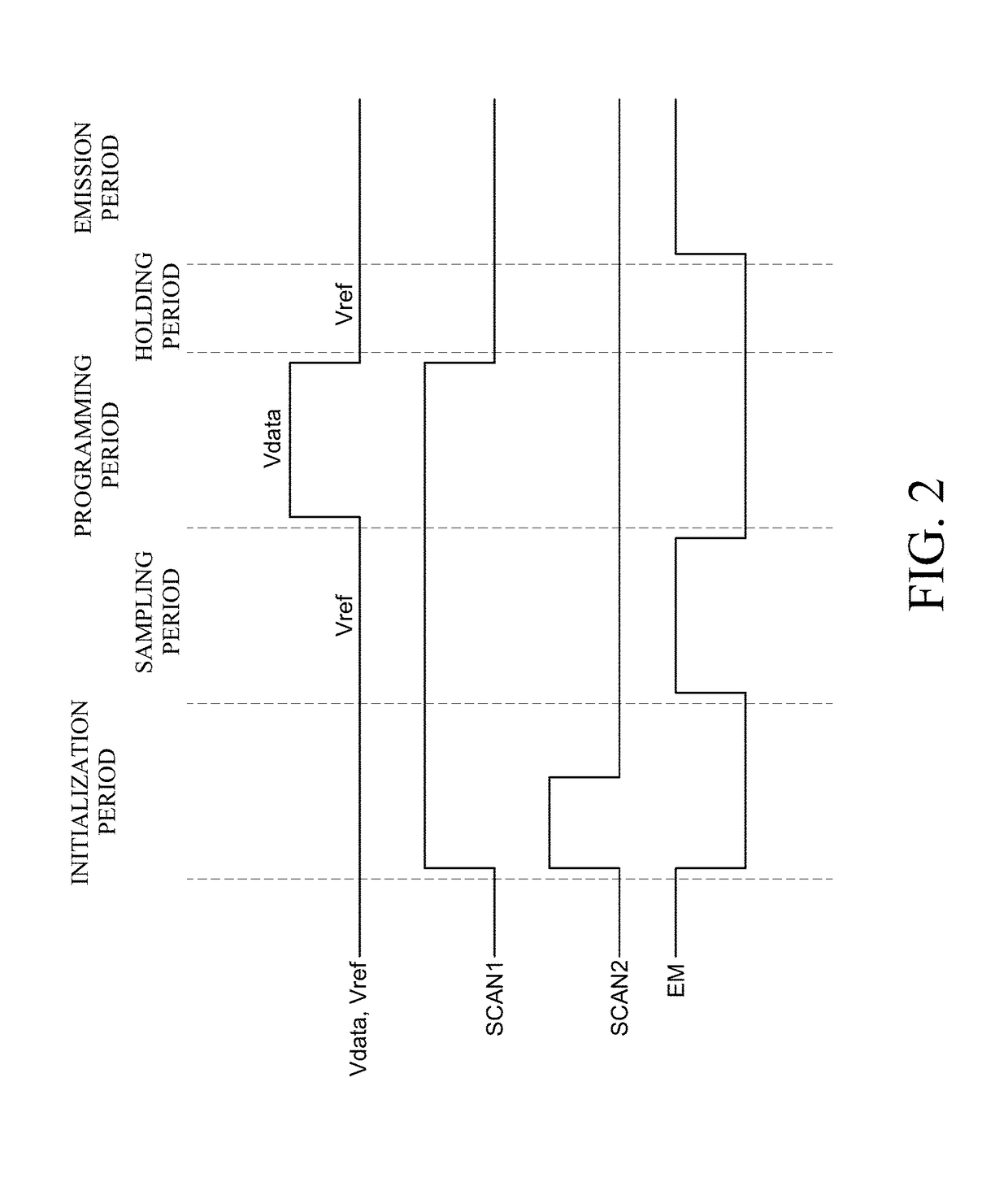

PendingUS20220230586A1Avoid light deteriorationMinimizing leakage currentStatic indicating devicesComputer hardwareScan line

In a pixel, a display device including a pixel, and a method of driving the display device, the pixel includes a first transistor connected to a first power source, a fourth node and a first node, a second transistor connected to a third node, a data line and an i-th first scan line, a third transistor connected to the first node, the fourth node, and an i-th third scan line, a fourth transistor connected to the second node, an initialization voltage, and an i-th second scan line, a first capacitor connected between the third node and the first node, a second capacitor connected between the first node and the second node, and an organic light emitting diode connected between the second node and a second power source, wherein I is a natural number and the third transistor is an N-type transistor.

Owner:SAMSUNG DISPLAY CO LTD

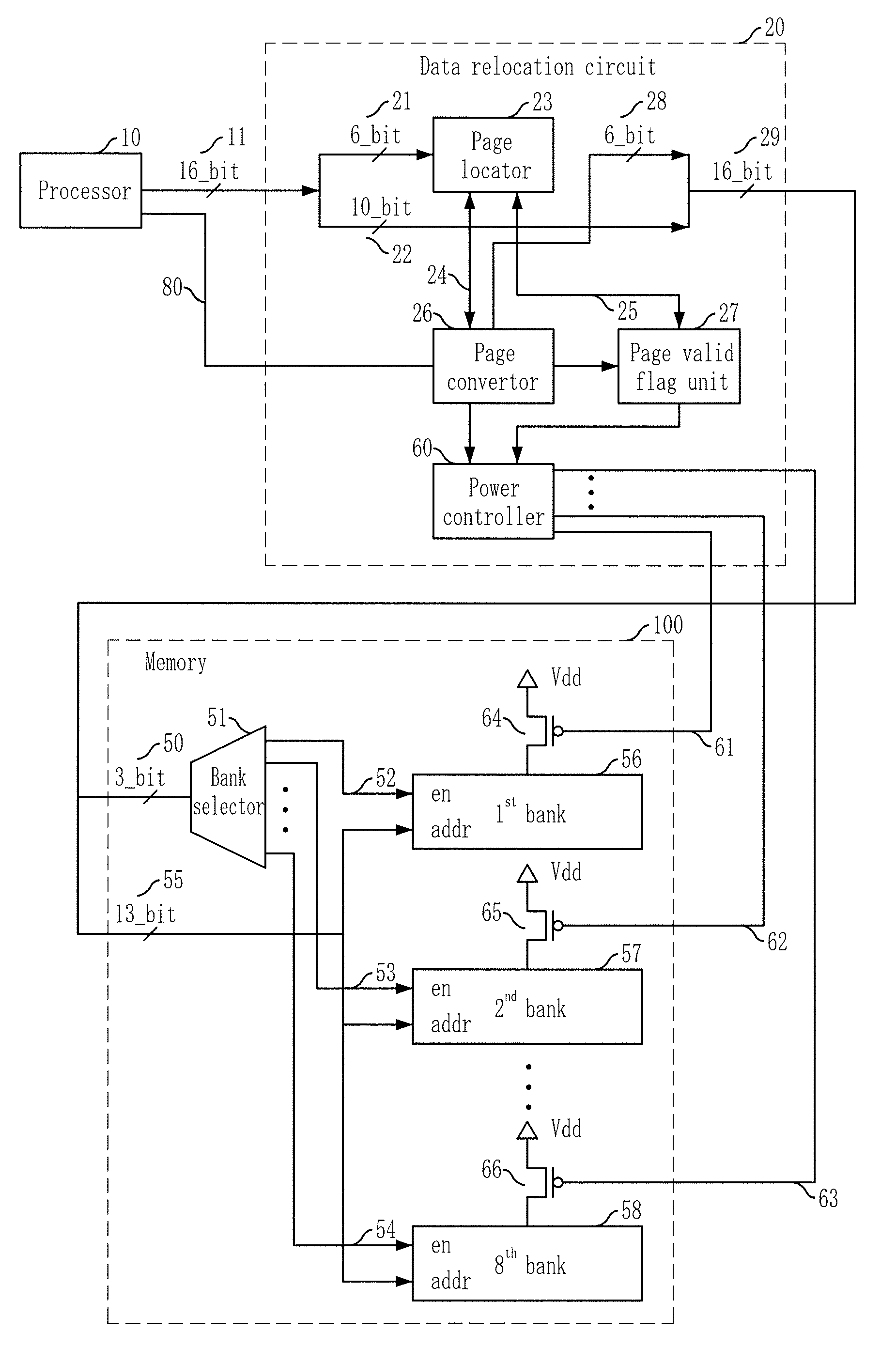

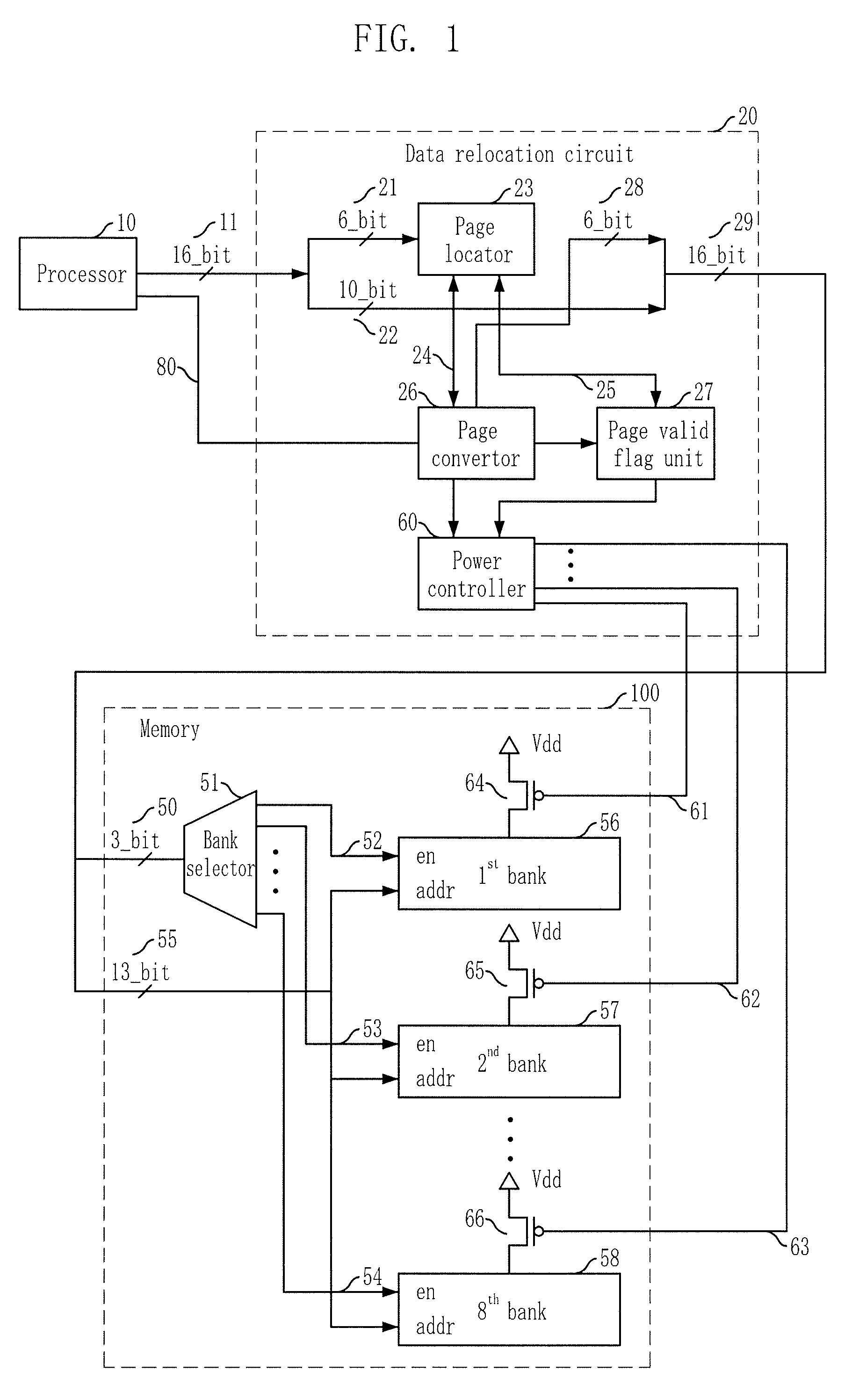

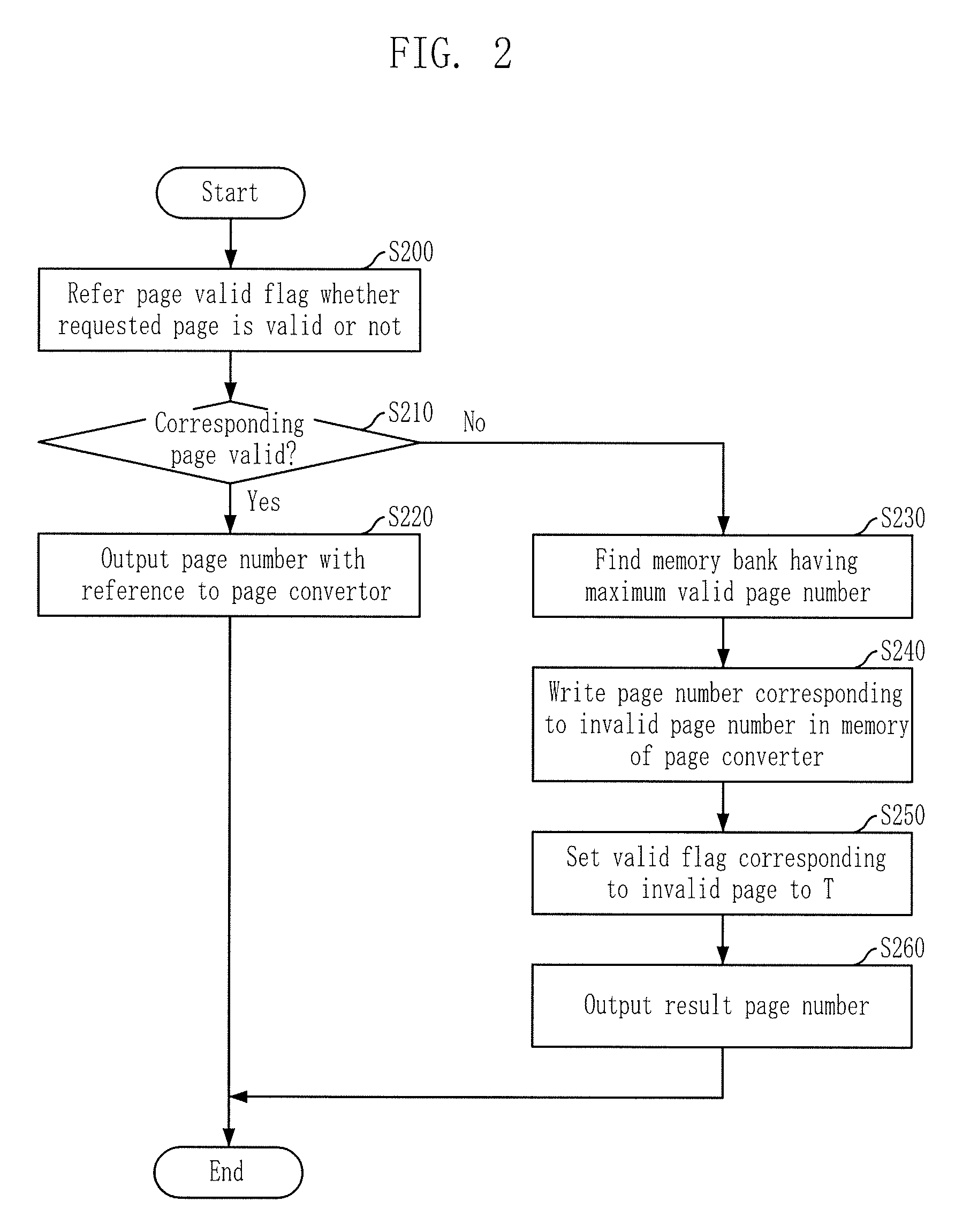

Embedded system and page relocation method therefor

ActiveUS7900018B2Minimizing leakage currentReduce power consumptionEnergy efficient ICTDigital data processing detailsMemory addressControl signal

Provided are an embedded system and a method for relocating memory pages therefor. The embedded system includes a processor, a data relocating circuit for receiving a logical address from the processor, mapping the received logical address to a physical address to locate a valid page in a predetermined bank, and generating a bank power control signal according to whether or not a corresponding memory bank includes valid pages, and a memory including a plurality of memory banks addressed by a physical address outputted from the data relocating circuit and a plurality of switching means for selectively supplying a power voltage to each of memory banks in response to the bank power control signal.

Owner:ELECTRONICS & TELECOMM RES INST

Liquid crystal display

InactiveUS7736011B2Minimizing leakage currentIncrease brightnessCoupling device connectionsLighting support devicesLiquid-crystal displayEngineering

Owner:LG DISPLAY CO LTD

Secondary battery having constant-voltage device

ActiveUS7737661B2Avoid explosionAvoid ignitionBatteries circuit arrangementsMaterial analysis by electric/magnetic meansCapacity valueIgnition voltage

Disclosed is a secondary battery having a constant-voltage device for preventing the secondary battery from being excessively overcharged. The breakdown voltage of the constant-voltage device is lower than the explosion or ignition voltage of the secondary battery, so the discharge operation may occur before the secondary battery is exploded or ignited even if the voltage of the secondary battery rises above the overcharge voltage, thereby protecting the secondary battery from explosion or ignition. The leakage current value of the constant-voltage device is less than 0.05% of the capacity value of the secondary battery under the maximum charge voltage of the secondary battery, or the breakdown voltage of the constant-voltage device is higher than the maximum charge voltage of the secondary battery. Thus, the constant-voltage device rarely generates the leakage current even if the secondary battery has been charged with the maximum charge voltage.

Owner:LG ENERGY SOLUTION LTD

Method of healing defect at junction of semiconductor device using germanium

ActiveUS8999825B2Reduce depthMinimizing leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesIn situ dopingSemiconductor

Owner:KOREA ADVANCED NANO FAB CENT +1

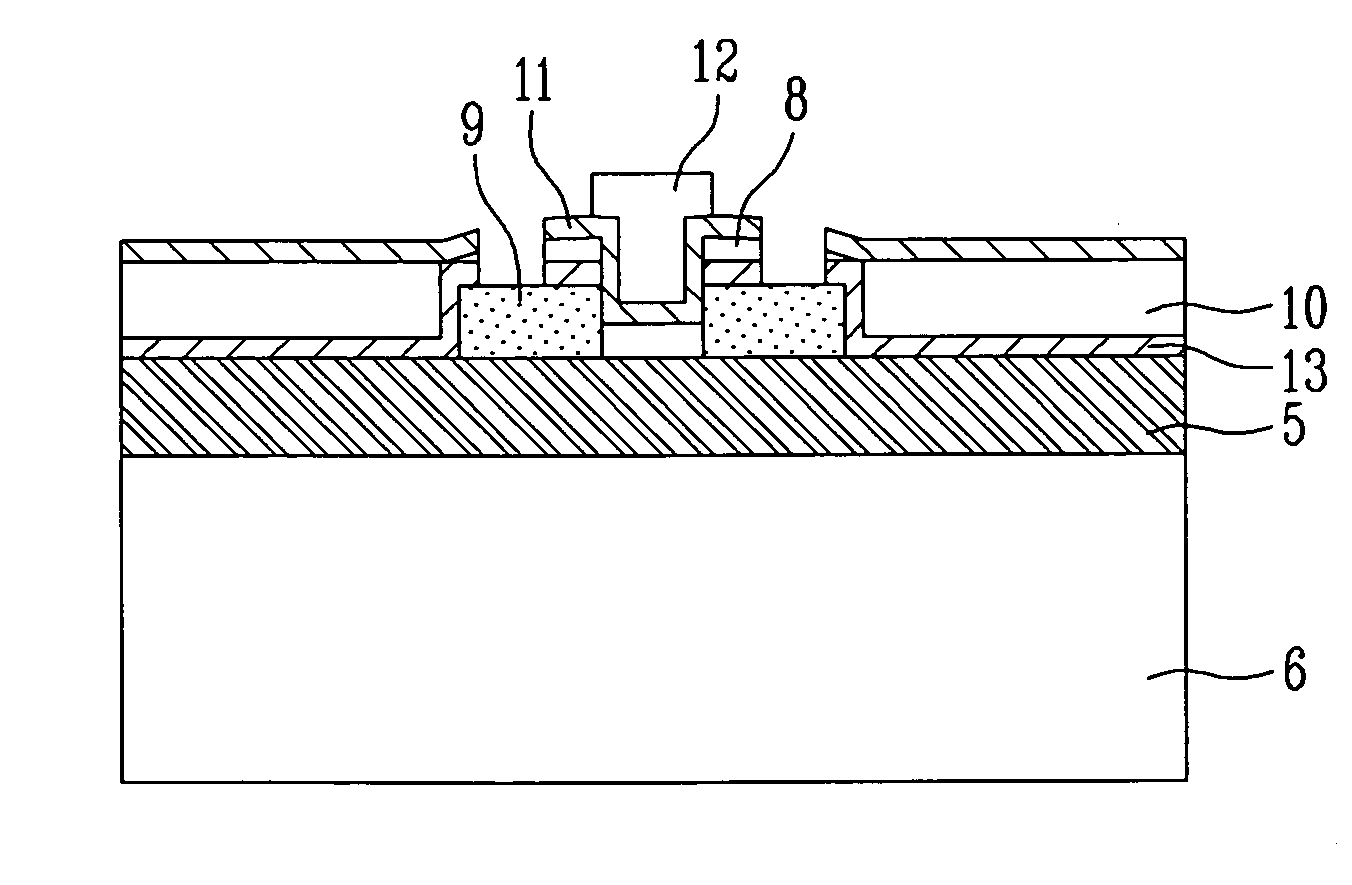

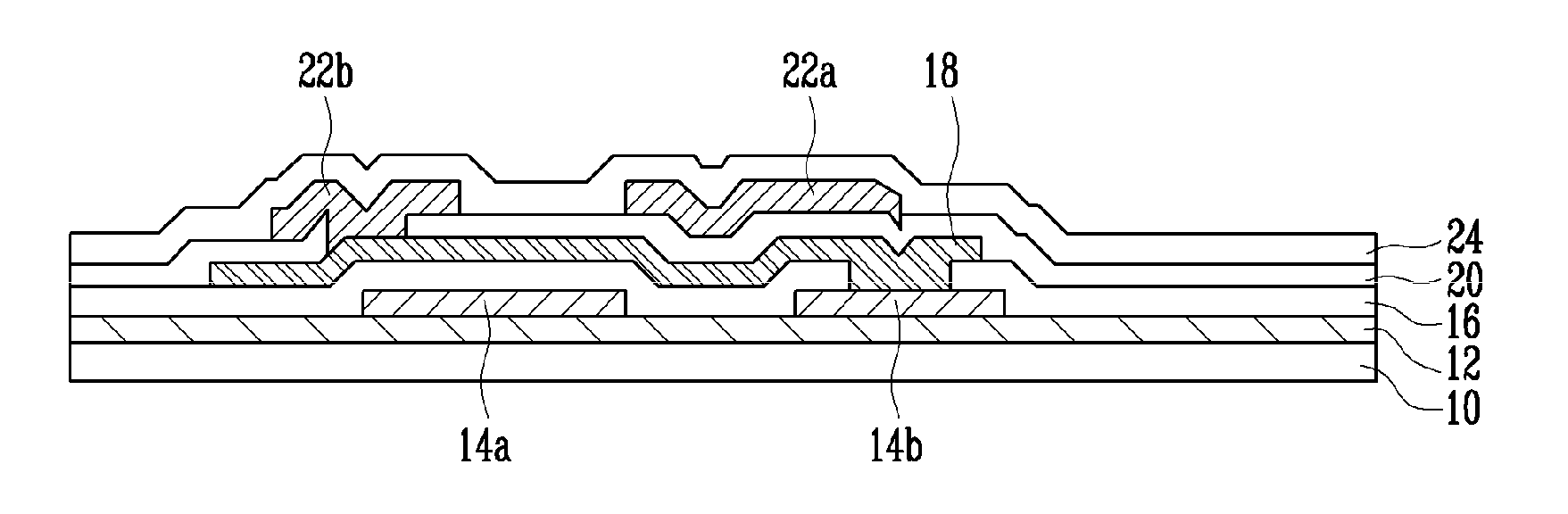

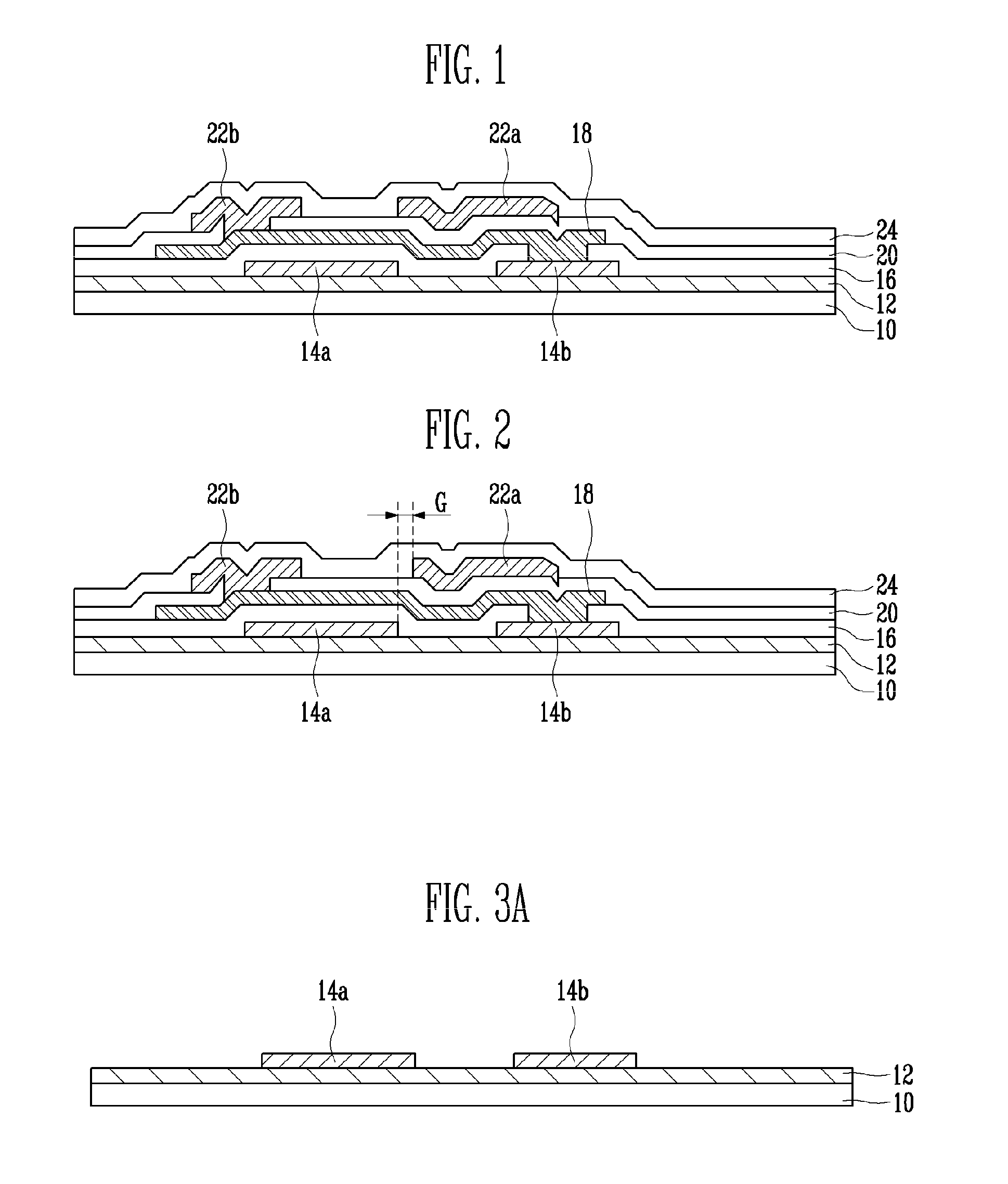

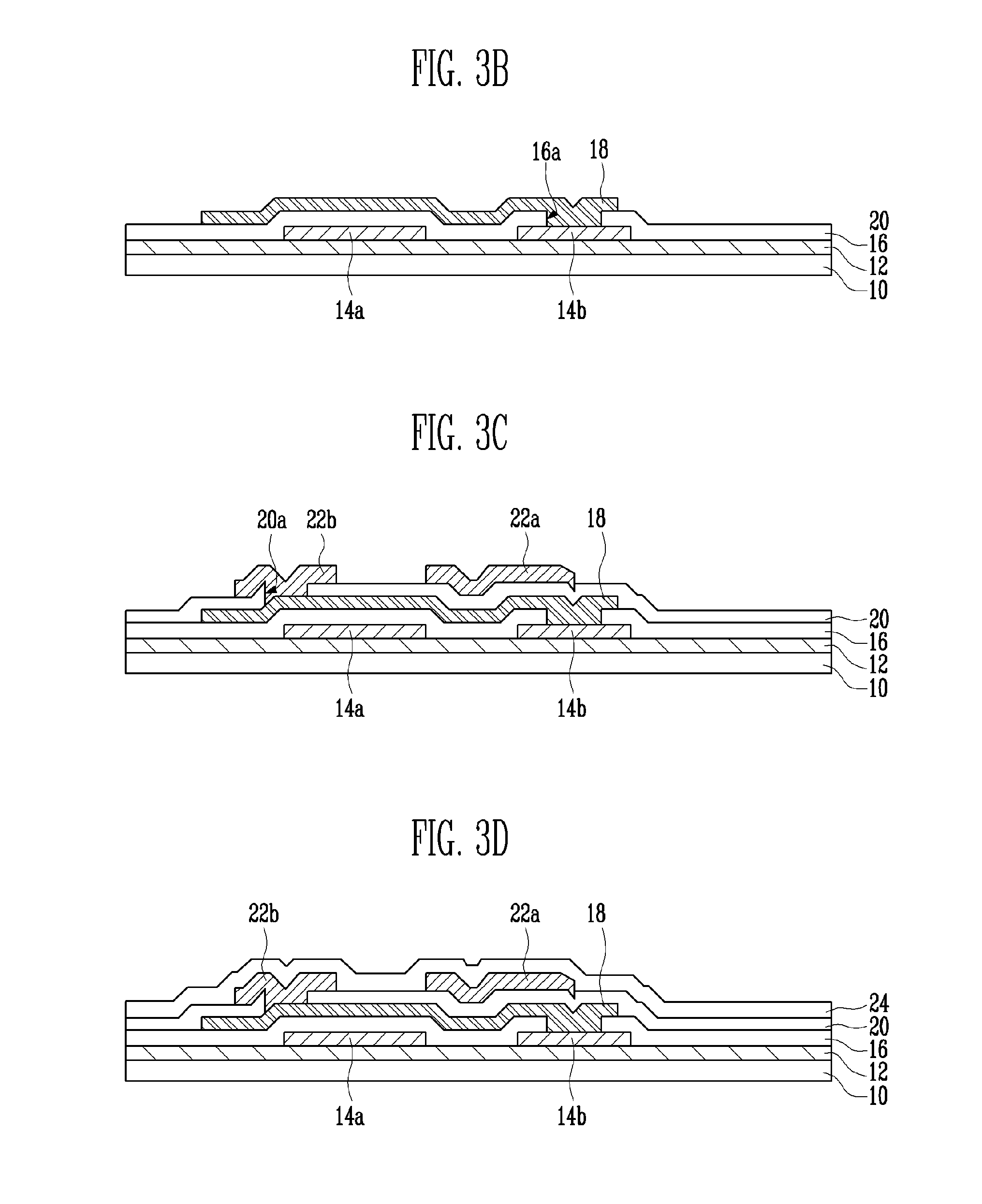

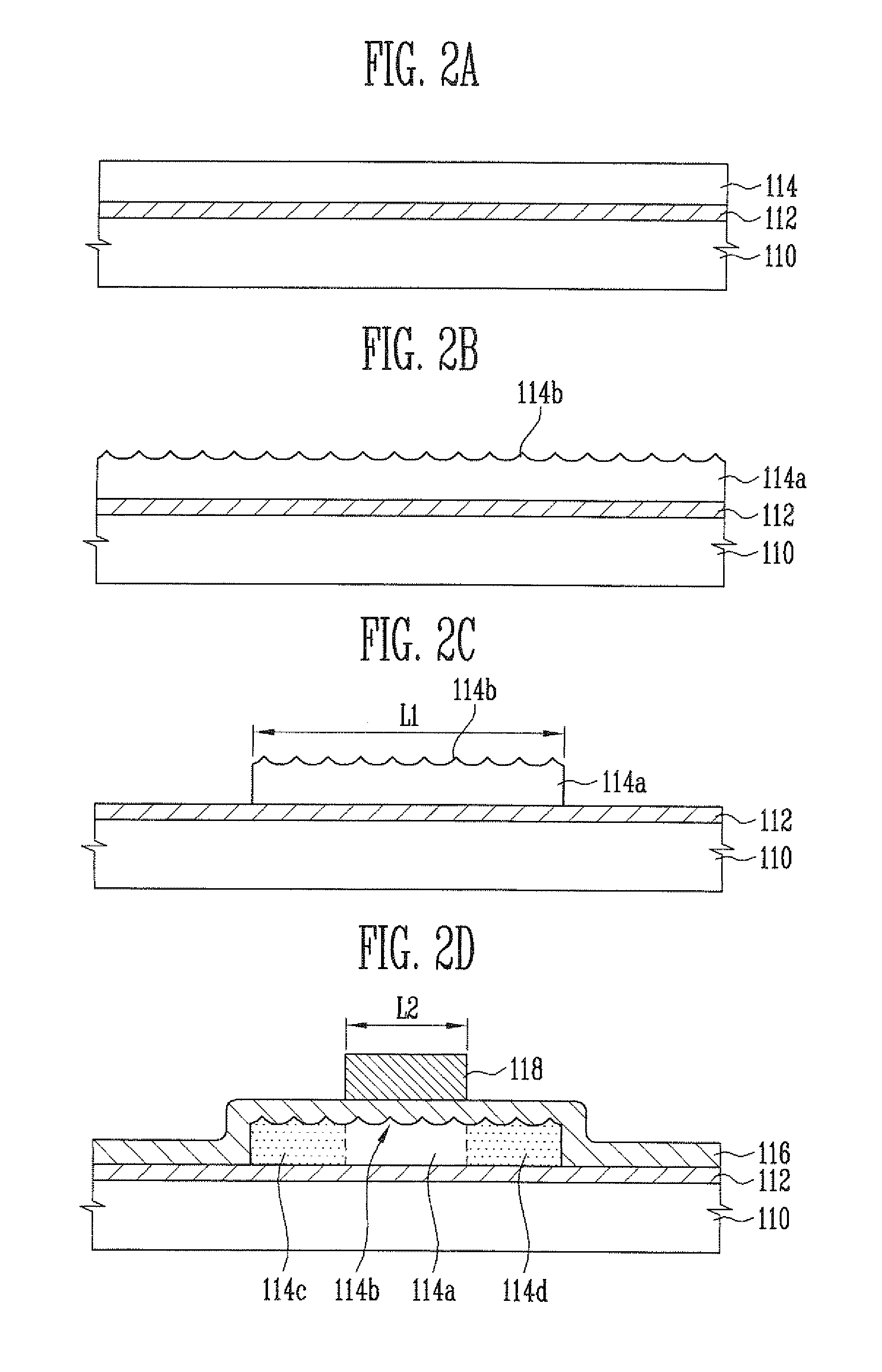

Thin film transistor, method of manufacturing the thin film transistor and organic light emitting display device having the thin film transistor

ActiveUS20110095286A1Excellent electrical propertiesMinimizing leakage currentSolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceActive layer

A thin film transistor (TFT) using an oxide semiconductor as an active layer, a method of manufacturing the TFT and an organic light emitting display device having the TFT. In one embodiment, a TFT includes a first gate electrode formed on a substrate. A source electrode is formed to be spaced apart from the gate electrode on the substrate. A first insulating layer is formed on the substrate. An active layer is formed of an oxide semiconductor on the first insulating layer, and connected to the source electrode. A second insulating layer is formed on the first insulating layer. A second gate electrode is formed on the second insulating layer so as not to overlap with the first gate electrode. A drain electrode is formed to be spaced apart from the second gate electrode on the second insulating layer, and connected to the active layer.

Owner:SAMSUNG DISPLAY CO LTD

Semiconductor device and method of manufacturing the same

ActiveUS7763953B2Minimizing leakage currentSufficient capacitanceTransistorSolid-state devicesDielectric layerCapacitor

A semiconductor device including a capacitor which includes a first electrode, a second electrode, and a dielectric layer disposed between the first electrode and the second electrode, the dielectric layer including: a first paraelectric film formed of a material containing a first metal element and at least one kind of second metal element; a second paraelectric film disposed between the first electrode and the first paraelectric film; and a third paraelectric film disposed between the second electrode and the first paraelectric film, wherein the second paraelectric film is formed of a material containing the first metal element but substantially not containing the second metal element, and the third paraelectric film is formed of a material containing the first metal element but substantially not containing the second metal element.

Owner:MICRON TECH INC

Sonar system and impedance matching method thereof

ActiveUS9103905B2Reduce physical sizeHigh bandwidthSeismic energy generationMechanical vibrations separationPower factorTransducer

This specification relates to an active SONAR system comprising a transmitter, a transducer and an impedance matching circuit for expanding bandwidth and increasing a power factor value in sound and ultrasonic wave bands by mutually matching resonant frequencies of the transducer and the impedance matching circuit or a resonant frequency between the transducer and the impedance matching circuit using an electrical equivalent model corresponding to actual impedance data of the transducer and controlling the positions and the intervals of the frequencies at which reactance components of the transducer including the impedance matching circuit become zero, and an impedance matching method thereof. This allows for efficient driving in a broadband between the transmitter and the transducer in the active SONAR system, contributing to output power performance and detection performance of the active SONAR system.

Owner:AGENCY FOR DEFENSE DEV

Thin Film Transistor, Method of Manufacturing the Same, and Display Device Having Thin Film Transistor

ActiveUS20110221991A1Minimizing leakage currentMinimize leakage currentSolid-state devicesSemiconductor/solid-state device manufacturingOxide thin-film transistorImaging quality

A thin film transistor, a manufacturing method thereof, and a display device having the same are disclosed. The thin film transistor includes a semiconductor layer formed on a substrate, a gate insulating layer formed on the substrate including the semiconductor layer, a gate electrode formed on the gate insulating above the semiconductor layer, source and drain electrodes connected to the semiconductor layer, and 3.5 to 4.5 protrusions formed on the semiconductor layer overlapped with the gate electrode. Malfunction of the thin film transistor and inferior image quality of the display device can be prevented by adjusting the number of protrusions to minimize leakage current and defects.

Owner:SAMSUNG DISPLAY CO LTD