Patents

Literature

142 results about "Surface conduction" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

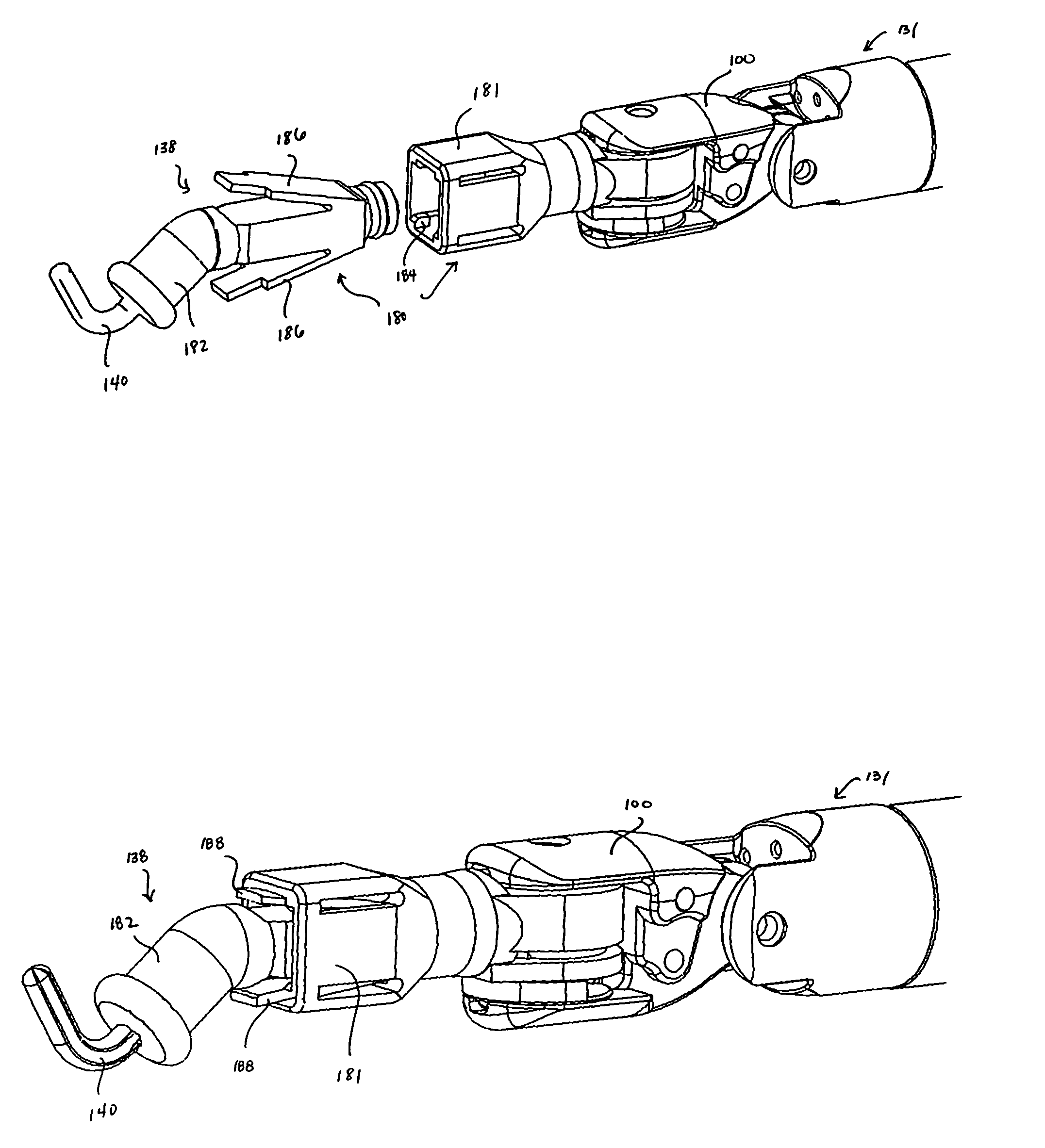

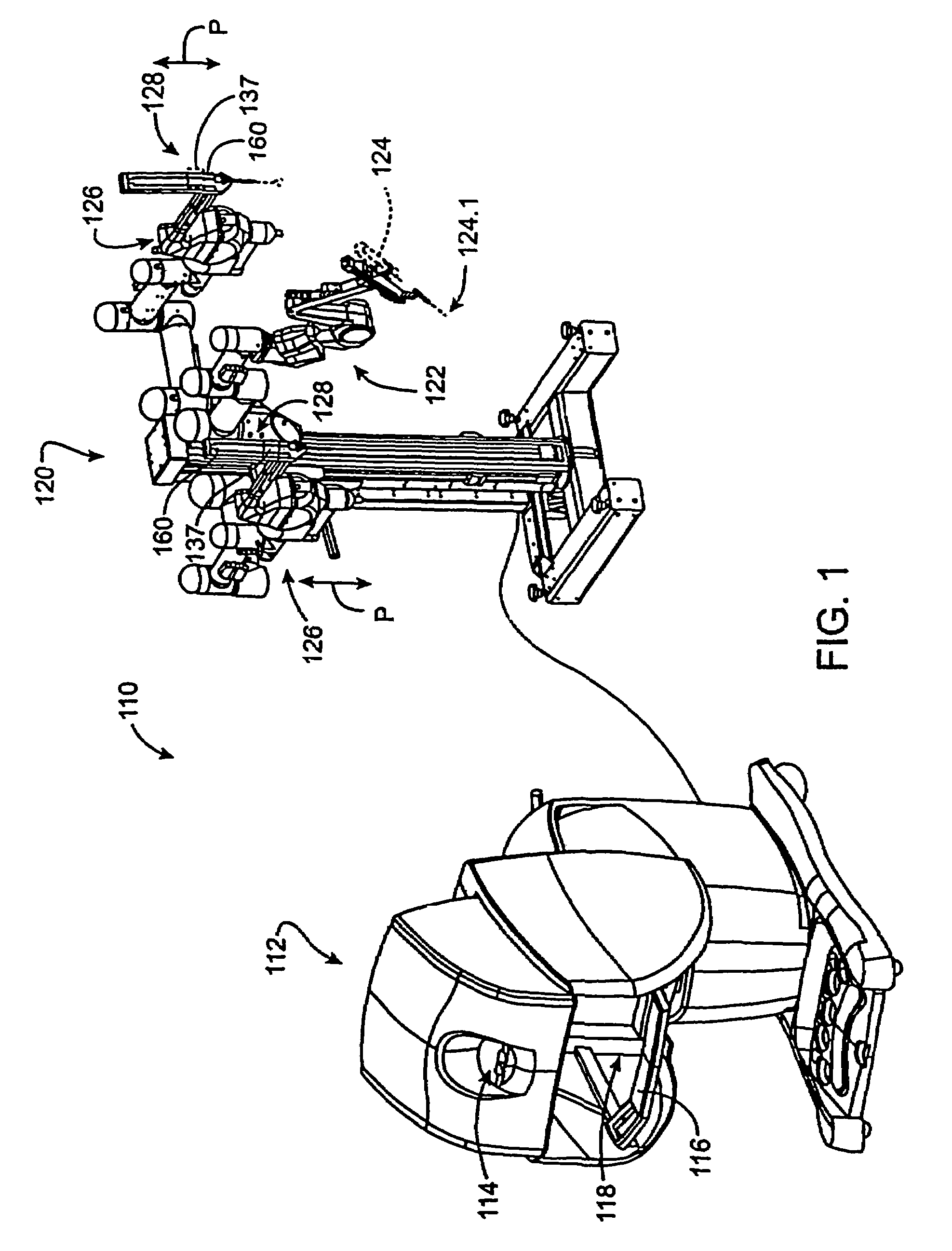

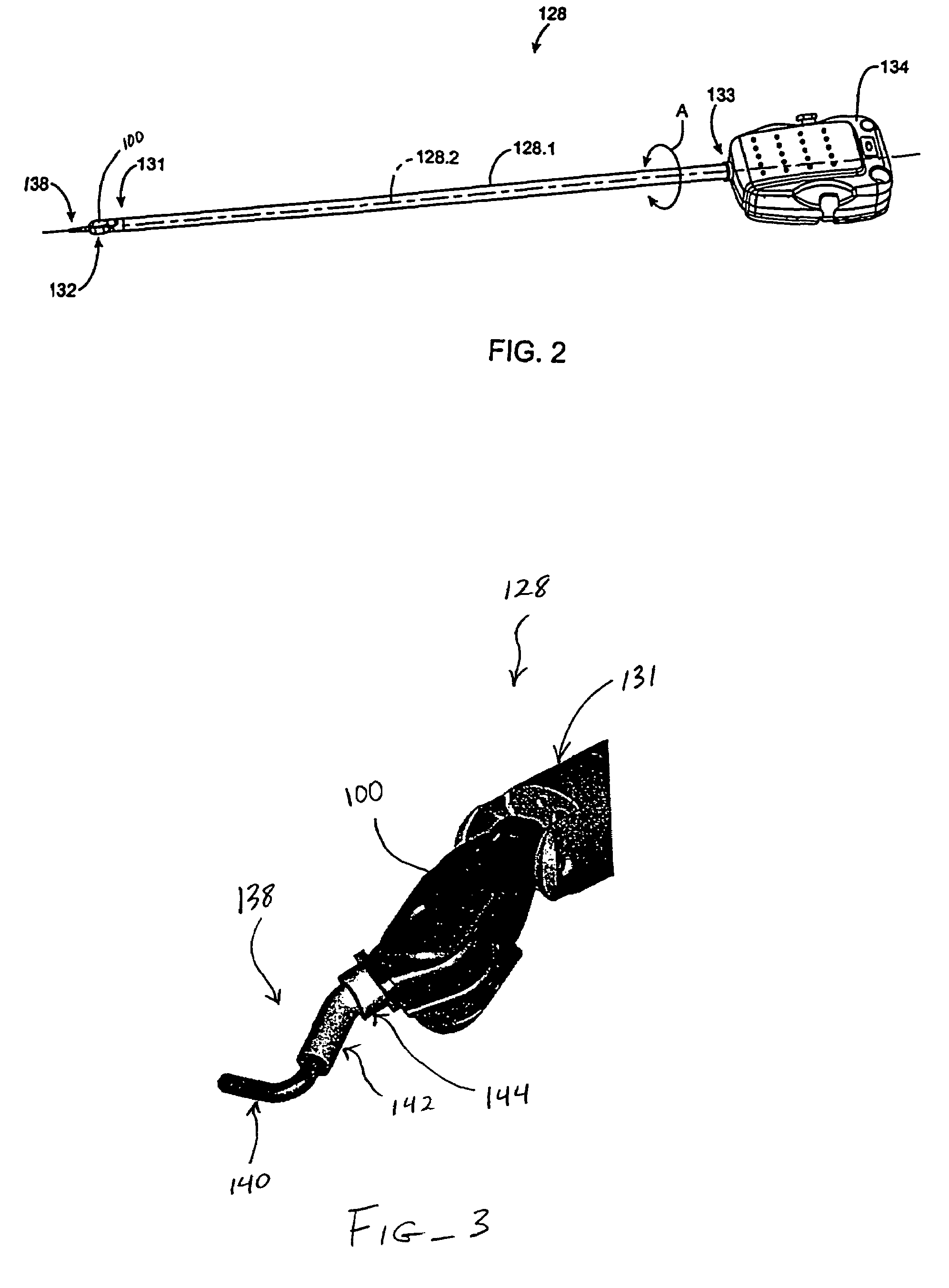

Electro-surgical instrument with replaceable end-effectors and inhibited surface conduction

ActiveUS7367973B2Avoid conductionInhibit currentDiagnosticsSurgical instruments for heatingElectricityActive electrode

Improved robotic surgery end-effectors include at least one insulation material for inhibiting surface conduction of electrical current in a proximal direction, from a distal active electrode toward the proximal end of the end-effector and toward the rest of the surgical instrument itself. Some embodiments include two layers of insulation to further prevent proximally-directed current. By inhibiting proximal current flow, the end-effectors prevent unwanted patient burns as well as electricity-related wear and tear in and around the area where the end-effector is coupled with the rest of the surgical instrument. In various embodiments, such end-effectors are preferably removably coupleable with a robotic surgical instrument.

Owner:INTUITIVE SURGICAL OPERATIONS INC

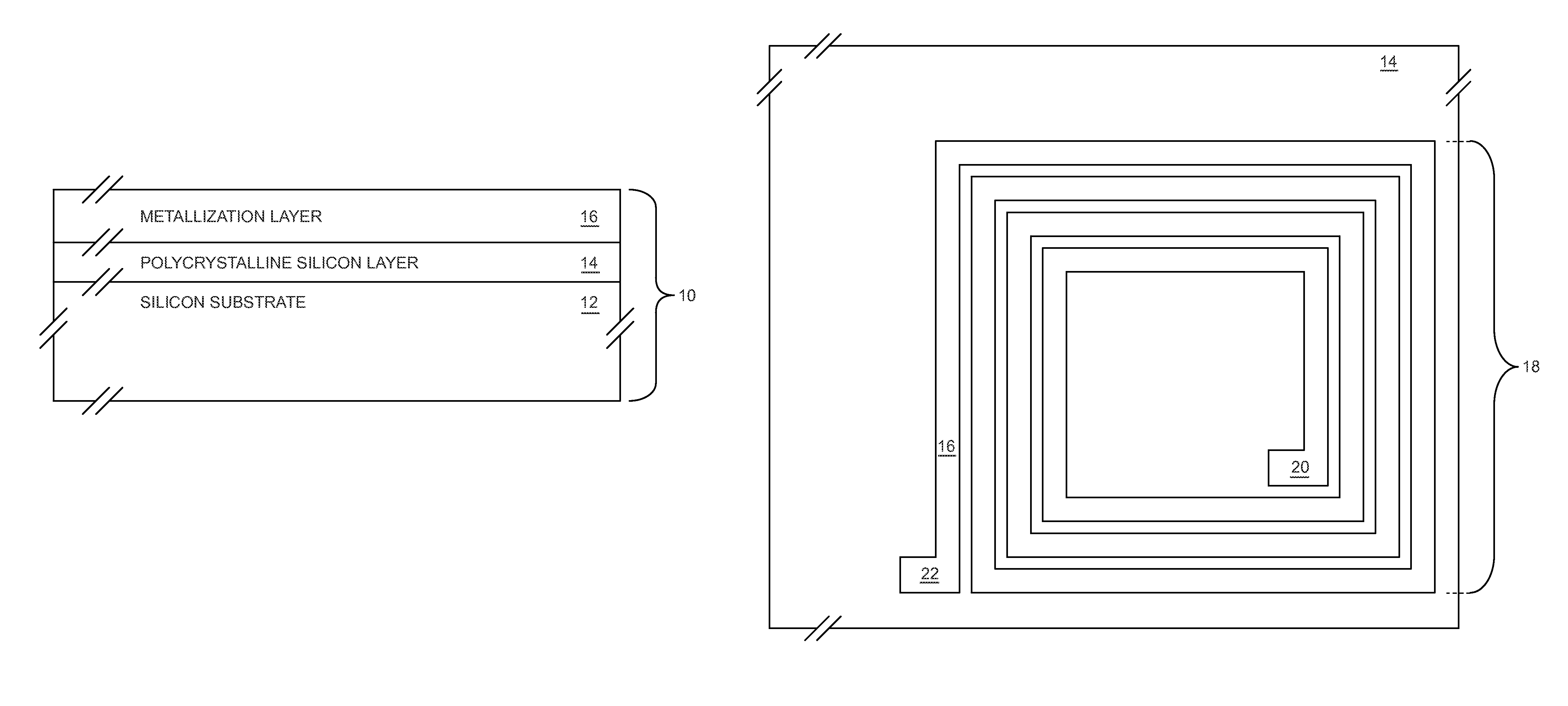

Linearity improvements of semiconductor substrate based radio frequency devices

ActiveUS7868419B1Effectively layerPrevent capacitance changeSemiconductor/solid-state device detailsSolid-state devicesCapacitanceHigh density

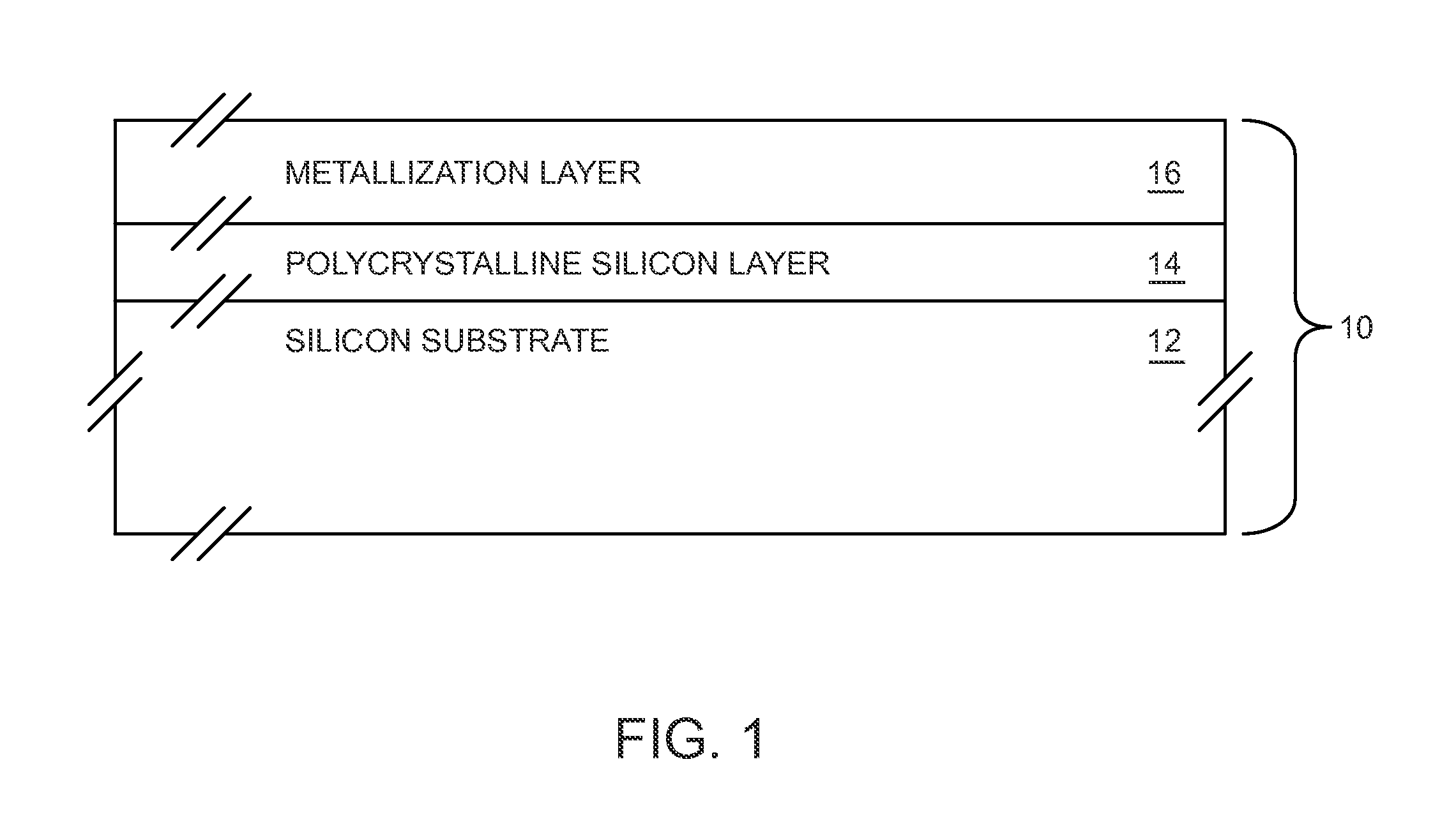

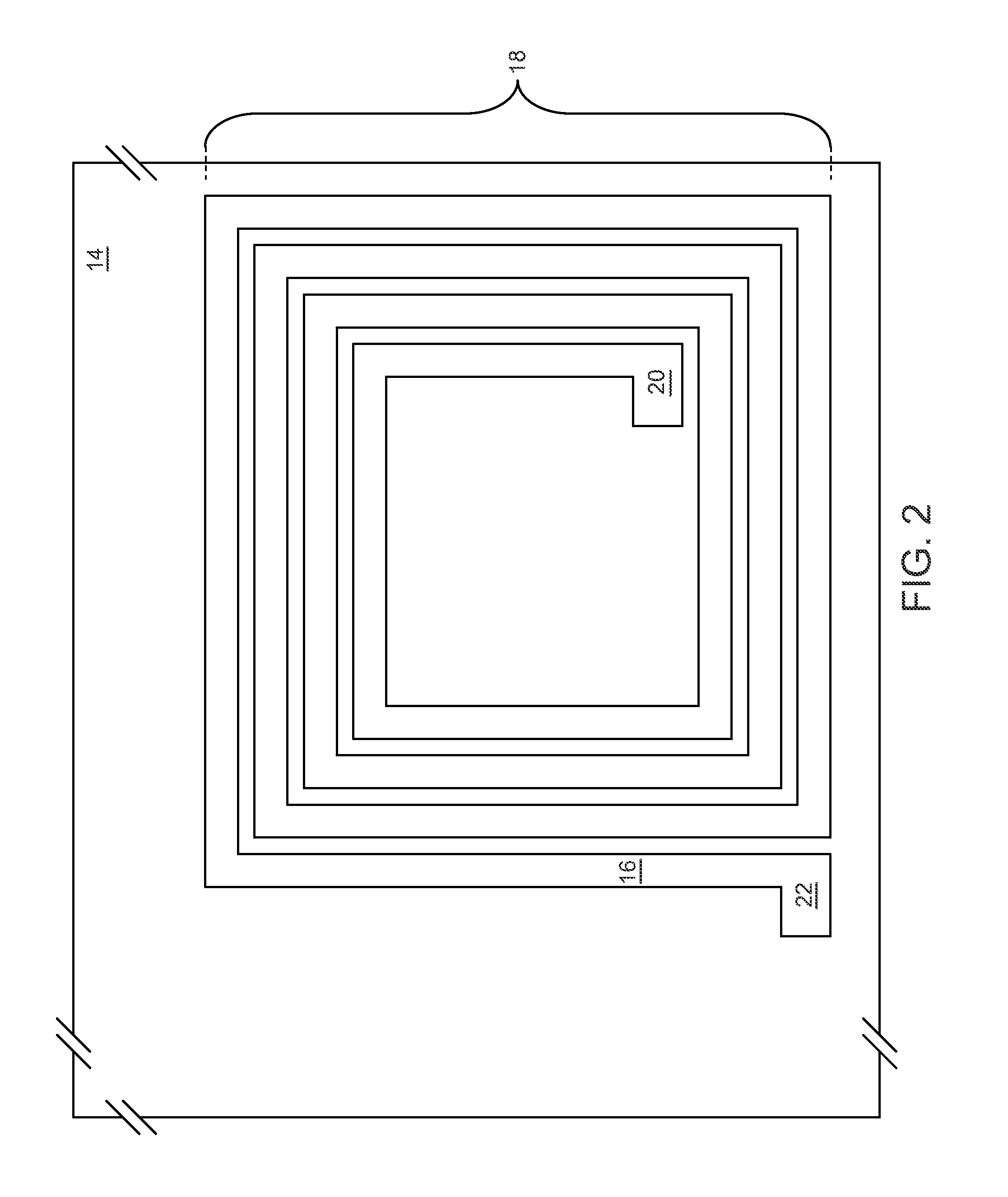

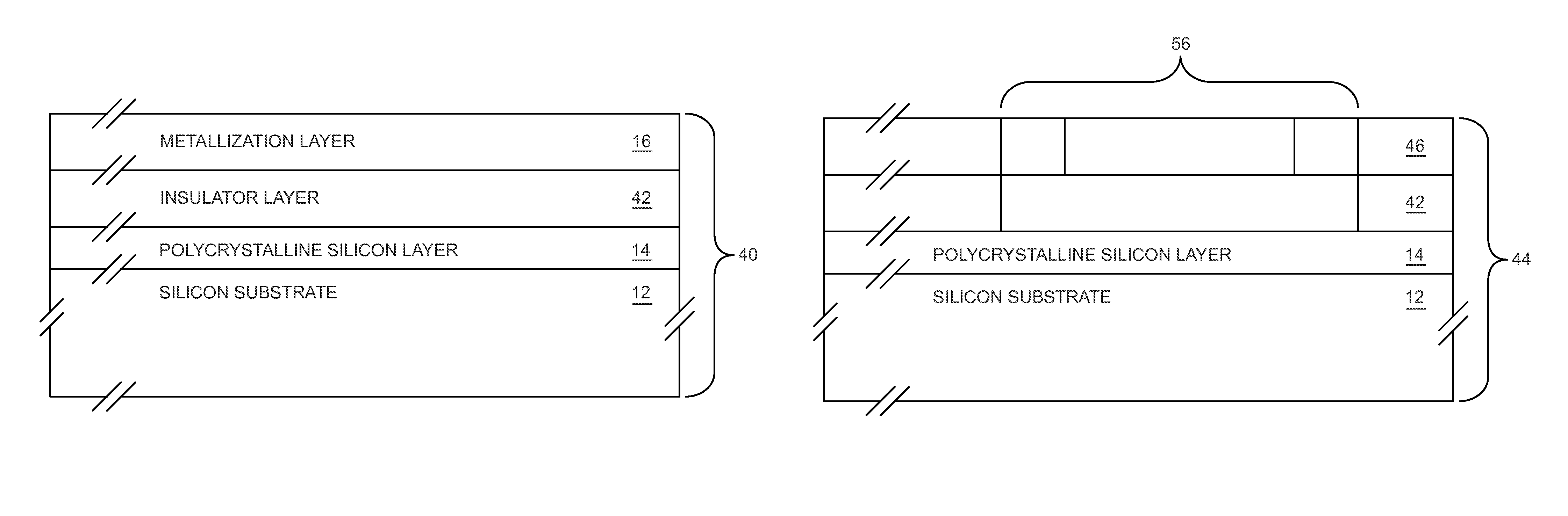

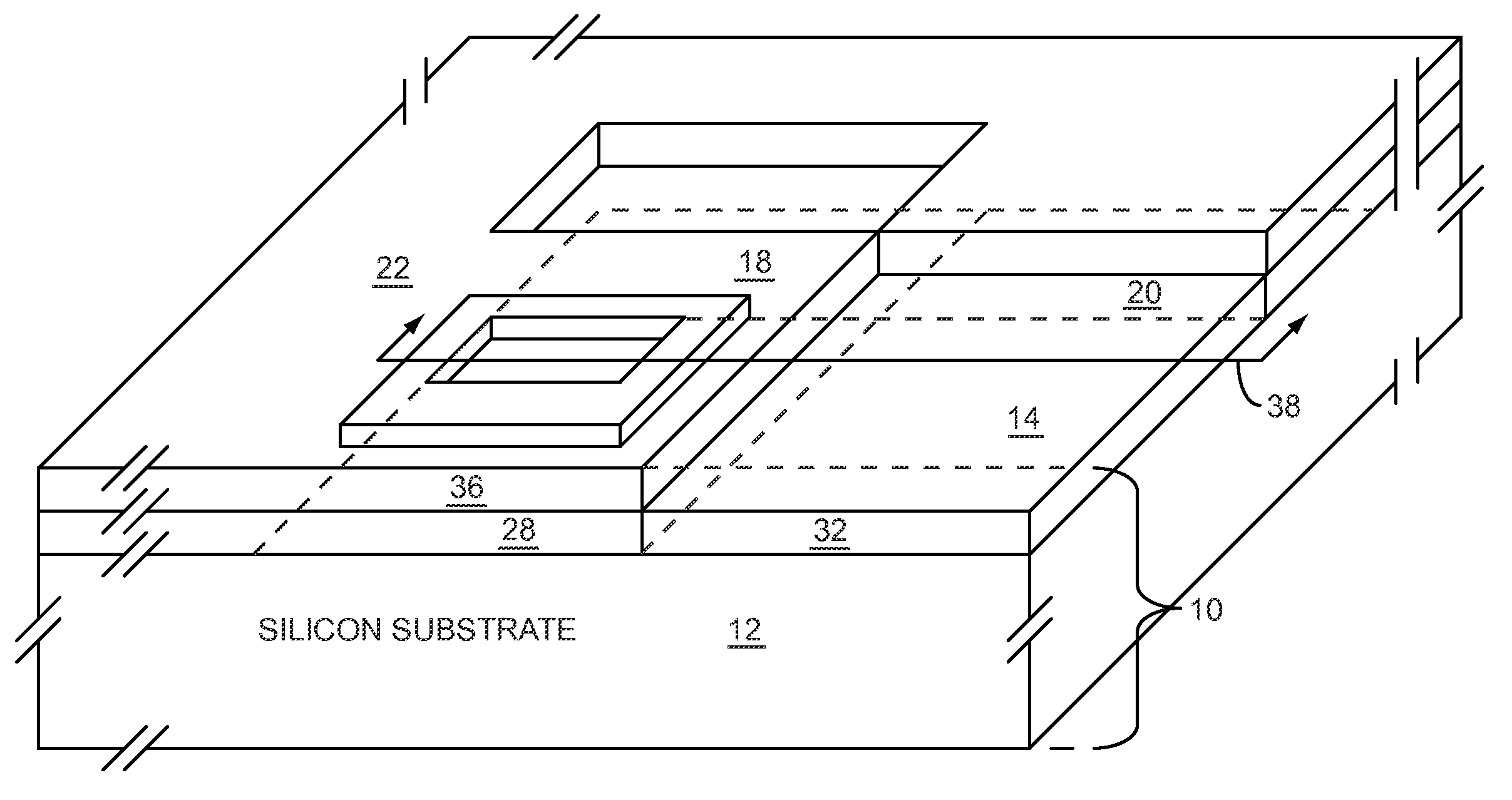

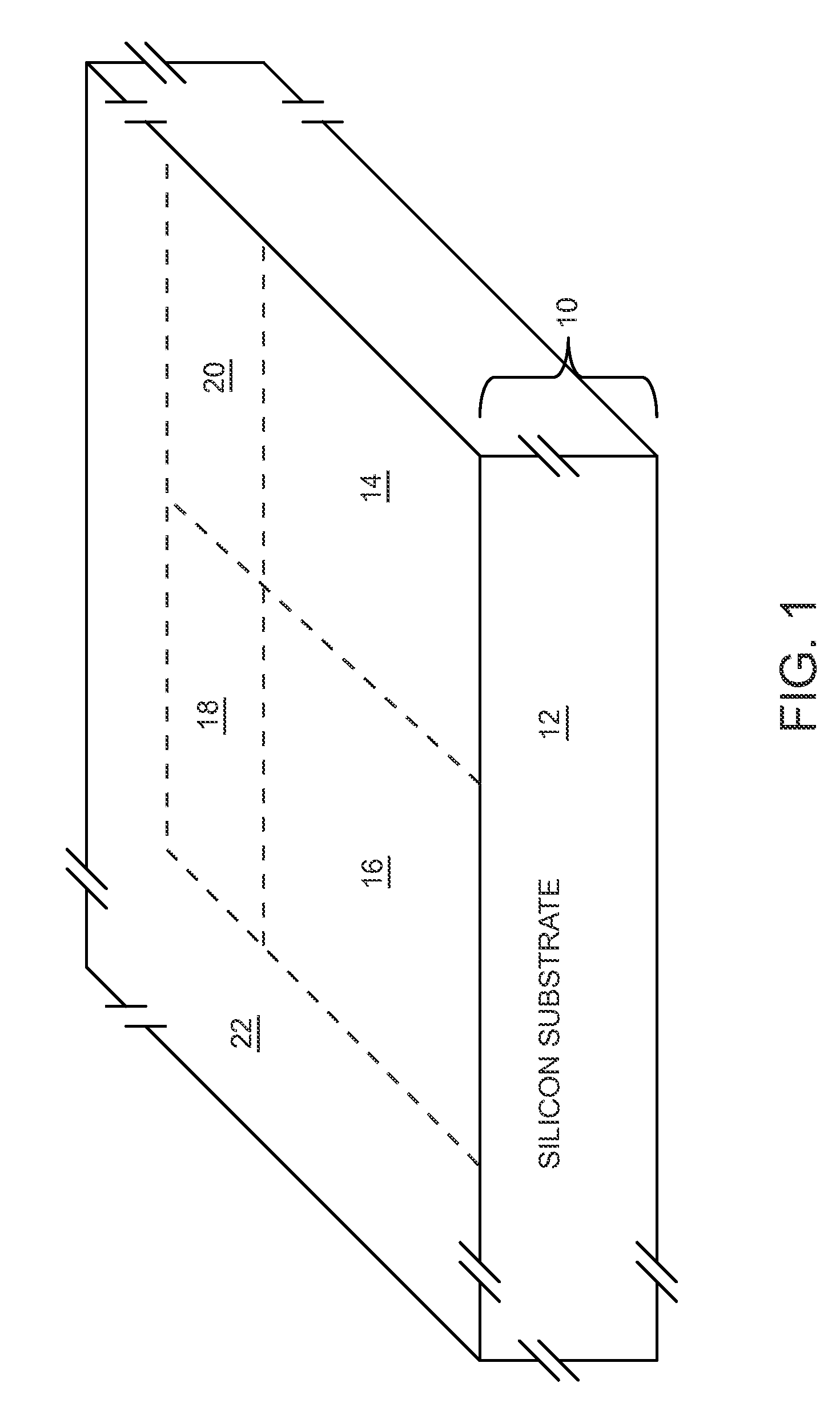

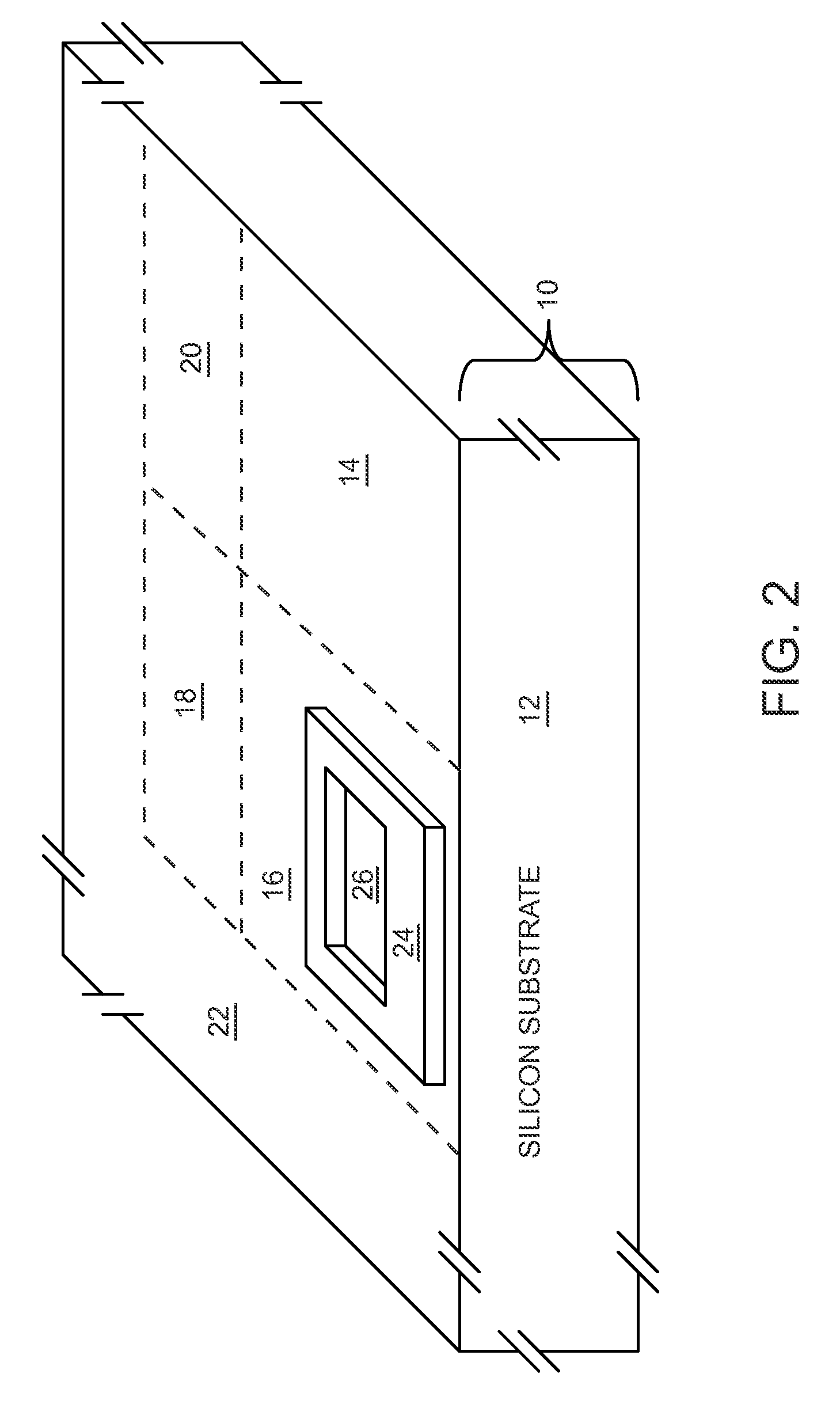

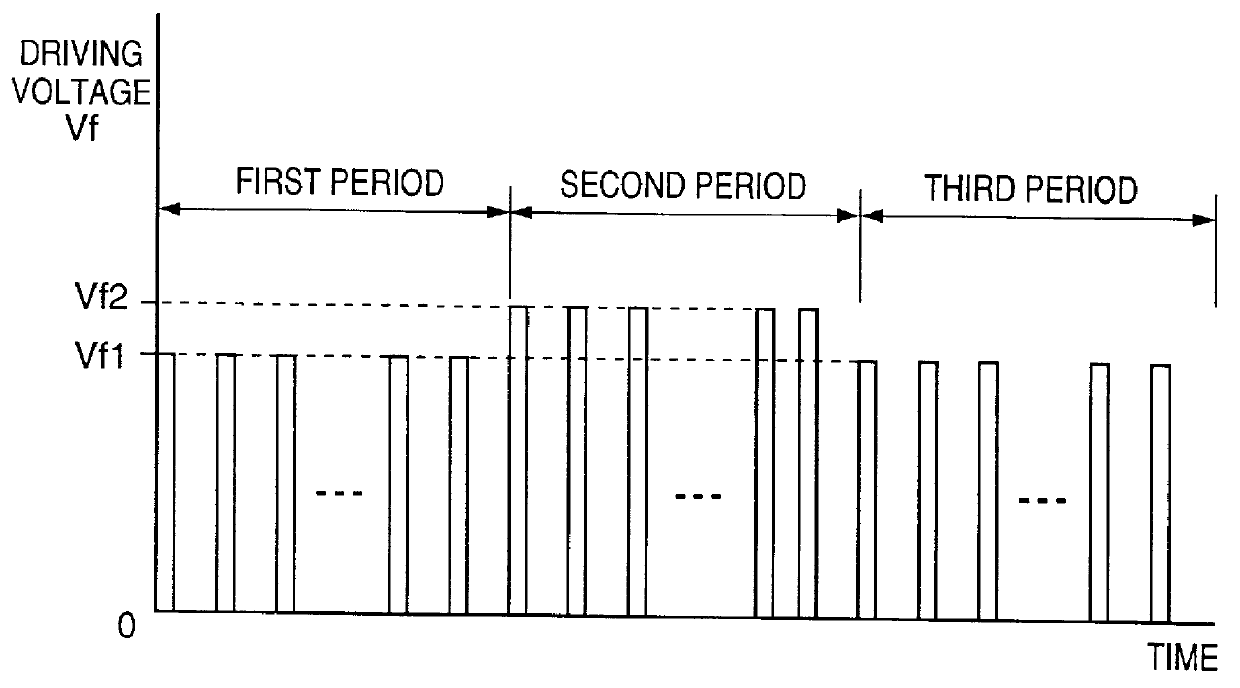

The present invention relates to using a trap-rich layer, such as a polycrystalline Silicon layer, over a semiconductor substrate to substantially immobilize a surface conduction layer at the surface of the semiconductor substrate at radio frequency (RF) frequencies. The trap-rich layer may have a high density of traps that trap carriers from the surface conduction layer. The average release time from the traps may be longer than the period of any present RF signals, thereby effectively immobilizing the surface conduction layer, which may substantially prevent capacitance and inductance changes due to the RF signals. Therefore, harmonic distortion of the RF signals may be significantly reduced or eliminated. The semiconductor substrate may be a Silicon substrate, a Gallium Arsenide substrate, or another substrate.

Owner:QORVO US INC

Linearity improvements of semiconductor substrate based radio frequency devices

ActiveUS8076750B1Effectively immobilizing the surface conduction layerPrevent capacitanceSemiconductor/solid-state device detailsSolid-state devicesCapacitanceRelease time

The present invention relates to using a trap-rich layer, such as a polycrystalline Silicon layer, over a semiconductor substrate to substantially immobilize a surface conduction layer at the surface of the semiconductor substrate at radio frequency (RF) frequencies. The trap-rich layer may have a high density of traps that trap carriers from the surface conduction layer. The average release time from the traps may be longer than the period of any present RF signals, thereby effectively immobilizing the surface conduction layer, which may substantially prevent capacitance and inductance changes due to the RF signals. Therefore, harmonic distortion of the RF signals may be significantly reduced or eliminated. The semiconductor substrate may be a Silicon substrate, a Gallium Arsenide substrate, or another substrate.

Owner:QORVO US INC

Method for fabricating electron emitter

ActiveUS7780496B2Low efficiencyDischarge tube luminescnet screensCathode ray tubes/electron beam tubesCarbon nanotubeFissure

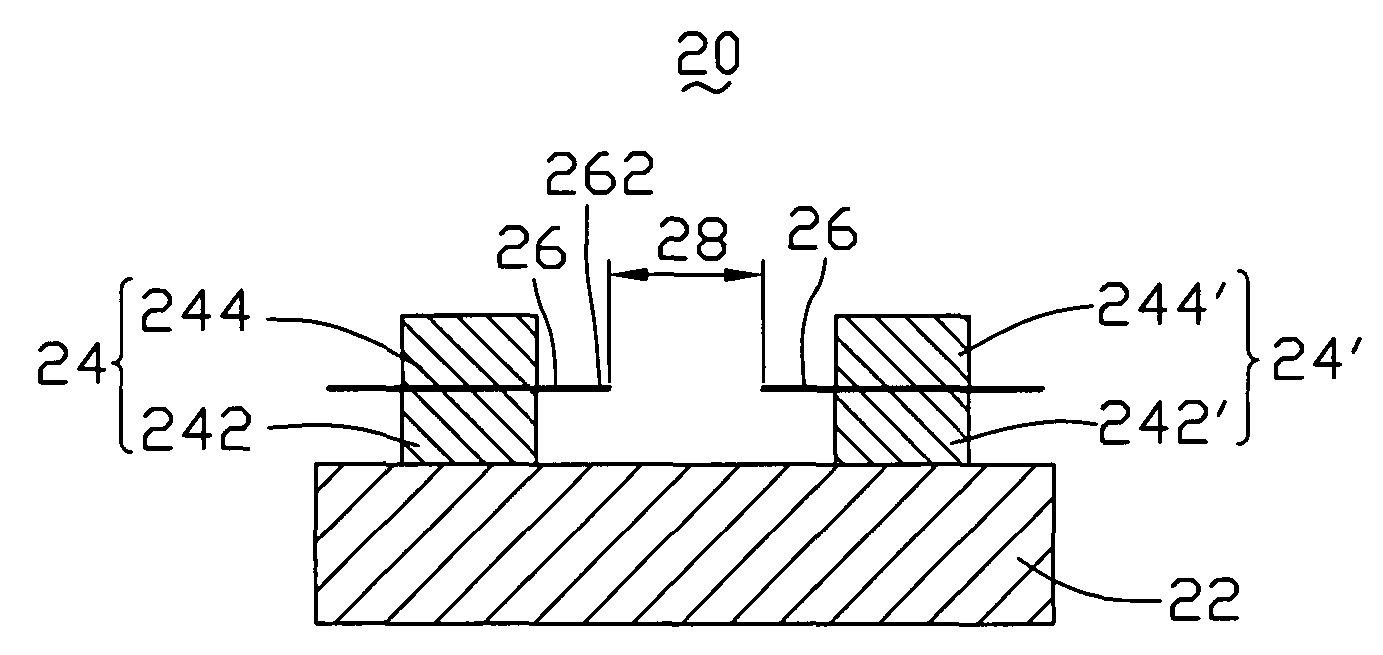

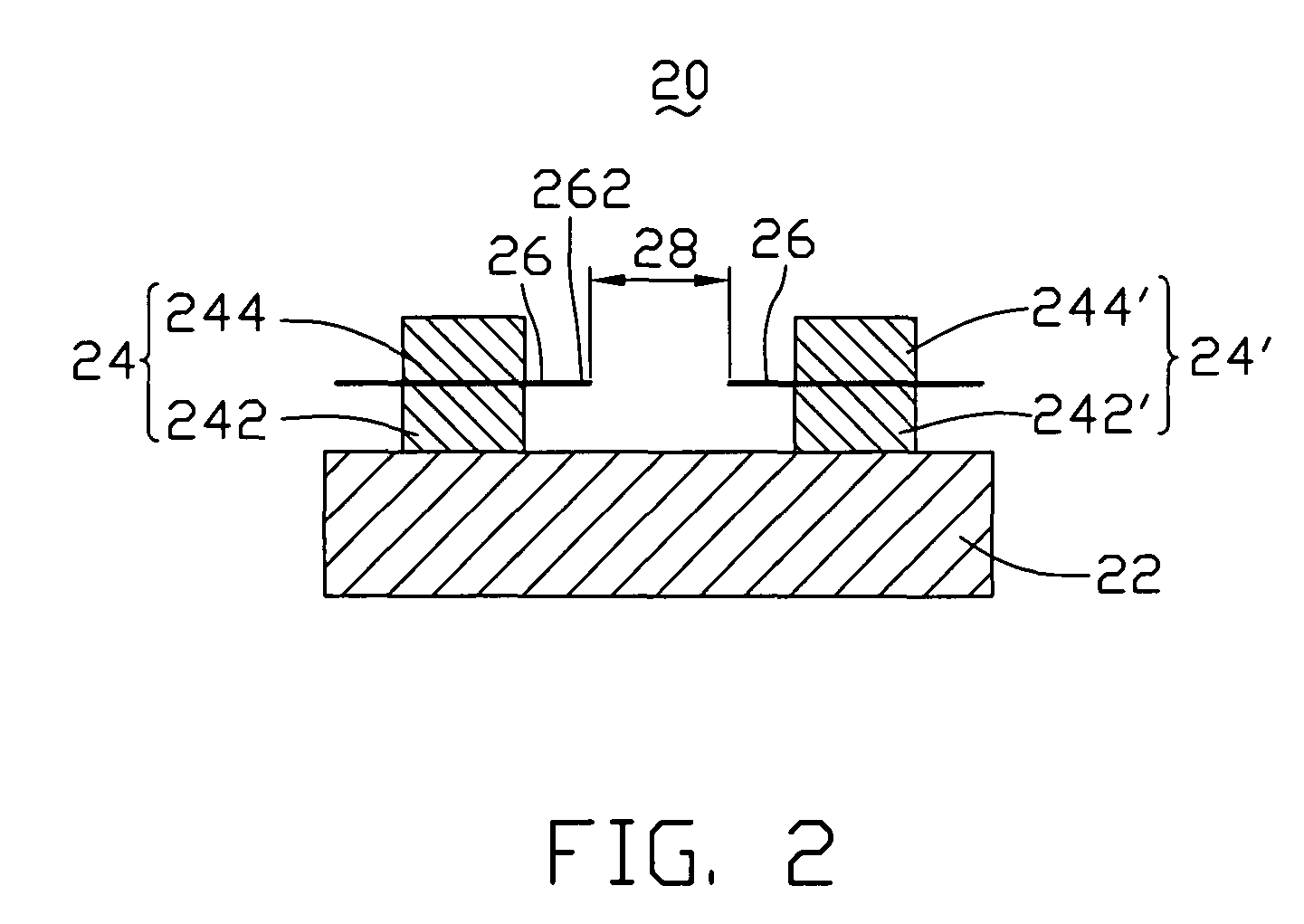

A method for fabricating a surface-conduction electron emitter includes the steps of: (a) providing a substrate; (b) disposing two lower layers on the surface of the substrate, the two lower layers are parallel and apart from each other; (c) disposing a plurality of carbon nanotube elements on the lower layers; (d) disposing two upper layers on the two lower layers, and thereby, sandwiching the carbon nanotube elements therebetween; and (e) forming a micro-fissure between the carbon nanotube elements.

Owner:TSINGHUA UNIV +1

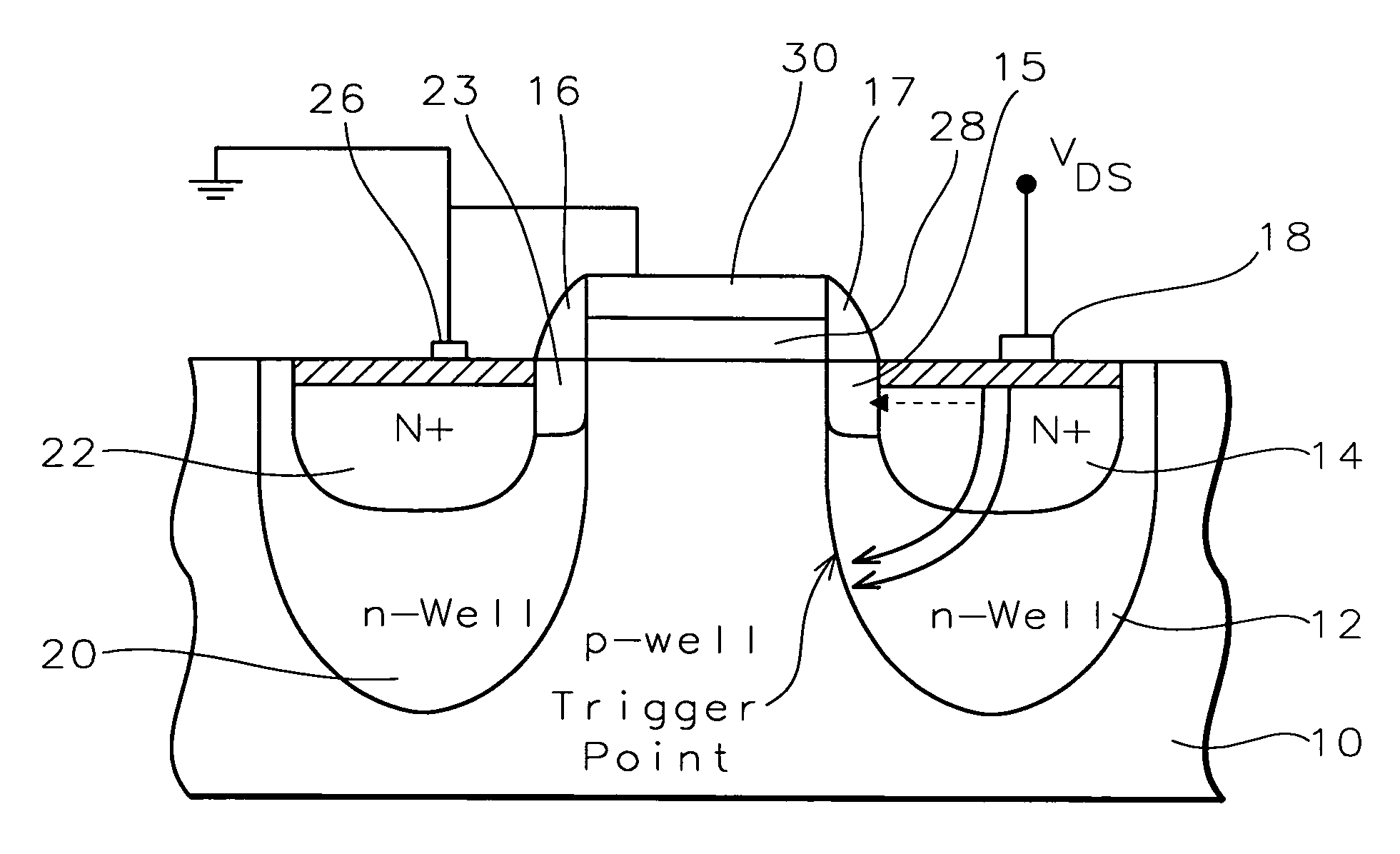

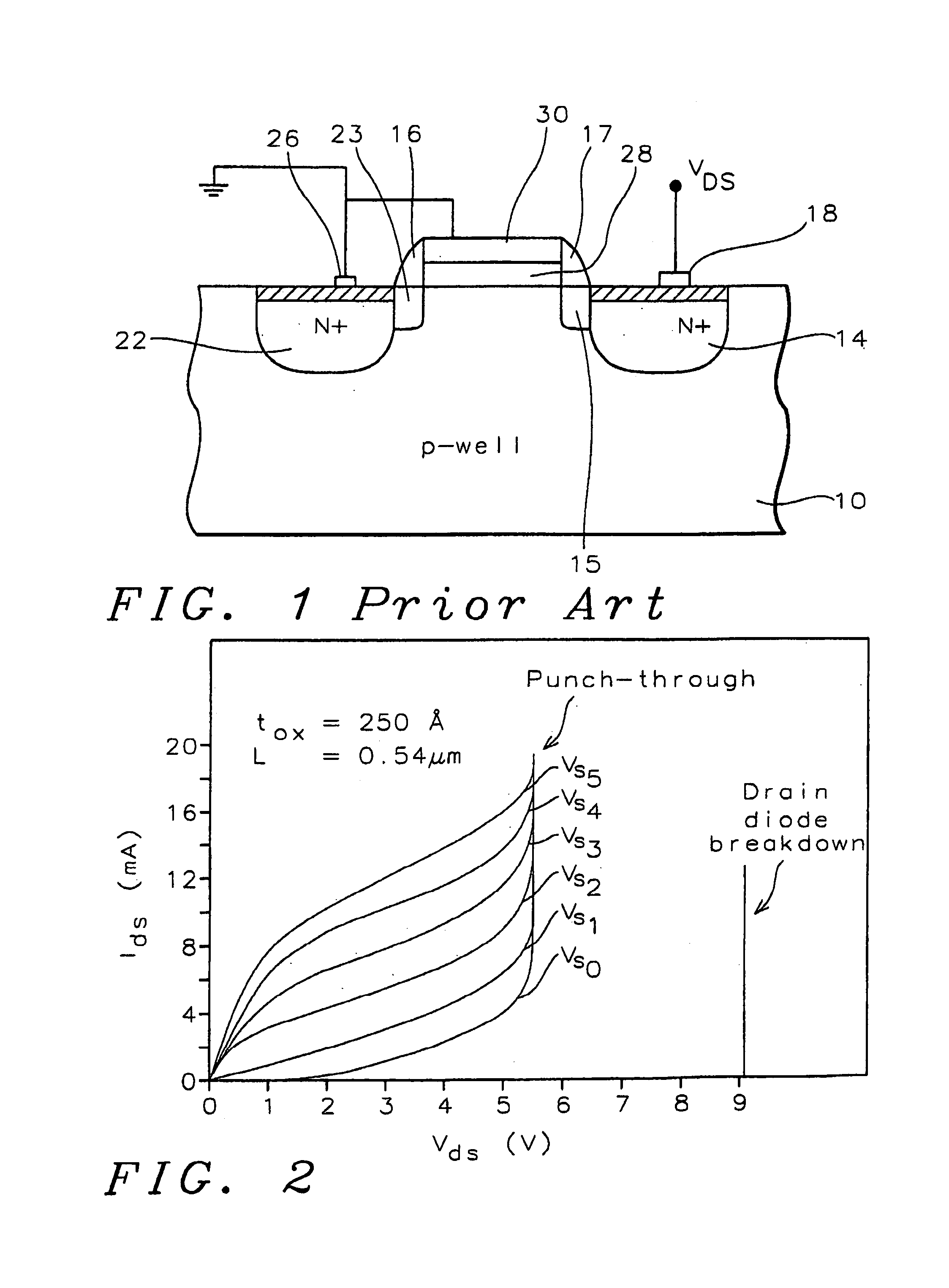

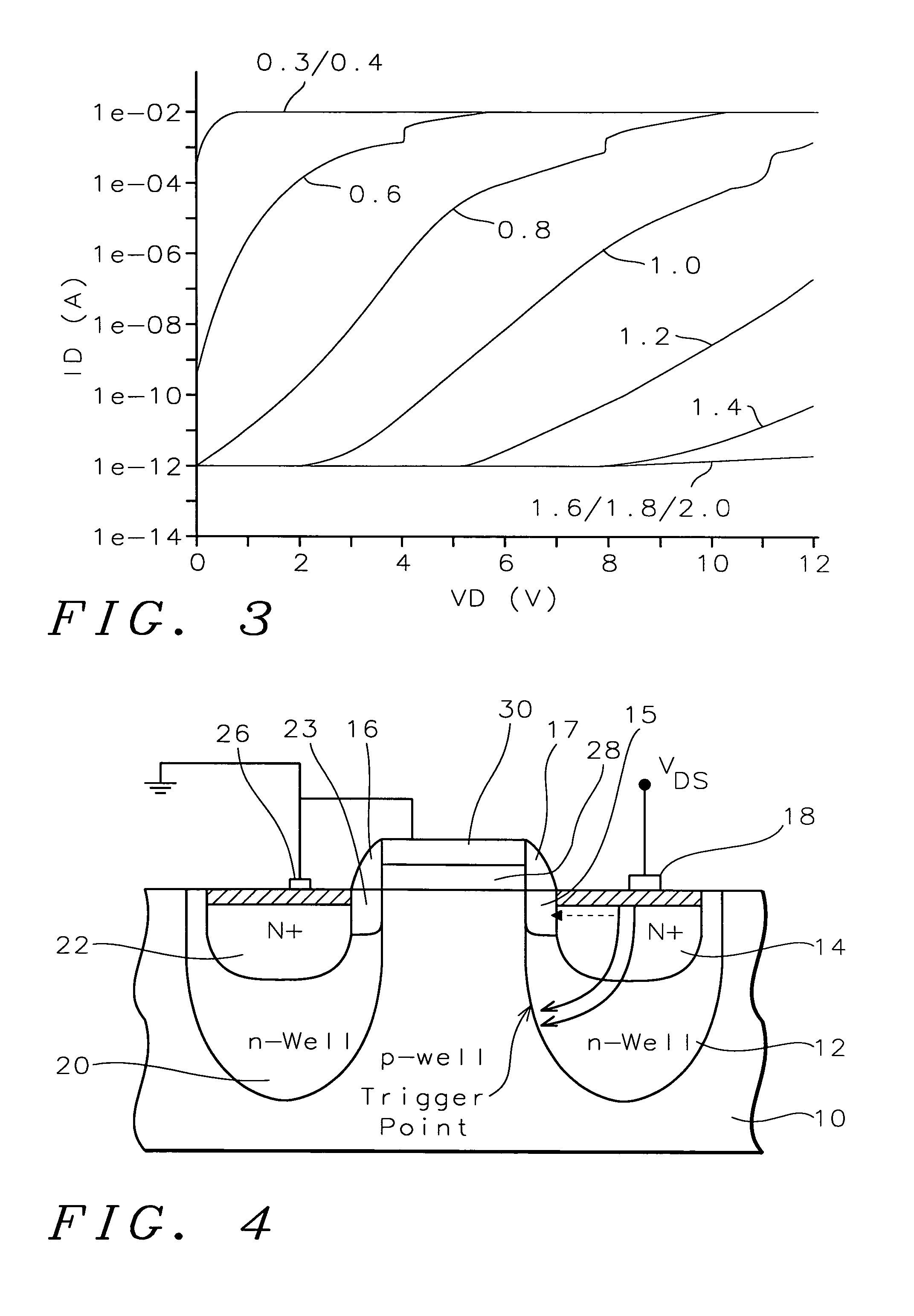

Fully silicided NMOS device for electrostatic discharge protection

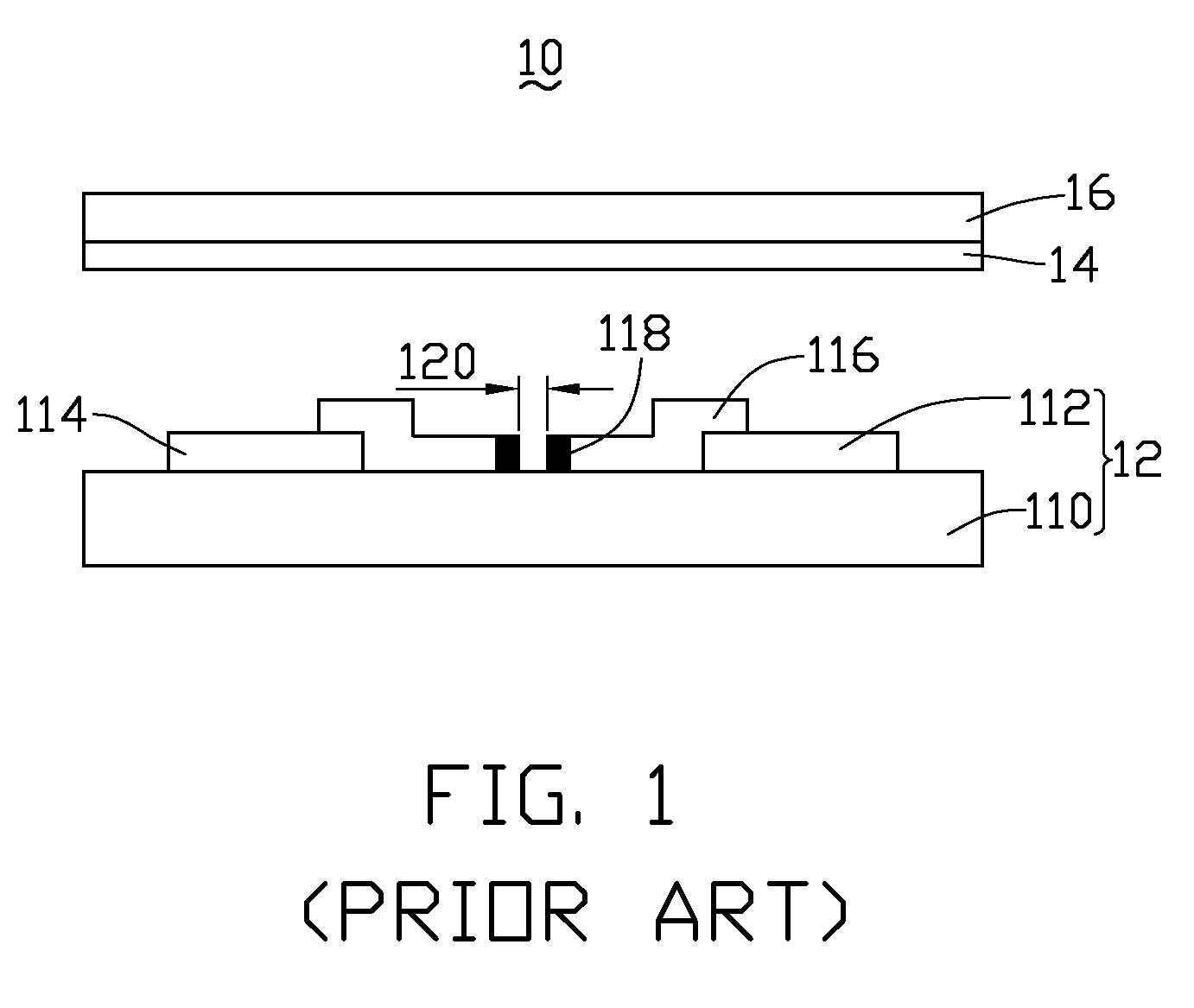

A device and method are described for forming a grounded gate NMOS (GGNMOS) device used to provide protection against electrostatic discharge (ESD) in an integrated circuit (IC). The device is achieved by adding n-wells below the source and drain regions. By tailoring the dopant concentration profiles of the p-well and n-wells provided in the fabrication process, peak dopant concentrations are moved below the silicon surface. This moves ESD conduction deeper into the IC where thermal conductivity is improved, thereby avoiding thermal damage occurring with surface conduction. The device does not require a salicidation block or additional implantation and uses standard NMOS fabrication processing steps, making it advantageous over prior art solutions.

Owner:CHARTERED SEMICONDUCTOR MANUFACTURING

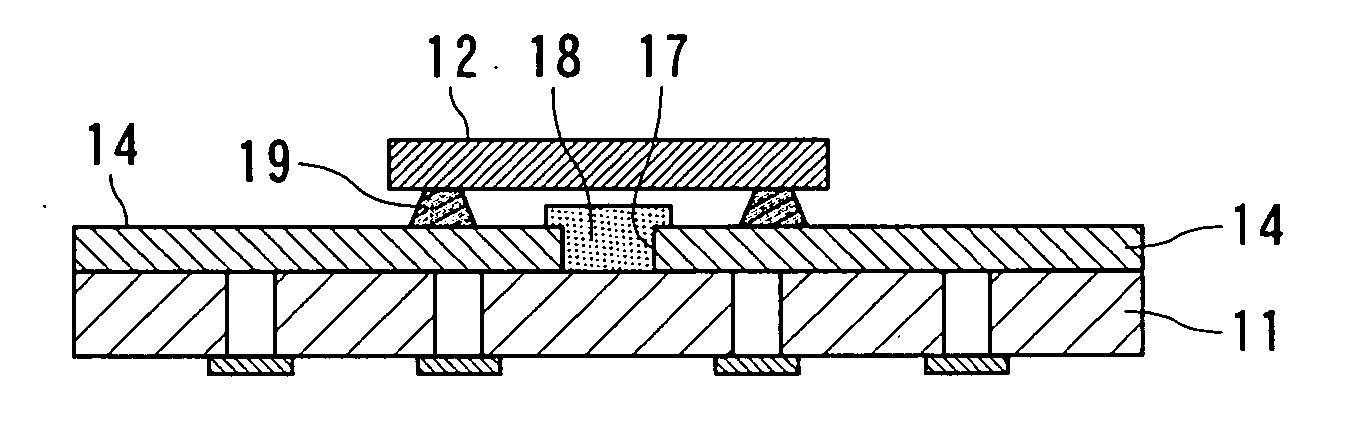

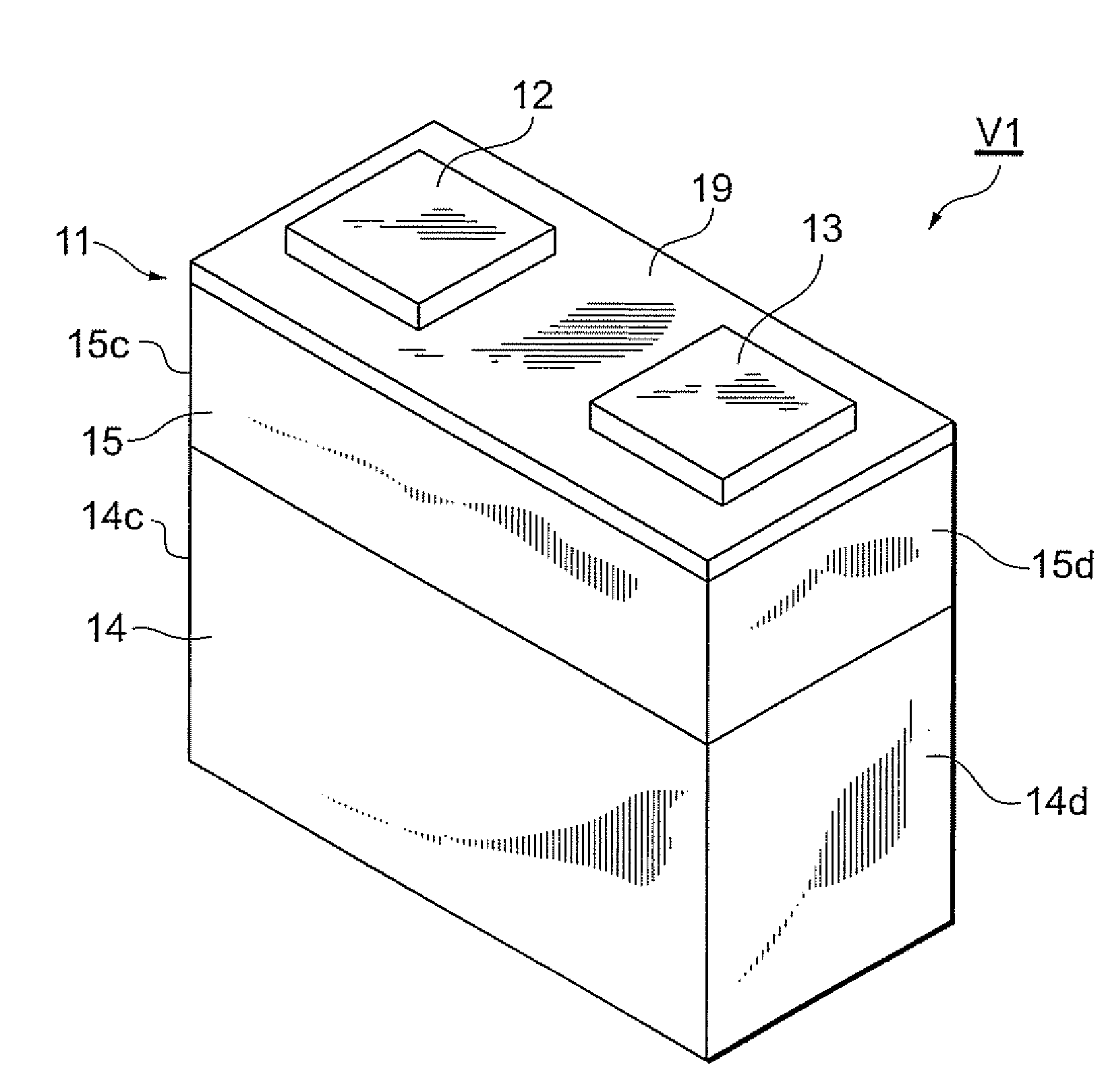

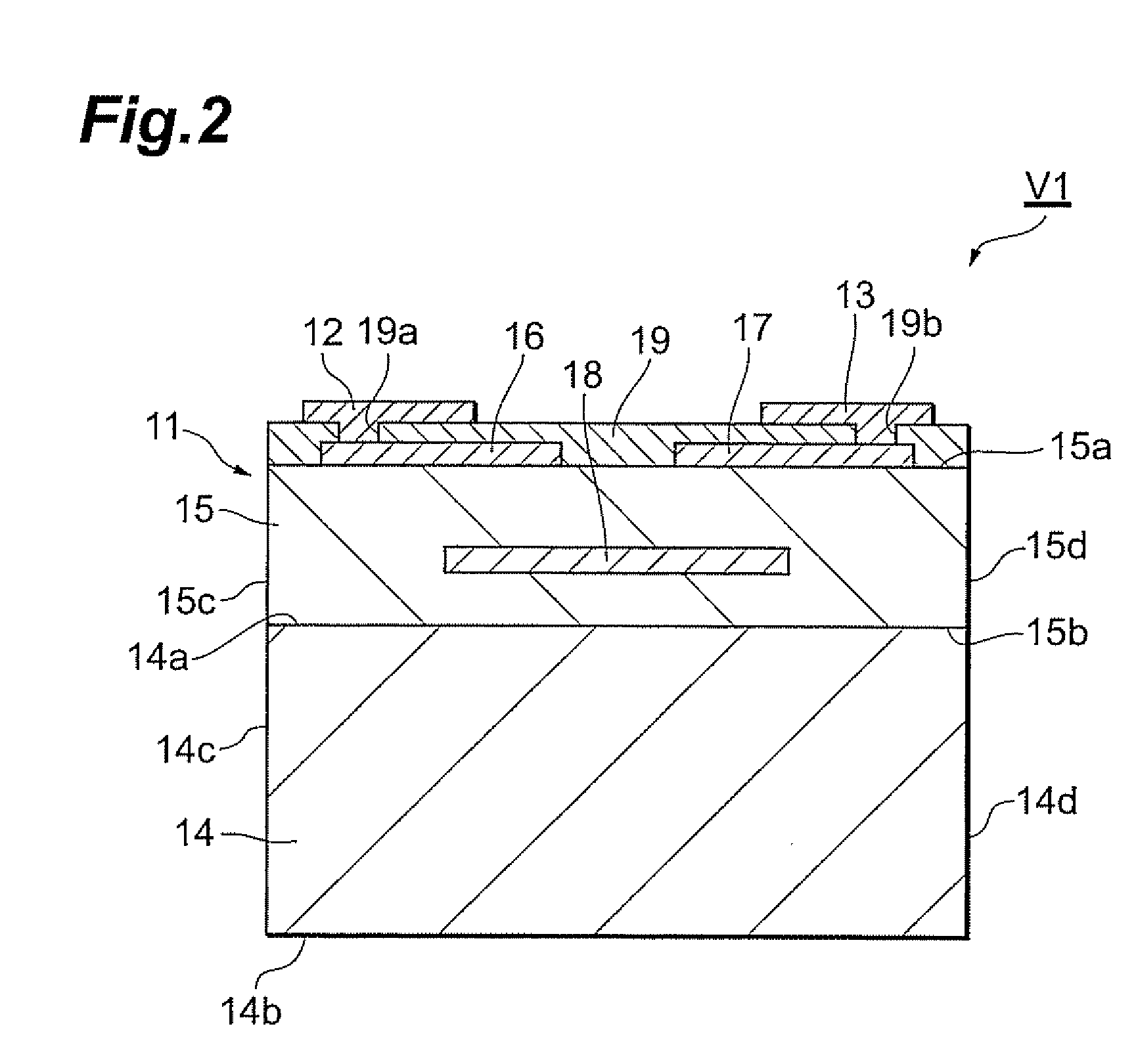

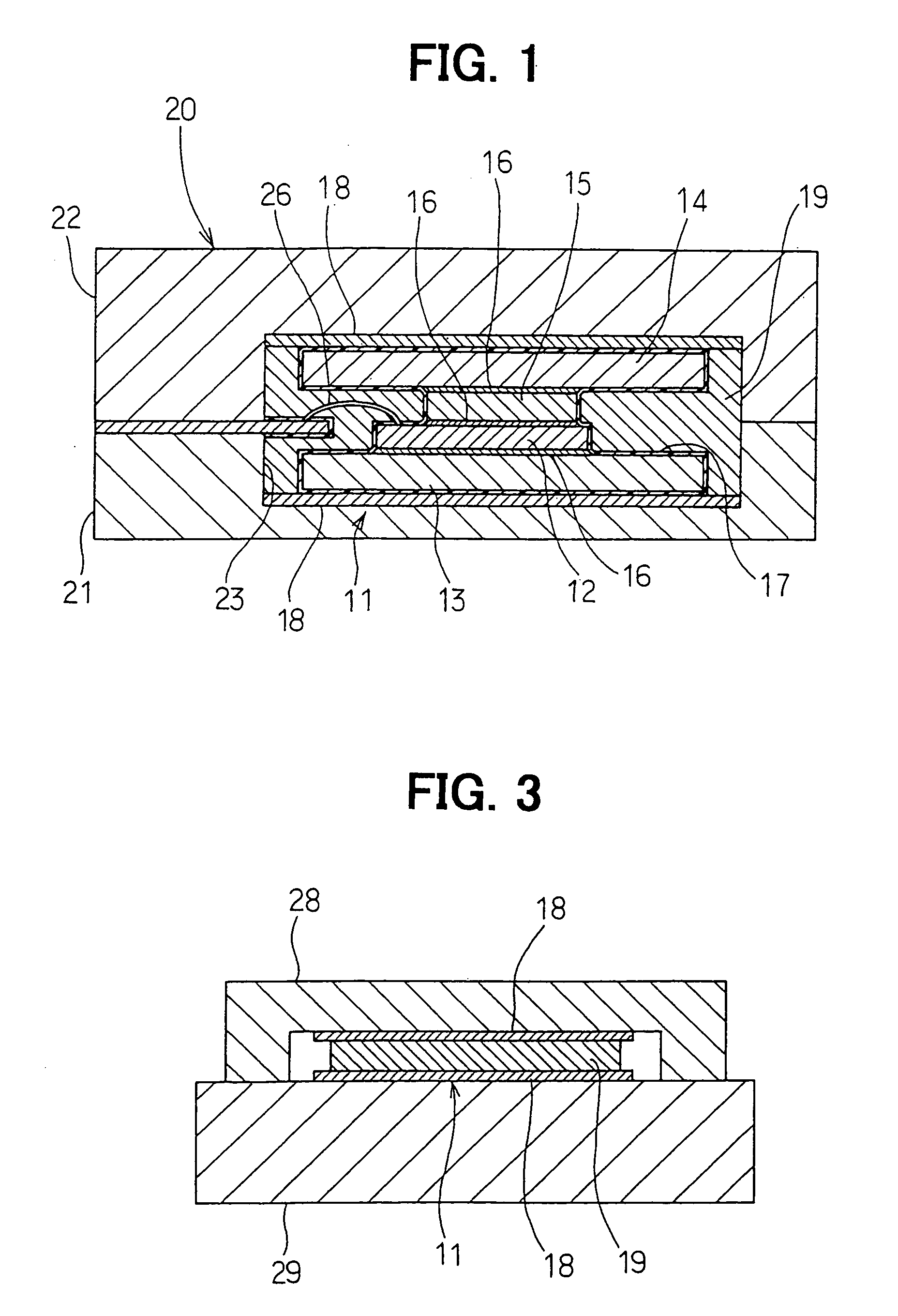

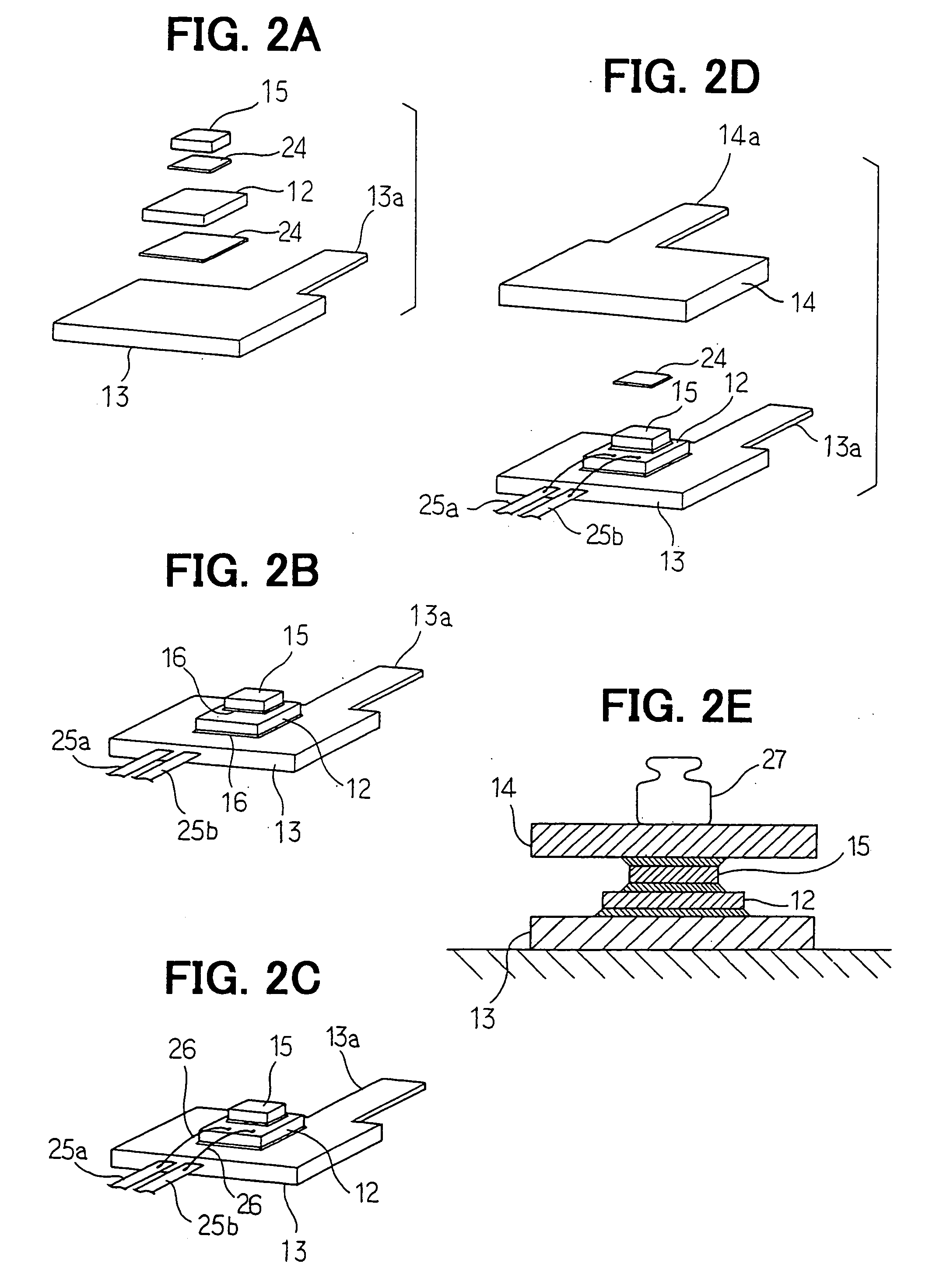

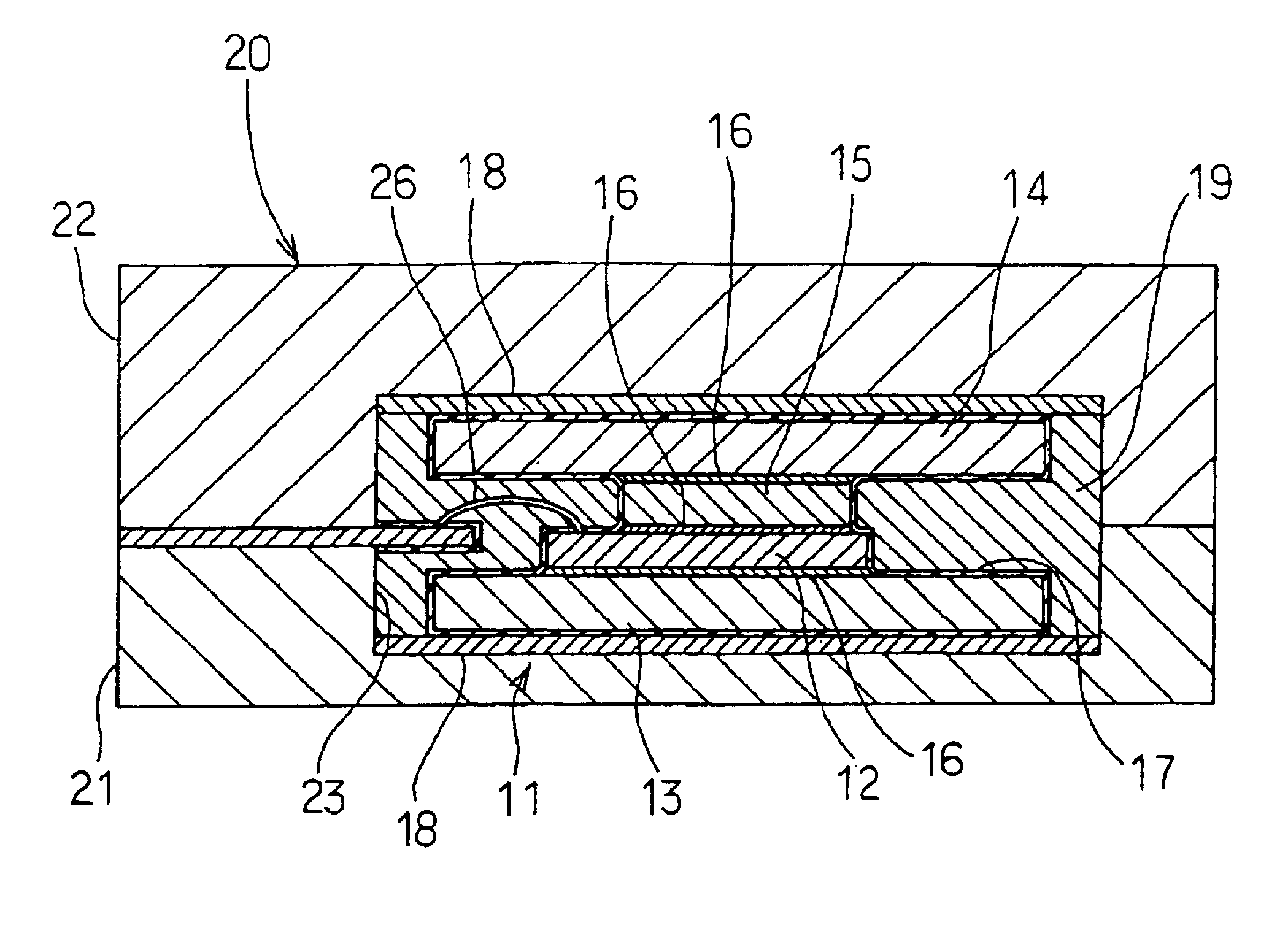

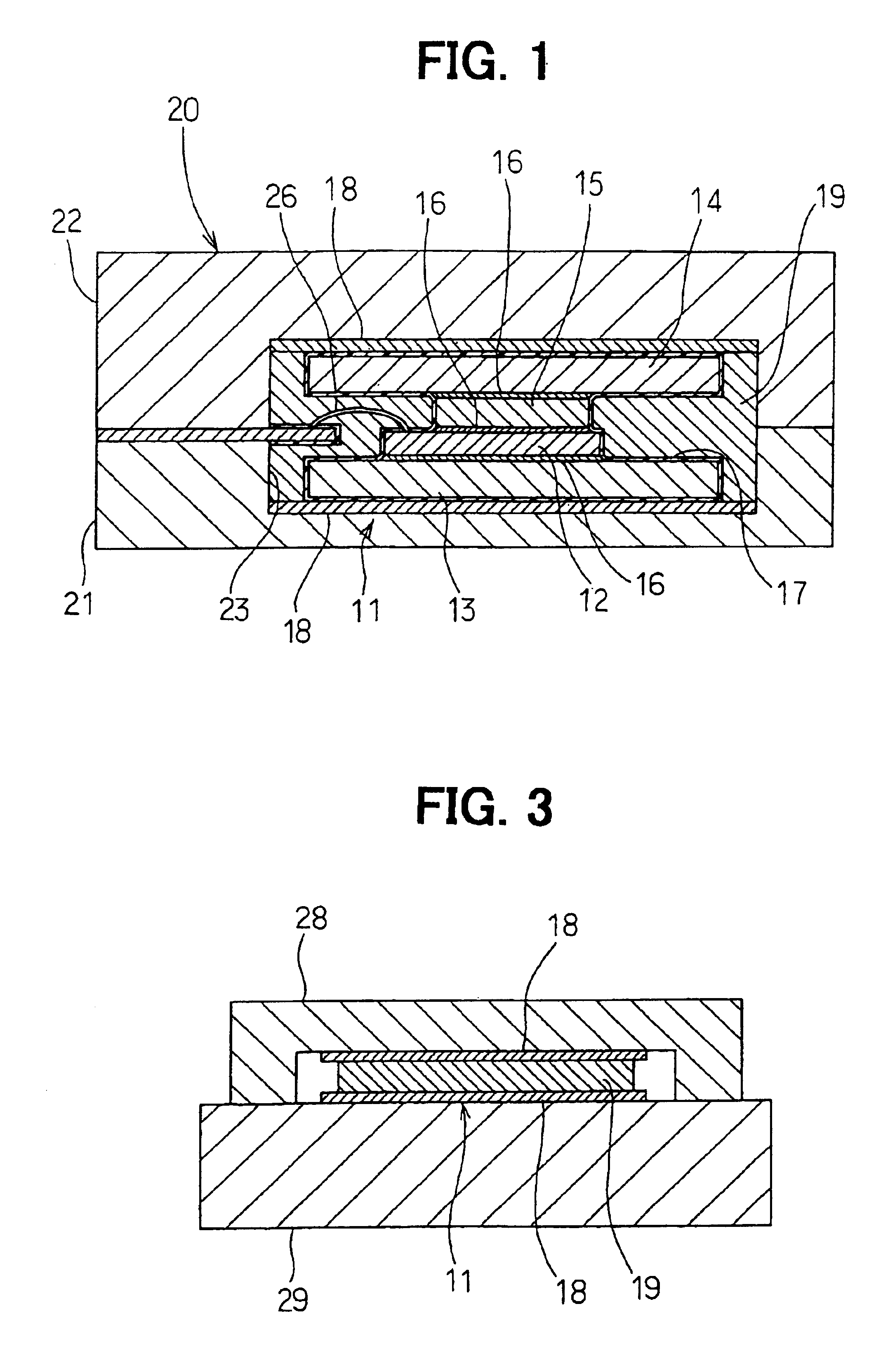

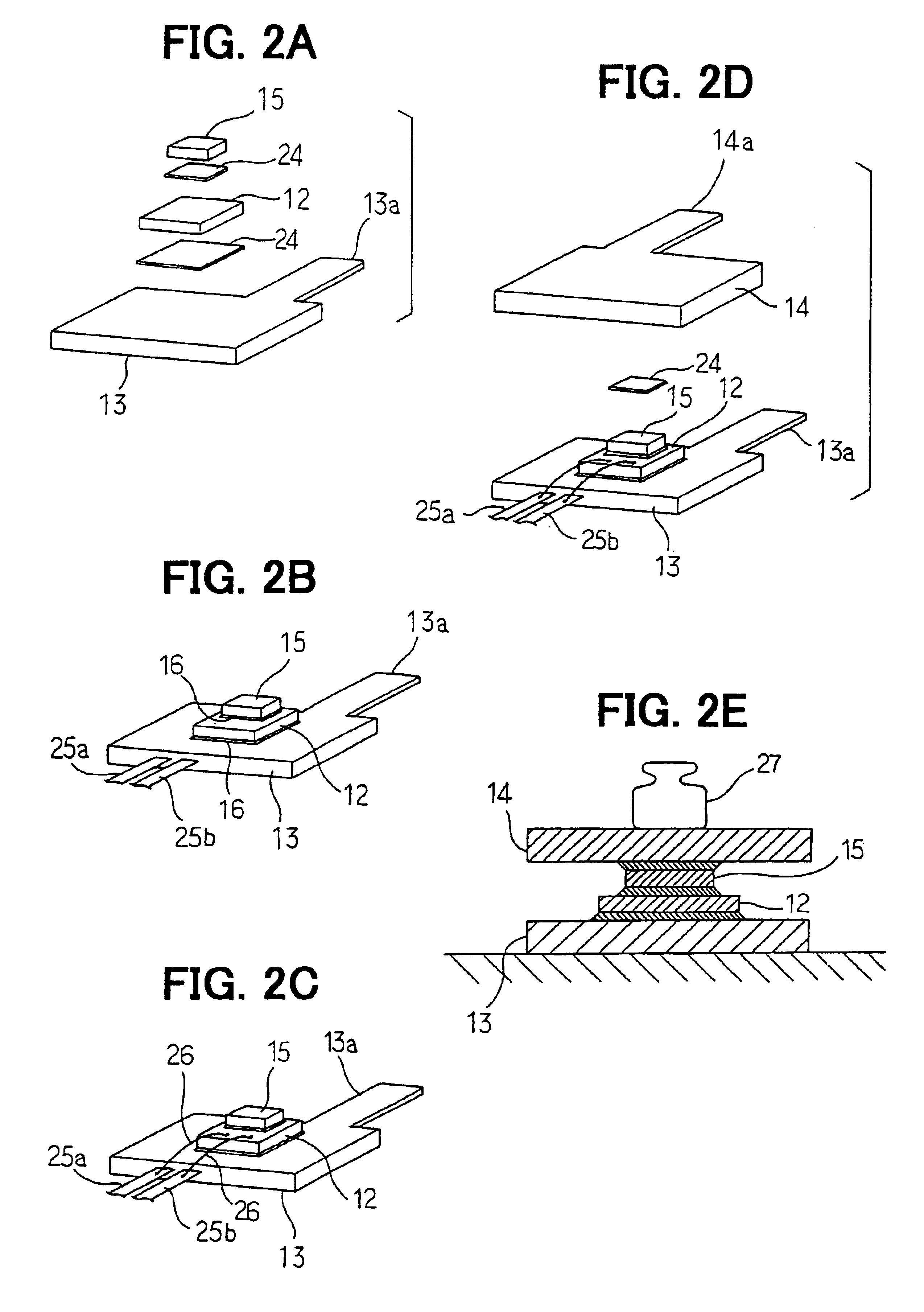

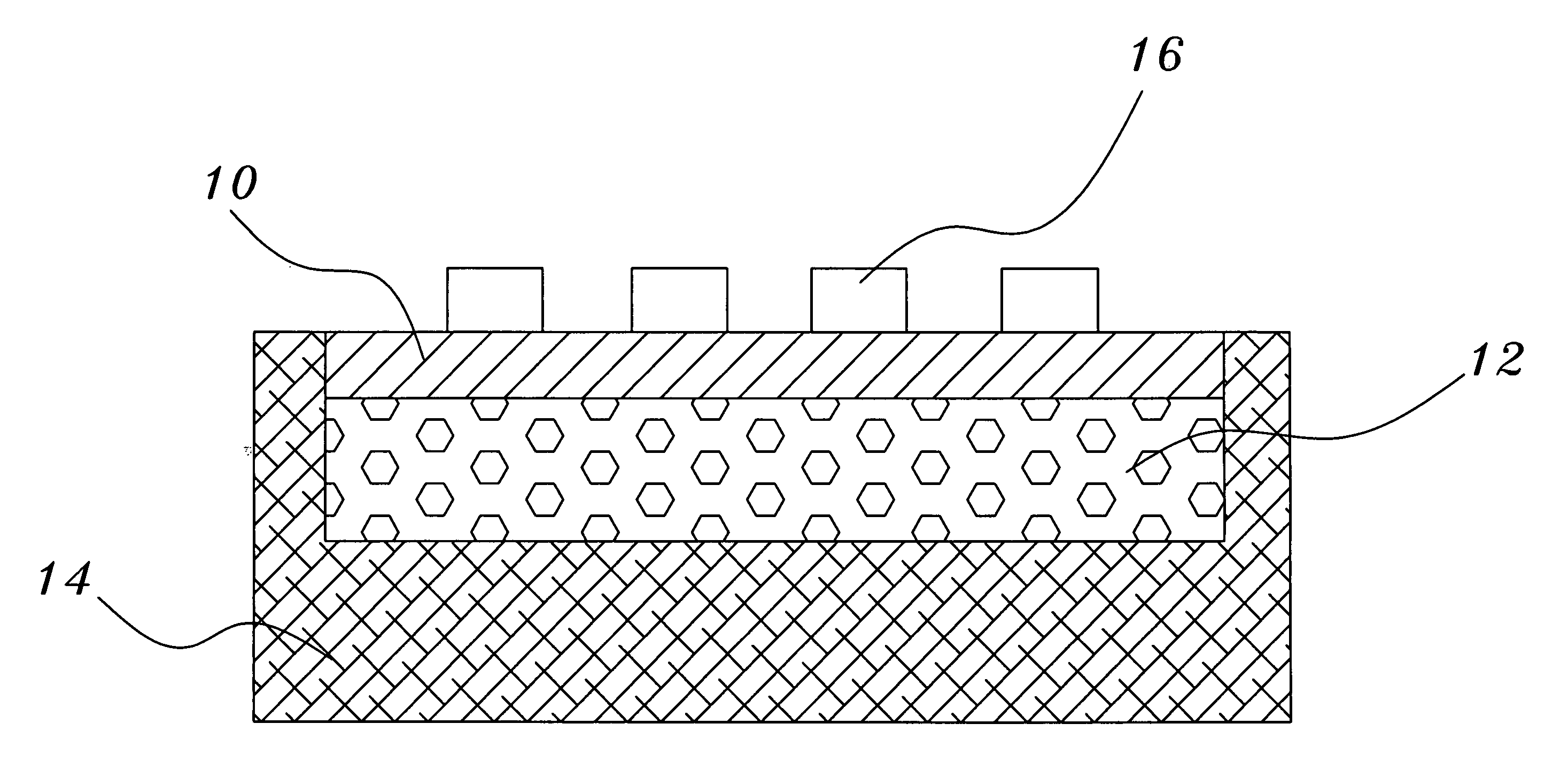

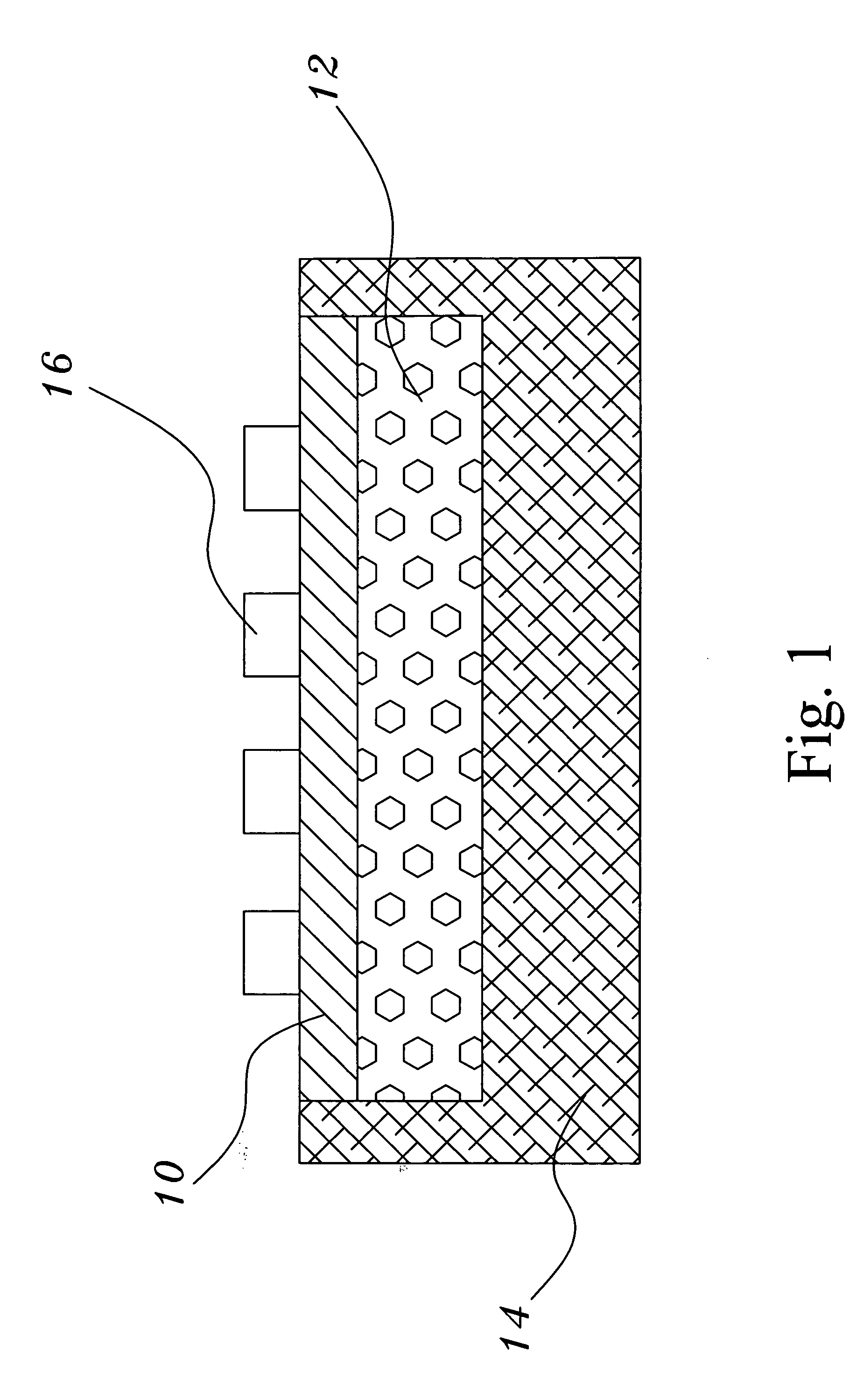

Light Emitting Device

ActiveUS20070200128A1Improve reflectivityIncrease brightnessDischarge tube luminescnet screensSemiconductor/solid-state device detailsGas phaseSurface roughness

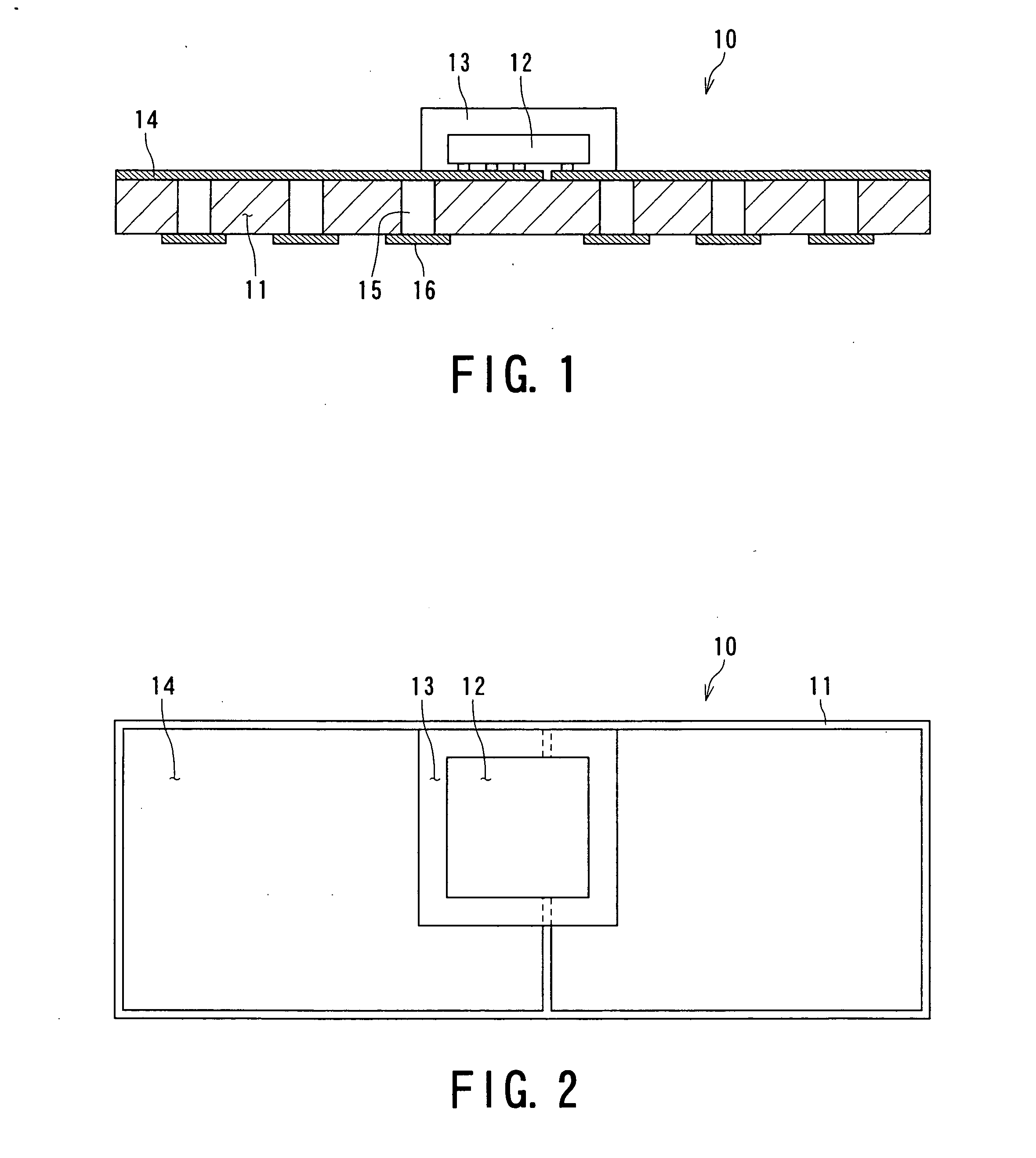

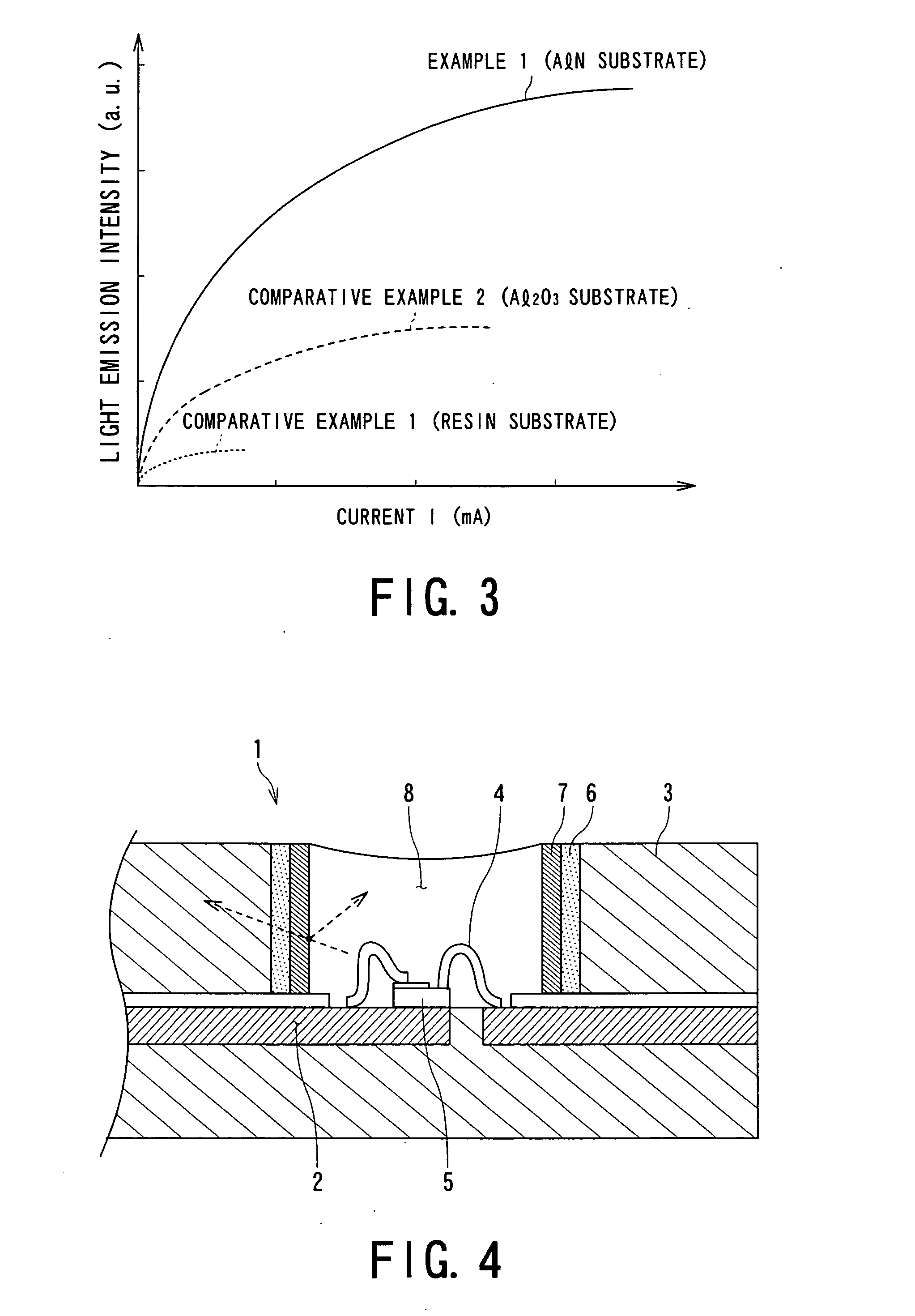

A light emitting apparatus 10 includes an aluminum nitride co-fired substrate 11 and a light emitting device 12 arranged on a front surface of the co-fired substrate, in which the front surface of the aluminum nitride substrate 11 bearing the light emitting device 12 is mirror-polished so as to have a surface roughness of 0.3 μm Ra or less, and the light emitting apparatus 10 further includes a vapor-deposited metal film 14 and via holes 15. The vapor-deposited metal film 14 is arranged on the front surface of the aluminum nitride substrate 11 around the light emitting device 12 and has a reflectivity of 90% or more with respect to light emitted from the light emitting device 12. The via holes 15 penetrates the aluminum nitride substrate 11 from the front surface bearing the light emitting device 12 to the rear surface to thereby allow conduction to the light emitting device 12 from the rear surface. This configuration can reduce light emitting apparatuses in size and can provide light emitting apparatuses that are excellent in heat radiation performance, allow a larger current to pass therethrough, and can have a significantly increased luminance with a high luminous efficiency.

Owner:KK TOSHIBA +1

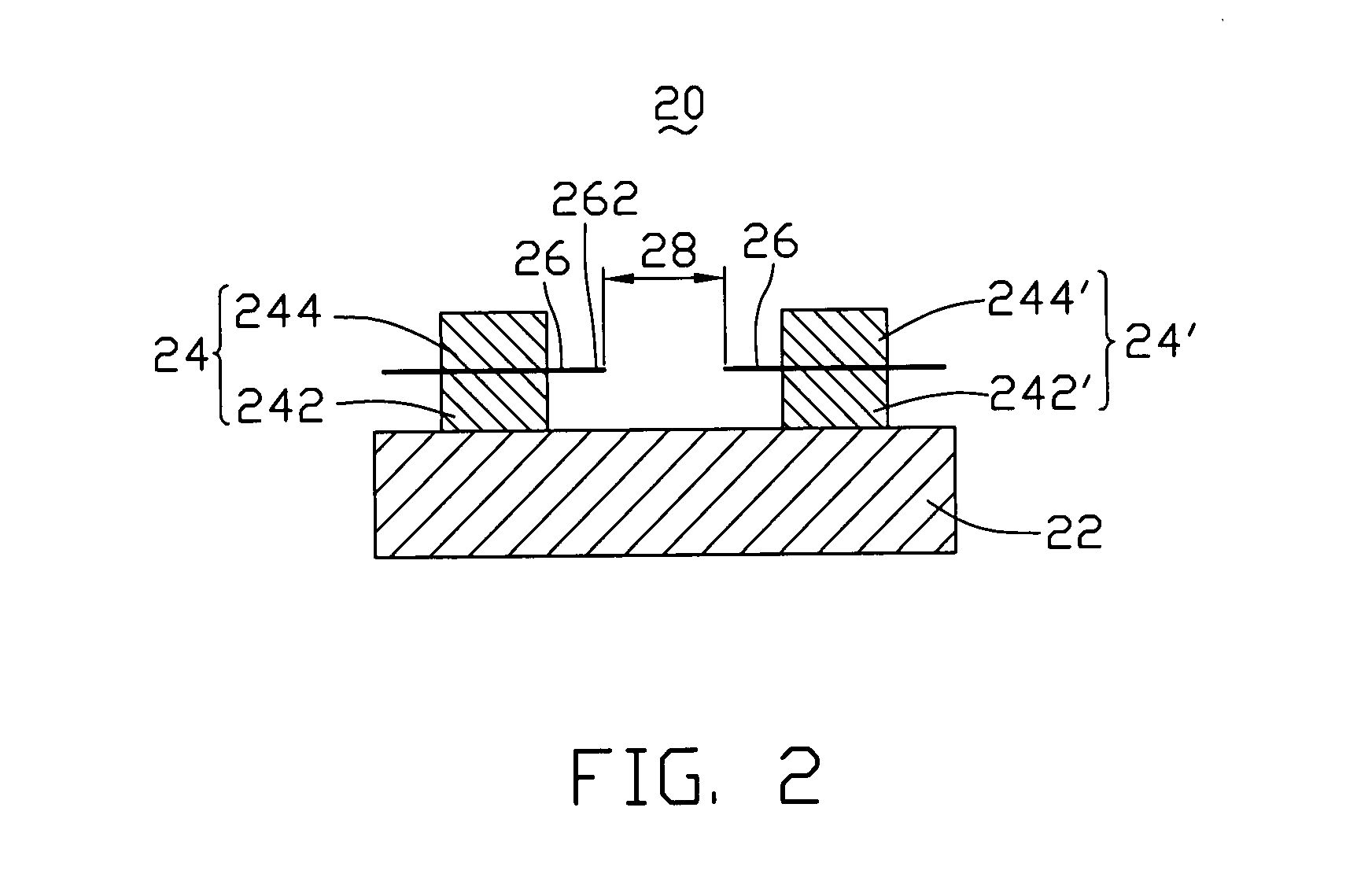

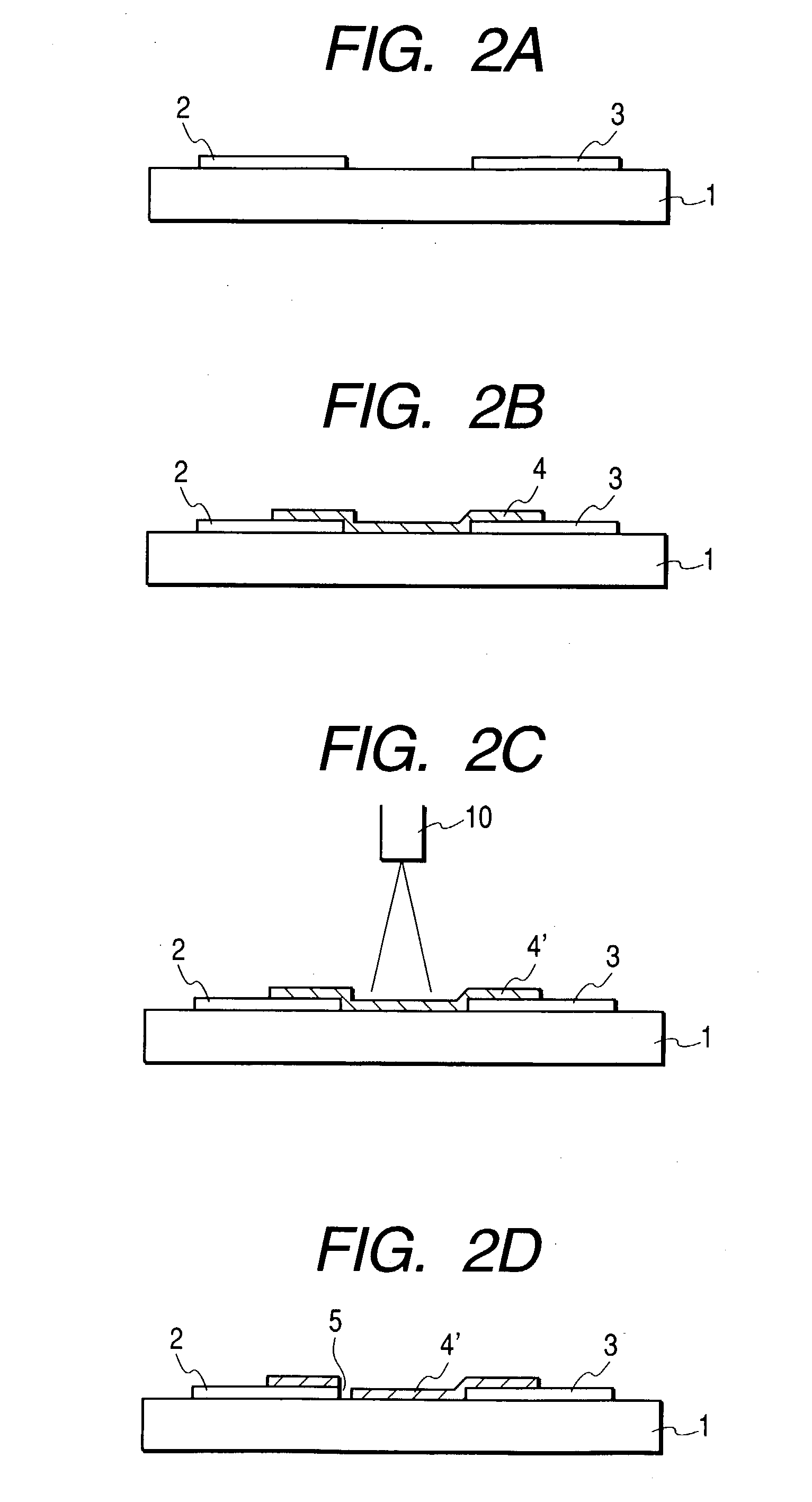

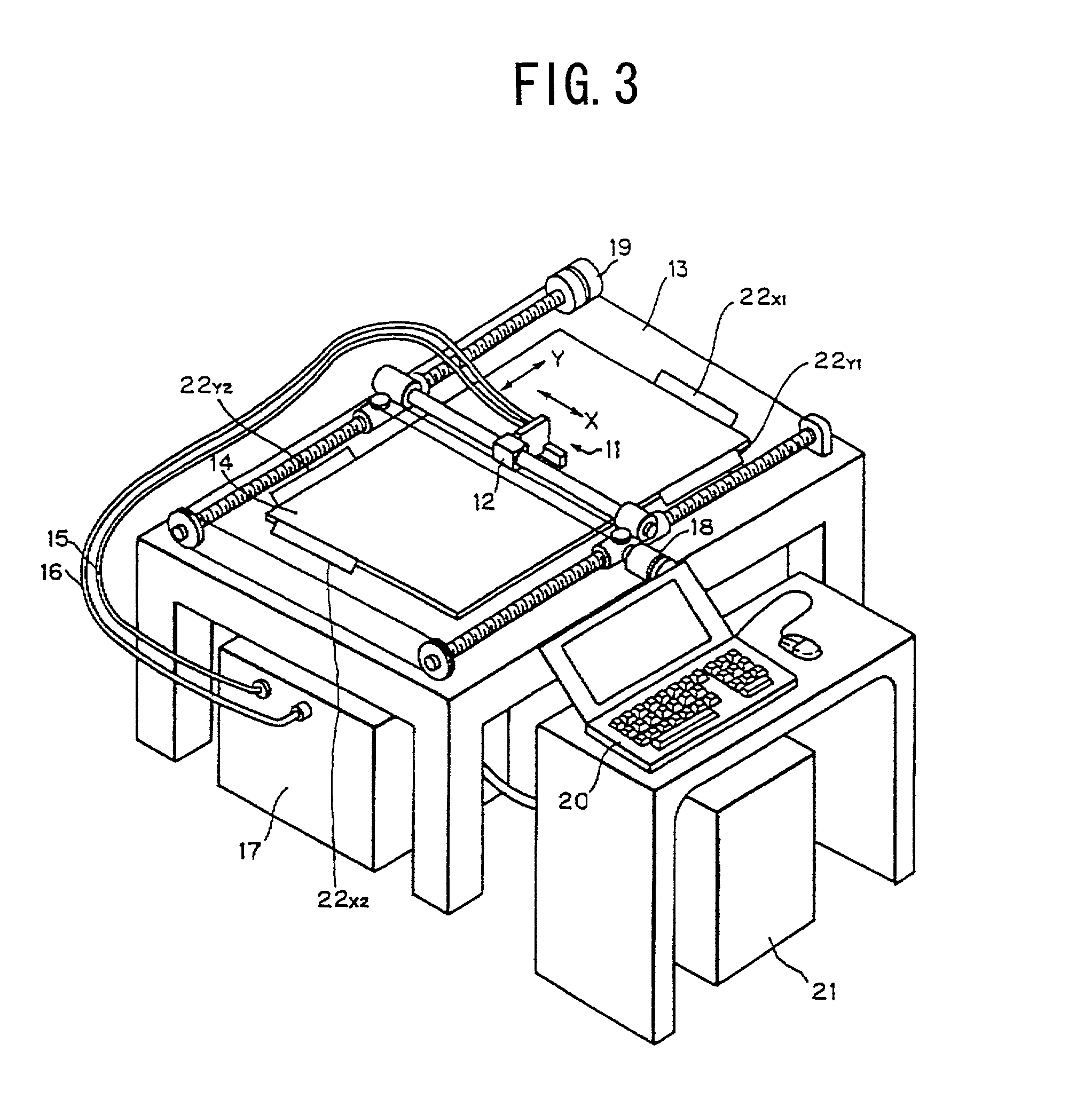

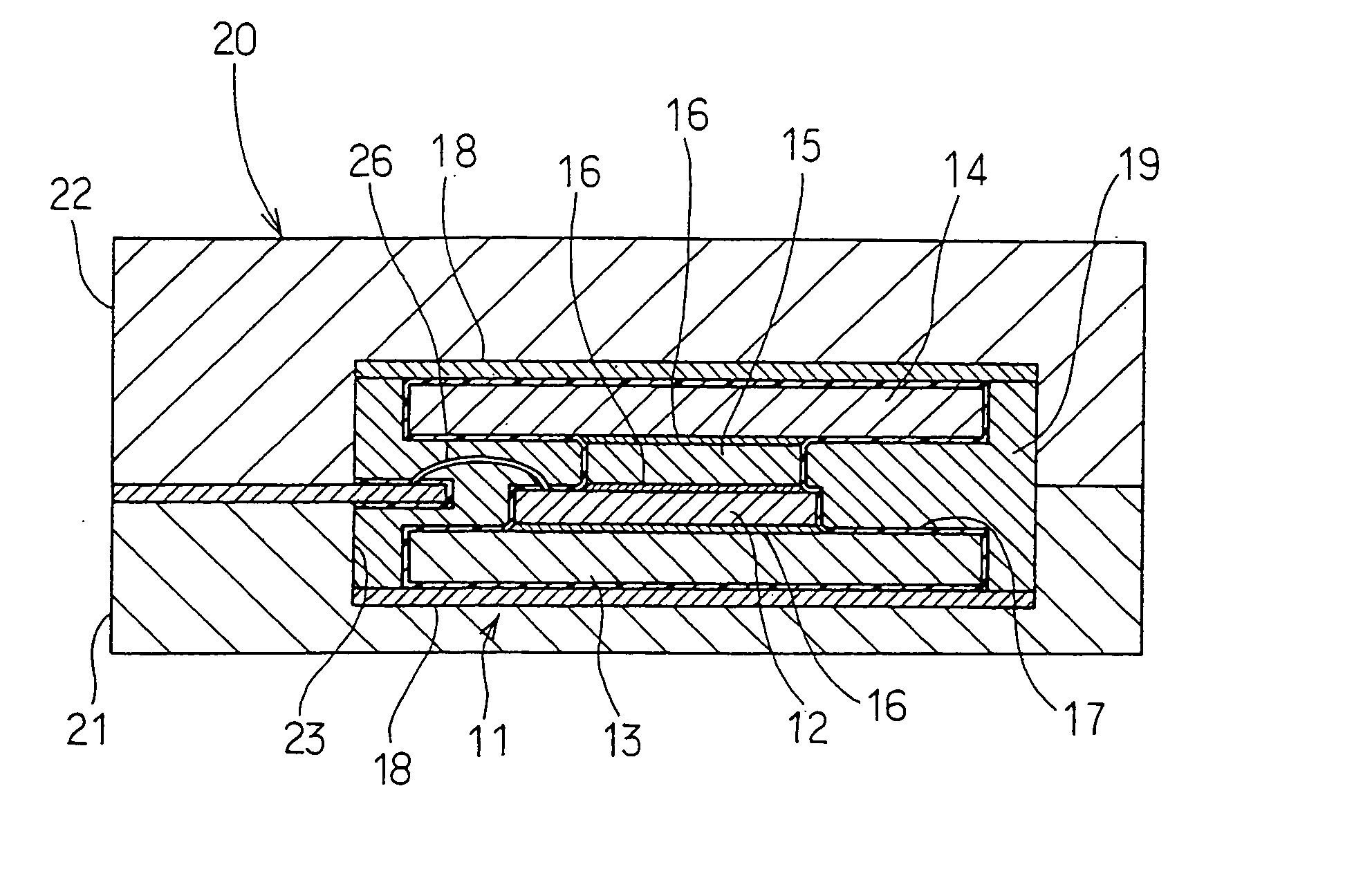

Methods of manufacturing electron-emitting device, electron source, and image display apparatus

InactiveUS6896571B2Save power consumptionImprove featuresSemiconductor/solid-state device manufacturingImage/pattern display tubesElectron sourcePolymer

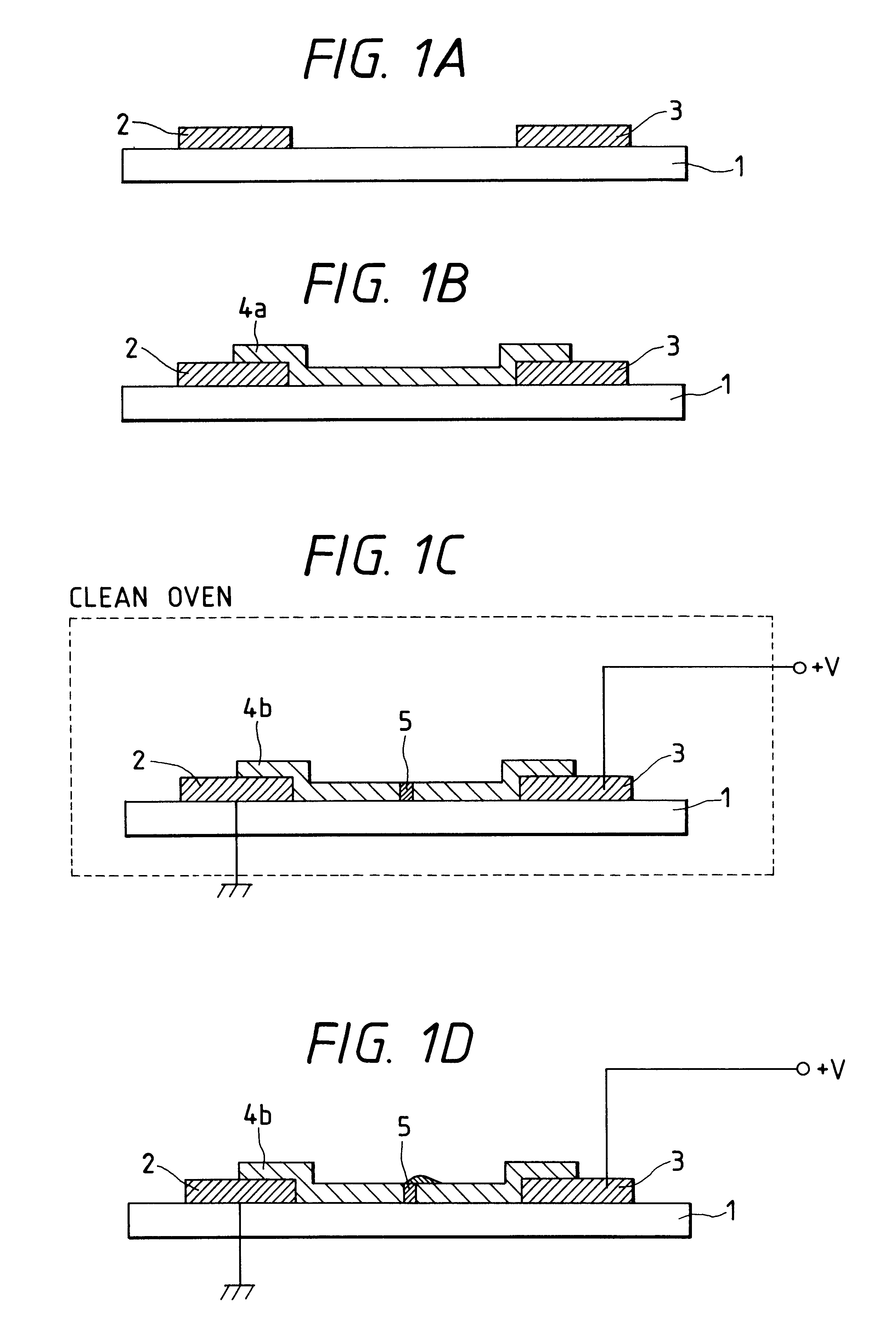

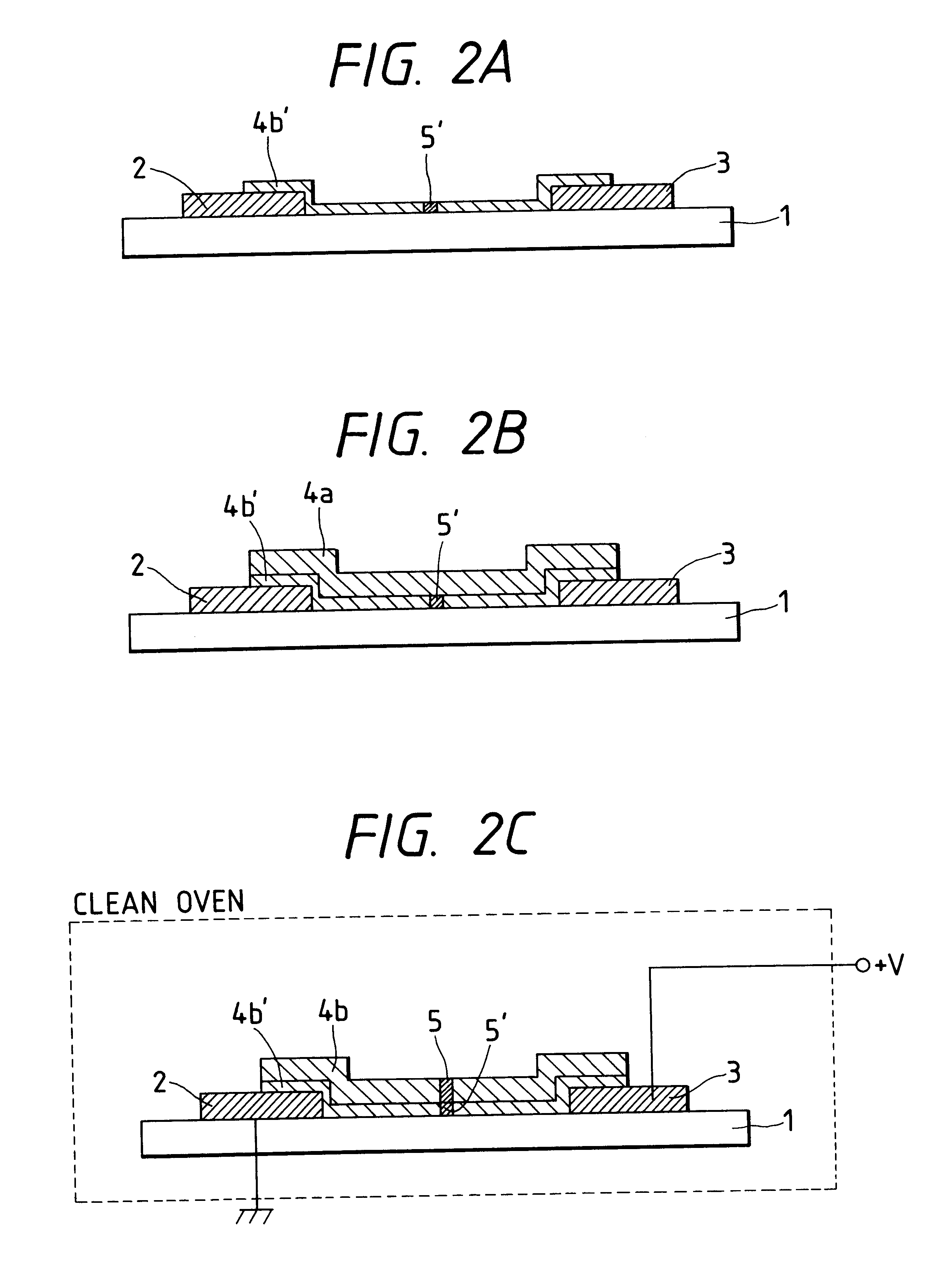

In a process of reducing a resistivity of a polymer film for carbonization in a surface conduction electron-emitting device, by irradiating an energy beam onto the polymer film, when an energy intensity of the beam given in a unit area in a unit time is assumed to be W W / m2, W satisfies a formula W≧2×T×(ρsub·Csub·λsub / τ)1 / 2, where T is defined as a temperature ° C. at which the polymer film is heated for one hour in a vacuum degree of 1×10−4 Pa to reduce a resistivity of the polymer film to 0.1 Ω·cm, Csub is a specific heat J / kg·K of the substrate, ρsub is a specific gravity kg / m3 of the substrate, λsub is a heat conductivity W / m·K of the substrate, and τ is an irradiation time in the range of 10−9 sec to 10 sec.

Owner:CANON KK

Method of manufacturing electron-emitting device, electron source and image-forming apparatus using the same

InactiveUS6334803B1Image/pattern display tubesTube/lamp factory adjustmentElectron sourceDecomposition

A surface conduction electron-emitting device has an electroconductive film including an electron-emitting region between a pair of electrode on a substrate. The electroconductive film is formed by producing a precursor film of an organic metal compound or complex thereof and then turning the precursor film into the electroconductive film by keeping the temperature of the film above the decomposition temperature of the organic metal compound or the complex thereof and applying a voltage to the film. A plurality of such electron-emitting devices are arranged on a substrate in a matrix or ladder-like manner to constitute an electron source. Such an electron source is used with an image-forming member disposed vis-a-vis the electron source to form an image-forming member.

Owner:CANON KK

Linearity improvements of semiconductor substrate using passivation

ActiveUS7915706B1Effectively layerPrevent capacitance changeTransistorSolid-state devicesCapacitanceRelease time

The present invention relates to using a potentially trap-rich layer, such as a polycrystalline Silicon layer, over a passivation region of a semiconductor substrate or a Silicon-on-insulator (SOI) device layer to substantially immobilize a surface conduction layer at the surface of the semiconductor substrate or SOI device layer at radio frequency (RF) frequencies. The potentially trap-rich layer may have a high density of traps that trap carriers from the surface conduction layer. The average release time from the traps may be longer than the period of any present RF signals, thereby effectively immobilizing the surface conduction layer, which may substantially prevent capacitance and inductance changes due to the RF signals. Therefore, harmonic distortion of the RF signals may be significantly reduced or eliminated. The semiconductor substrate may be a Silicon substrate, a Gallium Arsenide substrate, or another substrate.

Owner:QORVO US INC

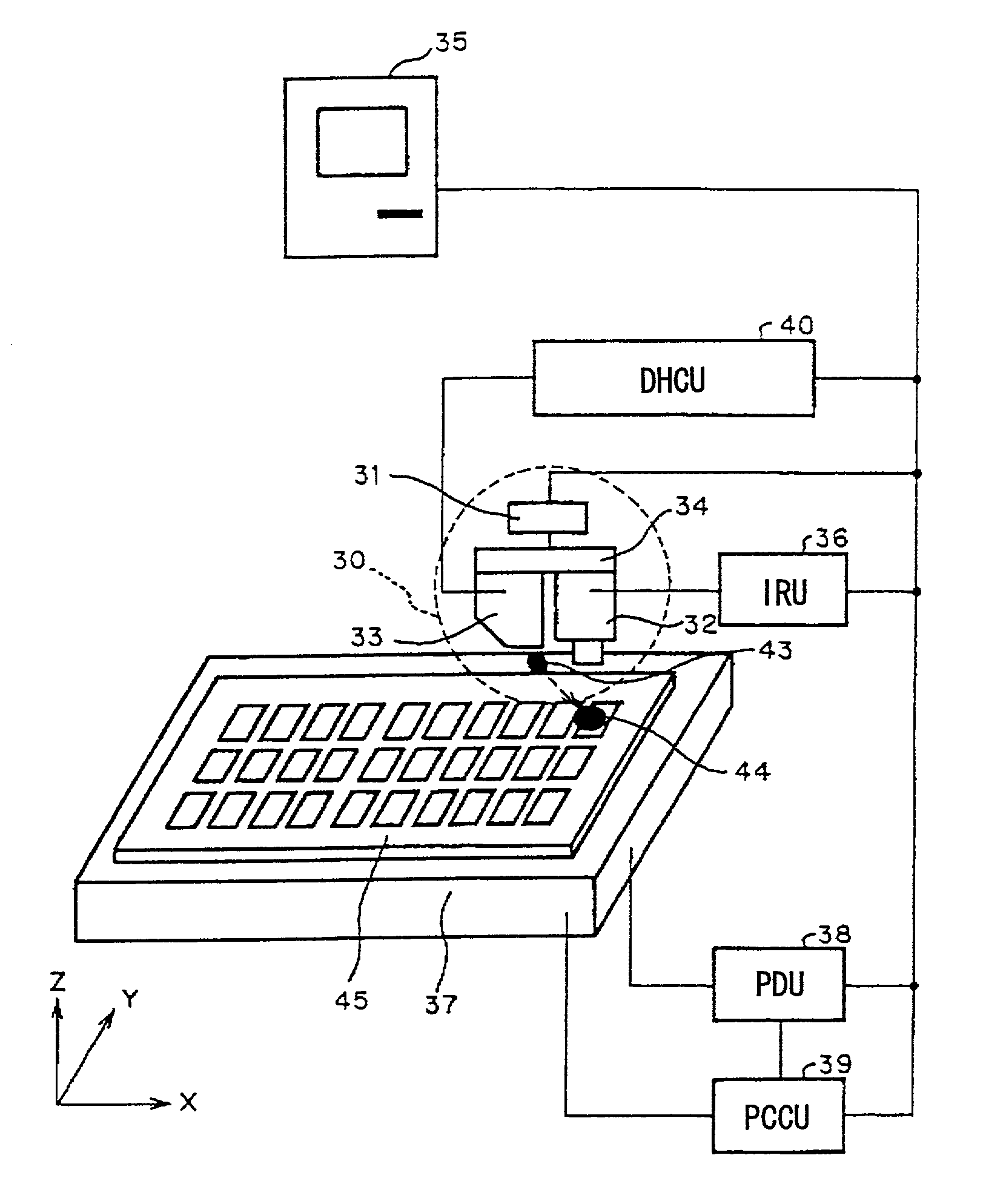

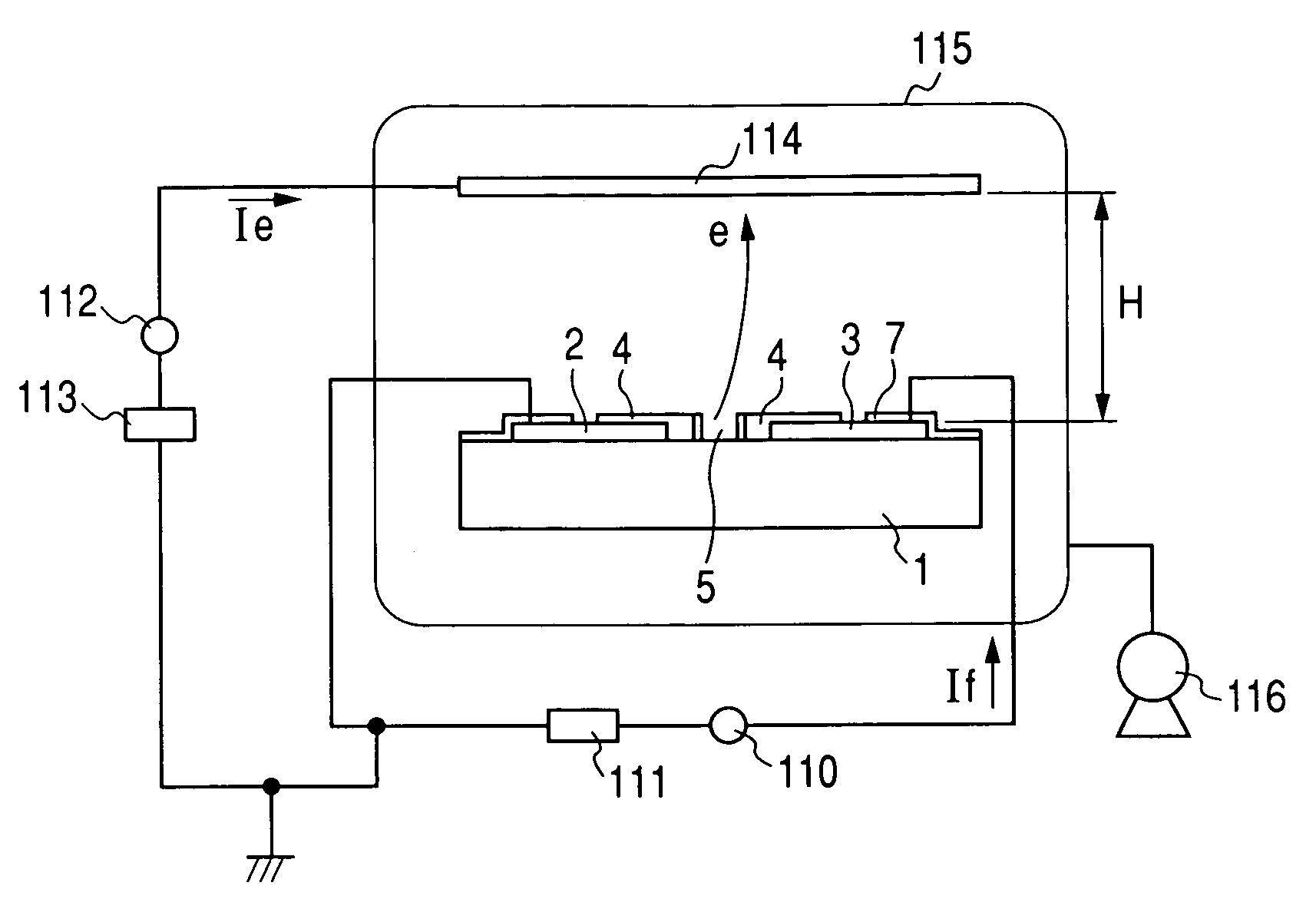

Electron generating apparatus, image forming apparatus, and method of manufacturing and adjusting the same

InactiveUS6144350AStatic indicating devicesSemiconductor/solid-state device manufacturingBeam sourceVoltage shift

Owner:CANON KK

Varistor and light emitting device

InactiveUS20080238604A1High bonding strengthAvoid crackingResistor terminals/electrodesCurrent responsive resistorsElectrical resistance and conductanceThermal radiation

In a varistor, a heat radiating portion contains the same components as ZnO that is the main component of a varistor element body, as metal oxides, thereby, the structural components of the varistor element body and the heat radiating portion are caused to be common. During firing, Ag contained in the heat radiating portion diffuses into the grain boundaries of ZnO, near the interface between surfaces of the heat radiating portion and the varistor element body. Consequently, in the varistor, cracks hardly occur between the varistor portion and the heat radiating portion during firing (or during binder removal), thereby, ensuring sufficient bonding strength between the varistor portion and the heat radiating portion. Therefore, heat conducted to the varistor portion is radiated efficiently conducting through electrically conducted paths formed in the heat radiating portion from the surface facing the varistor element body to other three surfaces of the heat radiating portion.

Owner:TDK CORPARATION

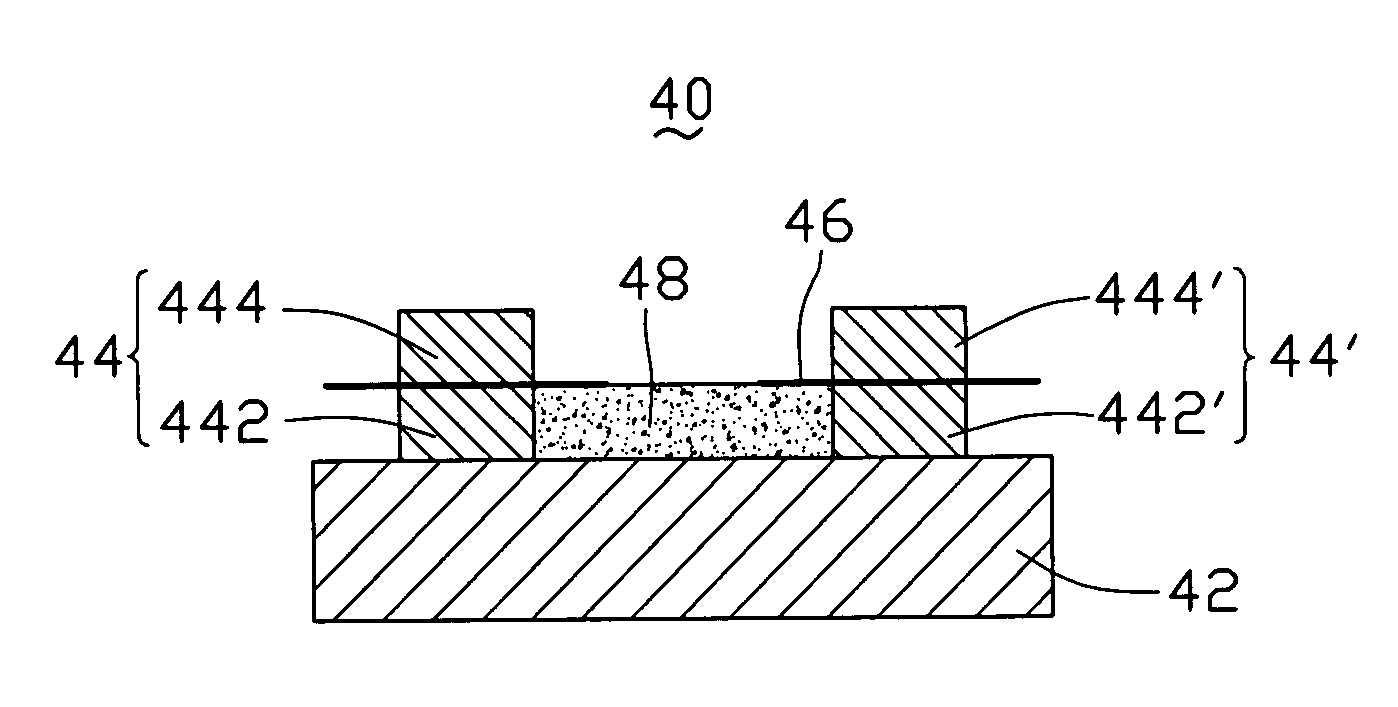

Surface-conduction electron emitter and electron source using the same

ActiveUS20080122335A1Low efficiencyIncadescent body mountings/supportElectrode assembly support/mounting/spacing/insulationElectron sourceCarbon nanotube

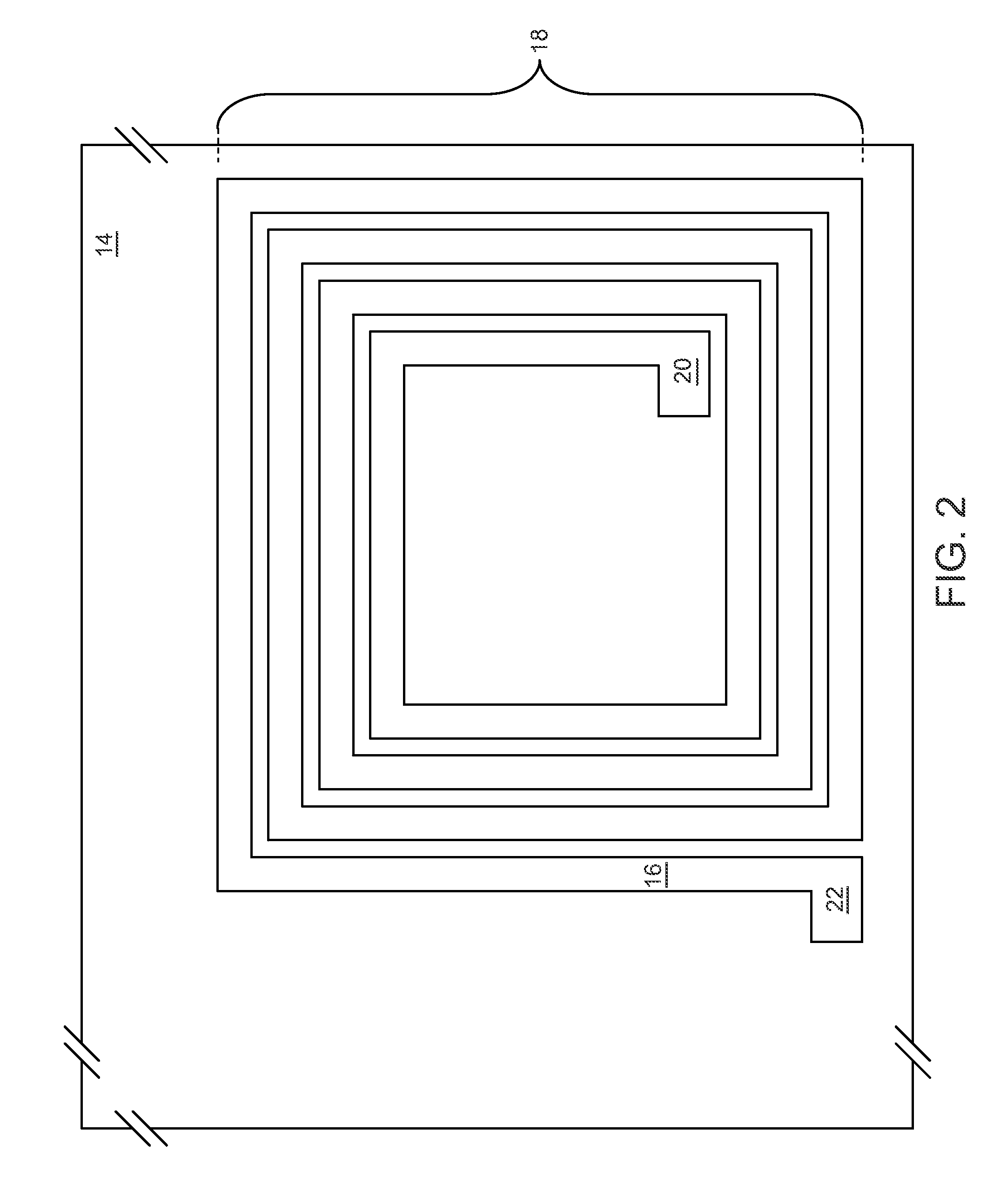

A surface-conduction electron emitter includes a substrate, two electrodes disposed on the substrate and parallel to each other, and a plurality of line-shaped carbon nanotube elements fixed on at least one electrode. One end of each carbon nanotube element points to the other electrode. An electron source using the surface-conduction electron emitter includes a substrate, a plurality of electrodes disposed on the substrate and parallel to each other, and a plurality of line-shaped carbon nanotube elements fixed on at least one electrode. One end of each carbon nanotube element points to the other electrode.

Owner:TSINGHUA UNIV +1

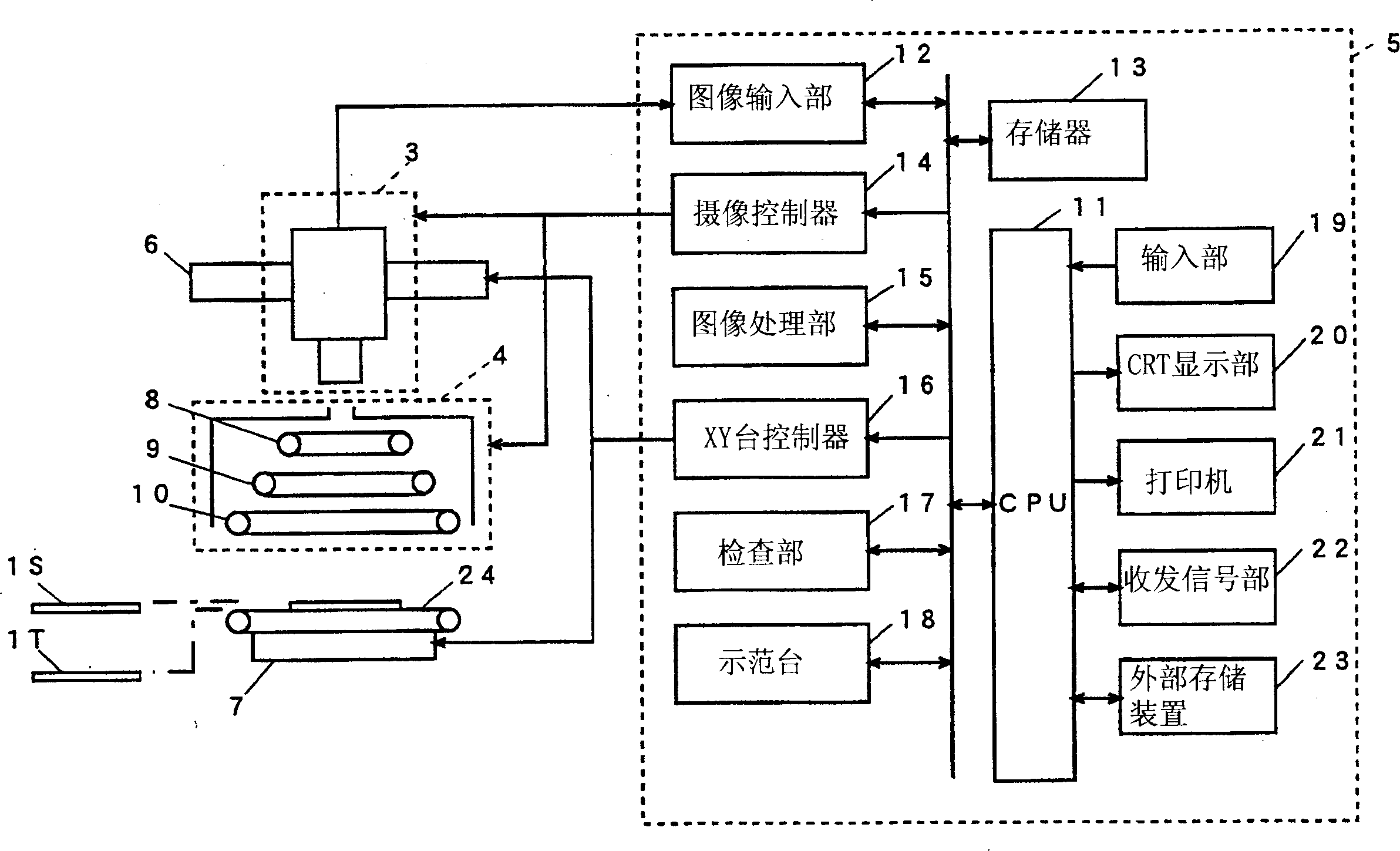

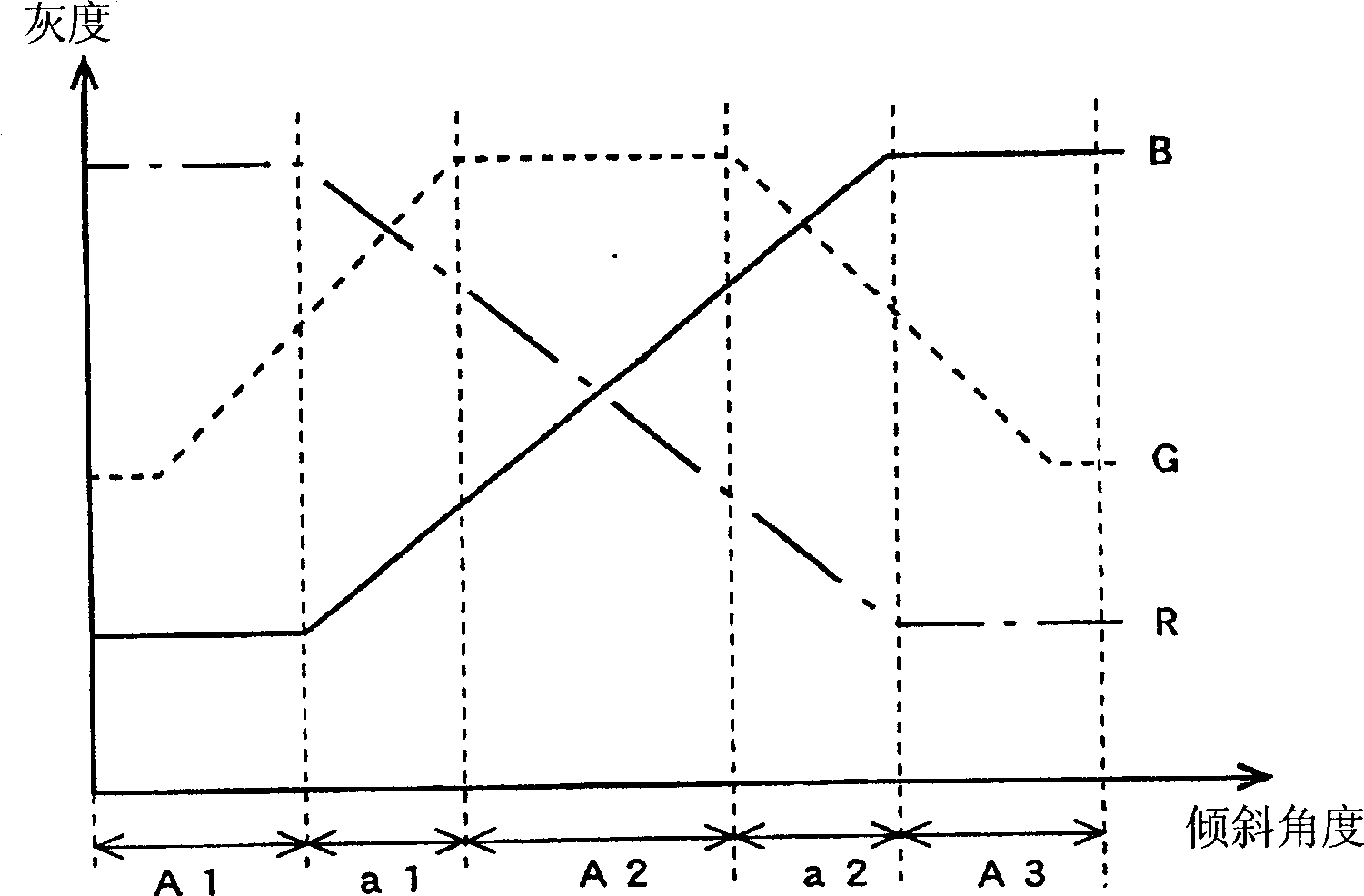

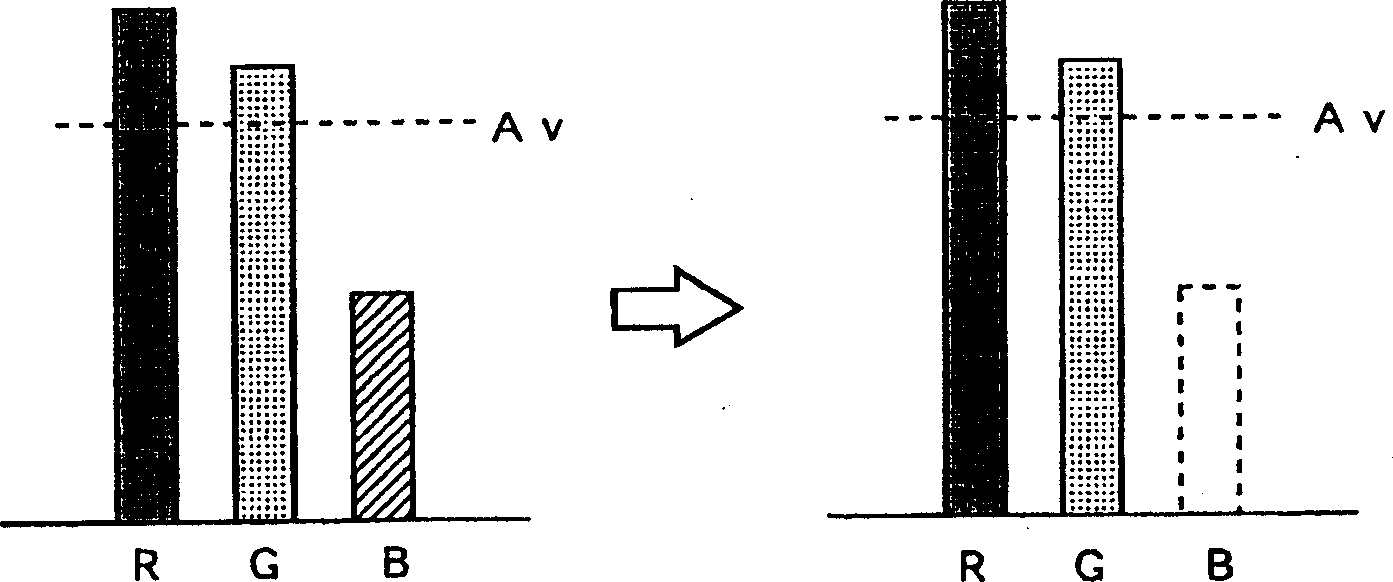

Surface state checking method and circuit board checker

InactiveCN1431482AImprove judgment accuracyImprove performanceRadiation pyrometryColor measuring devicesState of artAdditive ingredient

The invention provides a surface conduction examination method and a substrate examination device, using the optical system which is the same as its prior art to promote the tilting angle resolution, thereby enhancing the examination accuracy. A substrate examination device having a light projecting section 4 consisting of the light sources which emits respectively the R, G, B coloring light and are installed respectively in different azimuth directions with respect to the examination region including soldering portion., extracts 1 or 2 color ingredients which have intensity higher than that of average value. The tilting surfaces adapting to each of light sources 8, 9, 10 are converted respectively into a light and shade monochrome red, green and blue image. Further, the tilting surface at boundary position, which a adapts to light sources 8, 9 is converted into a light and shade image having a color mixed with red and green, whereas the tilting surface at boundary position, which adapts to the light sources 9, 10 is converted into a light and shade image having a color mixed with green and blue.

Owner:ORMON CORP

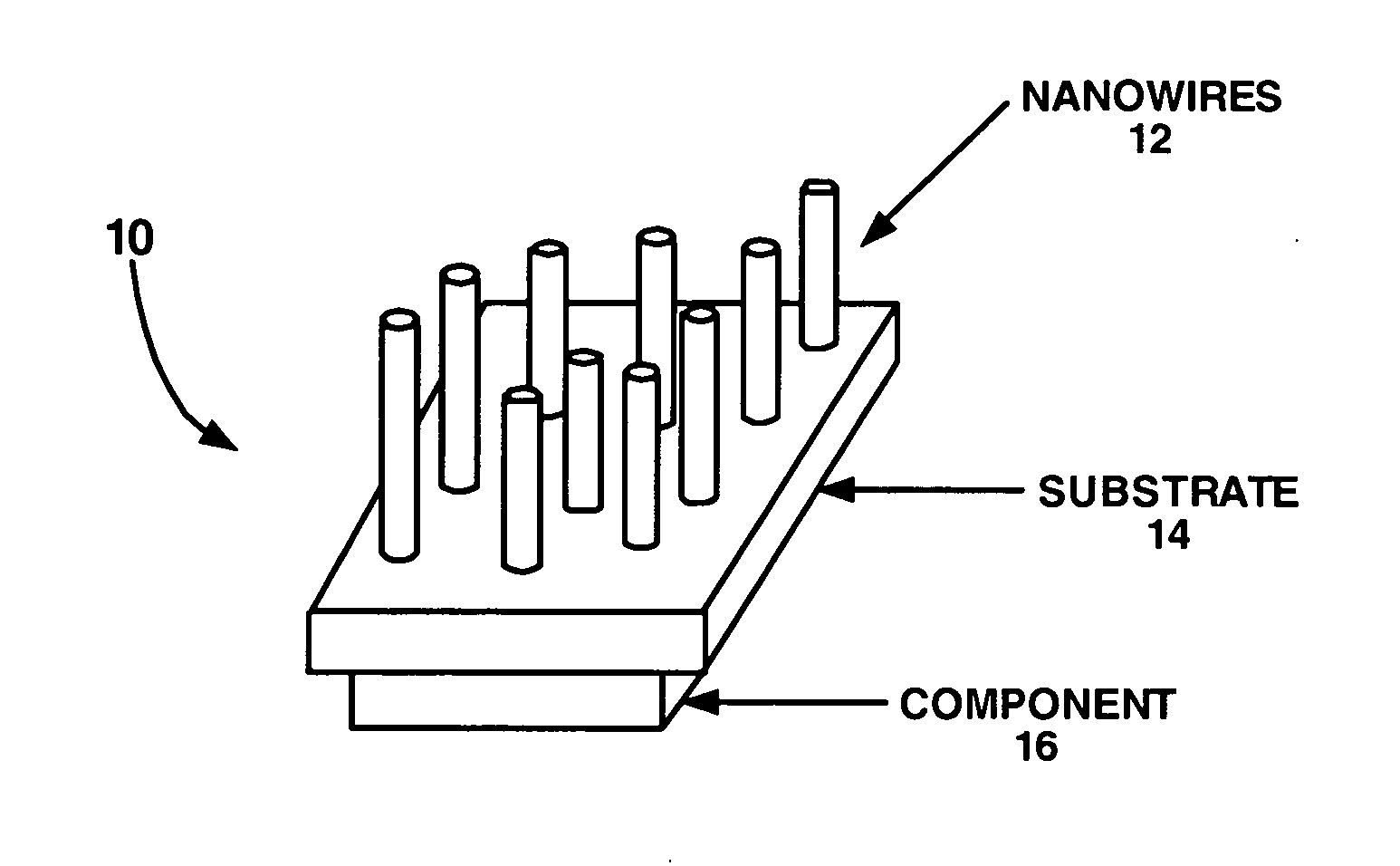

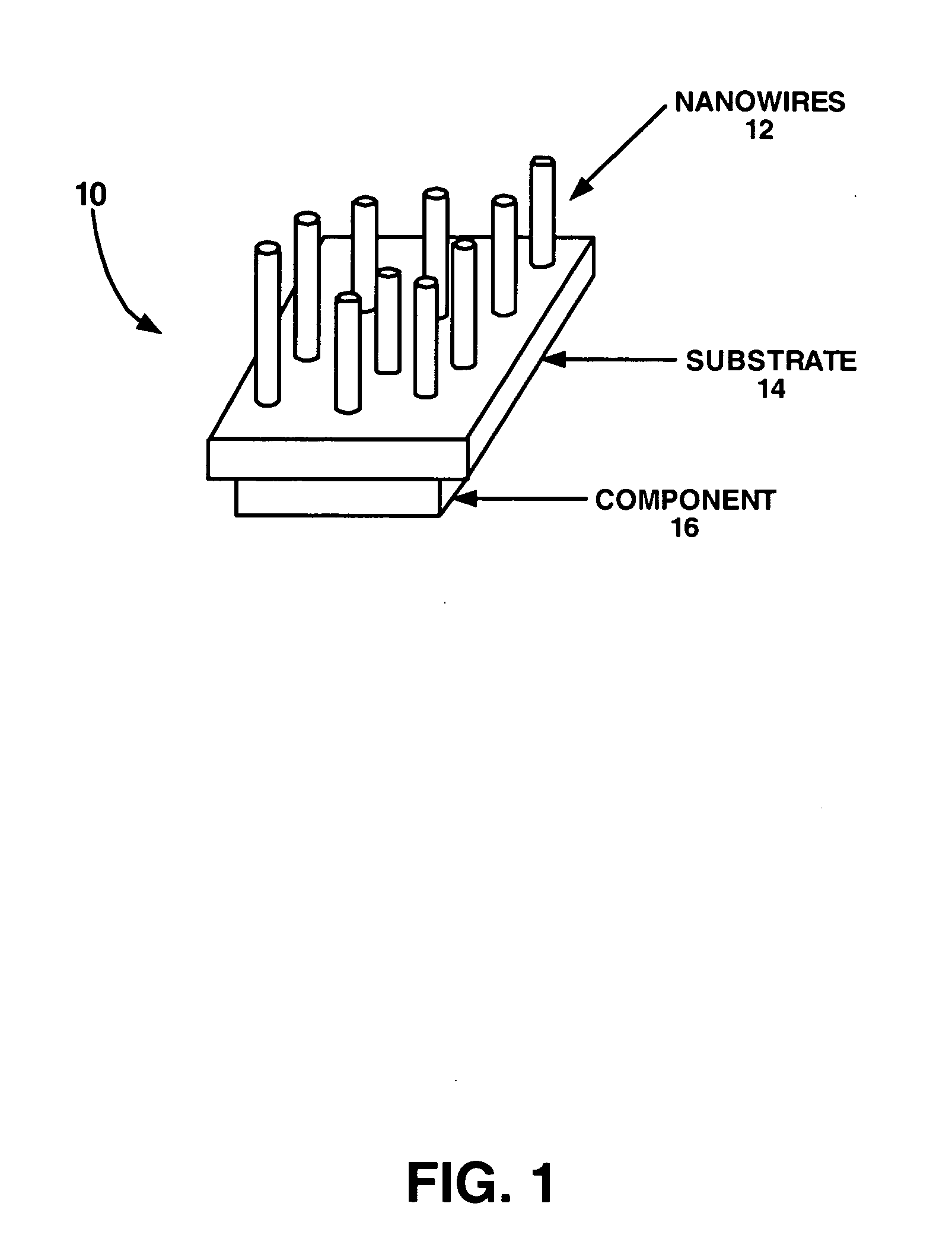

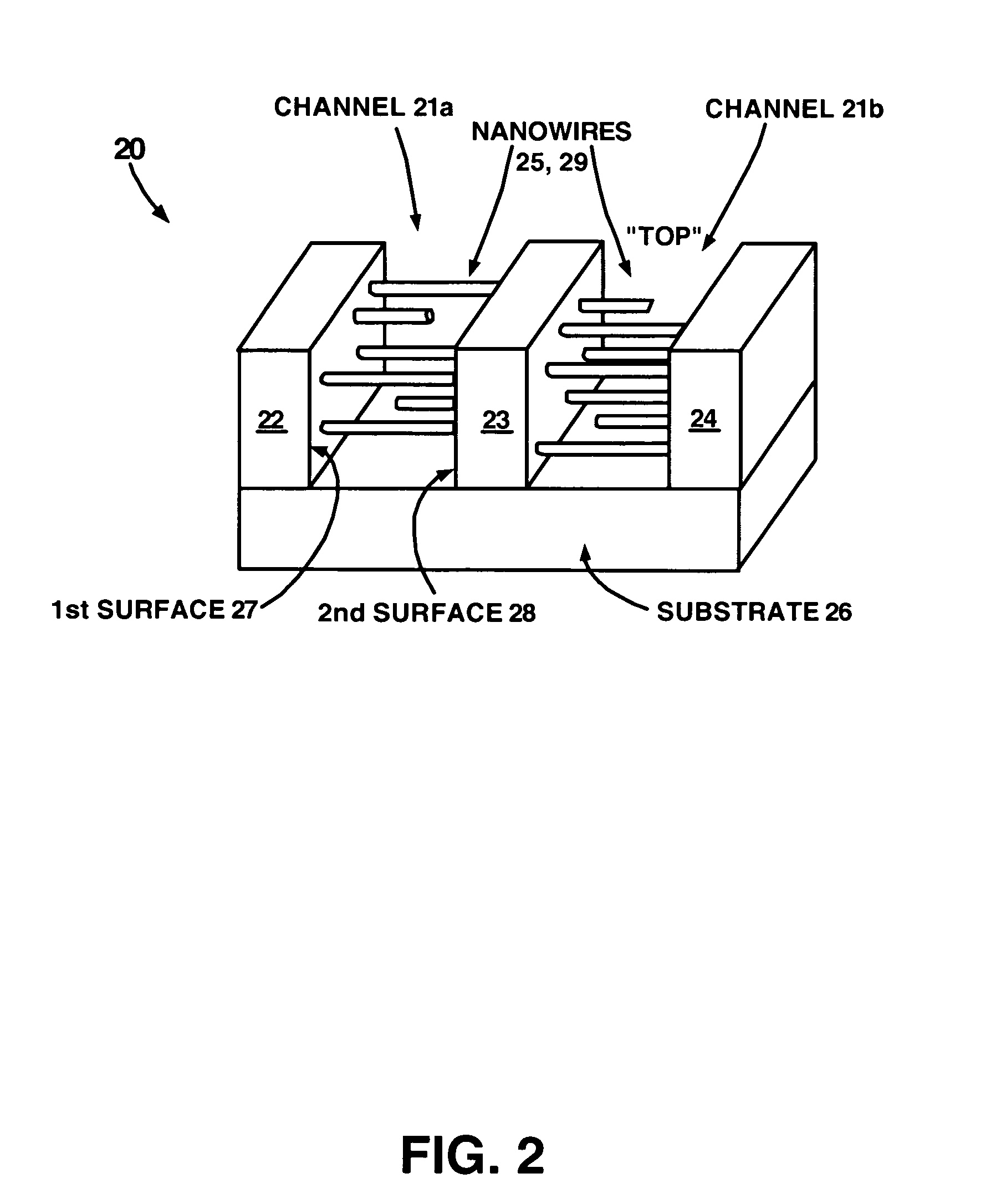

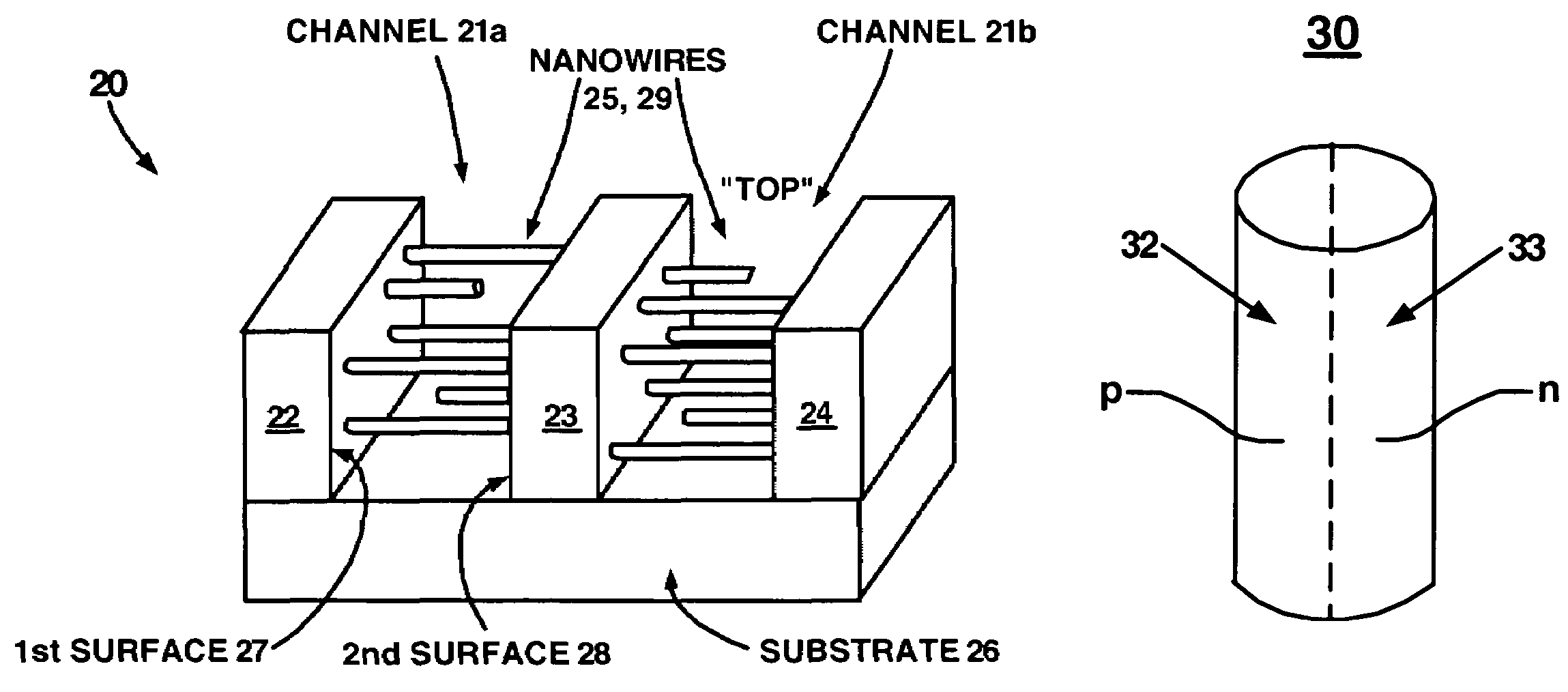

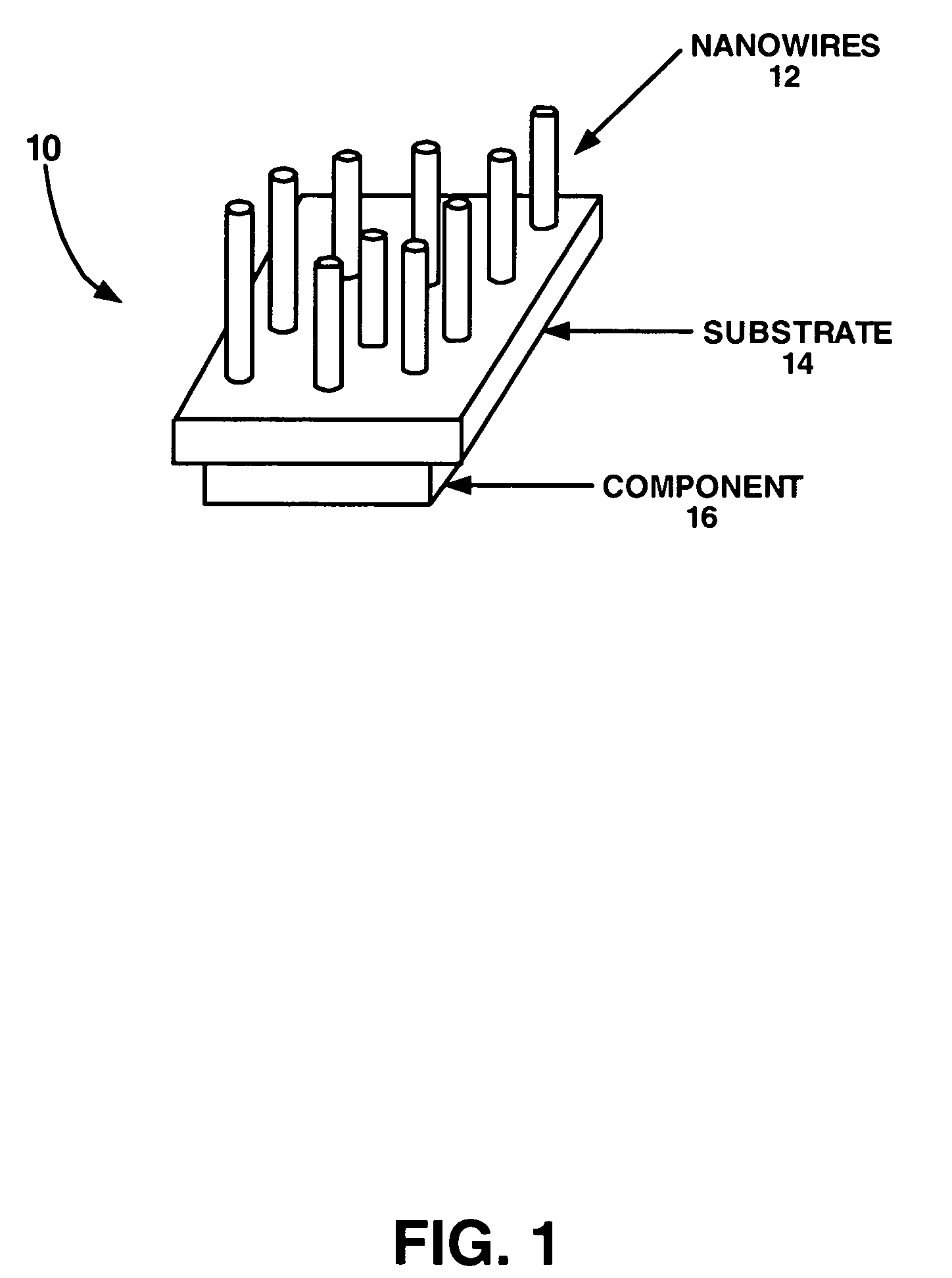

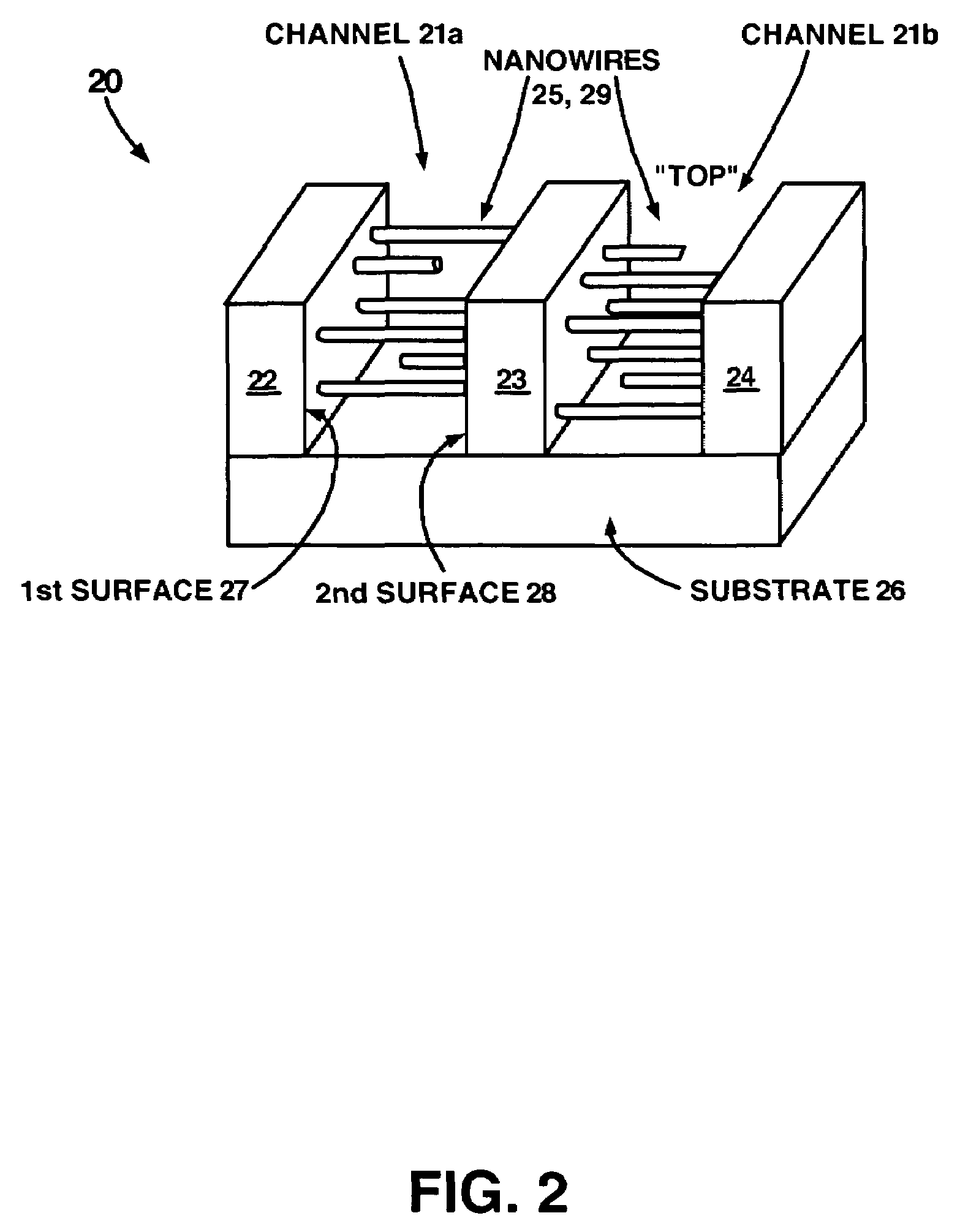

Cooling devices that use nanowires

ActiveUS20060255452A1Thermoelectric device with peltier/seeback effectSemiconductor/solid-state device detailsNanowireHeat energy

Different types of cooling devices using nanowires are described. For example, a cooling device may include a plurality of diamond nanowires coupled to a surface. The diamond nanowires conduct heat energy from the surface and dissipate the heat energy into a neighboring fluid.

Owner:SAMSUNG ELECTRONICS CO LTD

Methods of manufacturing electron-emitting device, electron source, and image display apparatus

InactiveUS20030162465A1Easy to manufactureImprove featuresSemiconductor/solid-state device manufacturingImage/pattern display tubesElectron sourceLight beam

In a process of reducing a resistivity of a polymer film for carbonization in a surface conduction electron-emitting device, by irradiating an energy beam onto the polymer film, when an energy intensity of the beam given in a unit area in a unit time is assumed to be W W / m2, W satisfies a formula W>=2xTx(rhosub.Csub.lambdsub / T)1 / 2, where T is defined as a temperature ° C. at which the polymer film is heated for one hour in a vacuum degree of 1x10-4 Pa to reduce a resistivity of the polymer film to 0.1 OMEGA.cm, Csub is a specific heat J / kg.K of the substrate, rhosub is a specific gravity kg / m3 of the substrate, lambdsub is a heat conductivity W / m.K of the substrate, and T is an irradiation time in the range of 10-9 sec to 10 sec.

Owner:CANON KK

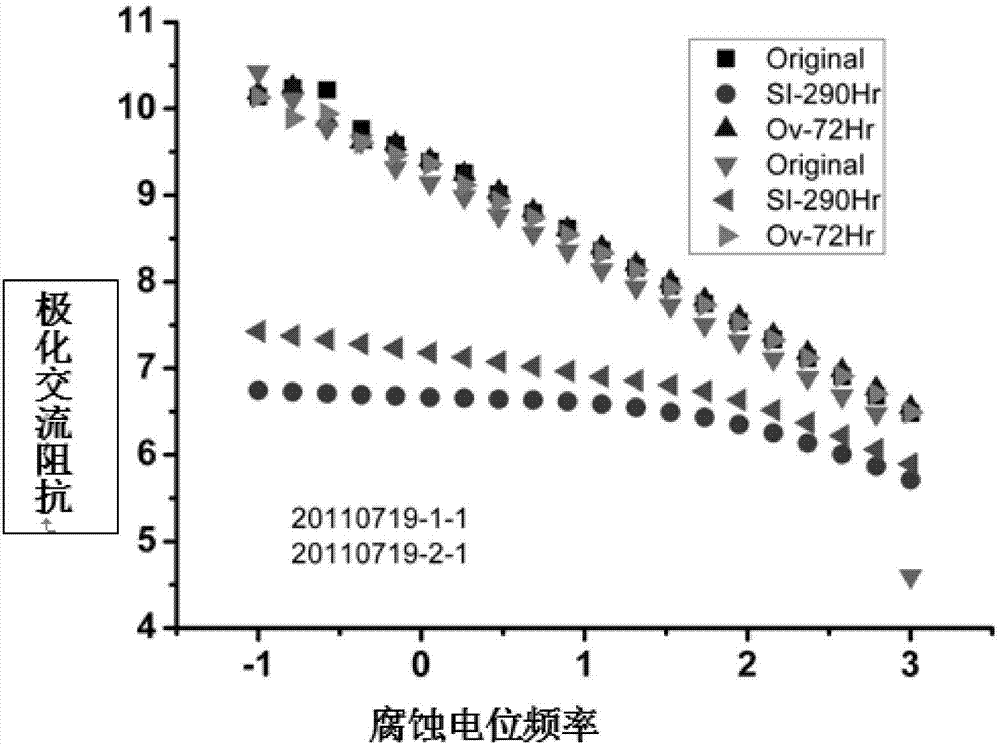

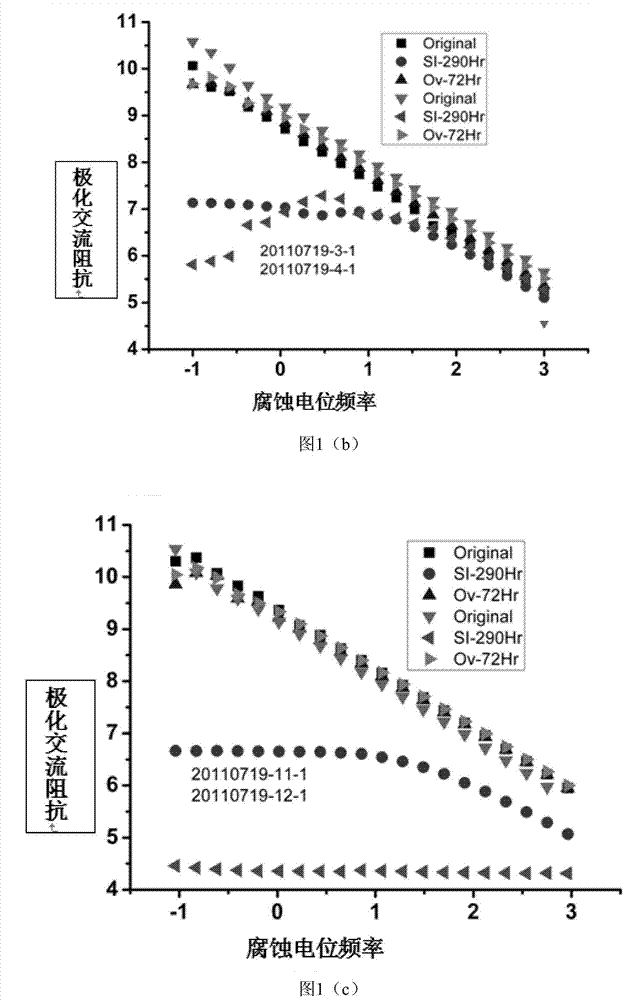

Special anticorrosion conductive powder coating for vertical shaft fluidized bed dip-coating as well as preparation method and application of coating

ActiveCN104710908AHigh glass transition temperatureLight weightAnti-corrosive paintsPolyurea/polyurethane coatingsNano al2o3Conductive materials

The invention relates to a special anticorrosion conductive powder coating for vertical shaft fluidized bed dip-coating. The special anticorrosion conductive powder coating is prepared from the following raw materials in parts by weight: 500-900 parts of film-forming resin and curing agent, 0-200 parts of glass flakes, 0-350 parts of filler, 15-50 parts of auxiliaries, 5-100 parts of conductive material and 1-5 parts of nanometer aluminum oxide or nano fumed silica. The powder coating has the characteristics of a high glass transition temperature, low specific gravity which is generally less than or equal to 1.1g / cm<3>, and easiness for fluidization; even though hundreds of tons of powder is added to a 20m deep well, the powder can be fluidized easily and uniformly; in case of too high specific gravity and difficult fluidization, the vertical shaft dip-coating method can not be utilized; the powder aims at a hot-dip coating construction process, and the film formed by the coating has surface conduction characteristics and high temperature water boiling resistance, and therefore, the coating is suitable for anti-corrosion coating of long linear workpieces such as mine mining anti-explosion gas pipelines, natural gas pipelines and liquefied gas pipelines; the coating is adaptive to the vertical shaft fluidized beds as deep as 20m, and still has good fluidity, which cannot be realized by common powders easily.

Owner:阜阳市诗雅涤新材料科技有限公司

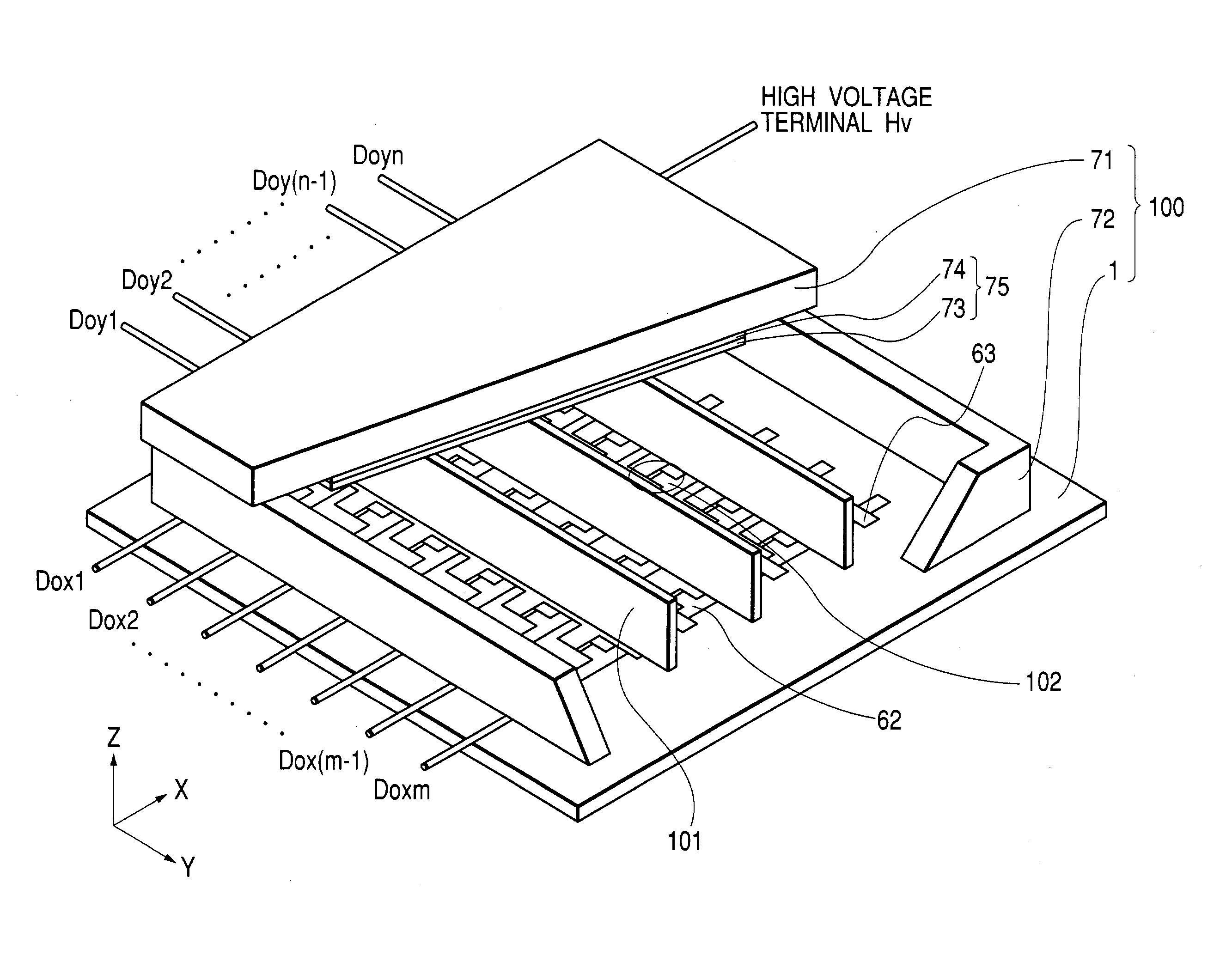

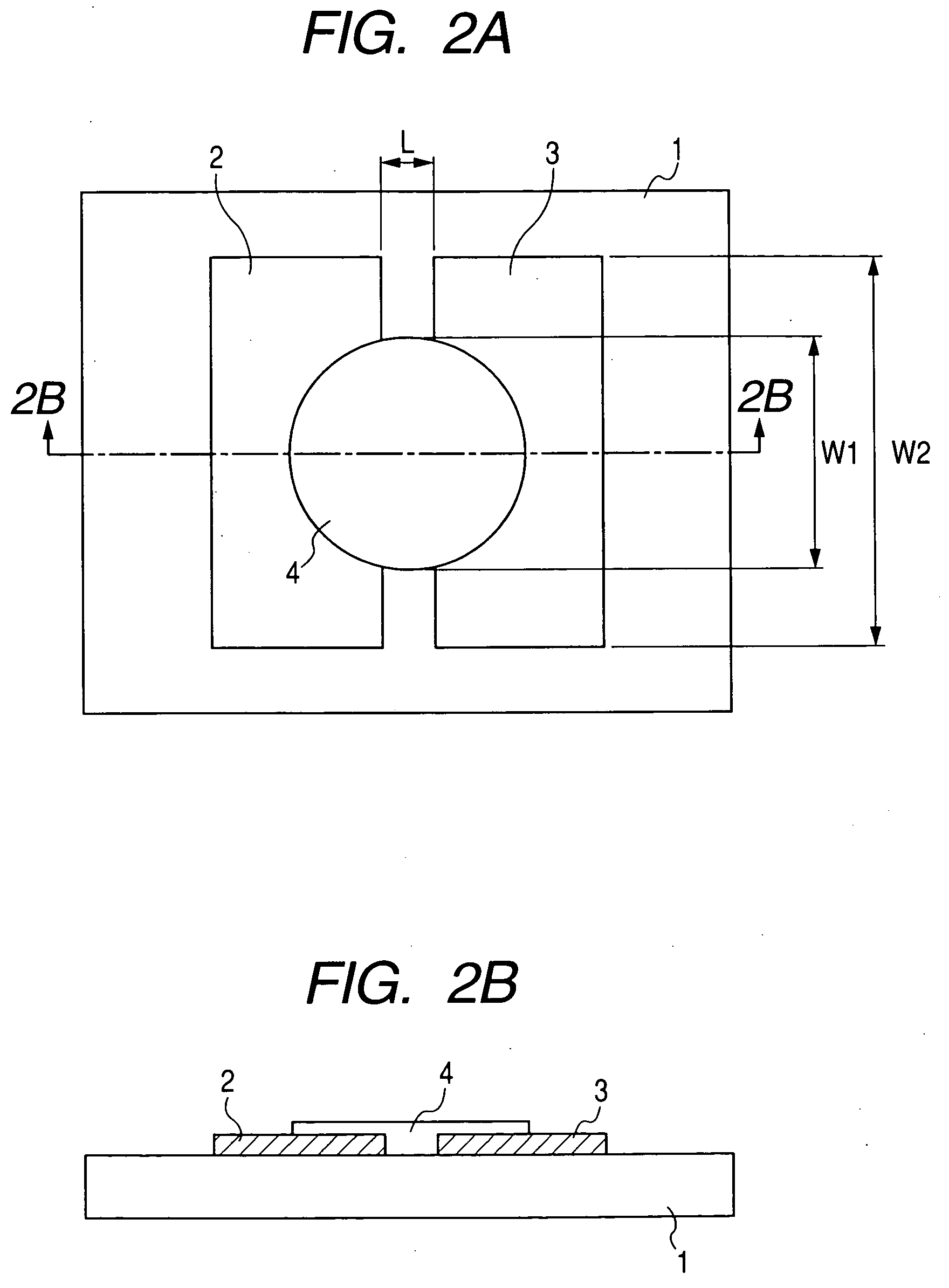

Electron-emitting device and image display apparatus using the same

InactiveUS6992433B2Easy to produceSimple structureInking apparatusDischarge tube luminescnet screensElement spaceSource material

An electron-emitting device and an image display apparatus in which the electron-emitting device is provided. In the electron-emitting device, a substrate has sides in two orthogonal first directions. A plurality of pairs of electrodes are disposed on the substrate. A conductive thin film is disposed between each of the electrode pairs. A plurality of surface conduction electron-emitting elements are disposed in the conductive thin film by discharging drops of a source material of the film thereto, each electron-emitting element spaced apart from the opposing electrodes of one of the electrode pairs. The electron-emitting elements are arrayed in a matrix formation, the matrix having rows and columns in two orthogonal second directions, the electron-emitting elements being disposed such that the second directions of the matrix are parallel to the first directions of the substrate.

Owner:RICOH KK

Semiconductor device having heat conducting plates

InactiveUS20050073043A1Efficient use ofSimple structureSemiconductor/solid-state device detailsSolid-state devicesHeat conductingSemiconductor chip

A semiconductor device includes a semiconductor chip generating heat, a pair of heat sinks, which face each other, to conduct heat from both surfaces of the chip, a pair of compressible insulating sheets, and a mold resin covering the chip, the heat sinks, and the sheets such that the sheets are exposed from the surface of the resin. The mold resin is prevented from covering the outer surfaces of the heat sinks, which are pressed by mold parts, and breakage of the chip is avoided during molding. The plates are insulated by the sheets, so no dedicated insulating sheets for the heat sinks are needed after the device is completed.

Owner:DENSO CORP

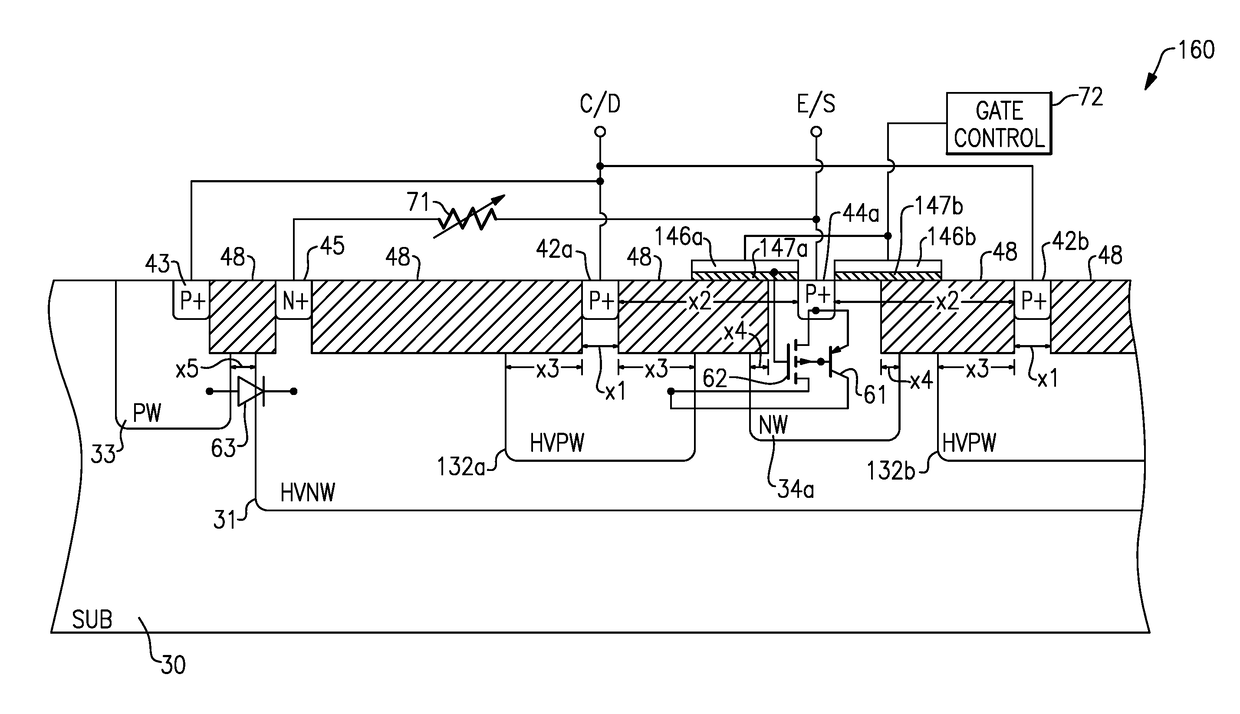

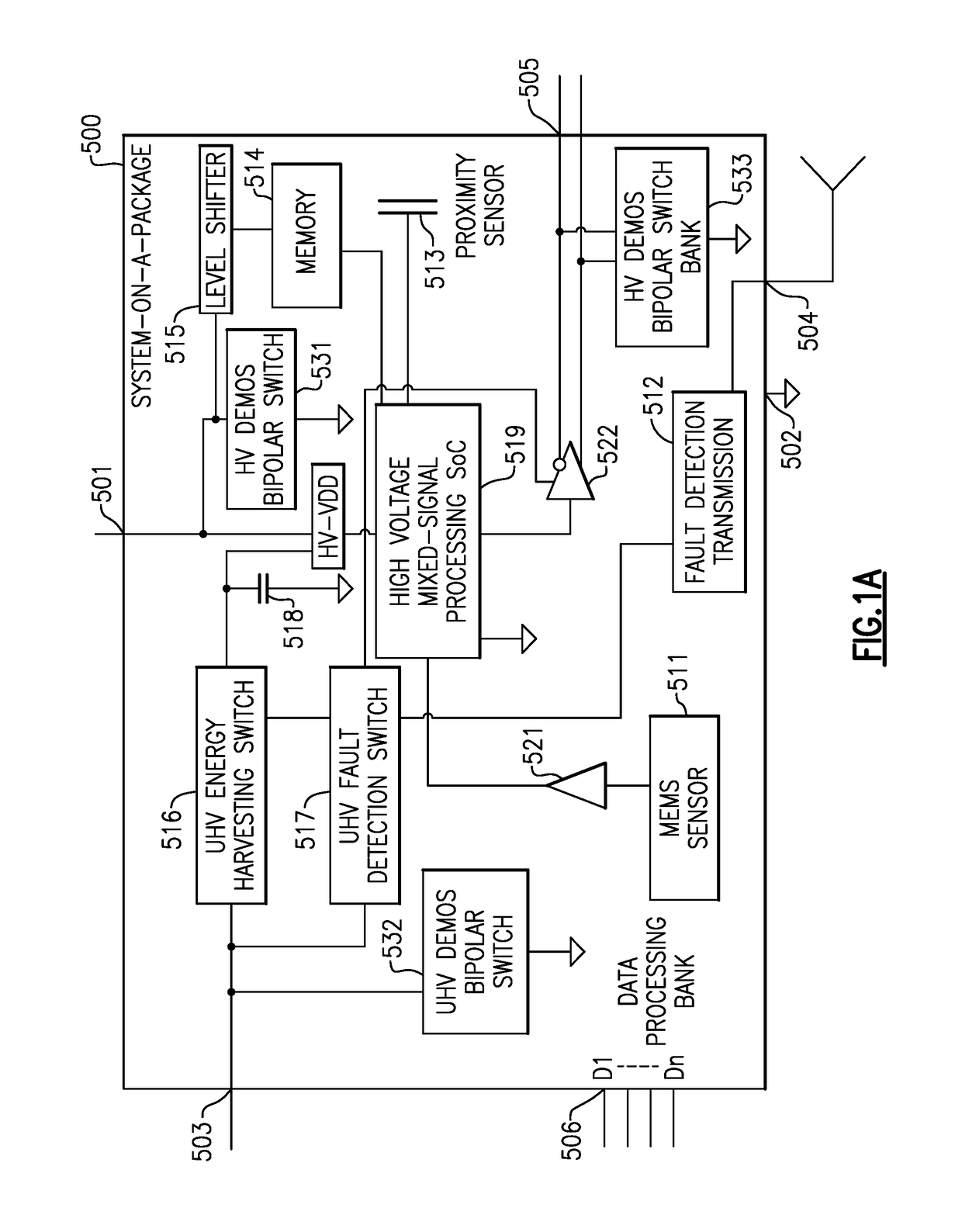

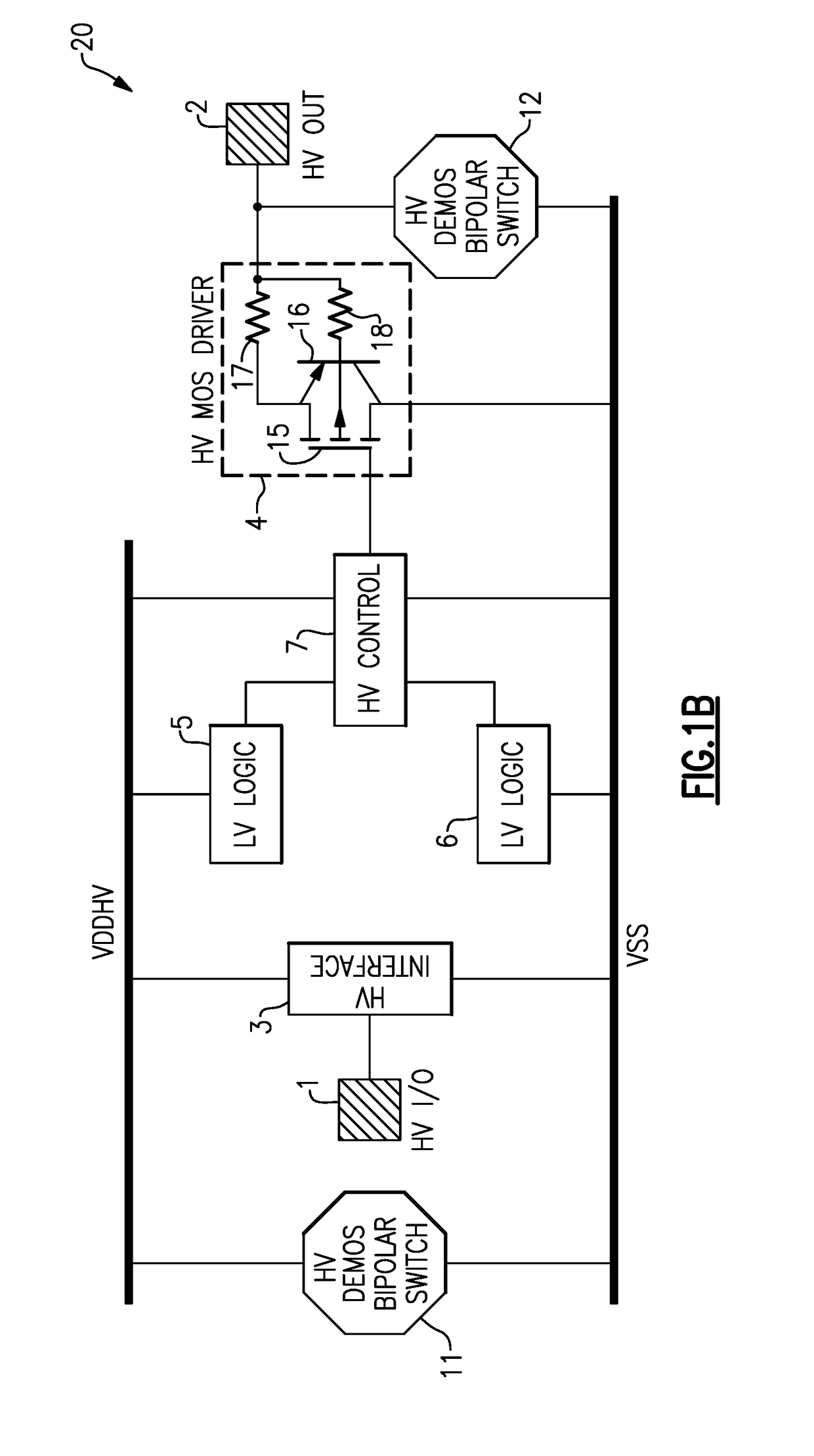

Drain-extended metal-oxide-semiconductor bipolar switch for electrical overstress protection

ActiveUS20180211951A1Fast switch device turnLow voltage overshootTransistorSemiconductor/solid-state device detailsLow voltageEngineering

High voltage drain-extended metal-oxide-semiconductor (DEMOS) bipolar switches for electrical overstress protection are provided. In certain configurations herein, an electrical overstress switch embodiment for providing electrical overstress protection, such as electrostatic discharge / electrical overstress (ESD / EOS) protection includes both a DEMOS device and an embedded bipolar device. The switch is implemented to achieve the advantages provided by the combined conduction of DEMOS and bipolar devices. For example, the DEMOS device provides surface conduction at the gate region for relatively fast switch device turn on and low voltage overshoot, while the bipolar device provides high current conduction during stress condition and a high holding voltage characteristics to prevent latch-up in mission critical integrated circuit applications.

Owner:ANALOG DEVICES INC

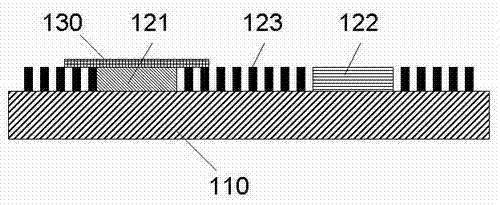

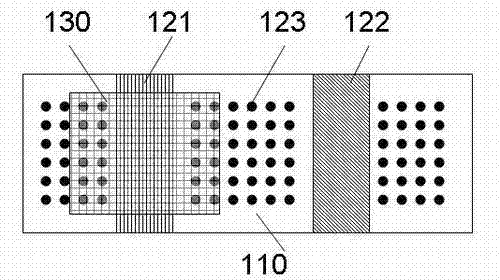

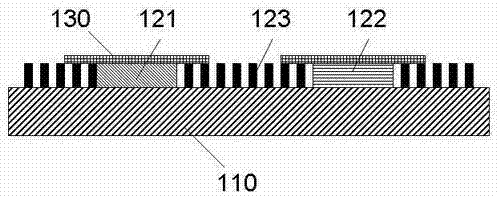

Surface-conduction electron emission source based on graphene

InactiveCN102856139AImprove emission efficiencySimple processDischarge tube/lamp detailsHigh electronSecondary electrons

The invention relates to the technical field of surface-conduction electron emission panel display, in particular to a surface-conduction electron emission source based on graphene. The surface-conduction electron emission source comprises a substrate and two electrodes arranged on the surface of the substrate in parallel, nanometer material layers are arranged in a gap between the two electrodes and outer sides of the two electrodes, a graphene film element is respectively arranged on upper portions of the two electrodes or is arranged on the upper portion of one of the electrodes, and one or two sides of each graphene film element extends outwards. The surface-conduction electron emission source has the advantages that a surface-conduction field emission structure, high electron emission performance of the graphene and secondary electron emission performance of a nanometer material array are effectively combined, the graphene in the surface-conduction electron emission source is used as an electron emission source, and the nanometer material array not only is used as a surface electron conductive layer, but also is used as a support for the graphene; and the surface-conduction electron emission source is low in working voltage, high in electron emission efficiency, stable and reliable in emission and simple in manufacturing process.

Owner:FUZHOU UNIV

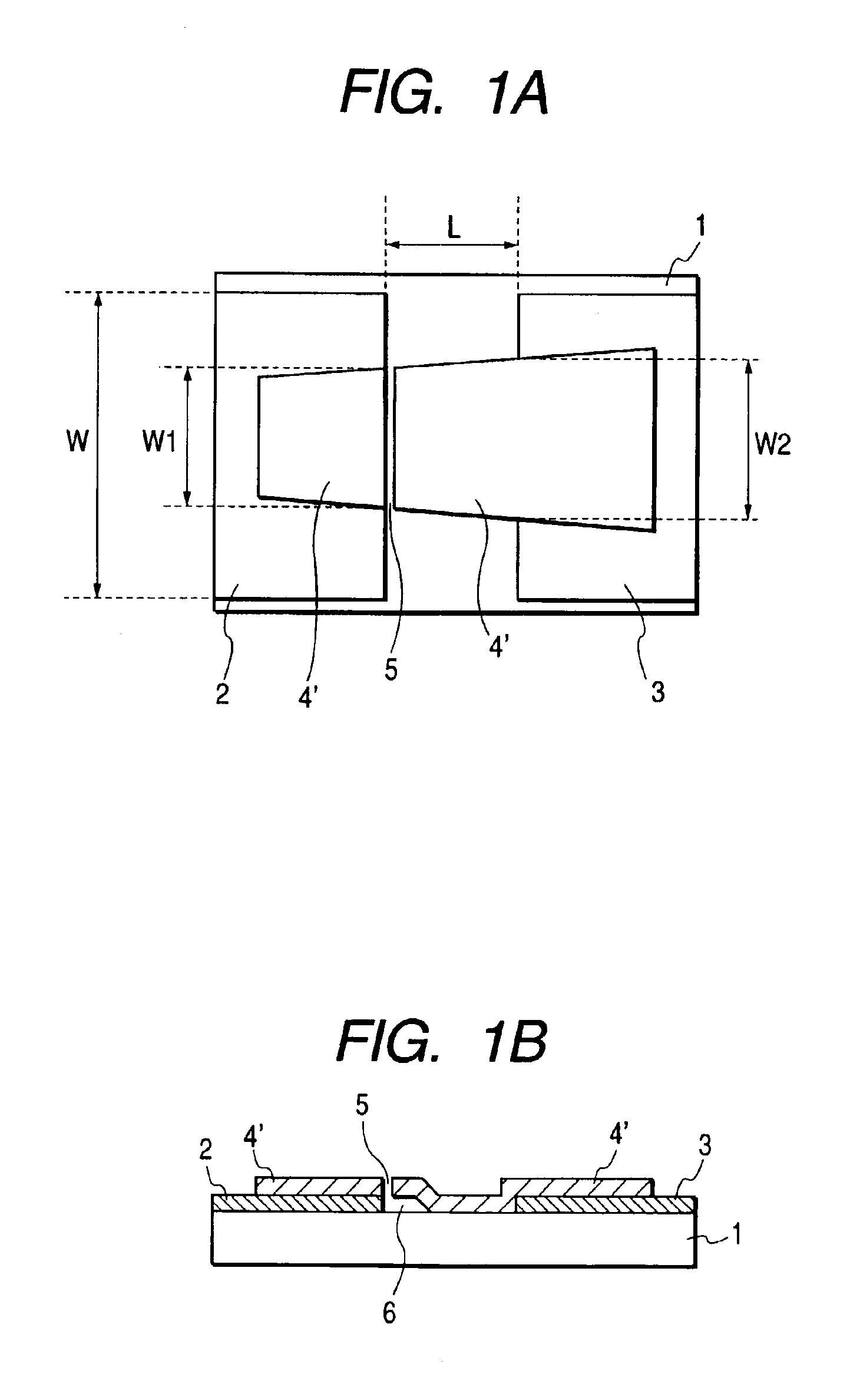

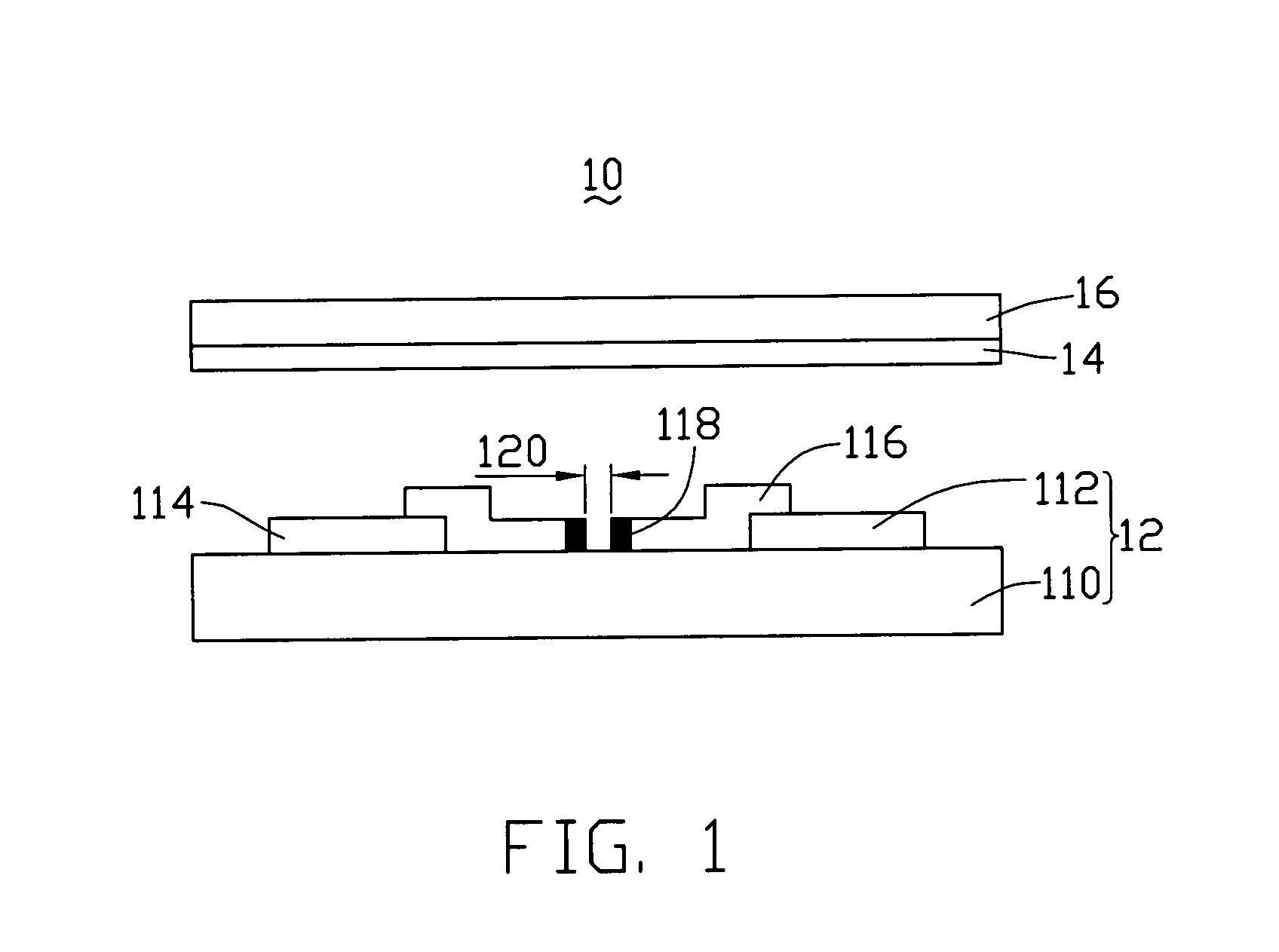

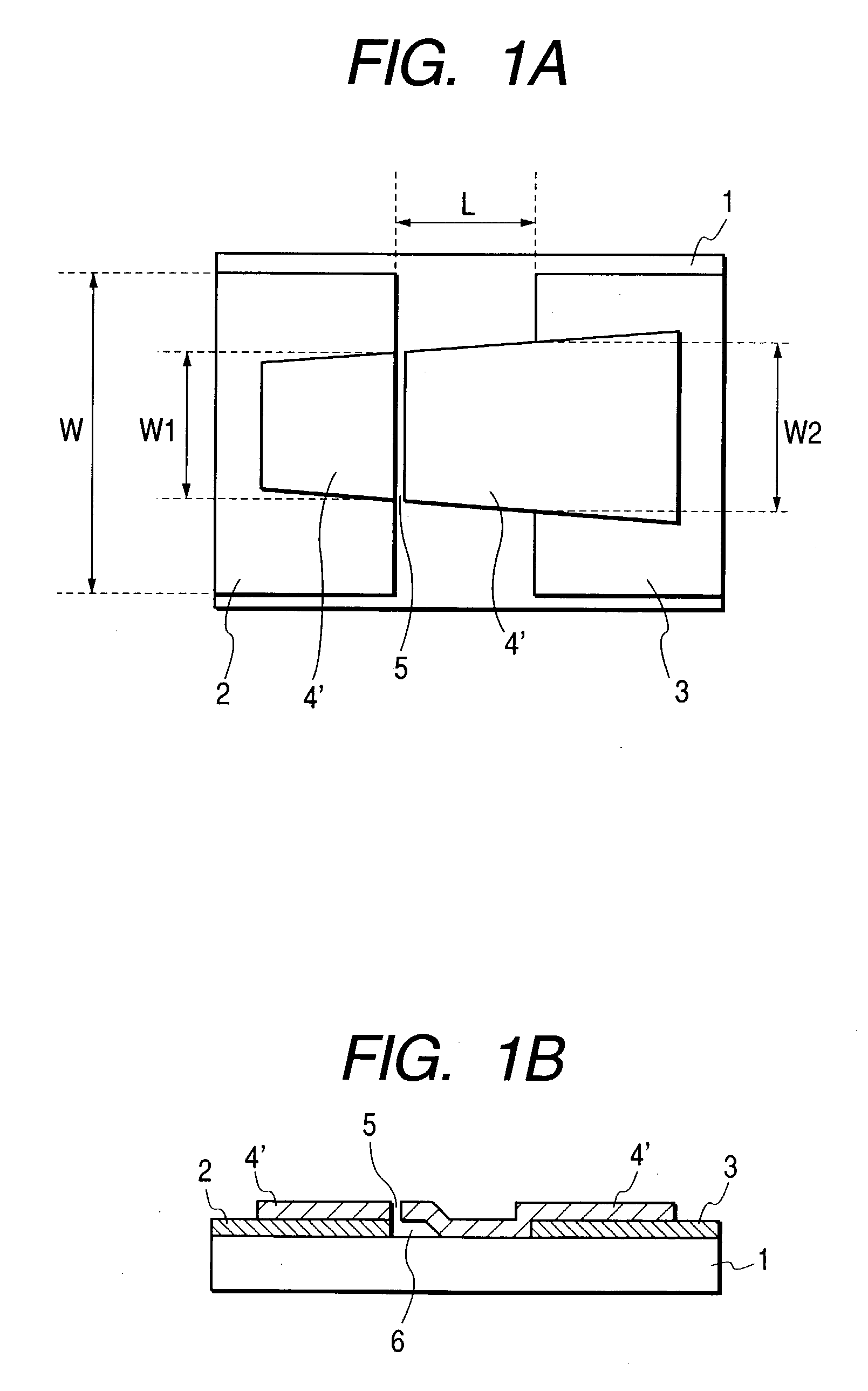

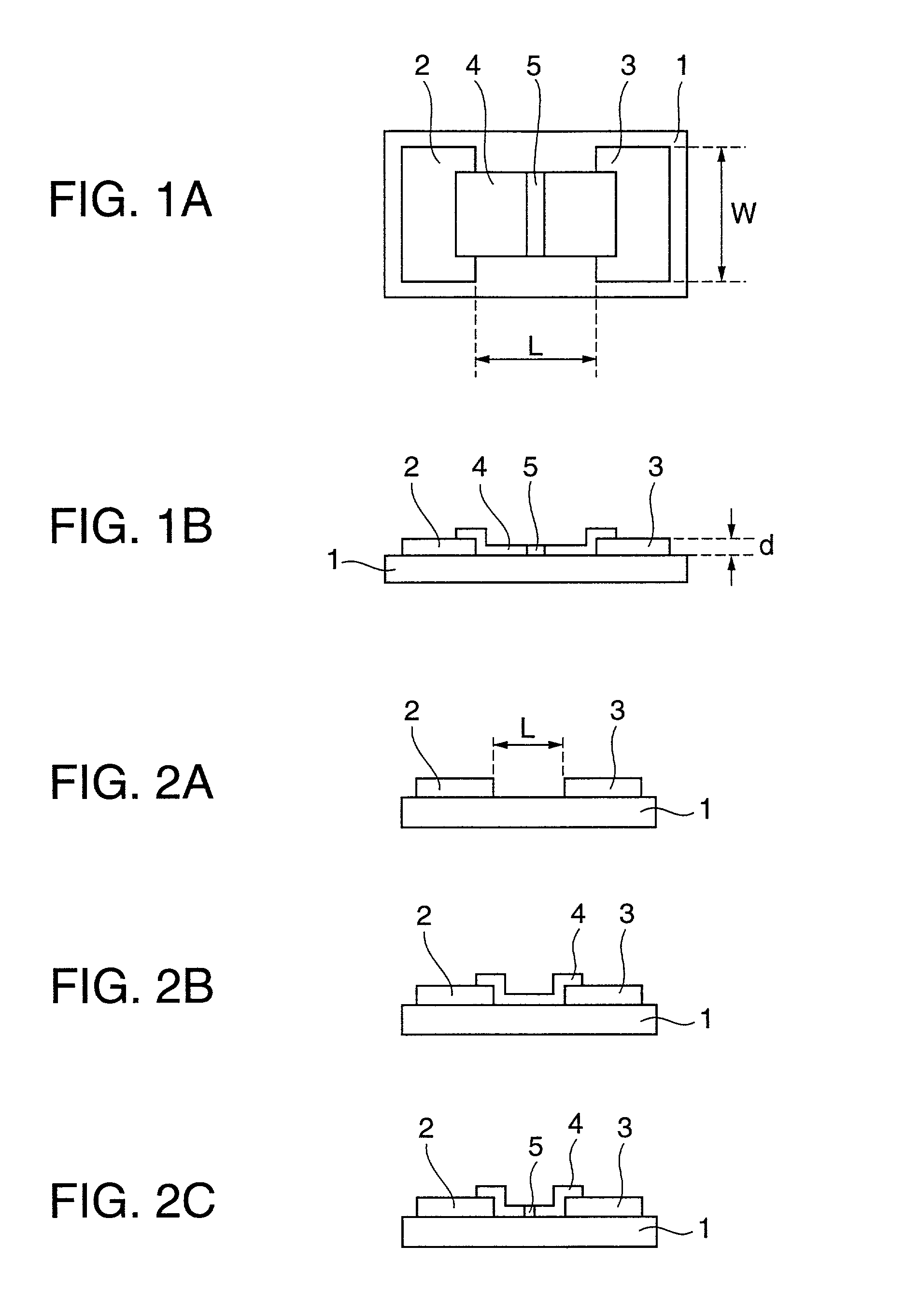

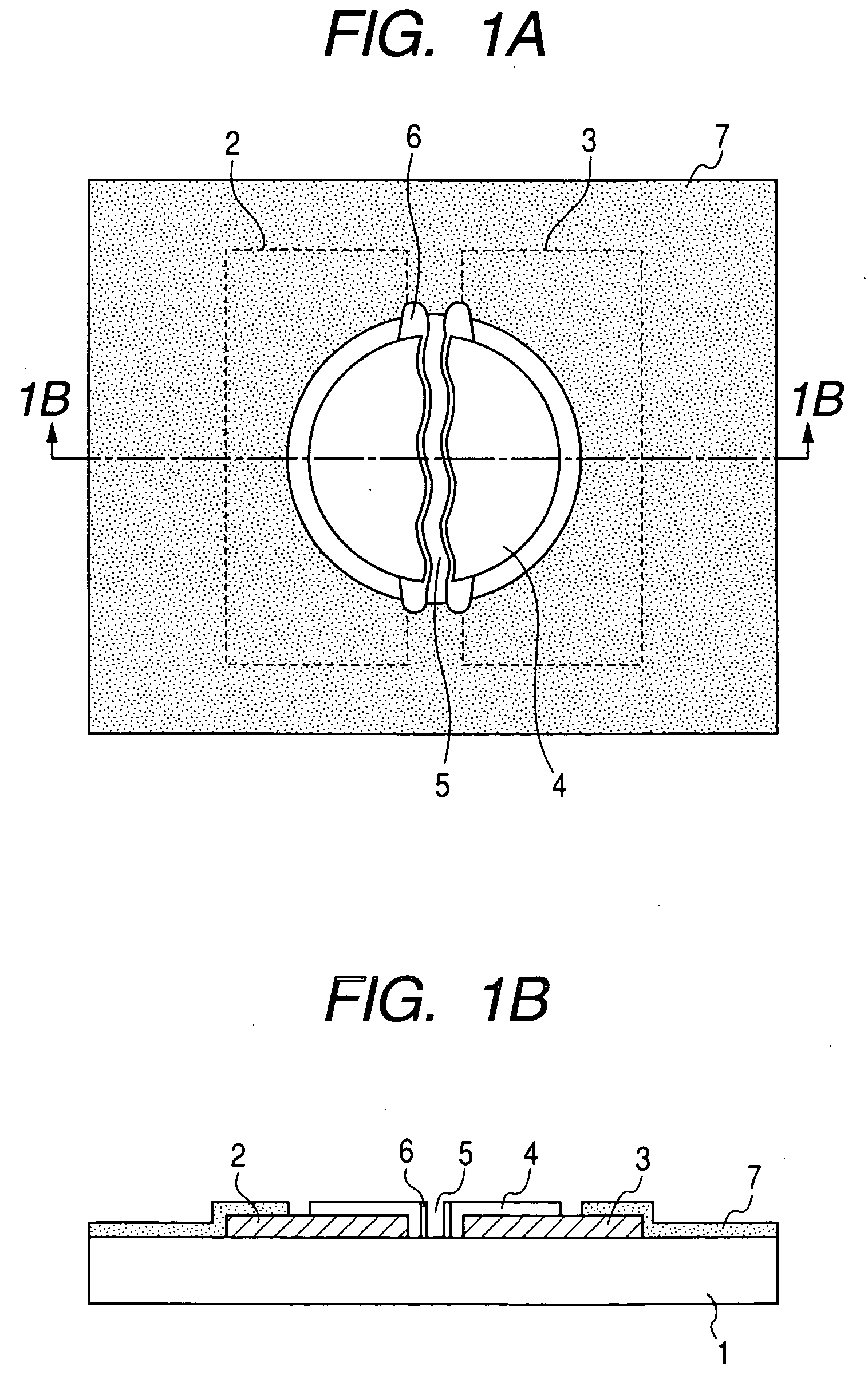

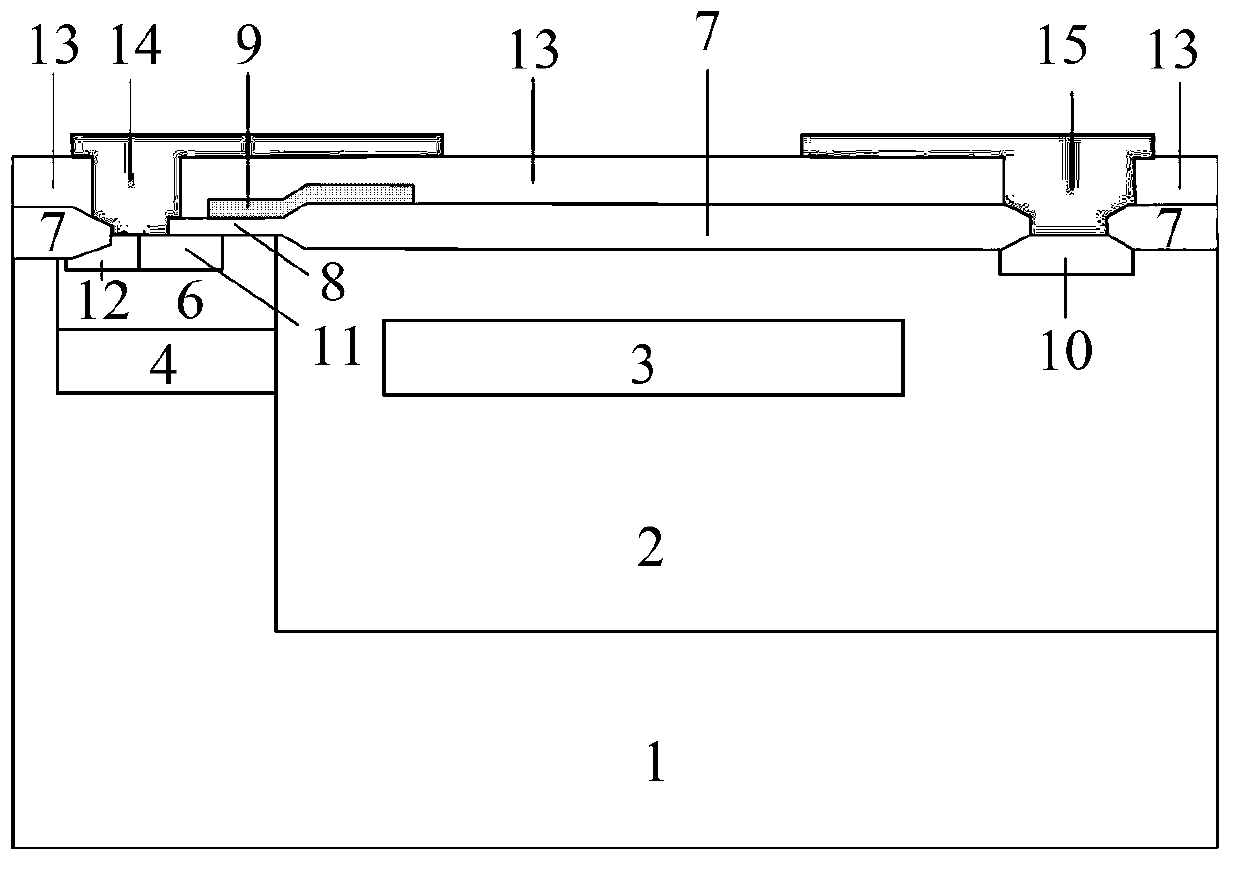

Electron-emitting device, electron source, picture display unit and manufacturing process therefor

InactiveUS20050269936A1Well formedReduce panel costDischarge tube luminescnet screensLamp detailsCarbon filmManufacturing technology

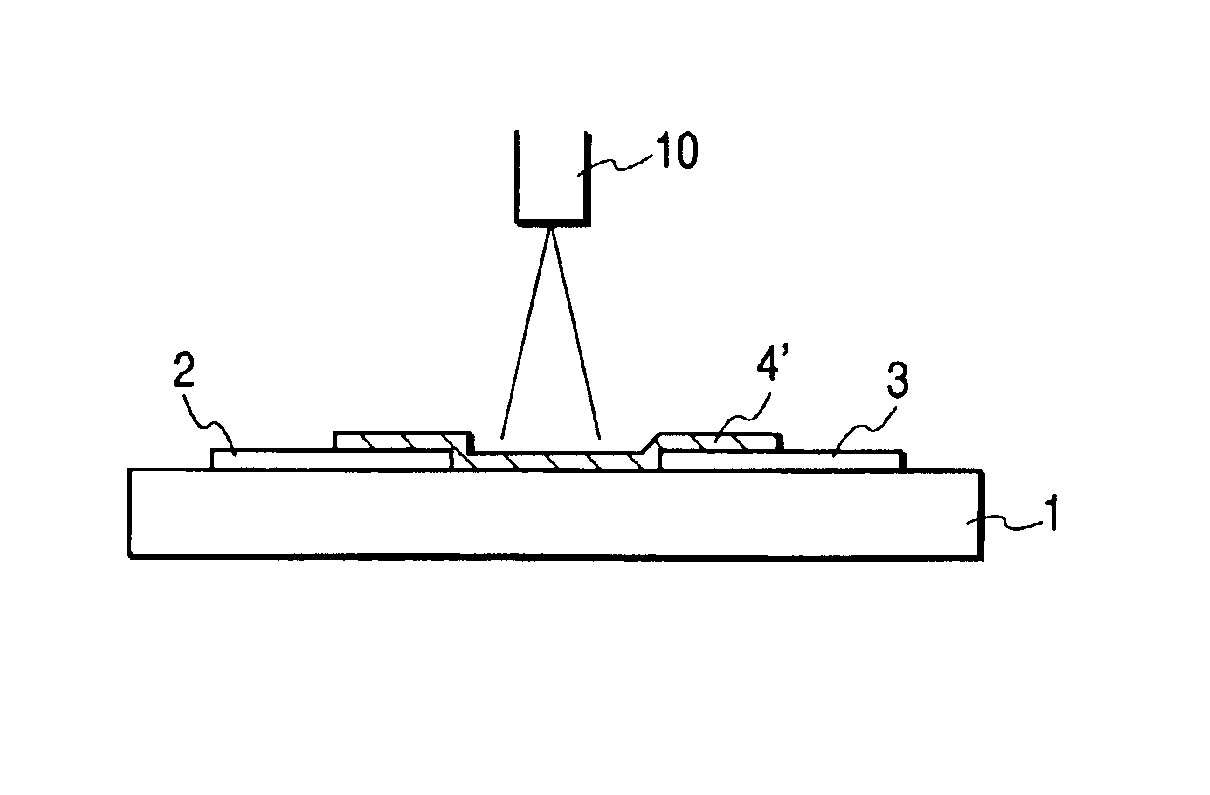

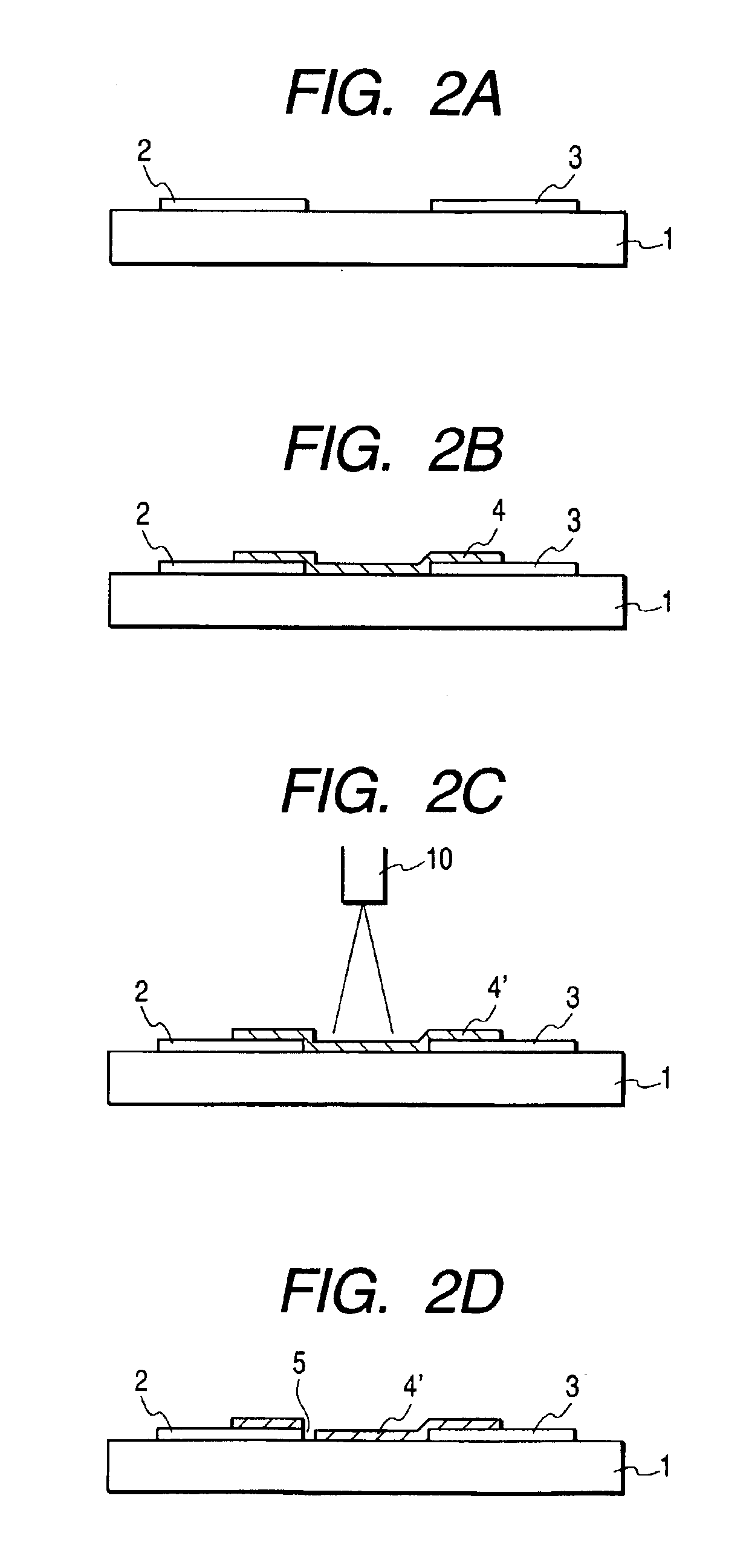

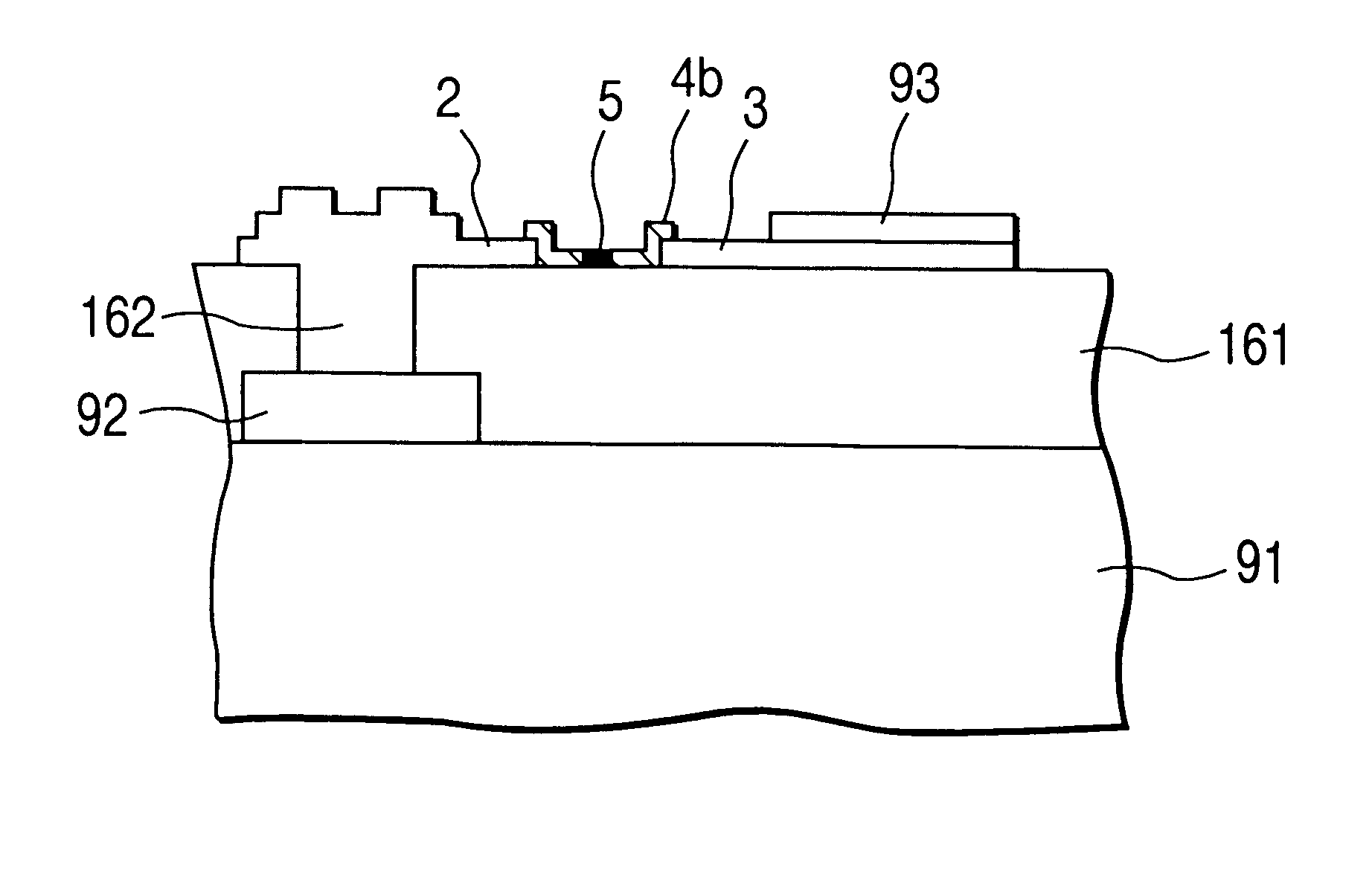

An object of the present invention is to prevent a device portion from being electrostatically charged with the use of the high resistivity film, and at the same time prevent a leak current passing the device portion due to an existing high resistivity film, in an electron source with the use of a surface-conduction electron-emitting device. This process for manufacturing the electron-emitting device comprises the steps of: forming an electroconductive thin film 4 astride device electrodes; forming the high resistivity film 7 in a region except the electroconductive thin film 4 and a perimeter thereof; subjecting the electroconductive thin film 4 to forming processing, to form a fissure 5 therein; and depositing a carbon film 6 inside the fissure 5 and in a region reaching the high resistivity film 7 from the edge of the fissure 5, by applying voltage between device electrodes 2 and 3 under an atmosphere containing a carbon compound.

Owner:CANON KK

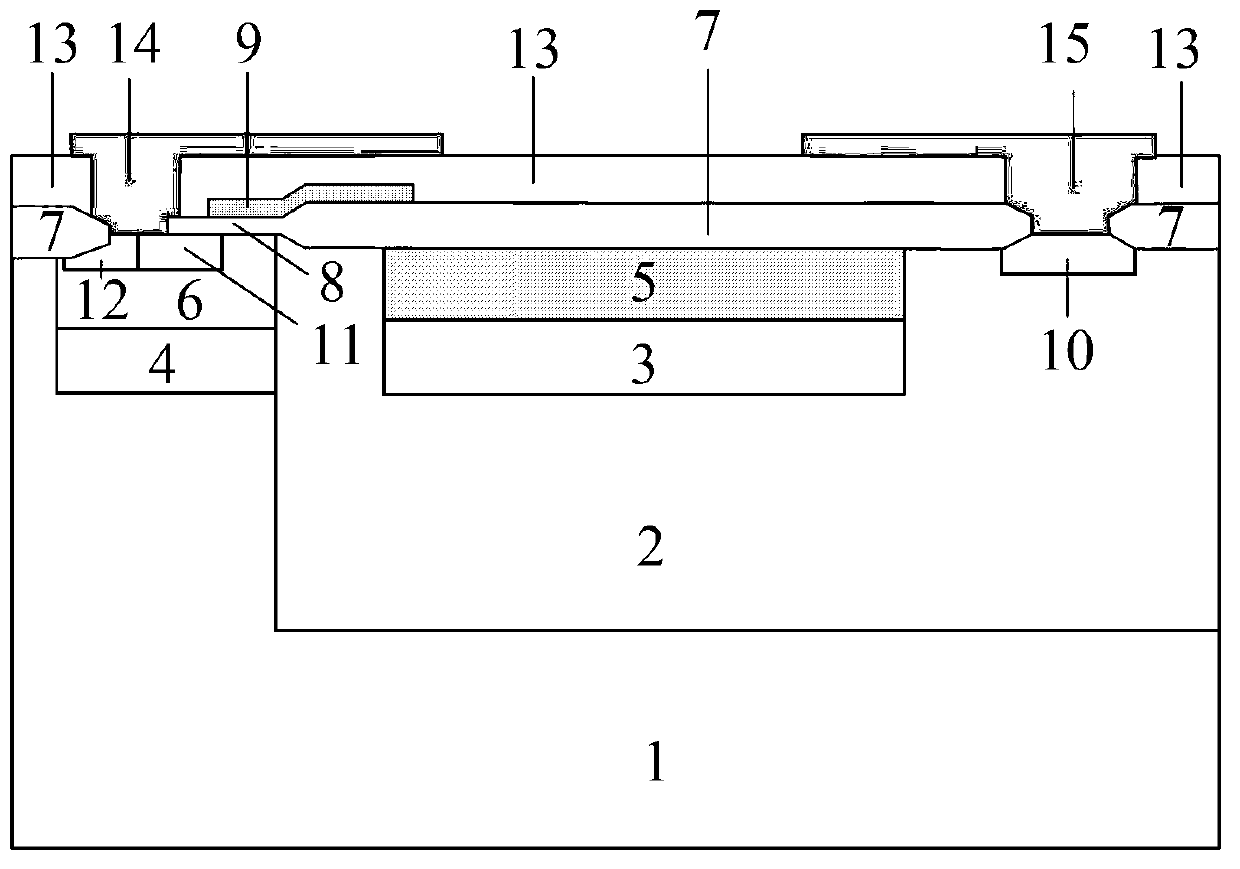

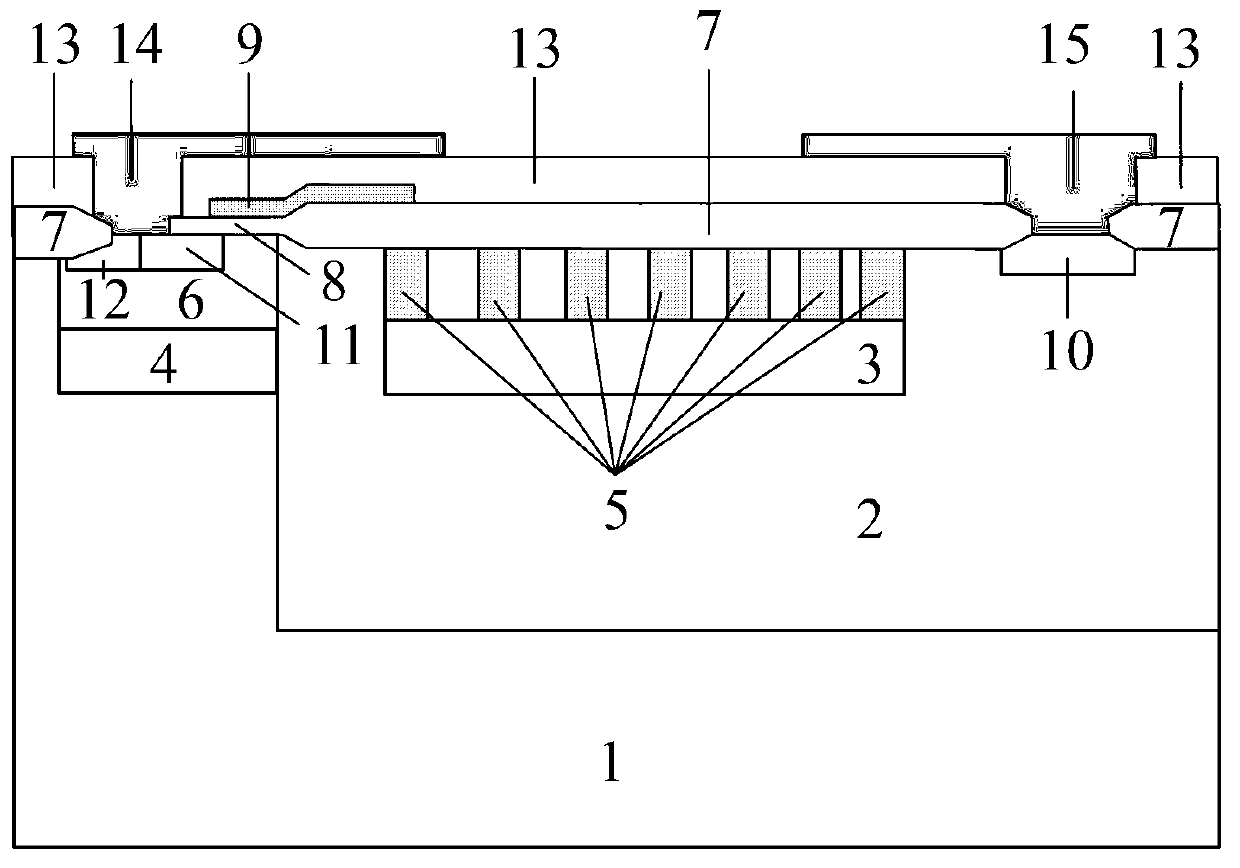

Transverse high-voltage power device with ultralow specific on-conduction resistance and manufacturing method of transverse high-voltage power device

ActiveCN103280457ALower on-resistanceLow resistivitySemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringHigh pressure

The invention relates to a transverse high-voltage power device with ultralow specific on-resistance and a manufacturing method of the transverse high-voltage power device and belongs to the technical field of a power semiconductor device. Through photoetching and ion implantation processes, a second conducting type semiconductor heavy doping layer (5) formed at the surface of a second conducting type semiconductor drift region (2) provides a low-resistance surface conduction passage for the device during the on state and provides two conduction passages for the device together with the second conducting type semiconductor drift region (2) arranged under a reduced field layer (3). Because the ion implantation is adopted, the low-resistance surface conduction passages are added, the surface electric resistivity of the device is reduced, and the on resistance of the device is greatly reduced. Compared with an ordinary high-voltage device with the reduced field layer, the transverse high-voltage power device provided by the invention has smaller on resistance under the condition of the same chip area (or the transverse high-voltage power device has smaller chip area under the condition of the same conduction capability). The transverse high-voltage power device can be applied to various products such as consumer electronics and display driving products.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

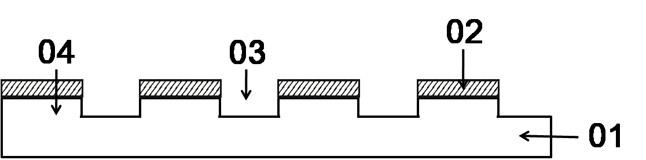

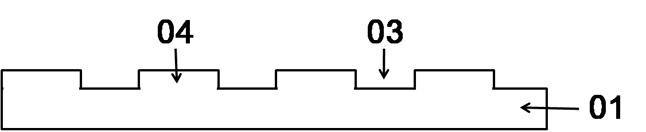

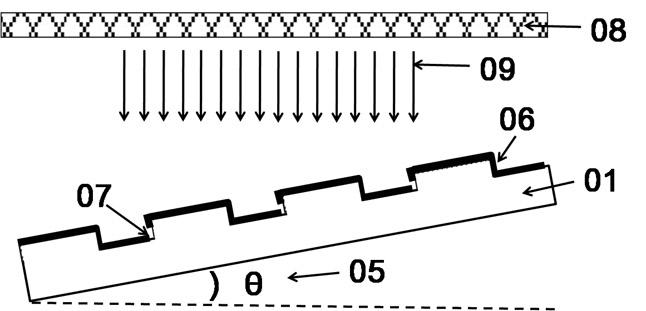

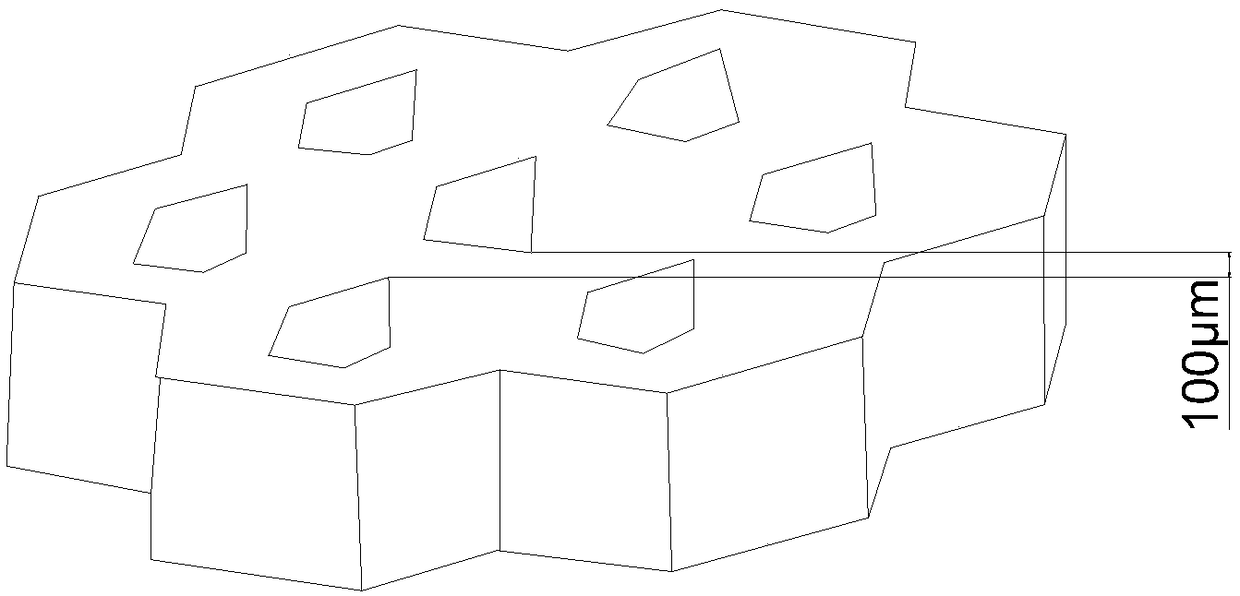

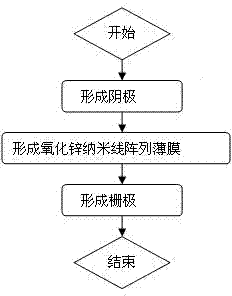

Manufacturing method of surface conduction electron emission source with uniform and controllable nano gaps

ActiveCN102637561AAvoid pollutionImprove emission efficiencyCold cathode manufactureThin membraneElectrode array

The invention discloses a manufacturing method of a surface conduction electron emission source with uniform and controllable nano gaps. The manufacturing method comprises the following concrete steps of: firstly, preparing a columnar pattern array with height ranging from 10 nanometers to hundreds of nanometers and rectangular, triangular or trapezoidal vertical cross section on a flat insulation substrate; then depositing an SED (surface-conduction electron-emitter display) electron-emitting source film layer with the thickness ranging from 10 nanometers to 500 nanometers toward an inclined direction on the flat insulation substrate prepared with the columnar pattern; directly producing a gap with the width ranging from a few nanometers to dozens of nanometers or by virtue of follow-up dry etching or wet etching as no film or extremely thin film is deposited on the part blocked by the columnar pattern; and finally manufacturing an SED electron emission electrode array on the substrate. The manufacturing process of the SED electron emission source is simple, and nano gaps which realize electron emission are uniform and controllable.

Owner:FUZHOU UNIV

Semiconductor device having heat conducting plate

InactiveUS6946730B2Efficient use ofSimple structureSemiconductor/solid-state device detailsSolid-state devicesDevice materialHeat conducting

A semiconductor device includes a semiconductor chip generating heat, a pair of heat sinks, which face each other, to conduct heat from both surfaces of the chip, a pair of compressible insulating sheets, and a mold resin covering the chip, the heat sinks, and the sheets such that the sheets are exposed from the surface of the resin. The mold resin is prevented from covering the outer surfaces of the heat sinks, which are pressed by mold parts, and breakage of the chip is avoided during molding. The plates are insulated by the sheets, so no dedicated insulating sheets for the heat sinks are needed after the device is completed.

Owner:DENSO CORP

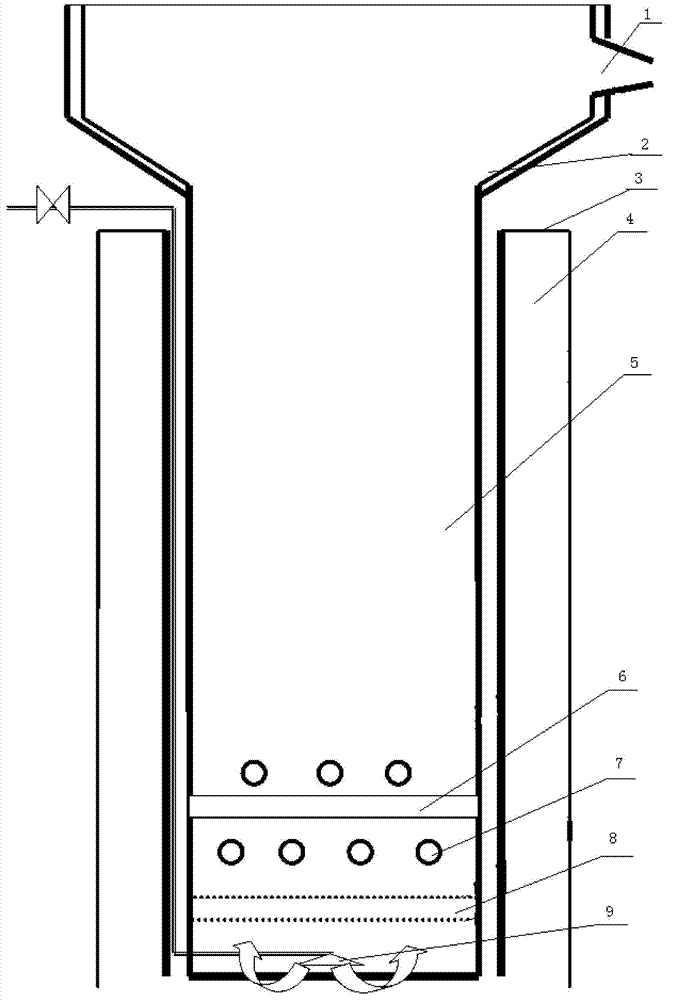

Railroad rail anticorrosion and surface conduction enhancing method

InactiveCN1580315ASolve corrosionSolve conductivity problemsRailsMolten spray coatingParticulatesHigh pressure

This invention is about a method to antisepticize railway and increase its surface conductivity, which contains only two steps: 1. use high pressure gas to eject high-speed hard granule to the railway surface, in order to make a deoxidated rough coat on it; 2. metal spraying, use method of combustion or electric arc to fuse the metal alloy thread constantly moving on the railway surface, add a driven nozzle when it reaches to the melting point, spray the molten alloy onto the railway surface. The combustion method mentioned refers to autogenous welding and the electric arc method refers to adding a voltage between two alloy thread and keeping them moving constantly at an angle. The alloy thread discharges and becomes melting at the point of intersection. The advantage of this invention is it is suitable on the outside, meanwhile low cost, short machining period, easy to carry away, safe operation and strong adhesion between the rail surface and worked coat.

Owner:裘国建

Cooling devices that use nanowires

ActiveUS7449776B2Thermoelectric device with peltier/seeback effectSemiconductor/solid-state device detailsNanowireHeat energy

Different types of cooling devices using nanowires are described. For example, a cooling device may include a plurality of diamond nanowires coupled to a surface. The diamond nanowires conduct heat energy from the surface and dissipate the heat energy into a neighboring fluid.

Owner:SAMSUNG ELECTRONICS CO LTD

Manufacturing method for surface type-P conductive diamond heat sink material

ActiveCN105331948AGood thermal conductivityGood mechanical strengthChemical vapor deposition coatingMicrowaveSurface roughness

The invention discloses a manufacturing method for a surface type-P conductive diamond heat sink material, and belongs to the technical field of diamond free-standing film application. A polished thick free-standing diamond film is adopted as a substrate, and a thin boron-doped diamond film with the type-P conductivity is deposited after microwave hydrogen plasma surface treatment is performed. Due to the fact that homoepitaxy growth is adopted, an epitaxial conductive layer and the substrate have the perfect attachment performance, and the interface resistance can be lowered to the minimum extent; and the microwave CVD technology is adopted for manufacturing the boron-doped diamond film, the thickness is controllable, the surface roughness is low, and the film conductivity is high. Hydrogen plasma is adopted in the middle for processing the surface of the substrate, atomic-size cleaning can be performed on the substrate, and epitaxial growth of the boron-doped diamond film is further facilitated through a formed hydrogen dangling bond. The surface type-P conductive diamond heat sink material can be used for the field of packaging of some high-power electronic devices needing heat sink material surface conduction.

Owner:UNIV OF SCI & TECH BEIJING

Preparation method for 3D-printed conductive hydrogel

InactiveCN108948379AImprove conductivityReduce complex cross-linking processCross-linkConductive polymer

The invention discloses a preparation method for a 3D-printed conductive hydrogel. The preparation method easily and efficiently realizes the conductivity of the hydrogel in two steps and effectivelyreduces the complex cross-linking process in direct preparation of a conductive hydrogel compound; a prepared hydrogel structure can be obtained through 3D printing, so the application scope of the structure is greatly broadened, and the problem of uneven mixing of a conductive filler in conventional methods is avoided; the method only realizes surface conduction, which is not only in accordance with requirements for conductivity in application but also allows the application of materials to be greatly saved; in addition, the obtained structure can achieve the purpose of multiple repairs to acertain extent; and the whole preparation method is simple and can be learned through simple training, so the method can be easily promoted to more people. The method of the invention can also be applied to the preparation of conductive polymers of other types, and is simple to operate, low in cost and suitable for large-scale industrial application.

Owner:郭秋泉

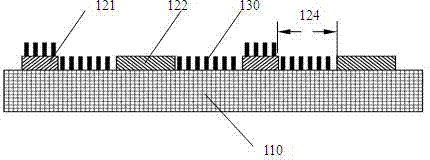

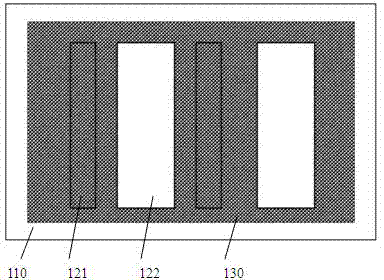

Surface conduction electron emission source based on oxide nanostructure and its manufacturing method

ActiveCN102262994ACathode ray tubes/electron beam tubesCold cathode manufactureHigh electronParticle physics

The invention discloses an oxide-nano-structure-based surface-conduction electron emission source and a manufacturing method thereof. The surface-conduction electron emission source comprises a glass substrate, cathodes and grids which are positioned on the surface of the glass substrate in parallel in a staggered way, and electron emission layers which are arranged on the surfaces of the cathodes and in gaps between the cathodes and the grids and have an oxide nano structure. In the oxide-nano-structure-based surface-conduction electron emission source, the high electron emission performanceof the electron emission layer having a planar field emission structure and the high electron emission performance of the electron emission layer having the oxide nano structure are combined effectively; the electron emission layers having the oxide nano structures form an oxide nano structure array; and the array is positioned on the surfaces of the cathodes and in the gaps between the cathodes and the grids. The electron emission layers having the oxide nano structures in the array can be used as an electron emission source and a surface electron conduction layer, and the electron emission current density is large and the electron emission efficiency is high; furthermore, the process is simple, the cost is low and the emission is stable and reliable.

Owner:FUZHOU UNIV

Heat dissipating assembly for a heat element

InactiveUS20060131010A1Effective temperatureIncrease brightnessSemiconductor/solid-state device detailsSolid-state devicesEngineeringHeat sink

The present invention provides a heat dissipating assembly for a heat element comprising a board on which at least a heat source, heat conductive layer and a heat dissipating sheet are set. The heat conductive layer is formed between the heat dissipating sheet and the board by squeeze bonding, thermal fusion or ultrasonic fusion. The heat conductive layer is made up of a material possessing the properties of quick heat conduction and compressive flexibility. While the heat conductive layer is adhered by squeeze bonding, thermal fusion or ultrasonic fusion, heat is conducted by its entire surface. The present invention is able to raise the heat dissipating efficacy and draw out the heat from the heat source quickly, therefore, increases the brightness and durability of the light source.

Owner:CLEVAGE ENTERPRISE